コンバータモジュールにおけるスイッチング損失の低減

【課題】スイッチング損失を低減した、DC入力電圧をDC出力電圧またはAC出力電圧に変換するコンバータを提供する。

【解決手段】コンバータは、入力端子101と出力端子103に電圧を供給するスイッチング素子104を備え、スイッチング素子104をオフしたとき、寄生インダクタンスLparasiticによって誘導されるエネルギをキャパシタC110に一時的に蓄えるために、ダイオードD110およびキャパシタC110の第1の直列回路110が設けられている。ダイオードD110は一方の入力端子101に結合され、並列に結合されている能動回路120によって、第1の直列回路110のキャパシタC110に一時的に蓄えられているエネルギを解放制御する。

【解決手段】コンバータは、入力端子101と出力端子103に電圧を供給するスイッチング素子104を備え、スイッチング素子104をオフしたとき、寄生インダクタンスLparasiticによって誘導されるエネルギをキャパシタC110に一時的に蓄えるために、ダイオードD110およびキャパシタC110の第1の直列回路110が設けられている。ダイオードD110は一方の入力端子101に結合され、並列に結合されている能動回路120によって、第1の直列回路110のキャパシタC110に一時的に蓄えられているエネルギを解放制御する。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、DC入力電圧をDC出力電圧またはAC出力電圧に変換するコンバータ回路に関する。詳細には、本発明は、DC入力電圧を変換して出力端子にDC出力電圧またはAC出力電圧を提供するコンバータにおいてスイッチング損失を低減することに関する。

【背景技術】

【0002】

最近、例えば発電装置におけるソーラーコンバータとして使用するための高効率の電力変換装置、あるいは高速電動機駆動装置、スイッチング電源装置、または無停電電源装置の電力変換装置として使用するための高効率の電力変換装置が、強く求められている。

【0003】

この目的には、スイッチングレギュレータを使用してDC入力電圧をDC出力電圧に変換する、またはDC入力電圧をAC出力電圧に変換することが知られている。

【0004】

スイッチングレギュレータにはさまざまな実施態様が存在するが、すべてのスイッチングレギュレータの共通点として、少なくとも1つのスイッチング素子を含んでいる。図13は、DC/DCスイッチングレギュレータの例を示しており、図14〜図16は、DC/ACスイッチングレギュレータの例を示している。

【0005】

図13を参照し、このDC/DCスイッチングレギュレータは、入力端子1301,1302を介して供給されるDC入力電圧を、より低いDC出力電圧に変換する。これを目的として、コントローラがスイッチング素子1304を制御して導通状態と非導通状態の間で切り替える。スイッチング素子1304をオンすると、入力端子1301から、負荷(例:RloadおよびLloadの直列回路)が接続されている出力端子1303に、電流が流れる。スイッチング素子1304をオフすると、スイッチング素子1304を介して供給される電流が遮断され、出力端子における電圧が中性点電圧まで低下する。

【0006】

図13においてインダクタLloadによって示したように、誘導性負荷の場合、スイッチング素子1304をオフすると、インダクタLloadによって電流が誘導され、ダイオード1305と、Rloadと、Lloadとを循環する。この誘導電流は、フリーホイーリング電流とも称され、フリーホイーリング電流を伝えるためのダイオードがフリーホイーリングダイオード1305として設けられている。

【0007】

図14は、2つの入力端子1401,1402を有するハーフブリッジコンバータを示しており、出力端子1403に高電圧と低電圧を交互に提供する。従来、第1の入力端子1401には正電圧が供給され、したがって正入力端子1401と称され、第2の入力端子1402には負電圧が供給され、したがって負入力端子1402と称される。

【0008】

出力にAC電流を提供する場合、このハーフブリッジコンバータは、2つのスイッチング素子1404,1405を利用し、出力端子1403に正電圧を供給する第1のスイッチング素子1404と、負電圧を供給する第2のスイッチング素子1405とを、交互にオンする。

【0009】

図14のハーフブリッジコンバータの2つのスイッチング素子それぞれは、誘導性負荷によって誘導されるフリーホイーリング電流を伝えるためのボディダイオードを含んでいる。特に、誘導性負荷の場合、第1のスイッチング素子1404または第2のスイッチング素子1405をオフすると、フリーホイーリング誘導電流がトリガーされ、相補スイッチング素子1405または1404のボディダイオードによって伝えられる。

【0010】

図15は、図14のハーフブリッジコンバータに似たDC/ACスイッチングレギュレータを示している。特に、このスイッチングレギュレータは、正入力端子1501と出力端子1503との間に結合された第1のスイッチング素子1504と、負入力端子1502と出力端子1503との間に結合された第2のスイッチング素子1505とを含んでいる。図15のスイッチングレギュレータは、これら第1のスイッチング素子1504と第2のスイッチング素子1505を交互にスイッチングすることによって、出力にAC電流を供給する。

【0011】

さらに、このDC/ACスイッチングレギュレータは、互いに逆向きに結合された2つのスイッチング素子の中性点回路1530を含んでおり、この中性点回路1530は、中性点端子1506の中性点電圧を断続的に出力端子1503に提供する。中性点回路1530の2つのスイッチング素子のうち、出力端子1503におけるプリチャージ状態(pre-charge state)に応じて適切な方をオンすると、出力端子1503から中性点端子1506に、またはその逆方向に電流が流れることができる。

【0012】

図15のDC/ACスイッチングレギュレータは、混合電圧NPC(中性点クランプ形)コンバータ(mixed voltage NPC converter)と称することもでき、なぜなら、スイッチング素子1504,1505には、全入力電圧(すなわち正入力端子1501の正電圧と負入力端子1502の負電圧の差)に耐える電圧定格が要求されるのに対して、直列回路1530のスイッチング素子には、この電圧定格の約半分のみが要求されるためである。

【0013】

次に図16を参照し、この図は、従来のNPCコンバータを示しており、正入力端子1601に接続されている第1のスイッチング素子1604と、負入力端子1602に接続されている第2のスイッチング素子1605とを備えている。これら第1および第2のスイッチング素子1604,1605によって、中性点端子1606に対する正電圧および負電圧を出力端子1603に提供することができる。

【0014】

このNPCコンバータにおいては、第1および第2のスイッチング素子1604,1605は、中性点回路(neutral circuit)1630を介して出力端子1603に結合されている。中性点回路1630は、特に、第1のスイッチング素子1604と出力端子1603との間に結合されている第3のスイッチング素子と、第2のスイッチング素子1605と出力端子1603との間に結合されている第4のスイッチング素子とを含んでいる。

【0015】

中性点回路1630の第3のスイッチング素子および第4のスイッチング素子がそれぞれの第1のスイッチング素子1604および第2のスイッチング素子1605を出力端子1603に接続しているため、コントローラは、第1のスイッチング素子と第3のスイッチング素子のスイッチオンを同時に制御しなければならず、第2のスイッチング素子と第4のスイッチング素子のスイッチオンを同時に制御しなければならない。詳細には、第1、第2、第3、および第4のスイッチング素子のスイッチングを制御するコントローラは、第1のスイッチング素子1604がオンである時間と少なくとも同じ時間だけ第3のスイッチング素子がオンのままであり、第2のスイッチング素子1605がオンである時間と少なくとも同じ時間だけ第4のスイッチング素子がオンのままであるように、構成されている。

【0016】

さらには、中性点回路1630によって出力端子1603に中性点電圧が提供されるように、第3および第4のスイッチング素子は、断続的にオンになる(それぞれの第1または第2のスイッチング素子がオフである)ように制御される。

【0017】

さらに詳細には、第1のスイッチング素子1604がオフのとき、中性点回路1630の第3のスイッチング素子をオンすると、中性点端子1606から、中性点回路1630のダイオードおよび第3のスイッチング素子を通って出力端子1603に、電流が流れることができる。同様に、第2のスイッチング素子1605がオフのとき、中性点回路1630の第4のスイッチング素子をオンすると、出力端子1603から、中性点回路1630のダイオードおよび第4のスイッチング素子を通って中性点端子1606に、電流が流れることができる。

【0018】

ここまでに説明したスイッチングレギュレータは、すべてにおいてスイッチング損失が発生し、以下ではこれについて説明する。スイッチングレギュレータにおいて、スイッチング損失は、ターンオン損失とターンオフ損失とに分類することができる。実際の条件下では、ターンオン損失は、スイッチング素子のパラメータ(例えばトランジスタのゲート充電損失)と、スイッチングレギュレータの寄生インダクタンスと、逆回復損失とに依存する。ターンオフ損失も、主としてスイッチング素子のパラメータおよび直列インダクタンスに依存するが、フリーホイーリング素子の順方向特性はほぼ無視できる。

【0019】

図13を参照して詳しく説明する。スイッチング素子1304をオンすると、第1の入力端子1301から寄生インダクタンスLparasiticおよびスイッチング素子1304を通って出力端子1303に電流が流れ始める。電流がスイッチング素子1304に流れるためには、スイッチング素子1304のゲート容量が充電されなければならず、結果としてゲート充電損失となる。これと同時に、フリーホイーリング素子1305(例:フリーホイーリングダイオード)では、遮断状態に回復するために相当な量の逆回復電荷が要求され、結果として逆回復損失となる。寄生インダクタンスLparasiticは電圧に対して電流を遅らせるため、スイッチング素子1304のスイッチオン速度は寄生インダクタンスによってマイナスの影響を受ける。

【0020】

さらには、寄生インダクタンスは逆回復損失にも影響する。ダイオードの逆回復時間は、順方向に電流が流れているダイオードにおいて、印加電圧が突然に逆方向になったときに遮断状態に回復するまでに要する時間として定義される。この逆回復時に、一時的な短絡の結果として大きな逆電流および大きな電力散逸が発生することがある。

【0021】

図13において、寄生インダクタンスによって電流の変化率が小さくなるため、フリーホイーリングダイオード1305は、より低いピーク電流においてリカバリすることができる。低いピーク電流に対応して、フリーホイーリングダイオードが遮断状態に回復するときのスイッチング素子1304のドレイン・ソース電圧の変化率dv/dtも小さい。したがって、ターンオン時の逆回復損失が減少する。

【0022】

スイッチング素子1304をオフするとき、ターンオフ損失は、主として、スイッチング素子1304を非導通状態に駆動する能力と、フリーホイーリング素子がオン状態に遷移する速度とに依存する。遷移時、電流がスイッチング素子1304とフリーホイーリング素子1305を流れ、ターンオフ損失につながる。さらには誘導性負荷によって、スイッチング素子1304に電流が流れるため、負荷の直列インダクタンスもターンオフ損失に寄与する。

【0023】

ターンオン損失およびターンオフ損失の上述した分析は、図13のスイッチングレギュレータ以外にもあてはまる。

【0024】

すべてのスイッチングレギュレータ(例えば図13〜図16に示したスイッチングレギュレータ)は、同じかまたは同様の影響を受ける。したがって、スイッチング損失を低減するための改良策が求められている。

【発明の概要】

【発明が解決しようとする課題】

【0025】

本発明の1つの目的は、DC電圧とDC電圧との間の変換、またはDC電圧とAC電圧との間の変換を行うスイッチングレギュレータの効率を改善することである。

【0026】

本発明の別の目的は、相補スイッチング段を有するスイッチングレギュレータにおける逆回復損失を低減することである。

【0027】

本発明のさらなる目的は、パワーモジュールの設計において寄生インダクタンスのマイナスの影響を低減することである。

【課題を解決するための手段】

【0028】

これらの目的の少なくとも1つは、独立請求項の主題によって解決される。本発明の有利な実施形態は、従属請求項の主題である。

【0029】

スイッチングレギュレータのスイッチング損失は、スイッチングレギュレータのパラメータおよび制御に依存するのみならず、周囲の回路の設計によっても影響される。例えば、あらゆるパワーエレクトロニクス回路に存在する寄生インダクタンスも、レギュレータのスイッチング損失に影響する。

【0030】

スイッチングレギュレータでは、ターンオン時には寄生インダクタンスがプラスに影響し、スイッチングレギュレータのターンオン損失が減少する。しかしながら、スイッチングレギュレータは、寄生インダクタンスのマイナスの影響も同様に受ける。したがって、本発明の第1の態様は、スイッチングレギュレータがマイナスの影響を受けることを防止する目的で、ターンオフ時に寄生インダクタンスによって誘導される電流の代替経路を提案することである。具体的には、スイッチングレギュレータをオンしたとき、寄生インダクタンスが磁界にエネルギを一時的に蓄える。寄生インダクタンスは、スイッチングレギュレータにおける逆回復損失の低減に寄与する。スイッチングレギュレータをオフすると、一時的に蓄えられたエネルギが寄生インダクタンスによってスイッチングレギュレータを流れ、スイッチングレギュレータのターンオフ損失が増大する。したがって、本発明によるスイッチングレギュレータは、寄生インダクタンスによって誘導されたエネルギを一時的に蓄えるための直列回路と、一時的に蓄えられているエネルギの解放を制御する能動回路であって、オプションとして、一時的に蓄えられているエネルギを入力に供給する能動回路、を採用し、結果として、スイッチングレギュレータの全体的な効率が向上する。

【0031】

本発明の別の態様は、多段スイッチングレギュレータ(multi-stage switching regulator)の変型形態として、インダクタ(またはオプションとして人工的に発生させる寄生インダクタンス)を有する複数の異なる段をデカップリングすることを提案する。スイッチングレギュレータのスイッチング段は、出力に所定の供給電圧を提供する。例えばDC/ACコンバータにおいて複数の電圧をスイッチングするためには、複数の異なるスイッチング段が要求される。この第2の態様によると、スイッチング段の1つをターンオンするときの交差導通損失(cross conduction loss)を防止するため、複数の異なるスイッチング段を、互いに誘導的にデカップリング(inductively decoupled)する。

【0032】

本発明のさらなる第3の態様は、スイッチングレギュレータの構成要素を、複数の異なるパワー基板(power substrate)上または複数の異なるパワーモジュールにグループ化することであって、1つのグループの構成要素間の誘導結合を最小にする一方で、異なるグループの構成要素間の誘導結合が許容されるようにグループ化することを提案する。誘導結合を利用することでスイッチングレギュレータの効率を改善することができ、あるいはインダクタを誘導結合に置き換えることでスイッチングレギュレータのコストを低減することができる。

【0033】

本発明の第2の態様および第3の態様による例示的な実施形態においては、多段スイッチングレギュレータにおける交差導通損失を防止するため、多段スイッチングレギュレータのスイッチング段が、複数の異なるパワー基板または複数の異なるパワーモジュールにグループ化され、異なるスイッチング段の間の誘導結合によって、複数の異なるスイッチング段が誘導的にデカップリングされる。

【0034】

本発明の一実施形態は、第1の入力端子および第2の入力端子を介して供給されるDC入力電圧を、出力端子におけるDC出力電圧に変換するDC/DCコンバータ、を提供する。このDC/DCコンバータは、寄生インダクタンスを有する。このDC/DCコンバータは、第1の入力端子または第2の入力端子の一方に接続されているスイッチング素子であって、出力端子に第1の電圧を供給する、スイッチング素子と、他方の入力端子と出力端子との間に結合されているフリーホイーリング素子であって、フリーホイーリング電流が出力端子に流れることができるようにする、フリーホイーリング素子と、を備えている。さらに、このDC/DCコンバータは、ダイオードおよびキャパシタの第1の直列回路を含んでおり、ダイオードは、一方の入力端子に結合されており、スイッチング素子をオフしたとき、寄生インダクタンスによって誘導されるエネルギをキャパシタに一時的に蓄えることができるようにする。さらに、このDC/DCコンバータは、第1の直列回路のダイオードに並列に結合されている能動回路であって、第1の直列回路のキャパシタからの一時的に蓄えられているエネルギの解放を制御する、能動回路、を含んでいる。

【0035】

例示的な一実施例においては、DC/DCコンバータの第1の直列回路は、第1の入力端子と第2の入力端子との間に結合されている、または、第1の入力端子と第3の入力端子との間に結合されており、第1の入力端子と第3の入力端子は同じ第1の電圧を供給する。

【0036】

さらに詳細な実施例においては、DC/DCコンバータの能動回路は、第1の直列回路のダイオードに並列に接続されているインダクタおよび抵抗の第2の直列回路、を備えている。この能動回路は、スイッチング素子をオンしたとき、第1の直列回路のキャパシタから、一時的に蓄えられているエネルギが解放されることを防止する。さらに、この能動回路は、スイッチング素子をオフしたとき、キャパシタの一時的に蓄えられているエネルギを、一時的に蓄えられているエネルギの少なくとも一部を抵抗に放散させることによって解放できるようにする。

【0037】

詳細な代替実施形態においては、DC/DCコンバータの能動回路は、第1の直列回路のダイオードとキャパシタとを相互接続しているノード、に接続されている第1の端子と、第1の入力端子に接続されている第2の端子と、を有する抵抗、を備えている。この能動回路は、スイッチング素子をオンしたとき、第1の直列回路のキャパシタから、一時的に蓄えられているエネルギが解放されることを防止する。さらに、この能動回路は、スイッチング素子をオフしたとき、キャパシタの一時的に蓄えられているエネルギを、一時的に蓄えられているエネルギの少なくとも一部を抵抗に放散させることによって解放できるようにする。

【0038】

別の詳細な実施形態においては、DC/DCコンバータの能動回路は、第1の直列回路のダイオードに並列に接続されている第1および第2の端子と、第2の入力端子に接続されている第3の端子と、を有する中間コンバータ、を備えている。この中間コンバータは、スイッチング素子をオンしたとき、第1の直列回路のキャパシタから、一時的に蓄えられているエネルギが解放されることを防止するように制御される。さらに、この中間コンバータは、スイッチング素子をオフしたとき、第1の直列回路のキャパシタの一時的に蓄えられているエネルギを、外部から供給されるDC入力電圧に基づいて変換し、変換されたエネルギを第1の入力端子に供給するように制御される。

【0039】

より詳細なさらなる実施形態においては、DC/DCコンバータの中間コンバータは、第1の入力端子に接続されているインダクタ、を含んでいる、または、中間コンバータは、高電圧要素を利用している。

【0040】

別の代替実施形態においては、DC/DCコンバータの能動回路は、第1の直列回路のダイオードとキャパシタとを相互接続しているノード、に接続されている第1の端子と、第1の入力端子に接続されている第2の端子と、第2の入力端子に接続されている第3の端子と、を有する中間コンバータ、を備えている。この中間コンバータは、スイッチング素子をオンしたとき、第1の直列回路のキャパシタから、一時的に蓄えられているエネルギが解放されることを防止するように制御される。さらに、この中間コンバータは、スイッチング素子をオフしたとき、第1の直列回路のキャパシタの一時的に蓄えられているエネルギを、外部から供給されるDC入力電圧に基づいて変換し、変換されたエネルギを第1の入力端子に供給するように制御される。

【0041】

本発明の別の実施形態は、正入力端子および負入力端子を介して正電圧および負電圧として供給されるDC入力電圧を、出力端子におけるAC出力電圧に変換するハーフブリッジコンバータ、を提供する。このハーフブリッジコンバータは、寄生インダクタンスを有する。このハーフブリッジコンバータは、正入力端子に接続されている第1のスイッチング素子であって、出力端子に正電圧を供給する、第1のスイッチング素子と、負入力端子に接続されている第2のスイッチング素子であって、出力端子に負電圧を供給する、第2のスイッチング素子と、を備えている。さらに、このハーフブリッジコンバータは、第1のダイオード、キャパシタ、および第2のダイオードの第1の直列回路、を備えている。第1の直列回路は、正入力端子と負入力端子との間に結合されており、第1のスイッチング素子をオフしたとき、第1のダイオードは、寄生インダクタンスによって誘導されるエネルギをキャパシタに一時的に蓄えることができるようにし、第2のスイッチング素子をオフしたとき、第2のダイオードは、この寄生インダクタンスまたは別の寄生インダクタンスによって誘導されるエネルギをキャパシタに一時的に蓄えることができるようにする。さらに、このハーフブリッジコンバータは、第1の直列回路に並列に結合されている能動回路であって、第1の直列回路のキャパシタからの、一時的に蓄えられているエネルギの解放、を制御する、能動回路、を備えている。

【0042】

例示的な一実施例においては、ハーフブリッジコンバータの能動回路は、第1の抵抗および第1のインダクタの第2の直列回路であって、第1の直列回路の第1のダイオードに並列に接続されている、第2の直列回路と、第2の抵抗および第2のインダクタの第3の直列回路であって、第1の直列回路の第2のダイオードに並列に接続されている、第3の直列回路と、を備えている。この能動回路は、第1または第2のスイッチング素子をオンしたとき、直列回路のキャパシタから、一時的に蓄えられているエネルギが解放されることを防止する。さらに、この能動回路は、第1または第2のスイッチング素子をオフしたとき、第1の直列回路のキャパシタの一時的に蓄えられているエネルギを、一時的に蓄えられているエネルギの少なくとも一部をそれぞれの第1または第2の抵抗に放散させることによって解放できるようにする。

【0043】

別の例示的な実施例においては、ハーフブリッジコンバータの能動回路は、第1の直列回路の第1のダイオードに並列に接続されている第1および第2の端子と、第1の直列回路の第2のダイオードに並列に接続されている第3および第4の端子と、を有する中間コンバータ、を備えている。この中間コンバータは、第1または第2のスイッチング素子をオンしたとき、第1の直列回路(510)のキャパシタから、一時的に蓄えられているエネルギが解放されることを防止するように制御される。さらに、この中間コンバータは、第1または第2のスイッチング素子をオフしたとき、第1の直列回路のキャパシタの一時的に蓄えられているエネルギを、外部から供給されるDC入力電圧に基づいて変換し、変換されたエネルギを第1または第2の入力端子に供給するように制御される。

【0044】

さらに詳細な実施例においては、ハーフブリッジコンバータは、第1のスイッチング素子と出力端子との間に結合されている第1のインダクタと、第2のスイッチング素子と出力端子との間に結合されている第2のインダクタと、を備えた出力回路、を含んでいる。さらに、このハーフブリッジコンバータは、第1のダイオードであって、そのカソードによって正入力端子に接続されており、そのアノードによって第1のノードに接続されており、第1のノードが第2のスイッチング素子と出力回路とを接続している、第1のダイオードと、第2のダイオードであって、そのアノードによって負入力端子に接続されており、そのカソードによって第2のノードに接続されており、第2のノードが第1のスイッチング素子と出力回路とを接続している、第2のダイオードと、を含んでいる。

【0045】

本発明のさらなる実施形態は、正入力端子および負入力端子を介して、中性点端子に対する正電圧および負電圧として供給されるDC入力電圧を、出力端子におけるAC出力電圧に変換する、中性点クランプ形(NPC)コンバータ、を提供することである。このNPCコンバータは、寄生インダクタンスを有する。このNPCコンバータは、正入力端子に接続されている第1のスイッチング素子であって、出力回路を介して出力端子に正電圧を供給する、第1のスイッチング素子と、負入力端子に接続されている第2のスイッチング素子であって、出力回路を介して出力端子に負電圧を供給する、第2のスイッチング素子と、を備えている。出力回路は、第1のスイッチング素子と出力端子との間に結合されている第1のインダクタと、第2のスイッチング素子と出力端子との間に結合されている第2のインダクタと、を備えている。このNPCコンバータは、中性点端子と出力回路との間に結合されている中性点スイッチング回路であって、出力端子に中性点電圧を供給する、中性点スイッチング回路、を備えている。さらに、このNPCコンバータは、第1のダイオードおよび第1のキャパシタの第1の直列回路であって、正入力端子と中性点端子との間に結合されており、第1のスイッチング素子をオフしたとき、第1のダイオードが、寄生インダクタンスによって誘導されるエネルギを第1のキャパシタに一時的に蓄えることができるようにする、第1の直列回路と、第2のダイオードおよび第2のキャパシタの第2の直列回路であって、負入力端子と中性点端子との間に結合されており、第2のスイッチング素子をオフしたとき、第2のダイオードが、同じ寄生インダクタンスまたは別の寄生インダクタンスによって誘導されるエネルギを第2のキャパシタに一時的に蓄えることができるようにする、第2の直列回路と、を備えている。さらに、このNPCコンバータは、第1の直列回路の第1のダイオードに並列に結合されている第1の能動回路であって、第1の直列回路の第1のキャパシタからの、一時的に蓄えられているエネルギの解放、を制御する、第1の能動回路と、第2の直列回路の第2のダイオードに並列に結合されている第2の能動回路であって、第2の直列回路の第2のキャパシタからの、一時的に蓄えられているエネルギの解放、を制御する、第2の能動回路と、を備えている。

【0046】

例示的な実施例においては、NPCコンバータの第1の能動回路が第3の直列回路を備えており、第2の能動回路が第4の直列回路を備えており、第3の直列回路および第4の直列回路のそれぞれが、抵抗およびインダクタを含んでおり、それぞれの第1の直列回路の第1のダイオード、または第2の直列回路の第2のダイオード、に並列に接続されている。第1または第2のスイッチング素子をオンしたとき、それぞれの第1または第2の能動回路は、それぞれの第1の直列回路の第1のキャパシタまたは第2の直列回路の第2のキャパシタから、一時的に蓄えられているエネルギが解放されることを防止する。第1または第2のスイッチング素子をオフしたとき、それぞれの第1または第2の能動回路は、それぞれの第1の直列回路の第1のキャパシタまたは第2の直列回路の第2のキャパシタの一時的に蓄えられているエネルギを、一時的に蓄えられているエネルギの少なくとも一部をそれぞれの抵抗に放散させることによって解放する。

【0047】

代替の一実施例においては、NPCコンバータの第1の能動回路が第1の中間コンバータを備えており、第2の能動回路が第2の中間コンバータを備えており、第1の中間コンバータおよび第2の中間コンバータの各々は、それぞれの第1の直列回路の第1のダイオードまたは第2の直列回路の第2のダイオードに並列に接続されている第1および第2の端子と、中性点端子に接続されている第3の端子と、を有する。第1または第2のスイッチング素子をオンしたとき、それぞれの第1または第2の中間コンバータは、それぞれの第1の直列回路の第1のキャパシタまたは第2の直列回路の第2のキャパシタから、一時的に蓄えられているエネルギが解放されることを防止するように制御される。さらに、第1または第2のスイッチング素子をオフしたとき、それぞれの第1または第2の中間コンバータは、それぞれの第1の直列回路の第1のキャパシタまたは第2の直列回路の第2のキャパシタの一時的に蓄えられているエネルギを、外部から供給されるDC入力電圧に基づいて変換し、変換されたエネルギをそれぞれの第1または第2の入力端子に供給するように制御される。

【0048】

さらに詳細な実施例においては、NPCコンバータは、正入力端子と第1のノードとの間に結合されている少なくとも1つの第1のダイオード、を備えた第1の回路であって、第2のスイッチング素子が第1のノードを通じて負電圧を出力回路に提供する、第1の回路、を備えている。少なくとも1つの第1のダイオードは、出力回路から正入力端子に電流が流れることができるようにする。さらに、NPCコンバータは、負入力端子と第2のノードとの間に結合されている少なくとも1つの第2のダイオード、を備えた第2の回路であって、第1のスイッチング素子が第2のノードを通じて正電圧を出力回路に提供する、第2の回路、を備えている。少なくとも1つの第2のダイオードは、負入力端子から出力回路に電流が流れることができるようにする。

【0049】

以下では、本発明を深く理解できるように、図面に示した実施形態に基づいて本発明について説明する。対応する要素には対応する参照数字および名称を使用してある。さらには、さまざまな実施形態において記載されている個々の特徴または特徴の組合せは、それ自体が個別の独創的な解決策となり得る。以下では、一例として図面を参照しながら、本発明について説明する。

【図面の簡単な説明】

【0050】

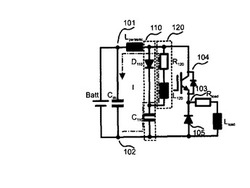

【図1】本発明の例示的な実施形態によるDC/DCコンバータの回路図を示している。

【図2】本発明の別の例示的な実施形態によるDC/DCコンバータの回路図を示している。

【図3】本発明のさらなる例示的な実施形態によるDC/DCコンバータの回路図を示している。

【図4】本発明のさらに別の例示的な実施形態によるDC/DCコンバータの回路図を示している。

【図5】本発明の例示的な実施形態によるハーフブリッジコンバータの回路図を示している。

【図6】本発明の別の例示的な実施形態によるハーフブリッジコンバータの回路図を示している。

【図7】本発明の例示的な実施形態による混合電圧NPCコンバータの回路図を示している。

【図8】本発明の別の例示的な実施形態による混合電圧NPCコンバータの回路図を示している。

【図9】本発明の別の例示的な実施形態によるNPCコンバータの回路図を示している。

【図10】本発明の例示的な実施形態による相補型スイッチングレギュレータの回路図を示している。

【図11】本発明の例示的な実施形態によるNPCコンバータのパワーモジュールの設計を示している。

【図12】本発明の例示的な実施形態による混合電圧NPCコンバータのパワーモジュールの設計を示している。

【図13】別の例示的な実施形態によるDC/DCコンバータの回路図を示している。

【図14】例示的な実施形態によるハーフブリッジコンバータの回路図を示している。

【図15】例示的な実施形態による混合電圧NPCコンバータのパワーモジュールを実施するための部分的な回路図を示している。

【図16】例示的な実施形態によるNPCコンバータのパワーモジュールを実施するための部分的な回路図を示している。

【図17】本発明の例示的な実施形態によるDC/DCコンバータの回路図を示している。

【図18】本発明の例示的な実施形態によるDC/DCコンバータの回路図を示している。

【発明を実施するための形態】

【0051】

図1を参照し、本発明の例示的な実施形態によるDC/DCコンバータの回路図を示している。この実施形態のDC/DCコンバータは、DC電圧からDC電圧に変換するために使用することができる。これを目的として、このDC/DCコンバータには、2つの入力端子101,102を介してDC入力電圧が供給される。

【0052】

図1に示した実施形態においては、キャパシタが結合されている電池が、第1の入力端子101と第2の入力端子102との間に接続されている。出力端子103に第1の電圧を供給するためのスイッチング素子104が、第1の入力端子101に接続されている。

【0053】

図1に示した例示的な実施形態においては、出力端子103に負荷が接続されており、この負荷は、抵抗RloadおよびインダクタLloadによって表してある。

【0054】

さらに、図1のDC/DCコンバータは、第2の入力端子102と出力端子103との間に結合されているフリーホイーリングダイオード105を含んでいる。誘導性負荷の場合(図1の例示的な実施形態ではインダクタLloadによって示してある)、スイッチング素子104をオフすると、誘導性負荷Lloadによってフリーホイーリング電流が誘導される。このフリーホイーリング電流は、フリーホイーリングダイオード105に流れる。図1に示した例示的な実施形態においては、フリーホイーリング電流は、フリーホイーリングダイオード105、抵抗Rload、およびインダクタLloadからなる導電ループに流れる。

【0055】

さらに図1に示したように、このDC/DCコンバータは、寄生インダクタLparasiticも含んでいる。寄生インダクタは、DC/DCコンバータの入力端子101の位置に示してある。しかしながら図示した寄生インダクタは、図1のDC/DCコンバータにおける寄生インダクタンスの存在を示しているにすぎない。したがって、図1のDC/DCコンバータの寄生インダクタは、特定の位置の電気回路要素(すなわちインダクタ)に対応するのではなく、さまざまな要因の結果として生じ、設計に固有であるものと想定することができる。

【0056】

例えば、図1のDC/DCコンバータにおいて、寄生インダクタンスは、主として、DC入力電圧源と入力端子101,102との間の接続の実施によって生じる。詳細には、DC/DCコンバータに電池を接続している配線およびねじ接点(screwed contact)が、寄生インダクタンスに主として寄与する。

【0057】

スイッチング素子104をオンすると、入力端子101と出力端子103との間に電流が流れ始める。図1のDC/DCコンバータの寄生インダクタンスの結果として、電圧に対して電流が遅れる。言い換えれば、寄生インダクタンスによって電流の変化率が小さくなり、したがって、図1のDC/DCコンバータにおけるターンオン損失の減少に有利に寄与する。

【0058】

しかしながら、寄生インダクタンスは、図1のDC/DCコンバータのターンオフ挙動にはマイナスの影響を及ぼす。具体的には、スイッチング素子104をオフすると、寄生インダクタンスの磁界に蓄えられているエネルギが解放される。寄生インダクタンスによってスイッチング素子104に電流が流れ、これによりスイッチング素子104がただちにターンオフすることが妨げられる。

【0059】

この点において、図1のDC/DCコンバータには、第1の入力端子101と第2の入力端子102との間に結合されている第1の直列回路110が設けられている。この第1の直列回路は、ダイオードD110およびキャパシタC110を備えている。ダイオードD110は、第1の入力端子101に接続されたアノード端子を有する。

【0060】

より詳細には、第1の直列回路110は、誘導電流のための追加の導電ループを提供する。具体的には、寄生インダクタンスLparasiticによって誘導される電流のAC成分は、寄生インダクタンスLparasiticと、ダイオードD110と、キャパシタC110と、入力端子101,102の間に接続された入力電源とを有するループを循環することができる。したがって、スイッチング素子104をオフしたとき、誘導電流をキャパシタC110に一時的に蓄えておくことができる。

【0061】

したがって、第1の直列回路110は、スイッチング素子104をオフしたとき、寄生インダクタンスによって誘導される電流が、図1のDC/DCコンバータのターンオフ損失に寄与することを防止する。

【0062】

図1に示した例示的な実施形態のDC/DCコンバータは、直列回路110のキャパシタC110に一時的に蓄えられているエネルギを変換する目的で、第1の直列回路110のダイオードD110に並列に結合されている能動回路120をさらに含んでいる。

【0063】

特に、能動回路120は、スイッチング素子104をオンしたときの寄生インダクタンスのプラスの影響が維持されるように、第1の直列回路110のキャパシタC110に一時的に蓄えられているエネルギの解放を制御する。

【0064】

図1のDC/DCコンバータにおいては、能動回路120は、インダクタL120および抵抗R120の直列回路を備えている。インダクタL120および抵抗R120の直列回路は、第1の直列回路110のダイオードD110に並列に接続されている。

【0065】

能動回路は、スイッチング素子104をオンしたとき、第1の直列回路110のキャパシタC110から、一時的に蓄えられているエネルギが解放されることを防止し、インダクタL120はこの効果に寄与する。これを目的として、インダクタL120の値は、DC/DCコンバータの寄生インダクタンスLparasiticの推定値または測定値に基づいて決定される。

【0066】

詳細には、スイッチング素子104をオンしたとき、キャパシタC110には、スイッチング素子104の前回のスイッチオフ動作からのエネルギが依然として蓄えられている。しかしながら、インダクタL120は、寄生インダクタンスLparasiticの作用と同じように、電流を遅らせる。したがって、インダクタL120および抵抗R120の能動回路120は、スイッチング素子104をオンしたとき、キャパシタC110からスイッチング素子104に流れる電流を、2つの入力端子101,102を介してスイッチング素子104に供給される電流よりもずっと小さい電流値に制限する。

【0067】

さらに、能動回路120は、スイッチング素子104をオフしたとき、キャパシタC110の一時的に蓄えられているエネルギの少なくとも一部を抵抗R120に放散させることによって、一時的に蓄えられているエネルギの解放を制御する。

【0068】

言い換えれば、スイッチング素子104をオフしたとき、キャパシタC110と、インダクタL120と、抵抗R120と、入力端子101,102の間に接続されたDC入力電圧源とを含んだ導電ループを、放電電流が流れ始める。この導電ループは、図1にはループIとして示してある。

【0069】

これによって、第1の直列回路110のキャパシタC110から、一時的に蓄えられているエネルギが解放され、図1のDC/DCコンバータの良好なターンオン挙動にマイナスの影響が及ばない。

【0070】

したがって、直列回路110と能動回路120とを組み合わせることによって、図1のDC/DCコンバータの寄生インダクタンスの影響として、スイッチング素子104をオフしたときのマイナスの影響なしに、スイッチング素子104をオンしたときのプラスの影響を保持することができる。

【0071】

次に図2を参照し、本発明の別の例示的な実施形態によるDC/DCコンバータを示している。図2のDC/DCコンバータは、図1のDC/DCコンバータがベースとなっており、対応する要素には対応する参照数字および名称を使用してある。簡潔さのため、対応する要素の詳しい説明は省く。

【0072】

図2のDC/DCコンバータと図1のDC/DCコンバータの異なる点は、能動回路220である。

【0073】

詳細には、図2のDC/DCコンバータも、第1の入力端子101と第2の入力端子102との間に結合されているダイオードD110およびキャパシタC110の第1の直列回路110を含んでいる。この第1の直列回路110のダイオードD110も、スイッチング素子104をオフしたときに寄生インダクタンスによって誘導されるエネルギをキャパシタC110に一時的に蓄えることができるようにする。

【0074】

キャパシタC110の一時的に蓄えられているエネルギを解放する目的で、図2のDC/DCコンバータには、抵抗R220を備えた能動回路220が設けられている。この能動回路220も、スイッチング素子104をオフしたとき、キャパシタC110の一時的に蓄えられているエネルギの少なくとも一部を抵抗R220に放散させることによって、一時的に蓄えられているエネルギの解放を制御する。

【0075】

外部抵抗R220を備えた能動回路220は、寄生インダクタンスによって誘導される、一時的に蓄えられるエネルギの量に基づいて設けることが有利である(例えば、外部取付け式のヒートシンクを設ける)。

【0076】

したがって、能動回路220は、抵抗R220を備えており、その第1の端子は、第1の直列回路110のダイオードD110とキャパシタC110とを相互接続しているノードに接続されており、第2の端子は、図2のDC/DCコンバータの第1の入力端子101に外部から接続されている。したがって、能動回路220は、図2のDC/DCコンバータのモジュールに組み込む必要はなく、モジュールに外部から取り付けることができる。

【0077】

さらには、図2のDC/DCコンバータの能動回路220は、第1の入力端子101に外部から接続されているため、図1のDC/DCコンバータと同様の寄生インダクタンスが生じる。

【0078】

したがって、抵抗R220の能動回路220は、スイッチング素子104をオンしたとき、キャパシタC110からスイッチング素子104に流れる電流を、2つの入力端子101,102を介してスイッチング素子104に供給される電流よりもずっと小さい電流値に制限する。

【0079】

したがって、直列回路110と能動回路220とを組み合わせることによって、図2のDC/DCコンバータの寄生インダクタンスの影響として、スイッチング素子104をオフしたときのマイナスの影響なしに、スイッチング素子104をオンしたときのプラスの影響を保持することができる。

【0080】

次に図3を参照し、本発明によるDC/DCコンバータの別の例示的な実施形態を示している。図3のDC/DCコンバータは、図1および図2のDC/DCコンバータがベースとなっている。対応する要素には対応する参照数字および名称を使用してあり、その要素については実施形態の説明から省いてある。

【0081】

図3に示したDC/DCコンバータの例示的な実施形態も、ダイオードD110およびキャパシタC110の第1の直列回路110を含んでいる。第1の直列回路110は、第1の入力端子101と第2の入力端子102との間に結合されている。

【0082】

スイッチング素子104をオフすると、DC/DCコンバータの中の寄生インダクタンスによって電流が誘導され、この電流を直列回路110のキャパシタC110に一時的に蓄えることができる。これを目的として、誘導電流はダイオードD110を通る。ダイオードD110のアノード端子は、DC/DCコンバータの第1の入力端子に接続されている。

【0083】

図3に示した特定の実施形態においては、能動回路320として中間DC/DCコンバータ320を利用している。中間DC/DCコンバータ320は、特に、その第1および第2の端子が第1の直列回路110のダイオードD110に並列に接続されており、第3の端子が第2の入力端子102に接続されている。中間DC/DCコンバータ320によって、第1の直列回路110のキャパシタの一時的に蓄えられているエネルギの解放を制御することができる。

【0084】

具体的には、スイッチング素子104をオンしたとき、第1の直列回路110のキャパシタC110から、一時的に蓄えられているエネルギが解放されることが防止されるように、中間DC/DCコンバータ320を制御することができる。スイッチング素子104をオンする前に、キャパシタC110の一時的に蓄えられているエネルギが解放されるように、中間DC/DCコンバータを制御することができる。

【0085】

この点において、スイッチング素子をオフしたとき、中間DC/DCコンバータ320が、キャパシタC110に一時的に蓄えられているエネルギからDC電圧への変換を開始することが有利である。

【0086】

一時的に蓄えられているエネルギを、外部から供給されるDC入力電圧に基づいて変換することによって、変換されたエネルギを第1の入力端子101に供給することができる。したがって、一時的に蓄えられているエネルギを回生することができ、このエネルギがDC/DCコンバータのスイッチング損失に寄与せず、したがってDC/DCコンバータの効率が向上する。

【0087】

中間DC/DCコンバータ320は、複数の異なる態様として実施することができる。

【0088】

第1の態様として、中間DC/DCコンバータ320をバックコンバータとして実施することができ、この場合、第1の端子が、入力端子として、第1の直列回路110のダイオードD110とキャパシタC110とを相互接続しているノードに接続されており、第2の端子が、出力端子として、第1の入力端子101に接続されており、第3の端子が、基準端子として、第2の入力端子102に接続されている。

【0089】

これに代えて、中間DC/DCコンバータ320をバックブーストコンバータとして実施することができ、この場合、第1の端子が、入力端子として、第1の直列回路110のダイオードD110とキャパシタC110とを相互接続しているノードに接続されており、第2の端子が、出力端子として、第2の入力端子102に接続されており、第3の端子が、基準端子として、第1の入力端子101に接続されている。

【0090】

さらには、中間DC/DCコンバータ320を、トランスをベースとする昇圧器として実施することができ、この場合、第1の端子が、第1の直列回路110のダイオードD110とキャパシタC110とを相互接続しているノードに接続されており、第2の端子が、出力端子として、第2の入力端子102に接続されており、第3の端子が、基準端子として、第1の入力端子101に接続されている。

【0091】

中間DC/DCコンバータの上述した2番目および3番目の実施態様においては、中間DC/DCコンバータは、入力端子と基準端子の間の低い入力電圧から、出力端子と基準端子の間の高い出力電圧に昇圧することが要求される。上述した最初の実施態様では、中間DC/DCコンバータは降圧コンバータとして動作する。

【0092】

次に図4を参照し、本発明によるDC/DCコンバータのさらなる例示的な実施形態を示している。図4のDC/DCコンバータの例示的な実施形態は、図3のDC/DCコンバータがベースとなっている。

【0093】

図4のDC/DCコンバータと図3のDC/DCコンバータの異なる点は、能動回路である。

【0094】

図4のDC/DCコンバータも、ダイオードD110およびキャパシタC110の第1の直列回路110を含んでいる。この第1の直列回路110は、第1の入力端子101と第2の入力端子102との間に結合されている。特に、ダイオードD110は、スイッチング素子104をオフしたとき、寄生インダクタンスによって誘導されるエネルギをキャパシタC110に一時的に蓄えることができるようにする。

【0095】

さらに、図4のDC/DCコンバータは、第1の直列回路のダイオードD110に並列に結合されている中間DC/DCコンバータ420を能動回路として含んでいる。この実施形態による中間DC/DCコンバータ420は、中に含まれている構成要素が原因で、DC/DCコンバータのモジュールまたはパワー基板上に組み込むことができないことがある。

【0096】

例えば、中間DC/DCコンバータをバックブーストコンバータとして実施するとき、必要なインダクタに起因して、図4のDC/DCコンバータと同じ基板上に組み込むことができないことがある。この点において、インダクタを個別に用意し、第1の入力端子101または第2の入力端子102に外部から接続することができる。

【0097】

図4のDC/DCコンバータの中間DC/DCコンバータは、その第1の端子が、第1の直列回路110のダイオードD110とキャパシタC110とを相互接続しているノードに接続されており、第2の端子が第1の入力端子101に外部から接続されており、第3の端子が第2の入力端子102に接続されている。

【0098】

これに代えて、図4のDC/DCコンバータの中間DC/DCコンバータを、個別のモジュールの中に設けて、第1の入力端子101と、第2の入力端子102と、第1の直列回路110のダイオードD110とキャパシタC110とを相互接続しているノードとに、外部から接続することができる。

【0099】

中間DC/DCコンバータ420は、図3に関連して説明したように、バックコンバータとして、またはバックブーストコンバータとして、または昇圧器を有するトランスとして、実施することができる。

【0100】

次に図5を参照し、本発明によるハーフブリッジコンバータの例示的な実施形態を示している。

【0101】

図5のハーフブリッジコンバータは、DC電圧をAC電圧に変換するために使用することができる。これを目的として、このハーフブリッジコンバータには、2つの入力端子501,502を介して正のDC電圧および負のDC電圧が供給され、出力端子503に正電圧または負電圧を供給する。

【0102】

さらに、このハーフブリッジコンバータは、正入力端子501に接続されている第1のスイッチング素子504と、負入力端子502に接続されている第2のスイッチング素子505とを含んでいる。

【0103】

このハーフブリッジコンバータは、出力端子503に正の半波および負の半波を連続的に供給するため、第1のスイッチング素子504および第2のスイッチング素子505を交互にオンするように構成されている。

【0104】

言い換えれば、第1のスイッチング素子504をオンすることによって、出力端子503に正電圧を供給することができ、第2のスイッチング素子505をオンすることによって、出力端子503に負電圧を供給することができる。

【0105】

第1および第2のスイッチング素子504,505それぞれは、誘導性負荷の場合にフリーホイーリング電流を流すことのできるボディダイオードを含んでいる。

【0106】

例えば、第1のスイッチング素子504をオフすると、誘導性負荷Lloadの結果として、第2のスイッチング素子505のボディダイオードにフリーホイーリング電流が流れる。同様に、第2のスイッチング素子505をオフすると、誘導性負荷の結果として、第1のスイッチング素子504のボディダイオードにフリーホイーリング電流が流れる。

【0107】

さらには、図5に示したように、このハーフブリッジコンバータも、寄生インダクタLparasiticを含んでいる。第1の寄生インダクタは、図5のハーフブリッジコンバータの正入力端子501の位置に示してあり、第2の寄生インダクタは、ハーフブリッジコンバータの負入力端子502の位置に示してある。

【0108】

しかしながら、図示した寄生インダクタは、図1に関連してすでに説明したように、図5のハーフブリッジコンバータにおける寄生インダクタンスの存在を示しているにすぎない。したがって、図5に示した寄生インダクタは、電気回路要素(すなわちインダクタ)に対応するのではなく、さまざまな要因の結果として生じ、設計に固有であるものと想定することができる。

【0109】

スイッチング素子504をオンすると、正入力端子501と出力端子503との間に電流が流れ始める。図5のハーフブリッジコンバータにおける寄生インダクタンスの結果として、電圧に対して電流が遅れる。これは、図5のハーフブリッジコンバータのスイッチング素子505をオンしたときも同様である。言い換えれば、寄生インダクタンスは、電流の変化率を小さくし、図5のハーフブリッジコンバータにおけるターンオン損失の減少に有利に寄与する。

【0110】

しかしながら、寄生インダクタンスは、図5のハーフブリッジコンバータのターンオフ挙動にはマイナスの影響を及ぼす。具体的には、スイッチング素子504をオフすると、寄生インダクタンスの磁界に蓄えられているエネルギが解放される。したがって寄生インダクタンスによってスイッチング素子504に電流が流れ、これによりスイッチング素子504のターンオフが妨げられる。同様に、スイッチング素子505をオフすると、寄生インダクタンスによってスイッチング素子505に電流が流れ、これによりスイッチング素子505がただちにターンオフすることが妨げられる。

【0111】

寄生インダクタンスによってスイッチング素子504,505のターンオフが妨げられることを回避する目的で、図5のハーフブリッジコンバータには、正入力端子501と負入力端子502との間に結合された第1の直列回路510が設けられている。

【0112】

第1の直列回路510は、第1のダイオードD511と、キャパシタC510と、第2のダイオードD512とを備えている。第1のダイオードD511は、そのアノード端子が正入力端子501に接続されており、第2のダイオードD512は、そのカソード端子が負入力端子502に接続されている。

【0113】

正入力端子501と負入力端子502との間に結合された第1の直列回路510が設けられていることによって、第1のスイッチング素子504をオフしたとき、正の誘導電流をキャパシタC510に一時的に蓄えることができ、第2のスイッチング素子505をオフしたとき、負の誘導電流をキャパシタC510に一時的に蓄えることができる。

【0114】

したがって、第1の直列回路510は、スイッチング素子504,505をオフしたときに寄生インダクタンスによって誘導される電流が、図5のハーフブリッジコンバータのターンオフ損失に寄与することを防止する。

【0115】

さらに、図5のハーフブリッジコンバータは、第1の直列回路510の第1のダイオードD511に並列に結合されている能動回路と、第2のダイオードD512に並列に結合されている能動回路を含んでいる。能動回路521,522は、スイッチング素子504またはスイッチング素子505をオンしたときの寄生インダクタンスのプラスの影響が維持されるように、第1の直列回路のキャパシタC510の一時的に蓄えられているエネルギの解放を制御することができる。

【0116】

図5のハーフブリッジコンバータにおいては、能動回路521および能動回路522は、それぞれ、インダクタL521および抵抗R521を有する直列回路と、インダクタL522および抵抗R522を有する直列回路を備えている。以下では、第1の直列回路510との混同を避ける目的で、インダクタL521および抵抗R521の直列回路を第2の直列回路521と称し、インダクタL522および抵抗R522の直列回路を第3の直列回路522と称する。

【0117】

第2の直列回路521は、第1の直列回路510の第1のダイオードD511に並列に接続されている。第3の直列回路522は、第1の直列回路510の第2のダイオードD512に並列に接続されている。

【0118】

能動回路521,522は、第1のスイッチング素子504または第2のスイッチング素子505をオンしたとき、第1の直列回路510のキャパシタC510から一時的に蓄えられているエネルギが解放されることを防止し、インダクタL521およびL522はこの効果に寄与する。これを目的として、インダクタL521およびL522の値は、図5のハーフブリッジコンバータの寄生インダクタンスの推定値または測定値に基づいて決定される。

【0119】

さらに詳細には、インダクタL521およびL522は、図5のハーフブリッジコンバータの寄生インダクタンスの作用と同様に電流を遅らせるため、能動回路521,522は、対応するスイッチング素子504,505をオンしたとき、キャパシタC510からスイッチング素子504,505に流れる電流を、それぞれの正入力端子501または負入力端子502を介してスイッチング素子504,505に供給される電流よりもずっと小さい電流値に制限する。

【0120】

さらに、能動回路521,522は、対応するスイッチング素子504,505をオフしたとき、キャパシタC510の一時的に蓄えられているエネルギの少なくとも一部をそれぞれの抵抗R521またはR522に放散させることによって、一時的に蓄えられているエネルギの解放を制御する。

【0121】

言い換えれば、スイッチング素子504またはスイッチング素子505のいずれかをオフすると、キャパシタC510からそれぞれの第2の直列回路521または第3の直列回路522に電流が流れ始め、したがって、対応する抵抗R521またはR522によって、キャパシタC510の一時的に蓄えられているエネルギの少なくとも一部が放散する。

【0122】

したがって、第1の直列回路510のキャパシタC510から、一時的に蓄えられているエネルギが解放され、図5のハーフブリッジコンバータの良好なターンオン挙動にマイナスの影響が及ばない。

【0123】

したがって、第1の直列回路510と能動回路521,522とを組み合わせることによって、図5のハーフブリッジコンバータの寄生インダクタンスの影響として、スイッチング素子504,505をオフしたときのマイナスの影響なしに、スイッチング素子504,505をオンしたときのプラスの影響を保持することができる。

【0124】

次に図6を参照し、本発明の別の例示的な実施形態によるハーフブリッジコンバータを示している。図6のハーフブリッジコンバータは、図5のハーフブリッジコンバータがベースとなっており、対応する要素には対応する参照数字および名称を使用してある。簡潔さのため、対応する要素の詳しい説明は省く。

【0125】

図6のハーフブリッジコンバータと図5のハーフブリッジコンバータの異なる点は、能動回路620である。

【0126】

詳細には、図6のハーフブリッジコンバータも、正入力端子501と負入力端子502との間に結合されている第1のダイオードD511、キャパシタC510、および第2のダイオードD512を含んだ第1の直列回路510を含んでいる。第1の直列回路のダイオードD511およびダイオードD512は、スイッチング素子504またはスイッチング素子505のいずれかをオフしたとき、寄生インダクタンスによって誘導されるエネルギをキャパシタC510に一時的に蓄えることができるようにする。

【0127】

キャパシタC510から一時的に蓄えられているエネルギを解放するため、図6のハーフブリッジコンバータには、中間DC/DCコンバータを備えた能動回路620が設けられている。

【0128】

図6のハーフブリッジコンバータの中間DC/DCコンバータ620は、第1の直列回路510の第1のダイオードD511に並列に接続されている第1および第2の端子と、第1の直列回路510の第2のダイオードD512に並列に接続されている第3および第4の端子と、を備えている。

【0129】

図3の中間DC/DCコンバータ320に関連して説明したように、第1の直列回路510のキャパシタC510からの蓄えられているエネルギを昇圧または降圧する目的には、DC/DCコンバータの一般に公知の実施態様を使用することができる。一般に公知の中間DC/DCコンバータの例は、バックコンバータ、バックブーストコンバータ、またはトランスをベースとする昇圧回路である。

【0130】

第1のスイッチング素子504または第2のスイッチング素子505をオンしたとき、第1の直列回路510のキャパシタC510から、一時的に蓄えられているエネルギが解放されることを防止するように、図6の中間DC/DCコンバータ620を制御することができる。

【0131】

これは、第1のスイッチング素子504をオンしたとき、第1の端子と第2の端子との間に電流が流れることを防止するように中間DC/DCコンバータ620を制御し、第2のスイッチング素子505をオンしたとき、第3の端子と第4の端子との間に電流が流れることを防止するように中間DC/DCコンバータ620を制御することによって、達成することができる。

【0132】

さらには、第1のスイッチング素子504または第2のスイッチング素子505をオフしたとき、第1の直列回路510のキャパシタC510の一時的に蓄えられているエネルギを、外部から供給されるDC入力電圧に基づいて変換し、変換されたエネルギをそれぞれの第1の入力端子501または第2の入力端子502に供給するように、中間DC/DCコンバータ620を制御することができる。

【0133】

言い換えれば、中間DC/DCコンバータ620の第1の端子と第2の端子との間に正電圧が検出されたとき、含まれているエネルギを、正入力端子501および負入力端子502を介して供給されるDC入力電圧にに基づいて変換し、変換されたエネルギを、中間DC/DCコンバータ620の第1および第3の端子を介して、正入力端子501および負入力端子502に供給するように、中間DC/DCコンバータ620を制御することができる。

【0134】

同様に、中間DC/DCコンバータ620の第3の端子と第4の端子との間に負電圧が検出されたとき、含まれているエネルギをDC入力電圧に基づいて変換し、変換されたエネルギを、中間DC/DCコンバータ620の第1および第3の端子を介して、正入力端子501および負入力端子502に供給するように、中間DC/DCコンバータ620を制御することができる。

【0135】

これによって、中間DC/DCコンバータは、キャパシタC510の蓄えられているエネルギを回生することができ、図6のハーフブリッジコンバータの全体的な効率の増大に寄与する。

【0136】

さらには、本発明によるハーフブリッジコンバータは、図5および図6に示した実施形態に制限されない。

【0137】

図5のハーフブリッジコンバータは、図2の実施形態と同様に修正改良することもでき、抵抗を外部から取り付けることができるようにする目的で、能動回路521および能動回路522に代えて、第1の直列回路510のダイオードD511とキャパシタC510とを相互接続しているノードに接続されている第1の端子と、正入力端子501に接続されている第2の端子と、を有する抵抗を備えた能動回路と、第1の直列回路510のダイオードD512とキャパシタC510とを相互接続しているノードに接続されている第1の端子と、負入力端子502に接続されている第2の端子と、を有するもう1つの抵抗を備えた能動回路と、に置き換える。

【0138】

さらに、図6のハーフブリッジコンバータは、図4の実施形態と同様に修正改良することもでき、ダイオードD511とキャパシタC510とを相互に接続している第1のノードに接続されている第1の端子と、第1の直列回路510のダイオードD512とキャパシタC510とを相互に接続している第2のノードに接続されている第2の端子と、正入力端子501に接続されている第3の端子と、負入力端子502に接続されている第4の端子と、を有する中間DC/DCコンバータ、を設ける。これによって、中間DC/DCコンバータに含まれている構成要素の少なくとも一部を外部から接続することができる。

【0139】

次に図7を参照し、本発明の例示的な実施形態による混合電圧NPC(MNPC)コンバータを示している。この実施形態の混合電圧NPCコンバータは、DC電圧をAC電圧に変換するため使用することができる。

【0140】

これを目的として、図7のMNPCコンバータは、正入力端子701および負入力端子702を介してDC正電圧およびDC負電圧が供給され、出力端子703に正電圧または負電圧を供給する。さらに、図7のMNPCコンバータは、正電圧および負電圧の間の中性点電圧を出力端子703に供給するための中性点端子706を含んでいる。

【0141】

図7のMNPCコンバータは、正入力端子701に接続されている第1のスイッチング素子704であって、出力回路730を介して出力端子703に正電圧を供給する第1のスイッチング素子704、を備えている。さらに、図7のMNPCコンバータは、負入力端子702に接続されている第2のスイッチング素子705であって、出力回路730を介して出力端子703に負電圧を供給する第2のスイッチング素子705を備えている。

【0142】

図7のMNPCコンバータの出力回路730は、第1のスイッチング素子704と出力端子703との間に結合されている第1のインダクタと、第2のスイッチング素子705と出力端子703との間に結合されている第2のインダクタとを備えている。この点において、第1のスイッチング素子704は、第1のインダクタを介して出力端子に結合されており、第2のスイッチング素子705は、第2のインダクタを介して出力端子703に結合されている。

【0143】

さらに、図7のMNPCコンバータは、中性点端子706と出力回路730との間に結合されている中性点スイッチング回路740であって、出力端子703に中性点電圧を供給する中性点スイッチング回路740、を含んでいる。中性点スイッチング回路740は、ダイオードおよびトランジスタの2つの相補直列回路によって実施することができる。第1の相補直列回路は、第1のスイッチング素子704をオフした後に出力回路730に中性点電圧を供給できるようにし、第2の相補直列回路は、第2のスイッチング素子705をオフした後に出力回路730に中性点電圧を供給できるようにする。

【0144】

さらに、図7のMNPCコンバータも、寄生インダクタLparasiticを含んでいる。寄生インダクタは、入力端子701、入力端子702、および入力端子706の位置に示してある。しかしながら、これらの寄生インダクタは、図7のMNPCコンバータにおける寄生インダクタンスの存在を示しているにすぎない。したがって、図7のMNPCコンバータの寄生インダクタは、電気回路要素(すなわちインダクタ)に対応するのではなく、さまざまな要因の結果として生じ、設計に固有であるものと想定することができる。

【0145】

第1のスイッチング素子704をオンすると、正入力端子701と出力端子703との間に電流が流れ始める。図7のMNPCコンバータの寄生インダクタンスの結果として、電圧に対して電流が遅れる。同様に、スイッチング素子705をオンすると、負入力端子702と出力端子703との間に電流が流れ始める。図7のMNPCコンバータの寄生インダクタンスの結果として、電圧に対して電流が遅れる。言い換えれば、寄生インダクタンスによって電流の変化率が小さくなり、したがって、図7のMNPCコンバータにおけるターンオン損失の減少に寄与する。

【0146】

しかしながら、図7のMNPCコンバータの寄生インダクタンスは、MNPCコンバータのターンオフ挙動にはマイナスの影響を及ぼす。

【0147】

特に、第1のスイッチング素子704または第2のスイッチング素子705のいずれかをオフすると、寄生インダクタンスの磁界に含まれているエネルギが解放される。

【0148】

したがって、寄生インダクタンスによって、それぞれの第1のスイッチング素子704または第2のスイッチング素子705に電流が流れ、これによりスイッチング素子がただちにターンオフすることが妨げられる。

【0149】

この点において、図7のMNPCコンバータには、正入力端子701と中性点端子706との間に結合されている第1のスイッチング直列回路711と、負入力端子702と中性点端子706との間に結合されている第2のスイッチング直列回路712とが設けられている。第1の直列回路711は、ダイオードD711とキャパシタC711とを備えている。ダイオードD711は、アノード端子が正入力端子701に接続されている。第2の直列回路712は、ダイオードD712とキャパシタC712とを備えている。ダイオードD712は、カソードが負入力端子702に接続されている。

【0150】

より詳細には、第1の直列回路711は追加の導電ループを提供し、寄生インダクタンスLparasiticによって誘導される電流は、寄生インダクタンスLparasiticと、ダイオードD711と、キャパシタC711と、入力端子701と入力端子706との間のDC入力電圧源とを含んだループを循環することができる。第2の直列回路712も導電ループを提供し、寄生インダクタンスLparasiticによって誘導される電流は、寄生インダクタンスLparasiticと、ダイオードD712と、キャパシタC712と、入力端子702と入力端子706との間のDC入力電源とを含んだループを循環することができる。

【0151】

したがって、スイッチング素子704をオフしたとき、誘導電流をキャパシタC711に一時的に蓄えることができ、スイッチング素子705をオフしたとき、誘導電流をキャパシタC712に一時的に蓄えることができる。

【0152】

したがって、第1の直列回路711および第2の直列回路712は、それぞれのスイッチング素子704,705をオフしたとき、寄生インダクタンスによって誘導される電流が図7のMNPCコンバータのターンオフ損失に寄与することを防止する。

【0153】

さらに、図7のMNPCコンバータは、直列回路711のキャパシタC711および第2の直列回路712のキャパシタC712の、一時的に蓄えられているエネルギを変換する目的で、第1の直列回路711のダイオードD711に並列に結合されている能動回路721と、第2の直列回路712のダイオードD712に並列に結合されている能動回路722とをさらに含んでいる。

【0154】

能動回路721および能動回路722は、特に、それぞれの第1のスイッチング素子704または第2のスイッチング素子705をオンしたときの寄生インダクタンスのプラスの影響が維持されるように、対応する第1のキャパシタC711または第2のキャパシタC712の一時的に蓄えられているエネルギの解放を制御することができる。

【0155】

図7のMNPCコンバータにおいて、第1の能動回路721は、インダクタL721と抵抗R721を備えている。このインダクタL721と抵抗R721の直列回路は、第1の直列回路711のダイオードD711に並列に接続されている。第2の能動回路722も、インダクタL722と抵抗R722の直列回路を備えている。このインダクタL722と抵抗R722の直列回路は、第2の直列回路712のダイオードD712に並列に接続されている。

【0156】

能動回路721および能動回路722は、それぞれのスイッチング素子704またはスイッチング素子705をオンしたときにそれぞれのキャパシタC711またはC712から一時的に蓄えられているエネルギが解放されることを防止し、インダクタL721およびインダクタL722はこの効果に寄与する。これを目的として、インダクタL721およびインダクタL722それぞれの値は、図7のMNPCコンバータの寄生インダクタンスの推定値または測定値に基づいて決定される。

【0157】

さらに詳細には、インダクタL721およびインダクタL722は、寄生インダクタンスの作用と同様に電流を遅らせるため、能動回路721および能動回路722それぞれは、それぞれのキャパシタC711,C712から対応するスイッチング素子704,705に流れる電流を制限し、スイッチング素子704およびスイッチング素子705には、それぞれをオンしたときに対応する正入力端子701または負入力端子702を介してそれぞれのスイッチング素子704またはスイッチング素子705に供給される電流よりもずっと小さい放電電流が流れるのみである。

【0158】

さらに、能動回路721および能動回路722は、対応するスイッチング素子704または705をオフしたとき、それぞれのキャパシタC711またはC712の一時的に蓄えられているエネルギの少なくとも一部をそれぞれの抵抗R721またはR722に放散させることによって、一時的に蓄えられているエネルギの解放を制御する。

【0159】

言い換えれば、スイッチング素子704をオフすると、キャパシタC711と、インダクタL721と、抵抗R721と、入力端子701,706の間に接続されたDC入力電圧源とを含んだ導電ループを、放電電流が流れ始める。同様に、スイッチング素子705をオフすると、キャパシタC712と、インダクタL722と、抵抗R722と、入力端子702と入力端子706の間に接続されたDC入力電圧源とを含んだ導電ループを、放電電流が流れ始める。

【0160】

これによって、第1の直列回路711のキャパシタC711と、第2の直列回路712のキャパシタC712から、一時的に蓄えられているエネルギが解放され、図7のMNPCコンバータの良好なターンオン挙動にマイナスの影響が及ばない。

【0161】

したがって、第1の直列回路711と第1の能動回路721の組合せと、第2の直列回路712と第2の能動回路722の組合せとによって、図7のMNPCコンバータの寄生インダクタンスの影響として、スイッチング素子704または705をオフしたときのマイナスの影響なしに、スイッチング素子704または705をオンしたときのプラスの影響を保持することができる。

【0162】

次に図8を参照し、本発明の別の例示的な実施形態によるMNPCコンバータを示している。図8のMNPCコンバータは、図7のMNPCコンバータがベースとなっており、対応する要素には対応する参照数字および名称を使用してある。簡潔さのため、対応する要素の詳しい説明は省く。

【0163】

図8のMNPCコンバータと図7のMNPCコンバータの異なる点は、第1および第2の能動回路821,822である。

【0164】

詳細には、図8のMNPCコンバータも、正入力端子701と中性点端子706との間に結合されているダイオードおよびキャパシタを有する第1の直列回路711と、負入力端子702と中性点端子706との間に結合されているダイオードおよびキャパシタを有する第2の直列回路712と、を含んでいる。

【0165】

第1の直列回路711のダイオードD711は、スイッチング素子704をオフしたとき、寄生インダクタンスによって誘導されるエネルギをキャパシタC711に一時的に蓄えることができるようにする。同様に、第2の直列回路712のダイオードD712は、スイッチング素子705をオフしたとき、寄生インダクタンスによって誘導されるエネルギをキャパシタC712に一時的に蓄えることができるようにする。

【0166】

キャパシタC711またはC712の一時的に蓄えられているエネルギを解放するため、図8のMNPCコンバータには、第1および第2の中間DC/DCコンバータ821,822が設けられており、これらの中間DC/DCコンバータは、それぞれの第1の直列回路711の第1のキャパシタC711または第2の直列回路712の第2のキャパシタC712の一時的に蓄えられているエネルギの解放を制御する。

【0167】

より詳細には、第1の中間DC/DCコンバータ821は、第1の直列回路711のダイオードD711に並列に接続されている第1および第2の端子と、中性点端子706に接続されている第3の端子とを含んでいる。第2の中間DC/DCコンバータ822は、第2の直列回路712のダイオードD712に並列に接続されている第1および第2の端子と、中性点端子706に接続されている第3の端子とを含んでいる。

【0168】

第1の中間DC/DCコンバータ821および第2の中間DC/DCコンバータ822は、それぞれの第1または第2のスイッチング素子704,705をオンしたとき、それぞれの第1の直列回路711の第1のキャパシタC711または第2の直列回路712の第2のキャパシタC712から、一時的に蓄えられているエネルギが解放されることを防止するように、制御することができる。

【0169】

言い換えれば、第1のスイッチング素子704をオンしたとき、第1の端子と第2の端子との間にエネルギが流れることを防止するように、第1の中間DC/DCコンバータ821を制御することができる。さらに、第2のスイッチング素子705をオンしたとき、第1の端子と第2の端子との間に電流が流れることを防止するように、第2の中間DC/DCコンバータ822を制御することができる。

【0170】

さらに、第1の中間DC/DCコンバータ821および第2の中間DC/DCコンバータ822は、それぞれの第1または第2のスイッチング素子704,705をオフしたとき、それぞれの第1の直列回路711の第1のキャパシタC711または第2の直列回路712の第2のキャパシタC712の一時的に蓄えられているエネルギを、外部から供給されるDC入力電圧に基づいて変換し、変換されたエネルギを、それぞれの正入力端子701または負入力端子702に供給するように、制御することができる。

【0171】

さらに詳細には、第1のスイッチング素子704をオフしたとき、第1の中間DC/DCコンバータ821が第1の入力端子と第2の入力端子との間の電圧を検出した時点で、正入力端子701と中性点端子706との間の電圧に対応して、含まれているエネルギを昇圧または降圧し、変換されたエネルギを正入力端子701に供給するように、第1の中間DC/DCコンバータ821を制御することができる。

【0172】

同様に、第2のスイッチング素子705をオフしたとき、第1の入力端子と第2の入力端子との間の電圧を検出した時点で、負入力端子702と中性点端子706との間の電圧に対応してエネルギを変換し、変換されたエネルギを負入力端子702に供給するように、第2の中間DC/DCコンバータ822を制御することができる。

【0173】

したがって、図8のMNPCコンバータでは、キャパシタC711およびキャパシタC712の蓄えられているエネルギを中間DC/DCコンバータによって回生することができ、MNPCコンバータ回路の全体的な効率が増大する。

【0174】

したがって、直列回路711と能動回路821の組合せと、直列回路712と能動回路822の組合せとによって、それぞれのスイッチング素子704または705をオフしたとき、蓄えられているエネルギが回生される一方で、それぞれのスイッチング素子704または705をオンしたときの図8のMNPCコンバータの寄生インダクタンスのプラスの影響を保持することができる。

【0175】

さらには、本発明によるMNPCコンバータは、図7または図8に示した実施形態に制限されず、図2および図4に関連して説明した利点が達成されるように、能動回路721,722,821,822の配置構造を容易に修正改良することができる。

【0176】

次に図9を参照し、本発明の例示的な実施形態によるNPCコンバータの回路図を示している。図9のNPCコンバータは、図7のNPCコンバータがベースとなっており、対応する要素には対応する参照数字および名称を使用してある。簡潔さのため、対応する要素の詳しい説明は省く。

【0177】

特に、図9のNPCコンバータと図7のNPCコンバータの異なる点は、中性点端子706と出力回路730との間に結合されており出力端子703に中性点電圧を供給する中性点スイッチング回路940である。

【0178】

図9のNPCコンバータの中性点スイッチング回路940は、本発明の背景技術の中ですでに説明した図16の回路に極めて似ている。したがって、簡潔さのためこの回路の詳細な説明は省く。

【0179】

図9から理解できるように、このNPCコンバータも、第1の直列回路711と第1の能動回路721の組合せと、第2の直列回路712と第2の能動回路722の組合せとを含んでおり、これによって、図9のNPCコンバータの寄生インダクタンスの影響として、それぞれのスイッチング素子704または705をオフしたときのマイナスの影響なしに、スイッチング素子704または705をオンしたときのプラスの影響を保持することができる。

【0180】

次に図10を参照し、本発明によるハーフブリッジコンバータの例示的な実施形態を示している。この実施形態によるハーフブリッジコンバータは、DC電圧をAC電圧に変換するために使用することができる。これを目的として、図10のハーフブリッジコンバータには、正入力端子501および負入力端子502を介してDC入力電圧が供給される。

【0181】

図10のハーフブリッジコンバータは、正入力端子501に接続されている第1のスイッチング素子504であって、出力回路1030を介して出力端子503に正の入力電圧を供給する第1のスイッチング素子504、を含んでいる。さらに、図10のハーフブリッジコンバータは、負入力端子502に接続されている第2のスイッチング素子505であって、出力回路1030を介して出力端子503に負の入力電圧を供給する第2のスイッチング素子505、を含んでいる。第1のスイッチング素子504および第2のスイッチング素子505のそれぞれは、誘導性負荷の場合にフリーホイーリング電流を流すことのできるボディダイオードを含んでいる。

【0182】

出力回路1030は、第1のスイッチング素子504と出力端子との間に結合されている第1のインダクタと、第2のスイッチング素子505と出力端子との間に結合されている第2のインダクタとを含んでいる。

【0183】

言い換えれば、スイッチング素子504をオンすると、正入力端子501と、第1のスイッチング素子504と、出力回路1030の第1のインダクタと、出力端子503との間に電流が流れる。さらに、スイッチング素子505をオンすると、負入力端子502と、第2のスイッチング素子505と、出力回路1030の第2のインダクタと、出力端子503との間に電流が流れる。

【0184】

図10のハーフブリッジコンバータでは、第1のダイオードD1は、そのカソード端子が第1の入力端子501に接続されており、アノード端子が、第2のスイッチング素子505と出力回路1030の第2のインダクタとを相互接続しているノードに接続されている。第2のダイオードD2は、そのアノード端子が第2の入力端子502に接続されており、カソード端子が、第1のスイッチング素子504と出力回路1030の第1のインダクタとを相互に接続している別のノードに接続されている。

【0185】

したがって、第1のスイッチング素子504と第2のスイッチング素子505は、第1の入力端子501と第2の入力端子502との間の異なる導電経路上に設けられている。第1のスイッチング素子504の導電経路と第2のスイッチング素子505の導電経路は、出力回路を介して互いにデカップリングされている。

【0186】

したがって、図10のハーフブリッジコンバータでは、スイッチング電流が第1のスイッチング素子504と第2のスイッチング素子505とに流れることが防止され、すなわちこの回路では、第1のスイッチング素子504または第2のスイッチング素子505のいずれか一方がターンオンするときの交差導通が排除されている。これは以下のように説明される。

【0187】

いま、仮想の交差導通電流を想定すると、図10のハーフブリッジコンバータにおいては、この交差導通電流は、第1のスイッチング素子504、出力回路1030の第1のインダクタ、出力回路1030の第2のインダクタ、および第2のスイッチング素子505を、またはこの逆方向に、流れなければならない。しかしながら、出力回路1030の第1および第2のインダクタによって、電圧に対して電流が遅れるため、スイッチング素子504またはスイッチング素子505のボディダイオードのリカバリが、低誘導性で結合されているダイオードD1およびD2と比較して遅れる。したがって、第1のスイッチング素子504または第2のスイッチング素子505をオンしたとき、相補的な第1または第2のスイッチング素子504,505のボディダイオードは、逆回復電流を流さない。

【0188】

言い換えれば、図10のハーフブリッジコンバータの第1のスイッチング素子504と第2のスイッチング素子505をデカップリングすることによって、第1または第2のスイッチング素子504,505をオンしたとき、相補的な第1または第2のスイッチング素子504,505のボディダイオードから、それぞれのダイオードD1またはD2に、逆回復電流をシフトさせることが可能であり、これにより、相補的な第1または第2のスイッチング素子504,505が一時的にターンオンすることが防止される(一時的なターンオンは、相補的な第1または第2のスイッチング素子504,505のゲート・コレクタ容量またはゲート・ドレイン容量への容量性電圧パルス(capacitive voltage pulse)によってトリガーされることがある)。

【0189】

別の代替実施形態によると、図10のハーフブリッジコンバータを修正改良し、第1および第2のインダクタを含んだ出力回路1030を、代替の出力構造として、接続の結果として寄生インダクタンスが生じる構造に置き換える。例えば、第1および第2のスイッチング素子504,505と出力端子503との間の接続を、ねじ接続として実施することによって、第1のスイッチング素子504と第2のスイッチング素子505とが誘導的にデカップリングされる。

【0190】

図10のハーフブリッジコンバータの例示的な実施形態をさらに修正して、ハーフブリッジコンバータのターンオン損失を低減することができる。第1のスイッチング素子504および第2のスイッチング素子505に含まれているボディダイオードよりも順方向電圧降下が大きいように、それぞれのダイオードD1およびダイオードD2を選択することによって、ターンオフ時にこれらのダイオードはアクティブである。したがって、フリーホイーリング電流は、それぞれの第1および第2のスイッチング素子504,505のボディダイオードに流れる。

【0191】

しかしながら、(用途によっては)異なる順方向電圧降下のダイオードを選択することによって達成できる電圧差は、誘導されるフリーホイーリング電流によって生じる電位差と比較して小さいことがあるため、フリーホイーリング電流が第1または第2のスイッチング素子504,505のボディダイオードのみを流れ、ダイオードD1およびダイオードD2を流れない状態となるまで時間がかかる。

【0192】

次に図11および図12を参照し、これらの図は、図8および図9のNPCコンバータの例示的な実施態様を示している。

【0193】

パワーモジュールを設計するときは、一般的な方法として、回路における誘導結合を最小にする。これは例えば、回路構成要素間の距離が最小になるように幾何学的配置を適合させたり、形成されるハードウェアモジュールやパワー基板の数ができる限り少なくなるように回路の分割を調節する、あるいは発生しうる寄生インダクタンスができる限り小さくなるようなハードウェア要素間の相互接続(例えば、セラミック層における銅配線、モジュール/パワー基板間の同軸ケーブル、モジュール/パワー基板間のツイストペアケーブル)を利用することによる。

【0194】

これとは異なり、図11および図12に示したように、図8および図9のNPCコンバータのいずれか一方の実施態様では、モジュールを設計するとき、構成要素間の距離が最適ではないことによる寄生インダクタンスや、複数の異なるパワーモジュールまたはパワー基板上への回路構成要素のグループ化、あるいは高インダクタンスの相互接続の使用を、意図的に利用している。例えば、大きな電流が流れる接続(すなわち、ねじ接点接続)では、高い誘導結合が生じる。

【0195】

図11および図12に示したように、図8および図9のNPCコンバータのいずれか一方の実施態様では、複数の異なるパワー基板上または複数の異なるパワーモジュールに構成要素を配置する必要がある。この場合、回路の性能にプラスに影響する位置に「寄生」インダクタンスが発生するように、構成要素を配置することが可能である。

【0196】

さらに詳細には、図11のNPCコンバータの実施態様では、第1のスイッチング素子704がグループ1152に配置されており、第2のスイッチング素子705がグループ1151に配置されている。この図11のNPCコンバータの実施態様では、グループ1151およびグループ1152は、異なるパワー基板または異なるパワーモジュールに対応する。

【0197】

具体的には、グループ1151は、構成要素として、ダイオードD11,D12と、トランジスタT941と、第2のスイッチング素子705と、ダイオードD941とを備えている。グループ1152は、構成要素として、ダイオードD21,D22と、トランジスタT942と、第1のスイッチング素子704と、ダイオードD942とを備えている。グループ1151およびグループ1152のそれぞれにおいて、含まれている構成要素間の誘導結合は最小である。

【0198】

グループ1151およびグループ1152それぞれの外側の構成要素との接続については、誘導結合を最小にする必要はない。例えば、2つのグループ1151およびグループ1152の間での構成要素の接続では、インダクタンスが発生してよい。

【0199】

第1の直列回路711および第2の直列回路712は、それぞれ対応する第2のグループ1152および第1のグループ1151に接続されることが特に重要である。第1および第2の直列回路711,712の第1および第2のキャパシタC711,C712と、対応する第2または第1の構成要素グループ1152,1151との誘導結合を最小にすることによって、キャパシタC711,C712に一時的に蓄えられるエネルギの量が増大し、したがって、図11のNPCコンバータの効率が向上する。したがって、第1および第2のキャパシタC711,C712と、対応する第2または第1の構成要素グループ1152,1151との接続は、低誘導性として行うべきであり、あるいは、第1または第2の直列回路711,712を、対応する第2または第1の構成要素グループ1152,1151に組み込まなければならない。

【0200】

さらには、図12のMNPCコンバータの実施態様では、第1のスイッチング素子704がグループ1252に配置されており、第2のスイッチング素子705がグループ1251に配置されている。この図12のMNPCコンバータの実施態様では、グループ1251およびグループ1252は、異なるパワー基板または異なるパワーモジュールに対応する。

【0201】

具体的には、グループ1251は、構成要素として、ダイオードD1と、トランジスタT741と、第2のスイッチング素子705と、ダイオードD741とを備えている。グループ1252は、構成要素として、ダイオードD2と、トランジスタT742と、第1のスイッチング素子704と、ダイオードD742とを備えている。グループ1251およびグループ1252のそれぞれにおいて、含まれている構成要素間の誘導結合は最小である。

【0202】

グループ1251およびグループ1252それぞれの外側の構成要素との接続については、誘導結合を最小にする必要はない。例えば、2つのグループ1251およびグループ1252の間での構成要素の接続では、インダクタンスが発生してよい。

【0203】

第1の直列回路711および第2の直列回路712は、それぞれ対応する第2のグループ1252および第1のグループ1251に接続されることが特に重要である。第1および第2の直列回路711,712の第1および第2のキャパシタC711,C712と、対応する第2または第1の構成要素グループ1252,1251との誘導結合を最小にすることによって、キャパシタC711,C712に一時的に蓄えられるエネルギの量が増大し、したがって、図12のNPCコンバータの効率が向上する。

【0204】

したがって、第1および第2のキャパシタC711,C712と、対応する第2または第1の構成要素グループ1152,1151との接続は、低誘導性として行うべきであり、あるいは、第1および第2の直列回路711,712を、それぞれ対応する第2または第1の構成要素グループ1252,1251に組み込まなければならない。

【0205】

次に図17を参照し、本発明によるDC/DCコンバータの代替実施形態を示している。図17のDC/DCコンバータは、図2のDC/DCコンバータがベースとなっており、対応する要素には対応する参照数字および名称を使用してある。簡潔さのため、対応する要素の詳しい説明は省く。

【0206】

図17のDC/DCコンバータは、図2のDC/DCコンバータと異なる点として、スイッチング素子1705が第2の入力端子102に結合されており、出力端子103に低電圧を供給し、フリーホイーリングダイオード1704が第1の入力端子101と出力端子103との間に結合されている。図17の例示的な実施形態においてインダクタLloadによって示したように、誘導性負荷の場合、スイッチング素子1705をオフすると、誘導性負荷Lloadによってフリーホイーリング電流が誘導される。このフリーホイーリング電流は、フリーホイーリングダイオード1704によって流れる。

【0207】

さらに、図17のDC/DCコンバータは、アクティブインダクタ(電圧源およびインダクタLloadの直列回路によって表してある)に接続されている。

【0208】

さらに、このDC/DCコンバータは、図2を参照しながら説明したものと同じ直列回路110および同じ能動回路220を含んでおり、直列回路110と能動回路220の組合せによって、図17のDC/DCコンバータの寄生インダクタンスの影響として、スイッチング素子1705をオフしたときのマイナスの影響なしに、スイッチング素子1705をオンしたときのプラスの影響を保持することができる。

【0209】

別の実施形態によると、このDC/DCコンバータの回路を、DC/DC昇圧器として、またはアクティブPFC昇圧器として利用することができる。これを目的として、端子103と、端子102または101の一方とを、第1および第2の入力端子として使用し、他方の端子101または102を出力端子として使用する。したがって、図17のDC/DCコンバータを、電池の充電に使用することができる。

【0210】

次に図18を参照し、本発明によるDC/DCコンバータの代替実施形態を示している。図18のDC/DCコンバータは、DC/DCコンバータとDC入力電圧源(例:電池)との異なる接続方法を示している。

【0211】

図18のDC/DCコンバータは、図2のDC/DCコンバータがベースとなっており、対応する要素には対応する参照数字および名称を使用してある。簡潔さのため、対応する要素の詳しい説明は省く。

【0212】

図18のDC/DCコンバータと図2のDC/DCコンバータの異なる点は、第1の直列回路である。

【0213】

詳細には、図18のDC/DCコンバータも、ダイオードD1810とキャパシタC1810の第1の直列回路1810を含んでいる。この第1の直列回路1810は、第1の入力端子101と第3の入力端子1807との間に接続されている。第1の入力端子101と第3の入力端子1807は、DC/DCコンバータに同じ電圧を供給する。第1の入力端子101と第3の入力端子1807は、いずれもDC電源の正端子に接続されており、第2の入力端子102はDC電源の負端子に接続されている。

【0214】

第1の入力端子101と第3の入力端子1807は、導入される誘導結合の大きさが異なる。第1の入力端子101は、高い誘導結合を伴ってDC電源の正端子に接続されており、第3の入力端子1807は、低い誘導結合を伴ってDC電源の正端子に接続されている。

【0215】

図18の実施形態において、異なる誘導結合は、異なる接続の結果である。第1の入力端子101を介しての接続は、例えば、誘導電流が大きいねじ接続として実施することができる。第1の入力端子を介しての接続によって、寄生インダクタンスLparasiticが発生する。第3の入力端子1807を介しての接続は、例えば、低誘導性であり小さい電流が流れる同軸ケーブルまたはツイストペアケーブルとして実施することができる。

【0216】

例として図18の実施形態において、このDC/DCコンバータは第4の入力端子1808を含んでおり、この入力端子1808は、フリーホイーリング素子105が接続される第2の入力端子102と同じ電圧を供給する。第4の入力端子1808によって、第3の入力端子1807の接続に対する相補接続が提供され、この入力端子は、低誘導性であり小さい逆電流が流れる同軸ケーブルまたはツイストペアケーブルの第2のワイヤとして実施することができる。

【0217】

スイッチング素子104をオンすると、第1の入力端子101と出力端子103との間に電流が流れ始める。図18のDC/DCコンバータの寄生インダクタンスLparasiticによって、電圧に対して電流が遅れる。言い換えれば、寄生インダクタンスによって電流の変化率が小さくなり、したがって、図18のDC/DCコンバータにおけるターンオン損失の減少に有利に寄与する。

【0218】

図18のDC/DCコンバータの第1の直列回路1810により、寄生インダクタンスLparasiticによって誘導された電流は、寄生インダクタンスLparasiticと、ダイオードD1810と、キャパシタC1810と、第1および第3の入力端子101,1807とを含んだループを循環することができる。したがって、スイッチング素子104をオフしたとき、誘導電流の少なくとも一部をキャパシタC1810に一時的に蓄えることができる。

【0219】

さらに、図18のDC/DCコンバータは、ダイオードD1810に並列に結合されている能動回路220を含んでいる。能動回路220は、スイッチング素子104をオンしたときの寄生インダクタンスのプラスの影響が維持されるように、第1の直列回路1810のキャパシタC1810の一時的に蓄えられているエネルギの解放を制御する。

【0220】

特に、能動回路220は、スイッチング素子104をオンしたときの寄生インダクタンスのプラスの影響が維持されるように、第1の直列回路1810のキャパシタC1810の一時的に蓄えられているエネルギの解放を制御する。

【0221】

図18のDC/DCコンバータにおいては、能動回路220は抵抗R220を備えている。抵抗R220は、第1の入力端子101および第3の入力端子1807を介して、第1の直列回路1810のダイオードD1810に並列に接続されている。さらに、抵抗R220は、キャパシタC1810に並列に接続されている。能動回路220の抵抗R220と、第1の直列回路1810のキャパシタC1810とが並列に接続されていることによって、スイッチング素子104をオフしたとき、寄生インダクタンスLparasiticの誘導電流のエネルギの少なくとも一部を抵抗R220に放散させることができる。さらに、キャパシタC1810の一時的に蓄えられているエネルギの少なくとも一部を、キャパシタC1810と抵抗R220とを含んだ導電ループに電流が流れることによって放散させることができる。

【0222】

これによって、第1の直列回路1810のキャパシタC1810から、一時的に蓄えられているエネルギが解放され、図18のDC/DCコンバータの良好なターンオン挙動にマイナスの影響が及ばない。

【0223】

したがって、直列回路1810と能動回路220の組合せによって、図18のDC/DCコンバータの寄生インダクタンスの影響として、スイッチング素子104をオフしたときのマイナスの影響なしに、スイッチング素子104をオンしたときのプラスの影響を保持することができる。

【技術分野】

【0001】

本発明は、DC入力電圧をDC出力電圧またはAC出力電圧に変換するコンバータ回路に関する。詳細には、本発明は、DC入力電圧を変換して出力端子にDC出力電圧またはAC出力電圧を提供するコンバータにおいてスイッチング損失を低減することに関する。

【背景技術】

【0002】

最近、例えば発電装置におけるソーラーコンバータとして使用するための高効率の電力変換装置、あるいは高速電動機駆動装置、スイッチング電源装置、または無停電電源装置の電力変換装置として使用するための高効率の電力変換装置が、強く求められている。

【0003】

この目的には、スイッチングレギュレータを使用してDC入力電圧をDC出力電圧に変換する、またはDC入力電圧をAC出力電圧に変換することが知られている。

【0004】

スイッチングレギュレータにはさまざまな実施態様が存在するが、すべてのスイッチングレギュレータの共通点として、少なくとも1つのスイッチング素子を含んでいる。図13は、DC/DCスイッチングレギュレータの例を示しており、図14〜図16は、DC/ACスイッチングレギュレータの例を示している。

【0005】

図13を参照し、このDC/DCスイッチングレギュレータは、入力端子1301,1302を介して供給されるDC入力電圧を、より低いDC出力電圧に変換する。これを目的として、コントローラがスイッチング素子1304を制御して導通状態と非導通状態の間で切り替える。スイッチング素子1304をオンすると、入力端子1301から、負荷(例:RloadおよびLloadの直列回路)が接続されている出力端子1303に、電流が流れる。スイッチング素子1304をオフすると、スイッチング素子1304を介して供給される電流が遮断され、出力端子における電圧が中性点電圧まで低下する。

【0006】

図13においてインダクタLloadによって示したように、誘導性負荷の場合、スイッチング素子1304をオフすると、インダクタLloadによって電流が誘導され、ダイオード1305と、Rloadと、Lloadとを循環する。この誘導電流は、フリーホイーリング電流とも称され、フリーホイーリング電流を伝えるためのダイオードがフリーホイーリングダイオード1305として設けられている。

【0007】

図14は、2つの入力端子1401,1402を有するハーフブリッジコンバータを示しており、出力端子1403に高電圧と低電圧を交互に提供する。従来、第1の入力端子1401には正電圧が供給され、したがって正入力端子1401と称され、第2の入力端子1402には負電圧が供給され、したがって負入力端子1402と称される。

【0008】

出力にAC電流を提供する場合、このハーフブリッジコンバータは、2つのスイッチング素子1404,1405を利用し、出力端子1403に正電圧を供給する第1のスイッチング素子1404と、負電圧を供給する第2のスイッチング素子1405とを、交互にオンする。

【0009】

図14のハーフブリッジコンバータの2つのスイッチング素子それぞれは、誘導性負荷によって誘導されるフリーホイーリング電流を伝えるためのボディダイオードを含んでいる。特に、誘導性負荷の場合、第1のスイッチング素子1404または第2のスイッチング素子1405をオフすると、フリーホイーリング誘導電流がトリガーされ、相補スイッチング素子1405または1404のボディダイオードによって伝えられる。

【0010】

図15は、図14のハーフブリッジコンバータに似たDC/ACスイッチングレギュレータを示している。特に、このスイッチングレギュレータは、正入力端子1501と出力端子1503との間に結合された第1のスイッチング素子1504と、負入力端子1502と出力端子1503との間に結合された第2のスイッチング素子1505とを含んでいる。図15のスイッチングレギュレータは、これら第1のスイッチング素子1504と第2のスイッチング素子1505を交互にスイッチングすることによって、出力にAC電流を供給する。

【0011】

さらに、このDC/ACスイッチングレギュレータは、互いに逆向きに結合された2つのスイッチング素子の中性点回路1530を含んでおり、この中性点回路1530は、中性点端子1506の中性点電圧を断続的に出力端子1503に提供する。中性点回路1530の2つのスイッチング素子のうち、出力端子1503におけるプリチャージ状態(pre-charge state)に応じて適切な方をオンすると、出力端子1503から中性点端子1506に、またはその逆方向に電流が流れることができる。

【0012】

図15のDC/ACスイッチングレギュレータは、混合電圧NPC(中性点クランプ形)コンバータ(mixed voltage NPC converter)と称することもでき、なぜなら、スイッチング素子1504,1505には、全入力電圧(すなわち正入力端子1501の正電圧と負入力端子1502の負電圧の差)に耐える電圧定格が要求されるのに対して、直列回路1530のスイッチング素子には、この電圧定格の約半分のみが要求されるためである。

【0013】

次に図16を参照し、この図は、従来のNPCコンバータを示しており、正入力端子1601に接続されている第1のスイッチング素子1604と、負入力端子1602に接続されている第2のスイッチング素子1605とを備えている。これら第1および第2のスイッチング素子1604,1605によって、中性点端子1606に対する正電圧および負電圧を出力端子1603に提供することができる。

【0014】

このNPCコンバータにおいては、第1および第2のスイッチング素子1604,1605は、中性点回路(neutral circuit)1630を介して出力端子1603に結合されている。中性点回路1630は、特に、第1のスイッチング素子1604と出力端子1603との間に結合されている第3のスイッチング素子と、第2のスイッチング素子1605と出力端子1603との間に結合されている第4のスイッチング素子とを含んでいる。

【0015】

中性点回路1630の第3のスイッチング素子および第4のスイッチング素子がそれぞれの第1のスイッチング素子1604および第2のスイッチング素子1605を出力端子1603に接続しているため、コントローラは、第1のスイッチング素子と第3のスイッチング素子のスイッチオンを同時に制御しなければならず、第2のスイッチング素子と第4のスイッチング素子のスイッチオンを同時に制御しなければならない。詳細には、第1、第2、第3、および第4のスイッチング素子のスイッチングを制御するコントローラは、第1のスイッチング素子1604がオンである時間と少なくとも同じ時間だけ第3のスイッチング素子がオンのままであり、第2のスイッチング素子1605がオンである時間と少なくとも同じ時間だけ第4のスイッチング素子がオンのままであるように、構成されている。

【0016】

さらには、中性点回路1630によって出力端子1603に中性点電圧が提供されるように、第3および第4のスイッチング素子は、断続的にオンになる(それぞれの第1または第2のスイッチング素子がオフである)ように制御される。

【0017】

さらに詳細には、第1のスイッチング素子1604がオフのとき、中性点回路1630の第3のスイッチング素子をオンすると、中性点端子1606から、中性点回路1630のダイオードおよび第3のスイッチング素子を通って出力端子1603に、電流が流れることができる。同様に、第2のスイッチング素子1605がオフのとき、中性点回路1630の第4のスイッチング素子をオンすると、出力端子1603から、中性点回路1630のダイオードおよび第4のスイッチング素子を通って中性点端子1606に、電流が流れることができる。

【0018】

ここまでに説明したスイッチングレギュレータは、すべてにおいてスイッチング損失が発生し、以下ではこれについて説明する。スイッチングレギュレータにおいて、スイッチング損失は、ターンオン損失とターンオフ損失とに分類することができる。実際の条件下では、ターンオン損失は、スイッチング素子のパラメータ(例えばトランジスタのゲート充電損失)と、スイッチングレギュレータの寄生インダクタンスと、逆回復損失とに依存する。ターンオフ損失も、主としてスイッチング素子のパラメータおよび直列インダクタンスに依存するが、フリーホイーリング素子の順方向特性はほぼ無視できる。

【0019】

図13を参照して詳しく説明する。スイッチング素子1304をオンすると、第1の入力端子1301から寄生インダクタンスLparasiticおよびスイッチング素子1304を通って出力端子1303に電流が流れ始める。電流がスイッチング素子1304に流れるためには、スイッチング素子1304のゲート容量が充電されなければならず、結果としてゲート充電損失となる。これと同時に、フリーホイーリング素子1305(例:フリーホイーリングダイオード)では、遮断状態に回復するために相当な量の逆回復電荷が要求され、結果として逆回復損失となる。寄生インダクタンスLparasiticは電圧に対して電流を遅らせるため、スイッチング素子1304のスイッチオン速度は寄生インダクタンスによってマイナスの影響を受ける。

【0020】

さらには、寄生インダクタンスは逆回復損失にも影響する。ダイオードの逆回復時間は、順方向に電流が流れているダイオードにおいて、印加電圧が突然に逆方向になったときに遮断状態に回復するまでに要する時間として定義される。この逆回復時に、一時的な短絡の結果として大きな逆電流および大きな電力散逸が発生することがある。

【0021】

図13において、寄生インダクタンスによって電流の変化率が小さくなるため、フリーホイーリングダイオード1305は、より低いピーク電流においてリカバリすることができる。低いピーク電流に対応して、フリーホイーリングダイオードが遮断状態に回復するときのスイッチング素子1304のドレイン・ソース電圧の変化率dv/dtも小さい。したがって、ターンオン時の逆回復損失が減少する。

【0022】

スイッチング素子1304をオフするとき、ターンオフ損失は、主として、スイッチング素子1304を非導通状態に駆動する能力と、フリーホイーリング素子がオン状態に遷移する速度とに依存する。遷移時、電流がスイッチング素子1304とフリーホイーリング素子1305を流れ、ターンオフ損失につながる。さらには誘導性負荷によって、スイッチング素子1304に電流が流れるため、負荷の直列インダクタンスもターンオフ損失に寄与する。

【0023】

ターンオン損失およびターンオフ損失の上述した分析は、図13のスイッチングレギュレータ以外にもあてはまる。

【0024】

すべてのスイッチングレギュレータ(例えば図13〜図16に示したスイッチングレギュレータ)は、同じかまたは同様の影響を受ける。したがって、スイッチング損失を低減するための改良策が求められている。

【発明の概要】

【発明が解決しようとする課題】

【0025】

本発明の1つの目的は、DC電圧とDC電圧との間の変換、またはDC電圧とAC電圧との間の変換を行うスイッチングレギュレータの効率を改善することである。

【0026】

本発明の別の目的は、相補スイッチング段を有するスイッチングレギュレータにおける逆回復損失を低減することである。

【0027】

本発明のさらなる目的は、パワーモジュールの設計において寄生インダクタンスのマイナスの影響を低減することである。

【課題を解決するための手段】

【0028】

これらの目的の少なくとも1つは、独立請求項の主題によって解決される。本発明の有利な実施形態は、従属請求項の主題である。

【0029】

スイッチングレギュレータのスイッチング損失は、スイッチングレギュレータのパラメータおよび制御に依存するのみならず、周囲の回路の設計によっても影響される。例えば、あらゆるパワーエレクトロニクス回路に存在する寄生インダクタンスも、レギュレータのスイッチング損失に影響する。

【0030】

スイッチングレギュレータでは、ターンオン時には寄生インダクタンスがプラスに影響し、スイッチングレギュレータのターンオン損失が減少する。しかしながら、スイッチングレギュレータは、寄生インダクタンスのマイナスの影響も同様に受ける。したがって、本発明の第1の態様は、スイッチングレギュレータがマイナスの影響を受けることを防止する目的で、ターンオフ時に寄生インダクタンスによって誘導される電流の代替経路を提案することである。具体的には、スイッチングレギュレータをオンしたとき、寄生インダクタンスが磁界にエネルギを一時的に蓄える。寄生インダクタンスは、スイッチングレギュレータにおける逆回復損失の低減に寄与する。スイッチングレギュレータをオフすると、一時的に蓄えられたエネルギが寄生インダクタンスによってスイッチングレギュレータを流れ、スイッチングレギュレータのターンオフ損失が増大する。したがって、本発明によるスイッチングレギュレータは、寄生インダクタンスによって誘導されたエネルギを一時的に蓄えるための直列回路と、一時的に蓄えられているエネルギの解放を制御する能動回路であって、オプションとして、一時的に蓄えられているエネルギを入力に供給する能動回路、を採用し、結果として、スイッチングレギュレータの全体的な効率が向上する。

【0031】

本発明の別の態様は、多段スイッチングレギュレータ(multi-stage switching regulator)の変型形態として、インダクタ(またはオプションとして人工的に発生させる寄生インダクタンス)を有する複数の異なる段をデカップリングすることを提案する。スイッチングレギュレータのスイッチング段は、出力に所定の供給電圧を提供する。例えばDC/ACコンバータにおいて複数の電圧をスイッチングするためには、複数の異なるスイッチング段が要求される。この第2の態様によると、スイッチング段の1つをターンオンするときの交差導通損失(cross conduction loss)を防止するため、複数の異なるスイッチング段を、互いに誘導的にデカップリング(inductively decoupled)する。

【0032】

本発明のさらなる第3の態様は、スイッチングレギュレータの構成要素を、複数の異なるパワー基板(power substrate)上または複数の異なるパワーモジュールにグループ化することであって、1つのグループの構成要素間の誘導結合を最小にする一方で、異なるグループの構成要素間の誘導結合が許容されるようにグループ化することを提案する。誘導結合を利用することでスイッチングレギュレータの効率を改善することができ、あるいはインダクタを誘導結合に置き換えることでスイッチングレギュレータのコストを低減することができる。

【0033】

本発明の第2の態様および第3の態様による例示的な実施形態においては、多段スイッチングレギュレータにおける交差導通損失を防止するため、多段スイッチングレギュレータのスイッチング段が、複数の異なるパワー基板または複数の異なるパワーモジュールにグループ化され、異なるスイッチング段の間の誘導結合によって、複数の異なるスイッチング段が誘導的にデカップリングされる。

【0034】

本発明の一実施形態は、第1の入力端子および第2の入力端子を介して供給されるDC入力電圧を、出力端子におけるDC出力電圧に変換するDC/DCコンバータ、を提供する。このDC/DCコンバータは、寄生インダクタンスを有する。このDC/DCコンバータは、第1の入力端子または第2の入力端子の一方に接続されているスイッチング素子であって、出力端子に第1の電圧を供給する、スイッチング素子と、他方の入力端子と出力端子との間に結合されているフリーホイーリング素子であって、フリーホイーリング電流が出力端子に流れることができるようにする、フリーホイーリング素子と、を備えている。さらに、このDC/DCコンバータは、ダイオードおよびキャパシタの第1の直列回路を含んでおり、ダイオードは、一方の入力端子に結合されており、スイッチング素子をオフしたとき、寄生インダクタンスによって誘導されるエネルギをキャパシタに一時的に蓄えることができるようにする。さらに、このDC/DCコンバータは、第1の直列回路のダイオードに並列に結合されている能動回路であって、第1の直列回路のキャパシタからの一時的に蓄えられているエネルギの解放を制御する、能動回路、を含んでいる。

【0035】

例示的な一実施例においては、DC/DCコンバータの第1の直列回路は、第1の入力端子と第2の入力端子との間に結合されている、または、第1の入力端子と第3の入力端子との間に結合されており、第1の入力端子と第3の入力端子は同じ第1の電圧を供給する。

【0036】

さらに詳細な実施例においては、DC/DCコンバータの能動回路は、第1の直列回路のダイオードに並列に接続されているインダクタおよび抵抗の第2の直列回路、を備えている。この能動回路は、スイッチング素子をオンしたとき、第1の直列回路のキャパシタから、一時的に蓄えられているエネルギが解放されることを防止する。さらに、この能動回路は、スイッチング素子をオフしたとき、キャパシタの一時的に蓄えられているエネルギを、一時的に蓄えられているエネルギの少なくとも一部を抵抗に放散させることによって解放できるようにする。

【0037】

詳細な代替実施形態においては、DC/DCコンバータの能動回路は、第1の直列回路のダイオードとキャパシタとを相互接続しているノード、に接続されている第1の端子と、第1の入力端子に接続されている第2の端子と、を有する抵抗、を備えている。この能動回路は、スイッチング素子をオンしたとき、第1の直列回路のキャパシタから、一時的に蓄えられているエネルギが解放されることを防止する。さらに、この能動回路は、スイッチング素子をオフしたとき、キャパシタの一時的に蓄えられているエネルギを、一時的に蓄えられているエネルギの少なくとも一部を抵抗に放散させることによって解放できるようにする。

【0038】

別の詳細な実施形態においては、DC/DCコンバータの能動回路は、第1の直列回路のダイオードに並列に接続されている第1および第2の端子と、第2の入力端子に接続されている第3の端子と、を有する中間コンバータ、を備えている。この中間コンバータは、スイッチング素子をオンしたとき、第1の直列回路のキャパシタから、一時的に蓄えられているエネルギが解放されることを防止するように制御される。さらに、この中間コンバータは、スイッチング素子をオフしたとき、第1の直列回路のキャパシタの一時的に蓄えられているエネルギを、外部から供給されるDC入力電圧に基づいて変換し、変換されたエネルギを第1の入力端子に供給するように制御される。

【0039】

より詳細なさらなる実施形態においては、DC/DCコンバータの中間コンバータは、第1の入力端子に接続されているインダクタ、を含んでいる、または、中間コンバータは、高電圧要素を利用している。

【0040】

別の代替実施形態においては、DC/DCコンバータの能動回路は、第1の直列回路のダイオードとキャパシタとを相互接続しているノード、に接続されている第1の端子と、第1の入力端子に接続されている第2の端子と、第2の入力端子に接続されている第3の端子と、を有する中間コンバータ、を備えている。この中間コンバータは、スイッチング素子をオンしたとき、第1の直列回路のキャパシタから、一時的に蓄えられているエネルギが解放されることを防止するように制御される。さらに、この中間コンバータは、スイッチング素子をオフしたとき、第1の直列回路のキャパシタの一時的に蓄えられているエネルギを、外部から供給されるDC入力電圧に基づいて変換し、変換されたエネルギを第1の入力端子に供給するように制御される。

【0041】

本発明の別の実施形態は、正入力端子および負入力端子を介して正電圧および負電圧として供給されるDC入力電圧を、出力端子におけるAC出力電圧に変換するハーフブリッジコンバータ、を提供する。このハーフブリッジコンバータは、寄生インダクタンスを有する。このハーフブリッジコンバータは、正入力端子に接続されている第1のスイッチング素子であって、出力端子に正電圧を供給する、第1のスイッチング素子と、負入力端子に接続されている第2のスイッチング素子であって、出力端子に負電圧を供給する、第2のスイッチング素子と、を備えている。さらに、このハーフブリッジコンバータは、第1のダイオード、キャパシタ、および第2のダイオードの第1の直列回路、を備えている。第1の直列回路は、正入力端子と負入力端子との間に結合されており、第1のスイッチング素子をオフしたとき、第1のダイオードは、寄生インダクタンスによって誘導されるエネルギをキャパシタに一時的に蓄えることができるようにし、第2のスイッチング素子をオフしたとき、第2のダイオードは、この寄生インダクタンスまたは別の寄生インダクタンスによって誘導されるエネルギをキャパシタに一時的に蓄えることができるようにする。さらに、このハーフブリッジコンバータは、第1の直列回路に並列に結合されている能動回路であって、第1の直列回路のキャパシタからの、一時的に蓄えられているエネルギの解放、を制御する、能動回路、を備えている。

【0042】

例示的な一実施例においては、ハーフブリッジコンバータの能動回路は、第1の抵抗および第1のインダクタの第2の直列回路であって、第1の直列回路の第1のダイオードに並列に接続されている、第2の直列回路と、第2の抵抗および第2のインダクタの第3の直列回路であって、第1の直列回路の第2のダイオードに並列に接続されている、第3の直列回路と、を備えている。この能動回路は、第1または第2のスイッチング素子をオンしたとき、直列回路のキャパシタから、一時的に蓄えられているエネルギが解放されることを防止する。さらに、この能動回路は、第1または第2のスイッチング素子をオフしたとき、第1の直列回路のキャパシタの一時的に蓄えられているエネルギを、一時的に蓄えられているエネルギの少なくとも一部をそれぞれの第1または第2の抵抗に放散させることによって解放できるようにする。

【0043】

別の例示的な実施例においては、ハーフブリッジコンバータの能動回路は、第1の直列回路の第1のダイオードに並列に接続されている第1および第2の端子と、第1の直列回路の第2のダイオードに並列に接続されている第3および第4の端子と、を有する中間コンバータ、を備えている。この中間コンバータは、第1または第2のスイッチング素子をオンしたとき、第1の直列回路(510)のキャパシタから、一時的に蓄えられているエネルギが解放されることを防止するように制御される。さらに、この中間コンバータは、第1または第2のスイッチング素子をオフしたとき、第1の直列回路のキャパシタの一時的に蓄えられているエネルギを、外部から供給されるDC入力電圧に基づいて変換し、変換されたエネルギを第1または第2の入力端子に供給するように制御される。

【0044】

さらに詳細な実施例においては、ハーフブリッジコンバータは、第1のスイッチング素子と出力端子との間に結合されている第1のインダクタと、第2のスイッチング素子と出力端子との間に結合されている第2のインダクタと、を備えた出力回路、を含んでいる。さらに、このハーフブリッジコンバータは、第1のダイオードであって、そのカソードによって正入力端子に接続されており、そのアノードによって第1のノードに接続されており、第1のノードが第2のスイッチング素子と出力回路とを接続している、第1のダイオードと、第2のダイオードであって、そのアノードによって負入力端子に接続されており、そのカソードによって第2のノードに接続されており、第2のノードが第1のスイッチング素子と出力回路とを接続している、第2のダイオードと、を含んでいる。

【0045】

本発明のさらなる実施形態は、正入力端子および負入力端子を介して、中性点端子に対する正電圧および負電圧として供給されるDC入力電圧を、出力端子におけるAC出力電圧に変換する、中性点クランプ形(NPC)コンバータ、を提供することである。このNPCコンバータは、寄生インダクタンスを有する。このNPCコンバータは、正入力端子に接続されている第1のスイッチング素子であって、出力回路を介して出力端子に正電圧を供給する、第1のスイッチング素子と、負入力端子に接続されている第2のスイッチング素子であって、出力回路を介して出力端子に負電圧を供給する、第2のスイッチング素子と、を備えている。出力回路は、第1のスイッチング素子と出力端子との間に結合されている第1のインダクタと、第2のスイッチング素子と出力端子との間に結合されている第2のインダクタと、を備えている。このNPCコンバータは、中性点端子と出力回路との間に結合されている中性点スイッチング回路であって、出力端子に中性点電圧を供給する、中性点スイッチング回路、を備えている。さらに、このNPCコンバータは、第1のダイオードおよび第1のキャパシタの第1の直列回路であって、正入力端子と中性点端子との間に結合されており、第1のスイッチング素子をオフしたとき、第1のダイオードが、寄生インダクタンスによって誘導されるエネルギを第1のキャパシタに一時的に蓄えることができるようにする、第1の直列回路と、第2のダイオードおよび第2のキャパシタの第2の直列回路であって、負入力端子と中性点端子との間に結合されており、第2のスイッチング素子をオフしたとき、第2のダイオードが、同じ寄生インダクタンスまたは別の寄生インダクタンスによって誘導されるエネルギを第2のキャパシタに一時的に蓄えることができるようにする、第2の直列回路と、を備えている。さらに、このNPCコンバータは、第1の直列回路の第1のダイオードに並列に結合されている第1の能動回路であって、第1の直列回路の第1のキャパシタからの、一時的に蓄えられているエネルギの解放、を制御する、第1の能動回路と、第2の直列回路の第2のダイオードに並列に結合されている第2の能動回路であって、第2の直列回路の第2のキャパシタからの、一時的に蓄えられているエネルギの解放、を制御する、第2の能動回路と、を備えている。

【0046】

例示的な実施例においては、NPCコンバータの第1の能動回路が第3の直列回路を備えており、第2の能動回路が第4の直列回路を備えており、第3の直列回路および第4の直列回路のそれぞれが、抵抗およびインダクタを含んでおり、それぞれの第1の直列回路の第1のダイオード、または第2の直列回路の第2のダイオード、に並列に接続されている。第1または第2のスイッチング素子をオンしたとき、それぞれの第1または第2の能動回路は、それぞれの第1の直列回路の第1のキャパシタまたは第2の直列回路の第2のキャパシタから、一時的に蓄えられているエネルギが解放されることを防止する。第1または第2のスイッチング素子をオフしたとき、それぞれの第1または第2の能動回路は、それぞれの第1の直列回路の第1のキャパシタまたは第2の直列回路の第2のキャパシタの一時的に蓄えられているエネルギを、一時的に蓄えられているエネルギの少なくとも一部をそれぞれの抵抗に放散させることによって解放する。

【0047】

代替の一実施例においては、NPCコンバータの第1の能動回路が第1の中間コンバータを備えており、第2の能動回路が第2の中間コンバータを備えており、第1の中間コンバータおよび第2の中間コンバータの各々は、それぞれの第1の直列回路の第1のダイオードまたは第2の直列回路の第2のダイオードに並列に接続されている第1および第2の端子と、中性点端子に接続されている第3の端子と、を有する。第1または第2のスイッチング素子をオンしたとき、それぞれの第1または第2の中間コンバータは、それぞれの第1の直列回路の第1のキャパシタまたは第2の直列回路の第2のキャパシタから、一時的に蓄えられているエネルギが解放されることを防止するように制御される。さらに、第1または第2のスイッチング素子をオフしたとき、それぞれの第1または第2の中間コンバータは、それぞれの第1の直列回路の第1のキャパシタまたは第2の直列回路の第2のキャパシタの一時的に蓄えられているエネルギを、外部から供給されるDC入力電圧に基づいて変換し、変換されたエネルギをそれぞれの第1または第2の入力端子に供給するように制御される。

【0048】

さらに詳細な実施例においては、NPCコンバータは、正入力端子と第1のノードとの間に結合されている少なくとも1つの第1のダイオード、を備えた第1の回路であって、第2のスイッチング素子が第1のノードを通じて負電圧を出力回路に提供する、第1の回路、を備えている。少なくとも1つの第1のダイオードは、出力回路から正入力端子に電流が流れることができるようにする。さらに、NPCコンバータは、負入力端子と第2のノードとの間に結合されている少なくとも1つの第2のダイオード、を備えた第2の回路であって、第1のスイッチング素子が第2のノードを通じて正電圧を出力回路に提供する、第2の回路、を備えている。少なくとも1つの第2のダイオードは、負入力端子から出力回路に電流が流れることができるようにする。

【0049】

以下では、本発明を深く理解できるように、図面に示した実施形態に基づいて本発明について説明する。対応する要素には対応する参照数字および名称を使用してある。さらには、さまざまな実施形態において記載されている個々の特徴または特徴の組合せは、それ自体が個別の独創的な解決策となり得る。以下では、一例として図面を参照しながら、本発明について説明する。

【図面の簡単な説明】

【0050】

【図1】本発明の例示的な実施形態によるDC/DCコンバータの回路図を示している。

【図2】本発明の別の例示的な実施形態によるDC/DCコンバータの回路図を示している。

【図3】本発明のさらなる例示的な実施形態によるDC/DCコンバータの回路図を示している。

【図4】本発明のさらに別の例示的な実施形態によるDC/DCコンバータの回路図を示している。

【図5】本発明の例示的な実施形態によるハーフブリッジコンバータの回路図を示している。

【図6】本発明の別の例示的な実施形態によるハーフブリッジコンバータの回路図を示している。

【図7】本発明の例示的な実施形態による混合電圧NPCコンバータの回路図を示している。

【図8】本発明の別の例示的な実施形態による混合電圧NPCコンバータの回路図を示している。

【図9】本発明の別の例示的な実施形態によるNPCコンバータの回路図を示している。

【図10】本発明の例示的な実施形態による相補型スイッチングレギュレータの回路図を示している。

【図11】本発明の例示的な実施形態によるNPCコンバータのパワーモジュールの設計を示している。

【図12】本発明の例示的な実施形態による混合電圧NPCコンバータのパワーモジュールの設計を示している。

【図13】別の例示的な実施形態によるDC/DCコンバータの回路図を示している。

【図14】例示的な実施形態によるハーフブリッジコンバータの回路図を示している。

【図15】例示的な実施形態による混合電圧NPCコンバータのパワーモジュールを実施するための部分的な回路図を示している。

【図16】例示的な実施形態によるNPCコンバータのパワーモジュールを実施するための部分的な回路図を示している。

【図17】本発明の例示的な実施形態によるDC/DCコンバータの回路図を示している。

【図18】本発明の例示的な実施形態によるDC/DCコンバータの回路図を示している。

【発明を実施するための形態】

【0051】

図1を参照し、本発明の例示的な実施形態によるDC/DCコンバータの回路図を示している。この実施形態のDC/DCコンバータは、DC電圧からDC電圧に変換するために使用することができる。これを目的として、このDC/DCコンバータには、2つの入力端子101,102を介してDC入力電圧が供給される。

【0052】

図1に示した実施形態においては、キャパシタが結合されている電池が、第1の入力端子101と第2の入力端子102との間に接続されている。出力端子103に第1の電圧を供給するためのスイッチング素子104が、第1の入力端子101に接続されている。

【0053】

図1に示した例示的な実施形態においては、出力端子103に負荷が接続されており、この負荷は、抵抗RloadおよびインダクタLloadによって表してある。

【0054】

さらに、図1のDC/DCコンバータは、第2の入力端子102と出力端子103との間に結合されているフリーホイーリングダイオード105を含んでいる。誘導性負荷の場合(図1の例示的な実施形態ではインダクタLloadによって示してある)、スイッチング素子104をオフすると、誘導性負荷Lloadによってフリーホイーリング電流が誘導される。このフリーホイーリング電流は、フリーホイーリングダイオード105に流れる。図1に示した例示的な実施形態においては、フリーホイーリング電流は、フリーホイーリングダイオード105、抵抗Rload、およびインダクタLloadからなる導電ループに流れる。

【0055】

さらに図1に示したように、このDC/DCコンバータは、寄生インダクタLparasiticも含んでいる。寄生インダクタは、DC/DCコンバータの入力端子101の位置に示してある。しかしながら図示した寄生インダクタは、図1のDC/DCコンバータにおける寄生インダクタンスの存在を示しているにすぎない。したがって、図1のDC/DCコンバータの寄生インダクタは、特定の位置の電気回路要素(すなわちインダクタ)に対応するのではなく、さまざまな要因の結果として生じ、設計に固有であるものと想定することができる。

【0056】

例えば、図1のDC/DCコンバータにおいて、寄生インダクタンスは、主として、DC入力電圧源と入力端子101,102との間の接続の実施によって生じる。詳細には、DC/DCコンバータに電池を接続している配線およびねじ接点(screwed contact)が、寄生インダクタンスに主として寄与する。

【0057】

スイッチング素子104をオンすると、入力端子101と出力端子103との間に電流が流れ始める。図1のDC/DCコンバータの寄生インダクタンスの結果として、電圧に対して電流が遅れる。言い換えれば、寄生インダクタンスによって電流の変化率が小さくなり、したがって、図1のDC/DCコンバータにおけるターンオン損失の減少に有利に寄与する。

【0058】

しかしながら、寄生インダクタンスは、図1のDC/DCコンバータのターンオフ挙動にはマイナスの影響を及ぼす。具体的には、スイッチング素子104をオフすると、寄生インダクタンスの磁界に蓄えられているエネルギが解放される。寄生インダクタンスによってスイッチング素子104に電流が流れ、これによりスイッチング素子104がただちにターンオフすることが妨げられる。

【0059】

この点において、図1のDC/DCコンバータには、第1の入力端子101と第2の入力端子102との間に結合されている第1の直列回路110が設けられている。この第1の直列回路は、ダイオードD110およびキャパシタC110を備えている。ダイオードD110は、第1の入力端子101に接続されたアノード端子を有する。

【0060】

より詳細には、第1の直列回路110は、誘導電流のための追加の導電ループを提供する。具体的には、寄生インダクタンスLparasiticによって誘導される電流のAC成分は、寄生インダクタンスLparasiticと、ダイオードD110と、キャパシタC110と、入力端子101,102の間に接続された入力電源とを有するループを循環することができる。したがって、スイッチング素子104をオフしたとき、誘導電流をキャパシタC110に一時的に蓄えておくことができる。

【0061】

したがって、第1の直列回路110は、スイッチング素子104をオフしたとき、寄生インダクタンスによって誘導される電流が、図1のDC/DCコンバータのターンオフ損失に寄与することを防止する。

【0062】

図1に示した例示的な実施形態のDC/DCコンバータは、直列回路110のキャパシタC110に一時的に蓄えられているエネルギを変換する目的で、第1の直列回路110のダイオードD110に並列に結合されている能動回路120をさらに含んでいる。

【0063】

特に、能動回路120は、スイッチング素子104をオンしたときの寄生インダクタンスのプラスの影響が維持されるように、第1の直列回路110のキャパシタC110に一時的に蓄えられているエネルギの解放を制御する。

【0064】

図1のDC/DCコンバータにおいては、能動回路120は、インダクタL120および抵抗R120の直列回路を備えている。インダクタL120および抵抗R120の直列回路は、第1の直列回路110のダイオードD110に並列に接続されている。

【0065】

能動回路は、スイッチング素子104をオンしたとき、第1の直列回路110のキャパシタC110から、一時的に蓄えられているエネルギが解放されることを防止し、インダクタL120はこの効果に寄与する。これを目的として、インダクタL120の値は、DC/DCコンバータの寄生インダクタンスLparasiticの推定値または測定値に基づいて決定される。

【0066】

詳細には、スイッチング素子104をオンしたとき、キャパシタC110には、スイッチング素子104の前回のスイッチオフ動作からのエネルギが依然として蓄えられている。しかしながら、インダクタL120は、寄生インダクタンスLparasiticの作用と同じように、電流を遅らせる。したがって、インダクタL120および抵抗R120の能動回路120は、スイッチング素子104をオンしたとき、キャパシタC110からスイッチング素子104に流れる電流を、2つの入力端子101,102を介してスイッチング素子104に供給される電流よりもずっと小さい電流値に制限する。

【0067】

さらに、能動回路120は、スイッチング素子104をオフしたとき、キャパシタC110の一時的に蓄えられているエネルギの少なくとも一部を抵抗R120に放散させることによって、一時的に蓄えられているエネルギの解放を制御する。

【0068】

言い換えれば、スイッチング素子104をオフしたとき、キャパシタC110と、インダクタL120と、抵抗R120と、入力端子101,102の間に接続されたDC入力電圧源とを含んだ導電ループを、放電電流が流れ始める。この導電ループは、図1にはループIとして示してある。

【0069】

これによって、第1の直列回路110のキャパシタC110から、一時的に蓄えられているエネルギが解放され、図1のDC/DCコンバータの良好なターンオン挙動にマイナスの影響が及ばない。

【0070】

したがって、直列回路110と能動回路120とを組み合わせることによって、図1のDC/DCコンバータの寄生インダクタンスの影響として、スイッチング素子104をオフしたときのマイナスの影響なしに、スイッチング素子104をオンしたときのプラスの影響を保持することができる。

【0071】

次に図2を参照し、本発明の別の例示的な実施形態によるDC/DCコンバータを示している。図2のDC/DCコンバータは、図1のDC/DCコンバータがベースとなっており、対応する要素には対応する参照数字および名称を使用してある。簡潔さのため、対応する要素の詳しい説明は省く。

【0072】

図2のDC/DCコンバータと図1のDC/DCコンバータの異なる点は、能動回路220である。

【0073】

詳細には、図2のDC/DCコンバータも、第1の入力端子101と第2の入力端子102との間に結合されているダイオードD110およびキャパシタC110の第1の直列回路110を含んでいる。この第1の直列回路110のダイオードD110も、スイッチング素子104をオフしたときに寄生インダクタンスによって誘導されるエネルギをキャパシタC110に一時的に蓄えることができるようにする。

【0074】

キャパシタC110の一時的に蓄えられているエネルギを解放する目的で、図2のDC/DCコンバータには、抵抗R220を備えた能動回路220が設けられている。この能動回路220も、スイッチング素子104をオフしたとき、キャパシタC110の一時的に蓄えられているエネルギの少なくとも一部を抵抗R220に放散させることによって、一時的に蓄えられているエネルギの解放を制御する。

【0075】

外部抵抗R220を備えた能動回路220は、寄生インダクタンスによって誘導される、一時的に蓄えられるエネルギの量に基づいて設けることが有利である(例えば、外部取付け式のヒートシンクを設ける)。

【0076】

したがって、能動回路220は、抵抗R220を備えており、その第1の端子は、第1の直列回路110のダイオードD110とキャパシタC110とを相互接続しているノードに接続されており、第2の端子は、図2のDC/DCコンバータの第1の入力端子101に外部から接続されている。したがって、能動回路220は、図2のDC/DCコンバータのモジュールに組み込む必要はなく、モジュールに外部から取り付けることができる。

【0077】

さらには、図2のDC/DCコンバータの能動回路220は、第1の入力端子101に外部から接続されているため、図1のDC/DCコンバータと同様の寄生インダクタンスが生じる。

【0078】

したがって、抵抗R220の能動回路220は、スイッチング素子104をオンしたとき、キャパシタC110からスイッチング素子104に流れる電流を、2つの入力端子101,102を介してスイッチング素子104に供給される電流よりもずっと小さい電流値に制限する。

【0079】

したがって、直列回路110と能動回路220とを組み合わせることによって、図2のDC/DCコンバータの寄生インダクタンスの影響として、スイッチング素子104をオフしたときのマイナスの影響なしに、スイッチング素子104をオンしたときのプラスの影響を保持することができる。

【0080】

次に図3を参照し、本発明によるDC/DCコンバータの別の例示的な実施形態を示している。図3のDC/DCコンバータは、図1および図2のDC/DCコンバータがベースとなっている。対応する要素には対応する参照数字および名称を使用してあり、その要素については実施形態の説明から省いてある。

【0081】

図3に示したDC/DCコンバータの例示的な実施形態も、ダイオードD110およびキャパシタC110の第1の直列回路110を含んでいる。第1の直列回路110は、第1の入力端子101と第2の入力端子102との間に結合されている。

【0082】

スイッチング素子104をオフすると、DC/DCコンバータの中の寄生インダクタンスによって電流が誘導され、この電流を直列回路110のキャパシタC110に一時的に蓄えることができる。これを目的として、誘導電流はダイオードD110を通る。ダイオードD110のアノード端子は、DC/DCコンバータの第1の入力端子に接続されている。

【0083】

図3に示した特定の実施形態においては、能動回路320として中間DC/DCコンバータ320を利用している。中間DC/DCコンバータ320は、特に、その第1および第2の端子が第1の直列回路110のダイオードD110に並列に接続されており、第3の端子が第2の入力端子102に接続されている。中間DC/DCコンバータ320によって、第1の直列回路110のキャパシタの一時的に蓄えられているエネルギの解放を制御することができる。

【0084】

具体的には、スイッチング素子104をオンしたとき、第1の直列回路110のキャパシタC110から、一時的に蓄えられているエネルギが解放されることが防止されるように、中間DC/DCコンバータ320を制御することができる。スイッチング素子104をオンする前に、キャパシタC110の一時的に蓄えられているエネルギが解放されるように、中間DC/DCコンバータを制御することができる。

【0085】

この点において、スイッチング素子をオフしたとき、中間DC/DCコンバータ320が、キャパシタC110に一時的に蓄えられているエネルギからDC電圧への変換を開始することが有利である。

【0086】

一時的に蓄えられているエネルギを、外部から供給されるDC入力電圧に基づいて変換することによって、変換されたエネルギを第1の入力端子101に供給することができる。したがって、一時的に蓄えられているエネルギを回生することができ、このエネルギがDC/DCコンバータのスイッチング損失に寄与せず、したがってDC/DCコンバータの効率が向上する。

【0087】

中間DC/DCコンバータ320は、複数の異なる態様として実施することができる。

【0088】

第1の態様として、中間DC/DCコンバータ320をバックコンバータとして実施することができ、この場合、第1の端子が、入力端子として、第1の直列回路110のダイオードD110とキャパシタC110とを相互接続しているノードに接続されており、第2の端子が、出力端子として、第1の入力端子101に接続されており、第3の端子が、基準端子として、第2の入力端子102に接続されている。

【0089】

これに代えて、中間DC/DCコンバータ320をバックブーストコンバータとして実施することができ、この場合、第1の端子が、入力端子として、第1の直列回路110のダイオードD110とキャパシタC110とを相互接続しているノードに接続されており、第2の端子が、出力端子として、第2の入力端子102に接続されており、第3の端子が、基準端子として、第1の入力端子101に接続されている。

【0090】

さらには、中間DC/DCコンバータ320を、トランスをベースとする昇圧器として実施することができ、この場合、第1の端子が、第1の直列回路110のダイオードD110とキャパシタC110とを相互接続しているノードに接続されており、第2の端子が、出力端子として、第2の入力端子102に接続されており、第3の端子が、基準端子として、第1の入力端子101に接続されている。

【0091】

中間DC/DCコンバータの上述した2番目および3番目の実施態様においては、中間DC/DCコンバータは、入力端子と基準端子の間の低い入力電圧から、出力端子と基準端子の間の高い出力電圧に昇圧することが要求される。上述した最初の実施態様では、中間DC/DCコンバータは降圧コンバータとして動作する。

【0092】

次に図4を参照し、本発明によるDC/DCコンバータのさらなる例示的な実施形態を示している。図4のDC/DCコンバータの例示的な実施形態は、図3のDC/DCコンバータがベースとなっている。

【0093】

図4のDC/DCコンバータと図3のDC/DCコンバータの異なる点は、能動回路である。

【0094】

図4のDC/DCコンバータも、ダイオードD110およびキャパシタC110の第1の直列回路110を含んでいる。この第1の直列回路110は、第1の入力端子101と第2の入力端子102との間に結合されている。特に、ダイオードD110は、スイッチング素子104をオフしたとき、寄生インダクタンスによって誘導されるエネルギをキャパシタC110に一時的に蓄えることができるようにする。

【0095】

さらに、図4のDC/DCコンバータは、第1の直列回路のダイオードD110に並列に結合されている中間DC/DCコンバータ420を能動回路として含んでいる。この実施形態による中間DC/DCコンバータ420は、中に含まれている構成要素が原因で、DC/DCコンバータのモジュールまたはパワー基板上に組み込むことができないことがある。

【0096】

例えば、中間DC/DCコンバータをバックブーストコンバータとして実施するとき、必要なインダクタに起因して、図4のDC/DCコンバータと同じ基板上に組み込むことができないことがある。この点において、インダクタを個別に用意し、第1の入力端子101または第2の入力端子102に外部から接続することができる。

【0097】

図4のDC/DCコンバータの中間DC/DCコンバータは、その第1の端子が、第1の直列回路110のダイオードD110とキャパシタC110とを相互接続しているノードに接続されており、第2の端子が第1の入力端子101に外部から接続されており、第3の端子が第2の入力端子102に接続されている。

【0098】

これに代えて、図4のDC/DCコンバータの中間DC/DCコンバータを、個別のモジュールの中に設けて、第1の入力端子101と、第2の入力端子102と、第1の直列回路110のダイオードD110とキャパシタC110とを相互接続しているノードとに、外部から接続することができる。

【0099】

中間DC/DCコンバータ420は、図3に関連して説明したように、バックコンバータとして、またはバックブーストコンバータとして、または昇圧器を有するトランスとして、実施することができる。

【0100】

次に図5を参照し、本発明によるハーフブリッジコンバータの例示的な実施形態を示している。

【0101】

図5のハーフブリッジコンバータは、DC電圧をAC電圧に変換するために使用することができる。これを目的として、このハーフブリッジコンバータには、2つの入力端子501,502を介して正のDC電圧および負のDC電圧が供給され、出力端子503に正電圧または負電圧を供給する。

【0102】

さらに、このハーフブリッジコンバータは、正入力端子501に接続されている第1のスイッチング素子504と、負入力端子502に接続されている第2のスイッチング素子505とを含んでいる。

【0103】

このハーフブリッジコンバータは、出力端子503に正の半波および負の半波を連続的に供給するため、第1のスイッチング素子504および第2のスイッチング素子505を交互にオンするように構成されている。

【0104】

言い換えれば、第1のスイッチング素子504をオンすることによって、出力端子503に正電圧を供給することができ、第2のスイッチング素子505をオンすることによって、出力端子503に負電圧を供給することができる。

【0105】

第1および第2のスイッチング素子504,505それぞれは、誘導性負荷の場合にフリーホイーリング電流を流すことのできるボディダイオードを含んでいる。

【0106】

例えば、第1のスイッチング素子504をオフすると、誘導性負荷Lloadの結果として、第2のスイッチング素子505のボディダイオードにフリーホイーリング電流が流れる。同様に、第2のスイッチング素子505をオフすると、誘導性負荷の結果として、第1のスイッチング素子504のボディダイオードにフリーホイーリング電流が流れる。

【0107】

さらには、図5に示したように、このハーフブリッジコンバータも、寄生インダクタLparasiticを含んでいる。第1の寄生インダクタは、図5のハーフブリッジコンバータの正入力端子501の位置に示してあり、第2の寄生インダクタは、ハーフブリッジコンバータの負入力端子502の位置に示してある。

【0108】

しかしながら、図示した寄生インダクタは、図1に関連してすでに説明したように、図5のハーフブリッジコンバータにおける寄生インダクタンスの存在を示しているにすぎない。したがって、図5に示した寄生インダクタは、電気回路要素(すなわちインダクタ)に対応するのではなく、さまざまな要因の結果として生じ、設計に固有であるものと想定することができる。

【0109】

スイッチング素子504をオンすると、正入力端子501と出力端子503との間に電流が流れ始める。図5のハーフブリッジコンバータにおける寄生インダクタンスの結果として、電圧に対して電流が遅れる。これは、図5のハーフブリッジコンバータのスイッチング素子505をオンしたときも同様である。言い換えれば、寄生インダクタンスは、電流の変化率を小さくし、図5のハーフブリッジコンバータにおけるターンオン損失の減少に有利に寄与する。

【0110】

しかしながら、寄生インダクタンスは、図5のハーフブリッジコンバータのターンオフ挙動にはマイナスの影響を及ぼす。具体的には、スイッチング素子504をオフすると、寄生インダクタンスの磁界に蓄えられているエネルギが解放される。したがって寄生インダクタンスによってスイッチング素子504に電流が流れ、これによりスイッチング素子504のターンオフが妨げられる。同様に、スイッチング素子505をオフすると、寄生インダクタンスによってスイッチング素子505に電流が流れ、これによりスイッチング素子505がただちにターンオフすることが妨げられる。

【0111】

寄生インダクタンスによってスイッチング素子504,505のターンオフが妨げられることを回避する目的で、図5のハーフブリッジコンバータには、正入力端子501と負入力端子502との間に結合された第1の直列回路510が設けられている。

【0112】

第1の直列回路510は、第1のダイオードD511と、キャパシタC510と、第2のダイオードD512とを備えている。第1のダイオードD511は、そのアノード端子が正入力端子501に接続されており、第2のダイオードD512は、そのカソード端子が負入力端子502に接続されている。

【0113】

正入力端子501と負入力端子502との間に結合された第1の直列回路510が設けられていることによって、第1のスイッチング素子504をオフしたとき、正の誘導電流をキャパシタC510に一時的に蓄えることができ、第2のスイッチング素子505をオフしたとき、負の誘導電流をキャパシタC510に一時的に蓄えることができる。

【0114】

したがって、第1の直列回路510は、スイッチング素子504,505をオフしたときに寄生インダクタンスによって誘導される電流が、図5のハーフブリッジコンバータのターンオフ損失に寄与することを防止する。

【0115】

さらに、図5のハーフブリッジコンバータは、第1の直列回路510の第1のダイオードD511に並列に結合されている能動回路と、第2のダイオードD512に並列に結合されている能動回路を含んでいる。能動回路521,522は、スイッチング素子504またはスイッチング素子505をオンしたときの寄生インダクタンスのプラスの影響が維持されるように、第1の直列回路のキャパシタC510の一時的に蓄えられているエネルギの解放を制御することができる。

【0116】

図5のハーフブリッジコンバータにおいては、能動回路521および能動回路522は、それぞれ、インダクタL521および抵抗R521を有する直列回路と、インダクタL522および抵抗R522を有する直列回路を備えている。以下では、第1の直列回路510との混同を避ける目的で、インダクタL521および抵抗R521の直列回路を第2の直列回路521と称し、インダクタL522および抵抗R522の直列回路を第3の直列回路522と称する。

【0117】

第2の直列回路521は、第1の直列回路510の第1のダイオードD511に並列に接続されている。第3の直列回路522は、第1の直列回路510の第2のダイオードD512に並列に接続されている。

【0118】

能動回路521,522は、第1のスイッチング素子504または第2のスイッチング素子505をオンしたとき、第1の直列回路510のキャパシタC510から一時的に蓄えられているエネルギが解放されることを防止し、インダクタL521およびL522はこの効果に寄与する。これを目的として、インダクタL521およびL522の値は、図5のハーフブリッジコンバータの寄生インダクタンスの推定値または測定値に基づいて決定される。

【0119】

さらに詳細には、インダクタL521およびL522は、図5のハーフブリッジコンバータの寄生インダクタンスの作用と同様に電流を遅らせるため、能動回路521,522は、対応するスイッチング素子504,505をオンしたとき、キャパシタC510からスイッチング素子504,505に流れる電流を、それぞれの正入力端子501または負入力端子502を介してスイッチング素子504,505に供給される電流よりもずっと小さい電流値に制限する。

【0120】

さらに、能動回路521,522は、対応するスイッチング素子504,505をオフしたとき、キャパシタC510の一時的に蓄えられているエネルギの少なくとも一部をそれぞれの抵抗R521またはR522に放散させることによって、一時的に蓄えられているエネルギの解放を制御する。

【0121】

言い換えれば、スイッチング素子504またはスイッチング素子505のいずれかをオフすると、キャパシタC510からそれぞれの第2の直列回路521または第3の直列回路522に電流が流れ始め、したがって、対応する抵抗R521またはR522によって、キャパシタC510の一時的に蓄えられているエネルギの少なくとも一部が放散する。

【0122】

したがって、第1の直列回路510のキャパシタC510から、一時的に蓄えられているエネルギが解放され、図5のハーフブリッジコンバータの良好なターンオン挙動にマイナスの影響が及ばない。

【0123】

したがって、第1の直列回路510と能動回路521,522とを組み合わせることによって、図5のハーフブリッジコンバータの寄生インダクタンスの影響として、スイッチング素子504,505をオフしたときのマイナスの影響なしに、スイッチング素子504,505をオンしたときのプラスの影響を保持することができる。

【0124】

次に図6を参照し、本発明の別の例示的な実施形態によるハーフブリッジコンバータを示している。図6のハーフブリッジコンバータは、図5のハーフブリッジコンバータがベースとなっており、対応する要素には対応する参照数字および名称を使用してある。簡潔さのため、対応する要素の詳しい説明は省く。

【0125】

図6のハーフブリッジコンバータと図5のハーフブリッジコンバータの異なる点は、能動回路620である。

【0126】

詳細には、図6のハーフブリッジコンバータも、正入力端子501と負入力端子502との間に結合されている第1のダイオードD511、キャパシタC510、および第2のダイオードD512を含んだ第1の直列回路510を含んでいる。第1の直列回路のダイオードD511およびダイオードD512は、スイッチング素子504またはスイッチング素子505のいずれかをオフしたとき、寄生インダクタンスによって誘導されるエネルギをキャパシタC510に一時的に蓄えることができるようにする。

【0127】

キャパシタC510から一時的に蓄えられているエネルギを解放するため、図6のハーフブリッジコンバータには、中間DC/DCコンバータを備えた能動回路620が設けられている。

【0128】

図6のハーフブリッジコンバータの中間DC/DCコンバータ620は、第1の直列回路510の第1のダイオードD511に並列に接続されている第1および第2の端子と、第1の直列回路510の第2のダイオードD512に並列に接続されている第3および第4の端子と、を備えている。

【0129】

図3の中間DC/DCコンバータ320に関連して説明したように、第1の直列回路510のキャパシタC510からの蓄えられているエネルギを昇圧または降圧する目的には、DC/DCコンバータの一般に公知の実施態様を使用することができる。一般に公知の中間DC/DCコンバータの例は、バックコンバータ、バックブーストコンバータ、またはトランスをベースとする昇圧回路である。

【0130】

第1のスイッチング素子504または第2のスイッチング素子505をオンしたとき、第1の直列回路510のキャパシタC510から、一時的に蓄えられているエネルギが解放されることを防止するように、図6の中間DC/DCコンバータ620を制御することができる。

【0131】

これは、第1のスイッチング素子504をオンしたとき、第1の端子と第2の端子との間に電流が流れることを防止するように中間DC/DCコンバータ620を制御し、第2のスイッチング素子505をオンしたとき、第3の端子と第4の端子との間に電流が流れることを防止するように中間DC/DCコンバータ620を制御することによって、達成することができる。

【0132】

さらには、第1のスイッチング素子504または第2のスイッチング素子505をオフしたとき、第1の直列回路510のキャパシタC510の一時的に蓄えられているエネルギを、外部から供給されるDC入力電圧に基づいて変換し、変換されたエネルギをそれぞれの第1の入力端子501または第2の入力端子502に供給するように、中間DC/DCコンバータ620を制御することができる。

【0133】

言い換えれば、中間DC/DCコンバータ620の第1の端子と第2の端子との間に正電圧が検出されたとき、含まれているエネルギを、正入力端子501および負入力端子502を介して供給されるDC入力電圧にに基づいて変換し、変換されたエネルギを、中間DC/DCコンバータ620の第1および第3の端子を介して、正入力端子501および負入力端子502に供給するように、中間DC/DCコンバータ620を制御することができる。

【0134】

同様に、中間DC/DCコンバータ620の第3の端子と第4の端子との間に負電圧が検出されたとき、含まれているエネルギをDC入力電圧に基づいて変換し、変換されたエネルギを、中間DC/DCコンバータ620の第1および第3の端子を介して、正入力端子501および負入力端子502に供給するように、中間DC/DCコンバータ620を制御することができる。

【0135】

これによって、中間DC/DCコンバータは、キャパシタC510の蓄えられているエネルギを回生することができ、図6のハーフブリッジコンバータの全体的な効率の増大に寄与する。

【0136】

さらには、本発明によるハーフブリッジコンバータは、図5および図6に示した実施形態に制限されない。

【0137】

図5のハーフブリッジコンバータは、図2の実施形態と同様に修正改良することもでき、抵抗を外部から取り付けることができるようにする目的で、能動回路521および能動回路522に代えて、第1の直列回路510のダイオードD511とキャパシタC510とを相互接続しているノードに接続されている第1の端子と、正入力端子501に接続されている第2の端子と、を有する抵抗を備えた能動回路と、第1の直列回路510のダイオードD512とキャパシタC510とを相互接続しているノードに接続されている第1の端子と、負入力端子502に接続されている第2の端子と、を有するもう1つの抵抗を備えた能動回路と、に置き換える。

【0138】

さらに、図6のハーフブリッジコンバータは、図4の実施形態と同様に修正改良することもでき、ダイオードD511とキャパシタC510とを相互に接続している第1のノードに接続されている第1の端子と、第1の直列回路510のダイオードD512とキャパシタC510とを相互に接続している第2のノードに接続されている第2の端子と、正入力端子501に接続されている第3の端子と、負入力端子502に接続されている第4の端子と、を有する中間DC/DCコンバータ、を設ける。これによって、中間DC/DCコンバータに含まれている構成要素の少なくとも一部を外部から接続することができる。

【0139】

次に図7を参照し、本発明の例示的な実施形態による混合電圧NPC(MNPC)コンバータを示している。この実施形態の混合電圧NPCコンバータは、DC電圧をAC電圧に変換するため使用することができる。

【0140】

これを目的として、図7のMNPCコンバータは、正入力端子701および負入力端子702を介してDC正電圧およびDC負電圧が供給され、出力端子703に正電圧または負電圧を供給する。さらに、図7のMNPCコンバータは、正電圧および負電圧の間の中性点電圧を出力端子703に供給するための中性点端子706を含んでいる。

【0141】

図7のMNPCコンバータは、正入力端子701に接続されている第1のスイッチング素子704であって、出力回路730を介して出力端子703に正電圧を供給する第1のスイッチング素子704、を備えている。さらに、図7のMNPCコンバータは、負入力端子702に接続されている第2のスイッチング素子705であって、出力回路730を介して出力端子703に負電圧を供給する第2のスイッチング素子705を備えている。

【0142】

図7のMNPCコンバータの出力回路730は、第1のスイッチング素子704と出力端子703との間に結合されている第1のインダクタと、第2のスイッチング素子705と出力端子703との間に結合されている第2のインダクタとを備えている。この点において、第1のスイッチング素子704は、第1のインダクタを介して出力端子に結合されており、第2のスイッチング素子705は、第2のインダクタを介して出力端子703に結合されている。

【0143】

さらに、図7のMNPCコンバータは、中性点端子706と出力回路730との間に結合されている中性点スイッチング回路740であって、出力端子703に中性点電圧を供給する中性点スイッチング回路740、を含んでいる。中性点スイッチング回路740は、ダイオードおよびトランジスタの2つの相補直列回路によって実施することができる。第1の相補直列回路は、第1のスイッチング素子704をオフした後に出力回路730に中性点電圧を供給できるようにし、第2の相補直列回路は、第2のスイッチング素子705をオフした後に出力回路730に中性点電圧を供給できるようにする。

【0144】

さらに、図7のMNPCコンバータも、寄生インダクタLparasiticを含んでいる。寄生インダクタは、入力端子701、入力端子702、および入力端子706の位置に示してある。しかしながら、これらの寄生インダクタは、図7のMNPCコンバータにおける寄生インダクタンスの存在を示しているにすぎない。したがって、図7のMNPCコンバータの寄生インダクタは、電気回路要素(すなわちインダクタ)に対応するのではなく、さまざまな要因の結果として生じ、設計に固有であるものと想定することができる。

【0145】

第1のスイッチング素子704をオンすると、正入力端子701と出力端子703との間に電流が流れ始める。図7のMNPCコンバータの寄生インダクタンスの結果として、電圧に対して電流が遅れる。同様に、スイッチング素子705をオンすると、負入力端子702と出力端子703との間に電流が流れ始める。図7のMNPCコンバータの寄生インダクタンスの結果として、電圧に対して電流が遅れる。言い換えれば、寄生インダクタンスによって電流の変化率が小さくなり、したがって、図7のMNPCコンバータにおけるターンオン損失の減少に寄与する。

【0146】

しかしながら、図7のMNPCコンバータの寄生インダクタンスは、MNPCコンバータのターンオフ挙動にはマイナスの影響を及ぼす。

【0147】

特に、第1のスイッチング素子704または第2のスイッチング素子705のいずれかをオフすると、寄生インダクタンスの磁界に含まれているエネルギが解放される。

【0148】

したがって、寄生インダクタンスによって、それぞれの第1のスイッチング素子704または第2のスイッチング素子705に電流が流れ、これによりスイッチング素子がただちにターンオフすることが妨げられる。

【0149】

この点において、図7のMNPCコンバータには、正入力端子701と中性点端子706との間に結合されている第1のスイッチング直列回路711と、負入力端子702と中性点端子706との間に結合されている第2のスイッチング直列回路712とが設けられている。第1の直列回路711は、ダイオードD711とキャパシタC711とを備えている。ダイオードD711は、アノード端子が正入力端子701に接続されている。第2の直列回路712は、ダイオードD712とキャパシタC712とを備えている。ダイオードD712は、カソードが負入力端子702に接続されている。

【0150】

より詳細には、第1の直列回路711は追加の導電ループを提供し、寄生インダクタンスLparasiticによって誘導される電流は、寄生インダクタンスLparasiticと、ダイオードD711と、キャパシタC711と、入力端子701と入力端子706との間のDC入力電圧源とを含んだループを循環することができる。第2の直列回路712も導電ループを提供し、寄生インダクタンスLparasiticによって誘導される電流は、寄生インダクタンスLparasiticと、ダイオードD712と、キャパシタC712と、入力端子702と入力端子706との間のDC入力電源とを含んだループを循環することができる。

【0151】

したがって、スイッチング素子704をオフしたとき、誘導電流をキャパシタC711に一時的に蓄えることができ、スイッチング素子705をオフしたとき、誘導電流をキャパシタC712に一時的に蓄えることができる。

【0152】

したがって、第1の直列回路711および第2の直列回路712は、それぞれのスイッチング素子704,705をオフしたとき、寄生インダクタンスによって誘導される電流が図7のMNPCコンバータのターンオフ損失に寄与することを防止する。

【0153】

さらに、図7のMNPCコンバータは、直列回路711のキャパシタC711および第2の直列回路712のキャパシタC712の、一時的に蓄えられているエネルギを変換する目的で、第1の直列回路711のダイオードD711に並列に結合されている能動回路721と、第2の直列回路712のダイオードD712に並列に結合されている能動回路722とをさらに含んでいる。

【0154】

能動回路721および能動回路722は、特に、それぞれの第1のスイッチング素子704または第2のスイッチング素子705をオンしたときの寄生インダクタンスのプラスの影響が維持されるように、対応する第1のキャパシタC711または第2のキャパシタC712の一時的に蓄えられているエネルギの解放を制御することができる。

【0155】

図7のMNPCコンバータにおいて、第1の能動回路721は、インダクタL721と抵抗R721を備えている。このインダクタL721と抵抗R721の直列回路は、第1の直列回路711のダイオードD711に並列に接続されている。第2の能動回路722も、インダクタL722と抵抗R722の直列回路を備えている。このインダクタL722と抵抗R722の直列回路は、第2の直列回路712のダイオードD712に並列に接続されている。

【0156】

能動回路721および能動回路722は、それぞれのスイッチング素子704またはスイッチング素子705をオンしたときにそれぞれのキャパシタC711またはC712から一時的に蓄えられているエネルギが解放されることを防止し、インダクタL721およびインダクタL722はこの効果に寄与する。これを目的として、インダクタL721およびインダクタL722それぞれの値は、図7のMNPCコンバータの寄生インダクタンスの推定値または測定値に基づいて決定される。

【0157】

さらに詳細には、インダクタL721およびインダクタL722は、寄生インダクタンスの作用と同様に電流を遅らせるため、能動回路721および能動回路722それぞれは、それぞれのキャパシタC711,C712から対応するスイッチング素子704,705に流れる電流を制限し、スイッチング素子704およびスイッチング素子705には、それぞれをオンしたときに対応する正入力端子701または負入力端子702を介してそれぞれのスイッチング素子704またはスイッチング素子705に供給される電流よりもずっと小さい放電電流が流れるのみである。

【0158】

さらに、能動回路721および能動回路722は、対応するスイッチング素子704または705をオフしたとき、それぞれのキャパシタC711またはC712の一時的に蓄えられているエネルギの少なくとも一部をそれぞれの抵抗R721またはR722に放散させることによって、一時的に蓄えられているエネルギの解放を制御する。

【0159】

言い換えれば、スイッチング素子704をオフすると、キャパシタC711と、インダクタL721と、抵抗R721と、入力端子701,706の間に接続されたDC入力電圧源とを含んだ導電ループを、放電電流が流れ始める。同様に、スイッチング素子705をオフすると、キャパシタC712と、インダクタL722と、抵抗R722と、入力端子702と入力端子706の間に接続されたDC入力電圧源とを含んだ導電ループを、放電電流が流れ始める。

【0160】

これによって、第1の直列回路711のキャパシタC711と、第2の直列回路712のキャパシタC712から、一時的に蓄えられているエネルギが解放され、図7のMNPCコンバータの良好なターンオン挙動にマイナスの影響が及ばない。

【0161】

したがって、第1の直列回路711と第1の能動回路721の組合せと、第2の直列回路712と第2の能動回路722の組合せとによって、図7のMNPCコンバータの寄生インダクタンスの影響として、スイッチング素子704または705をオフしたときのマイナスの影響なしに、スイッチング素子704または705をオンしたときのプラスの影響を保持することができる。

【0162】

次に図8を参照し、本発明の別の例示的な実施形態によるMNPCコンバータを示している。図8のMNPCコンバータは、図7のMNPCコンバータがベースとなっており、対応する要素には対応する参照数字および名称を使用してある。簡潔さのため、対応する要素の詳しい説明は省く。

【0163】

図8のMNPCコンバータと図7のMNPCコンバータの異なる点は、第1および第2の能動回路821,822である。

【0164】

詳細には、図8のMNPCコンバータも、正入力端子701と中性点端子706との間に結合されているダイオードおよびキャパシタを有する第1の直列回路711と、負入力端子702と中性点端子706との間に結合されているダイオードおよびキャパシタを有する第2の直列回路712と、を含んでいる。

【0165】