コンバータ回路、およびこのコンバータ回路を備える電子システム

【課題】 送出される電力が大きく変動し得る電気エネルギー源に接続される、低消費電力のコンバータ回路を提供する。

【解決手段】 このコンバータ回路(2)は、電気エネルギー源(3)に接続可能な、デューティサイクルが可変であるチョッパ回路(11)と、電気エネルギー源の最大電力点を追尾する制御ループ形成手段(57)と、制御ループ形成手段からの設定値信号に応じて、所定の時間間隔で、チョッパ回路のデューティサイクルの変更を命令するように構成されている制御ユニット(53)とを備えている。制御ループ形成手段は、連続する少なくとも3つのデューティサイクルに対する、電気エネルギー源からの出力電圧に対応する情報をアナログ的に記憶する手段(60)と、アナログ的に記憶された情報に応じて、制御ユニットによるデューティサイクルの増減に用いられる設定値信号を送出するアナログ比較ユニット(62)とを備えている。

【解決手段】 このコンバータ回路(2)は、電気エネルギー源(3)に接続可能な、デューティサイクルが可変であるチョッパ回路(11)と、電気エネルギー源の最大電力点を追尾する制御ループ形成手段(57)と、制御ループ形成手段からの設定値信号に応じて、所定の時間間隔で、チョッパ回路のデューティサイクルの変更を命令するように構成されている制御ユニット(53)とを備えている。制御ループ形成手段は、連続する少なくとも3つのデューティサイクルに対する、電気エネルギー源からの出力電圧に対応する情報をアナログ的に記憶する手段(60)と、アナログ的に記憶された情報に応じて、制御ユニットによるデューティサイクルの増減に用いられる設定値信号を送出するアナログ比較ユニット(62)とを備えている。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、コンバータ回路、およびこのコンバータ回路を備える電子システムに関する。

【0002】

二酸化炭素排出によってもたらされる有害な温室効果を軽減するために、再生可能エネルギー源の使用を継続的に増大させるという目的で、近年、太陽電池パネルの開発が著しく進められている。

【0003】

このことは、風力や熱電などの再生可能エネルギー源にも当てはまる。

【0004】

これらの再生可能エネルギー源は、出力される電気エネルギーが、エネルギーを供給する自然現象に応じて、極端に変動するという特殊な性質を有している。また、太陽電池発電装置は、極めて非線形な電流−電圧特性I=f(U)を有する発電装置である。したがって、太陽光照射値が同じであっても、送出される電力は、負荷に応じて変化する。

【0005】

すなわち、効率、したがって太陽電池から送出される電力は、1日を通じて変化する太陽光線の向きだけではなく、例えば雲または他の気象現象によって生じる日陰による日光の遮蔽状態に依存する。

【0006】

太陽電池が、例えば電力消費部品などの負荷(例えばセンサまたは再充電されるバッテリ)に接続されている場合に、負荷に伝達される電力は、一般に、太陽電池が送出することができる最大電力に一致しないということがこれまでに明らかになっている。同様の問題が、風力エネルギーの場合にも発生することが知られている。そのため、例えば日光が弱くなると、効率が低下するだけではなく、与えられた動作点が、太陽電池の有する潜在能力を発揮することができる動作点より劣る位置に設定されることによって、効率は悪化する。

【0007】

このような欠点を克服し、最適動作点に可能な限り近い動作点で電気エネルギーを発生させるために、1968年以来開発されてきている最大電力点追尾(MPPT)法として知られている方法を組み込んだ回路が用いられている。これは、非線形な再生可能エネルギー源と任意の負荷との間のより良い接続を提供するための方法である。

【0008】

このような回路は、発電装置、例えば太陽電池を、その最大電力点において動作させ、それによって、効率を改善させるようになっている。

【0009】

したがって、MPPTコントローラは、負荷(例えばバッテリ)と太陽電池パネルとを接続している静的コンバータを、恒久的に負荷に最大電力を供給するように駆動する。

【背景技術】

【0010】

最大電力点追尾、すなわちMPP追尾のために、P&O(Perturbation and Observation)アプローチに基づく方法を適用する手法が公知である。

【0011】

太陽電池への適用の場合には、この手法は、一定電圧U1に対して、発電装置から送出される対応する電力値P1を測定し、次いで、一定期間の後に、電圧U2=U1+ΔUを定めて、再度、対応する電力値P2を測定するアルゴリズムである。その後、電力値P2がP1を超過している場合には、太陽電池の電圧は、電圧U3=U2+ΔUとされ、そうでない場合には、電圧U3=U2−ΔUとされる。

【0012】

しかし、これは、電流の測定を必ず伴い、また無視できない電気エネルギー量を消費する大規模な計算リソースを必要とする。このために、大型の太陽電池機器においては、太陽電池の1つのサブグループが、MPPT回路を制御するために必要な電気エネルギーの供給に専用に用いられる。

【0013】

しかし、例えば自律センサなどの電子マイクロシステムにおいては、空間要求と重量に関する制約が大きく、自律性の拡張によって、システムを可能な限り小さくすることが必要であるため、このアプローチを適用することはできない。

【0014】

さらに、さらなる駆動セルを有する最大電力点追尾回路が公知である。しかし、これは、必ずしも望ましいとは限らない。

【0015】

一定周波数で、太陽電池パネルと、回路の残りの部分との間の接続を切って、開回路において電圧を測定することによって遂行される、開回路での電圧サンプリングに基づく、駆動セルを用いないMPPT回路も存在する。このシステムは、その後、新しく最適化されたパラメータを取り入れたエネルギー収集回路に、太陽電池パネルを再接続する。しかしながら、これによって、エネルギー収集プロセスは、頻繁に中断される。これは、自律的に動作するように作られている電子マイクロシステムにとっては受け入れがたいことである。

【0016】

最後に、電圧測定に基づいたMPP追尾法について開示している非特許文献1による公知の方法が存在する。

【0017】

この非特許文献1は、デューティサイクルに関する、電気エネルギー源の動作電圧の微分係数は、最大電力点(MPP)の近傍において最大値を有することを開示している。したがって、動作電圧の微分係数の最大値を追尾することは、最大電力点を追尾することと等価である。

【0018】

したがって、単純な電圧測定、減算操作および比較操作によって、コンバータを、最大電力点(MPP)の近傍で動作させることができる。

【0019】

このために、デューティサイクルαは、あらかじめ定められた時間間隔で、例えば約10Hzの周波数で、あらかじめ定められた量Δαだけ変更され、動作電圧の微分係数、すなわちデューティサイクルの変更後に得られる、動作電圧間の電圧差の推移が追尾される。

【先行技術文献】

【非特許文献】

【0020】

【非特許文献1】「A simple single-sensor MPPT solution(単一のセンサを用いる単純なMPPT手法)」、IEEE Transactions on Power Electronics、2007年3月、第22巻、第2号

【発明の概要】

【発明が解決しようとする課題】

【0021】

上述の非特許文献1において、このMPPTのための制御ループ形成手段は、マイクロコントローラによって構成されている。

【0022】

利用可能なエネルギー量が少ないということを前提として、本発明は、この制御ループ形成手段における電気エネルギーの消費量を最適にし、さらに、特に、エネルギーの収集を最適化するとともに、このシステムの空間要求の十分な低減を可能にすることを目的としている。

【課題を解決するための手段】

【0023】

この目的を達成するために、本発明は、送出される電力が大きく変動し得る電気エネルギー源に接続されるように作られ、次のものを備えているコンバータ回路を提供するものである。

− 電気エネルギー源に接続可能な、デューティサイクルが可変であるチョッパ回路。

− チョッパ回路に接続されている少なくとも1つの出力回路。

− 電気エネルギー源の出力端子に接続される、電気エネルギー源の最大電力点を追尾するように動作する制御ループ形成手段。

− 制御ループ形成手段からの設定値信号に応じて、あらかじめ定められた時間間隔で、チョッパ回路のデューティサイクルの変更を命令するように構成されている制御ユニット。

制御ループ形成手段は、連続する少なくとも3つのデューティサイクルに対する、電気エネルギー源からの出力電圧に対応する情報をアナログ的に記憶するためのアナログ情報記憶手段と、アナログ的に記憶されたこの情報に応じて、制御ユニットによるデューティサイクルの増減に用いられる設定値信号を出力から送出するアナログ比較ユニットとを備えている。

【0024】

このコンバータ回路は、次の特性のうちの1つ以上を、単独でまたは組み合わせて有している。

【0025】

一態様によれば、アナログ情報記憶手段は、第1の、連続する2つのデューティサイクルに対応する出力電圧間の電圧差を特定するための第1のユニット、および第2の、連続する2つのデューティサイクルに対応する出力電圧間の電圧差を特定するための第2のユニットを有しており、第2の、連続する2つのデューティサイクルのうちの少なくとも1つは、第1の、連続する2つのデューティサイクルに続くデューティサイクルである。

【0026】

別の一態様によれば、第1および第2のユニットの各々は、並列回路の一部を構成している少なくとも1つの第1のブランチと少なくとも1つの第2のブランチとを備えており、第1および第2のブランチの各々は、それぞれ1つのキャパシタを有しており、かつ少なくとも1つのスイッチを介して、電気エネルギー源の出力端子に接続可能であり、第1のブランチのキャパシタと第2のブランチのキャパシタとは、それらに蓄積される電荷の平衡、および第1または第2の、連続する2つのデューティサイクルに対する電圧差の特定のために互いに並列に接続可能である。

【0027】

一代替例として、アナログ情報記憶手段は、スイッチを介して、連続する第1および第3のデューティサイクルに対して、電気エネルギー源からの出力電圧に対応する電荷を蓄積するように構成されているキャパシタを有している第1のブランチと、スイッチを介して、連続する第1と第3とのデューティサイクルの間に挿入されている第2のデューティサイクルに対して、電気エネルギー源からの出力電圧に対応する電荷を蓄積するように構成されているキャパシタを有している第2のブランチとを備えており、第1および第2のブランチの各々は、アナログ比較ユニットの対応する入力に接続されており、第2のブランチの重みは、第1のブランチの重みの2倍である。

【0028】

第1の変形例において、第1のブランチは、分圧ブリッジを介して、電気エネルギー源に接続されるように作られている。

【0029】

第2の変形例において、第2のブランチは、第2のデューティサイクルに対して、第2のブランチのキャパシタに誘起される電荷を2倍にするスイッチ回路を有している。

【0030】

さらなる一態様においては、アナログ比較ユニットは、コンパレータとして構成されている演算増幅器である。

【0031】

制御ループ形成手段は、例えばデューティサイクルの変更に続く、あらかじめ定められた整定時間の後に、電気エネルギー源の出力電圧を特定するように構成されている。

【0032】

別の一態様においては、制御ユニットは、あらかじめ定められた量だけのデューティサイクルの変更を、制御ループ形成手段からの設定値信号に応じて制御する手段を、さらに備えている。

【0033】

さらなる別の一態様においては、制御ユニットは、設定値信号が正の極性を有している場合に、あらかじめ定められた量だけのデューティサイクルの増加を命令するように構成されている。

【0034】

制御ユニットは、設定値信号が負の極性を有している場合に、あらかじめ定められた量だけのデューティサイクルの増加を命令するように構成されている場合もある。

【0035】

最後に、別の一態様においては、制御ユニットは、論理ブロックだけで構成されている。

【0036】

本発明は、さらに、送出される電力が大きく変動し得る少なくとも1つの電気エネルギー源と、この少なくとも1つの電気エネルギー源に接続されている少なくとも1つの、上述のコンバータ回路とを備えている電子システムを提供するものである。

【0037】

一態様においては、電気エネルギー源は、太陽電池、風力発電装置、熱電素子によって構成されているグループのなかの少なくとも1つのものを有している。

【図面の簡単な説明】

【0038】

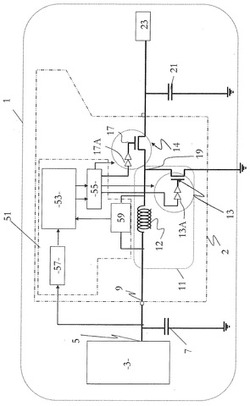

【図1】本発明のコンバータ回路を備えている電子システムのブロック図である。

【図2】図1のコンバータ回路の第1の実施形態の部分詳細図である。

【図3】図2のアナログ情報記憶手段の一実施例を示す回路図である。

【図4】図3のスイッチの切り替えのタイミング図である。

【図5】図1のコンバータ回路の第2の実施形態の部分詳細図である。

【図6】図5のアナログ情報記憶手段の一実施例を示す回路図である。

【図7】図6のスイッチの切り替えのタイミング図である。

【図8】図5のアナログ情報記憶手段の別の一実施例を示す回路図である。

【発明を実施するための形態】

【0039】

添付図面を参照して、以下の説明を読むことによって、本発明の他の特徴および利点が明らかになると思う。

【0040】

図1は、コンバータ回路2、およびコンバータ回路2に接続されている電気エネルギー源3を備えている電子システム1の一例を示す。

【0041】

送出される電力に大きな変動を示し得る電気エネルギー源3は、例えば太陽電池または太陽電池パネル、熱電素子、または風力発電装置(特に小型のユニットの)である。

【0042】

用語「大きな変動」は、図1に示されているような電気エネルギー源3から送出することができる電力が、その最低値と最高値との間で約100倍だけ変動することを意味している。

【0043】

電気エネルギー源3の出力端子5は、キャパシタによって形成されているローパスフィルタ7を介して、コンバータ回路2の入力端子9に接続されている。

【0044】

コンバータ回路2は、デューティサイクルαが可変であるチョッパ回路11を有しており、チョッパ回路11の入力端子は、電気エネルギー源3に接続されている、コンバータ回路2の入力端子9を形成している。

【0045】

チョッパ回路11は、電気エネルギー蓄積インダクタ12、および少なくとも1つのチョッパスイッチ13を備えている。

【0046】

図1において、電気エネルギー蓄積インダクタ12およびチョッパスイッチ13は、昇圧構造に構成されている。すなわち、電気エネルギー蓄積インダクタ12の入力が電気エネルギー源3に接続されており、かつチョッパスイッチ13が「オン」状態にあるときに、電気エネルギー蓄積インダクタ12の出力が接地されて、電気エネルギー蓄積インダクタ12の周囲に磁界が形成されている。チョッピング周波数は、例えば200kHzである。

【0047】

図示しない一変形例によれば、電気エネルギー蓄積インダクタ12およびチョッパスイッチ13は、降圧構造に配置されている場合もある。

【0048】

コンバータ回路は、さらに、出力回路14を備えている。

【0049】

この出力回路14は、その上流側で、チョッパスイッチ17を、チョッパ回路11の出力端子19に接続されている。

【0050】

この出力回路14は、その下流側で、ローパスフィルタ21を介して、電子システム1に属する電気的な負荷23に接続されている。

【0051】

コンバータ回路2は、制御回路51によって駆動される。

【0052】

制御回路51は、第1に、チョッパ回路11したがってチョッパスイッチ13のデューティサイクルαを制御し、第2に、チョッパスイッチ17のスイッチングを制御する制御ユニット53を備えている。

【0053】

これらの制御を行うために、制御ユニット53は、チョッパスイッチ13および17を制御する命令発生器(DTCLユニット、すなわちデッドタイム制御ロジックユニットとも呼ばれる)55を制御するために、PWM(パルス幅変調)信号を出力する。

【0054】

チョッパスイッチ13は、NMOSタイプのトランジスタであり、そのベースは、バッファ(遅延線とも呼ばれる)13Aを介して、命令発生器55の対応する出力に接続されていることに注意されたい。

【0055】

チョッパスイッチ17は、PMOSタイプのトランジスタであり、そのベースは、バッファ17Aを介して、命令発生器55の対応する出力に接続されている。

【0056】

制御回路51は、さらに、送出される電力が変動し得る電気エネルギー源3の出力端子5に接続されている、電気エネルギー源3の最大電力点を追尾するように働く制御ループ制御手段57を備えている。

【0057】

制御ループ形成手段57の出力は、制御ユニット53の1つの入力に接続されている。この制御ユニット53は、制御ループ形成手段57からの設定値信号にしたがって、一定時間間隔で、チョッパ回路11のデューティサイクルαの変更を命令するように構成されており、次に詳細に説明される。

【0058】

制御ループ形成手段57が、デューティサイクルαを増減させるために、設定値信号を直接に送出する場合には、制御ユニット53を、単純な論理ブロックで形成することができる。その結果、コンバータ回路2は、電気エネルギー消費量および空間要求の面から、主要なコスト増大源である、いかなるマイクロプロセッサも備える必要がなくなる。

【0059】

チョッパスイッチ17の制御のために、制御回路51は、電気エネルギー蓄積インダクタ12を通る電流のキャンセルを特定する電流零点センサ59を備えている。電流零点センサ59は、制御ユニット53の対応する入力に信号を送出する。

【0060】

図示しない一変形例によれば、電流零点センサを、スイッチに並列に配置された、非常に低い電圧閾値を有するダイオードと置き換えることが可能である。

【0061】

動作特性として、制御ユニット53は、次のようになるように、命令発生器55を制御する。

− チョッパスイッチ13が閉じられている(オン状態)とき、チョッパスイッチ17は開かれており(オフ状態)、

− チョッパスイッチ17が閉じられている(オン状態)とき、チョッパスイッチ13は開かれている(オフ状態)。

【0062】

したがって、任意の時点において、チョッパスイッチ13と17とのうちのいずれか一方しか閉じられない。

【0063】

不連続動作モードで、チョッパ回路11を制御するように、制御回路を構成することができる。すなわち、電気エネルギー蓄積インダクタ12中の電流は、周期的にキャンセルされる。

【0064】

次に、制御ループ形成手段57について、より詳細に説明する。

【0065】

図2は、図1の電子システムの部分詳細図である。

【0066】

制御ループ形成手段57は、連続する少なくとも3つのデューティサイクル(αi-1、αi、αi+1)に対する、電気エネルギー源3の出力電圧に対応する情報をアナログ的に記憶するためのアナログ情報記憶手段60、およびアナログ的に記憶されたこれらの情報から作られた、制御ユニット53によるデューティサイクルの増減に用いられる設定値信号を出力から送出するアナログ比較ユニット62を備えている。

【0067】

より詳細には、アナログ情報記憶手段60は、第1の、連続する2つのデューティサイクル(αi-1、αi)に対応する出力電圧間の電圧差を特定するための第1のユニット64、および第2の、連続する2つのデューティサイクル(αi、αi+1)に対応する出力電圧間の電圧差を特定するための第2のユニット66を有している。単純化のために、第1のユニット64と第2のユニット66には、互いに同一の特性を有するものが選ばれている。

【0068】

しかしながら、第1のユニット64は、第1の、連続する2つのデューティサイクル(αi-1、αi)に対応する第1の電圧差を特定するように構成されている。したがって、第1のユニット64は、次のものを特定する。

ΔViS=|VS(αi)−VS(αi-1)|

【0069】

一方、第2のユニット66は、第2の、連続する2つのデューティサイクル(αi、αi+1)に対応する第2の電圧差を特定するように構成されている。第2の、連続する2つのデューティサイクル(αi、αi+1)のうちの少なくとも1つ(αi+1)は、第1の、連続する2つのデューティサイクル(αi-1、αi)に続くデューティサイクルである。

【0070】

したがって、第2のユニット66は、次のものを特定する。

ΔVi+1S=|VS(αi+1)−VS(αi)|

【0071】

第1および第2のユニット64および66の各出力は、アナログ比較ユニット62の対応する入力に接続されている。アナログ比較ユニット62は、例えばコンパレータ68として構成されている演算増幅器である。このコンパレータ68は、例えば消費電力を制限することができるラッチコンパレータである。

【0072】

図3は、第1のユニット64または第2のユニット66の一実施例を示している。

【0073】

図3の回路の一般原理として、この回路は、与えられた時点において、電気エネルギー源3の第1の出力電圧VSに対応する第1の電荷量を、第1のキャパシタC1に蓄積することができ、次に、デューティサイクルαの変更後の与えられた時点において、電気エネルギー源3の第2の出力電圧VSに対応する第2の電荷量を、第2のキャパシタC2に蓄積することができる。次いで、相異なる2つのデューティサイクルに対して得られた2つの出力電圧間の電圧差を表わす、2つのキャパシタC1およびC2に蓄積されている電荷を平衡させるために、2つのキャパシタC1とC2とは、並列に接続される。

【0074】

当然ながら、デューティサイクルのそれぞれの変更後、キャパシタに電荷を蓄積させる前に、あらかじめ定められた整定時間だけの待機がなされる。

【0075】

より詳細には、図3に示すように、第1のユニット64および第2のユニット66の各々は、並列回路の一部を構成している少なくとも1つの第1のブランチ70と少なくとも1つの第2のブランチ72とを有している。

【0076】

第1のブランチ70、第2のブランチ72は、それぞれ同じ容量値のキャパシタC1、C2を有している。

【0077】

2つのスイッチH1をオン状態にすることによって、これらの2つのスイッチH1を介して、キャパシタC1を、その一端において電気エネルギー源3の出力電圧VSに、他端においてオフセット電圧2×VOFFSETに接続することができる。

【0078】

スイッチH2をオン状態にすることによって、このスイッチH2を介して、キャパシタC2を、その一端において電気エネルギー源3の出力電圧VSに接続することができる。キャパシタC2の他端は、接地電位GNDに接続されている。

【0079】

さらに、2つのスイッチH3をオン状態にすることによって、これらの2つのスイッチH3を介して、第1のブランチ70と第2のブランチ72とを、互いに並列に接続することができる。

【0080】

キャパシタC1の1つの端子に、電気エネルギー源3の出力電圧VSが印加され、次に、デューティサイクルの変更後に、キャパシタC2の反対側の端子に、出力電圧VSが印加される。そうすると、キャパシタC1とC2との電荷を平衡させることによって、第1のユニット64または第2のユニット66の出力に、電圧差ΔVSが現れることに注意されたい。

【0081】

実際、C1=C2=Cであると仮定し、さらに、スイッチH1、H2、H3の制御、およびデューティサイクルの変更〔αi=αi-1±Δα(ただし、Δα>0)〕の、図4に示されているタイミング図を考えると、時刻tjにおいて、2つのスイッチH1が「オン」状態に切り替えられて、電荷Qi-1=C×(2×VOFFSET−Vi-1S)がキャパシタC1に蓄積され、次いで、時刻tj+1において、デューティサイクルが変更される。

【0082】

整定時間の後、時刻tj+2において、スイッチH2が閉じられ、電荷Qi=C×ViSが、キャパシタC2に蓄積される。

【0083】

最後に、時刻tj+3において、2つのスイッチH3が閉じられる。これによって、電荷の平衡がもたらされ、その結果、出力の電圧値として、ΔViS=(Qi-1+Qi)/2C=VOFFSET+(ViS−Vi-1S)/2が得られる。

【0084】

この説明は、第1の、連続する2つのデューティサイクル(αi-1、αi)に対応する第1の電圧差を特定する、例えば第1のユニット64によって行われるサイクルに対するものである。

【0085】

第2のユニット66も同様に動作し、そのスイッチH1のオン状態への切り替えを、第1のユニット64が、そのスイッチH2および/またはH3を閉じられているときのデューティサイクルαiにおいて行うことができる。

【0086】

当然ながら、デューティサイクルのリフレッシュ周波数(約10Hz)は、チョッピング周波数(約100Hz)よりはるかに低いから、適切な周波数分周器を用いることによって、チョッパ回路11を制御するクロック発生器を、スイッチH1、H2、H3の制御に利用することができる。

【0087】

第1のユニット64および第2のユニット66の出力は、それぞれコンパレータ68の対応する入力に接続されている。したがって、コンパレータ68の出力信号は、ΔVi+1SとΔViSとの差の符号と一致する。

【0088】

デューティサイクルαを調整するために、制御ユニット53が、あらかじめ定められた量Δα(ただしΔα>0)だけの、デューティサイクルαi+2の増減を行うために必要なものは、電気エネルギー源3の出力電圧に対応する情報だけである。すなわち、次のようになる。

ΔVi+1S−ΔViS>0のとき、αi+2=αi+1+Δα:Δα>0

ΔVi+1S−ΔViS<0のとき、αi+2=αi+1−Δα:Δα>0

【0089】

したがって、電気エネルギーをほとんど消費しない完全なアナログ回路を用いることによって、MPPTのための効率的な制御ループ形成手段を得ることができ、それによって、マイクロコントローラを不要にすることができる。

【0090】

したがって、コンバータ回路2は、電気エネルギー源3の出力電圧を、最大電力点(MPP)の近傍で揺らし、それによって、電気エネルギー源3で利用可能な最高レベルの電力の収集を確実にする。

【0091】

さらに、Δαの値が小さいほど、この電子システムは、最大電力点のより近傍で動作することができることは理解されるであろう。この場合に、デューティサイクルが、動作状態の変化に、より迅速に順応することができるようにしたい場合には、リフレッシュ周波数は、より高く選ばれる。

【0092】

次に、第2の実施形態による、図1の制御ループ形成手段57の詳細を示している図5を参照する。

【0093】

この実施形態においては、アナログ情報記憶手段60は、単一ユニット80で構成されており、その例示的な一構造が、図6に示されている。

【0094】

図5および図6の回路の一般原理は、連続する3つのデューティサイクルαi-1、αi、αi+1のそれぞれに対して、電気エネルギー源3の出力電圧Vi-1S、ViS、Vi+1Sを測定することができるという考えに基づいている。

【0095】

デューティサイクルの変更のためには、3つのデューティサイクル間の電圧差の推移の符号、すなわち、次式で定義されるδVSの符号が分かるだけで十分である。

δVS=ΔVi+1S-ΔViS=(Vi+1S-ViS)-(ViS-Vi-1S)=Vi+1S+Vi-1S-2ViS

【0096】

この符号の判定は、図6の回路によって行われる。

【0097】

連続する少なくとも3つのデューティサイクル(αi-1、αi、αi+1)に対して、電気エネルギー源の出力電圧に対応する情報をアナログ的に記憶するアナログ情報記憶手段60は、スイッチを介して、連続する第1および第3のデューティサイクル(αi-1、αi+1)に対して、電気エネルギー源からの出力電圧に対応する電荷を蓄積するように構成されているキャパシタを有している第1のブランチ82、およびスイッチを介して、連続する第1と第3とのデューティサイクル(αi-1、αi+1)の間に挿入されている第2のデューティサイクルαiに対して、電気エネルギー源からの出力電圧に対応する電荷を蓄積するように構成されているキャパシタを有している第2のブランチ84を備えている。

【0098】

各ブランチは、アナログ比較ユニット62の対応する入力に接続されている。第2のブランチの重みは、第1のブランチの重みの2倍である。

【0099】

第1のブランチ82は、電気エネルギー源3の出力電圧VSを2分割するために、例えば同一の抵抗値を有する2つの抵抗Rによって形成されている分圧ブリッジを介して、電気エネルギー源3に接続されている。

【0100】

第1のブランチ82、第2のブランチ84は、それぞれ同一の容量値を有するキャパシタC1、C2を有している。

【0101】

2つのスイッチH1または2つのスイッチH3(スイッチH3の1つはスイッチH1の1つと共通である)をオン状態にすることによって、これらのスイッチおよび抵抗Rを介して、キャパシタC1を、電気エネルギー源3の出力電圧VSおよび接地電位GNDに接続することができる。

【0102】

全てのスイッチH1がオン状態にあるときには、キャパシタC1の第1の端子に出力電圧VSの半分が印加され、一方、全てのスイッチH3がオン状態にあるときには、同じキャパシタC1の反対側の端子に出力電圧VSの半分が印加される。したがって、スイッチH1をオン状態にした後で、スイッチH3をオン状態にすることによって、相異なる2つの時点において得られた出力電圧VSの和の半分が、コンパレータ68の、第1のブランチ側の入力に現れることに注意されたい。

【0103】

スイッチH2がオン状態にあるときには、スイッチH2を介して、キャパシタC2を、その第1の端子において電気エネルギー源3の出力電圧VSに、第2の端子において接地電位GNDに接続することができる。

【0104】

動作特性として、C1=C2=Cであると仮定し、さらに、図7に示されている、スイッチH1、H2、H3の制御、およびデューティサイクルの変更〔αi=αi-1±Δα(ただし、Δα>0)〕のタイミング図を考えると、時刻tjにおいて、全てのスイッチH1が「オン」状態に切り替えられて、電荷Qi-1=C×Vi-1S/2がキャパシタC1に蓄積され、次いで、時刻tj+1において、デューティサイクルが変更される。

【0105】

整定時間の後、時刻tj+2において、スイッチH2が閉じられて、電荷Qi=C×ViSがキャパシタC2に蓄積され、次いで、時刻tj+3において、デューティサイクルが変更される。

【0106】

最後に、再度の整定時間の後に、時刻tj+4において、全てのスイッチH3が閉じられる。その結果、コンパレータ68の、第1のブランチ82側の入力に、電圧(Vi+1S+Vi-1S)/2が現れる。一方、コンパレータ68の、第2のブランチ84側の入力には、電圧ViSが、時刻tj+2から印加されている。

【0107】

コンパレータ68はラッチコンパレータであるから、コンパレータ68の出力を有効にするために、スイッチH3に対する切り替え信号を用いることができる。

【0108】

したがって、コンパレータ68の出力において、ΔVi+1SとΔViSとの差の符号に対応する出力信号が得られる。

【0109】

その後、デューティサイクルαの調整が、第1の実施形態に対する上述の説明と同様に行われる。

【0110】

図8は、この第2の実施形態の一変形例を示している。この変形例は、第2のブランチ84が、第2のデューティサイクルαiに対して、キャパシタに誘起される電荷を2倍にするためのスイッチ回路を有しているという点で、図6の実施形態と異なっている。この変形例は、図7のタイミング図と同じタイミング図にしたがって動作する。

【0111】

より詳細には、第1のブランチ82は、電気エネルギー源の出力電圧VSに直接接続されており、一方、第2のブランチ84は、さらなるキャパシタC3およびスイッチH3を有している。

【0112】

第2のブランチ84の動作特性として、スイッチH2を閉じることによって、キャパシタC2およびC3が帯電し、次に、この第2のブランチ84のスイッチH3を閉じることによって、コンパレータ68の、第2のブランチ84側の入力に、電圧2×ViSが現れる。一方、コンパレータ68の、第1のブランチ82側の入力には、最終的に、第2の実施形態と同様に、しかしながら分圧ブリッジが存在しないために、電圧(Vi+1S+Vi-1S)が現れる。

【0113】

本発明の範囲を逸脱することなく、種々の変形例を導出することが可能であることは明らかである。

【0114】

例えばキャパシタC1、C2、C3を、それらの容量値が同一ではないように選ぶことができる。さらに、コンパレータ68の応答特性および/または入力特性を、より効率的にするように、バイアス電圧を適応させる、または加えることができる。

【0115】

さらに、コンパレータ68は、非ラッチ型のコンパレータである場合がある。ラッチコンパレータは、サンプル値の更新の間のみ動作する。これによって、サンプリング間隔が長い(低周波でサンプリングが行われる)場合に、アナログ比較ユニットの電力消費を抑えることができる。

【0116】

本明細書に示されているアーキテクチャおよび回路において、ダブラーおよびデバイダーのブロックを、従来の電圧ダブラーシステム(電荷ポンプなど)、または演算増幅器を用いる公知のアーキテクチャに置き換えることが十分に可能である。

【0117】

本発明のコンバータ回路は、低コストおよび低消費電力の効率的な、MPPTのための制御ループ発生手段を備えているものである。この特徴から、本発明のコンバータ回路は、特に小型の電子システムにおける使用に適している。

【符号の説明】

【0118】

1 電子システム

2 コンバータ回路

3 電気エネルギー源

5、19 出力端子

7、21 ローパスフィルタ

9 入力端子

11 チョッパ回路

12 電気エネルギー蓄積インダクタ

13、17 チョッパスイッチ

13A、17A バッファ

14 出力回路

23 電気的な負荷

51 制御回路

53 制御ユニット

55 命令発生器

57 制御ループ形成手段

59 電流零点センサ

60 アナログ情報記憶手段

62 アナログ比較ユニット

64 第1のユニット

66 第2のユニット

68 コンパレータ

70、82 第1のブランチ

72、84 第2のブランチ

80 単一ユニット

【技術分野】

【0001】

本発明は、コンバータ回路、およびこのコンバータ回路を備える電子システムに関する。

【0002】

二酸化炭素排出によってもたらされる有害な温室効果を軽減するために、再生可能エネルギー源の使用を継続的に増大させるという目的で、近年、太陽電池パネルの開発が著しく進められている。

【0003】

このことは、風力や熱電などの再生可能エネルギー源にも当てはまる。

【0004】

これらの再生可能エネルギー源は、出力される電気エネルギーが、エネルギーを供給する自然現象に応じて、極端に変動するという特殊な性質を有している。また、太陽電池発電装置は、極めて非線形な電流−電圧特性I=f(U)を有する発電装置である。したがって、太陽光照射値が同じであっても、送出される電力は、負荷に応じて変化する。

【0005】

すなわち、効率、したがって太陽電池から送出される電力は、1日を通じて変化する太陽光線の向きだけではなく、例えば雲または他の気象現象によって生じる日陰による日光の遮蔽状態に依存する。

【0006】

太陽電池が、例えば電力消費部品などの負荷(例えばセンサまたは再充電されるバッテリ)に接続されている場合に、負荷に伝達される電力は、一般に、太陽電池が送出することができる最大電力に一致しないということがこれまでに明らかになっている。同様の問題が、風力エネルギーの場合にも発生することが知られている。そのため、例えば日光が弱くなると、効率が低下するだけではなく、与えられた動作点が、太陽電池の有する潜在能力を発揮することができる動作点より劣る位置に設定されることによって、効率は悪化する。

【0007】

このような欠点を克服し、最適動作点に可能な限り近い動作点で電気エネルギーを発生させるために、1968年以来開発されてきている最大電力点追尾(MPPT)法として知られている方法を組み込んだ回路が用いられている。これは、非線形な再生可能エネルギー源と任意の負荷との間のより良い接続を提供するための方法である。

【0008】

このような回路は、発電装置、例えば太陽電池を、その最大電力点において動作させ、それによって、効率を改善させるようになっている。

【0009】

したがって、MPPTコントローラは、負荷(例えばバッテリ)と太陽電池パネルとを接続している静的コンバータを、恒久的に負荷に最大電力を供給するように駆動する。

【背景技術】

【0010】

最大電力点追尾、すなわちMPP追尾のために、P&O(Perturbation and Observation)アプローチに基づく方法を適用する手法が公知である。

【0011】

太陽電池への適用の場合には、この手法は、一定電圧U1に対して、発電装置から送出される対応する電力値P1を測定し、次いで、一定期間の後に、電圧U2=U1+ΔUを定めて、再度、対応する電力値P2を測定するアルゴリズムである。その後、電力値P2がP1を超過している場合には、太陽電池の電圧は、電圧U3=U2+ΔUとされ、そうでない場合には、電圧U3=U2−ΔUとされる。

【0012】

しかし、これは、電流の測定を必ず伴い、また無視できない電気エネルギー量を消費する大規模な計算リソースを必要とする。このために、大型の太陽電池機器においては、太陽電池の1つのサブグループが、MPPT回路を制御するために必要な電気エネルギーの供給に専用に用いられる。

【0013】

しかし、例えば自律センサなどの電子マイクロシステムにおいては、空間要求と重量に関する制約が大きく、自律性の拡張によって、システムを可能な限り小さくすることが必要であるため、このアプローチを適用することはできない。

【0014】

さらに、さらなる駆動セルを有する最大電力点追尾回路が公知である。しかし、これは、必ずしも望ましいとは限らない。

【0015】

一定周波数で、太陽電池パネルと、回路の残りの部分との間の接続を切って、開回路において電圧を測定することによって遂行される、開回路での電圧サンプリングに基づく、駆動セルを用いないMPPT回路も存在する。このシステムは、その後、新しく最適化されたパラメータを取り入れたエネルギー収集回路に、太陽電池パネルを再接続する。しかしながら、これによって、エネルギー収集プロセスは、頻繁に中断される。これは、自律的に動作するように作られている電子マイクロシステムにとっては受け入れがたいことである。

【0016】

最後に、電圧測定に基づいたMPP追尾法について開示している非特許文献1による公知の方法が存在する。

【0017】

この非特許文献1は、デューティサイクルに関する、電気エネルギー源の動作電圧の微分係数は、最大電力点(MPP)の近傍において最大値を有することを開示している。したがって、動作電圧の微分係数の最大値を追尾することは、最大電力点を追尾することと等価である。

【0018】

したがって、単純な電圧測定、減算操作および比較操作によって、コンバータを、最大電力点(MPP)の近傍で動作させることができる。

【0019】

このために、デューティサイクルαは、あらかじめ定められた時間間隔で、例えば約10Hzの周波数で、あらかじめ定められた量Δαだけ変更され、動作電圧の微分係数、すなわちデューティサイクルの変更後に得られる、動作電圧間の電圧差の推移が追尾される。

【先行技術文献】

【非特許文献】

【0020】

【非特許文献1】「A simple single-sensor MPPT solution(単一のセンサを用いる単純なMPPT手法)」、IEEE Transactions on Power Electronics、2007年3月、第22巻、第2号

【発明の概要】

【発明が解決しようとする課題】

【0021】

上述の非特許文献1において、このMPPTのための制御ループ形成手段は、マイクロコントローラによって構成されている。

【0022】

利用可能なエネルギー量が少ないということを前提として、本発明は、この制御ループ形成手段における電気エネルギーの消費量を最適にし、さらに、特に、エネルギーの収集を最適化するとともに、このシステムの空間要求の十分な低減を可能にすることを目的としている。

【課題を解決するための手段】

【0023】

この目的を達成するために、本発明は、送出される電力が大きく変動し得る電気エネルギー源に接続されるように作られ、次のものを備えているコンバータ回路を提供するものである。

− 電気エネルギー源に接続可能な、デューティサイクルが可変であるチョッパ回路。

− チョッパ回路に接続されている少なくとも1つの出力回路。

− 電気エネルギー源の出力端子に接続される、電気エネルギー源の最大電力点を追尾するように動作する制御ループ形成手段。

− 制御ループ形成手段からの設定値信号に応じて、あらかじめ定められた時間間隔で、チョッパ回路のデューティサイクルの変更を命令するように構成されている制御ユニット。

制御ループ形成手段は、連続する少なくとも3つのデューティサイクルに対する、電気エネルギー源からの出力電圧に対応する情報をアナログ的に記憶するためのアナログ情報記憶手段と、アナログ的に記憶されたこの情報に応じて、制御ユニットによるデューティサイクルの増減に用いられる設定値信号を出力から送出するアナログ比較ユニットとを備えている。

【0024】

このコンバータ回路は、次の特性のうちの1つ以上を、単独でまたは組み合わせて有している。

【0025】

一態様によれば、アナログ情報記憶手段は、第1の、連続する2つのデューティサイクルに対応する出力電圧間の電圧差を特定するための第1のユニット、および第2の、連続する2つのデューティサイクルに対応する出力電圧間の電圧差を特定するための第2のユニットを有しており、第2の、連続する2つのデューティサイクルのうちの少なくとも1つは、第1の、連続する2つのデューティサイクルに続くデューティサイクルである。

【0026】

別の一態様によれば、第1および第2のユニットの各々は、並列回路の一部を構成している少なくとも1つの第1のブランチと少なくとも1つの第2のブランチとを備えており、第1および第2のブランチの各々は、それぞれ1つのキャパシタを有しており、かつ少なくとも1つのスイッチを介して、電気エネルギー源の出力端子に接続可能であり、第1のブランチのキャパシタと第2のブランチのキャパシタとは、それらに蓄積される電荷の平衡、および第1または第2の、連続する2つのデューティサイクルに対する電圧差の特定のために互いに並列に接続可能である。

【0027】

一代替例として、アナログ情報記憶手段は、スイッチを介して、連続する第1および第3のデューティサイクルに対して、電気エネルギー源からの出力電圧に対応する電荷を蓄積するように構成されているキャパシタを有している第1のブランチと、スイッチを介して、連続する第1と第3とのデューティサイクルの間に挿入されている第2のデューティサイクルに対して、電気エネルギー源からの出力電圧に対応する電荷を蓄積するように構成されているキャパシタを有している第2のブランチとを備えており、第1および第2のブランチの各々は、アナログ比較ユニットの対応する入力に接続されており、第2のブランチの重みは、第1のブランチの重みの2倍である。

【0028】

第1の変形例において、第1のブランチは、分圧ブリッジを介して、電気エネルギー源に接続されるように作られている。

【0029】

第2の変形例において、第2のブランチは、第2のデューティサイクルに対して、第2のブランチのキャパシタに誘起される電荷を2倍にするスイッチ回路を有している。

【0030】

さらなる一態様においては、アナログ比較ユニットは、コンパレータとして構成されている演算増幅器である。

【0031】

制御ループ形成手段は、例えばデューティサイクルの変更に続く、あらかじめ定められた整定時間の後に、電気エネルギー源の出力電圧を特定するように構成されている。

【0032】

別の一態様においては、制御ユニットは、あらかじめ定められた量だけのデューティサイクルの変更を、制御ループ形成手段からの設定値信号に応じて制御する手段を、さらに備えている。

【0033】

さらなる別の一態様においては、制御ユニットは、設定値信号が正の極性を有している場合に、あらかじめ定められた量だけのデューティサイクルの増加を命令するように構成されている。

【0034】

制御ユニットは、設定値信号が負の極性を有している場合に、あらかじめ定められた量だけのデューティサイクルの増加を命令するように構成されている場合もある。

【0035】

最後に、別の一態様においては、制御ユニットは、論理ブロックだけで構成されている。

【0036】

本発明は、さらに、送出される電力が大きく変動し得る少なくとも1つの電気エネルギー源と、この少なくとも1つの電気エネルギー源に接続されている少なくとも1つの、上述のコンバータ回路とを備えている電子システムを提供するものである。

【0037】

一態様においては、電気エネルギー源は、太陽電池、風力発電装置、熱電素子によって構成されているグループのなかの少なくとも1つのものを有している。

【図面の簡単な説明】

【0038】

【図1】本発明のコンバータ回路を備えている電子システムのブロック図である。

【図2】図1のコンバータ回路の第1の実施形態の部分詳細図である。

【図3】図2のアナログ情報記憶手段の一実施例を示す回路図である。

【図4】図3のスイッチの切り替えのタイミング図である。

【図5】図1のコンバータ回路の第2の実施形態の部分詳細図である。

【図6】図5のアナログ情報記憶手段の一実施例を示す回路図である。

【図7】図6のスイッチの切り替えのタイミング図である。

【図8】図5のアナログ情報記憶手段の別の一実施例を示す回路図である。

【発明を実施するための形態】

【0039】

添付図面を参照して、以下の説明を読むことによって、本発明の他の特徴および利点が明らかになると思う。

【0040】

図1は、コンバータ回路2、およびコンバータ回路2に接続されている電気エネルギー源3を備えている電子システム1の一例を示す。

【0041】

送出される電力に大きな変動を示し得る電気エネルギー源3は、例えば太陽電池または太陽電池パネル、熱電素子、または風力発電装置(特に小型のユニットの)である。

【0042】

用語「大きな変動」は、図1に示されているような電気エネルギー源3から送出することができる電力が、その最低値と最高値との間で約100倍だけ変動することを意味している。

【0043】

電気エネルギー源3の出力端子5は、キャパシタによって形成されているローパスフィルタ7を介して、コンバータ回路2の入力端子9に接続されている。

【0044】

コンバータ回路2は、デューティサイクルαが可変であるチョッパ回路11を有しており、チョッパ回路11の入力端子は、電気エネルギー源3に接続されている、コンバータ回路2の入力端子9を形成している。

【0045】

チョッパ回路11は、電気エネルギー蓄積インダクタ12、および少なくとも1つのチョッパスイッチ13を備えている。

【0046】

図1において、電気エネルギー蓄積インダクタ12およびチョッパスイッチ13は、昇圧構造に構成されている。すなわち、電気エネルギー蓄積インダクタ12の入力が電気エネルギー源3に接続されており、かつチョッパスイッチ13が「オン」状態にあるときに、電気エネルギー蓄積インダクタ12の出力が接地されて、電気エネルギー蓄積インダクタ12の周囲に磁界が形成されている。チョッピング周波数は、例えば200kHzである。

【0047】

図示しない一変形例によれば、電気エネルギー蓄積インダクタ12およびチョッパスイッチ13は、降圧構造に配置されている場合もある。

【0048】

コンバータ回路は、さらに、出力回路14を備えている。

【0049】

この出力回路14は、その上流側で、チョッパスイッチ17を、チョッパ回路11の出力端子19に接続されている。

【0050】

この出力回路14は、その下流側で、ローパスフィルタ21を介して、電子システム1に属する電気的な負荷23に接続されている。

【0051】

コンバータ回路2は、制御回路51によって駆動される。

【0052】

制御回路51は、第1に、チョッパ回路11したがってチョッパスイッチ13のデューティサイクルαを制御し、第2に、チョッパスイッチ17のスイッチングを制御する制御ユニット53を備えている。

【0053】

これらの制御を行うために、制御ユニット53は、チョッパスイッチ13および17を制御する命令発生器(DTCLユニット、すなわちデッドタイム制御ロジックユニットとも呼ばれる)55を制御するために、PWM(パルス幅変調)信号を出力する。

【0054】

チョッパスイッチ13は、NMOSタイプのトランジスタであり、そのベースは、バッファ(遅延線とも呼ばれる)13Aを介して、命令発生器55の対応する出力に接続されていることに注意されたい。

【0055】

チョッパスイッチ17は、PMOSタイプのトランジスタであり、そのベースは、バッファ17Aを介して、命令発生器55の対応する出力に接続されている。

【0056】

制御回路51は、さらに、送出される電力が変動し得る電気エネルギー源3の出力端子5に接続されている、電気エネルギー源3の最大電力点を追尾するように働く制御ループ制御手段57を備えている。

【0057】

制御ループ形成手段57の出力は、制御ユニット53の1つの入力に接続されている。この制御ユニット53は、制御ループ形成手段57からの設定値信号にしたがって、一定時間間隔で、チョッパ回路11のデューティサイクルαの変更を命令するように構成されており、次に詳細に説明される。

【0058】

制御ループ形成手段57が、デューティサイクルαを増減させるために、設定値信号を直接に送出する場合には、制御ユニット53を、単純な論理ブロックで形成することができる。その結果、コンバータ回路2は、電気エネルギー消費量および空間要求の面から、主要なコスト増大源である、いかなるマイクロプロセッサも備える必要がなくなる。

【0059】

チョッパスイッチ17の制御のために、制御回路51は、電気エネルギー蓄積インダクタ12を通る電流のキャンセルを特定する電流零点センサ59を備えている。電流零点センサ59は、制御ユニット53の対応する入力に信号を送出する。

【0060】

図示しない一変形例によれば、電流零点センサを、スイッチに並列に配置された、非常に低い電圧閾値を有するダイオードと置き換えることが可能である。

【0061】

動作特性として、制御ユニット53は、次のようになるように、命令発生器55を制御する。

− チョッパスイッチ13が閉じられている(オン状態)とき、チョッパスイッチ17は開かれており(オフ状態)、

− チョッパスイッチ17が閉じられている(オン状態)とき、チョッパスイッチ13は開かれている(オフ状態)。

【0062】

したがって、任意の時点において、チョッパスイッチ13と17とのうちのいずれか一方しか閉じられない。

【0063】

不連続動作モードで、チョッパ回路11を制御するように、制御回路を構成することができる。すなわち、電気エネルギー蓄積インダクタ12中の電流は、周期的にキャンセルされる。

【0064】

次に、制御ループ形成手段57について、より詳細に説明する。

【0065】

図2は、図1の電子システムの部分詳細図である。

【0066】

制御ループ形成手段57は、連続する少なくとも3つのデューティサイクル(αi-1、αi、αi+1)に対する、電気エネルギー源3の出力電圧に対応する情報をアナログ的に記憶するためのアナログ情報記憶手段60、およびアナログ的に記憶されたこれらの情報から作られた、制御ユニット53によるデューティサイクルの増減に用いられる設定値信号を出力から送出するアナログ比較ユニット62を備えている。

【0067】

より詳細には、アナログ情報記憶手段60は、第1の、連続する2つのデューティサイクル(αi-1、αi)に対応する出力電圧間の電圧差を特定するための第1のユニット64、および第2の、連続する2つのデューティサイクル(αi、αi+1)に対応する出力電圧間の電圧差を特定するための第2のユニット66を有している。単純化のために、第1のユニット64と第2のユニット66には、互いに同一の特性を有するものが選ばれている。

【0068】

しかしながら、第1のユニット64は、第1の、連続する2つのデューティサイクル(αi-1、αi)に対応する第1の電圧差を特定するように構成されている。したがって、第1のユニット64は、次のものを特定する。

ΔViS=|VS(αi)−VS(αi-1)|

【0069】

一方、第2のユニット66は、第2の、連続する2つのデューティサイクル(αi、αi+1)に対応する第2の電圧差を特定するように構成されている。第2の、連続する2つのデューティサイクル(αi、αi+1)のうちの少なくとも1つ(αi+1)は、第1の、連続する2つのデューティサイクル(αi-1、αi)に続くデューティサイクルである。

【0070】

したがって、第2のユニット66は、次のものを特定する。

ΔVi+1S=|VS(αi+1)−VS(αi)|

【0071】

第1および第2のユニット64および66の各出力は、アナログ比較ユニット62の対応する入力に接続されている。アナログ比較ユニット62は、例えばコンパレータ68として構成されている演算増幅器である。このコンパレータ68は、例えば消費電力を制限することができるラッチコンパレータである。

【0072】

図3は、第1のユニット64または第2のユニット66の一実施例を示している。

【0073】

図3の回路の一般原理として、この回路は、与えられた時点において、電気エネルギー源3の第1の出力電圧VSに対応する第1の電荷量を、第1のキャパシタC1に蓄積することができ、次に、デューティサイクルαの変更後の与えられた時点において、電気エネルギー源3の第2の出力電圧VSに対応する第2の電荷量を、第2のキャパシタC2に蓄積することができる。次いで、相異なる2つのデューティサイクルに対して得られた2つの出力電圧間の電圧差を表わす、2つのキャパシタC1およびC2に蓄積されている電荷を平衡させるために、2つのキャパシタC1とC2とは、並列に接続される。

【0074】

当然ながら、デューティサイクルのそれぞれの変更後、キャパシタに電荷を蓄積させる前に、あらかじめ定められた整定時間だけの待機がなされる。

【0075】

より詳細には、図3に示すように、第1のユニット64および第2のユニット66の各々は、並列回路の一部を構成している少なくとも1つの第1のブランチ70と少なくとも1つの第2のブランチ72とを有している。

【0076】

第1のブランチ70、第2のブランチ72は、それぞれ同じ容量値のキャパシタC1、C2を有している。

【0077】

2つのスイッチH1をオン状態にすることによって、これらの2つのスイッチH1を介して、キャパシタC1を、その一端において電気エネルギー源3の出力電圧VSに、他端においてオフセット電圧2×VOFFSETに接続することができる。

【0078】

スイッチH2をオン状態にすることによって、このスイッチH2を介して、キャパシタC2を、その一端において電気エネルギー源3の出力電圧VSに接続することができる。キャパシタC2の他端は、接地電位GNDに接続されている。

【0079】

さらに、2つのスイッチH3をオン状態にすることによって、これらの2つのスイッチH3を介して、第1のブランチ70と第2のブランチ72とを、互いに並列に接続することができる。

【0080】

キャパシタC1の1つの端子に、電気エネルギー源3の出力電圧VSが印加され、次に、デューティサイクルの変更後に、キャパシタC2の反対側の端子に、出力電圧VSが印加される。そうすると、キャパシタC1とC2との電荷を平衡させることによって、第1のユニット64または第2のユニット66の出力に、電圧差ΔVSが現れることに注意されたい。

【0081】

実際、C1=C2=Cであると仮定し、さらに、スイッチH1、H2、H3の制御、およびデューティサイクルの変更〔αi=αi-1±Δα(ただし、Δα>0)〕の、図4に示されているタイミング図を考えると、時刻tjにおいて、2つのスイッチH1が「オン」状態に切り替えられて、電荷Qi-1=C×(2×VOFFSET−Vi-1S)がキャパシタC1に蓄積され、次いで、時刻tj+1において、デューティサイクルが変更される。

【0082】

整定時間の後、時刻tj+2において、スイッチH2が閉じられ、電荷Qi=C×ViSが、キャパシタC2に蓄積される。

【0083】

最後に、時刻tj+3において、2つのスイッチH3が閉じられる。これによって、電荷の平衡がもたらされ、その結果、出力の電圧値として、ΔViS=(Qi-1+Qi)/2C=VOFFSET+(ViS−Vi-1S)/2が得られる。

【0084】

この説明は、第1の、連続する2つのデューティサイクル(αi-1、αi)に対応する第1の電圧差を特定する、例えば第1のユニット64によって行われるサイクルに対するものである。

【0085】

第2のユニット66も同様に動作し、そのスイッチH1のオン状態への切り替えを、第1のユニット64が、そのスイッチH2および/またはH3を閉じられているときのデューティサイクルαiにおいて行うことができる。

【0086】

当然ながら、デューティサイクルのリフレッシュ周波数(約10Hz)は、チョッピング周波数(約100Hz)よりはるかに低いから、適切な周波数分周器を用いることによって、チョッパ回路11を制御するクロック発生器を、スイッチH1、H2、H3の制御に利用することができる。

【0087】

第1のユニット64および第2のユニット66の出力は、それぞれコンパレータ68の対応する入力に接続されている。したがって、コンパレータ68の出力信号は、ΔVi+1SとΔViSとの差の符号と一致する。

【0088】

デューティサイクルαを調整するために、制御ユニット53が、あらかじめ定められた量Δα(ただしΔα>0)だけの、デューティサイクルαi+2の増減を行うために必要なものは、電気エネルギー源3の出力電圧に対応する情報だけである。すなわち、次のようになる。

ΔVi+1S−ΔViS>0のとき、αi+2=αi+1+Δα:Δα>0

ΔVi+1S−ΔViS<0のとき、αi+2=αi+1−Δα:Δα>0

【0089】

したがって、電気エネルギーをほとんど消費しない完全なアナログ回路を用いることによって、MPPTのための効率的な制御ループ形成手段を得ることができ、それによって、マイクロコントローラを不要にすることができる。

【0090】

したがって、コンバータ回路2は、電気エネルギー源3の出力電圧を、最大電力点(MPP)の近傍で揺らし、それによって、電気エネルギー源3で利用可能な最高レベルの電力の収集を確実にする。

【0091】

さらに、Δαの値が小さいほど、この電子システムは、最大電力点のより近傍で動作することができることは理解されるであろう。この場合に、デューティサイクルが、動作状態の変化に、より迅速に順応することができるようにしたい場合には、リフレッシュ周波数は、より高く選ばれる。

【0092】

次に、第2の実施形態による、図1の制御ループ形成手段57の詳細を示している図5を参照する。

【0093】

この実施形態においては、アナログ情報記憶手段60は、単一ユニット80で構成されており、その例示的な一構造が、図6に示されている。

【0094】

図5および図6の回路の一般原理は、連続する3つのデューティサイクルαi-1、αi、αi+1のそれぞれに対して、電気エネルギー源3の出力電圧Vi-1S、ViS、Vi+1Sを測定することができるという考えに基づいている。

【0095】

デューティサイクルの変更のためには、3つのデューティサイクル間の電圧差の推移の符号、すなわち、次式で定義されるδVSの符号が分かるだけで十分である。

δVS=ΔVi+1S-ΔViS=(Vi+1S-ViS)-(ViS-Vi-1S)=Vi+1S+Vi-1S-2ViS

【0096】

この符号の判定は、図6の回路によって行われる。

【0097】

連続する少なくとも3つのデューティサイクル(αi-1、αi、αi+1)に対して、電気エネルギー源の出力電圧に対応する情報をアナログ的に記憶するアナログ情報記憶手段60は、スイッチを介して、連続する第1および第3のデューティサイクル(αi-1、αi+1)に対して、電気エネルギー源からの出力電圧に対応する電荷を蓄積するように構成されているキャパシタを有している第1のブランチ82、およびスイッチを介して、連続する第1と第3とのデューティサイクル(αi-1、αi+1)の間に挿入されている第2のデューティサイクルαiに対して、電気エネルギー源からの出力電圧に対応する電荷を蓄積するように構成されているキャパシタを有している第2のブランチ84を備えている。

【0098】

各ブランチは、アナログ比較ユニット62の対応する入力に接続されている。第2のブランチの重みは、第1のブランチの重みの2倍である。

【0099】

第1のブランチ82は、電気エネルギー源3の出力電圧VSを2分割するために、例えば同一の抵抗値を有する2つの抵抗Rによって形成されている分圧ブリッジを介して、電気エネルギー源3に接続されている。

【0100】

第1のブランチ82、第2のブランチ84は、それぞれ同一の容量値を有するキャパシタC1、C2を有している。

【0101】

2つのスイッチH1または2つのスイッチH3(スイッチH3の1つはスイッチH1の1つと共通である)をオン状態にすることによって、これらのスイッチおよび抵抗Rを介して、キャパシタC1を、電気エネルギー源3の出力電圧VSおよび接地電位GNDに接続することができる。

【0102】

全てのスイッチH1がオン状態にあるときには、キャパシタC1の第1の端子に出力電圧VSの半分が印加され、一方、全てのスイッチH3がオン状態にあるときには、同じキャパシタC1の反対側の端子に出力電圧VSの半分が印加される。したがって、スイッチH1をオン状態にした後で、スイッチH3をオン状態にすることによって、相異なる2つの時点において得られた出力電圧VSの和の半分が、コンパレータ68の、第1のブランチ側の入力に現れることに注意されたい。

【0103】

スイッチH2がオン状態にあるときには、スイッチH2を介して、キャパシタC2を、その第1の端子において電気エネルギー源3の出力電圧VSに、第2の端子において接地電位GNDに接続することができる。

【0104】

動作特性として、C1=C2=Cであると仮定し、さらに、図7に示されている、スイッチH1、H2、H3の制御、およびデューティサイクルの変更〔αi=αi-1±Δα(ただし、Δα>0)〕のタイミング図を考えると、時刻tjにおいて、全てのスイッチH1が「オン」状態に切り替えられて、電荷Qi-1=C×Vi-1S/2がキャパシタC1に蓄積され、次いで、時刻tj+1において、デューティサイクルが変更される。

【0105】

整定時間の後、時刻tj+2において、スイッチH2が閉じられて、電荷Qi=C×ViSがキャパシタC2に蓄積され、次いで、時刻tj+3において、デューティサイクルが変更される。

【0106】

最後に、再度の整定時間の後に、時刻tj+4において、全てのスイッチH3が閉じられる。その結果、コンパレータ68の、第1のブランチ82側の入力に、電圧(Vi+1S+Vi-1S)/2が現れる。一方、コンパレータ68の、第2のブランチ84側の入力には、電圧ViSが、時刻tj+2から印加されている。

【0107】

コンパレータ68はラッチコンパレータであるから、コンパレータ68の出力を有効にするために、スイッチH3に対する切り替え信号を用いることができる。

【0108】

したがって、コンパレータ68の出力において、ΔVi+1SとΔViSとの差の符号に対応する出力信号が得られる。

【0109】

その後、デューティサイクルαの調整が、第1の実施形態に対する上述の説明と同様に行われる。

【0110】

図8は、この第2の実施形態の一変形例を示している。この変形例は、第2のブランチ84が、第2のデューティサイクルαiに対して、キャパシタに誘起される電荷を2倍にするためのスイッチ回路を有しているという点で、図6の実施形態と異なっている。この変形例は、図7のタイミング図と同じタイミング図にしたがって動作する。

【0111】

より詳細には、第1のブランチ82は、電気エネルギー源の出力電圧VSに直接接続されており、一方、第2のブランチ84は、さらなるキャパシタC3およびスイッチH3を有している。

【0112】

第2のブランチ84の動作特性として、スイッチH2を閉じることによって、キャパシタC2およびC3が帯電し、次に、この第2のブランチ84のスイッチH3を閉じることによって、コンパレータ68の、第2のブランチ84側の入力に、電圧2×ViSが現れる。一方、コンパレータ68の、第1のブランチ82側の入力には、最終的に、第2の実施形態と同様に、しかしながら分圧ブリッジが存在しないために、電圧(Vi+1S+Vi-1S)が現れる。

【0113】

本発明の範囲を逸脱することなく、種々の変形例を導出することが可能であることは明らかである。

【0114】

例えばキャパシタC1、C2、C3を、それらの容量値が同一ではないように選ぶことができる。さらに、コンパレータ68の応答特性および/または入力特性を、より効率的にするように、バイアス電圧を適応させる、または加えることができる。

【0115】

さらに、コンパレータ68は、非ラッチ型のコンパレータである場合がある。ラッチコンパレータは、サンプル値の更新の間のみ動作する。これによって、サンプリング間隔が長い(低周波でサンプリングが行われる)場合に、アナログ比較ユニットの電力消費を抑えることができる。

【0116】

本明細書に示されているアーキテクチャおよび回路において、ダブラーおよびデバイダーのブロックを、従来の電圧ダブラーシステム(電荷ポンプなど)、または演算増幅器を用いる公知のアーキテクチャに置き換えることが十分に可能である。

【0117】

本発明のコンバータ回路は、低コストおよび低消費電力の効率的な、MPPTのための制御ループ発生手段を備えているものである。この特徴から、本発明のコンバータ回路は、特に小型の電子システムにおける使用に適している。

【符号の説明】

【0118】

1 電子システム

2 コンバータ回路

3 電気エネルギー源

5、19 出力端子

7、21 ローパスフィルタ

9 入力端子

11 チョッパ回路

12 電気エネルギー蓄積インダクタ

13、17 チョッパスイッチ

13A、17A バッファ

14 出力回路

23 電気的な負荷

51 制御回路

53 制御ユニット

55 命令発生器

57 制御ループ形成手段

59 電流零点センサ

60 アナログ情報記憶手段

62 アナログ比較ユニット

64 第1のユニット

66 第2のユニット

68 コンパレータ

70、82 第1のブランチ

72、84 第2のブランチ

80 単一ユニット

【特許請求の範囲】

【請求項1】

送出される電力が大きく変動し得る電気エネルギー源(3)に接続されるコンバータ回路(2)であって、

前記電気エネルギー源(3)に接続可能な、デューティサイクル(α)が可変であるチョッパ回路(11)と、

前記チョッパ回路(11)に接続されている少なくとも1つの出力回路(14)と、

前記電気エネルギー源の出力端子に接続される、前記電気エネルギー源の最大電力点を追尾するように動作する制御ループ形成手段(57)と、

前記制御ループ形成手段(57)からの設定値信号に応じて、あらかじめ定められた時間間隔で、前記チョッパ回路(11)のデューティサイクル(α)の変更を命令するように構成されている制御ユニット(53)とを備えているコンバータ回路(2)において、

前記制御ループ形成手段(57)は、連続する少なくとも3つのデューティサイクル(αi-1、αi、αi+1)に対する、前記電気エネルギー源(3)からの出力電圧に対応する情報をアナログ的に記憶するためのアナログ情報記憶手段(60)と、アナログ的に記憶された前記情報に応じて、前記制御ユニット(53)による前記デューティサイクルの増減に用いられる前記設定値信号を出力から送出するアナログ比較ユニット(62)とを備えているコンバータ回路。

【請求項2】

前記アナログ情報記憶手段(60)は、第1の、連続する2つのデューティサイクル(αi-1、αi)に対応する前記出力電圧間の電圧差を特定するための第1のユニット(64)、および第2の、連続する2つのデューティサイクル(αi、αi+1)に対応する前記出力電圧間の電圧差を特定するための第2のユニット(66)を有しており、前記第2の、連続する2つのデューティサイクル(αi、αi+1)のうちの少なくとも1つ(αi+1)は、前記第1の、連続する2つのデューティサイクル(αi-1、αi)に続くデューティサイクルである、請求項1に記載のコンバータ回路。

【請求項3】

前記第1および第2のユニットの各々は、並列回路の一部を構成している少なくとも1つの第1のブランチ(70)と少なくとも1つの第2のブランチ(72)とを備えており、該第1および第2のブランチの各々は、それぞれ1つのキャパシタ(C1、C2)を有しており、かつ少なくとも1つのスイッチを介して、前記電気エネルギー源の出力端子に接続可能であり、該第1のブランチのキャパシタ(C1)と第2のブランチのキャパシタ(C2)とは、それらに蓄積される電荷の平衡、および前記第1または第2の、連続する2つのデューティサイクルに対する前記電圧差の特定のために互いに並列に接続可能である、請求項2に記載のコンバータ回路。

【請求項4】

前記アナログ情報記憶手段(60)は、スイッチを介して、連続する第1および第3のデューティサイクル(αi-1、αi+1)に対して、前記電気エネルギー源からの出力電圧に対応する電荷を蓄積するように構成されているキャパシタ(C1)を有している第1のブランチ(82)と、スイッチを介して、連続する前記第1と第3とのデューティサイクル(αi-1、αi+1)の間に挿入されている第2のデューティサイクル(αi)に対して、前記電気エネルギー源からの出力電圧に対応する電荷を蓄積するように構成されているキャパシタ(C2)を有している第2のブランチ(84)とを備えており、該第1および第2のブランチ(82、84)の各々は、前記アナログ比較ユニットの対応する入力に接続されており、前記第2のブランチの重みは、前記第1のブランチの重みの2倍である、請求項1に記載のコンバータ回路。

【請求項5】

前記第1のブランチ(82)は、分圧ブリッジを介して、前記電気エネルギー源に接続される、請求項4に記載のコンバータ回路。

【請求項6】

前記第2のブランチ(84)は、前記第2のデューティサイクル(αi)に対して、前記第2のブランチ(84)のキャパシタ(C2)に誘起される電荷を2倍にするためのスイッチ回路を有している、請求項4に記載のコンバータ回路。

【請求項7】

前記アナログ比較ユニット(62)は、コンパレータとして構成されている演算増幅器(68)である、請求項1〜6のいずれか1項に記載のコンバータ回路。

【請求項8】

前記制御ループ形成手段(57)は、前記デューティサイクルの変更に続く、あらかじめ定められた整定時間の後に、前記電気エネルギー源の出力電圧を特定するように構成されている、請求項1〜7のいずれか1項に記載のコンバータ回路。

【請求項9】

前記制御ユニット(53)は、あらかじめ定められた量(Δα)だけの前記デューティサイクル(α)の変更を、前記制御ループ形成手段からの設定値信号に応じて制御する手段を、さらに備えている、請求項1〜8のいずれか1項に記載のコンバータ回路。

【請求項10】

前記制御ユニット(53)は、前記設定値信号が正の極性を有している場合に、前記あらかじめ定められた量(Δα)だけの前記デューティサイクル(α)の増加を命令するように構成されている、請求項9に記載のコンバータ回路。

【請求項11】

前記制御ユニット(53)は、前記設定値信号が負の極性を有している場合に、前記あらかじめ定められた量(Δα)だけの前記デューティサイクル(α)の増加を命令するように構成されている、請求項9に記載のコンバータ回路。

【請求項12】

前記制御ユニット(53)は、論理ブロックだけで構成されている、請求項1〜11のいずれか1項に記載のコンバータ回路。

【請求項13】

送出される電力が大きく変動し得る少なくとも1つの電気エネルギー源(3)と、該少なくとも1つの電気エネルギー源(3)に接続されている少なくとも1つの、請求項1〜12のいずれか1項に記載のコンバータ回路(2)とを備えている電子システム(1)。

【請求項14】

前記電気エネルギー源(3)は、太陽電池、風力発電装置、熱電素子によって構成されているグループのなかの少なくとも1つのものを有している、請求項13に記載の電子システム。

【請求項1】

送出される電力が大きく変動し得る電気エネルギー源(3)に接続されるコンバータ回路(2)であって、

前記電気エネルギー源(3)に接続可能な、デューティサイクル(α)が可変であるチョッパ回路(11)と、

前記チョッパ回路(11)に接続されている少なくとも1つの出力回路(14)と、

前記電気エネルギー源の出力端子に接続される、前記電気エネルギー源の最大電力点を追尾するように動作する制御ループ形成手段(57)と、

前記制御ループ形成手段(57)からの設定値信号に応じて、あらかじめ定められた時間間隔で、前記チョッパ回路(11)のデューティサイクル(α)の変更を命令するように構成されている制御ユニット(53)とを備えているコンバータ回路(2)において、

前記制御ループ形成手段(57)は、連続する少なくとも3つのデューティサイクル(αi-1、αi、αi+1)に対する、前記電気エネルギー源(3)からの出力電圧に対応する情報をアナログ的に記憶するためのアナログ情報記憶手段(60)と、アナログ的に記憶された前記情報に応じて、前記制御ユニット(53)による前記デューティサイクルの増減に用いられる前記設定値信号を出力から送出するアナログ比較ユニット(62)とを備えているコンバータ回路。

【請求項2】

前記アナログ情報記憶手段(60)は、第1の、連続する2つのデューティサイクル(αi-1、αi)に対応する前記出力電圧間の電圧差を特定するための第1のユニット(64)、および第2の、連続する2つのデューティサイクル(αi、αi+1)に対応する前記出力電圧間の電圧差を特定するための第2のユニット(66)を有しており、前記第2の、連続する2つのデューティサイクル(αi、αi+1)のうちの少なくとも1つ(αi+1)は、前記第1の、連続する2つのデューティサイクル(αi-1、αi)に続くデューティサイクルである、請求項1に記載のコンバータ回路。

【請求項3】

前記第1および第2のユニットの各々は、並列回路の一部を構成している少なくとも1つの第1のブランチ(70)と少なくとも1つの第2のブランチ(72)とを備えており、該第1および第2のブランチの各々は、それぞれ1つのキャパシタ(C1、C2)を有しており、かつ少なくとも1つのスイッチを介して、前記電気エネルギー源の出力端子に接続可能であり、該第1のブランチのキャパシタ(C1)と第2のブランチのキャパシタ(C2)とは、それらに蓄積される電荷の平衡、および前記第1または第2の、連続する2つのデューティサイクルに対する前記電圧差の特定のために互いに並列に接続可能である、請求項2に記載のコンバータ回路。

【請求項4】

前記アナログ情報記憶手段(60)は、スイッチを介して、連続する第1および第3のデューティサイクル(αi-1、αi+1)に対して、前記電気エネルギー源からの出力電圧に対応する電荷を蓄積するように構成されているキャパシタ(C1)を有している第1のブランチ(82)と、スイッチを介して、連続する前記第1と第3とのデューティサイクル(αi-1、αi+1)の間に挿入されている第2のデューティサイクル(αi)に対して、前記電気エネルギー源からの出力電圧に対応する電荷を蓄積するように構成されているキャパシタ(C2)を有している第2のブランチ(84)とを備えており、該第1および第2のブランチ(82、84)の各々は、前記アナログ比較ユニットの対応する入力に接続されており、前記第2のブランチの重みは、前記第1のブランチの重みの2倍である、請求項1に記載のコンバータ回路。

【請求項5】

前記第1のブランチ(82)は、分圧ブリッジを介して、前記電気エネルギー源に接続される、請求項4に記載のコンバータ回路。

【請求項6】

前記第2のブランチ(84)は、前記第2のデューティサイクル(αi)に対して、前記第2のブランチ(84)のキャパシタ(C2)に誘起される電荷を2倍にするためのスイッチ回路を有している、請求項4に記載のコンバータ回路。

【請求項7】

前記アナログ比較ユニット(62)は、コンパレータとして構成されている演算増幅器(68)である、請求項1〜6のいずれか1項に記載のコンバータ回路。

【請求項8】

前記制御ループ形成手段(57)は、前記デューティサイクルの変更に続く、あらかじめ定められた整定時間の後に、前記電気エネルギー源の出力電圧を特定するように構成されている、請求項1〜7のいずれか1項に記載のコンバータ回路。

【請求項9】

前記制御ユニット(53)は、あらかじめ定められた量(Δα)だけの前記デューティサイクル(α)の変更を、前記制御ループ形成手段からの設定値信号に応じて制御する手段を、さらに備えている、請求項1〜8のいずれか1項に記載のコンバータ回路。

【請求項10】

前記制御ユニット(53)は、前記設定値信号が正の極性を有している場合に、前記あらかじめ定められた量(Δα)だけの前記デューティサイクル(α)の増加を命令するように構成されている、請求項9に記載のコンバータ回路。

【請求項11】

前記制御ユニット(53)は、前記設定値信号が負の極性を有している場合に、前記あらかじめ定められた量(Δα)だけの前記デューティサイクル(α)の増加を命令するように構成されている、請求項9に記載のコンバータ回路。

【請求項12】

前記制御ユニット(53)は、論理ブロックだけで構成されている、請求項1〜11のいずれか1項に記載のコンバータ回路。

【請求項13】

送出される電力が大きく変動し得る少なくとも1つの電気エネルギー源(3)と、該少なくとも1つの電気エネルギー源(3)に接続されている少なくとも1つの、請求項1〜12のいずれか1項に記載のコンバータ回路(2)とを備えている電子システム(1)。

【請求項14】

前記電気エネルギー源(3)は、太陽電池、風力発電装置、熱電素子によって構成されているグループのなかの少なくとも1つのものを有している、請求項13に記載の電子システム。

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【公開番号】特開2011−258202(P2011−258202A)

【公開日】平成23年12月22日(2011.12.22)

【国際特許分類】

【外国語出願】

【出願番号】特願2011−124736(P2011−124736)

【出願日】平成23年6月3日(2011.6.3)

【出願人】(510132347)コミサリア ア レネルジ アトミク エ オウ エネルジ アルタナティヴ (51)

【Fターム(参考)】

【公開日】平成23年12月22日(2011.12.22)

【国際特許分類】

【出願番号】特願2011−124736(P2011−124736)

【出願日】平成23年6月3日(2011.6.3)

【出願人】(510132347)コミサリア ア レネルジ アトミク エ オウ エネルジ アルタナティヴ (51)

【Fターム(参考)】

[ Back to top ]