コンパレータおよびそれを用いたDC/DCコンバータの制御回路、電子機器

【課題】コンパレータを小型化、および/または、低消費電力化する。

【解決手段】第1電圧V1と第2電圧V2を比較するコンパレータ10が提供される。デプレッション型PチャンネルMOSFETの第1トランジスタM1のソースには、第1電圧V1が、そのゲートには、第2電圧V2が印加される。デプレッション型PチャンネルMOSFETの第2トランジスタM2のソースおよびゲートは、第1トランジスタM1のドレインと接続され、第2トランジスタM2のドレインの電位は固定される。コンパレータ10は、第1トランジスタM1と第2トランジスタM2の接続点N1の電位VN1に応じた出力信号OUTを生成する。

【解決手段】第1電圧V1と第2電圧V2を比較するコンパレータ10が提供される。デプレッション型PチャンネルMOSFETの第1トランジスタM1のソースには、第1電圧V1が、そのゲートには、第2電圧V2が印加される。デプレッション型PチャンネルMOSFETの第2トランジスタM2のソースおよびゲートは、第1トランジスタM1のドレインと接続され、第2トランジスタM2のドレインの電位は固定される。コンパレータ10は、第1トランジスタM1と第2トランジスタM2の接続点N1の電位VN1に応じた出力信号OUTを生成する。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、コンパレータに関する。

【背景技術】

【0002】

2つの電圧の大小関係を判定するために、電圧コンパレータ(以下、単にコンパレータという)が用いられる。一般的なコンパレータは、差動増幅器を用いて構成される。ところが差動増幅器はトランジスタなどの素子数が多いため、回路面積が大きく、また素子のばらつきにより、入力電圧オフセットが発生するという問題がある。オフセット電圧を低減するためには、バイアス電流を増大させる必要があり、これは消費電力の増大という問題を引き起こす。

【発明の概要】

【発明が解決しようとする課題】

【0003】

本発明はかかる課題に鑑みてなされたものであり、そのある態様の例示的な目的のひとつは、コンパレータの小型化、および/または、低消費電力化にある。

【課題を解決するための手段】

【0004】

本発明のある態様は、第1電圧と第2電圧を比較するコンパレータに関する。このコンパレータは、そのソースに第1電圧が印加され、そのゲートに第2電圧が印加されたデプレッション型PチャンネルMOSFETの第1トランジスタと、そのソースおよびそのゲートが、第1トランジスタのドレインと接続され、そのドレインの電位が固定されたデプレッション型PチャンネルMOSFETの第2トランジスタと、を備える。コンパレータは、第1トランジスタと第2トランジスタの接続点の電位に応じた出力信号を生成する。

【0005】

デプレッション型の第2トランジスタのゲートソース間電圧は0Vであり、所定のバイアス電流が流れる。一方、第1トランジスタのゲートソース間電圧は、第1電圧と第2電圧の電位差となる。第1トランジスタのドレインソース間電圧は、第1トランジスタに流れる電流がバイアス電流に近づくように変化する。

第1電圧と第2電圧の電位差がゼロの平衡状態において、第1トランジスタと第2トランジスタのゲートソース間電圧は等しくなるため、第1トランジスタと第2トランジスタそれぞれのドレインソース間電圧は等しくなる。また、第1トランジスタのゲートソース間電圧が負のときには、第1トランジスタのドレインソース間電圧の方が大きくなり、第1トランジスタと第2トランジスタの接続点の電位はローレベルとなる。反対に、第1トランジスタのゲートソース間電圧が正のときには、第1トランジスタのドレインソース間電圧の方が小さくなり、第1トランジスタと第2トランジスタの接続点の電位はハイレベルとなる。したがって、この構成によれば、2つのデプレッション型トランジスタを用いて、電圧比較を行うことができ、差動増幅器を利用したコンパレータに比べて、回路面積を削減でき、および/または、消費電力を低減できる。

【0006】

ある態様のコンパレータは、第1トランジスタと第2トランジスタの接続点の電位を受け、出力信号を出力するバッファもしくはインバータをさらに備えてもよい。

【0007】

本発明の別の態様は、第3電圧と第4電圧を比較するコンパレータに関する。このコンパレータは、そのゲートに第3電圧が印加され、そのソースに第4電圧が印加されたデプレッション型NチャンネルMOSFETの第3トランジスタと、そのソースおよびそのゲートが、第3トランジスタのドレインと接続され、そのドレインの電位が固定されたデプレッション型NチャンネルMOSFETの第4トランジスタと、を備える。コンパレータは、第3トランジスタと第4トランジスタの接続点の電位に応じた出力信号を生成する。

【0008】

デプレッション型の第4トランジスタのゲートソース間電圧は0Vであり、所定のバイアス電流が流れる。一方、第3トランジスタのゲートソース間電圧は、第3電圧と第4電圧の電位差となる。第4トランジスタのドレインソース間電圧は、第4トランジスタに流れる電流がバイアス電流に近づくように変化する。

第3電圧と第4電圧の電位差がゼロの平衡状態において、第3トランジスタと第4トランジスタのゲートソース間電圧は等しくなるため、第3トランジスタと第4トランジスタそれぞれのドレインソース間電圧は等しくなる。また、第3トランジスタのゲートソース間電圧が負のときには、第3トランジスタのドレインソース間電圧の方が大きくなり、第3トランジスタと第4トランジスタの接続点の電位はハイレベルとなる。反対に、第3トランジスタのゲートソース間電圧が正のときには、第3トランジスタのドレインソース間電圧の方が小さくなり、第3トランジスタと第4トランジスタの接続点の電位はローレベルとなる。したがって、この構成によれば、2つのデプレッション型トランジスタを用いて、電圧比較を行うことができ、差動増幅器を利用したコンパレータに比べて、回路面積を削減でき、および/または、消費電力を低減できる。

【0009】

ある態様のコンパレータは、第3トランジスタと第4トランジスタの接続点の電位を受け、出力信号を出力するバッファもしくはインバータをさらに備えてもよい。

【0010】

本発明の別の態様は、スイッチングトランジスタおよび同期整流トランジスタを有する同期整流型昇圧DC/DCコンバータの制御回路に関する。制御回路は、同期整流トランジスタの一端の電位と、同期整流トランジスタの他端の電位を比較し、2つの電位が等しくなるとアサートされる比較信号を生成する上述のいずれかのコンパレータと、DC/DCコンバータの出力電圧が所定の目標値に近づくようにデューティ比が調節されるパルス信号であって、比較信号がアサートされるとオンレベルに遷移するパルス信号を生成するパルス変調器と、パルス信号がオンレベルのときスイッチングトランジスタをオン、オフレベルのとき同期整流トランジスタをオンするドライバと、を備える。

この態様によれば、同期整流トランジスタに流れる電流がゼロとなるタイミングを検出し、スイッチングトランジスタをオンすることができる。

【0011】

本発明の別の態様は、スイッチングトランジスタおよび同期整流トランジスタを有する同期整流型降圧DC/DCコンバータの制御回路に関する。制御回路は、同期整流トランジスタの一端の電位と、同期整流トランジスタの他端の電位を比較し、2つの電位が等しくなるとアサートされる比較信号を生成する上述のいずれかの態様のコンパレータと、DC/DCコンバータの出力電圧が所定の目標値に近づくようにデューティ比が調節されるパルス信号であって、比較信号がアサートされるとオンレベルに遷移するパルス信号を生成するパルス変調器と、パルス信号がオンレベルのときスイッチングトランジスタをオン、オフレベルのとき同期整流トランジスタをオンするドライバと、を備える。

【0012】

この態様によれば、同期整流トランジスタに流れる電流がゼロとなるタイミングを検出し、スイッチングトランジスタをオンすることができる。

【0013】

なお、以上の構成要素の任意の組み合わせや本発明の構成要素や表現を、方法、装置、システムなどの間で相互に置換したものもまた、本発明の態様として有効である。

【発明の効果】

【0014】

本発明によれば、コンパレータを小型化し、および/または、低消費電力化できる。

【図面の簡単な説明】

【0015】

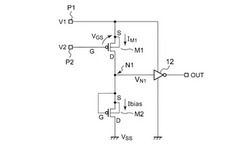

【図1】第1の実施の形態に係るコンパレータの構成を示す回路図である。

【図2】図2(a)〜(e)は、図1のコンパレータの動作を示す図である。

【図3】第2の実施の形態に係るコンパレータの構成を示す回路図である。

【図4】図4(a)、(b)は、図1、図3のコンパレータを用いたDC/DCコンバータの構成を示す回路図である。

【発明を実施するための形態】

【0016】

以下、本発明を好適な実施の形態をもとに図面を参照しながら説明する。各図面に示される同一または同等の構成要素、部材、処理には、同一の符号を付するものとし、適宜重複した説明は省略する。また、実施の形態は、発明を限定するものではなく例示であって、実施の形態に記述されるすべての特徴やその組み合わせは、必ずしも発明の本質的なものであるとは限らない。

【0017】

本明細書において、「部材Aが、部材Bと接続された状態」とは、部材Aと部材Bが物理的に直接的に接続される場合のほか、部材Aと部材Bが、それらの電気的な接続状態に実質的な影響を及ぼさない、あるいはそれらの結合により奏される機能や効果を損なわせない、その他の部材を介して間接的に接続される場合も含む。

同様に、「部材Cが、部材Aと部材Bの間に設けられた状態」とは、部材Aと部材C、あるいは部材Bと部材Cが直接的に接続される場合のほか、それらの電気的な接続状態に実質的な影響を及ぼさない、あるいはそれらの結合により奏される機能や効果を損なわせない、その他の部材を介して間接的に接続される場合も含む。

【0018】

(第1の実施の形態)

図1は、第1の実施の形態に係るコンパレータ10の構成を示す回路図である。コンパレータ10は、第1端子P1、第2端子P2、第1トランジスタM1、第2トランジスタM2、インバータ12を備え、第1端子P1に入力される第1電圧V1と、第2端子P2に入力される第2電圧V2を比較し、比較結果を示す出力信号OUTを出力する。

【0019】

第1トランジスタM1は、デプレッション型PチャンネルMOSFETである。第1トランジスタM1のソースは、第1端子P1と接続され、そのゲートは第2端子P2と接続される。第2トランジスタM2も、第1トランジスタM1と同型のデプレッション型PチャンネルMOSFETである。第2トランジスタM2のソースおよびゲートは、第1トランジスタM1のドレインと接続される。第2トランジスタM2のドレインは、接地などに接続され、その電位が固定される。第1トランジスタM1と第2トランジスタM2は半導体基板上の隣接する箇所に、ペアリングして形成されることが望ましい。

【0020】

コンパレータ10は、第1トランジスタM1と第2トランジスタM2の接続点N1の電位VN1に応じた出力信号OUTを生成する。インバータ12は、接続点N1の電位VN1を受け、それを反転して出力信号OUTを出力する。インバータ12に代えて、電位VN1を非反転で出力するバッファを設けてもよい。

【0021】

以上がコンパレータ10の構成である。続いてその動作を説明する。

図2(a)〜(e)は、図1のコンパレータ10の動作を示す図である。

デプレッション型の第2トランジスタM2のゲートソース間電圧VGS_M2は0Vであり、第2トランジスタM2には、所定のバイアス電流Ibiasが流れる。一方、第1トランジスタM1のゲートソース間電圧VGS_M1は、第1電圧V1と第2電圧V2の電位差V1−V2となる。ここでは便宜上、V2>V1のときゲートソース間電圧VGS_M1は正、V2<V1のときゲートソース間電圧VGS_M1は負とする。

【0022】

第1トランジスタM1は、第2トランジスタM2と同一経路上に設けられているため、コンパレータ10は、第1トランジスタM1に流れるドレイン電流IM1がバイアス電流Ibiasと等しくなるように動作する。

図2(a)は、第1トランジスタM1のドレインソース間電圧VDS_M1と、ドレイン電流IM1の関係を示す。図2(b)は、第1トランジスタM1のゲートソース間電圧VGSと、第1トランジスタM1に流れる電流IM1の関係を示す。図2(c)は、第1トランジスタM1のゲートソース間電圧VGSと、そのドレインソース間電圧VDS_M1の関係を示す。図2(d)は、第1トランジスタM1のゲートソース間電圧VGSと、接続点N1の電位VN1の関係を示す。図2(e)は、第1トランジスタM1のゲートソース間電圧VGSと、出力信号OUTの関係を示す。

【0023】

図2(a)に示すように、第1トランジスタM1のゲートソース間電圧VGSが変化すると、第1トランジスタM1のドレインソース間電圧VDS_M1は、図2(a)の関係に従って、第1トランジスタM1に流れる電流がバイアス電流Ibiasに近づくように変化する。具体的には、ゲートソース間電圧VGSが大きくなるにしたがい、ドレインソース間電圧VDS_M1は小さくなる。

【0024】

コンパレータ10の状態を、(1)V1=V2、(2)V2>V1、(3)V2<V1の3つに分けて説明する。

【0025】

(1) V1=V2のとき

第1電圧V1と第2電圧V2の電位差がゼロの平衡状態においては、第1トランジスタM1のゲートソース間電圧VGSはゼロとなり、第2トランジスタM2のバイアス状態と等しくなる。このとき、第1トランジスタM1のドレインソース間電圧VDS_M1と、第2トランジスタM2のドレインソース間電圧VDS_M2は等しくなる。

【0026】

(2) V2>V1のとき

このとき、第1トランジスタM1のゲートソース間電圧VGSは負となり、第1トランジスタM1のドレインソース間電圧VDS_M1の方が、第2トランジスタM2のドレインソース間電圧VDS_M2より大きくなる。したがって、第1トランジスタM1と第2トランジスタM2の接続点N1の電位VN1はローレベル(Vss)となる。

【0027】

(3) V2<V1のとき

このとき第1トランジスタM1のゲートソース間電圧VGSは正となり、第1トランジスタM1のドレインソース間電圧VDS_M1の方が、第2トランジスタM2のドレインソース間電圧VDS_M2より小さくなり、第1トランジスタM1と第2トランジスタM2の接続点N1の電位VN1はハイレベル(V1)となる。

【0028】

インバータ12により生成される出力信号OUTは、接続点N1の電位VN1を反転した信号となる。つまり出力信号OUTは、V2>V1のときハイレベル、V2<V1のときローレベルとなる。インバータ12をバッファに置き換えた場合、出力信号OUTの論理レベルは反対となる。

【0029】

以上がコンパレータ10の動作である。

図1のコンパレータ10によれば、2つのデプレッション型トランジスタを用いて、電圧比較を行うことができる。コンパレータ10によれば、差動増幅器を利用したコンパレータに比べて、回路面積を削減でき、さらには消費電力を低減できる。

【0030】

また、コンパレータ10は、同型の第1トランジスタM1と第2トランジスタM2で構成されるため、ばらつきの影響を受けにくく、したがってコンパレータ10の入力オフセット電圧をゼロに近づけることができる。

【0031】

(第2の実施の形態)

図3は、第2の実施の形態に係るコンパレータ20の構成を示す回路図である。コンパレータ20は、第3端子P3、第4端子P4、第3トランジスタM3、第4トランジスタM4、インバータ22を備え、第3端子P3に入力される第3電圧V3と、第4端子P4に入力される第4電圧V4を比較し、比較結果を示す出力信号OUTを出力する。

【0032】

第3トランジスタM3および第4トランジスタM4は、デプレッション型NチャンネルMOSFETである。第3トランジスタM3のゲートは、第3端子P3に接続され、そのソースは第4端子P4に接続される。第4トランジスタM4のソースおよびゲートは、第3トランジスタM3のドレインと接続される。第4トランジスタM4のドレインは、たとえば電源ラインVDDと接続され、その電位が固定される。

【0033】

コンパレータ20は、第3トランジスタM3と第4トランジスタM4の接続点N2の電位VN2に応じた出力信号OUTを生成する。インバータ22は、接続点N2の電位VN2を受け、それを反転して出力信号OUTを出力する。インバータ22に代えて、電位VN2を非反転で出力するバッファを設けてもよい。

【0034】

以上がコンパレータ20の構成である。

コンパレータ20は、図1のコンパレータ10と同様に動作する。コンパレータ20の状態を、(1)V3=V4、(2)V3<V4、(3)V3>V4の3つに分けて説明する。

【0035】

(1) V3=V4のとき

第3電圧V3と第4電圧V4の電位差がゼロの平衡状態において、第3トランジスタM3と第4トランジスタM4のゲートソース間電圧VGSは等しくなるため、第3トランジスタM3と第4トランジスタM4それぞれのドレインソース間電圧VDS_M3、VDS_M4は等しくなる。

【0036】

(2) V3<V4のとき

第3トランジスタM3のゲートソース間電圧VGSが負のときには、第3トランジスタM3のドレインソース間電圧VDS_M3の方が第4トランジスタM4のそれVDS_M4より大きくなり、接続点N2の電位VN2はハイレベル(VDD)となる。

【0037】

(4) V3>V4のとき

第3トランジスタM3のゲートソース間電圧VGSが正のときには、第3トランジスタM3のドレインソース間電圧VDS_M3の方が、第4トランジスタM4のそれVDS_M4小さくなり、接続点N2の電位VN2はローレベルとなる。

【0038】

以上がコンパレータ20の動作である。

【0039】

図3のコンパレータ20によれば、2つのデプレッション型トランジスタを用いて、電圧比較を行うことができ、差動増幅器を利用したコンパレータに比べて、回路面積を削減でき、および/または、消費電力を低減できる。

【0040】

また、同型の第3トランジスタM3、第4トランジスタM4で構成されるため、ばらつきの影響を受けにくく、したがってコンパレータ20の入力オフセット電圧をゼロに近づけることができる。

【0041】

続いて、第1、第2の実施の形態に係るコンパレータのアプリケーションの一例を説明する。

【0042】

図4(a)、(b)は、図1、図3のコンパレータを用いたDC/DCコンバータの構成を示す回路図である。DC/DCコンバータは、携帯電話端末、PDA(Personal Digital Assistant)、オーディオプレイヤ、ノート型PCなどの電子機器に搭載され、電池からの入力電圧VINを昇圧、または降圧し、マイコン、LCDパネル、LED(発光ダイオード)をはじめとする負荷に供給する。

【0043】

図4(a)のDC/DCコンバータ30は、同期整流型の昇圧コンバータである。DC/DCコンバータ30は、スイッチングトランジスタM11、同期整流トランジスタM12、インダクタL1、出力キャパシタC1、制御回路40を備える。

【0044】

DC/DCコンバータ30の制御回路40を除く部分のトポロジーは一般的なものであるため説明を省略する。制御回路40は、スイッチングトランジスタM11および同期整流トランジスタM12を相補的にスイッチングすることにより、入力電圧VINを昇圧し、出力電圧VOUTを目標値に安定化する。

【0045】

制御回路40は、第1の実施の形態に係るコンパレータ10と、パルス変調器42と、ドライバ44を備える。

【0046】

コンパレータ10は、同期整流トランジスタM12の一端の電位V1と、同期整流トランジスタM12の他端の電位V2を比較し、2つの電位が等しくなるとアサートされる比較信号S1を生成する。コンパレータ10がインバータ12を有する場合、アサートはローレベルである。

【0047】

同期整流トランジスタM12がオンの期間、同期整流トランジスタM12には、インダクタL1の電流ILが流れる。同期整流トランジスタM12のオン抵抗をRONとすれば、同期整流トランジスタM12の電圧降下(V1−V2)は、

V1−V2=RON×IL

で与えられる。

【0048】

同期整流トランジスタM12がオンした直後、V1>V2が成り立ち、インダクタL1のエネルギーが減少するにしたがい、コイル電流ILも減少し、電位差V1−V2がゼロに近づく。コンパレータ10から出力される比較信号S1は、コイル電流ILがゼロになるとアサートされる。

【0049】

パルス変調器42は、DC/DCコンバータ30の出力電圧VOUTが所定の目標値に近づくようにデューティ比が調節されるパルス信号S2を生成する。パルス変調器42は、比較信号S1がアサートされると、パルス信号S2をオンレベルに遷移させる。オンレベルとは、スイッチングトランジスタM11のオンに対応するレベルである。パルス変調器42の構成は特に限定されず、公知の回路を利用すればよい。

【0050】

ドライバ44は、パルス信号S2がオンレベルのとき、スイッチングトランジスタM11をオン、オフレベルのとき同期整流トランジスタM12をオンする。

【0051】

以上がDC/DCコンバータ30の構成である。

DC/DCコンバータ30によれば、コンパレータ10によって、コイル電流ILがゼロとなったことを検出でき、それに応じてスイッチングトランジスタM12をオフすることができる。

【0052】

図4(b)のDC/DCコンバータ50は、同期整流型の降圧コンバータである。DC/DCコンバータ50は、スイッチングトランジスタM21、同期整流トランジスタM22、インダクタL1、出力キャパシタC1、制御回路60を備える。

【0053】

DC/DCコンバータ50の制御回路60を除く部分のトポロジーは一般的なものであるため説明を省略する。制御回路60は、スイッチングトランジスタM21および同期整流トランジスタM22を相補的にスイッチングすることにより、入力電圧VINを降圧し、出力電圧VOUTを目標値に安定化する。

【0054】

制御回路60は、第2の実施の形態に係るコンパレータ20と、パルス変調器62と、ドライバ64を備える。

【0055】

コンパレータ20は、同期整流トランジスタM22の一端の電位V3と、同期整流トランジスタM22の他端の電位V4を比較し、2つの電位が等しくなるとアサートされる比較信号S3を生成する。

【0056】

同期整流トランジスタM22がオンの期間、同期整流トランジスタM22には、インダクタL1の電流ILが流れる。同期整流トランジスタM22のオン抵抗をRONとすれば、同期整流トランジスタM22の電圧降下(V4−V3)は、

V4−V3=RON×IL

で与えられる。

【0057】

同期整流トランジスタM22がオンした直後、V4>V3が成り立ち、インダクタL1のエネルギーが減少するにしたがい、コイル電流ILも減少し、電位差V4−V3がゼロに近づく。コンパレータ20から出力される比較信号S3は、コイル電流ILがゼロになるとアサートされる。

【0058】

パルス変調器62は、DC/DCコンバータ50の出力電圧VOUTが所定の目標値に近づくようにデューティ比が調節されるパルス信号S4を生成する。パルス変調器62は、比較信号S3がアサートされると、パルス信号S4をオンレベルに遷移させる。オンレベルとは、スイッチングトランジスタM21のオンに対応するレベルである。パルス変調器62の構成は特に限定されず、公知の回路を利用すればよい。

【0059】

ドライバ64は、パルス信号S4がオンレベルのとき、スイッチングトランジスタM21をオン、オフレベルのとき同期整流トランジスタM22をオンする。

【0060】

以上がDC/DCコンバータ50の構成である。

DC/DCコンバータ50によれば、コンパレータ20によって、コイル電流ILがゼロとなったことを検出でき、それに応じてスイッチングトランジスタM22をオフすることができる。

【0061】

以上、本発明について、実施の形態をもとに説明した。この実施の形態は例示であり、それらの各構成要素や各処理プロセス、それらの組み合わせには、さまざまな変形例が存在しうる。以下、こうした変形例について説明する。

【0062】

実施の形態では、コンパレータ10(20)にインバータ12(22)が設けられているが、本発明はそれに限定されない。コンパレータ10の出力端子に接続される回路の入力インピーダンスが十分に高い場合、あるいは第1トランジスタM1(M3)、第2トランジスタM2(M4)の電流能力が十分に高い場合には、インバータ12(22)を省略してもよい。

【0063】

コンパレータ10(20)の用途は、図4(a)、(b)のDC/DCコンバータには限定されない。コンパレータ10(20)は、ある経路の電流がゼロとなることを検出する用途に広く利用できる。この場合、監視対象の経路に、インピーダンス素子、たとえば抵抗やトランジスタを配置し、コンパレータ10(20)によって、インピーダンス素子の両端の電圧を比較すればよい。

【0064】

それ以外にも、コンパレータ10(20)は、2つの電圧の大小を比較するさまざまな用途に利用できる。

【0065】

実施の形態にもとづき、具体的な用語を用いて本発明を説明したが、実施の形態は、本発明の原理、応用を示しているにすぎず、実施の形態には、請求の範囲に規定された本発明の思想を逸脱しない範囲において、多くの変形例や配置の変更が認められる。

【符号の説明】

【0066】

M1…第1トランジスタ、P1…第1端子、C1…出力キャパシタ、L1…インダクタ、M2…第2トランジスタ、P2…第2端子、M3…第3トランジスタ、P3…第3端子、M4…第4トランジスタ、P4…第4端子、10…コンパレータ、M11…スイッチングトランジスタ、12…インバータ、M12…同期整流トランジスタ、20…コンパレータ、22…インバータ、30…DC/DCコンバータ、40…制御回路、42…パルス変調器、44…ドライバ、50…DC/DCコンバータ、60…制御回路、62…パルス変調器、64…ドライバ。

【技術分野】

【0001】

本発明は、コンパレータに関する。

【背景技術】

【0002】

2つの電圧の大小関係を判定するために、電圧コンパレータ(以下、単にコンパレータという)が用いられる。一般的なコンパレータは、差動増幅器を用いて構成される。ところが差動増幅器はトランジスタなどの素子数が多いため、回路面積が大きく、また素子のばらつきにより、入力電圧オフセットが発生するという問題がある。オフセット電圧を低減するためには、バイアス電流を増大させる必要があり、これは消費電力の増大という問題を引き起こす。

【発明の概要】

【発明が解決しようとする課題】

【0003】

本発明はかかる課題に鑑みてなされたものであり、そのある態様の例示的な目的のひとつは、コンパレータの小型化、および/または、低消費電力化にある。

【課題を解決するための手段】

【0004】

本発明のある態様は、第1電圧と第2電圧を比較するコンパレータに関する。このコンパレータは、そのソースに第1電圧が印加され、そのゲートに第2電圧が印加されたデプレッション型PチャンネルMOSFETの第1トランジスタと、そのソースおよびそのゲートが、第1トランジスタのドレインと接続され、そのドレインの電位が固定されたデプレッション型PチャンネルMOSFETの第2トランジスタと、を備える。コンパレータは、第1トランジスタと第2トランジスタの接続点の電位に応じた出力信号を生成する。

【0005】

デプレッション型の第2トランジスタのゲートソース間電圧は0Vであり、所定のバイアス電流が流れる。一方、第1トランジスタのゲートソース間電圧は、第1電圧と第2電圧の電位差となる。第1トランジスタのドレインソース間電圧は、第1トランジスタに流れる電流がバイアス電流に近づくように変化する。

第1電圧と第2電圧の電位差がゼロの平衡状態において、第1トランジスタと第2トランジスタのゲートソース間電圧は等しくなるため、第1トランジスタと第2トランジスタそれぞれのドレインソース間電圧は等しくなる。また、第1トランジスタのゲートソース間電圧が負のときには、第1トランジスタのドレインソース間電圧の方が大きくなり、第1トランジスタと第2トランジスタの接続点の電位はローレベルとなる。反対に、第1トランジスタのゲートソース間電圧が正のときには、第1トランジスタのドレインソース間電圧の方が小さくなり、第1トランジスタと第2トランジスタの接続点の電位はハイレベルとなる。したがって、この構成によれば、2つのデプレッション型トランジスタを用いて、電圧比較を行うことができ、差動増幅器を利用したコンパレータに比べて、回路面積を削減でき、および/または、消費電力を低減できる。

【0006】

ある態様のコンパレータは、第1トランジスタと第2トランジスタの接続点の電位を受け、出力信号を出力するバッファもしくはインバータをさらに備えてもよい。

【0007】

本発明の別の態様は、第3電圧と第4電圧を比較するコンパレータに関する。このコンパレータは、そのゲートに第3電圧が印加され、そのソースに第4電圧が印加されたデプレッション型NチャンネルMOSFETの第3トランジスタと、そのソースおよびそのゲートが、第3トランジスタのドレインと接続され、そのドレインの電位が固定されたデプレッション型NチャンネルMOSFETの第4トランジスタと、を備える。コンパレータは、第3トランジスタと第4トランジスタの接続点の電位に応じた出力信号を生成する。

【0008】

デプレッション型の第4トランジスタのゲートソース間電圧は0Vであり、所定のバイアス電流が流れる。一方、第3トランジスタのゲートソース間電圧は、第3電圧と第4電圧の電位差となる。第4トランジスタのドレインソース間電圧は、第4トランジスタに流れる電流がバイアス電流に近づくように変化する。

第3電圧と第4電圧の電位差がゼロの平衡状態において、第3トランジスタと第4トランジスタのゲートソース間電圧は等しくなるため、第3トランジスタと第4トランジスタそれぞれのドレインソース間電圧は等しくなる。また、第3トランジスタのゲートソース間電圧が負のときには、第3トランジスタのドレインソース間電圧の方が大きくなり、第3トランジスタと第4トランジスタの接続点の電位はハイレベルとなる。反対に、第3トランジスタのゲートソース間電圧が正のときには、第3トランジスタのドレインソース間電圧の方が小さくなり、第3トランジスタと第4トランジスタの接続点の電位はローレベルとなる。したがって、この構成によれば、2つのデプレッション型トランジスタを用いて、電圧比較を行うことができ、差動増幅器を利用したコンパレータに比べて、回路面積を削減でき、および/または、消費電力を低減できる。

【0009】

ある態様のコンパレータは、第3トランジスタと第4トランジスタの接続点の電位を受け、出力信号を出力するバッファもしくはインバータをさらに備えてもよい。

【0010】

本発明の別の態様は、スイッチングトランジスタおよび同期整流トランジスタを有する同期整流型昇圧DC/DCコンバータの制御回路に関する。制御回路は、同期整流トランジスタの一端の電位と、同期整流トランジスタの他端の電位を比較し、2つの電位が等しくなるとアサートされる比較信号を生成する上述のいずれかのコンパレータと、DC/DCコンバータの出力電圧が所定の目標値に近づくようにデューティ比が調節されるパルス信号であって、比較信号がアサートされるとオンレベルに遷移するパルス信号を生成するパルス変調器と、パルス信号がオンレベルのときスイッチングトランジスタをオン、オフレベルのとき同期整流トランジスタをオンするドライバと、を備える。

この態様によれば、同期整流トランジスタに流れる電流がゼロとなるタイミングを検出し、スイッチングトランジスタをオンすることができる。

【0011】

本発明の別の態様は、スイッチングトランジスタおよび同期整流トランジスタを有する同期整流型降圧DC/DCコンバータの制御回路に関する。制御回路は、同期整流トランジスタの一端の電位と、同期整流トランジスタの他端の電位を比較し、2つの電位が等しくなるとアサートされる比較信号を生成する上述のいずれかの態様のコンパレータと、DC/DCコンバータの出力電圧が所定の目標値に近づくようにデューティ比が調節されるパルス信号であって、比較信号がアサートされるとオンレベルに遷移するパルス信号を生成するパルス変調器と、パルス信号がオンレベルのときスイッチングトランジスタをオン、オフレベルのとき同期整流トランジスタをオンするドライバと、を備える。

【0012】

この態様によれば、同期整流トランジスタに流れる電流がゼロとなるタイミングを検出し、スイッチングトランジスタをオンすることができる。

【0013】

なお、以上の構成要素の任意の組み合わせや本発明の構成要素や表現を、方法、装置、システムなどの間で相互に置換したものもまた、本発明の態様として有効である。

【発明の効果】

【0014】

本発明によれば、コンパレータを小型化し、および/または、低消費電力化できる。

【図面の簡単な説明】

【0015】

【図1】第1の実施の形態に係るコンパレータの構成を示す回路図である。

【図2】図2(a)〜(e)は、図1のコンパレータの動作を示す図である。

【図3】第2の実施の形態に係るコンパレータの構成を示す回路図である。

【図4】図4(a)、(b)は、図1、図3のコンパレータを用いたDC/DCコンバータの構成を示す回路図である。

【発明を実施するための形態】

【0016】

以下、本発明を好適な実施の形態をもとに図面を参照しながら説明する。各図面に示される同一または同等の構成要素、部材、処理には、同一の符号を付するものとし、適宜重複した説明は省略する。また、実施の形態は、発明を限定するものではなく例示であって、実施の形態に記述されるすべての特徴やその組み合わせは、必ずしも発明の本質的なものであるとは限らない。

【0017】

本明細書において、「部材Aが、部材Bと接続された状態」とは、部材Aと部材Bが物理的に直接的に接続される場合のほか、部材Aと部材Bが、それらの電気的な接続状態に実質的な影響を及ぼさない、あるいはそれらの結合により奏される機能や効果を損なわせない、その他の部材を介して間接的に接続される場合も含む。

同様に、「部材Cが、部材Aと部材Bの間に設けられた状態」とは、部材Aと部材C、あるいは部材Bと部材Cが直接的に接続される場合のほか、それらの電気的な接続状態に実質的な影響を及ぼさない、あるいはそれらの結合により奏される機能や効果を損なわせない、その他の部材を介して間接的に接続される場合も含む。

【0018】

(第1の実施の形態)

図1は、第1の実施の形態に係るコンパレータ10の構成を示す回路図である。コンパレータ10は、第1端子P1、第2端子P2、第1トランジスタM1、第2トランジスタM2、インバータ12を備え、第1端子P1に入力される第1電圧V1と、第2端子P2に入力される第2電圧V2を比較し、比較結果を示す出力信号OUTを出力する。

【0019】

第1トランジスタM1は、デプレッション型PチャンネルMOSFETである。第1トランジスタM1のソースは、第1端子P1と接続され、そのゲートは第2端子P2と接続される。第2トランジスタM2も、第1トランジスタM1と同型のデプレッション型PチャンネルMOSFETである。第2トランジスタM2のソースおよびゲートは、第1トランジスタM1のドレインと接続される。第2トランジスタM2のドレインは、接地などに接続され、その電位が固定される。第1トランジスタM1と第2トランジスタM2は半導体基板上の隣接する箇所に、ペアリングして形成されることが望ましい。

【0020】

コンパレータ10は、第1トランジスタM1と第2トランジスタM2の接続点N1の電位VN1に応じた出力信号OUTを生成する。インバータ12は、接続点N1の電位VN1を受け、それを反転して出力信号OUTを出力する。インバータ12に代えて、電位VN1を非反転で出力するバッファを設けてもよい。

【0021】

以上がコンパレータ10の構成である。続いてその動作を説明する。

図2(a)〜(e)は、図1のコンパレータ10の動作を示す図である。

デプレッション型の第2トランジスタM2のゲートソース間電圧VGS_M2は0Vであり、第2トランジスタM2には、所定のバイアス電流Ibiasが流れる。一方、第1トランジスタM1のゲートソース間電圧VGS_M1は、第1電圧V1と第2電圧V2の電位差V1−V2となる。ここでは便宜上、V2>V1のときゲートソース間電圧VGS_M1は正、V2<V1のときゲートソース間電圧VGS_M1は負とする。

【0022】

第1トランジスタM1は、第2トランジスタM2と同一経路上に設けられているため、コンパレータ10は、第1トランジスタM1に流れるドレイン電流IM1がバイアス電流Ibiasと等しくなるように動作する。

図2(a)は、第1トランジスタM1のドレインソース間電圧VDS_M1と、ドレイン電流IM1の関係を示す。図2(b)は、第1トランジスタM1のゲートソース間電圧VGSと、第1トランジスタM1に流れる電流IM1の関係を示す。図2(c)は、第1トランジスタM1のゲートソース間電圧VGSと、そのドレインソース間電圧VDS_M1の関係を示す。図2(d)は、第1トランジスタM1のゲートソース間電圧VGSと、接続点N1の電位VN1の関係を示す。図2(e)は、第1トランジスタM1のゲートソース間電圧VGSと、出力信号OUTの関係を示す。

【0023】

図2(a)に示すように、第1トランジスタM1のゲートソース間電圧VGSが変化すると、第1トランジスタM1のドレインソース間電圧VDS_M1は、図2(a)の関係に従って、第1トランジスタM1に流れる電流がバイアス電流Ibiasに近づくように変化する。具体的には、ゲートソース間電圧VGSが大きくなるにしたがい、ドレインソース間電圧VDS_M1は小さくなる。

【0024】

コンパレータ10の状態を、(1)V1=V2、(2)V2>V1、(3)V2<V1の3つに分けて説明する。

【0025】

(1) V1=V2のとき

第1電圧V1と第2電圧V2の電位差がゼロの平衡状態においては、第1トランジスタM1のゲートソース間電圧VGSはゼロとなり、第2トランジスタM2のバイアス状態と等しくなる。このとき、第1トランジスタM1のドレインソース間電圧VDS_M1と、第2トランジスタM2のドレインソース間電圧VDS_M2は等しくなる。

【0026】

(2) V2>V1のとき

このとき、第1トランジスタM1のゲートソース間電圧VGSは負となり、第1トランジスタM1のドレインソース間電圧VDS_M1の方が、第2トランジスタM2のドレインソース間電圧VDS_M2より大きくなる。したがって、第1トランジスタM1と第2トランジスタM2の接続点N1の電位VN1はローレベル(Vss)となる。

【0027】

(3) V2<V1のとき

このとき第1トランジスタM1のゲートソース間電圧VGSは正となり、第1トランジスタM1のドレインソース間電圧VDS_M1の方が、第2トランジスタM2のドレインソース間電圧VDS_M2より小さくなり、第1トランジスタM1と第2トランジスタM2の接続点N1の電位VN1はハイレベル(V1)となる。

【0028】

インバータ12により生成される出力信号OUTは、接続点N1の電位VN1を反転した信号となる。つまり出力信号OUTは、V2>V1のときハイレベル、V2<V1のときローレベルとなる。インバータ12をバッファに置き換えた場合、出力信号OUTの論理レベルは反対となる。

【0029】

以上がコンパレータ10の動作である。

図1のコンパレータ10によれば、2つのデプレッション型トランジスタを用いて、電圧比較を行うことができる。コンパレータ10によれば、差動増幅器を利用したコンパレータに比べて、回路面積を削減でき、さらには消費電力を低減できる。

【0030】

また、コンパレータ10は、同型の第1トランジスタM1と第2トランジスタM2で構成されるため、ばらつきの影響を受けにくく、したがってコンパレータ10の入力オフセット電圧をゼロに近づけることができる。

【0031】

(第2の実施の形態)

図3は、第2の実施の形態に係るコンパレータ20の構成を示す回路図である。コンパレータ20は、第3端子P3、第4端子P4、第3トランジスタM3、第4トランジスタM4、インバータ22を備え、第3端子P3に入力される第3電圧V3と、第4端子P4に入力される第4電圧V4を比較し、比較結果を示す出力信号OUTを出力する。

【0032】

第3トランジスタM3および第4トランジスタM4は、デプレッション型NチャンネルMOSFETである。第3トランジスタM3のゲートは、第3端子P3に接続され、そのソースは第4端子P4に接続される。第4トランジスタM4のソースおよびゲートは、第3トランジスタM3のドレインと接続される。第4トランジスタM4のドレインは、たとえば電源ラインVDDと接続され、その電位が固定される。

【0033】

コンパレータ20は、第3トランジスタM3と第4トランジスタM4の接続点N2の電位VN2に応じた出力信号OUTを生成する。インバータ22は、接続点N2の電位VN2を受け、それを反転して出力信号OUTを出力する。インバータ22に代えて、電位VN2を非反転で出力するバッファを設けてもよい。

【0034】

以上がコンパレータ20の構成である。

コンパレータ20は、図1のコンパレータ10と同様に動作する。コンパレータ20の状態を、(1)V3=V4、(2)V3<V4、(3)V3>V4の3つに分けて説明する。

【0035】

(1) V3=V4のとき

第3電圧V3と第4電圧V4の電位差がゼロの平衡状態において、第3トランジスタM3と第4トランジスタM4のゲートソース間電圧VGSは等しくなるため、第3トランジスタM3と第4トランジスタM4それぞれのドレインソース間電圧VDS_M3、VDS_M4は等しくなる。

【0036】

(2) V3<V4のとき

第3トランジスタM3のゲートソース間電圧VGSが負のときには、第3トランジスタM3のドレインソース間電圧VDS_M3の方が第4トランジスタM4のそれVDS_M4より大きくなり、接続点N2の電位VN2はハイレベル(VDD)となる。

【0037】

(4) V3>V4のとき

第3トランジスタM3のゲートソース間電圧VGSが正のときには、第3トランジスタM3のドレインソース間電圧VDS_M3の方が、第4トランジスタM4のそれVDS_M4小さくなり、接続点N2の電位VN2はローレベルとなる。

【0038】

以上がコンパレータ20の動作である。

【0039】

図3のコンパレータ20によれば、2つのデプレッション型トランジスタを用いて、電圧比較を行うことができ、差動増幅器を利用したコンパレータに比べて、回路面積を削減でき、および/または、消費電力を低減できる。

【0040】

また、同型の第3トランジスタM3、第4トランジスタM4で構成されるため、ばらつきの影響を受けにくく、したがってコンパレータ20の入力オフセット電圧をゼロに近づけることができる。

【0041】

続いて、第1、第2の実施の形態に係るコンパレータのアプリケーションの一例を説明する。

【0042】

図4(a)、(b)は、図1、図3のコンパレータを用いたDC/DCコンバータの構成を示す回路図である。DC/DCコンバータは、携帯電話端末、PDA(Personal Digital Assistant)、オーディオプレイヤ、ノート型PCなどの電子機器に搭載され、電池からの入力電圧VINを昇圧、または降圧し、マイコン、LCDパネル、LED(発光ダイオード)をはじめとする負荷に供給する。

【0043】

図4(a)のDC/DCコンバータ30は、同期整流型の昇圧コンバータである。DC/DCコンバータ30は、スイッチングトランジスタM11、同期整流トランジスタM12、インダクタL1、出力キャパシタC1、制御回路40を備える。

【0044】

DC/DCコンバータ30の制御回路40を除く部分のトポロジーは一般的なものであるため説明を省略する。制御回路40は、スイッチングトランジスタM11および同期整流トランジスタM12を相補的にスイッチングすることにより、入力電圧VINを昇圧し、出力電圧VOUTを目標値に安定化する。

【0045】

制御回路40は、第1の実施の形態に係るコンパレータ10と、パルス変調器42と、ドライバ44を備える。

【0046】

コンパレータ10は、同期整流トランジスタM12の一端の電位V1と、同期整流トランジスタM12の他端の電位V2を比較し、2つの電位が等しくなるとアサートされる比較信号S1を生成する。コンパレータ10がインバータ12を有する場合、アサートはローレベルである。

【0047】

同期整流トランジスタM12がオンの期間、同期整流トランジスタM12には、インダクタL1の電流ILが流れる。同期整流トランジスタM12のオン抵抗をRONとすれば、同期整流トランジスタM12の電圧降下(V1−V2)は、

V1−V2=RON×IL

で与えられる。

【0048】

同期整流トランジスタM12がオンした直後、V1>V2が成り立ち、インダクタL1のエネルギーが減少するにしたがい、コイル電流ILも減少し、電位差V1−V2がゼロに近づく。コンパレータ10から出力される比較信号S1は、コイル電流ILがゼロになるとアサートされる。

【0049】

パルス変調器42は、DC/DCコンバータ30の出力電圧VOUTが所定の目標値に近づくようにデューティ比が調節されるパルス信号S2を生成する。パルス変調器42は、比較信号S1がアサートされると、パルス信号S2をオンレベルに遷移させる。オンレベルとは、スイッチングトランジスタM11のオンに対応するレベルである。パルス変調器42の構成は特に限定されず、公知の回路を利用すればよい。

【0050】

ドライバ44は、パルス信号S2がオンレベルのとき、スイッチングトランジスタM11をオン、オフレベルのとき同期整流トランジスタM12をオンする。

【0051】

以上がDC/DCコンバータ30の構成である。

DC/DCコンバータ30によれば、コンパレータ10によって、コイル電流ILがゼロとなったことを検出でき、それに応じてスイッチングトランジスタM12をオフすることができる。

【0052】

図4(b)のDC/DCコンバータ50は、同期整流型の降圧コンバータである。DC/DCコンバータ50は、スイッチングトランジスタM21、同期整流トランジスタM22、インダクタL1、出力キャパシタC1、制御回路60を備える。

【0053】

DC/DCコンバータ50の制御回路60を除く部分のトポロジーは一般的なものであるため説明を省略する。制御回路60は、スイッチングトランジスタM21および同期整流トランジスタM22を相補的にスイッチングすることにより、入力電圧VINを降圧し、出力電圧VOUTを目標値に安定化する。

【0054】

制御回路60は、第2の実施の形態に係るコンパレータ20と、パルス変調器62と、ドライバ64を備える。

【0055】

コンパレータ20は、同期整流トランジスタM22の一端の電位V3と、同期整流トランジスタM22の他端の電位V4を比較し、2つの電位が等しくなるとアサートされる比較信号S3を生成する。

【0056】

同期整流トランジスタM22がオンの期間、同期整流トランジスタM22には、インダクタL1の電流ILが流れる。同期整流トランジスタM22のオン抵抗をRONとすれば、同期整流トランジスタM22の電圧降下(V4−V3)は、

V4−V3=RON×IL

で与えられる。

【0057】

同期整流トランジスタM22がオンした直後、V4>V3が成り立ち、インダクタL1のエネルギーが減少するにしたがい、コイル電流ILも減少し、電位差V4−V3がゼロに近づく。コンパレータ20から出力される比較信号S3は、コイル電流ILがゼロになるとアサートされる。

【0058】

パルス変調器62は、DC/DCコンバータ50の出力電圧VOUTが所定の目標値に近づくようにデューティ比が調節されるパルス信号S4を生成する。パルス変調器62は、比較信号S3がアサートされると、パルス信号S4をオンレベルに遷移させる。オンレベルとは、スイッチングトランジスタM21のオンに対応するレベルである。パルス変調器62の構成は特に限定されず、公知の回路を利用すればよい。

【0059】

ドライバ64は、パルス信号S4がオンレベルのとき、スイッチングトランジスタM21をオン、オフレベルのとき同期整流トランジスタM22をオンする。

【0060】

以上がDC/DCコンバータ50の構成である。

DC/DCコンバータ50によれば、コンパレータ20によって、コイル電流ILがゼロとなったことを検出でき、それに応じてスイッチングトランジスタM22をオフすることができる。

【0061】

以上、本発明について、実施の形態をもとに説明した。この実施の形態は例示であり、それらの各構成要素や各処理プロセス、それらの組み合わせには、さまざまな変形例が存在しうる。以下、こうした変形例について説明する。

【0062】

実施の形態では、コンパレータ10(20)にインバータ12(22)が設けられているが、本発明はそれに限定されない。コンパレータ10の出力端子に接続される回路の入力インピーダンスが十分に高い場合、あるいは第1トランジスタM1(M3)、第2トランジスタM2(M4)の電流能力が十分に高い場合には、インバータ12(22)を省略してもよい。

【0063】

コンパレータ10(20)の用途は、図4(a)、(b)のDC/DCコンバータには限定されない。コンパレータ10(20)は、ある経路の電流がゼロとなることを検出する用途に広く利用できる。この場合、監視対象の経路に、インピーダンス素子、たとえば抵抗やトランジスタを配置し、コンパレータ10(20)によって、インピーダンス素子の両端の電圧を比較すればよい。

【0064】

それ以外にも、コンパレータ10(20)は、2つの電圧の大小を比較するさまざまな用途に利用できる。

【0065】

実施の形態にもとづき、具体的な用語を用いて本発明を説明したが、実施の形態は、本発明の原理、応用を示しているにすぎず、実施の形態には、請求の範囲に規定された本発明の思想を逸脱しない範囲において、多くの変形例や配置の変更が認められる。

【符号の説明】

【0066】

M1…第1トランジスタ、P1…第1端子、C1…出力キャパシタ、L1…インダクタ、M2…第2トランジスタ、P2…第2端子、M3…第3トランジスタ、P3…第3端子、M4…第4トランジスタ、P4…第4端子、10…コンパレータ、M11…スイッチングトランジスタ、12…インバータ、M12…同期整流トランジスタ、20…コンパレータ、22…インバータ、30…DC/DCコンバータ、40…制御回路、42…パルス変調器、44…ドライバ、50…DC/DCコンバータ、60…制御回路、62…パルス変調器、64…ドライバ。

【特許請求の範囲】

【請求項1】

第1電圧と第2電圧を比較するコンパレータであって、

そのソースに前記第1電圧が印加され、そのゲートに前記第2電圧が印加されたデプレッション型PチャンネルMOSFETの第1トランジスタと、

そのソースおよびそのゲートが、前記第1トランジスタのドレインと接続され、そのドレインの電位が固定されたデプレッション型PチャンネルMOSFETの第2トランジスタと、

を備え、前記第1トランジスタと前記第2トランジスタの接続点の電位に応じた出力信号を生成することを特徴とするコンパレータ。

【請求項2】

前記第1トランジスタと前記第2トランジスタの接続点の電位を受け、前記出力信号を出力するバッファもしくはインバータをさらに備えることを特徴とする請求項1に記載のコンパレータ。

【請求項3】

第3電圧と第4電圧を比較するコンパレータであって、

そのゲートに前記第3電圧が印加され、そのソースに前記第4電圧が印加されたデプレッション型NチャンネルMOSFETの第3トランジスタと、

そのソースおよびそのゲートが、前記第3トランジスタのドレインと接続され、そのドレインの電位が固定されたデプレッション型NチャンネルMOSFETの第4トランジスタと、

を備え、前記第3トランジスタと前記第4トランジスタの接続点の電位に応じた出力信号を生成することを特徴とするコンパレータ。

【請求項4】

前記第3トランジスタと前記第4トランジスタの接続点の電位を受け、前記出力信号を出力するバッファもしくはインバータをさらに備えることを特徴とする請求項3に記載のコンパレータ。

【請求項5】

スイッチングトランジスタおよび同期整流トランジスタを有する同期整流型昇圧DC/DCコンバータの制御回路であって、

前記同期整流トランジスタの一端の電位と、前記同期整流トランジスタの他端の電位を比較し、2つの電位が等しくなるとアサートされる比較信号を生成する請求項1または2に記載のコンパレータと、

前記DC/DCコンバータの出力電圧が所定の目標値に近づくようにデューティ比が調節されるパルス信号であって、前記比較信号がアサートされるとオンレベルに遷移するパルス信号を生成するパルス変調器と、

前記パルス信号がオンレベルのとき前記スイッチングトランジスタをオン、オフレベルのとき前記同期整流トランジスタをオンするドライバと、

を備えることを特徴とする制御回路。

【請求項6】

スイッチングトランジスタおよび同期整流トランジスタを有する同期整流型降圧DC/DCコンバータの制御回路であって、

前記同期整流トランジスタの一端の電位と、前記同期整流トランジスタの他端の電位を比較し、2つの電位が等しくなるとアサートされる比較信号を生成する請求項3または4に記載のコンパレータと、

前記DC/DCコンバータの出力電圧が所定の目標値に近づくようにデューティ比が調節されるパルス信号であって、前記比較信号がアサートされるとオンレベルに遷移するパルス信号を生成するパルス変調器と、

前記パルス信号がオンレベルのとき前記スイッチングトランジスタをオン、オフレベルのとき前記同期整流トランジスタをオンするドライバと、

を備えることを特徴とする制御回路。

【請求項7】

請求項5または6に記載の制御回路を有するDC/DCコンバータを備えることを特徴とする電子機器。

【請求項1】

第1電圧と第2電圧を比較するコンパレータであって、

そのソースに前記第1電圧が印加され、そのゲートに前記第2電圧が印加されたデプレッション型PチャンネルMOSFETの第1トランジスタと、

そのソースおよびそのゲートが、前記第1トランジスタのドレインと接続され、そのドレインの電位が固定されたデプレッション型PチャンネルMOSFETの第2トランジスタと、

を備え、前記第1トランジスタと前記第2トランジスタの接続点の電位に応じた出力信号を生成することを特徴とするコンパレータ。

【請求項2】

前記第1トランジスタと前記第2トランジスタの接続点の電位を受け、前記出力信号を出力するバッファもしくはインバータをさらに備えることを特徴とする請求項1に記載のコンパレータ。

【請求項3】

第3電圧と第4電圧を比較するコンパレータであって、

そのゲートに前記第3電圧が印加され、そのソースに前記第4電圧が印加されたデプレッション型NチャンネルMOSFETの第3トランジスタと、

そのソースおよびそのゲートが、前記第3トランジスタのドレインと接続され、そのドレインの電位が固定されたデプレッション型NチャンネルMOSFETの第4トランジスタと、

を備え、前記第3トランジスタと前記第4トランジスタの接続点の電位に応じた出力信号を生成することを特徴とするコンパレータ。

【請求項4】

前記第3トランジスタと前記第4トランジスタの接続点の電位を受け、前記出力信号を出力するバッファもしくはインバータをさらに備えることを特徴とする請求項3に記載のコンパレータ。

【請求項5】

スイッチングトランジスタおよび同期整流トランジスタを有する同期整流型昇圧DC/DCコンバータの制御回路であって、

前記同期整流トランジスタの一端の電位と、前記同期整流トランジスタの他端の電位を比較し、2つの電位が等しくなるとアサートされる比較信号を生成する請求項1または2に記載のコンパレータと、

前記DC/DCコンバータの出力電圧が所定の目標値に近づくようにデューティ比が調節されるパルス信号であって、前記比較信号がアサートされるとオンレベルに遷移するパルス信号を生成するパルス変調器と、

前記パルス信号がオンレベルのとき前記スイッチングトランジスタをオン、オフレベルのとき前記同期整流トランジスタをオンするドライバと、

を備えることを特徴とする制御回路。

【請求項6】

スイッチングトランジスタおよび同期整流トランジスタを有する同期整流型降圧DC/DCコンバータの制御回路であって、

前記同期整流トランジスタの一端の電位と、前記同期整流トランジスタの他端の電位を比較し、2つの電位が等しくなるとアサートされる比較信号を生成する請求項3または4に記載のコンパレータと、

前記DC/DCコンバータの出力電圧が所定の目標値に近づくようにデューティ比が調節されるパルス信号であって、前記比較信号がアサートされるとオンレベルに遷移するパルス信号を生成するパルス変調器と、

前記パルス信号がオンレベルのとき前記スイッチングトランジスタをオン、オフレベルのとき前記同期整流トランジスタをオンするドライバと、

を備えることを特徴とする制御回路。

【請求項7】

請求項5または6に記載の制御回路を有するDC/DCコンバータを備えることを特徴とする電子機器。

【図1】

【図2】

【図3】

【図4】

【図2】

【図3】

【図4】

【公開番号】特開2013−74537(P2013−74537A)

【公開日】平成25年4月22日(2013.4.22)

【国際特許分類】

【出願番号】特願2011−213324(P2011−213324)

【出願日】平成23年9月28日(2011.9.28)

【出願人】(000116024)ローム株式会社 (3,539)

【Fターム(参考)】

【公開日】平成25年4月22日(2013.4.22)

【国際特許分類】

【出願日】平成23年9月28日(2011.9.28)

【出願人】(000116024)ローム株式会社 (3,539)

【Fターム(参考)】

[ Back to top ]