コンピュータシステム、メモリ初期化方法、及びプログラム

【課題】メモリ初期化処理の更なる高速化を実現可能なコンピュータシステムを提供する。

【解決手段】仕様情報を含む第1のSPD情報を格納する複数のメモリモジュールと、システム内のメモリアクセスに用いられるアクセス設定値と、第1のSPD情報の複製である第2のSPD情報とを記憶する不揮発性メモリとを備える。読み出し制御部は、メモリ初期化処理において、第1のSPD情報と第2のSPD情報とが一致するか否か判定して、一致しない不一致メモリモジュールを特定すると、不一致メモリモジュールの第1のSPD情報を読み出して不揮発性メモリへ第2のSPD情報として書き込む。設定値生成部は、不一致メモリモジュールが存在する場合に、不一致メモリモジュールの第2のSPD情報が生成に用いられるアクセス設定値を、第2のSPD情報に基づいて生成して、不揮発性メモリへ書き込む。

【解決手段】仕様情報を含む第1のSPD情報を格納する複数のメモリモジュールと、システム内のメモリアクセスに用いられるアクセス設定値と、第1のSPD情報の複製である第2のSPD情報とを記憶する不揮発性メモリとを備える。読み出し制御部は、メモリ初期化処理において、第1のSPD情報と第2のSPD情報とが一致するか否か判定して、一致しない不一致メモリモジュールを特定すると、不一致メモリモジュールの第1のSPD情報を読み出して不揮発性メモリへ第2のSPD情報として書き込む。設定値生成部は、不一致メモリモジュールが存在する場合に、不一致メモリモジュールの第2のSPD情報が生成に用いられるアクセス設定値を、第2のSPD情報に基づいて生成して、不揮発性メモリへ書き込む。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、メモリ初期化処理を高速に実行するコンピュータシステムに関する。

【背景技術】

【0002】

コンピュータシステムは、起動時にメモリ初期化処理を実行する。近年、コンピュータシステムに搭載されるメモリ数の増加、及びメモリ容量の増大により、メモリ初期化処理の実行時間は増加傾向にある。そのため、メモリ初期化処理の高速化と、実行時間の短縮化が求められている。

【0003】

特許文献1は、メモリ初期化処理を高速実行することが可能な情報処理装置を開示している。特許文献1の情報処理装置は、各種プログラムを実行するCPU(Central Processing Unit)を有する情報処理装置である。情報処理装置は、RAM(Random Access Memory)と第1の不揮発性メモリとが搭載されたメモリモジュールと、第2の不揮発性メモリと、保存処理モジュールと、設定処理モジュールとを備える。

【0004】

RAMは、主メモリを構成するのに用いられる。第1の不揮発性メモリは、第1のSPD(Serial Presence Detect)を格納する。第2の不揮発性メモリは、CPUが直接アクセス可能なメモリ空間に割り当てられる。保存処理モジュールは、メモリモジュールの第1の不揮発性メモリに格納されている第1のSPDデータを第2のSPDデータとして第2の不揮発性メモリの所定領域に保存する。設定処理モジュールは、情報処理装置の電源オン時に第2の不揮発性メモリの所定領域に保存されている第2のSPDデータに基づいて、メモリモジュールに搭載されたRAMを主メモリの構成要素として機能させるための初期設定処理を行う。

【0005】

特許文献1の情報処理装置によれば、メモリモジュールの第1の不揮発性メモリに格納されたSPDデータではなく、CPUが直接アクセス可能なメモリ空間に割り当てられる第2の不揮発性メモリに保存されたSPDデータに基づいてメモリ初期化処理を実行することで、メモリ初期化処理を高速に実行することが可能になる。

【0006】

しかし、特許文献1の情報処理装置では、システムの備えるメモリモジュールのSPD情報のみを第2の不揮発性メモリであるフラッシュROM(Read Only Memory)へ格納する。そのため、以後の起動時におけるメモリ初期化処理では、SPD情報の読み出し処理については高速化を図れるものの、SPD情報の読み出し以降の処理については、高速化されない。

【0007】

また、特許文献1の情報処理装置では、コンピュータシステム上のフラッシュROM、及びメモリモジュールの双方のSPDへ、メモリモジュールの一致を確認するための専用フラグを記録する必要がある。そのため、フラッシュROMとメモリモジュールへデータを書き込む構成を必要とする。

【0008】

なお、関連技術として、特許文献2は、初期化された状態を直ちに判別することにより、初期化の時間を短縮可能な集積回路を開示している。また、特許文献3は、RAMなどの揮発性メモリに記憶される情報の量を低減しつつ処理の効率化を実現する半導体装置を開示している。

【先行技術文献】

【特許文献】

【0009】

【特許文献1】特開2007−122627号公報

【特許文献2】特開昭64−073409号公報

【特許文献3】特開2006−011533号公報

【発明の概要】

【発明が解決しようとする課題】

【0010】

本発明の目的は、メモリ初期化処理の更なる高速化を実現可能なコンピュータシステムを提供することである。

【課題を解決するための手段】

【0011】

本発明のコンピュータシステムは、第1のSPD情報を格納する複数のメモリモジュールと、第1のSPD情報は、複数のメモリモジュールの各々の仕様情報を含み、各メモリモジュールへアクセスするためにシステム内で用いられるアクセス設定値と、各メモリモジュールに対応させて第1のSPD情報の複製である第2のSPD情報とを記憶する不揮発性メモリと、複数のメモリモジュールの初期化処理において第1のSPD情報と第2のSPD情報とが一致するか否か比較判定処理を行って、比較判定処理において複数のメモリモジュールのうちから第1のSPD情報と第2のSPD情報とが一致しない不一致メモリモジュールを特定して、不一致メモリモジュールから第1のSPD情報を読み出して不揮発性メモリへ第2のSPD情報として書き込む読み出し制御部と、複数のメモリモジュールに不一致メモリモジュールが存在する場合に、アクセス設定値のうちで不一致メモリモジュールの第2のSPD情報が生成に用いられる選択アクセス設定値を、第2のSPD情報に基づいて生成して、選択アクセス設定値を不揮発性メモリへ書き込む設定値生成部とを備える。

【0012】

本発明のコンピュータシステムのメモリ初期化方法は、第1のSPD情報を格納する複数のメモリモジュールと、第1のSPD情報は、複数のメモリモジュールの各々の仕様情報を含み、不揮発性メモリとを備えるコンピュータシステムにおいて、各メモリモジュールへアクセスするためにシステム内で用いられるアクセス設定値と、各メモリモジュールに対応させて第1のSPD情報の複製である第2のSPD情報とを記憶するステップと、複数のメモリモジュールの初期化処理において第1のSPD情報と第2のSPD情報とが一致するか否か比較判定処理を行うステップと、比較判定処理において複数のメモリモジュールのうちから第1のSPD情報と第2のSPD情報とが一致しない不一致メモリモジュールを特定するステップと、不一致メモリモジュールから第1のSPD情報を読み出して不揮発性メモリへ第2のSPD情報として書き込むステップと、複数のメモリモジュールに不一致メモリモジュールが存在する場合に、アクセス設定値のうちで不一致メモリモジュールの第2のSPD情報が生成に用いられる選択アクセス設定値を第2のSPD情報に基づいて生成するステップと、選択アクセス設定値を不揮発性メモリへ書き込むステップとを備える。

【0013】

本発明のメモリ初期化プログラムは、上述のコンピュータシステムのメモリ初期化方法をコンピュータに実行させる。

【発明の効果】

【0014】

本発明によれば、メモリ初期化処理の更なる高速化を実現可能なコンピュータシステムを提供することができる。

【図面の簡単な説明】

【0015】

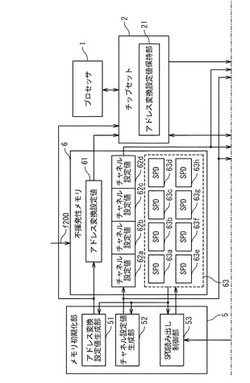

【図1A】図1Aは、本発明の実施形態におけるコンピュータシステムの構成を示す図である。

【図1B】図1Bは、本発明の実施形態におけるコンピュータシステムの構成を示す図である。

【図2】図2は、本発明の実施形態におけるSPD701〜708のデータフォーマットを示す図である。

【図3A】図3Aは、本発明の実施形態におけるコンピュータシステムの動作を示すフローチャートである。

【図3B】図3Bは、本発明の実施形態におけるコンピュータシステムの動作を示すフローチャートである。

【発明を実施するための形態】

【0016】

添付図面を参照して、本発明の実施形態によるコンピュータシステムを以下に説明する。

【0017】

[概要]

本実施形態におけるコンピュータシステムは、コンピュータシステムの備える全てのメモリモジュールのSPDと、メモリコントローラにおけるメモリチャネルのチャネル設定値と、各メモリモジュールのアドレス空間に対応させて生成されたアドレス変換設定値とを記憶する不揮発性メモリを備える。また、コンピュータシステムは、メモリ初期化処理において各メモリモジュールのSPDを読み出して不揮発性メモリに記憶されたSPDと比較するSPD比較処理を行うSPD読み出し制御部と、メモリチャネル毎のチャネル設定値の生成処理を行うチャネル設定値生成部と、及びアドレス変換設定値の生成処理を行うアドレス変換設定値生成部とを備える。

【0018】

SPDは、仕様情報と製造者関連情報とを含む。さらに、製造者関連情報は、メモリモジュールの型式番号、及びシリアル番号を含む。SPD読み出し制御部は、SPD比較処理において、メモリモジュールの型式番号とシリアル番号とを比較する。SPD読み出し制御部は、型式番号とシリアル番号の、いずれも一致したメモリモジュールについて、不揮発性メモリに記憶されたSPDの更新は行わない。SPDが一致するということは、搭載されているメモリモジュールが前回のメモリ初期化処理時のメモリモジュールと同一であると確認できたことを意味する。そのため、SPDが一致したメモリモジュールは、不揮発性メモリに記憶されたSPDの更新処理を省略することができる。

【0019】

一方、SPD読み出し制御部は、型式番号が不一致であるメモリモジュールからSPDに格納された仕様情報と製造者関連情報とを読み出して不揮発性メモリに記憶されたSPDを更新する。型式番号が不一致であるメモリモジュールは、異なる仕様を有したメモリモジュールへ交換が行われたと考えることができるからである。また、SPD読み出し制御部は、型式番号が一致するもののシリアル番号が不一致であるメモリモジュールからSPDの製造者関連情報のみを読み出して不揮発性メモリに記憶されたSPDを更新する。型式番号が一致するもののシリアル番号が不一致であるメモリモジュールは、同じ仕様を有する異なるシリアル番号のメモリモジュールに交換されたと考えられるからである。

【0020】

チャネル設定値生成部は、型式番号が不一致であるメモリモジュールと接続されるメモリチャネルに対してのみチャネル設定値の生成処理を行う。さらに、アドレス変換設定値生成部は、コンピュータシステムの備える全てのメモリモジュールにおいて、型式番号が不一致であるメモリモジュールが存在した場合にのみアドレス変換値生成処理を行う。チャネル設定値生成部とアドレス変換設定値生成部は、いずれも不揮発性メモリに記憶されたSPDの仕様情報を基にして、チャネル設定値とアドレス変換設定値とを生成する。SPD読み出し制御部は、型式番号が不一致である場合のみ、不揮発性メモリ記憶にされたSPDの仕様情報を更新する。

【0021】

型式番号が一致する場合、あるいは、型式番号が一致するもののシリアル番号が不一致である場合、不揮発性メモリ記憶にされたSPDの仕様情報に変更は無い。そのため、チャネル設定値生成部とアドレス変換設定値生成部とが、生成するチャネル設定値、及びアドレス変換設定値も同一の値となる。そこで、本実施形態におけるコンピュータシステムは、の型式番号が一致する場合、あるいは、型式番号が一致するもののシリアル番号が不一致である場合には、チャネル設定値及びアドレス変換設定値の生成処理を省略する。そして、不揮発性メモリに記憶されたチャネル設定値及びアドレス変換設定値を用いてメモリ初期化処理を行う。これによって、メモリ初期化処理の更なる高速化を計ることができる。以下、本実施形態におけるコンピュータシステムの構成及び動作を詳細に説明する。

【0022】

[構成の説明]

はじめに、本実施形態におけるコンピュータシステムの構成の説明を行う。図1A、図1Bは、本実施形態におけるコンピュータシステムの構成を示す図である。本実施形態のコンピュータシステムは、プロセッサ1と、チップセット2と、メモリコントローラ3、及び4と、メモリ初期化部5と、不揮発性メモリ6と、メモリモジュール部7とを備える。

【0023】

まず、プロセッサ1はCPU(Central Processing Unit)に例示される、プロセッサ1は、コンピュータプログラムを実行してコンピュータシステムの機能を実現する。

【0024】

次に、チップセット2は、プロセッサ1と、メモリコントローラ3、及び4と、メモリ初期化部5と、不揮発性メモリ6との間を接続して、それぞれの間で行われるデータ送受信を制御する。チップセット2は、アドレス変換設定値保持部21を備える。アドレス変換設定値保持部21は、アドレス変換設定値を保持している。アドレス変換設定値保持部21は、後述されるメモリ初期化部5のアドレス変換設定値生成部により、アドレス変換設定値を記憶される。チップセット2は、アドレス変換設定値に基づいて、プロセッサ1から入力するトランザクションをメモリコントローラ3、4へ振り分ける。

【0025】

次に、メモリモジュール部7は、メモリモジュール71〜78を備える。メモリモジュール71〜78は、RAM(Random Access Memory)に例示され、メモリ制御装置を含むコンピュータシステムにおける主記憶装置として使用される。メモリモジュール71〜78は、JEDEC(Joint Electron Device Engineering Council)に準拠した汎用的なメモリモジュールである。メモリモジュール71〜78は、それぞれSPD(Serial Presence Detect)701〜708を備える。SPD701〜708は、それぞれメモリモジュール71〜78に関する情報を記録している。

【0026】

ここで、図2は、本実施形態におけるSPD701〜708のデータフォーマットを示す図である。図2に記載されたSPD701〜708のデータフォーマットは、JEDECに準拠した一般的な汎用メモリのデータフォーマットと同様である。SPD701〜708のデータフォーマットは同様であるので、図2ではSPD701を例として説明を行う。SPD701は、256Byteのデータを格納することが可能である。SPD701は、3つのデータ格納領域701a〜701cに区分される。

【0027】

データ格納領域701aは、64byteのデータを格納可能であり、メモリモジュール71の物理的な仕様情報を格納する。メモリモジュール71の仕様情報とは、メモリモジュールの構成、容量、遅延パラメータ等である。これらのメモリモジュール71の仕様情報は、アドレス空間の設定や、メモリアクセスモードの設定等に用いられる。データ格納領域701bは、64byteのデータを格納可能であり、メモリモジュール71の製造者関連情報を格納する。製造者関連情報とは、メモリモジュール71の型式番号、及びシリアル番号を含む。データ格納領域701cは、128byteのデータを格納可能であり、ユーザに解放された領域となっている。以上が、SPD701〜708に格納されたデータフォーマットの説明である。

【0028】

次に、図1A、図1Bへ戻り、メモリコントローラ3、4は、プロセッサ1によるメモリモジュール部7のメモリモジュール71〜78へのアクセスを制御する。メモリコントローラ3は、2つのメモリチャネル311、及び321を備える。メモリコントローラ3は、メモリチャネル311を介して、メモリモジュール71、及び72と接続される。メモリコントローラ3は、メモリチャネル321を介して、メモリモジュール73、及び74と接続される。同様に、メモリコントローラ4は、2つのメモリチャネルであるメモリチャネル411、及び421を備える。メモリコントローラ4は、メモリチャネル411を介して、メモリモジュール75、及び76と接続される。メモリコントローラ4は、メモリチャネル421を介して、メモリモジュール77、及び78と接続される。

【0029】

また、メモリコントローラ3は、メモリチャネル311、及び321にそれぞれ対応するチャネル設定値保持部31、及び32を備える。チャネル設定値保持部31は、メモリチャネル311の制御に用いられるチャネル設定値を記憶する。チャネル設定値保持部32は、メモリチャネル321の制御に用いられるチャネル設定値を記憶する。チャネル設定値は、メモリチャネル31、あるいは32における、終端抵抗値や、遅延パラメータや、インピーダンス設定値といった値を含む。同様に、メモリコントローラ4は、メモリチャネル411、及び421にそれぞれ対応するチャネル設定値保持部41、及び42を備える。チャネル設定値保持部41は、メモリチャネル411の制御に用いられるチャネル設定値を記憶する。チャネル設定値保持部42は、メモリチャネル421の制御に用いられるチャネル設定値を記憶する。チャネル設定値は、メモリチャネル41、あるいは42における、終端抵抗値や、遅延パラメータや、インピーダンス設定値といった値を含む。

【0030】

なお、メモリコントローラ3、4の数は、2つに限定しない。これより多くても良いし、あるいは少なくとも良い。また、メモリコントローラ3、4は、デュアルチャネルでなくとも良い。メモリコントローラ3、4の備えるチャネル数は、1つでも良いし、あるいは2つより多くともよい。

【0031】

次に、不揮発性メモリ6は、アドレス変換設定値61と、チャネル設定値62a〜62dと、SPD62a〜62hとを記憶する。アドレス変換設定値61は、チップセット2のアドレス変換設定値保持部21に記憶されるアドレス変換設定値の複製である。また、チャネル設定値62a〜62dは、メモリコントローラ3、4のチャネル設定値保持部31、32、41、及び42にそれぞれ記憶されるチャネル設定値の複製である。さらに、SPD62a〜62hは、メモリモジュール71〜78のSPD701〜708に含まれる情報の複製である。SPD62a〜62hは、図2で説明を行った、SPD701〜708に格納されたデータのうち、データ格納領域701a〜708aの仕様情報、及び701b〜708bの製造者関連情報のみを記憶する。SPD62a〜62hは、データ格納領域701c〜708cのユーザ定義情報を記憶しない。

【0032】

なお、メモリモジュール部7のメモリモジュールの数や、メモリコントローラ3、4の数、あるいはメモリコントローラ3、4の備えるチャネル数が増減する場合には、これに応じて記憶するべきSPD、チャネル設定値、及びアドレス変換設定値のデータ量も変化する。

【0033】

次に、メモリ初期化部5は、アドレス変換設定値生成部51と、チャネル設定値生成部52と、SPD読み出し制御部53とを備える。

【0034】

まず、SPD読み出し部53は、メモリ初期化処理において、SPD比較処理を行う。SPD読み出し部53は、メモリモジュール71〜78に格納されたSPD701〜708を読み出して、不揮発性メモリ6に記憶されたSPD701〜708にそれぞれ対応するSPD63a〜63hと比較を行うことによりSPD比較処理を行う。SPD読み出し部53は、図2に示したデータ格納領域701b〜708b(製造者関連情報)から、メモリモジュール71〜78の型式番号とシリアル番号とを読み出して比較を行う。SPD読み出し部53は、SPD比較処理の結果に基づいて、SPD63a〜63hの更新を行う。

【0035】

SPD読み出し部53は、SPD比較処理においてメモリモジュール71〜78の型式番号が不一致であった場合、SPD701〜708のデータ格納領域701a〜708aとデータ格納領域701b〜708bからそれぞれ仕様情報と製造者関連情報とを読み出して、SPD63a〜63hとして不揮発性メモリ6へ記憶させる。メモリモジュール71〜78の型式番号が不一致である場合、前回のメモリ初期化処理以降に、メモリモジュール71〜78が仕様の異なるメモリモジュールへ交換されたと考えられる。そのため、SPD読み出し部53は、SPD701〜708から仕様情報と製造者関連情報とを読み出してSPD63a〜63hを更新する。

【0036】

また、SPD読み出し部53は、SPD比較処理においてメモリモジュール71〜78の型式番号は一致するもののシリアル番号が不一致であった場合、SPD701〜708のデータ格納領域701b〜708bから製造者関連情報のみを読み出して、SPD63a〜63hとして不揮発性メモリ6へ記憶させる。メモリモジュール71〜78の型式番号は一致するもののシリアル番号が不一致であった場合、前回のメモリ初期化処理以降に、メモリモジュール71〜78が仕様は同一であるがシリアル番号のみが異なるメモリモジュールへ交換されたと考えられる。そのため、SPD読み出し部53は、SPD701〜708から製造者関連情報のみを読み出してSPD63a〜63hを更新する。

【0037】

一方、SPD読み出し部53は、SPD比較処理において、メモリモジュール71〜78の型式番号及びシリアル番号が共に一致する場合、SPD701〜708から情報の読み出しを行わない。メモリモジュール71〜78の型式番号及びシリアル番号が一致する場合、メモリモジュール71〜78は、前回のメモリ初期化処理時のメモリモジュール71〜78と同一であり、交換は行われていないと考えられる。そのため、SPD読み出し部53は、SPD63a〜63hを省略して、メモリ初期化処理を高速化する。

【0038】

次に、チャネル設定値生成部52は、チャネル設定を生成するチャネル設定値生成処理を行う。チャネル設定値生成部52は、メモリコントローラ3のメモリチャネル311、321、及びメモリコントローラ4のメモリチャネル411、421に、それぞれ対応するチャネル設定値を生成する。チャネル設定値生成部52は、不揮発性メモリ6に記憶されたSPD63a、63bに基づいて、メモリチャネル311に対応するチャネル設定値を生成する。同様に、チャネル設定値生成部52は、不揮発性メモリ6に記憶されたSPD63c〜63hに基づいて、メモリチャネル321、411、421に対応するチャネル設定値を生成する。チャネル設定値生成部52は、生成されたチャネル設定値を、それぞれメモリチャネル311、321、411、421に対応する、チャネル設定値保持部31、32、41、42へ書き込む。同時に、チャネル設定値生成部52は、生成されたチャネル設定値を、それぞれメモリチャネル311、321、411、421に対応する、チャネル設定値62a、62b、62c、62dとして不揮発性メモリ6へ書き込む。

【0039】

チャネル設定値生成部52は、SPD比読み出し制御部53によるSPD比較処理において、型式番号が不一致であると判定されたメモリモジュール71〜78と接続されるメモリチャネル311、321、411、421に対してのみ、チャネル設定値生成処理を行う。SPD比較処理において型式番号が不一致であると判定されたメモリモジュール71〜78は、SPD読み出し制御部53により、SPD63a〜63hに記憶されたメモリモジュール71〜78の仕様情報を更新されるためである。一方、チャネル設定値生成部52は、メモリチャネル311、321、411、421と接続されるメモリモジュール71〜78が、それぞれSPD読み出し制御部53によるSPD比較処理において型式番号が一致すると判定された場合、チャネル設定値生成処理を省略する。この場合、不揮発性メモリ6に記憶されたチャネル設定値62a〜62dを用いてメモリ初期化処理が行われる。これによって、メモリ初期化処理が高速化される。

【0040】

次に、アドレス変換設定値生成部51は、アドレス変換設定値を生成するアドレス変換値生成処理を行う。まず、アドレス変換設定値生成部51は、アドレス変換値生成処理において、不揮発性メモリ6に記憶されたSPD63a〜63hに基づいてメモリモジュール71〜78の実装状況を検出してアドレス空間を設定する。次に、アドレス変換設定値生成部51は、設定されたアドレス空間を用いてアドレス変換設定値を生成する。アドレス変換設定値生成部51は、生成されたアドレス変換設定値を、チップセット2のアドレス変換設定値保持部21へ記憶させると共に、不揮発性メモリ6にアドレス変換設定値61として記憶させる。

【0041】

アドレス変換設定値生成部51は、コンピュータシステムの備える全てのメモリモジュ−ル71〜78にSPD読み出し制御部53によるSPD比較処理において型式番号が不一致であるメモリモジュール71〜78が存在する場合にのみ、アドレス変換設定値生成処理を行う。SPD比較処理において型式番号が不一致であると判定されたメモリモジュール71〜78は、SPD読み出し制御部53により、SPD63a〜63hに記憶されたメモリモジュール71〜78の仕様情報を更新されるためである。アドレス変換設定値生成部51は、コンピュータシステムの備える全てのメモリモジュ−ル71〜78にSPD読み出し制御部53によるSPD比較処理において型式番号が不一致であるメモリモジュール71〜78が存在しない場合、アドレス変換設定値生成処理を省略する。この場合、不揮発性メモリ6に記憶されたアドレス設定値61を用いてメモリ初期化処理が行われる。これによって、メモリ初期化処理が高速化される。以上が、メモリ初期化部5の説明である。

【0042】

なお、メモリ初期化部5は、ハードウェアとして実現されても良いし、ソフトウェアとして実現されても良い。メモリ初期化部5がソフトウェアとして実現される場合には、メモリ初期化部5の機能を実現するためのコンピュータプログラムが、不揮発性メモリ6に記憶される。プロセッサ1が、不揮発性メモリ6に記憶されたコンピュータプログラムを実行することにより、メモリ初期化部5の機能が実現される。

【0043】

以上が、本実施形態におけるコンピュータシステムの構成の説明である。

【0044】

[動作の説明]

次に、上述のような構成の本実施形態におけるコンピュータシステムの動作の説明を行う。図3A、図3Bは、本実施形態におけるコンピュータシステムの動作を示すフローチャートである。

【0045】

まず、コンピュータシステムの電源が「ON」される(ステップS10)。メモリ初期化部5のSPD読み出し制御部53は、SPD比較処理を開始する。SPD読み出し制御部53は、メモリモジュール部7のメモリモジュール71〜78のSPD701〜708へ順にアクセスを開始する(ステップS20)。

【0046】

はじめに、SPD読み出し制御部53は、メモリモジュール71のSPD701にアクセスすると、図2に示したデータ格納領域701bに格納されたメモリモジュールの型式番号を読み出す。SPD読み出し制御部53は、SPD701から読み出されたメモリモジュールの型式番号と、不揮発性メモリ6にSPD701に対応して記憶されたSPD63aのメモリモジュールの型式番号とが一致するか否かを比較する(ステップS30)。

【0047】

一致しない場合(ステップS30のNo)、SPD読み出し制御部53は、SPD701のデータ格納領域701a、及び701bに格納されたメモリモジュール71の仕様情報と製造者関連情報とを読み出して、不揮発性メモリ6にSPD701に対応するSPD63aとして記憶させる(ステップS40)。その後、ステップS70へ進む。

【0048】

一方、一致する場合(ステップS30のYes)、SPD読み出し制御部53は、SPD701から図2に示したデータ格納領域701bに格納されるメモリモジュールのシリアル番号を読み出して、不揮発性メモリ6にSPD701に対応して記憶されたSPD63aのメモリモジュールのシリアル番号と一致するか否かを比較する(ステップS50)。

【0049】

一致しない場合(ステップS50のNo)、SPD読み出し制御部53は、SPD701のデータ格納領域701bに格納されたメモリモジュール71の製造者関連情報を読み出して、不揮発性メモリ6にSPD701に対応するSPD63aとして記憶させる(ステップS60)。このように、型式番号が一致するもののシリアル番号が不一致であるメモリモジュールは、同一の仕様で異なるシリアル番号のメモリモジュールへの交換があったと考えられるためである。SPD読み出し制御部53は、SPD701からの読み出し範囲と、SPD63aにおける更新範囲を限定することで、メモリ初期化処理の高速化を計ることができる。その後、ステップS70へ進む。

【0050】

続いて、SPD701のメモリモジュールのシリアル番号と、SPD63aのメモリモジュールのシリアル番号とが一致する場合(ステップS50のYes)、ステップS70へ進む。この場合、メモリモジュール71の型式番号もシリアル番号も一致しているため、電源ONの前後にメモリモジュール71の交換は発生していないと判断できるからである。

【0051】

SPD読み出し制御部53は、メモリモジュール部7の備える全てのメモリモジュール71〜78に対するSPD比較処理が完了したか否かを判定する(ステップS70)。全てのメモリモジュール71〜78に対するSPD比較処理が完了していない場合(ステップS70のNo)、ステップS20へ戻り、次のメモリモジュール(この場合、例えば、メモリモジュール72)に対するSPD比較処理を行う。一方、全てのメモリモジュール71〜78に対するSPD比較処理が完了した場合(ステップS70のYes)、ステップS80へ進む。

【0052】

続いて、チャネル設定値生成部52は、チャネル設定値生成処理を開始する(ステップS80)。チャネル設定値生成部52は、メモリチャネル311、321、411、421に対して順に処理を行う。はじめに、チャネル設定値生成部52は、メモリチャネル311に対するチャネル処理生成処理を行う。チャネル設定値生成部52は、メモリチャネル311に接続されたメモリモジュール71、及び72に対して、メモリモジュールの型式番号の不一致が無かったかを判定する(ステップS90)。すなわち、メモリチャネル311に接続されたメモリモジュール71、及び72のSPD701、及び702に対して、ステップS40が実行されたか否かを判定する。メモリモジュール71、及び72のいずれにおいても、メモリモジュールの型式番号不一致が無い場合(ステップS90のYes)、すなわち、SPD701、及び702に対するステップS40の実行が無い場合、チャネル設定値生成部52は、メモリチャネル311に対するチャネル設定値生成処理を行わずに、ステップS110へ進む。

【0053】

一方、メモリモジュール71、あるいは72の少なくともいずれかにおいて、メモリモジュールの型式番号不一致が有った場合(ステップS90のNo)、すなわち、SPD701、あるいは702の少なくともいずれかに対してステップS40が実行された場合、チャネル設定値生成部52は、メモリチャネル311に対するチャネル設定値生成処理を行う(ステップS100)。チャネル設定値生成部52は、不揮発性メモリ6に記憶されたSPD63a、63bに基づいて、メモリチャネル311に対応するチャネル設定値を生成する。チャネル設定値生成部52は、生成されたチャネル設定値を、メモリコントローラ31のチャネル設定値保持部31へ記憶させるともに、不揮発性メモリ6にチャネル設定値62aとして記憶させる。その後、ステップS110へ進む。

【0054】

このように、チャネル設定値生成部52は、各メモリチャネル311、321、411、421に接続されるメモリモジュール71〜78に、SPD読み出し制御部53によるSPD比較処理において、型式番号が不一致であると判定されたメモリモジュールが存在す場合のみ、当該メモリチャネルに対してチャネル設定値生成処理を行う。この場合、当該メモリモジュールは、前回のメモリ初期化処理後に仕様の異なるメモリモジュールへ交換されたと考えられるからである。一般的に、メモリチャネル設定値生成処理は、メモリチャネル上において段階的にインピーダンス確認試験や、メモリモジュールを正常にリード/ライトするための遅延の窓(eye)を確保する試験が必要となり時間を要する。そこで、メモリモジュール71〜78の型式番号が一致した場合、あるいは、型式番号は一致しているがシリアル番号のみが不一致の場合には、メモリモジュール71〜78の仕様に変更は無いと考えて、チャネル設定値生成部52は、対応するメモリチャネル311、321、411、421に対するチャネル設定値生成処理を省略する。この場合、不揮発性メモリ6に記憶されたチャネル設定値62a〜62dを用いてメモリ初期化処理が行われて、メモリ初期化処理が高速化される。

【0055】

図3A、図3Bの説明に戻り、チャネル設定値生成部52は、全てのメモリチャネル311、321、411、421に対するチャネル設定値生成処理を完了したかを判定する(ステップS110)。全てのメモリチャネル311、321、411、421に対するチャネル設定値生成処理が完了していない場合(ステップS110のNo)、ステップS80へ戻り、次のメモリチャネル(この場合、例えば、メモリチャネル321)、に対するチャネル設定値生成処理を行う。一方、全てのメモリチャネル311、321、411、421に対するチャネル設定値生成処理が完了した場合(ステップS110のYes)、チャネル設定値生成部52は、メモリチャネル311、321、411、421を初期化する(ステップS120)。

【0056】

続いて、アドレス変換設定値生成部51は、メモリモジュール7の備える任意のメモリモジュール71〜78において、メモリモジュールの型式番号の不一致が無かったかを判定する(ステップS130)。すなわち、メモリモジュール7の備える任意のメモリモジュール71〜78に対して、ステップS40が実行されたか否かを判定する。

【0057】

メモリモジュール7の備える任意のメモリモジュール71〜78において、メモリモジュールの型式番号に不一致が有った場合(ステップS130のNo)、すなわち、メモリモジュール7の備える任意のメモリモジュール71〜78に対して、ステップS40の実行があった場合、アドレス変換設定値生成部51は、アドレス変換設定値生成処理を実行する(ステップS140)。アドレス変換設定値生成部51は、不揮発性メモリ6に記憶されたSPD63a〜63hに基づいて、メモリモジュール71〜78の実装状況を検出してアドレス空間を設定する。アドレス変換設定値生成部51は、設定されたアドレス空間を用いてアドレス変換設定値を生成する。アドレス変換設定値生成部51は、生成されたアドレス変換設定値を、チップセット2のアドレス変換設定値保持部21へ記憶させると共に、不揮発性メモリ6にアドレス変換設定値61として記憶させる。これにより、本フローチャートにおける動作は終了となる。

【0058】

一方、メモリモジュール7の備える任意のメモリモジュール71〜78において、メモリモジュールの型式番号不一致が無い場合(ステップS130のYes)、すなわち、メモリモジュール7の備える任意のメモリモジュール71〜78に対して、ステップS40の実行が無い場合、アドレス変換設定値生成部51は、アドレス変換設定値生成処理を行わない。この場合、本フローチャートにおける動作は終了となる。

【0059】

このように、アドレス変換設定値生成部51は、SPD比較処理においてメモリモジュール71〜78の少なくとも一つの型式番号に不一致があった場合のみ、アドレス変換設定値処理を行う。この場合、メモリモジュール71〜78が前回のメモリ初期化処理の後に仕様の異なるメモリモジュールへ交換されたと考えられるからである。一方で、アドレス変換設定値生成部51は、SPD比較処理において、メモリモジュール71〜78に型式番号の不一致が無い場合、あるいは、型式番号が一致するもののシリアル番号のみが不一致の場合には、メモリモジュール71〜78に仕様の変更は無いと判断できるため、アドレス変換設定値処理を省略する。この場合、不揮発性メモリ6に記憶されたアドレス変換設定値を用いてメモリ初期化処理が行われてメモリ初期化処理が高速化される。

【0060】

以上が、本実施形態におけるコンピュータシステムの動作の説明である。

【0061】

[実施例の説明]

次に、図1Aから図3Bまでを参照して、上述のような構成及び動作である本実施形態におけるコンピュータシステムの具体的な動作例を説明する。

【0062】

はじめに、初めてコンピュータシステムの電源を投入した場合の動作例を説明する。

【0063】

まず、コンピュータシステムの電源が「ON」される(ステップS10)。このとき、不揮発性メモリ6は、図1Aに示された外部からのリセット指示f200に基づいて、データの初期化(無効化)が行われる。メモリ初期化部5のSPD読み出し制御部53は、SPD比較処理を開始する。まず、SPD読み出し制御部53は、メモリモジュール71のSPD701にアクセスして(ステップS20)、データ格納領域701bに格納されたメモリモジュールの型式番号を読み出す。SPD読み出し制御部53は、SPD701から読み出されたメモリモジュールの型式番号と、不揮発性メモリ6にSPD701に対応して記憶されたSPD63aのメモリモジュールの型式番号とが一致するか否かを比較する(ステップS30)。

【0064】

今回は、初めての電源投入であり、SPD63aは無効データであるため、メモリモジュールの型式番号は一致しない(ステップS30のNo)、SPD読み出し制御部53は、SPD701のデータ格納領域701a、及び701bに格納されたメモリモジュール71の仕様情報と製造者関連情報とを読み出して、不揮発性メモリ6にSPD701に対応するSPD63aとして記憶させる(ステップS40)。その後、全メモリモジュールに対するSPD比較処理を完了したかを判定し(ステップS70)、完了していないため(ステップS70のNo)、SPD702〜708に対して順にアクセスして(ステップS20)、SPD比較処理を繰り返す。

【0065】

前述の通り、現時点でSPD63b〜63hは無効データであるため、SPD702〜708に格納されたメモリモジュールの型式番号とはいずれも一致しない(ステップS30のNo)。そのため、SPD読み出し制御部53は、SPD702〜708のデータ格納領域702a〜708a、及び702b〜708bに格納されたメモリモジュール72〜78の仕様情報と製造者関連情報とを読み出して、不揮発性メモリ6へSPD63b〜hとして記憶させる(ステップS40)処理を繰り返すことになる。

【0066】

SPD読み出し制御部53が全てのメモリモジュール71〜78に対するSPD比較処理が完了すると(ステップS70のYes)、チャネル設定値生成部52は、チャネル設定値生成処理を開始する(ステップS80)。まず、チャネル設定値生成部52は、メモリチャネル311に対するチャネル処理生成処理を行う。チャネル設定値生成部52は、メモリチャネル311に接続されたメモリモジュール71、及び72に対して、メモリモジュールの型式番号の不一致が無かったかを判定する(ステップS90)。

【0067】

今回は、SPD701、SPD702の双方ともメモリモジュールの型式番号が不一致である(ステップS90のNo)。そのため、チャネル設定値生成部52は、メモリチャネル311に対するチャネル設定値生成処理を行う(ステップS100)。チャネル設定値生成部52は、不揮発性メモリ6に記憶されたSPD63a、63bに基づいて、メモリチャネル311に対応するチャネル設定値を生成する。チャネル設定値生成部52は、生成されたチャネル設定値を、メモリコントローラ31のチャネル設定値保持部31へ記憶させるともに、不揮発性メモリ6にチャネル設定値62aとして記憶させる。

【0068】

チャネル設定値生成部52は、全てのメモリチャネル311、321、411、421に対するチャネル設定値生成処理を完了したかを判定し(ステップS110)、完了していないため(ステップS110のNo)、メモリチャネル321、411、421に対して順にチャネル設定値生成処理を行う(ステップS80)。今回は、SPD701〜708に格納されたメモリモジュールの型式番号が不一致であったため(ステップS90のNo)、チャネル設定値生成部52は、メモリチャネル321、411、421に対してもチャネル設定値生成処理を行うことになる(ステップS100)。

【0069】

すなわち、チャネル設定値生成部52は、不揮発性メモリ6に記憶されたSPD63c、63dに基づいて、メモリチャネル321に対応するチャネル設定値を生成し、同様に、SPD63e、63fに基づいてメモリチャネル411、SPD63g、63hに基づいてメモリチャネル421を生成する。チャネル設定値生成部52は、生成されたチャネル設定値を、それぞれメモリコントローラ3、4のチャネル設定値保持部32、41、42へ記憶させるともに、不揮発性メモリ6にチャネル設定値62b、62c、62dとして記憶させる。

【0070】

全てのメモリチャネル311、321、411、421に対するチャネル設定値生成処理すると(ステップS110のYes)、チャネル設定値生成部52は、メモリチャネル311、321、411、421を初期化する(ステップS120)。

【0071】

続いて、アドレス変換設定値生成部51は、メモリモジュール7の備える任意のメモリモジュール71〜78において、メモリモジュールの型式番号の不一致が無かったかを判定する(ステップS130)。今回は、全てのメモリモジュール71〜78の型式番号が不一致であったため(ステップS130のNo)、アドレス変換設定値生成部51は、アドレス変換設定値生成処理を実行する(ステップS140)。アドレス変換設定値生成部51は、不揮発性メモリ6に記憶されたSPD63a〜63hに基づいて、メモリモジュール71〜78の実装状況を検出してアドレス空間を設定する。アドレス変換設定値生成部51は、設定されたアドレス空間を用いてアドレス変換設定値を生成する。アドレス変換設定値生成部51は、生成されたアドレス変換設定値を、チップセット2のアドレス変換設定値保持部21へ記憶させると共に、不揮発性メモリ6にアドレス変換設定値61として記憶させて、本フローチャートにおける動作を終了する。

【0072】

以上が、初めてコンピュータシステムの電源を投入した場合の動作例を説明である。

【0073】

続いて、2回目にコンピュータシステムの電源を投入した場合であって、前回以降、メモリモジュール71〜78の交換がされていない場合の動作例の説明を行う。

【0074】

まず、コンピュータシステムの電源が「ON」される(ステップS10)。メモリ初期化部5のSPD読み出し制御部53は、SPD比較処理を開始する。まず、SPD読み出し制御部53は、メモリモジュール71のSPD701にアクセスして(ステップS20)、データ格納領域701bに格納されたメモリモジュールの型式番号を読み出す。SPD読み出し制御部53は、SPD701から読み出されたメモリモジュールの型式番号と、不揮発性メモリ6にSPD701に対応して記憶されたSPD63aのメモリモジュールの型式番号とが一致するか否かを比較する(ステップS30)。

【0075】

SPD63aは、初回の電源投入時にSPD701の内容を複製して保存された内容であるため、メモリモジュールの型式番号は一致する(ステップS30のYes)。続いて、SPD読み出し制御部53は、SPD701からメモリモジュールのシリアル番号を読み出して、不揮発性メモリ6にSPDに対応して記憶されたSPD63aのメモリモジュールのシリアル番号と一致するか否かを比較する(ステップS50)。SPD63aは、初回の電源投入時にSPD701の内容を複製して保存された内容であるため、メモリモジュールのシリアル番号も一致する(ステップS50のYes)。このように、メモリモジュール71の型式番号もシリアル番号も一致しているため、電源ONの前後にメモリモジュール71の交換は発生していないと判断できる。そのため、SPD読み出し制御部53は、SPD63aの更新処理を行わずにSPD701に対するSPD比較処理を完了する。

【0076】

SPD読み出し制御部53は、メモリモジュール部7の備える全てのメモリモジュール71〜78に対するSPD比較処理が完了したか否かを判定し、(ステップS70)、完了していないため(ステップS70のNo)、SPD702〜708に対して順にアクセスして(ステップS20)、SPD比較処理を繰り返す。

【0077】

前述の通り、現時点でSPD63b〜63hは、初回の電源投入時にSPD702〜708の内容を複製して保存された内容であるため、メモリモジュールの型式番号とはいずれも一致し(ステップS30のYes)、また、メモリモジュールのシリアル番号もいずれも一致する(ステップS50のYes)。そのため、SPD読み出し制御部53は、SPD702〜708に格納された仕様情報(702a〜708a)と製造者関連情報(702b〜708b)のいずれも、不揮発性メモリ6へ記憶させることは無く、メモリ初期化処理を高速化できる。

【0078】

SPD読み出し制御部53が全てのメモリモジュール71〜78に対するSPD比較処理が完了すると(ステップS70のYes)、チャネル設定値生成部52は、チャネル設定値生成処理を開始する(ステップS80)。まず、チャネル設定値生成部52は、メモリチャネル311に対するチャネル設定値生成処理を行う。チャネル設定値生成部52は、メモリチャネル311に接続されたメモリモジュール71、及び72に対して、メモリモジュールの型式番号の不一致が無かったかを判定する(ステップS90)。

【0079】

今回は、SPD701、SPD702の双方ともメモリモジュールの型式番号に不一致が無い(ステップS90のYes)。そのため、チャネル設定値生成部52は、メモリチャネル311に対するチャネル設定値生成処理を行わない。チャネル設定値生成部52は、全てのメモリチャネル311、321、411、421に対するチャネル設定値生成処理を完了したかを判定し(ステップS110)、完了していないため(ステップS110のNo)、メモリチャネル321、411、421に対して順にチャネル設定値生成処理を行う(ステップS80)。今回はSPD701〜708の全てにおいてメモリモジュールの型式番号に不一致が無かったため(ステップS90のYes)、チャネル設定値生成部52は、メモリチャネル321、411、421に対してもチャネル設定値生成処理を行わない。SPD比較処理においてメモリモジュール71〜78の型式番号とシリアル番号とに不一致が無いため、メモリモジュール71〜78に仕様の変更が発生していないと判断できるためである。この場合、不揮発性メモリ6に記憶されたチャネル設定値62a〜62dを用いてメモリ初期化処理が行われて、メモリ初期化処理が高速化される。

【0080】

全てのメモリチャネル311、321、411、421に対するチャネル設定値生成処理すると(ステップS110のYes)、チャネル設定値生成部52は、メモリチャネル311、321、411、421を初期化する(ステップS120)。

【0081】

続いて、アドレス変換設定値生成部51は、メモリモジュール7の備える任意のメモリモジュール71〜78において、メモリモジュールの型式番号の不一致が無かったかを判定する(ステップS130)。今回は、全てのメモリモジュール71〜78の型式番号が不一致でなかったため(ステップS130のYes)、アドレス変換設定値生成部51は、アドレス変換設定値生成処理を実行せず、本フローチャートにおける動作を終了する。SPD比較処理においてメモリモジュール71〜78の型式番号とシリアル番号とに不一致が無い場合、メモリモジュール71〜78に仕様の変更が発生していないと判断することができるためである。この場合、不揮発性メモリ6に記憶されたアドレス変換設定値61を用いてメモリ初期化処理が行われて、メモリ初期化処理が高速化される。

【0082】

以上が、2回目にコンピュータシステムの電源を投入した場合であって、前回以降、メモリモジュール71〜78の交換がされていない場合の動作例の説明である。

【0083】

続いて、2回目にコンピュータシステムの電源を投入した場合であって、前回以降に、メモリモジュール71を同一の型式番号で異なるシリアル番号のメモリモジュールへ交換を行った場合の動作例の説明を行う。

【0084】

まず、コンピュータシステムの電源が「ON」される(ステップS10)。メモリ初期化部5のSPD読み出し制御部53は、SPD比較処理を開始する。まず、SPD読み出し制御部53は、メモリモジュール71のSPD701にアクセスして(ステップS20)、データ格納領域701bに格納されたメモリモジュールの型式番号を読み出す。SPD読み出し制御部53は、SPD701から読み出されたメモリモジュールの型式番号と、不揮発性メモリ6にSPD701に対応して記憶されたSPD63aのメモリモジュールの型式番号とが一致するか否かを比較する(ステップS30)。

【0085】

メモリモジュール71は交換されているもののSPD701に格納されたメモリモジュールの型式番号は交換前後で同一であるため、メモリモジュールの型式番号は一致する(ステップS30のYes)。続いて、SPD読み出し制御部53は、SPD701からメモリモジュールのシリアル番号を読み出して、不揮発性メモリ6にSPDに対応して記憶されたSPD63aのメモリモジュールのシリアル番号と一致するか否かを比較する(ステップS50)。メモリモジュール71は交換されており、SPD701に格納されたメモリモジュールのシリアル番号は交換前後で異なるため、メモリモジュールのシリアル番号は一致しない(ステップS50のNo)。SPD読み出し制御部53は、SPD701のデータ格納領域701bに格納された製造者関連情報を読み出して、不揮発性メモリ6にSPD701に対応するSPD63aとして記憶させる(ステップS60)。このように、SPD読み出し制御部53は、SPD701からの情報の読み出し範囲を、データ格納領域701bの製造者関連情報のみ限定することで、メモリ初期化処理の高速化を計ることができる。その後、ステップS70へ進む。

【0086】

SPD読み出し制御部53は、メモリモジュール部7の備える全てのメモリモジュール71〜78に対するSPD比較処理が完了したか否かを判定し、(ステップS70)、完了していないため(ステップS70のNo)、SPD702〜708に対して順にアクセスして(ステップS20)、SPD比較処理を繰り返す。

【0087】

現時点でSPD63b〜63hは、初回の電源投入時にSPD702〜708の内容を複製して保存された内容であるため、メモリモジュールの型式番号とはいずれも一致し(ステップS30のYes)、また、メモリモジュールのシリアル番号もいずれも一致する(ステップS50のYes)。そのため、SPD読み出し制御部53は、SPD702〜708に格納された仕様情報(702a〜708a)と製造者関連情報(702b〜708b)のいずれも、不揮発性メモリ6へ記憶させる処理を行うことが無く、SPD比較処理を高速化できる。

【0088】

SPD読み出し制御部53が全てのメモリモジュール71〜78に対するSPD比較処理が完了すると(ステップS70のYes)、チャネル設定値生成部52は、チャネル設定値生成処理を開始する(ステップS80)。まず、チャネル設定値生成部52は、メモリチャネル311に対するチャネル処理生成処理を行う。チャネル設定値生成部52は、メモリチャネル311に接続されたメモリモジュール71、及び72に対して、メモリモジュールの型式番号の不一致が無かったかを判定する(ステップS90)。

【0089】

今回は、SPD701においてメモリモジュールのシリアル番号の変更はあったものの、SPD701、SPD702の双方ともメモリモジュールの型式番号に不一致が無い(ステップS90のYes)。そのため、チャネル設定値生成部52は、メモリチャネル311に対するチャネル設定値生成処理を行わない。チャネル設定値生成部52は、全てのメモリチャネル311、321、411、421に対するチャネル設定値生成処理を完了したかを判定し(ステップS110)、完了していないため(ステップS110のNo)、メモリチャネル321、411、421に対して順にチャネル設定値生成処理を行う(ステップS80)。SPD703〜708においてメモリモジュールの型式番号には不一致が無かったため(ステップS90のYes)、メモリモジュール71〜78の交換に伴う仕様の変更が無いと考えられるため、チャネル設定値生成部52は、メモリチャネル321、411、421に対してもチャネル設定値生成処理を行わない。この場合、不揮発性メモリ6に記憶されたチャネル設定値62a〜62dを用いてメモリ初期化処理が行われて、メモリ初期化処理が高速化される。全てのメモリチャネル311、321、411、421に対するチャネル設定値生成処理すると(ステップS110のYes)、チャネル設定値生成部52は、メモリチャネル311、321、411、421を初期化する(ステップS120)。

【0090】

続いて、アドレス変換設定値生成部51は、メモリモジュール7の備える任意のメモリモジュール71〜78において、メモリモジュールの型式番号の不一致が無かったかを判定する(ステップS130)。今回は、メモリモジュール71のシリアル番号に不一致があったものの、メモリモジュール71〜78の型式番号に不一致は無かったため(ステップS130のYes)、アドレス変換設定値生成部51は、アドレス変換設定値生成処理を実行せず、本フローチャートにおける動作を終了する。このように、SPD701〜708とSPD63a〜hとの比較においてメモリモジュールの型式番号に不一致が無くシリアル番号にのみ不一致が有る場合、メモリモジュール71〜78の交換に伴う仕様の変更は発生していないと判断することができる。そのため、アドレス変換設定値生成部51は、アドレス変換設定値生成処理を実行しない。この場合、不揮発性メモリ6に記憶されたアドレス変換設定値51を用いてメモリ初期化処理が行われて、メモリ初期化処理が高速化される。

【0091】

以上が、2回目にコンピュータシステムの電源を投入した場合であって、前回以降に、メモリモジュール71を同一の型式番号で異なるシリアル番号のメモリモジュールへ交換を行った場合の動作例の説明である。

【0092】

続いて、2回目にコンピュータシステムの電源を投入した場合であって、前回以降に、メモリモジュール71を型式番号及びシリアル番号の異なるメモリモジュールへ交換を行った場合の動作例の説明を行う。

【0093】

まず、コンピュータシステムの電源が「ON」される(ステップS10)。メモリ初期化部5のSPD読み出し制御部53は、SPD比較処理を開始する。まず、SPD読み出し制御部53は、メモリモジュール71のSPD701にアクセスして(ステップS20)、データ格納領域701bに格納されたメモリモジュールの型式番号を読み出す。SPD読み出し制御部53は、SPD701から読み出されたメモリモジュールの型式番号と、不揮発性メモリ6にSPD701に対応して記憶されたSPD63aのメモリモジュールの型式番号とが一致するか否かを比較する(ステップS30)。

【0094】

メモリモジュール71は交換にされておりSPD701に格納されたメモリモジュールの型式番号は交換前後で異なっている、メモリモジュールの型式番号は一致しない(ステップS30のNo)。そのため、SPD読み出し制御部53は、SPD701のデータ格納領域701a、及び701bに格納されたメモリモジュール71の仕様情報と製造者関連情報とを読み出して、不揮発性メモリ6にSPD701に対応するSPD63aとして記憶させる(ステップS40)。その後、全メモリモジュールに対するSPD比較処理を完了したかを判定し(ステップS70)、完了していないため(ステップS70のNo)、SPD702〜708に対して順にアクセスして(ステップS20)、SPD比較処理を繰り返す。

【0095】

現時点でSPD63b〜63hは、初回の電源投入時にSPD702〜708の内容を複製して保存された内容であるため、メモリモジュールの型式番号とはいずれも一致し(ステップS30のYes)、また、メモリモジュールのシリアル番号もいずれも一致する(ステップS50のYes)。そのため、SPD読み出し制御部53は、SPD702〜708に格納された仕様情報(702a〜708a)と製造者関連情報(702b〜708b)のいずれも、不揮発性メモリ6へ記憶させる処理を行わない。このように、交換によりメモリモジュールの型式番号の不一致が発生したメモリモジュール71に対してのみ、仕様情報(701a〜708a)と製造者関連情報(701a〜708a)の更新を行うため、交換の行われていないメモリモジュール72〜78に対するSPD比較処理を高速化できる。

【0096】

SPD読み出し制御部53が全てのメモリモジュール71〜78に対するSPD比較処理が完了すると(ステップS70のYes)、チャネル設定値生成部52は、チャネル設定値生成処理を開始する(ステップS80)。まず、チャネル設定値生成部52は、メモリチャネル311に対するチャネル処理生成処理を行う。チャネル設定値生成部52は、メモリチャネル311に接続されたメモリモジュール71、及び72に対して、メモリモジュールの型式番号の不一致が無かったかを判定する(ステップS90)。

【0097】

今回は、交換によりSPD701のメモリモジュールの型式番号に不一致があった(ステップS90のNo)。そのため、チャネル設定値生成部52は、メモリチャネル311に対するチャネル設定値生成処理を行う(ステップS100)。チャネル設定値生成部52は、不揮発性メモリ6に記憶されたSPD63a、63bに基づいて、メモリチャネル311に対応するチャネル設定値を生成する。ここで、SPD63aは、ステップS40において、交換後のメモリモジュール71のSPD701と同一の内容となっている。チャネル設定値生成部52は、生成されたチャネル設定値を、メモリコントローラ31のチャネル設定値保持部31へ記憶させるともに、不揮発性メモリ6にチャネル設定値62aとして記憶させる。

【0098】

チャネル設定値生成部52は、全てのメモリチャネル311、321、411、421に対するチャネル設定値生成処理を完了したかを判定し(ステップS110)、完了していないため(ステップS110のNo)、メモリチャネル321、411、421に対して順にチャネル設定値生成処理を行う(ステップS80)。SPD703〜708においてメモリモジュールの型式番号に不一致が無いため(ステップS90のYes)、チャネル設定値生成部52は、メモリチャネル321、411、421に対してチャネル設定値生成処理を行わない。このように、チャネル設定値生成部52は、メモリモジュールの型式番号に不一致を検出されたメモリモジュール71と接続されるメモリチャネル311に対してのみチャネル設定値生成処理を行う。これにより、メモリ初期化処理を高速化できる。

【0099】

全てのメモリチャネル311、321、411、421に対するチャネル設定値生成処理すると(ステップS110のYes)、チャネル設定値生成部52は、メモリチャネル311、321、411、421を初期化する(ステップS120)。

【0100】

続いて、アドレス変換設定値生成部51は、メモリモジュール7の備える任意のメモリモジュール71〜78において、メモリモジュールの型式番号の不一致が無かったかを判定する(ステップS130)。今回は、メモリモジュール71の型式番号に不一致が有ったため(ステップS130のNo)、アドレス変換設定値生成部51は、アドレス変換設定値生成処理を実行する(ステップS140)。

【0101】

アドレス変換設定値生成部51は、不揮発性メモリ6に記憶されたSPD63a〜63hに基づいて、メモリモジュール71〜78の実装状況を検出してアドレス空間を設定する。アドレス変換設定値生成部51は、設定されたアドレス空間を用いてアドレス変換設定値を生成する。アドレス変換設定値生成部51は、生成されたアドレス変換設定値を、チップセット2のアドレス変換設定値保持部21へ記憶させると共に、不揮発性メモリ6にアドレス変換設定値61として記憶させて、本フローチャートにおける動作を終了する。

【0102】

以上が、2回目にコンピュータシステムの電源を投入した場合であって、前回以降に、メモリモジュール71を同一の型式番号の異なるシリアル番号のメモリモジュールへ交換を行った場合の動作例の説明である。

【0103】

ここまで説明を行ってきたように、本実施形態におけるコンピュータシステムは、コンピュータシステムの備える全てのメモリモジュール71〜78のSPD701〜708に対応するSPD63a〜63hと、メモリコントローラ3、4におけるメモリチャネル311、321、411、421のチャネル設定値と、各メモリモジュール71〜78のアドレス空間に対応させて生成されたアドレス変換設定値とを記憶する不揮発性メモリ6を備える。また、コンピュータシステムは、メモリ初期化処理において、各メモリモジュール71〜78のSPD710〜708を読み出して不揮発性メモリ6に記憶されたSPD63a〜63hと比較するメモリ比較処理を行うSPD読み出し制御部53と、メモリチャネル311、321、411、421毎のチャネル設定値の生成処理を行うチャネル設定値生成部52と、及びアドレス変換設定値の生成処理を行うアドレス変換設定値生成部51とを備える。

【0104】

SPD701〜708は、仕様情報(データ格納領域701a〜708a)と製造者関連情報(データ格納領域701b〜708b)とを含む。さらに、製造者関連情報は、メモリモジュールの型式番号、及びシリアル番号を含む。SPD読み出し制御部53は、SPD比較処理において、メモリモジュールの型式番号とシリアル番号とを比較する。SPD読み出し制御部53は、型式番号とシリアル番号がいずれも一致したメモリモジュール71〜78について、不揮発性メモリ6に記憶されたSPD63a〜63hの更新は行わない。SPD比較処理においてメモリモジュールの型式番号とシリアル番号とが一致するということは、搭載されているメモリモジュール71〜78が前回のメモリ初期化処理時のメモリモジュール71〜78と同一あると確認できたことを意味する。そのため、このようなメモリモジュールに対しては、不揮発性メモリ6のSPD63a〜63hの更新処理を省略することができる。

【0105】

一方、SPD読み出し制御部53は、型式番号が不一致であるメモリモジュール71〜78のSPD701〜708に格納された仕様情報と製造者関連情報とを読み出して不揮発性メモリ6に記憶されたSPD63a〜63hを更新する。型式番号が不一致であるメモリモジュール71〜78は、異なる仕様を有したメモリモジュール71〜78へ交換が行われたと考えることができるからである。また、SPD読み出し制御部53は、型式番号が一致するもののシリアル番号が不一致であるメモリモジュール71〜78のSPD701〜708から製造者関連情報のみを読み出して不揮発性メモリに記憶されたSPDを更新する。型式番号が一致するもののシリアル番号が不一致であるメモリモジュール71〜78は、同じ仕様を有する異なるシリアル番号のメモリモジュール71〜78に交換されたと考えられるからである。

【0106】

チャネル設定値生成部52は、型式番号が不一致であるメモリモジュール71〜78と接続されるメモリチャネル311、321、411、421に対してのみチャネル設定値の生成処理を行う。さらに、アドレス変換設定値生成部51は、コンピュータシステムの備える全てのメモリモジュール71〜78において、型式番号が不一致であるメモリモジュール71〜78が存在した場合にのみアドレス変換値生成処理を行う。チャネル設定値生成部52とアドレス変換設定値生成部51は、いずれも不揮発性メモリ6に記憶されたSPD53a〜53hの仕様情報を基にして、チャネル設定値とアドレス変換設定値とを生成する。SPD読み出し制御部53は、型式番号が不一致である場合のみ、不揮発性メモリ6に記憶されたSPD63a〜63hの仕様情報を更新する。型式番号が一致する場合、あるいは、型式番号が一致するもののシリアル番号が不一致である場合、不揮発性メモリ記憶6にされたSPD63a〜63hの仕様情報に変更は無い。そのため、チャネル設定値生成部52とアドレス変換設定値生成部51とが、生成するチャネル設定値、及びアドレス変換設定値も同一の値となる。そこで、型式番号が一致する場合、あるいは、型式番号が一致するもののシリアル番号が不一致である場合には、チャネル設定値及びアドレス変換設定値の生成処理を省略して、メモリ初期化処理の更なる高速化を計ることができる。

【0107】

以上、実施形態を参照して本発明のメモリ初期化装置を説明したが、本発明は上記実施形態に限定されるものではない。本発明の構成や詳細には、本発明の範囲内で当業者が理解し得る様々な変更を行うことができる。

【符号の説明】

【0108】

1 プロセッサ

2 チップセット

3、4 メモリコントローラ

5 メモリ初期化部

6 不揮発性メモリ

7 メモリモジュール部

21 アドレス変換設定値保持部

31、32、41、42 チャネル設定値保持部

51 アドレス変換設定値生成部

52 チャネル設定値生成部

53 SPD読み出し制御部

61 アドレス変換設定値

62a〜62d チャネル設定値

63a〜63h SPD

71〜78 メモリモジュール

311、321、411、421 メモリチャネル

701〜708 SPD

701a〜708a、701b〜708b、701c〜708c データ格納領域

【技術分野】

【0001】

本発明は、メモリ初期化処理を高速に実行するコンピュータシステムに関する。

【背景技術】

【0002】

コンピュータシステムは、起動時にメモリ初期化処理を実行する。近年、コンピュータシステムに搭載されるメモリ数の増加、及びメモリ容量の増大により、メモリ初期化処理の実行時間は増加傾向にある。そのため、メモリ初期化処理の高速化と、実行時間の短縮化が求められている。

【0003】

特許文献1は、メモリ初期化処理を高速実行することが可能な情報処理装置を開示している。特許文献1の情報処理装置は、各種プログラムを実行するCPU(Central Processing Unit)を有する情報処理装置である。情報処理装置は、RAM(Random Access Memory)と第1の不揮発性メモリとが搭載されたメモリモジュールと、第2の不揮発性メモリと、保存処理モジュールと、設定処理モジュールとを備える。

【0004】

RAMは、主メモリを構成するのに用いられる。第1の不揮発性メモリは、第1のSPD(Serial Presence Detect)を格納する。第2の不揮発性メモリは、CPUが直接アクセス可能なメモリ空間に割り当てられる。保存処理モジュールは、メモリモジュールの第1の不揮発性メモリに格納されている第1のSPDデータを第2のSPDデータとして第2の不揮発性メモリの所定領域に保存する。設定処理モジュールは、情報処理装置の電源オン時に第2の不揮発性メモリの所定領域に保存されている第2のSPDデータに基づいて、メモリモジュールに搭載されたRAMを主メモリの構成要素として機能させるための初期設定処理を行う。

【0005】

特許文献1の情報処理装置によれば、メモリモジュールの第1の不揮発性メモリに格納されたSPDデータではなく、CPUが直接アクセス可能なメモリ空間に割り当てられる第2の不揮発性メモリに保存されたSPDデータに基づいてメモリ初期化処理を実行することで、メモリ初期化処理を高速に実行することが可能になる。

【0006】

しかし、特許文献1の情報処理装置では、システムの備えるメモリモジュールのSPD情報のみを第2の不揮発性メモリであるフラッシュROM(Read Only Memory)へ格納する。そのため、以後の起動時におけるメモリ初期化処理では、SPD情報の読み出し処理については高速化を図れるものの、SPD情報の読み出し以降の処理については、高速化されない。

【0007】

また、特許文献1の情報処理装置では、コンピュータシステム上のフラッシュROM、及びメモリモジュールの双方のSPDへ、メモリモジュールの一致を確認するための専用フラグを記録する必要がある。そのため、フラッシュROMとメモリモジュールへデータを書き込む構成を必要とする。

【0008】

なお、関連技術として、特許文献2は、初期化された状態を直ちに判別することにより、初期化の時間を短縮可能な集積回路を開示している。また、特許文献3は、RAMなどの揮発性メモリに記憶される情報の量を低減しつつ処理の効率化を実現する半導体装置を開示している。

【先行技術文献】

【特許文献】

【0009】

【特許文献1】特開2007−122627号公報

【特許文献2】特開昭64−073409号公報

【特許文献3】特開2006−011533号公報

【発明の概要】

【発明が解決しようとする課題】

【0010】

本発明の目的は、メモリ初期化処理の更なる高速化を実現可能なコンピュータシステムを提供することである。

【課題を解決するための手段】

【0011】

本発明のコンピュータシステムは、第1のSPD情報を格納する複数のメモリモジュールと、第1のSPD情報は、複数のメモリモジュールの各々の仕様情報を含み、各メモリモジュールへアクセスするためにシステム内で用いられるアクセス設定値と、各メモリモジュールに対応させて第1のSPD情報の複製である第2のSPD情報とを記憶する不揮発性メモリと、複数のメモリモジュールの初期化処理において第1のSPD情報と第2のSPD情報とが一致するか否か比較判定処理を行って、比較判定処理において複数のメモリモジュールのうちから第1のSPD情報と第2のSPD情報とが一致しない不一致メモリモジュールを特定して、不一致メモリモジュールから第1のSPD情報を読み出して不揮発性メモリへ第2のSPD情報として書き込む読み出し制御部と、複数のメモリモジュールに不一致メモリモジュールが存在する場合に、アクセス設定値のうちで不一致メモリモジュールの第2のSPD情報が生成に用いられる選択アクセス設定値を、第2のSPD情報に基づいて生成して、選択アクセス設定値を不揮発性メモリへ書き込む設定値生成部とを備える。

【0012】

本発明のコンピュータシステムのメモリ初期化方法は、第1のSPD情報を格納する複数のメモリモジュールと、第1のSPD情報は、複数のメモリモジュールの各々の仕様情報を含み、不揮発性メモリとを備えるコンピュータシステムにおいて、各メモリモジュールへアクセスするためにシステム内で用いられるアクセス設定値と、各メモリモジュールに対応させて第1のSPD情報の複製である第2のSPD情報とを記憶するステップと、複数のメモリモジュールの初期化処理において第1のSPD情報と第2のSPD情報とが一致するか否か比較判定処理を行うステップと、比較判定処理において複数のメモリモジュールのうちから第1のSPD情報と第2のSPD情報とが一致しない不一致メモリモジュールを特定するステップと、不一致メモリモジュールから第1のSPD情報を読み出して不揮発性メモリへ第2のSPD情報として書き込むステップと、複数のメモリモジュールに不一致メモリモジュールが存在する場合に、アクセス設定値のうちで不一致メモリモジュールの第2のSPD情報が生成に用いられる選択アクセス設定値を第2のSPD情報に基づいて生成するステップと、選択アクセス設定値を不揮発性メモリへ書き込むステップとを備える。

【0013】

本発明のメモリ初期化プログラムは、上述のコンピュータシステムのメモリ初期化方法をコンピュータに実行させる。

【発明の効果】

【0014】

本発明によれば、メモリ初期化処理の更なる高速化を実現可能なコンピュータシステムを提供することができる。

【図面の簡単な説明】

【0015】

【図1A】図1Aは、本発明の実施形態におけるコンピュータシステムの構成を示す図である。

【図1B】図1Bは、本発明の実施形態におけるコンピュータシステムの構成を示す図である。

【図2】図2は、本発明の実施形態におけるSPD701〜708のデータフォーマットを示す図である。

【図3A】図3Aは、本発明の実施形態におけるコンピュータシステムの動作を示すフローチャートである。

【図3B】図3Bは、本発明の実施形態におけるコンピュータシステムの動作を示すフローチャートである。

【発明を実施するための形態】

【0016】

添付図面を参照して、本発明の実施形態によるコンピュータシステムを以下に説明する。

【0017】

[概要]

本実施形態におけるコンピュータシステムは、コンピュータシステムの備える全てのメモリモジュールのSPDと、メモリコントローラにおけるメモリチャネルのチャネル設定値と、各メモリモジュールのアドレス空間に対応させて生成されたアドレス変換設定値とを記憶する不揮発性メモリを備える。また、コンピュータシステムは、メモリ初期化処理において各メモリモジュールのSPDを読み出して不揮発性メモリに記憶されたSPDと比較するSPD比較処理を行うSPD読み出し制御部と、メモリチャネル毎のチャネル設定値の生成処理を行うチャネル設定値生成部と、及びアドレス変換設定値の生成処理を行うアドレス変換設定値生成部とを備える。

【0018】

SPDは、仕様情報と製造者関連情報とを含む。さらに、製造者関連情報は、メモリモジュールの型式番号、及びシリアル番号を含む。SPD読み出し制御部は、SPD比較処理において、メモリモジュールの型式番号とシリアル番号とを比較する。SPD読み出し制御部は、型式番号とシリアル番号の、いずれも一致したメモリモジュールについて、不揮発性メモリに記憶されたSPDの更新は行わない。SPDが一致するということは、搭載されているメモリモジュールが前回のメモリ初期化処理時のメモリモジュールと同一であると確認できたことを意味する。そのため、SPDが一致したメモリモジュールは、不揮発性メモリに記憶されたSPDの更新処理を省略することができる。

【0019】

一方、SPD読み出し制御部は、型式番号が不一致であるメモリモジュールからSPDに格納された仕様情報と製造者関連情報とを読み出して不揮発性メモリに記憶されたSPDを更新する。型式番号が不一致であるメモリモジュールは、異なる仕様を有したメモリモジュールへ交換が行われたと考えることができるからである。また、SPD読み出し制御部は、型式番号が一致するもののシリアル番号が不一致であるメモリモジュールからSPDの製造者関連情報のみを読み出して不揮発性メモリに記憶されたSPDを更新する。型式番号が一致するもののシリアル番号が不一致であるメモリモジュールは、同じ仕様を有する異なるシリアル番号のメモリモジュールに交換されたと考えられるからである。

【0020】

チャネル設定値生成部は、型式番号が不一致であるメモリモジュールと接続されるメモリチャネルに対してのみチャネル設定値の生成処理を行う。さらに、アドレス変換設定値生成部は、コンピュータシステムの備える全てのメモリモジュールにおいて、型式番号が不一致であるメモリモジュールが存在した場合にのみアドレス変換値生成処理を行う。チャネル設定値生成部とアドレス変換設定値生成部は、いずれも不揮発性メモリに記憶されたSPDの仕様情報を基にして、チャネル設定値とアドレス変換設定値とを生成する。SPD読み出し制御部は、型式番号が不一致である場合のみ、不揮発性メモリ記憶にされたSPDの仕様情報を更新する。

【0021】

型式番号が一致する場合、あるいは、型式番号が一致するもののシリアル番号が不一致である場合、不揮発性メモリ記憶にされたSPDの仕様情報に変更は無い。そのため、チャネル設定値生成部とアドレス変換設定値生成部とが、生成するチャネル設定値、及びアドレス変換設定値も同一の値となる。そこで、本実施形態におけるコンピュータシステムは、の型式番号が一致する場合、あるいは、型式番号が一致するもののシリアル番号が不一致である場合には、チャネル設定値及びアドレス変換設定値の生成処理を省略する。そして、不揮発性メモリに記憶されたチャネル設定値及びアドレス変換設定値を用いてメモリ初期化処理を行う。これによって、メモリ初期化処理の更なる高速化を計ることができる。以下、本実施形態におけるコンピュータシステムの構成及び動作を詳細に説明する。

【0022】

[構成の説明]

はじめに、本実施形態におけるコンピュータシステムの構成の説明を行う。図1A、図1Bは、本実施形態におけるコンピュータシステムの構成を示す図である。本実施形態のコンピュータシステムは、プロセッサ1と、チップセット2と、メモリコントローラ3、及び4と、メモリ初期化部5と、不揮発性メモリ6と、メモリモジュール部7とを備える。

【0023】

まず、プロセッサ1はCPU(Central Processing Unit)に例示される、プロセッサ1は、コンピュータプログラムを実行してコンピュータシステムの機能を実現する。

【0024】

次に、チップセット2は、プロセッサ1と、メモリコントローラ3、及び4と、メモリ初期化部5と、不揮発性メモリ6との間を接続して、それぞれの間で行われるデータ送受信を制御する。チップセット2は、アドレス変換設定値保持部21を備える。アドレス変換設定値保持部21は、アドレス変換設定値を保持している。アドレス変換設定値保持部21は、後述されるメモリ初期化部5のアドレス変換設定値生成部により、アドレス変換設定値を記憶される。チップセット2は、アドレス変換設定値に基づいて、プロセッサ1から入力するトランザクションをメモリコントローラ3、4へ振り分ける。

【0025】

次に、メモリモジュール部7は、メモリモジュール71〜78を備える。メモリモジュール71〜78は、RAM(Random Access Memory)に例示され、メモリ制御装置を含むコンピュータシステムにおける主記憶装置として使用される。メモリモジュール71〜78は、JEDEC(Joint Electron Device Engineering Council)に準拠した汎用的なメモリモジュールである。メモリモジュール71〜78は、それぞれSPD(Serial Presence Detect)701〜708を備える。SPD701〜708は、それぞれメモリモジュール71〜78に関する情報を記録している。

【0026】

ここで、図2は、本実施形態におけるSPD701〜708のデータフォーマットを示す図である。図2に記載されたSPD701〜708のデータフォーマットは、JEDECに準拠した一般的な汎用メモリのデータフォーマットと同様である。SPD701〜708のデータフォーマットは同様であるので、図2ではSPD701を例として説明を行う。SPD701は、256Byteのデータを格納することが可能である。SPD701は、3つのデータ格納領域701a〜701cに区分される。

【0027】

データ格納領域701aは、64byteのデータを格納可能であり、メモリモジュール71の物理的な仕様情報を格納する。メモリモジュール71の仕様情報とは、メモリモジュールの構成、容量、遅延パラメータ等である。これらのメモリモジュール71の仕様情報は、アドレス空間の設定や、メモリアクセスモードの設定等に用いられる。データ格納領域701bは、64byteのデータを格納可能であり、メモリモジュール71の製造者関連情報を格納する。製造者関連情報とは、メモリモジュール71の型式番号、及びシリアル番号を含む。データ格納領域701cは、128byteのデータを格納可能であり、ユーザに解放された領域となっている。以上が、SPD701〜708に格納されたデータフォーマットの説明である。

【0028】

次に、図1A、図1Bへ戻り、メモリコントローラ3、4は、プロセッサ1によるメモリモジュール部7のメモリモジュール71〜78へのアクセスを制御する。メモリコントローラ3は、2つのメモリチャネル311、及び321を備える。メモリコントローラ3は、メモリチャネル311を介して、メモリモジュール71、及び72と接続される。メモリコントローラ3は、メモリチャネル321を介して、メモリモジュール73、及び74と接続される。同様に、メモリコントローラ4は、2つのメモリチャネルであるメモリチャネル411、及び421を備える。メモリコントローラ4は、メモリチャネル411を介して、メモリモジュール75、及び76と接続される。メモリコントローラ4は、メモリチャネル421を介して、メモリモジュール77、及び78と接続される。

【0029】

また、メモリコントローラ3は、メモリチャネル311、及び321にそれぞれ対応するチャネル設定値保持部31、及び32を備える。チャネル設定値保持部31は、メモリチャネル311の制御に用いられるチャネル設定値を記憶する。チャネル設定値保持部32は、メモリチャネル321の制御に用いられるチャネル設定値を記憶する。チャネル設定値は、メモリチャネル31、あるいは32における、終端抵抗値や、遅延パラメータや、インピーダンス設定値といった値を含む。同様に、メモリコントローラ4は、メモリチャネル411、及び421にそれぞれ対応するチャネル設定値保持部41、及び42を備える。チャネル設定値保持部41は、メモリチャネル411の制御に用いられるチャネル設定値を記憶する。チャネル設定値保持部42は、メモリチャネル421の制御に用いられるチャネル設定値を記憶する。チャネル設定値は、メモリチャネル41、あるいは42における、終端抵抗値や、遅延パラメータや、インピーダンス設定値といった値を含む。

【0030】

なお、メモリコントローラ3、4の数は、2つに限定しない。これより多くても良いし、あるいは少なくとも良い。また、メモリコントローラ3、4は、デュアルチャネルでなくとも良い。メモリコントローラ3、4の備えるチャネル数は、1つでも良いし、あるいは2つより多くともよい。

【0031】

次に、不揮発性メモリ6は、アドレス変換設定値61と、チャネル設定値62a〜62dと、SPD62a〜62hとを記憶する。アドレス変換設定値61は、チップセット2のアドレス変換設定値保持部21に記憶されるアドレス変換設定値の複製である。また、チャネル設定値62a〜62dは、メモリコントローラ3、4のチャネル設定値保持部31、32、41、及び42にそれぞれ記憶されるチャネル設定値の複製である。さらに、SPD62a〜62hは、メモリモジュール71〜78のSPD701〜708に含まれる情報の複製である。SPD62a〜62hは、図2で説明を行った、SPD701〜708に格納されたデータのうち、データ格納領域701a〜708aの仕様情報、及び701b〜708bの製造者関連情報のみを記憶する。SPD62a〜62hは、データ格納領域701c〜708cのユーザ定義情報を記憶しない。

【0032】

なお、メモリモジュール部7のメモリモジュールの数や、メモリコントローラ3、4の数、あるいはメモリコントローラ3、4の備えるチャネル数が増減する場合には、これに応じて記憶するべきSPD、チャネル設定値、及びアドレス変換設定値のデータ量も変化する。

【0033】

次に、メモリ初期化部5は、アドレス変換設定値生成部51と、チャネル設定値生成部52と、SPD読み出し制御部53とを備える。

【0034】

まず、SPD読み出し部53は、メモリ初期化処理において、SPD比較処理を行う。SPD読み出し部53は、メモリモジュール71〜78に格納されたSPD701〜708を読み出して、不揮発性メモリ6に記憶されたSPD701〜708にそれぞれ対応するSPD63a〜63hと比較を行うことによりSPD比較処理を行う。SPD読み出し部53は、図2に示したデータ格納領域701b〜708b(製造者関連情報)から、メモリモジュール71〜78の型式番号とシリアル番号とを読み出して比較を行う。SPD読み出し部53は、SPD比較処理の結果に基づいて、SPD63a〜63hの更新を行う。

【0035】

SPD読み出し部53は、SPD比較処理においてメモリモジュール71〜78の型式番号が不一致であった場合、SPD701〜708のデータ格納領域701a〜708aとデータ格納領域701b〜708bからそれぞれ仕様情報と製造者関連情報とを読み出して、SPD63a〜63hとして不揮発性メモリ6へ記憶させる。メモリモジュール71〜78の型式番号が不一致である場合、前回のメモリ初期化処理以降に、メモリモジュール71〜78が仕様の異なるメモリモジュールへ交換されたと考えられる。そのため、SPD読み出し部53は、SPD701〜708から仕様情報と製造者関連情報とを読み出してSPD63a〜63hを更新する。

【0036】

また、SPD読み出し部53は、SPD比較処理においてメモリモジュール71〜78の型式番号は一致するもののシリアル番号が不一致であった場合、SPD701〜708のデータ格納領域701b〜708bから製造者関連情報のみを読み出して、SPD63a〜63hとして不揮発性メモリ6へ記憶させる。メモリモジュール71〜78の型式番号は一致するもののシリアル番号が不一致であった場合、前回のメモリ初期化処理以降に、メモリモジュール71〜78が仕様は同一であるがシリアル番号のみが異なるメモリモジュールへ交換されたと考えられる。そのため、SPD読み出し部53は、SPD701〜708から製造者関連情報のみを読み出してSPD63a〜63hを更新する。

【0037】

一方、SPD読み出し部53は、SPD比較処理において、メモリモジュール71〜78の型式番号及びシリアル番号が共に一致する場合、SPD701〜708から情報の読み出しを行わない。メモリモジュール71〜78の型式番号及びシリアル番号が一致する場合、メモリモジュール71〜78は、前回のメモリ初期化処理時のメモリモジュール71〜78と同一であり、交換は行われていないと考えられる。そのため、SPD読み出し部53は、SPD63a〜63hを省略して、メモリ初期化処理を高速化する。

【0038】

次に、チャネル設定値生成部52は、チャネル設定を生成するチャネル設定値生成処理を行う。チャネル設定値生成部52は、メモリコントローラ3のメモリチャネル311、321、及びメモリコントローラ4のメモリチャネル411、421に、それぞれ対応するチャネル設定値を生成する。チャネル設定値生成部52は、不揮発性メモリ6に記憶されたSPD63a、63bに基づいて、メモリチャネル311に対応するチャネル設定値を生成する。同様に、チャネル設定値生成部52は、不揮発性メモリ6に記憶されたSPD63c〜63hに基づいて、メモリチャネル321、411、421に対応するチャネル設定値を生成する。チャネル設定値生成部52は、生成されたチャネル設定値を、それぞれメモリチャネル311、321、411、421に対応する、チャネル設定値保持部31、32、41、42へ書き込む。同時に、チャネル設定値生成部52は、生成されたチャネル設定値を、それぞれメモリチャネル311、321、411、421に対応する、チャネル設定値62a、62b、62c、62dとして不揮発性メモリ6へ書き込む。

【0039】

チャネル設定値生成部52は、SPD比読み出し制御部53によるSPD比較処理において、型式番号が不一致であると判定されたメモリモジュール71〜78と接続されるメモリチャネル311、321、411、421に対してのみ、チャネル設定値生成処理を行う。SPD比較処理において型式番号が不一致であると判定されたメモリモジュール71〜78は、SPD読み出し制御部53により、SPD63a〜63hに記憶されたメモリモジュール71〜78の仕様情報を更新されるためである。一方、チャネル設定値生成部52は、メモリチャネル311、321、411、421と接続されるメモリモジュール71〜78が、それぞれSPD読み出し制御部53によるSPD比較処理において型式番号が一致すると判定された場合、チャネル設定値生成処理を省略する。この場合、不揮発性メモリ6に記憶されたチャネル設定値62a〜62dを用いてメモリ初期化処理が行われる。これによって、メモリ初期化処理が高速化される。

【0040】

次に、アドレス変換設定値生成部51は、アドレス変換設定値を生成するアドレス変換値生成処理を行う。まず、アドレス変換設定値生成部51は、アドレス変換値生成処理において、不揮発性メモリ6に記憶されたSPD63a〜63hに基づいてメモリモジュール71〜78の実装状況を検出してアドレス空間を設定する。次に、アドレス変換設定値生成部51は、設定されたアドレス空間を用いてアドレス変換設定値を生成する。アドレス変換設定値生成部51は、生成されたアドレス変換設定値を、チップセット2のアドレス変換設定値保持部21へ記憶させると共に、不揮発性メモリ6にアドレス変換設定値61として記憶させる。

【0041】

アドレス変換設定値生成部51は、コンピュータシステムの備える全てのメモリモジュ−ル71〜78にSPD読み出し制御部53によるSPD比較処理において型式番号が不一致であるメモリモジュール71〜78が存在する場合にのみ、アドレス変換設定値生成処理を行う。SPD比較処理において型式番号が不一致であると判定されたメモリモジュール71〜78は、SPD読み出し制御部53により、SPD63a〜63hに記憶されたメモリモジュール71〜78の仕様情報を更新されるためである。アドレス変換設定値生成部51は、コンピュータシステムの備える全てのメモリモジュ−ル71〜78にSPD読み出し制御部53によるSPD比較処理において型式番号が不一致であるメモリモジュール71〜78が存在しない場合、アドレス変換設定値生成処理を省略する。この場合、不揮発性メモリ6に記憶されたアドレス設定値61を用いてメモリ初期化処理が行われる。これによって、メモリ初期化処理が高速化される。以上が、メモリ初期化部5の説明である。

【0042】

なお、メモリ初期化部5は、ハードウェアとして実現されても良いし、ソフトウェアとして実現されても良い。メモリ初期化部5がソフトウェアとして実現される場合には、メモリ初期化部5の機能を実現するためのコンピュータプログラムが、不揮発性メモリ6に記憶される。プロセッサ1が、不揮発性メモリ6に記憶されたコンピュータプログラムを実行することにより、メモリ初期化部5の機能が実現される。

【0043】

以上が、本実施形態におけるコンピュータシステムの構成の説明である。

【0044】

[動作の説明]

次に、上述のような構成の本実施形態におけるコンピュータシステムの動作の説明を行う。図3A、図3Bは、本実施形態におけるコンピュータシステムの動作を示すフローチャートである。

【0045】

まず、コンピュータシステムの電源が「ON」される(ステップS10)。メモリ初期化部5のSPD読み出し制御部53は、SPD比較処理を開始する。SPD読み出し制御部53は、メモリモジュール部7のメモリモジュール71〜78のSPD701〜708へ順にアクセスを開始する(ステップS20)。

【0046】

はじめに、SPD読み出し制御部53は、メモリモジュール71のSPD701にアクセスすると、図2に示したデータ格納領域701bに格納されたメモリモジュールの型式番号を読み出す。SPD読み出し制御部53は、SPD701から読み出されたメモリモジュールの型式番号と、不揮発性メモリ6にSPD701に対応して記憶されたSPD63aのメモリモジュールの型式番号とが一致するか否かを比較する(ステップS30)。

【0047】

一致しない場合(ステップS30のNo)、SPD読み出し制御部53は、SPD701のデータ格納領域701a、及び701bに格納されたメモリモジュール71の仕様情報と製造者関連情報とを読み出して、不揮発性メモリ6にSPD701に対応するSPD63aとして記憶させる(ステップS40)。その後、ステップS70へ進む。

【0048】

一方、一致する場合(ステップS30のYes)、SPD読み出し制御部53は、SPD701から図2に示したデータ格納領域701bに格納されるメモリモジュールのシリアル番号を読み出して、不揮発性メモリ6にSPD701に対応して記憶されたSPD63aのメモリモジュールのシリアル番号と一致するか否かを比較する(ステップS50)。

【0049】

一致しない場合(ステップS50のNo)、SPD読み出し制御部53は、SPD701のデータ格納領域701bに格納されたメモリモジュール71の製造者関連情報を読み出して、不揮発性メモリ6にSPD701に対応するSPD63aとして記憶させる(ステップS60)。このように、型式番号が一致するもののシリアル番号が不一致であるメモリモジュールは、同一の仕様で異なるシリアル番号のメモリモジュールへの交換があったと考えられるためである。SPD読み出し制御部53は、SPD701からの読み出し範囲と、SPD63aにおける更新範囲を限定することで、メモリ初期化処理の高速化を計ることができる。その後、ステップS70へ進む。

【0050】

続いて、SPD701のメモリモジュールのシリアル番号と、SPD63aのメモリモジュールのシリアル番号とが一致する場合(ステップS50のYes)、ステップS70へ進む。この場合、メモリモジュール71の型式番号もシリアル番号も一致しているため、電源ONの前後にメモリモジュール71の交換は発生していないと判断できるからである。

【0051】

SPD読み出し制御部53は、メモリモジュール部7の備える全てのメモリモジュール71〜78に対するSPD比較処理が完了したか否かを判定する(ステップS70)。全てのメモリモジュール71〜78に対するSPD比較処理が完了していない場合(ステップS70のNo)、ステップS20へ戻り、次のメモリモジュール(この場合、例えば、メモリモジュール72)に対するSPD比較処理を行う。一方、全てのメモリモジュール71〜78に対するSPD比較処理が完了した場合(ステップS70のYes)、ステップS80へ進む。

【0052】

続いて、チャネル設定値生成部52は、チャネル設定値生成処理を開始する(ステップS80)。チャネル設定値生成部52は、メモリチャネル311、321、411、421に対して順に処理を行う。はじめに、チャネル設定値生成部52は、メモリチャネル311に対するチャネル処理生成処理を行う。チャネル設定値生成部52は、メモリチャネル311に接続されたメモリモジュール71、及び72に対して、メモリモジュールの型式番号の不一致が無かったかを判定する(ステップS90)。すなわち、メモリチャネル311に接続されたメモリモジュール71、及び72のSPD701、及び702に対して、ステップS40が実行されたか否かを判定する。メモリモジュール71、及び72のいずれにおいても、メモリモジュールの型式番号不一致が無い場合(ステップS90のYes)、すなわち、SPD701、及び702に対するステップS40の実行が無い場合、チャネル設定値生成部52は、メモリチャネル311に対するチャネル設定値生成処理を行わずに、ステップS110へ進む。

【0053】

一方、メモリモジュール71、あるいは72の少なくともいずれかにおいて、メモリモジュールの型式番号不一致が有った場合(ステップS90のNo)、すなわち、SPD701、あるいは702の少なくともいずれかに対してステップS40が実行された場合、チャネル設定値生成部52は、メモリチャネル311に対するチャネル設定値生成処理を行う(ステップS100)。チャネル設定値生成部52は、不揮発性メモリ6に記憶されたSPD63a、63bに基づいて、メモリチャネル311に対応するチャネル設定値を生成する。チャネル設定値生成部52は、生成されたチャネル設定値を、メモリコントローラ31のチャネル設定値保持部31へ記憶させるともに、不揮発性メモリ6にチャネル設定値62aとして記憶させる。その後、ステップS110へ進む。

【0054】

このように、チャネル設定値生成部52は、各メモリチャネル311、321、411、421に接続されるメモリモジュール71〜78に、SPD読み出し制御部53によるSPD比較処理において、型式番号が不一致であると判定されたメモリモジュールが存在す場合のみ、当該メモリチャネルに対してチャネル設定値生成処理を行う。この場合、当該メモリモジュールは、前回のメモリ初期化処理後に仕様の異なるメモリモジュールへ交換されたと考えられるからである。一般的に、メモリチャネル設定値生成処理は、メモリチャネル上において段階的にインピーダンス確認試験や、メモリモジュールを正常にリード/ライトするための遅延の窓(eye)を確保する試験が必要となり時間を要する。そこで、メモリモジュール71〜78の型式番号が一致した場合、あるいは、型式番号は一致しているがシリアル番号のみが不一致の場合には、メモリモジュール71〜78の仕様に変更は無いと考えて、チャネル設定値生成部52は、対応するメモリチャネル311、321、411、421に対するチャネル設定値生成処理を省略する。この場合、不揮発性メモリ6に記憶されたチャネル設定値62a〜62dを用いてメモリ初期化処理が行われて、メモリ初期化処理が高速化される。

【0055】

図3A、図3Bの説明に戻り、チャネル設定値生成部52は、全てのメモリチャネル311、321、411、421に対するチャネル設定値生成処理を完了したかを判定する(ステップS110)。全てのメモリチャネル311、321、411、421に対するチャネル設定値生成処理が完了していない場合(ステップS110のNo)、ステップS80へ戻り、次のメモリチャネル(この場合、例えば、メモリチャネル321)、に対するチャネル設定値生成処理を行う。一方、全てのメモリチャネル311、321、411、421に対するチャネル設定値生成処理が完了した場合(ステップS110のYes)、チャネル設定値生成部52は、メモリチャネル311、321、411、421を初期化する(ステップS120)。

【0056】

続いて、アドレス変換設定値生成部51は、メモリモジュール7の備える任意のメモリモジュール71〜78において、メモリモジュールの型式番号の不一致が無かったかを判定する(ステップS130)。すなわち、メモリモジュール7の備える任意のメモリモジュール71〜78に対して、ステップS40が実行されたか否かを判定する。

【0057】

メモリモジュール7の備える任意のメモリモジュール71〜78において、メモリモジュールの型式番号に不一致が有った場合(ステップS130のNo)、すなわち、メモリモジュール7の備える任意のメモリモジュール71〜78に対して、ステップS40の実行があった場合、アドレス変換設定値生成部51は、アドレス変換設定値生成処理を実行する(ステップS140)。アドレス変換設定値生成部51は、不揮発性メモリ6に記憶されたSPD63a〜63hに基づいて、メモリモジュール71〜78の実装状況を検出してアドレス空間を設定する。アドレス変換設定値生成部51は、設定されたアドレス空間を用いてアドレス変換設定値を生成する。アドレス変換設定値生成部51は、生成されたアドレス変換設定値を、チップセット2のアドレス変換設定値保持部21へ記憶させると共に、不揮発性メモリ6にアドレス変換設定値61として記憶させる。これにより、本フローチャートにおける動作は終了となる。

【0058】

一方、メモリモジュール7の備える任意のメモリモジュール71〜78において、メモリモジュールの型式番号不一致が無い場合(ステップS130のYes)、すなわち、メモリモジュール7の備える任意のメモリモジュール71〜78に対して、ステップS40の実行が無い場合、アドレス変換設定値生成部51は、アドレス変換設定値生成処理を行わない。この場合、本フローチャートにおける動作は終了となる。

【0059】

このように、アドレス変換設定値生成部51は、SPD比較処理においてメモリモジュール71〜78の少なくとも一つの型式番号に不一致があった場合のみ、アドレス変換設定値処理を行う。この場合、メモリモジュール71〜78が前回のメモリ初期化処理の後に仕様の異なるメモリモジュールへ交換されたと考えられるからである。一方で、アドレス変換設定値生成部51は、SPD比較処理において、メモリモジュール71〜78に型式番号の不一致が無い場合、あるいは、型式番号が一致するもののシリアル番号のみが不一致の場合には、メモリモジュール71〜78に仕様の変更は無いと判断できるため、アドレス変換設定値処理を省略する。この場合、不揮発性メモリ6に記憶されたアドレス変換設定値を用いてメモリ初期化処理が行われてメモリ初期化処理が高速化される。

【0060】

以上が、本実施形態におけるコンピュータシステムの動作の説明である。

【0061】

[実施例の説明]

次に、図1Aから図3Bまでを参照して、上述のような構成及び動作である本実施形態におけるコンピュータシステムの具体的な動作例を説明する。

【0062】

はじめに、初めてコンピュータシステムの電源を投入した場合の動作例を説明する。

【0063】

まず、コンピュータシステムの電源が「ON」される(ステップS10)。このとき、不揮発性メモリ6は、図1Aに示された外部からのリセット指示f200に基づいて、データの初期化(無効化)が行われる。メモリ初期化部5のSPD読み出し制御部53は、SPD比較処理を開始する。まず、SPD読み出し制御部53は、メモリモジュール71のSPD701にアクセスして(ステップS20)、データ格納領域701bに格納されたメモリモジュールの型式番号を読み出す。SPD読み出し制御部53は、SPD701から読み出されたメモリモジュールの型式番号と、不揮発性メモリ6にSPD701に対応して記憶されたSPD63aのメモリモジュールの型式番号とが一致するか否かを比較する(ステップS30)。

【0064】

今回は、初めての電源投入であり、SPD63aは無効データであるため、メモリモジュールの型式番号は一致しない(ステップS30のNo)、SPD読み出し制御部53は、SPD701のデータ格納領域701a、及び701bに格納されたメモリモジュール71の仕様情報と製造者関連情報とを読み出して、不揮発性メモリ6にSPD701に対応するSPD63aとして記憶させる(ステップS40)。その後、全メモリモジュールに対するSPD比較処理を完了したかを判定し(ステップS70)、完了していないため(ステップS70のNo)、SPD702〜708に対して順にアクセスして(ステップS20)、SPD比較処理を繰り返す。

【0065】

前述の通り、現時点でSPD63b〜63hは無効データであるため、SPD702〜708に格納されたメモリモジュールの型式番号とはいずれも一致しない(ステップS30のNo)。そのため、SPD読み出し制御部53は、SPD702〜708のデータ格納領域702a〜708a、及び702b〜708bに格納されたメモリモジュール72〜78の仕様情報と製造者関連情報とを読み出して、不揮発性メモリ6へSPD63b〜hとして記憶させる(ステップS40)処理を繰り返すことになる。

【0066】

SPD読み出し制御部53が全てのメモリモジュール71〜78に対するSPD比較処理が完了すると(ステップS70のYes)、チャネル設定値生成部52は、チャネル設定値生成処理を開始する(ステップS80)。まず、チャネル設定値生成部52は、メモリチャネル311に対するチャネル処理生成処理を行う。チャネル設定値生成部52は、メモリチャネル311に接続されたメモリモジュール71、及び72に対して、メモリモジュールの型式番号の不一致が無かったかを判定する(ステップS90)。

【0067】

今回は、SPD701、SPD702の双方ともメモリモジュールの型式番号が不一致である(ステップS90のNo)。そのため、チャネル設定値生成部52は、メモリチャネル311に対するチャネル設定値生成処理を行う(ステップS100)。チャネル設定値生成部52は、不揮発性メモリ6に記憶されたSPD63a、63bに基づいて、メモリチャネル311に対応するチャネル設定値を生成する。チャネル設定値生成部52は、生成されたチャネル設定値を、メモリコントローラ31のチャネル設定値保持部31へ記憶させるともに、不揮発性メモリ6にチャネル設定値62aとして記憶させる。

【0068】

チャネル設定値生成部52は、全てのメモリチャネル311、321、411、421に対するチャネル設定値生成処理を完了したかを判定し(ステップS110)、完了していないため(ステップS110のNo)、メモリチャネル321、411、421に対して順にチャネル設定値生成処理を行う(ステップS80)。今回は、SPD701〜708に格納されたメモリモジュールの型式番号が不一致であったため(ステップS90のNo)、チャネル設定値生成部52は、メモリチャネル321、411、421に対してもチャネル設定値生成処理を行うことになる(ステップS100)。

【0069】

すなわち、チャネル設定値生成部52は、不揮発性メモリ6に記憶されたSPD63c、63dに基づいて、メモリチャネル321に対応するチャネル設定値を生成し、同様に、SPD63e、63fに基づいてメモリチャネル411、SPD63g、63hに基づいてメモリチャネル421を生成する。チャネル設定値生成部52は、生成されたチャネル設定値を、それぞれメモリコントローラ3、4のチャネル設定値保持部32、41、42へ記憶させるともに、不揮発性メモリ6にチャネル設定値62b、62c、62dとして記憶させる。

【0070】

全てのメモリチャネル311、321、411、421に対するチャネル設定値生成処理すると(ステップS110のYes)、チャネル設定値生成部52は、メモリチャネル311、321、411、421を初期化する(ステップS120)。

【0071】

続いて、アドレス変換設定値生成部51は、メモリモジュール7の備える任意のメモリモジュール71〜78において、メモリモジュールの型式番号の不一致が無かったかを判定する(ステップS130)。今回は、全てのメモリモジュール71〜78の型式番号が不一致であったため(ステップS130のNo)、アドレス変換設定値生成部51は、アドレス変換設定値生成処理を実行する(ステップS140)。アドレス変換設定値生成部51は、不揮発性メモリ6に記憶されたSPD63a〜63hに基づいて、メモリモジュール71〜78の実装状況を検出してアドレス空間を設定する。アドレス変換設定値生成部51は、設定されたアドレス空間を用いてアドレス変換設定値を生成する。アドレス変換設定値生成部51は、生成されたアドレス変換設定値を、チップセット2のアドレス変換設定値保持部21へ記憶させると共に、不揮発性メモリ6にアドレス変換設定値61として記憶させて、本フローチャートにおける動作を終了する。

【0072】

以上が、初めてコンピュータシステムの電源を投入した場合の動作例を説明である。

【0073】

続いて、2回目にコンピュータシステムの電源を投入した場合であって、前回以降、メモリモジュール71〜78の交換がされていない場合の動作例の説明を行う。

【0074】

まず、コンピュータシステムの電源が「ON」される(ステップS10)。メモリ初期化部5のSPD読み出し制御部53は、SPD比較処理を開始する。まず、SPD読み出し制御部53は、メモリモジュール71のSPD701にアクセスして(ステップS20)、データ格納領域701bに格納されたメモリモジュールの型式番号を読み出す。SPD読み出し制御部53は、SPD701から読み出されたメモリモジュールの型式番号と、不揮発性メモリ6にSPD701に対応して記憶されたSPD63aのメモリモジュールの型式番号とが一致するか否かを比較する(ステップS30)。

【0075】

SPD63aは、初回の電源投入時にSPD701の内容を複製して保存された内容であるため、メモリモジュールの型式番号は一致する(ステップS30のYes)。続いて、SPD読み出し制御部53は、SPD701からメモリモジュールのシリアル番号を読み出して、不揮発性メモリ6にSPDに対応して記憶されたSPD63aのメモリモジュールのシリアル番号と一致するか否かを比較する(ステップS50)。SPD63aは、初回の電源投入時にSPD701の内容を複製して保存された内容であるため、メモリモジュールのシリアル番号も一致する(ステップS50のYes)。このように、メモリモジュール71の型式番号もシリアル番号も一致しているため、電源ONの前後にメモリモジュール71の交換は発生していないと判断できる。そのため、SPD読み出し制御部53は、SPD63aの更新処理を行わずにSPD701に対するSPD比較処理を完了する。

【0076】

SPD読み出し制御部53は、メモリモジュール部7の備える全てのメモリモジュール71〜78に対するSPD比較処理が完了したか否かを判定し、(ステップS70)、完了していないため(ステップS70のNo)、SPD702〜708に対して順にアクセスして(ステップS20)、SPD比較処理を繰り返す。

【0077】

前述の通り、現時点でSPD63b〜63hは、初回の電源投入時にSPD702〜708の内容を複製して保存された内容であるため、メモリモジュールの型式番号とはいずれも一致し(ステップS30のYes)、また、メモリモジュールのシリアル番号もいずれも一致する(ステップS50のYes)。そのため、SPD読み出し制御部53は、SPD702〜708に格納された仕様情報(702a〜708a)と製造者関連情報(702b〜708b)のいずれも、不揮発性メモリ6へ記憶させることは無く、メモリ初期化処理を高速化できる。

【0078】

SPD読み出し制御部53が全てのメモリモジュール71〜78に対するSPD比較処理が完了すると(ステップS70のYes)、チャネル設定値生成部52は、チャネル設定値生成処理を開始する(ステップS80)。まず、チャネル設定値生成部52は、メモリチャネル311に対するチャネル設定値生成処理を行う。チャネル設定値生成部52は、メモリチャネル311に接続されたメモリモジュール71、及び72に対して、メモリモジュールの型式番号の不一致が無かったかを判定する(ステップS90)。

【0079】

今回は、SPD701、SPD702の双方ともメモリモジュールの型式番号に不一致が無い(ステップS90のYes)。そのため、チャネル設定値生成部52は、メモリチャネル311に対するチャネル設定値生成処理を行わない。チャネル設定値生成部52は、全てのメモリチャネル311、321、411、421に対するチャネル設定値生成処理を完了したかを判定し(ステップS110)、完了していないため(ステップS110のNo)、メモリチャネル321、411、421に対して順にチャネル設定値生成処理を行う(ステップS80)。今回はSPD701〜708の全てにおいてメモリモジュールの型式番号に不一致が無かったため(ステップS90のYes)、チャネル設定値生成部52は、メモリチャネル321、411、421に対してもチャネル設定値生成処理を行わない。SPD比較処理においてメモリモジュール71〜78の型式番号とシリアル番号とに不一致が無いため、メモリモジュール71〜78に仕様の変更が発生していないと判断できるためである。この場合、不揮発性メモリ6に記憶されたチャネル設定値62a〜62dを用いてメモリ初期化処理が行われて、メモリ初期化処理が高速化される。

【0080】

全てのメモリチャネル311、321、411、421に対するチャネル設定値生成処理すると(ステップS110のYes)、チャネル設定値生成部52は、メモリチャネル311、321、411、421を初期化する(ステップS120)。

【0081】

続いて、アドレス変換設定値生成部51は、メモリモジュール7の備える任意のメモリモジュール71〜78において、メモリモジュールの型式番号の不一致が無かったかを判定する(ステップS130)。今回は、全てのメモリモジュール71〜78の型式番号が不一致でなかったため(ステップS130のYes)、アドレス変換設定値生成部51は、アドレス変換設定値生成処理を実行せず、本フローチャートにおける動作を終了する。SPD比較処理においてメモリモジュール71〜78の型式番号とシリアル番号とに不一致が無い場合、メモリモジュール71〜78に仕様の変更が発生していないと判断することができるためである。この場合、不揮発性メモリ6に記憶されたアドレス変換設定値61を用いてメモリ初期化処理が行われて、メモリ初期化処理が高速化される。

【0082】

以上が、2回目にコンピュータシステムの電源を投入した場合であって、前回以降、メモリモジュール71〜78の交換がされていない場合の動作例の説明である。

【0083】

続いて、2回目にコンピュータシステムの電源を投入した場合であって、前回以降に、メモリモジュール71を同一の型式番号で異なるシリアル番号のメモリモジュールへ交換を行った場合の動作例の説明を行う。

【0084】

まず、コンピュータシステムの電源が「ON」される(ステップS10)。メモリ初期化部5のSPD読み出し制御部53は、SPD比較処理を開始する。まず、SPD読み出し制御部53は、メモリモジュール71のSPD701にアクセスして(ステップS20)、データ格納領域701bに格納されたメモリモジュールの型式番号を読み出す。SPD読み出し制御部53は、SPD701から読み出されたメモリモジュールの型式番号と、不揮発性メモリ6にSPD701に対応して記憶されたSPD63aのメモリモジュールの型式番号とが一致するか否かを比較する(ステップS30)。

【0085】

メモリモジュール71は交換されているもののSPD701に格納されたメモリモジュールの型式番号は交換前後で同一であるため、メモリモジュールの型式番号は一致する(ステップS30のYes)。続いて、SPD読み出し制御部53は、SPD701からメモリモジュールのシリアル番号を読み出して、不揮発性メモリ6にSPDに対応して記憶されたSPD63aのメモリモジュールのシリアル番号と一致するか否かを比較する(ステップS50)。メモリモジュール71は交換されており、SPD701に格納されたメモリモジュールのシリアル番号は交換前後で異なるため、メモリモジュールのシリアル番号は一致しない(ステップS50のNo)。SPD読み出し制御部53は、SPD701のデータ格納領域701bに格納された製造者関連情報を読み出して、不揮発性メモリ6にSPD701に対応するSPD63aとして記憶させる(ステップS60)。このように、SPD読み出し制御部53は、SPD701からの情報の読み出し範囲を、データ格納領域701bの製造者関連情報のみ限定することで、メモリ初期化処理の高速化を計ることができる。その後、ステップS70へ進む。

【0086】

SPD読み出し制御部53は、メモリモジュール部7の備える全てのメモリモジュール71〜78に対するSPD比較処理が完了したか否かを判定し、(ステップS70)、完了していないため(ステップS70のNo)、SPD702〜708に対して順にアクセスして(ステップS20)、SPD比較処理を繰り返す。

【0087】

現時点でSPD63b〜63hは、初回の電源投入時にSPD702〜708の内容を複製して保存された内容であるため、メモリモジュールの型式番号とはいずれも一致し(ステップS30のYes)、また、メモリモジュールのシリアル番号もいずれも一致する(ステップS50のYes)。そのため、SPD読み出し制御部53は、SPD702〜708に格納された仕様情報(702a〜708a)と製造者関連情報(702b〜708b)のいずれも、不揮発性メモリ6へ記憶させる処理を行うことが無く、SPD比較処理を高速化できる。

【0088】

SPD読み出し制御部53が全てのメモリモジュール71〜78に対するSPD比較処理が完了すると(ステップS70のYes)、チャネル設定値生成部52は、チャネル設定値生成処理を開始する(ステップS80)。まず、チャネル設定値生成部52は、メモリチャネル311に対するチャネル処理生成処理を行う。チャネル設定値生成部52は、メモリチャネル311に接続されたメモリモジュール71、及び72に対して、メモリモジュールの型式番号の不一致が無かったかを判定する(ステップS90)。

【0089】

今回は、SPD701においてメモリモジュールのシリアル番号の変更はあったものの、SPD701、SPD702の双方ともメモリモジュールの型式番号に不一致が無い(ステップS90のYes)。そのため、チャネル設定値生成部52は、メモリチャネル311に対するチャネル設定値生成処理を行わない。チャネル設定値生成部52は、全てのメモリチャネル311、321、411、421に対するチャネル設定値生成処理を完了したかを判定し(ステップS110)、完了していないため(ステップS110のNo)、メモリチャネル321、411、421に対して順にチャネル設定値生成処理を行う(ステップS80)。SPD703〜708においてメモリモジュールの型式番号には不一致が無かったため(ステップS90のYes)、メモリモジュール71〜78の交換に伴う仕様の変更が無いと考えられるため、チャネル設定値生成部52は、メモリチャネル321、411、421に対してもチャネル設定値生成処理を行わない。この場合、不揮発性メモリ6に記憶されたチャネル設定値62a〜62dを用いてメモリ初期化処理が行われて、メモリ初期化処理が高速化される。全てのメモリチャネル311、321、411、421に対するチャネル設定値生成処理すると(ステップS110のYes)、チャネル設定値生成部52は、メモリチャネル311、321、411、421を初期化する(ステップS120)。

【0090】

続いて、アドレス変換設定値生成部51は、メモリモジュール7の備える任意のメモリモジュール71〜78において、メモリモジュールの型式番号の不一致が無かったかを判定する(ステップS130)。今回は、メモリモジュール71のシリアル番号に不一致があったものの、メモリモジュール71〜78の型式番号に不一致は無かったため(ステップS130のYes)、アドレス変換設定値生成部51は、アドレス変換設定値生成処理を実行せず、本フローチャートにおける動作を終了する。このように、SPD701〜708とSPD63a〜hとの比較においてメモリモジュールの型式番号に不一致が無くシリアル番号にのみ不一致が有る場合、メモリモジュール71〜78の交換に伴う仕様の変更は発生していないと判断することができる。そのため、アドレス変換設定値生成部51は、アドレス変換設定値生成処理を実行しない。この場合、不揮発性メモリ6に記憶されたアドレス変換設定値51を用いてメモリ初期化処理が行われて、メモリ初期化処理が高速化される。

【0091】

以上が、2回目にコンピュータシステムの電源を投入した場合であって、前回以降に、メモリモジュール71を同一の型式番号で異なるシリアル番号のメモリモジュールへ交換を行った場合の動作例の説明である。

【0092】

続いて、2回目にコンピュータシステムの電源を投入した場合であって、前回以降に、メモリモジュール71を型式番号及びシリアル番号の異なるメモリモジュールへ交換を行った場合の動作例の説明を行う。

【0093】

まず、コンピュータシステムの電源が「ON」される(ステップS10)。メモリ初期化部5のSPD読み出し制御部53は、SPD比較処理を開始する。まず、SPD読み出し制御部53は、メモリモジュール71のSPD701にアクセスして(ステップS20)、データ格納領域701bに格納されたメモリモジュールの型式番号を読み出す。SPD読み出し制御部53は、SPD701から読み出されたメモリモジュールの型式番号と、不揮発性メモリ6にSPD701に対応して記憶されたSPD63aのメモリモジュールの型式番号とが一致するか否かを比較する(ステップS30)。

【0094】

メモリモジュール71は交換にされておりSPD701に格納されたメモリモジュールの型式番号は交換前後で異なっている、メモリモジュールの型式番号は一致しない(ステップS30のNo)。そのため、SPD読み出し制御部53は、SPD701のデータ格納領域701a、及び701bに格納されたメモリモジュール71の仕様情報と製造者関連情報とを読み出して、不揮発性メモリ6にSPD701に対応するSPD63aとして記憶させる(ステップS40)。その後、全メモリモジュールに対するSPD比較処理を完了したかを判定し(ステップS70)、完了していないため(ステップS70のNo)、SPD702〜708に対して順にアクセスして(ステップS20)、SPD比較処理を繰り返す。

【0095】

現時点でSPD63b〜63hは、初回の電源投入時にSPD702〜708の内容を複製して保存された内容であるため、メモリモジュールの型式番号とはいずれも一致し(ステップS30のYes)、また、メモリモジュールのシリアル番号もいずれも一致する(ステップS50のYes)。そのため、SPD読み出し制御部53は、SPD702〜708に格納された仕様情報(702a〜708a)と製造者関連情報(702b〜708b)のいずれも、不揮発性メモリ6へ記憶させる処理を行わない。このように、交換によりメモリモジュールの型式番号の不一致が発生したメモリモジュール71に対してのみ、仕様情報(701a〜708a)と製造者関連情報(701a〜708a)の更新を行うため、交換の行われていないメモリモジュール72〜78に対するSPD比較処理を高速化できる。

【0096】

SPD読み出し制御部53が全てのメモリモジュール71〜78に対するSPD比較処理が完了すると(ステップS70のYes)、チャネル設定値生成部52は、チャネル設定値生成処理を開始する(ステップS80)。まず、チャネル設定値生成部52は、メモリチャネル311に対するチャネル処理生成処理を行う。チャネル設定値生成部52は、メモリチャネル311に接続されたメモリモジュール71、及び72に対して、メモリモジュールの型式番号の不一致が無かったかを判定する(ステップS90)。

【0097】

今回は、交換によりSPD701のメモリモジュールの型式番号に不一致があった(ステップS90のNo)。そのため、チャネル設定値生成部52は、メモリチャネル311に対するチャネル設定値生成処理を行う(ステップS100)。チャネル設定値生成部52は、不揮発性メモリ6に記憶されたSPD63a、63bに基づいて、メモリチャネル311に対応するチャネル設定値を生成する。ここで、SPD63aは、ステップS40において、交換後のメモリモジュール71のSPD701と同一の内容となっている。チャネル設定値生成部52は、生成されたチャネル設定値を、メモリコントローラ31のチャネル設定値保持部31へ記憶させるともに、不揮発性メモリ6にチャネル設定値62aとして記憶させる。

【0098】

チャネル設定値生成部52は、全てのメモリチャネル311、321、411、421に対するチャネル設定値生成処理を完了したかを判定し(ステップS110)、完了していないため(ステップS110のNo)、メモリチャネル321、411、421に対して順にチャネル設定値生成処理を行う(ステップS80)。SPD703〜708においてメモリモジュールの型式番号に不一致が無いため(ステップS90のYes)、チャネル設定値生成部52は、メモリチャネル321、411、421に対してチャネル設定値生成処理を行わない。このように、チャネル設定値生成部52は、メモリモジュールの型式番号に不一致を検出されたメモリモジュール71と接続されるメモリチャネル311に対してのみチャネル設定値生成処理を行う。これにより、メモリ初期化処理を高速化できる。

【0099】

全てのメモリチャネル311、321、411、421に対するチャネル設定値生成処理すると(ステップS110のYes)、チャネル設定値生成部52は、メモリチャネル311、321、411、421を初期化する(ステップS120)。

【0100】

続いて、アドレス変換設定値生成部51は、メモリモジュール7の備える任意のメモリモジュール71〜78において、メモリモジュールの型式番号の不一致が無かったかを判定する(ステップS130)。今回は、メモリモジュール71の型式番号に不一致が有ったため(ステップS130のNo)、アドレス変換設定値生成部51は、アドレス変換設定値生成処理を実行する(ステップS140)。

【0101】

アドレス変換設定値生成部51は、不揮発性メモリ6に記憶されたSPD63a〜63hに基づいて、メモリモジュール71〜78の実装状況を検出してアドレス空間を設定する。アドレス変換設定値生成部51は、設定されたアドレス空間を用いてアドレス変換設定値を生成する。アドレス変換設定値生成部51は、生成されたアドレス変換設定値を、チップセット2のアドレス変換設定値保持部21へ記憶させると共に、不揮発性メモリ6にアドレス変換設定値61として記憶させて、本フローチャートにおける動作を終了する。

【0102】

以上が、2回目にコンピュータシステムの電源を投入した場合であって、前回以降に、メモリモジュール71を同一の型式番号の異なるシリアル番号のメモリモジュールへ交換を行った場合の動作例の説明である。

【0103】

ここまで説明を行ってきたように、本実施形態におけるコンピュータシステムは、コンピュータシステムの備える全てのメモリモジュール71〜78のSPD701〜708に対応するSPD63a〜63hと、メモリコントローラ3、4におけるメモリチャネル311、321、411、421のチャネル設定値と、各メモリモジュール71〜78のアドレス空間に対応させて生成されたアドレス変換設定値とを記憶する不揮発性メモリ6を備える。また、コンピュータシステムは、メモリ初期化処理において、各メモリモジュール71〜78のSPD710〜708を読み出して不揮発性メモリ6に記憶されたSPD63a〜63hと比較するメモリ比較処理を行うSPD読み出し制御部53と、メモリチャネル311、321、411、421毎のチャネル設定値の生成処理を行うチャネル設定値生成部52と、及びアドレス変換設定値の生成処理を行うアドレス変換設定値生成部51とを備える。

【0104】

SPD701〜708は、仕様情報(データ格納領域701a〜708a)と製造者関連情報(データ格納領域701b〜708b)とを含む。さらに、製造者関連情報は、メモリモジュールの型式番号、及びシリアル番号を含む。SPD読み出し制御部53は、SPD比較処理において、メモリモジュールの型式番号とシリアル番号とを比較する。SPD読み出し制御部53は、型式番号とシリアル番号がいずれも一致したメモリモジュール71〜78について、不揮発性メモリ6に記憶されたSPD63a〜63hの更新は行わない。SPD比較処理においてメモリモジュールの型式番号とシリアル番号とが一致するということは、搭載されているメモリモジュール71〜78が前回のメモリ初期化処理時のメモリモジュール71〜78と同一あると確認できたことを意味する。そのため、このようなメモリモジュールに対しては、不揮発性メモリ6のSPD63a〜63hの更新処理を省略することができる。

【0105】

一方、SPD読み出し制御部53は、型式番号が不一致であるメモリモジュール71〜78のSPD701〜708に格納された仕様情報と製造者関連情報とを読み出して不揮発性メモリ6に記憶されたSPD63a〜63hを更新する。型式番号が不一致であるメモリモジュール71〜78は、異なる仕様を有したメモリモジュール71〜78へ交換が行われたと考えることができるからである。また、SPD読み出し制御部53は、型式番号が一致するもののシリアル番号が不一致であるメモリモジュール71〜78のSPD701〜708から製造者関連情報のみを読み出して不揮発性メモリに記憶されたSPDを更新する。型式番号が一致するもののシリアル番号が不一致であるメモリモジュール71〜78は、同じ仕様を有する異なるシリアル番号のメモリモジュール71〜78に交換されたと考えられるからである。

【0106】

チャネル設定値生成部52は、型式番号が不一致であるメモリモジュール71〜78と接続されるメモリチャネル311、321、411、421に対してのみチャネル設定値の生成処理を行う。さらに、アドレス変換設定値生成部51は、コンピュータシステムの備える全てのメモリモジュール71〜78において、型式番号が不一致であるメモリモジュール71〜78が存在した場合にのみアドレス変換値生成処理を行う。チャネル設定値生成部52とアドレス変換設定値生成部51は、いずれも不揮発性メモリ6に記憶されたSPD53a〜53hの仕様情報を基にして、チャネル設定値とアドレス変換設定値とを生成する。SPD読み出し制御部53は、型式番号が不一致である場合のみ、不揮発性メモリ6に記憶されたSPD63a〜63hの仕様情報を更新する。型式番号が一致する場合、あるいは、型式番号が一致するもののシリアル番号が不一致である場合、不揮発性メモリ記憶6にされたSPD63a〜63hの仕様情報に変更は無い。そのため、チャネル設定値生成部52とアドレス変換設定値生成部51とが、生成するチャネル設定値、及びアドレス変換設定値も同一の値となる。そこで、型式番号が一致する場合、あるいは、型式番号が一致するもののシリアル番号が不一致である場合には、チャネル設定値及びアドレス変換設定値の生成処理を省略して、メモリ初期化処理の更なる高速化を計ることができる。

【0107】

以上、実施形態を参照して本発明のメモリ初期化装置を説明したが、本発明は上記実施形態に限定されるものではない。本発明の構成や詳細には、本発明の範囲内で当業者が理解し得る様々な変更を行うことができる。

【符号の説明】

【0108】

1 プロセッサ

2 チップセット

3、4 メモリコントローラ

5 メモリ初期化部

6 不揮発性メモリ

7 メモリモジュール部

21 アドレス変換設定値保持部

31、32、41、42 チャネル設定値保持部

51 アドレス変換設定値生成部

52 チャネル設定値生成部

53 SPD読み出し制御部

61 アドレス変換設定値

62a〜62d チャネル設定値

63a〜63h SPD

71〜78 メモリモジュール

311、321、411、421 メモリチャネル

701〜708 SPD

701a〜708a、701b〜708b、701c〜708c データ格納領域

【特許請求の範囲】

【請求項1】

第1のSPD情報を格納する複数のメモリモジュールと、

前記第1のSPD情報は、前記複数のメモリモジュールの各々の仕様情報を含み、

前記各メモリモジュールへアクセスするためにシステム内で用いられるアクセス設定値と、前記各メモリモジュールに対応させて前記第1のSPD情報の複製である第2のSPD情報とを記憶する不揮発性メモリと、

前記複数のメモリモジュールの初期化処理において前記第1のSPD情報と前記第2のSPD情報とが一致するか否か比較判定処理を行って、前記比較判定処理において前記複数のメモリモジュールのうちから前記第1のSPD情報と前記第2のSPD情報とが一致しない不一致メモリモジュールを特定して、前記不一致メモリモジュールから前記第1のSPD情報を読み出して前記不揮発性メモリへ前記第2のSPD情報として書き込む読み出し制御部と、

前記複数のメモリモジュールに不一致メモリモジュールが存在する場合に、前記アクセス設定値のうちで前記不一致メモリモジュールの第2のSPD情報が生成に用いられる選択アクセス設定値を、前記第2のSPD情報に基づいて生成して、前記選択アクセス設定値を前記不揮発性メモリへ書き込む設定値生成部と

を備えるコンピュータシステム。

【請求項2】

請求項1に記載のコンピュータシステムであって、

前記アクセス設定値は、前記複数のメモリモジュールへのアクセスを制御するメモリコントローラと前記複数のメモリモジュールとを接続するメモリチャネルにおけるチャネル設定値を含み、

前記複数のメモリモジュールに不一致メモリモジュールが存在する場合に、前記不一致メモリモジュールと接続される前記メモリチャネルにおける前記チャネル設定値のみを前記第2のSPD情報に基づいて生成して、生成された前記チャネル設定値を前記メモリチャネルに対応させて前記不揮発性メモリへ書き込むチャネル設定値生成部

をさらに備えるコンピュータシステム。

【請求項3】

請求項1または請求項2に記載のコンピュータシステムであって、

前記アクセス設定値は、プロセッサからのトランザクションを前記メモリコントローラへ振り分けるチップセットにおけるアドレス変換設定値含み、

前記複数のメモリモジュールに不一致メモリモジュールが存在する場合にのみ前記アドレス変換設定値を前記第2のSPD情報に基づいて生成して、生成された前記アドレス変換設定値を前記不揮発性メモリへ書き込むアドレス変換設定値生成部

をさらに備えるコンピュータシステム。

【請求項4】

請求項1から請求項3のいずれかに記載のコンピュータシステムであって、

前記第1のSPD情報は、前記複数のメモリモジュールの型式番号とシリアル番号とを更に含み、

前記読み出し制御部は、前記SPD比較処理において、前記各メモリモジュールのうち前記第1のSPD情報に含まれる前記型式番号と前記第2のSPD情報に含まれる前記型式番号とが一致しないメモリモジュールを前記不一致メモリモジュールと判定する

コンピュータシステム。

【請求項5】

請求項4に記載のコンピュータシステムであって、

前記SPD読み出し制御部は、前記SPD比較処理において、前記複数のメモリモジュールのうち前記第1のSPD情報に含まれる前記型式番号と前記第2のSPD情報に含まれる前記型式番号は一致するものの前記第1のSPD情報に含まれる前記シリアル番号と前記第2のSPD情報に含まれる前記シリアル番号は不一致である第2の不一致メモリモジュールを特定して、前記第2の不一致メモリモジュールの前記第1のSPD情報に含まれる前記型式番号と前記シリアル番号とを読み出して前記第2の不一致メモリモジュールに対応する前記第2のSPD情報として前記不揮発性メモリへ書き込む

コンピュータシステム。

【請求項6】

第1のSPD情報を格納する複数のメモリモジュールと、

前記第1のSPD情報は、前記複数のメモリモジュールの各々の仕様情報を含み、

不揮発性メモリと

を備えるコンピュータシステムにおいて、

前記各メモリモジュールへアクセスするためにシステム内で用いられるアクセス設定値と、前記各メモリモジュールに対応させて前記第1のSPD情報の複製である第2のSPD情報とを記憶するステップと、

前記複数のメモリモジュールの初期化処理において前記第1のSPD情報と前記第2のSPD情報とが一致するか否か比較判定処理を行うステップと、

前記比較判定処理において前記複数のメモリモジュールのうちから前記第1のSPD情報と前記第2のSPD情報とが一致しない不一致メモリモジュールを特定するステップと、

前記不一致メモリモジュールから前記第1のSPD情報を読み出して前記不揮発性メモリへ前記第2のSPD情報として書き込むステップと、

前記複数のメモリモジュールに不一致メモリモジュールが存在する場合に、前記アクセス設定値のうちで前記不一致メモリモジュールの第2のSPD情報が生成に用いられる選択アクセス設定値を前記第2のSPD情報に基づいて生成するステップと、

前記選択アクセス設定値を前記不揮発性メモリへ書き込むステップと

を備えるコンピュータシステムのメモリ初期化方法。

【請求項7】

請求項6に記載のコンピュータシステムのメモリ初期化方法をコンピュータに実行させるメモリ初期化プログラム。

【請求項1】

第1のSPD情報を格納する複数のメモリモジュールと、

前記第1のSPD情報は、前記複数のメモリモジュールの各々の仕様情報を含み、

前記各メモリモジュールへアクセスするためにシステム内で用いられるアクセス設定値と、前記各メモリモジュールに対応させて前記第1のSPD情報の複製である第2のSPD情報とを記憶する不揮発性メモリと、

前記複数のメモリモジュールの初期化処理において前記第1のSPD情報と前記第2のSPD情報とが一致するか否か比較判定処理を行って、前記比較判定処理において前記複数のメモリモジュールのうちから前記第1のSPD情報と前記第2のSPD情報とが一致しない不一致メモリモジュールを特定して、前記不一致メモリモジュールから前記第1のSPD情報を読み出して前記不揮発性メモリへ前記第2のSPD情報として書き込む読み出し制御部と、

前記複数のメモリモジュールに不一致メモリモジュールが存在する場合に、前記アクセス設定値のうちで前記不一致メモリモジュールの第2のSPD情報が生成に用いられる選択アクセス設定値を、前記第2のSPD情報に基づいて生成して、前記選択アクセス設定値を前記不揮発性メモリへ書き込む設定値生成部と

を備えるコンピュータシステム。

【請求項2】

請求項1に記載のコンピュータシステムであって、

前記アクセス設定値は、前記複数のメモリモジュールへのアクセスを制御するメモリコントローラと前記複数のメモリモジュールとを接続するメモリチャネルにおけるチャネル設定値を含み、

前記複数のメモリモジュールに不一致メモリモジュールが存在する場合に、前記不一致メモリモジュールと接続される前記メモリチャネルにおける前記チャネル設定値のみを前記第2のSPD情報に基づいて生成して、生成された前記チャネル設定値を前記メモリチャネルに対応させて前記不揮発性メモリへ書き込むチャネル設定値生成部

をさらに備えるコンピュータシステム。

【請求項3】

請求項1または請求項2に記載のコンピュータシステムであって、

前記アクセス設定値は、プロセッサからのトランザクションを前記メモリコントローラへ振り分けるチップセットにおけるアドレス変換設定値含み、

前記複数のメモリモジュールに不一致メモリモジュールが存在する場合にのみ前記アドレス変換設定値を前記第2のSPD情報に基づいて生成して、生成された前記アドレス変換設定値を前記不揮発性メモリへ書き込むアドレス変換設定値生成部

をさらに備えるコンピュータシステム。

【請求項4】

請求項1から請求項3のいずれかに記載のコンピュータシステムであって、

前記第1のSPD情報は、前記複数のメモリモジュールの型式番号とシリアル番号とを更に含み、

前記読み出し制御部は、前記SPD比較処理において、前記各メモリモジュールのうち前記第1のSPD情報に含まれる前記型式番号と前記第2のSPD情報に含まれる前記型式番号とが一致しないメモリモジュールを前記不一致メモリモジュールと判定する

コンピュータシステム。

【請求項5】

請求項4に記載のコンピュータシステムであって、

前記SPD読み出し制御部は、前記SPD比較処理において、前記複数のメモリモジュールのうち前記第1のSPD情報に含まれる前記型式番号と前記第2のSPD情報に含まれる前記型式番号は一致するものの前記第1のSPD情報に含まれる前記シリアル番号と前記第2のSPD情報に含まれる前記シリアル番号は不一致である第2の不一致メモリモジュールを特定して、前記第2の不一致メモリモジュールの前記第1のSPD情報に含まれる前記型式番号と前記シリアル番号とを読み出して前記第2の不一致メモリモジュールに対応する前記第2のSPD情報として前記不揮発性メモリへ書き込む

コンピュータシステム。

【請求項6】

第1のSPD情報を格納する複数のメモリモジュールと、

前記第1のSPD情報は、前記複数のメモリモジュールの各々の仕様情報を含み、

不揮発性メモリと

を備えるコンピュータシステムにおいて、

前記各メモリモジュールへアクセスするためにシステム内で用いられるアクセス設定値と、前記各メモリモジュールに対応させて前記第1のSPD情報の複製である第2のSPD情報とを記憶するステップと、

前記複数のメモリモジュールの初期化処理において前記第1のSPD情報と前記第2のSPD情報とが一致するか否か比較判定処理を行うステップと、

前記比較判定処理において前記複数のメモリモジュールのうちから前記第1のSPD情報と前記第2のSPD情報とが一致しない不一致メモリモジュールを特定するステップと、

前記不一致メモリモジュールから前記第1のSPD情報を読み出して前記不揮発性メモリへ前記第2のSPD情報として書き込むステップと、

前記複数のメモリモジュールに不一致メモリモジュールが存在する場合に、前記アクセス設定値のうちで前記不一致メモリモジュールの第2のSPD情報が生成に用いられる選択アクセス設定値を前記第2のSPD情報に基づいて生成するステップと、

前記選択アクセス設定値を前記不揮発性メモリへ書き込むステップと

を備えるコンピュータシステムのメモリ初期化方法。

【請求項7】

請求項6に記載のコンピュータシステムのメモリ初期化方法をコンピュータに実行させるメモリ初期化プログラム。

【図1A】

【図1B】

【図2】

【図3A】

【図3B】

【図1B】

【図2】

【図3A】

【図3B】

【公開番号】特開2011−175577(P2011−175577A)

【公開日】平成23年9月8日(2011.9.8)

【国際特許分類】

【出願番号】特願2010−40657(P2010−40657)

【出願日】平成22年2月25日(2010.2.25)

【出願人】(000168285)エヌイーシーコンピュータテクノ株式会社 (572)

【Fターム(参考)】

【公開日】平成23年9月8日(2011.9.8)

【国際特許分類】

【出願日】平成22年2月25日(2010.2.25)

【出願人】(000168285)エヌイーシーコンピュータテクノ株式会社 (572)

【Fターム(参考)】

[ Back to top ]