コンピュータシステム及び半導体記憶装置

【課題】高いセキュリティ性を有する半導体記憶装置及びそれを備えたコンピュータシステムを得る。

【解決手段】ホスト機器2は、半導体記憶装置3に送信するコマンドD1を所定の演算によって変換することにより、第1の変換値を生成する変換部12と、第1の変換値及びコマンドを半導体記憶装置3に送信する送信部14と、を有し、半導体記憶装置3は、ホスト機器2から半導体記憶装置3へのアクセスを制御する制御部23と、第1の変換値及びコマンドをホスト機器2から受信する受信部21と、を有し、制御部23は、受信部21が受信したコマンドを所定の演算によって変換することにより、第2の変換値を生成する変換部33と、受信部21が受信した第1の変換値と、変換部33が生成した第2の変換値とが一致しない場合に、不正なアクセスと判定する判定部34と、を含む。

【解決手段】ホスト機器2は、半導体記憶装置3に送信するコマンドD1を所定の演算によって変換することにより、第1の変換値を生成する変換部12と、第1の変換値及びコマンドを半導体記憶装置3に送信する送信部14と、を有し、半導体記憶装置3は、ホスト機器2から半導体記憶装置3へのアクセスを制御する制御部23と、第1の変換値及びコマンドをホスト機器2から受信する受信部21と、を有し、制御部23は、受信部21が受信したコマンドを所定の演算によって変換することにより、第2の変換値を生成する変換部33と、受信部21が受信した第1の変換値と、変換部33が生成した第2の変換値とが一致しない場合に、不正なアクセスと判定する判定部34と、を含む。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、コンピュータシステム及び半導体記憶装置に関し、特に、ホスト機器と、当該ホスト機器に外部接続可能な半導体記憶装置とを備えたコンピュータシステムに関する。

【背景技術】

【0002】

半導体メモリが搭載されているメモリカードをホストコンピュータ等の外部機器に着脱自在に接続することによって、半導体メモリに記憶されているデータ等を外部機器が利用可能な情報処理装置が実用化されている。

【0003】

この種のメモリカードの中には、半導体メモリに記憶されているデータ等が不正にコピーされることを防止すべく、特定のセキュリティ技術が搭載されているものがある。例えば下記特許文献1には、暗号化されたデータが記憶された半導体メモリと、半導体メモリに特定の順序でアドレスが入力された場合に所定のキーデータを出力する検出部と、半導体メモリから読み出したデータを、上記キーデータを用いて復号するデータ変換部と、を備えた半導体記憶装置が開示されている。

【先行技術文献】

【特許文献】

【0004】

【特許文献1】特開平9−106690号公報

【発明の概要】

【発明が解決しようとする課題】

【0005】

しかしながら、上記特許文献1に開示された半導体記憶装置では、大量のサンプルを解析することによって暗号が解読される可能性があり、しかも、外部機器からは半導体メモリの全領域に何の制約もなくアクセス可能である。そのため、一旦暗号が解読されると、半導体メモリに記憶されている全データが不正に復号されてしまうため、セキュリティ性が十分とはいえない。

【0006】

本発明はかかる事情に鑑みて成されたものであり、高いセキュリティ性を有する半導体記憶装置及びそれを備えたコンピュータシステムを得ることを目的とするものである。

【課題を解決するための手段】

【0007】

本発明の第1の態様に係るコンピュータシステムは、ホスト機器と、前記ホスト機器に外部接続可能な半導体記憶装置と、を備え、前記ホスト機器は、前記半導体記憶装置に送信するコマンドを所定の演算によって変換することにより、第1の変換値を生成する第1の生成部と、前記第1の変換値及び前記コマンドを前記半導体記憶装置に送信する送信部と、を有し、前記半導体記憶装置は、前記ホスト機器から前記半導体記憶装置へのアクセスを制御する制御部と、前記第1の変換値及び前記コマンドを前記ホスト機器から受信する受信部と、を有し、前記制御部は、前記受信部が受信した前記コマンドを前記所定の演算によって変換することにより、第2の変換値を生成する第2の生成部と、前記受信部が受信した前記第1の変換値と、前記第2の生成部が生成した前記第2の変換値とが一致しない場合に、不正なアクセスと判定する判定部と、を含むことを特徴とするものである。

【0008】

第1の態様に係るコンピュータシステムによれば、ホスト機器は、第1の変換値及びコマンドを半導体記憶装置に送信する。半導体記憶装置は、受信したコマンドを変換することによって第2の変換値を生成し、受信した第1の変換値が第2の変換値に一致しない場合に不正なアクセスと判定する。このように、コマンドのみならず第1の変換値をホスト機器から半導体記憶装置に送信し、第1の変換値が第2の変換値に一致しない場合には不正なアクセスと判定することにより、ホスト機器と半導体記憶装置との間における信号の送受信を複雑化することができる。その結果、半導体記憶装置のセキュリティ性を向上することが可能となる。

【0009】

本発明の第2の態様に係るコンピュータシステムは、第1の態様に係るコンピュータシステムにおいて特に、前記半導体記憶装置は、前記半導体記憶装置が前記ホスト機器から受信する予定の前記第1の変換値を記憶する記憶部をさらに有し、前記判定部はさらに、前記受信部が受信した前記第1の変換値が、前記記憶部に記憶されている前記第1の変換値に一致しない場合に、不正なアクセスと判定することを特徴とするものである。

【0010】

第2の態様に係るコンピュータシステムによれば、判定部は、受信した第1の変換値が、記憶部に記憶されている第1の変換値に一致しない場合に、不正なアクセスと判定する。従って、受信する予定の第1の変換値とは異なる変換値がホスト機器から送信されてきた場合には不正なアクセスと判定できるため、半導体記憶装置のセキュリティ性をさらに向上することが可能となる。

【0011】

本発明の第3の態様に係るコンピュータシステムは、第2の態様に係るコンピュータシステムにおいて特に、前記受信部が受信した前記第1の変換値が、前記記憶部に記憶されている前記第1の変換値に一致しない場合には、前記送信部は前記コマンドを送信しないことを特徴とするものである。

【0012】

第3の態様に係るコンピュータシステムによれば、受信した第1の変換値が、記憶部に記憶されている第1の変換値に一致しない場合には、ホスト機器から半導体記憶装置にコマンドが送信されない。従って、ホスト機器と半導体記憶装置との間における信号の送受信をさらに複雑化できるため、半導体記憶装置のセキュリティ性をさらに向上することが可能となる。

【0013】

本発明の第4の態様に係るコンピュータシステムは、第1〜第3のいずれか一つの態様に係るコンピュータシステムにおいて特に、前記ホスト機器は、前記第1の変換値を表すデータ内の所定の箇所に不定値のデータを挿入することにより、前記第1の変換値を加工する加工部をさらに有し、前記制御部は、前記受信部が受信した加工後の前記第1の変換値から、加工前の前記第1の変換値を復元する復元部をさらに含むことを特徴とするものである。

【0014】

第4の態様に係るコンピュータシステムによれば、加工部は、第1の変換値を表すデータ内の所定の箇所に不定値のデータを挿入することにより、第1の変換値を加工する。従って、ホスト機器から半導体記憶装置に送信される第1の変換値を複雑化できるため、半導体記憶装置のセキュリティ性をさらに向上することが可能となる。

【0015】

本発明の第5の態様に係るコンピュータシステムは、第1〜第4のいずれか一つの態様に係るコンピュータシステムにおいて特に、前記ホスト機器は、前記コマンド内の所定の箇所に不定値のデータを挿入することにより、前記コマンドを加工する加工部をさらに有し、前記制御部は、前記受信部が受信した加工後の前記コマンドから、加工前の前記コマンドを復元する復元部をさらに含むことを特徴とするものである。

【0016】

第5の態様に係るコンピュータシステムによれば、加工部は、コマンド内の所定の箇所に不定値のデータを挿入することにより、コマンドを加工する。従って、ホスト機器から半導体記憶装置に送信されるコマンドを複雑化できるため、半導体記憶装置のセキュリティ性をさらに向上することが可能となる。

【0017】

本発明の第6の態様に係るコンピュータシステムは、第1〜第5のいずれか一つの態様に係るコンピュータシステムにおいて特に、前記送信部は、前記第1の変換値を送信した後に前記コマンドを送信し、前記判定部はさらに、前記第1の変換値に関する送信時刻と前記コマンドに関する送信時刻との間の時間間隔が所定の許容範囲外である場合に、不正なアクセスと判定することを特徴とするものである。

【0018】

第6の態様に係るコンピュータシステムによれば、判定部は、第1の変換値に関する送信時刻とコマンドに関する送信時刻との間の時間間隔が所定の許容範囲外である場合に、不正なアクセスと判定する。このように、第1の変換値に関する送信時刻とコマンドに関する送信時刻との間の時間間隔に許容範囲を設定し、当該時間間隔が許容範囲外である場合には不正なアクセスと判定することにより、半導体記憶装置のセキュリティ性をさらに向上することが可能となる。

【0019】

本発明の第7の態様に係るコンピュータシステムは、第1〜第6のいずれか一つの態様に係るコンピュータシステムにおいて特に、前記第1の生成部は、予め規定された複数の演算のいずれかによって前記コマンドを変換することにより、前記第1の変換値を生成することを特徴とするものである。

【0020】

第7の態様に係るコンピュータシステムによれば、第1の生成部は、予め規定された複数の演算のいずれかによってコマンドを変換することにより、第1の変換値を生成する。従って、同一のコマンドに対して複数種類の第1の変換値が生成され、ホスト機器から半導体記憶装置に送信される第1の変換値を複雑化できるため、半導体記憶装置のセキュリティ性をさらに向上することが可能となる。

【0021】

本発明の第8の態様に係るコンピュータシステムは、第1〜第7のいずれか一つの態様に係るコンピュータシステムにおいて特に、前記判定部が不正なアクセスと判定した場合には、前記制御部は、前記ホスト機器に対する応答処理として、ダミーデータを返信する処理、エラーコードを返信する処理、及び何らのデータも返信しない処理のうちのいずれかを不定に選択して実行することを特徴とするものである。

【0022】

第8の態様に係るコンピュータシステムによれば、判定部が不正なアクセスと判定した場合には、制御部は、ホスト機器に対する応答処理として、ダミーデータを返信する処理、エラーコードを返信する処理、及び何らのデータも返信しない処理のうちのいずれかを不定に選択して実行する。従って、不正アクセスに対して常にエラーコードを返信する場合等と比較すると、不正アクセスを行う第三者は不正アクセスに失敗したことに気付きにくい。従って、解析のやり直しを開始する時期を遅らせることが可能となる。

【0023】

本発明の第9の態様に係る半導体記憶装置は、ホスト機器に外部接続可能な半導体記憶装置であって、前記ホスト機器から前記半導体記憶装置へのアクセスを制御する制御部と、前記ホスト機器から、コマンドと、当該コマンドを所定の演算によって変換することにより生成された第1の変換値とを受信する受信部と、を備え、前記制御部は、前記受信部が受信した前記コマンドを前記所定の演算によって変換することにより、第2の変換値を生成する生成部と、前記受信部が受信した前記第1の変換値と、前記生成部が生成した前記第2の変換値とが一致しない場合に、不正なアクセスと判定する判定部と、を有することを特徴とするものである。

【0024】

第9の態様に係る半導体記憶装置によれば、ホスト機器は、第1の変換値及びコマンドを半導体記憶装置に送信する。半導体記憶装置は、受信したコマンドを変換することによって第2の変換値を生成し、受信した第1の変換値が第2の変換値に一致しない場合に不正なアクセスと判定する。このように、コマンドのみならず第1の変換値をホスト機器から半導体記憶装置に送信し、第1の変換値が第2の変換値に一致しない場合には不正なアクセスと判定することにより、ホスト機器と半導体記憶装置との間における信号の送受信を複雑化することができる。その結果、半導体記憶装置のセキュリティ性を向上することが可能となる。

【発明の効果】

【0025】

本発明によれば、高いセキュリティ性を有する半導体記憶装置及びそれを備えたコンピュータシステムを得ることができる。

【図面の簡単な説明】

【0026】

【図1】本発明の実施の形態に係るコンピュータシステムの全体構成を簡略化して示す図である。

【図2】ホスト機器の構成を簡略化して示すブロック図である。

【図3】半導体記憶装置の構成を簡略化して示すブロック図である。

【図4】制御部の構成を具体的に示すブロック図である。

【図5】記憶部の構成を示す図である。

【図6】テーブルデータを簡略化して示す図である。

【図7】ホスト機器における処理内容を示すフローチャートである。

【図8】半導体記憶装置における処理内容を示すフローチャートである。

【図9】加工部によるハッシュ値の加工の例を示す図である。

【図10】加工部によるコマンドの加工の例を示す図である。

【図11】テーブルデータを簡略化して示す図である。

【図12】半導体記憶装置における処理内容を示すフローチャートである。

【図13】テーブルデータを簡略化して示す図である。

【発明を実施するための形態】

【0027】

以下、本発明の実施の形態について、図面を用いて詳細に説明する。なお、異なる図面において同一の符号を付した要素は、同一又は相応する要素を示すものとする。

【0028】

図1は、本発明の実施の形態に係るコンピュータシステム1の全体構成を簡略化して示す図である。コンピュータシステム1は、外部機器としてのホスト機器2と、ホスト機器2に対して着脱自在に外部接続可能なメモリカード等の半導体記憶装置3とを備えて構成されている。

【0029】

図2は、ホスト機器2の構成を簡略化して示すブロック図である。図2の接続関係で示すように、ホスト機器2は、コマンド生成部11、変換部12、加工部13、送信部14、制御部15、及び受信部16を備えて構成されている。

【0030】

図3は、半導体記憶装置3の構成を簡略化して示すブロック図である。図3の接続関係で示すように、半導体記憶装置3は、受信部21、送信部22、制御部23、及び記憶部24を備えて構成されている。

【0031】

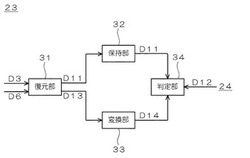

図4は、制御部23の構成を具体的に示すブロック図である。図4の接続関係で示すように、制御部23は、復元部31、保持部32、変換部33、及び判定部34を備えて構成されている。

【0032】

図5は、記憶部24の構成を示す図である。記憶部24は、任意のコンテンツデータD7が記憶された記憶領域AR1と、テーブルデータD12が記憶された記憶領域AR2とを有している。記憶領域AR1はホスト機器2からアクセス可能な領域であり、記憶領域AR2はホスト機器2からアクセス不可能な領域である。なお、記憶領域AR1と記憶領域AR2とが別個のICチップとして構成されていてもよい。

【0033】

図6は、テーブルデータD12の第1の例としてのテーブルデータD12Aを簡略化して示す図である。テーブルデータD12Aには、ホスト機器2から半導体記憶装置3に送信される予定の複数のコマンドと、各コマンドのハッシュ値との対応関係が記述されている。

【0034】

図7は、ホスト機器2における処理内容を示すフローチャートであり、図8は、半導体記憶装置3における処理内容を示すフローチャートである。以下、図1〜8を参照して、本実施の形態に係るコンピュータシステム1の動作について説明する。

【0035】

まずステップP101においてコマンド生成部11は、半導体記憶装置3に送信するコマンドD1を生成する。

【0036】

次にステップP102において変換部12は、所定のハッシュ関数を用いた演算によってコマンドD1を変換することにより、ハッシュ値D2を生成する。

【0037】

次にステップP103において加工部13は、所定の規則に従ってハッシュ値D2を加工することにより、加工後のハッシュ値D3を生成する。

【0038】

図9は、加工部13によるハッシュ値D2の加工の例を示す図である。図9の(A)に示すように、ハッシュ値D2は、上位4バイトのデータD2U及び下位4バイトのデータD2Lから成る合計8バイトのデータとして与えられる。また、加工部13はタイムカウンタを有しており、図9の(B)に示すように、当該タイムカウンタのカウンタ値D20は、上位4バイトのデータD20U及び下位4バイトのデータD20Lから成る合計8バイトのデータとして与えられる。そして、加工部13は、図9の(C)に示すように、データD2U,D20U,D2L,D20Lを上位側からこの順に配列することにより、合計16バイトのデータ長を有するハッシュ値D3を生成する。この例におけるハッシュ値D3に関しては、最上位の4バイトと、下位側から2番目の4バイトとに、加工前のハッシュ値D2が含まれている。

【0039】

次にステップP104において送信部14は、ハッシュ値D3を半導体記憶装置3に送信する。

【0040】

次にステップP201において受信部21は、ハッシュ値D3をホスト機器2から受信し、受信したハッシュ値D3を制御部23に入力する。

【0041】

次にステップP202において復元部31は、ハッシュ値D3から最上位の4バイトと下位側から2番目の4バイトとを抽出することにより、加工前のハッシュ値D2に相当するハッシュ値D11を復元する。復元されたハッシュ値D11は保持部32によって保持される。

【0042】

次にステップP203において判定部34は、保持部32が保持しているハッシュ値D11が、テーブルデータD12に登録されているいずれかのハッシュ値に一致するか否かを判定する。

【0043】

ハッシュ値D11が登録ハッシュ値に一致する場合(つまりステップP203における判定の結果が「YES」である場合)は、次にステップP204において制御部23は、コマンド要求D4を送信部22からホスト機器2に送信する。コマンド要求D4は、受信部16によって受信された後、制御部15に入力される。

【0044】

次にステップP105において制御部15は、ハッシュ値D3を送信してから所定時間内にコマンド要求D4を受信したか否かを判定する。

【0045】

所定時間内にコマンド要求D4を受信した場合(つまりステップP105における判定の結果が「YES」である場合)は、次にステップP106において制御部15は、コマンド送信命令D5を加工部13に入力する。コマンド送信命令D5を受けた加工部13は、所定の規則に従ってコマンドD1を加工することにより、加工後のコマンドD1を生成する。

【0046】

図10は、加工部13によるコマンドD1の加工の例を示す図である。図10の(A)に示すように、コマンドD1は、上位4バイトのデータD1U及び下位4バイトのデータD1Lから成る合計8バイトのデータとして与えられる。また、加工部13はタイムカウンタを有しており、図10の(B)に示すように、当該タイムカウンタのカウンタ値D30は、上位4バイトのデータD30U及び下位4バイトのデータD30Lから成る合計8バイトのデータとして与えられる。そして、加工部13は、図10の(C)に示すように、データD1U,D30U,D1L,D30Lを上位側からこの順に配列することにより、合計16バイトのデータ長を有するコマンドD6を生成する。この例におけるコマンドD6に関しては、最上位の4バイトと、下位側から2番目の4バイトとに、加工前のコマンドD1が含まれている。

【0047】

次にステップP107において送信部14は、コマンドD6を半導体記憶装置3に送信する。

【0048】

次にステップP205において受信部21は、コマンドD6をホスト機器2から受信し、受信したコマンドD6を制御部23に入力する。

【0049】

次にステップP206において復元部31は、コマンドD6から最上位の4バイトと下位側から2番目の4バイトとを抽出することにより、加工前のコマンドD1に相当するコマンドD13を復元する。

【0050】

次にステップP207において変換部33は、変換部12と同様のハッシュ関数を用いた演算によってコマンドD13を変換することにより、ハッシュ値D14を生成する。

【0051】

次にステップP208において判定部34は、変換部33によって生成されたハッシュ値D14が、保持部32が保持しているハッシュ値D11に一致するか否かを判定する。

【0052】

ハッシュ値D14がハッシュ値D11に一致する場合(つまりステップP208における判定の結果が「YES」である場合)は、判定部34は、ホスト機器2からのアクセスは正常なアクセスであると判定する。この場合、ステップP209において制御部23は、コマンドD13の内容に応じて記憶部24にアクセスする。コマンドD13が例えばリードコマンドである場合は、コマンドD13に付随するアドレスに従って記憶領域AR1からコンテンツデータD7を読み出し、読み出したコンテンツデータD7を送信部22からホスト機器2に送信する。また、コマンドD13が例えばライトコマンドである場合は、コマンドD13に付随するコンテンツデータを、コマンドD13に付随するアドレスに従って記憶領域AR1に書き込む。

【0053】

図8に示したフローチャートにおいて、保持部32が保持しているハッシュ値D11が、テーブルデータD12に登録されているいずれのハッシュ値にも一致しない場合(つまりステップP203における判定の結果が「NO」である場合)は、判定部34は、ホスト機器2からのアクセスは不正なアクセスであると判定する。この場合、ステップP210において制御部23は、ランダムなダミーデータD8を送信部22からホスト機器2に送信する(第1の応答処理)。あるいは所定のエラーコードD9を送信部22からホスト機器2に送信する(第2の応答処理)。あるいはホスト機器2に何らのデータも送信しない(第3の応答処理)。例えば、データD20Lを「3」で割った余り値が「0」である場合は第1の応答処理を実行し、余り値が「1」である場合は第2の応答処理を実行し、余り値が「2」である場合は第3の応答処理を実行する。

【0054】

図8に示したフローチャートにおいて、変換部33によって生成されたハッシュ値D14が、保持部32が保持しているハッシュ値D11に一致しない場合(つまりステップP208における判定の結果が「NO」である場合)も、ステップP210において上記と同様の応答処理が行われる。

【0055】

<第1の変形例>

図11は、テーブルデータD12の第2の例としてのテーブルデータD12Bを簡略化して示す図である。テーブルデータD12Bには、テーブルデータD12Aに加えて、ハッシュ値D3の送信時刻とコマンドD6の送信時刻との間の時間間隔に関する許容範囲が、コマンド毎に記述されている。許容範囲の上限値及び下限値は、正常なアクセスを行った場合に想定される時間間隔に基づいて設定される。

【0056】

図12は、本変形例に係る半導体記憶装置3における処理内容を示すフローチャートである。変換部33によって生成されたハッシュ値D14が、保持部32が保持しているハッシュ値D11に一致する場合(つまりステップP208における判定の結果が「YES」である場合)は、次にステップP211において判定部34は、ハッシュ値D3の送信時刻とコマンドD6の送信時刻との間の時間間隔が、コマンドD6に関して設定されている許容範囲内に含まれるか否かを判定する。なお、ハッシュ値D3の送信時刻はハッシュ値D3からカウンタ値D20を抽出することによって求められ、コマンドD6の送信時刻はコマンドD6からカウンタ値D30を抽出することによって求められる。

【0057】

両者の時間間隔が許容範囲内である場合(つまりステップP211における判定の結果が「YES」である場合)は、判定部34は、ホスト機器2からのアクセスは正常なアクセスであると判定する。この場合、ステップP209において制御部23は、コマンドD13の内容に応じて記憶部24にアクセスする。一方、両者の時間間隔が許容範囲外である場合(つまりステップP211における判定の結果が「NO」である場合)は、判定部34は、ホスト機器2からのアクセスは不正なアクセスであると判定する。この場合、ステップP210において制御部23は、ランダムなダミーデータD8を送信部22からホスト機器2に送信し、あるいは所定のエラーコードD9を送信部22からホスト機器2に送信し、あるいはホスト機器2に何らのデータも送信しない。

【0058】

<第2の変形例>

図13は、テーブルデータD12の第3の例としてのテーブルデータD12Cを簡略化して示す図である。本変形例では、変換部12によってコマンドD1を変換するためのハッシュ関数として複数のハッシュ関数(md5、sha1、sha256等)が準備されており、変換部12は、複数のハッシュ関数をランダムに選択することによってコマンドD1からハッシュ値D2を生成する。テーブルデータD12Cには、各ハッシュ関数を選択した場合のハッシュ値が記述されている。また、ハッシュ値D3の送信時刻とコマンドD6の送信時刻との間の時間間隔に関する許容時間も、ハッシュ関数毎に設定されている。

【0059】

図8に示したフローチャートにおいて、ステップP203において判定部34は、保持部32が保持しているハッシュ値D11が、テーブルデータD12Cに登録されているいずれかのハッシュ値に一致するか否かを判定する。例えばリードコマンドREAD1に関しては、保持部32が保持しているハッシュ値D11が、テーブルデータD12Cに登録されているハッシュ値A1,A2,A3のいずれかに一致すれば、ステップP203における判定の結果は「YES」となる。

【0060】

<第3の変形例>

上記実施の形態では、加工部13はハッシュ値及びコマンドにタイムカウンタのカウンタ値をそれぞれ挿入したが、カウンタ値の代わりに乱数値を挿入してもよい。

【0061】

また、上記実施の形態では、変換部12,33はハッシュ関数を用いた演算によってコマンドをハッシュ値に変換したが、コマンド毎に異なる任意のキーを用いた排他的論理和演算によってコマンドを変換してもよい。あるいは、ハフマン符号又はシャノン符号等の圧縮アルゴリズム、LPC(Linear Predictive coding)又はフーリエ変換等の音声コーディック、RLE(Run Length Encoding)又はウェーブレット変換等の画像コーディックを用いてコマンドを変換してもよい。

【0062】

<まとめ>

本実施の形態に係るコンピュータシステム1によれば、ホスト機器2は、ハッシュ値D2(第1の変換値)及びコマンドD1を半導体記憶装置3に送信する。半導体記憶装置3は、受信したコマンドD1を変換することによってハッシュ値D14(第2の変換値)を生成し、受信した第1の変換値が第2の変換値に一致しない場合に不正なアクセスと判定する。このように、コマンドのみならず第1の変換値をホスト機器2から半導体記憶装置3に送信し、第1の変換値が第2の変換値に一致しない場合には不正なアクセスと判定することにより、ホスト機器2と半導体記憶装置3との間における信号の送受信を複雑化することができる。その結果、半導体記憶装置3のセキュリティ性を向上することが可能となる。

【0063】

また、本実施の形態に係るコンピュータシステム1によれば、判定部34は、受信した第1の変換値が、記憶部24に記憶されている第1の変換値に一致しない場合に、不正なアクセスと判定する。従って、受信する予定の第1の変換値とは異なる変換値がホスト機器2から送信されてきた場合には不正なアクセスと判定できるため、半導体記憶装置3のセキュリティ性をさらに向上することが可能となる。

【0064】

また、本実施の形態に係るコンピュータシステム1によれば、受信した第1の変換値が、記憶部24に記憶されている第1の変換値に一致しない場合には、ホスト機器2から半導体記憶装置3にコマンドD1が送信されない。従って、ホスト機器2と半導体記憶装置3との間における信号の送受信をさらに複雑化できるため、半導体記憶装置3のセキュリティ性をさらに向上することが可能となる。

【0065】

また、本実施の形態に係るコンピュータシステム1によれば、加工部13は、第1の変換値を表すデータD2内の所定の箇所に不定値のデータD20を挿入することにより、第1の変換値を加工する。従って、ホスト機器2から半導体記憶装置3に送信される第1の変換値を複雑化できるため、半導体記憶装置3のセキュリティ性をさらに向上することが可能となる。

【0066】

また、本実施の形態に係るコンピュータシステム1によれば、加工部13は、コマンドD1内の所定の箇所に不定値のデータD30を挿入することにより、コマンドD1を加工する。従って、ホスト機器2から半導体記憶装置3に送信されるコマンドD1を複雑化できるため、半導体記憶装置3のセキュリティ性をさらに向上することが可能となる。

【0067】

また、本実施の形態に係るコンピュータシステム1によれば、判定部34は、第1の変換値に関する送信時刻とコマンドに関する送信時刻との間の時間間隔が所定の許容範囲外である場合に、不正なアクセスと判定する。このように、第1の変換値に関する送信時刻とコマンドに関する送信時刻との間の時間間隔に許容範囲を設定し、当該時間間隔が許容範囲外である場合には不正なアクセスと判定することにより、半導体記憶装置3のセキュリティ性をさらに向上することが可能となる。

【0068】

また、本実施の形態に係るコンピュータシステム1によれば、変換部12(第1の生成部)は、予め規定された複数の演算のいずれかによってコマンドD1を変換することにより、第1の変換値を生成する。従って、同一のコマンドD1に対して複数種類の第1の変換値が生成され、ホスト機器2から半導体記憶装置3に送信される第1の変換値を複雑化できるため、半導体記憶装置3のセキュリティ性をさらに向上することが可能となる。

【0069】

また、本実施の形態に係るコンピュータシステム1によれば、判定部34が不正なアクセスと判定した場合には、制御部23は、ホスト機器2に対する応答処理として、ダミーデータD8を返信する処理、エラーコードD9を返信する処理、及び何らのデータも返信しない処理のうちのいずれかを不定に選択して実行する。従って、不正アクセスに対して常にエラーコードを返信する場合等と比較すると、不正アクセスを行う第三者は不正アクセスに失敗したことに気付きにくい。従って、解析のやり直しを開始する時期を遅らせることが可能となる。

【符号の説明】

【0070】

1 コンピュータシステム

2 ホスト機器

3 半導体記憶装置

12 変換部

13 加工部

14 送信部

21 受信部

23 制御部

24 記憶部

31 復元部

32 保持部

33 変換部

34 判定部

【技術分野】

【0001】

本発明は、コンピュータシステム及び半導体記憶装置に関し、特に、ホスト機器と、当該ホスト機器に外部接続可能な半導体記憶装置とを備えたコンピュータシステムに関する。

【背景技術】

【0002】

半導体メモリが搭載されているメモリカードをホストコンピュータ等の外部機器に着脱自在に接続することによって、半導体メモリに記憶されているデータ等を外部機器が利用可能な情報処理装置が実用化されている。

【0003】

この種のメモリカードの中には、半導体メモリに記憶されているデータ等が不正にコピーされることを防止すべく、特定のセキュリティ技術が搭載されているものがある。例えば下記特許文献1には、暗号化されたデータが記憶された半導体メモリと、半導体メモリに特定の順序でアドレスが入力された場合に所定のキーデータを出力する検出部と、半導体メモリから読み出したデータを、上記キーデータを用いて復号するデータ変換部と、を備えた半導体記憶装置が開示されている。

【先行技術文献】

【特許文献】

【0004】

【特許文献1】特開平9−106690号公報

【発明の概要】

【発明が解決しようとする課題】

【0005】

しかしながら、上記特許文献1に開示された半導体記憶装置では、大量のサンプルを解析することによって暗号が解読される可能性があり、しかも、外部機器からは半導体メモリの全領域に何の制約もなくアクセス可能である。そのため、一旦暗号が解読されると、半導体メモリに記憶されている全データが不正に復号されてしまうため、セキュリティ性が十分とはいえない。

【0006】

本発明はかかる事情に鑑みて成されたものであり、高いセキュリティ性を有する半導体記憶装置及びそれを備えたコンピュータシステムを得ることを目的とするものである。

【課題を解決するための手段】

【0007】

本発明の第1の態様に係るコンピュータシステムは、ホスト機器と、前記ホスト機器に外部接続可能な半導体記憶装置と、を備え、前記ホスト機器は、前記半導体記憶装置に送信するコマンドを所定の演算によって変換することにより、第1の変換値を生成する第1の生成部と、前記第1の変換値及び前記コマンドを前記半導体記憶装置に送信する送信部と、を有し、前記半導体記憶装置は、前記ホスト機器から前記半導体記憶装置へのアクセスを制御する制御部と、前記第1の変換値及び前記コマンドを前記ホスト機器から受信する受信部と、を有し、前記制御部は、前記受信部が受信した前記コマンドを前記所定の演算によって変換することにより、第2の変換値を生成する第2の生成部と、前記受信部が受信した前記第1の変換値と、前記第2の生成部が生成した前記第2の変換値とが一致しない場合に、不正なアクセスと判定する判定部と、を含むことを特徴とするものである。

【0008】

第1の態様に係るコンピュータシステムによれば、ホスト機器は、第1の変換値及びコマンドを半導体記憶装置に送信する。半導体記憶装置は、受信したコマンドを変換することによって第2の変換値を生成し、受信した第1の変換値が第2の変換値に一致しない場合に不正なアクセスと判定する。このように、コマンドのみならず第1の変換値をホスト機器から半導体記憶装置に送信し、第1の変換値が第2の変換値に一致しない場合には不正なアクセスと判定することにより、ホスト機器と半導体記憶装置との間における信号の送受信を複雑化することができる。その結果、半導体記憶装置のセキュリティ性を向上することが可能となる。

【0009】

本発明の第2の態様に係るコンピュータシステムは、第1の態様に係るコンピュータシステムにおいて特に、前記半導体記憶装置は、前記半導体記憶装置が前記ホスト機器から受信する予定の前記第1の変換値を記憶する記憶部をさらに有し、前記判定部はさらに、前記受信部が受信した前記第1の変換値が、前記記憶部に記憶されている前記第1の変換値に一致しない場合に、不正なアクセスと判定することを特徴とするものである。

【0010】

第2の態様に係るコンピュータシステムによれば、判定部は、受信した第1の変換値が、記憶部に記憶されている第1の変換値に一致しない場合に、不正なアクセスと判定する。従って、受信する予定の第1の変換値とは異なる変換値がホスト機器から送信されてきた場合には不正なアクセスと判定できるため、半導体記憶装置のセキュリティ性をさらに向上することが可能となる。

【0011】

本発明の第3の態様に係るコンピュータシステムは、第2の態様に係るコンピュータシステムにおいて特に、前記受信部が受信した前記第1の変換値が、前記記憶部に記憶されている前記第1の変換値に一致しない場合には、前記送信部は前記コマンドを送信しないことを特徴とするものである。

【0012】

第3の態様に係るコンピュータシステムによれば、受信した第1の変換値が、記憶部に記憶されている第1の変換値に一致しない場合には、ホスト機器から半導体記憶装置にコマンドが送信されない。従って、ホスト機器と半導体記憶装置との間における信号の送受信をさらに複雑化できるため、半導体記憶装置のセキュリティ性をさらに向上することが可能となる。

【0013】

本発明の第4の態様に係るコンピュータシステムは、第1〜第3のいずれか一つの態様に係るコンピュータシステムにおいて特に、前記ホスト機器は、前記第1の変換値を表すデータ内の所定の箇所に不定値のデータを挿入することにより、前記第1の変換値を加工する加工部をさらに有し、前記制御部は、前記受信部が受信した加工後の前記第1の変換値から、加工前の前記第1の変換値を復元する復元部をさらに含むことを特徴とするものである。

【0014】

第4の態様に係るコンピュータシステムによれば、加工部は、第1の変換値を表すデータ内の所定の箇所に不定値のデータを挿入することにより、第1の変換値を加工する。従って、ホスト機器から半導体記憶装置に送信される第1の変換値を複雑化できるため、半導体記憶装置のセキュリティ性をさらに向上することが可能となる。

【0015】

本発明の第5の態様に係るコンピュータシステムは、第1〜第4のいずれか一つの態様に係るコンピュータシステムにおいて特に、前記ホスト機器は、前記コマンド内の所定の箇所に不定値のデータを挿入することにより、前記コマンドを加工する加工部をさらに有し、前記制御部は、前記受信部が受信した加工後の前記コマンドから、加工前の前記コマンドを復元する復元部をさらに含むことを特徴とするものである。

【0016】

第5の態様に係るコンピュータシステムによれば、加工部は、コマンド内の所定の箇所に不定値のデータを挿入することにより、コマンドを加工する。従って、ホスト機器から半導体記憶装置に送信されるコマンドを複雑化できるため、半導体記憶装置のセキュリティ性をさらに向上することが可能となる。

【0017】

本発明の第6の態様に係るコンピュータシステムは、第1〜第5のいずれか一つの態様に係るコンピュータシステムにおいて特に、前記送信部は、前記第1の変換値を送信した後に前記コマンドを送信し、前記判定部はさらに、前記第1の変換値に関する送信時刻と前記コマンドに関する送信時刻との間の時間間隔が所定の許容範囲外である場合に、不正なアクセスと判定することを特徴とするものである。

【0018】

第6の態様に係るコンピュータシステムによれば、判定部は、第1の変換値に関する送信時刻とコマンドに関する送信時刻との間の時間間隔が所定の許容範囲外である場合に、不正なアクセスと判定する。このように、第1の変換値に関する送信時刻とコマンドに関する送信時刻との間の時間間隔に許容範囲を設定し、当該時間間隔が許容範囲外である場合には不正なアクセスと判定することにより、半導体記憶装置のセキュリティ性をさらに向上することが可能となる。

【0019】

本発明の第7の態様に係るコンピュータシステムは、第1〜第6のいずれか一つの態様に係るコンピュータシステムにおいて特に、前記第1の生成部は、予め規定された複数の演算のいずれかによって前記コマンドを変換することにより、前記第1の変換値を生成することを特徴とするものである。

【0020】

第7の態様に係るコンピュータシステムによれば、第1の生成部は、予め規定された複数の演算のいずれかによってコマンドを変換することにより、第1の変換値を生成する。従って、同一のコマンドに対して複数種類の第1の変換値が生成され、ホスト機器から半導体記憶装置に送信される第1の変換値を複雑化できるため、半導体記憶装置のセキュリティ性をさらに向上することが可能となる。

【0021】

本発明の第8の態様に係るコンピュータシステムは、第1〜第7のいずれか一つの態様に係るコンピュータシステムにおいて特に、前記判定部が不正なアクセスと判定した場合には、前記制御部は、前記ホスト機器に対する応答処理として、ダミーデータを返信する処理、エラーコードを返信する処理、及び何らのデータも返信しない処理のうちのいずれかを不定に選択して実行することを特徴とするものである。

【0022】

第8の態様に係るコンピュータシステムによれば、判定部が不正なアクセスと判定した場合には、制御部は、ホスト機器に対する応答処理として、ダミーデータを返信する処理、エラーコードを返信する処理、及び何らのデータも返信しない処理のうちのいずれかを不定に選択して実行する。従って、不正アクセスに対して常にエラーコードを返信する場合等と比較すると、不正アクセスを行う第三者は不正アクセスに失敗したことに気付きにくい。従って、解析のやり直しを開始する時期を遅らせることが可能となる。

【0023】

本発明の第9の態様に係る半導体記憶装置は、ホスト機器に外部接続可能な半導体記憶装置であって、前記ホスト機器から前記半導体記憶装置へのアクセスを制御する制御部と、前記ホスト機器から、コマンドと、当該コマンドを所定の演算によって変換することにより生成された第1の変換値とを受信する受信部と、を備え、前記制御部は、前記受信部が受信した前記コマンドを前記所定の演算によって変換することにより、第2の変換値を生成する生成部と、前記受信部が受信した前記第1の変換値と、前記生成部が生成した前記第2の変換値とが一致しない場合に、不正なアクセスと判定する判定部と、を有することを特徴とするものである。

【0024】

第9の態様に係る半導体記憶装置によれば、ホスト機器は、第1の変換値及びコマンドを半導体記憶装置に送信する。半導体記憶装置は、受信したコマンドを変換することによって第2の変換値を生成し、受信した第1の変換値が第2の変換値に一致しない場合に不正なアクセスと判定する。このように、コマンドのみならず第1の変換値をホスト機器から半導体記憶装置に送信し、第1の変換値が第2の変換値に一致しない場合には不正なアクセスと判定することにより、ホスト機器と半導体記憶装置との間における信号の送受信を複雑化することができる。その結果、半導体記憶装置のセキュリティ性を向上することが可能となる。

【発明の効果】

【0025】

本発明によれば、高いセキュリティ性を有する半導体記憶装置及びそれを備えたコンピュータシステムを得ることができる。

【図面の簡単な説明】

【0026】

【図1】本発明の実施の形態に係るコンピュータシステムの全体構成を簡略化して示す図である。

【図2】ホスト機器の構成を簡略化して示すブロック図である。

【図3】半導体記憶装置の構成を簡略化して示すブロック図である。

【図4】制御部の構成を具体的に示すブロック図である。

【図5】記憶部の構成を示す図である。

【図6】テーブルデータを簡略化して示す図である。

【図7】ホスト機器における処理内容を示すフローチャートである。

【図8】半導体記憶装置における処理内容を示すフローチャートである。

【図9】加工部によるハッシュ値の加工の例を示す図である。

【図10】加工部によるコマンドの加工の例を示す図である。

【図11】テーブルデータを簡略化して示す図である。

【図12】半導体記憶装置における処理内容を示すフローチャートである。

【図13】テーブルデータを簡略化して示す図である。

【発明を実施するための形態】

【0027】

以下、本発明の実施の形態について、図面を用いて詳細に説明する。なお、異なる図面において同一の符号を付した要素は、同一又は相応する要素を示すものとする。

【0028】

図1は、本発明の実施の形態に係るコンピュータシステム1の全体構成を簡略化して示す図である。コンピュータシステム1は、外部機器としてのホスト機器2と、ホスト機器2に対して着脱自在に外部接続可能なメモリカード等の半導体記憶装置3とを備えて構成されている。

【0029】

図2は、ホスト機器2の構成を簡略化して示すブロック図である。図2の接続関係で示すように、ホスト機器2は、コマンド生成部11、変換部12、加工部13、送信部14、制御部15、及び受信部16を備えて構成されている。

【0030】

図3は、半導体記憶装置3の構成を簡略化して示すブロック図である。図3の接続関係で示すように、半導体記憶装置3は、受信部21、送信部22、制御部23、及び記憶部24を備えて構成されている。

【0031】

図4は、制御部23の構成を具体的に示すブロック図である。図4の接続関係で示すように、制御部23は、復元部31、保持部32、変換部33、及び判定部34を備えて構成されている。

【0032】

図5は、記憶部24の構成を示す図である。記憶部24は、任意のコンテンツデータD7が記憶された記憶領域AR1と、テーブルデータD12が記憶された記憶領域AR2とを有している。記憶領域AR1はホスト機器2からアクセス可能な領域であり、記憶領域AR2はホスト機器2からアクセス不可能な領域である。なお、記憶領域AR1と記憶領域AR2とが別個のICチップとして構成されていてもよい。

【0033】

図6は、テーブルデータD12の第1の例としてのテーブルデータD12Aを簡略化して示す図である。テーブルデータD12Aには、ホスト機器2から半導体記憶装置3に送信される予定の複数のコマンドと、各コマンドのハッシュ値との対応関係が記述されている。

【0034】

図7は、ホスト機器2における処理内容を示すフローチャートであり、図8は、半導体記憶装置3における処理内容を示すフローチャートである。以下、図1〜8を参照して、本実施の形態に係るコンピュータシステム1の動作について説明する。

【0035】

まずステップP101においてコマンド生成部11は、半導体記憶装置3に送信するコマンドD1を生成する。

【0036】

次にステップP102において変換部12は、所定のハッシュ関数を用いた演算によってコマンドD1を変換することにより、ハッシュ値D2を生成する。

【0037】

次にステップP103において加工部13は、所定の規則に従ってハッシュ値D2を加工することにより、加工後のハッシュ値D3を生成する。

【0038】

図9は、加工部13によるハッシュ値D2の加工の例を示す図である。図9の(A)に示すように、ハッシュ値D2は、上位4バイトのデータD2U及び下位4バイトのデータD2Lから成る合計8バイトのデータとして与えられる。また、加工部13はタイムカウンタを有しており、図9の(B)に示すように、当該タイムカウンタのカウンタ値D20は、上位4バイトのデータD20U及び下位4バイトのデータD20Lから成る合計8バイトのデータとして与えられる。そして、加工部13は、図9の(C)に示すように、データD2U,D20U,D2L,D20Lを上位側からこの順に配列することにより、合計16バイトのデータ長を有するハッシュ値D3を生成する。この例におけるハッシュ値D3に関しては、最上位の4バイトと、下位側から2番目の4バイトとに、加工前のハッシュ値D2が含まれている。

【0039】

次にステップP104において送信部14は、ハッシュ値D3を半導体記憶装置3に送信する。

【0040】

次にステップP201において受信部21は、ハッシュ値D3をホスト機器2から受信し、受信したハッシュ値D3を制御部23に入力する。

【0041】

次にステップP202において復元部31は、ハッシュ値D3から最上位の4バイトと下位側から2番目の4バイトとを抽出することにより、加工前のハッシュ値D2に相当するハッシュ値D11を復元する。復元されたハッシュ値D11は保持部32によって保持される。

【0042】

次にステップP203において判定部34は、保持部32が保持しているハッシュ値D11が、テーブルデータD12に登録されているいずれかのハッシュ値に一致するか否かを判定する。

【0043】

ハッシュ値D11が登録ハッシュ値に一致する場合(つまりステップP203における判定の結果が「YES」である場合)は、次にステップP204において制御部23は、コマンド要求D4を送信部22からホスト機器2に送信する。コマンド要求D4は、受信部16によって受信された後、制御部15に入力される。

【0044】

次にステップP105において制御部15は、ハッシュ値D3を送信してから所定時間内にコマンド要求D4を受信したか否かを判定する。

【0045】

所定時間内にコマンド要求D4を受信した場合(つまりステップP105における判定の結果が「YES」である場合)は、次にステップP106において制御部15は、コマンド送信命令D5を加工部13に入力する。コマンド送信命令D5を受けた加工部13は、所定の規則に従ってコマンドD1を加工することにより、加工後のコマンドD1を生成する。

【0046】

図10は、加工部13によるコマンドD1の加工の例を示す図である。図10の(A)に示すように、コマンドD1は、上位4バイトのデータD1U及び下位4バイトのデータD1Lから成る合計8バイトのデータとして与えられる。また、加工部13はタイムカウンタを有しており、図10の(B)に示すように、当該タイムカウンタのカウンタ値D30は、上位4バイトのデータD30U及び下位4バイトのデータD30Lから成る合計8バイトのデータとして与えられる。そして、加工部13は、図10の(C)に示すように、データD1U,D30U,D1L,D30Lを上位側からこの順に配列することにより、合計16バイトのデータ長を有するコマンドD6を生成する。この例におけるコマンドD6に関しては、最上位の4バイトと、下位側から2番目の4バイトとに、加工前のコマンドD1が含まれている。

【0047】

次にステップP107において送信部14は、コマンドD6を半導体記憶装置3に送信する。

【0048】

次にステップP205において受信部21は、コマンドD6をホスト機器2から受信し、受信したコマンドD6を制御部23に入力する。

【0049】

次にステップP206において復元部31は、コマンドD6から最上位の4バイトと下位側から2番目の4バイトとを抽出することにより、加工前のコマンドD1に相当するコマンドD13を復元する。

【0050】

次にステップP207において変換部33は、変換部12と同様のハッシュ関数を用いた演算によってコマンドD13を変換することにより、ハッシュ値D14を生成する。

【0051】

次にステップP208において判定部34は、変換部33によって生成されたハッシュ値D14が、保持部32が保持しているハッシュ値D11に一致するか否かを判定する。

【0052】

ハッシュ値D14がハッシュ値D11に一致する場合(つまりステップP208における判定の結果が「YES」である場合)は、判定部34は、ホスト機器2からのアクセスは正常なアクセスであると判定する。この場合、ステップP209において制御部23は、コマンドD13の内容に応じて記憶部24にアクセスする。コマンドD13が例えばリードコマンドである場合は、コマンドD13に付随するアドレスに従って記憶領域AR1からコンテンツデータD7を読み出し、読み出したコンテンツデータD7を送信部22からホスト機器2に送信する。また、コマンドD13が例えばライトコマンドである場合は、コマンドD13に付随するコンテンツデータを、コマンドD13に付随するアドレスに従って記憶領域AR1に書き込む。

【0053】

図8に示したフローチャートにおいて、保持部32が保持しているハッシュ値D11が、テーブルデータD12に登録されているいずれのハッシュ値にも一致しない場合(つまりステップP203における判定の結果が「NO」である場合)は、判定部34は、ホスト機器2からのアクセスは不正なアクセスであると判定する。この場合、ステップP210において制御部23は、ランダムなダミーデータD8を送信部22からホスト機器2に送信する(第1の応答処理)。あるいは所定のエラーコードD9を送信部22からホスト機器2に送信する(第2の応答処理)。あるいはホスト機器2に何らのデータも送信しない(第3の応答処理)。例えば、データD20Lを「3」で割った余り値が「0」である場合は第1の応答処理を実行し、余り値が「1」である場合は第2の応答処理を実行し、余り値が「2」である場合は第3の応答処理を実行する。

【0054】

図8に示したフローチャートにおいて、変換部33によって生成されたハッシュ値D14が、保持部32が保持しているハッシュ値D11に一致しない場合(つまりステップP208における判定の結果が「NO」である場合)も、ステップP210において上記と同様の応答処理が行われる。

【0055】

<第1の変形例>

図11は、テーブルデータD12の第2の例としてのテーブルデータD12Bを簡略化して示す図である。テーブルデータD12Bには、テーブルデータD12Aに加えて、ハッシュ値D3の送信時刻とコマンドD6の送信時刻との間の時間間隔に関する許容範囲が、コマンド毎に記述されている。許容範囲の上限値及び下限値は、正常なアクセスを行った場合に想定される時間間隔に基づいて設定される。

【0056】

図12は、本変形例に係る半導体記憶装置3における処理内容を示すフローチャートである。変換部33によって生成されたハッシュ値D14が、保持部32が保持しているハッシュ値D11に一致する場合(つまりステップP208における判定の結果が「YES」である場合)は、次にステップP211において判定部34は、ハッシュ値D3の送信時刻とコマンドD6の送信時刻との間の時間間隔が、コマンドD6に関して設定されている許容範囲内に含まれるか否かを判定する。なお、ハッシュ値D3の送信時刻はハッシュ値D3からカウンタ値D20を抽出することによって求められ、コマンドD6の送信時刻はコマンドD6からカウンタ値D30を抽出することによって求められる。

【0057】

両者の時間間隔が許容範囲内である場合(つまりステップP211における判定の結果が「YES」である場合)は、判定部34は、ホスト機器2からのアクセスは正常なアクセスであると判定する。この場合、ステップP209において制御部23は、コマンドD13の内容に応じて記憶部24にアクセスする。一方、両者の時間間隔が許容範囲外である場合(つまりステップP211における判定の結果が「NO」である場合)は、判定部34は、ホスト機器2からのアクセスは不正なアクセスであると判定する。この場合、ステップP210において制御部23は、ランダムなダミーデータD8を送信部22からホスト機器2に送信し、あるいは所定のエラーコードD9を送信部22からホスト機器2に送信し、あるいはホスト機器2に何らのデータも送信しない。

【0058】

<第2の変形例>

図13は、テーブルデータD12の第3の例としてのテーブルデータD12Cを簡略化して示す図である。本変形例では、変換部12によってコマンドD1を変換するためのハッシュ関数として複数のハッシュ関数(md5、sha1、sha256等)が準備されており、変換部12は、複数のハッシュ関数をランダムに選択することによってコマンドD1からハッシュ値D2を生成する。テーブルデータD12Cには、各ハッシュ関数を選択した場合のハッシュ値が記述されている。また、ハッシュ値D3の送信時刻とコマンドD6の送信時刻との間の時間間隔に関する許容時間も、ハッシュ関数毎に設定されている。

【0059】

図8に示したフローチャートにおいて、ステップP203において判定部34は、保持部32が保持しているハッシュ値D11が、テーブルデータD12Cに登録されているいずれかのハッシュ値に一致するか否かを判定する。例えばリードコマンドREAD1に関しては、保持部32が保持しているハッシュ値D11が、テーブルデータD12Cに登録されているハッシュ値A1,A2,A3のいずれかに一致すれば、ステップP203における判定の結果は「YES」となる。

【0060】

<第3の変形例>

上記実施の形態では、加工部13はハッシュ値及びコマンドにタイムカウンタのカウンタ値をそれぞれ挿入したが、カウンタ値の代わりに乱数値を挿入してもよい。

【0061】

また、上記実施の形態では、変換部12,33はハッシュ関数を用いた演算によってコマンドをハッシュ値に変換したが、コマンド毎に異なる任意のキーを用いた排他的論理和演算によってコマンドを変換してもよい。あるいは、ハフマン符号又はシャノン符号等の圧縮アルゴリズム、LPC(Linear Predictive coding)又はフーリエ変換等の音声コーディック、RLE(Run Length Encoding)又はウェーブレット変換等の画像コーディックを用いてコマンドを変換してもよい。

【0062】

<まとめ>

本実施の形態に係るコンピュータシステム1によれば、ホスト機器2は、ハッシュ値D2(第1の変換値)及びコマンドD1を半導体記憶装置3に送信する。半導体記憶装置3は、受信したコマンドD1を変換することによってハッシュ値D14(第2の変換値)を生成し、受信した第1の変換値が第2の変換値に一致しない場合に不正なアクセスと判定する。このように、コマンドのみならず第1の変換値をホスト機器2から半導体記憶装置3に送信し、第1の変換値が第2の変換値に一致しない場合には不正なアクセスと判定することにより、ホスト機器2と半導体記憶装置3との間における信号の送受信を複雑化することができる。その結果、半導体記憶装置3のセキュリティ性を向上することが可能となる。

【0063】

また、本実施の形態に係るコンピュータシステム1によれば、判定部34は、受信した第1の変換値が、記憶部24に記憶されている第1の変換値に一致しない場合に、不正なアクセスと判定する。従って、受信する予定の第1の変換値とは異なる変換値がホスト機器2から送信されてきた場合には不正なアクセスと判定できるため、半導体記憶装置3のセキュリティ性をさらに向上することが可能となる。

【0064】

また、本実施の形態に係るコンピュータシステム1によれば、受信した第1の変換値が、記憶部24に記憶されている第1の変換値に一致しない場合には、ホスト機器2から半導体記憶装置3にコマンドD1が送信されない。従って、ホスト機器2と半導体記憶装置3との間における信号の送受信をさらに複雑化できるため、半導体記憶装置3のセキュリティ性をさらに向上することが可能となる。

【0065】

また、本実施の形態に係るコンピュータシステム1によれば、加工部13は、第1の変換値を表すデータD2内の所定の箇所に不定値のデータD20を挿入することにより、第1の変換値を加工する。従って、ホスト機器2から半導体記憶装置3に送信される第1の変換値を複雑化できるため、半導体記憶装置3のセキュリティ性をさらに向上することが可能となる。

【0066】

また、本実施の形態に係るコンピュータシステム1によれば、加工部13は、コマンドD1内の所定の箇所に不定値のデータD30を挿入することにより、コマンドD1を加工する。従って、ホスト機器2から半導体記憶装置3に送信されるコマンドD1を複雑化できるため、半導体記憶装置3のセキュリティ性をさらに向上することが可能となる。

【0067】

また、本実施の形態に係るコンピュータシステム1によれば、判定部34は、第1の変換値に関する送信時刻とコマンドに関する送信時刻との間の時間間隔が所定の許容範囲外である場合に、不正なアクセスと判定する。このように、第1の変換値に関する送信時刻とコマンドに関する送信時刻との間の時間間隔に許容範囲を設定し、当該時間間隔が許容範囲外である場合には不正なアクセスと判定することにより、半導体記憶装置3のセキュリティ性をさらに向上することが可能となる。

【0068】

また、本実施の形態に係るコンピュータシステム1によれば、変換部12(第1の生成部)は、予め規定された複数の演算のいずれかによってコマンドD1を変換することにより、第1の変換値を生成する。従って、同一のコマンドD1に対して複数種類の第1の変換値が生成され、ホスト機器2から半導体記憶装置3に送信される第1の変換値を複雑化できるため、半導体記憶装置3のセキュリティ性をさらに向上することが可能となる。

【0069】

また、本実施の形態に係るコンピュータシステム1によれば、判定部34が不正なアクセスと判定した場合には、制御部23は、ホスト機器2に対する応答処理として、ダミーデータD8を返信する処理、エラーコードD9を返信する処理、及び何らのデータも返信しない処理のうちのいずれかを不定に選択して実行する。従って、不正アクセスに対して常にエラーコードを返信する場合等と比較すると、不正アクセスを行う第三者は不正アクセスに失敗したことに気付きにくい。従って、解析のやり直しを開始する時期を遅らせることが可能となる。

【符号の説明】

【0070】

1 コンピュータシステム

2 ホスト機器

3 半導体記憶装置

12 変換部

13 加工部

14 送信部

21 受信部

23 制御部

24 記憶部

31 復元部

32 保持部

33 変換部

34 判定部

【特許請求の範囲】

【請求項1】

ホスト機器と、

前記ホスト機器に外部接続可能な半導体記憶装置と、

を備え、

前記ホスト機器は、

前記半導体記憶装置に送信するコマンドを所定の演算によって変換することにより、第1の変換値を生成する第1の生成部と、

前記第1の変換値及び前記コマンドを前記半導体記憶装置に送信する送信部と、

を有し、

前記半導体記憶装置は、

前記ホスト機器から前記半導体記憶装置へのアクセスを制御する制御部と、

前記第1の変換値及び前記コマンドを前記ホスト機器から受信する受信部と、

を有し、

前記制御部は、

前記受信部が受信した前記コマンドを前記所定の演算によって変換することにより、第2の変換値を生成する第2の生成部と、

前記受信部が受信した前記第1の変換値と、前記第2の生成部が生成した前記第2の変換値とが一致しない場合に、不正なアクセスと判定する判定部と、

を含む、コンピュータシステム。

【請求項2】

前記半導体記憶装置は、

前記半導体記憶装置が前記ホスト機器から受信する予定の前記第1の変換値を記憶する記憶部

をさらに有し、

前記判定部はさらに、前記受信部が受信した前記第1の変換値が、前記記憶部に記憶されている前記第1の変換値に一致しない場合に、不正なアクセスと判定する、請求項1に記載のコンピュータシステム。

【請求項3】

前記受信部が受信した前記第1の変換値が、前記記憶部に記憶されている前記第1の変換値に一致しない場合には、前記送信部は前記コマンドを送信しない、請求項2に記載のコンピュータシステム。

【請求項4】

前記ホスト機器は、

前記第1の変換値を表すデータ内の所定の箇所に不定値のデータを挿入することにより、前記第1の変換値を加工する加工部

をさらに有し、

前記制御部は、

前記受信部が受信した加工後の前記第1の変換値から、加工前の前記第1の変換値を復元する復元部

をさらに含む、請求項1〜3のいずれか一つに記載のコンピュータシステム。

【請求項5】

前記ホスト機器は、

前記コマンド内の所定の箇所に不定値のデータを挿入することにより、前記コマンドを加工する加工部

をさらに有し、

前記制御部は、

前記受信部が受信した加工後の前記コマンドから、加工前の前記コマンドを復元する復元部

をさらに含む、請求項1〜4のいずれか一つに記載のコンピュータシステム。

【請求項6】

前記送信部は、前記第1の変換値を送信した後に前記コマンドを送信し、

前記判定部はさらに、前記第1の変換値に関する送信時刻と前記コマンドに関する送信時刻との間の時間間隔が所定の許容範囲外である場合に、不正なアクセスと判定する、請求項1〜5のいずれか一つに記載のコンピュータシステム。

【請求項7】

前記第1の生成部は、予め規定された複数の演算のいずれかによって前記コマンドを変換することにより、前記第1の変換値を生成する、請求項1〜6のいずれか一つに記載のコンピュータシステム。

【請求項8】

前記判定部が不正なアクセスと判定した場合には、前記制御部は、前記ホスト機器に対する応答処理として、ダミーデータを返信する処理、エラーコードを返信する処理、及び何らのデータも返信しない処理のうちのいずれかを不定に選択して実行する、請求項1〜7のいずれか一つに記載のコンピュータシステム。

【請求項9】

ホスト機器に外部接続可能な半導体記憶装置であって、

前記ホスト機器から前記半導体記憶装置へのアクセスを制御する制御部と、

前記ホスト機器から、コマンドと、当該コマンドを所定の演算によって変換することにより生成された第1の変換値とを受信する受信部と、

を備え、

前記制御部は、

前記受信部が受信した前記コマンドを前記所定の演算によって変換することにより、第2の変換値を生成する生成部と、

前記受信部が受信した前記第1の変換値と、前記生成部が生成した前記第2の変換値とが一致しない場合に、不正なアクセスと判定する判定部と、

を有する、半導体記憶装置。

【請求項1】

ホスト機器と、

前記ホスト機器に外部接続可能な半導体記憶装置と、

を備え、

前記ホスト機器は、

前記半導体記憶装置に送信するコマンドを所定の演算によって変換することにより、第1の変換値を生成する第1の生成部と、

前記第1の変換値及び前記コマンドを前記半導体記憶装置に送信する送信部と、

を有し、

前記半導体記憶装置は、

前記ホスト機器から前記半導体記憶装置へのアクセスを制御する制御部と、

前記第1の変換値及び前記コマンドを前記ホスト機器から受信する受信部と、

を有し、

前記制御部は、

前記受信部が受信した前記コマンドを前記所定の演算によって変換することにより、第2の変換値を生成する第2の生成部と、

前記受信部が受信した前記第1の変換値と、前記第2の生成部が生成した前記第2の変換値とが一致しない場合に、不正なアクセスと判定する判定部と、

を含む、コンピュータシステム。

【請求項2】

前記半導体記憶装置は、

前記半導体記憶装置が前記ホスト機器から受信する予定の前記第1の変換値を記憶する記憶部

をさらに有し、

前記判定部はさらに、前記受信部が受信した前記第1の変換値が、前記記憶部に記憶されている前記第1の変換値に一致しない場合に、不正なアクセスと判定する、請求項1に記載のコンピュータシステム。

【請求項3】

前記受信部が受信した前記第1の変換値が、前記記憶部に記憶されている前記第1の変換値に一致しない場合には、前記送信部は前記コマンドを送信しない、請求項2に記載のコンピュータシステム。

【請求項4】

前記ホスト機器は、

前記第1の変換値を表すデータ内の所定の箇所に不定値のデータを挿入することにより、前記第1の変換値を加工する加工部

をさらに有し、

前記制御部は、

前記受信部が受信した加工後の前記第1の変換値から、加工前の前記第1の変換値を復元する復元部

をさらに含む、請求項1〜3のいずれか一つに記載のコンピュータシステム。

【請求項5】

前記ホスト機器は、

前記コマンド内の所定の箇所に不定値のデータを挿入することにより、前記コマンドを加工する加工部

をさらに有し、

前記制御部は、

前記受信部が受信した加工後の前記コマンドから、加工前の前記コマンドを復元する復元部

をさらに含む、請求項1〜4のいずれか一つに記載のコンピュータシステム。

【請求項6】

前記送信部は、前記第1の変換値を送信した後に前記コマンドを送信し、

前記判定部はさらに、前記第1の変換値に関する送信時刻と前記コマンドに関する送信時刻との間の時間間隔が所定の許容範囲外である場合に、不正なアクセスと判定する、請求項1〜5のいずれか一つに記載のコンピュータシステム。

【請求項7】

前記第1の生成部は、予め規定された複数の演算のいずれかによって前記コマンドを変換することにより、前記第1の変換値を生成する、請求項1〜6のいずれか一つに記載のコンピュータシステム。

【請求項8】

前記判定部が不正なアクセスと判定した場合には、前記制御部は、前記ホスト機器に対する応答処理として、ダミーデータを返信する処理、エラーコードを返信する処理、及び何らのデータも返信しない処理のうちのいずれかを不定に選択して実行する、請求項1〜7のいずれか一つに記載のコンピュータシステム。

【請求項9】

ホスト機器に外部接続可能な半導体記憶装置であって、

前記ホスト機器から前記半導体記憶装置へのアクセスを制御する制御部と、

前記ホスト機器から、コマンドと、当該コマンドを所定の演算によって変換することにより生成された第1の変換値とを受信する受信部と、

を備え、

前記制御部は、

前記受信部が受信した前記コマンドを前記所定の演算によって変換することにより、第2の変換値を生成する生成部と、

前記受信部が受信した前記第1の変換値と、前記生成部が生成した前記第2の変換値とが一致しない場合に、不正なアクセスと判定する判定部と、

を有する、半導体記憶装置。

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【公開番号】特開2012−243047(P2012−243047A)

【公開日】平成24年12月10日(2012.12.10)

【国際特許分類】

【出願番号】特願2011−111992(P2011−111992)

【出願日】平成23年5月19日(2011.5.19)

【出願人】(591128453)株式会社メガチップス (322)

【Fターム(参考)】

【公開日】平成24年12月10日(2012.12.10)

【国際特許分類】

【出願日】平成23年5月19日(2011.5.19)

【出願人】(591128453)株式会社メガチップス (322)

【Fターム(参考)】

[ Back to top ]