コンピュータ・システム

【課題】 マスタ・デバイス、スレーブ・デバイスの種類や数を問わず適用できる汎用的でスケーラブルなアクセス保護機構を有するコンピュータ・システム及びその処理方法を提供する。

【解決手段】 ソフトウエア・プロセス番号に関連づけられた第1のプロセスIDを格納する第1のレジスタ111を有し、かつトランザクションを生成するときに、システム・バス上に第1のプロセスIDを送出するマスタ・デバイス110と、

アクセスを許可する第2のプロセスIDを保持し、かつ第1のプロセスIDと第2のプロセスIDとが所定の関係を満たすときに、トランザクションを受け入れるスレーブ・デバイス120とを有するコンピュータ・システム。

【解決手段】 ソフトウエア・プロセス番号に関連づけられた第1のプロセスIDを格納する第1のレジスタ111を有し、かつトランザクションを生成するときに、システム・バス上に第1のプロセスIDを送出するマスタ・デバイス110と、

アクセスを許可する第2のプロセスIDを保持し、かつ第1のプロセスIDと第2のプロセスIDとが所定の関係を満たすときに、トランザクションを受け入れるスレーブ・デバイス120とを有するコンピュータ・システム。

【発明の詳細な説明】

【技術分野】

【0001】

本発明はコンピュータ・システム及びコンピュータ・システムの処理方法に関し、特に、アクセス保護機構を備えたコンピュータ・システム及びコンピュータ・システムの処理方法に関する。

【背景技術】

【0002】

現在、PCなどの汎用コンピュータ・システムか、携帯電話やカーナビなどの組込みコンピュータ・システムかを問わず、コンピュータ・システムに要求される性能は増加し、要求される機能は複雑化している。

【0003】

高い要求性能を満たすため、マイクロプロセッサを介さずに高速データ転送を行うダイレクト・メモリ・アクセス・コントローラ(Direct Memory Access Controller、 以下、DMACという)を備えたり、複数のマイクロプロセッサやアクセラレータ(特定機能を高速に処理する専用ハードウェア)を備え並列動作させるシステムが増えている。

【0004】

また、複雑な機能を実現するため、マルチタスク・オペレーティング・システムの制御下で複数のソフトウェア・プロセス(以下、単にプロセスという)を並行動作させるシステムが普通になってきた。

【0005】

車載や医療向けの機器など高い信頼性が求められるコンピュータ・システム上で、複数のプロセスを並行動作させる場合、あるプロセスのソフトウェアに内在する論理バグやノイズによる誤動作などが原因となって発生する不正なアドレス空間へのアクセス(読み出しまたは書き込み)が他のプロセスの状態を破壊しないよう保護する機構(以下、単に保護機構という)を導入することが必須である。ここで、プロセスの状態とは、そのプロセスが使用するメモリの内容や周辺デバイスの状態(内部状態を含む)を意味する。

【0006】

既存のコンピュータ・システム及び既存のコンピュータ・システムの保護機構についての関連技術としては、特許文献として、特開平06−236300号公報(特許文献1)、特開平10−240623号公報(特許文献2)、特開平01−265341号公報(特許文献3)、特開昭63−029849号公報(特許文献4)、特開2007−011580号公報(特許文献5)、特表平11−501141号公報(特許文献6)等がある。

【0007】

また、非特許文献として、Infineon、 TC1767 User's Manual V1.0、インターネット<http://www.infineon.com/dgdl/TC1767_UM_V1.0.pdf?folderId=db3a3043156fd5730115b892639c0e97&fileId=db3a30431be39b97011bff530d517bcd>(非特許文献1)、標準技術集インターネット<URL:http://www.jpo.go.jp/shiryou/s_sonota/hyoujun_gijutsu/handoutai_ip/1-3-9.htm>(非特許文献2)、非特許文献1に同じ、p.11-73(非特許文献3)等がある。

【先行技術文献】

【特許文献】

【0008】

【特許文献1】特開平06−236300号公報

【特許文献2】特開平10−240623号公報

【特許文献3】特開平01−265341号公報

【特許文献4】特開昭63−029849号公報

【特許文献5】特開2007−011580号公報

【特許文献6】特表平11-501141号公報

【非特許文献】

【0009】

【非特許文献1】Infineon、 TC1767 User's Manual V1.0、インターネット<http://www.infineon.com/dgdl/TC1767_UM_V1.0.pdf?folderId=db3a3043156fd5730115b892639c0e97&fileId=db3a30431be39b97011bff530d517bcd>

【非特許文献2】標準技術集インターネット<URL:http://www.jpo.go.jp/shiryou/s_sonota/hyoujun_gijutsu/handoutai_ip/1-3-9.htm>

【非特許文献3】Infineon、 TC1767 User's Manual V1.0、インターネット<http://www.infineon.com/dgdl/TC1767_UM_V1.0.pdf?folderId=db3a3043156fd5730115b892639c0e97&fileId=db3a30431be39b97011bff530d517bcd> p.11-73

【発明の概要】

【発明が解決しようとする課題】

【0010】

既存の保護機構では、マスタ・デバイスがマイクロプロセッサであり、かつスレーブ・デバイスがメモリであるときはMMUやMPUといった汎用的な仕組みが用意されており、例えばメモリ容量が異なる構成においても同一の保護機構がそのまま使える。

【0011】

以下、マイクロプロセッサやDMACなどトランザクションを開始するデバイスをマスタ・デバイス、マスタ・デバイスが開始したトランザクションのアクセス対象をスレーブ・デバイスと呼ぶことにする。

【0012】

しかし、マスタ・デバイスがDMACであるか、もしくはスレーブ・デバイスが周辺デバイスである場合に一般的に用いられている許可ビット・レジスタ方式には汎用性が欠けており、例えば、周辺デバイスが追加された場合には許可ビットを追加して保護機構全体を再設計する必要がある。また、ほぼ必ず設計ごとに保護機構が異なりソフトウェア互換性がないため、制御ソフトウェアを変更する必要もある。

【0013】

このように許可ビット・レジスタ方式には汎用性に欠け、再利用性に難があるため、バスマスタの種類を問わず適用できる統一性を備え、スレーブ・デバイス数が変化しても適用できるスケーラビリティを兼ね備えた保護機構が求められている。

【0014】

本発明の目的は、上述した課題であるマスタ・デバイス、スレーブ・デバイスの種類や数を問わず適用できる汎用的でスケーラブルなアクセス保護機構を有するコンピュータ・システム及びその処理方法を提供することにある。

【課題を解決するための手段】

【0015】

本発明のコンピュータ・システムでは、ソフトウエア・プロセス番号に関連づけられた第1のプロセスIDを格納する第1のレジスタを有し、かつトランザクションを生成するときに、システム・バス上に第1のプロセスIDを送出するマスタ・デバイスと、

アクセスを許可する第2のプロセスIDを保持し、かつ第1のプロセスIDと第2のプロセスIDとが所定の関係を満たすときに、トランザクションを受け入れるスレーブ・デバイスとを有する。

【0016】

以下、メモリや入出力デバイスなどのアクセス対象のアドレスを指定してデータを読み書きするという一ひとまとまりの通信をトランザクションと呼ぶ。

【0017】

また、本発明のマスタ・デバイスでは、ソフトウエア・プロセス番号に関連づけられた第1のプロセスIDを格納する第1のレジスタを有するマスタ・デバイスと、アクセスを許可する第2のプロセスIDを保持するスレーブ・デバイスと、マスタ・デバイスとスレーブ・デバイスに接続されたシステム・バスとを有するコンピュータ・システムにおいて、トランザクションを生成するときに、システム・バス上に第1のプロセスIDを送出する。

【0018】

また、本発明のスレーブ・デバイスでは、ソフトウエア・プロセス番号に関連づけられた第1のプロセスIDを格納する第1のレジスタを有するマスタ・デバイスと、アクセスを許可する第2のプロセスIDを保持するスレーブ・デバイスと、マスタ・デバイスとスレーブ・デバイスに接続されたシステム・バスとを有するコンピュータ・システムにおいて、第1のプロセスIDと第2のプロセスIDとが所定の関係を満たすときに、トランザクションを受け入れる。

【0019】

また、本発明のコンピュータ・システムの処理方法では、ソフトウエア・プロセス番号に関連づけられた第1のプロセスIDを格納する第1のレジスタを有するマスタ・デバイスと、アクセスを許可する第2のプロセスIDを保持するスレーブ・デバイスと、マスタ・デバイスとスレーブ・デバイスに接続されたシステム・バスとを有するコンピュータ・システムの処理方法において、

マスタ・デバイスは、トランザクションを生成するときに、システム・バス上に第1のプロセスIDを送出し、

スレーブ・デバイスは、第1のプロセスIDと第2のプロセスIDとが所定の関係を満たすときに、トランザクションを受け入れる。

【発明の効果】

【0020】

本発明によれば、マスタ・デバイスやスレーブ・デバイスの種類や数を問わない汎用かつスケーラブルなアクセス保護機構が実現できる。

【図面の簡単な説明】

【0021】

【図1】本発明の実施の形態のコンピュータ・システムを示すブロック図である。

【図2】本発明の実施の形態のスレーブ・デバイスを示すブロック図である。

【図3】本発明の実施の形態のマイクロプロセッサとMPUを示すブロック図である。

【図4】本発明の実施の形態のDMACを示すブロック図である。

【図5】本発明の実施の形態のマスタ・デバイスの動作概略を示すフローチャートである。

【図6】本発明の実施の形態のマイクロプロセッサの動作概略を示すフローチャートである。

【図7】本発明の実施の形態のMPUの動作概略を示すフローチャートである。

【図8】既存のコンピュータ・システムを示すブロック図である。

【図9】既存のマイクロプロセッサとMPUを表すブロック図である。

【図10】既存のDMACを示すブロック図である。

【図11】既存のマスタ・デバイスの動作概略を示すフローチャートである。

【図12】既存のマイクロプロセッサの動作概略を示すフローチャートである。

【図13】既存のMPUの動作概略を示すフローチャートである。

【発明を実施するための形態】

【0022】

(既存のコンピュータ・システム)

まず、最初に、本発明の理解が容易になるように、既存のコンピュータ・システムとその保護機構を図8から13を参照しながら説明する。

【0023】

まず、既存のコンピュータ・システムのシステム・バス周辺の構造と動作を説明する。

【0024】

コンピュータ・システムのハードウェアは、ソフトウェアを実行するマイクロプロセッサ、ソフトウェアやデータを記憶するメモリ、周辺デバイスなどから構成されている。ここで周辺デバイスとは入出力デバイスやアクセラレータなどを意味する。

【0025】

図8に示すように、これらのコンピュータ・システムの構成要素間では、システム・バス経由でデータのアクセス(読み出しまたは書き込み)が行われる。システム・バスはアクセス先のアドレスを指定するアドレス・バス803、アドレス・バスで指定されたアドレスに位置するデータを転送するデータ・バス801、アクセスの種類を指定するなどの管理を行うための制御バス802などから成る。

【0026】

ここで、上述のように、メモリや入出力デバイスなどのアクセス対象のアドレスを指定してデータを読み書きするという一ひとまとまりの通信をトランザクションと呼ぶ。また、マイクロプロセッサやDMACなどトランザクションを開始するデバイスをマスタ・デバイス810、マスタ・デバイスが開始したトランザクションのアクセス対象をスレーブ・デバイス820と呼ぶ。

【0027】

マスタ・デバイス、スレーブ・デバイスとはシステム・バス上での機能を表しているため、デバイスによっては両方の機能を備える場合がある。例えば、DMACはスレーブ・デバイスとしてマクロプロセッサから初期設定された後、マスタ・デバイスとしての動作を開始し、他のスレーブ・デバイス(周辺デバイスやメモリ等)をアクセスする。

【0028】

次に、トランザクションの手順の概略を図11に示す。

【0029】

まず、マスタ・デバイス810は、トランザクションを開始すると(ステップ1101)、アクセス先アドレスをアドレス・バス803に出力する(ステップ1102)。

【0030】

次に、トランザクションの種類を判定し(ステップ1103)、それがデータ読み出しの場合、マスタ・デバイス810は、このトランザクションがデータ読み出しであることを示す制御信号を制御バス802に出力する(ステップ1104)。

【0031】

最後に、マスタ・デバイス810は、アクセス対象のスレーブ・デバイス820がデータ・バス801上に出力したデータを取得する(ステップ1105)。

【0032】

または、トランザクションの種類がデータ書き込みの場合、マスタ・デバイス810が書き込みデータをデータ・バス801に出力する(ステップ1106)。

【0033】

最後に、マスタ・デバイス810は、このトランザクションがデータ書き込みであることを示す制御信号を制御バス802に出力する(ステップ1107)。

【0034】

既存のスレーブ・デバイスの動作を、周辺デバイスを例にとり説明する。既存の周辺デバイスはシステム・バスに接続され、マスタ・デバイス810が開始したトランザクションの対象アドレスをアドレス・デコーダで比較し、自身のアドレスと一致した場合にトランザクションの対象として選択され、例えば、周辺デバイスの内部レジスタのアクセスを許可する。

【0035】

次に、既存のコンピュータ・システムの保護機構について説明する。

【0036】

既存技術では、マスタ・デバイスとスレーブ・デバイスの組み合わせによって異なる保護機構が用いられてきた。

【0037】

マスタ・デバイスがマイクロプロセッサで、スレーブ・デバイスがメモリの場合、保護機構としてメモリ・プロテクション・ユニット(Memory Protection Unit、 以下MPUという)かメモリ・マネージメント・ユニット(Memory Management Unit、 以下MMUという)が導入されることが多い。

【0038】

MPUは特定のプロセスに対し決められたメモリ範囲のみアクセスを許可することで、あるプロセスの状態を他のプロセスから参照・変更できないようにする保護機構である。MPUは低コストな組込みマイクロプロセッサで採用されることが多い。既存のMPUの例としては上記特許文献1、特許文献2に挙げたようなものがある。

【0039】

既存の典型的なMPUの構成を図9を参照しながら説明する。

【0040】

既存のマイクロプロセッサ910は、システム・バスに接続され、MPU920によって保護されたメモリ930上のプログラムを実行したり、メモリ930や周辺デバイス上のデータをアクセスするためバス・トランザクションを生成する。

【0041】

図12にマイクロプロセッサ910がバス・トランザクションを生成する手順を示す。

【0042】

最初に、バス・トランザクション生成の目的を判定し(ステップ1202)、プログラム実行のために、次に実行する機械語命令を取得することが目的であれば、バス・インターフェース・ユニット(Bus Interface Unit、 以下BIUという)911は、その命令の位置を示すプログラム・カウンタ(Program Counter、 以下PCという)913の値をアドレス・バスに出力する(ステップ1203)。

【0043】

あるいは、データ・アクセスが目的であれば、汎用レジスタや命令語中の即値をもとにアドレス・ジェネレータ(Address Generator、以下AGという)912が生成したアクセス先のアドレス値をシステム・バスに出力する(ステップ1204)。

【0044】

以降の手順(ステップ1205からステップ1209)は図11と同様である。

【0045】

MPU920はシステム・バスとメモリ930の間に位置し、上限アドレス・レジスタ922と下限アドレス・レジスタ923を持つ。

【0046】

次に、MPUの動作を図13に示す。

【0047】

トランザクション発生時、MPU920はシステム・バス上のアドレス・バス903上の値と上限アドレス・レジスタ922、下限アドレス・レジスタ923の値を比較器921で比較し、アドレス・バス上の値が下限アドレス・レジスタの値以上で(ステップ1302)、上限アドレス・レジスタの値以下のとき(ステップ1303)、メモリへのアクセスを許可し(ステップ1304)、それ以外の場合は許可しない(ステップ1305)。

【0048】

MPU920はメモリ930の内容をきめ細かく保護できるように、上限アドレス・レジスタ922と下限アドレス・レジスタ923の組を複数持つことがある。あるいは、上記特許文献3に示すように、ソフトウェアがプロセスIDをMPU920に明示的に書き込むことにより、上限アドレス・レジスタ922と下限アドレス・レジスタ923の組を選択する機構を持ち、プロセスごとに独立した保護領域を持てるようにした例がある。あるいは、アクセスを許可するメモリ領域の上下限アドレスを設定するのではなく、アクセスを禁止するメモリ領域の上下限アドレスを設定する実装もあり得る。

【0049】

汎用プロセッサ(x86、MIPS、PowerPC、SPARCなど)では、マスタ・デバイスがマイクロプロセッサで、スレーブ・デバイスがメモリの場合、保護機構としてMMUが導入されることが多い(非特許文献2)。

【0050】

MMUでは、論理メモリ空間を4Kバイトなどのページ単位に分割し、ページごとに対応する物理メモリのアドレスやアクセス許可属性を設定する。これらの設定を納めたテーブルは各プロセス別に主記憶メモリ上に用意されるが、マイクロプロセッサはこのテーブルの一部を、高速化のためにマイクロプロセッサ内部のトランスレーション・ルックアサイド・バッファ(Translation Lookaside Buffer、 以下TLBという)にキャッシュして利用する。

【0051】

マスタ・デバイスがマイクロプロセッサで、スレーブ・デバイスが周辺デバイスの場合、周辺デバイスごとにアクセス許可・不許可を設定するビットマップを格納するレジスタを用いる方式の保護機構(以下、許可ビット・レジスタ方式という)がある。通常、固定アドレスに割り付けられ、小さいアドレス空間(数十バイト程度)を占有するという周辺デバイスの特性から、MMUまたはMPUによる保護機構より許可ビット・レジスタ方式が適している。

【0052】

他の、より汎用的な方法としては、I/Oアドレス1バイトごとに1ビットの許可ビット・テーブルを主記憶上に持つ方式がある(特許文献4)。ただし、アクセスごとに上記テーブルを参照するため、効率が悪いという問題がある。

【0053】

マスタ・デバイスが周辺デバイスの場合、許可ビット・レジスタ方式をメモリにも拡張した方式が用いられることがある。固定的なメモリ領域や周辺デバイスごとにアクセス許可・不許可を設定するビットマップを格納するレジスタを用いた例がある(非特許文献3)。

【0054】

既存の保護機構では、マスタ・デバイスがマイクロプロセッサであり、かつスレーブ・デバイスがメモリであるときはMMUやMPUといった汎用的な仕組みが用意されており、例えば、メモリ容量が異なる構成においても同一の保護機構がそのまま使える。

【0055】

しかし、マスタ・デバイスがDMACであるか、もしくはスレーブ・デバイスが周辺デバイスである場合に一般的に用いられている許可ビット・レジスタ方式には汎用性が欠けており、例えば、周辺デバイスが追加された場合には許可ビットを追加して保護機構全体を再設計する必要がある。また、ほぼ必ず設計ごとに保護機構が異なりソフトウェア互換性がないため、制御ソフトウェアを変更する必要もある。

【0056】

このように許可ビット・レジスタ方式には汎用性に欠け、再利用性に難があるため、バスマスタの種類を問わず適用できる統一性を備え、スレーブ・デバイス数が変化しても適用できるスケーラビリティを兼ね備えた保護機構が求められている。

【0057】

本発明の実施の形態は、コンピュータ・システムにおいて、マスタ・デバイス、スレーブ・デバイスの種類や数を問わず適用できる、汎用的でスケーラブルなアクセス保護機構を提供する。

【0058】

このため、本発明の実施の形態では、マスタ・デバイスは現在実行中のソフトウェアのプロセスID値を格納するレジスタを備え、システム・バス上にトランザクションを生成するとき、アクセス先アドレスと同時にプロセスIDを送出する。ターゲット・デバイスはアクセスを許可するプロセスIDを格納するレジスタを備え、プロセスIDが一致するトランザクションのみ受け入れる。

【0059】

(本発明の実施の形態)

次に、本発明の実施の形態について図を参照して説明する。

【0060】

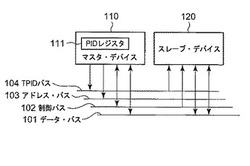

最初に、第1の実施の形態として、図1を参照しながら、本発明のコンピュータ・システムのマスタ・デバイスの動作を説明する。

【0061】

本発明のシステム・バスはアクセス先のアドレスを指定するアドレス・バス103、アドレス・バス103で指定されたアドレスに位置するデータを転送するデータ・バス101、アクセスの種類を指定するなどの管理を行うための制御バス102に加えトランザクション・プロセス識別子(Transaction Process Identifier)・バス(以下、TPIDバスという)104から成る。

【0062】

本発明の実施の形態のシステム・バスに接続されるマスタ・デバイス110はプロセス識別子(Process Identifier)・レジスタ111(以下、PIDレジスタという)を持つ。

【0063】

システム・バス上に接続されたマスタ・デバイス110がトランザクションを生成し、スレーブ・デバイス120をアクセスする手順を図5に示す。

【0064】

まず、マスタ・デバイス110は、トランザクションを開始すると(ステップ501)、アクセス先アドレスをアドレス・バス103に出力(ステップ502)し、PIDレジスタ111の値をTPIDバス104に出力する(ステップ503)。

【0065】

次に、トランザクションの種類を判定し(ステップ504)、それがデータ読み出しの場合、マスタ・デバイス110は、このトランザクションがデータ読み出しであることを示す制御信号を制御バス102に出力する(ステップ505)。

【0066】

最後に、マスタ・デバイス110は、アクセス対象のスレーブ・デバイス120がデータ・バス101上に出力したデータを取得する(ステップ506)。

【0067】

また、トランザクションの種類がデータ書き込みの場合、マスタ・デバイス110が書き込みデータをデータ・バス101に出力する(ステップ507)。

【0068】

最後に、マスタ・デバイス110は、このトランザクションがデータ書き込みであることを示す制御信号を制御バスに出力する(ステップ508)。

【0069】

これらの手順は典型的なバス・トランザクションの概略を例として示したもので、準拠するバスプロトコルによっては、アドレス、データ、制御信号、TPIDの出力順序が前後する場合がある。バスの利用権調停や、トランザクションの延長やキャンセル、その他の付加機能のための制御が追加される場合もある。

【0070】

次に、本発明の第2の実施の形態として、図2を参照しながら、もっとも単純なスレーブ・デバイスとして、固定アドレスに割り付けられた周辺デバイス(入出力デバイスなど)の例を説明する。

【0071】

本発明の第2の実施の形態のスレーブ・デバイス210中の比較器212は、トランザクション中にマスタ・デバイスがTPIDバス204に出力した値と、スレーブ・デバイス210自身が持つTPIDレジスタ211の値を比較し、一致したときのみ許可信号をデコーダ213に通知する。

【0072】

デコーダ213はトランザクション中にマスタ・デバイスがアドレス・バス203に出力したアドレス値が、スレーブ・デバイスが割り付けられたアドレス範囲に含まれ、かつ比較器212から許可信号が通知されているとき、そのトランザクションに正常に応答することを決定し、内部レジスタ214へのアクセスを許可する等の動作を行う。

【0073】

次に、図3を参照しながら、本発明の実施の形態の保護機構を持つバスマスタ・デバイスとしてマイクロプロセッサ、本発明の実施の形態の保護機構を持つスレーブ・デバイスとしてMPUを備えたメモリの動作を説明する。

【0074】

本発明の実施の形態の保護機構を持つマイクロプロセッサ310は、次に実行する機械語命令の位置を示すプログラム・カウンタ(Program Counter、 以下、PCという)313、データ・アクセス対象のアドレスを生成するアドレス・ジェネレータ(Address Generator、 以下、AGという)312、現在実行中のプロセス番号に関連づけられた値を格納するPIDレジスタ314を持つ。

【0075】

次に、本発明の実施の形態のマイクロプロセッサ310がトランザクションを生成する手順を図6に示す。

【0076】

バス・トランザクション生成の目的を判定し(ステップ602)、プログラム実行のために、次に実行する機械語命令を取得することが目的であれば、バス・インターフェース・ユニット(Bus Interface Unit、 以下、BIUという)311は、その命令の位置を示すPC313の値をアドレス・バス303に出力(ステップ603)するとともに、PIDレジスタ314の値をTPIDバス304に出力する(ステップ604)。

【0077】

また、データ・アクセスが目的であれば、AG312が生成したアクセス先のアドレス値をシステム・バスに出力(ステップ605)するとともに、PIDレジスタ314の値をTPIDバス304に出力する(ステップ606)。

【0078】

以降の手順(ステップ605からステップ611)は図5のステップ504からステップ508と同様である。

【0079】

次に、本発明の第3の実施の形態として、本発明の実施の形態のマスタ・デバイスの別の例であるDMACについて、図4を参照しながら説明する。

【0080】

DMACは、初期設定後はマイクロプロセッサ上のソフトウェアの介在なしに、自律的に高速なデータ転送を行う機構である。

【0081】

ここで、本発明の第3の実施の形態の理解を容易にするために、既存のDMACの例を図10に示す。

【0082】

これは1970年代から使われているIntel8257の主要部分を抜き出したものである。このDMACは転送元アドレス・レジスタ1012、転送先アドレス・レジスタ1013、転送回数レジスタ1014を持つ。これらのレジスタの値はマイクロプロセッサ上のソフトウェアにより初期設定される。

【0083】

既存のDMACによるトランザクションの例として、転送元が周辺デバイスで転送先がメモリである場合を考える。この場合、転送元の周辺デバイスからの専用信号線の指示によりDMAが開始される。

【0084】

まず、DMAC1010はマスタ・デバイスとして動作し、バス・インターフェース・ユニット(Bus Interface Unit、 以下、BIUという)1011は転送元アドレス・レジスタ1012の値をアドレス・バス1003に出力して周辺デバイスにデータ読み出しを要求することにより、トランザクションを開始する。周辺デバイスから読み出されたデータはDMAC1010内部の転送データ・レジスタ1015に書き込まれる。

【0085】

次に、再度、DMAC1010はマスタ・デバイスとして動作し、転送先アドレス・レジスタ1013の値をBIU1011経由でアドレス・バス1003に、転送データ・レジスタ1015の値をデータ・バス1001に出力することで、メモリへの書き込みトランザクションを開始する。

【0086】

メモリへの書き込みトランザクション終了後、転送先アドレス・レジスタ1013の値は更新される。以上の操作を転送回数レジスタ1014に設定された回数だけ繰り返す。DMAC1010には通常、種々の動作モードや動作タイミングの設定、ステータス通知のためのレジスタや信号端子が存在するが、以上の説明では簡単のために省略してある。

【0087】

次に、図4を参照して、本発明の実施の形態の保護機構を持つDMACを示す。

【0088】

本発明のDMAC410は、転送元アドレス・レジスタ412、転送先アドレス・レジスタ413、転送回数レジスタ414に加え、TPIDレジスタ416を持つ。これらのレジスタの値はマイクロプロセッサ上のソフトウェアにより初期設定される。

【0089】

本発明の実施の形態のDMACによるトランザクションの例として、転送元が周辺デバイスで転送先がメモリである場合を考える。この場合、転送元の周辺デバイスからの通知によりDMAが開始される。通知の手段としては、周辺デバイスからDMACへの専用信号線を敷設する等が考えられる。

【0090】

まず、DMAC410はマスタ・デバイスとして動作し、BIU411は転送元アドレス・レジスタ412の値をアドレス・バス403に、TPIDレジスタ416の値をTPIDバス404に出力して周辺デバイスにデータ読み出しを要求することにより、トランザクションを開始する。周辺デバイスから読み出されたデータはDMAC410内部の転送データ・レジスタ415に書き込まれる。

【0091】

次に、再度、DMAC410はマスタ・デバイスとして動作し、転送先アドレス・レジスタ413の値をアドレス・バス403に、転送データ・レジスタ415の値をデータ・バス401に、TPIDレジスタ416の値をTPIDバス404に出力することで、メモリへの書き込みトランザクションを開始する。

【0092】

メモリへの書き込みトランザクション終了後、転送先アドレス・レジスタ413の値は更新される。以上の操作を転送回数レジスタ414に設定された回数だけ繰り返す。

【0093】

なお、本発明の実施の形態は、DMAC410の実装細部の差異を問わず一般的に適用できる。例えば、図4では、簡単のためにDMAチャネル数が1であるとして説明したが、複数のDMAチャネルを持つDMACでも同様の議論が可能である。複数のDMAチャネルを持つとき、全DMAチャネルで共通のTPIDレジスタ416を持つ構成、チャネルごとに独立したTPIDレジスタ416を持つ構成が考えられる。また、図4では、転送先のメモリ領域を、転送先アドレス・レジスタ413と転送回数レジスタ414により示すとしたが、転送先開始アドレス・レジスタと転送先終了アドレス・レジスタにより示すこともできる。

【0094】

さらに、図4では、データを転送データ・レジスタ415経由で転送する構成としたが、周辺デバイスからメモリに直接データ転送する構成も考えられる。

【0095】

また、TPIDレジスタ416の値を、データ転送元向けとデータ転送先向けに、独立して持つ構成も考えられる。

【0096】

また、図4において、TPIDレジスタ416の値はマイクロプロセッサ上のソフトウェアが初期設定するとしたが、別の構成では、マイクロプロセッサがDMAC410上のレジスタ(転送元アドレス・レジスタ、転送先アドレス・レジスタ、転送回数レジスタ、モード設定レジスタ、コマンド・レジスタ、ステータス・レジスタ等)のうちいずれかをアクセスしたときの、TPIDバス404上の値を自動取得する構成も可能である。

【0097】

以上の説明ではDMAC410の初期設定はマイクロプロセッサ上のソフトウェアが行うとしたが、マイクロプロセッサと共有するメモリまたはDMACが持つ専用メモリ上に置かれたマイクロ・プログラム(デスクリプタと呼ばれることもある)をDMACが直接解釈することによって設定する構成も可能である。

【0098】

DMAC410の内部レジスタ群を図2に示したスレーブ・デバイスとして扱い、保護機構で守ることが可能である。図4に示したDMAC410では、マイクロプロセッサ上のソフトウェアが、転送元アドレス・レジスタ412、転送先アドレス・レジスタ413、転送回数レジスタ414、TPIDレジスタ416を初期設定するとした。これらのレジスタの初期設定中は、DMAC410はスレーブ・デバイスとして動作しており、バスマスタ・デバイスとして動作しているマイクロプロセッサからのアクセスを受け入れている。そのため、図2に示したように、スレーブ・デバイスとしてのTPIDレジスタを持ちこれらのレジスタを保護することが可能である。

【0099】

図4に関する議論はバスマスタ機能を持つ周辺デバイスに一般的に適用できる。

【0100】

本発明の保護機構を持つバスマスタ・デバイスは、アクセス先のメモリ・アドレスの値をアドレス・バスに、TPIDレジスタの値をTPIDバスに、その他必要な信号をシステム・バスに出力することでメモリへのトランザクションを開始する。

【0101】

次に、本発明の第4の実施の形態として、本発明の実施の形態の保護機構を備えたスレーブ・デバイスの例であるMPUについて、再度図3を参照しながら説明する。

【0102】

このMPU320はシステム・バスとメモリ330の間に位置し、既存のMPU(図9)が持つ上限アドレス・レジスタ322と下限アドレス・レジスタ323に加えTPIDレジスタ324を持つ。

【0103】

次に、MPU320の動作を図7に示す。

【0104】

トランザクション発生時、MPU320はシステム・バス上のアドレス・バス303上の値と上限アドレス・レジスタ322、下限アドレス・レジスタ323の値を比較器321で比較し、アドレス・バス上の値が下限アドレス・レジスタの値以上で(ステップ702)、上限アドレス・レジスタの値以下で(ステップ703)、かつTPIDバス304上の値がTPIDレジスタ324と一致したとき(ステップ704)のみメモリへのアクセスを許可し(ステップ705)、それ以外の場合は許可しない(ステップ706)。

【0105】

トランザクション発生時、MPU320はシステム・バス上のアドレス・バス303の値と上限アドレス・レジスタ322、下限アドレス・レジスタ323の値を比較し、アドレス・バス303の値が上限アドレス・レジスタの値以下で、下限アドレス・レジスタの値以上のとき、メモリへのアクセスを許可し、それ以外の場合は遮断する。

【0106】

既存のMPUでも、単一バスマスタ・システムであれば、プロセス切り替え時にMPUのレジスタ(上限アドレス・レジスタ、下限アドレス・レジスタ等)を入れ替えれば、他のプロセスの不正アクセスから保護できる。しかし、この方式ではプロセス切替時に、MPUレジスタ入替が必要になるためプロセス切替時間が長くなり、リアルタイム・システムに適さないという問題がある。

【0107】

また、今後主流になるであろうマルチプロセッサ・システム、または1個以上のマイクロプロセッサと1個以上のバスマスタ機能を持つアクセラレータを持つコンピュータ・システムでは、生成したプロセスが異なるトランザクションがシステム・バス上で細粒度で混在することになり、既存のMPUでは対応できなくなるが、本発明の実施の形態のMPU320(図3)では保護が可能である。

【0108】

本発明の実施の形態によれば、マスタ・デバイスやスレーブ・デバイスの種類によらず、アクセス保護を実現できる。例えば、マスタ・デバイスがマイクロプロセッサであっても、DMACやアクセラレータのような周辺デバイスであっても、スレーブ・デバイスがメモリであっても入出力デバイスのような周辺デバイスであっても、同一の機構でアクセス保護が行える。

【0109】

また、本発明の実施の形態によれば、システム・バス上に接続されるマスタ・デバイスやスレーブ・デバイスの数によらず同一の機構が行える。例えば、マイクロプロセッサが複数個存在する場合でも同一のアクセス保護機構で対応できる。また、スレーブ・デバイスの数が増加しても、既存部分の設計変更を行う必要がない。

【0110】

このように、本発明の実施の形態によればマスタ・デバイスやスレーブ・デバイスの種類や数を問わない、汎用かつスケーラブルなアクセス保護機構が実現できる。

【0111】

以上、本発明の実施の形態について具体的に説明したが、本発明は上述の実施形態に限定されるものではなく、本発明技術的思想に基づく各種の変形が可能である。

【0112】

例えば、マイクロプロセッサ310のPIDレジスタ314(図3)には、マイクロプロセッサ310上で動作するオペレーティング・システムが、現在実行中のソフトウェア・プロセスの番号をそのまま設定する構成、または、そのソフトウェア・プロセスに関連づけた値を設定する構成が可能である。後者の場合、マスタ・デバイスのPIDレジスタ、TPIDバス、スレーブ・デバイスのTPIDレジスタや比較器などのビット長を、同時にアクティブとなるプロセス数をカバーするのに充分な長さにまで削減できる。

【0113】

また、システム・バス上でTPIDバス104が専用の信号線で実現されているとしたが、ひとつのトランザクションにひとつのTPID値が付与されていれば、システム・バス実装の細部は問わない。例えば、物理的に同じ信号線を用い、時分割多重によりアドレス値とTPID値を伝達するシステム・バス構成も可能である。

【0114】

また、ひとつのスレーブ・デバイス210はひとつのTPIDレジスタ211(図2)を持つとした。しかし、ひとつのスレーブ・デバイス210が複数のTPIDレジスタ211を持ち、TPIDバス204上の値がいずれかのTPIDレジスタ211の値と一致したときにそのスレーブ・デバイス210にアクセスを許可する構成も可能である。また、ひとつのスレーブ・デバイス210が機能別に複数のTPIDレジスタ211を持ち、機能別に細かくアクセスを制御する構成も可能である。

【0115】

また、TPIDバス204上の値がスレーブ・デバイス210のTPIDレジスタ211の値と一致することをアクセス許可条件としたが、他の比較条件をアクセス許可条件とする構成も可能である。例えば、TPIDバス204上の値がスレーブ・デバイス210のTPIDレジスタ211の値より大きいとき、大きいか等しいとき、小さいとき、小さいか等しいときにアクセスを許可する構成も可能である。

【0116】

また、スレーブ・デバイス210はTPIDバス204上の値とTPIDレジスタ211の値を比較した結果に基づきアクセス許可するとしたが、TPIDレジスタ211を持たず固定値と比較した結果に基づきアクセス許可する構成も可能である。

【0117】

例えば、マイクロプロセッサが特権モード状態にあることをTPIDの特定値で示し、スレーブ・デバイス210はその特定のTPID値でのアクセスを許可する構成も可能である。さらに、TPIDバス204上の値と固定値との比較結果、TPIDバス204上の値とTPIDレジスタ211の値の比較結果の双方を勘案し、アクセスを許可する構成も可能である。

【0118】

また、スレーブ・デバイス210は、自身が割り付けられたアドレスとアドレス・バス203上の値を比較するデコーダ213と、TPIDレジスタ211の値とTPIDバス204上の値を比較する比較器212を別に持つとしたが、これらの働きは似ているため、デコーダ213と比較器212を一体化した構成も可能である。

【0119】

また、デコーダ213と比較器212をスレーブ・デバイス210ごとに持つとしたが、複数のスレーブ・デバイスのデコーダと比較器の一部もしくは全部を一体化した集中制御型の構成も可能である。さらにマスタ・デバイスのPIDレジスタも一体化した構成も可能である。

【0120】

また、メモリの保護機構としてMPUを取り上げ、TPIDによる保護機構を説明したが、メモリの保護機構としてMMUを採用する本発明の保護機構も可能である。MMUを備えるマイクロプロセッサは、通常PIDレジスタを持ち、TLBのヒット率向上のために内部的に利用しているので、そのPIDレジスタの値をシステム・バスに取り出すだけで本発明の保護機構を備えたマスタ・デバイスとすることができる。

【0121】

実際のコンピュータ・システムでは、マイクロプロセッサは図3の基本的な構成要素に加え、高速化や低電力化のために数々のキャッシュ機構、予測機構を備えているため、次に実行する機械語命令のアドレスを示すPC値だけでなく、さらに将来のPC値を予測した値がアドレス・バスに出力されることがある。このときのTPIDバスには、予測の元となったPC値が属するプロセス番号に関連づけた値を出力する。

【符号の説明】

【0122】

101 データ・バス

102 制御バス

103 アドレス・バス

104 TPIDバス

110 マスタ・デバイス

111 PIDレジスタ

120 スレーブ・デバイス

201 データ・バス

202 制御バス

203 アドレス・バス

204 TPIDバス

210 スレーブ・デバイス

211 TPIDレジスタ

212 比較器

213 デコーダ

214 内部レジスタ

301 データ・バス

302 制御バス

303 アドレス・バス

304 TPIDバス

310 マイクロプロセッサ

311 BIU

312 AG

313 PC

314 PIDレジスタ

320 MPU

321 比較器

322 上限アドレス・レジスタ

323 下限アドレス・レジスタ

324 TPIDレジスタ

330 メモリ

331 デコーダ

341 許可信号

401 データ・バス

402 制御バス

403 アドレス・バス

404 TPIDバス

410 DMAC

411 BIU

412 転送元アドレス・レジスタ

413 転送先アドレス・レジスタ

414 転送回数・レジスタ

415 転送データ・レジスタ

416 TPIDレジスタ

801 データ・バス

802 制御バス

803 アドレス・バス

810 マスタ・デバイス

820 スレーブ・デバイス

901 データ・バス

902 制御バス

903 アドレス・バス

910 マイクロプロセッサ

911 BIU

912 AG

913 PC

920 MPU

921 比較器

922 上限アドレス・レジスタ

923 下限アドレス・レジスタ

930 メモリ

931 デコーダ

941 許可信号

1001 データ・バス

1002 制御バス

1003 アドレス・バス

1010 DMAC

1011 BIU

1012 転送元アドレス・レジスタ

1013 転送先アドレス・レジスタ

1014 転送回数・レジスタ

1015 転送データ・レジスタ

【技術分野】

【0001】

本発明はコンピュータ・システム及びコンピュータ・システムの処理方法に関し、特に、アクセス保護機構を備えたコンピュータ・システム及びコンピュータ・システムの処理方法に関する。

【背景技術】

【0002】

現在、PCなどの汎用コンピュータ・システムか、携帯電話やカーナビなどの組込みコンピュータ・システムかを問わず、コンピュータ・システムに要求される性能は増加し、要求される機能は複雑化している。

【0003】

高い要求性能を満たすため、マイクロプロセッサを介さずに高速データ転送を行うダイレクト・メモリ・アクセス・コントローラ(Direct Memory Access Controller、 以下、DMACという)を備えたり、複数のマイクロプロセッサやアクセラレータ(特定機能を高速に処理する専用ハードウェア)を備え並列動作させるシステムが増えている。

【0004】

また、複雑な機能を実現するため、マルチタスク・オペレーティング・システムの制御下で複数のソフトウェア・プロセス(以下、単にプロセスという)を並行動作させるシステムが普通になってきた。

【0005】

車載や医療向けの機器など高い信頼性が求められるコンピュータ・システム上で、複数のプロセスを並行動作させる場合、あるプロセスのソフトウェアに内在する論理バグやノイズによる誤動作などが原因となって発生する不正なアドレス空間へのアクセス(読み出しまたは書き込み)が他のプロセスの状態を破壊しないよう保護する機構(以下、単に保護機構という)を導入することが必須である。ここで、プロセスの状態とは、そのプロセスが使用するメモリの内容や周辺デバイスの状態(内部状態を含む)を意味する。

【0006】

既存のコンピュータ・システム及び既存のコンピュータ・システムの保護機構についての関連技術としては、特許文献として、特開平06−236300号公報(特許文献1)、特開平10−240623号公報(特許文献2)、特開平01−265341号公報(特許文献3)、特開昭63−029849号公報(特許文献4)、特開2007−011580号公報(特許文献5)、特表平11−501141号公報(特許文献6)等がある。

【0007】

また、非特許文献として、Infineon、 TC1767 User's Manual V1.0、インターネット<http://www.infineon.com/dgdl/TC1767_UM_V1.0.pdf?folderId=db3a3043156fd5730115b892639c0e97&fileId=db3a30431be39b97011bff530d517bcd>(非特許文献1)、標準技術集インターネット<URL:http://www.jpo.go.jp/shiryou/s_sonota/hyoujun_gijutsu/handoutai_ip/1-3-9.htm>(非特許文献2)、非特許文献1に同じ、p.11-73(非特許文献3)等がある。

【先行技術文献】

【特許文献】

【0008】

【特許文献1】特開平06−236300号公報

【特許文献2】特開平10−240623号公報

【特許文献3】特開平01−265341号公報

【特許文献4】特開昭63−029849号公報

【特許文献5】特開2007−011580号公報

【特許文献6】特表平11-501141号公報

【非特許文献】

【0009】

【非特許文献1】Infineon、 TC1767 User's Manual V1.0、インターネット<http://www.infineon.com/dgdl/TC1767_UM_V1.0.pdf?folderId=db3a3043156fd5730115b892639c0e97&fileId=db3a30431be39b97011bff530d517bcd>

【非特許文献2】標準技術集インターネット<URL:http://www.jpo.go.jp/shiryou/s_sonota/hyoujun_gijutsu/handoutai_ip/1-3-9.htm>

【非特許文献3】Infineon、 TC1767 User's Manual V1.0、インターネット<http://www.infineon.com/dgdl/TC1767_UM_V1.0.pdf?folderId=db3a3043156fd5730115b892639c0e97&fileId=db3a30431be39b97011bff530d517bcd> p.11-73

【発明の概要】

【発明が解決しようとする課題】

【0010】

既存の保護機構では、マスタ・デバイスがマイクロプロセッサであり、かつスレーブ・デバイスがメモリであるときはMMUやMPUといった汎用的な仕組みが用意されており、例えばメモリ容量が異なる構成においても同一の保護機構がそのまま使える。

【0011】

以下、マイクロプロセッサやDMACなどトランザクションを開始するデバイスをマスタ・デバイス、マスタ・デバイスが開始したトランザクションのアクセス対象をスレーブ・デバイスと呼ぶことにする。

【0012】

しかし、マスタ・デバイスがDMACであるか、もしくはスレーブ・デバイスが周辺デバイスである場合に一般的に用いられている許可ビット・レジスタ方式には汎用性が欠けており、例えば、周辺デバイスが追加された場合には許可ビットを追加して保護機構全体を再設計する必要がある。また、ほぼ必ず設計ごとに保護機構が異なりソフトウェア互換性がないため、制御ソフトウェアを変更する必要もある。

【0013】

このように許可ビット・レジスタ方式には汎用性に欠け、再利用性に難があるため、バスマスタの種類を問わず適用できる統一性を備え、スレーブ・デバイス数が変化しても適用できるスケーラビリティを兼ね備えた保護機構が求められている。

【0014】

本発明の目的は、上述した課題であるマスタ・デバイス、スレーブ・デバイスの種類や数を問わず適用できる汎用的でスケーラブルなアクセス保護機構を有するコンピュータ・システム及びその処理方法を提供することにある。

【課題を解決するための手段】

【0015】

本発明のコンピュータ・システムでは、ソフトウエア・プロセス番号に関連づけられた第1のプロセスIDを格納する第1のレジスタを有し、かつトランザクションを生成するときに、システム・バス上に第1のプロセスIDを送出するマスタ・デバイスと、

アクセスを許可する第2のプロセスIDを保持し、かつ第1のプロセスIDと第2のプロセスIDとが所定の関係を満たすときに、トランザクションを受け入れるスレーブ・デバイスとを有する。

【0016】

以下、メモリや入出力デバイスなどのアクセス対象のアドレスを指定してデータを読み書きするという一ひとまとまりの通信をトランザクションと呼ぶ。

【0017】

また、本発明のマスタ・デバイスでは、ソフトウエア・プロセス番号に関連づけられた第1のプロセスIDを格納する第1のレジスタを有するマスタ・デバイスと、アクセスを許可する第2のプロセスIDを保持するスレーブ・デバイスと、マスタ・デバイスとスレーブ・デバイスに接続されたシステム・バスとを有するコンピュータ・システムにおいて、トランザクションを生成するときに、システム・バス上に第1のプロセスIDを送出する。

【0018】

また、本発明のスレーブ・デバイスでは、ソフトウエア・プロセス番号に関連づけられた第1のプロセスIDを格納する第1のレジスタを有するマスタ・デバイスと、アクセスを許可する第2のプロセスIDを保持するスレーブ・デバイスと、マスタ・デバイスとスレーブ・デバイスに接続されたシステム・バスとを有するコンピュータ・システムにおいて、第1のプロセスIDと第2のプロセスIDとが所定の関係を満たすときに、トランザクションを受け入れる。

【0019】

また、本発明のコンピュータ・システムの処理方法では、ソフトウエア・プロセス番号に関連づけられた第1のプロセスIDを格納する第1のレジスタを有するマスタ・デバイスと、アクセスを許可する第2のプロセスIDを保持するスレーブ・デバイスと、マスタ・デバイスとスレーブ・デバイスに接続されたシステム・バスとを有するコンピュータ・システムの処理方法において、

マスタ・デバイスは、トランザクションを生成するときに、システム・バス上に第1のプロセスIDを送出し、

スレーブ・デバイスは、第1のプロセスIDと第2のプロセスIDとが所定の関係を満たすときに、トランザクションを受け入れる。

【発明の効果】

【0020】

本発明によれば、マスタ・デバイスやスレーブ・デバイスの種類や数を問わない汎用かつスケーラブルなアクセス保護機構が実現できる。

【図面の簡単な説明】

【0021】

【図1】本発明の実施の形態のコンピュータ・システムを示すブロック図である。

【図2】本発明の実施の形態のスレーブ・デバイスを示すブロック図である。

【図3】本発明の実施の形態のマイクロプロセッサとMPUを示すブロック図である。

【図4】本発明の実施の形態のDMACを示すブロック図である。

【図5】本発明の実施の形態のマスタ・デバイスの動作概略を示すフローチャートである。

【図6】本発明の実施の形態のマイクロプロセッサの動作概略を示すフローチャートである。

【図7】本発明の実施の形態のMPUの動作概略を示すフローチャートである。

【図8】既存のコンピュータ・システムを示すブロック図である。

【図9】既存のマイクロプロセッサとMPUを表すブロック図である。

【図10】既存のDMACを示すブロック図である。

【図11】既存のマスタ・デバイスの動作概略を示すフローチャートである。

【図12】既存のマイクロプロセッサの動作概略を示すフローチャートである。

【図13】既存のMPUの動作概略を示すフローチャートである。

【発明を実施するための形態】

【0022】

(既存のコンピュータ・システム)

まず、最初に、本発明の理解が容易になるように、既存のコンピュータ・システムとその保護機構を図8から13を参照しながら説明する。

【0023】

まず、既存のコンピュータ・システムのシステム・バス周辺の構造と動作を説明する。

【0024】

コンピュータ・システムのハードウェアは、ソフトウェアを実行するマイクロプロセッサ、ソフトウェアやデータを記憶するメモリ、周辺デバイスなどから構成されている。ここで周辺デバイスとは入出力デバイスやアクセラレータなどを意味する。

【0025】

図8に示すように、これらのコンピュータ・システムの構成要素間では、システム・バス経由でデータのアクセス(読み出しまたは書き込み)が行われる。システム・バスはアクセス先のアドレスを指定するアドレス・バス803、アドレス・バスで指定されたアドレスに位置するデータを転送するデータ・バス801、アクセスの種類を指定するなどの管理を行うための制御バス802などから成る。

【0026】

ここで、上述のように、メモリや入出力デバイスなどのアクセス対象のアドレスを指定してデータを読み書きするという一ひとまとまりの通信をトランザクションと呼ぶ。また、マイクロプロセッサやDMACなどトランザクションを開始するデバイスをマスタ・デバイス810、マスタ・デバイスが開始したトランザクションのアクセス対象をスレーブ・デバイス820と呼ぶ。

【0027】

マスタ・デバイス、スレーブ・デバイスとはシステム・バス上での機能を表しているため、デバイスによっては両方の機能を備える場合がある。例えば、DMACはスレーブ・デバイスとしてマクロプロセッサから初期設定された後、マスタ・デバイスとしての動作を開始し、他のスレーブ・デバイス(周辺デバイスやメモリ等)をアクセスする。

【0028】

次に、トランザクションの手順の概略を図11に示す。

【0029】

まず、マスタ・デバイス810は、トランザクションを開始すると(ステップ1101)、アクセス先アドレスをアドレス・バス803に出力する(ステップ1102)。

【0030】

次に、トランザクションの種類を判定し(ステップ1103)、それがデータ読み出しの場合、マスタ・デバイス810は、このトランザクションがデータ読み出しであることを示す制御信号を制御バス802に出力する(ステップ1104)。

【0031】

最後に、マスタ・デバイス810は、アクセス対象のスレーブ・デバイス820がデータ・バス801上に出力したデータを取得する(ステップ1105)。

【0032】

または、トランザクションの種類がデータ書き込みの場合、マスタ・デバイス810が書き込みデータをデータ・バス801に出力する(ステップ1106)。

【0033】

最後に、マスタ・デバイス810は、このトランザクションがデータ書き込みであることを示す制御信号を制御バス802に出力する(ステップ1107)。

【0034】

既存のスレーブ・デバイスの動作を、周辺デバイスを例にとり説明する。既存の周辺デバイスはシステム・バスに接続され、マスタ・デバイス810が開始したトランザクションの対象アドレスをアドレス・デコーダで比較し、自身のアドレスと一致した場合にトランザクションの対象として選択され、例えば、周辺デバイスの内部レジスタのアクセスを許可する。

【0035】

次に、既存のコンピュータ・システムの保護機構について説明する。

【0036】

既存技術では、マスタ・デバイスとスレーブ・デバイスの組み合わせによって異なる保護機構が用いられてきた。

【0037】

マスタ・デバイスがマイクロプロセッサで、スレーブ・デバイスがメモリの場合、保護機構としてメモリ・プロテクション・ユニット(Memory Protection Unit、 以下MPUという)かメモリ・マネージメント・ユニット(Memory Management Unit、 以下MMUという)が導入されることが多い。

【0038】

MPUは特定のプロセスに対し決められたメモリ範囲のみアクセスを許可することで、あるプロセスの状態を他のプロセスから参照・変更できないようにする保護機構である。MPUは低コストな組込みマイクロプロセッサで採用されることが多い。既存のMPUの例としては上記特許文献1、特許文献2に挙げたようなものがある。

【0039】

既存の典型的なMPUの構成を図9を参照しながら説明する。

【0040】

既存のマイクロプロセッサ910は、システム・バスに接続され、MPU920によって保護されたメモリ930上のプログラムを実行したり、メモリ930や周辺デバイス上のデータをアクセスするためバス・トランザクションを生成する。

【0041】

図12にマイクロプロセッサ910がバス・トランザクションを生成する手順を示す。

【0042】

最初に、バス・トランザクション生成の目的を判定し(ステップ1202)、プログラム実行のために、次に実行する機械語命令を取得することが目的であれば、バス・インターフェース・ユニット(Bus Interface Unit、 以下BIUという)911は、その命令の位置を示すプログラム・カウンタ(Program Counter、 以下PCという)913の値をアドレス・バスに出力する(ステップ1203)。

【0043】

あるいは、データ・アクセスが目的であれば、汎用レジスタや命令語中の即値をもとにアドレス・ジェネレータ(Address Generator、以下AGという)912が生成したアクセス先のアドレス値をシステム・バスに出力する(ステップ1204)。

【0044】

以降の手順(ステップ1205からステップ1209)は図11と同様である。

【0045】

MPU920はシステム・バスとメモリ930の間に位置し、上限アドレス・レジスタ922と下限アドレス・レジスタ923を持つ。

【0046】

次に、MPUの動作を図13に示す。

【0047】

トランザクション発生時、MPU920はシステム・バス上のアドレス・バス903上の値と上限アドレス・レジスタ922、下限アドレス・レジスタ923の値を比較器921で比較し、アドレス・バス上の値が下限アドレス・レジスタの値以上で(ステップ1302)、上限アドレス・レジスタの値以下のとき(ステップ1303)、メモリへのアクセスを許可し(ステップ1304)、それ以外の場合は許可しない(ステップ1305)。

【0048】

MPU920はメモリ930の内容をきめ細かく保護できるように、上限アドレス・レジスタ922と下限アドレス・レジスタ923の組を複数持つことがある。あるいは、上記特許文献3に示すように、ソフトウェアがプロセスIDをMPU920に明示的に書き込むことにより、上限アドレス・レジスタ922と下限アドレス・レジスタ923の組を選択する機構を持ち、プロセスごとに独立した保護領域を持てるようにした例がある。あるいは、アクセスを許可するメモリ領域の上下限アドレスを設定するのではなく、アクセスを禁止するメモリ領域の上下限アドレスを設定する実装もあり得る。

【0049】

汎用プロセッサ(x86、MIPS、PowerPC、SPARCなど)では、マスタ・デバイスがマイクロプロセッサで、スレーブ・デバイスがメモリの場合、保護機構としてMMUが導入されることが多い(非特許文献2)。

【0050】

MMUでは、論理メモリ空間を4Kバイトなどのページ単位に分割し、ページごとに対応する物理メモリのアドレスやアクセス許可属性を設定する。これらの設定を納めたテーブルは各プロセス別に主記憶メモリ上に用意されるが、マイクロプロセッサはこのテーブルの一部を、高速化のためにマイクロプロセッサ内部のトランスレーション・ルックアサイド・バッファ(Translation Lookaside Buffer、 以下TLBという)にキャッシュして利用する。

【0051】

マスタ・デバイスがマイクロプロセッサで、スレーブ・デバイスが周辺デバイスの場合、周辺デバイスごとにアクセス許可・不許可を設定するビットマップを格納するレジスタを用いる方式の保護機構(以下、許可ビット・レジスタ方式という)がある。通常、固定アドレスに割り付けられ、小さいアドレス空間(数十バイト程度)を占有するという周辺デバイスの特性から、MMUまたはMPUによる保護機構より許可ビット・レジスタ方式が適している。

【0052】

他の、より汎用的な方法としては、I/Oアドレス1バイトごとに1ビットの許可ビット・テーブルを主記憶上に持つ方式がある(特許文献4)。ただし、アクセスごとに上記テーブルを参照するため、効率が悪いという問題がある。

【0053】

マスタ・デバイスが周辺デバイスの場合、許可ビット・レジスタ方式をメモリにも拡張した方式が用いられることがある。固定的なメモリ領域や周辺デバイスごとにアクセス許可・不許可を設定するビットマップを格納するレジスタを用いた例がある(非特許文献3)。

【0054】

既存の保護機構では、マスタ・デバイスがマイクロプロセッサであり、かつスレーブ・デバイスがメモリであるときはMMUやMPUといった汎用的な仕組みが用意されており、例えば、メモリ容量が異なる構成においても同一の保護機構がそのまま使える。

【0055】

しかし、マスタ・デバイスがDMACであるか、もしくはスレーブ・デバイスが周辺デバイスである場合に一般的に用いられている許可ビット・レジスタ方式には汎用性が欠けており、例えば、周辺デバイスが追加された場合には許可ビットを追加して保護機構全体を再設計する必要がある。また、ほぼ必ず設計ごとに保護機構が異なりソフトウェア互換性がないため、制御ソフトウェアを変更する必要もある。

【0056】

このように許可ビット・レジスタ方式には汎用性に欠け、再利用性に難があるため、バスマスタの種類を問わず適用できる統一性を備え、スレーブ・デバイス数が変化しても適用できるスケーラビリティを兼ね備えた保護機構が求められている。

【0057】

本発明の実施の形態は、コンピュータ・システムにおいて、マスタ・デバイス、スレーブ・デバイスの種類や数を問わず適用できる、汎用的でスケーラブルなアクセス保護機構を提供する。

【0058】

このため、本発明の実施の形態では、マスタ・デバイスは現在実行中のソフトウェアのプロセスID値を格納するレジスタを備え、システム・バス上にトランザクションを生成するとき、アクセス先アドレスと同時にプロセスIDを送出する。ターゲット・デバイスはアクセスを許可するプロセスIDを格納するレジスタを備え、プロセスIDが一致するトランザクションのみ受け入れる。

【0059】

(本発明の実施の形態)

次に、本発明の実施の形態について図を参照して説明する。

【0060】

最初に、第1の実施の形態として、図1を参照しながら、本発明のコンピュータ・システムのマスタ・デバイスの動作を説明する。

【0061】

本発明のシステム・バスはアクセス先のアドレスを指定するアドレス・バス103、アドレス・バス103で指定されたアドレスに位置するデータを転送するデータ・バス101、アクセスの種類を指定するなどの管理を行うための制御バス102に加えトランザクション・プロセス識別子(Transaction Process Identifier)・バス(以下、TPIDバスという)104から成る。

【0062】

本発明の実施の形態のシステム・バスに接続されるマスタ・デバイス110はプロセス識別子(Process Identifier)・レジスタ111(以下、PIDレジスタという)を持つ。

【0063】

システム・バス上に接続されたマスタ・デバイス110がトランザクションを生成し、スレーブ・デバイス120をアクセスする手順を図5に示す。

【0064】

まず、マスタ・デバイス110は、トランザクションを開始すると(ステップ501)、アクセス先アドレスをアドレス・バス103に出力(ステップ502)し、PIDレジスタ111の値をTPIDバス104に出力する(ステップ503)。

【0065】

次に、トランザクションの種類を判定し(ステップ504)、それがデータ読み出しの場合、マスタ・デバイス110は、このトランザクションがデータ読み出しであることを示す制御信号を制御バス102に出力する(ステップ505)。

【0066】

最後に、マスタ・デバイス110は、アクセス対象のスレーブ・デバイス120がデータ・バス101上に出力したデータを取得する(ステップ506)。

【0067】

また、トランザクションの種類がデータ書き込みの場合、マスタ・デバイス110が書き込みデータをデータ・バス101に出力する(ステップ507)。

【0068】

最後に、マスタ・デバイス110は、このトランザクションがデータ書き込みであることを示す制御信号を制御バスに出力する(ステップ508)。

【0069】

これらの手順は典型的なバス・トランザクションの概略を例として示したもので、準拠するバスプロトコルによっては、アドレス、データ、制御信号、TPIDの出力順序が前後する場合がある。バスの利用権調停や、トランザクションの延長やキャンセル、その他の付加機能のための制御が追加される場合もある。

【0070】

次に、本発明の第2の実施の形態として、図2を参照しながら、もっとも単純なスレーブ・デバイスとして、固定アドレスに割り付けられた周辺デバイス(入出力デバイスなど)の例を説明する。

【0071】

本発明の第2の実施の形態のスレーブ・デバイス210中の比較器212は、トランザクション中にマスタ・デバイスがTPIDバス204に出力した値と、スレーブ・デバイス210自身が持つTPIDレジスタ211の値を比較し、一致したときのみ許可信号をデコーダ213に通知する。

【0072】

デコーダ213はトランザクション中にマスタ・デバイスがアドレス・バス203に出力したアドレス値が、スレーブ・デバイスが割り付けられたアドレス範囲に含まれ、かつ比較器212から許可信号が通知されているとき、そのトランザクションに正常に応答することを決定し、内部レジスタ214へのアクセスを許可する等の動作を行う。

【0073】

次に、図3を参照しながら、本発明の実施の形態の保護機構を持つバスマスタ・デバイスとしてマイクロプロセッサ、本発明の実施の形態の保護機構を持つスレーブ・デバイスとしてMPUを備えたメモリの動作を説明する。

【0074】

本発明の実施の形態の保護機構を持つマイクロプロセッサ310は、次に実行する機械語命令の位置を示すプログラム・カウンタ(Program Counter、 以下、PCという)313、データ・アクセス対象のアドレスを生成するアドレス・ジェネレータ(Address Generator、 以下、AGという)312、現在実行中のプロセス番号に関連づけられた値を格納するPIDレジスタ314を持つ。

【0075】

次に、本発明の実施の形態のマイクロプロセッサ310がトランザクションを生成する手順を図6に示す。

【0076】

バス・トランザクション生成の目的を判定し(ステップ602)、プログラム実行のために、次に実行する機械語命令を取得することが目的であれば、バス・インターフェース・ユニット(Bus Interface Unit、 以下、BIUという)311は、その命令の位置を示すPC313の値をアドレス・バス303に出力(ステップ603)するとともに、PIDレジスタ314の値をTPIDバス304に出力する(ステップ604)。

【0077】

また、データ・アクセスが目的であれば、AG312が生成したアクセス先のアドレス値をシステム・バスに出力(ステップ605)するとともに、PIDレジスタ314の値をTPIDバス304に出力する(ステップ606)。

【0078】

以降の手順(ステップ605からステップ611)は図5のステップ504からステップ508と同様である。

【0079】

次に、本発明の第3の実施の形態として、本発明の実施の形態のマスタ・デバイスの別の例であるDMACについて、図4を参照しながら説明する。

【0080】

DMACは、初期設定後はマイクロプロセッサ上のソフトウェアの介在なしに、自律的に高速なデータ転送を行う機構である。

【0081】

ここで、本発明の第3の実施の形態の理解を容易にするために、既存のDMACの例を図10に示す。

【0082】

これは1970年代から使われているIntel8257の主要部分を抜き出したものである。このDMACは転送元アドレス・レジスタ1012、転送先アドレス・レジスタ1013、転送回数レジスタ1014を持つ。これらのレジスタの値はマイクロプロセッサ上のソフトウェアにより初期設定される。

【0083】

既存のDMACによるトランザクションの例として、転送元が周辺デバイスで転送先がメモリである場合を考える。この場合、転送元の周辺デバイスからの専用信号線の指示によりDMAが開始される。

【0084】

まず、DMAC1010はマスタ・デバイスとして動作し、バス・インターフェース・ユニット(Bus Interface Unit、 以下、BIUという)1011は転送元アドレス・レジスタ1012の値をアドレス・バス1003に出力して周辺デバイスにデータ読み出しを要求することにより、トランザクションを開始する。周辺デバイスから読み出されたデータはDMAC1010内部の転送データ・レジスタ1015に書き込まれる。

【0085】

次に、再度、DMAC1010はマスタ・デバイスとして動作し、転送先アドレス・レジスタ1013の値をBIU1011経由でアドレス・バス1003に、転送データ・レジスタ1015の値をデータ・バス1001に出力することで、メモリへの書き込みトランザクションを開始する。

【0086】

メモリへの書き込みトランザクション終了後、転送先アドレス・レジスタ1013の値は更新される。以上の操作を転送回数レジスタ1014に設定された回数だけ繰り返す。DMAC1010には通常、種々の動作モードや動作タイミングの設定、ステータス通知のためのレジスタや信号端子が存在するが、以上の説明では簡単のために省略してある。

【0087】

次に、図4を参照して、本発明の実施の形態の保護機構を持つDMACを示す。

【0088】

本発明のDMAC410は、転送元アドレス・レジスタ412、転送先アドレス・レジスタ413、転送回数レジスタ414に加え、TPIDレジスタ416を持つ。これらのレジスタの値はマイクロプロセッサ上のソフトウェアにより初期設定される。

【0089】

本発明の実施の形態のDMACによるトランザクションの例として、転送元が周辺デバイスで転送先がメモリである場合を考える。この場合、転送元の周辺デバイスからの通知によりDMAが開始される。通知の手段としては、周辺デバイスからDMACへの専用信号線を敷設する等が考えられる。

【0090】

まず、DMAC410はマスタ・デバイスとして動作し、BIU411は転送元アドレス・レジスタ412の値をアドレス・バス403に、TPIDレジスタ416の値をTPIDバス404に出力して周辺デバイスにデータ読み出しを要求することにより、トランザクションを開始する。周辺デバイスから読み出されたデータはDMAC410内部の転送データ・レジスタ415に書き込まれる。

【0091】

次に、再度、DMAC410はマスタ・デバイスとして動作し、転送先アドレス・レジスタ413の値をアドレス・バス403に、転送データ・レジスタ415の値をデータ・バス401に、TPIDレジスタ416の値をTPIDバス404に出力することで、メモリへの書き込みトランザクションを開始する。

【0092】

メモリへの書き込みトランザクション終了後、転送先アドレス・レジスタ413の値は更新される。以上の操作を転送回数レジスタ414に設定された回数だけ繰り返す。

【0093】

なお、本発明の実施の形態は、DMAC410の実装細部の差異を問わず一般的に適用できる。例えば、図4では、簡単のためにDMAチャネル数が1であるとして説明したが、複数のDMAチャネルを持つDMACでも同様の議論が可能である。複数のDMAチャネルを持つとき、全DMAチャネルで共通のTPIDレジスタ416を持つ構成、チャネルごとに独立したTPIDレジスタ416を持つ構成が考えられる。また、図4では、転送先のメモリ領域を、転送先アドレス・レジスタ413と転送回数レジスタ414により示すとしたが、転送先開始アドレス・レジスタと転送先終了アドレス・レジスタにより示すこともできる。

【0094】

さらに、図4では、データを転送データ・レジスタ415経由で転送する構成としたが、周辺デバイスからメモリに直接データ転送する構成も考えられる。

【0095】

また、TPIDレジスタ416の値を、データ転送元向けとデータ転送先向けに、独立して持つ構成も考えられる。

【0096】

また、図4において、TPIDレジスタ416の値はマイクロプロセッサ上のソフトウェアが初期設定するとしたが、別の構成では、マイクロプロセッサがDMAC410上のレジスタ(転送元アドレス・レジスタ、転送先アドレス・レジスタ、転送回数レジスタ、モード設定レジスタ、コマンド・レジスタ、ステータス・レジスタ等)のうちいずれかをアクセスしたときの、TPIDバス404上の値を自動取得する構成も可能である。

【0097】

以上の説明ではDMAC410の初期設定はマイクロプロセッサ上のソフトウェアが行うとしたが、マイクロプロセッサと共有するメモリまたはDMACが持つ専用メモリ上に置かれたマイクロ・プログラム(デスクリプタと呼ばれることもある)をDMACが直接解釈することによって設定する構成も可能である。

【0098】

DMAC410の内部レジスタ群を図2に示したスレーブ・デバイスとして扱い、保護機構で守ることが可能である。図4に示したDMAC410では、マイクロプロセッサ上のソフトウェアが、転送元アドレス・レジスタ412、転送先アドレス・レジスタ413、転送回数レジスタ414、TPIDレジスタ416を初期設定するとした。これらのレジスタの初期設定中は、DMAC410はスレーブ・デバイスとして動作しており、バスマスタ・デバイスとして動作しているマイクロプロセッサからのアクセスを受け入れている。そのため、図2に示したように、スレーブ・デバイスとしてのTPIDレジスタを持ちこれらのレジスタを保護することが可能である。

【0099】

図4に関する議論はバスマスタ機能を持つ周辺デバイスに一般的に適用できる。

【0100】

本発明の保護機構を持つバスマスタ・デバイスは、アクセス先のメモリ・アドレスの値をアドレス・バスに、TPIDレジスタの値をTPIDバスに、その他必要な信号をシステム・バスに出力することでメモリへのトランザクションを開始する。

【0101】

次に、本発明の第4の実施の形態として、本発明の実施の形態の保護機構を備えたスレーブ・デバイスの例であるMPUについて、再度図3を参照しながら説明する。

【0102】

このMPU320はシステム・バスとメモリ330の間に位置し、既存のMPU(図9)が持つ上限アドレス・レジスタ322と下限アドレス・レジスタ323に加えTPIDレジスタ324を持つ。

【0103】

次に、MPU320の動作を図7に示す。

【0104】

トランザクション発生時、MPU320はシステム・バス上のアドレス・バス303上の値と上限アドレス・レジスタ322、下限アドレス・レジスタ323の値を比較器321で比較し、アドレス・バス上の値が下限アドレス・レジスタの値以上で(ステップ702)、上限アドレス・レジスタの値以下で(ステップ703)、かつTPIDバス304上の値がTPIDレジスタ324と一致したとき(ステップ704)のみメモリへのアクセスを許可し(ステップ705)、それ以外の場合は許可しない(ステップ706)。

【0105】

トランザクション発生時、MPU320はシステム・バス上のアドレス・バス303の値と上限アドレス・レジスタ322、下限アドレス・レジスタ323の値を比較し、アドレス・バス303の値が上限アドレス・レジスタの値以下で、下限アドレス・レジスタの値以上のとき、メモリへのアクセスを許可し、それ以外の場合は遮断する。

【0106】

既存のMPUでも、単一バスマスタ・システムであれば、プロセス切り替え時にMPUのレジスタ(上限アドレス・レジスタ、下限アドレス・レジスタ等)を入れ替えれば、他のプロセスの不正アクセスから保護できる。しかし、この方式ではプロセス切替時に、MPUレジスタ入替が必要になるためプロセス切替時間が長くなり、リアルタイム・システムに適さないという問題がある。

【0107】

また、今後主流になるであろうマルチプロセッサ・システム、または1個以上のマイクロプロセッサと1個以上のバスマスタ機能を持つアクセラレータを持つコンピュータ・システムでは、生成したプロセスが異なるトランザクションがシステム・バス上で細粒度で混在することになり、既存のMPUでは対応できなくなるが、本発明の実施の形態のMPU320(図3)では保護が可能である。

【0108】

本発明の実施の形態によれば、マスタ・デバイスやスレーブ・デバイスの種類によらず、アクセス保護を実現できる。例えば、マスタ・デバイスがマイクロプロセッサであっても、DMACやアクセラレータのような周辺デバイスであっても、スレーブ・デバイスがメモリであっても入出力デバイスのような周辺デバイスであっても、同一の機構でアクセス保護が行える。

【0109】

また、本発明の実施の形態によれば、システム・バス上に接続されるマスタ・デバイスやスレーブ・デバイスの数によらず同一の機構が行える。例えば、マイクロプロセッサが複数個存在する場合でも同一のアクセス保護機構で対応できる。また、スレーブ・デバイスの数が増加しても、既存部分の設計変更を行う必要がない。

【0110】

このように、本発明の実施の形態によればマスタ・デバイスやスレーブ・デバイスの種類や数を問わない、汎用かつスケーラブルなアクセス保護機構が実現できる。

【0111】

以上、本発明の実施の形態について具体的に説明したが、本発明は上述の実施形態に限定されるものではなく、本発明技術的思想に基づく各種の変形が可能である。

【0112】

例えば、マイクロプロセッサ310のPIDレジスタ314(図3)には、マイクロプロセッサ310上で動作するオペレーティング・システムが、現在実行中のソフトウェア・プロセスの番号をそのまま設定する構成、または、そのソフトウェア・プロセスに関連づけた値を設定する構成が可能である。後者の場合、マスタ・デバイスのPIDレジスタ、TPIDバス、スレーブ・デバイスのTPIDレジスタや比較器などのビット長を、同時にアクティブとなるプロセス数をカバーするのに充分な長さにまで削減できる。

【0113】

また、システム・バス上でTPIDバス104が専用の信号線で実現されているとしたが、ひとつのトランザクションにひとつのTPID値が付与されていれば、システム・バス実装の細部は問わない。例えば、物理的に同じ信号線を用い、時分割多重によりアドレス値とTPID値を伝達するシステム・バス構成も可能である。

【0114】

また、ひとつのスレーブ・デバイス210はひとつのTPIDレジスタ211(図2)を持つとした。しかし、ひとつのスレーブ・デバイス210が複数のTPIDレジスタ211を持ち、TPIDバス204上の値がいずれかのTPIDレジスタ211の値と一致したときにそのスレーブ・デバイス210にアクセスを許可する構成も可能である。また、ひとつのスレーブ・デバイス210が機能別に複数のTPIDレジスタ211を持ち、機能別に細かくアクセスを制御する構成も可能である。

【0115】

また、TPIDバス204上の値がスレーブ・デバイス210のTPIDレジスタ211の値と一致することをアクセス許可条件としたが、他の比較条件をアクセス許可条件とする構成も可能である。例えば、TPIDバス204上の値がスレーブ・デバイス210のTPIDレジスタ211の値より大きいとき、大きいか等しいとき、小さいとき、小さいか等しいときにアクセスを許可する構成も可能である。

【0116】

また、スレーブ・デバイス210はTPIDバス204上の値とTPIDレジスタ211の値を比較した結果に基づきアクセス許可するとしたが、TPIDレジスタ211を持たず固定値と比較した結果に基づきアクセス許可する構成も可能である。

【0117】

例えば、マイクロプロセッサが特権モード状態にあることをTPIDの特定値で示し、スレーブ・デバイス210はその特定のTPID値でのアクセスを許可する構成も可能である。さらに、TPIDバス204上の値と固定値との比較結果、TPIDバス204上の値とTPIDレジスタ211の値の比較結果の双方を勘案し、アクセスを許可する構成も可能である。

【0118】

また、スレーブ・デバイス210は、自身が割り付けられたアドレスとアドレス・バス203上の値を比較するデコーダ213と、TPIDレジスタ211の値とTPIDバス204上の値を比較する比較器212を別に持つとしたが、これらの働きは似ているため、デコーダ213と比較器212を一体化した構成も可能である。

【0119】

また、デコーダ213と比較器212をスレーブ・デバイス210ごとに持つとしたが、複数のスレーブ・デバイスのデコーダと比較器の一部もしくは全部を一体化した集中制御型の構成も可能である。さらにマスタ・デバイスのPIDレジスタも一体化した構成も可能である。

【0120】

また、メモリの保護機構としてMPUを取り上げ、TPIDによる保護機構を説明したが、メモリの保護機構としてMMUを採用する本発明の保護機構も可能である。MMUを備えるマイクロプロセッサは、通常PIDレジスタを持ち、TLBのヒット率向上のために内部的に利用しているので、そのPIDレジスタの値をシステム・バスに取り出すだけで本発明の保護機構を備えたマスタ・デバイスとすることができる。

【0121】

実際のコンピュータ・システムでは、マイクロプロセッサは図3の基本的な構成要素に加え、高速化や低電力化のために数々のキャッシュ機構、予測機構を備えているため、次に実行する機械語命令のアドレスを示すPC値だけでなく、さらに将来のPC値を予測した値がアドレス・バスに出力されることがある。このときのTPIDバスには、予測の元となったPC値が属するプロセス番号に関連づけた値を出力する。

【符号の説明】

【0122】

101 データ・バス

102 制御バス

103 アドレス・バス

104 TPIDバス

110 マスタ・デバイス

111 PIDレジスタ

120 スレーブ・デバイス

201 データ・バス

202 制御バス

203 アドレス・バス

204 TPIDバス

210 スレーブ・デバイス

211 TPIDレジスタ

212 比較器

213 デコーダ

214 内部レジスタ

301 データ・バス

302 制御バス

303 アドレス・バス

304 TPIDバス

310 マイクロプロセッサ

311 BIU

312 AG

313 PC

314 PIDレジスタ

320 MPU

321 比較器

322 上限アドレス・レジスタ

323 下限アドレス・レジスタ

324 TPIDレジスタ

330 メモリ

331 デコーダ

341 許可信号

401 データ・バス

402 制御バス

403 アドレス・バス

404 TPIDバス

410 DMAC

411 BIU

412 転送元アドレス・レジスタ

413 転送先アドレス・レジスタ

414 転送回数・レジスタ

415 転送データ・レジスタ

416 TPIDレジスタ

801 データ・バス

802 制御バス

803 アドレス・バス

810 マスタ・デバイス

820 スレーブ・デバイス

901 データ・バス

902 制御バス

903 アドレス・バス

910 マイクロプロセッサ

911 BIU

912 AG

913 PC

920 MPU

921 比較器

922 上限アドレス・レジスタ

923 下限アドレス・レジスタ

930 メモリ

931 デコーダ

941 許可信号

1001 データ・バス

1002 制御バス

1003 アドレス・バス

1010 DMAC

1011 BIU

1012 転送元アドレス・レジスタ

1013 転送先アドレス・レジスタ

1014 転送回数・レジスタ

1015 転送データ・レジスタ

【特許請求の範囲】

【請求項1】

ソフトウエア・プロセス番号に関連づけられた第1のプロセスIDを格納する第1のレジスタを有し、かつトランザクションを生成するときに、システム・バス上に第1のプロセスIDを送出するマスタ・デバイスと、

アクセスを許可する第2のプロセスIDを保持し、かつ第1のプロセスIDと第2のプロセスIDとが所定の関係を満たすときに、トランザクションを受け入れるスレーブ・デバイスとを有することを特徴とするコンピュータ・システム。

【請求項2】

前記システム・バスは、少なくともアドレス・バスとプロセスIDバスを有し、

前記マスタ・デバイスは、前記トランザクションを開始する際にアクセス先アドレスを前記アドレス・バスに出力し、前記第1のプロセスIDを前記プロセスIDバスに出力することを特徴とする請求項1に記載のコンピュータ・システム。

【請求項3】

前記スレーブ・デバイスは、前記第1のプロセスIDと前記第2のプロセスIDとを比較して一致したときのみアクセスを許可する判定手段を有することを特徴とする請求項1又は2に記載のコンピュータ・システム。

【請求項4】

前記判定手段は、前記第1のプロセスIDと前記第2のプロセスIDとを比較する比較手段と、比較の結果一致したときのみ許可信号を受け取るデコーダとを有することを特徴とする請求項3に記載のコンピュータ・システム。

【請求項5】

前記デコーダは、前記アドレス・バスに出力された前記アクセス先アドレスが、前記スレーブ・デバイスに割り付けられたアドレス範囲に含まれ、かつ前記比較手段から許可信号を受け取ったときに、前記トランザクションに正常に応答することを決定して前記アクセスを許可することを特徴とする請求項4に記載のコンピュータ・システム。

【請求項6】

前記マスタ・デバイスはマイクロプロセッサであり、前記スレーブ・デバイスはMPUを備えたメモリであり、

前記MPUは、前記システム・バスと前記メモリの間に位置し、かつ前記第2のレジスタを有し、

前記トランザクション発生時、前記MPUは前記アドレス・バス上の値が所定のアドレス範囲にあり、かつ前記第1のプロセスIDと前記第2のプロセスIDとが一致したときに前記メモリへのアクセスを許可することを特徴とする請求項2から5のいずれか1項に記載のコンピュータ・システム。

【請求項7】

前記マイクロプロセッサの第1のレジスタには、前記マイクロプロセッサ上で動作するオペレーティング・システムが現在実行中のソフトウェア・プロセスの番号をそのまま設定することを特徴とする請求項6に記載のコンピュータ・システム。

【請求項8】

前記マイクロプロセッサの第1のレジスタには、前記マイクロプロセッサ上で動作するオペレーティング・システムが現在実行中のソフトウェア・プロセスに関連づけた値を設定することを特徴とする請求項6に記載のコンピュータ・システム。

【請求項9】

前記マスタ・デバイス及び前記スレーブ・デバイスは、周辺デバイスとメモリとの間に接続されたDMACであり、

前記DMACは前記マスタ・デバイスとして動作して、前記第1のレジスタに格納されている前記第1のプロセスIDを前記システム・バス上に送出して前記トランザクションを開始し、前記周辺デバイスから読み出されたデータを前記DMACの内部の転送データ・レジスタに書き込み、

前記DMACは再度、前記マスタ・デバイスとして動作して、前記転送データ・レジスタの値を前記システム・バスに出力して前記メモリへの書き込みトランザクションを開始することを特徴とする請求項1に記載のコンピュータ・システム。

【請求項10】

前記第1のレジスタの値は、マイクロプロセッサ上のソフトウェアが初期設定することを特徴とする請求項9に記載のコンピュータ・システム。

【請求項11】

前記第1のレジスタは、マイクロプロセッサが前記DMACのレジスタをアクセスしたときに、前記システム・バス上の値を自動取得することを特徴とする請求項9に記載のコンピュータ・システム。

【請求項12】

前記DMACの内部レジスタ群をスレーブ・デバイスとして扱い、

前記第1のレジスタの初期設定中は、前記DMACは前記スレーブ・デバイスとして動作し、前記マスタ・デバイスとして動作しているマイクロプロセッサからのアクセスを受け入れることを特徴とする請求項9に記載のコンピュータ・システム。

【請求項13】

前記スレーブ・デバイスは、複数の前記第2のプロセスIDを保持し、

前記スレーブ・デバイスは、前記第1のプロセスIDと前記複数の第2の第2のプロセスIDの内のいずれか一つの値とが所定の関係を満たすときに、前記トランザクションを受け入れることを特徴とする請求項1に記載のコンピュータ・システム。

【請求項14】

前記スレーブ・デバイスは第2のレジスタを有し、

前記第2のプロセスIDはこの第2のレジスタに格納されていることを特徴とする請求項1に記載のコンピュータ・システム。

【請求項15】

前記第2のプロセスIDは固定値であることを特徴とする請求項1に記載のコンピュータ・システム。

【請求項16】

ソフトウエア・プロセス番号に関連づけられた第1のプロセスIDを格納する第1のレジスタを有するマスタ・デバイスと、アクセスを許可する第2のプロセスIDを保持するスレーブ・デバイスと、マスタ・デバイスとスレーブ・デバイスに接続されたシステム・バスとを有するコンピュータ・システムにおいて、

トランザクションを生成するときに、システム・バス上に第1のプロセスIDを送出することを特徴とするマスタ・デバイス。

【請求項17】

ソフトウエア・プロセス番号に関連づけられた第1のプロセスIDを格納する第1のレジスタを有するマスタ・デバイスと、アクセスを許可する第2のプロセスIDを保持するスレーブ・デバイスと、マスタ・デバイスとスレーブ・デバイスに接続されたシステム・バスとを有するコンピュータ・システムにおいて、

第1のプロセスIDと第2のプロセスIDとが所定の関係を満たすときに、トランザクションを受け入れることを特徴とするスレーブ・デバイス。

【請求項18】

前記スレーブ・デバイスは第2のレジスタを有し、

前記第2のプロセスIDはこの第2のレジスタに格納されていることを特徴とする請求項17に記載のスレーブ・デバイス。

【請求項19】

前記第2のプロセスIDは固定値であることを特徴とする請求項17に記載のスレーブ・デバイス。

【請求項20】

ソフトウエア・プロセス番号に関連づけられた第1のプロセスIDを格納する第1のレジスタを有するマスタ・デバイスと、アクセスを許可する第2のプロセスIDを保持するスレーブ・デバイスと、マスタ・デバイスとスレーブ・デバイスに接続されたシステム・バスとを有するコンピュータ・システムの処理方法において、

マスタ・デバイスは、トランザクションを生成するときに、システム・バス上に第1のプロセスIDを送出し、

スレーブ・デバイスは、第1のプロセスIDと第2のプロセスIDとが所定の関係を満たすときに、トランザクションを受け入れることを特徴とするコンピュータ・システムの処理方法。

【請求項21】

前記スレーブ・デバイスは、前記第1のプロセスIDと前記第2のプロセスIDとを比較して一致したときのみアクセスを許可することを特徴とする請求項20に記載のコンピュータ・システムの処理方法。

【請求項22】

前記マスタ・デバイスは、前記システム・バスのアドレス・バスにアクセス先アドレスを出力し、

前記スレーブ・デバイスは、前記アクセス先アドレスが、割り付けられたアドレス範囲に含まれかつ前記比較が一致したときに、前記トランザクションに正常に応答することを決定して前記アクセスを許可することを特徴とする請求項21に記載のコンピュータ・システムの処理方法。

【請求項1】

ソフトウエア・プロセス番号に関連づけられた第1のプロセスIDを格納する第1のレジスタを有し、かつトランザクションを生成するときに、システム・バス上に第1のプロセスIDを送出するマスタ・デバイスと、

アクセスを許可する第2のプロセスIDを保持し、かつ第1のプロセスIDと第2のプロセスIDとが所定の関係を満たすときに、トランザクションを受け入れるスレーブ・デバイスとを有することを特徴とするコンピュータ・システム。

【請求項2】

前記システム・バスは、少なくともアドレス・バスとプロセスIDバスを有し、

前記マスタ・デバイスは、前記トランザクションを開始する際にアクセス先アドレスを前記アドレス・バスに出力し、前記第1のプロセスIDを前記プロセスIDバスに出力することを特徴とする請求項1に記載のコンピュータ・システム。

【請求項3】

前記スレーブ・デバイスは、前記第1のプロセスIDと前記第2のプロセスIDとを比較して一致したときのみアクセスを許可する判定手段を有することを特徴とする請求項1又は2に記載のコンピュータ・システム。

【請求項4】

前記判定手段は、前記第1のプロセスIDと前記第2のプロセスIDとを比較する比較手段と、比較の結果一致したときのみ許可信号を受け取るデコーダとを有することを特徴とする請求項3に記載のコンピュータ・システム。

【請求項5】

前記デコーダは、前記アドレス・バスに出力された前記アクセス先アドレスが、前記スレーブ・デバイスに割り付けられたアドレス範囲に含まれ、かつ前記比較手段から許可信号を受け取ったときに、前記トランザクションに正常に応答することを決定して前記アクセスを許可することを特徴とする請求項4に記載のコンピュータ・システム。

【請求項6】

前記マスタ・デバイスはマイクロプロセッサであり、前記スレーブ・デバイスはMPUを備えたメモリであり、

前記MPUは、前記システム・バスと前記メモリの間に位置し、かつ前記第2のレジスタを有し、

前記トランザクション発生時、前記MPUは前記アドレス・バス上の値が所定のアドレス範囲にあり、かつ前記第1のプロセスIDと前記第2のプロセスIDとが一致したときに前記メモリへのアクセスを許可することを特徴とする請求項2から5のいずれか1項に記載のコンピュータ・システム。

【請求項7】

前記マイクロプロセッサの第1のレジスタには、前記マイクロプロセッサ上で動作するオペレーティング・システムが現在実行中のソフトウェア・プロセスの番号をそのまま設定することを特徴とする請求項6に記載のコンピュータ・システム。

【請求項8】

前記マイクロプロセッサの第1のレジスタには、前記マイクロプロセッサ上で動作するオペレーティング・システムが現在実行中のソフトウェア・プロセスに関連づけた値を設定することを特徴とする請求項6に記載のコンピュータ・システム。

【請求項9】

前記マスタ・デバイス及び前記スレーブ・デバイスは、周辺デバイスとメモリとの間に接続されたDMACであり、

前記DMACは前記マスタ・デバイスとして動作して、前記第1のレジスタに格納されている前記第1のプロセスIDを前記システム・バス上に送出して前記トランザクションを開始し、前記周辺デバイスから読み出されたデータを前記DMACの内部の転送データ・レジスタに書き込み、

前記DMACは再度、前記マスタ・デバイスとして動作して、前記転送データ・レジスタの値を前記システム・バスに出力して前記メモリへの書き込みトランザクションを開始することを特徴とする請求項1に記載のコンピュータ・システム。

【請求項10】

前記第1のレジスタの値は、マイクロプロセッサ上のソフトウェアが初期設定することを特徴とする請求項9に記載のコンピュータ・システム。

【請求項11】

前記第1のレジスタは、マイクロプロセッサが前記DMACのレジスタをアクセスしたときに、前記システム・バス上の値を自動取得することを特徴とする請求項9に記載のコンピュータ・システム。

【請求項12】

前記DMACの内部レジスタ群をスレーブ・デバイスとして扱い、

前記第1のレジスタの初期設定中は、前記DMACは前記スレーブ・デバイスとして動作し、前記マスタ・デバイスとして動作しているマイクロプロセッサからのアクセスを受け入れることを特徴とする請求項9に記載のコンピュータ・システム。

【請求項13】

前記スレーブ・デバイスは、複数の前記第2のプロセスIDを保持し、

前記スレーブ・デバイスは、前記第1のプロセスIDと前記複数の第2の第2のプロセスIDの内のいずれか一つの値とが所定の関係を満たすときに、前記トランザクションを受け入れることを特徴とする請求項1に記載のコンピュータ・システム。

【請求項14】

前記スレーブ・デバイスは第2のレジスタを有し、

前記第2のプロセスIDはこの第2のレジスタに格納されていることを特徴とする請求項1に記載のコンピュータ・システム。

【請求項15】

前記第2のプロセスIDは固定値であることを特徴とする請求項1に記載のコンピュータ・システム。

【請求項16】

ソフトウエア・プロセス番号に関連づけられた第1のプロセスIDを格納する第1のレジスタを有するマスタ・デバイスと、アクセスを許可する第2のプロセスIDを保持するスレーブ・デバイスと、マスタ・デバイスとスレーブ・デバイスに接続されたシステム・バスとを有するコンピュータ・システムにおいて、

トランザクションを生成するときに、システム・バス上に第1のプロセスIDを送出することを特徴とするマスタ・デバイス。

【請求項17】

ソフトウエア・プロセス番号に関連づけられた第1のプロセスIDを格納する第1のレジスタを有するマスタ・デバイスと、アクセスを許可する第2のプロセスIDを保持するスレーブ・デバイスと、マスタ・デバイスとスレーブ・デバイスに接続されたシステム・バスとを有するコンピュータ・システムにおいて、

第1のプロセスIDと第2のプロセスIDとが所定の関係を満たすときに、トランザクションを受け入れることを特徴とするスレーブ・デバイス。

【請求項18】

前記スレーブ・デバイスは第2のレジスタを有し、

前記第2のプロセスIDはこの第2のレジスタに格納されていることを特徴とする請求項17に記載のスレーブ・デバイス。

【請求項19】

前記第2のプロセスIDは固定値であることを特徴とする請求項17に記載のスレーブ・デバイス。

【請求項20】

ソフトウエア・プロセス番号に関連づけられた第1のプロセスIDを格納する第1のレジスタを有するマスタ・デバイスと、アクセスを許可する第2のプロセスIDを保持するスレーブ・デバイスと、マスタ・デバイスとスレーブ・デバイスに接続されたシステム・バスとを有するコンピュータ・システムの処理方法において、

マスタ・デバイスは、トランザクションを生成するときに、システム・バス上に第1のプロセスIDを送出し、

スレーブ・デバイスは、第1のプロセスIDと第2のプロセスIDとが所定の関係を満たすときに、トランザクションを受け入れることを特徴とするコンピュータ・システムの処理方法。

【請求項21】

前記スレーブ・デバイスは、前記第1のプロセスIDと前記第2のプロセスIDとを比較して一致したときのみアクセスを許可することを特徴とする請求項20に記載のコンピュータ・システムの処理方法。

【請求項22】

前記マスタ・デバイスは、前記システム・バスのアドレス・バスにアクセス先アドレスを出力し、

前記スレーブ・デバイスは、前記アクセス先アドレスが、割り付けられたアドレス範囲に含まれかつ前記比較が一致したときに、前記トランザクションに正常に応答することを決定して前記アクセスを許可することを特徴とする請求項21に記載のコンピュータ・システムの処理方法。

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【公開番号】特開2010−250470(P2010−250470A)

【公開日】平成22年11月4日(2010.11.4)

【国際特許分類】

【出願番号】特願2009−97813(P2009−97813)

【出願日】平成21年4月14日(2009.4.14)

【出願人】(000004237)日本電気株式会社 (19,353)

【Fターム(参考)】

【公開日】平成22年11月4日(2010.11.4)

【国際特許分類】

【出願日】平成21年4月14日(2009.4.14)

【出願人】(000004237)日本電気株式会社 (19,353)

【Fターム(参考)】

[ Back to top ]