サンプリング周波数変換装置

【課題】必要なサンプル信号のみを算出して分数比で入力信号のサンプリング周波数を変換するサンプリング周波数変換装置を提供する。

【解決手段】サンプリング周波数変換装置は、補間フィルタを備え、前記補間フィルタは、カスケード接続された複数の遅延器と、前記補間フィルタに入力された入力信号及び前記遅延器が出力する信号とタップ係数とを乗算してサンプル信号を得る複数の乗算器と、前記複数の乗算器が出力した前記サンプル信号を加算する複数の加算器と、第2クロック信号のパルス数をカウントするカウンタ回路を有し、前記カウンタ回路のカウント値に応じたタップ係数を前記複数の乗算器に出力することで、前記入力信号の第1サンプリング周波数を第2サンプリング周波数に変換する。

【解決手段】サンプリング周波数変換装置は、補間フィルタを備え、前記補間フィルタは、カスケード接続された複数の遅延器と、前記補間フィルタに入力された入力信号及び前記遅延器が出力する信号とタップ係数とを乗算してサンプル信号を得る複数の乗算器と、前記複数の乗算器が出力した前記サンプル信号を加算する複数の加算器と、第2クロック信号のパルス数をカウントするカウンタ回路を有し、前記カウンタ回路のカウント値に応じたタップ係数を前記複数の乗算器に出力することで、前記入力信号の第1サンプリング周波数を第2サンプリング周波数に変換する。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、入力信号のサンプリング周波数を分数比で変換することができるサンプリング周波数変換装置に関する。

【背景技術】

【0002】

下記特許文献1には、入力信号のサンプリング周波数をM倍にアップサンプリングしてから、1/N倍にダウンサンプリングすることで(1/Nに間引くことで)、入力信号のサンプリング周波数を、分数比M/Nに変換することが記載されている。

【0003】

また、下記特許文献2には、アップサンプリングする場合に、各入力信号の各離散データ間に0を挿入することなく、補間処理を行うことができるサンプリングレート変換装置が記載されている。

【先行技術文献】

【特許文献】

【0004】

【特許文献1】特開2009−004848号公報

【特許文献2】特開2009−232079号公報

【発明の概要】

【発明が解決しようとする課題】

【0005】

しかしながら、上記特許文献1は、入力信号のサンプリング周波数をアップサンプリングからダウンサンプリングするので、実際に必要のないサンプル信号を算出してしまい、計算量が増大する。また、前記特許文献2は、離散データ間に0を挿入することなく、補間処理を行うことができるが、上記特許文献1に記載された手法でしか、入力信号のサンプリング周波数を分数比に変換することができない。

【0006】

そこで本発明は、かかる従来の問題点に鑑みてなされたものであり、必要なサンプル信号のみを算出して分数比で入力信号のサンプリング周波数を変換するサンプリング周波数変換装置を提供することを目的とする。

【課題を解決するための手段】

【0007】

上記目的を達成するために、本発明は、第1クロック信号に同期した前記入力信号の幅を変更するFIFO回路と、FIFO回路が出力する前記入力信号の第1サンプリング周波数を、前記第1サンプリング周波数のM/N倍の分数比である第2サンプリング周波数に変換する補間フィルタを備え、前記FIFO回路は、前記第2サンプリング周波数と同じ周波数の第2クロック信号を用いて、入力された前記入力信号の幅を変更して、前記補間フィルタに出力し、前記補間フィルタは、カスケード接続された複数の遅延器と、前記補間フィルタに入力された前記入力信号及び前記遅延器が出力する信号とタップ係数とを乗算してサンプル信号を得る複数の乗算器と、前記複数の乗算器が出力した前記サンプル信号を加算する複数の加算器と、前記第2クロック信号のパルス数をカウントするカウンタ回路を有し、該カウンタ回路のカウント値に応じたタップ係数を前記複数の乗算器に出力することで、前記入力信号の前記第1サンプリング周波数を前記第2サンプリング周波数に変換することを特徴とする。

【0008】

前記FIFO回路は、前記第1サンプリング周波数及び前記第2サンプリング周波数に応じて前記入力信号の幅を変更し、前記カウンタ回路のカウント値に応じたタップ係数は、前記第1サンプリング周波数及び前記第2サンプリング周波数に応じて決められる。

【0009】

前記カウンタ回路のカウント値に応じたタップ係数は、前記入力信号の前記第1サンプリング周波数を前記第2サンプリング周波数に変換するための前記サンプル信号を算出するのに必要なタップ係数である。

【0010】

前記FIFO回路は、前記第1サンプリング周波数を前記第2サンプリング周波数に変換するための前記サンプル信号を算出するのに必要な幅に、前記入力信号の幅を変更する。

【発明の効果】

【0011】

本願発明によれば、必要なサンプルのみを算出して分数比で入力信号のサンプリング周波数を変換することができ、サンプリング周波数の変換に必要な計算量を減少させることができる。

【図面の簡単な説明】

【0012】

【図1】実施の形態に係る補間フィルタの構成を示す図である。

【図2】サンプリング周波数を8倍の周波数に変換する場合のタイムチャートを示す図である。

【図3】図2において斜線で示したタップ係数のみを用いて、乗算器が出力する信号のタイムチャートを示す図である。

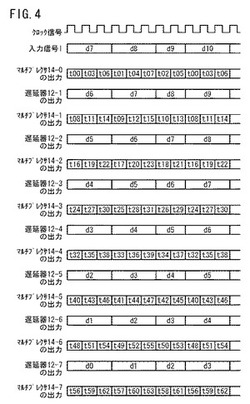

【図4】各乗算器が図3に示すような信号を出力するように、補間フィルタに入力される入力信号Iと、マルチプレクサが選択して出力するタップ係数のタイムチャートである。

【図5】サンプリング周波数変換装置の構成を示す図である。

【図6】図5に示すFIFO回路に入力される入力信号I及びFIFO回路から出力される入力信号Iを示す図である。

【発明を実施するための形態】

【0013】

本発明に係るサンプリング周波数変換装置について、好適な実施の形態を掲げ、添付の図面を参照しながら以下、詳細に説明する。

【0014】

図1は、実施の形態に係るサンプリング周波数変換装置の補間フィルタ10の構成を示す図である。補間フィルタ10は、M/N倍(本実施の形態においては、M=8,N=3とする。つまり、8/3倍)に入力信号のサンプリング周波数を変換するものであり、入力信号Iのサンプリング周波数(第1サンプリング周波数)をf1、補間フィルタ10の出力信号Oのサンプリング周波数(第2サンプリング周波数)をf2とする。

【0015】

補間フィルタ10は、複数の遅延器12、複数のマルチプレクサ14、複数の乗算器16、複数の加算器18、及びカウンタ回路20を有する。遅延器12は、入力された信号を所定時間遅延させて出力する。複数の遅延器12は、カスケード接続されており、初段の遅延器12−1には、入力信号Iが入力され、2段以降の遅延器12(12−2〜12−7)は、前段の遅延器12(12−1〜12−6)の出力が入力される。この遅延器12は、信号が入力されるタイミングで、前回入力された信号を出力するものであり、各遅延器12の出力タイミングは互いに同期している。なお、遅延器12−1〜12−7を総称して遅延器12と呼ぶ。

【0016】

各マルチプレクサ14は、8つのタップ係数tn(n=00〜63)が入力され、入力される8つのタップ係数tnのうち、カウンタ回路20から送られてくるカウント値にしたがって、何れか1つのタップ係数を選択して出力する。詳しくは、マルチプレクサ14−0には、タップ係数t00〜t07が入力され、マルチプレクサ14−1には、タップ係数t08〜t15が入力され、マルチプレクサ14−2には、タップ係数t16〜t23が入力され、マルチプレクサ14−3には、タップ係数t24〜t31が入力され、マルチプレクサ14−4には、タップ係数t32〜t39が入力され、マルチプレクサ14−5には、タップ係数t40〜t47が入力され、マルチプレクサ14−6には、タップ係数t48〜t55が入力され、マルチプレクサ14−7には、タップ係数t56〜t63が入力される。このタップ係数tnの「tn(t00〜t63)」は、タップ係数の値そのものを示すものではなく、入力されるタップ係数の番号を示す。なお、マルチプレクサ14−0〜14−7を総称してマルチプレクサ14と呼ぶ。

【0017】

乗算器16は、入力信号I又は遅延器12によって遅延された入力信号Iと、マルチプレクサ14が出力したタップ係数tnを乗算してサンプル信号を得る。詳しくは、乗算器16−0は、入力信号Iとマルチプレクサ14−0が出力するタップ係数tnとを乗算し、乗算器16−1は、遅延器12−1が出力する信号と、マルチプレクサ14−1が出力するタップ係数tnとを乗算し、乗算器16−2は、遅延器12−2が出力する信号と、マルチプレクサ14−2が出力するタップ係数tnとを乗算し、乗算器16−3は、遅延器12−3が出力する信号と、マルチプレクサ14−3が出力するタップ係数tnとを乗算し、乗算器16−4は、遅延器12−4が出力する信号と、マルチプレクサ14−4が出力するタップ係数tnとを乗算し、乗算器16−5は、遅延器12−5が出力する信号と、マルチプレクサ14−5が出力するタップ係数tnとを乗算し、乗算器16−6は、遅延器12−6が出力する信号と、マルチプレクサ14−6が出力するタップ係数tnとを乗算し、乗算器16−7は、遅延器12−7が出力する信号と、マルチプレクサ14−7が出力するタップ係数tnとを乗算する。

【0018】

複数の加算器18は、複数の乗算器16が出力するサンプル信号を加算して出力する。この全ての加算器18によって加算されたサンプル信号がサンプリング周波数f2の出力信号Oとなる。詳しくは、加算器18−1は、乗算器16−0及び乗算器16−1が出力したサンプル信号を加算し、加算器18−2は、加算器18−1が出力した信号と乗算器16−2が出力したサンプル信号とを加算し、加算器18−3は、加算器18−2が出力した信号と乗算器16−3が出力したサンプル信号とを加算し、加算器18−4は、加算器18−3が出力した信号と乗算器16−4が出力したサンプル信号とを加算し、加算器18−5は、加算器18−4が出力した信号と乗算器16−5が出力したサンプル信号とを加算し、加算器18−6は、加算器18−5が出力した信号と乗算器16−6が出力したサンプル信号とを加算し、加算器18−7は、加算器18−6が出力した信号と乗算器16−7が出力したサンプル信号とを加算する。したがって、この加算器18−7が出力する信号が、サンプリング周波数f2の出力信号Oとなる。これにより、入力信号Iのサンプリング周波数f1がサンプリング周波数f2に変換される。

【0019】

なお、カウンタ回路20は、入力されたクロック信号をカウントしていき、各マルチプレクサ14にカウント値を出力する。

【0020】

次に、8/3倍へのサンプリング周波数f1の変換を説明する前に、図1の補間フィルタ10を用いて、サンプリング周波数f1を8倍に変換する場合について説明する。図2は、入力信号Iのサンプリング周波数f1を8倍の周波数に変換する場合のタイムチャートを示す図である。ここで、入力信号Iのサンプリング周波数f1を23.04MHzとし、クロック信号の周波数を23.04MHzの8倍である184.32MHzとする。

【0021】

図2に示すクロック信号は、補間フィルタ10のカウンタ回路20に入力される信号であり、クロック信号の8パルス分が入力信号Iの幅(時間幅)となる。入力信号Iは、信号d0、d1、d2、d3、d4、・・・、というように複数の信号を有し、補間フィルタ10には、信号d0、d1、d2、d3、d4、・・・、が入力信号Iとして順次入力される。つまり、信号d1が入力信号Iとして入力されると、次に信号d2が入力信号Iとして入力され、次に信号d3が入力信号Iとして入力される。

【0022】

また、各遅延器12は、クロック信号の8パルスに1回だけ、入力された信号を入力信号Iの幅(Δt)分遅延させるので、補間フィルタ10に入力信号Iとして信号d7が入力される場合は、遅延器12−1から出力される信号は、Δt遅延された入力信号I、つまり、信号d6であり、遅延器12−2から出力される信号は、2×Δt遅延された入力信号I、つまり、信号d5であり、遅延器12−3から出力される信号は、3×Δt遅延された入力信号I、つまり、信号d4であり、遅延器12−4から出力される信号は、4×Δt遅延された入力信号I、つまり、信号d3であり、遅延器12−5から出力される信号は、5×Δt遅延された入力信号I、つまり、信号d2であり、遅延器12−6から出力される信号は、6×Δt遅延された入力信号I、つまり、信号d1であり、遅延器12−7から出力される信号は、7×Δt遅延された入力信号I、つまり、信号d0である。

【0023】

カウンタ回路20は、入力されたクロック信号のパルス数をカウントし、カウントしたカウント値を各マルチプレクサ14に入力する。各マルチプレクサ14は、入力されたカウント値に応じて、入力される8つのタップ係数tnのうち、いずれか1つのタップ係数tnを選択して各乗算器16に出力する。

【0024】

各マルチプレクサ14は、カウント値が1の場合は、入力される複数のタップ係数tnのうち、番号が最も小さいタップ係数tnを選択して出力し、カウント値が2の場合は、入力される複数のタップ係数tnのうち、次に(2番目に)番号が小さいタップ係数tnを選択して出力し、カウント値が3の場合は、入力される複数のタップ係数tnのうち、3番目に番号が小さいタップ係数tnを選択して出力し、カウント値が4の場合は、入力される複数のタップ係数tnのうち、4番目に番号が小さいタップ係数tnを選択して出力し、カウント値が5の場合は、入力される複数のタップ係数tnのうち、5番目に番号が小さいタップ係数tnを選択して出力し、カウント値が6の場合は、入力される複数のタップ係数tnのうち、6番目に番号が小さいタップ係数tnを選択して出力し、カウント値が7の場合は、入力される複数のタップ係数tnのうち、7番目に番号が小さいタップ係数tnを選択して出力し、カウント値が8の場合は、入力される複数のタップ係数tnのうち、番号が一番大きいタップ係数tnを選択して出力する。なお、説明を簡単にするため、図2では、カウンタ回路20は、カウント値が8になるとリセットされる。

【0025】

例えば、入力されたカウント値が1の場合は、マルチプレクサ14−0は、タップ係数t00を選択して乗算器16−0に出力し、マルチプレクサ14−1は、タップ係数t08を選択して乗算器16−1に出力し、マルチプレクサ14−2は、タップ係数t16を選択して乗算器16−2に出力し、マルチプレクサ14−3は、タップ係数t24を選択して乗算器16−3に出力し、マルチプレクサ14−4は、タップ係数t32を選択して乗算器16−4に出力し、マルチプレクサ14−5は、タップ係数t40を選択して乗算器16−5に出力し、マルチプレクサ14−6は、タップ係数t48を選択して乗算器16−6に出力し、マルチプレクサ14−7は、タップ係数t56を選択して乗算器16−7に出力する。

【0026】

また、例えば、入力されたカウント値が5の場合は、マルチプレクサ14−0は、タップ係数t04を選択して乗算器16−0に出力し、マルチプレクサ14−1は、タップ係数t12を選択して乗算器16−1に出力し、マルチプレクサ14−2は、タップ係数t20を選択して乗算器16−2に出力し、マルチプレクサ14−3は、タップ係数t28を選択して乗算器16−3に出力し、マルチプレクサ14−4は、タップ係数t36を選択して乗算器16−4に出力し、マルチプレクサ14−5は、タップ係数t44を選択して乗算器16−5に出力し、マルチプレクサ14−6は、タップ係数t52を選択して乗算器16−6に出力し、マルチプレクサ14−7は、タップ係数t60を選択して乗算器16−7に出力する。

【0027】

したがって、乗算器16−0は、補間フィルタ10に入力信号Iとして信号d7が入力されている場合であって、カウント値が1の場合は、信号d7とタップ係数t00とを乗算し、カウント値が2の場合は、信号d7とタップ係数t01とを乗算し、カウント値が3の場合は、信号d7とタップ係数t02とを乗算し、カウント値が4の場合は、信号d7とタップ係数t03とを乗算し、カウント値が5の場合は、信号d7とタップ係数t04とを乗算し、カウント値が6の場合は、信号d7とタップ係数t05とを乗算し、カウント値が7の場合は、信号d7とタップ係数t06とを乗算し、カウント値が8の場合は、信号d7とタップ係数t07とを乗算する。

【0028】

また、乗算器16−1は、補間フィルタ10に入力信号Iとして信号d7が入力されている場合であって、カウント値が1の場合は、遅延器12−1が出力する信号(つまり、信号d6)とタップ係数t08とを乗算し、カウント値が2の場合は、遅延器12−1が出力する信号(つまり、信号d6)とタップ係数t09とを乗算し、カウント値が3の場合は、遅延器12−1が出力する信号(つまり、信号d6)とタップ係数t10とを乗算し、カウント値が4の場合は、遅延器12−1が出力する信号(つまり、信号d6)とタップ係数t11とを乗算し、カウント値が5の場合は、遅延器12−1が出力する信号(つまり、信号d6)とタップ係数t12とを乗算し、カウント値が6の場合は、遅延器12−1が出力する信号(つまり、信号d6)とタップ係数t13とを乗算し、カウント値が7の場合は、遅延器12−1が出力する信号(つまり、信号d6)とタップ係数t14とを乗算し、カウント値が8の場合は、遅延器12−1が出力する信号(つまり、信号d6)とタップ係数t15とを乗算する。

【0029】

乗算器16−2〜16−7も同様に、前段の遅延器12が出力した信号とカウント値に応じてマルチプレクサ14−2〜14−7が出力したタップ係数tnとを乗算していく。複数の加算器18は、各乗算器16が出力した信号を加算して、サンプリング周波数f2の出力信号Oを出力する。このときの出力信号Oのサンプリング周波数f2は、184.32MHzとなる。

【0030】

図2において、マルチプレクサ14が出力するタップ係数tnのうち、斜線で表しているタップ係数tnは、8倍に変換されたサンプリング周波数を1/3倍に変換した(1/3に間引いた)場合に、入力信号Iのサンプリング周波数の変換に用いられるタップ係数tnを示す。図2に示すように、8倍に変換されるサンプリング周波数を1/3倍に間引くため、用いられるタップ係数tnも、1/3に間引かれている。したがって、1/3に間引く場合は、各乗算器16が出力するサンプル信号は、図3に示すようになる。なお、図3においては、図2に示すタイムチャートを1/3に間引いたものなので、クロック信号の周波数は、184.32MHzの1/3倍である61.44MHzとなる。このときの、出力信号Oのサンプリング周波数f2は、入力信号Iのサンプリング周波数f1の8/3倍である、61.44MHzとなる。

【0031】

したがって、各乗算器16が図3に示すようなサンプル信号を出力するようにすれば、入力信号Iのサンプリング周波数f1を8/3倍の周波数に変換することができる。

【0032】

図4は、各乗算器16が図3に示すような信号を出力するように、補間フィルタ10に入力される入力信号Iと、マルチプレクサ14が選択して出力するタップ係数tnのタイムチャートである。ここで、クロック信号の周波数は、出力信号Oのサンプリング周波数f2と同じ、61.44MHzである。

【0033】

入力信号Iは、補間フィルタ10に入力される信号d7、d8は、クロック信号の3パルス分の幅を有し、信号d9は、クロック信号の2パルス分の幅を有する。この場合も、カウンタ回路20は、カウント値が8になるとリセットされる。

【0034】

各遅延器12は、入力された信号をクロック信号の幅分(クロック信号の3パルス分又は2パルス分)遅延させる。ここで、各遅延器12は、入力された信号をクロック信号の3パルス分遅延させ、3回に1回は、入力された信号をクロック信号の2パルス分遅延させる。各遅延器12の出力タイミングは互いに同期している。

【0035】

補間フィルタ10に入力信号Iとして、クロック信号の3パルス分の幅の信号d7が入力される期間は、遅延器12−1〜12−7から信号d6、d5、d4、d3、d2、d1、d0が出力され、補間フィルタ10に入力信号Iとして、クロック信号の3パルス分の幅の信号d8が入力される期間は、遅延器12−1〜12−7から信号d7、d6、d5、d4、d3、d2、d1が出力され、補間フィルタ10に入力信号Iとして、クロック信号の2パルス分の幅の信号d9が入力される期間は、遅延器12−1〜12−7から信号d8、d7、d6、d5、d4、d3、d2が出力される。

【0036】

また、各マルチプレクサ14は、カウント値が1の場合は、入力される複数のタップ係数tnのうち、最も番号が小さいタップ係数tnを選択して出力し、カウント値が2の場合は、入力される複数のタップ係数tnのうち、4番目に番号が小さいタップ係数tnを選択して出力し、カウント値が3の場合は、入力される複数のタップ係数tnのうち、7番目に番号が小さいタップ係数tnを選択して出力し、カウント値が4の場合は、入力される複数のタップ係数tnのうち、2番目に番号が小さいタップ係数tnを選択して出力し、カウント値が5の場合は、入力される複数のタップ係数tnのうち、5番目に番号が小さいタップ係数tnを選択して出力し、カウント値が6の場合は、入力される複数のタップ係数tnのうち、番号が最も大きいタップ係数tnを選択して出力し、カウント値が7の場合は、入力される複数のタップ係数tnのうち、3番目に番号が小さいタップ係数tnを選択して出力し、カウント値が8の場合は、入力される複数のタップ係数tnのうち、6番目に番号が小さいタップ係数tnを選択して出力する。

【0037】

例えば、入力されたカウント値が2の場合は、マルチプレクサ14−0は、タップ係数t03を選択して乗算器16−0に出力し、マルチプレクサ14−1は、タップ係数t11を選択して乗算器16−1に出力し、マルチプレクサ14−2は、タップ係数t19を選択して乗算器16−2に出力し、マルチプレクサ14−3は、タップ係数t27を選択して乗算器16−3に出力し、マルチプレクサ14−4は、タップ係数t35を選択して乗算器16−4に出力し、マルチプレクサ14−5は、タップ係数t43を選択して乗算器16−5に出力し、マルチプレクサ14−6は、タップ係数t51を選択して乗算器16−6に出力し、マルチプレクサ14−7は、タップ係数t59を選択して乗算器16−7に出力する。

【0038】

また、例えば、入力されたカウント値が6の場合は、マルチプレクサ14−0は、タップ係数t07を選択して乗算器16−0に出力し、マルチプレクサ14−1は、タップ係数t15を選択して乗算器16−1に出力し、マルチプレクサ14−2は、タップ係数t23を選択して乗算器16−2に出力し、マルチプレクサ14−3は、タップ係数t31を選択して乗算器16−3に出力し、マルチプレクサ14−4は、タップ係数t39を選択して乗算器16−4に出力し、マルチプレクサ14−5は、タップ係数t47を選択して乗算器16−5に出力し、マルチプレクサ14−6は、タップ係数t55を選択して乗算器16−6に出力し、マルチプレクサ14−7は、タップ係数t63を選択して乗算器16−7に出力する。

【0039】

また、例えば、入力されたカウント値が8の場合は、マルチプレクサ14−0は、タップ係数t05を選択して乗算器16−0に出力し、マルチプレクサ14−1は、タップ係数t13を選択して乗算器16−1に出力し、マルチプレクサ14−2は、タップ係数t21を選択して乗算器16−2に出力し、マルチプレクサ14−3は、タップ係数t29を選択して乗算器16−3に出力し、マルチプレクサ14−4は、タップ係数t37を選択して乗算器16−4に出力し、マルチプレクサ14−5は、タップ係数t45を選択して乗算器16−5に出力し、マルチプレクサ14−6は、タップ係数t53を選択して乗算器16−6に出力し、マルチプレクサ14−7は、タップ係数t61を選択して乗算器16−7に出力する。

【0040】

したがって、カウント値が2の場合は、乗算器16−0は、信号d7とタップ係数t03とを乗算し、乗算器16−1は、信号d6とタップ係数t11とを乗算し、乗算器16−2は、信号d5とタップ係数t19とを乗算し、乗算器16−3は、信号d4とタップ係数t27とを乗算し、乗算器16−4は、信号d3とタップ係数t35とを乗算し、乗算器16−5は、信号d2とタップ係数t43とを乗算し、乗算器16−6は、信号d1とタップ係数t51とを乗算し、乗算器16−7は、信号d0とタップ係数t59とを乗算する。

【0041】

また、カウント値が6の場合は、乗算器16−0は、信号d8とタップ係数t07とを乗算し、乗算器16−1は、信号d7とタップ係数t15とを乗算し、乗算器16−2は、信号d6とタップ係数t23とを乗算し、乗算器16−3は、信号d5とタップ係数t31とを乗算し、乗算器16−4は、信号d4とタップ係数t39とを乗算し、乗算器16−5は、信号d3とタップ係数t47とを乗算し、乗算器16−6は、信号d2とタップ係数t55とを乗算し、乗算器16−7は、信号d1とタップ係数t63とを乗算する。

【0042】

また、カウント値が8の場合は、乗算器16−0は、信号d9とタップ係数t05とを乗算し、乗算器16−1は、信号d8とタップ係数t13とを乗算し、乗算器16−2は、信号d7とタップ係数t21とを乗算し、乗算器16−3は、信号d6とタップ係数t29とを乗算し、乗算器16−4は、信号d5とタップ係数t37とを乗算し、乗算器16−5は、信号d4とタップ係数t45とを乗算し、乗算器16−6は、信号d3とタップ係数t53とを乗算し、乗算器16−7は、信号d2とタップ係数t61とを乗算する。

【0043】

このように、カウンタ回路20がカウントしたカウント値に応じて各マルチプレクサ14が出力するタップ係数tnを図4に示すように定めておけば、つまり、各マルチプレクサ14が、サンプリング周波数f1をサンプリング周波数f2に変換するためのサンプル信号を算出するのに必要なタップ係数を、カウント値に応じて出力するように定めておけば、各乗算器16が出力する信号は、図3に示すようになり、入力信号Iのサンプリング周波数を8/3倍のサンプリング周波数に変換することができる。

【0044】

次に、補間フィルタ10に、図4に示すような入力信号Iを入力するために、サンプリング周波数変換装置30は、図5に示すように、補間フィルタ10と、補間フィルタ10の前段に設けられたFIFO回路32とを有する。FIFO回路32には、サンプリング周波数f1(23.04MHz)の入力信号Iと、23.04MHzのクロック信号1(第1クロック信号)と、61.44MHzのクロック信号2(第2クロック信号)とが入力される。なお、出力信号Oのサンプリング周波数f2は、61.44MHzとする。

【0045】

図6に示すように、FIFO回路32には、クロック信号1と同期して、信号d1、d2、d3、・・・・、の入力信号Iが入力される。FIFO回路32は、クロック信号1に同期して、入力された入力信号Iをライトポインタwpn(n=00,01,02,03,・・・)に対応する記憶領域に記憶する。例えば、FIFO回路32は、信号d7が入力されると、ライトポインタwp07に対応する記憶領域に信号d7を記憶し、信号d8が入力されると、ライトポインタwp08に対応する記憶領域に信号d8を記憶し、信号d9が入力されると、ライトポインタwp09に対応する記憶領域に信号d9を記憶させる。

【0046】

また、FIFO回路32は、クロック信号2に基づいて、リードポインタrpn(n=00,01,02,03,・・・)に対応した記憶領域に記憶した入力信号を出力する。例えば、FIFO回路32は、信号d7が記憶された後に、リードポインタrp07に対応する記憶領域に記憶された信号d7を、クロック信号2の3パルス分出力する。そして、信号d8が記憶された後に、リードポインタrp08に対応する記憶領域に記憶された信号d8を、クロック信号2の3パルス分出力する。そして、信号d9が記憶された後に、リードポインタrp09に対応する記憶領域に記憶された信号d9を、クロック信号2の2パルス分出力する。つまり、FIFO回路32は、サンプリング周波数f1をサンプリング周波数f2に変換するためのサンプル信号を算出するのに必要な幅に、入力信号Iの幅を変更する。これにより、図4に示すような入力信号Iを補間フィルタ10に出力することができる。なお、ライトポインタwpn及びリードポインタrpnに対応する記憶領域は同一である。例えば、ライトポインタwp07及びリードポインタrp07に対応する記憶領域は同一である。

【0047】

このように、入力信号Iのサンプリング周波数の8/3倍のサンプリング周波数の変換に必要なタップ係数のみを用いてサンプル信号を算出するので、分数比で入力信号のサンプリング周波数を変換することができ、サンプリング周波数の変換に必要な計算量を減少させることができる。また、出力信号Oのサンプリング周波数より高周波数のクロック信号が不要となる。つまり、入力信号Iのサンプリング周波数f1を8倍にしてから、1/3倍に間引く場合であって、サンプリング周波数f1が23.04MHzの場合、184.32MHzのクロック信号が必要となるが、出力信号Oのサンプリング周波数f2より高周波数になってしまうが、本実施の形態では、出力信号Oのサンプリング周波数f2より低周波数である、23.04MHzのクロック信号1と61.44MHzのクロック信号2があれば良い。

【0048】

以上、本発明を実施の形態を用いて説明したが、本発明の技術的範囲は上記実施の形態に記載の範囲には限定されない。上記実施の形態に、多様な変更または改良を加えることが可能であることが当業者に明らかである。その様な変更または改良を加えた形態も本発明の技術的範囲に含まれ得ることが、特許請求の範囲の記載から明らかである。

【符号の説明】

【0049】

10…補間フィルタ 12…遅延器

14…マルチプレクサ 16…乗算器

18…加算器 20…カウンタ回路

30…サンプリング周波数変換装置 32…FIFO回路

【技術分野】

【0001】

本発明は、入力信号のサンプリング周波数を分数比で変換することができるサンプリング周波数変換装置に関する。

【背景技術】

【0002】

下記特許文献1には、入力信号のサンプリング周波数をM倍にアップサンプリングしてから、1/N倍にダウンサンプリングすることで(1/Nに間引くことで)、入力信号のサンプリング周波数を、分数比M/Nに変換することが記載されている。

【0003】

また、下記特許文献2には、アップサンプリングする場合に、各入力信号の各離散データ間に0を挿入することなく、補間処理を行うことができるサンプリングレート変換装置が記載されている。

【先行技術文献】

【特許文献】

【0004】

【特許文献1】特開2009−004848号公報

【特許文献2】特開2009−232079号公報

【発明の概要】

【発明が解決しようとする課題】

【0005】

しかしながら、上記特許文献1は、入力信号のサンプリング周波数をアップサンプリングからダウンサンプリングするので、実際に必要のないサンプル信号を算出してしまい、計算量が増大する。また、前記特許文献2は、離散データ間に0を挿入することなく、補間処理を行うことができるが、上記特許文献1に記載された手法でしか、入力信号のサンプリング周波数を分数比に変換することができない。

【0006】

そこで本発明は、かかる従来の問題点に鑑みてなされたものであり、必要なサンプル信号のみを算出して分数比で入力信号のサンプリング周波数を変換するサンプリング周波数変換装置を提供することを目的とする。

【課題を解決するための手段】

【0007】

上記目的を達成するために、本発明は、第1クロック信号に同期した前記入力信号の幅を変更するFIFO回路と、FIFO回路が出力する前記入力信号の第1サンプリング周波数を、前記第1サンプリング周波数のM/N倍の分数比である第2サンプリング周波数に変換する補間フィルタを備え、前記FIFO回路は、前記第2サンプリング周波数と同じ周波数の第2クロック信号を用いて、入力された前記入力信号の幅を変更して、前記補間フィルタに出力し、前記補間フィルタは、カスケード接続された複数の遅延器と、前記補間フィルタに入力された前記入力信号及び前記遅延器が出力する信号とタップ係数とを乗算してサンプル信号を得る複数の乗算器と、前記複数の乗算器が出力した前記サンプル信号を加算する複数の加算器と、前記第2クロック信号のパルス数をカウントするカウンタ回路を有し、該カウンタ回路のカウント値に応じたタップ係数を前記複数の乗算器に出力することで、前記入力信号の前記第1サンプリング周波数を前記第2サンプリング周波数に変換することを特徴とする。

【0008】

前記FIFO回路は、前記第1サンプリング周波数及び前記第2サンプリング周波数に応じて前記入力信号の幅を変更し、前記カウンタ回路のカウント値に応じたタップ係数は、前記第1サンプリング周波数及び前記第2サンプリング周波数に応じて決められる。

【0009】

前記カウンタ回路のカウント値に応じたタップ係数は、前記入力信号の前記第1サンプリング周波数を前記第2サンプリング周波数に変換するための前記サンプル信号を算出するのに必要なタップ係数である。

【0010】

前記FIFO回路は、前記第1サンプリング周波数を前記第2サンプリング周波数に変換するための前記サンプル信号を算出するのに必要な幅に、前記入力信号の幅を変更する。

【発明の効果】

【0011】

本願発明によれば、必要なサンプルのみを算出して分数比で入力信号のサンプリング周波数を変換することができ、サンプリング周波数の変換に必要な計算量を減少させることができる。

【図面の簡単な説明】

【0012】

【図1】実施の形態に係る補間フィルタの構成を示す図である。

【図2】サンプリング周波数を8倍の周波数に変換する場合のタイムチャートを示す図である。

【図3】図2において斜線で示したタップ係数のみを用いて、乗算器が出力する信号のタイムチャートを示す図である。

【図4】各乗算器が図3に示すような信号を出力するように、補間フィルタに入力される入力信号Iと、マルチプレクサが選択して出力するタップ係数のタイムチャートである。

【図5】サンプリング周波数変換装置の構成を示す図である。

【図6】図5に示すFIFO回路に入力される入力信号I及びFIFO回路から出力される入力信号Iを示す図である。

【発明を実施するための形態】

【0013】

本発明に係るサンプリング周波数変換装置について、好適な実施の形態を掲げ、添付の図面を参照しながら以下、詳細に説明する。

【0014】

図1は、実施の形態に係るサンプリング周波数変換装置の補間フィルタ10の構成を示す図である。補間フィルタ10は、M/N倍(本実施の形態においては、M=8,N=3とする。つまり、8/3倍)に入力信号のサンプリング周波数を変換するものであり、入力信号Iのサンプリング周波数(第1サンプリング周波数)をf1、補間フィルタ10の出力信号Oのサンプリング周波数(第2サンプリング周波数)をf2とする。

【0015】

補間フィルタ10は、複数の遅延器12、複数のマルチプレクサ14、複数の乗算器16、複数の加算器18、及びカウンタ回路20を有する。遅延器12は、入力された信号を所定時間遅延させて出力する。複数の遅延器12は、カスケード接続されており、初段の遅延器12−1には、入力信号Iが入力され、2段以降の遅延器12(12−2〜12−7)は、前段の遅延器12(12−1〜12−6)の出力が入力される。この遅延器12は、信号が入力されるタイミングで、前回入力された信号を出力するものであり、各遅延器12の出力タイミングは互いに同期している。なお、遅延器12−1〜12−7を総称して遅延器12と呼ぶ。

【0016】

各マルチプレクサ14は、8つのタップ係数tn(n=00〜63)が入力され、入力される8つのタップ係数tnのうち、カウンタ回路20から送られてくるカウント値にしたがって、何れか1つのタップ係数を選択して出力する。詳しくは、マルチプレクサ14−0には、タップ係数t00〜t07が入力され、マルチプレクサ14−1には、タップ係数t08〜t15が入力され、マルチプレクサ14−2には、タップ係数t16〜t23が入力され、マルチプレクサ14−3には、タップ係数t24〜t31が入力され、マルチプレクサ14−4には、タップ係数t32〜t39が入力され、マルチプレクサ14−5には、タップ係数t40〜t47が入力され、マルチプレクサ14−6には、タップ係数t48〜t55が入力され、マルチプレクサ14−7には、タップ係数t56〜t63が入力される。このタップ係数tnの「tn(t00〜t63)」は、タップ係数の値そのものを示すものではなく、入力されるタップ係数の番号を示す。なお、マルチプレクサ14−0〜14−7を総称してマルチプレクサ14と呼ぶ。

【0017】

乗算器16は、入力信号I又は遅延器12によって遅延された入力信号Iと、マルチプレクサ14が出力したタップ係数tnを乗算してサンプル信号を得る。詳しくは、乗算器16−0は、入力信号Iとマルチプレクサ14−0が出力するタップ係数tnとを乗算し、乗算器16−1は、遅延器12−1が出力する信号と、マルチプレクサ14−1が出力するタップ係数tnとを乗算し、乗算器16−2は、遅延器12−2が出力する信号と、マルチプレクサ14−2が出力するタップ係数tnとを乗算し、乗算器16−3は、遅延器12−3が出力する信号と、マルチプレクサ14−3が出力するタップ係数tnとを乗算し、乗算器16−4は、遅延器12−4が出力する信号と、マルチプレクサ14−4が出力するタップ係数tnとを乗算し、乗算器16−5は、遅延器12−5が出力する信号と、マルチプレクサ14−5が出力するタップ係数tnとを乗算し、乗算器16−6は、遅延器12−6が出力する信号と、マルチプレクサ14−6が出力するタップ係数tnとを乗算し、乗算器16−7は、遅延器12−7が出力する信号と、マルチプレクサ14−7が出力するタップ係数tnとを乗算する。

【0018】

複数の加算器18は、複数の乗算器16が出力するサンプル信号を加算して出力する。この全ての加算器18によって加算されたサンプル信号がサンプリング周波数f2の出力信号Oとなる。詳しくは、加算器18−1は、乗算器16−0及び乗算器16−1が出力したサンプル信号を加算し、加算器18−2は、加算器18−1が出力した信号と乗算器16−2が出力したサンプル信号とを加算し、加算器18−3は、加算器18−2が出力した信号と乗算器16−3が出力したサンプル信号とを加算し、加算器18−4は、加算器18−3が出力した信号と乗算器16−4が出力したサンプル信号とを加算し、加算器18−5は、加算器18−4が出力した信号と乗算器16−5が出力したサンプル信号とを加算し、加算器18−6は、加算器18−5が出力した信号と乗算器16−6が出力したサンプル信号とを加算し、加算器18−7は、加算器18−6が出力した信号と乗算器16−7が出力したサンプル信号とを加算する。したがって、この加算器18−7が出力する信号が、サンプリング周波数f2の出力信号Oとなる。これにより、入力信号Iのサンプリング周波数f1がサンプリング周波数f2に変換される。

【0019】

なお、カウンタ回路20は、入力されたクロック信号をカウントしていき、各マルチプレクサ14にカウント値を出力する。

【0020】

次に、8/3倍へのサンプリング周波数f1の変換を説明する前に、図1の補間フィルタ10を用いて、サンプリング周波数f1を8倍に変換する場合について説明する。図2は、入力信号Iのサンプリング周波数f1を8倍の周波数に変換する場合のタイムチャートを示す図である。ここで、入力信号Iのサンプリング周波数f1を23.04MHzとし、クロック信号の周波数を23.04MHzの8倍である184.32MHzとする。

【0021】

図2に示すクロック信号は、補間フィルタ10のカウンタ回路20に入力される信号であり、クロック信号の8パルス分が入力信号Iの幅(時間幅)となる。入力信号Iは、信号d0、d1、d2、d3、d4、・・・、というように複数の信号を有し、補間フィルタ10には、信号d0、d1、d2、d3、d4、・・・、が入力信号Iとして順次入力される。つまり、信号d1が入力信号Iとして入力されると、次に信号d2が入力信号Iとして入力され、次に信号d3が入力信号Iとして入力される。

【0022】

また、各遅延器12は、クロック信号の8パルスに1回だけ、入力された信号を入力信号Iの幅(Δt)分遅延させるので、補間フィルタ10に入力信号Iとして信号d7が入力される場合は、遅延器12−1から出力される信号は、Δt遅延された入力信号I、つまり、信号d6であり、遅延器12−2から出力される信号は、2×Δt遅延された入力信号I、つまり、信号d5であり、遅延器12−3から出力される信号は、3×Δt遅延された入力信号I、つまり、信号d4であり、遅延器12−4から出力される信号は、4×Δt遅延された入力信号I、つまり、信号d3であり、遅延器12−5から出力される信号は、5×Δt遅延された入力信号I、つまり、信号d2であり、遅延器12−6から出力される信号は、6×Δt遅延された入力信号I、つまり、信号d1であり、遅延器12−7から出力される信号は、7×Δt遅延された入力信号I、つまり、信号d0である。

【0023】

カウンタ回路20は、入力されたクロック信号のパルス数をカウントし、カウントしたカウント値を各マルチプレクサ14に入力する。各マルチプレクサ14は、入力されたカウント値に応じて、入力される8つのタップ係数tnのうち、いずれか1つのタップ係数tnを選択して各乗算器16に出力する。

【0024】

各マルチプレクサ14は、カウント値が1の場合は、入力される複数のタップ係数tnのうち、番号が最も小さいタップ係数tnを選択して出力し、カウント値が2の場合は、入力される複数のタップ係数tnのうち、次に(2番目に)番号が小さいタップ係数tnを選択して出力し、カウント値が3の場合は、入力される複数のタップ係数tnのうち、3番目に番号が小さいタップ係数tnを選択して出力し、カウント値が4の場合は、入力される複数のタップ係数tnのうち、4番目に番号が小さいタップ係数tnを選択して出力し、カウント値が5の場合は、入力される複数のタップ係数tnのうち、5番目に番号が小さいタップ係数tnを選択して出力し、カウント値が6の場合は、入力される複数のタップ係数tnのうち、6番目に番号が小さいタップ係数tnを選択して出力し、カウント値が7の場合は、入力される複数のタップ係数tnのうち、7番目に番号が小さいタップ係数tnを選択して出力し、カウント値が8の場合は、入力される複数のタップ係数tnのうち、番号が一番大きいタップ係数tnを選択して出力する。なお、説明を簡単にするため、図2では、カウンタ回路20は、カウント値が8になるとリセットされる。

【0025】

例えば、入力されたカウント値が1の場合は、マルチプレクサ14−0は、タップ係数t00を選択して乗算器16−0に出力し、マルチプレクサ14−1は、タップ係数t08を選択して乗算器16−1に出力し、マルチプレクサ14−2は、タップ係数t16を選択して乗算器16−2に出力し、マルチプレクサ14−3は、タップ係数t24を選択して乗算器16−3に出力し、マルチプレクサ14−4は、タップ係数t32を選択して乗算器16−4に出力し、マルチプレクサ14−5は、タップ係数t40を選択して乗算器16−5に出力し、マルチプレクサ14−6は、タップ係数t48を選択して乗算器16−6に出力し、マルチプレクサ14−7は、タップ係数t56を選択して乗算器16−7に出力する。

【0026】

また、例えば、入力されたカウント値が5の場合は、マルチプレクサ14−0は、タップ係数t04を選択して乗算器16−0に出力し、マルチプレクサ14−1は、タップ係数t12を選択して乗算器16−1に出力し、マルチプレクサ14−2は、タップ係数t20を選択して乗算器16−2に出力し、マルチプレクサ14−3は、タップ係数t28を選択して乗算器16−3に出力し、マルチプレクサ14−4は、タップ係数t36を選択して乗算器16−4に出力し、マルチプレクサ14−5は、タップ係数t44を選択して乗算器16−5に出力し、マルチプレクサ14−6は、タップ係数t52を選択して乗算器16−6に出力し、マルチプレクサ14−7は、タップ係数t60を選択して乗算器16−7に出力する。

【0027】

したがって、乗算器16−0は、補間フィルタ10に入力信号Iとして信号d7が入力されている場合であって、カウント値が1の場合は、信号d7とタップ係数t00とを乗算し、カウント値が2の場合は、信号d7とタップ係数t01とを乗算し、カウント値が3の場合は、信号d7とタップ係数t02とを乗算し、カウント値が4の場合は、信号d7とタップ係数t03とを乗算し、カウント値が5の場合は、信号d7とタップ係数t04とを乗算し、カウント値が6の場合は、信号d7とタップ係数t05とを乗算し、カウント値が7の場合は、信号d7とタップ係数t06とを乗算し、カウント値が8の場合は、信号d7とタップ係数t07とを乗算する。

【0028】

また、乗算器16−1は、補間フィルタ10に入力信号Iとして信号d7が入力されている場合であって、カウント値が1の場合は、遅延器12−1が出力する信号(つまり、信号d6)とタップ係数t08とを乗算し、カウント値が2の場合は、遅延器12−1が出力する信号(つまり、信号d6)とタップ係数t09とを乗算し、カウント値が3の場合は、遅延器12−1が出力する信号(つまり、信号d6)とタップ係数t10とを乗算し、カウント値が4の場合は、遅延器12−1が出力する信号(つまり、信号d6)とタップ係数t11とを乗算し、カウント値が5の場合は、遅延器12−1が出力する信号(つまり、信号d6)とタップ係数t12とを乗算し、カウント値が6の場合は、遅延器12−1が出力する信号(つまり、信号d6)とタップ係数t13とを乗算し、カウント値が7の場合は、遅延器12−1が出力する信号(つまり、信号d6)とタップ係数t14とを乗算し、カウント値が8の場合は、遅延器12−1が出力する信号(つまり、信号d6)とタップ係数t15とを乗算する。

【0029】

乗算器16−2〜16−7も同様に、前段の遅延器12が出力した信号とカウント値に応じてマルチプレクサ14−2〜14−7が出力したタップ係数tnとを乗算していく。複数の加算器18は、各乗算器16が出力した信号を加算して、サンプリング周波数f2の出力信号Oを出力する。このときの出力信号Oのサンプリング周波数f2は、184.32MHzとなる。

【0030】

図2において、マルチプレクサ14が出力するタップ係数tnのうち、斜線で表しているタップ係数tnは、8倍に変換されたサンプリング周波数を1/3倍に変換した(1/3に間引いた)場合に、入力信号Iのサンプリング周波数の変換に用いられるタップ係数tnを示す。図2に示すように、8倍に変換されるサンプリング周波数を1/3倍に間引くため、用いられるタップ係数tnも、1/3に間引かれている。したがって、1/3に間引く場合は、各乗算器16が出力するサンプル信号は、図3に示すようになる。なお、図3においては、図2に示すタイムチャートを1/3に間引いたものなので、クロック信号の周波数は、184.32MHzの1/3倍である61.44MHzとなる。このときの、出力信号Oのサンプリング周波数f2は、入力信号Iのサンプリング周波数f1の8/3倍である、61.44MHzとなる。

【0031】

したがって、各乗算器16が図3に示すようなサンプル信号を出力するようにすれば、入力信号Iのサンプリング周波数f1を8/3倍の周波数に変換することができる。

【0032】

図4は、各乗算器16が図3に示すような信号を出力するように、補間フィルタ10に入力される入力信号Iと、マルチプレクサ14が選択して出力するタップ係数tnのタイムチャートである。ここで、クロック信号の周波数は、出力信号Oのサンプリング周波数f2と同じ、61.44MHzである。

【0033】

入力信号Iは、補間フィルタ10に入力される信号d7、d8は、クロック信号の3パルス分の幅を有し、信号d9は、クロック信号の2パルス分の幅を有する。この場合も、カウンタ回路20は、カウント値が8になるとリセットされる。

【0034】

各遅延器12は、入力された信号をクロック信号の幅分(クロック信号の3パルス分又は2パルス分)遅延させる。ここで、各遅延器12は、入力された信号をクロック信号の3パルス分遅延させ、3回に1回は、入力された信号をクロック信号の2パルス分遅延させる。各遅延器12の出力タイミングは互いに同期している。

【0035】

補間フィルタ10に入力信号Iとして、クロック信号の3パルス分の幅の信号d7が入力される期間は、遅延器12−1〜12−7から信号d6、d5、d4、d3、d2、d1、d0が出力され、補間フィルタ10に入力信号Iとして、クロック信号の3パルス分の幅の信号d8が入力される期間は、遅延器12−1〜12−7から信号d7、d6、d5、d4、d3、d2、d1が出力され、補間フィルタ10に入力信号Iとして、クロック信号の2パルス分の幅の信号d9が入力される期間は、遅延器12−1〜12−7から信号d8、d7、d6、d5、d4、d3、d2が出力される。

【0036】

また、各マルチプレクサ14は、カウント値が1の場合は、入力される複数のタップ係数tnのうち、最も番号が小さいタップ係数tnを選択して出力し、カウント値が2の場合は、入力される複数のタップ係数tnのうち、4番目に番号が小さいタップ係数tnを選択して出力し、カウント値が3の場合は、入力される複数のタップ係数tnのうち、7番目に番号が小さいタップ係数tnを選択して出力し、カウント値が4の場合は、入力される複数のタップ係数tnのうち、2番目に番号が小さいタップ係数tnを選択して出力し、カウント値が5の場合は、入力される複数のタップ係数tnのうち、5番目に番号が小さいタップ係数tnを選択して出力し、カウント値が6の場合は、入力される複数のタップ係数tnのうち、番号が最も大きいタップ係数tnを選択して出力し、カウント値が7の場合は、入力される複数のタップ係数tnのうち、3番目に番号が小さいタップ係数tnを選択して出力し、カウント値が8の場合は、入力される複数のタップ係数tnのうち、6番目に番号が小さいタップ係数tnを選択して出力する。

【0037】

例えば、入力されたカウント値が2の場合は、マルチプレクサ14−0は、タップ係数t03を選択して乗算器16−0に出力し、マルチプレクサ14−1は、タップ係数t11を選択して乗算器16−1に出力し、マルチプレクサ14−2は、タップ係数t19を選択して乗算器16−2に出力し、マルチプレクサ14−3は、タップ係数t27を選択して乗算器16−3に出力し、マルチプレクサ14−4は、タップ係数t35を選択して乗算器16−4に出力し、マルチプレクサ14−5は、タップ係数t43を選択して乗算器16−5に出力し、マルチプレクサ14−6は、タップ係数t51を選択して乗算器16−6に出力し、マルチプレクサ14−7は、タップ係数t59を選択して乗算器16−7に出力する。

【0038】

また、例えば、入力されたカウント値が6の場合は、マルチプレクサ14−0は、タップ係数t07を選択して乗算器16−0に出力し、マルチプレクサ14−1は、タップ係数t15を選択して乗算器16−1に出力し、マルチプレクサ14−2は、タップ係数t23を選択して乗算器16−2に出力し、マルチプレクサ14−3は、タップ係数t31を選択して乗算器16−3に出力し、マルチプレクサ14−4は、タップ係数t39を選択して乗算器16−4に出力し、マルチプレクサ14−5は、タップ係数t47を選択して乗算器16−5に出力し、マルチプレクサ14−6は、タップ係数t55を選択して乗算器16−6に出力し、マルチプレクサ14−7は、タップ係数t63を選択して乗算器16−7に出力する。

【0039】

また、例えば、入力されたカウント値が8の場合は、マルチプレクサ14−0は、タップ係数t05を選択して乗算器16−0に出力し、マルチプレクサ14−1は、タップ係数t13を選択して乗算器16−1に出力し、マルチプレクサ14−2は、タップ係数t21を選択して乗算器16−2に出力し、マルチプレクサ14−3は、タップ係数t29を選択して乗算器16−3に出力し、マルチプレクサ14−4は、タップ係数t37を選択して乗算器16−4に出力し、マルチプレクサ14−5は、タップ係数t45を選択して乗算器16−5に出力し、マルチプレクサ14−6は、タップ係数t53を選択して乗算器16−6に出力し、マルチプレクサ14−7は、タップ係数t61を選択して乗算器16−7に出力する。

【0040】

したがって、カウント値が2の場合は、乗算器16−0は、信号d7とタップ係数t03とを乗算し、乗算器16−1は、信号d6とタップ係数t11とを乗算し、乗算器16−2は、信号d5とタップ係数t19とを乗算し、乗算器16−3は、信号d4とタップ係数t27とを乗算し、乗算器16−4は、信号d3とタップ係数t35とを乗算し、乗算器16−5は、信号d2とタップ係数t43とを乗算し、乗算器16−6は、信号d1とタップ係数t51とを乗算し、乗算器16−7は、信号d0とタップ係数t59とを乗算する。

【0041】

また、カウント値が6の場合は、乗算器16−0は、信号d8とタップ係数t07とを乗算し、乗算器16−1は、信号d7とタップ係数t15とを乗算し、乗算器16−2は、信号d6とタップ係数t23とを乗算し、乗算器16−3は、信号d5とタップ係数t31とを乗算し、乗算器16−4は、信号d4とタップ係数t39とを乗算し、乗算器16−5は、信号d3とタップ係数t47とを乗算し、乗算器16−6は、信号d2とタップ係数t55とを乗算し、乗算器16−7は、信号d1とタップ係数t63とを乗算する。

【0042】

また、カウント値が8の場合は、乗算器16−0は、信号d9とタップ係数t05とを乗算し、乗算器16−1は、信号d8とタップ係数t13とを乗算し、乗算器16−2は、信号d7とタップ係数t21とを乗算し、乗算器16−3は、信号d6とタップ係数t29とを乗算し、乗算器16−4は、信号d5とタップ係数t37とを乗算し、乗算器16−5は、信号d4とタップ係数t45とを乗算し、乗算器16−6は、信号d3とタップ係数t53とを乗算し、乗算器16−7は、信号d2とタップ係数t61とを乗算する。

【0043】

このように、カウンタ回路20がカウントしたカウント値に応じて各マルチプレクサ14が出力するタップ係数tnを図4に示すように定めておけば、つまり、各マルチプレクサ14が、サンプリング周波数f1をサンプリング周波数f2に変換するためのサンプル信号を算出するのに必要なタップ係数を、カウント値に応じて出力するように定めておけば、各乗算器16が出力する信号は、図3に示すようになり、入力信号Iのサンプリング周波数を8/3倍のサンプリング周波数に変換することができる。

【0044】

次に、補間フィルタ10に、図4に示すような入力信号Iを入力するために、サンプリング周波数変換装置30は、図5に示すように、補間フィルタ10と、補間フィルタ10の前段に設けられたFIFO回路32とを有する。FIFO回路32には、サンプリング周波数f1(23.04MHz)の入力信号Iと、23.04MHzのクロック信号1(第1クロック信号)と、61.44MHzのクロック信号2(第2クロック信号)とが入力される。なお、出力信号Oのサンプリング周波数f2は、61.44MHzとする。

【0045】

図6に示すように、FIFO回路32には、クロック信号1と同期して、信号d1、d2、d3、・・・・、の入力信号Iが入力される。FIFO回路32は、クロック信号1に同期して、入力された入力信号Iをライトポインタwpn(n=00,01,02,03,・・・)に対応する記憶領域に記憶する。例えば、FIFO回路32は、信号d7が入力されると、ライトポインタwp07に対応する記憶領域に信号d7を記憶し、信号d8が入力されると、ライトポインタwp08に対応する記憶領域に信号d8を記憶し、信号d9が入力されると、ライトポインタwp09に対応する記憶領域に信号d9を記憶させる。

【0046】

また、FIFO回路32は、クロック信号2に基づいて、リードポインタrpn(n=00,01,02,03,・・・)に対応した記憶領域に記憶した入力信号を出力する。例えば、FIFO回路32は、信号d7が記憶された後に、リードポインタrp07に対応する記憶領域に記憶された信号d7を、クロック信号2の3パルス分出力する。そして、信号d8が記憶された後に、リードポインタrp08に対応する記憶領域に記憶された信号d8を、クロック信号2の3パルス分出力する。そして、信号d9が記憶された後に、リードポインタrp09に対応する記憶領域に記憶された信号d9を、クロック信号2の2パルス分出力する。つまり、FIFO回路32は、サンプリング周波数f1をサンプリング周波数f2に変換するためのサンプル信号を算出するのに必要な幅に、入力信号Iの幅を変更する。これにより、図4に示すような入力信号Iを補間フィルタ10に出力することができる。なお、ライトポインタwpn及びリードポインタrpnに対応する記憶領域は同一である。例えば、ライトポインタwp07及びリードポインタrp07に対応する記憶領域は同一である。

【0047】

このように、入力信号Iのサンプリング周波数の8/3倍のサンプリング周波数の変換に必要なタップ係数のみを用いてサンプル信号を算出するので、分数比で入力信号のサンプリング周波数を変換することができ、サンプリング周波数の変換に必要な計算量を減少させることができる。また、出力信号Oのサンプリング周波数より高周波数のクロック信号が不要となる。つまり、入力信号Iのサンプリング周波数f1を8倍にしてから、1/3倍に間引く場合であって、サンプリング周波数f1が23.04MHzの場合、184.32MHzのクロック信号が必要となるが、出力信号Oのサンプリング周波数f2より高周波数になってしまうが、本実施の形態では、出力信号Oのサンプリング周波数f2より低周波数である、23.04MHzのクロック信号1と61.44MHzのクロック信号2があれば良い。

【0048】

以上、本発明を実施の形態を用いて説明したが、本発明の技術的範囲は上記実施の形態に記載の範囲には限定されない。上記実施の形態に、多様な変更または改良を加えることが可能であることが当業者に明らかである。その様な変更または改良を加えた形態も本発明の技術的範囲に含まれ得ることが、特許請求の範囲の記載から明らかである。

【符号の説明】

【0049】

10…補間フィルタ 12…遅延器

14…マルチプレクサ 16…乗算器

18…加算器 20…カウンタ回路

30…サンプリング周波数変換装置 32…FIFO回路

【特許請求の範囲】

【請求項1】

第1クロック信号に同期した入力信号の幅を変更するFIFO回路と、FIFO回路が出力する前記入力信号の第1サンプリング周波数を、前記第1サンプリング周波数のM/N倍の分数比である第2サンプリング周波数に変換する補間フィルタを備え、

前記FIFO回路は、前記第2サンプリング周波数と同じ周波数の第2クロック信号を用いて、入力された前記入力信号の幅を変更して、前記補間フィルタに出力し、

前記補間フィルタは、

カスケード接続された複数の遅延器と、前記補間フィルタに入力された前記入力信号及び前記遅延器が出力する信号とタップ係数とを乗算してサンプル信号を得る複数の乗算器と、前記複数の乗算器が出力した前記サンプル信号を加算する複数の加算器と、前記第2クロック信号のパルス数をカウントするカウンタ回路を有し、前記カウンタ回路のカウント値に応じたタップ係数を前記複数の乗算器に出力することで、前記入力信号の前記第1サンプリング周波数を前記第2サンプリング周波数に変換する

ことを特徴とするサンプリング周波数変換装置。

【請求項2】

請求項1に記載のサンプリング周波数変換装置において、

前記FIFO回路は、前記第1サンプリング周波数及び前記第2サンプリング周波数に応じて前記入力信号の幅を変更し、

前記カウンタ回路のカウント値に応じたタップ係数は、前記第1サンプリング周波数及び前記第2サンプリング周波数に応じて決められる

ことを特徴とするサンプリング周波数変換装置。

【請求項3】

請求項1又は2に記載のサンプリング周波数変換装置において、

前記カウンタ回路のカウント値に応じたタップ係数は、前記入力信号の前記第1サンプリング周波数を前記第2サンプリング周波数に変換するための前記サンプル信号を算出するのに必要なタップ係数である

ことを特徴とするサンプリング周波数変換装置。

【請求項4】

請求項1〜3のいずれか1項に記載のサンプリング周波数変換装置において、

前記FIFO回路は、前記第1サンプリング周波数を前記第2サンプリング周波数に変換するための前記サンプル信号を算出するのに必要な幅に、前記入力信号の幅を変更する

ことを特徴とするサンプリング周波数変換装置。

【請求項1】

第1クロック信号に同期した入力信号の幅を変更するFIFO回路と、FIFO回路が出力する前記入力信号の第1サンプリング周波数を、前記第1サンプリング周波数のM/N倍の分数比である第2サンプリング周波数に変換する補間フィルタを備え、

前記FIFO回路は、前記第2サンプリング周波数と同じ周波数の第2クロック信号を用いて、入力された前記入力信号の幅を変更して、前記補間フィルタに出力し、

前記補間フィルタは、

カスケード接続された複数の遅延器と、前記補間フィルタに入力された前記入力信号及び前記遅延器が出力する信号とタップ係数とを乗算してサンプル信号を得る複数の乗算器と、前記複数の乗算器が出力した前記サンプル信号を加算する複数の加算器と、前記第2クロック信号のパルス数をカウントするカウンタ回路を有し、前記カウンタ回路のカウント値に応じたタップ係数を前記複数の乗算器に出力することで、前記入力信号の前記第1サンプリング周波数を前記第2サンプリング周波数に変換する

ことを特徴とするサンプリング周波数変換装置。

【請求項2】

請求項1に記載のサンプリング周波数変換装置において、

前記FIFO回路は、前記第1サンプリング周波数及び前記第2サンプリング周波数に応じて前記入力信号の幅を変更し、

前記カウンタ回路のカウント値に応じたタップ係数は、前記第1サンプリング周波数及び前記第2サンプリング周波数に応じて決められる

ことを特徴とするサンプリング周波数変換装置。

【請求項3】

請求項1又は2に記載のサンプリング周波数変換装置において、

前記カウンタ回路のカウント値に応じたタップ係数は、前記入力信号の前記第1サンプリング周波数を前記第2サンプリング周波数に変換するための前記サンプル信号を算出するのに必要なタップ係数である

ことを特徴とするサンプリング周波数変換装置。

【請求項4】

請求項1〜3のいずれか1項に記載のサンプリング周波数変換装置において、

前記FIFO回路は、前記第1サンプリング周波数を前記第2サンプリング周波数に変換するための前記サンプル信号を算出するのに必要な幅に、前記入力信号の幅を変更する

ことを特徴とするサンプリング周波数変換装置。

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図2】

【図3】

【図4】

【図5】

【図6】

【公開番号】特開2012−231257(P2012−231257A)

【公開日】平成24年11月22日(2012.11.22)

【国際特許分類】

【出願番号】特願2011−97478(P2011−97478)

【出願日】平成23年4月25日(2011.4.25)

【出願人】(000004330)日本無線株式会社 (1,186)

【公開日】平成24年11月22日(2012.11.22)

【国際特許分類】

【出願日】平成23年4月25日(2011.4.25)

【出願人】(000004330)日本無線株式会社 (1,186)

[ Back to top ]