システム回路及びその設定方法

【課題】誤動作を生じさせ得る外乱や雑音により、不測の動作を行うおそれがあった。

【解決手段】前段回路と、前段回路の後段かつ被制御装置の前段に位置に設けられた後段回路とを含み、被制御装置に動作を許可する第1の工程と、被制御装置に動作を維持させる第2の工程と、被制御装置に動作を引き続き維持させる第3の工程と、被制御装置に動作を禁止させる第4の工程とを、前段回路と後段回路とが協動して行う。

【解決手段】前段回路と、前段回路の後段かつ被制御装置の前段に位置に設けられた後段回路とを含み、被制御装置に動作を許可する第1の工程と、被制御装置に動作を維持させる第2の工程と、被制御装置に動作を引き続き維持させる第3の工程と、被制御装置に動作を禁止させる第4の工程とを、前段回路と後段回路とが協動して行う。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、回路動作の設定を行うデータを入力する為の信号入力端子を有するシステム回路に関し、データ入力後、信号入力用端子を電気的に切断可能とするシステム回路に関する。

【背景技術】

【0002】

図9に示されような従来の発振システムOSYSでは、温度補償回路4000は、PROM2000に記憶されている温度補償用データ7000に従って、発振回路6000による発振信号OSIG(水晶振動子5000により規定される発振周波数を有する。)の周波数温度特性を安定させるよう温度補償を行う。当該温度補償を行うことに先立ち、PROM2000に当該温度補償用データ7000を格納すべく、発振装置ODEVは、モード選択信号MSに従うモード設定回路1000による制御下で、3つのモード、即ち、RAMエミュレーションモード、PROM書込モード、及び、PROMベリファリモードを経ており、加えて、各モードでは、当該モードのために必要なデータ(図示せず。)が、データ信号DTにより与えられる。

【0003】

RAMエミュレーションモードでは、前記温度補償回路4000が、RAM3000に一時的に格納された温度補償用データを用いて前記水晶振動子5000と発振回路6000とからなる水晶発振装置の発振動作について前記温度補償を行うことにより、当該温度補償の動作を確認する。上記したRAMエミュレーションモードに引き続き行うPROM書込モードでは、前記RAM3000に一時的に格納されている前記温度補償用データをPROM2000に固定的に書き込む(図9に示す温度補償データ7000)。前記PROM書込モードに引き続くPROMベリファイモードでは、前記PROM2000に固定的に書き込んだ温度補償用データ7000の内容を検証する。前記PROM2000への温度補償用データ7000の書き込みに関連して、下記の特許文献1は、発振回路の温度補償のための最適パラメータをP−ROMに書き込むことを開示している。

【0004】

【特許文献1】特許第3310550号公報

【特許文献2】特開平08−307153号公報

【発明の開示】

【発明が解決しようとする課題】

【0005】

しかしながら、上記したPROMベリファイモードの終了の後に、前記モード選択信号MSが入力される端子であるモード選択信号端子MS_T、又は、前記データ信号DTが入力される端子であるデータ信号端子DT_Tから、前記モード設定回路1000に誤動作を生じさせ得る外乱(信号端子と他の配線との間に導電性異物が付着すること等の影響によるモード選択信号端子やデータ信号端子への不要電圧・信号の供給)や雑音が印加されることがあり、当該外乱や雑音により、前記モード設定回路1000が不測の動作を行うおそれがあるという問題があった。

このような問題発生を防止する方法としては特許文献2に開示された発明の如く、信号端子構造をデバイス実装面より物理的に浮かせた状態となるよう特殊なパッケージを利用する方法もあるが、この場合、パッケージ構造が複雑化する為、デバイスの小型化・低価格化が十分に達成できないという問題が発生する。

【課題を解決するための手段】

【0006】

本発明に係る動作制御装置は、上記した課題を解決すべく、

請求項1の発明は、被制御装置と、動作制御装置と、モード選択信号端子と、データ信号端子とを有し、

前記動作制御装置が前記モード選択信号端子に入力されたモード選択信号と前記データ信号端子に入力されたデータ信号とを前記被制御装置に供給する機能を有するシステム回路であり、

前記被制御装置が、モード設定回路とメモリとを有し、

前記動作制御装置が、初段ユニットと中後段ユニットと遅延ユニットとヒューズユニットとを有し、

前記初段ユニットが、前記モード選択信号端子から供給された前記モード選択信号と前記データ信号端子から供給された前記データ信号とを初段出力信号として前記中後段ユニットへ供給するものであり、

前記中後段ユニットが、前記初段ユニットから供給された前記モード選択信号を前記モード設定回路に、前記初段ユニットから供給された前記データ信号を前記メモリと前記モード設定回路に、それぞれ中後段出力信号として供給するものであり、

前記遅延ユニットが、第1の遅延回路と、第2の遅延回路とを有し、

前記第1の遅延回路が、前記モード設定回路の切換信号に従い第1の制御信号を前記中後段ユニットに供給するものであり、

前記第2の遅延回路が、前記モード設定回路の制御信号に従い前記第1の制御信号の出力から遅れて第2の制御信号を前記中後段ユニットに供給するものであり、

前記ヒューズユニットが、前記モード設定回路の制御信号に従い前記第2の制御信号の出力から遅れて初段制御用信号を前記初段ユニットに供給するものであり、

前記中後段ユニットが、前記第1の制御信号を受けて該中後段ユニットの中後段出力信号をモード選択信号とデータ信号とを前記被制御装置の動作状態を保持させる為の保持信号に切り換えて出力する機能と、前記第2の制御信号を受けて前記初段ユニットとの前記モード選択信号及び前記データ信号の伝達路を遮断状態とする機能を有し、

前記初段ユニットが、前記初段制御用信号を受けて前記モード選択信号端子の入力インピーダンス及び入力抵抗の値と前記データ信号入力端子の入力インピーダンス及び入力抵抗の値とを大きくする機能と、該初段ユニットの前記初段出力信号を固定値とする機能を有する。

【0007】

請求項2の発明は請求項1に加えて前記初段ユニットが、前記初段制御用信号を受けて固定値0の前記初段出力信号を出力するものであることを特徴とする。

【0008】

請求項3の発明は、請求項1の発明に加えて、前記初段ユニットが、第1〜第4のスイッチ回路と、第1のクロックド・インバータと、第2のクロックド・インバータと、前記初段出力信号を出力する第1及び第2のインバータとを有し、

前記モード選択信号端子と固定電位間に第1のスイッチ回路を接続し、前記モード選択信号端子に第1のクロックド・インバータの入力端を接続し、前記第1のインバータの閾値電位よりも高電位の固定電位と前記第1のクロックド・インバータの出力端との間に第2のスイッチ回路を接続し、前記第1のクロックド・インバータの出力端と第1のインバータの入力端とを接続した構成と、

前記データ信号端子と固定電位間に第3のスイッチ回路を接続し、前記モード選択信号端子に第2のクロックド・インバータの入力端を接続し、前記第2のインバータの閾値電位よりも高電位の固定電位と前記第2のクロックド・インバータの出力端との間に第4のスイッチ回路を接続し、前記第2のクロックド・インバータの出力端と第2のインバータの入力端とを接続した構成と、を有し、

前記初段制御用信号による制御に基づき、前記第1のスイッチ回路と第3のスイッチ回路をオフに、第1のクロックド・インバータと第2のクロックド・インバータの出力インピーダンスを高インピーダンスに、前記第2のスイッチ回路と前記第4のスイッチ回路をオンにするものであることを特徴とする。

【0009】

請求項4の発明は請求項1乃至3のいずれかの一項の発明に加えて、

前記中後段ユニットが、第5〜第8のスイッチ回路と、第1のバッファと、第2のバッファとを有し、

前記第1のバッファの入力端と前記手段ユニットの前記第1のインバータの出力端との間に前記第5のスイッチ回路を接続し、前記第1のバッファの入力端と固定電位間に前記第6のスイッチ回路を接続し、前記第1のバッファの出力端を前記モード設定回路側に接続した構成を有し、

前記第2のバッファの入力端と前記初段ユニットの前記第2のインバータの出力端との間に前記第7のスイッチ回路を接続し、前記第2のバッファの入力端と固定電位間に前記第8のスイッチ回路を接続し、前記第2のバッファの出力端を前記メモリ側に接続した構成を有し、

前記第1の制御信号による制御に基づき、前記第6のスイッチ回路と前記第8のスイッチ回路をオンに、前記第2の制御信号による制御に基づき、前記第5のスイッチ回路と前記第7のスイッチ回路をオフにするものであることを特徴とする。

【0010】

請求項5の発明は請求項1乃至4のいずれか一項の発明に加えて、前記被制御装置が、圧電発振回路と、該圧電発振回路の周波数温度特性を補償する為の温度補償回路とを備え、

前記メモリに記憶されたデータに基づき前記温度補償回路の動作を制御する発振装置であることを特徴とする。

【0011】

請求項6の発明は被制御装置と、動作制御装置と、モード選択信号端子と、データ信号端子とを有し、

前記動作制御装置が、初段ユニットと中後段ユニットと遅延ユニットとヒューズユニットとを有し、前記モード選択信号端子に入力されたモード選択信号と前記データ信号端子に入力されたデータ信号とを前記被制御装置に供給する機能を有し、

前記遅延ユニットが、第1の遅延回路と、第2の遅延回路とを有し、

前記被制御装置が、モード設定回路とメモリとを有するシステム回路の設定方法であり、

前記初段ユニットが、前記モード選択信号端子から供給された前記モード選択信号と前記データ信号端子から供給された前記データ信号とを初段出力信号として前記中後段ユニットへ供給する工程と、

前記中後段ユニットが、前記初段ユニットから供給された前記モード選択信号を前記モード設定回路に、前記初段ユニットから供給された前記データ信号を前記メモリと前記モード設定回路に、それぞれ中後段出力信号として供給する工程と、

前記第1の遅延回路が、前記モード設定回路の制御信号に従い第1の制御信号を前記中後段ユニットに供給する工程と、

前記第2の遅延回路が、前記モード設定回路の切換信号に従い前記第1の制御信号の出力から遅れて第2の制御信号を前記中後段ユニットに供給する工程と、

前記ヒューズユニットが、前記モード設定回路の制御信号に従い前記第2の制御信号の出力から遅れて初段制御用信号を前記初段ユニットに供給する工程と、

前記中後段ユニットが、前記第1の制御信号を受けて該中後段ユニットの中後段出力信号をモード選択信号とデータ信号とを前記被制御装置の動作状態を保持させる為の保持信号に切り換えて出力する工程と、

前記中後段ユニットが、前記第2の制御信号を受けて前記初段ユニットとの前記モード選択信号及び前記データ信号の伝達路を遮断状態とする工程と、

前記初段ユニットが、前記初段制御用信号を受けて前記モード選択信号端子の入力インピーダンス及び入力抵抗の値と前記データ信号入力端子の入力インピーダンス及び入力抵抗の値とを大きくするよう制御する工程と、

前記初段ユニットが、該初段ユニットの前記初段出力信号を固定値とするよう制御する工程と、を有する。

【0012】

上記した本発明に係る動作制御装置は、前記被動作制御装置に前記動作を許可する前記第1の工程、前記被動作制御装置に前記動作を維持させる前記第2の工程、及び前記被動作制御装置に前記動作を引き続き維持させる前記第3の工程の後に、前記第4の工程で、前記前段回路の前記遮断状態及び前記後段回路の前記禁止状態により、前記被動作制御装置に前記動作を禁止させることから、前記被制御装置の前記動作の許否に悪影響を及ぼし得る外乱が混入したときであっても、当該外乱によって、前記被動作制御装置の前記動作が許可されてしまうような不測の事態を回避することが可能となる。

【発明を実施するための最良の形態】

【0013】

本発明に係る動作制御装置の実施例について図面を参照して説明する。

【0014】

《構成》

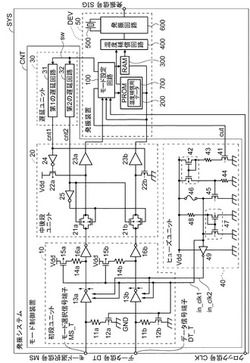

図1に示されるように、実施例の発振システム回路SYSは、『被動作制御装置』である発振装置DEV、及び、『動作制御装置』であるモード制御装置CNTを含み、入力されるモード選択信号MS、データ信号DT、及び、クロック信号CLK(いずれもデジタル信号)に従って、発振装置DEV内への温度補償用データ700入力に関する処理を行う。

【0015】

発振装置DEVは、モード設定回路100と、PROM200(Programmable Read on Memory)と、RAM300(Random Access Memory)と、温度補償回路400と、水晶振動子500と、発振回路600とを有する。発振装置DEVでは、従来の発振装置ODEVと同様に、RAMエミュレーションモード、PROM書込モード、及び、PROMベリファリモードを有し、他方で、従来の発振装置ODEVと異なり、端子遮断モードを更に有する。当該端子遮断モードでは、モード選択信号MSの入力を受けるためのモード選択信号端子MS_T、及び、データ信号DTの入力を受けるためのデータ信号端子DT_Tから不要信号等の外乱がモード設定回路100やメモリへ侵入することを阻止することができるようにモード制御装置CNTを設定する(後述の工程1〜工程4に相当。)。4つのモードは、それぞれ、モード選択信号MS並びにデータ信号DTにより特定され、各モードでの処理に必要なデータもまた、データ信号DTにより与えられる。

【0016】

モード制御装置CNTは、初段ユニット10と、中後段ユニット20と、遅延ユニット30と、ヒューズユニット40とを有する。

【0017】

〈初段ユニット〉

初段ユニット10は、クロック信号CLKに同期するモード選択信号MS及びデータ信号DTの入力を受ける。初段ユニット10は、前記モード選択信号MSについて、モード選択信号端子MS_Tに一端が接続された抵抗器11aと、当該抵抗器11aの他端及び接地電位GND間に設けられた第1のスイッチ回路であるNMOSトランジスタ12aと、当該モード選択信号MSを受ける、『前段回路』である第1のクロックド・インバータ13aと、第1のクロックド・インバータ13aの出力端に一端が接続された抵抗器14aと、当該抵抗器14aの他端及び電源電位Vdd間に設けられた第2のスイッチ回路であるPMOSトランジスタ15aと、第1のクロックド・インバータ13aの後段に設けられた第1のインバータ16aとを有する。

【0018】

初段ユニット10は、同様にして、前記データ信号DTについて、データ信号端子DT_Tに一端が接続された抵抗器11bと、当該抵抗器11bの他端及び接地電位GND間に設けられた第3のスイッチ回路であるNMOSトランジスタ12bと、当該データ信号DTを受ける、『前段回路』である第2のクロックド・インバータ13bと、当該第2のクロックド・インバータ13bの出力端に一端が接続された抵抗器14bと、当該抵抗器14bの他端及び電源電位Vdd間に設けられた第4のスイッチ回路であるPMOSトランジスタ15bと、第2のクロックド・インバータ13bの後段に設けられた第2のインバータ16bとを有する。

【0019】

クロックド・インバータ13a、13bは、それぞれ、図8に図示された構成を有し、ヒューズユニット40から出力される第1の初段制御用信号in_clk1及び第2の初段制御用信号in_clk2に従いつつ、モード選択信号端子MS_T及びデータ信号端子DT_Tから入力されるモード選択信号MS及びデータ信号DTを、後段の第1、第2のインバータ16a、16bに出力する。第1、第2のインバータ16a、16bは後述する中後段ユニットへを初段出力信号として供給する。

【0020】

〈中後段ユニット〉

中後段ユニット20は、モード選択信号MSについて、第5のスイッチ回路であるトランスミッションゲート21a(相互に並列接続されたPMOSトランジスタとNMOSトランジスタとからなる。)と、トランスミッションゲート21aの出力端及び電源電位Vdd間に設けられた第6のスイッチ回路であるPMOSトランジスタ22aと、前記トランスミッションゲート21aの後段に設けられた、『後段回路』である第1のバッファ23aとを有する。更に中後段ユニット20は、データ信号DTについて、第7のスイッチ回路であるトランスミッションゲート21b(トランスミッションゲート21aと同様な構成を有する。)と、当該トランスミッションゲート21bの出力端及び接地電位GND間に設けられた第8のスイッチ回路であるNMOSトランジスタ22bと、前記トランスミッションゲート21bの後段に設けられた、『後段回路』である第2のバッファ23bとを有する。

【0021】

中後段ユニット20は、また、インバータ24を有する。インバータ24の入力端及び上記したNMOSトランジスタ22bのゲート端には、遅延ユニット30から出力される第1の制御信号cnt1が入力され、また、当該インバータ24の出力端と上記したPMOSトランジスタ22aのゲート端が相互に接続されている。

【0022】

中後段ユニット20は、更に、インバータ25を有する。インバータ25の入力端及び上記したトランスミッションゲート21a、21b内のPMOSトランジスタのゲート端子には、遅延ユニット30から出力される第2の制御信号cnt2が入力され、また、当該インバータ25の出力端と前記トランスミッションゲート22a、22b内のNMOSトランジスタのゲート端子とが相互に接続されている。

そして、第1、第2のバッファ23a、23bは、被制御装置へ中後段出力信号として供給する。

【0023】

〈遅延ユニット〉

遅延ユニット30は、第1の遅延回路31と、第2の遅延回路32とを有する。第1、第2の遅延回路31、32は、共に、モード設定回路100から切換信号swを受けて第1の遅延回路31が第1の制御信号cnt1を出力し、第2の遅延回路32が第1の制御信号cnt2を出力する。当該切換信号swを受けてから第1の遅延回路31が第1の制御信号cnt1を出力するまでの時間(遅延時間)は、前記切換信号swを受けてから第2の遅延回路32が第2の制御信号cnt2を出力するまでの時間(遅延時間)よりも短い。

【0024】

〈ヒューズユニット〉

ヒューズユニット40は、発振装置DEVから出力される遮断信号cutをゲート端に受けるNMOSトランジスタ41と、第1のカレントミラー回路42と、前記NMOSトランジスタ41及び前記第1のカレントミラー回路42間に設けられた抵抗器43と、当該第1のカレントミラー回路42と接地電位GND間に設けられた抵抗器44と、前記第1のカレントミラー回路42にゲート端が接続された遮断用NMOSトランジスタ45と、当該遮断用NMOSトランジスタ45と電源電位Vdd間に設けられたヒューズ46(ポリシリコンヒューズ)と、第2のカレントミラー回路47と、当該第2のカレントミラー回路47及び電源電位Vdd間に設けられた抵抗器48と、前記ヒューズ46の一端と前記遮断用NMOSトランジスタ45のドレイン端、及び前記第2のカレントミラー回路47の出力端とがその入力端に接続されたインバータ49とを有する。

【0025】

インバータ49の入力端に印加される電圧は、第1の初段制御用信号in_clk1として、また、インバータ49の出力電圧は、第2の初段制御用信号in_clk2として、初段ユニット10に出力される。

【0026】

《動作》

実施例の発振システムSYSの動作について図2〜図7を用いて説明する。

【0027】

説明及び理解を容易にすべく、発振システムSYSの初期の状態は、図2に示されるように、初段ユニット10内の第1、第2のクロックド・インバータ13a、13bは、『導通状態』(第1、第2の初段制御用信号in_clk1、in_clk2を受けており、第1、第2のクロックド・インバータ13a、13bに入力されたモード選択信号MS及びデータ信号DTを出力することが可能な状態。)であり、第5、第7のトランスミッションゲート21a、21bは、『導通状態』であり、第1、第2のバッファ23a、23bは、PMOSトランジスタ22a及びNMOSトランジスタ22bによってその入力端に強制的に「1」又は「0」が印加されていない『導通状態』である。全体を要約すれば、初期には、モード選択信号端子MS_Tに与えられるモード選択信号MS、及び、データ信号端子DT_Tに与えられるデータ信号DTが、発振装置DEV内のモード設定回路100にそのまま到達することができる状態である。

【0028】

説明では、また、”正論理”を採用し、即ち、電源電位Vddを「1」(High信号)とし、接地電位GNDを「0」(Low信号)とする。

【0029】

説明では、さらに、中後段ユニット20内の第1のバッファ23aから、「1」の許可信号(後述)又はPMOSトランジスタ22aが強制的に設定する信号が出力されるとき、モード設定回路100は、第2のバッファ23bから出力されるデータ信号DTを受け付けるものである。

【0030】

工程1:第1の工程である工程1では、例えば、前記発振システム回路SYSの製造過程で、上記初期の状態の発振システム回路SYSに温度補償用データ700に関する処理(RAMエミュレーションモード、PROM書込モード、及び、PROMベリファリモード)を経た後、図3及び図7の工程1に示されるように、モード制御装置CNTにモード選択信号MS「1」が持続的に入力されている間、クロック信号CLKに同期して「端子遮断モード」の開始を表わす「1111」であるデータ信号DTがデータ信号端子DT_Tに入力された後、手段ユニット10、中後段ユニット20を介してモード設定回路に供給される。

尚、RAMエミュレーションモードでは、前記温度補償回路400が、初段ユニット10と中後段ユニット20とを介して供給を受けたデータ信号DTに基づくRAM300に一時的に格納された温度補償用データを用いて前記水晶振動子500と発振回路600とからなる水晶発振装置の発振動作について前記温度補償を行うことにより、当該温度補償の動作を確認する。上記したRAMエミュレーションモードに引き続き行うPROM書込モードでは、前記RAM300に一時的に格納されている前記温度補償用データをPROM200に固定的に書き込む(図1に示す温度補償データ700)。前記PROM書込モードに引き続くPROMベリファイモードでは、前記PROM200に固定的に書き込んだ温度補償用データ700の内容を検証するものである。

【0031】

工程2:第2の工程である工程2では、図4及び図7の工程2に示されるように、クロック信号CLKにおける5番目のパルスが入力されると、モード設定回路100は、「1」の切換信号swを出力する。当該「1」の切換信号swを受けると、第1の遅延回路31は、「1」の第1の制御信号cnt1を出力し、また、第2の遅延回路32は、前記第1の遅延回路31が「1」の第1の制御信号cnt1を出力することに僅かに遅れて、「1」の第2の制御信号cnt2を出力する。

【0032】

「1」の第1の制御信号cnt1を受けると、インバータ24は、「0」を出力し、これにより、PMOSトランジスタ22aは、「オン」になる。この結果、第1のバッファ23aは、その入力端に「1」が入力され、そのまま、当該「1」、即ち、発振装置DEVの動作(モード設定回路100の受け付け動作。)を保持すべき旨を示す「1」である『保持信号』を出力する。

【0033】

また、「1」の第1の制御信号cnt1を受けると、NMOSトランジスタ22bは、「オン」になり、これにより、第2のバッファ23bは、その入力端に「0」が入力され、そのまま、当該「0」を出力する。

【0034】

他方で、「1」の第2の制御信号cnt2を受けると、インバータ25は、「0」を出力する。さらに、前記「1」の第2の制御信号cnt2及びインバータ25からの信号「0」を受けると、トランスミッションゲート21a、21bは、『遮断状態』になる。

【0035】

上記した、第1のバッファ23aからの『保持信号』の出力、及び、トランスミッションゲート21a、21bの『遮断状態』により、発振装置DEVの動作、即ち、モード設定回路100の動作が保持される。

【0036】

工程3:図5及び図7の工程3に示されるように、クロック信号CLKにおけるn番目(nは、任意の正の整数)のビット「1」が入力されると、モード設定回路100は、ヒューズユニット40に、「1」の遮断信号cutを出力する。当該「1」の遮断信号cutを受けると、ヒューズユニット40では、NMOSトランジスタ41は、「オン」になり、これにより、第1のカレントミラー回路42に、抵抗器43により規定される電流i1が流れるとともに、第1のカレントミラー回路42のトランジスタ比に応じた電流i2が流れる。電流i2が高抵抗44に流れることでNMOSトランジスタ45のベース電圧が上昇し、当該遮断用NMOSトランジスタ45は、「オン」になり、これにより、ヒューズ46に電流i3(過大電流)が流れ、当該電流i3により、ヒューズは切断され、即ち、「オープン」になる。

【0037】

ヒューズ46が「オープン」になると、第2のカレントミラー回路47の引き込み電流によってインバータ49の入力電位がほぼGND電位になり、この結果、インバータ49は「1」を出力する。換言すれば、ヒューズユニット40は、「1」の遮断信号cutを受けて「0」の第1の初段制御用信号in_clk1と、「1」の第2の初段制御用信号in_clk2を初段ユニット10に出力する。前段ユニット10では、前記「0」の第1の初段制御用信号in_clk1及び前記「1」の第2の初段制御用信号in_clk2信号が入力されると、第1、第2のクロックド・インバータ13a、13bは、出力端がハイインピーダンスの状態、即ち、『遮断状態』になり、また、NMOSトランジスタ12a、12bは、「オフ」になるので、モード選択信号端子、データ信号端子からみて入力抵抗の値が大きい状態となる。しかしながら、このとき第1のバッファ23aは、『保持信号』を出力し続けることから、発振装置DEVの動作は、工程2での設定状態が引き続き維持される。

【0038】

工程4:図6及び図7の工程4に示されるように、前記発振システム回路SYSは、モード選択信号MSが「0」に設定されることによって、初段ユニット10の第1、第2のクロックド・インバータ13a、13bは、『遮断状態』となる。

【0039】

また、電源電圧Vddが再投入された後、初段ユニット10では、第1、第2のクロックド・インバータ13a、13bは、『遮断状態』のままである。すなわち、製品出荷後にユーザー側で電源電圧Vddを投入した場合においても、初段ユニット10は遮断状態が維持される。

【0040】

他方で、ヒューズユニット40では、ヒューズ46が「オープン(切断)」であることから、第1の初段制御用信号in_clk1は、実質的に「0」のままである。当該「0」である第1の初段制御用信号in_clk1を受けると、初段ユニット10内のPMOSトランジスタ15a、PMOSトランジスタ15bは、「オン」になり、これにより、インバータ16a、16bは、その入力端に「1」が印加され、その結果として、出力端から「0」を出力する。

【0041】

第1、第2のインバータ16a、16bから「0」を受けると、トランスミッションゲート21a、21bは、前記「0」をそのまま出力し、当該「0」を受けると、第1、第2のバッファ23a、23bは、当該「0」をそのまま出力し、即ち、前記発振装置DEVに前記動作(データ信号DTの受付動作)を禁止する『禁止信号』を出力する。

【0042】

《効果》

上記した発振システムSYSによれば、工程4以後には、仮に、モード選択信号端子MS_T及びデータ信号端子DT_Tに外乱が加わって、例えば、モード選択信号端子MS_Tに、発振装置DEVの動作(モード設定回路100によるデータ信号DTの受付動作)の許否に悪影響を及ぼし得る外乱「1」が印加されても、クロックド・インバータ13aが『遮断状態』であることから、当該外乱「1」が、トランスミッションゲート21a及びバッファ23aを経由してモード設定回路100等に出力されることはなく、これにより、モード設定回路100は、データ信号DTを受け付けることができず、即ち、上記のような外乱「1」の影響に起因する不測の誤動作を回避することが可能となる。更に、NMOSトランジスタ12a、12bがオフ状態であることによりモード選択信号端子MS_Tとデータ信号端子DT_Tとが接地電位GNDと切離され入力抵抗・入力インピーダンスが高い状態であるので例えば、発振システム回路SYSの電源電圧Vddの端子とモード選択信号端子MS_Tとの間が導電性異物等により短絡してしまっても、電源電圧Vddの端子と接地電位GNDである配線とが短絡しないので発振システム回路や発振システム回路を搭載した装置の動作が停止するなどの誤動作が起きるのを防止することができる。

更に、発振システム回路を有する発振装置として発振システム回路を収容するパッケージに設けたデータ信号端子やモード選択信号端子等の信号端子構造を特殊なものとすることなく外乱による異常動作発生を防止することができるので、パッケージの設計自由度が広がり、発振装置の小型化、低価格化を十分達成させることができる。

【図面の簡単な説明】

【0043】

【図1】実施例の発振システムの構成を示す図。

【図2】実施例の発振システムの動作を示す図(その1)。

【図3】実施例の発振システムの動作を示す図(その2)。

【図4】実施例の発振システムの動作を示す図(その3)。

【図5】実施例の発振システムの動作を示す図(その4)。

【図6】実施例の発振システムの動作を示す図(その5)。

【図7】実施例の発振システムの動作を示すタイミングチャート。

【図8】実施例のクロックド・インバータの構成を示す図。

【図9】従来の発振システムの構成を示す図。

【符号の説明】

【0044】

SYS…発振システム、CNT…モード制御装置、DEV…発振装置、10…初段ユニット、20…中後段ユニット、30…遅延ユニット、40…ヒューズユニット、13a、13b…クロックド・インバータ、23a、23b…バッファ。

【技術分野】

【0001】

本発明は、回路動作の設定を行うデータを入力する為の信号入力端子を有するシステム回路に関し、データ入力後、信号入力用端子を電気的に切断可能とするシステム回路に関する。

【背景技術】

【0002】

図9に示されような従来の発振システムOSYSでは、温度補償回路4000は、PROM2000に記憶されている温度補償用データ7000に従って、発振回路6000による発振信号OSIG(水晶振動子5000により規定される発振周波数を有する。)の周波数温度特性を安定させるよう温度補償を行う。当該温度補償を行うことに先立ち、PROM2000に当該温度補償用データ7000を格納すべく、発振装置ODEVは、モード選択信号MSに従うモード設定回路1000による制御下で、3つのモード、即ち、RAMエミュレーションモード、PROM書込モード、及び、PROMベリファリモードを経ており、加えて、各モードでは、当該モードのために必要なデータ(図示せず。)が、データ信号DTにより与えられる。

【0003】

RAMエミュレーションモードでは、前記温度補償回路4000が、RAM3000に一時的に格納された温度補償用データを用いて前記水晶振動子5000と発振回路6000とからなる水晶発振装置の発振動作について前記温度補償を行うことにより、当該温度補償の動作を確認する。上記したRAMエミュレーションモードに引き続き行うPROM書込モードでは、前記RAM3000に一時的に格納されている前記温度補償用データをPROM2000に固定的に書き込む(図9に示す温度補償データ7000)。前記PROM書込モードに引き続くPROMベリファイモードでは、前記PROM2000に固定的に書き込んだ温度補償用データ7000の内容を検証する。前記PROM2000への温度補償用データ7000の書き込みに関連して、下記の特許文献1は、発振回路の温度補償のための最適パラメータをP−ROMに書き込むことを開示している。

【0004】

【特許文献1】特許第3310550号公報

【特許文献2】特開平08−307153号公報

【発明の開示】

【発明が解決しようとする課題】

【0005】

しかしながら、上記したPROMベリファイモードの終了の後に、前記モード選択信号MSが入力される端子であるモード選択信号端子MS_T、又は、前記データ信号DTが入力される端子であるデータ信号端子DT_Tから、前記モード設定回路1000に誤動作を生じさせ得る外乱(信号端子と他の配線との間に導電性異物が付着すること等の影響によるモード選択信号端子やデータ信号端子への不要電圧・信号の供給)や雑音が印加されることがあり、当該外乱や雑音により、前記モード設定回路1000が不測の動作を行うおそれがあるという問題があった。

このような問題発生を防止する方法としては特許文献2に開示された発明の如く、信号端子構造をデバイス実装面より物理的に浮かせた状態となるよう特殊なパッケージを利用する方法もあるが、この場合、パッケージ構造が複雑化する為、デバイスの小型化・低価格化が十分に達成できないという問題が発生する。

【課題を解決するための手段】

【0006】

本発明に係る動作制御装置は、上記した課題を解決すべく、

請求項1の発明は、被制御装置と、動作制御装置と、モード選択信号端子と、データ信号端子とを有し、

前記動作制御装置が前記モード選択信号端子に入力されたモード選択信号と前記データ信号端子に入力されたデータ信号とを前記被制御装置に供給する機能を有するシステム回路であり、

前記被制御装置が、モード設定回路とメモリとを有し、

前記動作制御装置が、初段ユニットと中後段ユニットと遅延ユニットとヒューズユニットとを有し、

前記初段ユニットが、前記モード選択信号端子から供給された前記モード選択信号と前記データ信号端子から供給された前記データ信号とを初段出力信号として前記中後段ユニットへ供給するものであり、

前記中後段ユニットが、前記初段ユニットから供給された前記モード選択信号を前記モード設定回路に、前記初段ユニットから供給された前記データ信号を前記メモリと前記モード設定回路に、それぞれ中後段出力信号として供給するものであり、

前記遅延ユニットが、第1の遅延回路と、第2の遅延回路とを有し、

前記第1の遅延回路が、前記モード設定回路の切換信号に従い第1の制御信号を前記中後段ユニットに供給するものであり、

前記第2の遅延回路が、前記モード設定回路の制御信号に従い前記第1の制御信号の出力から遅れて第2の制御信号を前記中後段ユニットに供給するものであり、

前記ヒューズユニットが、前記モード設定回路の制御信号に従い前記第2の制御信号の出力から遅れて初段制御用信号を前記初段ユニットに供給するものであり、

前記中後段ユニットが、前記第1の制御信号を受けて該中後段ユニットの中後段出力信号をモード選択信号とデータ信号とを前記被制御装置の動作状態を保持させる為の保持信号に切り換えて出力する機能と、前記第2の制御信号を受けて前記初段ユニットとの前記モード選択信号及び前記データ信号の伝達路を遮断状態とする機能を有し、

前記初段ユニットが、前記初段制御用信号を受けて前記モード選択信号端子の入力インピーダンス及び入力抵抗の値と前記データ信号入力端子の入力インピーダンス及び入力抵抗の値とを大きくする機能と、該初段ユニットの前記初段出力信号を固定値とする機能を有する。

【0007】

請求項2の発明は請求項1に加えて前記初段ユニットが、前記初段制御用信号を受けて固定値0の前記初段出力信号を出力するものであることを特徴とする。

【0008】

請求項3の発明は、請求項1の発明に加えて、前記初段ユニットが、第1〜第4のスイッチ回路と、第1のクロックド・インバータと、第2のクロックド・インバータと、前記初段出力信号を出力する第1及び第2のインバータとを有し、

前記モード選択信号端子と固定電位間に第1のスイッチ回路を接続し、前記モード選択信号端子に第1のクロックド・インバータの入力端を接続し、前記第1のインバータの閾値電位よりも高電位の固定電位と前記第1のクロックド・インバータの出力端との間に第2のスイッチ回路を接続し、前記第1のクロックド・インバータの出力端と第1のインバータの入力端とを接続した構成と、

前記データ信号端子と固定電位間に第3のスイッチ回路を接続し、前記モード選択信号端子に第2のクロックド・インバータの入力端を接続し、前記第2のインバータの閾値電位よりも高電位の固定電位と前記第2のクロックド・インバータの出力端との間に第4のスイッチ回路を接続し、前記第2のクロックド・インバータの出力端と第2のインバータの入力端とを接続した構成と、を有し、

前記初段制御用信号による制御に基づき、前記第1のスイッチ回路と第3のスイッチ回路をオフに、第1のクロックド・インバータと第2のクロックド・インバータの出力インピーダンスを高インピーダンスに、前記第2のスイッチ回路と前記第4のスイッチ回路をオンにするものであることを特徴とする。

【0009】

請求項4の発明は請求項1乃至3のいずれかの一項の発明に加えて、

前記中後段ユニットが、第5〜第8のスイッチ回路と、第1のバッファと、第2のバッファとを有し、

前記第1のバッファの入力端と前記手段ユニットの前記第1のインバータの出力端との間に前記第5のスイッチ回路を接続し、前記第1のバッファの入力端と固定電位間に前記第6のスイッチ回路を接続し、前記第1のバッファの出力端を前記モード設定回路側に接続した構成を有し、

前記第2のバッファの入力端と前記初段ユニットの前記第2のインバータの出力端との間に前記第7のスイッチ回路を接続し、前記第2のバッファの入力端と固定電位間に前記第8のスイッチ回路を接続し、前記第2のバッファの出力端を前記メモリ側に接続した構成を有し、

前記第1の制御信号による制御に基づき、前記第6のスイッチ回路と前記第8のスイッチ回路をオンに、前記第2の制御信号による制御に基づき、前記第5のスイッチ回路と前記第7のスイッチ回路をオフにするものであることを特徴とする。

【0010】

請求項5の発明は請求項1乃至4のいずれか一項の発明に加えて、前記被制御装置が、圧電発振回路と、該圧電発振回路の周波数温度特性を補償する為の温度補償回路とを備え、

前記メモリに記憶されたデータに基づき前記温度補償回路の動作を制御する発振装置であることを特徴とする。

【0011】

請求項6の発明は被制御装置と、動作制御装置と、モード選択信号端子と、データ信号端子とを有し、

前記動作制御装置が、初段ユニットと中後段ユニットと遅延ユニットとヒューズユニットとを有し、前記モード選択信号端子に入力されたモード選択信号と前記データ信号端子に入力されたデータ信号とを前記被制御装置に供給する機能を有し、

前記遅延ユニットが、第1の遅延回路と、第2の遅延回路とを有し、

前記被制御装置が、モード設定回路とメモリとを有するシステム回路の設定方法であり、

前記初段ユニットが、前記モード選択信号端子から供給された前記モード選択信号と前記データ信号端子から供給された前記データ信号とを初段出力信号として前記中後段ユニットへ供給する工程と、

前記中後段ユニットが、前記初段ユニットから供給された前記モード選択信号を前記モード設定回路に、前記初段ユニットから供給された前記データ信号を前記メモリと前記モード設定回路に、それぞれ中後段出力信号として供給する工程と、

前記第1の遅延回路が、前記モード設定回路の制御信号に従い第1の制御信号を前記中後段ユニットに供給する工程と、

前記第2の遅延回路が、前記モード設定回路の切換信号に従い前記第1の制御信号の出力から遅れて第2の制御信号を前記中後段ユニットに供給する工程と、

前記ヒューズユニットが、前記モード設定回路の制御信号に従い前記第2の制御信号の出力から遅れて初段制御用信号を前記初段ユニットに供給する工程と、

前記中後段ユニットが、前記第1の制御信号を受けて該中後段ユニットの中後段出力信号をモード選択信号とデータ信号とを前記被制御装置の動作状態を保持させる為の保持信号に切り換えて出力する工程と、

前記中後段ユニットが、前記第2の制御信号を受けて前記初段ユニットとの前記モード選択信号及び前記データ信号の伝達路を遮断状態とする工程と、

前記初段ユニットが、前記初段制御用信号を受けて前記モード選択信号端子の入力インピーダンス及び入力抵抗の値と前記データ信号入力端子の入力インピーダンス及び入力抵抗の値とを大きくするよう制御する工程と、

前記初段ユニットが、該初段ユニットの前記初段出力信号を固定値とするよう制御する工程と、を有する。

【0012】

上記した本発明に係る動作制御装置は、前記被動作制御装置に前記動作を許可する前記第1の工程、前記被動作制御装置に前記動作を維持させる前記第2の工程、及び前記被動作制御装置に前記動作を引き続き維持させる前記第3の工程の後に、前記第4の工程で、前記前段回路の前記遮断状態及び前記後段回路の前記禁止状態により、前記被動作制御装置に前記動作を禁止させることから、前記被制御装置の前記動作の許否に悪影響を及ぼし得る外乱が混入したときであっても、当該外乱によって、前記被動作制御装置の前記動作が許可されてしまうような不測の事態を回避することが可能となる。

【発明を実施するための最良の形態】

【0013】

本発明に係る動作制御装置の実施例について図面を参照して説明する。

【0014】

《構成》

図1に示されるように、実施例の発振システム回路SYSは、『被動作制御装置』である発振装置DEV、及び、『動作制御装置』であるモード制御装置CNTを含み、入力されるモード選択信号MS、データ信号DT、及び、クロック信号CLK(いずれもデジタル信号)に従って、発振装置DEV内への温度補償用データ700入力に関する処理を行う。

【0015】

発振装置DEVは、モード設定回路100と、PROM200(Programmable Read on Memory)と、RAM300(Random Access Memory)と、温度補償回路400と、水晶振動子500と、発振回路600とを有する。発振装置DEVでは、従来の発振装置ODEVと同様に、RAMエミュレーションモード、PROM書込モード、及び、PROMベリファリモードを有し、他方で、従来の発振装置ODEVと異なり、端子遮断モードを更に有する。当該端子遮断モードでは、モード選択信号MSの入力を受けるためのモード選択信号端子MS_T、及び、データ信号DTの入力を受けるためのデータ信号端子DT_Tから不要信号等の外乱がモード設定回路100やメモリへ侵入することを阻止することができるようにモード制御装置CNTを設定する(後述の工程1〜工程4に相当。)。4つのモードは、それぞれ、モード選択信号MS並びにデータ信号DTにより特定され、各モードでの処理に必要なデータもまた、データ信号DTにより与えられる。

【0016】

モード制御装置CNTは、初段ユニット10と、中後段ユニット20と、遅延ユニット30と、ヒューズユニット40とを有する。

【0017】

〈初段ユニット〉

初段ユニット10は、クロック信号CLKに同期するモード選択信号MS及びデータ信号DTの入力を受ける。初段ユニット10は、前記モード選択信号MSについて、モード選択信号端子MS_Tに一端が接続された抵抗器11aと、当該抵抗器11aの他端及び接地電位GND間に設けられた第1のスイッチ回路であるNMOSトランジスタ12aと、当該モード選択信号MSを受ける、『前段回路』である第1のクロックド・インバータ13aと、第1のクロックド・インバータ13aの出力端に一端が接続された抵抗器14aと、当該抵抗器14aの他端及び電源電位Vdd間に設けられた第2のスイッチ回路であるPMOSトランジスタ15aと、第1のクロックド・インバータ13aの後段に設けられた第1のインバータ16aとを有する。

【0018】

初段ユニット10は、同様にして、前記データ信号DTについて、データ信号端子DT_Tに一端が接続された抵抗器11bと、当該抵抗器11bの他端及び接地電位GND間に設けられた第3のスイッチ回路であるNMOSトランジスタ12bと、当該データ信号DTを受ける、『前段回路』である第2のクロックド・インバータ13bと、当該第2のクロックド・インバータ13bの出力端に一端が接続された抵抗器14bと、当該抵抗器14bの他端及び電源電位Vdd間に設けられた第4のスイッチ回路であるPMOSトランジスタ15bと、第2のクロックド・インバータ13bの後段に設けられた第2のインバータ16bとを有する。

【0019】

クロックド・インバータ13a、13bは、それぞれ、図8に図示された構成を有し、ヒューズユニット40から出力される第1の初段制御用信号in_clk1及び第2の初段制御用信号in_clk2に従いつつ、モード選択信号端子MS_T及びデータ信号端子DT_Tから入力されるモード選択信号MS及びデータ信号DTを、後段の第1、第2のインバータ16a、16bに出力する。第1、第2のインバータ16a、16bは後述する中後段ユニットへを初段出力信号として供給する。

【0020】

〈中後段ユニット〉

中後段ユニット20は、モード選択信号MSについて、第5のスイッチ回路であるトランスミッションゲート21a(相互に並列接続されたPMOSトランジスタとNMOSトランジスタとからなる。)と、トランスミッションゲート21aの出力端及び電源電位Vdd間に設けられた第6のスイッチ回路であるPMOSトランジスタ22aと、前記トランスミッションゲート21aの後段に設けられた、『後段回路』である第1のバッファ23aとを有する。更に中後段ユニット20は、データ信号DTについて、第7のスイッチ回路であるトランスミッションゲート21b(トランスミッションゲート21aと同様な構成を有する。)と、当該トランスミッションゲート21bの出力端及び接地電位GND間に設けられた第8のスイッチ回路であるNMOSトランジスタ22bと、前記トランスミッションゲート21bの後段に設けられた、『後段回路』である第2のバッファ23bとを有する。

【0021】

中後段ユニット20は、また、インバータ24を有する。インバータ24の入力端及び上記したNMOSトランジスタ22bのゲート端には、遅延ユニット30から出力される第1の制御信号cnt1が入力され、また、当該インバータ24の出力端と上記したPMOSトランジスタ22aのゲート端が相互に接続されている。

【0022】

中後段ユニット20は、更に、インバータ25を有する。インバータ25の入力端及び上記したトランスミッションゲート21a、21b内のPMOSトランジスタのゲート端子には、遅延ユニット30から出力される第2の制御信号cnt2が入力され、また、当該インバータ25の出力端と前記トランスミッションゲート22a、22b内のNMOSトランジスタのゲート端子とが相互に接続されている。

そして、第1、第2のバッファ23a、23bは、被制御装置へ中後段出力信号として供給する。

【0023】

〈遅延ユニット〉

遅延ユニット30は、第1の遅延回路31と、第2の遅延回路32とを有する。第1、第2の遅延回路31、32は、共に、モード設定回路100から切換信号swを受けて第1の遅延回路31が第1の制御信号cnt1を出力し、第2の遅延回路32が第1の制御信号cnt2を出力する。当該切換信号swを受けてから第1の遅延回路31が第1の制御信号cnt1を出力するまでの時間(遅延時間)は、前記切換信号swを受けてから第2の遅延回路32が第2の制御信号cnt2を出力するまでの時間(遅延時間)よりも短い。

【0024】

〈ヒューズユニット〉

ヒューズユニット40は、発振装置DEVから出力される遮断信号cutをゲート端に受けるNMOSトランジスタ41と、第1のカレントミラー回路42と、前記NMOSトランジスタ41及び前記第1のカレントミラー回路42間に設けられた抵抗器43と、当該第1のカレントミラー回路42と接地電位GND間に設けられた抵抗器44と、前記第1のカレントミラー回路42にゲート端が接続された遮断用NMOSトランジスタ45と、当該遮断用NMOSトランジスタ45と電源電位Vdd間に設けられたヒューズ46(ポリシリコンヒューズ)と、第2のカレントミラー回路47と、当該第2のカレントミラー回路47及び電源電位Vdd間に設けられた抵抗器48と、前記ヒューズ46の一端と前記遮断用NMOSトランジスタ45のドレイン端、及び前記第2のカレントミラー回路47の出力端とがその入力端に接続されたインバータ49とを有する。

【0025】

インバータ49の入力端に印加される電圧は、第1の初段制御用信号in_clk1として、また、インバータ49の出力電圧は、第2の初段制御用信号in_clk2として、初段ユニット10に出力される。

【0026】

《動作》

実施例の発振システムSYSの動作について図2〜図7を用いて説明する。

【0027】

説明及び理解を容易にすべく、発振システムSYSの初期の状態は、図2に示されるように、初段ユニット10内の第1、第2のクロックド・インバータ13a、13bは、『導通状態』(第1、第2の初段制御用信号in_clk1、in_clk2を受けており、第1、第2のクロックド・インバータ13a、13bに入力されたモード選択信号MS及びデータ信号DTを出力することが可能な状態。)であり、第5、第7のトランスミッションゲート21a、21bは、『導通状態』であり、第1、第2のバッファ23a、23bは、PMOSトランジスタ22a及びNMOSトランジスタ22bによってその入力端に強制的に「1」又は「0」が印加されていない『導通状態』である。全体を要約すれば、初期には、モード選択信号端子MS_Tに与えられるモード選択信号MS、及び、データ信号端子DT_Tに与えられるデータ信号DTが、発振装置DEV内のモード設定回路100にそのまま到達することができる状態である。

【0028】

説明では、また、”正論理”を採用し、即ち、電源電位Vddを「1」(High信号)とし、接地電位GNDを「0」(Low信号)とする。

【0029】

説明では、さらに、中後段ユニット20内の第1のバッファ23aから、「1」の許可信号(後述)又はPMOSトランジスタ22aが強制的に設定する信号が出力されるとき、モード設定回路100は、第2のバッファ23bから出力されるデータ信号DTを受け付けるものである。

【0030】

工程1:第1の工程である工程1では、例えば、前記発振システム回路SYSの製造過程で、上記初期の状態の発振システム回路SYSに温度補償用データ700に関する処理(RAMエミュレーションモード、PROM書込モード、及び、PROMベリファリモード)を経た後、図3及び図7の工程1に示されるように、モード制御装置CNTにモード選択信号MS「1」が持続的に入力されている間、クロック信号CLKに同期して「端子遮断モード」の開始を表わす「1111」であるデータ信号DTがデータ信号端子DT_Tに入力された後、手段ユニット10、中後段ユニット20を介してモード設定回路に供給される。

尚、RAMエミュレーションモードでは、前記温度補償回路400が、初段ユニット10と中後段ユニット20とを介して供給を受けたデータ信号DTに基づくRAM300に一時的に格納された温度補償用データを用いて前記水晶振動子500と発振回路600とからなる水晶発振装置の発振動作について前記温度補償を行うことにより、当該温度補償の動作を確認する。上記したRAMエミュレーションモードに引き続き行うPROM書込モードでは、前記RAM300に一時的に格納されている前記温度補償用データをPROM200に固定的に書き込む(図1に示す温度補償データ700)。前記PROM書込モードに引き続くPROMベリファイモードでは、前記PROM200に固定的に書き込んだ温度補償用データ700の内容を検証するものである。

【0031】

工程2:第2の工程である工程2では、図4及び図7の工程2に示されるように、クロック信号CLKにおける5番目のパルスが入力されると、モード設定回路100は、「1」の切換信号swを出力する。当該「1」の切換信号swを受けると、第1の遅延回路31は、「1」の第1の制御信号cnt1を出力し、また、第2の遅延回路32は、前記第1の遅延回路31が「1」の第1の制御信号cnt1を出力することに僅かに遅れて、「1」の第2の制御信号cnt2を出力する。

【0032】

「1」の第1の制御信号cnt1を受けると、インバータ24は、「0」を出力し、これにより、PMOSトランジスタ22aは、「オン」になる。この結果、第1のバッファ23aは、その入力端に「1」が入力され、そのまま、当該「1」、即ち、発振装置DEVの動作(モード設定回路100の受け付け動作。)を保持すべき旨を示す「1」である『保持信号』を出力する。

【0033】

また、「1」の第1の制御信号cnt1を受けると、NMOSトランジスタ22bは、「オン」になり、これにより、第2のバッファ23bは、その入力端に「0」が入力され、そのまま、当該「0」を出力する。

【0034】

他方で、「1」の第2の制御信号cnt2を受けると、インバータ25は、「0」を出力する。さらに、前記「1」の第2の制御信号cnt2及びインバータ25からの信号「0」を受けると、トランスミッションゲート21a、21bは、『遮断状態』になる。

【0035】

上記した、第1のバッファ23aからの『保持信号』の出力、及び、トランスミッションゲート21a、21bの『遮断状態』により、発振装置DEVの動作、即ち、モード設定回路100の動作が保持される。

【0036】

工程3:図5及び図7の工程3に示されるように、クロック信号CLKにおけるn番目(nは、任意の正の整数)のビット「1」が入力されると、モード設定回路100は、ヒューズユニット40に、「1」の遮断信号cutを出力する。当該「1」の遮断信号cutを受けると、ヒューズユニット40では、NMOSトランジスタ41は、「オン」になり、これにより、第1のカレントミラー回路42に、抵抗器43により規定される電流i1が流れるとともに、第1のカレントミラー回路42のトランジスタ比に応じた電流i2が流れる。電流i2が高抵抗44に流れることでNMOSトランジスタ45のベース電圧が上昇し、当該遮断用NMOSトランジスタ45は、「オン」になり、これにより、ヒューズ46に電流i3(過大電流)が流れ、当該電流i3により、ヒューズは切断され、即ち、「オープン」になる。

【0037】

ヒューズ46が「オープン」になると、第2のカレントミラー回路47の引き込み電流によってインバータ49の入力電位がほぼGND電位になり、この結果、インバータ49は「1」を出力する。換言すれば、ヒューズユニット40は、「1」の遮断信号cutを受けて「0」の第1の初段制御用信号in_clk1と、「1」の第2の初段制御用信号in_clk2を初段ユニット10に出力する。前段ユニット10では、前記「0」の第1の初段制御用信号in_clk1及び前記「1」の第2の初段制御用信号in_clk2信号が入力されると、第1、第2のクロックド・インバータ13a、13bは、出力端がハイインピーダンスの状態、即ち、『遮断状態』になり、また、NMOSトランジスタ12a、12bは、「オフ」になるので、モード選択信号端子、データ信号端子からみて入力抵抗の値が大きい状態となる。しかしながら、このとき第1のバッファ23aは、『保持信号』を出力し続けることから、発振装置DEVの動作は、工程2での設定状態が引き続き維持される。

【0038】

工程4:図6及び図7の工程4に示されるように、前記発振システム回路SYSは、モード選択信号MSが「0」に設定されることによって、初段ユニット10の第1、第2のクロックド・インバータ13a、13bは、『遮断状態』となる。

【0039】

また、電源電圧Vddが再投入された後、初段ユニット10では、第1、第2のクロックド・インバータ13a、13bは、『遮断状態』のままである。すなわち、製品出荷後にユーザー側で電源電圧Vddを投入した場合においても、初段ユニット10は遮断状態が維持される。

【0040】

他方で、ヒューズユニット40では、ヒューズ46が「オープン(切断)」であることから、第1の初段制御用信号in_clk1は、実質的に「0」のままである。当該「0」である第1の初段制御用信号in_clk1を受けると、初段ユニット10内のPMOSトランジスタ15a、PMOSトランジスタ15bは、「オン」になり、これにより、インバータ16a、16bは、その入力端に「1」が印加され、その結果として、出力端から「0」を出力する。

【0041】

第1、第2のインバータ16a、16bから「0」を受けると、トランスミッションゲート21a、21bは、前記「0」をそのまま出力し、当該「0」を受けると、第1、第2のバッファ23a、23bは、当該「0」をそのまま出力し、即ち、前記発振装置DEVに前記動作(データ信号DTの受付動作)を禁止する『禁止信号』を出力する。

【0042】

《効果》

上記した発振システムSYSによれば、工程4以後には、仮に、モード選択信号端子MS_T及びデータ信号端子DT_Tに外乱が加わって、例えば、モード選択信号端子MS_Tに、発振装置DEVの動作(モード設定回路100によるデータ信号DTの受付動作)の許否に悪影響を及ぼし得る外乱「1」が印加されても、クロックド・インバータ13aが『遮断状態』であることから、当該外乱「1」が、トランスミッションゲート21a及びバッファ23aを経由してモード設定回路100等に出力されることはなく、これにより、モード設定回路100は、データ信号DTを受け付けることができず、即ち、上記のような外乱「1」の影響に起因する不測の誤動作を回避することが可能となる。更に、NMOSトランジスタ12a、12bがオフ状態であることによりモード選択信号端子MS_Tとデータ信号端子DT_Tとが接地電位GNDと切離され入力抵抗・入力インピーダンスが高い状態であるので例えば、発振システム回路SYSの電源電圧Vddの端子とモード選択信号端子MS_Tとの間が導電性異物等により短絡してしまっても、電源電圧Vddの端子と接地電位GNDである配線とが短絡しないので発振システム回路や発振システム回路を搭載した装置の動作が停止するなどの誤動作が起きるのを防止することができる。

更に、発振システム回路を有する発振装置として発振システム回路を収容するパッケージに設けたデータ信号端子やモード選択信号端子等の信号端子構造を特殊なものとすることなく外乱による異常動作発生を防止することができるので、パッケージの設計自由度が広がり、発振装置の小型化、低価格化を十分達成させることができる。

【図面の簡単な説明】

【0043】

【図1】実施例の発振システムの構成を示す図。

【図2】実施例の発振システムの動作を示す図(その1)。

【図3】実施例の発振システムの動作を示す図(その2)。

【図4】実施例の発振システムの動作を示す図(その3)。

【図5】実施例の発振システムの動作を示す図(その4)。

【図6】実施例の発振システムの動作を示す図(その5)。

【図7】実施例の発振システムの動作を示すタイミングチャート。

【図8】実施例のクロックド・インバータの構成を示す図。

【図9】従来の発振システムの構成を示す図。

【符号の説明】

【0044】

SYS…発振システム、CNT…モード制御装置、DEV…発振装置、10…初段ユニット、20…中後段ユニット、30…遅延ユニット、40…ヒューズユニット、13a、13b…クロックド・インバータ、23a、23b…バッファ。

【特許請求の範囲】

【請求項1】

被制御装置と、動作制御装置と、モード選択信号端子と、データ信号端子とを有し、

前記動作制御装置が前記モード選択信号端子に入力されたモード選択信号と前記データ信号端子に入力されたデータ信号とを前記被制御装置に供給する機能を有するシステム回路であり、

前記被制御装置が、モード設定回路とメモリとを有し、

前記動作制御装置が、初段ユニットと中後段ユニットと遅延ユニットとヒューズユニットとを有し、

前記初段ユニットが、前記モード選択信号端子から供給された前記モード選択信号と前記データ信号端子から供給された前記データ信号とを初段出力信号として前記中後段ユニットへ供給するものであり、

前記中後段ユニットが、前記初段ユニットから供給された前記モード選択信号を前記モード設定回路に、前記初段ユニットから供給された前記データ信号を前記メモリと前記モード設定回路に、それぞれ中後段出力信号として供給するものであり、

前記遅延ユニットが、第1の遅延回路と、第2の遅延回路とを有し、

前記第1の遅延回路が、前記モード設定回路の切換信号に従い第1の制御信号を前記中後段ユニットに供給するものであり、

前記第2の遅延回路が、前記モード設定回路の制御信号に従い前記第1の制御信号の出力から遅れて第2の制御信号を前記中後段ユニットに供給するものであり、

前記ヒューズユニットが、前記モード設定回路の制御信号に従い前記第2の制御信号の出力から遅れて初段制御用信号を前記初段ユニットに供給するものであり、

前記中後段ユニットが、前記第1の制御信号を受けて該中後段ユニットの中後段出力信号をモード選択信号とデータ信号とを前記被制御装置の動作状態を保持させる為の保持信号に切り換えて出力する機能と、前記第2の制御信号を受けて前記初段ユニットとの前記モード選択信号及び前記データ信号の伝達路を遮断状態とする機能を有し、

前記初段ユニットが、前記初段制御用信号を受けて前記モード選択信号端子の入力インピーダンス及び入力抵抗の値と前記データ信号入力端子の入力インピーダンス及び入力抵抗の値とを大きくする機能と、該初段ユニットの前記初段出力信号を固定値とする機能を有するシステム回路。

【請求項2】

前記初段ユニットが、前記初段制御用信号を受けて固定値0の前記初段出力信号を出力するものであることを特徴とする請求項1に記載のシステム回路。

【請求項3】

前記初段ユニットが、第1〜第4のスイッチ回路と、第1のクロックド・インバータと、第2のクロックド・インバータと、前記初段出力信号を出力する第1及び第2のインバータとを有し、

前記モード選択信号端子と固定電位間に第1のスイッチ回路を接続し、前記モード選択信号端子に第1のクロックド・インバータの入力端を接続し、前記第1のインバータの閾値電位よりも高電位の固定電位と前記第1のクロックド・インバータの出力端との間に第2のスイッチ回路を接続し、前記第1のクロックド・インバータの出力端と第1のインバータの入力端とを接続した構成と、

前記データ信号端子と固定電位間に第3のスイッチ回路を接続し、前記モード選択信号端子に第2のクロックド・インバータの入力端を接続し、前記第2のインバータの閾値電位よりも高電位の固定電位と前記第2のクロックド・インバータの出力端との間に第4のスイッチ回路を接続し、前記第2のクロックド・インバータの出力端と第2のインバータの入力端とを接続した構成と、を有し、

前記初段制御用信号による制御に基づき、前記第1のスイッチ回路と第3のスイッチ回路をオフに、第1のクロックド・インバータと第2のクロックド・インバータの出力インピーダンスを高インピーダンスに、前記第2のスイッチ回路と前記第4のスイッチ回路をオンにするものであることを特徴とする請求項1に記載のシステム回路。

【請求項4】

前記中後段ユニットが、第5〜第8のスイッチ回路と、第1のバッファと、第2のバッファとを有し、

前記第1のバッファの入力端と前記手段ユニットの前記第1のインバータの出力端との間に前記第5のスイッチ回路を接続し、前記第1のバッファの入力端と固定電位間に前記第6のスイッチ回路を接続し、前記第1のバッファの出力端を前記モード設定回路側に接続した構成を有し、

前記第2のバッファの入力端と前記初段ユニットの前記第2のインバータの出力端との間に前記第7のスイッチ回路を接続し、前記第2のバッファの入力端と固定電位間に前記第8のスイッチ回路を接続し、前記第2のバッファの出力端を前記メモリ側に接続した構成を有し、

前記第1の制御信号による制御に基づき、前記第6のスイッチ回路と前記第8のスイッチ回路をオンに、前記第2の制御信号による制御に基づき、前記第5のスイッチ回路と前記第7のスイッチ回路をオフにするものであることを特徴とする請求項1乃至3のいずれか一項に記載のシステム回路。

【請求項5】

前記被制御装置が、圧電発振回路と、該圧電発振回路の周波数温度特性を補償する為の温度補償回路とを備え、

前記メモリに記憶されたデータに基づき前記温度補償回路の動作を制御する発振装置であることを特徴とする請求項1乃至4のいずれか一項に記載のシステム回路。

【請求項6】

被制御装置と、動作制御装置と、モード選択信号端子と、データ信号端子とを有し、

前記動作制御装置が、初段ユニットと中後段ユニットと遅延ユニットとヒューズユニットとを有し、前記モード選択信号端子に入力されたモード選択信号と前記データ信号端子に入力されたデータ信号とを前記被制御装置に供給する機能を有し、

前記遅延ユニットが、第1の遅延回路と、第2の遅延回路とを有し、

前記被制御装置が、モード設定回路とメモリとを有するシステム回路の設定方法であり、

前記初段ユニットが、前記モード選択信号端子から供給された前記モード選択信号と前記データ信号端子から供給された前記データ信号とを初段出力信号として前記中後段ユニットへ供給する工程と、

前記中後段ユニットが、前記初段ユニットから供給された前記モード選択信号を前記モード設定回路に、前記初段ユニットから供給された前記データ信号を前記メモリと前記モード設定回路に、それぞれ中後段出力信号として供給する工程と、

前記第1の遅延回路が、前記モード設定回路の制御信号に従い第1の制御信号を前記中後段ユニットに供給する工程と、

前記第2の遅延回路が、前記モード設定回路の切換信号に従い前記第1の制御信号の出力から遅れて第2の制御信号を前記中後段ユニットに供給する工程と、

前記ヒューズユニットが、前記モード設定回路の制御信号に従い前記第2の制御信号の出力から遅れて初段制御用信号を前記初段ユニットに供給する工程と、

前記中後段ユニットが、前記第1の制御信号を受けて該中後段ユニットの中後段出力信号をモード選択信号とデータ信号とを前記被制御装置の動作状態を保持させる為の保持信号に切り換えて出力する工程と、

前記中後段ユニットが、前記第2の制御信号を受けて前記初段ユニットとの前記モード選択信号及び前記データ信号の伝達路を遮断状態とする工程と、

前記初段ユニットが、前記初段制御用信号を受けて前記モード選択信号端子の入力インピーダンス及び入力抵抗の値と前記データ信号入力端子の入力インピーダンス及び入力抵抗の値とを大きくするよう制御する工程と、

前記初段ユニットが、該初段ユニットの前記初段出力信号を固定値とするよう制御する工程と、を有するシステム回路の設定方法。

【請求項1】

被制御装置と、動作制御装置と、モード選択信号端子と、データ信号端子とを有し、

前記動作制御装置が前記モード選択信号端子に入力されたモード選択信号と前記データ信号端子に入力されたデータ信号とを前記被制御装置に供給する機能を有するシステム回路であり、

前記被制御装置が、モード設定回路とメモリとを有し、

前記動作制御装置が、初段ユニットと中後段ユニットと遅延ユニットとヒューズユニットとを有し、

前記初段ユニットが、前記モード選択信号端子から供給された前記モード選択信号と前記データ信号端子から供給された前記データ信号とを初段出力信号として前記中後段ユニットへ供給するものであり、

前記中後段ユニットが、前記初段ユニットから供給された前記モード選択信号を前記モード設定回路に、前記初段ユニットから供給された前記データ信号を前記メモリと前記モード設定回路に、それぞれ中後段出力信号として供給するものであり、

前記遅延ユニットが、第1の遅延回路と、第2の遅延回路とを有し、

前記第1の遅延回路が、前記モード設定回路の切換信号に従い第1の制御信号を前記中後段ユニットに供給するものであり、

前記第2の遅延回路が、前記モード設定回路の制御信号に従い前記第1の制御信号の出力から遅れて第2の制御信号を前記中後段ユニットに供給するものであり、

前記ヒューズユニットが、前記モード設定回路の制御信号に従い前記第2の制御信号の出力から遅れて初段制御用信号を前記初段ユニットに供給するものであり、

前記中後段ユニットが、前記第1の制御信号を受けて該中後段ユニットの中後段出力信号をモード選択信号とデータ信号とを前記被制御装置の動作状態を保持させる為の保持信号に切り換えて出力する機能と、前記第2の制御信号を受けて前記初段ユニットとの前記モード選択信号及び前記データ信号の伝達路を遮断状態とする機能を有し、

前記初段ユニットが、前記初段制御用信号を受けて前記モード選択信号端子の入力インピーダンス及び入力抵抗の値と前記データ信号入力端子の入力インピーダンス及び入力抵抗の値とを大きくする機能と、該初段ユニットの前記初段出力信号を固定値とする機能を有するシステム回路。

【請求項2】

前記初段ユニットが、前記初段制御用信号を受けて固定値0の前記初段出力信号を出力するものであることを特徴とする請求項1に記載のシステム回路。

【請求項3】

前記初段ユニットが、第1〜第4のスイッチ回路と、第1のクロックド・インバータと、第2のクロックド・インバータと、前記初段出力信号を出力する第1及び第2のインバータとを有し、

前記モード選択信号端子と固定電位間に第1のスイッチ回路を接続し、前記モード選択信号端子に第1のクロックド・インバータの入力端を接続し、前記第1のインバータの閾値電位よりも高電位の固定電位と前記第1のクロックド・インバータの出力端との間に第2のスイッチ回路を接続し、前記第1のクロックド・インバータの出力端と第1のインバータの入力端とを接続した構成と、

前記データ信号端子と固定電位間に第3のスイッチ回路を接続し、前記モード選択信号端子に第2のクロックド・インバータの入力端を接続し、前記第2のインバータの閾値電位よりも高電位の固定電位と前記第2のクロックド・インバータの出力端との間に第4のスイッチ回路を接続し、前記第2のクロックド・インバータの出力端と第2のインバータの入力端とを接続した構成と、を有し、

前記初段制御用信号による制御に基づき、前記第1のスイッチ回路と第3のスイッチ回路をオフに、第1のクロックド・インバータと第2のクロックド・インバータの出力インピーダンスを高インピーダンスに、前記第2のスイッチ回路と前記第4のスイッチ回路をオンにするものであることを特徴とする請求項1に記載のシステム回路。

【請求項4】

前記中後段ユニットが、第5〜第8のスイッチ回路と、第1のバッファと、第2のバッファとを有し、

前記第1のバッファの入力端と前記手段ユニットの前記第1のインバータの出力端との間に前記第5のスイッチ回路を接続し、前記第1のバッファの入力端と固定電位間に前記第6のスイッチ回路を接続し、前記第1のバッファの出力端を前記モード設定回路側に接続した構成を有し、

前記第2のバッファの入力端と前記初段ユニットの前記第2のインバータの出力端との間に前記第7のスイッチ回路を接続し、前記第2のバッファの入力端と固定電位間に前記第8のスイッチ回路を接続し、前記第2のバッファの出力端を前記メモリ側に接続した構成を有し、

前記第1の制御信号による制御に基づき、前記第6のスイッチ回路と前記第8のスイッチ回路をオンに、前記第2の制御信号による制御に基づき、前記第5のスイッチ回路と前記第7のスイッチ回路をオフにするものであることを特徴とする請求項1乃至3のいずれか一項に記載のシステム回路。

【請求項5】

前記被制御装置が、圧電発振回路と、該圧電発振回路の周波数温度特性を補償する為の温度補償回路とを備え、

前記メモリに記憶されたデータに基づき前記温度補償回路の動作を制御する発振装置であることを特徴とする請求項1乃至4のいずれか一項に記載のシステム回路。

【請求項6】

被制御装置と、動作制御装置と、モード選択信号端子と、データ信号端子とを有し、

前記動作制御装置が、初段ユニットと中後段ユニットと遅延ユニットとヒューズユニットとを有し、前記モード選択信号端子に入力されたモード選択信号と前記データ信号端子に入力されたデータ信号とを前記被制御装置に供給する機能を有し、

前記遅延ユニットが、第1の遅延回路と、第2の遅延回路とを有し、

前記被制御装置が、モード設定回路とメモリとを有するシステム回路の設定方法であり、

前記初段ユニットが、前記モード選択信号端子から供給された前記モード選択信号と前記データ信号端子から供給された前記データ信号とを初段出力信号として前記中後段ユニットへ供給する工程と、

前記中後段ユニットが、前記初段ユニットから供給された前記モード選択信号を前記モード設定回路に、前記初段ユニットから供給された前記データ信号を前記メモリと前記モード設定回路に、それぞれ中後段出力信号として供給する工程と、

前記第1の遅延回路が、前記モード設定回路の制御信号に従い第1の制御信号を前記中後段ユニットに供給する工程と、

前記第2の遅延回路が、前記モード設定回路の切換信号に従い前記第1の制御信号の出力から遅れて第2の制御信号を前記中後段ユニットに供給する工程と、

前記ヒューズユニットが、前記モード設定回路の制御信号に従い前記第2の制御信号の出力から遅れて初段制御用信号を前記初段ユニットに供給する工程と、

前記中後段ユニットが、前記第1の制御信号を受けて該中後段ユニットの中後段出力信号をモード選択信号とデータ信号とを前記被制御装置の動作状態を保持させる為の保持信号に切り換えて出力する工程と、

前記中後段ユニットが、前記第2の制御信号を受けて前記初段ユニットとの前記モード選択信号及び前記データ信号の伝達路を遮断状態とする工程と、

前記初段ユニットが、前記初段制御用信号を受けて前記モード選択信号端子の入力インピーダンス及び入力抵抗の値と前記データ信号入力端子の入力インピーダンス及び入力抵抗の値とを大きくするよう制御する工程と、

前記初段ユニットが、該初段ユニットの前記初段出力信号を固定値とするよう制御する工程と、を有するシステム回路の設定方法。

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【公開番号】特開2008−28800(P2008−28800A)

【公開日】平成20年2月7日(2008.2.7)

【国際特許分類】

【出願番号】特願2006−200394(P2006−200394)

【出願日】平成18年7月24日(2006.7.24)

【出願人】(000003104)エプソントヨコム株式会社 (1,528)

【Fターム(参考)】

【公開日】平成20年2月7日(2008.2.7)

【国際特許分類】

【出願日】平成18年7月24日(2006.7.24)

【出願人】(000003104)エプソントヨコム株式会社 (1,528)

【Fターム(参考)】

[ Back to top ]