シフトレジスタ

【課題】シフトレジスタ動作を小さいチップ面積で実現可能とし且つクロック入力の立ち上がり(もしくは立ち下がり)エッジのみで動作可能とするシフトレジスタを提供する。

【解決手段】制御信号CK(36)がLで制御信号CKb(37)がHのとき、スイッチ12を経て入力信号D(11)はラッチセル13のインバータ14に加えられ、インバータ14の出力信号がラッチセル13の出力としてインバータ16で反転されてシフト出力Q0(17)となる。スイッチ18は制御信号CKb(37)が立ち下がる時点、すなわちクロック入力CK_in(34)の立ち上がり時点で動作してラッチセル13の出力を通過させ、ラッチセル19のインバータ20に加え、インバータ20の出力信号がラッチセル19の出力としてシフト出力Q1(22)となる。以下同様に、スイッチ23,29及びラッチセル24,30を経て入力信号D(11)がシフト出力Q2(28),Q3(33)に次々と伝搬される。

【解決手段】制御信号CK(36)がLで制御信号CKb(37)がHのとき、スイッチ12を経て入力信号D(11)はラッチセル13のインバータ14に加えられ、インバータ14の出力信号がラッチセル13の出力としてインバータ16で反転されてシフト出力Q0(17)となる。スイッチ18は制御信号CKb(37)が立ち下がる時点、すなわちクロック入力CK_in(34)の立ち上がり時点で動作してラッチセル13の出力を通過させ、ラッチセル19のインバータ20に加え、インバータ20の出力信号がラッチセル19の出力としてシフト出力Q1(22)となる。以下同様に、スイッチ23,29及びラッチセル24,30を経て入力信号D(11)がシフト出力Q2(28),Q3(33)に次々と伝搬される。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、シフトレジスタ動作を小さいチップ面積で実現可能とし且つ入力信号をクロック信号毎にシフトさせることができるシフトレジスタに関する。

【背景技術】

【0002】

図5A及び図5Bは、従来のシフトレジスタの基本構成を示す回路図である。図5A(a)に示すように従来のシフトレジスタは、入力信号D(151)を印加する側から順に第1のアナログスイッチ152、第1のラッチセル153、・・・、第4のアナログスイッチ165、第4のラッチセル166を並べて構成し、2つのアナログスイッチ及び2つのラッチセルの組で1つのフリップフロップ170,171を形成しフリップフロップ170,171の出力端から出力Q0(160),Q1(169)を得るものである。ラッチセル例えば第1のラッチセル153は、インバータ154と、インバータ154の出力にその入力が接続されまたインバータ154の入力にその出力が接続されるクロックドインバータ155とで構成される。図5A(b)は、クロック入力CK_in(172)から制御信号CK及び制御信号CKbを生成する回路を示すもので、インバータ173とインバータ175の直列回路であり、クロック入力CK_in(172)が入力されている。制御信号CK(176)は2つ目のインバータ175の出力から生成され、また制御信号CKb(174)は1つ目のインバータ173の出力から生成され、図5A(a)のアナログスイッチ及びクロックドインバータにそれぞれ印加される。

【0003】

図5Bは、図5Aに示した回路記号の詳細を示す回路図である。図5B(a)に示すアナログスイッチ181は、回路的にはPチャネルMOSFET(182)とNチャネルMOSFET(183)より成り、両方のMOSFETの各ソース同士、各ドレイン同士を接続している。そしてMOSFET(182,183)のゲートに印加される制御信号Gp(184),Gn(185)によってT1(186)及びT2(187)相互間の信号通過をスイッチング制御する。いまGp(184)が「L」(LOW)レベルでGn(185)が「H」(HIGH)レベルのときは、スイッチはオン動作をし、T1(186)及びT2(187)相互間に信号を流すことができる。またGp(184)が「H」レベルでGn(185)が「L」レベルのときは、スイッチはオフ動作をし、T1(186)及びT2(187)相互間の信号通過を遮断する。

【0004】

図5B(b)に示すインバータ191は、反転(NOT)回路であり、回路的にはPチャネルMOSFET(192)とNチャネルMOSFET(193)より成り、2個のMOSFET(192,193)が電源からグランドに直列に結線される。そして入力IN(194)が「L」レベルのときは、出力OUT(195)は「H」レベルとなるよう動作する。また入力IN(194)が「H」レベルのときは、出力OUT(195)は「L」レベルとなるよう動作する。

【0005】

図5B(c)に示すクロックドインバータ201は、回路的には2つのPチャネルMOSFET(202,203)と2つのNチャネルMOSFET(204,205)より成り、4個のMOSFET(202〜205)が電源からグランドにすべて直列に結線される。そしてGp(206)が「L」レベルでGn(207)が「H」レベルのときは、入力IN(208)のレベルを反転した出力を出力OUT(209)から出力して通常のインバータと同じ動作をする。またGp(206)が「H」レベルでGn(207)が「L」レベルのときは、入力IN(208)の状態にかかわらず出力OUT(209)は電源、グランド双方から切り離され、いわゆるオープンの状態となり、ハイインピーダンスを呈する。

【0006】

図6は、図5A及び図5Bに示した従来のシフトレジスタの典型的な動作波形を示すタイミング図である。図6に示すように、制御信号CK(176)が「L」レベルで制御信号CKb(174)が「H」レベルのとき、入力信号D(151)が第1のフリップフロップ170の第1のラッチセル153に取り込まれ、次いで制御信号CK(176)が「H」レベルで制御信号CKb(174)が「L」レベルのとき、第1のフリップフロップ170の第1のラッチセル153に取り込まれた入力信号D(151)が第1のフリップフロップ170の第2のラッチセル157に取り込まれて保持される。第2のフリップフロップ171についても同様な動作をする。このようにして、入力信号D(151)が、クロック入力CK_in(172)の立ち上がり毎にシフトされて、フリップフロップ出力Q0(160),Q1(169),・・・と、順にシフト出力されることが分かる。

【0007】

このように従来のシフトレジスタは、2つのスイッチおよびラッチセルから構成されるフリップフロップを並べて構成され、入力信号D(151)が、クロック入力CK_in(172)の立ち上がり毎にシフトされて、出力Q0(160),Q1(169),・・・として出力を取り出すため、LSIでこのシフトレジスタを実現するとチップ面積が大きくなってしまうという問題があった。

【0008】

この問題を解決するための一方策が特許文献1に提示されている。すなわち特許文献1の図1に開示されたシフトレジスタでは、シフトレジスタを構成するハーフステージ20a,20b,・・・からそれぞれ出力を取り出すことによってシフトレジスタ動作を小さいチップ面積で実現可能としている。

【特許文献1】特開平11-164090号公報(段落0009〜0011、図1)

【発明の開示】

【発明が解決しようとする課題】

【0009】

しかし特許文献1に提示されているシフトレジスタは、シフトレジスタ動作を小さいチップ面積で実現可能としてはいるものの、クロック入力の立ち上がり及び立ち下がりの両側エッジで動作させているため、通常のシフトレジスタと同様に扱うことができず当該シフトレジスタを利用しようとする回路設計者には扱いにくいという課題がある。

【0010】

上記した課題を解決するため本発明は、シフトレジスタ動作を小さいチップ面積で実現可能とし且つクロック入力の立ち上がりもしくは立ち下がりの一方のエッジのみで動作可能とするシフトレジスタを提供することを目的とする。

【課題を解決するための手段】

【0011】

本発明のシフトレジスタは、シフトデータの入力側から出力側に向けてアナログスイッチおよびラッチセルをこの順に複数並べ且つ前段のラッチセルの出力を直接アナログスイッチに入力するようにし、前記ラッチセルのそれぞれの出力端からシフト出力を引き出すシフトレジスタであって、クロック入力の立ち上がりもしくは立ち下がりの一方のエッジのみで動作するトグルフリップフロップの出力から制御信号を生成する制御信号生成回路を備え、前記アナログスイッチおよび前記ラッチセルの動作を制御する制御端子に前記制御信号生成回路が生成した制御信号を入力して前記ラッチセルから前記シフト出力を得ることを特徴とするものである。

【発明の効果】

【0012】

本発明によれば、シフトレジスタ動作を小さいチップ面積で実現可能とし且つクロック入力の立ち上がりもしくは立ち下がりの一方のエッジのみで動作させることができるので、通常のシフトレジスタと同様に一般回路と馴染みがよく、所定部分のみを従来回路と置き換えることも可能で、シフトレジスタを利用しようとする回路設計者にとって扱いやすい。また本発明によれば、出力の正論理/負論理の整合をとるためのインバータの個数を削減することができる。

【図面の簡単な説明】

【0013】

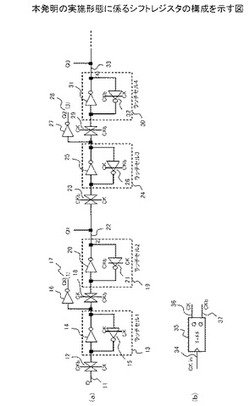

【図1A】本発明の実施形態に係るシフトレジスタの構成を示す図である。

【図1B】図1Aに示した回路記号の詳細を示す回路図である。

【図2】本発明の実施形態に係るシフトレジスタの動作波形を示すタイミング図である。

【図3】本発明を双方向シフトレジスタに適用した場合の参考例を示す図である。

【図4】本発明を双方向シフトレジスタに適用した場合の参考例の動作波形を示すタイミング図である。

【図5A】従来のシフトレジスタの基本構成を示す図である。

【図5B】図5Aに示した回路記号の詳細を示す回路図である。

【図6】従来のシフトレジスタの典型的な動作波形を示すタイミング図である。

【発明を実施するための最良の形態】

【0014】

以下、本発明の実施の形態を、図面を参照しながら説明する。

[実施形態]

図1A及び図1Bは、本発明の実施形態に係るシフトレジスタの構成を示す回路図である。図1A(a)に示すように本発明の実施形態に係るシフトレジスタは、入力信号D(11)を印加する側から順に第1のアナログスイッチ12、第1のラッチセル13、・・・、第4のアナログスイッチ29、第4のラッチセル30を並べて構成し且つ前段のラッチセルの出力を直接アナログスイッチに入力するようにし、各ラッチセルの出力端から出力Q0(17)、Q1(22)、Q2(28)、Q3(33)を得るものである。ラッチセル、例えば第1のラッチセル13は、インバータ14と、インバータ14の出力にその入力が接続されまたインバータ14の入力にその出力が接続されるクロックドインバータ15とにより構成される。ラッチセル出力端から取り出す論理は出力を利用する形態に応じてインバータ(反転回路)16,27を適宜付加する。図1A(b)は、クロック入力CK_in(34)の立ち上がり信号にて動作するT-FF(トグルフリップフロップ)35を有し、T-FF35に対してクロック入力CK_in(34)を入力し、クロックの立ち上がり信号にて動作するT-FF35から制御信号CK(36)及びCKb(37)を得る制御信号生成回路を示す。すなわち、制御信号CK(36)は、T-FF35のQ出力から生成され、また制御信号CKb(37)は、T-FF35のQb出力から生成され、それぞれ図1A(a)のアナログスイッチ及びクロックドインバータに印加される。

【0015】

図1Bは、図1Aに示した回路記号の詳細を示す回路図であり、既述した図5Bの回路図の構成と同じであるが、再度説明すれば、図1B(a)に示すアナログスイッチ41は、回路的にはPチャネルMOSFET(42)とNチャネルMOSFET(43)より成り、両方のMOSFETの各ソース同士、各ドレイン同士を接続している。そしてMOSFET(42,43)のゲートに印加される制御信号Gp(44),Gn(45)によってT1(46)及びT2(47)相互間の信号通過をスイッチング制御する。いまGp(44)が「L」レベルでGn(45)が「H」レベルのときは、スイッチすなわちMOSFET(42,43)はオン動作をし、T1(46)及びT2(47)相互間に信号を流すことができる。またGp(44)が「H」レベルでGn(45)が「L」レベルのときは、スイッチすなわちMOSFET(42,43)はオフ動作をし、T1(46)及びT2(47)相互間の信号通過を遮断する。

【0016】

図1B(b)に示すインバータ51は、反転(NOT)回路であり、回路的にはPチャネルMOSFET(52)とNチャネルMOSFET(53)より成り、2個のMOSFET(52,53)が電源からグランドに直列に結線される。そして入力IN(54)が「L」レベルのときは、PチャネルMOSFET(52)が導通し、PチャネルMOSFET(52)ドレインからの出力により出力OUT(55)は「H」レベルとなるよう動作する。また入力IN(54)が「H」レベルのときは、NチャネルMOSFET(53)が導通し、NチャネルMOSFET(53)ドレインからの出力により出力OUT(55)は「L」レベルとなるよう動作する。

【0017】

図1B(c)に示すクロックドインバータ61は、回路的には2つのPチャネルMOSFET(62,63)と2つのNチャネルMOSFET(64,65)より成り、4個のMOSFET(62〜65)が電源からグランドにすべて直列に結線される。そしてGp(66)が「L」レベルでGn(67)が「H」レベルのときは、入力IN(68)のレベルを反転した出力を出力OUT(69)から出力して通常のインバータと同じ動作をする。またGp(66)が「H」レベルでGn(67)が「L」レベルのときは、入力IN(68)の状態にかかわらず出力OUT(69)は電源、グランド双方から切り離され、いわゆるオープンの状態となり、ハイインピーダンスを呈する。

【0018】

図2は、図1A及び図1Bに示した本発明の実施形態に係るシフトレジスタの動作波形を示すタイミング図である。図2に示すように、制御信号CK(36)が「L」レベルで制御信号CKb(37)が「H」レベルのとき、第1のアナログスイッチ12を経て入力信号D(ここでDは「H」レベルに固定とする)(11)は第1のラッチセル13のインバータ14に加えられ、インバータ14の出力信号が第1のラッチセル13の出力としてインバータ16で反転されて出力信号(1)、すなわちシフト出力Q0(17)となる。図1A(b)に示すT-FF(トグルフリップフロップ)35は、クロック入力CK_in(34)の立ち上がり信号で動作することでクロック入力CK_in(34)は、T-FF35により1/2に分周され、その間に次のステージのアナログスイッチ18とラッチセル19に入力信号D(11)が伝搬される。つまり、第2のアナログスイッチ18は第1のアナログスイッチ12と異なる制御信号により制御されるため制御信号CKb(37)が立ち下がる時点、すなわちクロック入力CK_in(34)の立ち上がり時点で動作して第1のラッチセル13の出力を通過させて第2のラッチセル19のインバータ20に加え、インバータ20の出力信号が第2のラッチセル19の出力として出力信号(2)、すなわちシフト出力Q1(22)となる。

【0019】

以下のステージも同様に、制御信号CK(36)および制御信号CKb(37)によって制御されるアナログスイッチ23,29およびラッチセル24,30により入力信号D(11)が次々と伝搬されることにより、入力CK_in(11)の立ち上がり毎に、ラッチセルの出力Q0(17),Q1(22),Q2(28),Q3(33),・・・(初期状態は、全て「L」レベルとした)は、順に「H」レベルに変化し、すなわち、シフトレジスタとして動作する。

【0020】

このように本発明の実施形態に係るシフトレジスタは、クロック入力CK_in(11)がT-FF35により分周されて制御信号36,37が生成され、この制御信号によってアナログスイッチ12,18,23,29およびラッチセル13,19,24,30 (これらを“コア回路”と称する)が制御されるものである。これにより、シフトレジスタ動作を小さいチップ面積で実現可能とし且つクロックの立ち上がりエッジのみで動作させることができるので、通常のシフトレジスタと同様に一般の回路と馴染みがよく、所定部分のみを従来回路と置き換えることも可能で、回路設計者にとって扱いやすいシフトレジスタを提供することができる。また本発明の実施形態に係るシフトレジスタは、出力の正論理/負論理の整合をとるためのインバータの個数を削減することができる。

【0021】

なお本発明の実施形態に係るシフトレジスタは、1つのラッチセルで、1つのシフト出力を得ることを基本にし、クロック入力がT-FFにより分周されて制御信号が生成され、この制御信号によってコア回路が制御されるものであるが、必要に応じて、クロックと独立に初期値を確定するためのリセット回路等をコア回路に設けてコア回路を条件付けるようにしても良い。

【0022】

図3は、本発明を双方向シフトレジスタに適用した場合の参考例を示す図である。図3(a)では、説明の都合上、双方向のシフトデータをQ0,Q1,Q2の3ビットを出力するもの(アナログスイッチ120と121の間から後述の右シフトの4ビット目を、アナログスイッチ112と113の間から後述の左シフトの4ビット目を、それぞれ出力しうるが、これらは単方向のシフトデータを出力するものである)について説明するが、ビット数を増やして4ビットシフト以上にすることもできる。

【0023】

図3(a)に示す本双方向シフトレジスタは、双方向に入力信号をシフトさせることができるシフトレジスタであって、図の左から右方向へのシフト動作、すなわちQ0→Q2方向シフト(以降、「右シフト」と称する)と、図の右から左方向へのシフト動作、すなわちQ2→Q0方向シフト(以降、「左シフト」と称する)を行えるよう構成している。そして入力信号DL101は、右シフトの際の入力信号(本例では「H」レベル固定)、また入力信号DR131は左シフトの際の入力信号(本例では「L」レベル固定)である。

【0024】

図3(a)において各々のクロックドインバータおよびアナログスイッチ(「スイッチ」と称する)は、X群およびY群にグループ分けされている(図中の各回路素子にXもしくはYの符号が付されていて、どちらの群に属するかを示している)。右シフトの場合には、X群のクロックドインバータおよびスイッチが常に導通で(クロックドインバータが導通とは、クロック信号(CK,CKb)とは無関係に、通常のインバータとして動作することを意味する。また、クロックドインバータが非導通とは、クロック信号(CK,CKb)によりハイインピーダンス出力と通常出力とを切り替える本来のクロックドインバータとして動作することを意味する。)、Y群のクロックドインバータおよびスイッチがシフトレジスタ機能を実現する動作をし、左シフトの場合には、逆に、Y群のクロックドインバータおよびスイッチが常に導通でX群のクロックドインバータおよびスイッチがシフトレジスタ機能を実現する動作をし、左右いずれの向きに入力信号をシフトさせるか(図3(b)に示す方向入力DIR_in(138)によって決定される)に応じてX群およびY群のクロックドインバータおよびスイッチの動作がそれぞれ制御される。

【0025】

図3(b)は、上記本発明の実施形態で説明したように、T-FF135に対してクロック入力CK_in(134)を入力し、クロック入力CK_in(134)の立ち上がり信号にて動作するT-FF135から制御信号CK(136)及び制御信号CKb(137)を得る制御信号生成回路と、D-FF(遅延型フリップフロップ)139に対して方向入力DIR_in(138)を入力し、D-FF139のクロック端子にクロック入力CK_in(134)の立ち上がり信号を受けたときD-FF139に入力された方向入力DIR_in(138)に応じてD-FF139から方向制御信号DIR(140)及び方向制御信号DIRb(141)を得る方向制御信号生成回路を示す。図3(c)は、図示しないスイッチ制御信号生成回路によりスイッチング制御信号を生成するときの論理式を示すテーブル142である。スイッチ制御信号生成回路は、制御信号CK(136),CKb(137)と方向制御信号DIR(140),DIRb(141)との論理的組み合せからスイッチ制御信号D00,D00b,・・・,D11,D11bを生成する。そして図3(a)のコア回路(上記本発明の実施形態で定義したように、各制御信号により制御されるスイッチおよびラッチセルにより構成される)には、方向制御信号DIR(140),DIRb(141)とスイッチ制御信号D00,D00b,・・・,D11,D11bを与えて、X群およびY群のクロックドインバータおよびスイッチの動作を制御する。

【0026】

図4は、本発明を双方向シフトレジスタに適用した場合の参考例の動作波形を示すタイミング図である。図4のタイミング図に基づいて図3に示す本発明を双方向シフトレジスタに適用した場合の参考例の動作を説明する。いま右シフト動作の場合、方向入力DIR_in(138)は「L」レベルに置かれ、方向制御信号DIR(140)も「L」レベルに置かれているので、D00=D10b=CKb,D00b=D10=CK,D01=D11=L,D01b=D11b=Hとなり、右シフトの第1ステージでは、「H」レベル固定された入力信号DL101はX群の第1のスイッチ112を通過し、第2のスイッチ113で留め置かれる。そしてクロック入力CK_in(134)が立ち上がりその立ち上がりエッジでスイッチ制御信号D10(=CK)が「L」レベルとなると第2のスイッチ113が導通して、留め置かれた入力信号DL101を通過させ、第1のラッチセル102のX群クロックドインバータ103に印加する。クロックドインバータ103はX群のため導通し入力信号DL101を反転した第1のラッチセル102の出力を第3のスイッチ114に印加する。第3のスイッチ114はX群のため導通し第1のラッチセル102の出力はインバータ105でさらに反転して出力信号(1)、すなわちシフト出力Q0(106)を出力する。このため出力Q0(106)は入力信号DL101と同じ「H」レベルになる。

【0027】

右シフトの第2のステージでは、第4のスイッチ115はスイッチ制御信号D00(=CKb)が「L」レベルとなるまで第1のラッチセル102の「L」レベルの出力を留め置く。そしてスイッチ制御信号D00が「L」レベルとなると第1のラッチセル102の出力を通過させ、第2のラッチセル107のX群クロックドインバータ108に印加する。クロックドインバータ108はX群のため導通し反転した入力信号DL101を反転した第2のラッチセル107の「H」レベルの出力を第5のスイッチ116に印加する。第5のスイッチ116はX群のため導通し第2のラッチセル107の「H」レベルの出力を出力信号(2)、すなわちシフト出力Q1(110)として出力する。このため出力Q1(110)は入力信号DL101と同じ「H」レベルになる。

【0028】

右シフトの第3のステージでは、第6のスイッチ117はスイッチ制御信号D10(=CK)が「L」レベルとなるまで第2のラッチセル107の「H」レベルの出力を留め置く。そしてスイッチ制御信号D10が「L」レベルとなると第2のラッチセル107の「H」レベルの出力を通過させ、第3のラッチセル122のX群クロックドインバータ123に印加する。クロックドインバータ123はX群のため導通し入力信号DL101を反転した第3のラッチセル122の出力を第7のスイッチ118に印加する。第7のスイッチ118はX群のため導通し第3のラッチセル122の出力をインバータ125でさらに反転して出力信号(3)、すなわちシフト出力Q2(126)を出力する。このため出力Q2(126)は入力信号DL101と同じ「H」レベルになる。

【0029】

このように右シフトの3ステージまで入力信号DL101が次々と伝搬されることにより、入力CK_in(134)の立ち上がり毎に、ラッチセルの出力Q0(106),Q1(110),Q2(126)(初期状態は、全て「L」レベルとした)は、順に「H」レベルに変化し、すなわち、右シフトするシフトレジスタとして動作していることが分かる。

【0030】

図4における双方向シフトレジスタの動作波形を示すタイミング図では、上記第3ステージにおける右シフト出力、すなわち出力Q2(126)を得た後に図3のシフトレジスタを左シフトに切り替えている。左シフト動作させる、すなわちシフト方向を反転させる場合、方向入力DIR_in(138)が「H」レベルに置かれ、クロック入力CK_in(134)の立ち上がりで方向制御信号DIR(140)およびDIRb(141)がそれぞれ「H」レベルおよび「L」レベルに置かれる。

【0031】

図3に示す双方向シフトレジスタにおいて、D-FF139は、方向制御信号DIR(140)を「L」レベル(右シフト)から「H」レベル(左シフト)に切り替えると同時に次のクロック入力CK_in(134)の立ち上がりエッジまで信号のシフトを防止する役目を担っている。すなわち左シフトに切り替えられてもスイッチ121へのスイッチ制御信号DIRb(141)が「L」レベルになるまでスイッチ121で入力信号DR131の通過を留め置き、これにより信号のシフトを防止する。また入力信号DR131のコア回路におけるシフト動作はクロック入力CK_in(134)の立ち上がりエッジでスイッチ制御信号DIRb(141)が「L」レベルになる時点で開始されることから方向反転入力もクロック同期するようにされる。

【0032】

左シフト動作のため方向制御信号DIR(140),DIRb(141)がそれぞれ「H」レベル,「L」レベルに置かれると、図3(c)のテーブル142に示される論理式を実現するスイッチ制御信号生成回路(図示せず)からのスイッチ制御信号D00,D00b,・・・,D11,D11b(D01=D11b=CKb,D01b=D11=CK,D00=D10=L,D00b=D10b=H)により、上述と同様にY群のクロックドインバータおよびスイッチが常に導通でX群のクロックドインバータおよびスイッチがシフトレジスタ機能を実現する動作を行う。左シフトの第1ステージでは、「L」レベル固定された入力信号DR131はY群の第10のスイッチ121を通過し、第9のスイッチ120はスイッチ制御信号D01(=CKb)が「L」レベルとなるまで入力信号DR131の通過を留め置く。そしてクロック入力CK_in(134)が立ち上がり、その立ち上がりエッジでスイッチ制御信号D01が「L」レベルとなったら第9のスイッチ120が導通して、留め置いた入力信号DR131を通過させ、第4のラッチセル127のY群クロックドインバータ129に印加する。クロックドインバータ129はY群のため導通し入力信号DR131を反転した第4のラッチセル127の「H」レベルの出力を第8のスイッチ119に印加する。第8のスイッチ119はY群のため導通し第4のラッチセル127の「H」レベルの出力をインバータ125でさらに反転して出力信号(3)、すなわちシフト出力Q2(126)を出力する。このため出力Q2(126)は入力信号DR131と同じ「L」レベルになる。

【0033】

左シフトの第2のステージでは、第7のスイッチ118はスイッチ制御信号D11(=CK)が「L」レベルとなるまで第4のラッチセル127の「H」レベル出力を留め置く。そしてスイッチ制御信号D11が「L」レベルとなると第4のラッチセル127の出力を通過させ、第3のラッチセル122のY群クロックドインバータ124に印加する。クロックドインバータ124はY群のため導通し入力信号DR131を反転した第4のラッチセル127の「H」レベルの出力を第6のスイッチ117に印加する。第6のスイッチ117はY群のため導通し第4のラッチセル127の「H」レベルの出力を反転した出力信号(2)、すなわちシフト出力Q1(110)を出力する。このため出力Q1(110)は入力信号DR131と同じ「L」レベルになる。

【0034】

左シフトの第3のステージでは、第5のスイッチ116はスイッチ制御信号D01(=CKb)が「L」レベルとなるまで第3のラッチセル122の「L」レベルの出力を留め置く。そして図4には図示されていないがスイッチ制御信号D01が「L」レベルとなると第5のスイッチ116は第3のラッチセル122の「L」レベルの出力を通過させ、第2のラッチセル107のY群クロックドインバータ109に印加する。クロックドインバータ109はY群のため導通し入力信号DR131を反転した「H」レベルの第2のラッチセル107の出力を第4のスイッチ115に印加する。第4のスイッチ115はY群のため導通し第2のラッチセル107の「H」レベルの出力をインバータ105でさらに反転して出力信号(1)、すなわちシフト出力Q0(106)を出力する。このため出力Q0(106)は入力信号DR131と同じ「L」レベル(図示せず)になる。

【0035】

このように左シフトの3ステージまで入力信号DR131が次々と伝搬されることにより、入力CK_in(134)の立ち上がり毎に、ラッチセルの出力Q2(126),Q1(110),Q0(106)(初期状態は、全て「H」レベルとした)は、順に「L」レベルに変化し、すなわち、左シフトするシフトレジスタとして動作していることが分かる。また方向入力DIR_in(138)を任意のタイミングで切り替えても、ラッチセルの出力Q2(126),Q1(110),Q0(106)はクロックCK_in(134)の立ち上がりエッジでのみ変化することが分かる。

【0036】

以上説明したように本発明を双方向シフトレジスタに適用した場合の参考例は、クロック入力CK_in(134)がT-FF135により分周されて制御信号136,137が生成され、さらに方向入力DIR_in(138)がD-FF139に入力され、D-FF139のクロック端子にクロック入力CK_in(134)の立ち上がり信号を受けたときD-FF139に入力された方向入力DIR_in(138)に応じてD-FF139から方向制御信号140,141が生成され、生成された制御信号136,137と方向制御信号140,141との論理的組み合せからスイッチ制御信号を生成し、方向制御信号140,141とスイッチ制御信号(D00,D00b,・・・,D11,D11b)をコア回路に与えて、コア回路のラッチセルおよびアナログスイッチの動作を制御する。これにより、上記本発明の実施形態に係るシフトレジスタと同様にシフトレジスタ動作を小さいチップ面積で実現可能とし且つクロックの立ち上がりエッジのみで動作させることができるので、通常のシフトレジスタと同様に一般の回路と馴染みがよく、所定部分のみを従来回路と置き換えることも可能で、回路設計者にとって扱いやすい双方向シフトレジスタを提供することができる。

【0037】

なお本発明を双方向シフトレジスタに適用した場合の参考例は、1つのラッチセルで、1つのシフト出力を得ることを基本にし、クロック入力がT-FFにより分周されて制御信号が生成され、さらに方向入力がD-FFに入力され、D-FFのクロック端子にクロック入力の立ち上がり信号を受けたときD-FFに入力された方向入力に応じてD-FFから方向制御信号が生成され、生成された制御信号と方向制御信号との論理的組み合せからスイッチ制御信号を生成し、方向制御信号とスイッチ制御信号をコア回路に与えて、コア回路が制御されるものであるが、必要に応じて、クロックと独立に初期値を確定するためのリセット回路等をコア回路に設けてコア回路を条件付けるようにしても良い。

【0038】

また、今までクロックCK_in(134)の立ち上がりエッジに同期して動作する例について説明してきたが、T-FF(トグルフリップフロップ)35,135およびD-FF(遅延型フリップフロップ)139をクロックCK_in(134)の立ち下がりエッジで出力が切り替わるものに置き換えれば、クロックCK_in(134)の立ち下がりエッジに同期して動作するシフトレジスタを得ることができる。

【符号の説明】

【0039】

11 入力信号D

12 第1のアナログスイッチ

13 第1のラッチセル

14 インバータ

15 クロックドインバータ

16 インバータ

17 シフト出力Q0

18 第2のアナログスイッチ

19 第2のラッチセル

20 インバータ

21 クロックドインバータ

22 シフト出力Q1

23 第3のアナログスイッチ

24 第3のラッチセル

25 インバータ

26 クロックドインバータ

27 インバータ

28 シフト出力Q2

29 第4のアナログスイッチ

30 第4のラッチセル

31 インバータ

32 クロックドインバータ

33 シフト出力Q3

34 入力IN

35 T-FF(トグルフリップフロップ)

36 制御信号CK

37 制御信号CKb

41 アナログスイッチ

42 PMOSFET

43 NMOSFET

44 ゲート入力信号

45 ゲート入力信号

51 インバータ

52 PMOSFET

53 NMOSFET

54 入力IN

55 出力OUT

61 クロックドインバータ

62 PMOSFET

63 PMOSFET

64 NMOSFET

65 NMOSFET

66 ゲート入力信号

67 ゲート入力信号

68 入力IN

69 出力OUT

【技術分野】

【0001】

本発明は、シフトレジスタ動作を小さいチップ面積で実現可能とし且つ入力信号をクロック信号毎にシフトさせることができるシフトレジスタに関する。

【背景技術】

【0002】

図5A及び図5Bは、従来のシフトレジスタの基本構成を示す回路図である。図5A(a)に示すように従来のシフトレジスタは、入力信号D(151)を印加する側から順に第1のアナログスイッチ152、第1のラッチセル153、・・・、第4のアナログスイッチ165、第4のラッチセル166を並べて構成し、2つのアナログスイッチ及び2つのラッチセルの組で1つのフリップフロップ170,171を形成しフリップフロップ170,171の出力端から出力Q0(160),Q1(169)を得るものである。ラッチセル例えば第1のラッチセル153は、インバータ154と、インバータ154の出力にその入力が接続されまたインバータ154の入力にその出力が接続されるクロックドインバータ155とで構成される。図5A(b)は、クロック入力CK_in(172)から制御信号CK及び制御信号CKbを生成する回路を示すもので、インバータ173とインバータ175の直列回路であり、クロック入力CK_in(172)が入力されている。制御信号CK(176)は2つ目のインバータ175の出力から生成され、また制御信号CKb(174)は1つ目のインバータ173の出力から生成され、図5A(a)のアナログスイッチ及びクロックドインバータにそれぞれ印加される。

【0003】

図5Bは、図5Aに示した回路記号の詳細を示す回路図である。図5B(a)に示すアナログスイッチ181は、回路的にはPチャネルMOSFET(182)とNチャネルMOSFET(183)より成り、両方のMOSFETの各ソース同士、各ドレイン同士を接続している。そしてMOSFET(182,183)のゲートに印加される制御信号Gp(184),Gn(185)によってT1(186)及びT2(187)相互間の信号通過をスイッチング制御する。いまGp(184)が「L」(LOW)レベルでGn(185)が「H」(HIGH)レベルのときは、スイッチはオン動作をし、T1(186)及びT2(187)相互間に信号を流すことができる。またGp(184)が「H」レベルでGn(185)が「L」レベルのときは、スイッチはオフ動作をし、T1(186)及びT2(187)相互間の信号通過を遮断する。

【0004】

図5B(b)に示すインバータ191は、反転(NOT)回路であり、回路的にはPチャネルMOSFET(192)とNチャネルMOSFET(193)より成り、2個のMOSFET(192,193)が電源からグランドに直列に結線される。そして入力IN(194)が「L」レベルのときは、出力OUT(195)は「H」レベルとなるよう動作する。また入力IN(194)が「H」レベルのときは、出力OUT(195)は「L」レベルとなるよう動作する。

【0005】

図5B(c)に示すクロックドインバータ201は、回路的には2つのPチャネルMOSFET(202,203)と2つのNチャネルMOSFET(204,205)より成り、4個のMOSFET(202〜205)が電源からグランドにすべて直列に結線される。そしてGp(206)が「L」レベルでGn(207)が「H」レベルのときは、入力IN(208)のレベルを反転した出力を出力OUT(209)から出力して通常のインバータと同じ動作をする。またGp(206)が「H」レベルでGn(207)が「L」レベルのときは、入力IN(208)の状態にかかわらず出力OUT(209)は電源、グランド双方から切り離され、いわゆるオープンの状態となり、ハイインピーダンスを呈する。

【0006】

図6は、図5A及び図5Bに示した従来のシフトレジスタの典型的な動作波形を示すタイミング図である。図6に示すように、制御信号CK(176)が「L」レベルで制御信号CKb(174)が「H」レベルのとき、入力信号D(151)が第1のフリップフロップ170の第1のラッチセル153に取り込まれ、次いで制御信号CK(176)が「H」レベルで制御信号CKb(174)が「L」レベルのとき、第1のフリップフロップ170の第1のラッチセル153に取り込まれた入力信号D(151)が第1のフリップフロップ170の第2のラッチセル157に取り込まれて保持される。第2のフリップフロップ171についても同様な動作をする。このようにして、入力信号D(151)が、クロック入力CK_in(172)の立ち上がり毎にシフトされて、フリップフロップ出力Q0(160),Q1(169),・・・と、順にシフト出力されることが分かる。

【0007】

このように従来のシフトレジスタは、2つのスイッチおよびラッチセルから構成されるフリップフロップを並べて構成され、入力信号D(151)が、クロック入力CK_in(172)の立ち上がり毎にシフトされて、出力Q0(160),Q1(169),・・・として出力を取り出すため、LSIでこのシフトレジスタを実現するとチップ面積が大きくなってしまうという問題があった。

【0008】

この問題を解決するための一方策が特許文献1に提示されている。すなわち特許文献1の図1に開示されたシフトレジスタでは、シフトレジスタを構成するハーフステージ20a,20b,・・・からそれぞれ出力を取り出すことによってシフトレジスタ動作を小さいチップ面積で実現可能としている。

【特許文献1】特開平11-164090号公報(段落0009〜0011、図1)

【発明の開示】

【発明が解決しようとする課題】

【0009】

しかし特許文献1に提示されているシフトレジスタは、シフトレジスタ動作を小さいチップ面積で実現可能としてはいるものの、クロック入力の立ち上がり及び立ち下がりの両側エッジで動作させているため、通常のシフトレジスタと同様に扱うことができず当該シフトレジスタを利用しようとする回路設計者には扱いにくいという課題がある。

【0010】

上記した課題を解決するため本発明は、シフトレジスタ動作を小さいチップ面積で実現可能とし且つクロック入力の立ち上がりもしくは立ち下がりの一方のエッジのみで動作可能とするシフトレジスタを提供することを目的とする。

【課題を解決するための手段】

【0011】

本発明のシフトレジスタは、シフトデータの入力側から出力側に向けてアナログスイッチおよびラッチセルをこの順に複数並べ且つ前段のラッチセルの出力を直接アナログスイッチに入力するようにし、前記ラッチセルのそれぞれの出力端からシフト出力を引き出すシフトレジスタであって、クロック入力の立ち上がりもしくは立ち下がりの一方のエッジのみで動作するトグルフリップフロップの出力から制御信号を生成する制御信号生成回路を備え、前記アナログスイッチおよび前記ラッチセルの動作を制御する制御端子に前記制御信号生成回路が生成した制御信号を入力して前記ラッチセルから前記シフト出力を得ることを特徴とするものである。

【発明の効果】

【0012】

本発明によれば、シフトレジスタ動作を小さいチップ面積で実現可能とし且つクロック入力の立ち上がりもしくは立ち下がりの一方のエッジのみで動作させることができるので、通常のシフトレジスタと同様に一般回路と馴染みがよく、所定部分のみを従来回路と置き換えることも可能で、シフトレジスタを利用しようとする回路設計者にとって扱いやすい。また本発明によれば、出力の正論理/負論理の整合をとるためのインバータの個数を削減することができる。

【図面の簡単な説明】

【0013】

【図1A】本発明の実施形態に係るシフトレジスタの構成を示す図である。

【図1B】図1Aに示した回路記号の詳細を示す回路図である。

【図2】本発明の実施形態に係るシフトレジスタの動作波形を示すタイミング図である。

【図3】本発明を双方向シフトレジスタに適用した場合の参考例を示す図である。

【図4】本発明を双方向シフトレジスタに適用した場合の参考例の動作波形を示すタイミング図である。

【図5A】従来のシフトレジスタの基本構成を示す図である。

【図5B】図5Aに示した回路記号の詳細を示す回路図である。

【図6】従来のシフトレジスタの典型的な動作波形を示すタイミング図である。

【発明を実施するための最良の形態】

【0014】

以下、本発明の実施の形態を、図面を参照しながら説明する。

[実施形態]

図1A及び図1Bは、本発明の実施形態に係るシフトレジスタの構成を示す回路図である。図1A(a)に示すように本発明の実施形態に係るシフトレジスタは、入力信号D(11)を印加する側から順に第1のアナログスイッチ12、第1のラッチセル13、・・・、第4のアナログスイッチ29、第4のラッチセル30を並べて構成し且つ前段のラッチセルの出力を直接アナログスイッチに入力するようにし、各ラッチセルの出力端から出力Q0(17)、Q1(22)、Q2(28)、Q3(33)を得るものである。ラッチセル、例えば第1のラッチセル13は、インバータ14と、インバータ14の出力にその入力が接続されまたインバータ14の入力にその出力が接続されるクロックドインバータ15とにより構成される。ラッチセル出力端から取り出す論理は出力を利用する形態に応じてインバータ(反転回路)16,27を適宜付加する。図1A(b)は、クロック入力CK_in(34)の立ち上がり信号にて動作するT-FF(トグルフリップフロップ)35を有し、T-FF35に対してクロック入力CK_in(34)を入力し、クロックの立ち上がり信号にて動作するT-FF35から制御信号CK(36)及びCKb(37)を得る制御信号生成回路を示す。すなわち、制御信号CK(36)は、T-FF35のQ出力から生成され、また制御信号CKb(37)は、T-FF35のQb出力から生成され、それぞれ図1A(a)のアナログスイッチ及びクロックドインバータに印加される。

【0015】

図1Bは、図1Aに示した回路記号の詳細を示す回路図であり、既述した図5Bの回路図の構成と同じであるが、再度説明すれば、図1B(a)に示すアナログスイッチ41は、回路的にはPチャネルMOSFET(42)とNチャネルMOSFET(43)より成り、両方のMOSFETの各ソース同士、各ドレイン同士を接続している。そしてMOSFET(42,43)のゲートに印加される制御信号Gp(44),Gn(45)によってT1(46)及びT2(47)相互間の信号通過をスイッチング制御する。いまGp(44)が「L」レベルでGn(45)が「H」レベルのときは、スイッチすなわちMOSFET(42,43)はオン動作をし、T1(46)及びT2(47)相互間に信号を流すことができる。またGp(44)が「H」レベルでGn(45)が「L」レベルのときは、スイッチすなわちMOSFET(42,43)はオフ動作をし、T1(46)及びT2(47)相互間の信号通過を遮断する。

【0016】

図1B(b)に示すインバータ51は、反転(NOT)回路であり、回路的にはPチャネルMOSFET(52)とNチャネルMOSFET(53)より成り、2個のMOSFET(52,53)が電源からグランドに直列に結線される。そして入力IN(54)が「L」レベルのときは、PチャネルMOSFET(52)が導通し、PチャネルMOSFET(52)ドレインからの出力により出力OUT(55)は「H」レベルとなるよう動作する。また入力IN(54)が「H」レベルのときは、NチャネルMOSFET(53)が導通し、NチャネルMOSFET(53)ドレインからの出力により出力OUT(55)は「L」レベルとなるよう動作する。

【0017】

図1B(c)に示すクロックドインバータ61は、回路的には2つのPチャネルMOSFET(62,63)と2つのNチャネルMOSFET(64,65)より成り、4個のMOSFET(62〜65)が電源からグランドにすべて直列に結線される。そしてGp(66)が「L」レベルでGn(67)が「H」レベルのときは、入力IN(68)のレベルを反転した出力を出力OUT(69)から出力して通常のインバータと同じ動作をする。またGp(66)が「H」レベルでGn(67)が「L」レベルのときは、入力IN(68)の状態にかかわらず出力OUT(69)は電源、グランド双方から切り離され、いわゆるオープンの状態となり、ハイインピーダンスを呈する。

【0018】

図2は、図1A及び図1Bに示した本発明の実施形態に係るシフトレジスタの動作波形を示すタイミング図である。図2に示すように、制御信号CK(36)が「L」レベルで制御信号CKb(37)が「H」レベルのとき、第1のアナログスイッチ12を経て入力信号D(ここでDは「H」レベルに固定とする)(11)は第1のラッチセル13のインバータ14に加えられ、インバータ14の出力信号が第1のラッチセル13の出力としてインバータ16で反転されて出力信号(1)、すなわちシフト出力Q0(17)となる。図1A(b)に示すT-FF(トグルフリップフロップ)35は、クロック入力CK_in(34)の立ち上がり信号で動作することでクロック入力CK_in(34)は、T-FF35により1/2に分周され、その間に次のステージのアナログスイッチ18とラッチセル19に入力信号D(11)が伝搬される。つまり、第2のアナログスイッチ18は第1のアナログスイッチ12と異なる制御信号により制御されるため制御信号CKb(37)が立ち下がる時点、すなわちクロック入力CK_in(34)の立ち上がり時点で動作して第1のラッチセル13の出力を通過させて第2のラッチセル19のインバータ20に加え、インバータ20の出力信号が第2のラッチセル19の出力として出力信号(2)、すなわちシフト出力Q1(22)となる。

【0019】

以下のステージも同様に、制御信号CK(36)および制御信号CKb(37)によって制御されるアナログスイッチ23,29およびラッチセル24,30により入力信号D(11)が次々と伝搬されることにより、入力CK_in(11)の立ち上がり毎に、ラッチセルの出力Q0(17),Q1(22),Q2(28),Q3(33),・・・(初期状態は、全て「L」レベルとした)は、順に「H」レベルに変化し、すなわち、シフトレジスタとして動作する。

【0020】

このように本発明の実施形態に係るシフトレジスタは、クロック入力CK_in(11)がT-FF35により分周されて制御信号36,37が生成され、この制御信号によってアナログスイッチ12,18,23,29およびラッチセル13,19,24,30 (これらを“コア回路”と称する)が制御されるものである。これにより、シフトレジスタ動作を小さいチップ面積で実現可能とし且つクロックの立ち上がりエッジのみで動作させることができるので、通常のシフトレジスタと同様に一般の回路と馴染みがよく、所定部分のみを従来回路と置き換えることも可能で、回路設計者にとって扱いやすいシフトレジスタを提供することができる。また本発明の実施形態に係るシフトレジスタは、出力の正論理/負論理の整合をとるためのインバータの個数を削減することができる。

【0021】

なお本発明の実施形態に係るシフトレジスタは、1つのラッチセルで、1つのシフト出力を得ることを基本にし、クロック入力がT-FFにより分周されて制御信号が生成され、この制御信号によってコア回路が制御されるものであるが、必要に応じて、クロックと独立に初期値を確定するためのリセット回路等をコア回路に設けてコア回路を条件付けるようにしても良い。

【0022】

図3は、本発明を双方向シフトレジスタに適用した場合の参考例を示す図である。図3(a)では、説明の都合上、双方向のシフトデータをQ0,Q1,Q2の3ビットを出力するもの(アナログスイッチ120と121の間から後述の右シフトの4ビット目を、アナログスイッチ112と113の間から後述の左シフトの4ビット目を、それぞれ出力しうるが、これらは単方向のシフトデータを出力するものである)について説明するが、ビット数を増やして4ビットシフト以上にすることもできる。

【0023】

図3(a)に示す本双方向シフトレジスタは、双方向に入力信号をシフトさせることができるシフトレジスタであって、図の左から右方向へのシフト動作、すなわちQ0→Q2方向シフト(以降、「右シフト」と称する)と、図の右から左方向へのシフト動作、すなわちQ2→Q0方向シフト(以降、「左シフト」と称する)を行えるよう構成している。そして入力信号DL101は、右シフトの際の入力信号(本例では「H」レベル固定)、また入力信号DR131は左シフトの際の入力信号(本例では「L」レベル固定)である。

【0024】

図3(a)において各々のクロックドインバータおよびアナログスイッチ(「スイッチ」と称する)は、X群およびY群にグループ分けされている(図中の各回路素子にXもしくはYの符号が付されていて、どちらの群に属するかを示している)。右シフトの場合には、X群のクロックドインバータおよびスイッチが常に導通で(クロックドインバータが導通とは、クロック信号(CK,CKb)とは無関係に、通常のインバータとして動作することを意味する。また、クロックドインバータが非導通とは、クロック信号(CK,CKb)によりハイインピーダンス出力と通常出力とを切り替える本来のクロックドインバータとして動作することを意味する。)、Y群のクロックドインバータおよびスイッチがシフトレジスタ機能を実現する動作をし、左シフトの場合には、逆に、Y群のクロックドインバータおよびスイッチが常に導通でX群のクロックドインバータおよびスイッチがシフトレジスタ機能を実現する動作をし、左右いずれの向きに入力信号をシフトさせるか(図3(b)に示す方向入力DIR_in(138)によって決定される)に応じてX群およびY群のクロックドインバータおよびスイッチの動作がそれぞれ制御される。

【0025】

図3(b)は、上記本発明の実施形態で説明したように、T-FF135に対してクロック入力CK_in(134)を入力し、クロック入力CK_in(134)の立ち上がり信号にて動作するT-FF135から制御信号CK(136)及び制御信号CKb(137)を得る制御信号生成回路と、D-FF(遅延型フリップフロップ)139に対して方向入力DIR_in(138)を入力し、D-FF139のクロック端子にクロック入力CK_in(134)の立ち上がり信号を受けたときD-FF139に入力された方向入力DIR_in(138)に応じてD-FF139から方向制御信号DIR(140)及び方向制御信号DIRb(141)を得る方向制御信号生成回路を示す。図3(c)は、図示しないスイッチ制御信号生成回路によりスイッチング制御信号を生成するときの論理式を示すテーブル142である。スイッチ制御信号生成回路は、制御信号CK(136),CKb(137)と方向制御信号DIR(140),DIRb(141)との論理的組み合せからスイッチ制御信号D00,D00b,・・・,D11,D11bを生成する。そして図3(a)のコア回路(上記本発明の実施形態で定義したように、各制御信号により制御されるスイッチおよびラッチセルにより構成される)には、方向制御信号DIR(140),DIRb(141)とスイッチ制御信号D00,D00b,・・・,D11,D11bを与えて、X群およびY群のクロックドインバータおよびスイッチの動作を制御する。

【0026】

図4は、本発明を双方向シフトレジスタに適用した場合の参考例の動作波形を示すタイミング図である。図4のタイミング図に基づいて図3に示す本発明を双方向シフトレジスタに適用した場合の参考例の動作を説明する。いま右シフト動作の場合、方向入力DIR_in(138)は「L」レベルに置かれ、方向制御信号DIR(140)も「L」レベルに置かれているので、D00=D10b=CKb,D00b=D10=CK,D01=D11=L,D01b=D11b=Hとなり、右シフトの第1ステージでは、「H」レベル固定された入力信号DL101はX群の第1のスイッチ112を通過し、第2のスイッチ113で留め置かれる。そしてクロック入力CK_in(134)が立ち上がりその立ち上がりエッジでスイッチ制御信号D10(=CK)が「L」レベルとなると第2のスイッチ113が導通して、留め置かれた入力信号DL101を通過させ、第1のラッチセル102のX群クロックドインバータ103に印加する。クロックドインバータ103はX群のため導通し入力信号DL101を反転した第1のラッチセル102の出力を第3のスイッチ114に印加する。第3のスイッチ114はX群のため導通し第1のラッチセル102の出力はインバータ105でさらに反転して出力信号(1)、すなわちシフト出力Q0(106)を出力する。このため出力Q0(106)は入力信号DL101と同じ「H」レベルになる。

【0027】

右シフトの第2のステージでは、第4のスイッチ115はスイッチ制御信号D00(=CKb)が「L」レベルとなるまで第1のラッチセル102の「L」レベルの出力を留め置く。そしてスイッチ制御信号D00が「L」レベルとなると第1のラッチセル102の出力を通過させ、第2のラッチセル107のX群クロックドインバータ108に印加する。クロックドインバータ108はX群のため導通し反転した入力信号DL101を反転した第2のラッチセル107の「H」レベルの出力を第5のスイッチ116に印加する。第5のスイッチ116はX群のため導通し第2のラッチセル107の「H」レベルの出力を出力信号(2)、すなわちシフト出力Q1(110)として出力する。このため出力Q1(110)は入力信号DL101と同じ「H」レベルになる。

【0028】

右シフトの第3のステージでは、第6のスイッチ117はスイッチ制御信号D10(=CK)が「L」レベルとなるまで第2のラッチセル107の「H」レベルの出力を留め置く。そしてスイッチ制御信号D10が「L」レベルとなると第2のラッチセル107の「H」レベルの出力を通過させ、第3のラッチセル122のX群クロックドインバータ123に印加する。クロックドインバータ123はX群のため導通し入力信号DL101を反転した第3のラッチセル122の出力を第7のスイッチ118に印加する。第7のスイッチ118はX群のため導通し第3のラッチセル122の出力をインバータ125でさらに反転して出力信号(3)、すなわちシフト出力Q2(126)を出力する。このため出力Q2(126)は入力信号DL101と同じ「H」レベルになる。

【0029】

このように右シフトの3ステージまで入力信号DL101が次々と伝搬されることにより、入力CK_in(134)の立ち上がり毎に、ラッチセルの出力Q0(106),Q1(110),Q2(126)(初期状態は、全て「L」レベルとした)は、順に「H」レベルに変化し、すなわち、右シフトするシフトレジスタとして動作していることが分かる。

【0030】

図4における双方向シフトレジスタの動作波形を示すタイミング図では、上記第3ステージにおける右シフト出力、すなわち出力Q2(126)を得た後に図3のシフトレジスタを左シフトに切り替えている。左シフト動作させる、すなわちシフト方向を反転させる場合、方向入力DIR_in(138)が「H」レベルに置かれ、クロック入力CK_in(134)の立ち上がりで方向制御信号DIR(140)およびDIRb(141)がそれぞれ「H」レベルおよび「L」レベルに置かれる。

【0031】

図3に示す双方向シフトレジスタにおいて、D-FF139は、方向制御信号DIR(140)を「L」レベル(右シフト)から「H」レベル(左シフト)に切り替えると同時に次のクロック入力CK_in(134)の立ち上がりエッジまで信号のシフトを防止する役目を担っている。すなわち左シフトに切り替えられてもスイッチ121へのスイッチ制御信号DIRb(141)が「L」レベルになるまでスイッチ121で入力信号DR131の通過を留め置き、これにより信号のシフトを防止する。また入力信号DR131のコア回路におけるシフト動作はクロック入力CK_in(134)の立ち上がりエッジでスイッチ制御信号DIRb(141)が「L」レベルになる時点で開始されることから方向反転入力もクロック同期するようにされる。

【0032】

左シフト動作のため方向制御信号DIR(140),DIRb(141)がそれぞれ「H」レベル,「L」レベルに置かれると、図3(c)のテーブル142に示される論理式を実現するスイッチ制御信号生成回路(図示せず)からのスイッチ制御信号D00,D00b,・・・,D11,D11b(D01=D11b=CKb,D01b=D11=CK,D00=D10=L,D00b=D10b=H)により、上述と同様にY群のクロックドインバータおよびスイッチが常に導通でX群のクロックドインバータおよびスイッチがシフトレジスタ機能を実現する動作を行う。左シフトの第1ステージでは、「L」レベル固定された入力信号DR131はY群の第10のスイッチ121を通過し、第9のスイッチ120はスイッチ制御信号D01(=CKb)が「L」レベルとなるまで入力信号DR131の通過を留め置く。そしてクロック入力CK_in(134)が立ち上がり、その立ち上がりエッジでスイッチ制御信号D01が「L」レベルとなったら第9のスイッチ120が導通して、留め置いた入力信号DR131を通過させ、第4のラッチセル127のY群クロックドインバータ129に印加する。クロックドインバータ129はY群のため導通し入力信号DR131を反転した第4のラッチセル127の「H」レベルの出力を第8のスイッチ119に印加する。第8のスイッチ119はY群のため導通し第4のラッチセル127の「H」レベルの出力をインバータ125でさらに反転して出力信号(3)、すなわちシフト出力Q2(126)を出力する。このため出力Q2(126)は入力信号DR131と同じ「L」レベルになる。

【0033】

左シフトの第2のステージでは、第7のスイッチ118はスイッチ制御信号D11(=CK)が「L」レベルとなるまで第4のラッチセル127の「H」レベル出力を留め置く。そしてスイッチ制御信号D11が「L」レベルとなると第4のラッチセル127の出力を通過させ、第3のラッチセル122のY群クロックドインバータ124に印加する。クロックドインバータ124はY群のため導通し入力信号DR131を反転した第4のラッチセル127の「H」レベルの出力を第6のスイッチ117に印加する。第6のスイッチ117はY群のため導通し第4のラッチセル127の「H」レベルの出力を反転した出力信号(2)、すなわちシフト出力Q1(110)を出力する。このため出力Q1(110)は入力信号DR131と同じ「L」レベルになる。

【0034】

左シフトの第3のステージでは、第5のスイッチ116はスイッチ制御信号D01(=CKb)が「L」レベルとなるまで第3のラッチセル122の「L」レベルの出力を留め置く。そして図4には図示されていないがスイッチ制御信号D01が「L」レベルとなると第5のスイッチ116は第3のラッチセル122の「L」レベルの出力を通過させ、第2のラッチセル107のY群クロックドインバータ109に印加する。クロックドインバータ109はY群のため導通し入力信号DR131を反転した「H」レベルの第2のラッチセル107の出力を第4のスイッチ115に印加する。第4のスイッチ115はY群のため導通し第2のラッチセル107の「H」レベルの出力をインバータ105でさらに反転して出力信号(1)、すなわちシフト出力Q0(106)を出力する。このため出力Q0(106)は入力信号DR131と同じ「L」レベル(図示せず)になる。

【0035】

このように左シフトの3ステージまで入力信号DR131が次々と伝搬されることにより、入力CK_in(134)の立ち上がり毎に、ラッチセルの出力Q2(126),Q1(110),Q0(106)(初期状態は、全て「H」レベルとした)は、順に「L」レベルに変化し、すなわち、左シフトするシフトレジスタとして動作していることが分かる。また方向入力DIR_in(138)を任意のタイミングで切り替えても、ラッチセルの出力Q2(126),Q1(110),Q0(106)はクロックCK_in(134)の立ち上がりエッジでのみ変化することが分かる。

【0036】

以上説明したように本発明を双方向シフトレジスタに適用した場合の参考例は、クロック入力CK_in(134)がT-FF135により分周されて制御信号136,137が生成され、さらに方向入力DIR_in(138)がD-FF139に入力され、D-FF139のクロック端子にクロック入力CK_in(134)の立ち上がり信号を受けたときD-FF139に入力された方向入力DIR_in(138)に応じてD-FF139から方向制御信号140,141が生成され、生成された制御信号136,137と方向制御信号140,141との論理的組み合せからスイッチ制御信号を生成し、方向制御信号140,141とスイッチ制御信号(D00,D00b,・・・,D11,D11b)をコア回路に与えて、コア回路のラッチセルおよびアナログスイッチの動作を制御する。これにより、上記本発明の実施形態に係るシフトレジスタと同様にシフトレジスタ動作を小さいチップ面積で実現可能とし且つクロックの立ち上がりエッジのみで動作させることができるので、通常のシフトレジスタと同様に一般の回路と馴染みがよく、所定部分のみを従来回路と置き換えることも可能で、回路設計者にとって扱いやすい双方向シフトレジスタを提供することができる。

【0037】

なお本発明を双方向シフトレジスタに適用した場合の参考例は、1つのラッチセルで、1つのシフト出力を得ることを基本にし、クロック入力がT-FFにより分周されて制御信号が生成され、さらに方向入力がD-FFに入力され、D-FFのクロック端子にクロック入力の立ち上がり信号を受けたときD-FFに入力された方向入力に応じてD-FFから方向制御信号が生成され、生成された制御信号と方向制御信号との論理的組み合せからスイッチ制御信号を生成し、方向制御信号とスイッチ制御信号をコア回路に与えて、コア回路が制御されるものであるが、必要に応じて、クロックと独立に初期値を確定するためのリセット回路等をコア回路に設けてコア回路を条件付けるようにしても良い。

【0038】

また、今までクロックCK_in(134)の立ち上がりエッジに同期して動作する例について説明してきたが、T-FF(トグルフリップフロップ)35,135およびD-FF(遅延型フリップフロップ)139をクロックCK_in(134)の立ち下がりエッジで出力が切り替わるものに置き換えれば、クロックCK_in(134)の立ち下がりエッジに同期して動作するシフトレジスタを得ることができる。

【符号の説明】

【0039】

11 入力信号D

12 第1のアナログスイッチ

13 第1のラッチセル

14 インバータ

15 クロックドインバータ

16 インバータ

17 シフト出力Q0

18 第2のアナログスイッチ

19 第2のラッチセル

20 インバータ

21 クロックドインバータ

22 シフト出力Q1

23 第3のアナログスイッチ

24 第3のラッチセル

25 インバータ

26 クロックドインバータ

27 インバータ

28 シフト出力Q2

29 第4のアナログスイッチ

30 第4のラッチセル

31 インバータ

32 クロックドインバータ

33 シフト出力Q3

34 入力IN

35 T-FF(トグルフリップフロップ)

36 制御信号CK

37 制御信号CKb

41 アナログスイッチ

42 PMOSFET

43 NMOSFET

44 ゲート入力信号

45 ゲート入力信号

51 インバータ

52 PMOSFET

53 NMOSFET

54 入力IN

55 出力OUT

61 クロックドインバータ

62 PMOSFET

63 PMOSFET

64 NMOSFET

65 NMOSFET

66 ゲート入力信号

67 ゲート入力信号

68 入力IN

69 出力OUT

【特許請求の範囲】

【請求項1】

シフトデータの入力側から出力側に向けてアナログスイッチおよびラッチセルをこの順に複数並べ且つ前段のラッチセルの出力を直接アナログスイッチに入力するようにし、前記ラッチセルのそれぞれの出力端からシフト出力を引き出すシフトレジスタであって、クロック入力の立ち上がりもしくは立ち下がりの一方のエッジのみで動作するトグルフリップフロップの出力から制御信号を生成する制御信号生成回路を備え、前記アナログスイッチおよび前記ラッチセルの動作を制御する制御端子に前記制御信号生成回路が生成した制御信号を入力して前記ラッチセルから前記シフト出力を得ることを特徴とするシフトレジスタ。

【請求項2】

前記制御信号生成回路は前記トグルフリップフロップにより前記クロック入力を分周して分周したクロック入力に応じた制御信号を生成することを特徴とする請求項1に記載のシフトレジスタ。

【請求項3】

前記ラッチセル出力端に反転回路を一つおきに備え、前記シフト出力を利用する形態に応じて前記シフト出力の論理を変えることを特徴とする請求項1に記載のシフトレジスタ。

【請求項4】

前記クロック入力と独立に初期値を確定するためのリセット回路を前記ラッチセルに設け、前記ラッチセルの初期値を設定するよう構成したことを特徴とする請求項1に記載のシフトレジスタ。

【請求項1】

シフトデータの入力側から出力側に向けてアナログスイッチおよびラッチセルをこの順に複数並べ且つ前段のラッチセルの出力を直接アナログスイッチに入力するようにし、前記ラッチセルのそれぞれの出力端からシフト出力を引き出すシフトレジスタであって、クロック入力の立ち上がりもしくは立ち下がりの一方のエッジのみで動作するトグルフリップフロップの出力から制御信号を生成する制御信号生成回路を備え、前記アナログスイッチおよび前記ラッチセルの動作を制御する制御端子に前記制御信号生成回路が生成した制御信号を入力して前記ラッチセルから前記シフト出力を得ることを特徴とするシフトレジスタ。

【請求項2】

前記制御信号生成回路は前記トグルフリップフロップにより前記クロック入力を分周して分周したクロック入力に応じた制御信号を生成することを特徴とする請求項1に記載のシフトレジスタ。

【請求項3】

前記ラッチセル出力端に反転回路を一つおきに備え、前記シフト出力を利用する形態に応じて前記シフト出力の論理を変えることを特徴とする請求項1に記載のシフトレジスタ。

【請求項4】

前記クロック入力と独立に初期値を確定するためのリセット回路を前記ラッチセルに設け、前記ラッチセルの初期値を設定するよう構成したことを特徴とする請求項1に記載のシフトレジスタ。

【図1A】

【図1B】

【図2】

【図3】

【図4】

【図5A】

【図5B】

【図6】

【図1B】

【図2】

【図3】

【図4】

【図5A】

【図5B】

【図6】

【公開番号】特開2013−80557(P2013−80557A)

【公開日】平成25年5月2日(2013.5.2)

【国際特許分類】

【出願番号】特願2012−268981(P2012−268981)

【出願日】平成24年12月10日(2012.12.10)

【分割の表示】特願2007−87960(P2007−87960)の分割

【原出願日】平成19年3月29日(2007.3.29)

【出願人】(000005234)富士電機株式会社 (3,146)

【公開日】平成25年5月2日(2013.5.2)

【国際特許分類】

【出願日】平成24年12月10日(2012.12.10)

【分割の表示】特願2007−87960(P2007−87960)の分割

【原出願日】平成19年3月29日(2007.3.29)

【出願人】(000005234)富士電機株式会社 (3,146)

[ Back to top ]