シミュレーション装置、プログラム、記憶媒体、及び方法

【課題】 本発明の課題は、ソフトウェアとハードウェアの協調シミュレーションにおいて、ソフトウェアとハードウェア間の同期回数を削減することを目的とする。

【解決手段】 上記課題は、組込みソフトウェアを検証するための論理的な単体又は複数のハードウェアモデルを駆動するハードウェアシミュレータと、前記組込みソフトウェアを実行するCPUの動作を模した前記単体又は複数のハードウェアモデルの一つであり、前記ハードウェアシミュレータとの命令毎の同期を省略して該組込みソフトウェアを動作させるCPUモデルとを有することを特徴とするシミュレーション装置により達成される。

【解決手段】 上記課題は、組込みソフトウェアを検証するための論理的な単体又は複数のハードウェアモデルを駆動するハードウェアシミュレータと、前記組込みソフトウェアを実行するCPUの動作を模した前記単体又は複数のハードウェアモデルの一つであり、前記ハードウェアシミュレータとの命令毎の同期を省略して該組込みソフトウェアを動作させるCPUモデルとを有することを特徴とするシミュレーション装置により達成される。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、ハードウェアシミュレーションを用いて組込みソフトウェアを動作させ検証するシミュレーション装置、プログラム、記憶媒体、及び方法に関する。

【背景技術】

【0002】

近年、ソフトウェアを組み込んだ種々の電化製品、精密機器などの製品が普及するようになった。このような組込みソフトウェアの開発では、ソフトウェアを組み込むハードウェアの動作を模した論理的なハードウェアモデルによってシミュレーションするハードウェアシミュレータを用いて、ソフトウェアの動作を検証することが行なわれている。

【0003】

ソフトウェアとハードウェアとの協調シミュレーションに関して、ソフトウェアを実機で動作させた場合と同様に動作する模擬的なハードウェアシミュレーションで動作させた場合とで実行タイミングが不一致とならないようにソフトウェアとハードウェアのシミュレーション間で適切に同期させて検証することが重要である。その一方で、ソフトウェアの検証を高速に行なうために、ソフトウェアの動作に影響を与えないハードウェアモデルによるシミュレーションを抑制する等が提案されている。

【先行技術文献】

【特許文献】

【0004】

【特許文献1】特開平10−312315号公報

【特許文献2】特開2005−321848号公報

【特許文献3】特開2009−3683号公報

【発明の概要】

【発明が解決しようとする課題】

【0005】

しかしながら、組込みソフトウェアには無限ループが存在し、その無限ループが実行される際にもソフトウェアとハードウェアのシミュレーション間で同期させるため、シミュレーション時間が消費されると言った問題があった。上述した従来技術では、このようなソフトウェアの検証に影響を与えない動作についてもシミュレーションが行われてしまい、シミュレーションを効率的に行うことができなかった。

【課題を解決するための手段】

【0006】

開示の技術は、組込みソフトウェアを検証するための論理的な単体又は複数のハードウェアモデルを駆動するハードウェアシミュレータと、前記組込みソフトウェアを実行するCPUの動作を模した前記単体又は複数のハードウェアモデルの一つであり、前記ハードウェアシミュレータとの命令毎の同期を省略して該組込みソフトウェアを動作させるCPUモデルとを有するシミュレーション装置のように構成される。

【0007】

また、上記課題を解決するための手段として、コンピュータに上記シミュレーション装置として機能させるためのプログラム、そのプログラムを記録した記録媒体、及びシミュレーション方法とすることもできる。

【発明の効果】

【0008】

開示の技術では、ソフトウェアとハードウェアの協調シミュレーションにおいて、ソフトウェアとハードウェア間の同期回数を削減することができ、高速にシミュレーションを行うことができる。

【図面の簡単な説明】

【0009】

【図1】シミュレーション対象の例を説明するための図である。

【図2】シミュレーション対象のソフトウェアの構成例を示す図である。

【図3】ソフトウェアの処理フローを説明するための図である。

【図4】本実施の形態に係るシミュレーション装置のハードウェア構成を示す図である。

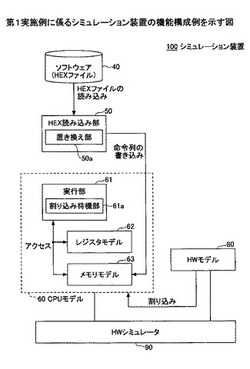

【図5】第1実施例に係るシミュレーション装置の機能構成例を示す図である。

【図6】実機とシミュレーション装置との対応を説明するための図である。

【図7】第1実施例に係るHEX読み込み部による処理概要を説明するための図である。

【図8】HEXファイル読み込み処理を説明するためのフローチャート図である。

【図9】置き換え部による処理を説明するための図である。

【図10】置き換え例を説明するための図である。

【図11】実行部による処理の概要を説明するための図である。

【図12】実行部による処理を説明するためのフローチャート図である。

【図13】割り込み処理を考慮した命令列の実行処理を説明するためのフローチャート図である。

【図14】シミュレーションの実行時間の比較例を示す図である。

【図15】第2実施例に係るシミュレーション装置の機能構成例を示す図である。

【図16】第2実施例に係るソフトウェアの例を示す図である。

【図17】第2実施例に係るレジスタモデルの例を示す図である。

【図18】第2実施例に係るメモリモデルの例を示す図である。

【図19】メモリモデルの初期化処理を説明するためのフローチャート図である。

【図20】メモリモデルのデータ読出処理を説明するためのフローチャート図である。

【図21】メモリモデルのデータ書込処理を説明するためのフローチャート図である。

【図22】タイマーモデルの構成例を示す図である。

【図23】タイマーモデルのプログラム例である。

【図24】第2実施例に係るシミュレーション装置の動作シーケンスを示す図である。

【発明を実施するための形態】

【0010】

以下、本発明の実施の形態を図面に基づいて説明する。本実施の形態に係るシミュレーション装置は、組み込みソフトウェア(以下、単に「SW」と示す場合がある)と、そのソフトウェアを動作させるハードウェア(以下、単に「HW」と示す場合がある)とを協調させてシミュレーションを行う装置であり、SWとHWとの協調シミュレーション時において、SW−HW間のオーバーヘッドとなるSW−HW間同期回数を削減することによって、高速シミュレーションを実現するものである。

【0011】

先ず、シミュレーション装置で検証されるシミュレーション対象について説明する。図1は、シミュレーション対象の例を説明するための図である。図1において、シミュレーション対象となるソフトウェアは、CPU31に組み込まれ、バス33によってCPU31と接続される周期タイマー32の割り込み要求に応じて所定動作を行う。周期タイマー32は、5μs周期で割り込み要求を行うタイマーである。

【0012】

シミュレーション対象のソフトウェアは、周期タイマー32からの割り込み要求に応じて、レジスタ0(単に、「r0」とする)に1を加算するアプリケーションとする。

【0013】

CPU31は、少なくとも、

・1命令の命令長は1バイト

・1命令の実行は1サイクル

・動作は1MHz

の構成を有する。

【0014】

周期タイマー32は、所定間隔(5μs周期)でCPU31に割り込み要求を行う。

【0015】

図2は、シミュレーション対象のソフトウェアの構成例を示す図である。シミュレーション対象のソフトウェアは、図2に示すリストL1及びL2を表現するメモリに書き込まれるデータ形式のHEXファイルであるとする。HEXファイルには、命令語とその配置アドレスを対応させたリストが記述されている。

【0016】

リストL1は、スタートアップルーチンであり、アイドルループのみで構成される。また、リストL2は、タイマー割り込みルーチンであり、レジスタ0(r0)に1を加算する処理を行う。

【0017】

ソフトウェアは、CPU31がリストL1及びL2を実行することにより、図3に示すように動作する。図3は、ソフトウェアの処理フローを説明するための図である。図3中、リストL1の範囲4aがステップS1に相当し、リストL2の範囲4bがステップS3及びS4に相当する。

【0018】

CPU31によりシミュレーション対象のソフトウェアが実行開始されると、CPU31によりリストL1の"jump end"命令が実行される(ステップS1)。この"jump end"命令は自分自身を次に実行する命令(リストL1の"end"ラベルの次の命令)に指定し、アイドルループを形成する。

【0019】

そして、CPU31によりタイマー割り込みが発生したか否かが判断される(ステップS2)。発生していない場合、CPU31は、通常処理のステップS1を繰り返すアイドルループを続行する。一方、発生していた場合、CPU31は、通常処理(ステップS1の繰り返し)の代わりにリストL2に記述されるタイマー割り込みルーチンを実行するため、ステップS3へと進む。

【0020】

タイマー割り込みルーチンが実行されると、CPU31により"inc r0"命令が実行される(ステップS3)。この"inc r0"命令により、レジスタ0(r0)に1が加算される。

【0021】

続けて、CPU31により"reti"(return from interrupt)命令が実行される(ステップS4)。この"reti"命令により、CPU31は、ステップS1へ戻り通常処理を繰り返す。

【0022】

上述したようなシミュレーション対象のソフトウェアに対して、SW−HW間のオーバーヘッドとなるSW−HW間同期回数を削減する仕組みについて、以下に説明する。

【0023】

図4は、本実施の形態に係るシミュレーション装置のハードウェア構成を示す図である。図4に示すシミュレーション装置100は、コンピュータによって制御される装置であって、CPU(Central Processing Unit)11と、メモリユニット12と、表示ユニット13と、出力ユニット14と、入力ユニット15と、記憶装置17と、ドライバ18とを有し、システムバスBに接続される。

【0024】

CPU11は、メモリユニット12に格納されたプログラムに従ってシミュレーション装置100を制御する。メモリユニット12には、RAM(Random Access Memory)及びROM(Read-Only Memory)等が用いられ、CPU11にて実行されるプログラム、CPU11での処理に必要なデータ、CPU11での処理にて得られたデータ等を格納する。また、メモリユニット12の一部の領域が、CPU11での処理に利用されるワークエリアとして割り付けられている。

【0025】

表示ユニット13は、CPU11の制御のもとに必要な各種情報を表示する。出力ユニット14は、プリンタ等を有し、利用者からの指示に応じて各種情報を出力するために用いられる。入力ユニット15は、マウス、キーボード等を有し、ユーザが、シミュレーション装置100が処理を行なうための必要な各種情報を入力するために用いられる。記憶装置17には、例えば、ハードディスクユニットが用いられ、各種処理を実行するプログラム等のデータを格納する。

【0026】

シミュレーション装置100によって行われる処理を実現するプログラムは、例えば、CD−ROM(Compact Disc Read-Only Memory)等の記憶媒体19によってシミュレーション装置100に提供される。即ち、プログラムが保存された記憶媒体19がドライバ18にセットされると、ドライバ18が記憶媒体19からプログラムを読み出し、その読み出されたプログラムがシステムバスBを介して記憶装置17にインストールされる。そして、プログラムが起動されると、記憶装置17にインストールされたプログラムに従ってCPU11がその処理を開始する。尚、プログラムを格納する媒体としてCD−ROMに限定するものではなく、コンピュータが読み取り可能な媒体であればよい。コンピュータ読取可能な記憶媒体として、CD−ROMの他に、DVDディスク、USBメモリ等の可搬型記録媒体、フラッシュメモリ等の半導体メモリであっても良い。

【0027】

[第1実施例]

図5は、第1実施例に係るシミュレーション装置の機能構成例を示す図である。図5において、シミュレーション装置100は、図4のCPU11がプログラムを実行することによって実現される、HEX読み込み部50と、CPUモデル60と、HW(ハードウェア)モデル80と、HWシミュレータ90とを有する。

【0028】

ソフトウェア40は、HEXファイルであり、図4の記憶装置17に格納される。

【0029】

HEX読み込み部50は、記憶装置17に格納されるソフトウェア40を読み込んで、CPUモデル60のメモリモデル63に命令列を書き込む。また、HEX読み込み部50は、置き換え部50aを有し、置き換え部50aによって、メモリモデル63に書き込んだ命令列のうち、アイドルループを構成する命令列を全て割り込み待機命令に置き換える。

【0030】

CPUモデル60は、ソフトウェア40を組み込むCPU31(図1)の動作を模した論理的なハードウェアモデルであり、実行部61と、レジスタモデル62と、メモリモデル63とを有し、ソフトウェア40を実行することによって、HWモデル80からの割り込みに応じた処理を行う。

【0031】

実行部61は、レジスタモデル62と、メモリモデル63とにアクセスすることによって、メモリモデル63に格納された命令列を逐次的に解釈して実行する命令実行部のモデルである。また、実行部61は、割り込み待機部61aを有し、割り込み待機部61aによって、置き換え部50aによって置き換えられた割り込み待機命令を実行する。

【0032】

レジスタモデル62は、シミュレーション対象のCPUのレジスタファイルを表現するモデルであり、各レジスタはシミュレーション装置100上の変数として確保される。

【0033】

メモリモデル63は、シミュレーション対象の主記憶を表現するモデルである。

【0034】

HWモデル80は、例えば、5μsの所定間隔で割り込みを要求するタイマーモデルである。

【0035】

HWシミュレータ90は、CPUモデル60とHWモデル80とを駆動可能なシミュレータである。

【0036】

図6は、実機とシミュレーション装置との対応を説明するための図である。図6において、実機の場合において、ソフトウェア40は、デバイスプログラマ41によって実機CPU42内の記憶領域に書き込まれ組み込まれる。その同一のソフトウェア40が、シミュレーション装置100の場合、HEX読み込み部50によって、実機CPU42相当の動作をするCPUモデル60のメモリモデル63に書き込まれる。

【0037】

ソフトウェア40は、命令語と配置アドレスの対のリストか、これに変換可能な形式で記述されたHEXファイルである。命令語と配置アドレスの対のリストに変換可能な形式として、Intel HEX形式や、Motorola S19形式などが適用される。

【0038】

図7は、第1実施例に係るHEX読み込み部による処理概要を説明するための図である。図7において、HEXファイル7bは、フォーマット7aで示すように配置アドレスに対応させて命令語が記述される形式で、ソフトウェア40の処理が記述されている。例えば、HEXファイル7bでは、配置アドレス「23」と命令「C0」とが対で記述され、配置アドレス「42」と命令「FF」とが対で記述され、配置アドレス「43」と命令「EE」とが対で記述されている。ここで、命令「C0」は1命令でアイドルループを構成する命令とする。

【0039】

HEX読み込み部50によってHEXファイル7bが読み込まれると、記述に従ってメモリモデル63に命令列の書き込みが行われる。従って、メモリモデル63では、0x23番地に0xC0が書き込まれ、0x42番地に0xFFが書き込まれ、0x43番地に0xEEが書き込まれる。

【0040】

命令列がメモリモデル63に書き込まれると、HEX読み込み部50の置き換え部50aが、アイドルループを示す0xC0を割り込み待機命令を示す0xBBで置き換える。

【0041】

HEXファイル7bを読み込むHEXファイル読み込み処理について、置き換え部50aを備えないため置き換え処理が行われない場合の処理を対比させて、第1実施例に係る置き換え部50aを有するHEX読み込み部50による処理について説明する。

【0042】

図8は、HEXファイル読み込み処理を説明するためのフローチャート図である。図8(A)は置き換え処理が行われない場合のフローチャートを示し、図8(B)は置き換え処理が行われる場合のフローチャートを示しており、同一処理には同一ステップ番号を付してある。

【0043】

図8(B)を参照して、HEX読み込み部50による処理を説明する。図8(B)において、HEX読み込み部50は、HEXファイルの先頭から順に、配置アドレスを取得し、変数Aに設定し(ステップS11)、取得した配置アドレスに対応させたデータ列から1バイトのOP(命令語)を読み込み、OPをメモリモデル63のアドレスAに格納する(ステップS12)。

【0044】

HEX読み込み部50は、置き換え部50aによってアイドルループの割り込み待機命令への置き換え処理P20を実行する。置き換え処理P20は図9で説明される。

【0045】

置き換え処理P20の終了後、HEX読み込み部50は、HEXファイルの末尾まで読み込んだか否かを判断する(ステップS13)。HEXファイルの末尾まで読み込んでいない場合、HEX読み込み部50は、ステップS11へ戻り上述同様の処理を繰り返し、HEXファイルの末尾まで読み込んだ場合、この処理を終了する。

【0046】

図8(A)に示す置き換え処理が行われない場合のフローチャートでは、図8(B)と同様のステップS11及びS12を行った後、HEXファイルの末尾まで読み込んだか否かを判断するステップS13を行う処理となる。

【0047】

一方、図8(B)の置き換え処理が行われる場合では、図9に示すような置き換え処理P20が実行される。図9は、置き換え部による処理を説明するための図である。図9において、置き換え部50aは、OP(命令語)が変数Aの値以下のアドレスへの無条件ジャンプか否かを判断する(ステップS21)。無条件ジャンプでない場合、置き換え部50aは、この処理を終了する。

【0048】

一方、無条件ジャンプである場合、置き換え部50aは、ジャンプ先のアドレスを変数A'とする(ステップS22)。

【0049】

そして、置き換え部50aは、変数A'(アドレスA')から変数A(アドレスA)までの命令が全てnop又はwaitか否かを判断する(ステップS23)。ここで、waitはCPU固有の待機命令とする。全てnop又はwaitでない場合、置き換え部50aは、この処理を終了する。

【0050】

一方、全てnop又はwaitである場合、置き換え部50aは、変数A'(アドレスA')から変数A(アドレスA)の命令を全て割り込み待機命令に置き換える(ステップS24)。そして、置き換え部50aは、この処理を終了する。

【0051】

このような置き換え処理P20を実行することによって、置き換えられるアイドルループの例と、置き換えられた割り込み待機命令の例について説明する。図10は、置き換え例を説明するための図である。図10において、リストL3では、置き換えられるアイドルループ例(1)、(2)、(3)が示され、リストL4では、リストL3のアイドルループ例(1)、(2)、(3)を割り込み待機命令で置き換えた結果を示している。

【0052】

アイドルループ例(1)では、"end1"命令の直後に"jump end1"命令となるため、"jump end1"命令のみが割り込み待機命令である"wait-for-interrupt"命令に置き換わる。

【0053】

アイドルループ例(2)では、"end2"命令後に"nop"命令が2回続き"jump end2"命令となるため、2回の"nop"命令と"jump end2"とが"wait-for-interrupt"命令に置き換わる。

【0054】

アイドルループ例(3)では、"end3"命令後に"wait"命令そして"jump end3"命令となるため、その"wait"命令と"jump end3"命令とが"wait-for-interrupt"命令に置き換わる。

【0055】

図10では、置き換え前のリストL3と置き換え後のリストL4で、置き換え部50aによる置き換え処理P20の例を説明したが、置き換え処理P20は、図7で説明したように、メモリモデル63内のHEXコードが置き換わる処理である。

【0056】

次に、実行部61での処理について説明する。図11は、実行部による処理の概要を説明するための図である。図11において、レジスタモデル62は、PC(プログラムカウンタ)62aと、その他のレジスタ62bとを有する。

【0057】

先ず、実行部61は、PC62aから値を取得して(ステップS31)、取得した値をアドレスとしてメモリモデル63から命令を読み出す(ステップS32)。そして、実行部61は、ステップS32で読み出した命令の長さ分のバイト数をPC62aの値に加算する(ステップS33)。

【0058】

次に、実行部61は、読み出した命令が割り込み待機命令であるか否かを判断する(ステップS34)。

【0059】

割り込み待機命令である場合、実行部61は、ステップS33で加算したPC62aを加算前の状態に戻し、HWシミュレータ90から割り込みイベントが通知されるまで待機する。割り込みイベントが通知されると、実行部61は、ステップS31へ戻り、上述同様の処理を繰り返す。

【0060】

一方、割り込み待機命令でない場合、実行部61は、ステップS32で読み出した命令に相当するホストCPUの命令列を実行し、必要ならレジスタモデル62の値や、メモリモデル63の値を変更する。

【0061】

ステップS32の命令がメモリモデル63などを通してハードウェアにアクセスし、HWモデル80内で時間が経過し、その間に割り込みが発生した場合、実行部61は、ステップS32で読み出した命令が不可分であるか否かを判断する(ステップS35)。

【0062】

読み出した命令が不可分である場合、実行部61は、割り込み待機部61aによって、割り込みの発生を保存し、ステップS32の命令が完了するまで待機する。ステップS32の命令の処理完了後、割り込みを実行する。

【0063】

読み出した命令が不可分でない場合、実行部61は、ソフトウェア40が組み込まれるCPU31の仕様に従ってPC62aの値などを保存し、割り込みを実行する。CPU31がIntel社が開発したx86系のCPUであれば、x86系の仕様に従ってPC62aの値などを保存する。以下同様である。

【0064】

置き換え処理の有無の違いによる実行部の処理を対比させて、第1実施例に係る実行部61による処理について説明する。

【0065】

図12は、実行部による処理を説明するためのフローチャート図である。図12(A)は置き換え処理が行われない場合の実行部による処理のフローチャートを示し、図12(B)は置き換え処理が行われる場合の実行部61による処理のフローチャートを示しており、同一処理には同一ステップ番号を付してある。

【0066】

図12(B)を参照して、実行部61による処理を説明する。図12(B)において、実行部61は、メモリモデル63内のPC62aが示すアドレスから1バイトを読み込み、OP(命令語)を取得して(ステップS41)、PC62aの値に1を加算する(ステップS42)。

【0067】

実行部61は、ステップS41で取得したOPが割り込み待機命令か否かを判断する(ステップS42−5)。

【0068】

割り込み待機命令の場合、実行部61は、割り込み待機部61aによって割り込み待機処理P45を行う。割り込み待機処理P45は、以下のステップS45−1からS45−4を含む。

【0069】

割り込み待機部61aは、PC62aの値からステップS42で加算した値「1」を減算し(ステップS45−1)、割り込み発生まで待機する(ステップS45−2)。割り込み待機部61aは、PC62aの値を退避した後(ステップS45−3)、割り込み処理のアドレスをPC62aにセットする(ステップS45−4)。割り込み待機処理P45の終了後、実行部61は、ステップS41へと戻り、上述同様の処理を繰り返す。

【0070】

一方、ステップS42−5にて、割り込み待機命令ではないと判断した場合、実行部61は、割り込み処理を考慮しつつ、ソフトウェア40が組み込まれるCPU31の仕様に従って、OPに相当する命令列を実行し(ステップS46)、ステップS41へと戻る。ステップS46における命令列の実行中の割り込み処理については、図13で詳述される。

【0071】

図12(A)に示す置き換え処理が行われない場合のフローチャートでは、図12(B)と同様のステップS41及びS42を実行した後、単に、ソフトウェア40が組み込まれるCPU31の仕様に従って、OPに相当する命令列を実行し(ステップS43)、1μsの所定時間待機する(ステップS44)。

【0072】

図12(B)に戻り、第1実施例に係る実行部61の処理では、符号D44で示されるように、図12(A)に示す所定時間待機するステップS44の処理が省略可能となる。従って、1命令を実行する毎に発生する待機時間を省略することができる。

【0073】

図13は、割り込み処理を考慮した命令列の実行処理を説明するためのフローチャート図である。図13において、実行部61は、OP(命令語)の実行中に時間が経過したか否かを判断する(ステップS46−1)。経過していない場合、実行部61は、この処理を終了する。

【0074】

時間が経過した場合、実行部61は、OPの実行中に割り込みが発生したか否かを判断する(ステップS46−2)。発生していない場合、実行部61は、この処理を終了する。

【0075】

割り込みが発生した場合、実行部61は、更に、命令は不可分か否かを判断する(ステップS46−3)。不可分である場合、実行部61は、OP完了を待機し(ステップS46−4)、PC62aの値などを退避する(ステップS46−5)。そして、実行部61は、割り込み処理のアドレスをPC62aにセットして(ステップS46−6)、この処理を終了する。

【0076】

不可分でない場合、実行部61は、PC62aの値などを退避する(ステップS46−7)。そして、実行部61は、割り込み処理のアドレスをPC62aにセットして(ステップS46−8)、この処理を終了する。

【0077】

上述した、第1実施例に係るHEX読み込み部50及び実行部61によって、1命令毎の待機を省略し、割り込み毎の待機とすることで、シミュレーションの実行時間を短縮することができる。第1実施例を適用しないために1命令毎に待機処理が発生する場合と、第1実施例を適用することにより割り込み毎の待機処理とした場合の比較を図14に示す。

【0078】

図14は、シミュレーションの実行時間の比較例を示す図である。図14中、シミュレーション時間を横軸に示している。また、図2に示すリストL1及びL2に従って、図3に示すように動作するソフトウェアの処理フローをシミュレーションした場合の比較例を示す。図3に示すステップに相当する箇所を同一符号で示している。

【0079】

図14(A)では、第1実施例を適用しない場合を、HWシミュレータ14a、HWモデル14b、CPUモデル14cとして示す。ステップS2の割り込み発生によって、ステップS3の"inc"命令、ステップS4の"reti"命令、次の割り込みが発生するまでの間繰り返されるステップS1の"jump"命令の実行毎に、図12(A)のステップS44の実行により、1μsの待機処理14pがHWシミュレータ14aに発生する。

【0080】

そのため、1μsの待機処理14pにかかる300nsがシミュレーション時間に累積されることにより、次の割り込みまでの実時間の合計が2170nsとなる。

【0081】

一方、第1実施例を適用した図14(B)に示すシミュレーションでは、1命令毎の1μsの待機処理14p(図12(A)のステップS44)を省略可能とし(図12(B)の符号D44)、更に、"jump"命令が割り込み待機命令に置き換わることにより(図8及び図9の置き換え処理P20)、CPUモデル60による"jump"命令の実行が省略される。よって、1命令毎の1μsの待機処理14pにかかる300nsと、"jump"命令の実行に必要な10nsとが省略される。

【0082】

CPUモデル60は、1命令毎に待機することなく、1処理ルーチン内のアイドルループ以外の命令列を連続してソフトウェア40を動作させることができる。

【0083】

また、アイドルループが割り込み待機命令に置き換わることにより、HWシミュレータ90は、所定の5μs時間待機することなく、次の割り込み要求をHWモデル80からCPUモデル60に行わせることができる。

【0084】

このように、ソフトウェア40をシミュレーションする際のHWシミュレータ90との同期回数を削減することによって、シミュレーション全体における次の割り込みまでのシミュレーションの実時間の合計は950nsとなる。従って、第1実施例を適用しない図14(A)に示すシミュレーション例と比べると、よりシミュレーション時間を短縮することが可能となる。

【0085】

第1実施例では、レジスタモデル62は既存のレジスタモデルを適用可能である。また、メモリモデル63についても、時間精度が時間を評価するタイムドか時間を評価しないアンタイムドかを問わず既存のメモリモデルを適用可能である。同様に、HWモデル80についても、タイムドかアンタイムドかを問わず既存のHWモデルを適用可能である。HWシミュレータ90は、HWモデル80を駆動できるシミュレータであればよい。

【0086】

[第2実施例]

第2実施例では、オブジェクト指向言語C++を利用して電子回路設計を可能とするSystemCによるHWシミュレータにおいて、第1実施例で説明したHEX読み込み部50と実行部61とを適用した場合の各モデルの構成例について説明する。

【0087】

図15は、第2実施例に係るシミュレーション装置の機能構成例を示す図である。図15において、シミュレーション装置100−2は、図4のCPU11がプログラムを実行することによって実現される、HEX読み込み部50と、CPUモデル60−2と、HWモデルであるタイマーモデル80−2と、HWシミュレータ90−2とを有する。

【0088】

ソフトウェア40−2は、後述される図16に示すリストL5及びL6のHEXファイルであり、図4の記憶装置17に格納される。

【0089】

置き換え部50aを有するHEX読み込み部50は、第1実施例と同様である。

【0090】

CPUモデル60−2は、実行部61と、レジスタモデル62−2と、メモリモデル63−2とを有し、ソフトウェア40−2を実行することによって、タイマーモデル80−2からの割り込みに応じた処理を行う。

【0091】

実行部61は、第1実施例と同様である。

【0092】

レジスタモデル62−2は、シミュレーション対象のCPUのレジスタファイルを表現するモデルであり、各レジスタはシミュレーション装置100上の変数として確保される。レジスタモデル62−2は、後述される図17に示す5つのレジスタを有する。

【0093】

メモリモデル63は、シミュレーション対象の主記憶を表現するモデルであり、後述される図18に示す構造を有する。

【0094】

タイマーモデル80−2は、5μsの所定間隔で割り込みを要求するタイマーモデルであり、後述される図22の構成を有する。

【0095】

HWシミュレータ90は、タイマーモデル80−2を駆動可能なSystemCによるシミュレータである。

【0096】

図16は、第2実施例に係るソフトウェアの例を示す図である。図16に示すように、ソフトウェア40−2は、リストL5とリストL6を表現するHEXファイルである。HEXファイルには、命令語とその配置アドレスの対のリストが記述され、命令語長は4バイト、データ幅も4バイトである。

【0097】

リストL5は、スタートアップルーチンであり、アイドルループのみで構成される。リストL5の"jump end"命令は、第1実施例に従って割り込み待機命令である"wait-for-interrupt"命令に置き換わる。

【0098】

また、リストL6は、タイマー割り込み処理ルーチンであり、主記憶(mem0)にタイマーモデル80−2の値をコピーする"load"命令と、主記憶(後述されるメモリ領域63b)にレジスタ0をコピーする"store"命令と、割り込み処理ルーチンを完了する"reti"命令とを有する。第1実施例が適用されるため、ソフトウェア40−2を動作させた際には、1命令毎の待機は省略される。

【0099】

図17は、第2実施例に係るレジスタモデルの例を示す図である。図17に示すように、レジスタモデル62−2は、以下の5種類の32ビットレジスタを有する。

・R0レジスタ6aは、汎用レジスタである。

・PCレジスタ6bは、プログラムカウンタ用のレジスタである。

・STATUSレジスタ6cは、ステータス/フラグレジスタである。

・EIPCレジスタ6dは、割り込み発生時のPCレジスタ6bの値を退避するための退避レジスタである。

・EISTATISレジスタ6eは、割り込み発生時のSTATUSレジスタ6cの値を退避するための退避レジスタである。

【0100】

図18は、第2実施例に係るメモリモデルの例を示す図である。図18に示すメモリモデル63−2は、アンタイムドのメモリモデルとして、アドレスをキーとする連想配列63aの構造と、Init関数I/F(インタフェース)63iと、Read関数I/F63rと、Write関数I/F63wとを有する。

【0101】

連想配列63aは、アドレス値が32ビットの場合、上位8ビットをキー63a−2とし、メモリ領域63bへのポインタと連想配列63cへのポインタとの対を示す値63a−4によって構成される。

【0102】

連想配列63aにおいて、キー63a−2が「00」の場合、連想配列63aの値63a−4によって、メモリ領域63bへのポインタと、連想配列63cへのポインタとの対が与えられる。キー63a−2が「01」の場合、メモリ領域63bへのポインタと、連想配列63cは存在せず空ポインタとの対が与えられる。キー63a−2が「02」の場合、メモリ領域63b及び連想配列63cとも存在せず空ポインタの対が与えられる。

【0103】

メモリ領域63bは、16MBの連続した領域を持ち、シミュレーション装置100−2における主記憶を表現する。

【0104】

連想配列63cは、IO関数のアドレスをキー63c−2として、呼び出すIO関数が値63c−4で与えられる。IO関数の一例は、図22及び図23で後述される。

【0105】

Init関数I/F63iは、連想配列63aと連想配列63cとを初期化してIO関数を設定するためのInit(初期化)関数用のインタフェースである。

【0106】

Read関数I/F63rは、READモードでIO関数を呼び出してデータを読み出すRead関数用のインタフェースである。

【0107】

Write関数I/F63wは、WRITEモードでIO関数を呼び出してデータを書き込むWrite関数用のインタフェースである。

【0108】

メモリモデル63−2へのアクセスは、初期化時は、HWシミュレータ90−2によりInit関数を通してIO関数の設定が行われる。命令列の設定は、HWシミュレータ90−2により、Write関数を通して行われる。また、シミュレーション実行時は、実行部61からRead関数とWrite関数を通して行われる。

【0109】

図19は、メモリモデルの初期化処理を説明するためのフローチャート図である。図19に示すメモリモデル63−2の初期化関数は、Init関数I/F63iを介して、HWシミュレータ90−2のメイン処理部から呼び出され、IO関数のアドレスと、IO関数へのポインタと、アクセスワードサイズの組のリストを受け取り(ステップS101)、初期化処理が行われる。

【0110】

リストが空リストか否かが判断される(ステップS102)。リストが空リストでない場合、リストの先頭から順に組を取得して変数Hに設定し、リストの先頭が次の組を指定するようにして残りの組をリストとする(ステップS103)。そして、変数Hをメモリモデル63−2内に格納する処理を行い(リスト格納処理P120)、ステップS102へ戻る。

【0111】

一方、ステップS102において、リストが空リストである場合、つまり、メモリモデル63−2に格納する組が存在しない場合、この初期化処理が終了する。

【0112】

リスト格納処理P120について説明する。リスト格納処理P120では、IO関数のアドレスを変数Aに設定し、IO関数のポインタ値を変数Pに設定し、ワードサイズを変数Lに設定する(ステップS121)。そして、変数Aの上位8ビットを変数AHに設定し、下位24ビットを変数ALに設定する(ステップS122)。

【0113】

変数AHは連想配列63aのキー63a−2を示し、変数ALは連想配列63cのキー63c−2を示す。

【0114】

変数AHの値をキー63a−2とするメモリ領域63bへのポインタが空ポインタか否かを判断する(ステップS123)。空ポインタの場合、16MBのメモリ領域63bを確保し、その先頭アドレスを連想配列63aの値63a−4のメモリ領域へのポインタに格納する(ステップS124)。また、空の連想配列63cを作成し、その先頭アドレスを連想配列63aの値63a−4の連想配列へのポインタに格納して(ステップS125)、ステップS126へと進む。

【0115】

ステップS123にて、変数AHの値をキー63a−2とするメモリ領域63bへのポインタが空ポインタでない場合、更に、変数AHの値をキー63a−2とする連想配列63cへのポインタが空ポインタか否かを判断する(ステップS123−2)。空ポインタの場合、ステップS125での処理を行うことによって、空の連想配列63cを作成し、その先頭アドレスを連想配列63aの値63a−4の連想配列へのポインタに格納して、ステップS126へと進む。ステップS123−2にて、変数AHの値をキー63a―2とする連想配列63cへのポインタが空ポインタでない場合、ステップS126へ進む。

【0116】

[AL .. AL+L−1]の夫々をキー63c−2とする値63c−4に、空ポインタを格納し(ステップS126)、ALをキー63c−2とする値63c−4にステップS121で設定した変数Pの値を格納する(ステップS127)。そして、このリスト格納処理が終了する。

【0117】

図20は、メモリモデルのデータ読出処理を説明するためのフローチャート図である。ここでは、アライメントデータアクセスの場合で説明する。図20に示すメモリモデル63−2からデータを読み出すためのRead関数が、Read関数I/F63rを介して呼び出されると、データ読出処理を開始する。

【0118】

読み出すデータのアドレスを変数Aに設定し、読み出したデータの格納先へのポインタを変数Pに設定し、読み出しバイト数を変数Lに設定する(ステップS131)。また、変数Aの上位8ビットを変数AHに設定し、下位24ビットを変数ALに設定する(ステップS132)。

【0119】

そして、変数AHの値をキー63a−2とするメモリ領域63bへのポインタが空ポインタか否かを判断する(ステップS133)。空ポインタの場合、変数Pの指す格納先に0を格納して(ステップS134)、このデータ読出処理を終了する。これは、連想配列63aのキー63a−2が「02」を示す場合の処理である。

【0120】

一方、メモリ領域63bへのポインタが空ポインタでない場合、更に、変数AHの値をキー63a−2とする連想配列63cへのポインタが空ポインタか否かを判断する(ステップS135)。空ポインタの場合、メモリ領域63bのALバイト目からLバイトのデータを読み出して変数Pの指す格納先に格納し(ステップS136)、このデータ読出処理を終了する。メモリ領域63bの先頭に変数ALで示されるバイト数を加算した読み出し開始位置から変数Lで示される読み出しバイト数分のデータが読み出され、変数Pの指す格納先に格納される。これは、連想配列63aのキー63a−2が「01」を示す場合の処理である。

【0121】

以下のステップS137からS139での処理が連想配列63aのキー63a−2が「00」を示す場合の処理に相当する。

【0122】

ステップS135にて、連想配列63cへのポインタが空ポインタでない場合、連想配列63cに変数ALの値をキー63c−2とするエントリーが存在するか否かを判断する(ステップS137)。エントリーが存在しない場合、メモリ領域63bのALバイト目からLバイトのデータを読み出して変数Pの指す格納先に格納し(ステップS138)、このデータ読出処理を終了する。メモリ領域63bの先頭に変数ALで示されるバイト数を加算した読み出し開始位置から変数Lで示される読み出しバイト数分のデータが読み出され、変数Pの示す値に格納される。

【0123】

一方、エントリーが存在する場合、変数ALの値をキー63c−2とする連想配列63cの値63c−4のIO関数をREADモードで呼び出し、結果を変数Pの指す格納先に格納する(ステップS139)。そして、このデータ読出処理を終了する。

【0124】

図21は、メモリモデルのデータ書込処理を説明するためのフローチャート図である。ここでは、アライメントデータアクセスの場合で説明する。図21に示すメモリモデル63−2へデータを書き込むためのWrite関数が、Write関数I/F63wを介して、HWシミュレータ90−2のメイン処理部から呼び出されると、データ書込処理を開始する。

【0125】

書き込むアドレスを変数Aに設定し、書き込むデータが格納された左辺値へのポインタを変数Pに設定し、書き込むバイト数を変数Lに設定する(ステップS141)。また、変数Aの上位8ビットを変数AHに設定し、下位24ビットを変数ALに設定する(ステップS142)。

【0126】

そして、変数AHの値をキー63a−2とするメモリ領域63bへのポインタが空ポインタか否かを判断する(ステップS143)。空ポインタの場合、16MBのメモリ領域63bを確保し、先頭アドレスを連想配列63aのメモリ領域63bへのポインタに格納する(ステップS144)。続けて、メモリ領域63bのALバイト目からLバイトに変数Pの指す格納先のデータを書き込み(ステップS146)、このデータ書込処理を終了する。メモリ領域63bの先頭に変数ALで示されるバイト数を加算した書き込み開始位置から変数Lで示される書き込みバイト数分の領域に、変数Pの指す格納先のデータを書き込む。これは、連想配列63aのキー63a−2が「02」を示す場合の処理である。

【0127】

一方、メモリ領域63bへのポインタが空ポインタでない場合、更に、変数AHの値をキー63a−2とする連想配列63cへのポインタが空ポインタか否かを判断する(ステップS143−5)。空ポインタの場合、メモリ領域63bのALバイト目からLバイトに変数Pの指す格納先のデータを書き込み(ステップS146)、このデータ書込処理を終了する。これは、連想配列63aのキー63a−2が「01」を示す場合の処理である。

【0128】

以下のステップS147からS149での処理が連想配列63aのキー63a−2が「00」を示す場合の処理に相当する。

【0129】

ステップS145にて、連想配列63cへのポインタが空ポインタでない場合、連想配列63cに変数ALの値をキー63c−2とするエントリーが存在するか否かを判断する(ステップS147)。エントリーが存在しない場合、メモリ領域63bのALバイト目からLバイト分の領域に変数Pの指す格納先のデータを書き込み(ステップS148)、このデータ書込処理を終了する。メモリ領域63bの先頭に変数ALで示されるバイト数を加算した書き込む開始位置から変数Lで示される書き込みバイト数分の領域に、変数Pの指す格納先のデータが書き込まれる。

【0130】

一方、エントリーが存在する場合、変数ALの値をキー63c−2とする連想配列63cの値63c−4のIO関数をWRITEモードで呼び出す(ステップS139)。そして、このデータ書込処理を終了する。

【0131】

次に、タイマーモデル80−2について図22及び図23で説明する。図22は、タイマーモデルの構成例を示す図である。図23は、タイマーモデルのプログラム例である。図22において、タイマーモデル80−2は、SystemCを使用したHWシミュレータ上で動作するHWモデルであり、時刻データ(Tick)83と、図23に示すようなbehavior関数84a及びaccess関数84bと、behavior関数84a用のbehavior関数I/F82aと、access関数84b用のaccess関数I/F82bと、CPUモデル60−2に割り込み要求を行うためのIRQ(Interrupt ReQuest) I/F82cとを有する。

【0132】

behavior関数84aは、SystemCのSC_METHOD又はSC_THREADとして表現され、図23に示すように、時刻データ83に1加算して、CPUモデル60−2に割り込みを通知した後、所定間隔の5μs待機する処理を行う。

【0133】

access関数84bは、メモリモデル63−2にIO関数としてマッピングされる、制御の遷移の伴わない関数であり、図23に示すように、指定されたアドレスに時刻データ(Tick)83を書き込む処理を行う。時刻などの待機は行わない。

【0134】

図24は、第2実施例に係るシミュレーション装置の動作シーケンスを示す図である。図24中、横軸にシミュレーション時間を示す。図24において、割り込みが発生するたびに、LOAD命令、STORE命令、RETI命令、及び割り込み待機命令が行われることを示している。割り込み待機命後の動作は、図14(B)で説明した通りである。

【0135】

LOAD命令によって、CPUモデル60−2は、メモリモデル63−2を通して、タイマーモデル63−2から時刻データ83を取得する。タイマーモデル63−2の制御の遷移の伴わないaccess関数84bを通して時刻データ83を取得する。

【0136】

STORE命令によって、CPUモデル60−2は、メモリモデル63−2を通して、主記憶を表現するメモリ領域63bに時刻データ83を書き込む。

【0137】

RETI命令によって、CPUモデル60−2は、割り込み処理ルーチンを完了する。

【0138】

割り込み待機命令によって、CPUモデル60−2は、次の割り込み発生まで待機する。

【0139】

図24に示すシミュレーション装置100−2の動作シーケンスは、ソフトウェア40−2(図16に示すリストL5及びL6のHEXファイル)を実機で実行した場合と同じ動作であり、第2実施例に係るシミュレーション装置100−2でソフトウェア40−2の検証が可能であることを示している。

【0140】

上述したように、第1実施例では、HEX読み込み部50が、シミュレーション対象のCPU31が解釈可能な命令列から無限ループ部分を検出し、これをシミュレーション内でのみ有効な割り込み待機命令に置き換える置き換え部50aを有し、実行部61が、シミュレーション実行時に割り込み待機命令を解釈し、その命令によって周辺ハードウェアモデルからの割り込みが発生するまで待機する割り込み待機部61aを有することによって、HWシミュレータ90の処理における待機回数を削減できる。

【0141】

このように、協調シミュレーションにおいて、割り込みまでの無限ループ部分を割り込み待機命令に置き換えてソフトウェアとハードウェア間の命令毎の同期を省略し割り込み毎の同期とすることによりシミュレーションを高速に行うことができる。従って、クロック同期によるISS(命令セットシミュレータ)よりも高速にシミュレーションすることが可能となる。

【0142】

また、第1実施例の機能構成に加えて、第2実施例に示すようなアンタイムドのメモリモデル63−2をCPUモデル60−2に組み込むことによって、メモリ領域63b(主記憶)へのIOアクセスを、ソフトウェア40−2を実機で実行した場合と同じ動作で実現できる。

【0143】

本発明は、具体的に開示された実施例に限定されるものではなく、特許請求の範囲から逸脱することなく、種々の変形や変更が可能である。

【0144】

以上の第1から第2実施例を含む実施形態に関し、更に以下の付記を開示する。

(付記1)

組込みソフトウェアを検証するための論理的な単体又は複数のハードウェアモデルを駆動するハードウェアシミュレータと、

前記組込みソフトウェアを実行するCPUの動作を模した前記単体又は複数のハードウェアモデルの一つであり、前記ハードウェアシミュレータとの命令毎の同期を省略して該組込みソフトウェアを動作させるCPUモデルと

を有することを特徴とするシミュレーション装置。

(付記2)

前記単体又は複数のハードウェアモデルの一つであり、割り込みを発生させる割り込みモデル

を有することを特徴とする付記1記載のシミュレーション装置。

(付記3)

前記CPUモデルは、メモリモデルを有し、

前記シミュレーション装置は、更に、組込みソフトウェアを表現する命令列を読み込んで前記メモリモデルに書き込む際に、無限ループ部分となる命令を割り込み待機命令に置き換えて該メモリモデルに書き込む置換手段を有し、

前記CPUモデルは、前記割り込み待機命令により次の割り込みまで待機することを特徴とする付記1又は2記載のシミュレーション装置。

(付記4)

前記メモリモデルは、アドレスの所定ビットをキーとするIO関数呼び出しのための関数用連想配列を有し、

前記アドレスに従って対応する前記IO関数を呼び出してデータアクセスを行うことを特徴とする付記1乃至3のいずれか一項記載のシミュレーション装置。

(付記5)

前記メモリモデルは、前記アドレスの前記所定ビット以外をキーとして、メモリ領域の領域ポインタと前記関数用連想配列の配列ポインタの対を値とするポインタ用連想配列を有し、

前記アドレスに従って前記ポインタ用連想配列により与えられた前記対の値に、前記領域ポインタ及び前記配列ポインタが与えられると共に前記関数用連想配列のキーが存在し、前記関数用連想配列の値が空ポインタでない場合、前記アドレスに従って前記IO関数を呼び出してデータアクセスを行うことを特徴とする付記4記載のシミュレーション装置。

(付記6)

前記アドレスに従って前記ポインタ用連想配列により与えられた前記対の値に、前記領域ポインタ及び前記配列ポインタが与えられると共に前記関数用連想配列のキーが存在し、前記関数用連想配列の値が空ポインタの場合、前記関数用連想配列の値が空ポインタでない前記アドレスより小さい前記アドレスのうち、最も大きな前記アドレスに従って前記IO関数を呼び出してデータアクセスを行うことを特徴とする付記5記載のシミュレーション装置。

(付記7)

前記アドレスに従って前記ポインタ用連想配列により、空ポインタが前記配列ポインタに与えられる場合、前記メモリ領域のへのデータアクセスを行うことを特徴とする付記5又は6記載のシミュレーション装置。

(付記8)

前記IO関数は前記単体又は複数のハードウェアモデルが有するアクセス関数であることを特徴とする付記4乃至7のいずれか一項記載のシミュレーション装置。

(付記9)

コンピュータを組込みソフトウェアを検証するシミュレーション装置として機能させるコンピュータ実行可能なプログラムであって、該コンピュータを、

論理的な単体又は複数のハードウェアモデルを駆動するハードウェアシミュレータと、

前記組込みソフトウェアを実行するCPUの動作を模した前記単体又は複数のハードウェアモデルの一つであり、前記ハードウェアシミュレータとの命令毎の同期を省略して該組込みソフトウェアを動作させるCPUモデルとして機能させることを特徴とするコンピュータ実行可能なプログラム。

(付記10)

前記コンピュータを、前記単体又は複数のハードウェアモデルの一つであり、割り込みを発生させる割り込みモデルとして機能させることを特徴とする付記9記載のコンピュータ実行可能なプログラム。

(付記11)

前記CPUモデルは、メモリモデルを有し、

前記シミュレーション装置は、更に、組込みソフトウェアを表現する命令列を読み込んで前記メモリモデルに書き込む際に、無限ループ部分となる命令を割り込み待機命令に置き換えて該メモリモデルに書き込む置換手段を有し、

前記CPUモデルは、前記割り込みモデルからの割り込みに応じた前記組込みソフトウェアの動作後、前記割り込み待機命令により次の割り込みまで待機することを特徴とする付記10記載のコンピュータ実行可能なプログラム。

(付記12)

コンピュータを組込みソフトウェアを検証するシミュレーション装置として機能させるプログラムを格納したコンピュータ読取可能な記憶媒体であって、該コンピュータを、

論理的な単体又は複数のハードウェアモデルを駆動するハードウェアシミュレータと、

前記組込みソフトウェアを実行するCPUの動作を模した前記単体又は複数のハードウェアモデルの一つであり、前記ハードウェアシミュレータとの命令毎の同期を省略して該組込みソフトウェアを動作させるCPUモデルとして機能させることを特徴とするコンピュータ読取可能な記憶媒体。

(付記13)

前記コンピュータを、前記単体又は複数のハードウェアモデルの一つであり、割り込みを発生させる割り込みモデルとして機能させることを特徴とする請求項12記載のコンピュータ読み取り可能な記憶媒体。

(付記14)

前記CPUモデルは、メモリモデルを有し、

前記シミュレーション装置は、更に、組込みソフトウェアを表現する命令列を読み込んで前記メモリモデルに書き込む際に、無限ループ部分となる命令を割り込み待機命令に置き換えて該メモリモデルに書き込む置換手段を有し、

前記CPUモデルは、前記割り込みモデルからの割り込みに応じた前記組込みソフトウェアの動作後、前記割り込み待機命令により次の割り込みまで待機することを特徴とする付記13記載のコンピュータ読取可能な記憶媒体。

(付記15)

前記メモリモデルは、アドレスの所定ビットをキーとするIO関数呼び出しのための関数用連想配列を有し、

前記コンピュータに、前記アドレスに従って対応する前記IO関数を呼び出してデータアクセスを行わせることを特徴とする付記14記載のコンピュータ読取可能な記憶媒体。

(付記16)

組込みソフトウェアを検証するシミュレーション装置で実行されるシミュレーション方法であって、

ハードウェアシミュレータ上で駆動し、前記組込みソフトウェアを実行するCPUの動作を模したCPUモデルが、該ハードウェアシミュレータとの命令毎の同期を省略して該組込みソフトウェアを動作させることを特徴とするシミュレーション方法。

(付記17)

前記CPUモデルは、メモリモデルを有し、

前記シミュレーション装置は、更に、組込みソフトウェアを表現する命令列を読み込んで前記メモリモデルに書き込む際に、無限ループ部分となる命令を割り込み待機命令に置き換えて該メモリモデルに書き込む置換手段を有し、

前記CPUモデルは、所定間隔で割り込みを発生させる割り込みモデルからの割り込み要求に応じた前記組込みソフトウェアの動作後、前記割り込み待機命令により次の割り込みまで待機することを特徴とする

付記16記載のシミュレーション方法。

【符号の説明】

【0145】

6a R0レジスタ

6b PCレジスタ

6c STATUSレジスタ

6d EIPCレジスタ

6e EISTATISレジスタ

11 CPU

12 メモリユニット

13 表示ユニット

14 出力ユニット

15 入力ユニット

16 通信ユニット

17 記憶装置

18 ドライバ

19 記憶媒体

40、40−2 ソフトウェア

50 HEX読み込み部

50a 置き換え部

60、60−2 CPUモデル

61 実行部

61a 割り込み待機部

62、62−2 レジスタモデル

62a PC

62b その他のレジスタ

63、63−2 メモリモデル

63a 連想配列

63a−2 キー

63a−4 値

63b メモリ領域

63c 連想配列

63c−2 キー

63c−4 値

63i Init関数I/F

63r Read関数I/F

63w Write関数I/F

80 HWモデル

80−2 タイマーモデル

82a behavior関数I/F

82b access関数I/F

82c IRQ I/F

83 時刻データ

84a behavior関数

84b access関数

90 HWシミュレータ

L1、L2、L3、L4、L5、L6 リスト

【技術分野】

【0001】

本発明は、ハードウェアシミュレーションを用いて組込みソフトウェアを動作させ検証するシミュレーション装置、プログラム、記憶媒体、及び方法に関する。

【背景技術】

【0002】

近年、ソフトウェアを組み込んだ種々の電化製品、精密機器などの製品が普及するようになった。このような組込みソフトウェアの開発では、ソフトウェアを組み込むハードウェアの動作を模した論理的なハードウェアモデルによってシミュレーションするハードウェアシミュレータを用いて、ソフトウェアの動作を検証することが行なわれている。

【0003】

ソフトウェアとハードウェアとの協調シミュレーションに関して、ソフトウェアを実機で動作させた場合と同様に動作する模擬的なハードウェアシミュレーションで動作させた場合とで実行タイミングが不一致とならないようにソフトウェアとハードウェアのシミュレーション間で適切に同期させて検証することが重要である。その一方で、ソフトウェアの検証を高速に行なうために、ソフトウェアの動作に影響を与えないハードウェアモデルによるシミュレーションを抑制する等が提案されている。

【先行技術文献】

【特許文献】

【0004】

【特許文献1】特開平10−312315号公報

【特許文献2】特開2005−321848号公報

【特許文献3】特開2009−3683号公報

【発明の概要】

【発明が解決しようとする課題】

【0005】

しかしながら、組込みソフトウェアには無限ループが存在し、その無限ループが実行される際にもソフトウェアとハードウェアのシミュレーション間で同期させるため、シミュレーション時間が消費されると言った問題があった。上述した従来技術では、このようなソフトウェアの検証に影響を与えない動作についてもシミュレーションが行われてしまい、シミュレーションを効率的に行うことができなかった。

【課題を解決するための手段】

【0006】

開示の技術は、組込みソフトウェアを検証するための論理的な単体又は複数のハードウェアモデルを駆動するハードウェアシミュレータと、前記組込みソフトウェアを実行するCPUの動作を模した前記単体又は複数のハードウェアモデルの一つであり、前記ハードウェアシミュレータとの命令毎の同期を省略して該組込みソフトウェアを動作させるCPUモデルとを有するシミュレーション装置のように構成される。

【0007】

また、上記課題を解決するための手段として、コンピュータに上記シミュレーション装置として機能させるためのプログラム、そのプログラムを記録した記録媒体、及びシミュレーション方法とすることもできる。

【発明の効果】

【0008】

開示の技術では、ソフトウェアとハードウェアの協調シミュレーションにおいて、ソフトウェアとハードウェア間の同期回数を削減することができ、高速にシミュレーションを行うことができる。

【図面の簡単な説明】

【0009】

【図1】シミュレーション対象の例を説明するための図である。

【図2】シミュレーション対象のソフトウェアの構成例を示す図である。

【図3】ソフトウェアの処理フローを説明するための図である。

【図4】本実施の形態に係るシミュレーション装置のハードウェア構成を示す図である。

【図5】第1実施例に係るシミュレーション装置の機能構成例を示す図である。

【図6】実機とシミュレーション装置との対応を説明するための図である。

【図7】第1実施例に係るHEX読み込み部による処理概要を説明するための図である。

【図8】HEXファイル読み込み処理を説明するためのフローチャート図である。

【図9】置き換え部による処理を説明するための図である。

【図10】置き換え例を説明するための図である。

【図11】実行部による処理の概要を説明するための図である。

【図12】実行部による処理を説明するためのフローチャート図である。

【図13】割り込み処理を考慮した命令列の実行処理を説明するためのフローチャート図である。

【図14】シミュレーションの実行時間の比較例を示す図である。

【図15】第2実施例に係るシミュレーション装置の機能構成例を示す図である。

【図16】第2実施例に係るソフトウェアの例を示す図である。

【図17】第2実施例に係るレジスタモデルの例を示す図である。

【図18】第2実施例に係るメモリモデルの例を示す図である。

【図19】メモリモデルの初期化処理を説明するためのフローチャート図である。

【図20】メモリモデルのデータ読出処理を説明するためのフローチャート図である。

【図21】メモリモデルのデータ書込処理を説明するためのフローチャート図である。

【図22】タイマーモデルの構成例を示す図である。

【図23】タイマーモデルのプログラム例である。

【図24】第2実施例に係るシミュレーション装置の動作シーケンスを示す図である。

【発明を実施するための形態】

【0010】

以下、本発明の実施の形態を図面に基づいて説明する。本実施の形態に係るシミュレーション装置は、組み込みソフトウェア(以下、単に「SW」と示す場合がある)と、そのソフトウェアを動作させるハードウェア(以下、単に「HW」と示す場合がある)とを協調させてシミュレーションを行う装置であり、SWとHWとの協調シミュレーション時において、SW−HW間のオーバーヘッドとなるSW−HW間同期回数を削減することによって、高速シミュレーションを実現するものである。

【0011】

先ず、シミュレーション装置で検証されるシミュレーション対象について説明する。図1は、シミュレーション対象の例を説明するための図である。図1において、シミュレーション対象となるソフトウェアは、CPU31に組み込まれ、バス33によってCPU31と接続される周期タイマー32の割り込み要求に応じて所定動作を行う。周期タイマー32は、5μs周期で割り込み要求を行うタイマーである。

【0012】

シミュレーション対象のソフトウェアは、周期タイマー32からの割り込み要求に応じて、レジスタ0(単に、「r0」とする)に1を加算するアプリケーションとする。

【0013】

CPU31は、少なくとも、

・1命令の命令長は1バイト

・1命令の実行は1サイクル

・動作は1MHz

の構成を有する。

【0014】

周期タイマー32は、所定間隔(5μs周期)でCPU31に割り込み要求を行う。

【0015】

図2は、シミュレーション対象のソフトウェアの構成例を示す図である。シミュレーション対象のソフトウェアは、図2に示すリストL1及びL2を表現するメモリに書き込まれるデータ形式のHEXファイルであるとする。HEXファイルには、命令語とその配置アドレスを対応させたリストが記述されている。

【0016】

リストL1は、スタートアップルーチンであり、アイドルループのみで構成される。また、リストL2は、タイマー割り込みルーチンであり、レジスタ0(r0)に1を加算する処理を行う。

【0017】

ソフトウェアは、CPU31がリストL1及びL2を実行することにより、図3に示すように動作する。図3は、ソフトウェアの処理フローを説明するための図である。図3中、リストL1の範囲4aがステップS1に相当し、リストL2の範囲4bがステップS3及びS4に相当する。

【0018】

CPU31によりシミュレーション対象のソフトウェアが実行開始されると、CPU31によりリストL1の"jump end"命令が実行される(ステップS1)。この"jump end"命令は自分自身を次に実行する命令(リストL1の"end"ラベルの次の命令)に指定し、アイドルループを形成する。

【0019】

そして、CPU31によりタイマー割り込みが発生したか否かが判断される(ステップS2)。発生していない場合、CPU31は、通常処理のステップS1を繰り返すアイドルループを続行する。一方、発生していた場合、CPU31は、通常処理(ステップS1の繰り返し)の代わりにリストL2に記述されるタイマー割り込みルーチンを実行するため、ステップS3へと進む。

【0020】

タイマー割り込みルーチンが実行されると、CPU31により"inc r0"命令が実行される(ステップS3)。この"inc r0"命令により、レジスタ0(r0)に1が加算される。

【0021】

続けて、CPU31により"reti"(return from interrupt)命令が実行される(ステップS4)。この"reti"命令により、CPU31は、ステップS1へ戻り通常処理を繰り返す。

【0022】

上述したようなシミュレーション対象のソフトウェアに対して、SW−HW間のオーバーヘッドとなるSW−HW間同期回数を削減する仕組みについて、以下に説明する。

【0023】

図4は、本実施の形態に係るシミュレーション装置のハードウェア構成を示す図である。図4に示すシミュレーション装置100は、コンピュータによって制御される装置であって、CPU(Central Processing Unit)11と、メモリユニット12と、表示ユニット13と、出力ユニット14と、入力ユニット15と、記憶装置17と、ドライバ18とを有し、システムバスBに接続される。

【0024】

CPU11は、メモリユニット12に格納されたプログラムに従ってシミュレーション装置100を制御する。メモリユニット12には、RAM(Random Access Memory)及びROM(Read-Only Memory)等が用いられ、CPU11にて実行されるプログラム、CPU11での処理に必要なデータ、CPU11での処理にて得られたデータ等を格納する。また、メモリユニット12の一部の領域が、CPU11での処理に利用されるワークエリアとして割り付けられている。

【0025】

表示ユニット13は、CPU11の制御のもとに必要な各種情報を表示する。出力ユニット14は、プリンタ等を有し、利用者からの指示に応じて各種情報を出力するために用いられる。入力ユニット15は、マウス、キーボード等を有し、ユーザが、シミュレーション装置100が処理を行なうための必要な各種情報を入力するために用いられる。記憶装置17には、例えば、ハードディスクユニットが用いられ、各種処理を実行するプログラム等のデータを格納する。

【0026】

シミュレーション装置100によって行われる処理を実現するプログラムは、例えば、CD−ROM(Compact Disc Read-Only Memory)等の記憶媒体19によってシミュレーション装置100に提供される。即ち、プログラムが保存された記憶媒体19がドライバ18にセットされると、ドライバ18が記憶媒体19からプログラムを読み出し、その読み出されたプログラムがシステムバスBを介して記憶装置17にインストールされる。そして、プログラムが起動されると、記憶装置17にインストールされたプログラムに従ってCPU11がその処理を開始する。尚、プログラムを格納する媒体としてCD−ROMに限定するものではなく、コンピュータが読み取り可能な媒体であればよい。コンピュータ読取可能な記憶媒体として、CD−ROMの他に、DVDディスク、USBメモリ等の可搬型記録媒体、フラッシュメモリ等の半導体メモリであっても良い。

【0027】

[第1実施例]

図5は、第1実施例に係るシミュレーション装置の機能構成例を示す図である。図5において、シミュレーション装置100は、図4のCPU11がプログラムを実行することによって実現される、HEX読み込み部50と、CPUモデル60と、HW(ハードウェア)モデル80と、HWシミュレータ90とを有する。

【0028】

ソフトウェア40は、HEXファイルであり、図4の記憶装置17に格納される。

【0029】

HEX読み込み部50は、記憶装置17に格納されるソフトウェア40を読み込んで、CPUモデル60のメモリモデル63に命令列を書き込む。また、HEX読み込み部50は、置き換え部50aを有し、置き換え部50aによって、メモリモデル63に書き込んだ命令列のうち、アイドルループを構成する命令列を全て割り込み待機命令に置き換える。

【0030】

CPUモデル60は、ソフトウェア40を組み込むCPU31(図1)の動作を模した論理的なハードウェアモデルであり、実行部61と、レジスタモデル62と、メモリモデル63とを有し、ソフトウェア40を実行することによって、HWモデル80からの割り込みに応じた処理を行う。

【0031】

実行部61は、レジスタモデル62と、メモリモデル63とにアクセスすることによって、メモリモデル63に格納された命令列を逐次的に解釈して実行する命令実行部のモデルである。また、実行部61は、割り込み待機部61aを有し、割り込み待機部61aによって、置き換え部50aによって置き換えられた割り込み待機命令を実行する。

【0032】

レジスタモデル62は、シミュレーション対象のCPUのレジスタファイルを表現するモデルであり、各レジスタはシミュレーション装置100上の変数として確保される。

【0033】

メモリモデル63は、シミュレーション対象の主記憶を表現するモデルである。

【0034】

HWモデル80は、例えば、5μsの所定間隔で割り込みを要求するタイマーモデルである。

【0035】

HWシミュレータ90は、CPUモデル60とHWモデル80とを駆動可能なシミュレータである。

【0036】

図6は、実機とシミュレーション装置との対応を説明するための図である。図6において、実機の場合において、ソフトウェア40は、デバイスプログラマ41によって実機CPU42内の記憶領域に書き込まれ組み込まれる。その同一のソフトウェア40が、シミュレーション装置100の場合、HEX読み込み部50によって、実機CPU42相当の動作をするCPUモデル60のメモリモデル63に書き込まれる。

【0037】

ソフトウェア40は、命令語と配置アドレスの対のリストか、これに変換可能な形式で記述されたHEXファイルである。命令語と配置アドレスの対のリストに変換可能な形式として、Intel HEX形式や、Motorola S19形式などが適用される。

【0038】

図7は、第1実施例に係るHEX読み込み部による処理概要を説明するための図である。図7において、HEXファイル7bは、フォーマット7aで示すように配置アドレスに対応させて命令語が記述される形式で、ソフトウェア40の処理が記述されている。例えば、HEXファイル7bでは、配置アドレス「23」と命令「C0」とが対で記述され、配置アドレス「42」と命令「FF」とが対で記述され、配置アドレス「43」と命令「EE」とが対で記述されている。ここで、命令「C0」は1命令でアイドルループを構成する命令とする。

【0039】

HEX読み込み部50によってHEXファイル7bが読み込まれると、記述に従ってメモリモデル63に命令列の書き込みが行われる。従って、メモリモデル63では、0x23番地に0xC0が書き込まれ、0x42番地に0xFFが書き込まれ、0x43番地に0xEEが書き込まれる。

【0040】

命令列がメモリモデル63に書き込まれると、HEX読み込み部50の置き換え部50aが、アイドルループを示す0xC0を割り込み待機命令を示す0xBBで置き換える。

【0041】

HEXファイル7bを読み込むHEXファイル読み込み処理について、置き換え部50aを備えないため置き換え処理が行われない場合の処理を対比させて、第1実施例に係る置き換え部50aを有するHEX読み込み部50による処理について説明する。

【0042】

図8は、HEXファイル読み込み処理を説明するためのフローチャート図である。図8(A)は置き換え処理が行われない場合のフローチャートを示し、図8(B)は置き換え処理が行われる場合のフローチャートを示しており、同一処理には同一ステップ番号を付してある。

【0043】

図8(B)を参照して、HEX読み込み部50による処理を説明する。図8(B)において、HEX読み込み部50は、HEXファイルの先頭から順に、配置アドレスを取得し、変数Aに設定し(ステップS11)、取得した配置アドレスに対応させたデータ列から1バイトのOP(命令語)を読み込み、OPをメモリモデル63のアドレスAに格納する(ステップS12)。

【0044】

HEX読み込み部50は、置き換え部50aによってアイドルループの割り込み待機命令への置き換え処理P20を実行する。置き換え処理P20は図9で説明される。

【0045】

置き換え処理P20の終了後、HEX読み込み部50は、HEXファイルの末尾まで読み込んだか否かを判断する(ステップS13)。HEXファイルの末尾まで読み込んでいない場合、HEX読み込み部50は、ステップS11へ戻り上述同様の処理を繰り返し、HEXファイルの末尾まで読み込んだ場合、この処理を終了する。

【0046】

図8(A)に示す置き換え処理が行われない場合のフローチャートでは、図8(B)と同様のステップS11及びS12を行った後、HEXファイルの末尾まで読み込んだか否かを判断するステップS13を行う処理となる。

【0047】

一方、図8(B)の置き換え処理が行われる場合では、図9に示すような置き換え処理P20が実行される。図9は、置き換え部による処理を説明するための図である。図9において、置き換え部50aは、OP(命令語)が変数Aの値以下のアドレスへの無条件ジャンプか否かを判断する(ステップS21)。無条件ジャンプでない場合、置き換え部50aは、この処理を終了する。

【0048】

一方、無条件ジャンプである場合、置き換え部50aは、ジャンプ先のアドレスを変数A'とする(ステップS22)。

【0049】

そして、置き換え部50aは、変数A'(アドレスA')から変数A(アドレスA)までの命令が全てnop又はwaitか否かを判断する(ステップS23)。ここで、waitはCPU固有の待機命令とする。全てnop又はwaitでない場合、置き換え部50aは、この処理を終了する。

【0050】

一方、全てnop又はwaitである場合、置き換え部50aは、変数A'(アドレスA')から変数A(アドレスA)の命令を全て割り込み待機命令に置き換える(ステップS24)。そして、置き換え部50aは、この処理を終了する。

【0051】

このような置き換え処理P20を実行することによって、置き換えられるアイドルループの例と、置き換えられた割り込み待機命令の例について説明する。図10は、置き換え例を説明するための図である。図10において、リストL3では、置き換えられるアイドルループ例(1)、(2)、(3)が示され、リストL4では、リストL3のアイドルループ例(1)、(2)、(3)を割り込み待機命令で置き換えた結果を示している。

【0052】

アイドルループ例(1)では、"end1"命令の直後に"jump end1"命令となるため、"jump end1"命令のみが割り込み待機命令である"wait-for-interrupt"命令に置き換わる。

【0053】

アイドルループ例(2)では、"end2"命令後に"nop"命令が2回続き"jump end2"命令となるため、2回の"nop"命令と"jump end2"とが"wait-for-interrupt"命令に置き換わる。

【0054】

アイドルループ例(3)では、"end3"命令後に"wait"命令そして"jump end3"命令となるため、その"wait"命令と"jump end3"命令とが"wait-for-interrupt"命令に置き換わる。

【0055】

図10では、置き換え前のリストL3と置き換え後のリストL4で、置き換え部50aによる置き換え処理P20の例を説明したが、置き換え処理P20は、図7で説明したように、メモリモデル63内のHEXコードが置き換わる処理である。

【0056】

次に、実行部61での処理について説明する。図11は、実行部による処理の概要を説明するための図である。図11において、レジスタモデル62は、PC(プログラムカウンタ)62aと、その他のレジスタ62bとを有する。

【0057】

先ず、実行部61は、PC62aから値を取得して(ステップS31)、取得した値をアドレスとしてメモリモデル63から命令を読み出す(ステップS32)。そして、実行部61は、ステップS32で読み出した命令の長さ分のバイト数をPC62aの値に加算する(ステップS33)。

【0058】

次に、実行部61は、読み出した命令が割り込み待機命令であるか否かを判断する(ステップS34)。

【0059】

割り込み待機命令である場合、実行部61は、ステップS33で加算したPC62aを加算前の状態に戻し、HWシミュレータ90から割り込みイベントが通知されるまで待機する。割り込みイベントが通知されると、実行部61は、ステップS31へ戻り、上述同様の処理を繰り返す。

【0060】

一方、割り込み待機命令でない場合、実行部61は、ステップS32で読み出した命令に相当するホストCPUの命令列を実行し、必要ならレジスタモデル62の値や、メモリモデル63の値を変更する。

【0061】

ステップS32の命令がメモリモデル63などを通してハードウェアにアクセスし、HWモデル80内で時間が経過し、その間に割り込みが発生した場合、実行部61は、ステップS32で読み出した命令が不可分であるか否かを判断する(ステップS35)。

【0062】

読み出した命令が不可分である場合、実行部61は、割り込み待機部61aによって、割り込みの発生を保存し、ステップS32の命令が完了するまで待機する。ステップS32の命令の処理完了後、割り込みを実行する。

【0063】

読み出した命令が不可分でない場合、実行部61は、ソフトウェア40が組み込まれるCPU31の仕様に従ってPC62aの値などを保存し、割り込みを実行する。CPU31がIntel社が開発したx86系のCPUであれば、x86系の仕様に従ってPC62aの値などを保存する。以下同様である。

【0064】

置き換え処理の有無の違いによる実行部の処理を対比させて、第1実施例に係る実行部61による処理について説明する。

【0065】

図12は、実行部による処理を説明するためのフローチャート図である。図12(A)は置き換え処理が行われない場合の実行部による処理のフローチャートを示し、図12(B)は置き換え処理が行われる場合の実行部61による処理のフローチャートを示しており、同一処理には同一ステップ番号を付してある。

【0066】

図12(B)を参照して、実行部61による処理を説明する。図12(B)において、実行部61は、メモリモデル63内のPC62aが示すアドレスから1バイトを読み込み、OP(命令語)を取得して(ステップS41)、PC62aの値に1を加算する(ステップS42)。

【0067】

実行部61は、ステップS41で取得したOPが割り込み待機命令か否かを判断する(ステップS42−5)。

【0068】

割り込み待機命令の場合、実行部61は、割り込み待機部61aによって割り込み待機処理P45を行う。割り込み待機処理P45は、以下のステップS45−1からS45−4を含む。

【0069】

割り込み待機部61aは、PC62aの値からステップS42で加算した値「1」を減算し(ステップS45−1)、割り込み発生まで待機する(ステップS45−2)。割り込み待機部61aは、PC62aの値を退避した後(ステップS45−3)、割り込み処理のアドレスをPC62aにセットする(ステップS45−4)。割り込み待機処理P45の終了後、実行部61は、ステップS41へと戻り、上述同様の処理を繰り返す。

【0070】

一方、ステップS42−5にて、割り込み待機命令ではないと判断した場合、実行部61は、割り込み処理を考慮しつつ、ソフトウェア40が組み込まれるCPU31の仕様に従って、OPに相当する命令列を実行し(ステップS46)、ステップS41へと戻る。ステップS46における命令列の実行中の割り込み処理については、図13で詳述される。

【0071】

図12(A)に示す置き換え処理が行われない場合のフローチャートでは、図12(B)と同様のステップS41及びS42を実行した後、単に、ソフトウェア40が組み込まれるCPU31の仕様に従って、OPに相当する命令列を実行し(ステップS43)、1μsの所定時間待機する(ステップS44)。

【0072】

図12(B)に戻り、第1実施例に係る実行部61の処理では、符号D44で示されるように、図12(A)に示す所定時間待機するステップS44の処理が省略可能となる。従って、1命令を実行する毎に発生する待機時間を省略することができる。

【0073】

図13は、割り込み処理を考慮した命令列の実行処理を説明するためのフローチャート図である。図13において、実行部61は、OP(命令語)の実行中に時間が経過したか否かを判断する(ステップS46−1)。経過していない場合、実行部61は、この処理を終了する。

【0074】

時間が経過した場合、実行部61は、OPの実行中に割り込みが発生したか否かを判断する(ステップS46−2)。発生していない場合、実行部61は、この処理を終了する。

【0075】

割り込みが発生した場合、実行部61は、更に、命令は不可分か否かを判断する(ステップS46−3)。不可分である場合、実行部61は、OP完了を待機し(ステップS46−4)、PC62aの値などを退避する(ステップS46−5)。そして、実行部61は、割り込み処理のアドレスをPC62aにセットして(ステップS46−6)、この処理を終了する。

【0076】

不可分でない場合、実行部61は、PC62aの値などを退避する(ステップS46−7)。そして、実行部61は、割り込み処理のアドレスをPC62aにセットして(ステップS46−8)、この処理を終了する。

【0077】

上述した、第1実施例に係るHEX読み込み部50及び実行部61によって、1命令毎の待機を省略し、割り込み毎の待機とすることで、シミュレーションの実行時間を短縮することができる。第1実施例を適用しないために1命令毎に待機処理が発生する場合と、第1実施例を適用することにより割り込み毎の待機処理とした場合の比較を図14に示す。

【0078】

図14は、シミュレーションの実行時間の比較例を示す図である。図14中、シミュレーション時間を横軸に示している。また、図2に示すリストL1及びL2に従って、図3に示すように動作するソフトウェアの処理フローをシミュレーションした場合の比較例を示す。図3に示すステップに相当する箇所を同一符号で示している。

【0079】

図14(A)では、第1実施例を適用しない場合を、HWシミュレータ14a、HWモデル14b、CPUモデル14cとして示す。ステップS2の割り込み発生によって、ステップS3の"inc"命令、ステップS4の"reti"命令、次の割り込みが発生するまでの間繰り返されるステップS1の"jump"命令の実行毎に、図12(A)のステップS44の実行により、1μsの待機処理14pがHWシミュレータ14aに発生する。

【0080】

そのため、1μsの待機処理14pにかかる300nsがシミュレーション時間に累積されることにより、次の割り込みまでの実時間の合計が2170nsとなる。

【0081】

一方、第1実施例を適用した図14(B)に示すシミュレーションでは、1命令毎の1μsの待機処理14p(図12(A)のステップS44)を省略可能とし(図12(B)の符号D44)、更に、"jump"命令が割り込み待機命令に置き換わることにより(図8及び図9の置き換え処理P20)、CPUモデル60による"jump"命令の実行が省略される。よって、1命令毎の1μsの待機処理14pにかかる300nsと、"jump"命令の実行に必要な10nsとが省略される。

【0082】

CPUモデル60は、1命令毎に待機することなく、1処理ルーチン内のアイドルループ以外の命令列を連続してソフトウェア40を動作させることができる。

【0083】

また、アイドルループが割り込み待機命令に置き換わることにより、HWシミュレータ90は、所定の5μs時間待機することなく、次の割り込み要求をHWモデル80からCPUモデル60に行わせることができる。

【0084】

このように、ソフトウェア40をシミュレーションする際のHWシミュレータ90との同期回数を削減することによって、シミュレーション全体における次の割り込みまでのシミュレーションの実時間の合計は950nsとなる。従って、第1実施例を適用しない図14(A)に示すシミュレーション例と比べると、よりシミュレーション時間を短縮することが可能となる。

【0085】

第1実施例では、レジスタモデル62は既存のレジスタモデルを適用可能である。また、メモリモデル63についても、時間精度が時間を評価するタイムドか時間を評価しないアンタイムドかを問わず既存のメモリモデルを適用可能である。同様に、HWモデル80についても、タイムドかアンタイムドかを問わず既存のHWモデルを適用可能である。HWシミュレータ90は、HWモデル80を駆動できるシミュレータであればよい。

【0086】

[第2実施例]

第2実施例では、オブジェクト指向言語C++を利用して電子回路設計を可能とするSystemCによるHWシミュレータにおいて、第1実施例で説明したHEX読み込み部50と実行部61とを適用した場合の各モデルの構成例について説明する。

【0087】

図15は、第2実施例に係るシミュレーション装置の機能構成例を示す図である。図15において、シミュレーション装置100−2は、図4のCPU11がプログラムを実行することによって実現される、HEX読み込み部50と、CPUモデル60−2と、HWモデルであるタイマーモデル80−2と、HWシミュレータ90−2とを有する。

【0088】

ソフトウェア40−2は、後述される図16に示すリストL5及びL6のHEXファイルであり、図4の記憶装置17に格納される。

【0089】

置き換え部50aを有するHEX読み込み部50は、第1実施例と同様である。

【0090】

CPUモデル60−2は、実行部61と、レジスタモデル62−2と、メモリモデル63−2とを有し、ソフトウェア40−2を実行することによって、タイマーモデル80−2からの割り込みに応じた処理を行う。

【0091】

実行部61は、第1実施例と同様である。

【0092】

レジスタモデル62−2は、シミュレーション対象のCPUのレジスタファイルを表現するモデルであり、各レジスタはシミュレーション装置100上の変数として確保される。レジスタモデル62−2は、後述される図17に示す5つのレジスタを有する。

【0093】

メモリモデル63は、シミュレーション対象の主記憶を表現するモデルであり、後述される図18に示す構造を有する。

【0094】

タイマーモデル80−2は、5μsの所定間隔で割り込みを要求するタイマーモデルであり、後述される図22の構成を有する。

【0095】

HWシミュレータ90は、タイマーモデル80−2を駆動可能なSystemCによるシミュレータである。

【0096】

図16は、第2実施例に係るソフトウェアの例を示す図である。図16に示すように、ソフトウェア40−2は、リストL5とリストL6を表現するHEXファイルである。HEXファイルには、命令語とその配置アドレスの対のリストが記述され、命令語長は4バイト、データ幅も4バイトである。

【0097】

リストL5は、スタートアップルーチンであり、アイドルループのみで構成される。リストL5の"jump end"命令は、第1実施例に従って割り込み待機命令である"wait-for-interrupt"命令に置き換わる。

【0098】

また、リストL6は、タイマー割り込み処理ルーチンであり、主記憶(mem0)にタイマーモデル80−2の値をコピーする"load"命令と、主記憶(後述されるメモリ領域63b)にレジスタ0をコピーする"store"命令と、割り込み処理ルーチンを完了する"reti"命令とを有する。第1実施例が適用されるため、ソフトウェア40−2を動作させた際には、1命令毎の待機は省略される。

【0099】

図17は、第2実施例に係るレジスタモデルの例を示す図である。図17に示すように、レジスタモデル62−2は、以下の5種類の32ビットレジスタを有する。

・R0レジスタ6aは、汎用レジスタである。

・PCレジスタ6bは、プログラムカウンタ用のレジスタである。

・STATUSレジスタ6cは、ステータス/フラグレジスタである。

・EIPCレジスタ6dは、割り込み発生時のPCレジスタ6bの値を退避するための退避レジスタである。

・EISTATISレジスタ6eは、割り込み発生時のSTATUSレジスタ6cの値を退避するための退避レジスタである。

【0100】

図18は、第2実施例に係るメモリモデルの例を示す図である。図18に示すメモリモデル63−2は、アンタイムドのメモリモデルとして、アドレスをキーとする連想配列63aの構造と、Init関数I/F(インタフェース)63iと、Read関数I/F63rと、Write関数I/F63wとを有する。

【0101】

連想配列63aは、アドレス値が32ビットの場合、上位8ビットをキー63a−2とし、メモリ領域63bへのポインタと連想配列63cへのポインタとの対を示す値63a−4によって構成される。

【0102】

連想配列63aにおいて、キー63a−2が「00」の場合、連想配列63aの値63a−4によって、メモリ領域63bへのポインタと、連想配列63cへのポインタとの対が与えられる。キー63a−2が「01」の場合、メモリ領域63bへのポインタと、連想配列63cは存在せず空ポインタとの対が与えられる。キー63a−2が「02」の場合、メモリ領域63b及び連想配列63cとも存在せず空ポインタの対が与えられる。

【0103】

メモリ領域63bは、16MBの連続した領域を持ち、シミュレーション装置100−2における主記憶を表現する。

【0104】

連想配列63cは、IO関数のアドレスをキー63c−2として、呼び出すIO関数が値63c−4で与えられる。IO関数の一例は、図22及び図23で後述される。

【0105】

Init関数I/F63iは、連想配列63aと連想配列63cとを初期化してIO関数を設定するためのInit(初期化)関数用のインタフェースである。

【0106】

Read関数I/F63rは、READモードでIO関数を呼び出してデータを読み出すRead関数用のインタフェースである。

【0107】

Write関数I/F63wは、WRITEモードでIO関数を呼び出してデータを書き込むWrite関数用のインタフェースである。

【0108】

メモリモデル63−2へのアクセスは、初期化時は、HWシミュレータ90−2によりInit関数を通してIO関数の設定が行われる。命令列の設定は、HWシミュレータ90−2により、Write関数を通して行われる。また、シミュレーション実行時は、実行部61からRead関数とWrite関数を通して行われる。

【0109】

図19は、メモリモデルの初期化処理を説明するためのフローチャート図である。図19に示すメモリモデル63−2の初期化関数は、Init関数I/F63iを介して、HWシミュレータ90−2のメイン処理部から呼び出され、IO関数のアドレスと、IO関数へのポインタと、アクセスワードサイズの組のリストを受け取り(ステップS101)、初期化処理が行われる。

【0110】

リストが空リストか否かが判断される(ステップS102)。リストが空リストでない場合、リストの先頭から順に組を取得して変数Hに設定し、リストの先頭が次の組を指定するようにして残りの組をリストとする(ステップS103)。そして、変数Hをメモリモデル63−2内に格納する処理を行い(リスト格納処理P120)、ステップS102へ戻る。

【0111】

一方、ステップS102において、リストが空リストである場合、つまり、メモリモデル63−2に格納する組が存在しない場合、この初期化処理が終了する。

【0112】

リスト格納処理P120について説明する。リスト格納処理P120では、IO関数のアドレスを変数Aに設定し、IO関数のポインタ値を変数Pに設定し、ワードサイズを変数Lに設定する(ステップS121)。そして、変数Aの上位8ビットを変数AHに設定し、下位24ビットを変数ALに設定する(ステップS122)。

【0113】

変数AHは連想配列63aのキー63a−2を示し、変数ALは連想配列63cのキー63c−2を示す。

【0114】

変数AHの値をキー63a−2とするメモリ領域63bへのポインタが空ポインタか否かを判断する(ステップS123)。空ポインタの場合、16MBのメモリ領域63bを確保し、その先頭アドレスを連想配列63aの値63a−4のメモリ領域へのポインタに格納する(ステップS124)。また、空の連想配列63cを作成し、その先頭アドレスを連想配列63aの値63a−4の連想配列へのポインタに格納して(ステップS125)、ステップS126へと進む。

【0115】

ステップS123にて、変数AHの値をキー63a−2とするメモリ領域63bへのポインタが空ポインタでない場合、更に、変数AHの値をキー63a−2とする連想配列63cへのポインタが空ポインタか否かを判断する(ステップS123−2)。空ポインタの場合、ステップS125での処理を行うことによって、空の連想配列63cを作成し、その先頭アドレスを連想配列63aの値63a−4の連想配列へのポインタに格納して、ステップS126へと進む。ステップS123−2にて、変数AHの値をキー63a―2とする連想配列63cへのポインタが空ポインタでない場合、ステップS126へ進む。

【0116】

[AL .. AL+L−1]の夫々をキー63c−2とする値63c−4に、空ポインタを格納し(ステップS126)、ALをキー63c−2とする値63c−4にステップS121で設定した変数Pの値を格納する(ステップS127)。そして、このリスト格納処理が終了する。

【0117】

図20は、メモリモデルのデータ読出処理を説明するためのフローチャート図である。ここでは、アライメントデータアクセスの場合で説明する。図20に示すメモリモデル63−2からデータを読み出すためのRead関数が、Read関数I/F63rを介して呼び出されると、データ読出処理を開始する。

【0118】

読み出すデータのアドレスを変数Aに設定し、読み出したデータの格納先へのポインタを変数Pに設定し、読み出しバイト数を変数Lに設定する(ステップS131)。また、変数Aの上位8ビットを変数AHに設定し、下位24ビットを変数ALに設定する(ステップS132)。

【0119】

そして、変数AHの値をキー63a−2とするメモリ領域63bへのポインタが空ポインタか否かを判断する(ステップS133)。空ポインタの場合、変数Pの指す格納先に0を格納して(ステップS134)、このデータ読出処理を終了する。これは、連想配列63aのキー63a−2が「02」を示す場合の処理である。

【0120】

一方、メモリ領域63bへのポインタが空ポインタでない場合、更に、変数AHの値をキー63a−2とする連想配列63cへのポインタが空ポインタか否かを判断する(ステップS135)。空ポインタの場合、メモリ領域63bのALバイト目からLバイトのデータを読み出して変数Pの指す格納先に格納し(ステップS136)、このデータ読出処理を終了する。メモリ領域63bの先頭に変数ALで示されるバイト数を加算した読み出し開始位置から変数Lで示される読み出しバイト数分のデータが読み出され、変数Pの指す格納先に格納される。これは、連想配列63aのキー63a−2が「01」を示す場合の処理である。

【0121】

以下のステップS137からS139での処理が連想配列63aのキー63a−2が「00」を示す場合の処理に相当する。

【0122】

ステップS135にて、連想配列63cへのポインタが空ポインタでない場合、連想配列63cに変数ALの値をキー63c−2とするエントリーが存在するか否かを判断する(ステップS137)。エントリーが存在しない場合、メモリ領域63bのALバイト目からLバイトのデータを読み出して変数Pの指す格納先に格納し(ステップS138)、このデータ読出処理を終了する。メモリ領域63bの先頭に変数ALで示されるバイト数を加算した読み出し開始位置から変数Lで示される読み出しバイト数分のデータが読み出され、変数Pの示す値に格納される。

【0123】

一方、エントリーが存在する場合、変数ALの値をキー63c−2とする連想配列63cの値63c−4のIO関数をREADモードで呼び出し、結果を変数Pの指す格納先に格納する(ステップS139)。そして、このデータ読出処理を終了する。

【0124】

図21は、メモリモデルのデータ書込処理を説明するためのフローチャート図である。ここでは、アライメントデータアクセスの場合で説明する。図21に示すメモリモデル63−2へデータを書き込むためのWrite関数が、Write関数I/F63wを介して、HWシミュレータ90−2のメイン処理部から呼び出されると、データ書込処理を開始する。

【0125】

書き込むアドレスを変数Aに設定し、書き込むデータが格納された左辺値へのポインタを変数Pに設定し、書き込むバイト数を変数Lに設定する(ステップS141)。また、変数Aの上位8ビットを変数AHに設定し、下位24ビットを変数ALに設定する(ステップS142)。

【0126】

そして、変数AHの値をキー63a−2とするメモリ領域63bへのポインタが空ポインタか否かを判断する(ステップS143)。空ポインタの場合、16MBのメモリ領域63bを確保し、先頭アドレスを連想配列63aのメモリ領域63bへのポインタに格納する(ステップS144)。続けて、メモリ領域63bのALバイト目からLバイトに変数Pの指す格納先のデータを書き込み(ステップS146)、このデータ書込処理を終了する。メモリ領域63bの先頭に変数ALで示されるバイト数を加算した書き込み開始位置から変数Lで示される書き込みバイト数分の領域に、変数Pの指す格納先のデータを書き込む。これは、連想配列63aのキー63a−2が「02」を示す場合の処理である。

【0127】

一方、メモリ領域63bへのポインタが空ポインタでない場合、更に、変数AHの値をキー63a−2とする連想配列63cへのポインタが空ポインタか否かを判断する(ステップS143−5)。空ポインタの場合、メモリ領域63bのALバイト目からLバイトに変数Pの指す格納先のデータを書き込み(ステップS146)、このデータ書込処理を終了する。これは、連想配列63aのキー63a−2が「01」を示す場合の処理である。

【0128】

以下のステップS147からS149での処理が連想配列63aのキー63a−2が「00」を示す場合の処理に相当する。

【0129】

ステップS145にて、連想配列63cへのポインタが空ポインタでない場合、連想配列63cに変数ALの値をキー63c−2とするエントリーが存在するか否かを判断する(ステップS147)。エントリーが存在しない場合、メモリ領域63bのALバイト目からLバイト分の領域に変数Pの指す格納先のデータを書き込み(ステップS148)、このデータ書込処理を終了する。メモリ領域63bの先頭に変数ALで示されるバイト数を加算した書き込む開始位置から変数Lで示される書き込みバイト数分の領域に、変数Pの指す格納先のデータが書き込まれる。

【0130】

一方、エントリーが存在する場合、変数ALの値をキー63c−2とする連想配列63cの値63c−4のIO関数をWRITEモードで呼び出す(ステップS139)。そして、このデータ書込処理を終了する。

【0131】

次に、タイマーモデル80−2について図22及び図23で説明する。図22は、タイマーモデルの構成例を示す図である。図23は、タイマーモデルのプログラム例である。図22において、タイマーモデル80−2は、SystemCを使用したHWシミュレータ上で動作するHWモデルであり、時刻データ(Tick)83と、図23に示すようなbehavior関数84a及びaccess関数84bと、behavior関数84a用のbehavior関数I/F82aと、access関数84b用のaccess関数I/F82bと、CPUモデル60−2に割り込み要求を行うためのIRQ(Interrupt ReQuest) I/F82cとを有する。

【0132】

behavior関数84aは、SystemCのSC_METHOD又はSC_THREADとして表現され、図23に示すように、時刻データ83に1加算して、CPUモデル60−2に割り込みを通知した後、所定間隔の5μs待機する処理を行う。

【0133】

access関数84bは、メモリモデル63−2にIO関数としてマッピングされる、制御の遷移の伴わない関数であり、図23に示すように、指定されたアドレスに時刻データ(Tick)83を書き込む処理を行う。時刻などの待機は行わない。

【0134】

図24は、第2実施例に係るシミュレーション装置の動作シーケンスを示す図である。図24中、横軸にシミュレーション時間を示す。図24において、割り込みが発生するたびに、LOAD命令、STORE命令、RETI命令、及び割り込み待機命令が行われることを示している。割り込み待機命後の動作は、図14(B)で説明した通りである。

【0135】

LOAD命令によって、CPUモデル60−2は、メモリモデル63−2を通して、タイマーモデル63−2から時刻データ83を取得する。タイマーモデル63−2の制御の遷移の伴わないaccess関数84bを通して時刻データ83を取得する。

【0136】

STORE命令によって、CPUモデル60−2は、メモリモデル63−2を通して、主記憶を表現するメモリ領域63bに時刻データ83を書き込む。

【0137】

RETI命令によって、CPUモデル60−2は、割り込み処理ルーチンを完了する。

【0138】

割り込み待機命令によって、CPUモデル60−2は、次の割り込み発生まで待機する。

【0139】

図24に示すシミュレーション装置100−2の動作シーケンスは、ソフトウェア40−2(図16に示すリストL5及びL6のHEXファイル)を実機で実行した場合と同じ動作であり、第2実施例に係るシミュレーション装置100−2でソフトウェア40−2の検証が可能であることを示している。

【0140】

上述したように、第1実施例では、HEX読み込み部50が、シミュレーション対象のCPU31が解釈可能な命令列から無限ループ部分を検出し、これをシミュレーション内でのみ有効な割り込み待機命令に置き換える置き換え部50aを有し、実行部61が、シミュレーション実行時に割り込み待機命令を解釈し、その命令によって周辺ハードウェアモデルからの割り込みが発生するまで待機する割り込み待機部61aを有することによって、HWシミュレータ90の処理における待機回数を削減できる。

【0141】

このように、協調シミュレーションにおいて、割り込みまでの無限ループ部分を割り込み待機命令に置き換えてソフトウェアとハードウェア間の命令毎の同期を省略し割り込み毎の同期とすることによりシミュレーションを高速に行うことができる。従って、クロック同期によるISS(命令セットシミュレータ)よりも高速にシミュレーションすることが可能となる。

【0142】

また、第1実施例の機能構成に加えて、第2実施例に示すようなアンタイムドのメモリモデル63−2をCPUモデル60−2に組み込むことによって、メモリ領域63b(主記憶)へのIOアクセスを、ソフトウェア40−2を実機で実行した場合と同じ動作で実現できる。

【0143】

本発明は、具体的に開示された実施例に限定されるものではなく、特許請求の範囲から逸脱することなく、種々の変形や変更が可能である。

【0144】

以上の第1から第2実施例を含む実施形態に関し、更に以下の付記を開示する。

(付記1)

組込みソフトウェアを検証するための論理的な単体又は複数のハードウェアモデルを駆動するハードウェアシミュレータと、

前記組込みソフトウェアを実行するCPUの動作を模した前記単体又は複数のハードウェアモデルの一つであり、前記ハードウェアシミュレータとの命令毎の同期を省略して該組込みソフトウェアを動作させるCPUモデルと

を有することを特徴とするシミュレーション装置。

(付記2)

前記単体又は複数のハードウェアモデルの一つであり、割り込みを発生させる割り込みモデル

を有することを特徴とする付記1記載のシミュレーション装置。

(付記3)

前記CPUモデルは、メモリモデルを有し、

前記シミュレーション装置は、更に、組込みソフトウェアを表現する命令列を読み込んで前記メモリモデルに書き込む際に、無限ループ部分となる命令を割り込み待機命令に置き換えて該メモリモデルに書き込む置換手段を有し、

前記CPUモデルは、前記割り込み待機命令により次の割り込みまで待機することを特徴とする付記1又は2記載のシミュレーション装置。

(付記4)

前記メモリモデルは、アドレスの所定ビットをキーとするIO関数呼び出しのための関数用連想配列を有し、

前記アドレスに従って対応する前記IO関数を呼び出してデータアクセスを行うことを特徴とする付記1乃至3のいずれか一項記載のシミュレーション装置。

(付記5)

前記メモリモデルは、前記アドレスの前記所定ビット以外をキーとして、メモリ領域の領域ポインタと前記関数用連想配列の配列ポインタの対を値とするポインタ用連想配列を有し、

前記アドレスに従って前記ポインタ用連想配列により与えられた前記対の値に、前記領域ポインタ及び前記配列ポインタが与えられると共に前記関数用連想配列のキーが存在し、前記関数用連想配列の値が空ポインタでない場合、前記アドレスに従って前記IO関数を呼び出してデータアクセスを行うことを特徴とする付記4記載のシミュレーション装置。

(付記6)

前記アドレスに従って前記ポインタ用連想配列により与えられた前記対の値に、前記領域ポインタ及び前記配列ポインタが与えられると共に前記関数用連想配列のキーが存在し、前記関数用連想配列の値が空ポインタの場合、前記関数用連想配列の値が空ポインタでない前記アドレスより小さい前記アドレスのうち、最も大きな前記アドレスに従って前記IO関数を呼び出してデータアクセスを行うことを特徴とする付記5記載のシミュレーション装置。

(付記7)

前記アドレスに従って前記ポインタ用連想配列により、空ポインタが前記配列ポインタに与えられる場合、前記メモリ領域のへのデータアクセスを行うことを特徴とする付記5又は6記載のシミュレーション装置。

(付記8)

前記IO関数は前記単体又は複数のハードウェアモデルが有するアクセス関数であることを特徴とする付記4乃至7のいずれか一項記載のシミュレーション装置。

(付記9)

コンピュータを組込みソフトウェアを検証するシミュレーション装置として機能させるコンピュータ実行可能なプログラムであって、該コンピュータを、

論理的な単体又は複数のハードウェアモデルを駆動するハードウェアシミュレータと、

前記組込みソフトウェアを実行するCPUの動作を模した前記単体又は複数のハードウェアモデルの一つであり、前記ハードウェアシミュレータとの命令毎の同期を省略して該組込みソフトウェアを動作させるCPUモデルとして機能させることを特徴とするコンピュータ実行可能なプログラム。

(付記10)

前記コンピュータを、前記単体又は複数のハードウェアモデルの一つであり、割り込みを発生させる割り込みモデルとして機能させることを特徴とする付記9記載のコンピュータ実行可能なプログラム。

(付記11)

前記CPUモデルは、メモリモデルを有し、

前記シミュレーション装置は、更に、組込みソフトウェアを表現する命令列を読み込んで前記メモリモデルに書き込む際に、無限ループ部分となる命令を割り込み待機命令に置き換えて該メモリモデルに書き込む置換手段を有し、

前記CPUモデルは、前記割り込みモデルからの割り込みに応じた前記組込みソフトウェアの動作後、前記割り込み待機命令により次の割り込みまで待機することを特徴とする付記10記載のコンピュータ実行可能なプログラム。

(付記12)

コンピュータを組込みソフトウェアを検証するシミュレーション装置として機能させるプログラムを格納したコンピュータ読取可能な記憶媒体であって、該コンピュータを、

論理的な単体又は複数のハードウェアモデルを駆動するハードウェアシミュレータと、

前記組込みソフトウェアを実行するCPUの動作を模した前記単体又は複数のハードウェアモデルの一つであり、前記ハードウェアシミュレータとの命令毎の同期を省略して該組込みソフトウェアを動作させるCPUモデルとして機能させることを特徴とするコンピュータ読取可能な記憶媒体。

(付記13)

前記コンピュータを、前記単体又は複数のハードウェアモデルの一つであり、割り込みを発生させる割り込みモデルとして機能させることを特徴とする請求項12記載のコンピュータ読み取り可能な記憶媒体。

(付記14)

前記CPUモデルは、メモリモデルを有し、

前記シミュレーション装置は、更に、組込みソフトウェアを表現する命令列を読み込んで前記メモリモデルに書き込む際に、無限ループ部分となる命令を割り込み待機命令に置き換えて該メモリモデルに書き込む置換手段を有し、

前記CPUモデルは、前記割り込みモデルからの割り込みに応じた前記組込みソフトウェアの動作後、前記割り込み待機命令により次の割り込みまで待機することを特徴とする付記13記載のコンピュータ読取可能な記憶媒体。

(付記15)

前記メモリモデルは、アドレスの所定ビットをキーとするIO関数呼び出しのための関数用連想配列を有し、

前記コンピュータに、前記アドレスに従って対応する前記IO関数を呼び出してデータアクセスを行わせることを特徴とする付記14記載のコンピュータ読取可能な記憶媒体。

(付記16)

組込みソフトウェアを検証するシミュレーション装置で実行されるシミュレーション方法であって、

ハードウェアシミュレータ上で駆動し、前記組込みソフトウェアを実行するCPUの動作を模したCPUモデルが、該ハードウェアシミュレータとの命令毎の同期を省略して該組込みソフトウェアを動作させることを特徴とするシミュレーション方法。

(付記17)

前記CPUモデルは、メモリモデルを有し、

前記シミュレーション装置は、更に、組込みソフトウェアを表現する命令列を読み込んで前記メモリモデルに書き込む際に、無限ループ部分となる命令を割り込み待機命令に置き換えて該メモリモデルに書き込む置換手段を有し、

前記CPUモデルは、所定間隔で割り込みを発生させる割り込みモデルからの割り込み要求に応じた前記組込みソフトウェアの動作後、前記割り込み待機命令により次の割り込みまで待機することを特徴とする

付記16記載のシミュレーション方法。

【符号の説明】

【0145】

6a R0レジスタ

6b PCレジスタ

6c STATUSレジスタ

6d EIPCレジスタ

6e EISTATISレジスタ

11 CPU

12 メモリユニット

13 表示ユニット

14 出力ユニット

15 入力ユニット

16 通信ユニット

17 記憶装置

18 ドライバ

19 記憶媒体

40、40−2 ソフトウェア

50 HEX読み込み部

50a 置き換え部

60、60−2 CPUモデル

61 実行部

61a 割り込み待機部

62、62−2 レジスタモデル

62a PC

62b その他のレジスタ

63、63−2 メモリモデル

63a 連想配列

63a−2 キー

63a−4 値

63b メモリ領域

63c 連想配列

63c−2 キー

63c−4 値

63i Init関数I/F

63r Read関数I/F

63w Write関数I/F

80 HWモデル

80−2 タイマーモデル

82a behavior関数I/F

82b access関数I/F

82c IRQ I/F

83 時刻データ

84a behavior関数

84b access関数

90 HWシミュレータ

L1、L2、L3、L4、L5、L6 リスト

【特許請求の範囲】

【請求項1】

組込みソフトウェアを検証するための論理的な単体又は複数のハードウェアモデルを駆動するハードウェアシミュレータと、

前記組込みソフトウェアを実行するCPUの動作を模した前記単体又は複数のハードウェアモデルの一つであり、前記ハードウェアシミュレータとの命令毎の同期を省略して該組込みソフトウェアを動作させるCPUモデルと

を有することを特徴とするシミュレーション装置。

【請求項2】

前記単体又は複数のハードウェアモデルの一つであり、割り込みを発生させる割り込みモデル

を有することを特徴とする請求項1記載のシミュレーション装置。

【請求項3】

前記CPUモデルは、メモリモデルを有し、

前記シミュレーション装置は、更に、組込みソフトウェアを表現する命令列を読み込んで前記メモリモデルに書き込む際に、無限ループ部分となる命令を割り込み待機命令に置き換えて該メモリモデルに書き込む置換手段を有し、

前記CPUモデルは、前記割り込み待機命令により次の割り込みまで待機することを特徴とする請求項1又は2記載のシミュレーション装置。

【請求項4】

前記メモリモデルは、アドレスの所定ビットをキーとするIO関数呼び出しのための関数用連想配列を有し、

前記アドレスに従って対応する前記IO関数を呼び出してデータアクセスを行うことを特徴とする請求項1乃至3のいずれか一項記載のシミュレーション装置。

【請求項5】

前記メモリモデルは、前記アドレスの前記所定ビット以外をキーとして、メモリ領域の領域ポインタと前記関数用連想配列の配列ポインタの対を値とするポインタ用連想配列を有し、

前記アドレスに従って前記ポインタ用連想配列により与えられた前記対の値に、前記領域ポインタ及び前記配列ポインタが与えられると共に前記関数用連想配列のキーが存在し、前記関数用連想配列の値が空ポインタでない場合、前記IO関数を呼び出してデータアクセスを行うことを特徴とする請求項4記載のシミュレーション装置。

【請求項6】

前記アドレスに従って前記ポインタ用連想配列により与えられた前記対の値に、前記領域ポインタ及び前記配列ポインタが与えられると共に前記関数用連想配列のキーが存在し、前記関数用連想配列の値が空ポインタの場合、前記関数用連想配列の値が空ポインタでない前記アドレスより小さい前記アドレスのうち、最も大きな前記アドレスに従って前記IO関数を呼び出してデータアクセスを行うことを特徴とする請求項5記載のシミュレーション装置。

【請求項7】

前記アドレスに従って前記ポインタ用連想配列により、空ポインタが前記配列ポインタに与えられる場合、前記メモリ領域のへのデータアクセスを行うことを特徴とする請求項5又は6記載のシミュレーション装置。

【請求項8】

前記IO関数は前記単体又は複数のハードウェアモデルが有するアクセス関数であることを特徴とする請求項4乃至7のいずれか一項記載のシミュレーション装置。

【請求項9】

コンピュータを組込みソフトウェアを検証するシミュレーション装置として機能させるコンピュータ実行可能なプログラムであって、該コンピュータを、

論理的な単体又は複数のハードウェアモデルを駆動するハードウェアシミュレータと、

前記組込みソフトウェアを実行するCPUの動作を模した前記単体又は複数のハードウェアモデルの一つであり、前記ハードウェアシミュレータとの命令毎の同期を省略して該組込みソフトウェアを動作させるCPUモデルとして機能させることを特徴とするコンピュータ実行可能なプログラム。

【請求項10】

前記コンピュータを、前記単体又は複数のハードウェアモデルの一つであり、割り込みを発生させるモデルとして機能させることを特徴とする請求項9記載のコンピュータ実行可能なプログラム。

【請求項11】

コンピュータを組込みソフトウェアを検証するシミュレーション装置として機能させるプログラムを格納したコンピュータ読取可能な記憶媒体であって、該コンピュータを、

論理的な単体又は複数のハードウェアモデルを駆動するハードウェアシミュレータと、

前記組込みソフトウェアを実行するCPUの動作を模した前記単体又は複数のハードウェアモデルの一つであり、前記ハードウェアシミュレータとの命令毎の同期を省略して該組込みソフトウェアを動作させるCPUモデルとして機能させることを特徴とするコンピュータ読取可能な記憶媒体。

【請求項12】

前記コンピュータを、前記単体又は複数のハードウェアモデルの一つであり、割り込みを発生させるモデルとして機能させることを特徴とする請求項11記載のコンピュータ読み取り可能な記憶媒体。

【請求項13】

組込みソフトウェアを検証するシミュレーション装置で実行されるシミュレーション方法であって、

ハードウェアシミュレータ上で駆動し、前記組込みソフトウェアを実行するCPUの動作を模したCPUモデルが、該ハードウェアシミュレータとの命令毎の同期を省略して該組込みソフトウェアを動作させることを特徴とするシミュレーション方法。

【請求項1】

組込みソフトウェアを検証するための論理的な単体又は複数のハードウェアモデルを駆動するハードウェアシミュレータと、

前記組込みソフトウェアを実行するCPUの動作を模した前記単体又は複数のハードウェアモデルの一つであり、前記ハードウェアシミュレータとの命令毎の同期を省略して該組込みソフトウェアを動作させるCPUモデルと

を有することを特徴とするシミュレーション装置。

【請求項2】

前記単体又は複数のハードウェアモデルの一つであり、割り込みを発生させる割り込みモデル

を有することを特徴とする請求項1記載のシミュレーション装置。

【請求項3】

前記CPUモデルは、メモリモデルを有し、

前記シミュレーション装置は、更に、組込みソフトウェアを表現する命令列を読み込んで前記メモリモデルに書き込む際に、無限ループ部分となる命令を割り込み待機命令に置き換えて該メモリモデルに書き込む置換手段を有し、

前記CPUモデルは、前記割り込み待機命令により次の割り込みまで待機することを特徴とする請求項1又は2記載のシミュレーション装置。

【請求項4】

前記メモリモデルは、アドレスの所定ビットをキーとするIO関数呼び出しのための関数用連想配列を有し、

前記アドレスに従って対応する前記IO関数を呼び出してデータアクセスを行うことを特徴とする請求項1乃至3のいずれか一項記載のシミュレーション装置。

【請求項5】

前記メモリモデルは、前記アドレスの前記所定ビット以外をキーとして、メモリ領域の領域ポインタと前記関数用連想配列の配列ポインタの対を値とするポインタ用連想配列を有し、

前記アドレスに従って前記ポインタ用連想配列により与えられた前記対の値に、前記領域ポインタ及び前記配列ポインタが与えられると共に前記関数用連想配列のキーが存在し、前記関数用連想配列の値が空ポインタでない場合、前記IO関数を呼び出してデータアクセスを行うことを特徴とする請求項4記載のシミュレーション装置。

【請求項6】

前記アドレスに従って前記ポインタ用連想配列により与えられた前記対の値に、前記領域ポインタ及び前記配列ポインタが与えられると共に前記関数用連想配列のキーが存在し、前記関数用連想配列の値が空ポインタの場合、前記関数用連想配列の値が空ポインタでない前記アドレスより小さい前記アドレスのうち、最も大きな前記アドレスに従って前記IO関数を呼び出してデータアクセスを行うことを特徴とする請求項5記載のシミュレーション装置。

【請求項7】

前記アドレスに従って前記ポインタ用連想配列により、空ポインタが前記配列ポインタに与えられる場合、前記メモリ領域のへのデータアクセスを行うことを特徴とする請求項5又は6記載のシミュレーション装置。

【請求項8】

前記IO関数は前記単体又は複数のハードウェアモデルが有するアクセス関数であることを特徴とする請求項4乃至7のいずれか一項記載のシミュレーション装置。

【請求項9】

コンピュータを組込みソフトウェアを検証するシミュレーション装置として機能させるコンピュータ実行可能なプログラムであって、該コンピュータを、

論理的な単体又は複数のハードウェアモデルを駆動するハードウェアシミュレータと、

前記組込みソフトウェアを実行するCPUの動作を模した前記単体又は複数のハードウェアモデルの一つであり、前記ハードウェアシミュレータとの命令毎の同期を省略して該組込みソフトウェアを動作させるCPUモデルとして機能させることを特徴とするコンピュータ実行可能なプログラム。

【請求項10】

前記コンピュータを、前記単体又は複数のハードウェアモデルの一つであり、割り込みを発生させるモデルとして機能させることを特徴とする請求項9記載のコンピュータ実行可能なプログラム。

【請求項11】

コンピュータを組込みソフトウェアを検証するシミュレーション装置として機能させるプログラムを格納したコンピュータ読取可能な記憶媒体であって、該コンピュータを、

論理的な単体又は複数のハードウェアモデルを駆動するハードウェアシミュレータと、

前記組込みソフトウェアを実行するCPUの動作を模した前記単体又は複数のハードウェアモデルの一つであり、前記ハードウェアシミュレータとの命令毎の同期を省略して該組込みソフトウェアを動作させるCPUモデルとして機能させることを特徴とするコンピュータ読取可能な記憶媒体。

【請求項12】

前記コンピュータを、前記単体又は複数のハードウェアモデルの一つであり、割り込みを発生させるモデルとして機能させることを特徴とする請求項11記載のコンピュータ読み取り可能な記憶媒体。

【請求項13】

組込みソフトウェアを検証するシミュレーション装置で実行されるシミュレーション方法であって、

ハードウェアシミュレータ上で駆動し、前記組込みソフトウェアを実行するCPUの動作を模したCPUモデルが、該ハードウェアシミュレータとの命令毎の同期を省略して該組込みソフトウェアを動作させることを特徴とするシミュレーション方法。

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【図14】

【図15】

【図16】

【図17】

【図18】

【図19】

【図20】

【図21】

【図22】

【図23】

【図24】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【図14】

【図15】

【図16】

【図17】

【図18】

【図19】

【図20】

【図21】

【図22】

【図23】

【図24】

【公開番号】特開2012−83834(P2012−83834A)

【公開日】平成24年4月26日(2012.4.26)

【国際特許分類】

【出願番号】特願2010−227409(P2010−227409)

【出願日】平成22年10月7日(2010.10.7)

【出願人】(308014341)富士通セミコンダクター株式会社 (2,507)

【Fターム(参考)】

【公開日】平成24年4月26日(2012.4.26)

【国際特許分類】

【出願日】平成22年10月7日(2010.10.7)

【出願人】(308014341)富士通セミコンダクター株式会社 (2,507)

【Fターム(参考)】

[ Back to top ]