シリアル・パラレル双方向変換装置,プリント基板及び情報処理装置

【課題】 シリアルROMインターフェースしか有しない機能デバイスでパラレルデータを扱うメモリにアクセス可能とするシリアル・パラレル双方向変換装置を提供すること。

【解決手段】 シリアルインターフェースを備えた機能デバイスと,パラレル信号で動作するメモリとの間に配置されるリアル・パラレル双方向変換装置を,シリアルデータ信号をパラレルデータ信号に変換するシリアル・パラレル変換回路と,データ信号とアドレス信号とを分離すると共にデータ信号を出力するデータ・アドレス分離回路と,出力されたデータ信号をメモリへのデータ信号としてアドレス信号と関連して出力し,メモリからのパラレルデータ信号を出力すると共に機能デバイスからの制御信号をメモリの制御信号に変換して出力するデータ制御回路と,前記データ制御回路からのパラレルデータをシリアルデータに変換するパラレル・シリアル変換回路とを備えて構成する。

【解決手段】 シリアルインターフェースを備えた機能デバイスと,パラレル信号で動作するメモリとの間に配置されるリアル・パラレル双方向変換装置を,シリアルデータ信号をパラレルデータ信号に変換するシリアル・パラレル変換回路と,データ信号とアドレス信号とを分離すると共にデータ信号を出力するデータ・アドレス分離回路と,出力されたデータ信号をメモリへのデータ信号としてアドレス信号と関連して出力し,メモリからのパラレルデータ信号を出力すると共に機能デバイスからの制御信号をメモリの制御信号に変換して出力するデータ制御回路と,前記データ制御回路からのパラレルデータをシリアルデータに変換するパラレル・シリアル変換回路とを備えて構成する。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は,シリアル・パラレル双方向変換装置,プリント基板及び情報処理装置に係り,特に記憶手段と,記憶制御手段との間に配置され,前記記憶手段と前記記憶制御手段との間でのデータの入出力を行うシリアル・パラレル双方向変換装置に関する。

【背景技術】

【0002】

一般に電子機器システムでは,電源オフ状態でもデータを記憶しておくことができるROMといわれる不揮発性メモリが多用されている。また,データアクセス方式としては,データバス(線),アドレスバス(線),制御線がそれぞれ独立(パラレル)に存在するEPROM,Flashメモリと,データ線とアドレス線が一本の専用線を共有し時分割でデータを転送するシリアルROMの2種類がある。

【0003】

このため,シリアルのデータ線から入力されたシリアルデータをパラレルデータとして使用するためシリアル・パラレル変換を行う必要がある。従来特許文献1には,マスタ装置,スレーブ装置間に受信データ線及び送信データ線を設け,受信データ線を介して入力される一定長のシリアルデータをパラレルデータに変換するシリアル/パラレル変換回路と,一定長のパラレルデータをシリアルデータに変換し送信データ線から出力するパラレル/シリアル変換回路と,受信データのアドレスデータと自装置のアドレスデータの一致を検出するアドレス一致検出回路と,両アドレスデータが一致したときアドレス一致検出回路により同時に起動される受信コントロール回路及び送信コントロール回路と,シリアル/パラレル変換回路で変換されたパラレルデータが受信コントロール回路により入力され,入力された順序にしたがって出力する受信データFIFO回路及び送信データが入力され,入力された順序にしたがって送信コントロール回路によりパラレル/シリアル変換回路へ出力する送信データFIFO回路と,受信データFIFO回路から出力された受信データをデータバスを介してアドレスデータを持つスレーブ装置のメモリに送出し,このスレーブ装置のメモリからの送信データを送信データFIFO回路に送出するデータバスインターフェース回路とを設けたものが記載されている。

【0004】

【特許文献1】特開平1−246941号公報

【発明の開示】

【発明が解決しようとする課題】

【0005】

ところで,通常大量データの保存にはEPROMまたはFlashメモリといったバスパラレルデータを取り扱うROMを用いるのが常であるが,シリアルROMの制御回路しか持たない装置があり,上述したパラレルデータを取り扱うROMを使用することができない。

【0006】

近年実用化されている機能デバイスを使用した装置では,基板としてシリアルROMインターフェースだけを備えるものがあり,このような基板を用いて大量のパラレルデータを高速に取り扱う上記DPROMやFlashメモリをそのまま使用したいという要望がある。一般の通信装置などで使用されるシリアル・パラレル変換に関しては,上述したようにシリアルデータをパラレルデータに変換するものがある。

【0007】

しかし,上述したシリアル・パラレル変換装置は,シリアルデータをパラレルデータに変換あるいはその逆方向の変換をするだけのものであり,シリアルROMインターフェースを備えた機能デバイスにパラレルデータを取り扱うEPROMやFlashメモリを直接接続することができるように構成した装置はなかった。

【0008】

本発明は,上述した従来の問題点に鑑みなされたものであり,シリアルROMインターフェースしか有しない装置でEPROMやFlashメモリを使用することができるシリアル・パラレル双方向変換装置を提供することを目的とする。

【課題を解決するための手段】

【0009】

請求項1に記載の発明は,シリアルROMインターフェース(SPIバス方式)を備えた機能デバイスと,パラレル信号で動作する記憶手段との間に配置され,入力されたデータ信号とアドレス信号とを含むシリアルデータ信号をパラレルデータ信号に変換するシリアル・パラレル変換回路と,前記変換されたパラレルデータ信号からデータ信号とアドレス信号とを分離してデータ信号を前記記憶手段に入力すると共に,前記データ信号を出力するデータ・アドレス分離回路と,前記出力されたデータ信号を前記記憶手段へのデータ信号として前記アドレス信号と関連して出力し,前記記憶手段からのパラレルデータ信号を出力すると共に,前記機能デバイスからの制御信号を前記記憶手段の制御信号に変換して出力するデータ制御回路と,前記データ制御回路からのパラレルデータをシリアルデータに変換するパラレル・シリアル変換回路とを備え,前記記憶手段と前記機能デバイスとの間でデータの入出力を行うことを特徴とするリアル・パラレル双方向変換装置である。

【0010】

請求項2の発明は,請求項1に記載のシリアル・パラレル双方向変換装置において,前記シリアル・パラレル双方向変換装置には,装置内部の状態を取得し,前記データ制御回路に入力する状態変更手段を備えたことを特徴とする。

【0011】

請求項3の発明は,請求項1または請求項2のいずれかに記載のシリアル・パラレル双方向変換装置において,前記記憶手段は,EPROMまたはFlashメモリを含むものであることを特徴とする。

【0012】

請求項4の発明は,請求項1乃至請求項3のいずれかに記載のシリアル・パラレル双方向変換装置において,シリアル・パラレル双方向変換装置は機能デバイスに取り付けられる入出力制御装置に設けられていることを特徴とする。

【0013】

請求項5に記載の発明は,請求項4に記載のシリアル・パラレル双方向変換装置において,前記機能デバイスと入出力制御装置とは同一のプリント基板内に設けられ,前記シリアル・パラレル双方向変換装置の入出力端子はプリント基板に配置される記憶手段に接続されていることを特徴とする。

【0014】

請求項6の発明は,機能デバイス及び請求項1乃至請求項5のいずれかに記載のシリアル・パラレル双方向変換装置を備えたことを特徴とするプリント基板である。ここでプリント基板は,画像処理,信号変換処理,電子機器システム評価等の情報処理を行うものを含む。

【0015】

請求項7に記載の発明は,請求項6に記載のプリント基板において,記憶手段を備えたことを特徴とする。

【0016】

請求項8に記載の発明は,機能デバイスと,請求項1乃至請求項4のいずれかに記載のシリアル・パラレル双方向変換装置を備えた情報処理装置である。ここで情報処理装置は,画像処理,信号変換処理,電子機器システム評価等の情報処理を行うものを含む。

【0017】

請求項9に記載の発明は,請求項5または請求項6のいずれかに記載のプリント基板を備えた情報処理装置である。

【発明の効果】

【0018】

請求項1に記載の発明によれば,シリアルROMインターフェースだけを備えた機能デバイスにシリアル・パラレル双方向変換装置を接続することによりEPROMやFlashメモリのようなパラレルデータを取り扱う記憶手段へ直接のアクセスすることができる。

【0019】

請求項2に記載の発明によれば,シリアル・パラレル双方向変換装置の状態を状態変更手段で変更することができ,常に適切なシリアル・パラレル双方向変換を行うことができる。

【0020】

請求項3に記載の発明によれば,リアルインターフェースだけを備えた機能デバイスに備えられた記憶制御手段でEPROM,Flashメモリをそのまま使用することができる。

【0021】

請求項4に記載の発明によれば,シリアル・パラレル双方向変換装置は機能デバイスに取り付けられる入出力制御装置に設けられているから,機能デバイスと入出力制御装置を組み合わせるだけで,機能デバイスからパラレルデータを取り扱う記憶手段にアクセスすることができる。

【0022】

請求項5に記載の発明によれば,機能デバイスと入出力制御装置とは同一のプリント基板内に設けられ,前記シリアル・パラレル双方向変換装置の入出力端子はプリント基板に配置される記憶手段に接続されているから,一枚のプリント基板上に機能デバイス,入出力制御装置,及び記憶手段を配置することができる

【0023】

請求項6に記載の発明によれば,機能デバイスを含むプリント基板にパラレルデータを取り扱う記憶手段を取り付けるだけで,機能デバイスは,前記記憶手段にアクセスすることができる。

【0024】

請求項7に記載の発明によれば,機能デバイスを備えたプリント基板だけでパラレルデータを取り扱う記憶手段を含む情報処理を行うことができる。

【0025】

請求項8に記載の発明によれば,情報処理装置は,パラレルデータを取り扱う記憶手段を接続することにより機能デバイスによる情報処理をおこなうことができる。

【0026】

請求項9に記載の発明によれば,情報処理装置は,それ自体で機能デバイスとパラレルデータを取り扱う記憶手段による情報処理を行うことができる。

【発明を実施するための最良の形態】

【0027】

以下,本発明を実施するための最良の形態を,図に基づいて説明する。

【実施例1】

【0028】

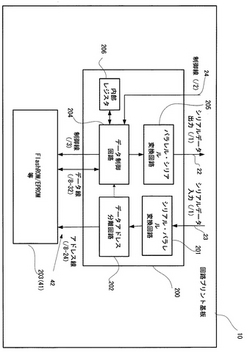

図1は実施の形態例に係るシリアル・パラレル双方向変換装置の構成を示すブロック図,図2は実施の形態例に係るシリアル・パラレル双方向変換装置を備えたプリント基板の構成を示すブロック図である。

【0029】

本実施例1では,シリアル・パラレル双方向変換装置200は,図2に示すように機能デバイス20を備えた情報処理装置10のプリント基板に設けられた入出力制御装置30内に設けられる。機能デバイスは公知のCPUその他の装置が使用される。

【0030】

本実施例1に係る情報処理装置10は,図2に示すように,シリアルROMインターフェース21を備えた機能デバイス20と,入出力制御装置30と,入出力制御装置30に接続されたFlashROM42とを備えている。機能デバイス20と入出力制御装置30とは,シリアル信号線22,23及び制御線24で接続され,FlashROM41は入出力制御装置30とパラレル信号線42で接続されている。

【0031】

本実施例1において,パラレル双方向変換装置200は,図1に示すように,入力されたデータ信号とアドレス信号とを含むシリアルデータ信号をパラレルデータ信号に変換するシリアル・パラレル変換回路201と,前記変換されたパラレルデータ信号からデータ信号とアドレス信号とを分離してデータ信号を前記記憶手段に入力すると共に,前記データ信号を出力するデータ・アドレス分離回路202と,前記出力されたデータ信号を前記記憶手段へのデータ信号として前記アドレス信号と関連して出力し,前記記憶手段からのパラレルデータ信号を出力すると共に,前記制御手段からの制御信号を前記記憶手段の制御信号に変換して出力するデータ制御回路204と,前記データ制御回路からのパラレルデータをシリアルデータに変換するパラレル・シリアル変換回路205と,パラレル双方向変換装置200内部の状態を取得し,前記データ制御回路に入力する状態変更手段状態変更手段である内部レジスタ206とを備える。

【0032】

本実施例1では,シリアル・パラレル変換回路201は,1ラインから経時的に伝送されるシリアル信号をパラレル信号に変更する。アドレス分離回路202は前記パラレル信号中のアドレス信号(8−12)とデータ信号を分離し,アドレス信号をアドレス線からメモリ203に出力する。また,アドレス分離回路202から出力されたデータ信号はデータ制御回路204からデータ線(8−32)を介してメモリ203に出力される。このとき,データ信号と,アドレス信号とはメモリ203が駆動可能なタイミングで出力される。

【0033】

メモリ203は,上記メモリへのデータ出力を行うほか,メモリ203からのデータ信号を受信し,パラレル・シリアル変換回路205へ出力する。パラレル・シリアル変換回路205では受け取ったパラレルデータをシリアルデータとして機能デバイス20に出力する。即ち,本実施例1では,シリアル・パラレル双方向変換装置200はシリアルROMインターフェース規約によるアドレス,データ,制御信号変換ロジック(シリアル−パラレル)を実装し,機能デバイス20から,直接メモリ203へのアクセスを実現する。

【0034】

また,内部レジスタ206はデバイス内部情報を取得してデータ制御回路204にその状態を送出する。

【0035】

次に本実施例1に係るパラレル双方向変換装置200の動作について説明する。本実施例1では,機能デバイス20がメモリ203(図2中FlashROM42に相当)に書き込む際には,アドレスと,データとを含むシリアルデータがパラレル変換回路201に入力される。パラレル変換回路201は1ラインから経時的に伝送されるシリアル信号をパラレル信号に変更し,アドレス分離回路202に送出する。アドレス分離回路202は前記パラレル信号中のアドレス信号(8−12)とデータ信号を分離し,アドレス信号をアドレス線からメモリ203に出力する。また,アドレス分離回路202から出力されたデータ信号はデータ制御回路204からデータ線(8−32)を介してメモリ203に出力される。これによりメモリ203の所定アドレスに送出されたデータが書き込まれる。

【0036】

一方,機能デバイス20が203のデータを読み出すときには,アドレスを含むシリアルデータがパラレル変換回路201に入力される。パラレル変換回路201は1ラインから経時的に伝送されるシリアル信号をパラレル信号に変更し,アドレス分離回路202に送出する。アドレス分離回路202は前記パラレル信号中のアドレス信号(8−12をアドレス線からメモリ203に出力する。これによりメモリ203の所定アドレスに送出されたデータが送出される。このデータは,パラレル・シリアル変換回路205でシリアル信号に変換され,機能デバイス20に出力される。

【0037】

以上説明したように,本実施例1によれば,シリアルROMインターフェースしか有しない機能デバイスを使用する装置であっても,係るシリアル・パラレル双方向変換装置を内蔵した入出力制御装置30を使用することで容易にEPROMやFlashメモリを利用することができる。

【図面の簡単な説明】

【0038】

【図1】実施例1に係るシリアル・パラレル双方向変換装置の構成を示すブロック図である。

【図2】実施例1に係るシリアル・パラレル双方向変換装置を備えた情報処理装置の構成を示すブロック図である。

【符号の説明】

【0039】

10 データ処理装置

20 機能デバイス

21 シリアルROMインターフェース

30 入出力制御装置(コンパニオンデバイス)

41 FlashROM

42 パラレル信号線

203 メモリ(記憶手段)

204 データ制御回路

205 パラレル・シリアル変換回路

206 内部レジスタ

【技術分野】

【0001】

本発明は,シリアル・パラレル双方向変換装置,プリント基板及び情報処理装置に係り,特に記憶手段と,記憶制御手段との間に配置され,前記記憶手段と前記記憶制御手段との間でのデータの入出力を行うシリアル・パラレル双方向変換装置に関する。

【背景技術】

【0002】

一般に電子機器システムでは,電源オフ状態でもデータを記憶しておくことができるROMといわれる不揮発性メモリが多用されている。また,データアクセス方式としては,データバス(線),アドレスバス(線),制御線がそれぞれ独立(パラレル)に存在するEPROM,Flashメモリと,データ線とアドレス線が一本の専用線を共有し時分割でデータを転送するシリアルROMの2種類がある。

【0003】

このため,シリアルのデータ線から入力されたシリアルデータをパラレルデータとして使用するためシリアル・パラレル変換を行う必要がある。従来特許文献1には,マスタ装置,スレーブ装置間に受信データ線及び送信データ線を設け,受信データ線を介して入力される一定長のシリアルデータをパラレルデータに変換するシリアル/パラレル変換回路と,一定長のパラレルデータをシリアルデータに変換し送信データ線から出力するパラレル/シリアル変換回路と,受信データのアドレスデータと自装置のアドレスデータの一致を検出するアドレス一致検出回路と,両アドレスデータが一致したときアドレス一致検出回路により同時に起動される受信コントロール回路及び送信コントロール回路と,シリアル/パラレル変換回路で変換されたパラレルデータが受信コントロール回路により入力され,入力された順序にしたがって出力する受信データFIFO回路及び送信データが入力され,入力された順序にしたがって送信コントロール回路によりパラレル/シリアル変換回路へ出力する送信データFIFO回路と,受信データFIFO回路から出力された受信データをデータバスを介してアドレスデータを持つスレーブ装置のメモリに送出し,このスレーブ装置のメモリからの送信データを送信データFIFO回路に送出するデータバスインターフェース回路とを設けたものが記載されている。

【0004】

【特許文献1】特開平1−246941号公報

【発明の開示】

【発明が解決しようとする課題】

【0005】

ところで,通常大量データの保存にはEPROMまたはFlashメモリといったバスパラレルデータを取り扱うROMを用いるのが常であるが,シリアルROMの制御回路しか持たない装置があり,上述したパラレルデータを取り扱うROMを使用することができない。

【0006】

近年実用化されている機能デバイスを使用した装置では,基板としてシリアルROMインターフェースだけを備えるものがあり,このような基板を用いて大量のパラレルデータを高速に取り扱う上記DPROMやFlashメモリをそのまま使用したいという要望がある。一般の通信装置などで使用されるシリアル・パラレル変換に関しては,上述したようにシリアルデータをパラレルデータに変換するものがある。

【0007】

しかし,上述したシリアル・パラレル変換装置は,シリアルデータをパラレルデータに変換あるいはその逆方向の変換をするだけのものであり,シリアルROMインターフェースを備えた機能デバイスにパラレルデータを取り扱うEPROMやFlashメモリを直接接続することができるように構成した装置はなかった。

【0008】

本発明は,上述した従来の問題点に鑑みなされたものであり,シリアルROMインターフェースしか有しない装置でEPROMやFlashメモリを使用することができるシリアル・パラレル双方向変換装置を提供することを目的とする。

【課題を解決するための手段】

【0009】

請求項1に記載の発明は,シリアルROMインターフェース(SPIバス方式)を備えた機能デバイスと,パラレル信号で動作する記憶手段との間に配置され,入力されたデータ信号とアドレス信号とを含むシリアルデータ信号をパラレルデータ信号に変換するシリアル・パラレル変換回路と,前記変換されたパラレルデータ信号からデータ信号とアドレス信号とを分離してデータ信号を前記記憶手段に入力すると共に,前記データ信号を出力するデータ・アドレス分離回路と,前記出力されたデータ信号を前記記憶手段へのデータ信号として前記アドレス信号と関連して出力し,前記記憶手段からのパラレルデータ信号を出力すると共に,前記機能デバイスからの制御信号を前記記憶手段の制御信号に変換して出力するデータ制御回路と,前記データ制御回路からのパラレルデータをシリアルデータに変換するパラレル・シリアル変換回路とを備え,前記記憶手段と前記機能デバイスとの間でデータの入出力を行うことを特徴とするリアル・パラレル双方向変換装置である。

【0010】

請求項2の発明は,請求項1に記載のシリアル・パラレル双方向変換装置において,前記シリアル・パラレル双方向変換装置には,装置内部の状態を取得し,前記データ制御回路に入力する状態変更手段を備えたことを特徴とする。

【0011】

請求項3の発明は,請求項1または請求項2のいずれかに記載のシリアル・パラレル双方向変換装置において,前記記憶手段は,EPROMまたはFlashメモリを含むものであることを特徴とする。

【0012】

請求項4の発明は,請求項1乃至請求項3のいずれかに記載のシリアル・パラレル双方向変換装置において,シリアル・パラレル双方向変換装置は機能デバイスに取り付けられる入出力制御装置に設けられていることを特徴とする。

【0013】

請求項5に記載の発明は,請求項4に記載のシリアル・パラレル双方向変換装置において,前記機能デバイスと入出力制御装置とは同一のプリント基板内に設けられ,前記シリアル・パラレル双方向変換装置の入出力端子はプリント基板に配置される記憶手段に接続されていることを特徴とする。

【0014】

請求項6の発明は,機能デバイス及び請求項1乃至請求項5のいずれかに記載のシリアル・パラレル双方向変換装置を備えたことを特徴とするプリント基板である。ここでプリント基板は,画像処理,信号変換処理,電子機器システム評価等の情報処理を行うものを含む。

【0015】

請求項7に記載の発明は,請求項6に記載のプリント基板において,記憶手段を備えたことを特徴とする。

【0016】

請求項8に記載の発明は,機能デバイスと,請求項1乃至請求項4のいずれかに記載のシリアル・パラレル双方向変換装置を備えた情報処理装置である。ここで情報処理装置は,画像処理,信号変換処理,電子機器システム評価等の情報処理を行うものを含む。

【0017】

請求項9に記載の発明は,請求項5または請求項6のいずれかに記載のプリント基板を備えた情報処理装置である。

【発明の効果】

【0018】

請求項1に記載の発明によれば,シリアルROMインターフェースだけを備えた機能デバイスにシリアル・パラレル双方向変換装置を接続することによりEPROMやFlashメモリのようなパラレルデータを取り扱う記憶手段へ直接のアクセスすることができる。

【0019】

請求項2に記載の発明によれば,シリアル・パラレル双方向変換装置の状態を状態変更手段で変更することができ,常に適切なシリアル・パラレル双方向変換を行うことができる。

【0020】

請求項3に記載の発明によれば,リアルインターフェースだけを備えた機能デバイスに備えられた記憶制御手段でEPROM,Flashメモリをそのまま使用することができる。

【0021】

請求項4に記載の発明によれば,シリアル・パラレル双方向変換装置は機能デバイスに取り付けられる入出力制御装置に設けられているから,機能デバイスと入出力制御装置を組み合わせるだけで,機能デバイスからパラレルデータを取り扱う記憶手段にアクセスすることができる。

【0022】

請求項5に記載の発明によれば,機能デバイスと入出力制御装置とは同一のプリント基板内に設けられ,前記シリアル・パラレル双方向変換装置の入出力端子はプリント基板に配置される記憶手段に接続されているから,一枚のプリント基板上に機能デバイス,入出力制御装置,及び記憶手段を配置することができる

【0023】

請求項6に記載の発明によれば,機能デバイスを含むプリント基板にパラレルデータを取り扱う記憶手段を取り付けるだけで,機能デバイスは,前記記憶手段にアクセスすることができる。

【0024】

請求項7に記載の発明によれば,機能デバイスを備えたプリント基板だけでパラレルデータを取り扱う記憶手段を含む情報処理を行うことができる。

【0025】

請求項8に記載の発明によれば,情報処理装置は,パラレルデータを取り扱う記憶手段を接続することにより機能デバイスによる情報処理をおこなうことができる。

【0026】

請求項9に記載の発明によれば,情報処理装置は,それ自体で機能デバイスとパラレルデータを取り扱う記憶手段による情報処理を行うことができる。

【発明を実施するための最良の形態】

【0027】

以下,本発明を実施するための最良の形態を,図に基づいて説明する。

【実施例1】

【0028】

図1は実施の形態例に係るシリアル・パラレル双方向変換装置の構成を示すブロック図,図2は実施の形態例に係るシリアル・パラレル双方向変換装置を備えたプリント基板の構成を示すブロック図である。

【0029】

本実施例1では,シリアル・パラレル双方向変換装置200は,図2に示すように機能デバイス20を備えた情報処理装置10のプリント基板に設けられた入出力制御装置30内に設けられる。機能デバイスは公知のCPUその他の装置が使用される。

【0030】

本実施例1に係る情報処理装置10は,図2に示すように,シリアルROMインターフェース21を備えた機能デバイス20と,入出力制御装置30と,入出力制御装置30に接続されたFlashROM42とを備えている。機能デバイス20と入出力制御装置30とは,シリアル信号線22,23及び制御線24で接続され,FlashROM41は入出力制御装置30とパラレル信号線42で接続されている。

【0031】

本実施例1において,パラレル双方向変換装置200は,図1に示すように,入力されたデータ信号とアドレス信号とを含むシリアルデータ信号をパラレルデータ信号に変換するシリアル・パラレル変換回路201と,前記変換されたパラレルデータ信号からデータ信号とアドレス信号とを分離してデータ信号を前記記憶手段に入力すると共に,前記データ信号を出力するデータ・アドレス分離回路202と,前記出力されたデータ信号を前記記憶手段へのデータ信号として前記アドレス信号と関連して出力し,前記記憶手段からのパラレルデータ信号を出力すると共に,前記制御手段からの制御信号を前記記憶手段の制御信号に変換して出力するデータ制御回路204と,前記データ制御回路からのパラレルデータをシリアルデータに変換するパラレル・シリアル変換回路205と,パラレル双方向変換装置200内部の状態を取得し,前記データ制御回路に入力する状態変更手段状態変更手段である内部レジスタ206とを備える。

【0032】

本実施例1では,シリアル・パラレル変換回路201は,1ラインから経時的に伝送されるシリアル信号をパラレル信号に変更する。アドレス分離回路202は前記パラレル信号中のアドレス信号(8−12)とデータ信号を分離し,アドレス信号をアドレス線からメモリ203に出力する。また,アドレス分離回路202から出力されたデータ信号はデータ制御回路204からデータ線(8−32)を介してメモリ203に出力される。このとき,データ信号と,アドレス信号とはメモリ203が駆動可能なタイミングで出力される。

【0033】

メモリ203は,上記メモリへのデータ出力を行うほか,メモリ203からのデータ信号を受信し,パラレル・シリアル変換回路205へ出力する。パラレル・シリアル変換回路205では受け取ったパラレルデータをシリアルデータとして機能デバイス20に出力する。即ち,本実施例1では,シリアル・パラレル双方向変換装置200はシリアルROMインターフェース規約によるアドレス,データ,制御信号変換ロジック(シリアル−パラレル)を実装し,機能デバイス20から,直接メモリ203へのアクセスを実現する。

【0034】

また,内部レジスタ206はデバイス内部情報を取得してデータ制御回路204にその状態を送出する。

【0035】

次に本実施例1に係るパラレル双方向変換装置200の動作について説明する。本実施例1では,機能デバイス20がメモリ203(図2中FlashROM42に相当)に書き込む際には,アドレスと,データとを含むシリアルデータがパラレル変換回路201に入力される。パラレル変換回路201は1ラインから経時的に伝送されるシリアル信号をパラレル信号に変更し,アドレス分離回路202に送出する。アドレス分離回路202は前記パラレル信号中のアドレス信号(8−12)とデータ信号を分離し,アドレス信号をアドレス線からメモリ203に出力する。また,アドレス分離回路202から出力されたデータ信号はデータ制御回路204からデータ線(8−32)を介してメモリ203に出力される。これによりメモリ203の所定アドレスに送出されたデータが書き込まれる。

【0036】

一方,機能デバイス20が203のデータを読み出すときには,アドレスを含むシリアルデータがパラレル変換回路201に入力される。パラレル変換回路201は1ラインから経時的に伝送されるシリアル信号をパラレル信号に変更し,アドレス分離回路202に送出する。アドレス分離回路202は前記パラレル信号中のアドレス信号(8−12をアドレス線からメモリ203に出力する。これによりメモリ203の所定アドレスに送出されたデータが送出される。このデータは,パラレル・シリアル変換回路205でシリアル信号に変換され,機能デバイス20に出力される。

【0037】

以上説明したように,本実施例1によれば,シリアルROMインターフェースしか有しない機能デバイスを使用する装置であっても,係るシリアル・パラレル双方向変換装置を内蔵した入出力制御装置30を使用することで容易にEPROMやFlashメモリを利用することができる。

【図面の簡単な説明】

【0038】

【図1】実施例1に係るシリアル・パラレル双方向変換装置の構成を示すブロック図である。

【図2】実施例1に係るシリアル・パラレル双方向変換装置を備えた情報処理装置の構成を示すブロック図である。

【符号の説明】

【0039】

10 データ処理装置

20 機能デバイス

21 シリアルROMインターフェース

30 入出力制御装置(コンパニオンデバイス)

41 FlashROM

42 パラレル信号線

203 メモリ(記憶手段)

204 データ制御回路

205 パラレル・シリアル変換回路

206 内部レジスタ

【特許請求の範囲】

【請求項1】

シリアルROMインターフェース(SPIバス方式)を備えた機能デバイスと,パラレル信号で動作する記憶手段との間に配置され,

入力されたデータ信号とアドレス信号とを含むシリアルデータ信号をパラレルデータ信号に変換するシリアル・パラレル変換回路と,

前記変換されたパラレルデータ信号からデータ信号とアドレス信号とを分離してデータ信号を前記記憶手段に入力すると共に,前記データ信号を出力するデータ・アドレス分離回路と,

前記出力されたデータ信号を前記記憶手段へのデータ信号として前記アドレス信号と関連して出力し,前記記憶手段からのパラレルデータ信号を出力すると共に,前記機能デバイスからの制御信号を前記記憶手段の制御信号に変換して出力するデータ制御回路と,

前記データ制御回路からのパラレルデータをシリアルデータに変換するパラレル・シリアル変換回路とを備え,

前記記憶手段と前記機能デバイスとの間でデータの入出力を行うことを特徴とするリアル・パラレル双方向変換装置。

【請求項2】

前記シリアル・パラレル双方向変換装置には,装置内部の状態を取得し,前記データ制御回路に入力する状態変更手段を備えたことを特徴とする請求項1に記載のシリアル・パラレル双方向変換装置。

【請求項3】

前記記憶手段は,EPROMまたはFlashメモリを含むものであることを特徴とする請求項1または請求項2のいずれかに記載のシリアル・パラレル双方向変換装置。

【請求項4】

シリアル・パラレル双方向変換装置は機能デバイスに取り付けられる入出力制御装置に設けられていることを特徴とする請求項1乃至請求項3のいずれかに記載のシリアル・パラレル双方向変換装置。

【請求項5】

前記機能デバイスと入出力制御装置とは同一のプリント基板内に設けられ,前記シリアル・パラレル双方向変換装置の入出力端子はプリント基板に配置される記憶手段に接続されていることを特徴とする請求項4に記載のシリアル・パラレル双方向変換装置。

【請求項6】

機能デバイス及び請求項1乃至請求項5のいずれかに記載のシリアル・パラレル双方向変換装置を備えたことを特徴とするプリント基板。

【請求項7】

記憶手段を備えたことを特徴とする請求項6に記載のプリント基板。

【請求項8】

機能デバイスと,請求項1乃至請求項4のいずれかに記載のシリアル・パラレル双方向変換装置とを備えたことを特徴とする情報処理装置。

【請求項9】

請求項5または請求項6に記載のプリント基板を備えたことを特徴とする情報処理装置。

【請求項1】

シリアルROMインターフェース(SPIバス方式)を備えた機能デバイスと,パラレル信号で動作する記憶手段との間に配置され,

入力されたデータ信号とアドレス信号とを含むシリアルデータ信号をパラレルデータ信号に変換するシリアル・パラレル変換回路と,

前記変換されたパラレルデータ信号からデータ信号とアドレス信号とを分離してデータ信号を前記記憶手段に入力すると共に,前記データ信号を出力するデータ・アドレス分離回路と,

前記出力されたデータ信号を前記記憶手段へのデータ信号として前記アドレス信号と関連して出力し,前記記憶手段からのパラレルデータ信号を出力すると共に,前記機能デバイスからの制御信号を前記記憶手段の制御信号に変換して出力するデータ制御回路と,

前記データ制御回路からのパラレルデータをシリアルデータに変換するパラレル・シリアル変換回路とを備え,

前記記憶手段と前記機能デバイスとの間でデータの入出力を行うことを特徴とするリアル・パラレル双方向変換装置。

【請求項2】

前記シリアル・パラレル双方向変換装置には,装置内部の状態を取得し,前記データ制御回路に入力する状態変更手段を備えたことを特徴とする請求項1に記載のシリアル・パラレル双方向変換装置。

【請求項3】

前記記憶手段は,EPROMまたはFlashメモリを含むものであることを特徴とする請求項1または請求項2のいずれかに記載のシリアル・パラレル双方向変換装置。

【請求項4】

シリアル・パラレル双方向変換装置は機能デバイスに取り付けられる入出力制御装置に設けられていることを特徴とする請求項1乃至請求項3のいずれかに記載のシリアル・パラレル双方向変換装置。

【請求項5】

前記機能デバイスと入出力制御装置とは同一のプリント基板内に設けられ,前記シリアル・パラレル双方向変換装置の入出力端子はプリント基板に配置される記憶手段に接続されていることを特徴とする請求項4に記載のシリアル・パラレル双方向変換装置。

【請求項6】

機能デバイス及び請求項1乃至請求項5のいずれかに記載のシリアル・パラレル双方向変換装置を備えたことを特徴とするプリント基板。

【請求項7】

記憶手段を備えたことを特徴とする請求項6に記載のプリント基板。

【請求項8】

機能デバイスと,請求項1乃至請求項4のいずれかに記載のシリアル・パラレル双方向変換装置とを備えたことを特徴とする情報処理装置。

【請求項9】

請求項5または請求項6に記載のプリント基板を備えたことを特徴とする情報処理装置。

【図1】

【図2】

【図2】

【公開番号】特開2006−119978(P2006−119978A)

【公開日】平成18年5月11日(2006.5.11)

【国際特許分類】

【出願番号】特願2004−308167(P2004−308167)

【出願日】平成16年10月22日(2004.10.22)

【出願人】(301010700)株式会社ユーエスシー・デジアーク (3)

【Fターム(参考)】

【公開日】平成18年5月11日(2006.5.11)

【国際特許分類】

【出願日】平成16年10月22日(2004.10.22)

【出願人】(301010700)株式会社ユーエスシー・デジアーク (3)

【Fターム(参考)】

[ Back to top ]