シリコン膜の形成方法及び半導体装置の製造方法

【課題】狭スペースへのシリコン膜の埋め込み性の向上を図る。

【解決手段】実施形態によれば、シリコン膜の形成方法は、凹部20の開口側からボトム側に向けてくぼんだくぼみ40を有するアンドープの第1のシリコン膜32を凹部20に形成する工程を含む。また、前記シリコン膜の形成方法は、凹部20内の第1のシリコン膜32の一部を塩素を含むガスを用いてエッチングし、第1のシリコン膜32に凹部20のボトム側よりも開口側で幅が広い隙間41を形成する工程を含む。また、前記シリコン膜の形成方法は、隙間41に面する第1のシリコン膜32の内壁に不純物を添加する工程を含む。また、前記シリコン膜の形成方法は、不純物の添加後、隙間41を埋める第2のシリコン膜33を形成する工程を含む。

【解決手段】実施形態によれば、シリコン膜の形成方法は、凹部20の開口側からボトム側に向けてくぼんだくぼみ40を有するアンドープの第1のシリコン膜32を凹部20に形成する工程を含む。また、前記シリコン膜の形成方法は、凹部20内の第1のシリコン膜32の一部を塩素を含むガスを用いてエッチングし、第1のシリコン膜32に凹部20のボトム側よりも開口側で幅が広い隙間41を形成する工程を含む。また、前記シリコン膜の形成方法は、隙間41に面する第1のシリコン膜32の内壁に不純物を添加する工程を含む。また、前記シリコン膜の形成方法は、不純物の添加後、隙間41を埋める第2のシリコン膜33を形成する工程を含む。

【発明の詳細な説明】

【技術分野】

【0001】

本発明の実施形態は、シリコン膜の形成方法及び半導体装置の製造方法に関する。

【背景技術】

【0002】

例えば、半導体記憶装置では、隣り合う浮遊ゲートの側壁間に絶縁膜を介して制御ゲートの一部となるシリコン膜を埋め込むなど、狭スペースにシリコン膜を埋め込むプロセスが求められている。近年のメモリセルの微細化の進展により、シリコン膜を埋め込むスペース幅がますます狭くなると、シリコン膜の埋め込み性の低下によるボイドが懸念される。

【先行技術文献】

【特許文献】

【0003】

【特許文献1】特開2011−171424号公報

【特許文献2】特開2001−196573号公報

【発明の概要】

【発明が解決しようとする課題】

【0004】

本発明の実施形態は、狭スペースへのシリコン膜の埋め込み性の向上を図ったシリコン膜の形成方法及び半導体装置の製造方法を提供することを目的とする。

【課題を解決するための手段】

【0005】

実施形態によれば、シリコン膜の形成方法は、凹部の開口側からボトム側に向けてくぼんだくぼみを有するアンドープの第1のシリコン膜を、前記凹部に形成する工程を含む。また、前記シリコン膜の形成方法は、前記凹部内の前記第1のシリコン膜の一部を塩素を含むガスを用いてエッチングし、前記第1のシリコン膜に、前記凹部の前記ボトム側よりも前記開口側で幅が広い隙間を形成する工程を含む。また、前記シリコン膜の形成方法は、前記隙間に面する前記第1のシリコン膜の内壁に、不純物を添加する工程を含む。また、前記シリコン膜の形成方法は、前記不純物の添加後、前記隙間を埋める第2のシリコン膜を形成する工程を含む。

【図面の簡単な説明】

【0006】

【図1】(a)は実施形態の半導体装置におけるアクティブ領域とスタックゲート構造のレイアウトを表す模式平面図であり、(b)は(a)におけるA−A断面に対応する模式断面図。

【図2】図1(a)におけるB−B断面に対応する部分の一部拡大模式断面図。

【図3】実施形態の半導体装置の製造方法を示す模式断面図。

【図4】実施形態の半導体装置の製造方法を示す模式断面図。

【図5】(a)は実施形態のシリコン膜の成膜シーケンス図であり、(b)は(a)に示す成膜シーケンスの各ステップで処理室内に導入されるガスの切り替えタイミングチャート。

【図6】実施形態のシリコン膜と、比較例のシリコン膜との、リン(P)の深さ方向の濃度分布図。

【図7】(a)は実施形態のシリコン膜を有するキャパシタと、比較例のシリコン膜を有するキャパシタとのCV特性図であり、(b)は実施形態のシリコン膜を有するメモリセルと比較例のシリコン膜を有するメモリセルとの書き込み電圧分布図。

【発明を実施するための形態】

【0007】

以下、図面を参照し、実施形態について説明する。なお、各図面中、同じ要素には同じ符号を付している。

【0008】

実施形態では、半導体装置として、例えば、浮遊ゲートと制御ゲートとを含むスタックゲート構造を有する不揮発性半導体記憶装置を一例に挙げて説明する。

【0009】

図1(a)は、実施形態の半導体装置におけるアクティブ領域11とスタックゲート構造のレイアウトを表す模式平面図である。

図1(b)は、図1(a)におけるA−A断面に対応する模式断面図である。

図2は、図1(a)におけるB−B断面に対応する部分の一部拡大模式断面図である。

【0010】

図1(b)は、半導体基板10の表面付近の断面を表す。半導体基板10の表面側にはアクティブ領域11が形成されている。アクティブ領域11は、図示しない第1導電型のチャネル領域、第2導電型のソース領域及びドレイン領域を有する。

【0011】

アクティブ領域11は、第1の方向Xに延びている。また、図1(a)に示すように、複数のアクティブ領域11が、第1の方向Xに対して直交する第2の方向Yに並んで形成されている。

【0012】

図2に示すように、第2の方向Yで隣り合うアクティブ領域11どうしは、例えばSTI(Shallow Trench Isolation)構造によって分離されている。すなわち、第2の方向Yで隣り合うアクティブ領域11間にはトレンチが形成され、そのトレンチ内に例えばシリコン酸化物等の絶縁体14が埋め込まれている。

【0013】

アクティブ領域11上には、トンネル絶縁膜12が設けられている。トンネル絶縁膜12は、図1(b)に示すように第1の方向Xに延び、また、図2に示すように第2の方向Yに複数に分断されている。

【0014】

トンネル絶縁膜12上には、第1の電極として複数の浮遊ゲートFGが設けられている。複数の浮遊ゲートFGは、図1(b)に示すように、第1の方向Xに分断されている。また、複数の浮遊ゲートFGは、図2に示すように、第2の方向Yにも分断されている。

【0015】

浮遊ゲートFGの上には、電極間絶縁膜13が設けられている。電極間絶縁膜13は、図1(b)に示すように、第1の方向Xに複数に分断されている。また、電極間絶縁膜13は、図2に示すように、第2の方向Yには分断されず、第2の方向Yにつながっている。

【0016】

さらに、浮遊ゲートFGにおいて、第2の方向Yで隣り合う他の浮遊ゲートFGに対向する側壁の一部にも、電極間絶縁膜13が設けられている。

【0017】

電極間絶縁膜13上には、第2の電極として制御ゲートCGが設けられている。制御ゲートCGは、図1(b)に示すように、第1の方向Xに複数に分断されている。また、制御ゲートCGは、図2に示すように、第2の方向Yには分断されず、第2の方向Yにつながっている。

【0018】

図2に示すように、第2の方向Yで隣り合う浮遊ゲートFGの対向側壁間には凹部20が設けられ、その凹部20の内壁に沿ってコンフォーマルに電極間絶縁膜13が設けられている。

【0019】

そして、制御ゲートCGの一部は、凹部20内における電極間絶縁膜13の内側に埋め込まれている。このように、電極間絶縁膜13及び制御ゲートCGを、浮遊ゲートFG上にだけでなく側壁にも設けることで、電極間絶縁膜13を介した浮遊ゲートFGと制御ゲートCG間の容量を大きくできる。この結果、書き込み電圧の低電圧化を図れる。

【0020】

浮遊ゲートFGは、図1(a)の平面視にて制御ゲートCGとアクティブ領域11との交差部に設けられている。すなわち、半導体基板10上に、複数のメモリセルMCがマトリクス状にレイアウトされている。図1(b)では図示を省略しているが、第1の方向Xで隣り合う浮遊ゲートFG間には、絶縁層が設けられている。したがって、1つのメモリセルMCは、そのまわりが絶縁された1つの浮遊ゲートFGを含む。

【0021】

すなわち、浮遊ゲートFGは、導電部分には直接接続されていない。そのため、電源を切っても、浮遊ゲートFG内に蓄積された電子は浮遊ゲートFGから漏れ出さず、また新たに入ることもない。

【0022】

次に、実施形態の半導体装置の製造方法について説明する。実施形態では、制御ゲートCGとしてシリコン膜を用いており、そのシリコン膜の形成方法を中心に製造方法を以下に説明する。

【0023】

アクティブ領域11上に、トンネル絶縁膜12と、浮遊ゲートFGとなる不純物を含むシリコン膜を積層した後、図示しないマスクを用いたエッチング加工により、アクティブ領域11、トンネル絶縁膜12及び浮遊ゲートFGの積層体は、図2に示すように第2の方向Yに複数に分断される。

【0024】

第2の方向Yで隣り合う上記積層体間には絶縁体14が埋め込まれる。その後、絶縁体14の上面側がエッチングされ、第2の方向Yで隣り合う浮遊ゲートFG間に、図3(a)に示すように凹部20が形成される。凹部20のボトムは、浮遊ゲートFGとトンネル絶縁膜12との界面よりも上方の浮遊ゲートFG側に位置する。

【0025】

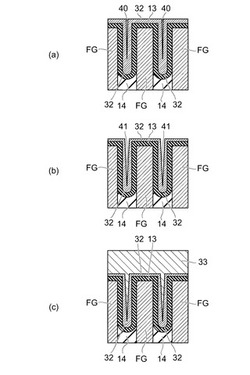

図3(a)〜図4(c)は、制御ゲートCGとなるシリコン膜の形成方法を示す模式断面図である。図3(a)〜図4(c)は、図2におけるトンネル絶縁膜12よりも上の部分の断面を表す。

【0026】

浮遊ゲートFG間の凹部20および浮遊ゲートFG上には、図3(b)に示すように、コンフォーマルに電極間絶縁膜13が形成される。

【0027】

以降、制御ゲートCGとなるシリコン膜の形成が続けられる。

【0028】

シリコン膜の成膜対象物を含むウェーハが処理室(または反応炉)内に収容され、所望の温度に加熱される。また、処理室内には、減圧下で各種ガスが導入される。

【0029】

図5(a)は、実施形態によるシリコン膜の成膜シーケンス図である。図5(a)における横軸は時間を、縦軸はウェーハ温度(以下、単に温度とも称する)を表す。

【0030】

また、図5(b)は、図5(a)に示す成膜シーケンスの各ステップで処理室内に導入されるガスの切り替えタイミングチャートである。

【0031】

まず、例えば、温度を400℃、処理室内圧力を1Torrに設定して、ジシラン(Si2H6)ガスを200ccの流量で処理室内に導入する。この処理を、例えば約10分間続ける。

【0032】

これにより、図3(c)に示すように、電極間絶縁膜13の表面に沿ってコンフォーマルに、シリコンを含むシード膜31が形成される。すなわち、シード膜31は、凹部20内の電極間絶縁膜13の内側、および浮遊ゲートFG上の電極間絶縁膜13の上面上に形成される。シード膜31は、例えば非晶質シリコン膜である。

【0033】

ジシランを原料ガス(第1の原料ガス)として用いたシード膜31の成膜時の温度(例えば400℃)では、例えばホスフィン(PH3)は分解しない。したがって、シード膜31の成膜時、シード膜31に導電性を付与する例えばリン(P)などの不純物ソースは導入せず、シード膜31はアンドープである。

【0034】

本明細書において、アンドープとは、シリコン膜に導電性を付与する不純物が意図的に添加されず、シリコン膜は成膜時のガスに起因する元素以外に、実質的に不純物を含まないことを表す。

【0035】

シード膜31の膜厚は、例えば1〜2nmである。また、シード膜31を形成するための第1の原料ガスとしては、ジシランに限らず、トリシラン、あるいはジイソプロピルアミノシランなどのアミノ基を持つガスを用いてもよい。

【0036】

シリコン膜は成膜初期に島状成長のため表面に凹凸が生じやすい。しかしながら、上記ジシランなどのガスを用いて形成されるシリコン膜であるシード膜31は、シラン(SiH4)ガスを用いて形成されるシリコン膜よりも、シリコンの凝集を抑制して表面粗さを小さくでき、表面の平坦性に優れる。したがって、凹部20内にボイドを残して、シード膜31が凹部20の一部を閉塞してしまうことがない。

【0037】

シード膜31の形成後、引き続き、ウェーハを処理室から出さず、処理室内に導入するガスを第1の原料ガスから水素ガス(H2ガス)に切り替え、さらに、ウェーハ温度を例えば520℃ほどに上げる。水素ガスの流量は、例えば1000ccに設定される。この昇温処理を、例えば約30分間続ける。

【0038】

ここで、水素を含まない雰囲気中でシード膜31を昇温すると、シリコンに結合していた、原料ガスに由来する水素がシリコンから離脱し、その水素が離脱したシリコンどうしの距離が短くなり、シリコンが凝集するおそれがある。このため、水素を含まない雰囲気中でシード膜31を昇温すると、昇温後のシード膜31の表面の平坦性は昇温前よりも低下する傾向にある。

【0039】

これに対し、実施形態のように、水素を含む雰囲気中でシード膜31を昇温すると、シリコンに結合している水素の離脱が抑制される。このため、昇温中におけるシード膜31のシリコンの凝集が抑制でき、シード膜31の表面平坦性はそのまま維持される。

【0040】

水素ガス雰囲気中での昇温ステップの後、引き続き、ウェーハを処理室から出さず、処理室内に導入するガスを水素ガスからシランガス(第2の原料ガス)に切り替える。例えば、処理室内圧力は0.56Torrに設定し、シランガスの流量は、例えば800ccに設定される。温度は約520℃に維持される。この処理を、例えば約3分間続ける。

【0041】

これにより、シード膜31の表面に、図4(a)に示す第1のシリコン膜32が形成される。すなわち、凹部20内におけるシード膜31の内側、およびシード膜31の上面上に、第1のシリコン膜32が形成される。

【0042】

第1のシリコン膜32は、シード膜31と同様、アンドープで非晶質のシリコン膜である。したがって、図4(a)以降の図においては、シード膜31は第1のシリコン膜32と区別せずに、第1のシリコン膜32に包含させて図示している。

【0043】

凹部20の側壁に形成された電極間絶縁膜13間の上端側の開口幅(図3(b)におけるa)は、例えば8nmである。第1のシリコン膜32の膜厚は、その開口幅aの半分よりも小さい膜厚に制御される。

【0044】

したがって、凹部20は第1のシリコン膜32で完全に埋まらず、第1のシリコン膜32には、図4(a)に示すように、凹部20の開口側からボトム側に向けてくぼんだくぼみ40が形成される。すなわち、第1のシリコン膜32は、凹部20の直上で平坦になっていない。

【0045】

くぼみ40が凹部20のボトム側に入り込んでいる深さは、図4(a)で表す位置に限らず、第1のシリコン膜32の膜厚等によって変わる。

【0046】

第1のシリコン膜32を形成するときの第2の原料ガスには、シード膜31を形成するときの第1の原料ガスとは異なり、シランガスが用いられる。

【0047】

第1の原料ガスとしては、前述したようにシリコン膜の成膜初期の島状成長を抑制するため、ジシランなどが用いられる。一方、第2の原料ガスであるシランを用いて形成されたシリコン膜は、ジシランなどの第1の原料ガスを用いて形成されたシリコン膜に比べて、ウェーハ面内の膜厚均一性及び埋め込み性に優れ、また成膜レートも高い。

【0048】

したがって、シード膜31は、表面平坦性を確保するための下地として薄い(例えば1〜2nmの)膜厚にとどめ、その後は、シランガスを用いて凹部20内に第1のシリコン膜32を形成することで、ジシランなどの第1の原料ガスに起因する良好な表面平坦性を得つつ、第2の原料ガス(シランガス)に起因する良好なステップカバレッジ及び高い生産性を実現できる。

【0049】

第1のシリコン膜32の形成後、引き続き、ウェーハを処理室から出さず、処理室内に導入するガスを第2の原料ガスから水素ガスに切り替え、さらに、ウェーハ温度を例えば300℃程度に降温する。水素ガスの流量は、例えば1000ccに設定される。この処理を、例えば約40分間続ける。

【0050】

水素ガス雰囲気中での降温ステップの後、引き続き、ウェーハを処理室から出さず、処理室内に導入するガスを水素ガスから塩素を含むエッチングガスに切り替えて、第1のシリコン膜32の一部をエッチングする。例えば、処理室内圧力は0.3Torrに設定され、温度は約300℃に維持される。

【0051】

このエッチング処理で処理室内には、例えば、塩素ガス(Cl2ガス)が500ccの流量で導入され、さらに窒素ガス(N2ガス)が800ccの流量で導入される。このエッチング処理を、例えば約15分間続ける。

【0052】

第1のシリコン膜32は、主に塩素の作用によりエッチングされる。図4(a)に示すエッチング前の状態で、第1のシリコン膜32にはくぼみ40が形成されている。そのくぼみ40の幅を広げるようにエッチングが進み、図4(b)に示すように、電極間絶縁膜13に沿うようにコンフォーマルに第1のシリコン膜32が残され、その内側に隙間41が形成される。隙間41の幅は、凹部20のボトム側よりも開口側で広い。

【0053】

エッチング前の状態で、第1のシリコン膜32が凹部20を完全に埋め込んで、凹部20の直上部分で平坦になっていると、凹部20内の第1のシリコン膜32の幅方向の全体が均一にエッチバックされてしまい、図4(b)に示すようなボトム側よりも開口側で幅が広い隙間41は形成されない。

【0054】

実施形態のように、エッチング前の状態で、第1のシリコン膜32に、図4(a)に示すくぼみ40があると、そのくぼみ40にエッチングガスが入り込み、くぼみ40を幅方向に広げつつエッチングが進む。

【0055】

そして、エッチングガスが侵入しにくいくぼみ40のボトム側よりも、エッチングガス濃度が高くなるウェーハ表面側でエッチングが促進される。このため、図4(b)に示すように、ボトム側よりも開口側で幅が広がった隙間41が形成される。隙間41に面する第1のシリコン膜32の側壁は、断面V字状のテーパー形状にされる。したがって、後述する第2のシリコン膜33を、ボイドを生じさせることなく、隙間41に埋め込みやすくできる。

【0056】

このエッチングは、アンドープの非晶質シリコン膜である第1のシリコン膜32に対して行われる。アンドープの非晶質シリコン膜に対して、例えば300℃で、Cl2ガスを使うと、エッチングレートを1オングストローム/分程度に制御することができる。これにより、凹部20のボトムと側壁に第1のシリコン膜32を残しつつ、図4(b)に示す形状の隙間41を制御性よく形成することができる。

【0057】

非晶質のシリコン膜に、不純物として例えばリンが少しでも添加されると、アンドープ非晶質シリコン膜に比べてエッチングレートが100〜1000倍に上がってしまい、凹部20内のシリコン膜のほとんどが短時間で除去され、図4(b)に示す形状の隙間41の形成が困難になる。

【0058】

第1のシリコン膜32のエッチング後、引き続き、ウェーハを処理室から出さず、処理室内に導入するガスを塩素を含むエッチングガスから不純物を含むドーパントガスに切り替え、例えば300℃から520℃に昇温する。処理室内圧力は、例えば4Torrに設定される。

【0059】

ドーパントガスとして、例えばリン(P)を含むホスフィン(PH3)ガスが用いられる。さらに具体的には、ヘリウムガスに1vol%の濃度でホスフィンガスを含む希釈ホスフィンガスが用いられ、この希釈ホスフィンガスは、例えば1000ccの流量で処理室内に導入される。例えば、約30分かけて300℃から520℃に昇温された後、約10分間、520℃の温度が維持される。

【0060】

すなわち、第1のシリコン膜32は、リンを含むガス雰囲気中で熱処理される。これにより、隙間41に面する第1のシリコン膜32の内壁(側壁及び底部)に、第1のシリコン膜32に導電性を付与する不純物としてリンが添加(ドーピング)される。

【0061】

ドーパントガスとしては、ホスフィンガスに限らず、アルシン(AsH3)ガス、ジボラン(B2H6)ガス、三塩化ボロン(BCl3)ガスなどを用いることもできる。

【0062】

第1のシリコン膜32への不純物ドーピングの後、引き続き、ウェーハを処理室から出さず、処理室内に導入するガスをドーパントガスから、シラン及びドーパントガスを含むガスに切り替える。例えば、処理室内圧力は0.56Torrに設定され、温度は約520℃に維持される。シランガスは、例えば800ccの流量で処理室内に導入される。ドーパントガスとしては、例えば前ステップと同じガスが90ccの流量で処理室内に導入される。この成膜処理を、例えば約20分間続ける。

【0063】

これにより、隙間41内、および浮遊ゲートFG上の第1のシリコン膜32上に、図4(c)に示すように、第2のシリコン膜33が形成される。第2のシリコン膜33は、不純物として例えばリンを含む非晶質シリコン膜である。

【0064】

あるいは、第2のシリコン膜33の成膜時に不純物をドーピングせず、アンドープの第2のシリコン膜33を形成した後、そのアンドープの第2のシリコン膜33に不純物をドーピングして、第2のシリコン膜33に導電性を与えてもよい。

【0065】

いずれも非晶質状態で成膜された第1のシリコン膜32及び第2のシリコン膜33は、最終的には、熱処理により結晶化され、多結晶シリコン膜となる。これら多結晶シリコン膜である第1のシリコン膜32及び第2のシリコン膜33は、前述した半導体記憶装置における制御ゲートCGとして機能する。

【0066】

前述した第1のシリコン膜32に対するエッチング及び不純物ドーピングは、第1のシリコン膜32を結晶化させる熱処理の温度よりも低い温度下で行われる。これにより、第1のシリコン膜32に対するエッチング中及び不純物ドーピング中、第1のシリコン膜32の非晶質状態を維持することができる。非晶質シリコン膜は、多結晶シリコン膜よりも表面粗さが小さいため、上記エッチング中及び不純物ドーピング中に第1のシリコン膜32の表面平坦性の低下をまねかない。

【0067】

ここで、実施形態とは異なるステップにより、制御ゲートCGとなるシリコン膜を形成する技術を比較例として挙げる。

【0068】

この比較例では、ジシランを用いてシード膜31を形成し、その後水素雰囲気中で昇温する工程までは、実施形態と同じであるが、それ以降の工程が実施形態と異なる。

【0069】

すなわち、比較例では、水素雰囲気中で520℃まで昇温した後、その温度下で、シランガスとドーパントガスを用いて残りのシリコン膜を形成する。このシリコン膜形成時の条件は、実施形態における第2のシリコン膜33を形成するときの条件と同じである。

【0070】

近年、メモリデバイスの微細化が進み、図3(b)に示す幅aが10nm以下になってきている。ここまで狭くなると、成膜初期にジシランで表面平坦性のよいシード膜31を形成しても、凹部20の局所的な閉塞が発生しやすくなる。また、凹部20の幅が狭くなるのにともない、シリコン膜を埋め込む部分に露出する電極間絶縁膜13の側壁が、基板に対して垂直になる傾向にあり、さらにはボトム側よりも開口側で凹部20の幅が狭くなるオーバーハング形状になる傾向にもある。このようなことから、比較例の技術では、凹部20内にボイドを生じさせることなくシリコン膜を埋め込むことが困難になりつつある。

【0071】

これに対して、実施形態によれば、シード膜31を形成した後、凹部20内を一度にシリコン膜で埋め込まず、第1のシリコン膜32の形成、第1のシリコン膜32のエッチング、そして第2のシリコン膜33の形成というステップにより、凹部20内にシリコン膜を埋め込んでいる。

【0072】

すなわち、第1のシリコン膜32を形成した後、第1のシリコン膜32に、図4(b)に示す隙間41を形成する。隙間41は、凹部20のボトム側よりも開口側で幅が広くなっており、深くなるほど漸次細くなるテーパー形状に形成されている。したがって、その隙間41にボイド(空隙)を生じさせることなく、第2のシリコン膜33を埋め込むことができる。

【0073】

また、アンドープの第1のシリコン膜32をエッチング対象とすることで、エッチング制御性を高めることができる。これにより、微小幅の凹部20内に、確実にテーパーをもたせて微小隙間41を形成することが可能になる。

【0074】

電極間絶縁膜13形成後の凹部20の開口幅a(図3(b)参照)が8nm、その開口付近における電極間絶縁膜13の上面から側壁にかけての角部の角度が89°の場合に、実施形態によれば、上記比較例に比べて、凹部20にシリコン膜を埋め込んだ後に生じたボイドの数を1/3以下に減少させることができた。

【0075】

また、ジシランを用いたシード膜31の成膜時の温度では、例えばホスフィンガスは分解せず、よってシード膜31に不純物をドープすることが困難である。また、シード膜31の形成後に、ドーパントガスを含む雰囲気でシリコン膜を形成しても、そのシリコン膜の成膜初期の段階で、所望の温度にまだ安定せずドーパントガスの分解が不十分な状態で、シリコン膜が凹部20内に埋め込まれてしまうことがある。凹部20に埋め込まれたシリコン膜の導電性が不十分であると、浮遊ゲートFG間のシリコン膜が空乏化し、制御ゲートCGとして機能しない。

【0076】

実施形態によれば、凹部20内を完全に埋め込む前に、図4(b)の状態で、例えばホスフィンガスを含む雰囲気中で熱処理する。このとき、シリコン膜の原料ガスは処理室内に導入されない。したがって、隙間41は閉塞されず、隙間41にホスフィンガスを侵入させることができ、隙間41に面する第1のシリコン膜32の側壁を通じて、凹部20内の第1のシリコン膜32に不純物としてリンを確実にドーピングすることができる。この結果、浮遊ゲートFG間のシリコン膜の空乏化を抑制することができる。

【0077】

図6は、実施形態のステップで形成したシリコン膜と、上記比較例のステップで形成したシリコン膜との、リン(P)の深さ方向の濃度分布図である。

【0078】

実施形態及び比較例ともに、シード膜31を形成した後のステップで形成した非晶質シリコン膜中のSIMS(Secondary Ion-microprobe Mass Spectrometer)分析によるP濃度を表す。横軸はシリコン膜の表面からの深さ(nm)を表し、縦軸はP濃度(atoms/cm3)を表す。

【0079】

比較例の方法では、40nm付近の深い位置に、すなわち成膜初期の段階でPが高濃度にドーピングされなかった。これに対して、実施形態によれば、凹部20が完全に埋め込まれる前にシリコン膜の成膜を一旦停止して制御性に優れたエッチングにより隙間41を形成した後、ホスフィンガスによる熱処理を行うことで、40nm付近の深い位置でのP濃度を比較例よりも高濃度にできた。

【0080】

図7(a)は、凹部20の下部における浮遊ゲートFGと、電極間絶縁膜13と、その電極間絶縁膜13の内側に実施形態による方法で形成されたシリコン膜とからなる実施形態のキャパシタの容量電圧特性(CV特性)と、凹部20の下部における浮遊ゲートFGと、電極間絶縁膜13と、その電極間絶縁膜13の内側に上記比較例による方法で形成されたシリコン膜とからなる比較例のキャパシタの容量電圧特性(CV特性)と、を表す。

【0081】

比較例では、凹部20の下部におけるボイド(空隙)あるいはシリコン膜中の不純物不足により、シリコン膜に印加する正電圧を高くするとシリコン膜中を空乏層が伸び、容量が低下するのに対し、実施形態では空乏層がほとんど伸びず、容量低下をまねかない。

【0082】

図7(b)は、実施形態による方法で形成されたシリコン膜を制御ゲートCGとして有するメモリセルと、比較例による方法で形成されたシリコン膜を制御ゲートCGとして有するメモリセルとの書き込み電圧分布図である。

【0083】

縦軸はビット数を表し、横軸は、メモリセルを所定のしきい値にするために制御ゲートCGに印加される書き込み電圧Vpgmを表す。

【0084】

実施形態によれば、比較例に比べて、書き込み電圧Vpgmを下げることができ、また書き込み電圧Vpgmのばらつきも大きく低減できる。

【0085】

第1のシリコン膜32の成膜及びその一部のエッチングは複数回繰り返してもよい。それらステップを複数回繰り返すと、隙間41のテーパー角(隙間41に面する第1のシリコン膜32の側壁の傾斜)をよりゆるやかにして、第2のシリコン膜33をより埋めやすくなる場合がある。

【0086】

本発明のいくつかの実施形態を説明したが、これらの実施形態は、例として提示したものであり、発明の範囲を限定することは意図していない。これら新規な実施形態は、その他の様々な形態で実施されることが可能であり、発明の要旨を逸脱しない範囲で、種々の省略、置き換え、変更を行うことができる。これら実施形態やその変形は、発明の範囲や要旨に含まれるとともに、特許請求の範囲に記載された発明とその均等の範囲に含まれる。

【符号の説明】

【0087】

11…アクティブ領域、12…トンネル絶縁膜、13…電極間絶縁膜、20…凹部、31…シード膜、32…第1のシリコン膜、33…第2のシリコン膜、40…くぼみ、41…隙間、FG…浮遊ゲート、CG…制御ゲート

【技術分野】

【0001】

本発明の実施形態は、シリコン膜の形成方法及び半導体装置の製造方法に関する。

【背景技術】

【0002】

例えば、半導体記憶装置では、隣り合う浮遊ゲートの側壁間に絶縁膜を介して制御ゲートの一部となるシリコン膜を埋め込むなど、狭スペースにシリコン膜を埋め込むプロセスが求められている。近年のメモリセルの微細化の進展により、シリコン膜を埋め込むスペース幅がますます狭くなると、シリコン膜の埋め込み性の低下によるボイドが懸念される。

【先行技術文献】

【特許文献】

【0003】

【特許文献1】特開2011−171424号公報

【特許文献2】特開2001−196573号公報

【発明の概要】

【発明が解決しようとする課題】

【0004】

本発明の実施形態は、狭スペースへのシリコン膜の埋め込み性の向上を図ったシリコン膜の形成方法及び半導体装置の製造方法を提供することを目的とする。

【課題を解決するための手段】

【0005】

実施形態によれば、シリコン膜の形成方法は、凹部の開口側からボトム側に向けてくぼんだくぼみを有するアンドープの第1のシリコン膜を、前記凹部に形成する工程を含む。また、前記シリコン膜の形成方法は、前記凹部内の前記第1のシリコン膜の一部を塩素を含むガスを用いてエッチングし、前記第1のシリコン膜に、前記凹部の前記ボトム側よりも前記開口側で幅が広い隙間を形成する工程を含む。また、前記シリコン膜の形成方法は、前記隙間に面する前記第1のシリコン膜の内壁に、不純物を添加する工程を含む。また、前記シリコン膜の形成方法は、前記不純物の添加後、前記隙間を埋める第2のシリコン膜を形成する工程を含む。

【図面の簡単な説明】

【0006】

【図1】(a)は実施形態の半導体装置におけるアクティブ領域とスタックゲート構造のレイアウトを表す模式平面図であり、(b)は(a)におけるA−A断面に対応する模式断面図。

【図2】図1(a)におけるB−B断面に対応する部分の一部拡大模式断面図。

【図3】実施形態の半導体装置の製造方法を示す模式断面図。

【図4】実施形態の半導体装置の製造方法を示す模式断面図。

【図5】(a)は実施形態のシリコン膜の成膜シーケンス図であり、(b)は(a)に示す成膜シーケンスの各ステップで処理室内に導入されるガスの切り替えタイミングチャート。

【図6】実施形態のシリコン膜と、比較例のシリコン膜との、リン(P)の深さ方向の濃度分布図。

【図7】(a)は実施形態のシリコン膜を有するキャパシタと、比較例のシリコン膜を有するキャパシタとのCV特性図であり、(b)は実施形態のシリコン膜を有するメモリセルと比較例のシリコン膜を有するメモリセルとの書き込み電圧分布図。

【発明を実施するための形態】

【0007】

以下、図面を参照し、実施形態について説明する。なお、各図面中、同じ要素には同じ符号を付している。

【0008】

実施形態では、半導体装置として、例えば、浮遊ゲートと制御ゲートとを含むスタックゲート構造を有する不揮発性半導体記憶装置を一例に挙げて説明する。

【0009】

図1(a)は、実施形態の半導体装置におけるアクティブ領域11とスタックゲート構造のレイアウトを表す模式平面図である。

図1(b)は、図1(a)におけるA−A断面に対応する模式断面図である。

図2は、図1(a)におけるB−B断面に対応する部分の一部拡大模式断面図である。

【0010】

図1(b)は、半導体基板10の表面付近の断面を表す。半導体基板10の表面側にはアクティブ領域11が形成されている。アクティブ領域11は、図示しない第1導電型のチャネル領域、第2導電型のソース領域及びドレイン領域を有する。

【0011】

アクティブ領域11は、第1の方向Xに延びている。また、図1(a)に示すように、複数のアクティブ領域11が、第1の方向Xに対して直交する第2の方向Yに並んで形成されている。

【0012】

図2に示すように、第2の方向Yで隣り合うアクティブ領域11どうしは、例えばSTI(Shallow Trench Isolation)構造によって分離されている。すなわち、第2の方向Yで隣り合うアクティブ領域11間にはトレンチが形成され、そのトレンチ内に例えばシリコン酸化物等の絶縁体14が埋め込まれている。

【0013】

アクティブ領域11上には、トンネル絶縁膜12が設けられている。トンネル絶縁膜12は、図1(b)に示すように第1の方向Xに延び、また、図2に示すように第2の方向Yに複数に分断されている。

【0014】

トンネル絶縁膜12上には、第1の電極として複数の浮遊ゲートFGが設けられている。複数の浮遊ゲートFGは、図1(b)に示すように、第1の方向Xに分断されている。また、複数の浮遊ゲートFGは、図2に示すように、第2の方向Yにも分断されている。

【0015】

浮遊ゲートFGの上には、電極間絶縁膜13が設けられている。電極間絶縁膜13は、図1(b)に示すように、第1の方向Xに複数に分断されている。また、電極間絶縁膜13は、図2に示すように、第2の方向Yには分断されず、第2の方向Yにつながっている。

【0016】

さらに、浮遊ゲートFGにおいて、第2の方向Yで隣り合う他の浮遊ゲートFGに対向する側壁の一部にも、電極間絶縁膜13が設けられている。

【0017】

電極間絶縁膜13上には、第2の電極として制御ゲートCGが設けられている。制御ゲートCGは、図1(b)に示すように、第1の方向Xに複数に分断されている。また、制御ゲートCGは、図2に示すように、第2の方向Yには分断されず、第2の方向Yにつながっている。

【0018】

図2に示すように、第2の方向Yで隣り合う浮遊ゲートFGの対向側壁間には凹部20が設けられ、その凹部20の内壁に沿ってコンフォーマルに電極間絶縁膜13が設けられている。

【0019】

そして、制御ゲートCGの一部は、凹部20内における電極間絶縁膜13の内側に埋め込まれている。このように、電極間絶縁膜13及び制御ゲートCGを、浮遊ゲートFG上にだけでなく側壁にも設けることで、電極間絶縁膜13を介した浮遊ゲートFGと制御ゲートCG間の容量を大きくできる。この結果、書き込み電圧の低電圧化を図れる。

【0020】

浮遊ゲートFGは、図1(a)の平面視にて制御ゲートCGとアクティブ領域11との交差部に設けられている。すなわち、半導体基板10上に、複数のメモリセルMCがマトリクス状にレイアウトされている。図1(b)では図示を省略しているが、第1の方向Xで隣り合う浮遊ゲートFG間には、絶縁層が設けられている。したがって、1つのメモリセルMCは、そのまわりが絶縁された1つの浮遊ゲートFGを含む。

【0021】

すなわち、浮遊ゲートFGは、導電部分には直接接続されていない。そのため、電源を切っても、浮遊ゲートFG内に蓄積された電子は浮遊ゲートFGから漏れ出さず、また新たに入ることもない。

【0022】

次に、実施形態の半導体装置の製造方法について説明する。実施形態では、制御ゲートCGとしてシリコン膜を用いており、そのシリコン膜の形成方法を中心に製造方法を以下に説明する。

【0023】

アクティブ領域11上に、トンネル絶縁膜12と、浮遊ゲートFGとなる不純物を含むシリコン膜を積層した後、図示しないマスクを用いたエッチング加工により、アクティブ領域11、トンネル絶縁膜12及び浮遊ゲートFGの積層体は、図2に示すように第2の方向Yに複数に分断される。

【0024】

第2の方向Yで隣り合う上記積層体間には絶縁体14が埋め込まれる。その後、絶縁体14の上面側がエッチングされ、第2の方向Yで隣り合う浮遊ゲートFG間に、図3(a)に示すように凹部20が形成される。凹部20のボトムは、浮遊ゲートFGとトンネル絶縁膜12との界面よりも上方の浮遊ゲートFG側に位置する。

【0025】

図3(a)〜図4(c)は、制御ゲートCGとなるシリコン膜の形成方法を示す模式断面図である。図3(a)〜図4(c)は、図2におけるトンネル絶縁膜12よりも上の部分の断面を表す。

【0026】

浮遊ゲートFG間の凹部20および浮遊ゲートFG上には、図3(b)に示すように、コンフォーマルに電極間絶縁膜13が形成される。

【0027】

以降、制御ゲートCGとなるシリコン膜の形成が続けられる。

【0028】

シリコン膜の成膜対象物を含むウェーハが処理室(または反応炉)内に収容され、所望の温度に加熱される。また、処理室内には、減圧下で各種ガスが導入される。

【0029】

図5(a)は、実施形態によるシリコン膜の成膜シーケンス図である。図5(a)における横軸は時間を、縦軸はウェーハ温度(以下、単に温度とも称する)を表す。

【0030】

また、図5(b)は、図5(a)に示す成膜シーケンスの各ステップで処理室内に導入されるガスの切り替えタイミングチャートである。

【0031】

まず、例えば、温度を400℃、処理室内圧力を1Torrに設定して、ジシラン(Si2H6)ガスを200ccの流量で処理室内に導入する。この処理を、例えば約10分間続ける。

【0032】

これにより、図3(c)に示すように、電極間絶縁膜13の表面に沿ってコンフォーマルに、シリコンを含むシード膜31が形成される。すなわち、シード膜31は、凹部20内の電極間絶縁膜13の内側、および浮遊ゲートFG上の電極間絶縁膜13の上面上に形成される。シード膜31は、例えば非晶質シリコン膜である。

【0033】

ジシランを原料ガス(第1の原料ガス)として用いたシード膜31の成膜時の温度(例えば400℃)では、例えばホスフィン(PH3)は分解しない。したがって、シード膜31の成膜時、シード膜31に導電性を付与する例えばリン(P)などの不純物ソースは導入せず、シード膜31はアンドープである。

【0034】

本明細書において、アンドープとは、シリコン膜に導電性を付与する不純物が意図的に添加されず、シリコン膜は成膜時のガスに起因する元素以外に、実質的に不純物を含まないことを表す。

【0035】

シード膜31の膜厚は、例えば1〜2nmである。また、シード膜31を形成するための第1の原料ガスとしては、ジシランに限らず、トリシラン、あるいはジイソプロピルアミノシランなどのアミノ基を持つガスを用いてもよい。

【0036】

シリコン膜は成膜初期に島状成長のため表面に凹凸が生じやすい。しかしながら、上記ジシランなどのガスを用いて形成されるシリコン膜であるシード膜31は、シラン(SiH4)ガスを用いて形成されるシリコン膜よりも、シリコンの凝集を抑制して表面粗さを小さくでき、表面の平坦性に優れる。したがって、凹部20内にボイドを残して、シード膜31が凹部20の一部を閉塞してしまうことがない。

【0037】

シード膜31の形成後、引き続き、ウェーハを処理室から出さず、処理室内に導入するガスを第1の原料ガスから水素ガス(H2ガス)に切り替え、さらに、ウェーハ温度を例えば520℃ほどに上げる。水素ガスの流量は、例えば1000ccに設定される。この昇温処理を、例えば約30分間続ける。

【0038】

ここで、水素を含まない雰囲気中でシード膜31を昇温すると、シリコンに結合していた、原料ガスに由来する水素がシリコンから離脱し、その水素が離脱したシリコンどうしの距離が短くなり、シリコンが凝集するおそれがある。このため、水素を含まない雰囲気中でシード膜31を昇温すると、昇温後のシード膜31の表面の平坦性は昇温前よりも低下する傾向にある。

【0039】

これに対し、実施形態のように、水素を含む雰囲気中でシード膜31を昇温すると、シリコンに結合している水素の離脱が抑制される。このため、昇温中におけるシード膜31のシリコンの凝集が抑制でき、シード膜31の表面平坦性はそのまま維持される。

【0040】

水素ガス雰囲気中での昇温ステップの後、引き続き、ウェーハを処理室から出さず、処理室内に導入するガスを水素ガスからシランガス(第2の原料ガス)に切り替える。例えば、処理室内圧力は0.56Torrに設定し、シランガスの流量は、例えば800ccに設定される。温度は約520℃に維持される。この処理を、例えば約3分間続ける。

【0041】

これにより、シード膜31の表面に、図4(a)に示す第1のシリコン膜32が形成される。すなわち、凹部20内におけるシード膜31の内側、およびシード膜31の上面上に、第1のシリコン膜32が形成される。

【0042】

第1のシリコン膜32は、シード膜31と同様、アンドープで非晶質のシリコン膜である。したがって、図4(a)以降の図においては、シード膜31は第1のシリコン膜32と区別せずに、第1のシリコン膜32に包含させて図示している。

【0043】

凹部20の側壁に形成された電極間絶縁膜13間の上端側の開口幅(図3(b)におけるa)は、例えば8nmである。第1のシリコン膜32の膜厚は、その開口幅aの半分よりも小さい膜厚に制御される。

【0044】

したがって、凹部20は第1のシリコン膜32で完全に埋まらず、第1のシリコン膜32には、図4(a)に示すように、凹部20の開口側からボトム側に向けてくぼんだくぼみ40が形成される。すなわち、第1のシリコン膜32は、凹部20の直上で平坦になっていない。

【0045】

くぼみ40が凹部20のボトム側に入り込んでいる深さは、図4(a)で表す位置に限らず、第1のシリコン膜32の膜厚等によって変わる。

【0046】

第1のシリコン膜32を形成するときの第2の原料ガスには、シード膜31を形成するときの第1の原料ガスとは異なり、シランガスが用いられる。

【0047】

第1の原料ガスとしては、前述したようにシリコン膜の成膜初期の島状成長を抑制するため、ジシランなどが用いられる。一方、第2の原料ガスであるシランを用いて形成されたシリコン膜は、ジシランなどの第1の原料ガスを用いて形成されたシリコン膜に比べて、ウェーハ面内の膜厚均一性及び埋め込み性に優れ、また成膜レートも高い。

【0048】

したがって、シード膜31は、表面平坦性を確保するための下地として薄い(例えば1〜2nmの)膜厚にとどめ、その後は、シランガスを用いて凹部20内に第1のシリコン膜32を形成することで、ジシランなどの第1の原料ガスに起因する良好な表面平坦性を得つつ、第2の原料ガス(シランガス)に起因する良好なステップカバレッジ及び高い生産性を実現できる。

【0049】

第1のシリコン膜32の形成後、引き続き、ウェーハを処理室から出さず、処理室内に導入するガスを第2の原料ガスから水素ガスに切り替え、さらに、ウェーハ温度を例えば300℃程度に降温する。水素ガスの流量は、例えば1000ccに設定される。この処理を、例えば約40分間続ける。

【0050】

水素ガス雰囲気中での降温ステップの後、引き続き、ウェーハを処理室から出さず、処理室内に導入するガスを水素ガスから塩素を含むエッチングガスに切り替えて、第1のシリコン膜32の一部をエッチングする。例えば、処理室内圧力は0.3Torrに設定され、温度は約300℃に維持される。

【0051】

このエッチング処理で処理室内には、例えば、塩素ガス(Cl2ガス)が500ccの流量で導入され、さらに窒素ガス(N2ガス)が800ccの流量で導入される。このエッチング処理を、例えば約15分間続ける。

【0052】

第1のシリコン膜32は、主に塩素の作用によりエッチングされる。図4(a)に示すエッチング前の状態で、第1のシリコン膜32にはくぼみ40が形成されている。そのくぼみ40の幅を広げるようにエッチングが進み、図4(b)に示すように、電極間絶縁膜13に沿うようにコンフォーマルに第1のシリコン膜32が残され、その内側に隙間41が形成される。隙間41の幅は、凹部20のボトム側よりも開口側で広い。

【0053】

エッチング前の状態で、第1のシリコン膜32が凹部20を完全に埋め込んで、凹部20の直上部分で平坦になっていると、凹部20内の第1のシリコン膜32の幅方向の全体が均一にエッチバックされてしまい、図4(b)に示すようなボトム側よりも開口側で幅が広い隙間41は形成されない。

【0054】

実施形態のように、エッチング前の状態で、第1のシリコン膜32に、図4(a)に示すくぼみ40があると、そのくぼみ40にエッチングガスが入り込み、くぼみ40を幅方向に広げつつエッチングが進む。

【0055】

そして、エッチングガスが侵入しにくいくぼみ40のボトム側よりも、エッチングガス濃度が高くなるウェーハ表面側でエッチングが促進される。このため、図4(b)に示すように、ボトム側よりも開口側で幅が広がった隙間41が形成される。隙間41に面する第1のシリコン膜32の側壁は、断面V字状のテーパー形状にされる。したがって、後述する第2のシリコン膜33を、ボイドを生じさせることなく、隙間41に埋め込みやすくできる。

【0056】

このエッチングは、アンドープの非晶質シリコン膜である第1のシリコン膜32に対して行われる。アンドープの非晶質シリコン膜に対して、例えば300℃で、Cl2ガスを使うと、エッチングレートを1オングストローム/分程度に制御することができる。これにより、凹部20のボトムと側壁に第1のシリコン膜32を残しつつ、図4(b)に示す形状の隙間41を制御性よく形成することができる。

【0057】

非晶質のシリコン膜に、不純物として例えばリンが少しでも添加されると、アンドープ非晶質シリコン膜に比べてエッチングレートが100〜1000倍に上がってしまい、凹部20内のシリコン膜のほとんどが短時間で除去され、図4(b)に示す形状の隙間41の形成が困難になる。

【0058】

第1のシリコン膜32のエッチング後、引き続き、ウェーハを処理室から出さず、処理室内に導入するガスを塩素を含むエッチングガスから不純物を含むドーパントガスに切り替え、例えば300℃から520℃に昇温する。処理室内圧力は、例えば4Torrに設定される。

【0059】

ドーパントガスとして、例えばリン(P)を含むホスフィン(PH3)ガスが用いられる。さらに具体的には、ヘリウムガスに1vol%の濃度でホスフィンガスを含む希釈ホスフィンガスが用いられ、この希釈ホスフィンガスは、例えば1000ccの流量で処理室内に導入される。例えば、約30分かけて300℃から520℃に昇温された後、約10分間、520℃の温度が維持される。

【0060】

すなわち、第1のシリコン膜32は、リンを含むガス雰囲気中で熱処理される。これにより、隙間41に面する第1のシリコン膜32の内壁(側壁及び底部)に、第1のシリコン膜32に導電性を付与する不純物としてリンが添加(ドーピング)される。

【0061】

ドーパントガスとしては、ホスフィンガスに限らず、アルシン(AsH3)ガス、ジボラン(B2H6)ガス、三塩化ボロン(BCl3)ガスなどを用いることもできる。

【0062】

第1のシリコン膜32への不純物ドーピングの後、引き続き、ウェーハを処理室から出さず、処理室内に導入するガスをドーパントガスから、シラン及びドーパントガスを含むガスに切り替える。例えば、処理室内圧力は0.56Torrに設定され、温度は約520℃に維持される。シランガスは、例えば800ccの流量で処理室内に導入される。ドーパントガスとしては、例えば前ステップと同じガスが90ccの流量で処理室内に導入される。この成膜処理を、例えば約20分間続ける。

【0063】

これにより、隙間41内、および浮遊ゲートFG上の第1のシリコン膜32上に、図4(c)に示すように、第2のシリコン膜33が形成される。第2のシリコン膜33は、不純物として例えばリンを含む非晶質シリコン膜である。

【0064】

あるいは、第2のシリコン膜33の成膜時に不純物をドーピングせず、アンドープの第2のシリコン膜33を形成した後、そのアンドープの第2のシリコン膜33に不純物をドーピングして、第2のシリコン膜33に導電性を与えてもよい。

【0065】

いずれも非晶質状態で成膜された第1のシリコン膜32及び第2のシリコン膜33は、最終的には、熱処理により結晶化され、多結晶シリコン膜となる。これら多結晶シリコン膜である第1のシリコン膜32及び第2のシリコン膜33は、前述した半導体記憶装置における制御ゲートCGとして機能する。

【0066】

前述した第1のシリコン膜32に対するエッチング及び不純物ドーピングは、第1のシリコン膜32を結晶化させる熱処理の温度よりも低い温度下で行われる。これにより、第1のシリコン膜32に対するエッチング中及び不純物ドーピング中、第1のシリコン膜32の非晶質状態を維持することができる。非晶質シリコン膜は、多結晶シリコン膜よりも表面粗さが小さいため、上記エッチング中及び不純物ドーピング中に第1のシリコン膜32の表面平坦性の低下をまねかない。

【0067】

ここで、実施形態とは異なるステップにより、制御ゲートCGとなるシリコン膜を形成する技術を比較例として挙げる。

【0068】

この比較例では、ジシランを用いてシード膜31を形成し、その後水素雰囲気中で昇温する工程までは、実施形態と同じであるが、それ以降の工程が実施形態と異なる。

【0069】

すなわち、比較例では、水素雰囲気中で520℃まで昇温した後、その温度下で、シランガスとドーパントガスを用いて残りのシリコン膜を形成する。このシリコン膜形成時の条件は、実施形態における第2のシリコン膜33を形成するときの条件と同じである。

【0070】

近年、メモリデバイスの微細化が進み、図3(b)に示す幅aが10nm以下になってきている。ここまで狭くなると、成膜初期にジシランで表面平坦性のよいシード膜31を形成しても、凹部20の局所的な閉塞が発生しやすくなる。また、凹部20の幅が狭くなるのにともない、シリコン膜を埋め込む部分に露出する電極間絶縁膜13の側壁が、基板に対して垂直になる傾向にあり、さらにはボトム側よりも開口側で凹部20の幅が狭くなるオーバーハング形状になる傾向にもある。このようなことから、比較例の技術では、凹部20内にボイドを生じさせることなくシリコン膜を埋め込むことが困難になりつつある。

【0071】

これに対して、実施形態によれば、シード膜31を形成した後、凹部20内を一度にシリコン膜で埋め込まず、第1のシリコン膜32の形成、第1のシリコン膜32のエッチング、そして第2のシリコン膜33の形成というステップにより、凹部20内にシリコン膜を埋め込んでいる。

【0072】

すなわち、第1のシリコン膜32を形成した後、第1のシリコン膜32に、図4(b)に示す隙間41を形成する。隙間41は、凹部20のボトム側よりも開口側で幅が広くなっており、深くなるほど漸次細くなるテーパー形状に形成されている。したがって、その隙間41にボイド(空隙)を生じさせることなく、第2のシリコン膜33を埋め込むことができる。

【0073】

また、アンドープの第1のシリコン膜32をエッチング対象とすることで、エッチング制御性を高めることができる。これにより、微小幅の凹部20内に、確実にテーパーをもたせて微小隙間41を形成することが可能になる。

【0074】

電極間絶縁膜13形成後の凹部20の開口幅a(図3(b)参照)が8nm、その開口付近における電極間絶縁膜13の上面から側壁にかけての角部の角度が89°の場合に、実施形態によれば、上記比較例に比べて、凹部20にシリコン膜を埋め込んだ後に生じたボイドの数を1/3以下に減少させることができた。

【0075】

また、ジシランを用いたシード膜31の成膜時の温度では、例えばホスフィンガスは分解せず、よってシード膜31に不純物をドープすることが困難である。また、シード膜31の形成後に、ドーパントガスを含む雰囲気でシリコン膜を形成しても、そのシリコン膜の成膜初期の段階で、所望の温度にまだ安定せずドーパントガスの分解が不十分な状態で、シリコン膜が凹部20内に埋め込まれてしまうことがある。凹部20に埋め込まれたシリコン膜の導電性が不十分であると、浮遊ゲートFG間のシリコン膜が空乏化し、制御ゲートCGとして機能しない。

【0076】

実施形態によれば、凹部20内を完全に埋め込む前に、図4(b)の状態で、例えばホスフィンガスを含む雰囲気中で熱処理する。このとき、シリコン膜の原料ガスは処理室内に導入されない。したがって、隙間41は閉塞されず、隙間41にホスフィンガスを侵入させることができ、隙間41に面する第1のシリコン膜32の側壁を通じて、凹部20内の第1のシリコン膜32に不純物としてリンを確実にドーピングすることができる。この結果、浮遊ゲートFG間のシリコン膜の空乏化を抑制することができる。

【0077】

図6は、実施形態のステップで形成したシリコン膜と、上記比較例のステップで形成したシリコン膜との、リン(P)の深さ方向の濃度分布図である。

【0078】

実施形態及び比較例ともに、シード膜31を形成した後のステップで形成した非晶質シリコン膜中のSIMS(Secondary Ion-microprobe Mass Spectrometer)分析によるP濃度を表す。横軸はシリコン膜の表面からの深さ(nm)を表し、縦軸はP濃度(atoms/cm3)を表す。

【0079】

比較例の方法では、40nm付近の深い位置に、すなわち成膜初期の段階でPが高濃度にドーピングされなかった。これに対して、実施形態によれば、凹部20が完全に埋め込まれる前にシリコン膜の成膜を一旦停止して制御性に優れたエッチングにより隙間41を形成した後、ホスフィンガスによる熱処理を行うことで、40nm付近の深い位置でのP濃度を比較例よりも高濃度にできた。

【0080】

図7(a)は、凹部20の下部における浮遊ゲートFGと、電極間絶縁膜13と、その電極間絶縁膜13の内側に実施形態による方法で形成されたシリコン膜とからなる実施形態のキャパシタの容量電圧特性(CV特性)と、凹部20の下部における浮遊ゲートFGと、電極間絶縁膜13と、その電極間絶縁膜13の内側に上記比較例による方法で形成されたシリコン膜とからなる比較例のキャパシタの容量電圧特性(CV特性)と、を表す。

【0081】

比較例では、凹部20の下部におけるボイド(空隙)あるいはシリコン膜中の不純物不足により、シリコン膜に印加する正電圧を高くするとシリコン膜中を空乏層が伸び、容量が低下するのに対し、実施形態では空乏層がほとんど伸びず、容量低下をまねかない。

【0082】

図7(b)は、実施形態による方法で形成されたシリコン膜を制御ゲートCGとして有するメモリセルと、比較例による方法で形成されたシリコン膜を制御ゲートCGとして有するメモリセルとの書き込み電圧分布図である。

【0083】

縦軸はビット数を表し、横軸は、メモリセルを所定のしきい値にするために制御ゲートCGに印加される書き込み電圧Vpgmを表す。

【0084】

実施形態によれば、比較例に比べて、書き込み電圧Vpgmを下げることができ、また書き込み電圧Vpgmのばらつきも大きく低減できる。

【0085】

第1のシリコン膜32の成膜及びその一部のエッチングは複数回繰り返してもよい。それらステップを複数回繰り返すと、隙間41のテーパー角(隙間41に面する第1のシリコン膜32の側壁の傾斜)をよりゆるやかにして、第2のシリコン膜33をより埋めやすくなる場合がある。

【0086】

本発明のいくつかの実施形態を説明したが、これらの実施形態は、例として提示したものであり、発明の範囲を限定することは意図していない。これら新規な実施形態は、その他の様々な形態で実施されることが可能であり、発明の要旨を逸脱しない範囲で、種々の省略、置き換え、変更を行うことができる。これら実施形態やその変形は、発明の範囲や要旨に含まれるとともに、特許請求の範囲に記載された発明とその均等の範囲に含まれる。

【符号の説明】

【0087】

11…アクティブ領域、12…トンネル絶縁膜、13…電極間絶縁膜、20…凹部、31…シード膜、32…第1のシリコン膜、33…第2のシリコン膜、40…くぼみ、41…隙間、FG…浮遊ゲート、CG…制御ゲート

【特許請求の範囲】

【請求項1】

第1の原料ガスを用いて、凹部にコンフォーマルにシリコンを含むシード膜を形成する工程と、

前記第1の原料ガスとは異なるシランを含む第2の原料ガスを用いて、前記凹部の開口側からボトム側に向けてくぼんだくぼみを有するアンドープで非晶質の第1のシリコン膜を、前記シード膜の内側に形成する工程と、

前記第1のシリコン膜を結晶化させる温度よりも低い温度下で、前記凹部内の前記第1のシリコン膜の一部を塩素を含むガスを用いてエッチングし、前記第1のシリコン膜に、前記凹部の前記ボトム側よりも前記開口側で幅が広い隙間を形成する工程と、

前記隙間に面する前記第1のシリコン膜の内壁に、前記第1のシリコン膜を結晶化させる温度よりも低い温度下で不純物を添加する工程と、

前記不純物の添加後、前記隙間を埋める非晶質の第2のシリコン膜を形成する工程と、

前記第1のシリコン膜及び前記第2のシリコン膜を結晶化させる熱処理を行う工程と、

を備えたシリコン膜の形成方法。

【請求項2】

凹部の開口側からボトム側に向けてくぼんだくぼみを有するアンドープの第1のシリコン膜を、前記凹部に形成する工程と、

前記凹部内の前記第1のシリコン膜の一部を塩素を含むガスを用いてエッチングし、前記第1のシリコン膜に、前記凹部の前記ボトム側よりも前記開口側で幅が広い隙間を形成する工程と、

前記隙間に面する前記第1のシリコン膜の内壁に、不純物を添加する工程と、

前記不純物の添加後、前記隙間を埋める第2のシリコン膜を形成する工程と、

を備えたシリコン膜の形成方法。

【請求項3】

前記第1のシリコン膜及び前記第2のシリコン膜を非晶質状態で形成し、

前記第2のシリコン膜の形成後、前記第1のシリコン膜及び前記第2のシリコン膜を結晶化させる熱処理を行う工程をさらに備えた請求項2記載のシリコン膜の形成方法。

【請求項4】

前記第1のシリコン膜に対するエッチング及び前記不純物の添加を、前記第1のシリコン膜を結晶化させる前記熱処理の温度よりも低い温度で行う請求項3記載のシリコン膜の形成方法。

【請求項5】

基板上に設けられた複数の第1の電極間の凹部および前記第1の電極上に、コンフォーマルに絶縁膜を形成する工程と、

前記複数の第1の電極間における前記絶縁膜の内側および前記第1の電極上の前記絶縁膜上に、第2の電極を形成する工程と、

を備え、

前記第2の電極を形成する工程は、

前記凹部の開口側からボトム側に向けてくぼんだくぼみを有するアンドープの第1のシリコン膜を、前記凹部に形成する工程と、

前記凹部内の前記第1のシリコン膜の一部を塩素を含むガスを用いてエッチングし、前記第1のシリコン膜に、前記凹部の前記ボトム側よりも前記開口側で幅が広い隙間を形成する工程と、

前記隙間に面する前記第1のシリコン膜の内壁に、不純物を添加する工程と、

前記不純物の添加後、前記隙間を埋める第2のシリコン膜を形成する工程と、

を有する半導体装置の製造方法。

【請求項1】

第1の原料ガスを用いて、凹部にコンフォーマルにシリコンを含むシード膜を形成する工程と、

前記第1の原料ガスとは異なるシランを含む第2の原料ガスを用いて、前記凹部の開口側からボトム側に向けてくぼんだくぼみを有するアンドープで非晶質の第1のシリコン膜を、前記シード膜の内側に形成する工程と、

前記第1のシリコン膜を結晶化させる温度よりも低い温度下で、前記凹部内の前記第1のシリコン膜の一部を塩素を含むガスを用いてエッチングし、前記第1のシリコン膜に、前記凹部の前記ボトム側よりも前記開口側で幅が広い隙間を形成する工程と、

前記隙間に面する前記第1のシリコン膜の内壁に、前記第1のシリコン膜を結晶化させる温度よりも低い温度下で不純物を添加する工程と、

前記不純物の添加後、前記隙間を埋める非晶質の第2のシリコン膜を形成する工程と、

前記第1のシリコン膜及び前記第2のシリコン膜を結晶化させる熱処理を行う工程と、

を備えたシリコン膜の形成方法。

【請求項2】

凹部の開口側からボトム側に向けてくぼんだくぼみを有するアンドープの第1のシリコン膜を、前記凹部に形成する工程と、

前記凹部内の前記第1のシリコン膜の一部を塩素を含むガスを用いてエッチングし、前記第1のシリコン膜に、前記凹部の前記ボトム側よりも前記開口側で幅が広い隙間を形成する工程と、

前記隙間に面する前記第1のシリコン膜の内壁に、不純物を添加する工程と、

前記不純物の添加後、前記隙間を埋める第2のシリコン膜を形成する工程と、

を備えたシリコン膜の形成方法。

【請求項3】

前記第1のシリコン膜及び前記第2のシリコン膜を非晶質状態で形成し、

前記第2のシリコン膜の形成後、前記第1のシリコン膜及び前記第2のシリコン膜を結晶化させる熱処理を行う工程をさらに備えた請求項2記載のシリコン膜の形成方法。

【請求項4】

前記第1のシリコン膜に対するエッチング及び前記不純物の添加を、前記第1のシリコン膜を結晶化させる前記熱処理の温度よりも低い温度で行う請求項3記載のシリコン膜の形成方法。

【請求項5】

基板上に設けられた複数の第1の電極間の凹部および前記第1の電極上に、コンフォーマルに絶縁膜を形成する工程と、

前記複数の第1の電極間における前記絶縁膜の内側および前記第1の電極上の前記絶縁膜上に、第2の電極を形成する工程と、

を備え、

前記第2の電極を形成する工程は、

前記凹部の開口側からボトム側に向けてくぼんだくぼみを有するアンドープの第1のシリコン膜を、前記凹部に形成する工程と、

前記凹部内の前記第1のシリコン膜の一部を塩素を含むガスを用いてエッチングし、前記第1のシリコン膜に、前記凹部の前記ボトム側よりも前記開口側で幅が広い隙間を形成する工程と、

前記隙間に面する前記第1のシリコン膜の内壁に、不純物を添加する工程と、

前記不純物の添加後、前記隙間を埋める第2のシリコン膜を形成する工程と、

を有する半導体装置の製造方法。

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【公開番号】特開2013−105812(P2013−105812A)

【公開日】平成25年5月30日(2013.5.30)

【国際特許分類】

【出願番号】特願2011−247275(P2011−247275)

【出願日】平成23年11月11日(2011.11.11)

【出願人】(000003078)株式会社東芝 (54,554)

【Fターム(参考)】

【公開日】平成25年5月30日(2013.5.30)

【国際特許分類】

【出願日】平成23年11月11日(2011.11.11)

【出願人】(000003078)株式会社東芝 (54,554)

【Fターム(参考)】

[ Back to top ]