シングルゲートまたはマルチゲートフィールドプレート製造

【課題】電界効果型トランジスタの表面に、誘電性材料の堆積/成長させ、誘電性材料をエッチングし、および、メタルを蒸着させる、連続的なステップを用いる、シングルゲートまたはマルチゲートプレートの製造プロセスの提供。

【解決手段】本製造プロセスは、誘電性材料の堆積/成長が、典型的には、非常によく制御できるプロセスなので、フィールドプレート動作を厳しく制御できる。さらに、デバイス表面に堆積された誘電性材料は、デバイスの真性領域から除去される必要はない。このため、乾式または湿式のエッチングプロセスで受けるダメージの少ない材料を用いることなく、フィールドプレートされたデバイスを、実現することができる。マルチゲートフィールドプレートを使うと、マルチ接続を使用するので、ゲート抵抗を減らすこともでき、こうして、大周辺デバイスおよび/またはサブミクロンゲートデバイスの性能を向上することができる。

【解決手段】本製造プロセスは、誘電性材料の堆積/成長が、典型的には、非常によく制御できるプロセスなので、フィールドプレート動作を厳しく制御できる。さらに、デバイス表面に堆積された誘電性材料は、デバイスの真性領域から除去される必要はない。このため、乾式または湿式のエッチングプロセスで受けるダメージの少ない材料を用いることなく、フィールドプレートされたデバイスを、実現することができる。マルチゲートフィールドプレートを使うと、マルチ接続を使用するので、ゲート抵抗を減らすこともでき、こうして、大周辺デバイスおよび/またはサブミクロンゲートデバイスの性能を向上することができる。

【発明の詳細な説明】

【技術分野】

【0001】

(関連出願の参照)

本出願は、以下の同時係属中で、同一出願人による米国仮特許出願(シリアル番号第60/501,557号、題名「FABRICATION OF SINGLE OR MULTIPLE GATE FIELD PLATES」、Alessandro Chini、 Umesh K. Mishra、 Primit Parikh、 および、Yifeng Wuによって、2003年9月9日に出願、代理人整理番号第30794.105−US−P1号)の米国法典第35巻第119条(e)項の利益を主張するものであり、その出願がここに援用される。

【0002】

(連邦によるスポンサー研究および開発に関する声明)

本発明は、ONR MURIプログラムによって与えられた助成金第N00014−01−1−0764号、および、AFOSR MURIプログラムによって与えられた助成金第F49620−99−1−0296号の下、政府支援により行われた。政府は、本発明に関し、特定の権利を有する。

【0003】

(本発明の分野)

本発明は、半導体デバイスに関し、特に、シングルゲートまたはマルチゲートフィールドプレートの製造に関する。

【背景技術】

【0004】

(注:本出願は、カッコ内の参照番号(例えば、[x]で、本明細書に示す様々な文献を参照している。これら刊行物のリストは、参照番号順に並べ、「参考文献」と題する節で、以下に列挙される。これら刊行物のそれぞれは、ここに援用される。)

半導体ベースの電界効果型トランジスタ(FET)において、動作中に、ゲート−ドレインのアクセス領域で、大きな電界が発生する。フィールドプレーティングは、高電界動作下におけるデバイス性能向上と、表面トラッピング現象を緩和する周知の技術である[1]、[2]。例えば、フィールドプレーティングは、高電界でデバイス動作中に起こる有害な影響全て(絶縁破壊電圧、トラッピングの影響、信頼性)を緩和する効果的で、周知の技術となっている。

【0005】

フィールドプレーティングの基本的概念は、デバイス活性領域の縦方向空乏に依存するもので、これにより、横方向の空乏領域に、より拡がりを持たせることができる。この結果、ある与えられたバイアス電圧において、デバイス活性領域の電界がより低くなり、デバイスが高電界で動作しているときに常に生じる有害な影響全て(低い絶縁破壊電圧、トラッピング現象、低い信頼性)を緩和できる。さらに、ゲート−ドレインアクセス領域に位置するフィールドプレートは、デバイス活性領域の調節能力もあり、その結果、高い無線周波数(RF)信号下での適切なデバイス動作を妨げる表面トラッピングの影響を減少させる。

【0006】

しかしながら、必要とされているのは、シングルゲートまたはマルチゲートフィールドプレート製造の改善方法、および、シングルゲートまたはマルチゲートフィールドプレートを組み込んだ改善構造である。

【発明の概要】

【課題を解決するための手段】

【0007】

(本発明の概要)

本発明の実施形態は、シングルゲートまたはマルチゲートフィールドプレート製造の改善方法を提供する。本発明に基づく製造プロセスは、電界効果型トランジスタの表面に、誘電性材料を堆積または成長させ、誘電性材料をエッチングし、および、メタルを蒸着させる、連続的なステップを含む。本製造プロセスの利点は、誘電性材料の厚みを厳しく(tight)制御できること、および、電界効果型トランジスタを形成する半導体材料にダメージを与えうる任意の乾式または湿式エッチングプロセスに、デバイス活性領域の表面を、一切曝さないことを含む。さらに、デバイス表面に堆積された誘電性材料は、デバイスの真性領域から除去される必要はない。このため、乾式または湿式エッチングプロセスで生じるダメージを受けることなく、フィールドプレートされたデバイスを、実現することができる。マルチゲートフィールドプレートを使うと、マルチ接続を使用するので、ゲート抵抗を減らすことができ、大周辺デバイスおよび/またはサブミクロンゲートデバイスの性能を向上できる。最終的に、誘電性材料の厚みを適切に調整すると、平行なゲートコンタクトを誘電性材料の上に、堆積させることができる。これは、デバイスの外因性領域で、平行なゲートコンタクトを電気的に接続して、ゲート抵抗を著しく減少するためである。

例えば、本願発明は以下の項目を提供する。

(項目1)

1以上のゲートフィールドプレートの製造方法であって、該方法は、

デバイスの表面に1つ以上のフィールドプレートを形成するために、誘電性材料を堆積または成長させること、誘電性材料をエッチングすること、および、メタル蒸着することからなる連続的ステップを実行することを包含し、

該表面に堆積される該誘電性材料は、活性領域から除去される必要がなく、それによって、低ダメージの乾式または湿式エッチングプロセスを用いずに、フィールドプレートされたデバイスの実現を可能とする、方法。

(項目2)

前記ステップが、フィールドプレートオペレーションの厳しい制御を可能とする、項目1に記載の方法。

(項目3)

ゲート抵抗を減少させるために、マルチフィールドプレートを用いてマルチ接続を形成することをさらに包含する、項目1に記載の方法。

(項目4)

前記フィールドプレートをゲートドレインアクセス領域に配置することで、前記活性領域の調節能力を提供し、その結果、高い無線周波数(RF)信号下での適切なデバイス動作を妨げる表面トラッピングの影響を減少させる、項目1に記載の方法。

(項目5)

前記デバイスにダメージを与えうる前記乾式または湿式エッチングプロセスに、前記活性領域の前記表面を、一切曝さないようにすることをさらに包含する、項目1に記載の方法。

(項目6)

外因性領域にある少なくとも2つの平行なゲートを電気的に接続することで、ゲート抵抗を著しく減少させるために、前記誘電性材料の厚さを適切に調整して、該誘電性材料のトップに、平行なゲートコンタクトを堆積させることをさらに包含する、項目1に記載の方法。

(項目7)

前記デバイスが、ソースオーミックコンタクトとドレインオーミックコンタクト、ゲートコンタクト、および、活性領域を含む電界効果型トランジスタである、項目1に記載の方法。

(項目8)

前記実行ステップが、

(1)前記デバイスの真性および外因性領域に、前記誘電性材料を堆積または成長させることと、

(2)該誘電性材料が、主として、前記デバイスの活性領域に残るように、該誘電性材料をパターニングすることと、

(3)該パターニングされた誘電性材料にフィールドプレートを生成することであって、ゲートフィールドコンタクトとフィールドプレートコンタクトとが、少なくとも、前記外因性領域での、少なくとも片側で電気的に短絡され、それによって、両コンタクト間に低抵抗接続を提供する、ことと

をさらに包含する、項目1に記載の方法。

(項目9)

前記誘電性材料の厚さが、前記デバイスの適切な動作を達成するために、制御される、項目8に記載の方法。

(項目10)

前記パターニングステップ(3)が、乾式または湿式エッチングプロセス、あるいは、リフトオフプロセスによって、前記誘電性材料をパターニングすることを包含する、項目8に記載の方法。

(項目11)

前記生成ステップ(3)が、前記誘電性材料上に、フィールドプレートを蒸着することを包含する、項目8に記載の方法。

(項目12)

複数のフィールドプレートを形成するために、前記ステップ(1)〜(3)が繰り返される、項目8に記載の方法。

(項目13)

前記フィールドプレートが、ゲート抵抗Rgに等価な抵抗Rfを有する、項目8に記載の方法。

(項目14)

前記フィールドプレートが、前記デバイスの真性領域の両側に接続されている、項目8に記載の方法。

(項目15)

ゲート抵抗を減少させるために、前記ゲートと前記フィールドプレートとの間に、マルチ接続を形成することをさらに包含する、項目8に記載の方法。

(項目16)

前記形成ステップが、前記ゲートと前記フィールドプレートとの間にマルチ接続を形成するための該ゲートの堆積の前に、前記活性領域の小部分をエッチングすることを包含する、項目15に記載の方法。

(項目17)

前記デバイスの熱インピーダンスを設計するために、前記活性領域間にスペーシングすることをさらに包含する、項目15に記載の方法。

(項目18)

前記デバイスは、エアブリッジの数を減少させた大周辺デバイスを含む、項目15に記載の方法。

(項目19)

前記生成ステップは、ゲート抵抗を低くするために、T字型プロセスを用いずに、前記マルチ接続を生成するステップを包含する、項目15に記載の方法。

(項目20)

前記生成ステップは、平行なフィールドプレートを用いて、前記マルチ接続を生成するステップを包含する、項目15に記載の方法。

(項目21)

前記生成ステップは、デバイスの線形性能を向上させるために、ソースアクセス抵抗を調節するために、ゲートソースアクセス領域をカバーする前記フィールドプレートを形成するステップを包含する、項目20に記載の方法。

(項目22)

項目1に記載の方法を使用して製造される、デバイス。

(項目23)

ゲートフィールドプレートを製造する方法であって、

(a)デバイスの真性領域と外因性領域上に、誘電性材料を堆積または成長することと、(b)該誘電性材料が、主として、該デバイスの活性化領域に残るように、該誘電性材料をパターニングすることと、

(c)該パターニングされた誘電性材料の上に、フィールドプレートを生成することであって、ゲートコンタクトとフィールドコンタクトは、該外因性領域の少なくとも片側で電気的に短絡され、それによって、両コンタクト間に低抵抗接続を提供する、ことと

を包含する、方法。

(項目24)

前記デバイスを適切な動作を達成するために、前記誘電性材料の厚さが制御されている、項目23に記載の方法。

(項目25)

前記パターニングステップ(b)は、乾式エッチングまたは湿式エッチング、あるいは、リフトオフプロセスによって、前記誘電体材料をパターニングすることを包含する、項目23に記載の方法。

(項目26)

前記生成ステップ(c)は、前記パターニングされた誘電体材料上に、フィールドプレートを蒸着することを包含する、項目23に記載の方法。

(項目27)

前記ステップ(a)と(b)は、複数のフィールドプレートを生成するために、繰り返し行われる、項目23に記載の方法。

(項目28)

基板と、

該基板上に成長させた核形成層と

該核形成層上に形成されたチャネル層と、

該チャネル層に形成されたバリア層と、

該バリア層上に成長させた半導体スペーサ層と、

ソース電極とドレイン電極であって、該ゲート電極が適切なレベルでバイアスされたとき、該ソース電極と該ドレイン電極との間で電流が流れるように、該バリア層を介してオーミックコンタクトするように形成された、ソース電極とドレイン電極と

を備える、高電子移動度トランジスタ(HEMT)であって、

該ゲート電極の少なくとも一部分がバリア層の表面上にあるように、該スペーサ層はエッチングされ、該ゲート電極は堆積され、

該ゲート電極が、該ゲート電極から該ドレイン電極に向かってある距離拡がるフィールドプレートを形成するように、該ゲート電極の一部分は、該スペーサ層を横切って拡がるようにパターニングされている、HEMT。

(項目29)

前記電流は、前記ゲート電極が適切なレベルでバイアスされているとき、前記チャネル層とバリア層との間のヘテロ界面で生じる二次元電子ガス(2DEG)を介して、前記ゲート電極とドレイン電極との間を流れる、項目28に記載のHEMT。

(項目30)

前記スペーサ層上の前記ゲート電極の一部分は、エピタキシャルフィールドプレートを形成する、項目28に記載のHEMT。

(項目31)

前記スペーサ層をカバーする誘電性パッシベーション層をさらに備える、項目28に記載のHEMT。

(項目32)

前記スペーサ層は、誘電性層、アンドープのまたは空乏化したAlxGa1−xN(0≦x≦1)材料の層、あるいは、その組合せを含む、項目28に記載のHEMT。

(項目33)

前記フィールド層は、前記スペーサ層の上に形成され、前記ゲート電極の端から前記ドレイン電極に向かって、距離Lf(フィールドプレート距離)まで拡がる、項目28に記載のHEMT。

(項目34)

前記フィールドプレートは、前記ゲート電極に電気的に接続されている、項目28に記載のHEMT。

(項目35)

前記フィールドプレートは、前記ゲート電極の成長と同じ堆積ステップの間に形成される、項目28に記載のHEMT。

(項目36)

前記フィールドプレートとゲート電極は、別個の堆積ステップの間に形成される、項目28に記載のHEMT。

(項目37)

前記基板は、シリコンカーバイド、サファイア、スピネル、酸化亜鉛、シリコン、あるいは、III族窒化物材料の成長をサポートできる他の任意の材料からなる、項目28に記載のHEMT。

(項目38)

前記核形成層は、AlzGa1−zN(0≦z≦1)核形成層である、項目28に記載のHEMT。

(項目39)

前記核形成層は、AlN核形成層である、項目28に記載のHEMT。

(項目40)

前記チャネル層は、高抵抗のIII族窒化物チャネル層である、項目28に記載のHEMT。

(項目41)

前記チャネル層は、AlxGayIn(1−x−y)N(0≦x≦1、0≦y≦1、x+y≦1)を含む、項目28に記載のHEMT。

(項目42)

前記チャネル層は、GaN:Feを含む、項目28に記載のHEMT。

(項目43)

前記バリア層は、AlxGa1−xN(0≦x≦1)を含む、項目28に記載のHEMT。

(項目44)

前記バリア層は、AlNおよびAlGaNを含む、項目28に記載のHEMT。

(項目45)

前記チャネル層とバリア層のそれぞれは、III族窒化物材料のドープまたはアンドープの層であるサブ層を含む、項目28に記載のHEMT。

(項目46)

前記スペーサ層は、AlxGa1−xNバリア層上に成長される、III族窒化物半導体スペーサ層を含む、項目28に記載のHEMT。

(項目47)

前記スペーサ層は、均一な組成を有する、項目28に記載のHEMT。

(項目48)

前記スペーサ層は、勾配のある組成を有する、項目28に記載のHEMT。

(項目49)

前記スペーサ層は、アンドープである、項目28に記載のHEMT。

(項目50)

前記スペーサ層は、成長すると完全に空乏化する、項目28に記載のHEMT。

(項目51)

前記ゲート電極は前記バリア層が形成された後に形成され、パッシベーション層は前記デバイス上に堆積され、

前記フィールドプレートは、該ゲートをオーバーラップし、ゲート−ドレイン領域で距離Lf拡がるように、該パッシベーション層に次いで形成され、該パッシベーション層は該フィールドプレートに対してスペーサ層として働く、項目28に記載のHEMT。

【図面の簡単な説明】

【0008】

【図1A】図1Aは、電界効果トランジスタ(FET)の断面図である。

【図1B】図1Bは、電界効果トランジスタ(FET)の平面図である。

【図2A】図2Aは、誘電性材料堆積/成長デバイスの断面図である。

【図2B】図2Bは、誘電性材料堆積/成長デバイスの平面図である。

【図3A】図3Aは、デバイスの外因性部分から、誘電性材料の除去を示すデバイス断面図である。

【図3B】図3Bは、デバイスの外因性部分から、誘電性材料の除去を示すデバイス平面図である。

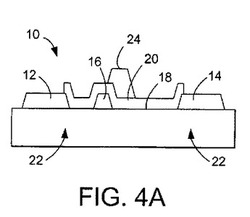

【図4A】図4Aは、ゲートフィールドプレートの蒸着を示すデバイス断面図である。

【図4B】図4Bは、ゲートフィールドプレートの蒸着を示すデバイス平面図である。

【図5A】図5Aは、マルチフィールドプレート構造の一例を示すデバイス断面図である。

【図5B】図5Bは、マルチフィールドプレート構造の一例を示すデバイス平面図である。

【図6】図6は、fmax依存性とゲートフィンガー幅との関係をシミュレーションしたグラフである。

【図7A】図7Aは、ゲート抵抗を減らしたマルチフィールドプレートデバイスのデバイス断面図である。

【図7B】図7Bは、ゲート抵抗を減らしたマルチフィールドプレートデバイスのデバイス平面図である。

【図7C】図7Cは、ゲート抵抗を減らしたマルチフィールドプレートデバイスのデバイス断面図である。

【図8】図8は、窒化膜ベースのHEMT(高電子移動度トランジスタ)デバイスのユニットセルの断面模式図である。

【図9】図9は、図8に示した図と異なる構成を有する窒化膜ベースのHEMTデバイスのユニットセルの断面模式図である。

【図10】図10は、フィールドプレート距離が、デバイス性能に与える影響を示すグラフである。

【発明を実施するための形態】

【0009】

(本発明の詳細な説明)

以下の好ましい実施形態の記述の中で、その記述の一部を形成する添付図面を参照する。その添付図面は、本発明が実施されうる特定の実施形態を図によって示すものである。本発明の範囲から逸脱することなく、他の実施形態も利用されうるし、構造的な変更もなされうることは、理解されるべきである。

【0010】

(概観)

本発明は、電界効果型トランジスタ(FET)用のシングルゲートまたはマルチゲートフィールドプレート構造を実現するためのものである。本発明は、シンプルで、典型的に十分制御された連続的なプロセッシングステップ(誘電性材料の堆積または成長、誘電性材料のエッチング、および、メタル蒸着)を用いる。

【0011】

(製造プロセス)

図1A、図1B、図2A、図2B、図3A、図3B、図4A、および、図4Bに、本発明の一実施形態に基づく製造プロセスを、一つの可能な形で実現するときのステップを示す。ここで、製造プロセスには、ゲートフィールドプレートを製造する方法を含む。

【0012】

図1Aは、電界効果トランジスタ(FET)10の断面図で、図1Bはその平面図である。電界効果型トランジスタ10は、ソースオーミックコンタクト12と、ドレインオーミックコンタクト14、ゲートコンタクト16、および、活性領域18を含む。製造プロセスの各ステップは、電界効果型トランジスタ10あるいは他のデバイスに適用される。一般的に、本方法は、誘電性材料の堆積または成長、誘電性材料のエッチング、および、メタル蒸着の連続的なステップの実施を包含する。これは、デバイスの表面に、1以上のフィールドプレートを生成するためである。ここで、各ステップは、フィールドプレートオペレーションを厳しく制御することができ、表面に堆積された誘電性材料は、活性領域18から除去される必要がない。そのため、誘電性材料に与えるダメージの少ない乾式または湿式エッチングプロセスを用いることなく、フィールドプレートされたデバイスを実現できることである。この実施ステップは、さらに、以下のステップを包含する。(1)デバイスの真性および外因性領域に、誘電性材料を堆積または成長させ、ここで、誘電性材料の厚さは、デバイスが適切な動作を実行するために制御され、(2)乾式または湿式エッチングプロセス、あるいは、リフトオフプロセスで、誘電性材料をパターニングし、誘電性材料が、主として、デバイスの活性領域に残るようにし、そして、(3)パターニングされた誘電性材料上にフィールドプレートを蒸着させ、ここで、ゲートコンタクトおよびフィールドコンタクトが少なくとも外因性領域の片側(one side)で電気的に短絡され、両コンタクト間に低抵抗接続を提供する。これらステップは、図2A、図2B、図3A、図3B、図4A、および、図4Bとともに、以下に、より詳細に記述される。

【0013】

図2Aはデバイスの断面図で、図2Bはデバイスの平面図であり、これらは製造プロセスの第一ステップを示す。このステップには、デバイス10の真性および外因性領域に、誘電性材料20を堆積または成長させることを含む。誘電性材料20の厚さは、最終デバイス10が適切な動作を実行するために制御されるべき、重要なパラメータである。しかしながら、これは、例えば、PECVD(プラズマ化学気相成長)などの多くの堆積/成長技術で、通常、十分制御されたプロセスである。典型的な材料としては、シリコン窒化物およびシリコン酸化物であるが、乾式または湿式エッチング、あるいは、リフトオフで、パターニングさせることが可能であれば、他の材料も使うことができる。

【0014】

図3Aは、デバイス断面図で、図3Bはデバイス平面図であり、これらは製造プロセスの第二ステップを示す。このステップには、デバイスの外因性領域22から、エッチングあるいは除去で、誘電性材料20をパターニングすることを含む。これは、誘電性材料20が、主として、デバイス10の活性領域18に残るようにするためである。パターンがエッチングで形成された場合、そのステップの間、デバイスを形成する半導体材料にダメージを与えうる任意の乾式または湿式エッチングに、活性領域18の表面を、一切曝さないので、デバイス10の表面が保護されるということは、強調されるべきである。このステップの後に、オーミックコンタクト12、14は、デバイスの外因性領域22に属するゲート部16とともに、電気的にアクセス可能となる。

【0015】

図4Aは、デバイス断面図で、図4Bはデバイス平面図であり、これらは製造プロセスの第三ステップを示す。このステップには、パターンニングされた誘電性材料20上に、フィールドプレート24を生成することを含む。ここで、ゲート16コンタクトおよびフィールドプレート24コンタクトは、両コンタクト間が低抵抗接続となるように、外因性領域の少なくとも片側で電気的に短絡されている。好ましくは、メタル蒸着は、フィールドプレート24を形成するために用いられる。ここで、フィールドプレート24は、メタルストライプまたはメタルコンタクトからなる。フィールドプレート24は、ゲート16ドレインのアクセス領域に位置することで、活性領域18の調節能力を提供し、その結果、高いRF信号下での適切なデバイス動作を妨げる表面トラッピングの影響を減少させることができる。フィールドプレート24は、デバイスの真性領域の両側に接続されており、ゲート16およびフィールドプレート24とは、外因性領域22の少なくとも片側で、電気的に短絡されており、その2つのメタル線間に低抵抗接続を提供している。フィールドプレート24のオフセットおよび長さは、狙いとするデバイス性能、すなわち、絶縁破壊電圧やRF性能などを考慮して、最適化される。

【0016】

マルチフィールドプレートが必要とされる場合には、図2A、図2B、図3A、図3B、図4A、および、図4Bとともに示した三つのステップ(誘電性材料の堆積または成長、誘電性材料のエッチング、および、メタル蒸着)が繰り返されて、可能となる。

【0017】

図5Aは、デバイス断面図で、図5Bはデバイス平面図であり、これらは、マルチゲートフィールドプレートで使う、マルチ接続を形成した一例を示す。これは、ゲート抵抗を減少させるためであり、これによって、大周辺デバイスおよび/またはサブミクロンゲートデバイスの性能を向上させることができる。本例は、2段フィールドプレート構造であり、誘電性材料26の更なる層と、メタルストライプまたはメタルコンタクトからなる更なるフィールドプレート28を含む。誘電性材料26の厚さ、ゲート16と他のフィールドプレート24とを考慮したフィールドプレート28の長さとオフセット、および、導入されるフィールドプレート24、28の数が、製造プロセスパラメータを構成する。マルチフィールドプレート24、28を使うことで、デバイス10の設計は、さらに自由になり、高電圧デバイス10の実現にも大きなインパクトをもたらす。

【0018】

また、本発明の利点は、大周辺デバイスのゲート抵抗によって引き起こされるRF性能低下を緩和する可能性である。典型的には、最大変動周波数(fmax)は、ゲート抵抗増加によるゲートフィンガー幅の拡大で、減少する。

【0019】

図6は、fmax依存性とゲートフィンガー幅との関係をシミュレーションしたグラフである。グラフに示すように、活性領域の両端で短絡されたフィールドプレート構造を導入すると、大きなフィンガー幅のデバイスのfmax性能は、向上する。ゲート抵抗Rgに等価な抵抗Rfを有し、活性領域の両側に接続されたフィールドプレートを使うと、fmax性能は著しく向上する。更なる向上は、フィールドプレート抵抗を下げることで、達成される。フィールドプレート構造によって追加された寄生容量が、真性デバイスの寄生容量に比べ、無視できる程度の場合のみ、この減少が見られることは、強調されるべきである。これは、誘電性材料を適切に選択し、その厚さを適切に選択することで達成でき、プロセスの最適化として、考えられねばならない。

【0020】

ゲートとフィールドプレート間のマルチ接続は、また、ゲート抵抗の著しい減少を招く。RF動作が著しく低下しないマルチ接続を達成するためには、活性領域の小部分をゲート堆積の前にエッチングする。これは、デバイスのRF動作を悪化させずに、ゲートとフィールドプレートの間にマルチ接続を生成するためである。

【0021】

この領域において、ゲートプレートおよびフィールドプレートは、デバイスに何ら寄生容量を追加することなく、接続されうる。繰り返しになるが、デバイス性能が改善するのは、導入された寄生容量が、真性デバイスの寄生容量に比し、小さい場合のみである。さらに、個々の活性領域間のスペーシングは、従来型配置のデバイスに比し、熱インピーダンスをより効率的にするように、設計するために使われている。

【0022】

重要なパラメータは、誘電性材料の選択、その誘電性材料の厚さ、フィールドプレートの長さである。これらの重要なパラメータは、ここで提案する製造プロセスの各ステップを最適化する上で、考えられなくてはならない。

【0023】

本方法を使うことで、エアブリッジの数を減らした大周辺デバイスの製造ができる。さらに、サブミクロンデバイスの製造にあたっては、本発明の利点を活かすことができる。典型的には、サブミクロンゲートは、T字型プロセス(T−shape process)を用いて、製造される。なぜなら、T字型にすると、標準のゲート形状に比べ、ゲート抵抗が減少するからである。サブミクロンゲートであっても、T字型プロセスを用いないマルチ接続を形成すると、ゲート抵抗を低くすることができる。

【0024】

さらに、平行なゲートコンタクトは、誘電性材料の厚さを適切に調整して、誘電性材料のトップに堆積されることができる。これは、デバイスの外因性領域上の平行なフィールドプレートを用いたマルチ接続を形成することで、ゲート抵抗を著しく減少させるためである。低い抵抗の経路は、ゲートプレートとフィールドプレートとの間の接続が起こる幅を適切に選択することで、平行なフィールドプレートによって、提供される。

【0025】

図7Aはデバイスの断面図で、図7Bはデバイスの平面図で、図7Cはデバイス断面図であり、これらは、ゲート抵抗を減らしたマルチフィールドプレート構造の例を示したものである。さらに、図7A、図7B、および、図7Cに示すように、ゲートソースアクセス領域をカバーするフィールドプレートを有することで、デバイスの線形性能を向上するため、ソースアクセス抵抗を調節するためにも、使われる。

【0026】

(ガリウム窒化物ベースのフィールドプレートを有する高電子移動度トランジスタ)

AlGaN/GaNの高電子移動度トランジスタ(HEMT)を含むGaNベースのトランジスタは、RF周波数、マイクロ波周波数、および、ミリ波周波数で、非常に高い電圧で、かつ、ハイパワーでの動作が可能である。しかしながら、電子トラッピング、および、それに続くDC特性とRF特性との違いによって、これらデバイスの性能に、制限がかけられていた。このトラッピング問題を緩和するために、SiNパッシベーションが用いられ、成功を収めてきた結果、10GHzで、電力密度10W/mmを超える高性能デバイスが可能になった。例えば、[3]は、GaNトランジスタのトラッピングの影響を減らすための方法と構造とを開示している。しかしながら、こうした構造に存在する高電界のために、電荷トラッピングは、相変わらず、問題となっている。

【0027】

本発明は、AlGaN/GaN HEMTパワーデバイスの性能向上に使われて、成功されてきた。4GHz動作では、サファイア基板において、電力密度は12W/mmが、シリコンカーバイド基板では、電力密度18.8W/mmが、それぞれ達成された。フィールドプレート製造にかかるプロセッシングのステップがシンプルであるので、本発明は、AlGaN/GaN HEMTの技術や他の半導体デバイスの開発に使われうる。適切に設計されたマルチフィールドプレートを使うと、このようなデバイスの絶縁破壊と大RF信号性能とを両方とも、大いに改善する。

【0028】

GaNベースのHEMTは、チャネル層、および、そのチャネル層上のバリア層とを含む。メタルソースコンタクトとドレインオーミックコンタクトは、バリア層に接して、形成される。ゲートコンタクトは、ソースコンタクトとドレインコンタクトの間のバリア層上(on)に形成され、スペーサ層は、バリア層の上に(above)形成される。スペーサ層は、誘電性層、アンドープの(undoped)または空乏化した(depleted)AlxGa1−xN(0≦x≦1)材料、あるいは、その組合せを含みうる。伝導性のフィールドプレートは、スペーサ層の上に(above)形成され、ゲートコンタクトの端からドレインコンタクトへ向かって、距離Lf(フィールドプレート距離)拡がる。フィールドプレートは、ゲートコンタクトに、電気的に接続されていてもよい。一部の実施形態においては、フィールドプレートは、ゲートコンタクトの成長(extension)と同じ堆積ステップの間に、形成される。また、一部の実施形態においては、フィールドプレートとゲートコンタクトは、別個の堆積ステップの間に形成される。この配置は、デバイスのピーク電界を減少し、この結果、絶縁破壊電圧も高くなり、トラッピングも減少する。電界の減少は、電流リークの減少や信頼性向上といった他のメリットにも繋がる。

【0029】

本発明の一実施形態を図8に示す。これは、窒化物ベースのHEMTデバイスのユニットセル30の断面模式図である。特に、デバイス30は、基板32を含む。基板32は、シリコンカーバイド、サファイア、スピネル、ZnO、シリコン、あるいは、III族窒化物材料の成長をサポートできる他の任意の材料を含みうる。AlzGa1−zN(0≦z≦1)の核形成(nucleation)層34は、MOCVD(有機金属化学気相成長法)、HVPE(ハイドライド気相成長法)、あるいは、MBE(分子線成長法)などのエピタキシャル結晶成長法で、基板32上に成長される。核形成層34の形成は、基板32の材料に依存しうる。例えば、様々な基板上に核形成層34を形成する方法は、[4]と[5]に教示されている。シリコンカーバイド基板32上に核形成層34を形成する方法は、[6]、[7]、および、[8]に開示されている。

【0030】

高抵抗のIII族窒化物チャネル層36は、核形成層34上の形成される。チャネル層36は、AlxGayIn(1−x−y)N(0≦x≦1、0≦y≦1、x+y≦1)を含みうる。次いで、AlxGa1−xN(0≦x≦1)のバリア層38は、チャネル層36上に形成される。チャネル層36とバリア層38の各層は、III族窒化物材料のドープまたはアンドープの層からなりうるサブ層を含みうる。例示的な構造は、[3]、[9]、[10〕、[11]、および、[12]に示されている。他の窒化物ベースのHEMTの構造は、[13]、および、[14]に示されている。

【0031】

図8に示される実施形態では、III族窒化物半導体スペーサ層40は、AlxGa1−xNバリア層38上に成長される。スペーサ層40の組成は、均一であっても、勾配を有していてもよい。スペーサ層40は、アンドープされることもあり、成長すると、完全に空乏化されるように設計されることもあるが、その一方のみ、その双方でもよい。

【0032】

ソース電極42とドレイン電極44は、バリア層38を介し、オーミックコンタクトをするように形成される。これは、電流がソース電極42とドレイン電極44との間に流れるようにするためである。その経路は、ゲート電極46に適切なレベルのバイアス電圧を印加したとき、チャネル層36とバリア層38間のヘテロ界面で生じる二次元電子ガス(2DEG)を介して(via)である。ソース電極42とドレイン電極44の形成は、上記で参照した特許文献および刊行物に詳細に記載されている。

【0033】

スペーサ層40は、エッチングされえて、ゲート電極46は、そのゲート電極46の底が、バリア層38の表面となるように堆積されうる。ゲート電極46を形成するメタルは、スペーサ層40を横切って拡がるように、パターニングされてもよい。それは、ゲート46の最上部が、ゲート46の端からドレイン44に向かって、距離Lf拡がるフィールドプレート構造48を形成するためである。別の言い方をすれば、スペーサ層40に残るゲート46のメタル部分が、エピタキシャルフィールドプレート48を形成する。最終的に、その構造は、シリコン窒化物のような誘電性パッシベーション層50で、覆われる。誘電性パッシベーション層50を形成する方法は、上記で参照した特許文献および刊行物に詳細に記載されている。

【0034】

また、本発明の別の実施形態が、図9に示されている。これは、図8に示した図と異なる構成を有する窒化膜ベースのHEMTデバイスのユニットセル30の断面模式図である。図9に示すデバイス30の基板32、核形成層34、チャネル層36、および、バリア層38は、図8に示す各層と対応する同じ層である。一部の実施形態では、基板32には、半絶縁性の4H−SiC(ノースカロライナ州DurhamのCree,Inc.より市販)を含み、核形成層34は、AlNで形成され、また、チャネル層36は、2μm厚のGaN:Fe層を含み、このとき、バリア層38は、0.8nmのAlNおよび22.5nmのAlxGa1−xNを含む。ここで、PL(光ルミネセンス)測定によると、x=0.195である。

【0035】

ゲート電極46は、バリア層38の形成後に形成され、パッシベーション層50がデバイスに堆積される。次いで、フィールドプレート48が、ゲート46とオーバーラップし、ゲート−ドレイン領域で距離Lf拡がるように、パッシベーション層50上に形成される。図9に示す実施形態では、パッシベーション層50は、フィールドプレート48のスペーサ層としての役割を果たす。ゲート46の上の(above)フィールドプレート48のオーバーラップ、および、ゲート−ドレイン領域での拡がり量は、最適な結果を得るために、変更されうる。フィールドプレート48とゲート46は、ビア(via)あるいは他の接続(図示せず)によって、接続している。

【0036】

一部の実施形態において、フィールドプレート48は、距離Lf0.2〜1μm拡がりうる。一部の実施形態において、フィールドプレート48は、距離Lf0.5〜0.9μm拡がりうる。好ましい実施形態として、フィールドプレート48は、距離Lf0.7μm拡がりうる。

【0037】

図9に従う構造GaNベースのHEMT構造が、構築され、テストされた。そのデバイスは、120Vと4GHzで動作したとき、55%の電力付加効率(PAE)、電力密度32W/mmを達成した。

【0038】

フィールドプレート距離(Lf)がデバイス性能に与える影響が、テストされた。デバイスは、図9の実施形態に、概ね従って、製造された。ただし、フィールドプレート長Lfは、0〜0.9μmと距離を変化させた。その後、得られたデバイスのPAEを測定した。図10に示すように、フィールドプレート長が0.5μmを一度超えると、PAEは向上し、その最適長さは約0.7μmであった。しかしながら、最適長さは、個々のデバイス設計に依存しうるし、また、動作する電圧と周波数にも依存しうる。

【0039】

(参考文献)

以下の参考文献が、本明細書中で、参考文献として、組み込まれている。

[1] K Asanoら、「Novel High Power AlGaAs/GaAs HFET with a Field−Modulating Plate Operated at 35V Drain Voltage」 IEDM Conference、 1998、 pp.59−62

[2] Y. Andoら、「10−W/mm AlGaN−GaN HFET With a Field Modulating Plate」、 IEEE Electron Device Letters, Vol. 24, No. 5, 2003年5月, pp. 289−291.

[3]米国特許第6,586,781号,2003年7月1日発行、Wuら、「Group III nitride based FETs and HEMTs with reduced trapping and method for producing the same」

[4]米国特許第5,290,393号、1994年3月1日発行、Nakamura、「Crystal growth method for gallium nitride−based compound semiconductor」

[5]米国特許第5,686,738号、1997年11月11日発行、Moustakas、「Highly insulating monocrystalline gallium nitride thin films.」

[6]米国特許第5,393,993号、1995年2月28日発行、Edmondら、「Buffer structure between silicon carbide and gallium nitride and resulting semiconductor devices」

[7]米国特許第5,523,589号、1996年6月4日発行、Edmondら、「Vertical geometry light emitting diode with group III nitride active layer and extended lifetime」

[8]米国特許第5,739,554号、1998年4月14日発行、Edmondら、「Double heterojunction light emitting diode with gallium nitride active layer」

[9]米国特許第6,316,793号、2001年11月13日発行、Sheppardら、「Nitride based transistors on semi−insulating silicon carbide substrates」

[10]米国特許第6,548,333号、2003年4月15日発行、Smith、「Aluminum gallium nitride/gallium nitride

high electron mobility transistors having a gate contact on a gallium nitride based cap segment」

[11]米国特許出願公開番号第2002/0167023号、2002年11月14日公開、Chavarkar, Prashantら、「Group−III nitride based high electron mobility transistor (HEMT) with barrier/spacer layer」

[12]米国特許出願公開番号第2003/0020092号、2003年1月30日公開,Parikh, Primitら、「Insulating gate AlGaN/GaN HEMT」

[13]米国特許第5,192,987号、1993年3月9日発行、Khanら、「High electron mobility transistor with GaN/AlxGa1−xN heterojunctions」

[14]米国特許第5,296,395号,1994年3月22日発行、Khanら、「Method of making a high electron mobility transistor」

[15] Y.−F. Wu、 A. Saxler、 M. Moore、 R.P.

Smith、 S. Sheppard、 P.M. Chavarkar、 T. Wisleder、 U.K. Mishra、 P. Parikh、「30 W/mm GaN HEMTs by field plate optimization」, IEEE EDL、 Vol.25、 No.3、 pp.117−119、2004年3月

[16] S.Karmalkar、 U.K. Mishra、 Very high

voltage AlGaN−GaN HEMT using a field plate deposited on a stepped insulator, Solid State Electronics, 45(2001)1645−1652.

(結論)

本明細書は、本発明の好ましい実施形態の記載を結論付けるものである。本発明の一以上の実施形態について前述してきたが、これは例示と記述の目的のために、示されたものである。ここに開示した細かな形式で、本発明の網羅を意図したものでも、本発明の制限を意図したものではない。上記に教示したことから、修正や変更を多数行うことも可能である。本発明の範囲は、ここに記載した詳細な記述で限定されることを意図しておらず、むしろ、以下に述べる請求項で限定されることを意図している。

【技術分野】

【0001】

(関連出願の参照)

本出願は、以下の同時係属中で、同一出願人による米国仮特許出願(シリアル番号第60/501,557号、題名「FABRICATION OF SINGLE OR MULTIPLE GATE FIELD PLATES」、Alessandro Chini、 Umesh K. Mishra、 Primit Parikh、 および、Yifeng Wuによって、2003年9月9日に出願、代理人整理番号第30794.105−US−P1号)の米国法典第35巻第119条(e)項の利益を主張するものであり、その出願がここに援用される。

【0002】

(連邦によるスポンサー研究および開発に関する声明)

本発明は、ONR MURIプログラムによって与えられた助成金第N00014−01−1−0764号、および、AFOSR MURIプログラムによって与えられた助成金第F49620−99−1−0296号の下、政府支援により行われた。政府は、本発明に関し、特定の権利を有する。

【0003】

(本発明の分野)

本発明は、半導体デバイスに関し、特に、シングルゲートまたはマルチゲートフィールドプレートの製造に関する。

【背景技術】

【0004】

(注:本出願は、カッコ内の参照番号(例えば、[x]で、本明細書に示す様々な文献を参照している。これら刊行物のリストは、参照番号順に並べ、「参考文献」と題する節で、以下に列挙される。これら刊行物のそれぞれは、ここに援用される。)

半導体ベースの電界効果型トランジスタ(FET)において、動作中に、ゲート−ドレインのアクセス領域で、大きな電界が発生する。フィールドプレーティングは、高電界動作下におけるデバイス性能向上と、表面トラッピング現象を緩和する周知の技術である[1]、[2]。例えば、フィールドプレーティングは、高電界でデバイス動作中に起こる有害な影響全て(絶縁破壊電圧、トラッピングの影響、信頼性)を緩和する効果的で、周知の技術となっている。

【0005】

フィールドプレーティングの基本的概念は、デバイス活性領域の縦方向空乏に依存するもので、これにより、横方向の空乏領域に、より拡がりを持たせることができる。この結果、ある与えられたバイアス電圧において、デバイス活性領域の電界がより低くなり、デバイスが高電界で動作しているときに常に生じる有害な影響全て(低い絶縁破壊電圧、トラッピング現象、低い信頼性)を緩和できる。さらに、ゲート−ドレインアクセス領域に位置するフィールドプレートは、デバイス活性領域の調節能力もあり、その結果、高い無線周波数(RF)信号下での適切なデバイス動作を妨げる表面トラッピングの影響を減少させる。

【0006】

しかしながら、必要とされているのは、シングルゲートまたはマルチゲートフィールドプレート製造の改善方法、および、シングルゲートまたはマルチゲートフィールドプレートを組み込んだ改善構造である。

【発明の概要】

【課題を解決するための手段】

【0007】

(本発明の概要)

本発明の実施形態は、シングルゲートまたはマルチゲートフィールドプレート製造の改善方法を提供する。本発明に基づく製造プロセスは、電界効果型トランジスタの表面に、誘電性材料を堆積または成長させ、誘電性材料をエッチングし、および、メタルを蒸着させる、連続的なステップを含む。本製造プロセスの利点は、誘電性材料の厚みを厳しく(tight)制御できること、および、電界効果型トランジスタを形成する半導体材料にダメージを与えうる任意の乾式または湿式エッチングプロセスに、デバイス活性領域の表面を、一切曝さないことを含む。さらに、デバイス表面に堆積された誘電性材料は、デバイスの真性領域から除去される必要はない。このため、乾式または湿式エッチングプロセスで生じるダメージを受けることなく、フィールドプレートされたデバイスを、実現することができる。マルチゲートフィールドプレートを使うと、マルチ接続を使用するので、ゲート抵抗を減らすことができ、大周辺デバイスおよび/またはサブミクロンゲートデバイスの性能を向上できる。最終的に、誘電性材料の厚みを適切に調整すると、平行なゲートコンタクトを誘電性材料の上に、堆積させることができる。これは、デバイスの外因性領域で、平行なゲートコンタクトを電気的に接続して、ゲート抵抗を著しく減少するためである。

例えば、本願発明は以下の項目を提供する。

(項目1)

1以上のゲートフィールドプレートの製造方法であって、該方法は、

デバイスの表面に1つ以上のフィールドプレートを形成するために、誘電性材料を堆積または成長させること、誘電性材料をエッチングすること、および、メタル蒸着することからなる連続的ステップを実行することを包含し、

該表面に堆積される該誘電性材料は、活性領域から除去される必要がなく、それによって、低ダメージの乾式または湿式エッチングプロセスを用いずに、フィールドプレートされたデバイスの実現を可能とする、方法。

(項目2)

前記ステップが、フィールドプレートオペレーションの厳しい制御を可能とする、項目1に記載の方法。

(項目3)

ゲート抵抗を減少させるために、マルチフィールドプレートを用いてマルチ接続を形成することをさらに包含する、項目1に記載の方法。

(項目4)

前記フィールドプレートをゲートドレインアクセス領域に配置することで、前記活性領域の調節能力を提供し、その結果、高い無線周波数(RF)信号下での適切なデバイス動作を妨げる表面トラッピングの影響を減少させる、項目1に記載の方法。

(項目5)

前記デバイスにダメージを与えうる前記乾式または湿式エッチングプロセスに、前記活性領域の前記表面を、一切曝さないようにすることをさらに包含する、項目1に記載の方法。

(項目6)

外因性領域にある少なくとも2つの平行なゲートを電気的に接続することで、ゲート抵抗を著しく減少させるために、前記誘電性材料の厚さを適切に調整して、該誘電性材料のトップに、平行なゲートコンタクトを堆積させることをさらに包含する、項目1に記載の方法。

(項目7)

前記デバイスが、ソースオーミックコンタクトとドレインオーミックコンタクト、ゲートコンタクト、および、活性領域を含む電界効果型トランジスタである、項目1に記載の方法。

(項目8)

前記実行ステップが、

(1)前記デバイスの真性および外因性領域に、前記誘電性材料を堆積または成長させることと、

(2)該誘電性材料が、主として、前記デバイスの活性領域に残るように、該誘電性材料をパターニングすることと、

(3)該パターニングされた誘電性材料にフィールドプレートを生成することであって、ゲートフィールドコンタクトとフィールドプレートコンタクトとが、少なくとも、前記外因性領域での、少なくとも片側で電気的に短絡され、それによって、両コンタクト間に低抵抗接続を提供する、ことと

をさらに包含する、項目1に記載の方法。

(項目9)

前記誘電性材料の厚さが、前記デバイスの適切な動作を達成するために、制御される、項目8に記載の方法。

(項目10)

前記パターニングステップ(3)が、乾式または湿式エッチングプロセス、あるいは、リフトオフプロセスによって、前記誘電性材料をパターニングすることを包含する、項目8に記載の方法。

(項目11)

前記生成ステップ(3)が、前記誘電性材料上に、フィールドプレートを蒸着することを包含する、項目8に記載の方法。

(項目12)

複数のフィールドプレートを形成するために、前記ステップ(1)〜(3)が繰り返される、項目8に記載の方法。

(項目13)

前記フィールドプレートが、ゲート抵抗Rgに等価な抵抗Rfを有する、項目8に記載の方法。

(項目14)

前記フィールドプレートが、前記デバイスの真性領域の両側に接続されている、項目8に記載の方法。

(項目15)

ゲート抵抗を減少させるために、前記ゲートと前記フィールドプレートとの間に、マルチ接続を形成することをさらに包含する、項目8に記載の方法。

(項目16)

前記形成ステップが、前記ゲートと前記フィールドプレートとの間にマルチ接続を形成するための該ゲートの堆積の前に、前記活性領域の小部分をエッチングすることを包含する、項目15に記載の方法。

(項目17)

前記デバイスの熱インピーダンスを設計するために、前記活性領域間にスペーシングすることをさらに包含する、項目15に記載の方法。

(項目18)

前記デバイスは、エアブリッジの数を減少させた大周辺デバイスを含む、項目15に記載の方法。

(項目19)

前記生成ステップは、ゲート抵抗を低くするために、T字型プロセスを用いずに、前記マルチ接続を生成するステップを包含する、項目15に記載の方法。

(項目20)

前記生成ステップは、平行なフィールドプレートを用いて、前記マルチ接続を生成するステップを包含する、項目15に記載の方法。

(項目21)

前記生成ステップは、デバイスの線形性能を向上させるために、ソースアクセス抵抗を調節するために、ゲートソースアクセス領域をカバーする前記フィールドプレートを形成するステップを包含する、項目20に記載の方法。

(項目22)

項目1に記載の方法を使用して製造される、デバイス。

(項目23)

ゲートフィールドプレートを製造する方法であって、

(a)デバイスの真性領域と外因性領域上に、誘電性材料を堆積または成長することと、(b)該誘電性材料が、主として、該デバイスの活性化領域に残るように、該誘電性材料をパターニングすることと、

(c)該パターニングされた誘電性材料の上に、フィールドプレートを生成することであって、ゲートコンタクトとフィールドコンタクトは、該外因性領域の少なくとも片側で電気的に短絡され、それによって、両コンタクト間に低抵抗接続を提供する、ことと

を包含する、方法。

(項目24)

前記デバイスを適切な動作を達成するために、前記誘電性材料の厚さが制御されている、項目23に記載の方法。

(項目25)

前記パターニングステップ(b)は、乾式エッチングまたは湿式エッチング、あるいは、リフトオフプロセスによって、前記誘電体材料をパターニングすることを包含する、項目23に記載の方法。

(項目26)

前記生成ステップ(c)は、前記パターニングされた誘電体材料上に、フィールドプレートを蒸着することを包含する、項目23に記載の方法。

(項目27)

前記ステップ(a)と(b)は、複数のフィールドプレートを生成するために、繰り返し行われる、項目23に記載の方法。

(項目28)

基板と、

該基板上に成長させた核形成層と

該核形成層上に形成されたチャネル層と、

該チャネル層に形成されたバリア層と、

該バリア層上に成長させた半導体スペーサ層と、

ソース電極とドレイン電極であって、該ゲート電極が適切なレベルでバイアスされたとき、該ソース電極と該ドレイン電極との間で電流が流れるように、該バリア層を介してオーミックコンタクトするように形成された、ソース電極とドレイン電極と

を備える、高電子移動度トランジスタ(HEMT)であって、

該ゲート電極の少なくとも一部分がバリア層の表面上にあるように、該スペーサ層はエッチングされ、該ゲート電極は堆積され、

該ゲート電極が、該ゲート電極から該ドレイン電極に向かってある距離拡がるフィールドプレートを形成するように、該ゲート電極の一部分は、該スペーサ層を横切って拡がるようにパターニングされている、HEMT。

(項目29)

前記電流は、前記ゲート電極が適切なレベルでバイアスされているとき、前記チャネル層とバリア層との間のヘテロ界面で生じる二次元電子ガス(2DEG)を介して、前記ゲート電極とドレイン電極との間を流れる、項目28に記載のHEMT。

(項目30)

前記スペーサ層上の前記ゲート電極の一部分は、エピタキシャルフィールドプレートを形成する、項目28に記載のHEMT。

(項目31)

前記スペーサ層をカバーする誘電性パッシベーション層をさらに備える、項目28に記載のHEMT。

(項目32)

前記スペーサ層は、誘電性層、アンドープのまたは空乏化したAlxGa1−xN(0≦x≦1)材料の層、あるいは、その組合せを含む、項目28に記載のHEMT。

(項目33)

前記フィールド層は、前記スペーサ層の上に形成され、前記ゲート電極の端から前記ドレイン電極に向かって、距離Lf(フィールドプレート距離)まで拡がる、項目28に記載のHEMT。

(項目34)

前記フィールドプレートは、前記ゲート電極に電気的に接続されている、項目28に記載のHEMT。

(項目35)

前記フィールドプレートは、前記ゲート電極の成長と同じ堆積ステップの間に形成される、項目28に記載のHEMT。

(項目36)

前記フィールドプレートとゲート電極は、別個の堆積ステップの間に形成される、項目28に記載のHEMT。

(項目37)

前記基板は、シリコンカーバイド、サファイア、スピネル、酸化亜鉛、シリコン、あるいは、III族窒化物材料の成長をサポートできる他の任意の材料からなる、項目28に記載のHEMT。

(項目38)

前記核形成層は、AlzGa1−zN(0≦z≦1)核形成層である、項目28に記載のHEMT。

(項目39)

前記核形成層は、AlN核形成層である、項目28に記載のHEMT。

(項目40)

前記チャネル層は、高抵抗のIII族窒化物チャネル層である、項目28に記載のHEMT。

(項目41)

前記チャネル層は、AlxGayIn(1−x−y)N(0≦x≦1、0≦y≦1、x+y≦1)を含む、項目28に記載のHEMT。

(項目42)

前記チャネル層は、GaN:Feを含む、項目28に記載のHEMT。

(項目43)

前記バリア層は、AlxGa1−xN(0≦x≦1)を含む、項目28に記載のHEMT。

(項目44)

前記バリア層は、AlNおよびAlGaNを含む、項目28に記載のHEMT。

(項目45)

前記チャネル層とバリア層のそれぞれは、III族窒化物材料のドープまたはアンドープの層であるサブ層を含む、項目28に記載のHEMT。

(項目46)

前記スペーサ層は、AlxGa1−xNバリア層上に成長される、III族窒化物半導体スペーサ層を含む、項目28に記載のHEMT。

(項目47)

前記スペーサ層は、均一な組成を有する、項目28に記載のHEMT。

(項目48)

前記スペーサ層は、勾配のある組成を有する、項目28に記載のHEMT。

(項目49)

前記スペーサ層は、アンドープである、項目28に記載のHEMT。

(項目50)

前記スペーサ層は、成長すると完全に空乏化する、項目28に記載のHEMT。

(項目51)

前記ゲート電極は前記バリア層が形成された後に形成され、パッシベーション層は前記デバイス上に堆積され、

前記フィールドプレートは、該ゲートをオーバーラップし、ゲート−ドレイン領域で距離Lf拡がるように、該パッシベーション層に次いで形成され、該パッシベーション層は該フィールドプレートに対してスペーサ層として働く、項目28に記載のHEMT。

【図面の簡単な説明】

【0008】

【図1A】図1Aは、電界効果トランジスタ(FET)の断面図である。

【図1B】図1Bは、電界効果トランジスタ(FET)の平面図である。

【図2A】図2Aは、誘電性材料堆積/成長デバイスの断面図である。

【図2B】図2Bは、誘電性材料堆積/成長デバイスの平面図である。

【図3A】図3Aは、デバイスの外因性部分から、誘電性材料の除去を示すデバイス断面図である。

【図3B】図3Bは、デバイスの外因性部分から、誘電性材料の除去を示すデバイス平面図である。

【図4A】図4Aは、ゲートフィールドプレートの蒸着を示すデバイス断面図である。

【図4B】図4Bは、ゲートフィールドプレートの蒸着を示すデバイス平面図である。

【図5A】図5Aは、マルチフィールドプレート構造の一例を示すデバイス断面図である。

【図5B】図5Bは、マルチフィールドプレート構造の一例を示すデバイス平面図である。

【図6】図6は、fmax依存性とゲートフィンガー幅との関係をシミュレーションしたグラフである。

【図7A】図7Aは、ゲート抵抗を減らしたマルチフィールドプレートデバイスのデバイス断面図である。

【図7B】図7Bは、ゲート抵抗を減らしたマルチフィールドプレートデバイスのデバイス平面図である。

【図7C】図7Cは、ゲート抵抗を減らしたマルチフィールドプレートデバイスのデバイス断面図である。

【図8】図8は、窒化膜ベースのHEMT(高電子移動度トランジスタ)デバイスのユニットセルの断面模式図である。

【図9】図9は、図8に示した図と異なる構成を有する窒化膜ベースのHEMTデバイスのユニットセルの断面模式図である。

【図10】図10は、フィールドプレート距離が、デバイス性能に与える影響を示すグラフである。

【発明を実施するための形態】

【0009】

(本発明の詳細な説明)

以下の好ましい実施形態の記述の中で、その記述の一部を形成する添付図面を参照する。その添付図面は、本発明が実施されうる特定の実施形態を図によって示すものである。本発明の範囲から逸脱することなく、他の実施形態も利用されうるし、構造的な変更もなされうることは、理解されるべきである。

【0010】

(概観)

本発明は、電界効果型トランジスタ(FET)用のシングルゲートまたはマルチゲートフィールドプレート構造を実現するためのものである。本発明は、シンプルで、典型的に十分制御された連続的なプロセッシングステップ(誘電性材料の堆積または成長、誘電性材料のエッチング、および、メタル蒸着)を用いる。

【0011】

(製造プロセス)

図1A、図1B、図2A、図2B、図3A、図3B、図4A、および、図4Bに、本発明の一実施形態に基づく製造プロセスを、一つの可能な形で実現するときのステップを示す。ここで、製造プロセスには、ゲートフィールドプレートを製造する方法を含む。

【0012】

図1Aは、電界効果トランジスタ(FET)10の断面図で、図1Bはその平面図である。電界効果型トランジスタ10は、ソースオーミックコンタクト12と、ドレインオーミックコンタクト14、ゲートコンタクト16、および、活性領域18を含む。製造プロセスの各ステップは、電界効果型トランジスタ10あるいは他のデバイスに適用される。一般的に、本方法は、誘電性材料の堆積または成長、誘電性材料のエッチング、および、メタル蒸着の連続的なステップの実施を包含する。これは、デバイスの表面に、1以上のフィールドプレートを生成するためである。ここで、各ステップは、フィールドプレートオペレーションを厳しく制御することができ、表面に堆積された誘電性材料は、活性領域18から除去される必要がない。そのため、誘電性材料に与えるダメージの少ない乾式または湿式エッチングプロセスを用いることなく、フィールドプレートされたデバイスを実現できることである。この実施ステップは、さらに、以下のステップを包含する。(1)デバイスの真性および外因性領域に、誘電性材料を堆積または成長させ、ここで、誘電性材料の厚さは、デバイスが適切な動作を実行するために制御され、(2)乾式または湿式エッチングプロセス、あるいは、リフトオフプロセスで、誘電性材料をパターニングし、誘電性材料が、主として、デバイスの活性領域に残るようにし、そして、(3)パターニングされた誘電性材料上にフィールドプレートを蒸着させ、ここで、ゲートコンタクトおよびフィールドコンタクトが少なくとも外因性領域の片側(one side)で電気的に短絡され、両コンタクト間に低抵抗接続を提供する。これらステップは、図2A、図2B、図3A、図3B、図4A、および、図4Bとともに、以下に、より詳細に記述される。

【0013】

図2Aはデバイスの断面図で、図2Bはデバイスの平面図であり、これらは製造プロセスの第一ステップを示す。このステップには、デバイス10の真性および外因性領域に、誘電性材料20を堆積または成長させることを含む。誘電性材料20の厚さは、最終デバイス10が適切な動作を実行するために制御されるべき、重要なパラメータである。しかしながら、これは、例えば、PECVD(プラズマ化学気相成長)などの多くの堆積/成長技術で、通常、十分制御されたプロセスである。典型的な材料としては、シリコン窒化物およびシリコン酸化物であるが、乾式または湿式エッチング、あるいは、リフトオフで、パターニングさせることが可能であれば、他の材料も使うことができる。

【0014】

図3Aは、デバイス断面図で、図3Bはデバイス平面図であり、これらは製造プロセスの第二ステップを示す。このステップには、デバイスの外因性領域22から、エッチングあるいは除去で、誘電性材料20をパターニングすることを含む。これは、誘電性材料20が、主として、デバイス10の活性領域18に残るようにするためである。パターンがエッチングで形成された場合、そのステップの間、デバイスを形成する半導体材料にダメージを与えうる任意の乾式または湿式エッチングに、活性領域18の表面を、一切曝さないので、デバイス10の表面が保護されるということは、強調されるべきである。このステップの後に、オーミックコンタクト12、14は、デバイスの外因性領域22に属するゲート部16とともに、電気的にアクセス可能となる。

【0015】

図4Aは、デバイス断面図で、図4Bはデバイス平面図であり、これらは製造プロセスの第三ステップを示す。このステップには、パターンニングされた誘電性材料20上に、フィールドプレート24を生成することを含む。ここで、ゲート16コンタクトおよびフィールドプレート24コンタクトは、両コンタクト間が低抵抗接続となるように、外因性領域の少なくとも片側で電気的に短絡されている。好ましくは、メタル蒸着は、フィールドプレート24を形成するために用いられる。ここで、フィールドプレート24は、メタルストライプまたはメタルコンタクトからなる。フィールドプレート24は、ゲート16ドレインのアクセス領域に位置することで、活性領域18の調節能力を提供し、その結果、高いRF信号下での適切なデバイス動作を妨げる表面トラッピングの影響を減少させることができる。フィールドプレート24は、デバイスの真性領域の両側に接続されており、ゲート16およびフィールドプレート24とは、外因性領域22の少なくとも片側で、電気的に短絡されており、その2つのメタル線間に低抵抗接続を提供している。フィールドプレート24のオフセットおよび長さは、狙いとするデバイス性能、すなわち、絶縁破壊電圧やRF性能などを考慮して、最適化される。

【0016】

マルチフィールドプレートが必要とされる場合には、図2A、図2B、図3A、図3B、図4A、および、図4Bとともに示した三つのステップ(誘電性材料の堆積または成長、誘電性材料のエッチング、および、メタル蒸着)が繰り返されて、可能となる。

【0017】

図5Aは、デバイス断面図で、図5Bはデバイス平面図であり、これらは、マルチゲートフィールドプレートで使う、マルチ接続を形成した一例を示す。これは、ゲート抵抗を減少させるためであり、これによって、大周辺デバイスおよび/またはサブミクロンゲートデバイスの性能を向上させることができる。本例は、2段フィールドプレート構造であり、誘電性材料26の更なる層と、メタルストライプまたはメタルコンタクトからなる更なるフィールドプレート28を含む。誘電性材料26の厚さ、ゲート16と他のフィールドプレート24とを考慮したフィールドプレート28の長さとオフセット、および、導入されるフィールドプレート24、28の数が、製造プロセスパラメータを構成する。マルチフィールドプレート24、28を使うことで、デバイス10の設計は、さらに自由になり、高電圧デバイス10の実現にも大きなインパクトをもたらす。

【0018】

また、本発明の利点は、大周辺デバイスのゲート抵抗によって引き起こされるRF性能低下を緩和する可能性である。典型的には、最大変動周波数(fmax)は、ゲート抵抗増加によるゲートフィンガー幅の拡大で、減少する。

【0019】

図6は、fmax依存性とゲートフィンガー幅との関係をシミュレーションしたグラフである。グラフに示すように、活性領域の両端で短絡されたフィールドプレート構造を導入すると、大きなフィンガー幅のデバイスのfmax性能は、向上する。ゲート抵抗Rgに等価な抵抗Rfを有し、活性領域の両側に接続されたフィールドプレートを使うと、fmax性能は著しく向上する。更なる向上は、フィールドプレート抵抗を下げることで、達成される。フィールドプレート構造によって追加された寄生容量が、真性デバイスの寄生容量に比べ、無視できる程度の場合のみ、この減少が見られることは、強調されるべきである。これは、誘電性材料を適切に選択し、その厚さを適切に選択することで達成でき、プロセスの最適化として、考えられねばならない。

【0020】

ゲートとフィールドプレート間のマルチ接続は、また、ゲート抵抗の著しい減少を招く。RF動作が著しく低下しないマルチ接続を達成するためには、活性領域の小部分をゲート堆積の前にエッチングする。これは、デバイスのRF動作を悪化させずに、ゲートとフィールドプレートの間にマルチ接続を生成するためである。

【0021】

この領域において、ゲートプレートおよびフィールドプレートは、デバイスに何ら寄生容量を追加することなく、接続されうる。繰り返しになるが、デバイス性能が改善するのは、導入された寄生容量が、真性デバイスの寄生容量に比し、小さい場合のみである。さらに、個々の活性領域間のスペーシングは、従来型配置のデバイスに比し、熱インピーダンスをより効率的にするように、設計するために使われている。

【0022】

重要なパラメータは、誘電性材料の選択、その誘電性材料の厚さ、フィールドプレートの長さである。これらの重要なパラメータは、ここで提案する製造プロセスの各ステップを最適化する上で、考えられなくてはならない。

【0023】

本方法を使うことで、エアブリッジの数を減らした大周辺デバイスの製造ができる。さらに、サブミクロンデバイスの製造にあたっては、本発明の利点を活かすことができる。典型的には、サブミクロンゲートは、T字型プロセス(T−shape process)を用いて、製造される。なぜなら、T字型にすると、標準のゲート形状に比べ、ゲート抵抗が減少するからである。サブミクロンゲートであっても、T字型プロセスを用いないマルチ接続を形成すると、ゲート抵抗を低くすることができる。

【0024】

さらに、平行なゲートコンタクトは、誘電性材料の厚さを適切に調整して、誘電性材料のトップに堆積されることができる。これは、デバイスの外因性領域上の平行なフィールドプレートを用いたマルチ接続を形成することで、ゲート抵抗を著しく減少させるためである。低い抵抗の経路は、ゲートプレートとフィールドプレートとの間の接続が起こる幅を適切に選択することで、平行なフィールドプレートによって、提供される。

【0025】

図7Aはデバイスの断面図で、図7Bはデバイスの平面図で、図7Cはデバイス断面図であり、これらは、ゲート抵抗を減らしたマルチフィールドプレート構造の例を示したものである。さらに、図7A、図7B、および、図7Cに示すように、ゲートソースアクセス領域をカバーするフィールドプレートを有することで、デバイスの線形性能を向上するため、ソースアクセス抵抗を調節するためにも、使われる。

【0026】

(ガリウム窒化物ベースのフィールドプレートを有する高電子移動度トランジスタ)

AlGaN/GaNの高電子移動度トランジスタ(HEMT)を含むGaNベースのトランジスタは、RF周波数、マイクロ波周波数、および、ミリ波周波数で、非常に高い電圧で、かつ、ハイパワーでの動作が可能である。しかしながら、電子トラッピング、および、それに続くDC特性とRF特性との違いによって、これらデバイスの性能に、制限がかけられていた。このトラッピング問題を緩和するために、SiNパッシベーションが用いられ、成功を収めてきた結果、10GHzで、電力密度10W/mmを超える高性能デバイスが可能になった。例えば、[3]は、GaNトランジスタのトラッピングの影響を減らすための方法と構造とを開示している。しかしながら、こうした構造に存在する高電界のために、電荷トラッピングは、相変わらず、問題となっている。

【0027】

本発明は、AlGaN/GaN HEMTパワーデバイスの性能向上に使われて、成功されてきた。4GHz動作では、サファイア基板において、電力密度は12W/mmが、シリコンカーバイド基板では、電力密度18.8W/mmが、それぞれ達成された。フィールドプレート製造にかかるプロセッシングのステップがシンプルであるので、本発明は、AlGaN/GaN HEMTの技術や他の半導体デバイスの開発に使われうる。適切に設計されたマルチフィールドプレートを使うと、このようなデバイスの絶縁破壊と大RF信号性能とを両方とも、大いに改善する。

【0028】

GaNベースのHEMTは、チャネル層、および、そのチャネル層上のバリア層とを含む。メタルソースコンタクトとドレインオーミックコンタクトは、バリア層に接して、形成される。ゲートコンタクトは、ソースコンタクトとドレインコンタクトの間のバリア層上(on)に形成され、スペーサ層は、バリア層の上に(above)形成される。スペーサ層は、誘電性層、アンドープの(undoped)または空乏化した(depleted)AlxGa1−xN(0≦x≦1)材料、あるいは、その組合せを含みうる。伝導性のフィールドプレートは、スペーサ層の上に(above)形成され、ゲートコンタクトの端からドレインコンタクトへ向かって、距離Lf(フィールドプレート距離)拡がる。フィールドプレートは、ゲートコンタクトに、電気的に接続されていてもよい。一部の実施形態においては、フィールドプレートは、ゲートコンタクトの成長(extension)と同じ堆積ステップの間に、形成される。また、一部の実施形態においては、フィールドプレートとゲートコンタクトは、別個の堆積ステップの間に形成される。この配置は、デバイスのピーク電界を減少し、この結果、絶縁破壊電圧も高くなり、トラッピングも減少する。電界の減少は、電流リークの減少や信頼性向上といった他のメリットにも繋がる。

【0029】

本発明の一実施形態を図8に示す。これは、窒化物ベースのHEMTデバイスのユニットセル30の断面模式図である。特に、デバイス30は、基板32を含む。基板32は、シリコンカーバイド、サファイア、スピネル、ZnO、シリコン、あるいは、III族窒化物材料の成長をサポートできる他の任意の材料を含みうる。AlzGa1−zN(0≦z≦1)の核形成(nucleation)層34は、MOCVD(有機金属化学気相成長法)、HVPE(ハイドライド気相成長法)、あるいは、MBE(分子線成長法)などのエピタキシャル結晶成長法で、基板32上に成長される。核形成層34の形成は、基板32の材料に依存しうる。例えば、様々な基板上に核形成層34を形成する方法は、[4]と[5]に教示されている。シリコンカーバイド基板32上に核形成層34を形成する方法は、[6]、[7]、および、[8]に開示されている。

【0030】

高抵抗のIII族窒化物チャネル層36は、核形成層34上の形成される。チャネル層36は、AlxGayIn(1−x−y)N(0≦x≦1、0≦y≦1、x+y≦1)を含みうる。次いで、AlxGa1−xN(0≦x≦1)のバリア層38は、チャネル層36上に形成される。チャネル層36とバリア層38の各層は、III族窒化物材料のドープまたはアンドープの層からなりうるサブ層を含みうる。例示的な構造は、[3]、[9]、[10〕、[11]、および、[12]に示されている。他の窒化物ベースのHEMTの構造は、[13]、および、[14]に示されている。

【0031】

図8に示される実施形態では、III族窒化物半導体スペーサ層40は、AlxGa1−xNバリア層38上に成長される。スペーサ層40の組成は、均一であっても、勾配を有していてもよい。スペーサ層40は、アンドープされることもあり、成長すると、完全に空乏化されるように設計されることもあるが、その一方のみ、その双方でもよい。

【0032】

ソース電極42とドレイン電極44は、バリア層38を介し、オーミックコンタクトをするように形成される。これは、電流がソース電極42とドレイン電極44との間に流れるようにするためである。その経路は、ゲート電極46に適切なレベルのバイアス電圧を印加したとき、チャネル層36とバリア層38間のヘテロ界面で生じる二次元電子ガス(2DEG)を介して(via)である。ソース電極42とドレイン電極44の形成は、上記で参照した特許文献および刊行物に詳細に記載されている。

【0033】

スペーサ層40は、エッチングされえて、ゲート電極46は、そのゲート電極46の底が、バリア層38の表面となるように堆積されうる。ゲート電極46を形成するメタルは、スペーサ層40を横切って拡がるように、パターニングされてもよい。それは、ゲート46の最上部が、ゲート46の端からドレイン44に向かって、距離Lf拡がるフィールドプレート構造48を形成するためである。別の言い方をすれば、スペーサ層40に残るゲート46のメタル部分が、エピタキシャルフィールドプレート48を形成する。最終的に、その構造は、シリコン窒化物のような誘電性パッシベーション層50で、覆われる。誘電性パッシベーション層50を形成する方法は、上記で参照した特許文献および刊行物に詳細に記載されている。

【0034】

また、本発明の別の実施形態が、図9に示されている。これは、図8に示した図と異なる構成を有する窒化膜ベースのHEMTデバイスのユニットセル30の断面模式図である。図9に示すデバイス30の基板32、核形成層34、チャネル層36、および、バリア層38は、図8に示す各層と対応する同じ層である。一部の実施形態では、基板32には、半絶縁性の4H−SiC(ノースカロライナ州DurhamのCree,Inc.より市販)を含み、核形成層34は、AlNで形成され、また、チャネル層36は、2μm厚のGaN:Fe層を含み、このとき、バリア層38は、0.8nmのAlNおよび22.5nmのAlxGa1−xNを含む。ここで、PL(光ルミネセンス)測定によると、x=0.195である。

【0035】

ゲート電極46は、バリア層38の形成後に形成され、パッシベーション層50がデバイスに堆積される。次いで、フィールドプレート48が、ゲート46とオーバーラップし、ゲート−ドレイン領域で距離Lf拡がるように、パッシベーション層50上に形成される。図9に示す実施形態では、パッシベーション層50は、フィールドプレート48のスペーサ層としての役割を果たす。ゲート46の上の(above)フィールドプレート48のオーバーラップ、および、ゲート−ドレイン領域での拡がり量は、最適な結果を得るために、変更されうる。フィールドプレート48とゲート46は、ビア(via)あるいは他の接続(図示せず)によって、接続している。

【0036】

一部の実施形態において、フィールドプレート48は、距離Lf0.2〜1μm拡がりうる。一部の実施形態において、フィールドプレート48は、距離Lf0.5〜0.9μm拡がりうる。好ましい実施形態として、フィールドプレート48は、距離Lf0.7μm拡がりうる。

【0037】

図9に従う構造GaNベースのHEMT構造が、構築され、テストされた。そのデバイスは、120Vと4GHzで動作したとき、55%の電力付加効率(PAE)、電力密度32W/mmを達成した。

【0038】

フィールドプレート距離(Lf)がデバイス性能に与える影響が、テストされた。デバイスは、図9の実施形態に、概ね従って、製造された。ただし、フィールドプレート長Lfは、0〜0.9μmと距離を変化させた。その後、得られたデバイスのPAEを測定した。図10に示すように、フィールドプレート長が0.5μmを一度超えると、PAEは向上し、その最適長さは約0.7μmであった。しかしながら、最適長さは、個々のデバイス設計に依存しうるし、また、動作する電圧と周波数にも依存しうる。

【0039】

(参考文献)

以下の参考文献が、本明細書中で、参考文献として、組み込まれている。

[1] K Asanoら、「Novel High Power AlGaAs/GaAs HFET with a Field−Modulating Plate Operated at 35V Drain Voltage」 IEDM Conference、 1998、 pp.59−62

[2] Y. Andoら、「10−W/mm AlGaN−GaN HFET With a Field Modulating Plate」、 IEEE Electron Device Letters, Vol. 24, No. 5, 2003年5月, pp. 289−291.

[3]米国特許第6,586,781号,2003年7月1日発行、Wuら、「Group III nitride based FETs and HEMTs with reduced trapping and method for producing the same」

[4]米国特許第5,290,393号、1994年3月1日発行、Nakamura、「Crystal growth method for gallium nitride−based compound semiconductor」

[5]米国特許第5,686,738号、1997年11月11日発行、Moustakas、「Highly insulating monocrystalline gallium nitride thin films.」

[6]米国特許第5,393,993号、1995年2月28日発行、Edmondら、「Buffer structure between silicon carbide and gallium nitride and resulting semiconductor devices」

[7]米国特許第5,523,589号、1996年6月4日発行、Edmondら、「Vertical geometry light emitting diode with group III nitride active layer and extended lifetime」

[8]米国特許第5,739,554号、1998年4月14日発行、Edmondら、「Double heterojunction light emitting diode with gallium nitride active layer」

[9]米国特許第6,316,793号、2001年11月13日発行、Sheppardら、「Nitride based transistors on semi−insulating silicon carbide substrates」

[10]米国特許第6,548,333号、2003年4月15日発行、Smith、「Aluminum gallium nitride/gallium nitride

high electron mobility transistors having a gate contact on a gallium nitride based cap segment」

[11]米国特許出願公開番号第2002/0167023号、2002年11月14日公開、Chavarkar, Prashantら、「Group−III nitride based high electron mobility transistor (HEMT) with barrier/spacer layer」

[12]米国特許出願公開番号第2003/0020092号、2003年1月30日公開,Parikh, Primitら、「Insulating gate AlGaN/GaN HEMT」

[13]米国特許第5,192,987号、1993年3月9日発行、Khanら、「High electron mobility transistor with GaN/AlxGa1−xN heterojunctions」

[14]米国特許第5,296,395号,1994年3月22日発行、Khanら、「Method of making a high electron mobility transistor」

[15] Y.−F. Wu、 A. Saxler、 M. Moore、 R.P.

Smith、 S. Sheppard、 P.M. Chavarkar、 T. Wisleder、 U.K. Mishra、 P. Parikh、「30 W/mm GaN HEMTs by field plate optimization」, IEEE EDL、 Vol.25、 No.3、 pp.117−119、2004年3月

[16] S.Karmalkar、 U.K. Mishra、 Very high

voltage AlGaN−GaN HEMT using a field plate deposited on a stepped insulator, Solid State Electronics, 45(2001)1645−1652.

(結論)

本明細書は、本発明の好ましい実施形態の記載を結論付けるものである。本発明の一以上の実施形態について前述してきたが、これは例示と記述の目的のために、示されたものである。ここに開示した細かな形式で、本発明の網羅を意図したものでも、本発明の制限を意図したものではない。上記に教示したことから、修正や変更を多数行うことも可能である。本発明の範囲は、ここに記載した詳細な記述で限定されることを意図しておらず、むしろ、以下に述べる請求項で限定されることを意図している。

【特許請求の範囲】

【請求項1】

バリア層と、

該バリア層上のスペーサ層と、

ソース電極とドレイン電極であって、ゲート電極が適切なレベルでバイアスされたとき、該ソース電極と該ドレイン電極との間に電流が流れるようにオーミックコンタクトを形成する、ソース電極とドレイン電極と

を備え、

該ゲート電極の少なくとも底部分がバリア層の表面上にあるように、該スペーサ層はエッチングされて該バリア層を曝して該ゲート電極が堆積され、

フィールドプレートは、該スペーサ層の少なくとも一部分に拡がり、

パッシベーション層は、該ゲート電極と該スペーサ層の少なくとも一部分との両方の上にある、高電子移動度トランジスタ(HEMT)。

【請求項2】

前記電流は、前記ゲート電極が前記適切なレベルでバイアスされているとき、チャネル層と前記バリア層との間のヘテロ界面で生じる二次元電子ガス(2DEG)を介して、前記ソース電極とドレイン電極との間を流れる、請求項1に記載のHEMT。

【請求項3】

前記スペーサ層上の前記ゲート電極の一部分は、前記フィールドプレートを形成する、請求項1に記載のHEMT。

【請求項4】

前記フィールドプレートは、前記ゲート電極から離れたところに前記ドレイン電極に向かって拡がる、請求項1に記載のHEMT。

【請求項5】

前記スペーサ層は、誘電性層、アンドープのまたは空乏化したAlxGa1−xN(0≦x≦1)材料の層、あるいは、その組合せを含む、請求項1に記載のHEMT。

【請求項6】

前記フィールド層は、前記スペーサ層の上に形成され、前記ゲート電極の端から前記ドレイン電極に向かって、距離Lf(フィールドプレート距離)まで拡がる、請求項1に記載のHEMT。

【請求項7】

前記フィールドプレートは、前記ゲート電極に電気的に接続されている、請求項1に記載のHEMT。

【請求項8】

前記フィールドプレートは、前記ゲート電極の延長と同じ堆積ステップの間に形成される、請求項1に記載のHEMT。

【請求項9】

前記フィールドプレートとゲート電極とは、別個の堆積ステップの間に形成される、請求項1に記載のHEMT。

【請求項10】

前記基板上のバリア層は、シリコンカーバイド、サファイア、スピネル、酸化亜鉛、シリコン、あるいは、III族窒化物材料の成長をサポートできる他の任意の材料を含む、請求項1に記載のHEMT。

【請求項11】

前記バリア層は、基板上の核形成層上にあり、該核形成層は、AlzGa1−zN(0≦z≦1)核形成層である、請求項1に記載のHEMT。

【請求項12】

前記核形成層は、AlN核形成層である、請求項1に記載のHEMT。

【請求項13】

前記バリア層は、高抵抗のIII族窒化物チャネル層上にある、請求項1に記載のHEMT。

【請求項14】

前記バリア層は、AlxGayIn(1−x−y)N(0≦x≦1、0≦y≦1、x+y≦1)チャネル層上にある、請求項1に記載のHEMT。

【請求項15】

前記チャネル層は、GaN:Feを含む、請求項14に記載のHEMT。

【請求項16】

前記バリア層は、AlxGa1−xN(0≦x≦1)を含む、請求項1に記載のHEMT。

【請求項17】

前記バリア層は、AlNおよびAlGaNを含む、請求項1に記載のHEMT。

【請求項18】

チャネル層をさらに含み、該チャネル層と前記バリア層のそれぞれは、III族窒化物材料のドープまたはアンドープの層であるサブ層を含む、請求項1に記載のHEMT。

【請求項19】

前記スペーサ層は、AlxGa1−xNバリア層であるバリア層上に成長される、III族窒化物半導体スペーサ層である、請求項1に記載のHEMT。

【請求項20】

前記スペーサ層は、均一な組成を有する、請求項1に記載のHEMT。

【請求項21】

前記スペーサ層は、勾配のある組成を有する、請求項1に記載のHEMT。

【請求項22】

前記スペーサ層は、アンドープである、請求項1に記載のHEMT。

【請求項23】

前記スペーサ層は、成長すると完全に空乏化する、請求項1に記載のHEMT。

【請求項24】

前記ゲート電極は前記バリア層が形成された後に形成され、パッシベーション層は前記デバイス上に堆積され、

前記フィールドプレートは、該ゲートをオーバーラップし、ゲート−ドレイン領域で距離Lf拡がるように、該パッシベーション層に次いで形成され、該パッシベーション層は該フィールドプレートに対して該スペーサ層として働く、請求項1に記載のHEMT。

【請求項25】

前記HEMTは、窒化物ベースのHEMTである、請求項1に記載のHEMT。

【請求項26】

基板と、該基板上の核形成層と、該核形成層上のチャネル層とをさらに含み、前記バリア層は該チャネル層上にある、請求項1に記載のHEMT。

【請求項1】

バリア層と、

該バリア層上のスペーサ層と、

ソース電極とドレイン電極であって、ゲート電極が適切なレベルでバイアスされたとき、該ソース電極と該ドレイン電極との間に電流が流れるようにオーミックコンタクトを形成する、ソース電極とドレイン電極と

を備え、

該ゲート電極の少なくとも底部分がバリア層の表面上にあるように、該スペーサ層はエッチングされて該バリア層を曝して該ゲート電極が堆積され、

フィールドプレートは、該スペーサ層の少なくとも一部分に拡がり、

パッシベーション層は、該ゲート電極と該スペーサ層の少なくとも一部分との両方の上にある、高電子移動度トランジスタ(HEMT)。

【請求項2】

前記電流は、前記ゲート電極が前記適切なレベルでバイアスされているとき、チャネル層と前記バリア層との間のヘテロ界面で生じる二次元電子ガス(2DEG)を介して、前記ソース電極とドレイン電極との間を流れる、請求項1に記載のHEMT。

【請求項3】

前記スペーサ層上の前記ゲート電極の一部分は、前記フィールドプレートを形成する、請求項1に記載のHEMT。

【請求項4】

前記フィールドプレートは、前記ゲート電極から離れたところに前記ドレイン電極に向かって拡がる、請求項1に記載のHEMT。

【請求項5】

前記スペーサ層は、誘電性層、アンドープのまたは空乏化したAlxGa1−xN(0≦x≦1)材料の層、あるいは、その組合せを含む、請求項1に記載のHEMT。

【請求項6】

前記フィールド層は、前記スペーサ層の上に形成され、前記ゲート電極の端から前記ドレイン電極に向かって、距離Lf(フィールドプレート距離)まで拡がる、請求項1に記載のHEMT。

【請求項7】

前記フィールドプレートは、前記ゲート電極に電気的に接続されている、請求項1に記載のHEMT。

【請求項8】

前記フィールドプレートは、前記ゲート電極の延長と同じ堆積ステップの間に形成される、請求項1に記載のHEMT。

【請求項9】

前記フィールドプレートとゲート電極とは、別個の堆積ステップの間に形成される、請求項1に記載のHEMT。

【請求項10】

前記基板上のバリア層は、シリコンカーバイド、サファイア、スピネル、酸化亜鉛、シリコン、あるいは、III族窒化物材料の成長をサポートできる他の任意の材料を含む、請求項1に記載のHEMT。

【請求項11】

前記バリア層は、基板上の核形成層上にあり、該核形成層は、AlzGa1−zN(0≦z≦1)核形成層である、請求項1に記載のHEMT。

【請求項12】

前記核形成層は、AlN核形成層である、請求項1に記載のHEMT。

【請求項13】

前記バリア層は、高抵抗のIII族窒化物チャネル層上にある、請求項1に記載のHEMT。

【請求項14】

前記バリア層は、AlxGayIn(1−x−y)N(0≦x≦1、0≦y≦1、x+y≦1)チャネル層上にある、請求項1に記載のHEMT。

【請求項15】

前記チャネル層は、GaN:Feを含む、請求項14に記載のHEMT。

【請求項16】

前記バリア層は、AlxGa1−xN(0≦x≦1)を含む、請求項1に記載のHEMT。

【請求項17】

前記バリア層は、AlNおよびAlGaNを含む、請求項1に記載のHEMT。

【請求項18】

チャネル層をさらに含み、該チャネル層と前記バリア層のそれぞれは、III族窒化物材料のドープまたはアンドープの層であるサブ層を含む、請求項1に記載のHEMT。

【請求項19】

前記スペーサ層は、AlxGa1−xNバリア層であるバリア層上に成長される、III族窒化物半導体スペーサ層である、請求項1に記載のHEMT。

【請求項20】

前記スペーサ層は、均一な組成を有する、請求項1に記載のHEMT。

【請求項21】

前記スペーサ層は、勾配のある組成を有する、請求項1に記載のHEMT。

【請求項22】

前記スペーサ層は、アンドープである、請求項1に記載のHEMT。

【請求項23】

前記スペーサ層は、成長すると完全に空乏化する、請求項1に記載のHEMT。

【請求項24】

前記ゲート電極は前記バリア層が形成された後に形成され、パッシベーション層は前記デバイス上に堆積され、

前記フィールドプレートは、該ゲートをオーバーラップし、ゲート−ドレイン領域で距離Lf拡がるように、該パッシベーション層に次いで形成され、該パッシベーション層は該フィールドプレートに対して該スペーサ層として働く、請求項1に記載のHEMT。

【請求項25】

前記HEMTは、窒化物ベースのHEMTである、請求項1に記載のHEMT。

【請求項26】

基板と、該基板上の核形成層と、該核形成層上のチャネル層とをさらに含み、前記バリア層は該チャネル層上にある、請求項1に記載のHEMT。

【図1A】

【図1B】

【図2A】

【図2B】

【図3A】

【図3B】

【図4A】

【図4B】

【図5A】

【図5B】

【図6】

【図7A】

【図7B】

【図7C】

【図8】

【図9】

【図10】

【図1B】

【図2A】

【図2B】

【図3A】

【図3B】

【図4A】

【図4B】

【図5A】

【図5B】

【図6】

【図7A】

【図7B】

【図7C】

【図8】

【図9】

【図10】

【公開番号】特開2012−44207(P2012−44207A)

【公開日】平成24年3月1日(2012.3.1)

【国際特許分類】

【外国語出願】

【出願番号】特願2011−229873(P2011−229873)

【出願日】平成23年10月19日(2011.10.19)

【分割の表示】特願2006−525544(P2006−525544)の分割

【原出願日】平成16年9月9日(2004.9.9)

【出願人】(592130699)ザ リージェンツ オブ ザ ユニバーシティ オブ カリフォルニア (364)

【氏名又は名称原語表記】The Regents of The University of California

【出願人】(592054856)クリー インコーポレイテッド (468)

【氏名又は名称原語表記】CREE INC.

【Fターム(参考)】

【公開日】平成24年3月1日(2012.3.1)

【国際特許分類】

【出願番号】特願2011−229873(P2011−229873)

【出願日】平成23年10月19日(2011.10.19)

【分割の表示】特願2006−525544(P2006−525544)の分割

【原出願日】平成16年9月9日(2004.9.9)

【出願人】(592130699)ザ リージェンツ オブ ザ ユニバーシティ オブ カリフォルニア (364)

【氏名又は名称原語表記】The Regents of The University of California

【出願人】(592054856)クリー インコーポレイテッド (468)

【氏名又は名称原語表記】CREE INC.

【Fターム(参考)】

[ Back to top ]