シンボルタイミングリカバリ回路

【課題】干渉波による精度の悪化を防止することができるシンボルタイミングリカバリ回路を提供することを課題とする。

【解決手段】第1のフィルタを用いて入力デジタル信号のゼロクロス点及び/又はデータ識別点の補間データを生成する補間器(14)と、第2のフィルタを用いて補間器により生成された補間データを基に入力デジタル信号から前方干渉波を除去し、その除去した信号、第1の識別信号及び第1の誤差信号を出力する前方等化器(21)と、第3のフィルタを用いて補間器により生成された補間データを基に入力デジタル信号から後方干渉波を除去し、その除去した信号、第2の識別信号及び第2の誤差信号を出力する後方等化器(23)と、第2のフィルタのタップ係数、第3のフィルタのタップ係数、第1の識別信号、第1の誤差信号、第2の識別信号及び第2の誤差信号を基に第1のフィルタのタップ係数を生成するタイミング再生部(20)とを有する。

【解決手段】第1のフィルタを用いて入力デジタル信号のゼロクロス点及び/又はデータ識別点の補間データを生成する補間器(14)と、第2のフィルタを用いて補間器により生成された補間データを基に入力デジタル信号から前方干渉波を除去し、その除去した信号、第1の識別信号及び第1の誤差信号を出力する前方等化器(21)と、第3のフィルタを用いて補間器により生成された補間データを基に入力デジタル信号から後方干渉波を除去し、その除去した信号、第2の識別信号及び第2の誤差信号を出力する後方等化器(23)と、第2のフィルタのタップ係数、第3のフィルタのタップ係数、第1の識別信号、第1の誤差信号、第2の識別信号及び第2の誤差信号を基に第1のフィルタのタップ係数を生成するタイミング再生部(20)とを有する。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、シンボルタイミングリカバリ回路に関する。

【背景技術】

【0002】

受信装置は、受信信号からシンボルタイミングを再生するためのシンボルタイミングリカバリ回路を有し、受信信号を再生する。受信信号の位相を制御してクロックに同期させる形式のシンボルタイミングリカバリ回路が知られている(例えば、特許文献1及び2参照)。

【0003】

また、トランスバーサルフィルタからなる前方等化器および後方等化器を有する等化器において、予備等化器と等化器制御回路を有する等化器が知られている(例えば、特許文献3参照)。

【0004】

また、推定したチャネル係数を用い、受信信号から送信信号を推定するビタビ型等化器であって、受信信号の時間軸に沿って等化を行う前方等化と時間軸の逆方向に等化を行う後方等化を行う双方向ビタビ型等化器が知られている(例えば、特許文献4参照)。

【先行技術文献】

【特許文献】

【0005】

【特許文献1】特開2000−101659号公報

【特許文献2】特開2009−33300号公報

【特許文献3】特開2010−161640号公報

【特許文献4】特開2001−251226号公報

【発明の概要】

【発明が解決しようとする課題】

【0006】

本発明の目的は、干渉波による精度の悪化を防止することができるシンボルタイミングリカバリ回路を提供することである。

【課題を解決するための手段】

【0007】

シンボルタイミングリカバリ回路は、第1の有限インパルス応答フィルタを用いて入力デジタル信号のゼロクロス点及び/又はデータ識別点の補間データを生成する補間器と、第2の有限インパルス応答フィルタを用いて前記補間器により生成された補間データを基に前記入力デジタル信号から前方干渉波を除去し、その除去した信号、第1の識別信号及び第1の誤差信号を出力する前方等化器と、第1の無限インパルス応答フィルタを用いて前記補間器により生成された補間データを基に前記入力デジタル信号から後方干渉波を除去し、その除去した信号、第2の識別信号及び第2の誤差信号を出力する後方等化器と、前記補間器により生成された補間データと前記前方等化器及び前記後方等化器により前記前方干渉波及び前記後方干渉波が除去された信号とを基に前記第2の有限インパルス応答フィルタのタップ係数を演算する第1のタップ係数演算部と、前記補間器により生成された補間データと前記前方等化器及び前記後方等化器により前記前方干渉波及び前記後方干渉波が除去された信号とを基に前記第1の無限インパルス応答フィルタのタップ係数を演算する第2のタップ係数演算部と、前記第2の有限インパルス応答フィルタのタップ係数、前記第1の無限インパルス応答フィルタのタップ係数、前記第1の識別信号、前記第1の誤差信号、前記第2の識別信号及び前記第2の誤差信号を基に前記第1の有限インパルス応答フィルタのタップ係数を生成するタイミング再生部とを有する。

【発明の効果】

【0008】

第2の有限インパルス応答フィルタのタップ係数及び第1の無限インパルス応答フィルタのタップ係数を用いて、第1の有限インパルス応答フィルタのタップ係数を生成することにより、干渉波による精度の悪化を防止することができる。

【図面の簡単な説明】

【0009】

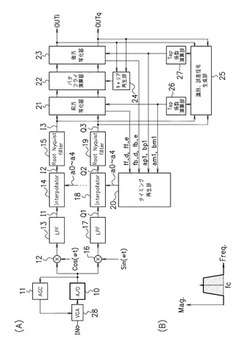

【図1】図1(A)は実施形態によるシンボルタイミングリカバリ回路を有するQAM復調器の構成例を示す図であり、図1(B)は中間周波数信号の周波数スペクトルを示す図である。

【図2】シンボルタイミングリカバリ回路の動作を説明するためのタイムチャートである。

【図3】図1(A)の補間器の構成例を示す図である。

【図4】補間器の動作を説明するための図である。

【図5】図1(A)の前方等化器及び後方等化器の構成例を示す図である。

【図6】図1(A)のタイミング再生部の構成例を示す図である。

【図7】図7(A)〜(D)は第1の位相比較部の動作を説明するための図である。

【図8】本実施形態によるタイミング再生部の構成例を示す図である。

【図9】図9(A)は前方等化器及び後方等化器のタップ係数を示す図であり、図9(B)は同相タップ係数及び直交タップ係数のベクトルの大きさを示す図である。

【図10】図10(A)及び(B)は図8のコントロール回路の動作を説明するための図である。

【図11】本実施形態によるコントロール回路の構成例を示す図である。

【図12】他の実施形態によるコントロール回路の構成例を示す図である。

【発明を実施するための形態】

【0010】

図1(A)は実施形態によるシンボルタイミングリカバリ回路を有するQAM(Quadrature Amplitude Modulation:直交振幅変調)復調器(受信装置)の構成例を示す図であり、図1(B)は中間周波数(Intermediate Frequency:IF)信号INの周波数スペクトルを示す図である。QAMは、互いに独立な2つの搬送波(同相搬送波及び直交搬送波)の振幅及び位相を調整することによりデータを伝達する変調方式である。例えばQAM復調器は、LSI上にハードウェアとして実現される。QAM変調されたIF信号INは、図1(B)に示すように、帯域伝送された信号であり、ある帯域内で台形の形状を有するスペクトルを持つものである。可変ゲイン増幅器28は、IF信号INを所定のゲインで増幅して出力する。アナログ/デジタル変換器10は、可変ゲイン増幅器28の出力信号をアナログからデジタルに変換して出力する。自動ゲインコントローラ11は、アナログ/デジタル変換器10の出力信号のパワーが所望の値より大きいか否かを判定し、可変ゲイン増幅器28のゲインを制御する。乗算器12は、アナログ/デジタル変換器10の出力信号に対して信号Cos(ωt)を乗算し、同相(I)チャネル信号を出力する。乗算器16は、アナログ/デジタル変換器10の出力信号に対して信号Sin(ωt)を乗算し、直交(Q)チャネル信号を出力する。すなわち、アナログ/デジタル変換器10の出力信号は、Iチャネル信号及びQチャネル信号に分離される。ここで、角周波数ωに対応する周波数として、図1(B)のIF信号スペクトルの台形の中心周波数fcが用いられる。すなわち、ω=2×π×fcで表される。ローパスフィルタ13は、乗算器12の出力Iチャネル信号の高周波数の成分をカットし、Iチャネル信号I1を出力する。ローパスフィルタ17は、乗算器16の出力Qチャネル信号の高周波数の成分をカットし、Qチャネル信号Q1を出力する。補間器14は、有限インパルス応答(Finite Impulse Response:FIR)フィルタを有し、タップ係数a0〜a4を基にIチャネル信号I1を補間してIチャネル信号I2を出力し、シンボルタイミングを再生する。補間器18は、FIRフィルタを有し、タップ係数a0〜a4を基にQチャネル信号Q1を補間してQチャネル信号Q2を出力し、シンボルタイミングを再生する。

【0011】

図2は、シンボルタイミングリカバリ回路の動作を説明するためのタイムチャートである。アナログ/デジタル変換器10のサンプリング周波数は、入力信号INのシンボルレートの周波数の2倍よりも高い。図2の例では、アナログ/デジタル変換器10によりサンプリングデジタルデータS1〜S14が得られている。図2において、白丸印はサンプリング点を示し、黒丸印は入力信号INのゼロクロス点及びデータ識別点を示している。

【0012】

図3は、図1(A)の補間器14の構成例を示す図である。図1(A)の補間器18も補間器14と同様の構成を有する。補間器14は、例えば、4個の遅延器(フリップフロップ)201〜204、5個の乗算器211〜215、及び加算器221を有する5タップの第1のFIRフィルタを備える。遅延器201は、Iチャネル信号I1を遅延して出力する。遅延器202は、遅延器201の出力信号を遅延して出力する。遅延器203は、遅延器202の出力信号を遅延して出力する。遅延器204は、遅延器203の出力信号を遅延して出力する。乗算器211は、Iチャネル信号I1及びタップ係数a0を乗算して出力する。乗算器212は、遅延器201の出力信号及びタップ係数a1を乗算して出力する。乗算器213は、遅延器202の出力信号及びタップ係数a2を乗算して出力する。乗算器214は、遅延器203の出力信号及びタップ係数a3を乗算して出力する。乗算器215は、遅延器204の出力信号及びタップ係数a4を乗算して出力する。加算器221は、乗算器211〜215の出力信号を加算し、Iチャネル信号I2を出力する。

【0013】

補間器14は、第1のFIRフィルタを用いて、入力デジタル信号I1のサンプリングデータS1〜S14を用いて補間処理することにより、入力デジタル信号I1のゼロクロス点K2,K4及びデータ識別点K1,K3の補間データを生成する。なお、補間器14は、補間処理によって入力デジタル信号I1のデータ識別点K1,K3及びゼロクロス点K2,K4の補間データを生成する場合に限定されず、データ識別点K1,K3又はゼロクロス点K2,K4のうちの一方(例えば、データ識別点K1,K3のみ)の補間データを生成するようにしてもよい。

【0014】

図4は、補間器(FIRフィルタ)14の動作を説明するための図である。以下、補間器14を例に説明するが、補間器18も同様である。図4に示す特性401は、カットオフ周波数が「2×fs 」であるローパスフィルタのインパルス応答に相当する。ここで、周波数fsは、入力信号INのシンボルレートの周波数である。時間Tは、補間器(FIRフィルタ)14が備える各遅延器201〜204の遅延量に相当する。なお、時間Tは、アナログ/デジタル変換器10のサンプリング周波数の1周期(すなわち、2π)に相当する。

【0015】

補間器14は、5個のタップ係数a0〜a4に基づいて、入力信号I1の位相を調整する。ここで、タップ係数a0〜a4は、後述する図8のタイミング再生部20内のタップ係数演算部704により位相信号θに応じて決定される。例えば、参照番号402で示すように、位相信号θが「ゼロ」であれば、タップ係数a2以外のインパルス応答はゼロとなる。この場合、補間器14は、遅延時間が2Tの遅延器として動作する。また、参照番号403で示すように、位相信号θが「+π/2」であるときは、対応する5個のタップ係数a0〜a4が与えられ、補間器14における遅延時間は「2T+T/4」となる。この場合、入力信号I1の位相は、補間器14を通過することにより、「T/4(すなわち、π/2)」だけ遅れることになる。一方、参照番号404で示すように、位相信号θが「−π/2」であれば、対応する5個のタップ係数a0〜a4が与えられ、補間器14における遅延時間は「2T−T/4」となる。この場合、入力信号I1の位相は、補間器14を通過することにより、「T/4(すなわち、π/2)」だけ進むことになる。同様に、参照番号405で示すように、位相信号θが「−π」であれば、対応する5個のタップ係数a0〜a4が与えられ、入力信号I1の位相は、補間器14を通過することにより、「π」だけ進むことになる。このように、補間器14は、入力信号I1の位相を調整することができる。

【0016】

例えば、図2において、サンプリングデータS1の位相は、データ識別点K1に対して3π/5だけ遅れている。この場合、補間器14には、入力信号I1の位相を3π/5だけ進めるためのタップ係数a0〜a4が与えられる。そうすると、補間器14は、データ識別点K1における値を出力する。サンプリングデータS2の位相は、ゼロクロス点K2に対して4π/5だけ遅れている。この場合、補間器14には、入力信号I1の位相を4π/5だけ進めるためのタップ係数a0〜a4が与えられる。そうすると、補間器14は、ゼロクロス点K2における値を出力する。サンプリングデータS3の位相は、データ識別点K3に対してπだけ遅れている。この場合、補間器14には、入力信号I1の位相をπだけ進めるためのタップ係数a0〜a4が与えられる。そうすると、補間器14は、データ識別点K3における値を出力する。このように、補間器14は、サンプリングデータを用いて補間処理を行うことにより、入力信号I1のデータ識別点K1,K3及びゼロクロス点K2,K4における値を出力する。

【0017】

図1(A)において、ルートナイキストフィルタ15は、補間器14の出力信号I2をフィルタリングし、Iチャネル信号I3を出力する。ルートナイキストフィルタ19は、補間器18の出力信号Q2をフィルタリングし、Qチャネル信号Q3を出力する。ルートナイキストフィルタ15及び19は、送信装置にも備えられており、送信装置と受信装置とでナイキストフィルタとしての帯域制限を行うものである。

【0018】

マルチパスでは、図10(A)及び(B)に示すように、送信装置から送信された信号が障害物によって反射・回折し、受信装置が複数の経路(パス)から同じ信号を遅延量が異なる主波(希望波)A1、前方干渉波(先行波)A2及び/又は後方干渉波(遅延波)A3として受信してしまう。主波A1は、マルチパスの中で最も電力が大きいパスの信号波である。前方干渉波A2は、主波A1に対して所定の遅延量進んでいるパスの干渉波である。後方干渉波A3は、主波A1に対して所定の遅延量遅れているパスの干渉波である。

【0019】

前方等化器21は、複素FIRフィルタで構成され、図10(A)に示すように主波A1の前側に前方干渉波A2が存在する時、前方干渉波A2を除去して出力する。前方等化器21は、主に、ノンミニマムフェーズ時(前ゴースト時)の前方干渉波A2を除去する。バタフライ演算器22は、前方等化器21の出力信号を入力し、キャリア周波数の誤差を補正し、キャリア再生を行うものである。キャリア再生部24は、復調後のIチャネル信号OUTi及びQチャネル信号OUTqによるコンスタレーションの回転を基にキャリア周波数のずれを検出し、コンスタレーションの回転を止める方向にバタフライ演算器22を制御する。後方等化器23は、複素IIR(Infinite Impulse Response:無限インパルス応答)フィルタで構成され、図10(B)に示すように主波A1の後ろ側に後方干渉波A3が存在する時、後方干渉波A3を除去し、復調後のIチャネル信号OUTi及びQチャネル信号OUTqを出力する。後方等化器23は、主に、ミニマムフェーズ時(後ゴースト時)の後方干渉波A3を除去する。識別、誤差信号生成部25は、前方等化器21の入力信号I3,Q3及び後方等化器23の出力信号OUTi,OUTqを基に識別信号及び誤差信号を生成してタップ係数演算部26及び27に出力する。第1のタップ係数演算部26は、前方干渉波A2を除去するため、上記の識別信号及び誤差信号を基にタップ係数を生成し、前方等化器21に出力する。前方等化器21は、そのタップ係数を基に、複素FIRフィルタを用いて前方干渉波A2を除去する。第2のタップ係数演算部27は、後方干渉波A3を除去するため、上記の識別信号及び誤差信号を基にタップ係数を生成し、後方等化器23に出力する。後方等化器21は、そのタップ係数を基に、複素IIRフィルタを用いて後方干渉波A3を除去する。

【0020】

タイミング再生部20は、前方等化器21から第1の識別信号ff_d及び第1の誤差信号ff_eを入力し、後方等化器23から第2の識別信号fb_d及び第2の誤差信号fb_eを入力し、第1のタップ係数演算部26から第1の同相タップ係数am1及び第1の直交タップ係数bm1を入力し、第2のタップ係数演算部27から第1の同相タップ係数ap1及び第1の直交タップ係数bp1を入力し、同じタップ係数a0〜a4を補間器14及び18に出力する。

【0021】

図5は、図1(A)の前方等化器21及び後方等化器23の構成例を示す図である。前方等化器21は、遅延器605、同相FIRフィルタ601,604、直交FIRフィルタ602,603、減算器606,608及び加算器607を有する複素FIRフィルタを備える。遅延器605は、Iチャネル信号I3に対して、同相FIRフィルタ601の遅延量と同じ遅延量遅延し、第1の識別信号ff_dを出力する。

【0022】

同相FIRフィルタ601は、図3の補間器(FIRフィルタ)14と同様の構成を有し、第1のタップ係数演算部26から入力した同相タップ係数a0,am1〜amnを基に、Iチャネル信号I3の実部をフィルタリングし、補正後の同相成分信号を出力する。直交FIRフィルタ603は、図3の補間器(FIRフィルタ)14と同様の構成を有し、第1のタップ係数演算部26から入力した直交タップ係数bm1〜bmnを基に、Iチャネル信号I3の虚部をフィルタリングし、補正後の直交成分信号を出力する。

【0023】

同相FIRフィルタ604は、図3の補間器(FIRフィルタ)14と同様の構成を有し、第1のタップ係数演算部26から入力した同相タップ係数a0,am1〜amnを基に、Qチャネル信号Q3の実部をフィルタリングし、補正後の同相成分信号を出力する。直交FIRフィルタ602は、図3の補間器(FIRフィルタ)14と同様の構成を有し、第1のタップ係数演算部26から入力した直交タップ係数bm1〜bmnを基に、Qチャネル信号Q3の虚部をフィルタリングし、補正後の直交成分信号を出力する。

【0024】

加算器607は、同相FIRフィルタ601により出力される補正後の同相成分信号及び直交FIRフィルタ602により出力される補正後の直交成分信号を加算し、前方干渉波A2が除去されたIチャネル信号を出力する。減算器608は、同相FIRフィルタ604により出力される補正後の同相成分信号から直交FIRフィルタ603により出力される補正後の直交成分信号を減算し、前方干渉波A2が除去されたQチャネル信号を出力する。減算器606は、同相FIRフィルタ601により出力される補正後の同相成分信号から第1の識別信号ff_dを減算し、第1の誤差信号(同相成分)ff_eを出力する。第1の誤差信号ff_eは、時間軸方向の誤差情報である。

【0025】

バタフライ演算器22は、加算器607により出力されるIチャネル信号及び減算器608により出力されるQチャネル信号を入力し、バタフライ演算を行い、コンスタレーションの回転を止めるためにキャリア周波数の誤差を補正し、Iチャネル信号及びQチャネル信号を出力する。

【0026】

後方等化器23は、同相IIRフィルタ演算部611,614、直交IIRフィルタ演算部612,613、加算器615、減算器616及び識別器617,618を有する複素IIRフィルタを備える。

【0027】

同相IIRフィルタ演算部611は、図3の補間器(FIRフィルタ)14と同様のハードウェア構成を有し、第2のタップ係数演算部27から入力した同相タップ係数ap1〜apnを基に、識別器617により出力されるIチャネル信号の実部をフィルタリングし、第2の誤差信号(同相成分)fb_eを出力する。第2の誤差信号fb_eは、時間軸方向の誤差情報である。また、第2の識別信号fb_dは、バラフライ演算器22により出力されるIチャネル信号と同じ信号である。直交IIRフィルタ演算部613は、図3の補間器(FIRフィルタ)14と同様のハードウェア構成を有し、第2のタップ係数演算部27から入力した直交タップ係数bp1〜bpnを基に、識別器617により出力されるIチャネル信号の虚部をフィルタリングし、直交成分の誤差信号を出力する。

【0028】

同相IIRフィルタ演算部614は、図3の補間器(FIRフィルタ)14と同様のハードウェア構成を有し、第2のタップ係数演算部27から入力した同相タップ係数ap1〜apnを基に、識別器618により出力されるQチャネル信号の実部をフィルタリングし、同相成分の誤差信号を出力する。直交IIRフィルタ演算部612は、図3の補間器(FIRフィルタ)14と同様のハードウェア構成を有し、第2のタップ係数演算部27から入力した直交タップ係数bp1〜bpnを基に、識別器618により出力されるQチャネル信号の虚部をフィルタリングし、直交成分の誤差信号を出力する。

【0029】

加算器615は、バタフライ演算器22により出力されるIチャネル信号、第2の誤差信号fb_e及び直交IIRフィルタ演算部612により出力される直交成分を加算し、後方干渉波A3が除去されたIチャネル信号OUTiを出力する。Iチャネル信号OUTiは、前方干渉波A2及び後方干渉波A3が除去された主波A1のIチャネル信号である。識別器617は、加算器615の出力信号OUTiを識別し、識別したIチャネル信号を出力する。

【0030】

減算器616は、バタフライ演算器22により出力されるQチャネル信号及び同相IIRフィルタ演算部614により出力される同相成分を加算し、その加算した信号から直交IIRフィルタ演算部613により出力される直交成分を減算し、後方干渉波A3が除去されたQチャネル信号OUTqを出力する。Qチャネル信号OUTqは、前方干渉波A2及び後方干渉波A3が除去された主波A1のQチャネル信号である。識別器618は、減算器616の出力信号OUTqを識別し、識別したQチャネル信号を出力する。

【0031】

なお、前方等化器21を前段に設け、後方等化器23を後段に設ける場合を例に説明したが、後方等化器23を前段に設け、前方等化器21を後段に設けるようにしてもよい。

【0032】

以上のように、前方等化器21は、第2のFIRフィルタ601〜604を用いて補間器14,18により生成された補間データを基に入力デジタル信号から前方干渉波A2を除去し、その除去した信号、第1の識別信号ff_d及び第1の誤差信号ff_eを出力する。第1の識別信号ff_dは、前方干渉波A2の除去前の信号である。第1の誤差信号ff_eは、前方干渉波A2の除去前の信号と前方干渉波A2の除去後の信号との差分の信号である。第1のタップ係数演算部26(図1(A))は、補間器14,18により生成された補間データI3,Q3と前方等化器21及び後方等化器23により前方干渉波A2及び後方干渉波A3が除去された信号OUTi,OUTqとを基に第2のFIRフィルタ601〜604のタップ係数a0,am1〜amn,bm1〜bmnを演算する。

【0033】

後方等化器23は、IIRフィルタ演算部611〜614を用いて補間器14,18により生成された補間データを基に入力デジタル信号から後方干渉波A3を除去し、その除去した信号、第2の識別信号fb_d及び第2の誤差信号fb_eを出力する。第2の識別信号fb_dは、後方干渉波A3の除去前の信号である。第2の誤差信号fb_eは、後方干渉波A3の除去前の信号と後方干渉波A3の除去後の信号との差分の信号である。第2のタップ係数演算部27(図1(A))は、補間器14,18により生成された補間データI3,Q3と前方等化器21及び後方等化器23により前方干渉波A2及び後方干渉波A3が除去された信号OUTi,OUTqとを基にIIRフィルタ演算部611〜614のタップ係数ap1〜apn,bp1〜bpnを演算する。

【0034】

図6は、第1の識別信号ff_d、第1の誤差信号ff_e、第2の識別信号fb_d及び第2の誤差信号fb_eのみを用いて補間器14、18に入力されるタップ係数a0〜a4を生成するタイミング再生部20(図1(A))の構成例を示す図である。第1の識別信号ff_d、第1の誤差信号ff_eは、図5の前方等化器21から入力される信号である。第2の識別信号fb_d及び第2の誤差信号fb_eは、図5の後方等化器23から入力される信号である。タイミング再生部20は、位相比較部701、ループフィルタ702、数値制御発振器(Numerically Controlled Oscillator:NCO)703及び第3のタップ係数演算部704を有する。数値制御発振器703は、位相信号θを出力する。第3のタップ係数演算部704は、位相信号θを基にタップ係数a0〜a4を演算する。位相比較部701は、第1の位相比較部731、第2の位相比較部732及び加算器727を有する。第1の位相比較部731は、遅延器711〜713、比較器714、乗算器715及びフリップフロップ716を有する。第2の位相比較部732は、遅延器721〜723、比較器724、乗算器725及びフリップフロップ726を有する。

【0035】

図7(A)〜(D)は、第1の位相比較部731の動作を説明するための図である。図7(A)及び(B)は入力データ502が理想サンプリング点502に対して進んでいる場合を示し、図7(A)は入力データ502が単調減少している場合を示し、図7(B)は入力データ502が単調増加している場合を示す。図7(C)及び(D)は入力データ502が理想サンプリング点502に対して遅れている場合を示し、図7(C)は入力データ502が単調減少している場合を示し、図7(D)は入力データ502が単調増加している場合を示す。入力データ502は、第1の識別信号ff_dに対応する。

【0036】

第1の位相比較部731は、第1の識別信号ff_dの位相誤差を検出する。遅延器711は、第1の識別信号ff_dのデータCを遅延し、データBを出力する。遅延器712は、遅延器711の出力データBを遅延し、データAを出力する。ここで、データBを現在のデータとすると、データCは未来のデータ、データAは過去のデータである。

【0037】

比較器714は、データA,B,Cの値を比較した結果、C>B>Aの場合には単調増加であると判断して「−1」を出力し、C<B<Aの場合には単調減少であると判断して「+1」を出力し、それ以外の場合には「0」を出力する。

【0038】

遅延器713は、タイミング調整のため、第1の誤差信号ff_eを遅延して出力する。これにより、比較器714の出力データと遅延器713の出力データとが同一時刻に調整される。乗算器715は、比較器714の出力データと遅延器713の出力データとを乗算する。フリップフロップ716は、比較器714の出力データが「−1」又は「+1」のときには乗算器715の出力データをラッチして出力し、比較器714の出力データが「0」のときには現在保持している前回と同じデータを出力する。第1の位相比較部731は、第1の識別信号ff_eの時間遷移に応じて第1の誤差信号ff_eに正負符号を付与する。

【0039】

このように、入力データ502の位相が理想サンプリング点501に対して進んでいれば、第1の位相比較部731は、位相誤差として正の値を出力する。一方、入力データ502の位相が理想サンプリング点501に対して遅れていれば、第1の位相比較部731は、位相誤差として負の値を出力する。

【0040】

次に、第2の位相比較部732について説明する。第2の位相比較部732は、第1の位相比較部731と同様に、第2の識別信号fb_d及び第2の誤差信号fb_eを入力し、位相誤差を出力する。遅延器721は、第2の識別信号fb_dのデータCを遅延し、データBを出力する。遅延器722は、遅延器721の出力データBを遅延し、データAを出力する。ここで、データBを現在のデータとすると、データCは未来のデータ、データAは過去のデータである。比較器724は、データA,B,Cの比較の結果、C>B>Aの場合には単調増加であると判断して「−1」を出力し、C<B<Aの場合には単調減少であると判断して「+1」を出力し、それ以外の場合には「0」を出力する。遅延器723は、タイミング調整のため、第2の誤差信号fb_eを遅延して出力する。これにより、比較器724の出力データと遅延器723の出力データとが同一時刻に調整される。乗算器725は、比較器724の出力データと遅延器723の出力データとを乗算する。フリップフロップ726は、比較器724の出力データが「−1」又は「+1」のときには乗算器725の出力データをラッチして出力し、比較器724の出力データが「0」のときには現在保持している前回と同じデータを出力する。第2の位相比較部732は、第2の識別信号fb_dの時間遷移に応じて第2の誤差信号fb_eに正負符号を付与する。

【0041】

加算器727は、フリップフロップ716及び726が出力する位相誤差データを加算して出力する。

【0042】

ループフィルタ702は、加算器727から出力される位相誤差データを平滑化(又は平均化)する。すなわち、ループフィルタ702は、ローパスフィルタとして動作する。そして、ループフィルタ702により平滑化された位相誤差データは、ほぼ一定の値に収束する。

【0043】

NCO703は、無限位相の積分器(又は完全積分器)であり、ループフィルタ702から与えられる位相誤差データを累積的に加算する。すなわち、位相誤差データは積分される。ここで、位相誤差データは、基本的に、ほぼ一定である。したがって、NCO703により出力される位相信号θは、時間経過に対して、ほぼリニアに増加してゆく。また、上述の位相誤差データは、1シンボル当たりの位相誤差を表す。NCO703には、1組の基準値が設定されている。1組の基準値は、入力信号の位相に換算したときに「+π」及び「−π」を表すように定義される。そして、NCO703により得られる位相信号θは、一方の基準値(例えば「+π」)を超えると、リセットされる。ここで、リセットとは、位相信号θに「2π」を加算する処理(あるいは、位相信号θから「2π」を減算する処理)を意味する。したがって、NCO703により生成される位相信号θの波形は、ノコギリ波となる。

【0044】

第3のタップ係数演算部704は、NCO703により生成される位相信号θに基づいてタップ係数a0〜a4を生成し、図1(A)の補間器14及び18に同じタップ係数a0〜a4を出力する。

【0045】

ここで、図6のタイミング再生部20において、主波A1の近傍に大電力の前方干渉波A2又は後方干渉波A3が存在する場合、前方等化器21及び後方等化器23から得られる第1の誤差信号ff_e又は第2の誤差信号fb_eの信頼度が落ちる。その結果、タイミング再生部20の精度が悪化し、干渉波耐力が上げられない問題が生ずる。そこで、主波A1の近傍に大電力の前方干渉波A2又は後方干渉波A3が存在する場合でも、タイミング再生部20の精度悪化を防止し、干渉波耐力を上げることができるタイミング再生部20の実施形態を説明する。

【0046】

図8は、本実施形態によるタイミング再生部20(図1(A))の構成例を示す図である。タイミング再生部20は、前方等化器21のタップ係数am1,bm1、後方等化器23のタップ係数ap1,bp1、第1の識別信号ff_d、第1の誤差信号ff_e、第2の識別信号fb_d及び第2の誤差信号fb_eを入力し、タップ係数a0〜a4を出力する。図8のタイミング再生部20は、図6のタイミング再生部20に対して、コントロール回路801、第1の乗算器802及び第2の乗算器803を追加したものである。以下、図8のタイミング再生部20が図6のタイミング再生部20と異なる点を説明する。

【0047】

コントロール回路801、第1の乗算器802及び第2の乗算器803は、位相比較部701内に設けられる。第1の乗算器802は、フリップフロップ716及び加算器727間に設けられる。第2の乗算器803は、フリップフロップ726及び加算器727間に設けられる。コントロール回路801は、前方等化器21のタップ係数am1,bm1及び後方等化器23のタップ係数ap1,bp1を基に第1のゲインFFg及び第2のゲインFBgを生成する。第1の乗算器802は、フリップフロップ716の出力データに対して第1のゲインFFgを乗算して出力する。第2の乗算器803は、フリップフロップ726の出力データに対して第2のゲインFBgを乗算して出力する。加算器727は、第1の乗算器802及び第2の乗算器803の出力データを加算して出力する。ループフィルタ702は、加算器727の出力データを平滑化して出力する。NCO703は、ループフィルタ702の出力データを入力し、位相信号θを出力する。第3のタップ係数演算部704は、位相信号θを基にタップ係数a0〜a4を演算し、図1(A)の補間器14及び18に同じタップ係数a0〜a4を出力する。

【0048】

図9(A)は、前方等化器21のタップ係数及び後方等化器23のタップ係数を示す図である。図5に示すように、タップ係数a0,am1〜amnは、前方等化器21内の同相FIRフィルタ601,604のタップ係数である。タップ係数a0は、主波A1に対応するセンタータップのタップ係数である。タップ係数am1〜amnは、前方干渉波A2に対応する同相タップ係数である。タップ係数bm1〜bmnは、前方等化器21内の直交FIRフィルタ602,603のタップ係数であり、前方干渉波A2に対応する直交タップ係数である。

【0049】

タップ係数ap1〜apnは、後方等化器23内の同相IIRフィルタ演算部611,614のタップ係数であり、後方干渉波A3に対応する同相タップ係数である。タップ係数bp1〜bpnは、後方等化器23内の直交IIRフィルタ演算部612,613のタップ係数であり、後方干渉波A3に対応する直交タップ係数である。

【0050】

同相タップ係数am1〜amn及び直交タップ係数bm1〜bmnは、センタータップのタップ係数0に対して時間的に前方(過去)のタップ係数である。第1の同相タップ係数am1は、センタータップ(タップ係数a0)に1番目に近い同相タップ係数である。第1の直交タップ係数bm1は、センタータップ(タップ係数a0)に1番目に近い直交タップ係数である。第2の同相タップ係数am2は、センタータップ(タップ係数a0)に2番目に近い同相タップ係数である。第2の直交タップ係数bm2は、センタータップ(タップ係数a0)に2番目に近い直交タップ係数である。

【0051】

これに対して、同相タップ係数ap1〜apn及び直交タップ係数bp1〜bpnは、センタータップのタップ係数0に対して時間的に後方(未来)のタップ係数である。第1の同相タップ係数ap1は、センタータップ(タップ係数a0)に1番目に近い同相タップ係数である。第1の直交タップ係数bp1は、センタータップ(タップ係数a0)に1番目に近い直交タップ係数である。第2の同相タップ係数ap2は、センタータップ(タップ係数a0)に2番目に近い同相タップ係数である。第2の直交タップ係数bp2は、センタータップ(タップ係数a0)に2番目に近い直交タップ係数である。

【0052】

図9(B)は、同相タップ係数am1及び直交タップ係数bm1のベクトル901の大きさを示す図である。位相平面上において、ベクトル901の大きさは、√(am12+bm12)で表される。

【0053】

図10(A)及び(B)は、図8のコントロール回路801の動作を説明するための図である。図10(A)は、主波A1の近傍に前方干渉波A2が存在する場合を示す図である。第1の同相タップ係数am1及び第1の直交タップ係数bm1のベクトルの大きさは、√(am12+bm12)で表され、主波A1に一番近いタップの前方干渉波A2の電力の大きさに対応する。これに対し、第1の同相タップ係数ap1及び第1の直交タップ係数bp1のベクトルの大きさは、√(ap12+bp12)で表され、主波A1に一番近いタップの後方干渉波A3の電力の大きさに対応する。√(am12+bm12)が√(ap12+bp12)よりある程度大きいときには、主波A1の近傍において前方干渉波A2のみが存在すること、又は主波A1の近傍において前方干渉波A2が後方干渉波A3より大きいことを意味する。その場合、前方等化器21の第1の誤差信号ff_eは、後方等化器23の第2の誤差信号fb_eより信頼度が低くなる。したがって、コントロール回路801は、第1のゲインFFgを小さくし、第2のゲインFBgを大きくする。これにより、主波A1の近傍に大電力の前方干渉波A2が存在する場合にも、タイミング再生部20は、高精度のタップ係数a0〜a4を演算することができる。

【0054】

図10(B)は、主波A1の近傍に後方干渉波A3が存在する場合を示す図である。√(ap12+bp12)が√(am12+bm12)よりある程度大きいときには、主波A1の近傍において後方干渉波A3のみが存在すること、又は主波A1の近傍において後方干渉波A3が前方干渉A2より大きいことを意味する。その場合、後方等化器23の第2の誤差信号fb_eは、前方等化器21の第1の誤差信号ff_eより信頼度が低くなる。したがって、コントロール回路801は、第1のゲインFFgを大きくし、第2のゲインFBgを小さくする。これにより、主波A1の近傍に大電力の後方干渉波A3が存在する場合にも、タイミング再生部20は、高精度のタップ係数a0〜a4を演算することができる。

【0055】

また、√(am12+bm12)と√(ap12+bp12)とが略同じであるときには、主波A1の近傍において前方干渉波A2及び後方干渉波A3が存在しないこと、又は主波A1の近傍において前方干渉波A2及び後方干渉波A3の大きさが略同じであることを意味する。その場合、前方等化器21の第1の誤差信号ff_eと後方等化器23の第2の誤差信号fb_eとは、信頼度が略同じである。したがって、コントロール回路801は、第1のゲインFFgと第2のゲインFBgとを略同じ値にする。これにより、タイミング再生部20は、高精度のタップ係数a0〜a4を演算することができる。

【0056】

図11は、本実施形態によるコントロール回路801(図8)の構成例を示す図である。乗算器1101は、前方等化器21の第1の同相タップ係数am1の2乗値am12を出力する。乗算器1102は、前方等化器21の第1の直交タップ係数bm1の2乗値bm12を出力する。加算器1103は、乗算器1101及び1102の出力値を加算し、値am12+bm12を出力する。値am12+bm12は、図10(A)及び(B)のベクトルの大きさ√(am12+bm12)に対応する。移動平均部1104は、加算器1103の出力値に対して移動平均(平滑化)を行って出力する。

【0057】

乗算器1111は、後方等化器23の第1の同相タップ係数ap1の2乗値ap12を出力する。乗算器1112は、後方等化器23の第1の直交タップ係数bp1の2乗値bp12を出力する。加算器1113は、乗算器1111及び1112の出力値を加算し、値ap12+bp12を出力する。値ap12+bp12は、図10(A)及び(B)のベクトルの大きさ√(ap12+bp12)に対応する。移動平均部1114は、加算器1113の出力値に対して移動平均(平滑化)を行って出力する。減算器1121は、移動平均部1104の出力値から移動平均部1114の出力値を減算し、C値を出力する。

【0058】

変換テーブル1122は、C値に対応する第1のゲインFFg及び第2のゲインFBgの変換テーブルを有し、加算器1121により出力されるC値を基に、第1のゲインFFg及び第2のゲインFBgを出力する。C値が正の値を取った場合、前方干渉波A2は後方干渉波A3より大きいことを意味し、C値が負の値を取った場合、後方干渉波A3は前方干渉波A2より大きいことを意味する。すなわち、C値が正の値を取った場合、前方干渉波A2が後方干渉波A3より大きいため前方等化器21からの第1の誤差信号ff_eの信頼度は低いと判断し、第1のゲインFFgは、「1.00」より小さい値を取り、第2のゲインFBgは、「1.00」より大きな値をとる。逆に、C値が負の値を取った場合、後方干渉波A3が前方干渉波A2より大きいため後方等化器23からの第2の誤差信号fb_eの信頼度は低いと判断し、第1のゲインFFgは、「1.00」より大きい値を取り、第2のゲインFBgは、「1.00」より小さい値をとる。また、C値が−10以上かつ+10以下であるときには、第1のゲインFFg及び第2のゲインFBgを「1.00」の同じ値にする。また、同じC値に対して、第1のゲインFFg及び第2のゲインFBgの乗算値FFg×FBgを略一定値(例えば、「1.00))としているのは、図8の位相比較部701の出力値が干渉波A2,A3によらず略一定となるようにすることで、タイミングリカバリループの安定化を図るためである。

【0059】

コントロール回路801は、前方等化器21のタップ係数am1,bm1及び後方等化器23のタップ係数ap1,bp1をモニタしながら、リアルタイムで動作しているため、干渉波の位置が主波A1に対して前方方向から後方方向(あるいはその逆)に移動した場合も、第1のゲインFFg及び第2のゲインFBgは、それに伴って変化する。

【0060】

図12は、他の実施形態によるコントロール回路801(図8)の構成例を示す図である。図12のコントロール回路801は、図11のコントロール回路801に対して、乗算器1201,1202,1211,1212、加算器1203,1213、移動平均部1204,1214及び加算器1205,1215を追加したものである。以下、図12の回路が図11の回路と異なる点を説明する。

【0061】

乗算器1201は、前方等化器21の第2の同相タップ係数am2の2乗値am22を出力する。乗算器1202は、前方等化器21の第2の直交タップ係数bm2の2乗値bm22を出力する。加算器1203は、乗算器1201及び1202の出力値を加算し、値am22+bm22を出力する。移動平均部1204は、加算器1203の出力値に対して移動平均(平滑化)を行って出力する。加算器1205は、移動平均部1104及び1204の出力値を加算して出力する。

【0062】

乗算器1211は、後方等化器23の第2の同相タップ係数ap2の2乗値ap22を出力する。乗算器1212は、後方等化器23の第2の直交タップ係数bp2の2乗値bp22を出力する。加算器1213は、乗算器1211及び1212の出力値を加算し、値ap22+bp22を出力する。移動平均部1214は、加算器1213の出力値に対して移動平均(平滑化)を行って出力する。加算器1215は、移動平均部1114及び1214の出力値を加算して出力する。減算器1121は、加算器1205の出力値から加算器1215の出力値を減算し、C値を出力する。変換テーブル1122は、減算器1121により出力されるC値を基に、第1のゲインFFg及び第2のゲインFBgを出力する。

【0063】

図12の回路は、図11の回路に対して、前方等化器21の第2の同相タップ係数am2及び第2の直交タップ係数bm2、並びに後方等化器23の第2の同相タップ係数ap2及び第2の直交タップ係数bp2が追加で入力されている点が異なる。これらのタップ係数am2,bm2,ap2,bp2は、センタータップ(タップ係数a0)に2番目に近いタップ係数である。図12の回路は、図11の回路に対して、より多くのタップ係数を用いることにより、前方干渉波A2及び後方干渉波A3の大きさをより正確に特定することができ、高精度の第1のゲインFFg及び第2のゲインFBgを設定することができる。

【0064】

以上のように、コントロール回路801は、前方干渉波A2が後方干渉波A3より大きいときには第1のゲインFFgを第2のゲインFBgより小さくし、後方干渉波A3が前方干渉波A2より大きいときには第2のゲインFBgを第1のゲインFFgより小さくする。

【0065】

また、コントロール回路801は、図5に示すように、前方等化器21の同相FIRフィルタ601,604、前方等化器21の直交FIRフィルタ602,603、後方等化器23の同相IIRフィルタ演算部611,614及び後方等化器23の直交IIRフィルタ演算部612,613のタップ係数を基に第1のゲインFFg及び第2のゲインFBgを生成する。

【0066】

また、コントロール回路801は、前方等化器21の同相FIRフィルタ601,604の同相タップ係数am1等及び前方等化器21の直交FIRフィルタ602,603の直交タップ係数bm1等のベクトルの大きさが、後方等化器23の同相IIRフィルタ演算部611,614の同相タップ係数ap1等及び後方等化器23の直交IIRフィルタ演算部612,613の直交タップ係数bp1等のベクトルの大きさより大きいときには、第1のゲインFFgを第2のゲインFBgより小さくする。

【0067】

これに対し、コントロール回路801は、後方等化器23の同相IIRフイルタ演算部611,614の同相タップ係数ap1等及び後方等化器23の直交IIRフィルタ演算部612,613の直交タップ係数bp1等のベクトルの大きさが、前方等化器21の同相FIRフィルタ601,604の同相タップ係数am1等及び前方等化器21の直交FIRフィルタ602,603の直交タップ係数bm1等のベクトルの大きさより大きいときには、第2のゲインFBgを第1のゲインFFgより小さくする。

【0068】

図11では、コントロール回路801は、前方等化器21の同相FIRフィルタ601,604のセンタータップ(タップ係数a0)に、時間的に1番目に近い第1の同相タップ係数am1及び第1の直交タップ係数bm1のベクトルの大きさと、後方等化器23の第1の同相タップ係数ap1及び第1の直交タップ係数bp1のベクトルの大きさとを比較し、第1のゲインFFg及び第2のゲインFBgを生成する。

【0069】

図12では、コントロール回路801は、前方等化器21の同相FIRフィルタ601,604のセンタータップ(タップ係数a0)に、時間的に1番目に近い第1の同相タップ係数am1及び第1の直交タップ係数bm1のベクトルの大きさと、後方等化器23の第1の同相タップ係数ap1及び第1の直交タップ係数bp1のベクトルの大きさと、前方等化器21の同相FIRフィルタ601,604のセンタータップ(タップ係数a0)に、時間的に2番目に近い第2の同相タップ係数am2及び第2の直交タップ係数bm2のベクトルの大きさと、後方等化器23の第2の同相タップ係数ap2及び第2の直交タップ係数bp2のベクトルの大きさを基に、第1のゲインFFg及び第2のゲインFBgを生成する。

【0070】

上記実施形態によれば、前方等化器21の第1の誤差信号ff_e及び後方等化器23の第2の誤差信号fb_eの信頼度に応じて、第1のFIRフィルタのタップ係数a0〜a4を演算するので、主波A1の近傍の干渉波A2,A3に対して、D/U比が数dB改善した効果が得られていることがFPGA(Field-Programmable Gate Array)により確認できた。ここで、D/U比は、主波A1の電力短区間平均値Dと干渉波A2,A3の電力短区間平均値Uとの比を示す。

【0071】

前方等化器21のFIRフィルタ601〜604のタップ係数及び後方等化器23のIIRフィルタ演算部611〜614のタップ係数を用いて、補間器(FIRフィルタ)14及び18のタップ係数a0〜a4を生成することにより、干渉波A2,A3による精度の悪化を防止することができる。

【0072】

なお、上記実施形態は、何れも本発明を実施するにあたっての具体化の例を示したものに過ぎず、これらによって本発明の技術的範囲が限定的に解釈されてはならないものである。すなわち、本発明はその技術思想、又はその主要な特徴から逸脱することなく、様々な形で実施することができる。

【符号の説明】

【0073】

10 アナログ/デジタル変換器

11 自動ゲインコントローラ

12,16 乗算器

13,17 ローパスフィルタ

14,18 補間器

15,19 ルートナイキストフィルタ

20 タイミング再生部

21 前方等化器

22 バタフライ演算器

23 後方等化器

24 キャリア再生部

25 識別、誤差信号生成部

26 第1のタップ係数演算部

27 第2のタップ係数演算部

28 可変ゲイン増幅器

【技術分野】

【0001】

本発明は、シンボルタイミングリカバリ回路に関する。

【背景技術】

【0002】

受信装置は、受信信号からシンボルタイミングを再生するためのシンボルタイミングリカバリ回路を有し、受信信号を再生する。受信信号の位相を制御してクロックに同期させる形式のシンボルタイミングリカバリ回路が知られている(例えば、特許文献1及び2参照)。

【0003】

また、トランスバーサルフィルタからなる前方等化器および後方等化器を有する等化器において、予備等化器と等化器制御回路を有する等化器が知られている(例えば、特許文献3参照)。

【0004】

また、推定したチャネル係数を用い、受信信号から送信信号を推定するビタビ型等化器であって、受信信号の時間軸に沿って等化を行う前方等化と時間軸の逆方向に等化を行う後方等化を行う双方向ビタビ型等化器が知られている(例えば、特許文献4参照)。

【先行技術文献】

【特許文献】

【0005】

【特許文献1】特開2000−101659号公報

【特許文献2】特開2009−33300号公報

【特許文献3】特開2010−161640号公報

【特許文献4】特開2001−251226号公報

【発明の概要】

【発明が解決しようとする課題】

【0006】

本発明の目的は、干渉波による精度の悪化を防止することができるシンボルタイミングリカバリ回路を提供することである。

【課題を解決するための手段】

【0007】

シンボルタイミングリカバリ回路は、第1の有限インパルス応答フィルタを用いて入力デジタル信号のゼロクロス点及び/又はデータ識別点の補間データを生成する補間器と、第2の有限インパルス応答フィルタを用いて前記補間器により生成された補間データを基に前記入力デジタル信号から前方干渉波を除去し、その除去した信号、第1の識別信号及び第1の誤差信号を出力する前方等化器と、第1の無限インパルス応答フィルタを用いて前記補間器により生成された補間データを基に前記入力デジタル信号から後方干渉波を除去し、その除去した信号、第2の識別信号及び第2の誤差信号を出力する後方等化器と、前記補間器により生成された補間データと前記前方等化器及び前記後方等化器により前記前方干渉波及び前記後方干渉波が除去された信号とを基に前記第2の有限インパルス応答フィルタのタップ係数を演算する第1のタップ係数演算部と、前記補間器により生成された補間データと前記前方等化器及び前記後方等化器により前記前方干渉波及び前記後方干渉波が除去された信号とを基に前記第1の無限インパルス応答フィルタのタップ係数を演算する第2のタップ係数演算部と、前記第2の有限インパルス応答フィルタのタップ係数、前記第1の無限インパルス応答フィルタのタップ係数、前記第1の識別信号、前記第1の誤差信号、前記第2の識別信号及び前記第2の誤差信号を基に前記第1の有限インパルス応答フィルタのタップ係数を生成するタイミング再生部とを有する。

【発明の効果】

【0008】

第2の有限インパルス応答フィルタのタップ係数及び第1の無限インパルス応答フィルタのタップ係数を用いて、第1の有限インパルス応答フィルタのタップ係数を生成することにより、干渉波による精度の悪化を防止することができる。

【図面の簡単な説明】

【0009】

【図1】図1(A)は実施形態によるシンボルタイミングリカバリ回路を有するQAM復調器の構成例を示す図であり、図1(B)は中間周波数信号の周波数スペクトルを示す図である。

【図2】シンボルタイミングリカバリ回路の動作を説明するためのタイムチャートである。

【図3】図1(A)の補間器の構成例を示す図である。

【図4】補間器の動作を説明するための図である。

【図5】図1(A)の前方等化器及び後方等化器の構成例を示す図である。

【図6】図1(A)のタイミング再生部の構成例を示す図である。

【図7】図7(A)〜(D)は第1の位相比較部の動作を説明するための図である。

【図8】本実施形態によるタイミング再生部の構成例を示す図である。

【図9】図9(A)は前方等化器及び後方等化器のタップ係数を示す図であり、図9(B)は同相タップ係数及び直交タップ係数のベクトルの大きさを示す図である。

【図10】図10(A)及び(B)は図8のコントロール回路の動作を説明するための図である。

【図11】本実施形態によるコントロール回路の構成例を示す図である。

【図12】他の実施形態によるコントロール回路の構成例を示す図である。

【発明を実施するための形態】

【0010】

図1(A)は実施形態によるシンボルタイミングリカバリ回路を有するQAM(Quadrature Amplitude Modulation:直交振幅変調)復調器(受信装置)の構成例を示す図であり、図1(B)は中間周波数(Intermediate Frequency:IF)信号INの周波数スペクトルを示す図である。QAMは、互いに独立な2つの搬送波(同相搬送波及び直交搬送波)の振幅及び位相を調整することによりデータを伝達する変調方式である。例えばQAM復調器は、LSI上にハードウェアとして実現される。QAM変調されたIF信号INは、図1(B)に示すように、帯域伝送された信号であり、ある帯域内で台形の形状を有するスペクトルを持つものである。可変ゲイン増幅器28は、IF信号INを所定のゲインで増幅して出力する。アナログ/デジタル変換器10は、可変ゲイン増幅器28の出力信号をアナログからデジタルに変換して出力する。自動ゲインコントローラ11は、アナログ/デジタル変換器10の出力信号のパワーが所望の値より大きいか否かを判定し、可変ゲイン増幅器28のゲインを制御する。乗算器12は、アナログ/デジタル変換器10の出力信号に対して信号Cos(ωt)を乗算し、同相(I)チャネル信号を出力する。乗算器16は、アナログ/デジタル変換器10の出力信号に対して信号Sin(ωt)を乗算し、直交(Q)チャネル信号を出力する。すなわち、アナログ/デジタル変換器10の出力信号は、Iチャネル信号及びQチャネル信号に分離される。ここで、角周波数ωに対応する周波数として、図1(B)のIF信号スペクトルの台形の中心周波数fcが用いられる。すなわち、ω=2×π×fcで表される。ローパスフィルタ13は、乗算器12の出力Iチャネル信号の高周波数の成分をカットし、Iチャネル信号I1を出力する。ローパスフィルタ17は、乗算器16の出力Qチャネル信号の高周波数の成分をカットし、Qチャネル信号Q1を出力する。補間器14は、有限インパルス応答(Finite Impulse Response:FIR)フィルタを有し、タップ係数a0〜a4を基にIチャネル信号I1を補間してIチャネル信号I2を出力し、シンボルタイミングを再生する。補間器18は、FIRフィルタを有し、タップ係数a0〜a4を基にQチャネル信号Q1を補間してQチャネル信号Q2を出力し、シンボルタイミングを再生する。

【0011】

図2は、シンボルタイミングリカバリ回路の動作を説明するためのタイムチャートである。アナログ/デジタル変換器10のサンプリング周波数は、入力信号INのシンボルレートの周波数の2倍よりも高い。図2の例では、アナログ/デジタル変換器10によりサンプリングデジタルデータS1〜S14が得られている。図2において、白丸印はサンプリング点を示し、黒丸印は入力信号INのゼロクロス点及びデータ識別点を示している。

【0012】

図3は、図1(A)の補間器14の構成例を示す図である。図1(A)の補間器18も補間器14と同様の構成を有する。補間器14は、例えば、4個の遅延器(フリップフロップ)201〜204、5個の乗算器211〜215、及び加算器221を有する5タップの第1のFIRフィルタを備える。遅延器201は、Iチャネル信号I1を遅延して出力する。遅延器202は、遅延器201の出力信号を遅延して出力する。遅延器203は、遅延器202の出力信号を遅延して出力する。遅延器204は、遅延器203の出力信号を遅延して出力する。乗算器211は、Iチャネル信号I1及びタップ係数a0を乗算して出力する。乗算器212は、遅延器201の出力信号及びタップ係数a1を乗算して出力する。乗算器213は、遅延器202の出力信号及びタップ係数a2を乗算して出力する。乗算器214は、遅延器203の出力信号及びタップ係数a3を乗算して出力する。乗算器215は、遅延器204の出力信号及びタップ係数a4を乗算して出力する。加算器221は、乗算器211〜215の出力信号を加算し、Iチャネル信号I2を出力する。

【0013】

補間器14は、第1のFIRフィルタを用いて、入力デジタル信号I1のサンプリングデータS1〜S14を用いて補間処理することにより、入力デジタル信号I1のゼロクロス点K2,K4及びデータ識別点K1,K3の補間データを生成する。なお、補間器14は、補間処理によって入力デジタル信号I1のデータ識別点K1,K3及びゼロクロス点K2,K4の補間データを生成する場合に限定されず、データ識別点K1,K3又はゼロクロス点K2,K4のうちの一方(例えば、データ識別点K1,K3のみ)の補間データを生成するようにしてもよい。

【0014】

図4は、補間器(FIRフィルタ)14の動作を説明するための図である。以下、補間器14を例に説明するが、補間器18も同様である。図4に示す特性401は、カットオフ周波数が「2×fs 」であるローパスフィルタのインパルス応答に相当する。ここで、周波数fsは、入力信号INのシンボルレートの周波数である。時間Tは、補間器(FIRフィルタ)14が備える各遅延器201〜204の遅延量に相当する。なお、時間Tは、アナログ/デジタル変換器10のサンプリング周波数の1周期(すなわち、2π)に相当する。

【0015】

補間器14は、5個のタップ係数a0〜a4に基づいて、入力信号I1の位相を調整する。ここで、タップ係数a0〜a4は、後述する図8のタイミング再生部20内のタップ係数演算部704により位相信号θに応じて決定される。例えば、参照番号402で示すように、位相信号θが「ゼロ」であれば、タップ係数a2以外のインパルス応答はゼロとなる。この場合、補間器14は、遅延時間が2Tの遅延器として動作する。また、参照番号403で示すように、位相信号θが「+π/2」であるときは、対応する5個のタップ係数a0〜a4が与えられ、補間器14における遅延時間は「2T+T/4」となる。この場合、入力信号I1の位相は、補間器14を通過することにより、「T/4(すなわち、π/2)」だけ遅れることになる。一方、参照番号404で示すように、位相信号θが「−π/2」であれば、対応する5個のタップ係数a0〜a4が与えられ、補間器14における遅延時間は「2T−T/4」となる。この場合、入力信号I1の位相は、補間器14を通過することにより、「T/4(すなわち、π/2)」だけ進むことになる。同様に、参照番号405で示すように、位相信号θが「−π」であれば、対応する5個のタップ係数a0〜a4が与えられ、入力信号I1の位相は、補間器14を通過することにより、「π」だけ進むことになる。このように、補間器14は、入力信号I1の位相を調整することができる。

【0016】

例えば、図2において、サンプリングデータS1の位相は、データ識別点K1に対して3π/5だけ遅れている。この場合、補間器14には、入力信号I1の位相を3π/5だけ進めるためのタップ係数a0〜a4が与えられる。そうすると、補間器14は、データ識別点K1における値を出力する。サンプリングデータS2の位相は、ゼロクロス点K2に対して4π/5だけ遅れている。この場合、補間器14には、入力信号I1の位相を4π/5だけ進めるためのタップ係数a0〜a4が与えられる。そうすると、補間器14は、ゼロクロス点K2における値を出力する。サンプリングデータS3の位相は、データ識別点K3に対してπだけ遅れている。この場合、補間器14には、入力信号I1の位相をπだけ進めるためのタップ係数a0〜a4が与えられる。そうすると、補間器14は、データ識別点K3における値を出力する。このように、補間器14は、サンプリングデータを用いて補間処理を行うことにより、入力信号I1のデータ識別点K1,K3及びゼロクロス点K2,K4における値を出力する。

【0017】

図1(A)において、ルートナイキストフィルタ15は、補間器14の出力信号I2をフィルタリングし、Iチャネル信号I3を出力する。ルートナイキストフィルタ19は、補間器18の出力信号Q2をフィルタリングし、Qチャネル信号Q3を出力する。ルートナイキストフィルタ15及び19は、送信装置にも備えられており、送信装置と受信装置とでナイキストフィルタとしての帯域制限を行うものである。

【0018】

マルチパスでは、図10(A)及び(B)に示すように、送信装置から送信された信号が障害物によって反射・回折し、受信装置が複数の経路(パス)から同じ信号を遅延量が異なる主波(希望波)A1、前方干渉波(先行波)A2及び/又は後方干渉波(遅延波)A3として受信してしまう。主波A1は、マルチパスの中で最も電力が大きいパスの信号波である。前方干渉波A2は、主波A1に対して所定の遅延量進んでいるパスの干渉波である。後方干渉波A3は、主波A1に対して所定の遅延量遅れているパスの干渉波である。

【0019】

前方等化器21は、複素FIRフィルタで構成され、図10(A)に示すように主波A1の前側に前方干渉波A2が存在する時、前方干渉波A2を除去して出力する。前方等化器21は、主に、ノンミニマムフェーズ時(前ゴースト時)の前方干渉波A2を除去する。バタフライ演算器22は、前方等化器21の出力信号を入力し、キャリア周波数の誤差を補正し、キャリア再生を行うものである。キャリア再生部24は、復調後のIチャネル信号OUTi及びQチャネル信号OUTqによるコンスタレーションの回転を基にキャリア周波数のずれを検出し、コンスタレーションの回転を止める方向にバタフライ演算器22を制御する。後方等化器23は、複素IIR(Infinite Impulse Response:無限インパルス応答)フィルタで構成され、図10(B)に示すように主波A1の後ろ側に後方干渉波A3が存在する時、後方干渉波A3を除去し、復調後のIチャネル信号OUTi及びQチャネル信号OUTqを出力する。後方等化器23は、主に、ミニマムフェーズ時(後ゴースト時)の後方干渉波A3を除去する。識別、誤差信号生成部25は、前方等化器21の入力信号I3,Q3及び後方等化器23の出力信号OUTi,OUTqを基に識別信号及び誤差信号を生成してタップ係数演算部26及び27に出力する。第1のタップ係数演算部26は、前方干渉波A2を除去するため、上記の識別信号及び誤差信号を基にタップ係数を生成し、前方等化器21に出力する。前方等化器21は、そのタップ係数を基に、複素FIRフィルタを用いて前方干渉波A2を除去する。第2のタップ係数演算部27は、後方干渉波A3を除去するため、上記の識別信号及び誤差信号を基にタップ係数を生成し、後方等化器23に出力する。後方等化器21は、そのタップ係数を基に、複素IIRフィルタを用いて後方干渉波A3を除去する。

【0020】

タイミング再生部20は、前方等化器21から第1の識別信号ff_d及び第1の誤差信号ff_eを入力し、後方等化器23から第2の識別信号fb_d及び第2の誤差信号fb_eを入力し、第1のタップ係数演算部26から第1の同相タップ係数am1及び第1の直交タップ係数bm1を入力し、第2のタップ係数演算部27から第1の同相タップ係数ap1及び第1の直交タップ係数bp1を入力し、同じタップ係数a0〜a4を補間器14及び18に出力する。

【0021】

図5は、図1(A)の前方等化器21及び後方等化器23の構成例を示す図である。前方等化器21は、遅延器605、同相FIRフィルタ601,604、直交FIRフィルタ602,603、減算器606,608及び加算器607を有する複素FIRフィルタを備える。遅延器605は、Iチャネル信号I3に対して、同相FIRフィルタ601の遅延量と同じ遅延量遅延し、第1の識別信号ff_dを出力する。

【0022】

同相FIRフィルタ601は、図3の補間器(FIRフィルタ)14と同様の構成を有し、第1のタップ係数演算部26から入力した同相タップ係数a0,am1〜amnを基に、Iチャネル信号I3の実部をフィルタリングし、補正後の同相成分信号を出力する。直交FIRフィルタ603は、図3の補間器(FIRフィルタ)14と同様の構成を有し、第1のタップ係数演算部26から入力した直交タップ係数bm1〜bmnを基に、Iチャネル信号I3の虚部をフィルタリングし、補正後の直交成分信号を出力する。

【0023】

同相FIRフィルタ604は、図3の補間器(FIRフィルタ)14と同様の構成を有し、第1のタップ係数演算部26から入力した同相タップ係数a0,am1〜amnを基に、Qチャネル信号Q3の実部をフィルタリングし、補正後の同相成分信号を出力する。直交FIRフィルタ602は、図3の補間器(FIRフィルタ)14と同様の構成を有し、第1のタップ係数演算部26から入力した直交タップ係数bm1〜bmnを基に、Qチャネル信号Q3の虚部をフィルタリングし、補正後の直交成分信号を出力する。

【0024】

加算器607は、同相FIRフィルタ601により出力される補正後の同相成分信号及び直交FIRフィルタ602により出力される補正後の直交成分信号を加算し、前方干渉波A2が除去されたIチャネル信号を出力する。減算器608は、同相FIRフィルタ604により出力される補正後の同相成分信号から直交FIRフィルタ603により出力される補正後の直交成分信号を減算し、前方干渉波A2が除去されたQチャネル信号を出力する。減算器606は、同相FIRフィルタ601により出力される補正後の同相成分信号から第1の識別信号ff_dを減算し、第1の誤差信号(同相成分)ff_eを出力する。第1の誤差信号ff_eは、時間軸方向の誤差情報である。

【0025】

バタフライ演算器22は、加算器607により出力されるIチャネル信号及び減算器608により出力されるQチャネル信号を入力し、バタフライ演算を行い、コンスタレーションの回転を止めるためにキャリア周波数の誤差を補正し、Iチャネル信号及びQチャネル信号を出力する。

【0026】

後方等化器23は、同相IIRフィルタ演算部611,614、直交IIRフィルタ演算部612,613、加算器615、減算器616及び識別器617,618を有する複素IIRフィルタを備える。

【0027】

同相IIRフィルタ演算部611は、図3の補間器(FIRフィルタ)14と同様のハードウェア構成を有し、第2のタップ係数演算部27から入力した同相タップ係数ap1〜apnを基に、識別器617により出力されるIチャネル信号の実部をフィルタリングし、第2の誤差信号(同相成分)fb_eを出力する。第2の誤差信号fb_eは、時間軸方向の誤差情報である。また、第2の識別信号fb_dは、バラフライ演算器22により出力されるIチャネル信号と同じ信号である。直交IIRフィルタ演算部613は、図3の補間器(FIRフィルタ)14と同様のハードウェア構成を有し、第2のタップ係数演算部27から入力した直交タップ係数bp1〜bpnを基に、識別器617により出力されるIチャネル信号の虚部をフィルタリングし、直交成分の誤差信号を出力する。

【0028】

同相IIRフィルタ演算部614は、図3の補間器(FIRフィルタ)14と同様のハードウェア構成を有し、第2のタップ係数演算部27から入力した同相タップ係数ap1〜apnを基に、識別器618により出力されるQチャネル信号の実部をフィルタリングし、同相成分の誤差信号を出力する。直交IIRフィルタ演算部612は、図3の補間器(FIRフィルタ)14と同様のハードウェア構成を有し、第2のタップ係数演算部27から入力した直交タップ係数bp1〜bpnを基に、識別器618により出力されるQチャネル信号の虚部をフィルタリングし、直交成分の誤差信号を出力する。

【0029】

加算器615は、バタフライ演算器22により出力されるIチャネル信号、第2の誤差信号fb_e及び直交IIRフィルタ演算部612により出力される直交成分を加算し、後方干渉波A3が除去されたIチャネル信号OUTiを出力する。Iチャネル信号OUTiは、前方干渉波A2及び後方干渉波A3が除去された主波A1のIチャネル信号である。識別器617は、加算器615の出力信号OUTiを識別し、識別したIチャネル信号を出力する。

【0030】

減算器616は、バタフライ演算器22により出力されるQチャネル信号及び同相IIRフィルタ演算部614により出力される同相成分を加算し、その加算した信号から直交IIRフィルタ演算部613により出力される直交成分を減算し、後方干渉波A3が除去されたQチャネル信号OUTqを出力する。Qチャネル信号OUTqは、前方干渉波A2及び後方干渉波A3が除去された主波A1のQチャネル信号である。識別器618は、減算器616の出力信号OUTqを識別し、識別したQチャネル信号を出力する。

【0031】

なお、前方等化器21を前段に設け、後方等化器23を後段に設ける場合を例に説明したが、後方等化器23を前段に設け、前方等化器21を後段に設けるようにしてもよい。

【0032】

以上のように、前方等化器21は、第2のFIRフィルタ601〜604を用いて補間器14,18により生成された補間データを基に入力デジタル信号から前方干渉波A2を除去し、その除去した信号、第1の識別信号ff_d及び第1の誤差信号ff_eを出力する。第1の識別信号ff_dは、前方干渉波A2の除去前の信号である。第1の誤差信号ff_eは、前方干渉波A2の除去前の信号と前方干渉波A2の除去後の信号との差分の信号である。第1のタップ係数演算部26(図1(A))は、補間器14,18により生成された補間データI3,Q3と前方等化器21及び後方等化器23により前方干渉波A2及び後方干渉波A3が除去された信号OUTi,OUTqとを基に第2のFIRフィルタ601〜604のタップ係数a0,am1〜amn,bm1〜bmnを演算する。

【0033】

後方等化器23は、IIRフィルタ演算部611〜614を用いて補間器14,18により生成された補間データを基に入力デジタル信号から後方干渉波A3を除去し、その除去した信号、第2の識別信号fb_d及び第2の誤差信号fb_eを出力する。第2の識別信号fb_dは、後方干渉波A3の除去前の信号である。第2の誤差信号fb_eは、後方干渉波A3の除去前の信号と後方干渉波A3の除去後の信号との差分の信号である。第2のタップ係数演算部27(図1(A))は、補間器14,18により生成された補間データI3,Q3と前方等化器21及び後方等化器23により前方干渉波A2及び後方干渉波A3が除去された信号OUTi,OUTqとを基にIIRフィルタ演算部611〜614のタップ係数ap1〜apn,bp1〜bpnを演算する。

【0034】

図6は、第1の識別信号ff_d、第1の誤差信号ff_e、第2の識別信号fb_d及び第2の誤差信号fb_eのみを用いて補間器14、18に入力されるタップ係数a0〜a4を生成するタイミング再生部20(図1(A))の構成例を示す図である。第1の識別信号ff_d、第1の誤差信号ff_eは、図5の前方等化器21から入力される信号である。第2の識別信号fb_d及び第2の誤差信号fb_eは、図5の後方等化器23から入力される信号である。タイミング再生部20は、位相比較部701、ループフィルタ702、数値制御発振器(Numerically Controlled Oscillator:NCO)703及び第3のタップ係数演算部704を有する。数値制御発振器703は、位相信号θを出力する。第3のタップ係数演算部704は、位相信号θを基にタップ係数a0〜a4を演算する。位相比較部701は、第1の位相比較部731、第2の位相比較部732及び加算器727を有する。第1の位相比較部731は、遅延器711〜713、比較器714、乗算器715及びフリップフロップ716を有する。第2の位相比較部732は、遅延器721〜723、比較器724、乗算器725及びフリップフロップ726を有する。

【0035】

図7(A)〜(D)は、第1の位相比較部731の動作を説明するための図である。図7(A)及び(B)は入力データ502が理想サンプリング点502に対して進んでいる場合を示し、図7(A)は入力データ502が単調減少している場合を示し、図7(B)は入力データ502が単調増加している場合を示す。図7(C)及び(D)は入力データ502が理想サンプリング点502に対して遅れている場合を示し、図7(C)は入力データ502が単調減少している場合を示し、図7(D)は入力データ502が単調増加している場合を示す。入力データ502は、第1の識別信号ff_dに対応する。

【0036】

第1の位相比較部731は、第1の識別信号ff_dの位相誤差を検出する。遅延器711は、第1の識別信号ff_dのデータCを遅延し、データBを出力する。遅延器712は、遅延器711の出力データBを遅延し、データAを出力する。ここで、データBを現在のデータとすると、データCは未来のデータ、データAは過去のデータである。

【0037】

比較器714は、データA,B,Cの値を比較した結果、C>B>Aの場合には単調増加であると判断して「−1」を出力し、C<B<Aの場合には単調減少であると判断して「+1」を出力し、それ以外の場合には「0」を出力する。

【0038】

遅延器713は、タイミング調整のため、第1の誤差信号ff_eを遅延して出力する。これにより、比較器714の出力データと遅延器713の出力データとが同一時刻に調整される。乗算器715は、比較器714の出力データと遅延器713の出力データとを乗算する。フリップフロップ716は、比較器714の出力データが「−1」又は「+1」のときには乗算器715の出力データをラッチして出力し、比較器714の出力データが「0」のときには現在保持している前回と同じデータを出力する。第1の位相比較部731は、第1の識別信号ff_eの時間遷移に応じて第1の誤差信号ff_eに正負符号を付与する。

【0039】

このように、入力データ502の位相が理想サンプリング点501に対して進んでいれば、第1の位相比較部731は、位相誤差として正の値を出力する。一方、入力データ502の位相が理想サンプリング点501に対して遅れていれば、第1の位相比較部731は、位相誤差として負の値を出力する。

【0040】

次に、第2の位相比較部732について説明する。第2の位相比較部732は、第1の位相比較部731と同様に、第2の識別信号fb_d及び第2の誤差信号fb_eを入力し、位相誤差を出力する。遅延器721は、第2の識別信号fb_dのデータCを遅延し、データBを出力する。遅延器722は、遅延器721の出力データBを遅延し、データAを出力する。ここで、データBを現在のデータとすると、データCは未来のデータ、データAは過去のデータである。比較器724は、データA,B,Cの比較の結果、C>B>Aの場合には単調増加であると判断して「−1」を出力し、C<B<Aの場合には単調減少であると判断して「+1」を出力し、それ以外の場合には「0」を出力する。遅延器723は、タイミング調整のため、第2の誤差信号fb_eを遅延して出力する。これにより、比較器724の出力データと遅延器723の出力データとが同一時刻に調整される。乗算器725は、比較器724の出力データと遅延器723の出力データとを乗算する。フリップフロップ726は、比較器724の出力データが「−1」又は「+1」のときには乗算器725の出力データをラッチして出力し、比較器724の出力データが「0」のときには現在保持している前回と同じデータを出力する。第2の位相比較部732は、第2の識別信号fb_dの時間遷移に応じて第2の誤差信号fb_eに正負符号を付与する。

【0041】

加算器727は、フリップフロップ716及び726が出力する位相誤差データを加算して出力する。

【0042】

ループフィルタ702は、加算器727から出力される位相誤差データを平滑化(又は平均化)する。すなわち、ループフィルタ702は、ローパスフィルタとして動作する。そして、ループフィルタ702により平滑化された位相誤差データは、ほぼ一定の値に収束する。

【0043】

NCO703は、無限位相の積分器(又は完全積分器)であり、ループフィルタ702から与えられる位相誤差データを累積的に加算する。すなわち、位相誤差データは積分される。ここで、位相誤差データは、基本的に、ほぼ一定である。したがって、NCO703により出力される位相信号θは、時間経過に対して、ほぼリニアに増加してゆく。また、上述の位相誤差データは、1シンボル当たりの位相誤差を表す。NCO703には、1組の基準値が設定されている。1組の基準値は、入力信号の位相に換算したときに「+π」及び「−π」を表すように定義される。そして、NCO703により得られる位相信号θは、一方の基準値(例えば「+π」)を超えると、リセットされる。ここで、リセットとは、位相信号θに「2π」を加算する処理(あるいは、位相信号θから「2π」を減算する処理)を意味する。したがって、NCO703により生成される位相信号θの波形は、ノコギリ波となる。

【0044】

第3のタップ係数演算部704は、NCO703により生成される位相信号θに基づいてタップ係数a0〜a4を生成し、図1(A)の補間器14及び18に同じタップ係数a0〜a4を出力する。

【0045】

ここで、図6のタイミング再生部20において、主波A1の近傍に大電力の前方干渉波A2又は後方干渉波A3が存在する場合、前方等化器21及び後方等化器23から得られる第1の誤差信号ff_e又は第2の誤差信号fb_eの信頼度が落ちる。その結果、タイミング再生部20の精度が悪化し、干渉波耐力が上げられない問題が生ずる。そこで、主波A1の近傍に大電力の前方干渉波A2又は後方干渉波A3が存在する場合でも、タイミング再生部20の精度悪化を防止し、干渉波耐力を上げることができるタイミング再生部20の実施形態を説明する。

【0046】

図8は、本実施形態によるタイミング再生部20(図1(A))の構成例を示す図である。タイミング再生部20は、前方等化器21のタップ係数am1,bm1、後方等化器23のタップ係数ap1,bp1、第1の識別信号ff_d、第1の誤差信号ff_e、第2の識別信号fb_d及び第2の誤差信号fb_eを入力し、タップ係数a0〜a4を出力する。図8のタイミング再生部20は、図6のタイミング再生部20に対して、コントロール回路801、第1の乗算器802及び第2の乗算器803を追加したものである。以下、図8のタイミング再生部20が図6のタイミング再生部20と異なる点を説明する。

【0047】

コントロール回路801、第1の乗算器802及び第2の乗算器803は、位相比較部701内に設けられる。第1の乗算器802は、フリップフロップ716及び加算器727間に設けられる。第2の乗算器803は、フリップフロップ726及び加算器727間に設けられる。コントロール回路801は、前方等化器21のタップ係数am1,bm1及び後方等化器23のタップ係数ap1,bp1を基に第1のゲインFFg及び第2のゲインFBgを生成する。第1の乗算器802は、フリップフロップ716の出力データに対して第1のゲインFFgを乗算して出力する。第2の乗算器803は、フリップフロップ726の出力データに対して第2のゲインFBgを乗算して出力する。加算器727は、第1の乗算器802及び第2の乗算器803の出力データを加算して出力する。ループフィルタ702は、加算器727の出力データを平滑化して出力する。NCO703は、ループフィルタ702の出力データを入力し、位相信号θを出力する。第3のタップ係数演算部704は、位相信号θを基にタップ係数a0〜a4を演算し、図1(A)の補間器14及び18に同じタップ係数a0〜a4を出力する。

【0048】

図9(A)は、前方等化器21のタップ係数及び後方等化器23のタップ係数を示す図である。図5に示すように、タップ係数a0,am1〜amnは、前方等化器21内の同相FIRフィルタ601,604のタップ係数である。タップ係数a0は、主波A1に対応するセンタータップのタップ係数である。タップ係数am1〜amnは、前方干渉波A2に対応する同相タップ係数である。タップ係数bm1〜bmnは、前方等化器21内の直交FIRフィルタ602,603のタップ係数であり、前方干渉波A2に対応する直交タップ係数である。

【0049】

タップ係数ap1〜apnは、後方等化器23内の同相IIRフィルタ演算部611,614のタップ係数であり、後方干渉波A3に対応する同相タップ係数である。タップ係数bp1〜bpnは、後方等化器23内の直交IIRフィルタ演算部612,613のタップ係数であり、後方干渉波A3に対応する直交タップ係数である。

【0050】

同相タップ係数am1〜amn及び直交タップ係数bm1〜bmnは、センタータップのタップ係数0に対して時間的に前方(過去)のタップ係数である。第1の同相タップ係数am1は、センタータップ(タップ係数a0)に1番目に近い同相タップ係数である。第1の直交タップ係数bm1は、センタータップ(タップ係数a0)に1番目に近い直交タップ係数である。第2の同相タップ係数am2は、センタータップ(タップ係数a0)に2番目に近い同相タップ係数である。第2の直交タップ係数bm2は、センタータップ(タップ係数a0)に2番目に近い直交タップ係数である。

【0051】

これに対して、同相タップ係数ap1〜apn及び直交タップ係数bp1〜bpnは、センタータップのタップ係数0に対して時間的に後方(未来)のタップ係数である。第1の同相タップ係数ap1は、センタータップ(タップ係数a0)に1番目に近い同相タップ係数である。第1の直交タップ係数bp1は、センタータップ(タップ係数a0)に1番目に近い直交タップ係数である。第2の同相タップ係数ap2は、センタータップ(タップ係数a0)に2番目に近い同相タップ係数である。第2の直交タップ係数bp2は、センタータップ(タップ係数a0)に2番目に近い直交タップ係数である。

【0052】

図9(B)は、同相タップ係数am1及び直交タップ係数bm1のベクトル901の大きさを示す図である。位相平面上において、ベクトル901の大きさは、√(am12+bm12)で表される。

【0053】

図10(A)及び(B)は、図8のコントロール回路801の動作を説明するための図である。図10(A)は、主波A1の近傍に前方干渉波A2が存在する場合を示す図である。第1の同相タップ係数am1及び第1の直交タップ係数bm1のベクトルの大きさは、√(am12+bm12)で表され、主波A1に一番近いタップの前方干渉波A2の電力の大きさに対応する。これに対し、第1の同相タップ係数ap1及び第1の直交タップ係数bp1のベクトルの大きさは、√(ap12+bp12)で表され、主波A1に一番近いタップの後方干渉波A3の電力の大きさに対応する。√(am12+bm12)が√(ap12+bp12)よりある程度大きいときには、主波A1の近傍において前方干渉波A2のみが存在すること、又は主波A1の近傍において前方干渉波A2が後方干渉波A3より大きいことを意味する。その場合、前方等化器21の第1の誤差信号ff_eは、後方等化器23の第2の誤差信号fb_eより信頼度が低くなる。したがって、コントロール回路801は、第1のゲインFFgを小さくし、第2のゲインFBgを大きくする。これにより、主波A1の近傍に大電力の前方干渉波A2が存在する場合にも、タイミング再生部20は、高精度のタップ係数a0〜a4を演算することができる。

【0054】

図10(B)は、主波A1の近傍に後方干渉波A3が存在する場合を示す図である。√(ap12+bp12)が√(am12+bm12)よりある程度大きいときには、主波A1の近傍において後方干渉波A3のみが存在すること、又は主波A1の近傍において後方干渉波A3が前方干渉A2より大きいことを意味する。その場合、後方等化器23の第2の誤差信号fb_eは、前方等化器21の第1の誤差信号ff_eより信頼度が低くなる。したがって、コントロール回路801は、第1のゲインFFgを大きくし、第2のゲインFBgを小さくする。これにより、主波A1の近傍に大電力の後方干渉波A3が存在する場合にも、タイミング再生部20は、高精度のタップ係数a0〜a4を演算することができる。

【0055】

また、√(am12+bm12)と√(ap12+bp12)とが略同じであるときには、主波A1の近傍において前方干渉波A2及び後方干渉波A3が存在しないこと、又は主波A1の近傍において前方干渉波A2及び後方干渉波A3の大きさが略同じであることを意味する。その場合、前方等化器21の第1の誤差信号ff_eと後方等化器23の第2の誤差信号fb_eとは、信頼度が略同じである。したがって、コントロール回路801は、第1のゲインFFgと第2のゲインFBgとを略同じ値にする。これにより、タイミング再生部20は、高精度のタップ係数a0〜a4を演算することができる。

【0056】

図11は、本実施形態によるコントロール回路801(図8)の構成例を示す図である。乗算器1101は、前方等化器21の第1の同相タップ係数am1の2乗値am12を出力する。乗算器1102は、前方等化器21の第1の直交タップ係数bm1の2乗値bm12を出力する。加算器1103は、乗算器1101及び1102の出力値を加算し、値am12+bm12を出力する。値am12+bm12は、図10(A)及び(B)のベクトルの大きさ√(am12+bm12)に対応する。移動平均部1104は、加算器1103の出力値に対して移動平均(平滑化)を行って出力する。

【0057】

乗算器1111は、後方等化器23の第1の同相タップ係数ap1の2乗値ap12を出力する。乗算器1112は、後方等化器23の第1の直交タップ係数bp1の2乗値bp12を出力する。加算器1113は、乗算器1111及び1112の出力値を加算し、値ap12+bp12を出力する。値ap12+bp12は、図10(A)及び(B)のベクトルの大きさ√(ap12+bp12)に対応する。移動平均部1114は、加算器1113の出力値に対して移動平均(平滑化)を行って出力する。減算器1121は、移動平均部1104の出力値から移動平均部1114の出力値を減算し、C値を出力する。

【0058】

変換テーブル1122は、C値に対応する第1のゲインFFg及び第2のゲインFBgの変換テーブルを有し、加算器1121により出力されるC値を基に、第1のゲインFFg及び第2のゲインFBgを出力する。C値が正の値を取った場合、前方干渉波A2は後方干渉波A3より大きいことを意味し、C値が負の値を取った場合、後方干渉波A3は前方干渉波A2より大きいことを意味する。すなわち、C値が正の値を取った場合、前方干渉波A2が後方干渉波A3より大きいため前方等化器21からの第1の誤差信号ff_eの信頼度は低いと判断し、第1のゲインFFgは、「1.00」より小さい値を取り、第2のゲインFBgは、「1.00」より大きな値をとる。逆に、C値が負の値を取った場合、後方干渉波A3が前方干渉波A2より大きいため後方等化器23からの第2の誤差信号fb_eの信頼度は低いと判断し、第1のゲインFFgは、「1.00」より大きい値を取り、第2のゲインFBgは、「1.00」より小さい値をとる。また、C値が−10以上かつ+10以下であるときには、第1のゲインFFg及び第2のゲインFBgを「1.00」の同じ値にする。また、同じC値に対して、第1のゲインFFg及び第2のゲインFBgの乗算値FFg×FBgを略一定値(例えば、「1.00))としているのは、図8の位相比較部701の出力値が干渉波A2,A3によらず略一定となるようにすることで、タイミングリカバリループの安定化を図るためである。

【0059】

コントロール回路801は、前方等化器21のタップ係数am1,bm1及び後方等化器23のタップ係数ap1,bp1をモニタしながら、リアルタイムで動作しているため、干渉波の位置が主波A1に対して前方方向から後方方向(あるいはその逆)に移動した場合も、第1のゲインFFg及び第2のゲインFBgは、それに伴って変化する。

【0060】

図12は、他の実施形態によるコントロール回路801(図8)の構成例を示す図である。図12のコントロール回路801は、図11のコントロール回路801に対して、乗算器1201,1202,1211,1212、加算器1203,1213、移動平均部1204,1214及び加算器1205,1215を追加したものである。以下、図12の回路が図11の回路と異なる点を説明する。

【0061】

乗算器1201は、前方等化器21の第2の同相タップ係数am2の2乗値am22を出力する。乗算器1202は、前方等化器21の第2の直交タップ係数bm2の2乗値bm22を出力する。加算器1203は、乗算器1201及び1202の出力値を加算し、値am22+bm22を出力する。移動平均部1204は、加算器1203の出力値に対して移動平均(平滑化)を行って出力する。加算器1205は、移動平均部1104及び1204の出力値を加算して出力する。

【0062】

乗算器1211は、後方等化器23の第2の同相タップ係数ap2の2乗値ap22を出力する。乗算器1212は、後方等化器23の第2の直交タップ係数bp2の2乗値bp22を出力する。加算器1213は、乗算器1211及び1212の出力値を加算し、値ap22+bp22を出力する。移動平均部1214は、加算器1213の出力値に対して移動平均(平滑化)を行って出力する。加算器1215は、移動平均部1114及び1214の出力値を加算して出力する。減算器1121は、加算器1205の出力値から加算器1215の出力値を減算し、C値を出力する。変換テーブル1122は、減算器1121により出力されるC値を基に、第1のゲインFFg及び第2のゲインFBgを出力する。

【0063】

図12の回路は、図11の回路に対して、前方等化器21の第2の同相タップ係数am2及び第2の直交タップ係数bm2、並びに後方等化器23の第2の同相タップ係数ap2及び第2の直交タップ係数bp2が追加で入力されている点が異なる。これらのタップ係数am2,bm2,ap2,bp2は、センタータップ(タップ係数a0)に2番目に近いタップ係数である。図12の回路は、図11の回路に対して、より多くのタップ係数を用いることにより、前方干渉波A2及び後方干渉波A3の大きさをより正確に特定することができ、高精度の第1のゲインFFg及び第2のゲインFBgを設定することができる。

【0064】

以上のように、コントロール回路801は、前方干渉波A2が後方干渉波A3より大きいときには第1のゲインFFgを第2のゲインFBgより小さくし、後方干渉波A3が前方干渉波A2より大きいときには第2のゲインFBgを第1のゲインFFgより小さくする。

【0065】

また、コントロール回路801は、図5に示すように、前方等化器21の同相FIRフィルタ601,604、前方等化器21の直交FIRフィルタ602,603、後方等化器23の同相IIRフィルタ演算部611,614及び後方等化器23の直交IIRフィルタ演算部612,613のタップ係数を基に第1のゲインFFg及び第2のゲインFBgを生成する。

【0066】

また、コントロール回路801は、前方等化器21の同相FIRフィルタ601,604の同相タップ係数am1等及び前方等化器21の直交FIRフィルタ602,603の直交タップ係数bm1等のベクトルの大きさが、後方等化器23の同相IIRフィルタ演算部611,614の同相タップ係数ap1等及び後方等化器23の直交IIRフィルタ演算部612,613の直交タップ係数bp1等のベクトルの大きさより大きいときには、第1のゲインFFgを第2のゲインFBgより小さくする。

【0067】

これに対し、コントロール回路801は、後方等化器23の同相IIRフイルタ演算部611,614の同相タップ係数ap1等及び後方等化器23の直交IIRフィルタ演算部612,613の直交タップ係数bp1等のベクトルの大きさが、前方等化器21の同相FIRフィルタ601,604の同相タップ係数am1等及び前方等化器21の直交FIRフィルタ602,603の直交タップ係数bm1等のベクトルの大きさより大きいときには、第2のゲインFBgを第1のゲインFFgより小さくする。

【0068】

図11では、コントロール回路801は、前方等化器21の同相FIRフィルタ601,604のセンタータップ(タップ係数a0)に、時間的に1番目に近い第1の同相タップ係数am1及び第1の直交タップ係数bm1のベクトルの大きさと、後方等化器23の第1の同相タップ係数ap1及び第1の直交タップ係数bp1のベクトルの大きさとを比較し、第1のゲインFFg及び第2のゲインFBgを生成する。

【0069】

図12では、コントロール回路801は、前方等化器21の同相FIRフィルタ601,604のセンタータップ(タップ係数a0)に、時間的に1番目に近い第1の同相タップ係数am1及び第1の直交タップ係数bm1のベクトルの大きさと、後方等化器23の第1の同相タップ係数ap1及び第1の直交タップ係数bp1のベクトルの大きさと、前方等化器21の同相FIRフィルタ601,604のセンタータップ(タップ係数a0)に、時間的に2番目に近い第2の同相タップ係数am2及び第2の直交タップ係数bm2のベクトルの大きさと、後方等化器23の第2の同相タップ係数ap2及び第2の直交タップ係数bp2のベクトルの大きさを基に、第1のゲインFFg及び第2のゲインFBgを生成する。

【0070】

上記実施形態によれば、前方等化器21の第1の誤差信号ff_e及び後方等化器23の第2の誤差信号fb_eの信頼度に応じて、第1のFIRフィルタのタップ係数a0〜a4を演算するので、主波A1の近傍の干渉波A2,A3に対して、D/U比が数dB改善した効果が得られていることがFPGA(Field-Programmable Gate Array)により確認できた。ここで、D/U比は、主波A1の電力短区間平均値Dと干渉波A2,A3の電力短区間平均値Uとの比を示す。

【0071】

前方等化器21のFIRフィルタ601〜604のタップ係数及び後方等化器23のIIRフィルタ演算部611〜614のタップ係数を用いて、補間器(FIRフィルタ)14及び18のタップ係数a0〜a4を生成することにより、干渉波A2,A3による精度の悪化を防止することができる。

【0072】

なお、上記実施形態は、何れも本発明を実施するにあたっての具体化の例を示したものに過ぎず、これらによって本発明の技術的範囲が限定的に解釈されてはならないものである。すなわち、本発明はその技術思想、又はその主要な特徴から逸脱することなく、様々な形で実施することができる。

【符号の説明】

【0073】

10 アナログ/デジタル変換器

11 自動ゲインコントローラ

12,16 乗算器

13,17 ローパスフィルタ

14,18 補間器

15,19 ルートナイキストフィルタ

20 タイミング再生部

21 前方等化器

22 バタフライ演算器

23 後方等化器

24 キャリア再生部

25 識別、誤差信号生成部

26 第1のタップ係数演算部

27 第2のタップ係数演算部

28 可変ゲイン増幅器

【特許請求の範囲】

【請求項1】

第1の有限インパルス応答フィルタを用いて入力デジタル信号のゼロクロス点及び/又はデータ識別点の補間データを生成する補間器と、

第2の有限インパルス応答フィルタを用いて前記補間器により生成された補間データを基に前記入力デジタル信号から前方干渉波を除去し、その除去した信号、第1の識別信号及び第1の誤差信号を出力する前方等化器と、

第1の無限インパルス応答フィルタを用いて前記補間器により生成された補間データを基に前記入力デジタル信号から後方干渉波を除去し、その除去した信号、第2の識別信号及び第2の誤差信号を出力する後方等化器と、

前記補間器により生成された補間データと前記前方等化器及び前記後方等化器により前記前方干渉波及び前記後方干渉波が除去された信号とを基に前記第2の有限インパルス応答フィルタのタップ係数を演算する第1のタップ係数演算部と、

前記補間器により生成された補間データと前記前方等化器及び前記後方等化器により前記前方干渉波及び前記後方干渉波が除去された信号とを基に前記第1の無限インパルス応答フィルタのタップ係数を演算する第2のタップ係数演算部と、

前記第2の有限インパルス応答フィルタのタップ係数、前記第1の無限インパルス応答フィルタのタップ係数、前記第1の識別信号、前記第1の誤差信号、前記第2の識別信号及び前記第2の誤差信号を基に前記第1の有限インパルス応答フィルタのタップ係数を生成するタイミング再生部と

を有することを特徴とするシンボルタイミングリカバリ回路。

【請求項2】

前記第1の識別信号は、前記前方干渉波の除去前の信号であり、

前記第1の誤差信号は、前記前方干渉波の除去前の信号と前記前方干渉波の除去後の信号との差分の信号であり、

前記第2の識別信号は、前記後方干渉波の除去前の信号であり、

前記第2の誤差信号は、前記後方干渉波の除去前の信号と前記後方干渉波の除去後の信号との差分の信号であることを特徴とする請求項1記載のシンボルタイミングリカバリ回路。

【請求項3】

前記タイミング再生部は、

前記第1の識別信号の時間遷移に応じて前記第1の誤差信号に正負符号を付与する第1の位相比較部と、

前記第2の識別信号の時間遷移に応じて前記第2の誤差信号に正負符号を付与する第2の位相比較部と、

前記第2の有限インパルス応答フィルタのタップ係数及び前記第1の無限インパルス応答フィルタのタップ係数を基に第1のゲイン及び第2のゲインを生成するコントロール回路と、

前記正負符号が付与された前記第1の誤差信号に対して前記第1のゲインを乗算する第1の乗算器と、

前記正負符号が付与された前記第2の誤差信号に対して前記第2のゲインを乗算する第2の乗算器と、

前記第1の乗算器の出力信号及び前記第2の乗算器の出力信号を基に前記第1の有限インパルス応答フィルタのタップ係数を演算する第3のタップ係数演算部とを有することを特徴とする請求項1又は2記載のシンボルタイミングリカバリ回路。

【請求項4】

前記コントロール回路は、前記前方干渉波が前記後方干渉波より大きいときには前記第1のゲインを前記第2のゲインより小さくし、前記後方干渉波が前記前方干渉波より大きいときには前記第2のゲインを前記第1のゲインより小さくすることを特徴とする請求項3記載のシンボルタイミングリカバリ回路。

【請求項5】

前記第1のゲイン及び前記第2のゲインの乗算値は、略一定値であることを特徴とする請求項4記載のシンボルタイミングリカバリ回路。

【請求項6】

前記第2の有限インパルス応答フィルタは、第1の同相有限インパルス応答フィルタ及び第1の直交有限インパルス応答フィルタを有し、

前記第1の無限インパルス応答フィルタは、第1の同相IIRフィルタ演算部及び第1の直交IIRフィルタ演算部を有し、

前記コントロール回路は、前記第1の同相有限インパルス応答フィルタ、前記第1の直交有限インパルス応答フィルタ、前記第1の同相IIRフィルタ演算部及び前記第1の直交IIRフィルタ演算部のタップ係数を基に前記第1のゲイン及び前記第2のゲインを生成することを特徴とする請求項3〜5のいずれか1項に記載のシンボルタイミングリカバリ回路。

【請求項7】

前記コントロール回路は、

前記第1の同相有限インパルス応答フィルタの同相タップ係数及び前記第1の直交有限インパルス応答フィルタの直交タップ係数のベクトルの大きさが、前記第1の同相IIRフィルタ演算部の同相タップ係数及び前記第1の直交IIRフィルタ演算部の直交タップ係数のベクトルの大きさより大きいときには、前記第1のゲインを前記第2のゲインより小さくし、

前記第1の同相IIRフィルタ演算部の同相タップ係数及び前記第1の直交IIRフィルタ演算部の直交タップ係数のベクトルの大きさが、前記第1の同相有限インパルス応答フィルタの同相タップ係数及び前記第1の直交有限インパルス応答フィルタの直交タップ係数のベクトルの大きさより大きいときには、前記第2のゲインを前記第1のゲインより小さくすることを特徴とする請求項6記載のシンボルタイミングリカバリ回路。

【請求項8】

前記コントロール回路は、前記第1の同相有限インパルス応答フィルタのセンタータップに1番目に近い第1の同相タップ係数及び第1の直交タップ係数のベクトルの大きさと、前記第1の同相IIRフィルタ演算部の第1の同相タップ係数及び第1の直交タップ係数のベクトルの大きさとを比較し、前記第1のゲイン及び前記第2のゲインを生成することを特徴とする請求項7記載のシンボルタイミングリカバリ回路。

【請求項9】

前記コントロール回路は、前記第1の同相有限インパルス応答フィルタのセンタータップに1番目に近い第1の同相タップ係数及び第1の直交タップ係数のベクトルの大きさと、前記第1の同相有限インパルス応答フィルタのセンタータップに2番目に近い第2の同相タップ係数及び第2の直交タップ係数のベクトルの大きさと、前記第1の同相IIRフィルタ演算部の第1の同相タップ係数及び第1の直交タップ係数のベクトルの大きさと、前記第1の同相IIRフィルタ演算部の第2の同相タップ係数及び第2の直交タップ係数のベクトルの大きさとを基に、前記第1のゲイン及び前記第2のゲインを生成することを特徴とする請求項7記載のシンボルタイミングリカバリ回路。

【請求項1】

第1の有限インパルス応答フィルタを用いて入力デジタル信号のゼロクロス点及び/又はデータ識別点の補間データを生成する補間器と、

第2の有限インパルス応答フィルタを用いて前記補間器により生成された補間データを基に前記入力デジタル信号から前方干渉波を除去し、その除去した信号、第1の識別信号及び第1の誤差信号を出力する前方等化器と、

第1の無限インパルス応答フィルタを用いて前記補間器により生成された補間データを基に前記入力デジタル信号から後方干渉波を除去し、その除去した信号、第2の識別信号及び第2の誤差信号を出力する後方等化器と、

前記補間器により生成された補間データと前記前方等化器及び前記後方等化器により前記前方干渉波及び前記後方干渉波が除去された信号とを基に前記第2の有限インパルス応答フィルタのタップ係数を演算する第1のタップ係数演算部と、

前記補間器により生成された補間データと前記前方等化器及び前記後方等化器により前記前方干渉波及び前記後方干渉波が除去された信号とを基に前記第1の無限インパルス応答フィルタのタップ係数を演算する第2のタップ係数演算部と、

前記第2の有限インパルス応答フィルタのタップ係数、前記第1の無限インパルス応答フィルタのタップ係数、前記第1の識別信号、前記第1の誤差信号、前記第2の識別信号及び前記第2の誤差信号を基に前記第1の有限インパルス応答フィルタのタップ係数を生成するタイミング再生部と

を有することを特徴とするシンボルタイミングリカバリ回路。

【請求項2】

前記第1の識別信号は、前記前方干渉波の除去前の信号であり、

前記第1の誤差信号は、前記前方干渉波の除去前の信号と前記前方干渉波の除去後の信号との差分の信号であり、

前記第2の識別信号は、前記後方干渉波の除去前の信号であり、

前記第2の誤差信号は、前記後方干渉波の除去前の信号と前記後方干渉波の除去後の信号との差分の信号であることを特徴とする請求項1記載のシンボルタイミングリカバリ回路。

【請求項3】

前記タイミング再生部は、

前記第1の識別信号の時間遷移に応じて前記第1の誤差信号に正負符号を付与する第1の位相比較部と、

前記第2の識別信号の時間遷移に応じて前記第2の誤差信号に正負符号を付与する第2の位相比較部と、

前記第2の有限インパルス応答フィルタのタップ係数及び前記第1の無限インパルス応答フィルタのタップ係数を基に第1のゲイン及び第2のゲインを生成するコントロール回路と、

前記正負符号が付与された前記第1の誤差信号に対して前記第1のゲインを乗算する第1の乗算器と、

前記正負符号が付与された前記第2の誤差信号に対して前記第2のゲインを乗算する第2の乗算器と、

前記第1の乗算器の出力信号及び前記第2の乗算器の出力信号を基に前記第1の有限インパルス応答フィルタのタップ係数を演算する第3のタップ係数演算部とを有することを特徴とする請求項1又は2記載のシンボルタイミングリカバリ回路。

【請求項4】

前記コントロール回路は、前記前方干渉波が前記後方干渉波より大きいときには前記第1のゲインを前記第2のゲインより小さくし、前記後方干渉波が前記前方干渉波より大きいときには前記第2のゲインを前記第1のゲインより小さくすることを特徴とする請求項3記載のシンボルタイミングリカバリ回路。

【請求項5】

前記第1のゲイン及び前記第2のゲインの乗算値は、略一定値であることを特徴とする請求項4記載のシンボルタイミングリカバリ回路。

【請求項6】

前記第2の有限インパルス応答フィルタは、第1の同相有限インパルス応答フィルタ及び第1の直交有限インパルス応答フィルタを有し、

前記第1の無限インパルス応答フィルタは、第1の同相IIRフィルタ演算部及び第1の直交IIRフィルタ演算部を有し、

前記コントロール回路は、前記第1の同相有限インパルス応答フィルタ、前記第1の直交有限インパルス応答フィルタ、前記第1の同相IIRフィルタ演算部及び前記第1の直交IIRフィルタ演算部のタップ係数を基に前記第1のゲイン及び前記第2のゲインを生成することを特徴とする請求項3〜5のいずれか1項に記載のシンボルタイミングリカバリ回路。

【請求項7】

前記コントロール回路は、

前記第1の同相有限インパルス応答フィルタの同相タップ係数及び前記第1の直交有限インパルス応答フィルタの直交タップ係数のベクトルの大きさが、前記第1の同相IIRフィルタ演算部の同相タップ係数及び前記第1の直交IIRフィルタ演算部の直交タップ係数のベクトルの大きさより大きいときには、前記第1のゲインを前記第2のゲインより小さくし、

前記第1の同相IIRフィルタ演算部の同相タップ係数及び前記第1の直交IIRフィルタ演算部の直交タップ係数のベクトルの大きさが、前記第1の同相有限インパルス応答フィルタの同相タップ係数及び前記第1の直交有限インパルス応答フィルタの直交タップ係数のベクトルの大きさより大きいときには、前記第2のゲインを前記第1のゲインより小さくすることを特徴とする請求項6記載のシンボルタイミングリカバリ回路。

【請求項8】

前記コントロール回路は、前記第1の同相有限インパルス応答フィルタのセンタータップに1番目に近い第1の同相タップ係数及び第1の直交タップ係数のベクトルの大きさと、前記第1の同相IIRフィルタ演算部の第1の同相タップ係数及び第1の直交タップ係数のベクトルの大きさとを比較し、前記第1のゲイン及び前記第2のゲインを生成することを特徴とする請求項7記載のシンボルタイミングリカバリ回路。

【請求項9】

前記コントロール回路は、前記第1の同相有限インパルス応答フィルタのセンタータップに1番目に近い第1の同相タップ係数及び第1の直交タップ係数のベクトルの大きさと、前記第1の同相有限インパルス応答フィルタのセンタータップに2番目に近い第2の同相タップ係数及び第2の直交タップ係数のベクトルの大きさと、前記第1の同相IIRフィルタ演算部の第1の同相タップ係数及び第1の直交タップ係数のベクトルの大きさと、前記第1の同相IIRフィルタ演算部の第2の同相タップ係数及び第2の直交タップ係数のベクトルの大きさとを基に、前記第1のゲイン及び前記第2のゲインを生成することを特徴とする請求項7記載のシンボルタイミングリカバリ回路。

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【公開番号】特開2013−38505(P2013−38505A)

【公開日】平成25年2月21日(2013.2.21)

【国際特許分類】

【出願番号】特願2011−171056(P2011−171056)

【出願日】平成23年8月4日(2011.8.4)

【出願人】(308014341)富士通セミコンダクター株式会社 (2,507)

【Fターム(参考)】

【公開日】平成25年2月21日(2013.2.21)

【国際特許分類】

【出願日】平成23年8月4日(2011.8.4)

【出願人】(308014341)富士通セミコンダクター株式会社 (2,507)

【Fターム(参考)】

[ Back to top ]