ジャンクションバリアショットキーダイオード

【課題】 リーク電流を低減することで、アクティブ領域の大きなSiCショットキーダイオードを高い良品率で提供する。

【解決手段】 SiCジャンクションバリアショットキーダイオードにおいて、ショットキー接合界面にかかる電界強度を0.1MV/cm以下になるようにトレンチの深さと間隔を設定することで実現する。その結果として、リーク電流が低減し、アクティブ領域の大きなSiCショットキーダイオードを高い良品率で提供できる。

【解決手段】 SiCジャンクションバリアショットキーダイオードにおいて、ショットキー接合界面にかかる電界強度を0.1MV/cm以下になるようにトレンチの深さと間隔を設定することで実現する。その結果として、リーク電流が低減し、アクティブ領域の大きなSiCショットキーダイオードを高い良品率で提供できる。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、炭化珪素基板を用いたジャンクションバリアショットキーダイオードに関するものである。

【背景技術】

【0002】

半導体パワー素子には高耐圧の他、低オン抵抗、低スイッチング損失が要求されるが、現在の主流である珪素(Si)パワー素子は、理論的な性能限界に近づいている。炭化珪素(SiC)はSiと比較して絶縁破壊電界強度が約1桁大きいため、耐圧を保持するドリフト層を約1/10に薄く、不純物濃度を約100倍高くすることで、素子抵抗を理論上3桁以上低減できる。また、Siに対してバンドギャップが約3倍大きいことから高温動作も可能であることから、Siを超える性能が期待できる。

【0003】

SiCを用いたパワー素子のなかでもユニポーラ型のショットキーバリアダイオード(SBD:Schottky Barrier Diode)は研究開発が進んでいる。現在主流のSiダイオードは、正孔と電子の2つのキャリアで動作するバイポーラ型であるため、スイッチング時に過剰少数キャリアの排出によるリカバリ電流が生じ、スイッチング損失が発生する。一方、ショットキーバリアダイオードは電子のみで動作するユニポーラ型であるため、理想的にはリカバリ電流は生じず、スイッチング損失の劇的な低減が可能である。しかし、Siで高耐圧のショットキーバリアダイオードを実現しようとすると、絶縁破壊電界強度が小さいためにドリフト層が厚く、不純物濃度が低くなる。その結果、素子抵抗が著しく増大するため、実用に適さない。一方、SiCは絶縁破壊強度が大きいため、高耐圧でも素子抵抗が小さく高性能なショットキーバリアダイオードが実現可能である。

【0004】

ショットキーバリアダイオードの整流作用は、金属の仕事関数と半導体の電子親和力の差によって生じるショットキー障壁によってなされている。逆方向漏れ電流は、熱励起されてショットキー障壁以上のエネルギーを持った電子が障壁を乗り越える熱放出電流、トンネル効果によって電子が障壁を透過する直接トンネル電流、半導体内のトラップ順位を介して電子が障壁を透過するトンネル電流、電子が半導体のバンドギャップを透過するバンド間トンネル電流がある。SiCを用いたパワー素子では金属/半導体界面(以下、ショットキー接合界面と呼ぶ)での絶縁破壊電界強度が2MV/cmを越えるため、逆方向漏れ電流は直接トンネル電流が支配的となり、ショットキー接合界面での電界強度に強く依存する。

【0005】

逆方向電圧印加時にショットキー接合界面にかかる電界強度を低減することで逆方向漏れ電流を抑制する構造として、ショットキー接合界面に複数の接合障壁を設ける接合障壁(Junction Barrier)ショットキーダイオード(以下、JBSダイオードと呼ぶ)と呼ばれる構造が提案されている。逆方向電圧印加時に接合障壁部から空乏層が伸び、ショットキー接合領域の下をピンチオフするため、ショットキー接合界面の電界を低減することができる。

【0006】

JBSダイオードが特許第3987957号(特許文献1)において開示されている。この構造を、図19に例示する。図19において、1はSiCからなるn+SiC基板を、2はn-ドリフト層を、3はショットキー接合領域を、4はp型半導体領域を、5はショットキーダイオードのアノード電極を、6はカソード電極を、それぞれ示している。そして、p型半導体領域の幅をLpn、p型半導体領域の間隔をLSBDとして示している。

【先行技術文献】

【特許文献】

【0007】

【特許文献1】特許第3987957号

【非特許文献】

【0008】

【非特許文献1】H.Fujiwara et al.:“Reverse Electrical Characteristics of 4H-SiC JBS Diodes Fabricated on Substrate with Low Threading Dislocation Density”, Materials Science Forum, Vol.679-680(2011), pp.694-697

【発明の概要】

【発明が解決しようとする課題】

【0009】

ショットキーバリアダイオードの逆方向特性はショットキー接合界面状態に非常に敏感であり、一般的にショットキーバリアダイオードはPNダイオードと比べて良品率は低くなる。エピタキシャル成長やイオン注入によってドリフト層の内部に接合障壁を形成するPNダイオードと比べ、ドリフト層の表面に金属膜を形成するショットキーバリアダイオードは、ドリフト層の欠陥や製造工程中のプロセス欠陥、異物の影響を受けやすいためである。ショットキー接合界面付近に異物や欠陥などが存在すると逆方向漏れ電流は急激に大きくなってしまい、所望の整流作用は得られなくなる。非特許文献1には、ショットキー接合界面にかかる電界強度を低減しているJBSダイオードにおいても、ドリフト層の欠陥やプロセス欠陥により逆方漏れ電流が増加することが開示されている。製造工程中のプロセス欠陥や異物は、製造工程において管理、低減が可能であるが、ドリフト層に含まれる欠陥は使用する基板のグレードやドリフト層のエピタキシャル成長条件によって決定される。

【0010】

欠陥の分布をランダムと仮定すると、良品率Y(ここでは、逆方向特性に異常なくチップを作製できる確率を示す。)はポアソン分布で考えられ、式1で示される。

【0011】

Y=exp(−DK×AS)・・・(式1)

(DK:逆方向特性に異常をきたすキラー欠陥密度、AS:ショットキー接合領域の面積)

図20に、式1で示した良品率Yとショットキー接合領域の面積ASの関係を、欠陥密度Dに対してプロットしたものを示す。例えば、ショットキー接合領域の面積ASが0.1cm2のとき、DK=1個/cm2の場合、良品率Yは90%程度となるが、DK=10個/cm2の場合Yは40%以下と大幅に減少することが分かる。このため、高い良品率のショットキーバリアダイオードを作製するためには、基板欠陥密度に応じた小面積の素子寸法を選択する必要があった。

【0012】

しかし、特に高耐圧用途では、大電流容量のチップが求められる。例えば600Vのショットキーバリアダイオードの場合、素子抵抗の観点から、通電時に電流が流れるアクティブ領域の電流密度は400A/cm2程度となることから、50A以上の素子電流を得るためには、0.1cm2程度以上のアクティブ面積が必要となる。 本発明の目的は、リーク電流を低減することで、アクティブ領域の大きなSiCショットキーダイオードを高い良品率で提供することである。

【課題を解決するための手段】

【0013】

本発明は、上記目的を達成する発明を複数含むものであるが、その代表的な発明は、SiCショットキーダイオードにおいて、ショットキー接合界面にかかる電界強度をJBSダイオードの10分の1以下としたものである。

【発明の効果】

【0014】

本発明によれば、リーク電流を低減することで、アクティブ領域の大きなSiCショットキーダイオードを高い良品率で提供することができる。

【図面の簡単な説明】

【0015】

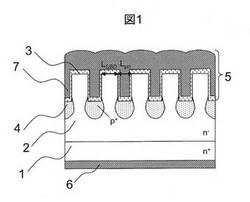

【図1】実施例1のショットキーダイオードのアクティブ領域の断面構造図である。

【図2】実施例1のショットキーダイオードの平面構造図である。

【図3】実施例1のショットキーダイオードの平面構造図である。

【図4】実施例1のショットキーダイオードの平面構造図である。

【図5】実施例1のショットキーダイオードの平面構造図である。

【図6】実施例1のショットキーダイオードの終端領域の断面構造図である。

【図7(a)】実施例1のショットキーダイオードの製造工程図である。

【図7(b)】実施例1のショットキーダイオードの製造工程図である。

【図7(c)】実施例1のショットキーダイオードの製造工程図である。

【図7(d)】実施例1のショットキーダイオードの製造工程図である。

【図8】実施例2のショットキーダイオードのアクティブ領域の断面構造図である。

【図9】実施例2のショットキーダイオードの終端領域の平面構造図である。

【図10(a)】実施例2のショットキーダイオードの製造工程図である。

【図10(b)】実施例2のショットキーダイオードの製造工程図である。

【図10(c)】実施例2のショットキーダイオードの製造工程図である。

【図10(d)】実施例2のショットキーダイオードの製造工程図である。

【図11】従来のJBSダイオードの逆方向電流電圧特性図である。

【図12】従来のJBSダイオードの良品率とショットキー接合領域の面積の関係を示す説明図である。

【図13】トレンチ深さとその間隔をパラメータとした、ショットキー接合界面での電界強度の計算結果である。

【図14】実施例2の逆方向電流電圧特性図である。

【図15】実施例2の良品率とショットキー接合領域の面積の関係を示す説明図である。

【図16】良品率80%、90%を実現する、ショットキー界面面積とエッチピット密度の関係を示す説明図である。

【図17】実施例3のショットキーダイオードのアクティブ領域の断面構造図である。

【図18】実施例4のショットキーダイオードのアクティブ領域の断面構造図である。

【図19】従来のJBSダイオードの断面構造図である。

【図20】良品率とショットキー接合面積の関係を示す説明図である。

【発明を実施するための形態】

【0016】

以下、発明の実施例に即して図面を用いてより具体的に説明する。なお、実施例を説明するための全図において、同一部材には原則として同一の符号を付し、その繰り返しの説明は省略する。特に異なる実施例間で機能が対応するものについては、形状、不純物濃度や結晶性等で違いがあっても同じ符号を付すこととする。また、断面構造図ではダイオードの主要部分のみを示しており、通常チップ周辺に形成されている電界集中緩和構造などを含めた周辺部分は省略されている。又、説明の便宜上、n型半導体基板を用いた例のみ説明するが、p型半導体基板を用いた場合であってもかまわない。この場合には、n型をp型と、p型をn型と読み替えればよい。

【実施例1】

【0017】

図1は実施例1のショットキーダイオードの通電時に電流が流れるアクティブ領域の断面構造図である。

【0018】

1はn+SiC基板を、2はSiCで構成されたn-ドリフト層を、3はショットキー接合領域を、4はp型半導体領域を、5はショットキーダイオードのアノード電極を、6はカソード電極を、7はドリフト層表面に形成されたトレンチを、それぞれ示す。そして、トレンチ7の開口幅をLpn、トレンチ7の間隔をLSBDとして示す。前記n-ドリフト層2と、前記トレンチ7内壁部に接するように配置された前記p型半導体領域4との界面でpn接合領域が形成される。ドリフト層2の表面からのp型半導体領域4の深さを、ショットキー接合界面にかかる電界強度が0.1MV/cm以下となるように設定した。このように設定することにより、ドリフト層2に多数の欠陥を有する場合においても、リーク電流を抑制することができ、従来のJBSダイオードよりも高い良品率が得られる。

【0019】

図2乃至5は実施例1のショットキーダイオードの平面構造図である。なお、図2のAAに沿った断面構造図が図1である。この平面図は当該半導体装置の主要部分の配置関係を示すものであり、全層の位置や寸法を正確に示すものではない。また、配置関係を見やすくするため、電極など一部の層は記載していない。図3乃至5は、図2の変形例である。p型半導体領域4のレイアウトは図2に示すようなライン状の配置を用いた。p型半導体領域のレイアウトは図3に示すような矩形のパターンにしても、図4に示すようにドットのパターンにしても、また図5に示すように六角形のパターンにしても同様の効果が得られる。また、8はトレンチ7を取り囲むように、形成された素子終端部のトレンチを示す。 図6は実施例1のショットキーダイオードの終端領域の断面構造図である。図2のBBに沿った断面構造図である。9はターミネーション領域を示す。本実施例ではターミネーション領域には、デバイス機能部分を帯上に囲むようにp領域を配置するJTE(Junction Termination Extension)構造を適用したが、リング状に複数本p型半導体領域を配置するFLR(Field Limiting Ring)構造でもよい。いずれの構造においても、素子終端部での電界集中を避けるため、素子終端部のトレンチ8は、素子中央部に形成されるトレンチ7よりも開口幅を広くする必要がある。以降は、素子終端部の説明は省略し、断面構造図では、ダイオードの主要部である素子中央部のみ示し、ターミネーション領域を含む素子終端部は省略する。

【0020】

図7の(a)から(d)は本実施例の製造工程図である。

【0021】

まず、n+SiC基板1上に低不純物濃度のn−ドリフト層2をエピタキシャル成長で形成したSiC基板を準備する。

【0022】

n+SiC基板1の不純物濃度は、1×1018〜1×1019cm−3の範囲が好適である。SiC基板の主面は(0001)面、(000−1)面、又は(11−20)面が好適である。本実施例では、ドリフト層2の不純物濃度は2×1018cm-3とし、基板厚さは356μmとし、基板の主面は(0001)面とした。

【0023】

n+SiC基板1上のn−ドリフト層2は、不純物濃度は基板と同一の導電型で1×1015〜4×1016cm−3程度の範囲で、厚さは3〜80μm程度の範囲で用いる。具体的には、耐圧600Vを実現するドリフト層2としては、不純物濃度が1×1016〜2×1016cm−3程度、厚さが4〜6μmが好適である。この場合、順方向通電時の抵抗は、基板抵抗とあわせて1mΩcm2程度に抑えることができ、300〜500A/cm2の電流密度での使用が可能である。また、耐圧3.3kVを実現するドリフト層2としては、不純物濃度が2×1015〜4×1015cm−3程度、厚さが20〜30μmの範囲が好適である。この場合、順方向通電時の抵抗は、基板抵抗とあわせて5〜10mΩcm2に抑えることができ、100〜150A/cm2程度の電流密度での使用が可能である。 次に、図7(a)に示すように、n-ドリフト層2の上にプラズマCVD(Chemical Vapor deposition)法によりシリコン酸化膜10を形成し、フォトリソグラフィー技術とドライエッチング技術を用いて、複数の開口部を形成する。

【0024】

そして、図7(b)に示すように、シリコン酸化膜10をマスクとしてドライエッチングし、n-ドリフト層2にトレンチ7を形成する。

【0025】

トレンチの加工には、プラズマ方式を採用したプラズマエッチング装置を用いた。加工に用いたガスは、ヘリウム(He)、六フッ化硫黄(SF6)の混合ガスで、0.25Paの圧力のもと2000Wのソースパワーと、600Wのバイアスパワーにて行った。装置の電極形状は直径200mmの円形であり、単位面積あたりのソースパワーは1.59W/cm2で、バイアスパワーは0.478W/cm2である。また、図7(b)中において、トレンチ7の深さ、トレンチ7の開口幅Lpn、トレンチ7の間隔LSBDは要求される性能によって異なってくる。

【0026】

次に、図7(c)に示すように、引き続き開口したシリコン酸化膜11をマスクとして、n-ドリフト層2表面に垂直方向にイオン注入することにより、トレンチ7の内壁部に接するように(トレンチ表面から内部に広がるように)p型半導体領域4を形成する。p型半導体領域4の不純物濃度は、1018〜1020cm−3程度で、接合深さは0.3〜2.0μm程度の範囲とする。p型のドーパントとしては、アルミ(Al)又はホウ素(B)を用いることが好ましい。ここでは、ドーパントとしてアルミを用い、総ドーズ量1.8×1014を35〜145keVの加速エネルギーで多段注入(複数条件での注入)を行い、表面付近の不純物濃度が9×1018程度、接合深さが0.55〜0.7μm程度となるようにp型半導体領域4を形成する。

【0027】

ここで、n-ドリフト層2表面に垂直な面からある角度を持たせることも有効である。具体的には、20度から30度の角度を持って斜めに注入した場合は、p型半導体領域4がトレンチ7の側面に沿って形成されるので、逆方向電圧印加時に第一のトレンチの側面の接合障壁部からも空乏層が伸び、ショットキー接合領域の下をピンチオフしやすいため、ショットキー接合界面の電界をより低減することができる。

【0028】

p型半導体領域4を形成した後は、p型半導体領域4の形成と同様の手順で、チップの外周部にp型不純物によるターミネーション領域9を形成した(図6参照)。そして、注入不純物の活性化アニールを1700℃で60秒行った。

【0029】

最後に、図7(d)に示すように、n+SiC基板1の裏面にオーミック接触するカソード電極6、及び表面にショットキーダイオードのアノード電極5を形成した。

【0030】

本実施例では、マスク材料にシリコン酸化膜を適用したが、例えば窒化シリコン膜やレジスト材料でもよく、イオン注入時のマスクとなる材料であれば、その他の材料でも適用できる。

【0031】

なお、本実施例では、注入不純物の活性化アニールを実施した後、すぐに裏面および表面の電極形成を行ったが、注入不純物の活性化アニールを実施した後に酸化処理を行い、n−ドリフト層2の表面に入ったダメージ層を除去する犠牲酸化工程を行ってもよい。犠牲酸化工程の有無にかかわらず、n−ドリフト層2の表面にプラズマCVDでシリコン酸化膜などの表面保護膜を形成し、n−ドリフト層2の表面を保護しても良い。この場合、表面保護膜を形成した後、ショットキー接合領域のみ開口するように加工する。

【実施例2】

【0032】

図8は実施例2のショットキーダイオードのアクティブ領域の断面構造図である。

【0033】

実施例1との相違点は、実施例1のトレンチ7が方形の溝であったのに対して、本実施例のトレンチ7は逆台形の溝で、順テーパな側壁面を備えている点である。トレンチ7のドリフト層2表面における開口幅よりもトレンチ7の底面の幅が小さく、トレンチ7の側面がドリフト層2表面に平行な面となす角度をテーパー角度11として示す。

【0034】

本実施例においても、ドリフト層2の表面からのp型半導体領域4の深さを、ショットキー接合界面にかかる電界強度が0.1MV/cm以下となるように設定した。このように設定することにより、ドリフト層2に多数の欠陥を有する場合においても、リーク電流を抑制することができ、従来のJBSダイオードよりも高い良品率が得られる。更に、トレンチ側面にもp型半導体領域4が形成されるので、逆方向電圧印加時にトレンチ7の側面の接合障壁部からも空乏層が伸び、ショットキー接合領域の下を十分にピンチオフし、トレンチ側面にp型半導体領域4が形成されないもの(図1参照)と比較してショットキー接合界面の電界をより低減することができる。

【0035】

図8のは図1の場合と同様で、図2のAAに沿った断面構造図である。なお、この平面図は当該半導体装置の主要部分の配置関係を示すものであり、全層の位置や寸法を正確に示すものではない。また、配置関係を見やすくするため、電極など一部の層は記載していない。図3乃至5は、図2の変形例である。p型半導体領域4のレイアウトは図2に示すようなライン状の配置を用いた。p型半導体領域のレイアウトは図3に示すような矩形のパターンにしても、図4に示すようにドットのパターンにしても、また図5に示すように六角形のパターンにしても同様の効果が得られる。

【0036】

図9は実施例2のショットキーダイオードの終端領域の断面構造図である。図2のBBに沿った断面構造図である。9はターミネーション領域を示す。本実施例ではターミネーション領域には、デバイス機能部分を帯上に囲むようにp領域を配置するJTE(Junction Termination Extension)構造を適用したが、リング状に複数本p型半導体領域を配置するFLR(Field Limiting Ring)構造でもよい。いずれの構造においても、素子終端部での電界集中を避けるため、素子終端部のトレンチ8は、素子中央部に形成されるトレンチ7よりも開口幅を広くする必要がある。以降は、素子終端部の説明は省略し、断面構造図では、ダイオードの主要部である素子中央部のみ示し、ターミネーション領域を含む素子終端部は省略する。

【0037】

図10(a)から(d)は本実施例の製造工程図である。

【0038】

まず、n+SiC基板1上に低不純物濃度のn−ドリフト層2をエピタキシャル成長で形成したSiC基板を準備する。構成は実施例1と同様である。次に、図10(a)に示すように、n-ドリフト層2の上にプラズマCVD(Chemical Vapor deposition)法によりシリコン酸化膜10を形成し、フォトリソグラフィー技術とドライエッチング技術を用いて、複数の開口部を形成する。

【0039】

そして、図10(b)に示すように、シリコン酸化膜10をマスクとしてドライエッチングし、n-ドリフト層2にトレンチ7を形成する。

【0040】

トレンチの加工には、プラズマ方式を採用したプラズマエッチング装置を用いた。加工に用いたガスは、ヘリウム(He)、六フッ化硫黄(SF6)の混合ガスで、0.25Paの圧力のもと2000Wのソースパワーと、300Wのバイアスパワーにて行った。装置の電極形状は直径200mmの円形であり、単位面積あたりのソースパワーは1.59W/cm2で、バイアスパワーは0.239W/cm2である。前記条件で加工することで、トレンチ7の側面がドリフト層2表面に平行な面となす角度のテーパー角度11を86度とした。

【0041】

また、トレンチ7の側面がドリフト層2表面に平行な面となす角度のテーパー角度11は所望の特性に応じて任意に設定できる。例えば、トレンチの加工にマイクロ波ECR(Electron Cyclotron Resonance)プラズマ方式を採用したプラズマエッチング装置を用い、加工に用いるガスは、アルゴン(Ar)、三フッ化メタン(CHF3)、六フッ化硫黄(SF6)の混合ガスとし、1.0Paの圧力のもと60Wのバイアスパワーにて行うと、トレンチ7の側面がドリフト層2表面となす角度のテーパー角度11は80度となった。装置の電極形状は直径200mmの円形であり、単位面積あたりのバイアスパワーは0.048W/cm2である。

【0042】

そして、図10(b)中において、トレンチ7の深さは1μmとした。トレンチ7の開口幅Lpn、トレンチ7の間隔LSBDは要求される性能によって異なってくる。本実施例ではトレンチ7の開口幅Lpnを1μm、トレンチ7の間隔LSBDを1μm、1.1μm、1.2μmとした。

【0043】

次に、図10(c)に示すように、引き続き開口したシリコン酸化膜11をマスクとして、n-ドリフト層2表面に垂直方向にイオン注入し、トレンチ7の内壁部に接するようにp型半導体領域4を形成する。p型半導体領域4の不純物濃度は、1018〜1020cm−3程度で、接合深さは0.3〜2.0μm程度の範囲で用いられる。p型のドーパントとしては、通常アルミ(Al)やホウ素(B)が用いられる。ここでは、ドーパントとしてアルミを用い、総ドーズ量1.8×1014を35〜145keVの加速エネルギーで多段注入を行い、表面付近の不純物濃度が9×1018程度、接合深さが0.55〜0.7μm程度となるようにp型半導体領域4を形成した。

【0044】

本実施例ではトレンチ7のドリフト層2表面における開口幅よりもトレンチ7の底面の幅が小さく、トレンチ7の側面がドリフト層2表面となす角度をテーパー角度11が存在するため、n-ドリフト層2表面に垂直方向に一回イオン注入するのみで、トレンチ側面にもp型半導体領域4が容易に形成可能である。

【0045】

p型半導体領域4を形成した後は、p型半導体領域4の形成と同様の手順で、チップの外周部にp型不純物によるターミネーション領域9を形成した(図6参照)。そして、通常行われる注入不純物の活性化アニールを1700℃で60秒行った。

【0046】

最後に、図10(d)に示すように、n+SiC基板1の裏面にオーミック接触するカソード電極6、及び表面にショットキーダイオードのアノード電極5を形成した。

【0047】

本実施例では、マスク材料にシリコン酸化膜を適用したが、例えば窒化シリコン膜やレジスト材料でもよく、イオン注入時のマスクとなる材料であれば、その他の材料でも適用できる。

【0048】

なお、本実施例では、注入不純物の活性化アニールを実施した後、すぐに裏面および表面の電極形成を行ったが、注入不純物の活性化アニールを実施した後に酸化処理を行い、n−ドリフト層2の表面に入ったダメージ層を除去する犠牲酸化工程を行ってもよい。犠牲酸化工程の有無にかかわらず、n−ドリフト層2の表面にプラズマCVDでシリコン酸化膜などの表面保護膜を形成し、n−ドリフト層2の表面を保護しても良い。この場合、表面保護膜を形成した後、ショットキー電極を形成する領域のみ開口するように加工する。次に、効果を、事前に実施した図19に示す従来のJBSダイオードの実験結果と比較して説明する。まず、図19に示す従来のJBSダイオードの実験結果を説明する。従来のJBSダイオードのドリフト層2の不純物濃度は2×1018cm-3とし、基板厚さは359μmとし、基板の主面は(0001)面である。また、p型半導体領域の幅Lpnを1μm、p型半導体領域の間隔LSBDを1μm、1.2μmとした。ショットキー接合領域の面積は、約0.06cm2と約0.01cm2であり、評価したダイオードはそれぞれ33個と48個である。耐圧600V以上(逆方向に600V印加したときの漏れ電流が1mA/cm2未満)を良品とする。

【0049】

図11に、ショットキー接合領域の面積が約0.06cm2の場合の逆方向電流電圧特性を示す。ショットキー障壁は形成されているが、600V以下で逆方向漏れ電流が1mA/cm2以上となり、不良品となっているものは42%であった。良品の600Vでの漏れ電流のレベルは1×10−5A/cm2から1×10−4A/cm2である。 また、ショットキー接合領域の面積が約0.01cm2の場合については、ショットキー障壁は形成されているが、600V以下で逆方向漏れ電流が1mA/cm2以上となり、不良品となっているものは12%であった。図12は、図20のSiCショットキーダイオードの逆方向特性良品率のショットキー接合面積依存性に、従来のJBSダイオードの実験結果を追加して示している。図12から、現状使用しているドリフト層には、ショットキーダイオードの逆方向特性に異常をきたすキラー欠陥密度DKが10個/cm2程度存在することを示している。

【0050】

続いて、実施例2の実験結果を説明する。図13にトレンチ7の間隔LSBDと、トレンチ7の深さをパラメータとして、ショットキー接合界面での電界強度を計算した結果を示す。図13から、本発明は従来のJBSダイオードと比較して、ショットキー接合界面での電界強度を10分の1以下にすることができ、トレンチ7の深さが1μmあるいは2μmでトレンチ7の間隔LSBDが1μmのとき、0.1MV/cm以下となる。

【0051】

実施例2では、ドリフト層2の不純物濃度は2×1018cm-3とし、基板厚さは356μmとし、基板の主面は(0001)面とした。また、トレンチ7の深さを1μm、トレンチ7の開口幅Lpnを1μm、トレンチ7の間隔LSBDを1μm、1.1μm、1.2μmとした。

【0052】

ショットキー接合領域の面積は、約0.06cm2であり、評価したダイオードは34個である。耐圧600V以上(逆方向に600V印加したときの漏れ電流が1mA/cm2未満)を良品とする。

【0053】

図14に、ショットキー接合領域の面積が約0.06cm2の場合の逆方向電流電圧特性を示す。ショットキー障壁は形成されているが、600V以下で逆方向漏れ電流が1mA/cm2以上となり、不良品となっているものは9%であった。良品の600Vでの漏れ電流のレベルは1×10−7から1×10−8である。従来のJBSダイオードでは、ショットキー障壁は形成されているが、600V以下で逆方向漏れ電流が1mA/cm2以上となり、不良品となっているものは30%で、良品の600Vでの漏れ電流のレベルは1×10−5から1×10−4であったので、大幅に逆方向漏れ電流が低減でき、ショットキー障壁は形成されているが、600V以下で逆方向漏れ電流が1mA/cm2以上となる不良品率も低減できた。

【0054】

図15には図12のSiCショットキーダイオードの逆方向特性良品率のショットキー接合面積依存性に、実施例2の実験結果を追加して示す。図15から、実施例2においては、現状使用しているドリフト層には、ショットキーダイオードの逆方向特性に異常をきたすキラー欠陥密度DKが1.5個/cm2程度存在することを示している。従来のJBSダイオードではショットキーダイオードの逆方向特性に異常をきたすキラー欠陥密度DKが10個/cm2程度存在するという結果だったので、実施例2ではショットキーダイオードの逆方向特性に異常をきたすキラー欠陥密度を5分の1以下に減らせた。ただし、キラー欠陥そのものがドリフト層表面から減少したのではなく、本発明を用いることでキラー欠陥に鈍感な構造となり、キラー欠陥の影響を受け受け辛くなったということである。

【0055】

式1を変換すると、以下の式2ように、欠陥密度と面積を表すことができる。

【0056】

DK×AS=−ln(Y)・・・(式2)

このため、80%以上の良品率を得るためには、以下の式3を満たす必要がある。

【0057】

DK×AS≦0.223・・・(式3)

同様に、90%以上の良品率を得るためには、以下の式4を満たす必要がある。

【0058】

DK×AS≦0.105・・・(式4)

を満たす必要がある。産業上の実用化を鑑みると、良品率80%は必須であるため、式3を満たすことが必須である。図15から、現状のキラー欠陥密度が1.5個/cm2程度であることから、現状のドリフト層上で以下の式5を満たす構造のときは80%以上の良品率で、式6を満たすときは90%以上の良品率で、ショットキーダイオードが得られる。

【0059】

AS≦0.149・・・(式5)

AS≦0.07・・・(式6)

このため、通電時に電流が流れるアクティブ領域の面積が0.3cm2のダイオードの場合、(p型半導体領域の面積)/(ショットキー接合領域の面積)=1程度の割合、例えばトレンチ7の開口幅Lpn=1μm、トレンチ7の間隔LSBD=1μmの縞状パターンでJBS構造を形成することで、式5を満たすことができる。また、(p型半導体領域の面積)/(ショットキー接合領域の面積)=3.5程度の割合、例えばトレンチ7の開口幅Lpn=3.5μm、トレンチ7の間隔LSBD=1μmの縞状パターンでJBS構造を形成することで、式6を満たすことができる。

【0060】

通電時に電流が流れるアクティブ領域の面積が0.5cm2のダイオードの場合は、(p型半導体領域の面積)/(ショットキー接合領域の面積)=2.5程度の割合、例えばトレンチ7の開口幅Lpn=2.5μm、トレンチ7の間隔LSBD=1μmの縞状パターンでJBS構造を形成することで式5を満たすことができる。また、(p型半導体領域の面積)/(ショットキー接合領域の面積)=6程度の割合、例えばトレンチ7の開口幅Lpn=6μm、トレンチ7の間隔LSBD=1μmの縞状パターンでJBS構造を形成することで式6を満たすことができる。

【0061】

しかし、実際のドリフト層中には、上述よりも多数の転位欠陥、積層欠陥を含んでいる。これらの欠陥を検出する方法として、溶融KOH法によるエッチピットの形成が一般的に知られている。溶融KOH法によって形成されるエッチピットの密度DEPは、一般的に10000から30000個/cm2程度である。このため、全ての欠陥がショットキーダイオードの逆方向特性に異常をきたすわけではなく、逆方向リークを引き起こす転位欠陥が複数存在する時に逆方向特性に異常をきたすと考えられている。ここから、エッチピットが6667から20000個存在する場合に1個のキラー欠陥が存在すると換算することができる。

【0062】

DK=DEP/6667 〜 DEP/20000・・・式7

このため、式3は式8へ、式4は式9へ変換することができる。

【0063】

DEP×AS≦1487・・・式8

DEP×AS≦700・・・式9

すなわち、DEP×ASを1487以下となる割合のJBS構造にすることで良品率80%以上を、700以下にすることで良品率90%以上を得ることができる。この関係を図16に示す。

【0064】

本実施例では、代表的なエッチピット密度DEPとアクティブ領域面積を用いて説明したが、式8および式9を満たす範囲であれば、ショットキー接合面積のアクティブ領域面積に対する割合を任意の値に設定できる。また、トレンチ7の深さやトレンチ7の間隔LSBDは、逆方向電圧保持時のショットキー接合界面での電界強度が0.1MV/cm以下となる場合であれば、任意の値に設定できる。

【実施例3】

【0065】

図17は実施例3のショットキーバリアダイオードのアクティブ領域の断面構造図である。ドリフト層の欠陥や製造工程中のプロセス欠陥、異物の影響を受けやすいショットキー接合領域の面積を、通電時に電流が流れるアクティブ領域の3分の1以下とすることで、更に良品率を高めることができる。本実施例の製造工程は、上記実施例1の製造工程と同様である。

【実施例4】

【0066】

図18は実施例4のショットキーバリアダイオードのアクティブ領域の断面構造図である。ドリフト層の欠陥や製造工程中のプロセス欠陥、異物の影響を受けやすいショットキー接合領域の面積を、通電時に電流が流れるアクティブ領域の3分の1以下とすることで、更に良品率を高めることができる。本実施例の製造工程は、上記実施例2の製造工程と同様である。

【0067】

本実施例では、ドリフト層2の不純物濃度は2×1018cm-3とし、基板厚さは356μmとし、基板の主面は(0001)面とした。また、トレンチ7の深さを1μm、トレンチ7の開口幅Lpnを1μmと3μm、トレンチ7の間隔LSBDを1μm、1.1μm、1.2μmとした。ショットキー接合領域の面積は、トレンチ7の開口幅Lpnが1μmの場合は約0.01cm2であり、トレンチ7の開口幅Lpnが3μmの場合は約0.005cm2であり、評価したダイオードはそれぞれ39個と21個である。耐圧600V以上(逆方向に600V印加したときの漏れ電流が1mA/cm2未満)を良品とすると、トレンチ7の開口幅Lpnが1μmの場合は90%、トレンチ7の開口幅Lpnが3μmの場合は100%となった。トレンチ7の開口幅Lpnが3μmの場合は評価数が少ないが、トレンチ7の開口幅Lpnを広くし、ショットキー接合領域の面積を通電時に電流が流れるアクティブ領域の面積に対して小さくすることで、良品率が高くなった。

【0068】

以上、本発明について実施例1から4を用いて説明した。本願ではこれまで本発明をダイオード単一素子に適用した場合についての実施例を記載してきたが、例えば、スイッチング素子である接合FETやMOSFETとの混載素子のダイオード部分に適用しても同様の効果が得られる。

【符号の説明】

【0069】

1:n+SiC基板、2:n-ドリフト層、3:ショットキー接合領域、4:p型半導体領域、5:ショットキーダイオードのアノード電極、6:カソード電極、7:トレンチ、8:素子終端部のトレンチ、9:ターミネーション領域、10:シリコン酸化膜、11:トレンチ側面のテーパー角度

【技術分野】

【0001】

本発明は、炭化珪素基板を用いたジャンクションバリアショットキーダイオードに関するものである。

【背景技術】

【0002】

半導体パワー素子には高耐圧の他、低オン抵抗、低スイッチング損失が要求されるが、現在の主流である珪素(Si)パワー素子は、理論的な性能限界に近づいている。炭化珪素(SiC)はSiと比較して絶縁破壊電界強度が約1桁大きいため、耐圧を保持するドリフト層を約1/10に薄く、不純物濃度を約100倍高くすることで、素子抵抗を理論上3桁以上低減できる。また、Siに対してバンドギャップが約3倍大きいことから高温動作も可能であることから、Siを超える性能が期待できる。

【0003】

SiCを用いたパワー素子のなかでもユニポーラ型のショットキーバリアダイオード(SBD:Schottky Barrier Diode)は研究開発が進んでいる。現在主流のSiダイオードは、正孔と電子の2つのキャリアで動作するバイポーラ型であるため、スイッチング時に過剰少数キャリアの排出によるリカバリ電流が生じ、スイッチング損失が発生する。一方、ショットキーバリアダイオードは電子のみで動作するユニポーラ型であるため、理想的にはリカバリ電流は生じず、スイッチング損失の劇的な低減が可能である。しかし、Siで高耐圧のショットキーバリアダイオードを実現しようとすると、絶縁破壊電界強度が小さいためにドリフト層が厚く、不純物濃度が低くなる。その結果、素子抵抗が著しく増大するため、実用に適さない。一方、SiCは絶縁破壊強度が大きいため、高耐圧でも素子抵抗が小さく高性能なショットキーバリアダイオードが実現可能である。

【0004】

ショットキーバリアダイオードの整流作用は、金属の仕事関数と半導体の電子親和力の差によって生じるショットキー障壁によってなされている。逆方向漏れ電流は、熱励起されてショットキー障壁以上のエネルギーを持った電子が障壁を乗り越える熱放出電流、トンネル効果によって電子が障壁を透過する直接トンネル電流、半導体内のトラップ順位を介して電子が障壁を透過するトンネル電流、電子が半導体のバンドギャップを透過するバンド間トンネル電流がある。SiCを用いたパワー素子では金属/半導体界面(以下、ショットキー接合界面と呼ぶ)での絶縁破壊電界強度が2MV/cmを越えるため、逆方向漏れ電流は直接トンネル電流が支配的となり、ショットキー接合界面での電界強度に強く依存する。

【0005】

逆方向電圧印加時にショットキー接合界面にかかる電界強度を低減することで逆方向漏れ電流を抑制する構造として、ショットキー接合界面に複数の接合障壁を設ける接合障壁(Junction Barrier)ショットキーダイオード(以下、JBSダイオードと呼ぶ)と呼ばれる構造が提案されている。逆方向電圧印加時に接合障壁部から空乏層が伸び、ショットキー接合領域の下をピンチオフするため、ショットキー接合界面の電界を低減することができる。

【0006】

JBSダイオードが特許第3987957号(特許文献1)において開示されている。この構造を、図19に例示する。図19において、1はSiCからなるn+SiC基板を、2はn-ドリフト層を、3はショットキー接合領域を、4はp型半導体領域を、5はショットキーダイオードのアノード電極を、6はカソード電極を、それぞれ示している。そして、p型半導体領域の幅をLpn、p型半導体領域の間隔をLSBDとして示している。

【先行技術文献】

【特許文献】

【0007】

【特許文献1】特許第3987957号

【非特許文献】

【0008】

【非特許文献1】H.Fujiwara et al.:“Reverse Electrical Characteristics of 4H-SiC JBS Diodes Fabricated on Substrate with Low Threading Dislocation Density”, Materials Science Forum, Vol.679-680(2011), pp.694-697

【発明の概要】

【発明が解決しようとする課題】

【0009】

ショットキーバリアダイオードの逆方向特性はショットキー接合界面状態に非常に敏感であり、一般的にショットキーバリアダイオードはPNダイオードと比べて良品率は低くなる。エピタキシャル成長やイオン注入によってドリフト層の内部に接合障壁を形成するPNダイオードと比べ、ドリフト層の表面に金属膜を形成するショットキーバリアダイオードは、ドリフト層の欠陥や製造工程中のプロセス欠陥、異物の影響を受けやすいためである。ショットキー接合界面付近に異物や欠陥などが存在すると逆方向漏れ電流は急激に大きくなってしまい、所望の整流作用は得られなくなる。非特許文献1には、ショットキー接合界面にかかる電界強度を低減しているJBSダイオードにおいても、ドリフト層の欠陥やプロセス欠陥により逆方漏れ電流が増加することが開示されている。製造工程中のプロセス欠陥や異物は、製造工程において管理、低減が可能であるが、ドリフト層に含まれる欠陥は使用する基板のグレードやドリフト層のエピタキシャル成長条件によって決定される。

【0010】

欠陥の分布をランダムと仮定すると、良品率Y(ここでは、逆方向特性に異常なくチップを作製できる確率を示す。)はポアソン分布で考えられ、式1で示される。

【0011】

Y=exp(−DK×AS)・・・(式1)

(DK:逆方向特性に異常をきたすキラー欠陥密度、AS:ショットキー接合領域の面積)

図20に、式1で示した良品率Yとショットキー接合領域の面積ASの関係を、欠陥密度Dに対してプロットしたものを示す。例えば、ショットキー接合領域の面積ASが0.1cm2のとき、DK=1個/cm2の場合、良品率Yは90%程度となるが、DK=10個/cm2の場合Yは40%以下と大幅に減少することが分かる。このため、高い良品率のショットキーバリアダイオードを作製するためには、基板欠陥密度に応じた小面積の素子寸法を選択する必要があった。

【0012】

しかし、特に高耐圧用途では、大電流容量のチップが求められる。例えば600Vのショットキーバリアダイオードの場合、素子抵抗の観点から、通電時に電流が流れるアクティブ領域の電流密度は400A/cm2程度となることから、50A以上の素子電流を得るためには、0.1cm2程度以上のアクティブ面積が必要となる。 本発明の目的は、リーク電流を低減することで、アクティブ領域の大きなSiCショットキーダイオードを高い良品率で提供することである。

【課題を解決するための手段】

【0013】

本発明は、上記目的を達成する発明を複数含むものであるが、その代表的な発明は、SiCショットキーダイオードにおいて、ショットキー接合界面にかかる電界強度をJBSダイオードの10分の1以下としたものである。

【発明の効果】

【0014】

本発明によれば、リーク電流を低減することで、アクティブ領域の大きなSiCショットキーダイオードを高い良品率で提供することができる。

【図面の簡単な説明】

【0015】

【図1】実施例1のショットキーダイオードのアクティブ領域の断面構造図である。

【図2】実施例1のショットキーダイオードの平面構造図である。

【図3】実施例1のショットキーダイオードの平面構造図である。

【図4】実施例1のショットキーダイオードの平面構造図である。

【図5】実施例1のショットキーダイオードの平面構造図である。

【図6】実施例1のショットキーダイオードの終端領域の断面構造図である。

【図7(a)】実施例1のショットキーダイオードの製造工程図である。

【図7(b)】実施例1のショットキーダイオードの製造工程図である。

【図7(c)】実施例1のショットキーダイオードの製造工程図である。

【図7(d)】実施例1のショットキーダイオードの製造工程図である。

【図8】実施例2のショットキーダイオードのアクティブ領域の断面構造図である。

【図9】実施例2のショットキーダイオードの終端領域の平面構造図である。

【図10(a)】実施例2のショットキーダイオードの製造工程図である。

【図10(b)】実施例2のショットキーダイオードの製造工程図である。

【図10(c)】実施例2のショットキーダイオードの製造工程図である。

【図10(d)】実施例2のショットキーダイオードの製造工程図である。

【図11】従来のJBSダイオードの逆方向電流電圧特性図である。

【図12】従来のJBSダイオードの良品率とショットキー接合領域の面積の関係を示す説明図である。

【図13】トレンチ深さとその間隔をパラメータとした、ショットキー接合界面での電界強度の計算結果である。

【図14】実施例2の逆方向電流電圧特性図である。

【図15】実施例2の良品率とショットキー接合領域の面積の関係を示す説明図である。

【図16】良品率80%、90%を実現する、ショットキー界面面積とエッチピット密度の関係を示す説明図である。

【図17】実施例3のショットキーダイオードのアクティブ領域の断面構造図である。

【図18】実施例4のショットキーダイオードのアクティブ領域の断面構造図である。

【図19】従来のJBSダイオードの断面構造図である。

【図20】良品率とショットキー接合面積の関係を示す説明図である。

【発明を実施するための形態】

【0016】

以下、発明の実施例に即して図面を用いてより具体的に説明する。なお、実施例を説明するための全図において、同一部材には原則として同一の符号を付し、その繰り返しの説明は省略する。特に異なる実施例間で機能が対応するものについては、形状、不純物濃度や結晶性等で違いがあっても同じ符号を付すこととする。また、断面構造図ではダイオードの主要部分のみを示しており、通常チップ周辺に形成されている電界集中緩和構造などを含めた周辺部分は省略されている。又、説明の便宜上、n型半導体基板を用いた例のみ説明するが、p型半導体基板を用いた場合であってもかまわない。この場合には、n型をp型と、p型をn型と読み替えればよい。

【実施例1】

【0017】

図1は実施例1のショットキーダイオードの通電時に電流が流れるアクティブ領域の断面構造図である。

【0018】

1はn+SiC基板を、2はSiCで構成されたn-ドリフト層を、3はショットキー接合領域を、4はp型半導体領域を、5はショットキーダイオードのアノード電極を、6はカソード電極を、7はドリフト層表面に形成されたトレンチを、それぞれ示す。そして、トレンチ7の開口幅をLpn、トレンチ7の間隔をLSBDとして示す。前記n-ドリフト層2と、前記トレンチ7内壁部に接するように配置された前記p型半導体領域4との界面でpn接合領域が形成される。ドリフト層2の表面からのp型半導体領域4の深さを、ショットキー接合界面にかかる電界強度が0.1MV/cm以下となるように設定した。このように設定することにより、ドリフト層2に多数の欠陥を有する場合においても、リーク電流を抑制することができ、従来のJBSダイオードよりも高い良品率が得られる。

【0019】

図2乃至5は実施例1のショットキーダイオードの平面構造図である。なお、図2のAAに沿った断面構造図が図1である。この平面図は当該半導体装置の主要部分の配置関係を示すものであり、全層の位置や寸法を正確に示すものではない。また、配置関係を見やすくするため、電極など一部の層は記載していない。図3乃至5は、図2の変形例である。p型半導体領域4のレイアウトは図2に示すようなライン状の配置を用いた。p型半導体領域のレイアウトは図3に示すような矩形のパターンにしても、図4に示すようにドットのパターンにしても、また図5に示すように六角形のパターンにしても同様の効果が得られる。また、8はトレンチ7を取り囲むように、形成された素子終端部のトレンチを示す。 図6は実施例1のショットキーダイオードの終端領域の断面構造図である。図2のBBに沿った断面構造図である。9はターミネーション領域を示す。本実施例ではターミネーション領域には、デバイス機能部分を帯上に囲むようにp領域を配置するJTE(Junction Termination Extension)構造を適用したが、リング状に複数本p型半導体領域を配置するFLR(Field Limiting Ring)構造でもよい。いずれの構造においても、素子終端部での電界集中を避けるため、素子終端部のトレンチ8は、素子中央部に形成されるトレンチ7よりも開口幅を広くする必要がある。以降は、素子終端部の説明は省略し、断面構造図では、ダイオードの主要部である素子中央部のみ示し、ターミネーション領域を含む素子終端部は省略する。

【0020】

図7の(a)から(d)は本実施例の製造工程図である。

【0021】

まず、n+SiC基板1上に低不純物濃度のn−ドリフト層2をエピタキシャル成長で形成したSiC基板を準備する。

【0022】

n+SiC基板1の不純物濃度は、1×1018〜1×1019cm−3の範囲が好適である。SiC基板の主面は(0001)面、(000−1)面、又は(11−20)面が好適である。本実施例では、ドリフト層2の不純物濃度は2×1018cm-3とし、基板厚さは356μmとし、基板の主面は(0001)面とした。

【0023】

n+SiC基板1上のn−ドリフト層2は、不純物濃度は基板と同一の導電型で1×1015〜4×1016cm−3程度の範囲で、厚さは3〜80μm程度の範囲で用いる。具体的には、耐圧600Vを実現するドリフト層2としては、不純物濃度が1×1016〜2×1016cm−3程度、厚さが4〜6μmが好適である。この場合、順方向通電時の抵抗は、基板抵抗とあわせて1mΩcm2程度に抑えることができ、300〜500A/cm2の電流密度での使用が可能である。また、耐圧3.3kVを実現するドリフト層2としては、不純物濃度が2×1015〜4×1015cm−3程度、厚さが20〜30μmの範囲が好適である。この場合、順方向通電時の抵抗は、基板抵抗とあわせて5〜10mΩcm2に抑えることができ、100〜150A/cm2程度の電流密度での使用が可能である。 次に、図7(a)に示すように、n-ドリフト層2の上にプラズマCVD(Chemical Vapor deposition)法によりシリコン酸化膜10を形成し、フォトリソグラフィー技術とドライエッチング技術を用いて、複数の開口部を形成する。

【0024】

そして、図7(b)に示すように、シリコン酸化膜10をマスクとしてドライエッチングし、n-ドリフト層2にトレンチ7を形成する。

【0025】

トレンチの加工には、プラズマ方式を採用したプラズマエッチング装置を用いた。加工に用いたガスは、ヘリウム(He)、六フッ化硫黄(SF6)の混合ガスで、0.25Paの圧力のもと2000Wのソースパワーと、600Wのバイアスパワーにて行った。装置の電極形状は直径200mmの円形であり、単位面積あたりのソースパワーは1.59W/cm2で、バイアスパワーは0.478W/cm2である。また、図7(b)中において、トレンチ7の深さ、トレンチ7の開口幅Lpn、トレンチ7の間隔LSBDは要求される性能によって異なってくる。

【0026】

次に、図7(c)に示すように、引き続き開口したシリコン酸化膜11をマスクとして、n-ドリフト層2表面に垂直方向にイオン注入することにより、トレンチ7の内壁部に接するように(トレンチ表面から内部に広がるように)p型半導体領域4を形成する。p型半導体領域4の不純物濃度は、1018〜1020cm−3程度で、接合深さは0.3〜2.0μm程度の範囲とする。p型のドーパントとしては、アルミ(Al)又はホウ素(B)を用いることが好ましい。ここでは、ドーパントとしてアルミを用い、総ドーズ量1.8×1014を35〜145keVの加速エネルギーで多段注入(複数条件での注入)を行い、表面付近の不純物濃度が9×1018程度、接合深さが0.55〜0.7μm程度となるようにp型半導体領域4を形成する。

【0027】

ここで、n-ドリフト層2表面に垂直な面からある角度を持たせることも有効である。具体的には、20度から30度の角度を持って斜めに注入した場合は、p型半導体領域4がトレンチ7の側面に沿って形成されるので、逆方向電圧印加時に第一のトレンチの側面の接合障壁部からも空乏層が伸び、ショットキー接合領域の下をピンチオフしやすいため、ショットキー接合界面の電界をより低減することができる。

【0028】

p型半導体領域4を形成した後は、p型半導体領域4の形成と同様の手順で、チップの外周部にp型不純物によるターミネーション領域9を形成した(図6参照)。そして、注入不純物の活性化アニールを1700℃で60秒行った。

【0029】

最後に、図7(d)に示すように、n+SiC基板1の裏面にオーミック接触するカソード電極6、及び表面にショットキーダイオードのアノード電極5を形成した。

【0030】

本実施例では、マスク材料にシリコン酸化膜を適用したが、例えば窒化シリコン膜やレジスト材料でもよく、イオン注入時のマスクとなる材料であれば、その他の材料でも適用できる。

【0031】

なお、本実施例では、注入不純物の活性化アニールを実施した後、すぐに裏面および表面の電極形成を行ったが、注入不純物の活性化アニールを実施した後に酸化処理を行い、n−ドリフト層2の表面に入ったダメージ層を除去する犠牲酸化工程を行ってもよい。犠牲酸化工程の有無にかかわらず、n−ドリフト層2の表面にプラズマCVDでシリコン酸化膜などの表面保護膜を形成し、n−ドリフト層2の表面を保護しても良い。この場合、表面保護膜を形成した後、ショットキー接合領域のみ開口するように加工する。

【実施例2】

【0032】

図8は実施例2のショットキーダイオードのアクティブ領域の断面構造図である。

【0033】

実施例1との相違点は、実施例1のトレンチ7が方形の溝であったのに対して、本実施例のトレンチ7は逆台形の溝で、順テーパな側壁面を備えている点である。トレンチ7のドリフト層2表面における開口幅よりもトレンチ7の底面の幅が小さく、トレンチ7の側面がドリフト層2表面に平行な面となす角度をテーパー角度11として示す。

【0034】

本実施例においても、ドリフト層2の表面からのp型半導体領域4の深さを、ショットキー接合界面にかかる電界強度が0.1MV/cm以下となるように設定した。このように設定することにより、ドリフト層2に多数の欠陥を有する場合においても、リーク電流を抑制することができ、従来のJBSダイオードよりも高い良品率が得られる。更に、トレンチ側面にもp型半導体領域4が形成されるので、逆方向電圧印加時にトレンチ7の側面の接合障壁部からも空乏層が伸び、ショットキー接合領域の下を十分にピンチオフし、トレンチ側面にp型半導体領域4が形成されないもの(図1参照)と比較してショットキー接合界面の電界をより低減することができる。

【0035】

図8のは図1の場合と同様で、図2のAAに沿った断面構造図である。なお、この平面図は当該半導体装置の主要部分の配置関係を示すものであり、全層の位置や寸法を正確に示すものではない。また、配置関係を見やすくするため、電極など一部の層は記載していない。図3乃至5は、図2の変形例である。p型半導体領域4のレイアウトは図2に示すようなライン状の配置を用いた。p型半導体領域のレイアウトは図3に示すような矩形のパターンにしても、図4に示すようにドットのパターンにしても、また図5に示すように六角形のパターンにしても同様の効果が得られる。

【0036】

図9は実施例2のショットキーダイオードの終端領域の断面構造図である。図2のBBに沿った断面構造図である。9はターミネーション領域を示す。本実施例ではターミネーション領域には、デバイス機能部分を帯上に囲むようにp領域を配置するJTE(Junction Termination Extension)構造を適用したが、リング状に複数本p型半導体領域を配置するFLR(Field Limiting Ring)構造でもよい。いずれの構造においても、素子終端部での電界集中を避けるため、素子終端部のトレンチ8は、素子中央部に形成されるトレンチ7よりも開口幅を広くする必要がある。以降は、素子終端部の説明は省略し、断面構造図では、ダイオードの主要部である素子中央部のみ示し、ターミネーション領域を含む素子終端部は省略する。

【0037】

図10(a)から(d)は本実施例の製造工程図である。

【0038】

まず、n+SiC基板1上に低不純物濃度のn−ドリフト層2をエピタキシャル成長で形成したSiC基板を準備する。構成は実施例1と同様である。次に、図10(a)に示すように、n-ドリフト層2の上にプラズマCVD(Chemical Vapor deposition)法によりシリコン酸化膜10を形成し、フォトリソグラフィー技術とドライエッチング技術を用いて、複数の開口部を形成する。

【0039】

そして、図10(b)に示すように、シリコン酸化膜10をマスクとしてドライエッチングし、n-ドリフト層2にトレンチ7を形成する。

【0040】

トレンチの加工には、プラズマ方式を採用したプラズマエッチング装置を用いた。加工に用いたガスは、ヘリウム(He)、六フッ化硫黄(SF6)の混合ガスで、0.25Paの圧力のもと2000Wのソースパワーと、300Wのバイアスパワーにて行った。装置の電極形状は直径200mmの円形であり、単位面積あたりのソースパワーは1.59W/cm2で、バイアスパワーは0.239W/cm2である。前記条件で加工することで、トレンチ7の側面がドリフト層2表面に平行な面となす角度のテーパー角度11を86度とした。

【0041】

また、トレンチ7の側面がドリフト層2表面に平行な面となす角度のテーパー角度11は所望の特性に応じて任意に設定できる。例えば、トレンチの加工にマイクロ波ECR(Electron Cyclotron Resonance)プラズマ方式を採用したプラズマエッチング装置を用い、加工に用いるガスは、アルゴン(Ar)、三フッ化メタン(CHF3)、六フッ化硫黄(SF6)の混合ガスとし、1.0Paの圧力のもと60Wのバイアスパワーにて行うと、トレンチ7の側面がドリフト層2表面となす角度のテーパー角度11は80度となった。装置の電極形状は直径200mmの円形であり、単位面積あたりのバイアスパワーは0.048W/cm2である。

【0042】

そして、図10(b)中において、トレンチ7の深さは1μmとした。トレンチ7の開口幅Lpn、トレンチ7の間隔LSBDは要求される性能によって異なってくる。本実施例ではトレンチ7の開口幅Lpnを1μm、トレンチ7の間隔LSBDを1μm、1.1μm、1.2μmとした。

【0043】

次に、図10(c)に示すように、引き続き開口したシリコン酸化膜11をマスクとして、n-ドリフト層2表面に垂直方向にイオン注入し、トレンチ7の内壁部に接するようにp型半導体領域4を形成する。p型半導体領域4の不純物濃度は、1018〜1020cm−3程度で、接合深さは0.3〜2.0μm程度の範囲で用いられる。p型のドーパントとしては、通常アルミ(Al)やホウ素(B)が用いられる。ここでは、ドーパントとしてアルミを用い、総ドーズ量1.8×1014を35〜145keVの加速エネルギーで多段注入を行い、表面付近の不純物濃度が9×1018程度、接合深さが0.55〜0.7μm程度となるようにp型半導体領域4を形成した。

【0044】

本実施例ではトレンチ7のドリフト層2表面における開口幅よりもトレンチ7の底面の幅が小さく、トレンチ7の側面がドリフト層2表面となす角度をテーパー角度11が存在するため、n-ドリフト層2表面に垂直方向に一回イオン注入するのみで、トレンチ側面にもp型半導体領域4が容易に形成可能である。

【0045】

p型半導体領域4を形成した後は、p型半導体領域4の形成と同様の手順で、チップの外周部にp型不純物によるターミネーション領域9を形成した(図6参照)。そして、通常行われる注入不純物の活性化アニールを1700℃で60秒行った。

【0046】

最後に、図10(d)に示すように、n+SiC基板1の裏面にオーミック接触するカソード電極6、及び表面にショットキーダイオードのアノード電極5を形成した。

【0047】

本実施例では、マスク材料にシリコン酸化膜を適用したが、例えば窒化シリコン膜やレジスト材料でもよく、イオン注入時のマスクとなる材料であれば、その他の材料でも適用できる。

【0048】

なお、本実施例では、注入不純物の活性化アニールを実施した後、すぐに裏面および表面の電極形成を行ったが、注入不純物の活性化アニールを実施した後に酸化処理を行い、n−ドリフト層2の表面に入ったダメージ層を除去する犠牲酸化工程を行ってもよい。犠牲酸化工程の有無にかかわらず、n−ドリフト層2の表面にプラズマCVDでシリコン酸化膜などの表面保護膜を形成し、n−ドリフト層2の表面を保護しても良い。この場合、表面保護膜を形成した後、ショットキー電極を形成する領域のみ開口するように加工する。次に、効果を、事前に実施した図19に示す従来のJBSダイオードの実験結果と比較して説明する。まず、図19に示す従来のJBSダイオードの実験結果を説明する。従来のJBSダイオードのドリフト層2の不純物濃度は2×1018cm-3とし、基板厚さは359μmとし、基板の主面は(0001)面である。また、p型半導体領域の幅Lpnを1μm、p型半導体領域の間隔LSBDを1μm、1.2μmとした。ショットキー接合領域の面積は、約0.06cm2と約0.01cm2であり、評価したダイオードはそれぞれ33個と48個である。耐圧600V以上(逆方向に600V印加したときの漏れ電流が1mA/cm2未満)を良品とする。

【0049】

図11に、ショットキー接合領域の面積が約0.06cm2の場合の逆方向電流電圧特性を示す。ショットキー障壁は形成されているが、600V以下で逆方向漏れ電流が1mA/cm2以上となり、不良品となっているものは42%であった。良品の600Vでの漏れ電流のレベルは1×10−5A/cm2から1×10−4A/cm2である。 また、ショットキー接合領域の面積が約0.01cm2の場合については、ショットキー障壁は形成されているが、600V以下で逆方向漏れ電流が1mA/cm2以上となり、不良品となっているものは12%であった。図12は、図20のSiCショットキーダイオードの逆方向特性良品率のショットキー接合面積依存性に、従来のJBSダイオードの実験結果を追加して示している。図12から、現状使用しているドリフト層には、ショットキーダイオードの逆方向特性に異常をきたすキラー欠陥密度DKが10個/cm2程度存在することを示している。

【0050】

続いて、実施例2の実験結果を説明する。図13にトレンチ7の間隔LSBDと、トレンチ7の深さをパラメータとして、ショットキー接合界面での電界強度を計算した結果を示す。図13から、本発明は従来のJBSダイオードと比較して、ショットキー接合界面での電界強度を10分の1以下にすることができ、トレンチ7の深さが1μmあるいは2μmでトレンチ7の間隔LSBDが1μmのとき、0.1MV/cm以下となる。

【0051】

実施例2では、ドリフト層2の不純物濃度は2×1018cm-3とし、基板厚さは356μmとし、基板の主面は(0001)面とした。また、トレンチ7の深さを1μm、トレンチ7の開口幅Lpnを1μm、トレンチ7の間隔LSBDを1μm、1.1μm、1.2μmとした。

【0052】

ショットキー接合領域の面積は、約0.06cm2であり、評価したダイオードは34個である。耐圧600V以上(逆方向に600V印加したときの漏れ電流が1mA/cm2未満)を良品とする。

【0053】

図14に、ショットキー接合領域の面積が約0.06cm2の場合の逆方向電流電圧特性を示す。ショットキー障壁は形成されているが、600V以下で逆方向漏れ電流が1mA/cm2以上となり、不良品となっているものは9%であった。良品の600Vでの漏れ電流のレベルは1×10−7から1×10−8である。従来のJBSダイオードでは、ショットキー障壁は形成されているが、600V以下で逆方向漏れ電流が1mA/cm2以上となり、不良品となっているものは30%で、良品の600Vでの漏れ電流のレベルは1×10−5から1×10−4であったので、大幅に逆方向漏れ電流が低減でき、ショットキー障壁は形成されているが、600V以下で逆方向漏れ電流が1mA/cm2以上となる不良品率も低減できた。

【0054】

図15には図12のSiCショットキーダイオードの逆方向特性良品率のショットキー接合面積依存性に、実施例2の実験結果を追加して示す。図15から、実施例2においては、現状使用しているドリフト層には、ショットキーダイオードの逆方向特性に異常をきたすキラー欠陥密度DKが1.5個/cm2程度存在することを示している。従来のJBSダイオードではショットキーダイオードの逆方向特性に異常をきたすキラー欠陥密度DKが10個/cm2程度存在するという結果だったので、実施例2ではショットキーダイオードの逆方向特性に異常をきたすキラー欠陥密度を5分の1以下に減らせた。ただし、キラー欠陥そのものがドリフト層表面から減少したのではなく、本発明を用いることでキラー欠陥に鈍感な構造となり、キラー欠陥の影響を受け受け辛くなったということである。

【0055】

式1を変換すると、以下の式2ように、欠陥密度と面積を表すことができる。

【0056】

DK×AS=−ln(Y)・・・(式2)

このため、80%以上の良品率を得るためには、以下の式3を満たす必要がある。

【0057】

DK×AS≦0.223・・・(式3)

同様に、90%以上の良品率を得るためには、以下の式4を満たす必要がある。

【0058】

DK×AS≦0.105・・・(式4)

を満たす必要がある。産業上の実用化を鑑みると、良品率80%は必須であるため、式3を満たすことが必須である。図15から、現状のキラー欠陥密度が1.5個/cm2程度であることから、現状のドリフト層上で以下の式5を満たす構造のときは80%以上の良品率で、式6を満たすときは90%以上の良品率で、ショットキーダイオードが得られる。

【0059】

AS≦0.149・・・(式5)

AS≦0.07・・・(式6)

このため、通電時に電流が流れるアクティブ領域の面積が0.3cm2のダイオードの場合、(p型半導体領域の面積)/(ショットキー接合領域の面積)=1程度の割合、例えばトレンチ7の開口幅Lpn=1μm、トレンチ7の間隔LSBD=1μmの縞状パターンでJBS構造を形成することで、式5を満たすことができる。また、(p型半導体領域の面積)/(ショットキー接合領域の面積)=3.5程度の割合、例えばトレンチ7の開口幅Lpn=3.5μm、トレンチ7の間隔LSBD=1μmの縞状パターンでJBS構造を形成することで、式6を満たすことができる。

【0060】

通電時に電流が流れるアクティブ領域の面積が0.5cm2のダイオードの場合は、(p型半導体領域の面積)/(ショットキー接合領域の面積)=2.5程度の割合、例えばトレンチ7の開口幅Lpn=2.5μm、トレンチ7の間隔LSBD=1μmの縞状パターンでJBS構造を形成することで式5を満たすことができる。また、(p型半導体領域の面積)/(ショットキー接合領域の面積)=6程度の割合、例えばトレンチ7の開口幅Lpn=6μm、トレンチ7の間隔LSBD=1μmの縞状パターンでJBS構造を形成することで式6を満たすことができる。

【0061】

しかし、実際のドリフト層中には、上述よりも多数の転位欠陥、積層欠陥を含んでいる。これらの欠陥を検出する方法として、溶融KOH法によるエッチピットの形成が一般的に知られている。溶融KOH法によって形成されるエッチピットの密度DEPは、一般的に10000から30000個/cm2程度である。このため、全ての欠陥がショットキーダイオードの逆方向特性に異常をきたすわけではなく、逆方向リークを引き起こす転位欠陥が複数存在する時に逆方向特性に異常をきたすと考えられている。ここから、エッチピットが6667から20000個存在する場合に1個のキラー欠陥が存在すると換算することができる。

【0062】

DK=DEP/6667 〜 DEP/20000・・・式7

このため、式3は式8へ、式4は式9へ変換することができる。

【0063】

DEP×AS≦1487・・・式8

DEP×AS≦700・・・式9

すなわち、DEP×ASを1487以下となる割合のJBS構造にすることで良品率80%以上を、700以下にすることで良品率90%以上を得ることができる。この関係を図16に示す。

【0064】

本実施例では、代表的なエッチピット密度DEPとアクティブ領域面積を用いて説明したが、式8および式9を満たす範囲であれば、ショットキー接合面積のアクティブ領域面積に対する割合を任意の値に設定できる。また、トレンチ7の深さやトレンチ7の間隔LSBDは、逆方向電圧保持時のショットキー接合界面での電界強度が0.1MV/cm以下となる場合であれば、任意の値に設定できる。

【実施例3】

【0065】

図17は実施例3のショットキーバリアダイオードのアクティブ領域の断面構造図である。ドリフト層の欠陥や製造工程中のプロセス欠陥、異物の影響を受けやすいショットキー接合領域の面積を、通電時に電流が流れるアクティブ領域の3分の1以下とすることで、更に良品率を高めることができる。本実施例の製造工程は、上記実施例1の製造工程と同様である。

【実施例4】

【0066】

図18は実施例4のショットキーバリアダイオードのアクティブ領域の断面構造図である。ドリフト層の欠陥や製造工程中のプロセス欠陥、異物の影響を受けやすいショットキー接合領域の面積を、通電時に電流が流れるアクティブ領域の3分の1以下とすることで、更に良品率を高めることができる。本実施例の製造工程は、上記実施例2の製造工程と同様である。

【0067】

本実施例では、ドリフト層2の不純物濃度は2×1018cm-3とし、基板厚さは356μmとし、基板の主面は(0001)面とした。また、トレンチ7の深さを1μm、トレンチ7の開口幅Lpnを1μmと3μm、トレンチ7の間隔LSBDを1μm、1.1μm、1.2μmとした。ショットキー接合領域の面積は、トレンチ7の開口幅Lpnが1μmの場合は約0.01cm2であり、トレンチ7の開口幅Lpnが3μmの場合は約0.005cm2であり、評価したダイオードはそれぞれ39個と21個である。耐圧600V以上(逆方向に600V印加したときの漏れ電流が1mA/cm2未満)を良品とすると、トレンチ7の開口幅Lpnが1μmの場合は90%、トレンチ7の開口幅Lpnが3μmの場合は100%となった。トレンチ7の開口幅Lpnが3μmの場合は評価数が少ないが、トレンチ7の開口幅Lpnを広くし、ショットキー接合領域の面積を通電時に電流が流れるアクティブ領域の面積に対して小さくすることで、良品率が高くなった。

【0068】

以上、本発明について実施例1から4を用いて説明した。本願ではこれまで本発明をダイオード単一素子に適用した場合についての実施例を記載してきたが、例えば、スイッチング素子である接合FETやMOSFETとの混載素子のダイオード部分に適用しても同様の効果が得られる。

【符号の説明】

【0069】

1:n+SiC基板、2:n-ドリフト層、3:ショットキー接合領域、4:p型半導体領域、5:ショットキーダイオードのアノード電極、6:カソード電極、7:トレンチ、8:素子終端部のトレンチ、9:ターミネーション領域、10:シリコン酸化膜、11:トレンチ側面のテーパー角度

【特許請求の範囲】

【請求項1】

第1導電型の炭化珪素基板上に、複数のトレンチを有する炭化珪素層と、前記複数のトレンチの間で前記炭化珪素層との間でショットキー接合された電極とを備え、

前記炭化珪素層は、

前記炭化珪素基板より不純物濃度が低い第1導電型の第1領域と、

前記第1導電型の半導体領域上に形成された第2導電型の第2領域とを有し、

前記電極は前記第1領域上に配置され、

前記複数のトレンチは、前記第2領域上に配置され、逆方向電圧保持時のショットキー接合界面での電界強度が0.1MV/cm以下となる深さと間隔を備えていることを特徴とするジャンクションバリアショットキーダイオード。

【請求項2】

請求項1において、

前記第1領域はドリフト層であることを特徴とするジャンクションバリアショットキーダイオード。

【請求項3】

請求項2において、

前記第2領域が前記トレンチの側壁の一部となっていることを特徴とするジャンクションバリアショットキーダイオード。

【請求項4】

請求項2において、

前記トレンチは順テーパな側壁を備えていることを特徴とするジャンクションバリアショットキーダイオード。

【請求項5】

請求項2において、

前記複数のトレンチは、アクティブ領域にある第1トレンチと、アクティブ領域を囲む終端領域にある第2トレンチとを有し、

前記第2トレンチは、前記1トレンチよりもドリフト層表面における開口幅が広いことを特徴とするジャンクションバリアショットキーダイオード。

【請求項6】

請求項2において、

前記ドリフト層の表面の欠陥密度をDEP個/cm2とし、ショットキー接合領域の面積をAScm2とすると、DEP×AS≦1487を満たすことを特徴とするジャンクションバリアショットキーダイオード。

【請求項7】

請求項2において、

前記ドリフト層の表面の欠陥密度をDEP個/cm2とし、ショットキー接合領域の面積をAScm2とすると、DEP×AS≦700を満たすことを特徴とするジャンクションバリアショットキーダイオード。

【請求項8】

請求項6または7において、

前記欠陥密度DEPは、溶融KOHエッチングによって形成したエッチピットの個数で定義されることを特徴とするジャンクションバリアショットキーダイオード。

【請求項9】

請求項6または7において、

前記ショットキー接合領域の面積AScm2が、0.1cm2以上であることを特徴とするジャンクションバリアショットキーダイオード。

【請求項10】

請求項6において、

前記ショットキー接合領域の面積AScm2が、通電時に電流が流れるアクティブ領域の3分の1以下であることを特徴とするジャンクションバリアショットキーダイオード。

【請求項11】

請求項6または7において、

前記ショットキー接合領域の面積AScm2が、通電時に電流が流れるアクティブ領域の3分の1以下であることを特徴とするジャンクションバリアショットキーダイオード。

【請求項12】

請求項2において、

前記第2領域のパターンは、ライン状、矩形状、ドット状、または六角形状であることを特徴とするジャンクションバリアショットキーダイオード。

【請求項13】

n型の炭化珪素基板上に、複数の縞状トレンチを有する炭化珪素層と、前記複数のトレンチの間で前記炭化珪素層との間でショットキー接合されたアノード電極とを備え、

前記炭化珪素層は、

前記炭化珪素基板より不純物濃度が低いn型ドリフト領域と、

前記第1導電型の半導体領域上に形成されたp型領域とを有し、

前記アノード電極は前記第1領域上に配置され、

前記複数のトレンチは前記第2領域上に配置され、前記ショットキー接合領域の面積AScm2が0.1cm2以上、かつ前記ショットキー接合領域の面積AScm2が通電時に電流が流れるアクティブ領域の3分の1以下で、前記ドリフト層の表面の欠陥密度DEP個/cm2との関係がDEP×AS≦1487を満たし、逆方向電圧保持時のショットキー接合界面での電界強度が0.1MV/cm以下となる深さと間隔を備えていることを特徴とするジャンクションバリアショットキーダイオード。

【請求項14】

n型の炭化珪素基板上に、複数の縞状トレンチを有する炭化珪素層と、前記複数のトレンチの間で前記炭化珪素層との間でショットキー接合されたアノード電極とを備え、

前記炭化珪素層は、

前記炭化珪素基板より不純物濃度が低いn型ドリフト領域と、

前記第1導電型の半導体領域上に形成されたp型領域とを有し、

前記アノード電極は前記第1領域上に配置され、

前記複数のトレンチは前記第2領域上に配置され、前記ショットキー接合領域の面積AScm2が0.1cm2以上、かつ前記ショットキー接合領域の面積AScm2が通電時に電流が流れるアクティブ領域の3分の1以下で、前記ドリフト層の表面の欠陥密度DEP個/cm2との関係がDEP×AS≦700を満たし、逆方向電圧保持時のショットキー接合界面での電界強度が0.1MV/cm以下となる深さと間隔を備えていることを特徴とするジャンクションバリアショットキーダイオード。

【請求項15】

第1導電型の炭化珪素基板上に、複数のトレンチを有する炭化珪素層と、前記複数のトレンチの間で前記炭化珪素層との間でショットキー接合された電極とを備え、

前記炭化珪素層は、

前記炭化珪素基板より不純物濃度が低い第1導電型の第1領域と、

前記第1導電型の半導体領域上に形成された第2導電型の第2領域とを有し、

前記第1領域はドリフト層を構成し、

前記電極は前記第1領域上に配置され、

前記複数のトレンチは、前記第2領域上に配置され、逆方向電圧保持時のショットキー接合界面での電界強度が0.1MV/cm以下となる深さと間隔を備えたジャンクションバリアショットキーダイオードの製造方法において、

前記ドリフト層の表面に開口部のある酸化膜のマスクを形成し、

前記マスクで前記トレンチを形成した後、前記マスクで前記トレンチの内壁へ、第2導電型の不純物を基板表面に対して垂直にイオン注入して前記第2領域を形成することを特徴とするジャンクションバリアショットキーダイオードの製造方法。

【請求項1】

第1導電型の炭化珪素基板上に、複数のトレンチを有する炭化珪素層と、前記複数のトレンチの間で前記炭化珪素層との間でショットキー接合された電極とを備え、

前記炭化珪素層は、

前記炭化珪素基板より不純物濃度が低い第1導電型の第1領域と、

前記第1導電型の半導体領域上に形成された第2導電型の第2領域とを有し、

前記電極は前記第1領域上に配置され、

前記複数のトレンチは、前記第2領域上に配置され、逆方向電圧保持時のショットキー接合界面での電界強度が0.1MV/cm以下となる深さと間隔を備えていることを特徴とするジャンクションバリアショットキーダイオード。

【請求項2】

請求項1において、

前記第1領域はドリフト層であることを特徴とするジャンクションバリアショットキーダイオード。

【請求項3】

請求項2において、

前記第2領域が前記トレンチの側壁の一部となっていることを特徴とするジャンクションバリアショットキーダイオード。

【請求項4】

請求項2において、

前記トレンチは順テーパな側壁を備えていることを特徴とするジャンクションバリアショットキーダイオード。

【請求項5】

請求項2において、

前記複数のトレンチは、アクティブ領域にある第1トレンチと、アクティブ領域を囲む終端領域にある第2トレンチとを有し、

前記第2トレンチは、前記1トレンチよりもドリフト層表面における開口幅が広いことを特徴とするジャンクションバリアショットキーダイオード。

【請求項6】

請求項2において、

前記ドリフト層の表面の欠陥密度をDEP個/cm2とし、ショットキー接合領域の面積をAScm2とすると、DEP×AS≦1487を満たすことを特徴とするジャンクションバリアショットキーダイオード。

【請求項7】

請求項2において、

前記ドリフト層の表面の欠陥密度をDEP個/cm2とし、ショットキー接合領域の面積をAScm2とすると、DEP×AS≦700を満たすことを特徴とするジャンクションバリアショットキーダイオード。

【請求項8】

請求項6または7において、

前記欠陥密度DEPは、溶融KOHエッチングによって形成したエッチピットの個数で定義されることを特徴とするジャンクションバリアショットキーダイオード。

【請求項9】

請求項6または7において、

前記ショットキー接合領域の面積AScm2が、0.1cm2以上であることを特徴とするジャンクションバリアショットキーダイオード。

【請求項10】

請求項6において、

前記ショットキー接合領域の面積AScm2が、通電時に電流が流れるアクティブ領域の3分の1以下であることを特徴とするジャンクションバリアショットキーダイオード。

【請求項11】

請求項6または7において、

前記ショットキー接合領域の面積AScm2が、通電時に電流が流れるアクティブ領域の3分の1以下であることを特徴とするジャンクションバリアショットキーダイオード。

【請求項12】

請求項2において、

前記第2領域のパターンは、ライン状、矩形状、ドット状、または六角形状であることを特徴とするジャンクションバリアショットキーダイオード。

【請求項13】

n型の炭化珪素基板上に、複数の縞状トレンチを有する炭化珪素層と、前記複数のトレンチの間で前記炭化珪素層との間でショットキー接合されたアノード電極とを備え、

前記炭化珪素層は、

前記炭化珪素基板より不純物濃度が低いn型ドリフト領域と、

前記第1導電型の半導体領域上に形成されたp型領域とを有し、

前記アノード電極は前記第1領域上に配置され、

前記複数のトレンチは前記第2領域上に配置され、前記ショットキー接合領域の面積AScm2が0.1cm2以上、かつ前記ショットキー接合領域の面積AScm2が通電時に電流が流れるアクティブ領域の3分の1以下で、前記ドリフト層の表面の欠陥密度DEP個/cm2との関係がDEP×AS≦1487を満たし、逆方向電圧保持時のショットキー接合界面での電界強度が0.1MV/cm以下となる深さと間隔を備えていることを特徴とするジャンクションバリアショットキーダイオード。

【請求項14】

n型の炭化珪素基板上に、複数の縞状トレンチを有する炭化珪素層と、前記複数のトレンチの間で前記炭化珪素層との間でショットキー接合されたアノード電極とを備え、

前記炭化珪素層は、

前記炭化珪素基板より不純物濃度が低いn型ドリフト領域と、

前記第1導電型の半導体領域上に形成されたp型領域とを有し、

前記アノード電極は前記第1領域上に配置され、

前記複数のトレンチは前記第2領域上に配置され、前記ショットキー接合領域の面積AScm2が0.1cm2以上、かつ前記ショットキー接合領域の面積AScm2が通電時に電流が流れるアクティブ領域の3分の1以下で、前記ドリフト層の表面の欠陥密度DEP個/cm2との関係がDEP×AS≦700を満たし、逆方向電圧保持時のショットキー接合界面での電界強度が0.1MV/cm以下となる深さと間隔を備えていることを特徴とするジャンクションバリアショットキーダイオード。

【請求項15】

第1導電型の炭化珪素基板上に、複数のトレンチを有する炭化珪素層と、前記複数のトレンチの間で前記炭化珪素層との間でショットキー接合された電極とを備え、

前記炭化珪素層は、

前記炭化珪素基板より不純物濃度が低い第1導電型の第1領域と、

前記第1導電型の半導体領域上に形成された第2導電型の第2領域とを有し、

前記第1領域はドリフト層を構成し、

前記電極は前記第1領域上に配置され、

前記複数のトレンチは、前記第2領域上に配置され、逆方向電圧保持時のショットキー接合界面での電界強度が0.1MV/cm以下となる深さと間隔を備えたジャンクションバリアショットキーダイオードの製造方法において、

前記ドリフト層の表面に開口部のある酸化膜のマスクを形成し、

前記マスクで前記トレンチを形成した後、前記マスクで前記トレンチの内壁へ、第2導電型の不純物を基板表面に対して垂直にイオン注入して前記第2領域を形成することを特徴とするジャンクションバリアショットキーダイオードの製造方法。

【図2】

【図3】

【図4】

【図5】

【図6】

【図7(a)】

【図7(b)】

【図7(c)】

【図9】

【図10(a)】

【図10(b)】

【図10(c)】

【図11】

【図12】

【図13】

【図14】

【図15】

【図16】

【図20】

【図1】

【図7(d)】

【図8】

【図10(d)】

【図17】

【図18】

【図19】

【図3】

【図4】

【図5】

【図6】

【図7(a)】

【図7(b)】

【図7(c)】

【図9】

【図10(a)】

【図10(b)】

【図10(c)】

【図11】

【図12】

【図13】

【図14】

【図15】

【図16】

【図20】

【図1】

【図7(d)】

【図8】

【図10(d)】

【図17】

【図18】

【図19】

【公開番号】特開2013−115394(P2013−115394A)

【公開日】平成25年6月10日(2013.6.10)

【国際特許分類】

【出願番号】特願2011−263200(P2011−263200)

【出願日】平成23年12月1日(2011.12.1)

【出願人】(000005108)株式会社日立製作所 (27,607)

【Fターム(参考)】

【公開日】平成25年6月10日(2013.6.10)

【国際特許分類】

【出願日】平成23年12月1日(2011.12.1)

【出願人】(000005108)株式会社日立製作所 (27,607)

【Fターム(参考)】

[ Back to top ]