スイッチトキャパシター回路、フィルター回路、物理量測定装置及び電子機器

【課題】所望の信号伝達関数でより一層の出力雑音成分を低減できるスイッチトキャパシター回路、フィルター回路、物理量測定装置及び電子機器等を提供する。

【解決手段】スイッチと、複数のサンプリング容量と、積分容量とを含んで構成されるスイッチトキャパシター積分回路10は、電荷充電期間T1の入力信号に対応した電荷をサンプリング容量の少なくとも1つに充電する。スイッチトキャパシター積分回路10は、電荷転送期間T2において、該電荷を積分容量に転送することで、該電荷に対応した信号を伝搬遅延させる。スイッチトキャパシター積分回路10は、例えばスイッチにより複数のサンプリング容量の接続を切り換えることにより、電荷充電期間T1にて決定される信号伝達関数と、電荷転送期間T2にて決定される雑音伝達関数とを異ならせる。

【解決手段】スイッチと、複数のサンプリング容量と、積分容量とを含んで構成されるスイッチトキャパシター積分回路10は、電荷充電期間T1の入力信号に対応した電荷をサンプリング容量の少なくとも1つに充電する。スイッチトキャパシター積分回路10は、電荷転送期間T2において、該電荷を積分容量に転送することで、該電荷に対応した信号を伝搬遅延させる。スイッチトキャパシター積分回路10は、例えばスイッチにより複数のサンプリング容量の接続を切り換えることにより、電荷充電期間T1にて決定される信号伝達関数と、電荷転送期間T2にて決定される雑音伝達関数とを異ならせる。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、スイッチトキャパシター回路、フィルター回路、物理量測定装置及び電子機器等に関する。

【背景技術】

【0002】

従来より、角速度等の物理量を測定するセンサー回路は、車両や電子機器等に搭載され、車両運動や手振れ等による振動の検出に用いられている。近年では、このセンサー回路の用途が広まる一方であり、用途によっては、より高精度な検出が可能なものが望まれている。ところが、センサー回路自体が発生する雑音成分が大きい場合、本来検出したい微少な信号が埋もれてしまい、高精度な検出ができなくなる。そのため、センサー回路によってできるだけ微少な信号を検出しようとする場合、センサー回路自体が発生する雑音成分をできるだけ低減することが重要な課題となっている。

【0003】

このようなセンサー回路には、所望の信号伝達関数を有するスイッチトキャパシター(Switched Capacitor:以下、SC)回路が用いられ、SC回路により信号増幅やフィルタリングを行う。このSC回路については、次の図に示す構成を有するものの他に、例えば特許文献1や非特許文献1に開示されている。特許文献1には、スイッチと容量とで構成されるSC回路が開示されている。また、非特許文献1には、SC回路を構成する素子の値の広がりを抑えた2次のスイッチトキャパシターフィルター(Switched Capacitor Filter:SCF)が開示されている。

【0004】

図19に、一般的なSC積分回路の構成例を示す。

SC積分回路は、SC回路を用いた積分回路であり、広義のSC回路である。SC積分回路は、演算増幅器と、サンプリング容量Ca(容量値C1)と、演算増幅器の出力ノードと仮想接地ノードとの間に設けられる積分容量Cb(容量値C2)とを備えている。まず、SC積分回路は、第1のクロックによりオンオフ制御される複数のスイッチと、第2のクロックによりオンオフ制御される複数のスイッチとにより、入力信号に対応した電荷をサンプリング容量Caに充電する。その後、SC積分回路は、サンプリング容量Caに充電した電荷を積分容量Cbに転送することで、電圧増幅やフィルタリングを行う。入力信号をVIN、出力信号をVOUTとすると、図19のSC積分回路の伝達関数H0(z)は、次の式のようになる。

【数1】

【0005】

このようなSC積分回路では、入力信号VINの出力への信号伝達関数(Signal Transfer Function:以下、STF)の他に、スイッチと演算増幅器による雑音の出力への雑音伝達関数(Noise Transfer Function:以下、NTF)が存在する。NTFを改善することにより、SC積分回路の出力雑音成分を低減でき、センサー回路に好適なSC回路を提供できる。

【先行技術文献】

【特許文献】

【0006】

【特許文献1】特開平06−061793号公報

【非特許文献】

【0007】

【非特許文献1】電子情報通信学会技術研究報告CAS89−163//CS89−123//DSP89−62『素子値の広がりを抑えた2次SCF』石川、安斎、藤井

【発明の概要】

【発明が解決しようとする課題】

【0008】

しかしながら、特許文献1、非特許文献1及び図19に示す構成のSC回路の伝達関数は、例えば式(1)に示すように、移動する電荷量のみで決定される。例えば図19において、サンプリング容量Caで充電した電荷を積分容量Cbに転送することにより、STF及びNTFが決定される。そのため、従来のSC回路では、STFを変更することなくNTFを改善することができず、所望の信号伝達関数を維持したまま出力雑音成分のみを低減させることができないという問題があった。

【0009】

本発明は、以上のような技術的課題に鑑みてなされたものである。本発明の幾つかの態様によれば、所望の信号伝達関数で、より一層の出力雑音成分を低減できるSC(スイッチトキャパシター)回路、フィルター回路、物理量測定装置及び電子機器等を提供することができる。

【課題を解決するための手段】

【0010】

(1)本発明の第1の態様は、第1の期間の入力信号に対応した信号を第2の期間に伝搬遅延させるSC回路は、前記第1の期間にて決定される信号伝達関数と、前記第2の期間にて決定される雑音伝達関数とが異なる。

【0011】

本態様によれば、所望の信号伝達関数を維持したまま、雑音伝達関数のみを変更できるようになるので、所望の信号伝達関数で、より一層の出力雑音成分を低減できるSC回路を提供できるようになる。

【0012】

(2)本発明の第2の態様に係るSC回路は、第1の態様において、積分容量と、前記入力信号に対応した電荷を充電する第1の回路とを含み、前記第1の期間において、前記第1の回路に前記電荷を充電し、前記第2の期間において、前記第1の回路に充電された電荷を前記積分容量に転送する。

【0013】

本態様によれば、第1の回路において電荷を充電した後、積分容量に電荷を転送する構成を採用したので、所望の信号伝達関数で、より一層の出力雑音成分を低減できるSC積分回路としてSC回路を提供できるようになる。

【0014】

(3)本発明の第3の態様に係るSC回路は、第2の態様において、演算増幅器を含み、前記積分容量は、前記演算増幅器の出力ノードと前記演算増幅器の仮想接地ノードとの間に設けられる。

【0015】

本態様によれば、演算増幅器からの雑音を考慮しても、所望の信号伝達関数で、より一層の出力雑音成分を低減できるSC積分回路としてSC回路を提供できるようになる。

【0016】

(4)本発明の第4の態様に係るSC回路では、第1の態様乃至第3の態様のいずれかにおいて、前記第1の回路は、複数のサンプリング容量を含み、前記第1の期間から前記第2の期間に遷移するとき、前記複数のサンプリング容量の電気的な接続を切り換える。

【0017】

本態様においては、複数野サンプリング容量の電気的な接続を切り換えることにより、第1の期間にて決定される信号伝達関数と第2の期間にて決定される雑音伝達関数とを異ならせるようにしている。これにより、簡素な構成で、所望の信号伝達関数で、より一層の出力雑音成分を低減できるSC回路を提供できるようになる。

【0018】

(5)本発明の第5の態様に係るSC回路では、第4の態様において、前記第1の回路は、前記第1の期間において前記複数のサンプリング容量を並列に接続し、前記第2の期間において前記複数のサンプリング容量を直列に接続し、前記第1の期間では、各サンプリング容量の一端に前記入力信号が供給され、前記第2の期間では、直列接続された前記複数のサンプリング容量の一端が前記積分容量の一端に電気的に接続される。

【0019】

本態様によれば、第1の期間では複数のサンプリング容量を並列接続して電荷を充電し、第2の期間ではこれらを直列接続するようにしたので、第1期間に現れる雑音は平均効果により、第2期間に現れる雑音はNTFの減衰によって、簡素な構成で、信号伝達関数と雑音伝達関数とを異ならせることができる。

【0020】

(6)本発明の第6の態様に係るSC回路は、第4の態様又は第5の態様において、前記複数のサンプリング容量を構成する各サンプリング容量の容量値は、同一である。

【0021】

本態様によれば、簡素な構成で、所望の信号伝達関数で、より一層の出力雑音成分を低減できるSC回路を提供できるようになる。

【0022】

(7)本発明の第7の態様に係るSC回路では、第4の態様乃至第6の態様にいずれかにおいて、前記第1の回路は、一端に前記入力信号が供給される第1のスイッチと、前記第1のスイッチの他端にその一端が電気的に接続される第1のサンプリング容量と、一端に前記入力信号が供給される第2のスイッチと、前記第2のスイッチの他端にその一端が電気的に接続される第2のサンプリング容量と、前記第1のサンプリング容量の一端と前記第2のサンプリング容量の他端との間に設けられる第3のスイッチと、前記第1のサンプリング容量の他端と接地端との間に設けられる第4のスイッチと、前記第2のサンプリング容量の一端と前記接地端との間に設けられる第5のスイッチと、前記第2のサンプリング容量の他端と前記接地端との間に設けられる第6のスイッチと、前記演算増幅器の仮想接地ノードと前記第1のサンプリング容量の他端との間に設けられる第7のスイッチとを含み、前記第1のスイッチ、前記第2のスイッチ、前記第4のスイッチ及び前記第6のスイッチは、第1のクロックに基づいてオンオフ制御され、前記第3のスイッチ、前記第5のスイッチ及び前記第7のスイッチは、第2のクロックに基づいてオンオフ制御される。

【0023】

本態様によれば、スイッチと容量という簡素な構成で、信号伝達関数と雑音伝達関数とを異ならせ、所望の信号伝達関数で、より一層の出力雑音成分を低減できるSC回路を提供できるようになる。

【0024】

(8)本発明の第8の態様に係るSC回路では、第7の態様において、前記第2のクロックは、前記第1のクロックの位相と逆位相のクロックである。

【0025】

本態様においては、SC回路を構成するスイッチの各々を、互いに逆相の第1のクロック及び第2のクロックのいずれかで動作させるようにしている。これにより、簡素なクロック制御により、上記の効果が得られるSC回路を提供できるようになる。

【0026】

(9)本発明の第9の態様は、フィルター回路が、第1の態様乃至第8の態様のいずれか記載のSC回路を含む。

【0027】

本態様によれば、雑音成分を大幅に削減できるSC回路を採用したので、フィルター性能の優れたフィルター回路を提供できるようになる。

【0028】

(10)本発明の第10の態様は、物理量測定装置が、振動子と、前記振動子と発振ループを形成し、該振動子に駆動振動を励振する駆動回路と、前記振動子に励振される駆動振動及び測定すべき物理量に応じて検出信号を出力する検出回路とを含み、前記検出回路は、前記駆動振動及び前記物理量に応じて前記検出信号を出力する上記のフィルター回路を含む。

【0029】

本態様によれば、これまでに比べてより一層物理量に対応した検出信号を高精度に出力できる物理量測定装置を提供できるようになる。

【0030】

(11)本発明の第11の態様に係る物理量測定装置では、第10の態様において、前記物理量は、角速度である。

【0031】

本態様によれば、より一層角速度に対応した検出信号を高精度に出力できる物理量測定装置を提供できるようになる。

【0032】

(12)本発明の第12の態様は、電子機器が、上記のいずれか記載の物理量測定装置を含む。

【0033】

本態様によれば、物理量に応じてより一層高精度な処理が可能な電子機器を提供できるようになる。

【図面の簡単な説明】

【0034】

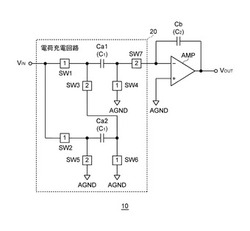

【図1】本発明の一実施形態に係るSC積分回路の構成例の回路図。

【図2】本実施形態における第1のクロック及び第2のクロックの説明図。

【図3】図3(A)、図3(B)は電荷充電回路の動作説明図。

【図4】図4(A)、図4(B)は電荷充電回路の動作説明図。

【図5】図5(A)、図5(B)は本実施形態の動作説明図。

【図6】図6(A)、図6(B)は図19のSC積分回路の動作時の構成の概要を示す図。

【図7】図7(A)、図7(B)は図19のSC積分回路における第1のフェーズスイッチの雑音のNTFを算出するための構成の概要を示す図。

【図8】図8(A)、図8(B)は図19のSC積分回路における第2のフェーズスイッチの雑音のNTFを算出するための構成の概要を示す図。

【図9】図19のSC積分回路を構成する演算増幅器が発生する雑音の説明図。

【図10】図10(A)、図10(B)は図1のSC積分回路の動作時の構成の概要を示す図。

【図11】図11(A)、図11(B)は図1のSC積分回路の第1のフェーズスイッチの雑音のNTFを算出するための構成の概要を示す図。

【図12】図12(A)、図12(B)は図1のSC積分回路の第2のフェーズスイッチの雑音のNTFを算出するための構成の概要を示す図。

【図13】図1のSC積分回路を構成する演算増幅器が発生する雑音の説明図。

【図14】サンプリング容量がNである場合のSC積分回路の構成例を示す図。

【図15】出力雑音電力スペクトラムのシミュレーション結果の一例を示す図。

【図16】本実施形態におけるSC積分回路を用いて構成された2次のローパスフィルターの構成例を示す図。

【図17】図16のローパスフィルターが適用されたセンサー回路の構成例を示す図。

【図18】本実施形態における電子機器のハードウェア構成例のブロック図。

【図19】一般的なSC積分回路の構成例を示す図。

【発明を実施するための形態】

【0035】

以下、本発明の実施の形態について図面を用いて詳細に説明する。なお、以下に説明する実施の形態は、特許請求の範囲に記載された本発明の内容を不当に限定するものではない。また以下で説明される構成のすべてが本発明の課題を解決するために必須の構成要件であるとは限らない。

【0036】

以下では、SC回路としてSC積分回路を例に説明するが、本発明に係るSC回路はSC積分回路に限定されるものではない。

【0037】

1. SC回路

図1に、本発明の一実施形態に係るSC積分回路の構成例の回路図を示す。

SC積分回路10は、演算増幅器AMPと、積分容量Cb(容量値C2)と、電荷充電回路(第1の回路)20とを含む。演算増幅器AMPは、公知の演算増幅器であり、演算増幅器AMPの非反転入力端子はアナログ接地電位AGNDに接続され、演算増幅器AMPの反転入力端子が仮想接地ノードとなる。積分容量Cbは、演算増幅器AMPの出力ノードと仮想接地ノードとの間に挿入される。電荷充電回路20は、SC積分回路10の入力端子と演算増幅器AMPの仮想接地ノードとの間に設けられる。演算増幅器AMPの出力ノードが、SC積分回路10の出力端子となる。

【0038】

電荷充電回路20は、複数のサンプリング容量と、複数のスイッチとを含み、電荷充電期間(第1の期間)T1において入力信号VINに対応した電荷を充電し、電荷転送期間(第2の期間)T2において電荷充電期間T1で充電した電荷を積分容量Cbに転送する。電荷充電回路20は、電荷充電期間T1から電荷転送期間T2に遷移するとき、複数のスイッチにより複数のサンプリング容量の電気的な接続を切り換える。これにより、電荷充電回路20は、信号と雑音との間で電荷転送の仕組みを異ならせる。例えば、電荷充電回路20は、電荷充電期間T1において複数のサンプリング容量を並列に接続し、電荷転送期間T2において複数のサンプリング容量を直列に接続する。電荷充電期間T1では、電荷充電回路20の各サンプリング容量の一端に入力信号VINが供給され、電荷転送期間T2では、直列接続された複数のサンプリング容量の一端を積分容量Cbの一端に電気的に接続する。こうすることで、電荷充電期間T1における入力信号VINを伝搬遅延させるSC積分回路10のSTF(信号伝達関数)とNTF(雑音伝達関数)とを異ならせることができる。これにより、所望のSTFを変更することなくNTFのみを小さくして雑音の増幅度を小さくすることができるようになる。

【0039】

以下、説明の便宜上、サンプリング容量の個数Nが「2」である例について説明するが、電荷充電回路20は、サンプリング容量の個数が3以上であってもよい。Nが「2」の場合、電荷充電回路20は、サンプリング容量Ca1(第1のサンプリング容量)、Ca2(第2のサンプリング容量)と、これらを並列接続又は直列接続に切り換えるための第1のスイッチSW1〜第7のスイッチSW7とを含む。第1のスイッチSW1〜第7のスイッチSW7は、それぞれ2相クロックのいずれか一方によりオンオフ制御される。図1では、各スイッチには、「1」と表記されるスイッチと、「2」と表記されるスイッチの2種類がある。「1」と表記されるスイッチは、第1のクロックCLK1で動作するスイッチ(第1のフェーズスイッチ)である。「2」と表記されるスイッチは、第2のクロックCLK2で動作するスイッチ(第2のフェーズスイッチ)である。

【0040】

第1のスイッチSW1の一端に、入力信号VINが供給される。サンプリング容量Ca1の一端は、第1のスイッチSW1の他端に電気的に接続される。第2のスイッチSW2の一端に、入力信号VINが供給される。サンプリング容量Ca2の一端は、第2のスイッチSW2の他端に電気的に接続される。第3のスイッチSW3は、サンプリング容量Ca1の一端とサンプリング容量Ca2の他端との間に設けられる。第4のスイッチSW4は、サンプリング容量Ca1の他端と接地端(アナログ接地電位AGND)との間に設けられる。第5のスイッチSW5は、サンプリング容量Ca2の一端と接地端との間に設けられる。第6のスイッチSW6は、サンプリング容量Ca2の他端と接地端との間に設けられる。第7のスイッチSW7は、演算増幅器AMPの仮想接地ノードとサンプリング容量Ca1の他端との間に設けられる。

【0041】

第1のスイッチSW1、第2のスイッチSW2、第4のスイッチSW4及び第6のスイッチSW6は、第1のクロックCLK1に基づいてオンオフ制御される。第3のスイッチSW3、第5のスイッチSW5及び第7のスイッチSW7は、第2のクロックCLK2に基づいてオンオフ制御される。

【0042】

図2に、本実施形態における第1のクロック及び第2のクロックの説明図を示す。

図1において「1」と表記される第1のフェーズスイッチは、第1のクロックCLK1がHレベルのときオン(導通状態)となり、第1のクロックCLK1がLレベルのときオフ(非導通状態)となる。「2」と表記される第2のフェーズスイッチは、第2のクロックCLK2がHレベルのときオン(導通状態)となり、第2のクロックCLK2がLレベルのときオフ(非導通状態)となる。

【0043】

第2のクロックCLK2は、第1のクロックCLK1とは逆相のクロックである。第1のクロックCLK1によりスイッチ制御されるスイッチと第2のクロックCLK2によりスイッチ制御されるスイッチとが同時にオンしないように、各クロックが変化するようになっている。

【0044】

このような2相のクロックによるスイッチ制御により、サンプリング容量Ca1、Ca2の接続関係を切り換えることで、信号と雑音との間で電荷転送の仕組みを異ならせる。ここで、このような電荷充電回路20における電荷転送の概要について説明する。

【0045】

図3(A)、図3(B)、図4(A)、図4(B)に、電荷充電回路20の動作説明図を示す。図3(A)は、電荷充電期間T1における電荷充電回路20の動作説明図を示す。図3(B)は、電荷転送期間T2における電荷充電回路20の動作説明図を示す。図4(A)は、N(Nは2以上の整数)個のサンプリング容量による電荷充電期間T1における電荷充電回路20の動作説明図を示す。図4(B)は、N個のサンプリング容量による電荷転送期間T2における電荷充電回路20の動作説明図を示す。

【0046】

電荷充電期間T1では、電荷充電回路20を構成する複数のサンプリング容量は並列に接続される。このとき、図3(A)に示すように、サンプリング容量Ca1には電圧V1が印加されて電荷QA、サンプリング容量Ca2には電圧V2が印加されて電荷QBが蓄積される。ここで、サンプリング容量Ca1、Ca2の容量値が同一(Ca1=Ca2=C)である場合、各サンプリング容量に電圧V1、V2がサンプリングされた後、電荷転送期間T2においてサンプリング容量が直列接続されたとき、次式で表される電荷Qが積分容量Cbに転送される。このとき、下の式において、V1=V2=VINとすると、電荷充電回路20で転送される電荷量は1つのサンプリング容量で転送される電荷量と等しくなる。

【数2】

【0047】

即ち、図4(A)のように、それぞれが同じ容量値のN個のサンプリング容量を並列に接続した場合に転送される電荷Qは、次式のように表される。このとき、それぞれの容量値が等しいN個のサンプリング容量(容量値C)を並列接続して充電(サンプリング)した電荷を直列接続して積分容量に転送する場合、1つのサンプリング容量で同じ電荷量を転送したことに相当する。これは、相関性がある電圧信号に対応した電荷を充電する場合に成り立つ。

【数3】

【0048】

これに対して、図3(A)において、雑音信号のような無相関の信号に対応した電荷を充電する場合、V1=V2=VNとすると、次式で表されるように、転送される電荷量に平均効果が現れる。

【数4】

【0049】

従って、無相関の信号について、図4(A)、図4(B)のように、それぞれが同じ容量値のN個のサンプリング容量(容量値C)を並列に接続した場合に転送される電荷Qは、次式のように表される。

【数5】

【0050】

ここで、式(3)及び式(5)に示すように、複数のサンプリング容量を並列接続して充電した電荷を直列接続して転送することで、信号の相関種類に応じて伝達関数を異ならせることができる。

【0051】

図5(A)、図5(B)に、本実施形態の動作説明図を示す。図5(A)は、図19の構成におけるSTF及びNTFの説明図を示す。図5(B)は、図1に構成におけるSTF及びNTFの説明図を示す。

【0052】

図19の構成では、図5(A)に示すように、電荷充電期間T1においてSTF及びNTFが決定される。そのため、STFを変更することなくNTFを改善することができない。これに対して、本実施形態の構成は、図5(B)に示すように、電荷充電期間T1においてSTFが決定され、電荷転送期間T2においてNTFが決定される。即ち、所望の信号に対してはSTFが変更されず、且つ雑音に対しては平均効果及びNTFの減衰が現れるように構成が切り換えられる。

【0053】

これにより、電荷充電期間T1において決定されるSTFを維持したまま、電荷転送期間T2において決定されるNTFのみを小さくして、雑音信号の伝達量を削減できる。このように、電荷充電期間T1におけるSTFと電荷転送期間T2におけるNTFとが異なるSC積分回路により、所望の信号伝達関数で、より一層の出力雑音成分を低減できるようになる。

【0054】

2. SC積分回路の雑音

以下、図19のSC積分回路の雑音を基準に、本実施形態におけるSC積分回路10の雑音について説明する。

【0055】

2.1 一般的なSC積分回路

まず、図19に示す一般的なSC積分回路のSTFを説明した後、一般的なSC積分回路の雑音について説明する。

【0056】

2.1.1 STF

図6(A)、図6(B)に、図19に示す一般的なSC積分回路の動作時の構成の概要を示す。図6(A)は、電荷充電期間T1におけるSC積分回路の構成の概要を示す。図6(B)は、電荷転送期間T2におけるSC積分回路の構成の概要を示す。図6(A)、図6(B)において、図19と同様の部分には同一符号を付し、適宜説明を省略する。

【0057】

積分容量Cbに電荷が転送されるタイミングを時刻nとすると、時刻(n−1)では、第1のクロックCLK1により、サンプリング容量Caに電荷が充電される。図6(A)に示すように、入力電圧VINが入力される側のサンプリング容量Caの電荷量を+Qa、演算増幅器AMP0の仮想接地ノード側の積分容量Cbの電荷量を+Qbとすると、次式が成り立つ。

【数6】

【0058】

次に、時刻nでは、第2のクロックCLK2により図6(B)に示す構成となり、サンプリング容量Caに充電された電荷が積分容量Cbに転送され、次式のように表される。

【数7】

【0059】

ここで、電荷保存の法則により、次式が成立する。

【数8】

【0060】

式(8)に式(6)及び式(7)を代入して求められる図19のSC積分回路のSTFであるH0(z)は、既出の式(1)のようになる。

【0061】

2.1.2 一般的なSC積分回路の雑音

SC積分回路の雑音は、SC積分回路を構成するスイッチ(フェーズスイッチ)が発生する雑音と、演算増幅器が発生する雑音とに区別することができる。

【0062】

2.1.2.1 スイッチが発生する雑音

各フェーズスイッチがオン状態のとき、スイッチのオン抵抗による白色雑音が発生する。この種の雑音スペクトラムは、スイッチのオン抵抗RONと容量Ca(容量値C1)とによる1次の周波数特性を有し、雑音電力は(k・T)/C1で表すことができる。ここで、kはボルツマン定数、Tは絶対温度である。即ち、雑音電力は、容量Caのみによって決まり、容量Caに接続されるスイッチの数及びオン抵抗RONには依存しない。このような各フェーズスイッチが発生する雑音のNTFは、次のように求められる。

【0063】

図7(A)、図7(B)に、図19のSC積分回路における第1のフェーズスイッチの雑音のNTFを算出するための構成の概要を示す。図7(A)は、電荷充電期間T1における図19のSC積分回路の構成の概要を示す。図7(B)は、電荷転送期間T2における図19のSC積分回路の構成の概要を示す。図7(A)、図7(B)において、サンプリング容量Caのうち入力信号VINの供給側の第1のフェーズスイッチを雑音成分Vn1の雑音源であるものとし、図19と同様の部分には同一符号を付し、適宜説明を省略する。

【0064】

図6(A)、図6(B)と同様に、積分容量Cbに電荷が転送されるタイミングを時刻nとすると、時刻(n−1)では、次式が成り立つ。

【数9】

【0065】

また、時刻nでは、図7(B)に示す構成となり、サンプリング容量Caに充電された電荷が積分容量Cbに転送され、次式のように表される。

【数10】

【0066】

ここで、電荷保存の法則により、式(8)が成立するので、式(8)に式(9)及び式(10)を代入して求められる図19のSC積分回路の第1のフェーズスイッチの雑音のNTFであるHn1(z)は、次式のようになる。

【数11】

【0067】

図8(A)、図8(B)に、図19のSC積分回路における第2のフェーズスイッチの雑音のNTFを算出するための構成の概要を示す。図8(A)は、電荷充電期間T1における図19のSC積分回路の構成の概要を示す。図8(B)は、電荷転送期間T2における図19のSC積分回路の構成の概要を示す。図8(A)、図8(B)において、サンプリング容量Caのうち入力信号VINの供給側の第2のフェーズスイッチを雑音成分Vn2の雑音源であるものとし、図19と同様の部分には同一符号を付し、適宜説明を省略する。

【0068】

図7(A)、図7(B)と同様に、積分容量Cbに電荷が転送されるタイミングを時刻nとすると、時刻(n−1)では、次式が成り立つ。

【数12】

【0069】

次に、時刻nでは、図8(B)に示す構成となり、次式のように表される。

【数13】

【0070】

ここで、電荷保存の法則により、式(8)が成立するので、式(8)に式(12)及び式(13)を代入して求められる図19のSC積分回路の第2のフェーズスイッチの雑音のNTFであるHn2(z)は、次式のようになる。

【数14】

【0071】

従って、図19のSC積分回路においてフェーズスイッチから出力に現れる出力雑音電力スペクトラムVOsw2は、次のように表すことができる。なお、以下では、Vns2=(k・T)/C1・fs)であり、Vns2はスイッチの雑音電力である。fsはサンプリング周波数に相当する第1のクロックCLK1又は第2のクロックCLK2のクロック周波数であり、サンプリングによる雑音スペクトラムの折り返しを表している。

【数15】

【0072】

第1のフェーズスイッチを構成する各スイッチ及び第2のフェーズスイッチを構成する各スイッチが同一構造のスイッチであるものとする。このとき、式(11)及び式(14)より各雑音成分のNTFは同じ振幅特性を有しているため、|Hn1(z)|2=|Hn2(z)|2であり、以下の式が成り立つ。なお、以下では、|Hn(z)|2=|Hn1(z)|2=|Hn2(z)|2とし、Hn(z)はスイッチの雑音のNTFを表す。

【数16】

【0073】

2.1.2.2 演算増幅器が発生する雑音

図19に示すSC積分回路において、第2のフェーズスイッチがオンするたびに、演算増幅器AMP0の雑音電圧に比例する電荷がサンプリング容量Caに充電される。そして、この電荷は積分容量Cbに転送され、結果として演算増幅器AMP0の雑音も積分され、演算増幅器AMP0からの雑音は、各フェーズスイッチの雑音と同様に、ある伝達関数Hnop(z)を有しながら出力に反映されることになる。

【0074】

図9に、図19のSC積分回路を構成する演算増幅器AMP0が発生する雑音の説明図を示す。図9において、演算増幅器AMP0の非反転入力端子に雑音成分Vnopの雑音源が設けられているものとし、図19と同様の部分には同一符号を付し、適宜説明を省略する。

【0075】

ここで、Vnop2は演算増幅器からの雑音電力スペクトラムであり、NTFはサンプリング容量Ca及び積分容量Cbによって決まるため|Hnop(z)|2=|Hn(z)|2と考えることができる。よって演算増幅器からの出力雑音電力スペクトラムVOop2は、次式のように表すことができる。

【数17】

【0076】

2.1.2.3 全体の出力雑音電力スペクトラム

式(16)及び式(17)より、図19に示す一般的なSC積分回路全体の出力雑音電力スペクトラムVO_tot12は、次のように表される。

【数18】

【0077】

2.2 本実施形態のSC積分回路

次に、これまで求めた図19のSC積分回路のSTF、NTF、出力雑音電力スペクトラムを基準に、本実施形態におけるSC積分回路10について説明する。以下では、SC積分回路10を構成する複数のサンプリング容量の容量値は同一であるものとして説明するが、NTFの改善前後においてSTFが厳密に同一でなくてもよい場合には、複数のサンプリング容量の容量値は同一でなくてもよい。この場合でも、ほぼ所望のSTFでNTFを改善することができる効果が得られる。

【0078】

2.2.1 STF

図10(A)、図10(B)に、図1のSC積分回路10の動作時の構成の概要を示す。図10(A)は、電荷充電期間T1におけるSC積分回路10の構成の概要を示す。図10(B)は、電荷転送期間T2におけるSC積分回路10の構成の概要を示す。図10(A)、図10(B)において、図1と同様の部分には同一符号を付し、適宜説明を省略する。

【0079】

積分容量Cbに電荷が転送されるタイミングを時刻nとすると、時刻(n−1)では、第1のクロックCLK1により、サンプリング容量Ca1、Ca2に電荷が充電される。図10(A)に示すように、入力電圧VINが入力される側のサンプリング容量Ca1、Ca2の電荷量を+Q1、+Q2とすると、次式が成り立つ。なお、積分容量Cbについては、図10(A)に示すように演算増幅器AMPの仮想接地ノード側の積分容量Cbの電荷量を+Q3としている。

【数19】

【0080】

次に、時刻nでは、第2のクロックCLK2により図10(B)に示す構成となり、サンプリング容量Ca1及びサンプリング容量Ca2は直列に接続され、式(2)に示す電荷が積分容量Cbに転送され、次式のように表される。

【数20】

【0081】

ここで、演算増幅器の仮想接地端子における電荷保存の法則より、次式が成立する。

【数21】

【0082】

式(21)に式(19)及び式(20)を代入して求められるSC積分回路10のSTFであるH(z)は、次式のようになり、図19のSC積分回路のSTFと同様である。

【数22】

【0083】

2.2.2 本実施形態のSC積分回路の雑音

本実施形態におけるSC積分回路においても、SC積分回路の雑音は、SC積分回路を構成するスイッチ(フェーズスイッチ)が発生する雑音と、演算増幅器が発生する雑音とに区別することができる。

【0084】

2.2.2.1 スイッチが発生する雑音

図11(A)、図11(B)に、図1のSC積分回路10の第1のフェーズスイッチの雑音のNTFを算出するための構成の概要を示す。図11(A)は、電荷充電期間T1におけるSC積分回路10の構成の概要を示す。図11(B)は、電荷転送期間T2におけるSC積分回路10の構成の概要を示す。図11(A)、図11(B)において、第1のスイッチSW1を雑音成分Vn1の雑音源であるものとし、図1と同様の部分には同一符号を付し、適宜説明を省略する。

【0085】

SC積分回路10の第1のフェーズスイッチの雑音のNTFは、上記と同様に求めることができるが、次のように導出することもできる。第1のフェーズスイッチがオンすると、図11(A)に示すように、サンプリング容量Ca1、Ca2には、それぞれ(k・T)/C1の雑音電力に対応する電荷が蓄積される。電荷としてサンプリング容量Ca1、Ca2に蓄積される雑音の伝達関数を求めるには、サンプリング容量Ca1、Ca2のどちらかのサンプリング容量に蓄えられる電荷の伝搬だけを考えればよい。ここで、電荷充電期間T1において、サンプリング容量Ca1には雑音電荷Qnが蓄積され、サンプリング容量Ca2には電荷が蓄積されない。第2のフェーズスイッチがオンすると、図11(B)に示すように、サンプリング容量Ca1に蓄積された電荷が積分容量Cbに転送されるが、電荷量存の法則により、転送される電荷量はQn/2である。従って、図11(A)に示す第1のスイッチSW1の雑音のNTFは、次式のようになり、図19のSC積分回路のNTF(式(11)参照)の半分になる。

【数23】

【0086】

ここで、第2のスイッチSW2の雑音のNTFも式(23)と同様である。雑音は無相関であることを考慮して、第1のフェーズスイッチから出力に現れる雑音電力は、第1のスイッチSW1からの出力雑音電力と第2のスイッチSW2からの雑音電力とを加算したものとなる。従って、第1のフェーズスイッチからの出力雑音電力スペクトラムVpno12は、次のようになる。

【数24】

【0087】

図12(A)、図12(B)に、図1のSC積分回路10の第2のフェーズスイッチの雑音のNTFを算出するための構成の概要を示す。図12(A)は、電荷充電期間T1におけるSC積分回路10の構成の概要を示す。図12(B)は、電荷転送期間T2におけるSC積分回路10の構成の概要を示す。図12(A)、図12(B)において、第5のスイッチSW5を雑音成分Vn2の雑音源であるものとし、図1と同様の部分には同一符号を付し、適宜説明を省略する。

【0088】

第2のフェーズスイッチがオンすると、サンプリング容量Ca1、Ca2が直列に接続されるため、第2のフェーズスイッチの雑音電力は(2・k・T/C1)になる。これは、容量が小さく見える分だけ雑音帯域が広がることに起因する。即ち、サンプリング容量の容量値が半分になるため、第2のフェーズスイッチの雑音のNTFは、次式のように表され、図19のSC積分回路のNTF(式(14)参照)の半分になる。

【数25】

【0089】

従って、第2のフェーズスイッチからの出力雑音電力スペクトラムVpno22は、次のようになる。

【数26】

【0090】

以上より、SC積分回路10において出力に現れる出力雑音電力スペクトラムVOswp2は、式(25)と式(26)とを加算することにより求められる。

【数27】

【0091】

式(16)と式(27)とを比較すると、本実施形態におけるSC積分回路10において、各フェーズスイッチの雑音のNTFを、一般的なSC積分回路のNTFより小さくすることができる。その上、雑音は無相関の信号であるため、各フェーズスイッチからの出力雑音電力スペクトラムも、一般的なSC積分回路の各フェーズスイッチからの出力雑音電力スペクトラムよりも小さくなる。そして、全スイッチからの出力雑音電力スペクトラムも、一般的なSC積分回路よりも小さくなる。

【0092】

2.2.2.2 演算増幅器が発生する雑音

図13に、図1のSC積分回路10を構成する演算増幅器AMPが発生する雑音の説明図を示す。図13において、演算増幅器AMPの非反転入力端子に雑音成分Vnopの雑音源が設けられているものとし、図1と同様の部分には同一符号を付し、適宜説明を省略する。

【0093】

SC積分回路10において、第2のフェーズスイッチがオンするたびに、演算増幅器AMPからの雑音が積分される。このとき、サンプリング容量の容量値はC1/2に見えるため、演算増幅器AMPからの雑音の伝達関数は、Hnop(z)/2となり、演算増幅器AMP0からの雑音の伝達関数Hnop(z)の半分となる。従って、演算増幅器AMPの雑音による出力雑音電力スペクトラムVOopp2は、次式のように表すことができる。

【数28】

【0094】

2.2.2.3 全体の出力雑音電力スペクトラム

式(27)及び式(28)より、本実施形態のSC積分回路10全体の出力雑音電力スペクトラムVO_tot22は、次のように表される。

【数29】

【0095】

以上説明したように、本実施形態では、並列に接続されたサンプリング容量に充電した電荷を、各サンプリング容量を直列に接続して積分容量に転送する構成としている。これにより、雑音のような無相関の信号に対する平均効果により、STFを変更することなく、NTFを小さくすることができるようになる。また、式(17)と式(29)とを比較すると、図1のSC積分回路10の素子数が図19のSC積分回路の素子数より増加するが、本実施形態のSC積分回路10における出力雑音は、図19のSC積分回路における出力雑音より小さいことは明らかである。

【0096】

図1では、サンプリング容量が2つである例について説明したが、サンプリング容量が3つ以上であっても同様である。

【0097】

図14に、サンプリング容量がNである場合のSC積分回路10aの構成例を示す。図14において、図1と同様の部分には同一符号を付し、適宜説明を省略する。

【0098】

SC積分回路10aは、図1の電荷充電回路20に代えて電荷充電回路20aを備えている。電荷充電回路20aは、複数のスイッチと、N個のサンプリング容量Ca1〜CaNとを含む。電荷充電回路20aは、これらのスイッチにより、電荷充電期間T1においてサンプリング容量Ca1〜CaNを並列に接続し、電荷転送期間T2においてサンプリング容量Ca1〜CaNを直列に接続する。電荷充電期間T1では、各サンプリング容量には入力信号VINが印加される。電荷転送期間T2では、直列接続されたサンプリング容量Ca1〜CaNのうち、サンプリング容量CaNの一端がアナログ接地電位AGNDに接続され、サンプリング容量Ca1の一端が演算増幅器AMPの仮想接地ノードに電気的に接続される。

【0099】

図14に示すように、サンプリング容量の個数がNのときのSC積分回路10aの出力雑音電力スペクトラムVO_tot32は、次にように表すことができる。

【数30】

【0100】

式(30)に示すように、Nが増えるほど、出力雑音電力スペクトラムVO_tot32が小さくなる。その一方、Nを増やすことは、サンプリング容量が増えることを意味し、SC積分回路10aの面積増大を招く。そこで、図19に示すSC積分回路の総容量値と、図14に示すSC積分回路10aの総容量値とが等しいという条件下で、両者の出力雑音スペクトラムを比較する。

【0101】

図19に示すSC積分回路の総容量値Ctcは、実数Mを用いて次のように表すことができる。下の式において、α=C1/C2であり、式(1)より、容量値をM倍にしても信号伝達関数は変化しない。

【数31】

【0102】

式(31)において、スイッチの雑音帯域は1/M倍になるため、この場合の出力雑音電力スペクトラムVO_tot42は、次のようになる。

【数32】

【0103】

これに対して、図14のSC積分回路10aの総容量値Ctpは、次のように表すことができる。なお、下の式において、N=1のときは図19のSC積分回路と同様の構成となり、Nが2以上であることが条件となる。

【数33】

【0104】

式(31)と式(33)とが等しいとき、Mは次のように表すことができる。

【数34】

【0105】

ここで、式(30)と式(32)とを比較したときに演算増幅器の雑音に着目すると、任意のN(N≧2)に対してSC積分回路10aの出力雑音電力スペクトラムはSC積分回路10の出力雑音電力スペクトラムよりも小さくなる。一方、式(30)と式(32)とを比較したときにスイッチの雑音に着目すると、N>Mのとき、SC積分回路10aの出力雑音電力スペクトラムが小さくなる。従って、式(34)をN>Mに代入すると、N>1となる。条件としてNが2以上である必要があるため、必ずN>1が成立する。

【0106】

以上より、図19に示すSC積分回路の総容量値と、図14に示すSC積分回路10aの総容量値とが等しい場合、SC積分回路10aの方が必ず出力雑音電力スペクトラムが小さくなる。

【0107】

図15に、出力雑音電力スペクトラムのシミュレーション結果の一例を示す。縦軸に出力雑音電力スペクトラムを表し、横軸にαを表す。図15は、N=2のときのシミュレーション結果を表す。

【0108】

このように、αを0.1から10まで変化させても、SC積分回路10aの出力雑音電力スペクトラムの方が必ず小さくなることを表している。

【0109】

以上説明したように、本実施形態によれば、STFとNTFとを分離できる構成を採用したので、所望の信号伝達関数で、より一層の出力雑音成分を低減できるSC回路を提供できるようになる。

【0110】

3. フィルター回路

本実施形態におけるSC積分回路10は、フィルター回路として例えば次のような2次のローパスフィルター(Low Pass Filter:以下、適宜LPFと略す)に適用することができる。

【0111】

図16に、本実施形態におけるSC積分回路を用いて構成された2次のローパスフィルターの構成例を示す。図16において、スイッチの表記は図1と同様であり、一般的に良く知られているFleisher−Lakerのローパスフィルターで表記される容量と対応する容量には同一の符号を付している。

【0112】

このローパスフィルター30では、後段側に図1のSC積分回路10と同様の構成を有するSC積分回路32が適用される。このSC積分回路32は、入力側に設けられたローパスフィルターとは互いに逆の位相で動作するため、図1のSC積分回路10を構成するフェーズスイッチの表記とSC積分回路32を構成するフェーズスイッチの表記とが逆になっている。このローパスフィルター30によれば、所望の信号伝達関数で動作し、且つ従来と比べて雑音成分を大幅に低減できるようになる。

【0113】

なお、図16において、ローパスフィルター30はSC積分回路10に代えてSC積分回路10aが適用されていてもよい。

【0114】

4. 物理量測定装置

図16のローパスフィルター30は、センサー回路に適用することにより、高精度なセンシングを行うことができるようになる。

【0115】

図17に、図16のローパスフィルターが適用されたセンサー回路の構成例を示す。なお、この回路構成は一例であり、例えば回路の細部の構成が変形される場合もあり得る。

【0116】

センサー回路50は、角速度を測定対象の物理量とする物理量測定装置である。センサー回路50は、駆動回路(駆動装置)100と、検出回路(検出装置)200とを含む。このセンサー回路50は、圧電材料で形成され、駆動振動片及び検出振動片を有する振動片(振動子)40を含む。

【0117】

駆動回路100は、駆動振動片に設けられた駆動電極42a、42bを介して駆動振動片を発振ループ内に設け、駆動振動片(広義には振動子)を励振させる。駆動回路100は、電流電圧変換器110、オートゲインコントロール(Auto Gain Control:以下、AGCと略す)回路120、帯域通過フィルター(Band Pass Filter:以下、BPFと略す)130を含む。更に、駆動回路100は、ゲインコントロールアンプ(Gain Control Amplifier:以下、GCAと略す)140、2値化回路150を含む。

【0118】

駆動振動片の駆動電極42aは、電流電圧変換器110の入力に電気的に接続され、電流電圧変換器110の出力は、AGC回路120及びBPF130に入力される。BPF130は、発振ループ内の発振信号の位相調整回路として機能し、BPF130の出力は、GCA140及び2値化回路150に入力される。AGC回路120は、電流電圧変換器110の出力に基づいて、GCA140のゲインを制御する。GCA140の出力は、駆動振動片の駆動電極42bに電気的に接続される。2値化回路150は、発振ループ内の発振信号を2値化し、参照信号として検出回路200に出力する。なお、図17では、駆動回路100の内部に振動片40の駆動振動片を設けるものとして説明したが、駆動回路100の外部に振動片40の駆動振動片が設けられていてもよい。

【0119】

検出回路200は、交流増幅回路210と、同期検波回路220と、直流増幅器230と、ローパスフィルター30とを含む。交流増幅回路210は、第1の電流電圧変換器212と、第2の電流電圧変換器214と、交流増幅器216と、BPF218とを含む。

【0120】

このような駆動回路100では、上記の構成の発振ループ内のゲインが「1」より大きい状態で発振スタートする。この時点では、駆動振動片への入力は雑音のみであるが、この雑音は、目的とする駆動振動の固有共振周波数を含む幅広い周波数の波動を含む。振動片40の駆動振動片の周波数フィルター作用によって、目的とする固有共振周波数の波動を多く含む信号が出力され、この信号が電流電圧変換器110において電圧値に変換される。AGC回路120は、この電圧値に基づいてGCA140のゲインを制御することで発振ループ内の発振振幅を制御する。発振ループ内でこうした操作が繰り返されることにより、目的とする固有共振周波数の信号の割合が高くなる。そして、GCA140のゲイン制御によって、次第に発振ループを信号が1周する間の利得(ループゲイン)が「1」となり、この状態で駆動振動片が安定発振する。

【0121】

駆動振動片を励振させて安定発振状態になり、振動片40を所与の方向に回転させると、コリオリ力が振動片40に作用し、検出振動片が屈曲振動する。検出振動片には検出電極44a、44b、46a、46bが設けられる。検出電極44b、46bにはアナログ接地電位が供給され、検出電極44a、46aは、交流増幅回路210の第1の電流電圧変換器212及び第2の電流電圧変換器214に接続される。検出回路200は、検出電極44a、46aからの互いに極性が異なる検出信号を交流増幅した後、駆動回路100からの参照信号を用いて同期検波して、ローパスフィルター30で検出信号OUTを出力する。

【0122】

5. 電子機器

上記のセンサー回路は、次のような電子機器に搭載することができる。このような電子機器によれば、所望の信号伝達関数で動作し、且つ高精度なセンシングを容易に実現できるようになる。

【0123】

図18に、本実施形態における電子機器のハードウェア構成例のブロック図を示す。

【0124】

電子機器400は、センサー回路50と、A/D変換回路410と、クロック生成回路510と、中央演算処理装置等の処理部520と、メモリー530と、操作部540と、表示部550とを有する。電子機器400を構成する各部は、バス(BUS)によって相互に接続されている。なお、A/D変換回路410は、処理部520に内蔵されていてもよい。

【0125】

例えば、処理部520は、メモリー530から読み込んだプログラムに従って処理を実行し、センサー回路50で検出された検出信号の振幅又は感度に応じてA/D変換回路410で変換されたディジタル値を用いて積分を行う。こうすることで、角速度及び回転角度を算出する。そして、処理部520は、算出した角速度又は回転角度に対応した処理を実行し、該処理に対応した表示データを生成し、表示部550に表示させる処理を行う。

【0126】

以上、本発明に係るSC回路、フィルター回路、物理量測定装置及び電子機器を上記の実施形態に基づいて説明したが、本発明は上記の実施形態に限定されるものではない。本発明は、その要旨を逸脱しない範囲において種々の態様において実施することが可能であり、例えば次のような変形も可能である。

【0127】

(1)本実施形態では、SC回路として図1又は図14の構成のSC積分回路を例に説明したが、本発明はこれらに限定されるものではない。スイッチと容量とを用いて電荷を充電して転送する原理を有するSC回路に限らず、信号を伝搬遅延させるSC回路に適用できる。

【0128】

(2)本実施形態では、平均効果によりNTFを小さくすることでSTFとNTFとを異ならせるものとして説明したが、本発明はこれに限定されるものではない。

【0129】

(3)本実施形態では、フィルター回路として図16に示す構成の2次のローパスフィルターを例に説明したが、本発明はこれに限定されるものではない。本発明に係るSC回路は、種々の構成のフィルター回路に適用することができる。

【符号の説明】

【0130】

10,10a,32…SC積分回路、 20,20a…電荷充電回路、

30…ローパスフィルター、 40…振動片、 42a,42b…駆動電極、

44a,44b,46a,46b…検出電極、 50…センサー回路、

100…駆動回路、 110…電流電圧変換器、 120…AGC回路、

130,218…BPF、 140…GCA、 150…2値化回路、

200…検出回路、 210…交流増幅回路、 212…第1の電流電圧変換器、

214…第2の電流電圧変換器、 216…交流増幅器、 220…同期検波回路、

230…直流増幅器、 400…電子機器、 410…A/D変換回路、

510…クロック生成回路、 520…処理部、 530…メモリー、

540…操作部、 550…表示部、 AMP,AMP0…演算増幅器、

CLK1…第1のクロック、 CLK2…第2のクロック、

Ca1…第1のサンプリング容量、 Ca2…第2のサンプリング容量、

Cb…積分容量、 SW1〜SW7…第1のスイッチ〜第7のスイッチ

【技術分野】

【0001】

本発明は、スイッチトキャパシター回路、フィルター回路、物理量測定装置及び電子機器等に関する。

【背景技術】

【0002】

従来より、角速度等の物理量を測定するセンサー回路は、車両や電子機器等に搭載され、車両運動や手振れ等による振動の検出に用いられている。近年では、このセンサー回路の用途が広まる一方であり、用途によっては、より高精度な検出が可能なものが望まれている。ところが、センサー回路自体が発生する雑音成分が大きい場合、本来検出したい微少な信号が埋もれてしまい、高精度な検出ができなくなる。そのため、センサー回路によってできるだけ微少な信号を検出しようとする場合、センサー回路自体が発生する雑音成分をできるだけ低減することが重要な課題となっている。

【0003】

このようなセンサー回路には、所望の信号伝達関数を有するスイッチトキャパシター(Switched Capacitor:以下、SC)回路が用いられ、SC回路により信号増幅やフィルタリングを行う。このSC回路については、次の図に示す構成を有するものの他に、例えば特許文献1や非特許文献1に開示されている。特許文献1には、スイッチと容量とで構成されるSC回路が開示されている。また、非特許文献1には、SC回路を構成する素子の値の広がりを抑えた2次のスイッチトキャパシターフィルター(Switched Capacitor Filter:SCF)が開示されている。

【0004】

図19に、一般的なSC積分回路の構成例を示す。

SC積分回路は、SC回路を用いた積分回路であり、広義のSC回路である。SC積分回路は、演算増幅器と、サンプリング容量Ca(容量値C1)と、演算増幅器の出力ノードと仮想接地ノードとの間に設けられる積分容量Cb(容量値C2)とを備えている。まず、SC積分回路は、第1のクロックによりオンオフ制御される複数のスイッチと、第2のクロックによりオンオフ制御される複数のスイッチとにより、入力信号に対応した電荷をサンプリング容量Caに充電する。その後、SC積分回路は、サンプリング容量Caに充電した電荷を積分容量Cbに転送することで、電圧増幅やフィルタリングを行う。入力信号をVIN、出力信号をVOUTとすると、図19のSC積分回路の伝達関数H0(z)は、次の式のようになる。

【数1】

【0005】

このようなSC積分回路では、入力信号VINの出力への信号伝達関数(Signal Transfer Function:以下、STF)の他に、スイッチと演算増幅器による雑音の出力への雑音伝達関数(Noise Transfer Function:以下、NTF)が存在する。NTFを改善することにより、SC積分回路の出力雑音成分を低減でき、センサー回路に好適なSC回路を提供できる。

【先行技術文献】

【特許文献】

【0006】

【特許文献1】特開平06−061793号公報

【非特許文献】

【0007】

【非特許文献1】電子情報通信学会技術研究報告CAS89−163//CS89−123//DSP89−62『素子値の広がりを抑えた2次SCF』石川、安斎、藤井

【発明の概要】

【発明が解決しようとする課題】

【0008】

しかしながら、特許文献1、非特許文献1及び図19に示す構成のSC回路の伝達関数は、例えば式(1)に示すように、移動する電荷量のみで決定される。例えば図19において、サンプリング容量Caで充電した電荷を積分容量Cbに転送することにより、STF及びNTFが決定される。そのため、従来のSC回路では、STFを変更することなくNTFを改善することができず、所望の信号伝達関数を維持したまま出力雑音成分のみを低減させることができないという問題があった。

【0009】

本発明は、以上のような技術的課題に鑑みてなされたものである。本発明の幾つかの態様によれば、所望の信号伝達関数で、より一層の出力雑音成分を低減できるSC(スイッチトキャパシター)回路、フィルター回路、物理量測定装置及び電子機器等を提供することができる。

【課題を解決するための手段】

【0010】

(1)本発明の第1の態様は、第1の期間の入力信号に対応した信号を第2の期間に伝搬遅延させるSC回路は、前記第1の期間にて決定される信号伝達関数と、前記第2の期間にて決定される雑音伝達関数とが異なる。

【0011】

本態様によれば、所望の信号伝達関数を維持したまま、雑音伝達関数のみを変更できるようになるので、所望の信号伝達関数で、より一層の出力雑音成分を低減できるSC回路を提供できるようになる。

【0012】

(2)本発明の第2の態様に係るSC回路は、第1の態様において、積分容量と、前記入力信号に対応した電荷を充電する第1の回路とを含み、前記第1の期間において、前記第1の回路に前記電荷を充電し、前記第2の期間において、前記第1の回路に充電された電荷を前記積分容量に転送する。

【0013】

本態様によれば、第1の回路において電荷を充電した後、積分容量に電荷を転送する構成を採用したので、所望の信号伝達関数で、より一層の出力雑音成分を低減できるSC積分回路としてSC回路を提供できるようになる。

【0014】

(3)本発明の第3の態様に係るSC回路は、第2の態様において、演算増幅器を含み、前記積分容量は、前記演算増幅器の出力ノードと前記演算増幅器の仮想接地ノードとの間に設けられる。

【0015】

本態様によれば、演算増幅器からの雑音を考慮しても、所望の信号伝達関数で、より一層の出力雑音成分を低減できるSC積分回路としてSC回路を提供できるようになる。

【0016】

(4)本発明の第4の態様に係るSC回路では、第1の態様乃至第3の態様のいずれかにおいて、前記第1の回路は、複数のサンプリング容量を含み、前記第1の期間から前記第2の期間に遷移するとき、前記複数のサンプリング容量の電気的な接続を切り換える。

【0017】

本態様においては、複数野サンプリング容量の電気的な接続を切り換えることにより、第1の期間にて決定される信号伝達関数と第2の期間にて決定される雑音伝達関数とを異ならせるようにしている。これにより、簡素な構成で、所望の信号伝達関数で、より一層の出力雑音成分を低減できるSC回路を提供できるようになる。

【0018】

(5)本発明の第5の態様に係るSC回路では、第4の態様において、前記第1の回路は、前記第1の期間において前記複数のサンプリング容量を並列に接続し、前記第2の期間において前記複数のサンプリング容量を直列に接続し、前記第1の期間では、各サンプリング容量の一端に前記入力信号が供給され、前記第2の期間では、直列接続された前記複数のサンプリング容量の一端が前記積分容量の一端に電気的に接続される。

【0019】

本態様によれば、第1の期間では複数のサンプリング容量を並列接続して電荷を充電し、第2の期間ではこれらを直列接続するようにしたので、第1期間に現れる雑音は平均効果により、第2期間に現れる雑音はNTFの減衰によって、簡素な構成で、信号伝達関数と雑音伝達関数とを異ならせることができる。

【0020】

(6)本発明の第6の態様に係るSC回路は、第4の態様又は第5の態様において、前記複数のサンプリング容量を構成する各サンプリング容量の容量値は、同一である。

【0021】

本態様によれば、簡素な構成で、所望の信号伝達関数で、より一層の出力雑音成分を低減できるSC回路を提供できるようになる。

【0022】

(7)本発明の第7の態様に係るSC回路では、第4の態様乃至第6の態様にいずれかにおいて、前記第1の回路は、一端に前記入力信号が供給される第1のスイッチと、前記第1のスイッチの他端にその一端が電気的に接続される第1のサンプリング容量と、一端に前記入力信号が供給される第2のスイッチと、前記第2のスイッチの他端にその一端が電気的に接続される第2のサンプリング容量と、前記第1のサンプリング容量の一端と前記第2のサンプリング容量の他端との間に設けられる第3のスイッチと、前記第1のサンプリング容量の他端と接地端との間に設けられる第4のスイッチと、前記第2のサンプリング容量の一端と前記接地端との間に設けられる第5のスイッチと、前記第2のサンプリング容量の他端と前記接地端との間に設けられる第6のスイッチと、前記演算増幅器の仮想接地ノードと前記第1のサンプリング容量の他端との間に設けられる第7のスイッチとを含み、前記第1のスイッチ、前記第2のスイッチ、前記第4のスイッチ及び前記第6のスイッチは、第1のクロックに基づいてオンオフ制御され、前記第3のスイッチ、前記第5のスイッチ及び前記第7のスイッチは、第2のクロックに基づいてオンオフ制御される。

【0023】

本態様によれば、スイッチと容量という簡素な構成で、信号伝達関数と雑音伝達関数とを異ならせ、所望の信号伝達関数で、より一層の出力雑音成分を低減できるSC回路を提供できるようになる。

【0024】

(8)本発明の第8の態様に係るSC回路では、第7の態様において、前記第2のクロックは、前記第1のクロックの位相と逆位相のクロックである。

【0025】

本態様においては、SC回路を構成するスイッチの各々を、互いに逆相の第1のクロック及び第2のクロックのいずれかで動作させるようにしている。これにより、簡素なクロック制御により、上記の効果が得られるSC回路を提供できるようになる。

【0026】

(9)本発明の第9の態様は、フィルター回路が、第1の態様乃至第8の態様のいずれか記載のSC回路を含む。

【0027】

本態様によれば、雑音成分を大幅に削減できるSC回路を採用したので、フィルター性能の優れたフィルター回路を提供できるようになる。

【0028】

(10)本発明の第10の態様は、物理量測定装置が、振動子と、前記振動子と発振ループを形成し、該振動子に駆動振動を励振する駆動回路と、前記振動子に励振される駆動振動及び測定すべき物理量に応じて検出信号を出力する検出回路とを含み、前記検出回路は、前記駆動振動及び前記物理量に応じて前記検出信号を出力する上記のフィルター回路を含む。

【0029】

本態様によれば、これまでに比べてより一層物理量に対応した検出信号を高精度に出力できる物理量測定装置を提供できるようになる。

【0030】

(11)本発明の第11の態様に係る物理量測定装置では、第10の態様において、前記物理量は、角速度である。

【0031】

本態様によれば、より一層角速度に対応した検出信号を高精度に出力できる物理量測定装置を提供できるようになる。

【0032】

(12)本発明の第12の態様は、電子機器が、上記のいずれか記載の物理量測定装置を含む。

【0033】

本態様によれば、物理量に応じてより一層高精度な処理が可能な電子機器を提供できるようになる。

【図面の簡単な説明】

【0034】

【図1】本発明の一実施形態に係るSC積分回路の構成例の回路図。

【図2】本実施形態における第1のクロック及び第2のクロックの説明図。

【図3】図3(A)、図3(B)は電荷充電回路の動作説明図。

【図4】図4(A)、図4(B)は電荷充電回路の動作説明図。

【図5】図5(A)、図5(B)は本実施形態の動作説明図。

【図6】図6(A)、図6(B)は図19のSC積分回路の動作時の構成の概要を示す図。

【図7】図7(A)、図7(B)は図19のSC積分回路における第1のフェーズスイッチの雑音のNTFを算出するための構成の概要を示す図。

【図8】図8(A)、図8(B)は図19のSC積分回路における第2のフェーズスイッチの雑音のNTFを算出するための構成の概要を示す図。

【図9】図19のSC積分回路を構成する演算増幅器が発生する雑音の説明図。

【図10】図10(A)、図10(B)は図1のSC積分回路の動作時の構成の概要を示す図。

【図11】図11(A)、図11(B)は図1のSC積分回路の第1のフェーズスイッチの雑音のNTFを算出するための構成の概要を示す図。

【図12】図12(A)、図12(B)は図1のSC積分回路の第2のフェーズスイッチの雑音のNTFを算出するための構成の概要を示す図。

【図13】図1のSC積分回路を構成する演算増幅器が発生する雑音の説明図。

【図14】サンプリング容量がNである場合のSC積分回路の構成例を示す図。

【図15】出力雑音電力スペクトラムのシミュレーション結果の一例を示す図。

【図16】本実施形態におけるSC積分回路を用いて構成された2次のローパスフィルターの構成例を示す図。

【図17】図16のローパスフィルターが適用されたセンサー回路の構成例を示す図。

【図18】本実施形態における電子機器のハードウェア構成例のブロック図。

【図19】一般的なSC積分回路の構成例を示す図。

【発明を実施するための形態】

【0035】

以下、本発明の実施の形態について図面を用いて詳細に説明する。なお、以下に説明する実施の形態は、特許請求の範囲に記載された本発明の内容を不当に限定するものではない。また以下で説明される構成のすべてが本発明の課題を解決するために必須の構成要件であるとは限らない。

【0036】

以下では、SC回路としてSC積分回路を例に説明するが、本発明に係るSC回路はSC積分回路に限定されるものではない。

【0037】

1. SC回路

図1に、本発明の一実施形態に係るSC積分回路の構成例の回路図を示す。

SC積分回路10は、演算増幅器AMPと、積分容量Cb(容量値C2)と、電荷充電回路(第1の回路)20とを含む。演算増幅器AMPは、公知の演算増幅器であり、演算増幅器AMPの非反転入力端子はアナログ接地電位AGNDに接続され、演算増幅器AMPの反転入力端子が仮想接地ノードとなる。積分容量Cbは、演算増幅器AMPの出力ノードと仮想接地ノードとの間に挿入される。電荷充電回路20は、SC積分回路10の入力端子と演算増幅器AMPの仮想接地ノードとの間に設けられる。演算増幅器AMPの出力ノードが、SC積分回路10の出力端子となる。

【0038】

電荷充電回路20は、複数のサンプリング容量と、複数のスイッチとを含み、電荷充電期間(第1の期間)T1において入力信号VINに対応した電荷を充電し、電荷転送期間(第2の期間)T2において電荷充電期間T1で充電した電荷を積分容量Cbに転送する。電荷充電回路20は、電荷充電期間T1から電荷転送期間T2に遷移するとき、複数のスイッチにより複数のサンプリング容量の電気的な接続を切り換える。これにより、電荷充電回路20は、信号と雑音との間で電荷転送の仕組みを異ならせる。例えば、電荷充電回路20は、電荷充電期間T1において複数のサンプリング容量を並列に接続し、電荷転送期間T2において複数のサンプリング容量を直列に接続する。電荷充電期間T1では、電荷充電回路20の各サンプリング容量の一端に入力信号VINが供給され、電荷転送期間T2では、直列接続された複数のサンプリング容量の一端を積分容量Cbの一端に電気的に接続する。こうすることで、電荷充電期間T1における入力信号VINを伝搬遅延させるSC積分回路10のSTF(信号伝達関数)とNTF(雑音伝達関数)とを異ならせることができる。これにより、所望のSTFを変更することなくNTFのみを小さくして雑音の増幅度を小さくすることができるようになる。

【0039】

以下、説明の便宜上、サンプリング容量の個数Nが「2」である例について説明するが、電荷充電回路20は、サンプリング容量の個数が3以上であってもよい。Nが「2」の場合、電荷充電回路20は、サンプリング容量Ca1(第1のサンプリング容量)、Ca2(第2のサンプリング容量)と、これらを並列接続又は直列接続に切り換えるための第1のスイッチSW1〜第7のスイッチSW7とを含む。第1のスイッチSW1〜第7のスイッチSW7は、それぞれ2相クロックのいずれか一方によりオンオフ制御される。図1では、各スイッチには、「1」と表記されるスイッチと、「2」と表記されるスイッチの2種類がある。「1」と表記されるスイッチは、第1のクロックCLK1で動作するスイッチ(第1のフェーズスイッチ)である。「2」と表記されるスイッチは、第2のクロックCLK2で動作するスイッチ(第2のフェーズスイッチ)である。

【0040】

第1のスイッチSW1の一端に、入力信号VINが供給される。サンプリング容量Ca1の一端は、第1のスイッチSW1の他端に電気的に接続される。第2のスイッチSW2の一端に、入力信号VINが供給される。サンプリング容量Ca2の一端は、第2のスイッチSW2の他端に電気的に接続される。第3のスイッチSW3は、サンプリング容量Ca1の一端とサンプリング容量Ca2の他端との間に設けられる。第4のスイッチSW4は、サンプリング容量Ca1の他端と接地端(アナログ接地電位AGND)との間に設けられる。第5のスイッチSW5は、サンプリング容量Ca2の一端と接地端との間に設けられる。第6のスイッチSW6は、サンプリング容量Ca2の他端と接地端との間に設けられる。第7のスイッチSW7は、演算増幅器AMPの仮想接地ノードとサンプリング容量Ca1の他端との間に設けられる。

【0041】

第1のスイッチSW1、第2のスイッチSW2、第4のスイッチSW4及び第6のスイッチSW6は、第1のクロックCLK1に基づいてオンオフ制御される。第3のスイッチSW3、第5のスイッチSW5及び第7のスイッチSW7は、第2のクロックCLK2に基づいてオンオフ制御される。

【0042】

図2に、本実施形態における第1のクロック及び第2のクロックの説明図を示す。

図1において「1」と表記される第1のフェーズスイッチは、第1のクロックCLK1がHレベルのときオン(導通状態)となり、第1のクロックCLK1がLレベルのときオフ(非導通状態)となる。「2」と表記される第2のフェーズスイッチは、第2のクロックCLK2がHレベルのときオン(導通状態)となり、第2のクロックCLK2がLレベルのときオフ(非導通状態)となる。

【0043】

第2のクロックCLK2は、第1のクロックCLK1とは逆相のクロックである。第1のクロックCLK1によりスイッチ制御されるスイッチと第2のクロックCLK2によりスイッチ制御されるスイッチとが同時にオンしないように、各クロックが変化するようになっている。

【0044】

このような2相のクロックによるスイッチ制御により、サンプリング容量Ca1、Ca2の接続関係を切り換えることで、信号と雑音との間で電荷転送の仕組みを異ならせる。ここで、このような電荷充電回路20における電荷転送の概要について説明する。

【0045】

図3(A)、図3(B)、図4(A)、図4(B)に、電荷充電回路20の動作説明図を示す。図3(A)は、電荷充電期間T1における電荷充電回路20の動作説明図を示す。図3(B)は、電荷転送期間T2における電荷充電回路20の動作説明図を示す。図4(A)は、N(Nは2以上の整数)個のサンプリング容量による電荷充電期間T1における電荷充電回路20の動作説明図を示す。図4(B)は、N個のサンプリング容量による電荷転送期間T2における電荷充電回路20の動作説明図を示す。

【0046】

電荷充電期間T1では、電荷充電回路20を構成する複数のサンプリング容量は並列に接続される。このとき、図3(A)に示すように、サンプリング容量Ca1には電圧V1が印加されて電荷QA、サンプリング容量Ca2には電圧V2が印加されて電荷QBが蓄積される。ここで、サンプリング容量Ca1、Ca2の容量値が同一(Ca1=Ca2=C)である場合、各サンプリング容量に電圧V1、V2がサンプリングされた後、電荷転送期間T2においてサンプリング容量が直列接続されたとき、次式で表される電荷Qが積分容量Cbに転送される。このとき、下の式において、V1=V2=VINとすると、電荷充電回路20で転送される電荷量は1つのサンプリング容量で転送される電荷量と等しくなる。

【数2】

【0047】

即ち、図4(A)のように、それぞれが同じ容量値のN個のサンプリング容量を並列に接続した場合に転送される電荷Qは、次式のように表される。このとき、それぞれの容量値が等しいN個のサンプリング容量(容量値C)を並列接続して充電(サンプリング)した電荷を直列接続して積分容量に転送する場合、1つのサンプリング容量で同じ電荷量を転送したことに相当する。これは、相関性がある電圧信号に対応した電荷を充電する場合に成り立つ。

【数3】

【0048】

これに対して、図3(A)において、雑音信号のような無相関の信号に対応した電荷を充電する場合、V1=V2=VNとすると、次式で表されるように、転送される電荷量に平均効果が現れる。

【数4】

【0049】

従って、無相関の信号について、図4(A)、図4(B)のように、それぞれが同じ容量値のN個のサンプリング容量(容量値C)を並列に接続した場合に転送される電荷Qは、次式のように表される。

【数5】

【0050】

ここで、式(3)及び式(5)に示すように、複数のサンプリング容量を並列接続して充電した電荷を直列接続して転送することで、信号の相関種類に応じて伝達関数を異ならせることができる。

【0051】

図5(A)、図5(B)に、本実施形態の動作説明図を示す。図5(A)は、図19の構成におけるSTF及びNTFの説明図を示す。図5(B)は、図1に構成におけるSTF及びNTFの説明図を示す。

【0052】

図19の構成では、図5(A)に示すように、電荷充電期間T1においてSTF及びNTFが決定される。そのため、STFを変更することなくNTFを改善することができない。これに対して、本実施形態の構成は、図5(B)に示すように、電荷充電期間T1においてSTFが決定され、電荷転送期間T2においてNTFが決定される。即ち、所望の信号に対してはSTFが変更されず、且つ雑音に対しては平均効果及びNTFの減衰が現れるように構成が切り換えられる。

【0053】

これにより、電荷充電期間T1において決定されるSTFを維持したまま、電荷転送期間T2において決定されるNTFのみを小さくして、雑音信号の伝達量を削減できる。このように、電荷充電期間T1におけるSTFと電荷転送期間T2におけるNTFとが異なるSC積分回路により、所望の信号伝達関数で、より一層の出力雑音成分を低減できるようになる。

【0054】

2. SC積分回路の雑音

以下、図19のSC積分回路の雑音を基準に、本実施形態におけるSC積分回路10の雑音について説明する。

【0055】

2.1 一般的なSC積分回路

まず、図19に示す一般的なSC積分回路のSTFを説明した後、一般的なSC積分回路の雑音について説明する。

【0056】

2.1.1 STF

図6(A)、図6(B)に、図19に示す一般的なSC積分回路の動作時の構成の概要を示す。図6(A)は、電荷充電期間T1におけるSC積分回路の構成の概要を示す。図6(B)は、電荷転送期間T2におけるSC積分回路の構成の概要を示す。図6(A)、図6(B)において、図19と同様の部分には同一符号を付し、適宜説明を省略する。

【0057】

積分容量Cbに電荷が転送されるタイミングを時刻nとすると、時刻(n−1)では、第1のクロックCLK1により、サンプリング容量Caに電荷が充電される。図6(A)に示すように、入力電圧VINが入力される側のサンプリング容量Caの電荷量を+Qa、演算増幅器AMP0の仮想接地ノード側の積分容量Cbの電荷量を+Qbとすると、次式が成り立つ。

【数6】

【0058】

次に、時刻nでは、第2のクロックCLK2により図6(B)に示す構成となり、サンプリング容量Caに充電された電荷が積分容量Cbに転送され、次式のように表される。

【数7】

【0059】

ここで、電荷保存の法則により、次式が成立する。

【数8】

【0060】

式(8)に式(6)及び式(7)を代入して求められる図19のSC積分回路のSTFであるH0(z)は、既出の式(1)のようになる。

【0061】

2.1.2 一般的なSC積分回路の雑音

SC積分回路の雑音は、SC積分回路を構成するスイッチ(フェーズスイッチ)が発生する雑音と、演算増幅器が発生する雑音とに区別することができる。

【0062】

2.1.2.1 スイッチが発生する雑音

各フェーズスイッチがオン状態のとき、スイッチのオン抵抗による白色雑音が発生する。この種の雑音スペクトラムは、スイッチのオン抵抗RONと容量Ca(容量値C1)とによる1次の周波数特性を有し、雑音電力は(k・T)/C1で表すことができる。ここで、kはボルツマン定数、Tは絶対温度である。即ち、雑音電力は、容量Caのみによって決まり、容量Caに接続されるスイッチの数及びオン抵抗RONには依存しない。このような各フェーズスイッチが発生する雑音のNTFは、次のように求められる。

【0063】

図7(A)、図7(B)に、図19のSC積分回路における第1のフェーズスイッチの雑音のNTFを算出するための構成の概要を示す。図7(A)は、電荷充電期間T1における図19のSC積分回路の構成の概要を示す。図7(B)は、電荷転送期間T2における図19のSC積分回路の構成の概要を示す。図7(A)、図7(B)において、サンプリング容量Caのうち入力信号VINの供給側の第1のフェーズスイッチを雑音成分Vn1の雑音源であるものとし、図19と同様の部分には同一符号を付し、適宜説明を省略する。

【0064】

図6(A)、図6(B)と同様に、積分容量Cbに電荷が転送されるタイミングを時刻nとすると、時刻(n−1)では、次式が成り立つ。

【数9】

【0065】

また、時刻nでは、図7(B)に示す構成となり、サンプリング容量Caに充電された電荷が積分容量Cbに転送され、次式のように表される。

【数10】

【0066】

ここで、電荷保存の法則により、式(8)が成立するので、式(8)に式(9)及び式(10)を代入して求められる図19のSC積分回路の第1のフェーズスイッチの雑音のNTFであるHn1(z)は、次式のようになる。

【数11】

【0067】

図8(A)、図8(B)に、図19のSC積分回路における第2のフェーズスイッチの雑音のNTFを算出するための構成の概要を示す。図8(A)は、電荷充電期間T1における図19のSC積分回路の構成の概要を示す。図8(B)は、電荷転送期間T2における図19のSC積分回路の構成の概要を示す。図8(A)、図8(B)において、サンプリング容量Caのうち入力信号VINの供給側の第2のフェーズスイッチを雑音成分Vn2の雑音源であるものとし、図19と同様の部分には同一符号を付し、適宜説明を省略する。

【0068】

図7(A)、図7(B)と同様に、積分容量Cbに電荷が転送されるタイミングを時刻nとすると、時刻(n−1)では、次式が成り立つ。

【数12】

【0069】

次に、時刻nでは、図8(B)に示す構成となり、次式のように表される。

【数13】

【0070】

ここで、電荷保存の法則により、式(8)が成立するので、式(8)に式(12)及び式(13)を代入して求められる図19のSC積分回路の第2のフェーズスイッチの雑音のNTFであるHn2(z)は、次式のようになる。

【数14】

【0071】

従って、図19のSC積分回路においてフェーズスイッチから出力に現れる出力雑音電力スペクトラムVOsw2は、次のように表すことができる。なお、以下では、Vns2=(k・T)/C1・fs)であり、Vns2はスイッチの雑音電力である。fsはサンプリング周波数に相当する第1のクロックCLK1又は第2のクロックCLK2のクロック周波数であり、サンプリングによる雑音スペクトラムの折り返しを表している。

【数15】

【0072】

第1のフェーズスイッチを構成する各スイッチ及び第2のフェーズスイッチを構成する各スイッチが同一構造のスイッチであるものとする。このとき、式(11)及び式(14)より各雑音成分のNTFは同じ振幅特性を有しているため、|Hn1(z)|2=|Hn2(z)|2であり、以下の式が成り立つ。なお、以下では、|Hn(z)|2=|Hn1(z)|2=|Hn2(z)|2とし、Hn(z)はスイッチの雑音のNTFを表す。

【数16】

【0073】

2.1.2.2 演算増幅器が発生する雑音

図19に示すSC積分回路において、第2のフェーズスイッチがオンするたびに、演算増幅器AMP0の雑音電圧に比例する電荷がサンプリング容量Caに充電される。そして、この電荷は積分容量Cbに転送され、結果として演算増幅器AMP0の雑音も積分され、演算増幅器AMP0からの雑音は、各フェーズスイッチの雑音と同様に、ある伝達関数Hnop(z)を有しながら出力に反映されることになる。

【0074】

図9に、図19のSC積分回路を構成する演算増幅器AMP0が発生する雑音の説明図を示す。図9において、演算増幅器AMP0の非反転入力端子に雑音成分Vnopの雑音源が設けられているものとし、図19と同様の部分には同一符号を付し、適宜説明を省略する。

【0075】

ここで、Vnop2は演算増幅器からの雑音電力スペクトラムであり、NTFはサンプリング容量Ca及び積分容量Cbによって決まるため|Hnop(z)|2=|Hn(z)|2と考えることができる。よって演算増幅器からの出力雑音電力スペクトラムVOop2は、次式のように表すことができる。

【数17】

【0076】

2.1.2.3 全体の出力雑音電力スペクトラム

式(16)及び式(17)より、図19に示す一般的なSC積分回路全体の出力雑音電力スペクトラムVO_tot12は、次のように表される。

【数18】

【0077】

2.2 本実施形態のSC積分回路

次に、これまで求めた図19のSC積分回路のSTF、NTF、出力雑音電力スペクトラムを基準に、本実施形態におけるSC積分回路10について説明する。以下では、SC積分回路10を構成する複数のサンプリング容量の容量値は同一であるものとして説明するが、NTFの改善前後においてSTFが厳密に同一でなくてもよい場合には、複数のサンプリング容量の容量値は同一でなくてもよい。この場合でも、ほぼ所望のSTFでNTFを改善することができる効果が得られる。

【0078】

2.2.1 STF

図10(A)、図10(B)に、図1のSC積分回路10の動作時の構成の概要を示す。図10(A)は、電荷充電期間T1におけるSC積分回路10の構成の概要を示す。図10(B)は、電荷転送期間T2におけるSC積分回路10の構成の概要を示す。図10(A)、図10(B)において、図1と同様の部分には同一符号を付し、適宜説明を省略する。

【0079】

積分容量Cbに電荷が転送されるタイミングを時刻nとすると、時刻(n−1)では、第1のクロックCLK1により、サンプリング容量Ca1、Ca2に電荷が充電される。図10(A)に示すように、入力電圧VINが入力される側のサンプリング容量Ca1、Ca2の電荷量を+Q1、+Q2とすると、次式が成り立つ。なお、積分容量Cbについては、図10(A)に示すように演算増幅器AMPの仮想接地ノード側の積分容量Cbの電荷量を+Q3としている。

【数19】

【0080】

次に、時刻nでは、第2のクロックCLK2により図10(B)に示す構成となり、サンプリング容量Ca1及びサンプリング容量Ca2は直列に接続され、式(2)に示す電荷が積分容量Cbに転送され、次式のように表される。

【数20】

【0081】

ここで、演算増幅器の仮想接地端子における電荷保存の法則より、次式が成立する。

【数21】

【0082】

式(21)に式(19)及び式(20)を代入して求められるSC積分回路10のSTFであるH(z)は、次式のようになり、図19のSC積分回路のSTFと同様である。

【数22】

【0083】

2.2.2 本実施形態のSC積分回路の雑音

本実施形態におけるSC積分回路においても、SC積分回路の雑音は、SC積分回路を構成するスイッチ(フェーズスイッチ)が発生する雑音と、演算増幅器が発生する雑音とに区別することができる。

【0084】

2.2.2.1 スイッチが発生する雑音

図11(A)、図11(B)に、図1のSC積分回路10の第1のフェーズスイッチの雑音のNTFを算出するための構成の概要を示す。図11(A)は、電荷充電期間T1におけるSC積分回路10の構成の概要を示す。図11(B)は、電荷転送期間T2におけるSC積分回路10の構成の概要を示す。図11(A)、図11(B)において、第1のスイッチSW1を雑音成分Vn1の雑音源であるものとし、図1と同様の部分には同一符号を付し、適宜説明を省略する。

【0085】

SC積分回路10の第1のフェーズスイッチの雑音のNTFは、上記と同様に求めることができるが、次のように導出することもできる。第1のフェーズスイッチがオンすると、図11(A)に示すように、サンプリング容量Ca1、Ca2には、それぞれ(k・T)/C1の雑音電力に対応する電荷が蓄積される。電荷としてサンプリング容量Ca1、Ca2に蓄積される雑音の伝達関数を求めるには、サンプリング容量Ca1、Ca2のどちらかのサンプリング容量に蓄えられる電荷の伝搬だけを考えればよい。ここで、電荷充電期間T1において、サンプリング容量Ca1には雑音電荷Qnが蓄積され、サンプリング容量Ca2には電荷が蓄積されない。第2のフェーズスイッチがオンすると、図11(B)に示すように、サンプリング容量Ca1に蓄積された電荷が積分容量Cbに転送されるが、電荷量存の法則により、転送される電荷量はQn/2である。従って、図11(A)に示す第1のスイッチSW1の雑音のNTFは、次式のようになり、図19のSC積分回路のNTF(式(11)参照)の半分になる。

【数23】

【0086】

ここで、第2のスイッチSW2の雑音のNTFも式(23)と同様である。雑音は無相関であることを考慮して、第1のフェーズスイッチから出力に現れる雑音電力は、第1のスイッチSW1からの出力雑音電力と第2のスイッチSW2からの雑音電力とを加算したものとなる。従って、第1のフェーズスイッチからの出力雑音電力スペクトラムVpno12は、次のようになる。

【数24】

【0087】

図12(A)、図12(B)に、図1のSC積分回路10の第2のフェーズスイッチの雑音のNTFを算出するための構成の概要を示す。図12(A)は、電荷充電期間T1におけるSC積分回路10の構成の概要を示す。図12(B)は、電荷転送期間T2におけるSC積分回路10の構成の概要を示す。図12(A)、図12(B)において、第5のスイッチSW5を雑音成分Vn2の雑音源であるものとし、図1と同様の部分には同一符号を付し、適宜説明を省略する。

【0088】

第2のフェーズスイッチがオンすると、サンプリング容量Ca1、Ca2が直列に接続されるため、第2のフェーズスイッチの雑音電力は(2・k・T/C1)になる。これは、容量が小さく見える分だけ雑音帯域が広がることに起因する。即ち、サンプリング容量の容量値が半分になるため、第2のフェーズスイッチの雑音のNTFは、次式のように表され、図19のSC積分回路のNTF(式(14)参照)の半分になる。

【数25】

【0089】

従って、第2のフェーズスイッチからの出力雑音電力スペクトラムVpno22は、次のようになる。

【数26】

【0090】

以上より、SC積分回路10において出力に現れる出力雑音電力スペクトラムVOswp2は、式(25)と式(26)とを加算することにより求められる。

【数27】

【0091】

式(16)と式(27)とを比較すると、本実施形態におけるSC積分回路10において、各フェーズスイッチの雑音のNTFを、一般的なSC積分回路のNTFより小さくすることができる。その上、雑音は無相関の信号であるため、各フェーズスイッチからの出力雑音電力スペクトラムも、一般的なSC積分回路の各フェーズスイッチからの出力雑音電力スペクトラムよりも小さくなる。そして、全スイッチからの出力雑音電力スペクトラムも、一般的なSC積分回路よりも小さくなる。

【0092】

2.2.2.2 演算増幅器が発生する雑音

図13に、図1のSC積分回路10を構成する演算増幅器AMPが発生する雑音の説明図を示す。図13において、演算増幅器AMPの非反転入力端子に雑音成分Vnopの雑音源が設けられているものとし、図1と同様の部分には同一符号を付し、適宜説明を省略する。

【0093】

SC積分回路10において、第2のフェーズスイッチがオンするたびに、演算増幅器AMPからの雑音が積分される。このとき、サンプリング容量の容量値はC1/2に見えるため、演算増幅器AMPからの雑音の伝達関数は、Hnop(z)/2となり、演算増幅器AMP0からの雑音の伝達関数Hnop(z)の半分となる。従って、演算増幅器AMPの雑音による出力雑音電力スペクトラムVOopp2は、次式のように表すことができる。

【数28】

【0094】

2.2.2.3 全体の出力雑音電力スペクトラム

式(27)及び式(28)より、本実施形態のSC積分回路10全体の出力雑音電力スペクトラムVO_tot22は、次のように表される。

【数29】

【0095】

以上説明したように、本実施形態では、並列に接続されたサンプリング容量に充電した電荷を、各サンプリング容量を直列に接続して積分容量に転送する構成としている。これにより、雑音のような無相関の信号に対する平均効果により、STFを変更することなく、NTFを小さくすることができるようになる。また、式(17)と式(29)とを比較すると、図1のSC積分回路10の素子数が図19のSC積分回路の素子数より増加するが、本実施形態のSC積分回路10における出力雑音は、図19のSC積分回路における出力雑音より小さいことは明らかである。

【0096】

図1では、サンプリング容量が2つである例について説明したが、サンプリング容量が3つ以上であっても同様である。

【0097】

図14に、サンプリング容量がNである場合のSC積分回路10aの構成例を示す。図14において、図1と同様の部分には同一符号を付し、適宜説明を省略する。

【0098】

SC積分回路10aは、図1の電荷充電回路20に代えて電荷充電回路20aを備えている。電荷充電回路20aは、複数のスイッチと、N個のサンプリング容量Ca1〜CaNとを含む。電荷充電回路20aは、これらのスイッチにより、電荷充電期間T1においてサンプリング容量Ca1〜CaNを並列に接続し、電荷転送期間T2においてサンプリング容量Ca1〜CaNを直列に接続する。電荷充電期間T1では、各サンプリング容量には入力信号VINが印加される。電荷転送期間T2では、直列接続されたサンプリング容量Ca1〜CaNのうち、サンプリング容量CaNの一端がアナログ接地電位AGNDに接続され、サンプリング容量Ca1の一端が演算増幅器AMPの仮想接地ノードに電気的に接続される。

【0099】

図14に示すように、サンプリング容量の個数がNのときのSC積分回路10aの出力雑音電力スペクトラムVO_tot32は、次にように表すことができる。

【数30】

【0100】

式(30)に示すように、Nが増えるほど、出力雑音電力スペクトラムVO_tot32が小さくなる。その一方、Nを増やすことは、サンプリング容量が増えることを意味し、SC積分回路10aの面積増大を招く。そこで、図19に示すSC積分回路の総容量値と、図14に示すSC積分回路10aの総容量値とが等しいという条件下で、両者の出力雑音スペクトラムを比較する。

【0101】

図19に示すSC積分回路の総容量値Ctcは、実数Mを用いて次のように表すことができる。下の式において、α=C1/C2であり、式(1)より、容量値をM倍にしても信号伝達関数は変化しない。

【数31】

【0102】

式(31)において、スイッチの雑音帯域は1/M倍になるため、この場合の出力雑音電力スペクトラムVO_tot42は、次のようになる。

【数32】

【0103】

これに対して、図14のSC積分回路10aの総容量値Ctpは、次のように表すことができる。なお、下の式において、N=1のときは図19のSC積分回路と同様の構成となり、Nが2以上であることが条件となる。

【数33】

【0104】

式(31)と式(33)とが等しいとき、Mは次のように表すことができる。

【数34】

【0105】

ここで、式(30)と式(32)とを比較したときに演算増幅器の雑音に着目すると、任意のN(N≧2)に対してSC積分回路10aの出力雑音電力スペクトラムはSC積分回路10の出力雑音電力スペクトラムよりも小さくなる。一方、式(30)と式(32)とを比較したときにスイッチの雑音に着目すると、N>Mのとき、SC積分回路10aの出力雑音電力スペクトラムが小さくなる。従って、式(34)をN>Mに代入すると、N>1となる。条件としてNが2以上である必要があるため、必ずN>1が成立する。

【0106】

以上より、図19に示すSC積分回路の総容量値と、図14に示すSC積分回路10aの総容量値とが等しい場合、SC積分回路10aの方が必ず出力雑音電力スペクトラムが小さくなる。

【0107】

図15に、出力雑音電力スペクトラムのシミュレーション結果の一例を示す。縦軸に出力雑音電力スペクトラムを表し、横軸にαを表す。図15は、N=2のときのシミュレーション結果を表す。

【0108】

このように、αを0.1から10まで変化させても、SC積分回路10aの出力雑音電力スペクトラムの方が必ず小さくなることを表している。

【0109】

以上説明したように、本実施形態によれば、STFとNTFとを分離できる構成を採用したので、所望の信号伝達関数で、より一層の出力雑音成分を低減できるSC回路を提供できるようになる。

【0110】

3. フィルター回路

本実施形態におけるSC積分回路10は、フィルター回路として例えば次のような2次のローパスフィルター(Low Pass Filter:以下、適宜LPFと略す)に適用することができる。

【0111】

図16に、本実施形態におけるSC積分回路を用いて構成された2次のローパスフィルターの構成例を示す。図16において、スイッチの表記は図1と同様であり、一般的に良く知られているFleisher−Lakerのローパスフィルターで表記される容量と対応する容量には同一の符号を付している。

【0112】

このローパスフィルター30では、後段側に図1のSC積分回路10と同様の構成を有するSC積分回路32が適用される。このSC積分回路32は、入力側に設けられたローパスフィルターとは互いに逆の位相で動作するため、図1のSC積分回路10を構成するフェーズスイッチの表記とSC積分回路32を構成するフェーズスイッチの表記とが逆になっている。このローパスフィルター30によれば、所望の信号伝達関数で動作し、且つ従来と比べて雑音成分を大幅に低減できるようになる。

【0113】

なお、図16において、ローパスフィルター30はSC積分回路10に代えてSC積分回路10aが適用されていてもよい。

【0114】

4. 物理量測定装置

図16のローパスフィルター30は、センサー回路に適用することにより、高精度なセンシングを行うことができるようになる。

【0115】

図17に、図16のローパスフィルターが適用されたセンサー回路の構成例を示す。なお、この回路構成は一例であり、例えば回路の細部の構成が変形される場合もあり得る。

【0116】

センサー回路50は、角速度を測定対象の物理量とする物理量測定装置である。センサー回路50は、駆動回路(駆動装置)100と、検出回路(検出装置)200とを含む。このセンサー回路50は、圧電材料で形成され、駆動振動片及び検出振動片を有する振動片(振動子)40を含む。

【0117】

駆動回路100は、駆動振動片に設けられた駆動電極42a、42bを介して駆動振動片を発振ループ内に設け、駆動振動片(広義には振動子)を励振させる。駆動回路100は、電流電圧変換器110、オートゲインコントロール(Auto Gain Control:以下、AGCと略す)回路120、帯域通過フィルター(Band Pass Filter:以下、BPFと略す)130を含む。更に、駆動回路100は、ゲインコントロールアンプ(Gain Control Amplifier:以下、GCAと略す)140、2値化回路150を含む。

【0118】

駆動振動片の駆動電極42aは、電流電圧変換器110の入力に電気的に接続され、電流電圧変換器110の出力は、AGC回路120及びBPF130に入力される。BPF130は、発振ループ内の発振信号の位相調整回路として機能し、BPF130の出力は、GCA140及び2値化回路150に入力される。AGC回路120は、電流電圧変換器110の出力に基づいて、GCA140のゲインを制御する。GCA140の出力は、駆動振動片の駆動電極42bに電気的に接続される。2値化回路150は、発振ループ内の発振信号を2値化し、参照信号として検出回路200に出力する。なお、図17では、駆動回路100の内部に振動片40の駆動振動片を設けるものとして説明したが、駆動回路100の外部に振動片40の駆動振動片が設けられていてもよい。

【0119】

検出回路200は、交流増幅回路210と、同期検波回路220と、直流増幅器230と、ローパスフィルター30とを含む。交流増幅回路210は、第1の電流電圧変換器212と、第2の電流電圧変換器214と、交流増幅器216と、BPF218とを含む。

【0120】

このような駆動回路100では、上記の構成の発振ループ内のゲインが「1」より大きい状態で発振スタートする。この時点では、駆動振動片への入力は雑音のみであるが、この雑音は、目的とする駆動振動の固有共振周波数を含む幅広い周波数の波動を含む。振動片40の駆動振動片の周波数フィルター作用によって、目的とする固有共振周波数の波動を多く含む信号が出力され、この信号が電流電圧変換器110において電圧値に変換される。AGC回路120は、この電圧値に基づいてGCA140のゲインを制御することで発振ループ内の発振振幅を制御する。発振ループ内でこうした操作が繰り返されることにより、目的とする固有共振周波数の信号の割合が高くなる。そして、GCA140のゲイン制御によって、次第に発振ループを信号が1周する間の利得(ループゲイン)が「1」となり、この状態で駆動振動片が安定発振する。

【0121】

駆動振動片を励振させて安定発振状態になり、振動片40を所与の方向に回転させると、コリオリ力が振動片40に作用し、検出振動片が屈曲振動する。検出振動片には検出電極44a、44b、46a、46bが設けられる。検出電極44b、46bにはアナログ接地電位が供給され、検出電極44a、46aは、交流増幅回路210の第1の電流電圧変換器212及び第2の電流電圧変換器214に接続される。検出回路200は、検出電極44a、46aからの互いに極性が異なる検出信号を交流増幅した後、駆動回路100からの参照信号を用いて同期検波して、ローパスフィルター30で検出信号OUTを出力する。

【0122】

5. 電子機器

上記のセンサー回路は、次のような電子機器に搭載することができる。このような電子機器によれば、所望の信号伝達関数で動作し、且つ高精度なセンシングを容易に実現できるようになる。

【0123】

図18に、本実施形態における電子機器のハードウェア構成例のブロック図を示す。

【0124】

電子機器400は、センサー回路50と、A/D変換回路410と、クロック生成回路510と、中央演算処理装置等の処理部520と、メモリー530と、操作部540と、表示部550とを有する。電子機器400を構成する各部は、バス(BUS)によって相互に接続されている。なお、A/D変換回路410は、処理部520に内蔵されていてもよい。

【0125】

例えば、処理部520は、メモリー530から読み込んだプログラムに従って処理を実行し、センサー回路50で検出された検出信号の振幅又は感度に応じてA/D変換回路410で変換されたディジタル値を用いて積分を行う。こうすることで、角速度及び回転角度を算出する。そして、処理部520は、算出した角速度又は回転角度に対応した処理を実行し、該処理に対応した表示データを生成し、表示部550に表示させる処理を行う。

【0126】

以上、本発明に係るSC回路、フィルター回路、物理量測定装置及び電子機器を上記の実施形態に基づいて説明したが、本発明は上記の実施形態に限定されるものではない。本発明は、その要旨を逸脱しない範囲において種々の態様において実施することが可能であり、例えば次のような変形も可能である。

【0127】

(1)本実施形態では、SC回路として図1又は図14の構成のSC積分回路を例に説明したが、本発明はこれらに限定されるものではない。スイッチと容量とを用いて電荷を充電して転送する原理を有するSC回路に限らず、信号を伝搬遅延させるSC回路に適用できる。

【0128】

(2)本実施形態では、平均効果によりNTFを小さくすることでSTFとNTFとを異ならせるものとして説明したが、本発明はこれに限定されるものではない。

【0129】

(3)本実施形態では、フィルター回路として図16に示す構成の2次のローパスフィルターを例に説明したが、本発明はこれに限定されるものではない。本発明に係るSC回路は、種々の構成のフィルター回路に適用することができる。

【符号の説明】

【0130】

10,10a,32…SC積分回路、 20,20a…電荷充電回路、

30…ローパスフィルター、 40…振動片、 42a,42b…駆動電極、

44a,44b,46a,46b…検出電極、 50…センサー回路、

100…駆動回路、 110…電流電圧変換器、 120…AGC回路、

130,218…BPF、 140…GCA、 150…2値化回路、

200…検出回路、 210…交流増幅回路、 212…第1の電流電圧変換器、

214…第2の電流電圧変換器、 216…交流増幅器、 220…同期検波回路、

230…直流増幅器、 400…電子機器、 410…A/D変換回路、

510…クロック生成回路、 520…処理部、 530…メモリー、

540…操作部、 550…表示部、 AMP,AMP0…演算増幅器、

CLK1…第1のクロック、 CLK2…第2のクロック、

Ca1…第1のサンプリング容量、 Ca2…第2のサンプリング容量、

Cb…積分容量、 SW1〜SW7…第1のスイッチ〜第7のスイッチ

【特許請求の範囲】

【請求項1】

第1の期間の入力信号に対応した信号を第2の期間に伝搬遅延させるスイッチトキャパシター回路であって、

前記第1の期間にて決定される信号伝達関数と、前記第2の期間にて決定される雑音伝達関数とが異なることを特徴とするスイッチトキャパシター回路。

【請求項2】

請求項1において、

積分容量と、

前記入力信号に対応した電荷を充電する第1の回路とを含み、

前記第1の期間において、前記第1の回路に前記電荷を充電し、

前記第2の期間において、前記第1の回路に充電された電荷を前記積分容量に転送することを特徴とするスイッチトキャパシター回路。

【請求項3】

請求項2において、

演算増幅器を含み、

前記積分容量は、

前記演算増幅器の出力ノードと前記演算増幅器の仮想接地ノードとの間に設けられることを特徴とするスイッチトキャパシター回路。

【請求項4】

請求項1乃至3のいずれかにおいて、

前記第1の回路は、

複数のサンプリング容量を含み、

前記第1の期間から前記第2の期間に遷移するとき、前記複数のサンプリング容量の電気的な接続を切り換えることを特徴とするスイッチトキャパシター回路。

【請求項5】

請求項4において、

前記第1の回路は、

前記第1の期間において前記複数のサンプリング容量を並列に接続し、前記第2の期間において前記複数のサンプリング容量を直列に接続し、

前記第1の期間では、各サンプリング容量の一端に前記入力信号が供給され、

前記第2の期間では、直列接続された前記複数のサンプリング容量の一端が前記積分容量の一端に電気的に接続されることを特徴とするスイッチトキャパシター回路。

【請求項6】

請求項4又は5において、

前記複数のサンプリング容量を構成する各サンプリング容量の容量値は、同一であることを特徴とするスイッチトキャパシター回路。

【請求項7】

請求項4乃至6のいずれかにおいて、

前記第1の回路は、

一端に前記入力信号が供給される第1のスイッチと、

前記第1のスイッチの他端にその一端が電気的に接続される第1のサンプリング容量と、

一端に前記入力信号が供給される第2のスイッチと、

前記第2のスイッチの他端にその一端が電気的に接続される第2のサンプリング容量と、

前記第1のサンプリング容量の一端と前記第2のサンプリング容量の他端との間に設けられる第3のスイッチと、

前記第1のサンプリング容量の他端と接地端との間に設けられる第4のスイッチと、

前記第2のサンプリング容量の一端と前記接地端との間に設けられる第5のスイッチと、

前記第2のサンプリング容量の他端と前記接地端との間に設けられる第6のスイッチと、

前記演算増幅器の仮想接地ノードと前記第1のサンプリング容量の他端との間に設けられる第7のスイッチとを含み、

前記第1のスイッチ、前記第2のスイッチ、前記第4のスイッチ及び前記第6のスイッチは、第1のクロックに基づいてオンオフ制御され、

前記第3のスイッチ、前記第5のスイッチ及び前記第7のスイッチは、第2のクロックに基づいてオンオフ制御されることを特徴とするスイッチトキャパシター回路。

【請求項8】

請求項7において、

前記第2のクロックは、

前記第1のクロックの位相と逆位相のクロックであることを特徴とするスイッチトキャパシター回路。

【請求項9】

請求項1乃至8のいずれか記載のスイッチトキャパシター回路を含むことを特徴とするフィルター回路。

【請求項10】

振動子と、

前記振動子と発振ループを形成し、該振動子に駆動振動を励振する駆動回路と、

前記振動子に励振される駆動振動及び測定すべき物理量に応じて検出信号を出力する検出回路とを含み、

前記検出回路は、

前記駆動振動及び前記物理量に応じて前記検出信号を出力する請求項9記載のフィルター回路を含むことを特徴とする物理量測定装置。

【請求項11】

請求項10において、

前記物理量は、角速度であることを特徴とする物理量測定装置。

【請求項12】

請求項10又は11記載の物理量測定装置を含むことを特徴とする電子機器。

【請求項1】

第1の期間の入力信号に対応した信号を第2の期間に伝搬遅延させるスイッチトキャパシター回路であって、

前記第1の期間にて決定される信号伝達関数と、前記第2の期間にて決定される雑音伝達関数とが異なることを特徴とするスイッチトキャパシター回路。

【請求項2】

請求項1において、

積分容量と、

前記入力信号に対応した電荷を充電する第1の回路とを含み、

前記第1の期間において、前記第1の回路に前記電荷を充電し、

前記第2の期間において、前記第1の回路に充電された電荷を前記積分容量に転送することを特徴とするスイッチトキャパシター回路。

【請求項3】

請求項2において、

演算増幅器を含み、

前記積分容量は、

前記演算増幅器の出力ノードと前記演算増幅器の仮想接地ノードとの間に設けられることを特徴とするスイッチトキャパシター回路。

【請求項4】

請求項1乃至3のいずれかにおいて、

前記第1の回路は、

複数のサンプリング容量を含み、

前記第1の期間から前記第2の期間に遷移するとき、前記複数のサンプリング容量の電気的な接続を切り換えることを特徴とするスイッチトキャパシター回路。

【請求項5】

請求項4において、

前記第1の回路は、

前記第1の期間において前記複数のサンプリング容量を並列に接続し、前記第2の期間において前記複数のサンプリング容量を直列に接続し、

前記第1の期間では、各サンプリング容量の一端に前記入力信号が供給され、

前記第2の期間では、直列接続された前記複数のサンプリング容量の一端が前記積分容量の一端に電気的に接続されることを特徴とするスイッチトキャパシター回路。

【請求項6】

請求項4又は5において、

前記複数のサンプリング容量を構成する各サンプリング容量の容量値は、同一であることを特徴とするスイッチトキャパシター回路。

【請求項7】

請求項4乃至6のいずれかにおいて、

前記第1の回路は、

一端に前記入力信号が供給される第1のスイッチと、

前記第1のスイッチの他端にその一端が電気的に接続される第1のサンプリング容量と、

一端に前記入力信号が供給される第2のスイッチと、

前記第2のスイッチの他端にその一端が電気的に接続される第2のサンプリング容量と、

前記第1のサンプリング容量の一端と前記第2のサンプリング容量の他端との間に設けられる第3のスイッチと、

前記第1のサンプリング容量の他端と接地端との間に設けられる第4のスイッチと、

前記第2のサンプリング容量の一端と前記接地端との間に設けられる第5のスイッチと、

前記第2のサンプリング容量の他端と前記接地端との間に設けられる第6のスイッチと、

前記演算増幅器の仮想接地ノードと前記第1のサンプリング容量の他端との間に設けられる第7のスイッチとを含み、

前記第1のスイッチ、前記第2のスイッチ、前記第4のスイッチ及び前記第6のスイッチは、第1のクロックに基づいてオンオフ制御され、

前記第3のスイッチ、前記第5のスイッチ及び前記第7のスイッチは、第2のクロックに基づいてオンオフ制御されることを特徴とするスイッチトキャパシター回路。

【請求項8】

請求項7において、

前記第2のクロックは、

前記第1のクロックの位相と逆位相のクロックであることを特徴とするスイッチトキャパシター回路。

【請求項9】

請求項1乃至8のいずれか記載のスイッチトキャパシター回路を含むことを特徴とするフィルター回路。

【請求項10】

振動子と、

前記振動子と発振ループを形成し、該振動子に駆動振動を励振する駆動回路と、

前記振動子に励振される駆動振動及び測定すべき物理量に応じて検出信号を出力する検出回路とを含み、

前記検出回路は、

前記駆動振動及び前記物理量に応じて前記検出信号を出力する請求項9記載のフィルター回路を含むことを特徴とする物理量測定装置。

【請求項11】

請求項10において、

前記物理量は、角速度であることを特徴とする物理量測定装置。

【請求項12】

請求項10又は11記載の物理量測定装置を含むことを特徴とする電子機器。

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【図14】

【図15】

【図16】

【図17】

【図18】

【図19】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【図14】

【図15】

【図16】

【図17】

【図18】

【図19】

【公開番号】特開2012−80382(P2012−80382A)

【公開日】平成24年4月19日(2012.4.19)

【国際特許分類】

【出願番号】特願2010−224591(P2010−224591)

【出願日】平成22年10月4日(2010.10.4)

【出願人】(000002369)セイコーエプソン株式会社 (51,324)

【出願人】(304021417)国立大学法人東京工業大学 (1,821)

【Fターム(参考)】

【公開日】平成24年4月19日(2012.4.19)

【国際特許分類】

【出願日】平成22年10月4日(2010.10.4)

【出願人】(000002369)セイコーエプソン株式会社 (51,324)

【出願人】(304021417)国立大学法人東京工業大学 (1,821)

【Fターム(参考)】

[ Back to top ]