スイッチトキャパシター積分回路、フィルター回路、多出力フィルター回路、物理量測定装置、及び電子機器

【課題】低周波数帯域の雑音の影響をより一層小さくすることができるスイッチトキャパシター積分回路等を提供する。

【解決手段】スイッチトキャパシター積分回路10は、第1の容量と第2の容量とを有する電圧電荷変換回路20と、第1の容量に充電された電荷を積分する電荷積分回路30とを含む。電圧電荷変換回路20は、第1の期間において、第1の容量に充電された電荷を転送すると共に入力信号に対応した電荷を第2の容量に充電し、第2の期間において、第2の容量に充電された電荷の一部を第1の容量に充電すると共に入力信号に対応した電荷を第1の容量に充電する。電荷積分回路30は、第3の期間において、演算増幅器の入力に接続されるオフセットキャンセル容量の他端と第1の容量の一端とを接続し、第4の期間において、オフセットキャンセル容量の他端と接地電位とを接続する。

【解決手段】スイッチトキャパシター積分回路10は、第1の容量と第2の容量とを有する電圧電荷変換回路20と、第1の容量に充電された電荷を積分する電荷積分回路30とを含む。電圧電荷変換回路20は、第1の期間において、第1の容量に充電された電荷を転送すると共に入力信号に対応した電荷を第2の容量に充電し、第2の期間において、第2の容量に充電された電荷の一部を第1の容量に充電すると共に入力信号に対応した電荷を第1の容量に充電する。電荷積分回路30は、第3の期間において、演算増幅器の入力に接続されるオフセットキャンセル容量の他端と第1の容量の一端とを接続し、第4の期間において、オフセットキャンセル容量の他端と接地電位とを接続する。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、スイッチトキャパシター積分回路、フィルター回路、多出力フィルター回路

、物理量測定装置、及び電子機器等に関する。

【背景技術】

【0002】

従来より、角速度等の物理量を測定するセンサー回路(広義には、物理量測定装置)は

、カメラ機器の手振れ補正、ナビゲーションやデッドレコニング等の位置情報検出、及び

モーションアナライザー等の身体運動の検出等に用いられる。このようなセンサー回路に

は、例えば極めて低いカットオフ周波数を有するフィルター回路が内蔵される。例えば特

許文献1〜特許文献3には、スイッチトキャパシター(Switched Capacitor:以下、SC

)回路により構成され、極めて低いカットオフ周波数を有するフィルター回路が開示され

ている。特許文献1〜特許文献3に開示されたフィルター回路によれば、演算増幅器の入

力容量と積分容量の比を大きくすることなく、極めて低いカットオフ周波数のフィルター

回路を高精度に実現することができる。

【0003】

ところで、この種のセンサー回路の用途が広まり、センサー回路には、速い動きや遅い

動きにも対応することが求められている。そのため、センサー回路には、ゲイン及び検出

範囲が異なる複数の検出信号を出力することが望まれる。そこで、特許文献1〜特許文献

3に開示されたフィルター回路を複数用いて、多出力が可能な構成とすることが考えられ

る。ところが、特許文献1〜特許文献3に開示されたフィルター回路を複数用いた場合、

集積化に伴う面積や消費電流の増大、各フィルター回路を構成する演算増幅器のオフセッ

トのずれという問題を招く。

【0004】

また、この種のセンサー回路には、更なる高精度化及び高安定化の観点から、特に低周

波数帯域における雑音低減が求められている。例えば非特許文献1及び非特許文献2には

、雑音を低減することができるSC回路が開示されている。非特許文献1には、いわゆる

相関ダブル・サンプリング(Correlated Double-Sampling:以下、CDS)積分器が開示

されている。非特許文献2には、いわゆるCapacitive-Reset Gain回路が開示されている

。

【先行技術文献】

【特許文献】

【0005】

【特許文献1】特開2009−200618号公報

【特許文献2】特開2010−177734号公報

【特許文献3】特開2010−177791号公報

【非特許文献】

【0006】

【非特許文献1】K.NAGARAJ, T.R.VISWANATHAN,K.SINGHAL, and J.VLACH, "Switched-Capacitor Circuits with ReducedSensitivity to Amplifier Gain", IEEE TRANSACTIONS ON CIRCUITS AND SYSTEMS,VOL.CAS-34, No.5, pp.571-574, May, 1987

【非特許文献2】H.MATSUMOTO, and W.WATANABE, "SPIKE-FREESWITCHED-CAPACITOR CIRCUITS", ELECTRONICS LETTERS, Vol.23, No.8,pp.428-429, 9th April, 1987

【発明の開示】

【発明が解決しようとする課題】

【0007】

しかしながら、特許文献1〜特許文献3に開示されたフィルター回路に、非特許文献1

及び非特許文献2に開示されたSC回路を単純に適用したとしても、低周波数帯域の雑音

の影響を十分に小さくすることができないという問題がある。

【0008】

本発明は、以上のような技術的課題に鑑みてなされたものである。本発明の幾つかの態

様によれば、低周波数帯域の雑音の影響をより一層小さくすることができるスイッチトキ

ャパシター積分回路、フィルター回路、多出力フィルター回路、物理量測定装置、及び電

子機器等を提供することができる。

【課題を解決するための手段】

【0009】

(1)本発明の第1の態様は、スイッチトキャパシター積分回路が、第1の容量と第2

の容量とを有する電圧電荷変換回路と、前記第1の容量に充電された電荷を積分する電荷

積分回路とを含み、前記電圧電荷変換回路は、第1の期間において、前記第1の容量に充

電された電荷を転送すると共に、入力信号に対応した電荷を前記第2の容量に充電し、第

2の期間において、前記第2の容量に充電された電荷の一部を前記第1の容量に充電する

と共に、前記入力信号に対応した電荷を前記第1の容量に充電し、前記電荷積分回路は、

演算増幅器と、一端が前記演算増幅器の第1の入力端子に接続されるオフセットキャンセ

ル容量と、第3の期間において前記オフセットキャンセル容量の他端と前記第1の容量の

一端とを電気的に接続する第1のスイッチと、第4の期間において前記オフセットキャン

セル容量の他端を接地電位に接続する第2のスイッチとを含む。

【0010】

本態様においては、演算増幅器の第1の入力端子にオフセットキャンセル容量を接続し

、第1のスイッチ及び第2のスイッチにより、オフセットキャンセル容量の他端を第1の

容量の一端に接続したり接地電位と電気的に接続したりするようにしている。即ち、電圧

電荷変換回路からの電荷の非転送期間において電気的に遮断し、オフセットキャンセル容

量の他端を接地電位に接続するように構成される。これにより、オフセットキャンセル容

量の他端を、電荷の非転送期間においても積分動作に寄与させることができ、該非転送期

間においてオフセットキャンセル容量に、目的とする電荷を充電させることができるよう

になる。この結果、低周波成分の雑音を確実にキャンセルする構成を実現でき、低周波数

帯域の雑音の影響をより一層小さくすることができるスイッチトキャパシター積分回路を

提供することができるようになる。

【0011】

(2)本発明の第2の態様に係るスイッチトキャパシター積分回路では、第1の態様に

おいて、前記電荷積分回路は、一端が前記演算増幅器の出力端子に接続される積分容量と

、前記第3の期間において前記積分容量の他端と前記第1の入力端子とを電気的に接続す

る第3のスイッチと、前記第4の期間において前記積分容量の他端と前記オフセットキャ

ンセル容量の他端とを電気的に接続する第4のスイッチとを含む。

【0012】

本態様によれば、第3にスイッチ及び第4のスイッチを追加することにより、演算増幅

器及び積分容量を用いた積分動作において、低周波数帯域の雑音の影響をより一層小さく

することができるようになる。

【0013】

(3)本発明の第3の態様に係るスイッチトキャパシター積分回路では、第1の態様又

は第2の態様において、前記第1の期間及び前記第3の期間は、第1のクロックに基づい

て規定される期間であり、前記第2の期間及び前記第4の期間は、前記第1のクロックと

逆相の第2のクロックに基づいて規定される期間である。

【0014】

本態様によれば、2相クロックのいずれかによりオンオフ制御されるスイッチを用いた

スイッチトキャパシター積分回路を提供することができる。これにより、非常に簡素な制

御及び構成により、低周波数帯域の雑音の影響をより一層小さくすることができるスイッ

チトキャパシター積分回路を提供することができるようになる。

【0015】

(4)本発明の第4の態様に係るスイッチトキャパシター積分回路は、第3の態様にお

いて、前記第1の期間において、前記スイッチトキャパシター積分回路の出力として前記

電荷積分回路の出力信号を出力する第5のスイッチを含む。

【0016】

本態様によれば、第2の期間における電荷積分回路の出力信号の伝搬を抑えることがで

きるので、低周波数帯域の雑音の影響を更に小さくすることができるスイッチトキャパシ

ター積分回路を提供することができるようになる。

【0017】

(5)本発明の第5の態様は、フィルター回路が、第1のスイッチトキャパシター積分

回路と、前記第1のスイッチトキャパシター積分回路の前段側又は後段側に接続される第

2のスイッチトキャパシター積分回路と、前記第1のスイッチトキャパシター積分回路及

び前記第2のスイッチトキャパシター積分回路のうち後段側のスイッチトキャパシター積

分回路から前段側のスイッチトキャパシター積分回路の帰還経路に挿入される第1の帰還

容量と、前記第2の期間において初期化され、前記第1の期間において前記第1の帰還容

量と並列に設けられる第2の帰還容量とを含み、前記第1のスイッチキャパシター積分回

路及び前記第2のスイッチトキャパシター積分回路の少なくとも一方は、第3の態様に係

るスイッチトキャパシター積分回路である。

【0018】

本態様によれば、低周波成分の雑音を確実にキャンセルする構成を有するスイッチトキ

ャパシター積分回路を用いて低域通過型フィルターの機能を実現することができる。これ

により、低周波数帯域の雑音の影響をより一層小さくすることができるフィルター回路を

提供することができるようになる。

【0019】

(6)本発明の第6の態様に係るフィルター回路は、第5の態様において、前記第1の

帰還容量を介した帰還経路に挿入され、前記第1の期間において導通し、前記第2の期間

において遮断される第5のスイッチとを含む。

【0020】

本態様においては、第1の期間において、後段側のスイッチトキャパシター積分回路の

出力信号を、第1の帰還容量を介して前段側に帰還させることができる。これにより、低

周波数帯域の雑音の影響を更に小さくすることができるフィルター回路を提供することが

できるようになる。

【0021】

(7)本発明の第7の態様に係るフィルター回路は、第1の態様乃至第4の態様のいず

れか記載のスイッチトキャパシター積分回路を含む。

【0022】

本態様によれば、低周波数帯域の雑音の影響をより一層小さくすることができるフィル

ター回路を提供することができるようになる。

【0023】

(8)本発明の第8の態様は、フィルター回路が、第1のスイッチトキャパシター積分

回路と、相関ダブル・サンプリング積分器を有し、前記第1のスイッチトキャパシター積

分回路の後段側に配置され、第1の期間で電荷を積分するスイッチトキャパシター積分回

路と、前記スイッチトキャパシター積分回路の出力と前記第1のスイッチトキャパシター

積分回路の所与のノードとの間に挿入される帰還容量と、前記第1の期間において、前記

スイッチトキャパシター積分回路の出力と前記帰還容量の一端とを電気的に接続するスイ

ッチとを含む。

【0024】

本態様においては、相関ダブル・サンプリング積分器により低周波成分の雑音をキャン

セルする構成を有するスイッチトキャパシター積分回路を用いて低域通過型フィルターの

機能を実現することができる。また、スイッチにより、雑音成分が小さい出力信号のみを

帰還させることができるので、低周波数帯域の雑音の影響を更に小さくすることができる

ようになる。これにより、低周波数帯域の雑音の影響をより一層小さくすることができる

フィルター回路を提供することができるようになる。

【0025】

(9)本発明の第9の態様は、フィルター回路が、第1のスイッチトキャパシター積分

回路と、相関ダブル・サンプリング積分器を有し、前記第1のスイッチトキャパシター積

分回路の後段側に配置され、第1の期間で電荷を積分するスイッチトキャパシター積分回

路と、前記スイッチトキャパシター積分回路の出力と前記第1のスイッチトキャパシター

積分回路の所与のノードとの間に挿入される帰還容量と、前記第1の期間において、前記

ノードと前記帰還容量の一端とを電気的に接続するスイッチとを含む。

【0026】

本態様においては、相関ダブル・サンプリング積分器により低周波成分の雑音をキャン

セルする構成を有するスイッチトキャパシター積分回路を用いて低域通過型フィルターの

機能を実現することができる。また、スイッチにより、雑音成分が小さい出力信号のみを

帰還させることができるので、低周波数帯域の雑音の影響を更に小さくすることができる

ようになる。これにより、低周波数帯域の雑音の影響をより一層小さくすることができる

フィルター回路を提供することができるようになる。

【0027】

(10)本発明の第10の態様に係るフィルター回路は、第5の態様乃至第9の態様の

いずれか記載のフィルター回路を含む高次のフィルター回路である。

【0028】

本態様によれば、低周波数帯域の雑音の影響をより一層小さくすることができる高次の

フィルター回路を提供することができるようになる。

【0029】

(11)本発明の第11の態様は、多出力フィルター回路が、第5の態様乃至第10の

態様のいずれか記載のフィルター回路と、前記フィルター回路の出力に接続され、前記フ

ィルター回路の出力を減衰させる減衰回路とを含む。

【0030】

本態様によれば、フィルター回路により、低周波数帯域の雑音の影響をより一層小さく

、且つゲインが異なる複数の出力が可能な多出力フィルター回路を提供することができる

ようになる。

【0031】

(12)本発明の第12の態様に係る多出力フィルター回路は、第11の態様において

、前記減衰回路は、演算増幅器と、一端が前記演算増幅器の反転入力端子に電気的に接続

される第1の入力容量と、一端が前記演算増幅器の反転入力端子に電気的に接続される第

1の積分容量と、一端が前記演算増幅器の出力端子に電気的に接続される第2の積分容量

とを含み、前記第1の入力容量は、前記第1の期間において他端が前記フィルター回路の

出力に電気的に接続され、前記第2の期間において他端が接地電位と電気的に接続され、

前記第1の積分容量は、前記第1の期間において他端が接地電位と電気的に接続され、前

記第2の期間において前記演算増幅器の出力端子に電気的に接続され、前記第2の積分容

量は、前記第1の期間において他端が前記反転入力端子に電気的に接続され、前記第2の

期間において他端が接地電位と電気的に接続される。

【0032】

本態様によれば、減衰回路において、演算増幅器からの雑音伝達を抑え、特に低周波数

帯域において雑音の影響をより一層小さくする出力が可能な多出力フィルター回路を提供

することができるようになる。

【0033】

(13)本発明の第13の態様は、物理量測定装置が、振動子と、前記振動子と発振ル

ープを形成し、該振動子に駆動振動を励振する駆動回路と、第11の態様又は第12の態

様に係る多出力フィルター回路を有し、前記振動子に励振される駆動振動及び測定すべき

物理量に応じて第1の検出信号及び第2の検出信号を出力する検出回路とを含み、前記検

出回路は、前記ファイルター回路の出力を前記第1の検出信号として出力し、前記減衰回

路の出力を前記第2の検出信号として出力する。

【0034】

本態様によれば、低周波数帯域の雑音の影響をより一層小さくしながら、ゲイン及び検

出範囲が異なる複数の検出信号を出力する物理量測定装置を提供することができるように

なる。

【0035】

(14)本発明の第14の態様は、電子機器が、第1の態様乃至第4の態様のいずれか

のスイッチトキャパシター積分回路を含む。

【0036】

本態様によれば、低周波数帯域の雑音の影響をより一層小さくするスイッチトキャパシ

ター積分回路が適用された電子機器を提供することができるようになる。

【0037】

(15)本発明の第15の態様は、電子機器が、第13の態様に係る物理量測定装置を

含む。

【0038】

本態様によれば、低周波数帯域の雑音の影響をより一層小さくしながら、ゲイン及び検

出範囲が異なる複数の検出信号の出力に基づいたセンシングが可能な電子機器を提供する

ことができるようになる。

【図面の簡単な説明】

【0039】

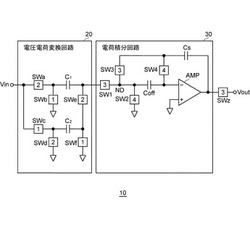

【図1】本発明の一実施形態に係るSC積分回路の構成例の回路図。

【図2】図2(A)は、第1の期間における図1のSC積分回路の動作説明図。図2(B)は、第2の期間における図1のSC積分回路の動作説明図。

【図3】本実施形態の比較例におけるSC積分回路の構成例の回路図。

【図4】図1のSC積分回路10と図3のSC積分回路のNTFの計算結果及びシミュレーション結果の一例を示す図。

【図5】本実施形態のSC積分回路を適用した2次のLPFの構成例の回路図。

【図6】本実施形態の比較例における2次のLPFの構成例の回路図。

【図7】図7(A)は、演算増幅器AMP1からの雑音伝達特性のシミュレーション結果の一例を示す図。図7(B)は、演算増幅器AMP2からの雑音伝達特性のシミュレーション結果の一例を示す図。

【図8】本実施形態における多出力フィルター回路の構成例の回路図。

【図9】図8の減衰回路の構成例の回路図。

【図10】図10(A)は、第1の期間における減衰回路の動作説明図。図10(B)は、第2の期間における減衰回路の動作説明図。

【図11】図11(A)は、演算増幅器AMP1からの雑音伝達特性のシミュレーション結果の一例を示す図。図11(B)は、演算増幅器AMP2からの雑音伝達特性のシミュレーション結果の一例を示す図。図11(C)は、演算増幅器AMP3からの雑音伝達特性のシミュレーション結果の一例を示す図。

【図12】本実施形態の第1の変形例における2次のLPFの構成例の回路図。

【図13】本実施形態の第2の変形例における2次のLPFの構成例の回路図。

【図14】図14(A)は、演算増幅器AMP1からの雑音伝達特性の一例を示す図。図14(B)は、演算増幅器AMP2からの雑音伝達特性の一例を示す図。

【図15】本実施形態の第3の変形例における2次のLPFの構成例の回路図。

【図16】本実施形態の第4の変形例における2次のLPFの構成例の回路図。

【図17】図17(A)は、演算増幅器AMP1からの雑音伝達特性の一例を示す図。図14(B)は、演算増幅器AMP2からの雑音伝達特性の一例を示す図。

【図18】本実施形態の第5の変形例における2次のLPFの構成例の回路図。

【図19】図19(A)は、演算増幅器AMP1からの雑音伝達特性の一例を示す図。図19(B)は、演算増幅器AMP2からの雑音伝達特性の一例を示す図。

【図20】本実施形態の第6の変形例における2次のLPFの構成例の回路図。

【図21】図21(A)は、演算増幅器AMP1からの雑音伝達特性の一例を示す図。図21(B)は、演算増幅器AMP2からの雑音伝達特性の一例を示す図。

【図22】本実施形態又はその変形例におけるLPFが適用された多出力フィルター回路を有するセンサー回路の構成例を示す図。

【図23】本実施形態における電子機器のハードウェア構成例のブロック図。

【発明を実施するための形態】

【0040】

以下、本発明の実施の形態について図面を用いて詳細に説明する。なお、以下に説明す

る実施の形態は、特許請求の範囲に記載された本発明の内容を不当に限定するものではな

い。また以下で説明される構成のすべてが本発明の課題を解決するために必須の構成要件

であるとは限らない。

【0041】

〔SC積分回路〕

図1に、本発明の一実施形態に係るSC積分回路の構成例の回路図を示す。

本実施形態におけるSC積分回路10は、電圧電荷変換回路20と、電荷積分回路30

とを備えている。また、SC積分回路10は、出力スイッチSWzを備えることができる

。電圧電荷変換回路20には、入力信号としての入力電圧Vinが入力され、入力電圧V

inに対応した電荷に変換する。電荷積分回路30は、電圧電荷変換回路20によって変

換された電荷を積分する。出力スイッチSWzは、オンに制御されたとき電荷積分回路3

0の出力信号をSC積分回路10の出力である出力電圧Voutとして出力する。出力ス

イッチSWzは、オフに制御されたとき電荷積分回路30の出力とSC積分回路10の出

力とを電気的に遮断する。

【0042】

電圧電荷変換回路20は、第1の入力容量C1(第1の容量)と、第2の入力容量C2

(第2の容量)とを備えている。電圧電荷変換回路20は、第1の期間T1において、第

1の入力容量C1に充電された電荷を電荷積分回路30に転送すると共に、入力電圧Vi

nに対応した電荷を第2の入力容量C2に充電する。また電圧電荷変換回路20は、第2

の期間T2において、第2の入力容量C2に充電された電荷の一部を第1の入力容量C1

に充電すると共に、入力電圧Vinに対応した電荷を第1の入力容量C1に充電する。こ

こで、第2の期間T2は、第1の期間T1に続く期間である。

【0043】

電荷積分回路30は、演算増幅器AMPと、一端が演算増幅器AMPの反転入力端子(

第1の入力端子)に接続されるオフセットキャンセル容量Coffと、第1のスイッチS

W1と、第2のスイッチSW2とを備えている。電荷積分回路30は、第3の期間T3に

おいて、第1のスイッチSW1が、オフセットキャンセル容量Coffの他端(ノードN

D)と第1の入力容量C1の一端とを電気的に接続する。また、第4の期間T4において

、第2のスイッチSW2が、オフセットキャンセル容量Coffの他端を接地電位と電気

的に接続する。ここで、第3の期間T3は、第2の期間T2に続く期間であり、第4の期

間T4は、第3の期間T3に続く期間である。

【0044】

出力スイッチSWz(第5のスイッチ)は、演算増幅器AMPの出力端子とSC積分回

路10の出力端子との間に挿入される。出力スイッチSWzは、第3の期間T3において

、演算増幅器AMPの出力端子をSC積分回路10の出力端子と電気的に接続する。

【0045】

このような電圧電荷変換回路20は、第1の入力容量C1及び第2の入力容量C2の他

にスイッチSWa〜SWfを備えることができる。スイッチSWa〜SWfは、第1の入

力容量C1及び第2の入力容量C2の接続を切り替える。スイッチSWa〜SWfは、そ

れぞれ2相クロックのいずれか一方によりオンオフ制御される。図1の電圧電荷変換回路

20を構成する各スイッチには、「1」と表記されるスイッチと、「2」と表記されるス

イッチの2種類がある。「1」と表記されるスイッチは、第1のクロックCLK1がHレ

ベルのとき(第1の期間)に動作するスイッチ(第1のフェーズスイッチ)である。「2

」と表記されるスイッチは、第1のクロックCLK1と逆相の第2のクロックCLK2が

Hレベルのとき(第2の期間)に動作するスイッチ(第2のフェーズスイッチ)である。

【0046】

図1において、スイッチSWaは、入力電圧Vinが入力される入力端子と第1の入力

容量C1の他端との間に挿入される。スイッチSWbは、第1の入力容量C1の他端と接

地電位(接地点)との間に挿入される。スイッチSWcは、入力端子と第2の入力容量C

2の一端との間に挿入される。スイッチSWdは、第2の入力容量C2の一端と接地電位

との間に挿入される。スイッチSWeは、第1の入力容量C1の一端と第2の入力容量C

2の他端との間に挿入される。スイッチSWfは、第2の入力容量C2の他端と接地電位

との間に挿入される。

【0047】

電荷積分回路30は、演算増幅器AMP、オフセットキャンセル容量Coff、第1の

スイッチSW1、及び第2のスイッチSW2の他に、積分容量Csと、第3のスイッチS

W3と、第4のスイッチSW4とを備えることができる。積分容量Csの一端は、演算増

幅器AMPの出力端子に接続される。第3のスイッチSW3は、第3の期間T3において

積分容量Csの他端とオフセットキャンセル容量Coffの他端とを電気的に接続する。

第4のスイッチSW4は、第4の期間T4において積分容量Csの他端と演算増幅器AM

Pの反転入力端子とを電気的に接続する。

【0048】

第1のスイッチSW1〜第4のスイッチSW4は、それぞれ2相クロックのいずれか一

方によりオンオフ制御される。図1の電荷積分回路30を構成する各スイッチには、「3

」と表記されるスイッチと、「4」と表記されるスイッチの2種類がある。「3」と表記

されるスイッチは、第3のクロックCLK3がHレベルのとき(第3の期間)に動作する

スイッチ(第3のフェーズスイッチ)である。「4」と表記されるスイッチは、第3のク

ロックCLK3と逆相の第4のクロックCLK4がHレベルのとき(第4の期間)に動作

するスイッチ(第4のフェーズスイッチ)である。なお、第3の期間T3が第1のクロッ

クCLK1がHレベルの期間、第4の期間T4が第2のクロックCLK2がHレベルの期

間とすることで、第1のクロックCLK1及び第2のクロックCLK2のみでSC積分動

作を実現することができる。そのため、以下では、T1=T3、T2=T4として説明す

る。

【0049】

図2(A)、図2(B)に、図1のSC積分回路10の動作説明図を示す。図2(A)

は、第1の期間T1におけるSC積分回路の構成の概要を表す。図2(B)は、第2の期

間T2におけるSC積分回路の構成の概要を表す。図2(A)及び図2(B)において、

図1と同様の部分には同一符号を付し、適宜説明を省略する。

【0050】

電圧電荷変換回路20は、図2(A)に示すように、第1の期間T1では、その時点に

おいて第1の入力容量C1に充電された電荷を電荷積分回路30に転送する。このとき、

第2の入力容量C2には入力電圧Vinが印加され、第2の入力容量C2に入力電圧Vi

nに対応した電荷が充電される。その後、第2の期間T2では、図2(B)に示すように

、第1の入力容量C1及び第2の入力容量C2が直列に接続され、第2の入力容量C2に

充電された電荷の一部が第1の入力容量C1に充電される。このとき、第1の入力容量C

1にも、入力電圧Vinに対応した電荷が第1の入力容量C1に充電される。その後、再

び、図2(A)に示す構成となり、第1の入力容量C1に充電された電荷が電荷積分回路

30に転送される。

【0051】

このように、電圧電荷変換回路20は、入力容量に充電された電荷の一部のみを転送し

、残りの電荷を電圧電荷変換回路20に留める。これにより、電荷積分回路30に転送さ

れる電荷量を減少させる。その結果、電圧電荷変換回路20を通過する電荷量が絞られた

ことに相当し、電圧電荷変換回路20全体で考えると容量を小さく見せることができる。

そのため、極端に小さなサイズのキャパシターを用いることなく余裕のあるサイズの容量

を用いて、見かけ上、より小さな容量を高精度に実現することができる。従って、SC積

分回路10によれば、カットオフ周波数を極めて低くするために、第1の入力容量C1及

び第2の入力容量C2と演算増幅器AMPの積分容量Csの比(素子係数)を大きくする

ことなく、高精度に実現することができる。

【0052】

また、電荷積分回路30では、オフセットキャンセル容量Coffの両端に印加される

電圧V1が、第2の期間T2から第1の期間T1への遷移時において変化しない。即ち、

電荷積分回路30は、非特許文献1に開示されたCDS積分回路と同様に、まず第2の期

間T2において、演算増幅器AMPのオフセット電圧や雑音に対応した雑音電荷をオフセ

ットキャンセル容量Coffに充電する。その後、電荷積分回路30は、第1の期間T1

において、積分動作時に該雑音電荷に対応した電圧分をキャンセルする。このように、電

荷積分回路30による積分動作において、演算増幅器AMPのオフセット電圧の影響を無

くすことができる。

【0053】

更に、電荷積分回路30は、第1のスイッチSW1及び第2のスイッチSW2を設け、

電圧電荷変換回路20からの電荷の非転送期間において電気的に遮断し、オフセットキャ

ンセル容量Coffの他端(ノードND)を接地電位に接続するように構成される。これ

により、非特許文献1に開示されたCDS積分回路では単純に電荷の転送と接地を繰り返

すためのノードNDを電荷の非転送期間においても積分動作に寄与させることができるよ

うになる。更に、該非転送期間においてオフセットキャンセル容量Coffに、目的とす

る電荷を充電させることができるようになる。この結果、低周波成分の雑音を確実にキャ

ンセルする構成を実現することができる。

【0054】

ここで、本実施形態の比較例を基準に、図1のSC積分回路10の伝達関数について説

明する。なお、以下では、説明の便宜上、第2の入力容量C2の容量値が、第1の入力容

量C1の容量値と等しいものとする。

【0055】

図3に、本実施形態の比較例におけるSC積分回路の構成例の回路図を示す。図3は、

図1のSC積分回路10においてオフセットキャンセル容量Coff等が省略された構成

を有するSC積分回路の回路図を表す。なお、図3において、図1と同様の部分には同一

符号を付し、適宜説明を省略する。

【0056】

本比較例におけるSC積分回路10aの構成が図1に示すSC積分回路10の構成と異

なる点は、スイッチSW1〜SW4、オフセットキャンセル容量Coff、及び出力スイ

ッチSWzが省略され、スイッチSWgが追加された点である。このような構成を有する

SC積分回路10aの入力電圧Vinの出力への信号伝達関数(Signal Transfer Functi

on:以下、STF)と、演算増幅器AMPによる雑音の出力への雑音伝達関数(Noise Tr

ansfer Function:以下、NTF)は、次式のように与えられる。

【数1】

【0057】

これに対して、図1に示すSC積分回路10の入力電圧Vinの出力へのSTFと、演

算増幅器AMPによる雑音の出力へのNTFは、次式のように与えられる。なお、式(2

)は、第1の期間T1におけるSTF及びNTFを表している。上記のように、電荷積分

回路30は、第2の期間T2(第4の期間T4)においてオフセットキャンセル容量Co

ffに雑音電荷を充電し、第1の期間T1(第3の期間T3)において雑音電荷に対応し

た電圧分のキャンセルを行う。そのため、第1の期間T1(第3の期間T3)においての

み、雑音電荷に対応した電圧分をキャンセルすることができることを表している。従って

、式(2)は、第1の期間T1(第3の期間T3)のSTF及びNTFのみを表し、正し

い出力が得られない第2の期間T2(第4の期間T4)のSTF及びNTFについては考

慮していない。

【数2】

【0058】

式(1)及び式(2)を比較すると、式(2)のCoff/Csが小さいほど雑音の伝

達量を減少させることができ、(1−z−1/2)は低周波数帯域ほど0に近づくことを

表す。即ち、電荷積分回路30によれば、演算増幅器AMPで発生する雑音の低周波成分

を低減することができ、オフセットキャンセル容量Coffの容量値に対して積分容量C

sの容量値を大きくすることで雑音の影響をより一層小さくすることができる。

【0059】

図4に、図1のSC積分回路10と図3のSC積分回路10aのNTFの計算結果及び

シミュレーション結果の一例を示す。図4は、横軸に周波数、縦軸に雑音レベルを表す。

図4では、図1のSC積分回路10のNTFの計算結果(図4のS1)を実線で表し、シ

ミュレーション結果をポイントで表している。また、図4では、図3のSC積分回路10

aのNTFの計算結果(図4のS2)を破線で表し、シミュレーション結果をポイントで

表している。

【0060】

図4では、図1又は図3における第1の入力容量C1の容量値を0.1pF、第2の入

力容量C2の容量値を0.1pF、オフセットキャンセル容量Coffの容量値を0.1

pF、積分容量Csの容量値を4.014pFとして計算している。図4に示すように、

S1は、低周波数帯域ほど雑音レベルが小さくなり、図1のSC積分回路10によれば、

演算増幅器AMPで発生する雑音の低周波成分を低減することができる。

【0061】

〔2次の低域通過型フィルター〕

本実施形態のSC積分回路10を適用することで、特に低周波数帯域の雑音の影響をよ

り一層低減させることができる2次の低域通過型フィルター(Low Pass Filter:以下、

LPF)を提供することができる。

【0062】

図5に、本実施形態のSC積分回路10を適用した2次のLPFの構成例の回路図を示

す。

LPF100は、第1のSC積分回路110と、第2のSC積分回路120と、第1の

帰還容量CR1と、第2の帰還容量CR2とを備えている。第1のSC積分回路110及

び第2のSC積分回路120の各々は、図1のSC積分回路10と同様の構成(但し、出

力スイッチSWzが省略された構成)を有し、第1のSC積分回路110は第2のSC積

分回路120の逆相で積分動作を行う。即ち、LPF100は、第1のSC積分回路と、

第2のSC積分回路と、帰還容量と、出力スイッチとを備えることができる。ここで、第

2のSC積分回路は、CDS積分器を有し、第1のSC積分回路の後段側に配置され第1

の期間で電荷を積分する。帰還容量は、第2のSC積分回路の出力と第1のSC積分回路

の所与のノードとの間に挿入される。出力スイッチは、第1の期間において第2のSC積

分回路の出力と帰還容量の一端とを電気的に接続する。

【0063】

具体的には、スイッチSWa1,SWa2は、スイッチSWaに対応する。スイッチS

Wb1,SWb2は、スイッチSWbに対応する。スイッチSWc1,SWc2は、スイ

ッチSWcに対応する。スイッチSWd1,SWd2は、スイッチSWdに対応する。ス

イッチSWe1,SWe2は、スイッチSWeに対応する。スイッチSWf1,SWf2

は、スイッチSWfに対応する。第1の入力容量C11,C12は、第1の入力容量C1

に対応する。第1の入力容量C11の容量値は、kG(kはゲイン)である。第1の入力

容量C12の容量値は、Aである。第2の入力容量C21,C22は、第2の入力容量C

2に対応する。第2の入力容量C21の容量値は、kGである。第2の入力容量C22の

容量値は、Aである。スイッチSW11,SW12は、スイッチSW1に対応する。スイ

ッチSW21,SW22は、スイッチSW2に対応する。スイッチSW31,SW32は

、スイッチSW3に対応する。スイッチSW41,SW42は、スイッチSW4に対応す

る。積分容量Cs1,Cs2は、積分容量Csに対応する。積分容量Cs1の容量値は、

Dである。積分容量Cs2の容量値は、Bである。演算増幅器AMP1,AMP2は、演

算増幅器AMPに対応する。

【0064】

第1の帰還容量CR1は、容量値がEであり、一端が出力スイッチSWz(第5のスイ

ッチ)を介して、第2のSC積分回路120を構成する演算増幅器AMP2の出力端子に

接続される。第1の帰還容量CR1の他端は、第1のSC積分回路110を構成する積分

容量Cs1の一端に接続される。出力スイッチSWzは、第1の期間T1においてオンと

なり、第2の期間T2においてオフとなる。即ち、出力スイッチSWzは、第1の期間T

1において、第2のSC積分回路120の出力端子と第1の帰還容量CR1の一端とを電

気的に接続する。また、出力スイッチSWzは、第2の期間T2において第1の帰還容量

CR1の一端と第2のSC積分回路120の出力端子とを電気的に遮断する。

【0065】

第2の帰還容量CR2は、容量値がCであり、第2の期間T2において電荷量が初期化

され、第1の期間T1において第1の帰還容量CR1と並列に設けられる。そのため、L

PF100には、第1の期間T1において第2の帰還容量CR2の一端と演算増幅器AM

P2の出力端子とを電気的に接続するスイッチと、第2の期間T2において第2の帰還容

量CR2の一端と接地電位とを電気的に接続するスイッチとが設けられる。また、LPF

100には、第1の期間T1において第2の帰還容量CR2の他端と積分容量Cs1の一

端とを電気的に接続するスイッチと、第2の期間T2において第2の帰還容量CR2の他

端と接地電位とを電気的に接続するスイッチとが設けられる。

【0066】

ここで、本実施形態の比較例を基準に、図5のLPF100について説明する。

【0067】

図6に、本実施形態の比較例における2次のLPFの構成例の回路図を示す。図6は、

図5のLPF100を構成する第1のSC積分回路110及び第2のSC積分回路120

の各々が図3のSC積分回路10aにより構成されるLPFを表す。なお、図6において

、図5の対応する容量については同一容量値であるものとする。

【0068】

図6に示す構成を有する本比較例におけるLPF190の入力電圧Vinの出力へのS

TFは、図5に示すLPF100の入力電圧Vinの出力へのSTFと同様であり、次式

のように与えられる。

【数3】

【0069】

これに対し、LPFを構成する各演算増幅器からの雑音伝達特性は、次のように変化す

る。

【0070】

図7(A)、図7(B)に、図5のLPF100と図6のLPF190のシミュレーシ

ョン結果の一例を示す。図7(A)は、演算増幅器AMP1からの雑音伝達特性のシミュ

レーション結果の一例を表す。図7(B)は、演算増幅器AMP2からの雑音伝達特性の

シミュレーション結果の一例を表す。図7(A)、図7(B)は、横軸に周波数、縦軸に

雑音レベルを表す。図7(A)、図7(B)において、図5のLPF100のシミュレー

ション結果(S3)を実線で表し、図6のLPF190のシミュレーション結果(S4)

を破線で表している。なお、図7(A)、図7(B)では、図5及び図6のA=C−G=

0.1pF、B=D=4.014pF、E=5.067pF、k=4.52(=13.1

dB)、T=1/50000s、カットオフ周波数fc=200Hz、Q=2−1/2と

して計算している。

【0071】

図7(A)に示すように、演算増幅器AMP2から帰還される信号や入力電圧Vinに

含まれる雑音が入力される演算増幅器AMP1からの雑音は、低周波数帯域において減少

している。また、図7(B)に示すように、演算増幅器AMP2からの雑音は、低周波数

帯域において減少している。従って、図5のLPF100によれば、2次のLPFを構成

する各演算増幅器で発生する雑音の低周波成分を低減することができるようになる。これ

により、LPFのより一層の高精度化及び高安定化に寄与することができるようになる。

【0072】

〔多出力フィルター回路〕

上記のLPF等のフィルター回路が適用されるセンサー回路では、面積や消費電流の増

大、複数の演算増幅器のオフセットの違い等を招くことなく、ゲイン及び検出範囲が異な

る複数の検出信号を出力することが望まれる。そこで、本実施形態では、上記のフィルタ

ー回路(SC積分回路)を用いて、次のように多出力フィルター回路を構成することで、

ゲイン及び検出範囲が異なる複数の検出信号を出力する。これにより、面積や消費電流の

増大、複数の演算増幅器のオフセットの違い等を招くことなく、複数の検出信号を出力す

る多出力フィルター回路を提供することができるようになる。なお、以下では、2種類の

検出信号を出力する例を説明するが、3種類以上の検出信号を出力する場合も同様である

。

【0073】

図8に、本実施形態における多出力フィルター回路の構成例の回路図を示す。図8にお

いて、図5と同様の部分には同一符号を付し、適宜説明を省略する。

【0074】

本実施形態における多出力フィルター回路200は、図5のLPF100と、減衰回路

300とを備えている。減衰回路300の入力は、LPF100の出力端子(OUT1)

に接続され、LPF100の出力を減衰させる。この多出力フィルター回路200は、1

種類の入力信号(Vin)に対して、2種類の第1の検出信号Vout1及び第2の検出

信号Vout2を出力する。具体的には、多出力フィルター回路200は、LPF100

の出力電圧を第1の検出信号Vout1として出力し、第1の検出信号Vout1を入力

とする減衰回路300の出力電圧を第2の検出信号Vout2として出力する。

【0075】

減衰回路300を次のようなCapacitive-Reset Gain回路により構成することで、減衰

回路300を構成する演算増幅器からの雑音伝達を抑えることができる。特に、低周波数

帯域において第2の検出信号Vout2として出力される出力端子への雑音伝達を大幅に

抑えることができる。図8では、例えば第2の期間T2においてCapacitive-Reset Gain

回路が雑音を抑えた出力を行う。そのため、多出力フィルター回路200は、減衰回路3

00の出力に、第2のフェーズスイッチであるスイッチSWx1を介して出力容量Cou

tの一端が接続されて、第2の検出信号Vout2の電位を保持する構成を有している。

【0076】

図9に、図8の減衰回路300の構成例の回路図を示す。図9において、スイッチを図

1と同様に表記している。

【0077】

減衰回路300は、演算増幅器AMP3と、入力容量Cg1(第1の入力容量)と、積

分容量Cg2(第1の積分容量),Cg3(第2の積分容量)とを備えたCapacitive-Res

et Gain回路である。入力容量Cg1の一端は、演算増幅器AMP3の反転入力端子に電

気的に接続される。入力容量Cg1の他端は、第1の期間T1においてLPF100の出

力に電気的に接続され、第2の期間T2において接地電位と電気的に接続される。積分容

量Cg2の一端は、演算増幅器AMP3の反転入力端子に電気的に接続される。積分容量

Cg2の他端は、第1の期間T1において接地電位と電気的に接続され、第2の期間T2

において演算増幅器AMP3の出力端子に電気的に接続される。積分容量Cg3の一端は

、演算増幅器AMP3の出力端子に電気的に接続される。積分容量Cg3の他端は、第1

の期間T1において演算増幅器AMP3の反転入力端子に電気的に接続され、第2の期間

T2において接地電位と電気的に接続される。図9に示す減衰回路300は、入力容量C

g1、積分容量Cg2,Cg3への電荷の充電及び放電が上記のように行われるようにス

イッチSWr1〜SWr6を備え、各スイッチは図9に示すようなフェーズスイッチとし

て動作する。

【0078】

図10(A)、図10(B)に、図9の減衰回路300の動作説明図を示す。図10(

A)は、第1の期間T1における減衰回路300の構成の概要を表す。図10(B)は、

第2の期間T2における減衰回路300の構成の概要を表す。図10(A)及び図10(

B)では、演算増幅器AMP3の雑音電圧Vnを発生する雑音源が演算増幅器AMP3の

非反転入力端子に接続されるものとし、図9と同様の部分には同一符号を付し、適宜説明

を省略する。

【0079】

減衰回路300では、図10(A)に示すように、第1の期間T1において、入力容量

Cg1に、雑音電圧Vnに対応した電荷が充電される。この入力容量Cg1に充電された

電荷量は、図10(B)に示す第2の期間T2においても変化しない。従って、一端が入

力容量Cg1(演算増幅器AMP3の反転入力端子)に接続される積分容量Cg2の他端

の電圧は、雑音電圧Vnだけ低くなる。第2の期間T2では、積分容量Cg2の他端が演

算増幅器AMP3の出力端子に接続されるため、演算増幅器AMP3の出力電圧は雑音電

圧Vnだけ低くなり、雑音電圧の影響が出力に反映されない。

【0080】

このような減衰回路300のSTFは、LPF100の出力端子(減衰回路300の入

力端子)OUT1の電圧をVout1、減衰回路300の出力端子OUT2の電圧をVo

ut2とすると、次式のようになる。

【数4】

【0081】

一方、NTFは、次式のように表される。

【数5】

【0082】

式(5)において、z−1/2は、低周波数帯域において1に近づくため、低周波数帯

域において減衰回路300を構成する演算増幅器からの雑音伝達を抑え、出力端子OUT

2への雑音伝達を大幅に抑えることができることを示す。

【0083】

図11(A)、図11(B)、図11(C)に、図8の多出力フィルター回路200の

シミュレーション結果の一例を示す。図11(A)は、多出力フィルター回路200を構

成する演算増幅器AMP1からの雑音伝達特性のシミュレーション結果の一例を表す。図

11(B)は、多出力フィルター回路200を構成する演算増幅器AMP2からの雑音伝

達特性のシミュレーション結果の一例を表す。図11(C)は、多出力フィルター回路2

00を構成する演算増幅器AMP3からの雑音伝達特性のシミュレーション結果の一例を

表す。図11(A)〜図11(C)は、横軸に周波数、縦軸に雑音レベルを表す。

【0084】

図11(A)及び図11(B)において、出力端子OUT1における雑音伝達特性(S

5)を実線で表し、出力端子OUT2における雑音伝達特性(S6)を破線で表す。図1

1(C)において、減衰回路300を公知の抵抗分割回路で実現したときの出力端子OU

T2における雑音伝達特性(S8)を破線で表し、減衰回路300を図9の構成で実現し

たときの出力端子OUT2における雑音伝達特性(S7)を実線で表している。また、図

11(A)〜図11(C)では、各素子の値が図7(A)及び図7(B)と同様であり、

−13.1dBとなるように減衰回路300における入力容量Cg1及び積分容量Cg3

の値が調整されているものとする。

【0085】

図11(A)〜図11(C)に示すように、出力端子OUT1,OUT2から出力され

る第1の検出信号Vout1及び第2の検出信号Vout2は、低周波数帯域になるほど

少なくとも演算増幅器AMP2,AMP3からの雑音成分が小さくなる。従って、ゲイン

が異なる複数の検出信号を出力する場合に、面積や消費電流の増大、複数の演算増幅器の

オフセットの違い等を招くことなく、低周波数帯域の雑音の影響をより一層小さくするこ

とができる多出力フィルター回路を提供することができるようになる。

【0086】

〔第1の変形例〕

本実施形態のLPF100及び多出力フィルター回路200では、図5に示す位置に出

力スイッチSWzが挿入されていたが、本実施形態は、出力スイッチSWzの挿入位置に

限定されるものではない。

【0087】

図12に、本実施形態の第1の変形例における2次のLPFの構成例の回路図を示す。

図12において、図5と同様の部分には同一符号を付し、適宜説明を省略する。

【0088】

第1の変形例におけるLPF100aが図5に示すLPF100と異なる点は、第5の

スイッチとしての出力スイッチの挿入位置である。LPF100aは、第1の期間T1に

おいて、第1のSC積分回路110を構成する積分容量Cs1の一端と第1の帰還容量C

R1の他端とを、スイッチSW41と共に電気的に接続する出力スイッチSWza(第5

のスイッチ)を備える。出力スイッチSWzaは、第2の期間T2において第1の帰還容

量CR1の他端と積分容量Cs1の一端とを電気的に遮断する。即ち、LPF100aは

、第1のSC積分回路と、第2のSC積分回路と、帰還容量と、出力スイッチとを備える

ことができる。ここで、第2のSC積分回路は、CDS積分器を有し、第1のSC積分回

路の後段側に配置され第1の期間で電荷を積分する。帰還容量は、第2のSC積分回路の

出力と第1のSC積分回路の所与のノードとの間に挿入される。出力スイッチは、第1の

期間において該ノードと帰還容量の一端とを電気的に接続する。

【0089】

各素子の値をLPF100と同様に設定すると、第1の変形例におけるLPF100a

のシミュレーション結果は、図7(A)及び図7(B)と同様である。従って、第1の変

形例においても、演算増幅器AMP2から帰還される信号や入力電圧Vinに含まれる雑

音が入力される演算増幅器AMP1からの雑音は、低周波数帯域において減少している。

また、演算増幅器AMP2からの雑音は、低周波数帯域において減少している。従って、

第1の変形例におけるLPF100aによれば、2次のLPFを構成する演算増幅器で発

生する雑音の低周波成分を低減することができるようになる。これにより、LPFのより

一層の高精度化及び高安定化に寄与することができるようになる。

【0090】

〔第2の変形例〕

本実施形態のLPF100又は第2の変形例のLPF100aでは、出力スイッチSW

z又は出力スイッチSWzaを設けて、第1の期間T1のみ第2のSC積分回路120の

出力を第1のSC積分回路110に帰還させていた。しかしながら、本実施形態は、これ

に限定されるものではない。

【0091】

図13に、本実施形態の第2の変形例における2次のLPFの構成例の回路図を示す。

図13において、図5と同様の部分には同一符号を付し、適宜説明を省略する。

【0092】

第2の変形例におけるLPF100bが図5に示すLPF100と異なる点は、第5の

スイッチとしての出力スイッチが省略された点である。即ち、LPF100bでは、積分

容量Cs1の一端と第1の帰還容量CR1の他端とが電気的に接続され、第1の帰還容量

CR1の一端と演算増幅器AMP2の出力端子とが電気的に接続される。

【0093】

図14(A)、図14(B)に、第2の変形例におけるLPF100bのシミュレーシ

ョン結果の一例を示す。図14(A)は、各素子の値をLPF100aと同様に設定した

ときの演算増幅器AMP1からの雑音伝達特性の一例を表す。図14(B)は、各素子の

値をLPF100aと同様に設定したときの演算増幅器AMP2からの雑音伝達特性の一

例を表す。図14(A)及び図14(B)は、横軸に周波数、縦軸に雑音レベルを表す。

【0094】

図14(A)において、LPF100aにおける演算増幅器AMP1からの雑音伝達特

性(S10)を破線で表し、LPF100bにおける演算増幅器AMP1からの雑音伝達

特性(S9)を実線で表している。また、図14(B)において、LPF100aにおけ

る演算増幅器AMP2からの雑音伝達特性を破線で表し、LPF100bにおける演算増

幅器AMP2からの雑音伝達特性を実線で表している。図14(A)及び図14(B)に

示すように、出力スイッチを省略した構成を採用しても、低周波数帯域において雑音成分

が減少している(図14(B)参照)。これは、図1のSC積分回路10を各SC積分回

路に適用するのみで得られる効果であることを示し、第2の変形例におけるLPF100

bによれば、2次のLPFを構成する演算増幅器で発生する雑音の低周波成分を低減する

ことができる。これにより、LPFのより一層の高精度化及び高安定化に寄与することが

できるようになる。

【0095】

〔第3の変形例〕

本実施形態のLPF100では、第1のSC積分回路110及び第2のSC積分回路1

20の両方に図1のSC積分回路を適用していたが、本実施形態は、これに限定されるも

のではない。

【0096】

図15に、本実施形態の第3の変形例における2次のLPFの構成例の回路図を示す。

図15において、図5と同様の部分には同一符号を付し、適宜説明を省略する。

【0097】

第3の変形例におけるLPF100cが本実施形態のLPF100と異なる点は、第1

のSC積分回路の構成である。具体的には、LPF100cは、第1のSC積分回路11

0に代えて、図3のSC積分回路10aと同様の構成を有する第1のSC積分回路110

aを備えている。即ち、LPF100cは、前段側のSC積分回路として図3のSC積分

回路10aを備え、後段型のSC積分回路として図1のSC積分回路10を備え、互いに

逆相で積分動作を行う。なお、LPF100cは、LPF100と同様に、第1の帰還容

量CR1と、第2の帰還容量CR2とを備えている。

【0098】

各素子の値をLPF100と同様に設定すると、第3の変形例におけるLPF100c

のシミュレーション結果は、演算増幅器AMP1からの雑音伝達特性は図6のLPF19

0と同様であり、演算増幅器AMP2からの雑音伝達特性は図7(B)と同様である。従

って、第3の変形例においても、演算増幅器AMP2からの雑音は、低周波数帯域におい

て減少している。従って、第3の変形例におけるLPF100cによれば、2次のLPF

を構成する演算増幅器で発生する雑音の低周波成分を低減することができるようになる。

これにより、LPFのより一層の高精度化及び高安定化に寄与することができるようにな

る。

【0099】

〔第4の変形例〕

本実施形態の第3の変形例におけるLPF100cでは、図15に示す位置に出力スイ

ッチSWzが挿入されていたが、出力スイッチSWzの挿入位置に限定されるものではな

い。

【0100】

図16に、本実施形態の第4の変形例における2次のLPFの構成例の回路図を示す。

図16において、図15と同様の部分には同一符号を付し、適宜説明を省略する。

【0101】

第5の変形例におけるLPF100dが図15に示すLPF100cと異なる点は、第

5のスイッチとしての出力スイッチの挿入位置である。LPF100dは、第1の期間T

1において、第1のSC積分回路110aを構成する積分容量Cs1の一端と第1の帰還

容量CR1の他端とを電気的に接続する出力スイッチSWza(第5のスイッチ)を備え

る。出力スイッチSWzaは、第2の期間T2において第1の帰還容量CR1の他端と積

分容量Cs1の一端とを電気的に遮断する。

【0102】

図17(A)、図17(B)に、第4の変形例におけるLPF100dのシミュレーシ

ョン結果の一例を示す。図17(A)は、各素子の値を図6に示すLPF190と同様に

設定したときの演算増幅器AMP1からの雑音伝達特性の一例を表す。図17(B)は、

各素子の値を図6のLPF190と同様に設定したときの演算増幅器AMP2からの雑音

伝達特性の一例を表す。図17(A)及び図17(B)は、横軸に周波数、縦軸に雑音レ

ベルを表す。

【0103】

図17(A)において、LPF190における演算増幅器AMP1からの雑音伝達特性

(S12)を破線で表し、LPF100dにおける演算増幅器AMP1からの雑音伝達特

性(S11)を実線で表している。このように、LPF190における演算増幅器AMP

1からの雑音伝達特性とLPF100dにおける演算増幅器AMP1からの雑音伝達特性

は一致している。一方、図17(B)において、LPF190における演算増幅器AMP

2からの雑音伝達特性を破線で表し、LPF100dにおける演算増幅器AMP2からの

雑音伝達特性を実線で表している。図17(B)に示すように、LPF100dによれば

、特に低周波数帯域において雑音成分が減少し、2次のLPFを構成する演算増幅器で発

生する雑音の低周波成分を低減することができる。これにより、LPFのより一層の高精

度化及び高安定化に寄与することができるようになる。

【0104】

なお、本実施形態の他の変形例として、図15において出力スイッチSWzを省略した

構成又は図16において出力スイッチSWzaを省略した構成を採用してもよい。

【0105】

〔第5の変形例〕

本実施形態の第3の変形例におけるLPF100cでは、第2のSC積分回路120に

図1のSC積分回路を適用していたが、本実施形態は、これに限定されるものではない。

【0106】

図18に、本実施形態の第5の変形例における2次のLPFの構成例の回路図を示す。

図18において、図5と同様の部分には同一符号を付し、適宜説明を省略する。

【0107】

第5の変形例におけるLPF100eが本実施形態のLPF100と異なる点は、第2

のSC積分回路の構成である。具体的には、LPF100eは、第2のSC積分回路12

0に代えて、図3のSC積分回路10aと同様の構成を有する第2のSC積分回路120

eを備えている。即ち、LPF100eは、前段側のSC積分回路として図1のSC積分

回路10を備え、後段型のSC積分回路として図3のSC積分回路10aを備え、互いに

逆相で積分動作を行う。なお、LPF100eは、LPF100と同様に、第1の帰還容

量CR1と、第2の帰還容量CR2とを備えている。

【0108】

図19(A)、図19(B)に、第5の変形例におけるLPF100eのシミュレーシ

ョン結果の一例を示す。図19(A)は、各素子の値を図6に示すLPF190と同様に

設定したときの演算増幅器AMP1からの雑音伝達特性の一例を表す。図19(B)は、

各素子の値を図6のLPF190と同様に設定したときの演算増幅器AMP2からの雑音

伝達特性の一例を表す。図19(A)及び図19(B)は、横軸に周波数、縦軸に雑音レ

ベルを表す。

【0109】

図19(A)において、LPF190における演算増幅器AMP1からの雑音伝達特性

(S14)を破線で表し、LPF100eにおける演算増幅器AMP1からの雑音伝達特

性(S13)を実線で表している。このように、LPF190における演算増幅器AMP

1からの雑音伝達特性に対し、LPF100eにおける演算増幅器AMP1からの雑音伝

達特性は、特に低周波数帯域において雑音成分が減少する。一方、図19(B)において

、LPF190における演算増幅器AMP2からの雑音伝達特性を破線で表し、LPF1

00eにおける演算増幅器AMP2からの雑音伝達特性を実線で表している。図19(B

)では、LPF190における演算増幅器AMP1からの雑音伝達特性が、LPF100

eにおける演算増幅器AMP1からの雑音伝達特性と一致する。従って、LPF100e

によれば、特に低周波数帯域において雑音成分が減少し、2次のLPFを構成する演算増

幅器で発生する雑音の低周波成分を低減することができる。これにより、LPFのより一

層の高精度化及び高安定化に寄与することができるようになる。

【0110】

〔第6の変形例〕

本実施形態の第5の変形例におけるLPF100eでは、出力スイッチを挿入していた

が、本実施形態は、これに限定されるものではない。

【0111】

図20に、本実施形態の第6の変形例における2次のLPFの構成例の回路図を示す。

図20において、図18と同様の部分には同一符号を付し、適宜説明を省略する。

【0112】

第6の変形例におけるLPF100fが第5の変形例におけるLPF100eと異なる

点は、出力スイッチSWzが省略された点である。即ち、LPF100fでは、積分容量

Cs1の一端と第1の帰還容量CR1の他端とが電気的に接続され、第1の帰還容量CR

1の一端と積分容量Cs1の一端とが電気的に接続される。

【0113】

図21(A)、図21(B)に、第6の変形例におけるLPF100fのシミュレーシ

ョン結果の一例を示す。図21(A)は、各素子の値を図6に示すLPF190と同様に

設定したときの演算増幅器AMP1からの雑音伝達特性の一例を表す。図21(B)は、

各素子の値を図6のLPF190と同様に設定したときの演算増幅器AMP2からの雑音

伝達特性の一例を表す。図21(A)及び図21(B)は、横軸に周波数、縦軸に雑音レ

ベルを表す。

【0114】

図21(A)において、LPF190における演算増幅器AMP1からの雑音伝達特性

(S17)を破線で表し、LPF100eにおける演算増幅器AMP1からの雑音伝達特

性を一点鎖線(S16)で表している。また、図21(A)において、LPF100fに

おける演算増幅器AMP1からの雑音伝達特性(S15)を実線で表している。このよう

に、LPF190における演算増幅器AMP1からの雑音伝達特性に対し、LPF100

fにおける演算増幅器AMP1からの雑音伝達特性は、特に低周波数帯域において雑音成

分が減少する。一方、図21(B)において、LPF190における演算増幅器AMP2

からの雑音伝達特性を破線で表し、LPF100eにおける演算増幅器AMP2からの雑

音伝達特性を一点鎖線で表している。また、図21(B)において、LPF100fにお

ける演算増幅器AMP2からの雑音伝達特性を実線で表している。図21(B)では、L

PF190における演算増幅器AMP1からの雑音伝達特性が、LPF100fにおける

演算増幅器AMP1からの雑音伝達特性と一致する。従って、LPF100fによれば、

特に低周波数帯域において雑音成分が減少し、2次のLPFを構成する演算増幅器で発生

する雑音の低周波成分を低減することができる。これにより、LPFのより一層の高精度

化及び高安定化に寄与することができるようになる。

【0115】

以上説明したように、本実施形態又はその変形例におけるフィルター回路としての2次

のLPFは、第1のSC積分回路と、第1のSC積分回路の前段側又は後段側に接続され

る第2のSC積分回路と、第1の帰還容量と、第2の帰還容量とを備えることができる。

第1の帰還容量は、第1のSC積分回路及び第2のSC積分回路のうち後段側のスイッチ

トキャパシター積分回路から前段側のSC積分回路の帰還経路に挿入される。第2の帰還

容量は、第2の期間において初期化され、第1の期間において第1の帰還容量と並列に設

けられる。そして、第1のSC積分回路及び第2のSC積分回路の少なくとも一方は、図

1のSC積分回路10により構成される。このとき、出力スイッチが、第1の帰還容量を

介した帰還経路に挿入され、第1の期間において導通し、第2の期間において遮断される

ことが望ましい。なお、高次のフィルター回路として、上記の2次のLPF(フィルター

回路)を含む構成を採用してもよい。

【0116】

〔物理量測定装置〕

本実施形態のいずれかの変形例におけるLPFは、図8においてLPF100に代えて

多出力フィルター回路200を構成するLPF100として採用することができる。この

ような多出力フィルター回路200は、センサー回路に適用することにより、高精度にセ

ンシングを行い、ゲイン及び検出範囲が異なる複数の検出信号を出力する物理量測定装置

を提供することができるようになる。

【0117】

図22に、本実施形態又はその変形例におけるLPFが適用された多出力フィルター回

路を有するセンサー回路の構成例を示す。なお、この回路構成は一例であり、例えば回路

の細部の構成が変形される場合もあり得る。

【0118】

センサー回路400は、角速度を測定対象の物理量とする物理量測定装置である。セン

サー回路400は、駆動回路(駆動装置)500と、検出回路(検出装置)600とを備

えている。このセンサー回路400は、圧電材料で形成され、駆動振動片及び検出振動片

を有する振動片(振動子、広義には圧電素子)510を含む。

【0119】

駆動回路500は、駆動振動片に設けられた駆動電極512a,512bを介して駆動

振動片を発振ループ内に設け、駆動振動片(広義には振動子)を励振させる。駆動回路5

00は、電流電圧変換器520、オートゲインコントロール(Auto Gain Control:以下

、AGC)回路530、高域通過フィルター(High Pass Filter:以下、HPF)540

を備えている。更に、駆動回路500は、ゲインコントロールアンプ(Gain Control Amp

lifier:以下、GCA)550、2値化回路560を備えている。

【0120】

駆動振動片の駆動電極512aは、電流電圧変換器520の入力に電気的に接続され、

電流電圧変換器520の出力は、AGC回路530及びHPF540に入力される。HP

F540は、発振ループ内の発振信号の位相調整回路として機能し、HPF540の出力

は、GCA550及び2値化回路560に入力される。AGC回路530は、電流電圧変

換器520の出力に基づいて、GCA550のゲインを制御する。GCA550の出力は

、駆動振動片の駆動電極512bに電気的に接続される。2値化回路560は、発振ルー

プ内の発振信号を2値化し、参照信号として検出回路600に出力する。なお、図22で

は、駆動回路500の内部に振動片510の駆動振動片を設けるものとして説明したが、

駆動回路500の外部に振動片510の駆動振動片が設けられていてもよい。

【0121】

検出回路600は、交流増幅回路610と、同期検波回路620と、直流増幅器630

と、多出力フィルター回路200とを備えている。多出力フィルター回路200は、図8

の構成、又は図8の構成におけるLPF100に代えて本実施形態のいずれかの変形例に

おけるLPFを採用した構成を有する。交流増幅回路610は、第1の電流電圧変換器6

12と、第2の電流電圧変換器614と、交流増幅器616と、HPF618とを含む。

【0122】

駆動回路500では、上記の構成の発振ループ内のゲインが「1」より大きい状態で発

振スタートする。この時点では、駆動振動片への入力は雑音のみであるが、この雑音は、

目的とする駆動振動の固有共振周波数を含む幅広い周波数の波動を含む。振動片510の

駆動振動片の周波数フィルター作用によって、目的とする固有共振周波数の波動を多く含

む信号が出力され、この信号が電流電圧変換器520において電圧値に変換される。AG

C回路530は、この電圧値に基づいてGCA550のゲインを制御することで発振ルー

プ内の発振振幅を制御する。発振ループ内でこうした操作が繰り返されることにより、目

的とする固有共振周波数の信号の割合が高くなる。そして、GCA550のゲイン制御に

よって、次第に発振ループを信号が1周する間の利得(ループゲイン)が「1」となり、

この状態で駆動振動片が安定発振する。

【0123】

駆動振動片を励振させて安定発振状態になり、振動片510を所与の方向に回転させる

と、コリオリ力が振動片510に作用し、検出振動片が屈曲振動する。検出振動片には検

出電極514a,514b,516a,516bが設けられる。検出電極514b,51

6bにはアナログ接地電位が供給され、検出電極514a,516aは、交流増幅回路6

10の第1の電流電圧変換器612及び第2の電流電圧変換器614に接続される。検出

回路600は、検出電極514a,516aからの互いに極性が異なる検出信号を交流増

幅した後、駆動回路500からの参照信号を用いて同期検波して、多出力フィルター回路

200で、第1の検出信号Vout1及び第2の検出信号Vout2を出力する。ここで

、第1の検出信号Vout1及び第2の検出信号Vout2は、互いにゲイン及び検出範

囲が異なる検出信号である。

【0124】

以上のように、センサー回路400は、振動片510と、駆動回路500と、検出回路

600とを備えることができる。駆動回路500は、振動片510と発振ループを形成し

、該振動片に駆動振動を励振する。検出回路600は、上記のいずれかのフィルター回路

を有し振動片510に励振される駆動振動及び測定すべき物理量に応じて、互いにゲイン

及び検出範囲が異なる複数の検出信号を出力する。

【0125】

〔電子機器〕

上記のセンサー回路は、次のような電子機器に搭載することができる。このような電子

機器によれば、低周波数帯域の雑音の影響をより一層小さくし、高精度なセンシングを容

易に実現できるようになる。

【0126】

図23に、本実施形態における電子機器のハードウェア構成例のブロック図を示す。

【0127】

電子機器700は、センサー回路400と、A/D変換回路710と、クロック生成回

路720と、中央演算処理装置等の処理部730と、メモリー740と、操作部750と

、表示部760とを備えている。電子機器700を構成する各部は、バス(BUS)によ

って相互に接続されている。なお、A/D変換回路710は、処理部730に内蔵されて

いてもよい。

【0128】

例えば、処理部730は、メモリー740から読み込んだプログラムに従って処理を実

行し、センサー回路400で検出された検出信号の振幅又は感度に応じてA/D変換回路

710で変換されたディジタル値を用いて積分を行う。こうすることで、角速度及び回転

角度を算出する。このとき、処理部730は、第1の検出信号又は第2の検出信号に応じ

て、速い動きや遅い動きに対応した角速度及び回転角度を高精度に算出することができる

。そして、処理部730は、算出した角速度又は回転角度に対応した処理を実行し、該処

理に対応した表示データを生成し、表示部760に表示させる処理を行う。

【0129】

以上、本発明に係るSC積分回路、フィルター回路、多出力フィルター回路、物理量測

定装置、及び電子機器等を上記の実施形態又はその変形例に基づいて説明したが、本発明

は上記の実施形態又はその変形例に限定されるものではない。本発明は、その要旨を逸脱

しない範囲において種々の態様において実施することが可能であり、例えば次のような変

形も可能である。

【0130】

(1)上記の実施形態では、SC積分回路として図1に示す構成を例に説明したが、本

発明はこれに限定されるものではない。本発明に係るSC積分回路は、例えば3以上の入

力容量を備えた構成であってもよい。

【0131】

(2)上記の実施形態又はその変形例では、フィルター回路として図5、図12、図1

3、図15、図16、図18又は図20に示す構成を例に説明したが、本発明はこれらに

限定されるものではない。本発明に係るフィルター回路として、n(nは3以上の整数)

次のLPFであってもよい。

【0132】

(3)上記の実施形態では、多出力フィルター回路として、図8に示すように2出力を

行う構成を例に説明したが、本発明はこれに限定されるものではない。本発明に係る多出

力フィルター回路として、3以上の出力を行うものであってもよい。

【0133】

(4)上記の実施形態では、物理量測定装置が多出力フィルター回路を備えた構成を例

に説明したが、本発明はこれに限定されるものではない。本発明に係る物理量測定装置が

、例えば出力毎に、本実施形態又はその変形例におけるLPFが設けられた構成であって

もよい。

【0134】

(5)上記の実施形態では、電子機器が、上記の多出力フィルター回路を備えた例を説

明したが、本発明はこれに限定されるものではない。本発明に係る電子機器が、上記のS

C積分回路又はフィルター回路を備えた構成を有していてもよい。

【符号の説明】

【0135】

10,10a…SC積分回路、 20…電圧電荷変換回路、 30…電荷積分回路、

100,100a〜100f…LPF、 110,110a…第1のSC積分回路、

120,120e…第2のSC積分回路、 200…多出力フィルター回路、

300…減衰回路、 400…センサー回路、 500…駆動回路、

510…振動片(振動子)、 512a,512b…駆動電極、

514a,514b,516a,516b…検出電極、 520…電流電圧変換器、

530…AGC回路、 540,618…HPF、 550…GCA、

560…2値化回路、 600…検出回路、 610…交流増幅回路、

612…第1の電流電圧変換器、 614…第2の電流電圧変換器、

616…交流増幅器、 620…同期検波回路、 630…直流増幅器、

700…電子機器、 710…A/D変換回路、 720…クロック生成回路、

730…処理部、 740…メモリー、 750…操作部、 760…表示部、

AMP,AMP1,AMP2…演算増幅器、 C1…第1の入力容量(第1の容量)、

C2…第2の入力容量(第2の容量)、 Cg1…入力容量、

CR1…第1の帰還容量、 CR2…第2の帰還容量、

Coff…オフセットキャンセル容量、 Cout…出力容量、

Cg2,Cg3,Cs,Cs1,Cs2…積分容量、

SW1,SW11,SW12…スイッチ(第1のスイッチ)、

SW2,SW21,SW22…スイッチ(第2のスイッチ)、

SW3,SW31,SW32…スイッチ(第3のスイッチ)、

SW4,SW41,SW42…スイッチ(第4のスイッチ)、

SWa〜SWg,SWa1〜SWg1,SWa2〜SWg2,SWr1〜SWr6,SW

x1…スイッチ、 SWz,SWza…出力スイッチ(第5のスイッチ)、

Vin…入力電圧、 Vout…出力電圧

【技術分野】

【0001】

本発明は、スイッチトキャパシター積分回路、フィルター回路、多出力フィルター回路

、物理量測定装置、及び電子機器等に関する。

【背景技術】

【0002】

従来より、角速度等の物理量を測定するセンサー回路(広義には、物理量測定装置)は

、カメラ機器の手振れ補正、ナビゲーションやデッドレコニング等の位置情報検出、及び

モーションアナライザー等の身体運動の検出等に用いられる。このようなセンサー回路に

は、例えば極めて低いカットオフ周波数を有するフィルター回路が内蔵される。例えば特

許文献1〜特許文献3には、スイッチトキャパシター(Switched Capacitor:以下、SC

)回路により構成され、極めて低いカットオフ周波数を有するフィルター回路が開示され

ている。特許文献1〜特許文献3に開示されたフィルター回路によれば、演算増幅器の入

力容量と積分容量の比を大きくすることなく、極めて低いカットオフ周波数のフィルター

回路を高精度に実現することができる。

【0003】

ところで、この種のセンサー回路の用途が広まり、センサー回路には、速い動きや遅い

動きにも対応することが求められている。そのため、センサー回路には、ゲイン及び検出

範囲が異なる複数の検出信号を出力することが望まれる。そこで、特許文献1〜特許文献

3に開示されたフィルター回路を複数用いて、多出力が可能な構成とすることが考えられ

る。ところが、特許文献1〜特許文献3に開示されたフィルター回路を複数用いた場合、

集積化に伴う面積や消費電流の増大、各フィルター回路を構成する演算増幅器のオフセッ

トのずれという問題を招く。

【0004】

また、この種のセンサー回路には、更なる高精度化及び高安定化の観点から、特に低周

波数帯域における雑音低減が求められている。例えば非特許文献1及び非特許文献2には

、雑音を低減することができるSC回路が開示されている。非特許文献1には、いわゆる

相関ダブル・サンプリング(Correlated Double-Sampling:以下、CDS)積分器が開示

されている。非特許文献2には、いわゆるCapacitive-Reset Gain回路が開示されている

。

【先行技術文献】

【特許文献】

【0005】

【特許文献1】特開2009−200618号公報

【特許文献2】特開2010−177734号公報

【特許文献3】特開2010−177791号公報

【非特許文献】

【0006】

【非特許文献1】K.NAGARAJ, T.R.VISWANATHAN,K.SINGHAL, and J.VLACH, "Switched-Capacitor Circuits with ReducedSensitivity to Amplifier Gain", IEEE TRANSACTIONS ON CIRCUITS AND SYSTEMS,VOL.CAS-34, No.5, pp.571-574, May, 1987

【非特許文献2】H.MATSUMOTO, and W.WATANABE, "SPIKE-FREESWITCHED-CAPACITOR CIRCUITS", ELECTRONICS LETTERS, Vol.23, No.8,pp.428-429, 9th April, 1987

【発明の開示】

【発明が解決しようとする課題】

【0007】

しかしながら、特許文献1〜特許文献3に開示されたフィルター回路に、非特許文献1

及び非特許文献2に開示されたSC回路を単純に適用したとしても、低周波数帯域の雑音

の影響を十分に小さくすることができないという問題がある。

【0008】

本発明は、以上のような技術的課題に鑑みてなされたものである。本発明の幾つかの態

様によれば、低周波数帯域の雑音の影響をより一層小さくすることができるスイッチトキ

ャパシター積分回路、フィルター回路、多出力フィルター回路、物理量測定装置、及び電

子機器等を提供することができる。

【課題を解決するための手段】

【0009】

(1)本発明の第1の態様は、スイッチトキャパシター積分回路が、第1の容量と第2

の容量とを有する電圧電荷変換回路と、前記第1の容量に充電された電荷を積分する電荷

積分回路とを含み、前記電圧電荷変換回路は、第1の期間において、前記第1の容量に充

電された電荷を転送すると共に、入力信号に対応した電荷を前記第2の容量に充電し、第

2の期間において、前記第2の容量に充電された電荷の一部を前記第1の容量に充電する

と共に、前記入力信号に対応した電荷を前記第1の容量に充電し、前記電荷積分回路は、

演算増幅器と、一端が前記演算増幅器の第1の入力端子に接続されるオフセットキャンセ

ル容量と、第3の期間において前記オフセットキャンセル容量の他端と前記第1の容量の

一端とを電気的に接続する第1のスイッチと、第4の期間において前記オフセットキャン

セル容量の他端を接地電位に接続する第2のスイッチとを含む。

【0010】

本態様においては、演算増幅器の第1の入力端子にオフセットキャンセル容量を接続し

、第1のスイッチ及び第2のスイッチにより、オフセットキャンセル容量の他端を第1の

容量の一端に接続したり接地電位と電気的に接続したりするようにしている。即ち、電圧

電荷変換回路からの電荷の非転送期間において電気的に遮断し、オフセットキャンセル容

量の他端を接地電位に接続するように構成される。これにより、オフセットキャンセル容

量の他端を、電荷の非転送期間においても積分動作に寄与させることができ、該非転送期

間においてオフセットキャンセル容量に、目的とする電荷を充電させることができるよう

になる。この結果、低周波成分の雑音を確実にキャンセルする構成を実現でき、低周波数

帯域の雑音の影響をより一層小さくすることができるスイッチトキャパシター積分回路を

提供することができるようになる。

【0011】

(2)本発明の第2の態様に係るスイッチトキャパシター積分回路では、第1の態様に

おいて、前記電荷積分回路は、一端が前記演算増幅器の出力端子に接続される積分容量と

、前記第3の期間において前記積分容量の他端と前記第1の入力端子とを電気的に接続す

る第3のスイッチと、前記第4の期間において前記積分容量の他端と前記オフセットキャ

ンセル容量の他端とを電気的に接続する第4のスイッチとを含む。

【0012】

本態様によれば、第3にスイッチ及び第4のスイッチを追加することにより、演算増幅

器及び積分容量を用いた積分動作において、低周波数帯域の雑音の影響をより一層小さく

することができるようになる。

【0013】

(3)本発明の第3の態様に係るスイッチトキャパシター積分回路では、第1の態様又

は第2の態様において、前記第1の期間及び前記第3の期間は、第1のクロックに基づい

て規定される期間であり、前記第2の期間及び前記第4の期間は、前記第1のクロックと

逆相の第2のクロックに基づいて規定される期間である。

【0014】

本態様によれば、2相クロックのいずれかによりオンオフ制御されるスイッチを用いた

スイッチトキャパシター積分回路を提供することができる。これにより、非常に簡素な制

御及び構成により、低周波数帯域の雑音の影響をより一層小さくすることができるスイッ

チトキャパシター積分回路を提供することができるようになる。

【0015】

(4)本発明の第4の態様に係るスイッチトキャパシター積分回路は、第3の態様にお

いて、前記第1の期間において、前記スイッチトキャパシター積分回路の出力として前記

電荷積分回路の出力信号を出力する第5のスイッチを含む。

【0016】

本態様によれば、第2の期間における電荷積分回路の出力信号の伝搬を抑えることがで

きるので、低周波数帯域の雑音の影響を更に小さくすることができるスイッチトキャパシ

ター積分回路を提供することができるようになる。

【0017】

(5)本発明の第5の態様は、フィルター回路が、第1のスイッチトキャパシター積分

回路と、前記第1のスイッチトキャパシター積分回路の前段側又は後段側に接続される第

2のスイッチトキャパシター積分回路と、前記第1のスイッチトキャパシター積分回路及

び前記第2のスイッチトキャパシター積分回路のうち後段側のスイッチトキャパシター積

分回路から前段側のスイッチトキャパシター積分回路の帰還経路に挿入される第1の帰還

容量と、前記第2の期間において初期化され、前記第1の期間において前記第1の帰還容

量と並列に設けられる第2の帰還容量とを含み、前記第1のスイッチキャパシター積分回

路及び前記第2のスイッチトキャパシター積分回路の少なくとも一方は、第3の態様に係

るスイッチトキャパシター積分回路である。

【0018】

本態様によれば、低周波成分の雑音を確実にキャンセルする構成を有するスイッチトキ

ャパシター積分回路を用いて低域通過型フィルターの機能を実現することができる。これ

により、低周波数帯域の雑音の影響をより一層小さくすることができるフィルター回路を

提供することができるようになる。

【0019】

(6)本発明の第6の態様に係るフィルター回路は、第5の態様において、前記第1の

帰還容量を介した帰還経路に挿入され、前記第1の期間において導通し、前記第2の期間

において遮断される第5のスイッチとを含む。

【0020】

本態様においては、第1の期間において、後段側のスイッチトキャパシター積分回路の

出力信号を、第1の帰還容量を介して前段側に帰還させることができる。これにより、低

周波数帯域の雑音の影響を更に小さくすることができるフィルター回路を提供することが

できるようになる。

【0021】

(7)本発明の第7の態様に係るフィルター回路は、第1の態様乃至第4の態様のいず

れか記載のスイッチトキャパシター積分回路を含む。

【0022】

本態様によれば、低周波数帯域の雑音の影響をより一層小さくすることができるフィル

ター回路を提供することができるようになる。

【0023】

(8)本発明の第8の態様は、フィルター回路が、第1のスイッチトキャパシター積分

回路と、相関ダブル・サンプリング積分器を有し、前記第1のスイッチトキャパシター積

分回路の後段側に配置され、第1の期間で電荷を積分するスイッチトキャパシター積分回

路と、前記スイッチトキャパシター積分回路の出力と前記第1のスイッチトキャパシター

積分回路の所与のノードとの間に挿入される帰還容量と、前記第1の期間において、前記

スイッチトキャパシター積分回路の出力と前記帰還容量の一端とを電気的に接続するスイ

ッチとを含む。

【0024】

本態様においては、相関ダブル・サンプリング積分器により低周波成分の雑音をキャン

セルする構成を有するスイッチトキャパシター積分回路を用いて低域通過型フィルターの

機能を実現することができる。また、スイッチにより、雑音成分が小さい出力信号のみを

帰還させることができるので、低周波数帯域の雑音の影響を更に小さくすることができる

ようになる。これにより、低周波数帯域の雑音の影響をより一層小さくすることができる

フィルター回路を提供することができるようになる。

【0025】

(9)本発明の第9の態様は、フィルター回路が、第1のスイッチトキャパシター積分

回路と、相関ダブル・サンプリング積分器を有し、前記第1のスイッチトキャパシター積

分回路の後段側に配置され、第1の期間で電荷を積分するスイッチトキャパシター積分回

路と、前記スイッチトキャパシター積分回路の出力と前記第1のスイッチトキャパシター

積分回路の所与のノードとの間に挿入される帰還容量と、前記第1の期間において、前記

ノードと前記帰還容量の一端とを電気的に接続するスイッチとを含む。

【0026】

本態様においては、相関ダブル・サンプリング積分器により低周波成分の雑音をキャン

セルする構成を有するスイッチトキャパシター積分回路を用いて低域通過型フィルターの

機能を実現することができる。また、スイッチにより、雑音成分が小さい出力信号のみを

帰還させることができるので、低周波数帯域の雑音の影響を更に小さくすることができる

ようになる。これにより、低周波数帯域の雑音の影響をより一層小さくすることができる

フィルター回路を提供することができるようになる。

【0027】

(10)本発明の第10の態様に係るフィルター回路は、第5の態様乃至第9の態様の

いずれか記載のフィルター回路を含む高次のフィルター回路である。

【0028】

本態様によれば、低周波数帯域の雑音の影響をより一層小さくすることができる高次の

フィルター回路を提供することができるようになる。

【0029】

(11)本発明の第11の態様は、多出力フィルター回路が、第5の態様乃至第10の

態様のいずれか記載のフィルター回路と、前記フィルター回路の出力に接続され、前記フ

ィルター回路の出力を減衰させる減衰回路とを含む。

【0030】

本態様によれば、フィルター回路により、低周波数帯域の雑音の影響をより一層小さく

、且つゲインが異なる複数の出力が可能な多出力フィルター回路を提供することができる

ようになる。

【0031】

(12)本発明の第12の態様に係る多出力フィルター回路は、第11の態様において

、前記減衰回路は、演算増幅器と、一端が前記演算増幅器の反転入力端子に電気的に接続

される第1の入力容量と、一端が前記演算増幅器の反転入力端子に電気的に接続される第

1の積分容量と、一端が前記演算増幅器の出力端子に電気的に接続される第2の積分容量

とを含み、前記第1の入力容量は、前記第1の期間において他端が前記フィルター回路の

出力に電気的に接続され、前記第2の期間において他端が接地電位と電気的に接続され、

前記第1の積分容量は、前記第1の期間において他端が接地電位と電気的に接続され、前

記第2の期間において前記演算増幅器の出力端子に電気的に接続され、前記第2の積分容

量は、前記第1の期間において他端が前記反転入力端子に電気的に接続され、前記第2の

期間において他端が接地電位と電気的に接続される。

【0032】

本態様によれば、減衰回路において、演算増幅器からの雑音伝達を抑え、特に低周波数

帯域において雑音の影響をより一層小さくする出力が可能な多出力フィルター回路を提供

することができるようになる。

【0033】

(13)本発明の第13の態様は、物理量測定装置が、振動子と、前記振動子と発振ル

ープを形成し、該振動子に駆動振動を励振する駆動回路と、第11の態様又は第12の態

様に係る多出力フィルター回路を有し、前記振動子に励振される駆動振動及び測定すべき

物理量に応じて第1の検出信号及び第2の検出信号を出力する検出回路とを含み、前記検

出回路は、前記ファイルター回路の出力を前記第1の検出信号として出力し、前記減衰回

路の出力を前記第2の検出信号として出力する。

【0034】

本態様によれば、低周波数帯域の雑音の影響をより一層小さくしながら、ゲイン及び検

出範囲が異なる複数の検出信号を出力する物理量測定装置を提供することができるように

なる。

【0035】

(14)本発明の第14の態様は、電子機器が、第1の態様乃至第4の態様のいずれか

のスイッチトキャパシター積分回路を含む。

【0036】

本態様によれば、低周波数帯域の雑音の影響をより一層小さくするスイッチトキャパシ

ター積分回路が適用された電子機器を提供することができるようになる。

【0037】

(15)本発明の第15の態様は、電子機器が、第13の態様に係る物理量測定装置を

含む。

【0038】

本態様によれば、低周波数帯域の雑音の影響をより一層小さくしながら、ゲイン及び検

出範囲が異なる複数の検出信号の出力に基づいたセンシングが可能な電子機器を提供する

ことができるようになる。

【図面の簡単な説明】

【0039】

【図1】本発明の一実施形態に係るSC積分回路の構成例の回路図。

【図2】図2(A)は、第1の期間における図1のSC積分回路の動作説明図。図2(B)は、第2の期間における図1のSC積分回路の動作説明図。

【図3】本実施形態の比較例におけるSC積分回路の構成例の回路図。

【図4】図1のSC積分回路10と図3のSC積分回路のNTFの計算結果及びシミュレーション結果の一例を示す図。

【図5】本実施形態のSC積分回路を適用した2次のLPFの構成例の回路図。

【図6】本実施形態の比較例における2次のLPFの構成例の回路図。

【図7】図7(A)は、演算増幅器AMP1からの雑音伝達特性のシミュレーション結果の一例を示す図。図7(B)は、演算増幅器AMP2からの雑音伝達特性のシミュレーション結果の一例を示す図。

【図8】本実施形態における多出力フィルター回路の構成例の回路図。

【図9】図8の減衰回路の構成例の回路図。

【図10】図10(A)は、第1の期間における減衰回路の動作説明図。図10(B)は、第2の期間における減衰回路の動作説明図。

【図11】図11(A)は、演算増幅器AMP1からの雑音伝達特性のシミュレーション結果の一例を示す図。図11(B)は、演算増幅器AMP2からの雑音伝達特性のシミュレーション結果の一例を示す図。図11(C)は、演算増幅器AMP3からの雑音伝達特性のシミュレーション結果の一例を示す図。

【図12】本実施形態の第1の変形例における2次のLPFの構成例の回路図。

【図13】本実施形態の第2の変形例における2次のLPFの構成例の回路図。

【図14】図14(A)は、演算増幅器AMP1からの雑音伝達特性の一例を示す図。図14(B)は、演算増幅器AMP2からの雑音伝達特性の一例を示す図。

【図15】本実施形態の第3の変形例における2次のLPFの構成例の回路図。

【図16】本実施形態の第4の変形例における2次のLPFの構成例の回路図。

【図17】図17(A)は、演算増幅器AMP1からの雑音伝達特性の一例を示す図。図14(B)は、演算増幅器AMP2からの雑音伝達特性の一例を示す図。

【図18】本実施形態の第5の変形例における2次のLPFの構成例の回路図。

【図19】図19(A)は、演算増幅器AMP1からの雑音伝達特性の一例を示す図。図19(B)は、演算増幅器AMP2からの雑音伝達特性の一例を示す図。

【図20】本実施形態の第6の変形例における2次のLPFの構成例の回路図。

【図21】図21(A)は、演算増幅器AMP1からの雑音伝達特性の一例を示す図。図21(B)は、演算増幅器AMP2からの雑音伝達特性の一例を示す図。

【図22】本実施形態又はその変形例におけるLPFが適用された多出力フィルター回路を有するセンサー回路の構成例を示す図。

【図23】本実施形態における電子機器のハードウェア構成例のブロック図。

【発明を実施するための形態】

【0040】

以下、本発明の実施の形態について図面を用いて詳細に説明する。なお、以下に説明す

る実施の形態は、特許請求の範囲に記載された本発明の内容を不当に限定するものではな

い。また以下で説明される構成のすべてが本発明の課題を解決するために必須の構成要件

であるとは限らない。

【0041】

〔SC積分回路〕

図1に、本発明の一実施形態に係るSC積分回路の構成例の回路図を示す。

本実施形態におけるSC積分回路10は、電圧電荷変換回路20と、電荷積分回路30

とを備えている。また、SC積分回路10は、出力スイッチSWzを備えることができる

。電圧電荷変換回路20には、入力信号としての入力電圧Vinが入力され、入力電圧V

inに対応した電荷に変換する。電荷積分回路30は、電圧電荷変換回路20によって変

換された電荷を積分する。出力スイッチSWzは、オンに制御されたとき電荷積分回路3

0の出力信号をSC積分回路10の出力である出力電圧Voutとして出力する。出力ス

イッチSWzは、オフに制御されたとき電荷積分回路30の出力とSC積分回路10の出

力とを電気的に遮断する。

【0042】

電圧電荷変換回路20は、第1の入力容量C1(第1の容量)と、第2の入力容量C2

(第2の容量)とを備えている。電圧電荷変換回路20は、第1の期間T1において、第

1の入力容量C1に充電された電荷を電荷積分回路30に転送すると共に、入力電圧Vi

nに対応した電荷を第2の入力容量C2に充電する。また電圧電荷変換回路20は、第2

の期間T2において、第2の入力容量C2に充電された電荷の一部を第1の入力容量C1

に充電すると共に、入力電圧Vinに対応した電荷を第1の入力容量C1に充電する。こ

こで、第2の期間T2は、第1の期間T1に続く期間である。

【0043】

電荷積分回路30は、演算増幅器AMPと、一端が演算増幅器AMPの反転入力端子(

第1の入力端子)に接続されるオフセットキャンセル容量Coffと、第1のスイッチS

W1と、第2のスイッチSW2とを備えている。電荷積分回路30は、第3の期間T3に

おいて、第1のスイッチSW1が、オフセットキャンセル容量Coffの他端(ノードN

D)と第1の入力容量C1の一端とを電気的に接続する。また、第4の期間T4において

、第2のスイッチSW2が、オフセットキャンセル容量Coffの他端を接地電位と電気

的に接続する。ここで、第3の期間T3は、第2の期間T2に続く期間であり、第4の期

間T4は、第3の期間T3に続く期間である。

【0044】

出力スイッチSWz(第5のスイッチ)は、演算増幅器AMPの出力端子とSC積分回

路10の出力端子との間に挿入される。出力スイッチSWzは、第3の期間T3において

、演算増幅器AMPの出力端子をSC積分回路10の出力端子と電気的に接続する。

【0045】

このような電圧電荷変換回路20は、第1の入力容量C1及び第2の入力容量C2の他

にスイッチSWa〜SWfを備えることができる。スイッチSWa〜SWfは、第1の入

力容量C1及び第2の入力容量C2の接続を切り替える。スイッチSWa〜SWfは、そ

れぞれ2相クロックのいずれか一方によりオンオフ制御される。図1の電圧電荷変換回路

20を構成する各スイッチには、「1」と表記されるスイッチと、「2」と表記されるス

イッチの2種類がある。「1」と表記されるスイッチは、第1のクロックCLK1がHレ

ベルのとき(第1の期間)に動作するスイッチ(第1のフェーズスイッチ)である。「2

」と表記されるスイッチは、第1のクロックCLK1と逆相の第2のクロックCLK2が

Hレベルのとき(第2の期間)に動作するスイッチ(第2のフェーズスイッチ)である。

【0046】

図1において、スイッチSWaは、入力電圧Vinが入力される入力端子と第1の入力

容量C1の他端との間に挿入される。スイッチSWbは、第1の入力容量C1の他端と接

地電位(接地点)との間に挿入される。スイッチSWcは、入力端子と第2の入力容量C

2の一端との間に挿入される。スイッチSWdは、第2の入力容量C2の一端と接地電位

との間に挿入される。スイッチSWeは、第1の入力容量C1の一端と第2の入力容量C

2の他端との間に挿入される。スイッチSWfは、第2の入力容量C2の他端と接地電位

との間に挿入される。

【0047】

電荷積分回路30は、演算増幅器AMP、オフセットキャンセル容量Coff、第1の

スイッチSW1、及び第2のスイッチSW2の他に、積分容量Csと、第3のスイッチS

W3と、第4のスイッチSW4とを備えることができる。積分容量Csの一端は、演算増

幅器AMPの出力端子に接続される。第3のスイッチSW3は、第3の期間T3において

積分容量Csの他端とオフセットキャンセル容量Coffの他端とを電気的に接続する。

第4のスイッチSW4は、第4の期間T4において積分容量Csの他端と演算増幅器AM

Pの反転入力端子とを電気的に接続する。

【0048】

第1のスイッチSW1〜第4のスイッチSW4は、それぞれ2相クロックのいずれか一

方によりオンオフ制御される。図1の電荷積分回路30を構成する各スイッチには、「3

」と表記されるスイッチと、「4」と表記されるスイッチの2種類がある。「3」と表記

されるスイッチは、第3のクロックCLK3がHレベルのとき(第3の期間)に動作する

スイッチ(第3のフェーズスイッチ)である。「4」と表記されるスイッチは、第3のク

ロックCLK3と逆相の第4のクロックCLK4がHレベルのとき(第4の期間)に動作

するスイッチ(第4のフェーズスイッチ)である。なお、第3の期間T3が第1のクロッ

クCLK1がHレベルの期間、第4の期間T4が第2のクロックCLK2がHレベルの期

間とすることで、第1のクロックCLK1及び第2のクロックCLK2のみでSC積分動

作を実現することができる。そのため、以下では、T1=T3、T2=T4として説明す

る。

【0049】

図2(A)、図2(B)に、図1のSC積分回路10の動作説明図を示す。図2(A)

は、第1の期間T1におけるSC積分回路の構成の概要を表す。図2(B)は、第2の期

間T2におけるSC積分回路の構成の概要を表す。図2(A)及び図2(B)において、

図1と同様の部分には同一符号を付し、適宜説明を省略する。

【0050】

電圧電荷変換回路20は、図2(A)に示すように、第1の期間T1では、その時点に

おいて第1の入力容量C1に充電された電荷を電荷積分回路30に転送する。このとき、

第2の入力容量C2には入力電圧Vinが印加され、第2の入力容量C2に入力電圧Vi

nに対応した電荷が充電される。その後、第2の期間T2では、図2(B)に示すように

、第1の入力容量C1及び第2の入力容量C2が直列に接続され、第2の入力容量C2に

充電された電荷の一部が第1の入力容量C1に充電される。このとき、第1の入力容量C

1にも、入力電圧Vinに対応した電荷が第1の入力容量C1に充電される。その後、再

び、図2(A)に示す構成となり、第1の入力容量C1に充電された電荷が電荷積分回路

30に転送される。

【0051】

このように、電圧電荷変換回路20は、入力容量に充電された電荷の一部のみを転送し

、残りの電荷を電圧電荷変換回路20に留める。これにより、電荷積分回路30に転送さ

れる電荷量を減少させる。その結果、電圧電荷変換回路20を通過する電荷量が絞られた

ことに相当し、電圧電荷変換回路20全体で考えると容量を小さく見せることができる。

そのため、極端に小さなサイズのキャパシターを用いることなく余裕のあるサイズの容量

を用いて、見かけ上、より小さな容量を高精度に実現することができる。従って、SC積

分回路10によれば、カットオフ周波数を極めて低くするために、第1の入力容量C1及

び第2の入力容量C2と演算増幅器AMPの積分容量Csの比(素子係数)を大きくする

ことなく、高精度に実現することができる。

【0052】

また、電荷積分回路30では、オフセットキャンセル容量Coffの両端に印加される

電圧V1が、第2の期間T2から第1の期間T1への遷移時において変化しない。即ち、

電荷積分回路30は、非特許文献1に開示されたCDS積分回路と同様に、まず第2の期

間T2において、演算増幅器AMPのオフセット電圧や雑音に対応した雑音電荷をオフセ

ットキャンセル容量Coffに充電する。その後、電荷積分回路30は、第1の期間T1

において、積分動作時に該雑音電荷に対応した電圧分をキャンセルする。このように、電

荷積分回路30による積分動作において、演算増幅器AMPのオフセット電圧の影響を無

くすことができる。

【0053】

更に、電荷積分回路30は、第1のスイッチSW1及び第2のスイッチSW2を設け、

電圧電荷変換回路20からの電荷の非転送期間において電気的に遮断し、オフセットキャ

ンセル容量Coffの他端(ノードND)を接地電位に接続するように構成される。これ

により、非特許文献1に開示されたCDS積分回路では単純に電荷の転送と接地を繰り返

すためのノードNDを電荷の非転送期間においても積分動作に寄与させることができるよ

うになる。更に、該非転送期間においてオフセットキャンセル容量Coffに、目的とす

る電荷を充電させることができるようになる。この結果、低周波成分の雑音を確実にキャ

ンセルする構成を実現することができる。

【0054】

ここで、本実施形態の比較例を基準に、図1のSC積分回路10の伝達関数について説

明する。なお、以下では、説明の便宜上、第2の入力容量C2の容量値が、第1の入力容

量C1の容量値と等しいものとする。

【0055】

図3に、本実施形態の比較例におけるSC積分回路の構成例の回路図を示す。図3は、

図1のSC積分回路10においてオフセットキャンセル容量Coff等が省略された構成

を有するSC積分回路の回路図を表す。なお、図3において、図1と同様の部分には同一

符号を付し、適宜説明を省略する。

【0056】

本比較例におけるSC積分回路10aの構成が図1に示すSC積分回路10の構成と異

なる点は、スイッチSW1〜SW4、オフセットキャンセル容量Coff、及び出力スイ

ッチSWzが省略され、スイッチSWgが追加された点である。このような構成を有する

SC積分回路10aの入力電圧Vinの出力への信号伝達関数(Signal Transfer Functi

on:以下、STF)と、演算増幅器AMPによる雑音の出力への雑音伝達関数(Noise Tr

ansfer Function:以下、NTF)は、次式のように与えられる。

【数1】

【0057】

これに対して、図1に示すSC積分回路10の入力電圧Vinの出力へのSTFと、演

算増幅器AMPによる雑音の出力へのNTFは、次式のように与えられる。なお、式(2

)は、第1の期間T1におけるSTF及びNTFを表している。上記のように、電荷積分

回路30は、第2の期間T2(第4の期間T4)においてオフセットキャンセル容量Co

ffに雑音電荷を充電し、第1の期間T1(第3の期間T3)において雑音電荷に対応し

た電圧分のキャンセルを行う。そのため、第1の期間T1(第3の期間T3)においての

み、雑音電荷に対応した電圧分をキャンセルすることができることを表している。従って

、式(2)は、第1の期間T1(第3の期間T3)のSTF及びNTFのみを表し、正し

い出力が得られない第2の期間T2(第4の期間T4)のSTF及びNTFについては考

慮していない。

【数2】

【0058】

式(1)及び式(2)を比較すると、式(2)のCoff/Csが小さいほど雑音の伝

達量を減少させることができ、(1−z−1/2)は低周波数帯域ほど0に近づくことを

表す。即ち、電荷積分回路30によれば、演算増幅器AMPで発生する雑音の低周波成分

を低減することができ、オフセットキャンセル容量Coffの容量値に対して積分容量C

sの容量値を大きくすることで雑音の影響をより一層小さくすることができる。

【0059】

図4に、図1のSC積分回路10と図3のSC積分回路10aのNTFの計算結果及び

シミュレーション結果の一例を示す。図4は、横軸に周波数、縦軸に雑音レベルを表す。

図4では、図1のSC積分回路10のNTFの計算結果(図4のS1)を実線で表し、シ

ミュレーション結果をポイントで表している。また、図4では、図3のSC積分回路10

aのNTFの計算結果(図4のS2)を破線で表し、シミュレーション結果をポイントで

表している。

【0060】

図4では、図1又は図3における第1の入力容量C1の容量値を0.1pF、第2の入

力容量C2の容量値を0.1pF、オフセットキャンセル容量Coffの容量値を0.1

pF、積分容量Csの容量値を4.014pFとして計算している。図4に示すように、

S1は、低周波数帯域ほど雑音レベルが小さくなり、図1のSC積分回路10によれば、

演算増幅器AMPで発生する雑音の低周波成分を低減することができる。

【0061】

〔2次の低域通過型フィルター〕

本実施形態のSC積分回路10を適用することで、特に低周波数帯域の雑音の影響をよ

り一層低減させることができる2次の低域通過型フィルター(Low Pass Filter:以下、

LPF)を提供することができる。

【0062】

図5に、本実施形態のSC積分回路10を適用した2次のLPFの構成例の回路図を示

す。

LPF100は、第1のSC積分回路110と、第2のSC積分回路120と、第1の

帰還容量CR1と、第2の帰還容量CR2とを備えている。第1のSC積分回路110及

び第2のSC積分回路120の各々は、図1のSC積分回路10と同様の構成(但し、出

力スイッチSWzが省略された構成)を有し、第1のSC積分回路110は第2のSC積

分回路120の逆相で積分動作を行う。即ち、LPF100は、第1のSC積分回路と、

第2のSC積分回路と、帰還容量と、出力スイッチとを備えることができる。ここで、第

2のSC積分回路は、CDS積分器を有し、第1のSC積分回路の後段側に配置され第1

の期間で電荷を積分する。帰還容量は、第2のSC積分回路の出力と第1のSC積分回路

の所与のノードとの間に挿入される。出力スイッチは、第1の期間において第2のSC積

分回路の出力と帰還容量の一端とを電気的に接続する。

【0063】

具体的には、スイッチSWa1,SWa2は、スイッチSWaに対応する。スイッチS

Wb1,SWb2は、スイッチSWbに対応する。スイッチSWc1,SWc2は、スイ

ッチSWcに対応する。スイッチSWd1,SWd2は、スイッチSWdに対応する。ス

イッチSWe1,SWe2は、スイッチSWeに対応する。スイッチSWf1,SWf2

は、スイッチSWfに対応する。第1の入力容量C11,C12は、第1の入力容量C1

に対応する。第1の入力容量C11の容量値は、kG(kはゲイン)である。第1の入力

容量C12の容量値は、Aである。第2の入力容量C21,C22は、第2の入力容量C

2に対応する。第2の入力容量C21の容量値は、kGである。第2の入力容量C22の

容量値は、Aである。スイッチSW11,SW12は、スイッチSW1に対応する。スイ

ッチSW21,SW22は、スイッチSW2に対応する。スイッチSW31,SW32は

、スイッチSW3に対応する。スイッチSW41,SW42は、スイッチSW4に対応す

る。積分容量Cs1,Cs2は、積分容量Csに対応する。積分容量Cs1の容量値は、

Dである。積分容量Cs2の容量値は、Bである。演算増幅器AMP1,AMP2は、演

算増幅器AMPに対応する。

【0064】

第1の帰還容量CR1は、容量値がEであり、一端が出力スイッチSWz(第5のスイ

ッチ)を介して、第2のSC積分回路120を構成する演算増幅器AMP2の出力端子に

接続される。第1の帰還容量CR1の他端は、第1のSC積分回路110を構成する積分

容量Cs1の一端に接続される。出力スイッチSWzは、第1の期間T1においてオンと

なり、第2の期間T2においてオフとなる。即ち、出力スイッチSWzは、第1の期間T

1において、第2のSC積分回路120の出力端子と第1の帰還容量CR1の一端とを電

気的に接続する。また、出力スイッチSWzは、第2の期間T2において第1の帰還容量

CR1の一端と第2のSC積分回路120の出力端子とを電気的に遮断する。

【0065】

第2の帰還容量CR2は、容量値がCであり、第2の期間T2において電荷量が初期化

され、第1の期間T1において第1の帰還容量CR1と並列に設けられる。そのため、L

PF100には、第1の期間T1において第2の帰還容量CR2の一端と演算増幅器AM

P2の出力端子とを電気的に接続するスイッチと、第2の期間T2において第2の帰還容

量CR2の一端と接地電位とを電気的に接続するスイッチとが設けられる。また、LPF

100には、第1の期間T1において第2の帰還容量CR2の他端と積分容量Cs1の一

端とを電気的に接続するスイッチと、第2の期間T2において第2の帰還容量CR2の他

端と接地電位とを電気的に接続するスイッチとが設けられる。

【0066】

ここで、本実施形態の比較例を基準に、図5のLPF100について説明する。

【0067】

図6に、本実施形態の比較例における2次のLPFの構成例の回路図を示す。図6は、

図5のLPF100を構成する第1のSC積分回路110及び第2のSC積分回路120

の各々が図3のSC積分回路10aにより構成されるLPFを表す。なお、図6において

、図5の対応する容量については同一容量値であるものとする。

【0068】

図6に示す構成を有する本比較例におけるLPF190の入力電圧Vinの出力へのS

TFは、図5に示すLPF100の入力電圧Vinの出力へのSTFと同様であり、次式

のように与えられる。

【数3】

【0069】

これに対し、LPFを構成する各演算増幅器からの雑音伝達特性は、次のように変化す

る。

【0070】

図7(A)、図7(B)に、図5のLPF100と図6のLPF190のシミュレーシ

ョン結果の一例を示す。図7(A)は、演算増幅器AMP1からの雑音伝達特性のシミュ

レーション結果の一例を表す。図7(B)は、演算増幅器AMP2からの雑音伝達特性の

シミュレーション結果の一例を表す。図7(A)、図7(B)は、横軸に周波数、縦軸に

雑音レベルを表す。図7(A)、図7(B)において、図5のLPF100のシミュレー

ション結果(S3)を実線で表し、図6のLPF190のシミュレーション結果(S4)

を破線で表している。なお、図7(A)、図7(B)では、図5及び図6のA=C−G=

0.1pF、B=D=4.014pF、E=5.067pF、k=4.52(=13.1

dB)、T=1/50000s、カットオフ周波数fc=200Hz、Q=2−1/2と

して計算している。

【0071】

図7(A)に示すように、演算増幅器AMP2から帰還される信号や入力電圧Vinに

含まれる雑音が入力される演算増幅器AMP1からの雑音は、低周波数帯域において減少

している。また、図7(B)に示すように、演算増幅器AMP2からの雑音は、低周波数

帯域において減少している。従って、図5のLPF100によれば、2次のLPFを構成

する各演算増幅器で発生する雑音の低周波成分を低減することができるようになる。これ

により、LPFのより一層の高精度化及び高安定化に寄与することができるようになる。

【0072】

〔多出力フィルター回路〕

上記のLPF等のフィルター回路が適用されるセンサー回路では、面積や消費電流の増

大、複数の演算増幅器のオフセットの違い等を招くことなく、ゲイン及び検出範囲が異な

る複数の検出信号を出力することが望まれる。そこで、本実施形態では、上記のフィルタ

ー回路(SC積分回路)を用いて、次のように多出力フィルター回路を構成することで、

ゲイン及び検出範囲が異なる複数の検出信号を出力する。これにより、面積や消費電流の

増大、複数の演算増幅器のオフセットの違い等を招くことなく、複数の検出信号を出力す

る多出力フィルター回路を提供することができるようになる。なお、以下では、2種類の

検出信号を出力する例を説明するが、3種類以上の検出信号を出力する場合も同様である

。

【0073】

図8に、本実施形態における多出力フィルター回路の構成例の回路図を示す。図8にお

いて、図5と同様の部分には同一符号を付し、適宜説明を省略する。

【0074】

本実施形態における多出力フィルター回路200は、図5のLPF100と、減衰回路

300とを備えている。減衰回路300の入力は、LPF100の出力端子(OUT1)

に接続され、LPF100の出力を減衰させる。この多出力フィルター回路200は、1

種類の入力信号(Vin)に対して、2種類の第1の検出信号Vout1及び第2の検出

信号Vout2を出力する。具体的には、多出力フィルター回路200は、LPF100

の出力電圧を第1の検出信号Vout1として出力し、第1の検出信号Vout1を入力

とする減衰回路300の出力電圧を第2の検出信号Vout2として出力する。

【0075】

減衰回路300を次のようなCapacitive-Reset Gain回路により構成することで、減衰

回路300を構成する演算増幅器からの雑音伝達を抑えることができる。特に、低周波数

帯域において第2の検出信号Vout2として出力される出力端子への雑音伝達を大幅に

抑えることができる。図8では、例えば第2の期間T2においてCapacitive-Reset Gain

回路が雑音を抑えた出力を行う。そのため、多出力フィルター回路200は、減衰回路3

00の出力に、第2のフェーズスイッチであるスイッチSWx1を介して出力容量Cou

tの一端が接続されて、第2の検出信号Vout2の電位を保持する構成を有している。

【0076】

図9に、図8の減衰回路300の構成例の回路図を示す。図9において、スイッチを図

1と同様に表記している。

【0077】

減衰回路300は、演算増幅器AMP3と、入力容量Cg1(第1の入力容量)と、積

分容量Cg2(第1の積分容量),Cg3(第2の積分容量)とを備えたCapacitive-Res

et Gain回路である。入力容量Cg1の一端は、演算増幅器AMP3の反転入力端子に電

気的に接続される。入力容量Cg1の他端は、第1の期間T1においてLPF100の出

力に電気的に接続され、第2の期間T2において接地電位と電気的に接続される。積分容

量Cg2の一端は、演算増幅器AMP3の反転入力端子に電気的に接続される。積分容量

Cg2の他端は、第1の期間T1において接地電位と電気的に接続され、第2の期間T2

において演算増幅器AMP3の出力端子に電気的に接続される。積分容量Cg3の一端は

、演算増幅器AMP3の出力端子に電気的に接続される。積分容量Cg3の他端は、第1

の期間T1において演算増幅器AMP3の反転入力端子に電気的に接続され、第2の期間

T2において接地電位と電気的に接続される。図9に示す減衰回路300は、入力容量C

g1、積分容量Cg2,Cg3への電荷の充電及び放電が上記のように行われるようにス

イッチSWr1〜SWr6を備え、各スイッチは図9に示すようなフェーズスイッチとし

て動作する。

【0078】

図10(A)、図10(B)に、図9の減衰回路300の動作説明図を示す。図10(

A)は、第1の期間T1における減衰回路300の構成の概要を表す。図10(B)は、

第2の期間T2における減衰回路300の構成の概要を表す。図10(A)及び図10(

B)では、演算増幅器AMP3の雑音電圧Vnを発生する雑音源が演算増幅器AMP3の

非反転入力端子に接続されるものとし、図9と同様の部分には同一符号を付し、適宜説明

を省略する。

【0079】

減衰回路300では、図10(A)に示すように、第1の期間T1において、入力容量

Cg1に、雑音電圧Vnに対応した電荷が充電される。この入力容量Cg1に充電された

電荷量は、図10(B)に示す第2の期間T2においても変化しない。従って、一端が入

力容量Cg1(演算増幅器AMP3の反転入力端子)に接続される積分容量Cg2の他端

の電圧は、雑音電圧Vnだけ低くなる。第2の期間T2では、積分容量Cg2の他端が演

算増幅器AMP3の出力端子に接続されるため、演算増幅器AMP3の出力電圧は雑音電

圧Vnだけ低くなり、雑音電圧の影響が出力に反映されない。

【0080】

このような減衰回路300のSTFは、LPF100の出力端子(減衰回路300の入

力端子)OUT1の電圧をVout1、減衰回路300の出力端子OUT2の電圧をVo

ut2とすると、次式のようになる。

【数4】

【0081】

一方、NTFは、次式のように表される。

【数5】

【0082】

式(5)において、z−1/2は、低周波数帯域において1に近づくため、低周波数帯

域において減衰回路300を構成する演算増幅器からの雑音伝達を抑え、出力端子OUT

2への雑音伝達を大幅に抑えることができることを示す。

【0083】

図11(A)、図11(B)、図11(C)に、図8の多出力フィルター回路200の

シミュレーション結果の一例を示す。図11(A)は、多出力フィルター回路200を構

成する演算増幅器AMP1からの雑音伝達特性のシミュレーション結果の一例を表す。図

11(B)は、多出力フィルター回路200を構成する演算増幅器AMP2からの雑音伝

達特性のシミュレーション結果の一例を表す。図11(C)は、多出力フィルター回路2

00を構成する演算増幅器AMP3からの雑音伝達特性のシミュレーション結果の一例を

表す。図11(A)〜図11(C)は、横軸に周波数、縦軸に雑音レベルを表す。

【0084】

図11(A)及び図11(B)において、出力端子OUT1における雑音伝達特性(S

5)を実線で表し、出力端子OUT2における雑音伝達特性(S6)を破線で表す。図1

1(C)において、減衰回路300を公知の抵抗分割回路で実現したときの出力端子OU

T2における雑音伝達特性(S8)を破線で表し、減衰回路300を図9の構成で実現し

たときの出力端子OUT2における雑音伝達特性(S7)を実線で表している。また、図

11(A)〜図11(C)では、各素子の値が図7(A)及び図7(B)と同様であり、

−13.1dBとなるように減衰回路300における入力容量Cg1及び積分容量Cg3

の値が調整されているものとする。

【0085】

図11(A)〜図11(C)に示すように、出力端子OUT1,OUT2から出力され

る第1の検出信号Vout1及び第2の検出信号Vout2は、低周波数帯域になるほど

少なくとも演算増幅器AMP2,AMP3からの雑音成分が小さくなる。従って、ゲイン

が異なる複数の検出信号を出力する場合に、面積や消費電流の増大、複数の演算増幅器の

オフセットの違い等を招くことなく、低周波数帯域の雑音の影響をより一層小さくするこ

とができる多出力フィルター回路を提供することができるようになる。

【0086】

〔第1の変形例〕

本実施形態のLPF100及び多出力フィルター回路200では、図5に示す位置に出

力スイッチSWzが挿入されていたが、本実施形態は、出力スイッチSWzの挿入位置に

限定されるものではない。

【0087】

図12に、本実施形態の第1の変形例における2次のLPFの構成例の回路図を示す。

図12において、図5と同様の部分には同一符号を付し、適宜説明を省略する。

【0088】

第1の変形例におけるLPF100aが図5に示すLPF100と異なる点は、第5の

スイッチとしての出力スイッチの挿入位置である。LPF100aは、第1の期間T1に

おいて、第1のSC積分回路110を構成する積分容量Cs1の一端と第1の帰還容量C

R1の他端とを、スイッチSW41と共に電気的に接続する出力スイッチSWza(第5

のスイッチ)を備える。出力スイッチSWzaは、第2の期間T2において第1の帰還容

量CR1の他端と積分容量Cs1の一端とを電気的に遮断する。即ち、LPF100aは

、第1のSC積分回路と、第2のSC積分回路と、帰還容量と、出力スイッチとを備える

ことができる。ここで、第2のSC積分回路は、CDS積分器を有し、第1のSC積分回

路の後段側に配置され第1の期間で電荷を積分する。帰還容量は、第2のSC積分回路の

出力と第1のSC積分回路の所与のノードとの間に挿入される。出力スイッチは、第1の

期間において該ノードと帰還容量の一端とを電気的に接続する。

【0089】

各素子の値をLPF100と同様に設定すると、第1の変形例におけるLPF100a

のシミュレーション結果は、図7(A)及び図7(B)と同様である。従って、第1の変

形例においても、演算増幅器AMP2から帰還される信号や入力電圧Vinに含まれる雑

音が入力される演算増幅器AMP1からの雑音は、低周波数帯域において減少している。

また、演算増幅器AMP2からの雑音は、低周波数帯域において減少している。従って、

第1の変形例におけるLPF100aによれば、2次のLPFを構成する演算増幅器で発

生する雑音の低周波成分を低減することができるようになる。これにより、LPFのより

一層の高精度化及び高安定化に寄与することができるようになる。

【0090】

〔第2の変形例〕

本実施形態のLPF100又は第2の変形例のLPF100aでは、出力スイッチSW

z又は出力スイッチSWzaを設けて、第1の期間T1のみ第2のSC積分回路120の

出力を第1のSC積分回路110に帰還させていた。しかしながら、本実施形態は、これ

に限定されるものではない。

【0091】

図13に、本実施形態の第2の変形例における2次のLPFの構成例の回路図を示す。

図13において、図5と同様の部分には同一符号を付し、適宜説明を省略する。

【0092】

第2の変形例におけるLPF100bが図5に示すLPF100と異なる点は、第5の

スイッチとしての出力スイッチが省略された点である。即ち、LPF100bでは、積分

容量Cs1の一端と第1の帰還容量CR1の他端とが電気的に接続され、第1の帰還容量

CR1の一端と演算増幅器AMP2の出力端子とが電気的に接続される。

【0093】

図14(A)、図14(B)に、第2の変形例におけるLPF100bのシミュレーシ

ョン結果の一例を示す。図14(A)は、各素子の値をLPF100aと同様に設定した

ときの演算増幅器AMP1からの雑音伝達特性の一例を表す。図14(B)は、各素子の

値をLPF100aと同様に設定したときの演算増幅器AMP2からの雑音伝達特性の一

例を表す。図14(A)及び図14(B)は、横軸に周波数、縦軸に雑音レベルを表す。

【0094】

図14(A)において、LPF100aにおける演算増幅器AMP1からの雑音伝達特

性(S10)を破線で表し、LPF100bにおける演算増幅器AMP1からの雑音伝達

特性(S9)を実線で表している。また、図14(B)において、LPF100aにおけ

る演算増幅器AMP2からの雑音伝達特性を破線で表し、LPF100bにおける演算増

幅器AMP2からの雑音伝達特性を実線で表している。図14(A)及び図14(B)に

示すように、出力スイッチを省略した構成を採用しても、低周波数帯域において雑音成分

が減少している(図14(B)参照)。これは、図1のSC積分回路10を各SC積分回

路に適用するのみで得られる効果であることを示し、第2の変形例におけるLPF100

bによれば、2次のLPFを構成する演算増幅器で発生する雑音の低周波成分を低減する

ことができる。これにより、LPFのより一層の高精度化及び高安定化に寄与することが

できるようになる。

【0095】

〔第3の変形例〕

本実施形態のLPF100では、第1のSC積分回路110及び第2のSC積分回路1

20の両方に図1のSC積分回路を適用していたが、本実施形態は、これに限定されるも

のではない。

【0096】

図15に、本実施形態の第3の変形例における2次のLPFの構成例の回路図を示す。

図15において、図5と同様の部分には同一符号を付し、適宜説明を省略する。

【0097】

第3の変形例におけるLPF100cが本実施形態のLPF100と異なる点は、第1

のSC積分回路の構成である。具体的には、LPF100cは、第1のSC積分回路11

0に代えて、図3のSC積分回路10aと同様の構成を有する第1のSC積分回路110

aを備えている。即ち、LPF100cは、前段側のSC積分回路として図3のSC積分

回路10aを備え、後段型のSC積分回路として図1のSC積分回路10を備え、互いに

逆相で積分動作を行う。なお、LPF100cは、LPF100と同様に、第1の帰還容

量CR1と、第2の帰還容量CR2とを備えている。

【0098】

各素子の値をLPF100と同様に設定すると、第3の変形例におけるLPF100c

のシミュレーション結果は、演算増幅器AMP1からの雑音伝達特性は図6のLPF19

0と同様であり、演算増幅器AMP2からの雑音伝達特性は図7(B)と同様である。従

って、第3の変形例においても、演算増幅器AMP2からの雑音は、低周波数帯域におい

て減少している。従って、第3の変形例におけるLPF100cによれば、2次のLPF

を構成する演算増幅器で発生する雑音の低周波成分を低減することができるようになる。

これにより、LPFのより一層の高精度化及び高安定化に寄与することができるようにな

る。

【0099】

〔第4の変形例〕

本実施形態の第3の変形例におけるLPF100cでは、図15に示す位置に出力スイ

ッチSWzが挿入されていたが、出力スイッチSWzの挿入位置に限定されるものではな

い。

【0100】

図16に、本実施形態の第4の変形例における2次のLPFの構成例の回路図を示す。

図16において、図15と同様の部分には同一符号を付し、適宜説明を省略する。

【0101】

第5の変形例におけるLPF100dが図15に示すLPF100cと異なる点は、第

5のスイッチとしての出力スイッチの挿入位置である。LPF100dは、第1の期間T

1において、第1のSC積分回路110aを構成する積分容量Cs1の一端と第1の帰還

容量CR1の他端とを電気的に接続する出力スイッチSWza(第5のスイッチ)を備え

る。出力スイッチSWzaは、第2の期間T2において第1の帰還容量CR1の他端と積

分容量Cs1の一端とを電気的に遮断する。

【0102】

図17(A)、図17(B)に、第4の変形例におけるLPF100dのシミュレーシ

ョン結果の一例を示す。図17(A)は、各素子の値を図6に示すLPF190と同様に

設定したときの演算増幅器AMP1からの雑音伝達特性の一例を表す。図17(B)は、

各素子の値を図6のLPF190と同様に設定したときの演算増幅器AMP2からの雑音

伝達特性の一例を表す。図17(A)及び図17(B)は、横軸に周波数、縦軸に雑音レ

ベルを表す。

【0103】

図17(A)において、LPF190における演算増幅器AMP1からの雑音伝達特性

(S12)を破線で表し、LPF100dにおける演算増幅器AMP1からの雑音伝達特

性(S11)を実線で表している。このように、LPF190における演算増幅器AMP

1からの雑音伝達特性とLPF100dにおける演算増幅器AMP1からの雑音伝達特性

は一致している。一方、図17(B)において、LPF190における演算増幅器AMP

2からの雑音伝達特性を破線で表し、LPF100dにおける演算増幅器AMP2からの

雑音伝達特性を実線で表している。図17(B)に示すように、LPF100dによれば

、特に低周波数帯域において雑音成分が減少し、2次のLPFを構成する演算増幅器で発

生する雑音の低周波成分を低減することができる。これにより、LPFのより一層の高精

度化及び高安定化に寄与することができるようになる。

【0104】

なお、本実施形態の他の変形例として、図15において出力スイッチSWzを省略した

構成又は図16において出力スイッチSWzaを省略した構成を採用してもよい。

【0105】

〔第5の変形例〕

本実施形態の第3の変形例におけるLPF100cでは、第2のSC積分回路120に

図1のSC積分回路を適用していたが、本実施形態は、これに限定されるものではない。

【0106】

図18に、本実施形態の第5の変形例における2次のLPFの構成例の回路図を示す。

図18において、図5と同様の部分には同一符号を付し、適宜説明を省略する。

【0107】

第5の変形例におけるLPF100eが本実施形態のLPF100と異なる点は、第2

のSC積分回路の構成である。具体的には、LPF100eは、第2のSC積分回路12

0に代えて、図3のSC積分回路10aと同様の構成を有する第2のSC積分回路120

eを備えている。即ち、LPF100eは、前段側のSC積分回路として図1のSC積分

回路10を備え、後段型のSC積分回路として図3のSC積分回路10aを備え、互いに

逆相で積分動作を行う。なお、LPF100eは、LPF100と同様に、第1の帰還容

量CR1と、第2の帰還容量CR2とを備えている。

【0108】

図19(A)、図19(B)に、第5の変形例におけるLPF100eのシミュレーシ

ョン結果の一例を示す。図19(A)は、各素子の値を図6に示すLPF190と同様に

設定したときの演算増幅器AMP1からの雑音伝達特性の一例を表す。図19(B)は、

各素子の値を図6のLPF190と同様に設定したときの演算増幅器AMP2からの雑音

伝達特性の一例を表す。図19(A)及び図19(B)は、横軸に周波数、縦軸に雑音レ

ベルを表す。

【0109】

図19(A)において、LPF190における演算増幅器AMP1からの雑音伝達特性

(S14)を破線で表し、LPF100eにおける演算増幅器AMP1からの雑音伝達特

性(S13)を実線で表している。このように、LPF190における演算増幅器AMP

1からの雑音伝達特性に対し、LPF100eにおける演算増幅器AMP1からの雑音伝

達特性は、特に低周波数帯域において雑音成分が減少する。一方、図19(B)において

、LPF190における演算増幅器AMP2からの雑音伝達特性を破線で表し、LPF1

00eにおける演算増幅器AMP2からの雑音伝達特性を実線で表している。図19(B

)では、LPF190における演算増幅器AMP1からの雑音伝達特性が、LPF100

eにおける演算増幅器AMP1からの雑音伝達特性と一致する。従って、LPF100e

によれば、特に低周波数帯域において雑音成分が減少し、2次のLPFを構成する演算増

幅器で発生する雑音の低周波成分を低減することができる。これにより、LPFのより一

層の高精度化及び高安定化に寄与することができるようになる。

【0110】

〔第6の変形例〕

本実施形態の第5の変形例におけるLPF100eでは、出力スイッチを挿入していた

が、本実施形態は、これに限定されるものではない。

【0111】

図20に、本実施形態の第6の変形例における2次のLPFの構成例の回路図を示す。

図20において、図18と同様の部分には同一符号を付し、適宜説明を省略する。

【0112】

第6の変形例におけるLPF100fが第5の変形例におけるLPF100eと異なる

点は、出力スイッチSWzが省略された点である。即ち、LPF100fでは、積分容量

Cs1の一端と第1の帰還容量CR1の他端とが電気的に接続され、第1の帰還容量CR

1の一端と積分容量Cs1の一端とが電気的に接続される。

【0113】

図21(A)、図21(B)に、第6の変形例におけるLPF100fのシミュレーシ

ョン結果の一例を示す。図21(A)は、各素子の値を図6に示すLPF190と同様に

設定したときの演算増幅器AMP1からの雑音伝達特性の一例を表す。図21(B)は、

各素子の値を図6のLPF190と同様に設定したときの演算増幅器AMP2からの雑音

伝達特性の一例を表す。図21(A)及び図21(B)は、横軸に周波数、縦軸に雑音レ

ベルを表す。

【0114】

図21(A)において、LPF190における演算増幅器AMP1からの雑音伝達特性

(S17)を破線で表し、LPF100eにおける演算増幅器AMP1からの雑音伝達特

性を一点鎖線(S16)で表している。また、図21(A)において、LPF100fに

おける演算増幅器AMP1からの雑音伝達特性(S15)を実線で表している。このよう

に、LPF190における演算増幅器AMP1からの雑音伝達特性に対し、LPF100

fにおける演算増幅器AMP1からの雑音伝達特性は、特に低周波数帯域において雑音成

分が減少する。一方、図21(B)において、LPF190における演算増幅器AMP2

からの雑音伝達特性を破線で表し、LPF100eにおける演算増幅器AMP2からの雑

音伝達特性を一点鎖線で表している。また、図21(B)において、LPF100fにお

ける演算増幅器AMP2からの雑音伝達特性を実線で表している。図21(B)では、L

PF190における演算増幅器AMP1からの雑音伝達特性が、LPF100fにおける

演算増幅器AMP1からの雑音伝達特性と一致する。従って、LPF100fによれば、

特に低周波数帯域において雑音成分が減少し、2次のLPFを構成する演算増幅器で発生

する雑音の低周波成分を低減することができる。これにより、LPFのより一層の高精度

化及び高安定化に寄与することができるようになる。

【0115】

以上説明したように、本実施形態又はその変形例におけるフィルター回路としての2次

のLPFは、第1のSC積分回路と、第1のSC積分回路の前段側又は後段側に接続され

る第2のSC積分回路と、第1の帰還容量と、第2の帰還容量とを備えることができる。

第1の帰還容量は、第1のSC積分回路及び第2のSC積分回路のうち後段側のスイッチ

トキャパシター積分回路から前段側のSC積分回路の帰還経路に挿入される。第2の帰還

容量は、第2の期間において初期化され、第1の期間において第1の帰還容量と並列に設

けられる。そして、第1のSC積分回路及び第2のSC積分回路の少なくとも一方は、図

1のSC積分回路10により構成される。このとき、出力スイッチが、第1の帰還容量を

介した帰還経路に挿入され、第1の期間において導通し、第2の期間において遮断される

ことが望ましい。なお、高次のフィルター回路として、上記の2次のLPF(フィルター

回路)を含む構成を採用してもよい。

【0116】

〔物理量測定装置〕

本実施形態のいずれかの変形例におけるLPFは、図8においてLPF100に代えて

多出力フィルター回路200を構成するLPF100として採用することができる。この

ような多出力フィルター回路200は、センサー回路に適用することにより、高精度にセ

ンシングを行い、ゲイン及び検出範囲が異なる複数の検出信号を出力する物理量測定装置

を提供することができるようになる。

【0117】

図22に、本実施形態又はその変形例におけるLPFが適用された多出力フィルター回

路を有するセンサー回路の構成例を示す。なお、この回路構成は一例であり、例えば回路

の細部の構成が変形される場合もあり得る。

【0118】

センサー回路400は、角速度を測定対象の物理量とする物理量測定装置である。セン

サー回路400は、駆動回路(駆動装置)500と、検出回路(検出装置)600とを備

えている。このセンサー回路400は、圧電材料で形成され、駆動振動片及び検出振動片

を有する振動片(振動子、広義には圧電素子)510を含む。

【0119】

駆動回路500は、駆動振動片に設けられた駆動電極512a,512bを介して駆動

振動片を発振ループ内に設け、駆動振動片(広義には振動子)を励振させる。駆動回路5

00は、電流電圧変換器520、オートゲインコントロール(Auto Gain Control:以下

、AGC)回路530、高域通過フィルター(High Pass Filter:以下、HPF)540

を備えている。更に、駆動回路500は、ゲインコントロールアンプ(Gain Control Amp

lifier:以下、GCA)550、2値化回路560を備えている。

【0120】

駆動振動片の駆動電極512aは、電流電圧変換器520の入力に電気的に接続され、

電流電圧変換器520の出力は、AGC回路530及びHPF540に入力される。HP

F540は、発振ループ内の発振信号の位相調整回路として機能し、HPF540の出力

は、GCA550及び2値化回路560に入力される。AGC回路530は、電流電圧変

換器520の出力に基づいて、GCA550のゲインを制御する。GCA550の出力は

、駆動振動片の駆動電極512bに電気的に接続される。2値化回路560は、発振ルー

プ内の発振信号を2値化し、参照信号として検出回路600に出力する。なお、図22で

は、駆動回路500の内部に振動片510の駆動振動片を設けるものとして説明したが、

駆動回路500の外部に振動片510の駆動振動片が設けられていてもよい。

【0121】

検出回路600は、交流増幅回路610と、同期検波回路620と、直流増幅器630

と、多出力フィルター回路200とを備えている。多出力フィルター回路200は、図8

の構成、又は図8の構成におけるLPF100に代えて本実施形態のいずれかの変形例に

おけるLPFを採用した構成を有する。交流増幅回路610は、第1の電流電圧変換器6

12と、第2の電流電圧変換器614と、交流増幅器616と、HPF618とを含む。

【0122】

駆動回路500では、上記の構成の発振ループ内のゲインが「1」より大きい状態で発

振スタートする。この時点では、駆動振動片への入力は雑音のみであるが、この雑音は、

目的とする駆動振動の固有共振周波数を含む幅広い周波数の波動を含む。振動片510の

駆動振動片の周波数フィルター作用によって、目的とする固有共振周波数の波動を多く含

む信号が出力され、この信号が電流電圧変換器520において電圧値に変換される。AG

C回路530は、この電圧値に基づいてGCA550のゲインを制御することで発振ルー

プ内の発振振幅を制御する。発振ループ内でこうした操作が繰り返されることにより、目

的とする固有共振周波数の信号の割合が高くなる。そして、GCA550のゲイン制御に

よって、次第に発振ループを信号が1周する間の利得(ループゲイン)が「1」となり、

この状態で駆動振動片が安定発振する。

【0123】

駆動振動片を励振させて安定発振状態になり、振動片510を所与の方向に回転させる

と、コリオリ力が振動片510に作用し、検出振動片が屈曲振動する。検出振動片には検

出電極514a,514b,516a,516bが設けられる。検出電極514b,51

6bにはアナログ接地電位が供給され、検出電極514a,516aは、交流増幅回路6

10の第1の電流電圧変換器612及び第2の電流電圧変換器614に接続される。検出

回路600は、検出電極514a,516aからの互いに極性が異なる検出信号を交流増

幅した後、駆動回路500からの参照信号を用いて同期検波して、多出力フィルター回路

200で、第1の検出信号Vout1及び第2の検出信号Vout2を出力する。ここで

、第1の検出信号Vout1及び第2の検出信号Vout2は、互いにゲイン及び検出範

囲が異なる検出信号である。

【0124】

以上のように、センサー回路400は、振動片510と、駆動回路500と、検出回路

600とを備えることができる。駆動回路500は、振動片510と発振ループを形成し

、該振動片に駆動振動を励振する。検出回路600は、上記のいずれかのフィルター回路

を有し振動片510に励振される駆動振動及び測定すべき物理量に応じて、互いにゲイン

及び検出範囲が異なる複数の検出信号を出力する。

【0125】

〔電子機器〕

上記のセンサー回路は、次のような電子機器に搭載することができる。このような電子

機器によれば、低周波数帯域の雑音の影響をより一層小さくし、高精度なセンシングを容

易に実現できるようになる。

【0126】

図23に、本実施形態における電子機器のハードウェア構成例のブロック図を示す。

【0127】

電子機器700は、センサー回路400と、A/D変換回路710と、クロック生成回

路720と、中央演算処理装置等の処理部730と、メモリー740と、操作部750と

、表示部760とを備えている。電子機器700を構成する各部は、バス(BUS)によ

って相互に接続されている。なお、A/D変換回路710は、処理部730に内蔵されて

いてもよい。

【0128】

例えば、処理部730は、メモリー740から読み込んだプログラムに従って処理を実

行し、センサー回路400で検出された検出信号の振幅又は感度に応じてA/D変換回路

710で変換されたディジタル値を用いて積分を行う。こうすることで、角速度及び回転

角度を算出する。このとき、処理部730は、第1の検出信号又は第2の検出信号に応じ

て、速い動きや遅い動きに対応した角速度及び回転角度を高精度に算出することができる

。そして、処理部730は、算出した角速度又は回転角度に対応した処理を実行し、該処

理に対応した表示データを生成し、表示部760に表示させる処理を行う。

【0129】

以上、本発明に係るSC積分回路、フィルター回路、多出力フィルター回路、物理量測

定装置、及び電子機器等を上記の実施形態又はその変形例に基づいて説明したが、本発明

は上記の実施形態又はその変形例に限定されるものではない。本発明は、その要旨を逸脱

しない範囲において種々の態様において実施することが可能であり、例えば次のような変

形も可能である。

【0130】

(1)上記の実施形態では、SC積分回路として図1に示す構成を例に説明したが、本

発明はこれに限定されるものではない。本発明に係るSC積分回路は、例えば3以上の入

力容量を備えた構成であってもよい。

【0131】

(2)上記の実施形態又はその変形例では、フィルター回路として図5、図12、図1

3、図15、図16、図18又は図20に示す構成を例に説明したが、本発明はこれらに

限定されるものではない。本発明に係るフィルター回路として、n(nは3以上の整数)

次のLPFであってもよい。

【0132】

(3)上記の実施形態では、多出力フィルター回路として、図8に示すように2出力を

行う構成を例に説明したが、本発明はこれに限定されるものではない。本発明に係る多出

力フィルター回路として、3以上の出力を行うものであってもよい。

【0133】

(4)上記の実施形態では、物理量測定装置が多出力フィルター回路を備えた構成を例

に説明したが、本発明はこれに限定されるものではない。本発明に係る物理量測定装置が

、例えば出力毎に、本実施形態又はその変形例におけるLPFが設けられた構成であって

もよい。

【0134】

(5)上記の実施形態では、電子機器が、上記の多出力フィルター回路を備えた例を説

明したが、本発明はこれに限定されるものではない。本発明に係る電子機器が、上記のS

C積分回路又はフィルター回路を備えた構成を有していてもよい。

【符号の説明】

【0135】

10,10a…SC積分回路、 20…電圧電荷変換回路、 30…電荷積分回路、

100,100a〜100f…LPF、 110,110a…第1のSC積分回路、

120,120e…第2のSC積分回路、 200…多出力フィルター回路、

300…減衰回路、 400…センサー回路、 500…駆動回路、

510…振動片(振動子)、 512a,512b…駆動電極、

514a,514b,516a,516b…検出電極、 520…電流電圧変換器、

530…AGC回路、 540,618…HPF、 550…GCA、

560…2値化回路、 600…検出回路、 610…交流増幅回路、

612…第1の電流電圧変換器、 614…第2の電流電圧変換器、

616…交流増幅器、 620…同期検波回路、 630…直流増幅器、

700…電子機器、 710…A/D変換回路、 720…クロック生成回路、

730…処理部、 740…メモリー、 750…操作部、 760…表示部、

AMP,AMP1,AMP2…演算増幅器、 C1…第1の入力容量(第1の容量)、

C2…第2の入力容量(第2の容量)、 Cg1…入力容量、

CR1…第1の帰還容量、 CR2…第2の帰還容量、

Coff…オフセットキャンセル容量、 Cout…出力容量、

Cg2,Cg3,Cs,Cs1,Cs2…積分容量、

SW1,SW11,SW12…スイッチ(第1のスイッチ)、

SW2,SW21,SW22…スイッチ(第2のスイッチ)、

SW3,SW31,SW32…スイッチ(第3のスイッチ)、

SW4,SW41,SW42…スイッチ(第4のスイッチ)、

SWa〜SWg,SWa1〜SWg1,SWa2〜SWg2,SWr1〜SWr6,SW

x1…スイッチ、 SWz,SWza…出力スイッチ(第5のスイッチ)、

Vin…入力電圧、 Vout…出力電圧

【特許請求の範囲】

【請求項1】

第1の容量と第2の容量とを有する電圧電荷変換回路と、

前記第1の容量に充電された電荷を積分する電荷積分回路とを含み、

前記電圧電荷変換回路は、

第1の期間において、前記第1の容量に充電された電荷を転送すると共に、入力信号に

対応した電荷を前記第2の容量に充電し、

第2の期間において、前記第2の容量に充電された電荷の一部を前記第1の容量に充電

すると共に、前記入力信号に対応した電荷を前記第1の容量に充電し、

前記電荷積分回路は、

演算増幅器と、

一端が前記演算増幅器の第1の入力端子に接続されるオフセットキャンセル容量と、

第3の期間において前記オフセットキャンセル容量の他端と前記第1の容量の一端とを

電気的に接続する第1のスイッチと、

第4の期間において前記オフセットキャンセル容量の他端を接地電位に接続する第2の

スイッチとを含むことを特徴とするスイッチトキャパシター積分回路。

【請求項2】

請求項1において、

前記電荷積分回路は、

一端が前記演算増幅器の出力端子に接続される積分容量と、

前記第3の期間において前記積分容量の他端と前記第1の入力端子とを電気的に接続す

る第3のスイッチと、

前記第4の期間において前記積分容量の他端と前記オフセットキャンセル容量の他端と

を電気的に接続する第4のスイッチとを含むことを特徴とするスイッチトキャパシター積

分回路。

【請求項3】

請求項1又は2において、

前記第1の期間及び前記第3の期間は、第1のクロックに基づいて規定される期間であ

り、

前記第2の期間及び前記第4の期間は、前記第1のクロックと逆相の第2のクロックに

基づいて規定される期間であることを特徴とするスイッチトキャパシター積分回路。

【請求項4】

請求項3において、

前記第1の期間において、前記スイッチトキャパシター積分回路の出力として前記電荷

積分回路の出力信号を出力する第5のスイッチを含むことを特徴とするスイッチトキャパ

シター積分回路。

【請求項5】

第1のスイッチトキャパシター積分回路と、

前記第1のスイッチトキャパシター積分回路の前段側又は後段側に接続される第2のス

イッチトキャパシター積分回路と、

前記第1のスイッチトキャパシター積分回路及び前記第2のスイッチトキャパシター積

分回路のうち後段側のスイッチトキャパシター積分回路から前段側のスイッチトキャパシ

ター積分回路の帰還経路に挿入される第1の帰還容量と、

前記第2の期間において初期化され、前記第1の期間において前記第1の帰還容量と並

列に設けられる第2の帰還容量とを含み、

前記第1のスイッチキャパシター積分回路及び前記第2のスイッチトキャパシター積分

回路の少なくとも一方は、請求項3記載のスイッチトキャパシター積分回路であることを

特徴とするフィルター回路。

【請求項6】

請求項5において、

前記第1の帰還容量を介した帰還経路に挿入され、前記第1の期間において導通し、前

記第2の期間において遮断される第5のスイッチとを含むことを特徴とするフィルター回

路。

【請求項7】

請求項1乃至4のいずれか記載のスイッチトキャパシター積分回路を含むことを特徴と

するフィルター回路。

【請求項8】

第1のスイッチトキャパシター積分回路と、

相関ダブル・サンプリング積分器を有し、前記第1のスイッチトキャパシター積分回路

の後段側に配置され、第1の期間で電荷を積分するスイッチトキャパシター積分回路と、

前記スイッチトキャパシター積分回路の出力と前記第1のスイッチトキャパシター積分

回路の所与のノードとの間に挿入される帰還容量と、

前記第1の期間において、前記スイッチトキャパシター積分回路の出力と前記帰還容量

の一端とを電気的に接続するスイッチとを含むことを特徴とするフィルター回路。

【請求項9】

第1のスイッチトキャパシター積分回路と、

相関ダブル・サンプリング積分器を有し、前記第1のスイッチトキャパシター積分回路

の後段側に配置され、第1の期間で電荷を積分するスイッチトキャパシター積分回路と、

前記スイッチトキャパシター積分回路の出力と前記第1のスイッチトキャパシター積分

回路の所与のノードとの間に挿入される帰還容量と、

前記第1の期間において、前記ノードと前記帰還容量の一端とを電気的に接続するスイ

ッチとを含むことを特徴とするフィルター回路。

【請求項10】

請求項5乃至9のいずれか記載のフィルター回路を含むことを特徴とする高次のフィル

ター回路。

【請求項11】

請求項5乃至10のいずれか記載のフィルター回路と、

前記フィルター回路の出力に接続され、前記フィルター回路の出力を減衰させる減衰回

路とを含むことを特徴とする多出力フィルター回路。

【請求項12】

請求項11において、

前記減衰回路は、

演算増幅器と、

一端が前記演算増幅器の反転入力端子に電気的に接続される第1の入力容量と、

一端が前記演算増幅器の反転入力端子に電気的に接続される第1の積分容量と、

一端が前記演算増幅器の出力端子に電気的に接続される第2の積分容量とを含み、

前記第1の入力容量は、前記第1の期間において他端が前記フィルター回路の出力に電

気的に接続され、前記第2の期間において他端が接地電位と電気的に接続され、

前記第1の積分容量は、前記第1の期間において他端が接地電位と電気的に接続され、

前記第2の期間において前記演算増幅器の出力端子に電気的に接続され、

前記第2の積分容量は、前記第1の期間において他端が前記反転入力端子に電気的に接

続され、前記第2の期間において他端が接地電位と電気的に接続されることを特徴とする

多出力フィルター回路。

【請求項13】

振動子と、

前記振動子と発振ループを形成し、該振動子に駆動振動を励振する駆動回路と、

請求項11又は12記載の多出力フィルター回路を有し、前記振動子に励振される駆動

振動及び測定すべき物理量に応じて第1の検出信号及び第2の検出信号を出力する検出回

路とを含み、

前記検出回路は、

前記ファイルター回路の出力を前記第1の検出信号として出力し、前記減衰回路の出力

を前記第2の検出信号として出力することを特徴とする物理量測定装置。

【請求項14】

請求項1乃至4のいずれか記載のスイッチトキャパシター積分回路を含むことを特徴と

する電子機器。

【請求項15】

請求項13記載の物理量測定装置を含むことを特徴とする電子機器。

【請求項1】

第1の容量と第2の容量とを有する電圧電荷変換回路と、

前記第1の容量に充電された電荷を積分する電荷積分回路とを含み、

前記電圧電荷変換回路は、

第1の期間において、前記第1の容量に充電された電荷を転送すると共に、入力信号に

対応した電荷を前記第2の容量に充電し、

第2の期間において、前記第2の容量に充電された電荷の一部を前記第1の容量に充電

すると共に、前記入力信号に対応した電荷を前記第1の容量に充電し、

前記電荷積分回路は、

演算増幅器と、

一端が前記演算増幅器の第1の入力端子に接続されるオフセットキャンセル容量と、

第3の期間において前記オフセットキャンセル容量の他端と前記第1の容量の一端とを

電気的に接続する第1のスイッチと、

第4の期間において前記オフセットキャンセル容量の他端を接地電位に接続する第2の

スイッチとを含むことを特徴とするスイッチトキャパシター積分回路。

【請求項2】

請求項1において、

前記電荷積分回路は、

一端が前記演算増幅器の出力端子に接続される積分容量と、

前記第3の期間において前記積分容量の他端と前記第1の入力端子とを電気的に接続す

る第3のスイッチと、

前記第4の期間において前記積分容量の他端と前記オフセットキャンセル容量の他端と

を電気的に接続する第4のスイッチとを含むことを特徴とするスイッチトキャパシター積

分回路。

【請求項3】

請求項1又は2において、

前記第1の期間及び前記第3の期間は、第1のクロックに基づいて規定される期間であ

り、

前記第2の期間及び前記第4の期間は、前記第1のクロックと逆相の第2のクロックに

基づいて規定される期間であることを特徴とするスイッチトキャパシター積分回路。

【請求項4】

請求項3において、

前記第1の期間において、前記スイッチトキャパシター積分回路の出力として前記電荷

積分回路の出力信号を出力する第5のスイッチを含むことを特徴とするスイッチトキャパ

シター積分回路。

【請求項5】

第1のスイッチトキャパシター積分回路と、

前記第1のスイッチトキャパシター積分回路の前段側又は後段側に接続される第2のス

イッチトキャパシター積分回路と、

前記第1のスイッチトキャパシター積分回路及び前記第2のスイッチトキャパシター積

分回路のうち後段側のスイッチトキャパシター積分回路から前段側のスイッチトキャパシ

ター積分回路の帰還経路に挿入される第1の帰還容量と、

前記第2の期間において初期化され、前記第1の期間において前記第1の帰還容量と並

列に設けられる第2の帰還容量とを含み、

前記第1のスイッチキャパシター積分回路及び前記第2のスイッチトキャパシター積分

回路の少なくとも一方は、請求項3記載のスイッチトキャパシター積分回路であることを

特徴とするフィルター回路。

【請求項6】

請求項5において、

前記第1の帰還容量を介した帰還経路に挿入され、前記第1の期間において導通し、前

記第2の期間において遮断される第5のスイッチとを含むことを特徴とするフィルター回

路。

【請求項7】

請求項1乃至4のいずれか記載のスイッチトキャパシター積分回路を含むことを特徴と

するフィルター回路。

【請求項8】

第1のスイッチトキャパシター積分回路と、

相関ダブル・サンプリング積分器を有し、前記第1のスイッチトキャパシター積分回路

の後段側に配置され、第1の期間で電荷を積分するスイッチトキャパシター積分回路と、

前記スイッチトキャパシター積分回路の出力と前記第1のスイッチトキャパシター積分

回路の所与のノードとの間に挿入される帰還容量と、

前記第1の期間において、前記スイッチトキャパシター積分回路の出力と前記帰還容量

の一端とを電気的に接続するスイッチとを含むことを特徴とするフィルター回路。

【請求項9】

第1のスイッチトキャパシター積分回路と、

相関ダブル・サンプリング積分器を有し、前記第1のスイッチトキャパシター積分回路

の後段側に配置され、第1の期間で電荷を積分するスイッチトキャパシター積分回路と、

前記スイッチトキャパシター積分回路の出力と前記第1のスイッチトキャパシター積分

回路の所与のノードとの間に挿入される帰還容量と、

前記第1の期間において、前記ノードと前記帰還容量の一端とを電気的に接続するスイ

ッチとを含むことを特徴とするフィルター回路。

【請求項10】

請求項5乃至9のいずれか記載のフィルター回路を含むことを特徴とする高次のフィル

ター回路。

【請求項11】