スイッチトキャパシター積分回路、フィルター回路、物理量測定装置、及び電子機器

【課題】面積が小さく、消費電流を大幅に低減することができるスイッチトキャパシター積分回路、フィルター回路、物理量測定装置、及び電子機器等を提供する。

【解決手段】スイッチトキャパシター積分回路としての2重正相積分回路10は、第1の容量CAを有し、第1の期間において入力信号に対応した電荷を第1の容量CAに充電する第1の電圧電荷変換回路20と、第2の容量CBを有し、第2の期間において第1の容量CAに充電された電荷の一部を第2の容量CBに充電し、第2の容量CBに充電された電荷の一部を転送する第1の電荷積分回路30とを含む。

【解決手段】スイッチトキャパシター積分回路としての2重正相積分回路10は、第1の容量CAを有し、第1の期間において入力信号に対応した電荷を第1の容量CAに充電する第1の電圧電荷変換回路20と、第2の容量CBを有し、第2の期間において第1の容量CAに充電された電荷の一部を第2の容量CBに充電し、第2の容量CBに充電された電荷の一部を転送する第1の電荷積分回路30とを含む。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、スイッチトキャパシター積分回路、フィルター回路、物理量測定装置、及び電子機器等に関する。

【背景技術】

【0002】

従来より、角速度等の物理量を測定するセンサー回路(広義には、物理量測定装置)は、カメラ機器の手振れ補正、ナビゲーションやデッドレコニング等の位置情報検出、及びモーションアナライザー等の身体運動の検出等に用いられる。このようなセンサー回路には、極めて低いカットオフ周波数を有するフィルター回路が内蔵される。

【0003】

例えば特許文献1〜特許文献3には、スイッチトキャパシター回路により構成され、極めて低いカットオフ周波数を有するフィルター回路が開示されている。特許文献1〜特許文献3に開示されたフィルター回路によれば、演算増幅器の入力容量と積分容量の比を大きくすることなく、極めて低いカットオフ周波数を有するフィルター回路を高精度に実現することができる。

【先行技術文献】

【特許文献】

【0004】

【特許文献1】特開2009−200618号公報

【特許文献2】特開2010−177734号公報

【特許文献3】特開2010−177791号公報

【発明の開示】

【発明が解決しようとする課題】

【0005】

ところで、センサー回路により角速度を検出するために用いる圧電素子(例えば、振動子)においては、駆動方向の共振周波数及びコリオリ力による振動を検出する検出方向の共振周波数について、互いの干渉を避けるために差を設けている。ところが、外乱の影響等により、この共振周波数の差(離調周波数)に相当する振動が圧電素子に加わると、不要な信号となる離調周波数の角速度信号が出力されてしまう。このような不要な信号を抑制するためには、離調周波数を十分大きくすることが考えられるが、駆動方向と検出方向の振動周波数が離れ、共振による感度増大の効果が得られなくなるという問題がある。そのため、この種の不要な信号は、ローパスフィルター回路により抑制する必要が生じる。この場合、ローパスフィルター回路は、できるだけ面積が小さく、消費電流が小さいことが望まれる。

【0006】

本発明は、以上のような技術的課題に鑑みてなされたものである。本発明の幾つかの態様によれば、面積が小さく、消費電流を大幅に低減することができるスイッチトキャパシター積分回路、フィルター回路、物理量測定装置、及び電子機器等を提供することができる。

【課題を解決するための手段】

【0007】

(1)本発明の第1の態様は、スイッチトキャパシター積分回路が、第1の容量を有し、第1の期間において入力信号に対応した電荷を前記第1の容量に充電する第1の電圧電荷変換回路と、第2の容量を有し、第2の期間において前記第1の容量に充電された電荷の一部を前記第2の容量に充電し、前記第2の容量に充電された電荷の一部を転送する第1の電荷積分回路とを含む。

【0008】

本態様においては、第1の容量に入力信号に対応した電荷を充電し、第1の容量に充電された電荷の一部を第2の容量に充電し、第2の容量に充電された電荷の一部を転送する。これにより、演算増幅器を用いることなくスイッチトキャパシター積分回路を提供することができるようになり、面積が小さく、消費電流を大幅に低減することができるようになる。

【0009】

(2)本発明の第2の態様に係るスイッチトキャパシター積分回路は、第1の態様において、入力容量と、第1の演算増幅器と、前記第1の演算増幅器の反転入力端子及び出力端子の間に挿入される第1の積分容量とを有する第1の積分器を含み、前記第2の期間において前記第1の容量に充電された電荷の一部を前記入力容量に充電し、第3の期間において前記入力容量に充電された電荷を前記第1の積分容量に転送する。

【0010】

本態様によれば、第1の積分器を設け、第1の容量に充電された電荷の一部を入力容量に充電し、入力容量に充電された電荷を第1の積分容量に転送するようにしたので、1つの演算増幅器を用いて2重正相積分を行うスイッチトキャパシター積分回路を提供することができるようになる。これにより、面積が小さく、消費電流を大幅に低減するスイッチトキャパシター積分回路を提供することができるようになる。

【0011】

(3)本発明の第3の態様に係るスイッチトキャパシター積分回路では、第2の態様において、前記第2の期間は、前記第1の期間と逆相の期間であり、前記第3の期間は、前記第1の期間と同相の期間である。

【0012】

本態様によれば、2相クロックによりスイッチ動作を行うスイッチを用いて構成される上記のスイッチトキャパシター積分回路を提供することができるようになる。従って、面積が小さく、消費電流を大幅に低減するスイッチトキャパシター積分回路を簡素な構成で提供することができるようになる。

【0013】

(4)本発明の第4の態様に係るスイッチトキャパシター積分回路では、第1の態様において、入力容量と、第2の演算増幅器と、前記第2の演算増幅器の反転入力端子及び出力端子の間に挿入される第2の積分容量とを有する第2の積分器を含み、第3の期間において前記第2の容量に充電された電荷を前記入力容量及び前記第2の積分容量に転送し、第4の期間において前記入力容量に充電された電荷を放電する。

【0014】

本態様によれば、第2の積分器を設け、第1の容量に充電された電荷の一部を入力容量に充電し、入力容量に充電された電荷を第2の積分容量に転送するようにしたので、1つの演算増幅器を用いて2重逆相積分を行うスイッチトキャパシター積分回路を提供することができるようになる。これにより、面積が小さく、消費電流を大幅に低減するスイッチトキャパシター積分回路を提供することができるようになる。

【0015】

(5)本発明の第5の態様に係るスイッチトキャパシター積分回路では、第1の態様において、入力容量と、第3の演算増幅器と、前記第3の演算増幅器の反転入力端子及び出力端子の間に挿入される第3の積分容量とを有する第3の積分器を含み、第3の期間において前記第2の容量に充電された電荷を前記入力容量に充電し、第4の期間において前記入力容量に充電された電荷を前記第3の積分容量に転送する。

【0016】

本態様によれば、第3の積分器を設け、第1の容量に充電された電荷の一部を入力容量に充電し、入力容量に充電された電荷を第1の積分容量に転送するようにしたので、1つの演算増幅器を用いて2重正相積分を行うスイッチトキャパシター積分回路を提供することができるようになる。これにより、面積が小さく、消費電流を大幅に低減するスイッチトキャパシター積分回路を提供することができるようになる。

【0017】

(6)本発明の第6の態様に係るスイッチトキャパシター積分回路では、第3の態様又は第4の態様において、前記第2の期間は、前記第1の期間と逆相の期間であり、前記第3の期間は、前記第1の期間と同相の期間であり、前記第4の期間は、前記第2の期間と同相の期間である。

【0018】

本態様によれば、2相クロックによりスイッチ動作を行うスイッチを用いて構成され、2重積分を行う上記のスイッチトキャパシター積分回路を提供することができるようになる。従って、面積が小さく、消費電流を大幅に低減するスイッチトキャパシター積分回路を簡素な構成で提供することができるようになる。

【0019】

(7)本発明の第7の態様に係るスイッチトキャパシター積分回路では、第2の態様乃至第6の態様のいずれかにおいて、前記第1の容量の容量値、前記第2の容量の容量値、及び前記入力容量の容量値は、整数比である。

【0020】

本態様によれば、上記の効果に加えて、第1の容量の容量値、第2の容量の容量値、及び入力容量の各々の寄生容量の影響を補償することができ、寄生容量の影響を最小限に抑えることができるようになる。

【0021】

(8)本発明の第8の態様は、フィルター回路が、第3の態様のスイッチトキャパシター積分回路と、帰還入力容量と、第3の容量を有し、前記第1の期間において前記第1の演算増幅器の出力信号に対応した電荷を前記第3の容量に充電する第2の電圧電荷変換回路と、第4の容量を有し、前記第2の期間において前記第3の容量に充電された電荷の一部を前記第4の容量に充電し、前記第4の容量に充電された電荷の一部を転送する第2の電荷積分回路とを含み、前記第1の期間において、前記第4の容量に充電された電荷を前記帰還入力容量及び前記第1の積分容量に転送し、前記第2の期間において前記帰還入力容量に充電された電荷を放電する。

【0022】

本態様によれば、1つの演算増幅器を用いて2次のローパスフィルターを構成することができるようになり、面積が小さく、消費電流を大幅に低減するスイッチトキャパシター積分回路を提供することができるようになる。

【0023】

(9)本発明の第9の態様は、フィルター回路が、第4の態様のスイッチトキャパシター積分回路と、帰還入力容量と、第3の容量を有し、前記第2の期間において前記第3の演算増幅器の出力信号に対応した電荷を前記第3の容量に充電する第2の電圧電荷変換回路と、第4の容量を有し、前記第1の期間において前記第3の容量に充電された電荷の一部を前記第4の容量に充電し、前記第4の容量に充電された電荷の一部を転送する第2の電荷積分回路とを含み、前記第2の期間において、前記第4の容量に充電された電荷を前記帰還入力容量及び前記第3の積分容量に転送し、前記第1の期間において前記帰還入力容量に充電された電荷を放電する。

【0024】

本態様によれば、1つの演算増幅器を用いて2次のローパスフィルターを構成することができるようになり、面積が小さく、消費電流を大幅に低減するスイッチトキャパシター積分回路を提供することができるようになる。

【0025】

(10)本発明の第10の態様は、フィルター回路が、第8の態様のフィルター回路を有する第1のフィルター回路と、前記第1のフィルター回路の出力に縦続接続され、第9の態様のフィルター回路を有する第2のフィルター回路とを含む。

【0026】

本態様によれば、最大で2つの演算増幅器を用いて4次のローパスフィルターを構成することができるようになり、面積が小さく、消費電流を大幅に低減するスイッチトキャパシター積分回路を提供することができるようになる。

【0027】

(11)本発明の第11の態様に係るフィルター回路は、第10の態様において、前記第1のフィルター回路を構成する前記第1の演算増幅器と、前記第2のフィルター回路を構成する前記第2の演算増幅器とが時分割で使用されるように構成される。

【0028】

本態様によれば、1つの演算増幅器を用いて4次のローパスフィルターを構成することができるようになり、面積が小さく、消費電流を大幅に低減するスイッチトキャパシター積分回路を提供することができるようになる。

【0029】

(12)本発明の第12の態様に係るフィルター回路は、第8の態様又は第9の態様のフィルター回路を含むn(nは3以上の整数)次のフィルター回路である。

【0030】

本態様によれば、できるだけ少ない数の演算増幅器を用いてフィルターを構成することができるようになり、面積が小さく、消費電流を大幅に低減するスイッチトキャパシター積分回路を提供することができるようになる。

【0031】

(13)本発明の第13の態様は、物理量測定装置が、振動子と、前記振動子と発振ループを形成し、該振動子に駆動振動を励振する駆動回路と、上記のいずれか記載のフィルター回路を有し、前記振動子に励振される駆動振動及び測定すべき物理量に応じて検出信号を出力する検出回路とを含む。

【0032】

本態様によれば、面積が小さく、消費電流を大幅に低減した物理量測定装置を提供することができるようになる。

【0033】

(14)本発明の第14の態様は、電子機器が、上記記載の物理量測定装置を含む。

【0034】

本態様によれば、物理量を測定する機能を有する電子機器の小型化及び低消費電力化に寄与することができるようになる。

【0035】

(15)本発明の第15の態様は、電子機器が、上記のいずれか記載のスイッチトキャパシター積分回路を含む。

【0036】

本態様によれば、電子機器の小型化及び低消費電力化に寄与することができるようになる。

【図面の簡単な説明】

【0037】

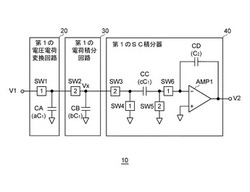

【図1】本発明の一実施形態に係る2重正相積分の構成例の回路図。

【図2】図2(A)は、第1の期間における2重正相積分回路の等価回路を示す図。図2(B)は、第2の期間における2重正相積分回路の等価回路を示す図。

【図3】式(4)の前半の有損失積分を表す部分をz関数で表した場合とs関数で近似した場合の関係の説明図。

【図4】一般的な2重正相積分回路のシグナルフローの一例を示す図。

【図5】図1の2重正相積分回路の寄生容量の説明図。

【図6】本発明の一実施形態に係る2重逆相積分回路の構成例の回路図。

【図7】一般的な2重逆相積分回路のシグナルフローの一例を示す図。

【図8】本発明の一実施形態に係る2重正相積分回路の他の構成例の回路図。

【図9】一般的な2次LPFのシグナルフローの一例を示す図。

【図10】本発明の一実施形態に係る2次LPFの構成例の回路図。

【図11】図10の2次LPFの周波数特性の計算結果の一例を示す図。

【図12】本発明の一実施形態に係る2次LPFの他の構成例の回路図。

【図13】図12の2次LPFの周波数特性の計算結果の一例を示す図。

【図14】本発明の一実施形態に係る4次LPFの構成例の回路図。

【図15】図14の4次LPFの周波数特性の計算結果の一例を示す図。

【図16】1つの演算増幅器を時分割使用したときの4次LPFの構成例の回路図。

【図17】本発明の一実施形態に係る3次LPFの構成例の回路図。

【図18】図17の3次LPFのシグナルフローを示す図。

【図19】図18の3次LPFの周波数特性の計算結果の一例を示す図。

【図20】1つの演算増幅器を時分割使用したときの3次LPFの構成例の回路図。

【図21】本実施形態におけるセンサー回路の構成例のブロック図。

【図22】本実施形態における電子機器の構成例のブロック図。

【発明を実施するための形態】

【0038】

以下、本発明の実施の形態について図面を用いて詳細に説明する。なお、以下に説明する実施の形態は、特許請求の範囲に記載された本発明の内容を不当に限定するものではない。また以下で説明される構成のすべてが本発明の課題を解決するために必須の構成要件であるとは限らない。

【0039】

1. スイッチトキャパシター(Switched Capacitor:SC)積分回路

1.1 2重正相積分回路

図1に、本発明の一実施形態に係るSC積分回路としての2重正相積分の構成例の回路図を示す。

【0040】

2重正相積分回路10は、第1の電圧電荷変換回路20と、第1の電荷積分回路30と、第1のSC積分器(第1の積分器)40とを備えている。第1の電圧電荷積分回路20及び第1の電荷積分回路30は、SC積分回路を構成し、有損失積分を行う。第1のSC積分器40は、演算増幅器を備え、無損失積分を行う。

【0041】

第1の電圧電荷積分回路20は、最小容量値をC1としたときに容量値がa×C1(aは正の整数)の第1の容量CAを有し、第1の期間T1において入力電圧V1(入力信号)に対応した電荷を第1の容量CAに充電する。第2の電荷積分回路30は、最小容量値をC1としたときに容量値がb×C1(bは正の整数)の第2の容量CBを有する。第2の電荷積分回路30は、第2の期間T2において第1の容量CAに充電された電荷の一部を第2の容量CBに充電し、第2の容量CBに充電された電荷の一部を第1のSC積分器40に転送することができる。ここで、第2の期間T2は、第1の期間T1に続く期間である。

【0042】

このような2重正相積分回路10において、第1の電圧電荷変換回路20は、入力電圧V1が入力される入力端と、第1の容量CAの一端との間に挿入されるスイッチSW1を備えることができる。第1の容量CAの他端は接地され、スイッチSW1がオンしたとき、第1の容量CAの両端に入力電圧V1が印加される。また、第1の電荷積分回路30は、第1の容量CAの一端と第2の容量CBの一端との間に挿入されるスイッチSW2を備えることができる。第2の容量CBの他端は接地され、スイッチSW2がオンしたとき、第1の容量CAの一端と第2の容量CBの一端とが電気的に接続される。

【0043】

ここで、スイッチSW1,SW2は、それぞれ2相クロックのいずれか一方によりオンオフ制御される。図1では、各スイッチには、「1」と表記されるスイッチと、「2」と表記されるスイッチの2種類がある。「1」と表記されるスイッチは、第1のクロックCLK1で動作するスイッチ(第1のフェーズスイッチ)であり、第1の期間T1でオンとなる。「2」と表記されるスイッチは、第2のクロックCLK2で動作するスイッチ(第2のフェーズスイッチ)であり、第1の期間T1と逆相の第2の期間T2でオンとなる。

【0044】

第1のSC積分器40は、容量値がc×C1(cは正の整数)の入力容量CCと、第1の演算増幅器AMP1と、第1の演算増幅器AMP1の反転入力端子及び出力端子の間に挿入され容量値がC2である第1の積分容量CDとを備えている。第1のSC積分器40は、第2の期間T2において第1の容量CAに充電された電荷の一部を入力容量CCに充電し、第3の期間T3において入力容量CCに充電された電荷を第1の積分容量CDに転送する。ここで、第3の期間T3は、第2の期間T2に続く期間である。

【0045】

このような第1のSC積分器40は、スイッチSW3,SW4,SW5,SW6を備えることができる。スイッチSW3は、第1の電荷積分回路30の第2の容量CBの一端と入力容量CCの一端との間に挿入される。スイッチSW4は、入力容量CCの一端と接地電位との間に挿入される。スイッチSW5は、入力容量CCの他端と接地電位との間に挿入される。スイッチSW6は、入力容量CCの他端と第1の演算増幅器AMP1の反転入力端子との間に挿入される。

【0046】

ここで、第3の期間T3が、第1の期間T1と同相の期間であるものとすると、スイッチSW4,SW6を第1のフェーズスイッチとし、スイッチSW3,SW5を第2のフェーズスイッチとすることができる。そのため、図1では、スイッチSW4,SW6を「1」と表記し、スイッチSW3,SW5を「2」と表記している。即ち、第1のSC積分器40は、クロール型のSC積分器である。

【0047】

図2(A)、図2(B)に、図1の2重正相積分10の動作説明図を示す。図2(A)は、第1の期間T1における2重正相積分回路10の等価回路を表す。図2(B)は、第2の期間T2における2重正相積分回路10の等価回路を表す。

【0048】

第2の容量CBの一端のノードの電圧Vx、第1の積分容量CDに電荷が転送される時刻をnとすると、式(1)、式(2)が成り立つ。式(1)及び式(2)では、図1で説明した容量値を用いている。

【数1】

【数2】

【0049】

式(1)についてz関数のVx(z)、式(2)についてz関数のV2(z)を求めると、式(3)のようになる。

【数3】

【0050】

式(3)より、2重正相積分回路10の伝達関数は、式(4)のように求められる。

【数4】

【0051】

式(4)において、前半のaz−1/2/(a+b+c−bz−1)は有損失積分であることを表し、後半のcC1z−1/2/C2(1−z−1)は無損失積分であることを表す。

【0052】

ここで、式(4)をs変数で表すことを考える。式(4)の前半の有損失積分を表す部分は、次のように変形することができる。

【数5】

【0053】

式(5)において、ωT/2≪1とすると、cos(ωT/2)は1に近似することができ、sin(ωT/2)は(ωT/2)に近似することができる。従って、式(5)は、次式のように表すことができる。

【数6】

【0054】

この結果、式(4)についてs変数を用いた場合は、次式のように表すことができる。

【数7】

【0055】

図3に、式(4)の前半の有損失積分を表す部分をz関数で表した場合とs関数で近似した場合の関係の説明図を示す。図3は、横軸に周波数、縦軸にゲインを表し、一例としてa=1、b=79、c=1としたときのz関数及びs関数の関係を表している。

【0056】

図3に示すように、10kHz以上の周波数帯域からz関数とs関数とで誤差が大きくなるものの、低周波数帯域では、z関数とs関数との誤差はほとんど無視することができる。即ち、図3は、低周波数帯域において式(5)、式(6)のようにs変数で表すことの妥当性を示している。

【0057】

ここで、2重正相積分回路のシグナルフローについて考える。

図4に、一般的な2重正相積分回路のシグナルフローの一例を示す。図4では、図1と同様に、入力電圧V1、出力電圧V2として表記している。

【0058】

図4と式(7)とを比較すると、図4のα,k1,k2は、次のように当てはめることができる。

【数8】

【0059】

従って、図1の構成によれば、1つの演算増幅器を用いたSC回路により2重積分回路を構成することができ、面積が小さく、消費電流を大幅に低減することができるSC積分回路を提供することができる。

【0060】

また、図1の構成によれば、第1の容量CAの容量値、第2の容量CBの容量値、及び入力容量CCの容量値が整数比となるように構成することで、第1の容量CA、第2の容量CB及び入力容量CCの各々の寄生容量の影響を補償することができる。これにより、寄生容量の影響を最小限に抑えることができる。

【0061】

図5に、図1の2重正相積分回路10の寄生容量の説明図を示す。図5において、図1と同様の部分には同一符号を付し、適宜説明を省略する。

【0062】

ここでは、容量Cを形成したときに寄生容量Cpが寄生すると考えることができる。(第1の容量CAの容量値):(第2の容量CBの容量値):(入力容量CCの容量値)=a:b:cであるため、第1の容量CAの一端が接続されるノードには、寄生容量Cpa=a×Cpが寄生する。同様に、第2の容量CBの一端が接続されるノードには、寄生容量Cpb=b×Cpが寄生する。また、入力容量CCの一端が接続されるノードには、寄生容量Cpc=c×Cpが寄生する。

【0063】

寄生容量Cpa,Cpb,Cpcを考慮した場合、式(3)は、次式のように表すことができるが、分子と分母で寄生容量分が相殺されるため、2重正相積分回路10の伝達関数は、式(4)と同じものとなる。即ち、第1の容量CAの容量値、第2の容量CBの容量値、及び入力容量CCの容量値が整数比となるように構成することで、式(9)に示すように寄生容量の影響が相殺され、寄生容量の影響を補償することができる。

【数9】

【0064】

1.2 2重逆相積分回路

図1では、2重正相積分回路を示したが、2重逆相積分回路についても同様である。

図6に、本発明の一実施形態に係るSC積分回路としての2重逆相積分回路の構成例の回路図を示す。

【0065】

2重逆相積分回路10aは、第2の電圧電荷変換回路20aと、第2の電荷積分回路30aと、第2のSC積分器(第2の積分器)40aとを備えている。2重逆相積分回路10aが2重正相積分回路10と異なる主な点は、第1のSC積分器40に代えて設けられる第2のSC積分器40aがバタフライ型のSC積分器である点である。第2の電圧電荷積分回路20a及び第2の電荷積分回路30aは、SC積分回路を構成し、有損失積分を行う。第2のSC積分器40aは、演算増幅器を備え、無損失積分を行う。

【0066】

第2の電圧電荷変換回路20aが第1の電圧電荷変換回路20と異なる点は、第1の容量CAaの容量値であり、第1の電圧電荷変換回路20と同様の動作を行う。第2の電圧電荷変換回路20aは、最小容量値をC12としたときに容量値がd×C12(dは正の整数)の第1の容量CAaを有する。第2の電荷積分回路30aが第1の電荷積分回路30と異なる点は、第2の容量CBaの容量値であり、第1の電荷積分回路30と同様の動作を行う。第2の電荷積分回路30aは、最小容量値をC12としたときに容量値がe×C12(eは正の整数)の第2の容量CBaを有する。

【0067】

第2のSC積分器40aは、容量値がf×C12(fは正の整数)の入力容量CCaと、第2の演算増幅器AMP2と、第2の演算増幅器AMP2の反転入力端子及び出力端子の間に挿入され容量値がC22である第2の積分容量CDaとを備えている。第2のSC積分器40aは、第3の期間T3において第2の容量CBaに充電された電荷を入力容量CCa及び第2の積分容量CDaに転送する。具体的には、第3の期間T3では、第2の容量CBaに充電された電荷が入力容量CCaに転送された結果、該入力容量CCaにその電荷量分だけ第2の積分容量CDaに転送する。その後、第2のSC積分器40aは、第4の期間T4において入力容量CCaに充電された電荷を放電する。ここで、第3の期間T3は、第2の期間T2に続く期間であり、第4の期間T4は、第3の期間T3に続く期間である。

【0068】

このような第2のSC積分器40aは、スイッチSW3a,SW4a,SW5a,SW6aを備えることができる。スイッチSW3aは、第2の電荷積分回路30aの第2の容量CBaの一端と入力容量CCaの一端との間に挿入される。スイッチSW4aは、入力容量CCaの一端と接地電位との間に挿入される。スイッチSW5aは、入力容量CCaの他端と接地電位との間に挿入される。スイッチSW6aは、入力容量CCaの他端と第2の演算増幅器AMP2の反転入力端子との間に挿入される。

【0069】

ここで、第3の期間T3が、第1の期間T1と同相の期間であり、第4の期間T4が第2の期間T2と同相の期間であるものとする。このとき、スイッチSW3a,SW6aを第1のフェーズスイッチとし、スイッチSW4a,SW5aを第2のフェーズスイッチとすることができる。そのため、図6では、スイッチSW3a,SW6aを「1」と表記し、スイッチSW4a,SW5aを「2」と表記している。即ち、第2のSC積分器40aは、バタフライ型のSC積分器である。

【0070】

2重逆相積分回路10aについて、2重正相積分回路10と同様に、伝達関数を求めると、次式のようになる。

【数10】

【0071】

式(10)について、式(5)及び式(6)と同様にs変数で表すと、次式のようになる。

【数11】

【0072】

式(11)において、分母にsTe2を含む部分が有損失積分を表す部分であり、分母がC22Tsを含む部分が無損失積分を表す部分である。

【0073】

図7に、一般的な2重逆相積分回路のシグナルフローの一例を示す。図7では、図4と同様に、入力電圧V1、出力電圧V2として表記している

【0074】

図7と式(11)とを比較すると、図7のβ,k1,k2は、次のように当てはめることができる。

【数12】

【0075】

従って、図6の構成によれば、図1と同様に、1つの演算増幅器を用いたSC回路により2重積分回路を構成することができ、面積が小さく、消費電流を大幅に低減することができるSC積分回路を提供することができる。また、図6の構成においても、第1の容量CAaの容量値、第2の容量CBaの容量値、及び入力容量CCaの容量値が整数比となるように構成することで、第1の容量CAa、第2の容量CBa及び入力容量CCaの各々の寄生容量の影響を補償することができる。

【0076】

1.3 他の2重正相積分回路

図1では、第1の演算増幅器AMP1を含む第1のSC積分器40が第1の期間T1において積分動作を行う2重正相積分回路を示したが、電荷積分回路の後段に接続されるSC積分器が第2の期間T2において積分動作を行ってもよい。

【0077】

図8に、本発明の一実施形態に係るSC積分回路としての2重正相積分回路の他の構成例の回路図を示す。

【0078】

2重正相積分回路10bは、第3の電圧電荷変換回路20bと、第3の電荷積分回路30bと、第3のSC積分器(第3の積分器)40bとを備えている。2重正相積分回路10bが2重正相積分回路10と異なる主な点は、第1のSC積分器40に代えて設けられる第3のSC積分器40bが第2の期間T2で積分動作を行うクロール型のSC積分器である点である。第3の電圧電荷積分回路20b及び第3の電荷積分回路30bは、SC積分回路を構成し、有損失積分を行う。第3のSC積分器40bは、演算増幅器を備え、無損失積分を行う。

【0079】

第3の電圧電荷変換回路20bが第1の電圧電荷変換回路20と異なる点は、第1の容量CAbの容量値であり、第1の電圧電荷変換回路20と同様の動作を行う。第3の電圧電荷変換回路20bは、最小容量値をC21としたときに容量値がa´×C21(a´は正の整数)の第1の容量CAbを有する。第3の電荷積分回路30bが第1の電荷積分回路30と異なる点は、第2の容量CBbの容量値であり、第1の電荷積分回路30と同様の動作を行う。第3の電荷積分回路30bは、最小容量値をC21としたときに容量値がb´×C21(b´は正の整数)の第2の容量CBbを有する。

【0080】

第3のSC積分器40bは、容量値がc´×C21(c´は正の整数)の入力容量CCbと、第3の演算増幅器AMP3と、第3の演算増幅器AMP3の反転入力端子及び出力端子の間に挿入され容量値がC2´である第3の積分容量CDbとを備えている。第3のSC積分器40bは、第3の期間T3において第2の容量CBbに充電された電荷を入力容量CCbに充電し、第4の期間T4において入力容量CCbに充電された電荷を第3の積分容量CDbに転送する。ここで、第3の期間T3は、第2の期間T2に続く期間であり、第4の期間T4は、第3の期間T3に続く期間である。

【0081】

このような第3のSC積分器40bは、スイッチSW3b,SW4b,SW5b,SW6bを備えることができる。スイッチSW3bは、第3の電荷積分回路30bの第2の容量CBbの一端と入力容量CCbの一端との間に挿入される。スイッチSW4bは、入力容量CCbの一端と接地電位との間に挿入される。スイッチSW5bは、入力容量CCbの他端と接地電位との間に挿入される。スイッチSW6bは、入力容量CCbの他端と第3の演算増幅器AMP3の反転入力端子との間に挿入される。

【0082】

ここで、第3の期間T3が、第1の期間T1と同相の期間であり、第4の期間T4が第2の期間T2と同相の期間であるものとする。このとき、スイッチSW3b,SW5bを第1のフェーズスイッチとし、スイッチSW4b,SW6bを第2のフェーズスイッチとすることができる。そのため、図8では、スイッチSW3b,SW5bを「1」と表記し、スイッチSW4b,SW6bを「2」と表記している。

【0083】

2重正相積分回路10bについて、2重正相積分回路10と同様に、伝達関数を求めると、次式のようになる。

【数13】

【0084】

式(13)について、式(5)及び式(6)と同様にs変数を用いて表すと、次式のようになる。

【数14】

【0085】

式(14)において、分母にsTb´2を含む部分が有損失積分を表す部分であり、分母がC2´Tsを含む部分が無損失積分を表す部分である。

【0086】

一般的な2重正相積分回路のシグナルフローを表す図4と式(14)とを比較すると、図4のα,k1,k2は、次のように当てはめることができる。

【数15】

【0087】

従って、図8の構成によれば、図1と同様に、1つの演算増幅器を用いたSC回路により2重積分回路を構成することができ、面積が小さく、消費電流を大幅に低減することができるSC積分回路を提供することができる。また、図8の構成においても、第1の容量CAbの容量値、第2の容量CBbの容量値、及び入力容量CCbの容量値が整数比となるように構成することで、第1の容量CAb、第2の容量CBb及び入力容量CCbの各々の寄生容量の影響を補償することができる。

【0088】

2. フィルター回路

2.1 2次ローパスフィルター

一般的な2次ローパスフィルター(Low Pass Filter:以下、LPF)(広義にはフィルター回路)は、図4の2重正相積分回路のシグナルフローと図7の2重逆相積分回路のシグナルフローとを用いて次のように表すことができる。

【0089】

図9に、一般的な2次LPFのシグナルフローの一例を示す。図9において、図4又は図7と同様の部分には同一符号を付し、適宜説明を省略する。

【0090】

図9のシグナルフローから、次式のような関係が成り立つ。

【数16】

【0091】

式(16)について伝達関数を求めると、次式のようになる。

【数17】

【0092】

一方、2次LPFの一般的な伝達関数T(s)は、直流ゲインをK、Q値をQ、カットオフ角周波数(cutoff angular frequency)をω0とすると、次式のように表すことができる。

【数18】

【0093】

式(17)と式(18)とを係数比較することで、α,k1,k2をK,Q,ω0,βで表すことができる。

【数19】

【0094】

図10に、本発明の一実施形態に係る2次LPFの構成例の回路図を示す。図10において、図1又は図6と同様の部分には同一符号を付し、適宜説明を省略する。

【0095】

2次LPF100は、図1に示す2重正相積分回路10と、帰還入力容量と、第2の電圧電荷変換回路20aと、第2の電荷積分回路30aとを備える2次バタワースLPFである。帰還入力容量は、図6の入力容量CCaに相当する。そして、2重正相積分回路10の出力信号が、第2の電圧電荷変換回路20a、第2の電荷積分回路30a及び帰還入力容量を介して、第2の2重正相積分回路10を構成する第1の演算増幅器AMP1の反転入力端子に帰還される。

【0096】

第2の電圧電荷変換回路20aは、第3の容量を有し、第1の期間T1において第1の演算増幅器AMP1の出力信号に対応した電荷を第3の容量に充電する。第3の容量は、図6の第1の容量CAaに対応し、図10では第3の容量をCAa(容量値d×C11)と表記している。第2の電荷積分回路30aは、第4の容量を有し、第2の期間T2において第3の容量(CAa)に充電された電荷の一部を第4の容量に充電し、第4の容量に充電された電荷の一部を帰還入力容量に転送する。第4の容量は、図6の第2の容量CBaに対応し、図10では第4の容量をCBa(容量値e×C11)と表記している。そして、2次LPF100は、第1の期間T1において、第4の容量(CBa)に充電された電荷を帰還入力容量(CCa)及び第1の積分容量CDに転送し、第2の期間T2において帰還入力容量(CCa)に充電された電荷を放電する。ここで、帰還入力容量の容量値は、f×C11であるものとする。このような2次LPF100は、図6と同様のスイッチを備え、図10では、図6と同様の符号を付している。

【0097】

図10の構成において、k1,k2はQやカットオフ周波数によって決まるため、式(19)、式(8)、及び式(12)から各素子の値を決めることができる。a=b=1としたとき、次のようになる。

【数20】

【0098】

同様に、d=f=1としたとき、次のようになる。

【数21】

【0099】

ここで、低周波数帯域では1/(ω0T)≫1であるため、K=1のときC1,C11が最小になる可能性があり、β=1/2として最小容量を1に正規化すると、次のように各素子の値を決定することができる。

【数22】

【0100】

図11に、図10の2次LPF100の周波数特性の計算結果の一例を示す。図11は、横軸に周波数、縦軸にゲインをとり、計算結果を実線で示し、シミュレーション結果を点で示している。

【0101】

ここでは、K=0[dB]、ω0=2π×200[rad/s]、T=1/5000[s]、Q=2−1/2、最小容量を0.1pFとすると、aC1=0.1pF、bC1=5.5pF、cC1=0.1pF、dC11=0.1pF、eC11=5.6pF、fC11=0.1pF、C2=2.8pFとしている。この結果、1つの演算増幅器を用いて、−40[dB/DEC]で減衰する2次LPFを構成することができる。しかも、総容量値が14.3pF、最小容量値と最大容量値との比である素子値の広がりを56(=5.6/0.1)に抑えた2次LPFを提供することができるようになる。従って、面積が小さく、消費電流を大幅に低減することができるフィルター回路を提供することができるようになる。

【0102】

2.2 他の2次LPF

図10では、第1の期間T1において動作する演算増幅器を1つ用いて2次LPFを構成する例を説明したが、第2の期間T2において動作する演算増幅器を1つ用いて2次LPFを構成することができる。

【0103】

図12に、本発明の一実施形態に係る2次LPFの他の構成例の回路図を示す。図12において、図6又は図8と同様の部分には同一符号を付し、適宜説明を省略する。

【0104】

2次LPF100aは、図8に示す2重正相積分回路10bと、帰還入力容量と、第2の電圧電荷変換回路20aと、第2の電荷積分回路30aとを備える2次バタワースLPFである。帰還入力容量は、図6の入力容量CCaに相当する。2重正相積分回路10bの出力信号が、第2の電圧電荷変換回路20a、第2の電荷積分回路30a及び帰還入力容量を介して、2重正相積分回路10bを構成する第3の演算増幅器AMP3の反転入力端子に帰還される。

【0105】

即ち、第2の電圧電荷変換回路20aは、第3の容量を有し、第2の期間T2において第3の演算増幅器AMP3の出力信号に対応した電荷を第3の容量に充電する。第3の容量は、図6の第1の容量CAaに対応し、図12では第3の容量をCAa(容量値d´×C11´)と表記している。第2の電荷積分回路30aは、第4の容量を有し、第1の期間T1において第3の容量(CAa)に充電された電荷の一部を第4の容量に充電し、第4の容量に充電された電荷の一部を転送する。第4の容量は、図6の第2の容量CBaに対応し、図12では第4の容量をCBa(容量値e´×C11´)と表記している。そして、2次LPF100aは、第2の期間T2において、第4の容量(CBa)に充電された電荷を帰還入力容量(CCa、容量値f´×C11´)及び第3の積分容量CDbに転送する。この2次LPF100aは、第1の期間T1において帰還入力容量(CCa)に充電された電荷を放電する。このような2次LPF100aは、図6と同様のスイッチを備え、図12では、図6と同様の符号を付している。なお、図12では、第2の電圧電荷変換回路20a、第2の電荷積分回路30aや帰還入力容量に接続されるスイッチの構成は、図10と同様であるが、各々が逆相のスイッチに入れ替わっている。

【0106】

図12の構成においても、図10と同様に、次のように各素子の値を決定することができる。以下の式は、式(22)と同じ値となる。

【数23】

【0107】

図13に、図12の2次LPF100aの周波数特性の計算結果の一例を示す。図13は、横軸に周波数、縦軸にゲインをとり、計算結果を実線で示し、シミュレーション結果を点で示している。

【0108】

ここでは、図11と同じ条件で計算した結果、図10と同じ素子値となる。従って、図12の構成においても、1つの演算増幅器を用いて、−40[dB/DEC]で減衰する2次LPFを構成することができる。しかも、総容量値が14.3pF、素子値の広がりを56に抑えた2次LPFを提供することができるようになる。従って、面積が小さく、消費電流を大幅に低減することができるフィルター回路を提供することができるようになる。

【0109】

2.3 4次LPF

2.3.1 原理構成

図10の2次LPF100の出力に、図12の2次LPF100aを縦続接続することで、4次LPFを構成することができる。

【0110】

図14に、本発明の一実施形態に係る4次LPFの構成例の回路図を示す。図14において、図10又は図12と同様の部分には同一符号を付し、適宜説明を省略する。

【0111】

4次LPF200は、第1のフィルター回路として図10の2次LPF100と、第2のフィルター回路として図12の2次LPF100aとを備える4次バタワースLPFである。ここで、2次LPF100aは、2次LPF100の出力に縦続接続される。

【0112】

4次LPF200は、例えば2次LPF100のQ値を「1.3065」、2次LPF100aのQ値を「0.541196」とすることで実現することができる。このとき、2次LPF100の各素子の値、2次LPF100aの各素子の値は、式(22)、式(23)により決定される。

【0113】

図15に、図14の4次LPF200の周波数特性の計算結果の一例を示す。図15は、横軸に周波数、縦軸にゲインをとり、計算結果を実線で示し、シミュレーション結果を点で示している。

【0114】

ここでは、K=0[dB]、ω0=2π×200[rad/s]、T=1/5000[s]、2次LPF100のQ=1.3065、2次LPF100aのQ=0.541196、最小容量を0.1pFとする。このとき、aC1=0.1pF、bC1=10.3pF、cC1=0.1pF、dC11=0.1pF、eC11=10.4pF、fC11=0.1pF、C2=1.5pFとなる。同様に、a´C1´=0.1pF、b´C1´=4.2pF、c´C1´=0.1pF、d´C11´=0.1pF、e´C11´=4.3pF、f´C11´=0.1pF、C2´=3.7pFとなる。この結果、2つの演算増幅器を用いて、−80[dB/DEC]で減衰する4次LPFを構成することができる。しかも、総容量値が35.2pF、素子値の広がりを104(=10.4/0.1)に抑えた4次LPFを提供することができるようになる。従って、面積が小さく、消費電流を大幅に低減することができるフィルター回路を提供することができるようになる。

【0115】

2.3.2 時分割使用構成

図14に示す4次LPF200では、2次LPF100を構成する第1の演算増幅器AMP1が第1の期間T1において積分動作を行い、2次LPF100aを構成する第3の演算増幅器AMP3が第2の期間T2において積分動作を行う。そこで、1つの演算増幅器を時分割使用して、第1の期間T1では第1の演算増幅器AMP1として機能させ、第2の期間T2では第3の演算増幅器AMP3として機能させることで、1つの演算増幅器を用いて4次LPFを提供することができる。

【0116】

図16に、1つの演算増幅器を時分割使用したときの4次LPFの構成例の回路図を示す。図16において、図14と同様の部分には同一符号を付し、適宜説明を省略する。

【0117】

4次LPF200aが図14の4次LPF200と異なる点は、演算増幅器が1つで構成された点と、第1の積分容量CDの両端に第1のフェーズスイッチが設けられ、且つ第3の積分容量CDbの両端に第2のフェーズスイッチが設けられた点である。更に、4次LPF200aの出力部に第2のフェーズスイッチが設けられている。

【0118】

これにより、4次LPF200aによれば、1つの演算増幅器を用いて4次LPFを提供することができるようになる。また、出力部にスイッチを設けるようにしたので、正確な4次LPFの処理後の出力電圧V3を取り出すことができるようになる。

【0119】

2.4 3次LPF

2.4.1 原理構成

4次LPFに限らず3次LPFについても、上記の2次LPFを用いることで構成することができる。

【0120】

図17に、本発明の一実施形態に係る3次LPFの構成例の回路図を示す。図17において、図10と同様の部分には同一符号を付し、適宜説明を省略する。

【0121】

3次LPF300は、図10の2次LPF100と、1次LPF310とを備える3次バタワースLPFである。ここで、1次LPF310は、2次LPF100の出力に縦続接続される。1次LPF310は、公知の1次LPFとすることができる。例えば、1次LPF310は、演算増幅器AMP4と、演算増幅器AMP4の反転入力端子と出力端子との間に挿入される積分容量Cyと、第2の期間T2において積分容量Cyと並列に接続される積分容量Czと、入力容量Cxとを備えることができる。入力容量Cxは、第1の期間T1において2次LPF100の出力電圧V2に対応した電荷を充電する。そして、第2の期間T2において、入力容量Cxに充電された電荷が、積分容量Cy,Czに転送される。なお、積分容量Czに充電された電荷は、第1の期間T1において放電される。

【0122】

図18に、図17の3次LPF300のシグナルフローを示す。図18において、図9と同様の部分には同一符号を付し、適宜説明を省略する。

【0123】

この場合も係数比較を行うことで、図18に示すように、k1,k2,k3,αを、Q,ω0,βを用いて各々表すことができる。

【0124】

図19に、図18の3次LPF300の周波数特性の計算結果の一例を示す。図19は、横軸に周波数、縦軸にゲインをとり、計算結果を実線で示し、シミュレーション結果を点で示している。

【0125】

ここで、K=0[dB]、ω0=2π×200[rad/s]、T=1/5000[s]、Q=1、最小容量を0.1pFとする。このとき、aC1=0.1pF、bC1=7.9pF、cC1=0.1pF、dC11=0.1pF、eC11=8.0pF、fC11=0.1pF、C2=2.0pF、Cx=0.1pF、Cy=3.9pF、Cz=0.1pFとすることができる。この結果、2つの演算増幅器を用いて、−60[dB/DEC]で減衰する3次LPFを構成することができる。しかも、総容量値が22.4pF、素子値の広がりを80(=8.0/0.1)に抑えた3次LPFを提供することができるようになる。従って、面積が小さく、消費電流を大幅に低減することができるフィルター回路を提供することができるようになる。

【0126】

2.4.2 時分割使用構成

図18に示す3次LPF300では、2次LPF100を構成する第1の演算増幅器AMP1が第1の期間T1において積分動作を行い、1次LPF310を構成する演算増幅器AMP4が第2の期間T2において積分動作を行う。そこで、1つの演算増幅器を時分割使用して、第1の期間T1では第1の演算増幅器AMP1として機能させ、第2の期間T2では演算増幅器AMP4として機能させることで、1つの演算増幅器を用いて3次LPFを提供することができる。

【0127】

図20に、1つの演算増幅器を時分割使用したときの3次LPFの構成例の回路図を示す。図20において、図17と同様の部分には同一符号を付し、適宜説明を省略する。

【0128】

3次LPF300aが図17の3次LPF300と異なる点は、演算増幅器が1つで構成された点と、積分容量Cyの両端に第2のフェーズスイッチが設けられた点である。更に、3次LPF300aの出力部に第2のフェーズスイッチが設けられている。

【0129】

これにより、3次LPF300aによれば、1つの演算増幅器を用いて3次LPFを提供することができるようになる。また、出力部にスイッチを設けるようにしたので、正確な3次LPFの処理後の出力電圧V3を取り出すことができるようになる。

【0130】

3. 物理量測定装置

上記で説明した2次LPF、3次LPF、又は4次LPFは、センサー回路に適用することにより、高精度なセンシングを行う物理量測定装置を提供することができるようになる。

【0131】

図21に、上記の2次LPF、3次LPF、又は4次LPFのいずれかが適用されたセンサー回路の構成例を示す。なお、この回路構成は一例であり、例えば回路の細部の構成が変形される場合もあり得る。

【0132】

センサー回路400は、角速度を測定対象の物理量とする物理量測定装置である。センサー回路400は、駆動回路(駆動装置)500と、検出回路(検出装置)600とを備えている。このセンサー回路400は、圧電材料で形成され、駆動振動片及び検出振動片を有する振動片(振動子、広義には圧電素子)510を含む。

【0133】

駆動回路500は、駆動振動片に設けられた駆動電極512a,512bを介して駆動振動片を発振ループ内に設け、駆動振動片(広義には振動子)を励振させる。駆動回路500は、電流電圧変換器520、オートゲインコントロール(Auto Gain Control:以下、AGC)回路530、帯域通過フィルター(Band Pass Filter:以下、BPF)540を備えている。更に、駆動回路500は、ゲインコントロールアンプ(Gain Control Amplifier:以下、GCA)550、2値化回路560を備えている。

【0134】

駆動振動片の駆動電極512aは、電流電圧変換器520の入力に電気的に接続され、電流電圧変換器520の出力は、AGC回路530及びBPF540に入力される。BPF540は、発振ループ内の発振信号の位相調整回路として機能し、BPF540の出力は、GCA550及び2値化回路560に入力される。AGC回路530は、電流電圧変換器520の出力に基づいて、GCA550のゲインを制御する。GCA550の出力は、駆動振動片の駆動電極512bに電気的に接続される。2値化回路560は、発振ループ内の発振信号を2値化し、参照信号として検出回路600に出力する。なお、図21では、駆動回路500の内部に振動片510の駆動振動片を設けるものとして説明したが、駆動回路500の外部に振動片510の駆動振動片が設けられていてもよい。

【0135】

検出回路600は、交流増幅回路610と、同期検波回路620と、直流増幅器630と、LPF640とを備えている。LPF640は、上記の2次LPF、3次LPF、又は4次LPFである。交流増幅回路610は、第1の電流電圧変換器612と、第2の電流電圧変換器614と、交流増幅器616と、BPF618とを含む。

【0136】

駆動回路500では、上記の構成の発振ループ内のゲインが「1」より大きい状態で発振スタートする。この時点では、駆動振動片への入力は雑音のみであるが、この雑音は、目的とする駆動振動の固有共振周波数を含む幅広い周波数の波動を含む。振動片510の駆動振動片の周波数フィルター作用によって、目的とする固有共振周波数の波動を多く含む信号が出力され、この信号が電流電圧変換器5210において電圧値に変換される。AGC回路530は、この電圧値に基づいてGCA550のゲインを制御することで発振ループ内の発振振幅を制御する。発振ループ内でこうした操作が繰り返されることにより、目的とする固有共振周波数の信号の割合が高くなる。そして、GCA550のゲイン制御によって、次第に発振ループを信号が1周する間の利得(ループゲイン)が「1」となり、この状態で駆動振動片が安定発振する。

【0137】

駆動振動片を励振させて安定発振状態になり、振動片510を所与の方向に回転させると、コリオリ力が振動片510に作用し、検出振動片が屈曲振動する。検出振動片には検出電極514a,514b,516a,516bが設けられる。検出電極514b,516bにはアナログ接地電位が供給され、検出電極514a,516aは、交流増幅回路610の第1の電流電圧変換器612及び第2の電流電圧変換器614に接続される。検出回路600は、検出電極514a,516aからの互いに極性が異なる検出信号を交流増幅した後、駆動回路500からの参照信号を用いて同期検波して、LPF640で検出信号OUTを出力する。

【0138】

以上のように、センサー回路400は、振動片510と、駆動回路500と、検出回路600とを備えることができる。駆動回路500は、振動片510と発振ループを形成し、該振動片に駆動振動を励振する。検出回路600は、上記のいずれかのフィルター回路を有し振動片510に励振される駆動振動及び測定すべき物理量に応じて検出信号を出力する。

【0139】

4. 電子機器

上記のセンサー回路は、次のような電子機器に搭載することができる。このような電子機器によれば、所望の信号伝達関数で動作し、且つ高精度なセンシングを容易に実現できるようになる。

【0140】

図22に、本実施形態における電子機器のハードウェア構成例のブロック図を示す。

【0141】

電子機器700は、センサー回路400と、A/D変換回路710と、クロック生成回路720と、中央演算処理装置等の処理部730と、メモリー740と、操作部750と、表示部760とを備えている。電子機器700を構成する各部は、バス(BUS)によって相互に接続されている。なお、A/D変換回路710は、処理部730に内蔵されていてもよい。

【0142】

例えば、処理部730は、メモリー740から読み込んだプログラムに従って処理を実行し、センサー回路400で検出された検出信号の振幅又は感度に応じてA/D変換回路710で変換されたディジタル値を用いて積分を行う。こうすることで、角速度及び回転角度を算出する。そして、処理部730は、算出した角速度又は回転角度に対応した処理を実行し、該処理に対応した表示データを生成し、表示部760に表示させる処理を行う。

【0143】

以上、本発明に係るSC積分回路、フィルター回路、物理量測定装置及び電子機器を上記の実施形態に基づいて説明したが、本発明は上記の実施形態に限定されるものではない。本発明は、その要旨を逸脱しない範囲において種々の態様において実施することが可能であり、例えば次のような変形も可能である。

【0144】

(1)上記の実施形態では、フィルター回路として、図10、図12、図14、図16、図17、又は図20を例に説明したが、本発明はこれらに限定されるものではない。

【0145】

(2)上記の実施形態では、フィルター回路として、2次LPF、3次LPF又は4次LPFを例に説明したが、図10又は図12の2次LPFを備えるn(nは3以上の整数)次のLPFに適用することができる。

【0146】

(3)上記の実施形態では、検出回路600が備えるLPF640として、上記の実施形態における2次LPF、3次LPF又は4次LPFを採用するものとして説明したが、本発明は、これに限定されるものではない。検出回路600が備えるLPF640は、例えば図10又は図12の2次LPFを備えるn(nは3以上の整数)次のLPFを採用することができる。

【0147】

(4)上記の実施形態では、電子機器が、上記のLPFが適用される例を説明したが、本発明はこれに限定されるものではない。本発明に係る電子機器が、上記のSC積分回路としての2重積分回路(2重正相積分回路、2重逆相積分回路)を備えていてもよい。

【符号の説明】

【0148】

10,10b…2重正相積分回路、 10a…2重逆相積分回路、

20…第1の電圧電荷変換回路、 20a…第2の電圧電荷変換回路、

20b…第3の電圧電荷変換回路、 30…第1の電荷積分回路、

30a…第2の電荷積分回路、 30b…第3の電荷積分回路、

40…第1のSC積分器、 40a…第2のSC積分器、 40b…第3のSC積分器、

100,100a…2次LPF、 200,200a…4次LPF、

300,300a…3次LPF、 400…センサー回路、

500…駆動回路(駆動装置)、 510…振動片(振動子)、

512a,512b…駆動電極、

514a,514b,516a,516b…検出電極、 520…電流電圧変換器、

530…AGC回路、 540,618…BPF、 550…GCA、

560…2値化回路、 600…検出回路(検出装置)、 610…交流増幅回路、

612…第1の電流電圧変換器、 614…第2の電流電圧変換器、

616…交流増幅器、 620…同期検波回路、 630…直流増幅器、

640…LPF、 700…電子機器、 710…A/D変換回路、

720…クロック生成回路、 730…処理部、 740…メモリー、

750…操作部、 760…表示部、 AMP…演算増幅器、

AMP1…第1の演算増幅器、 AMP2…第2の演算増幅器、

AMP3…第3の演算増幅器、 CA,CAa,CAb…第1の容量、

CB,CBa,CBb…第2の容量、 CC,CCa,CCb,Cx…入力容量、

CD…第1の積分容量、 CDa…第2の積分容量、 CDb…第3の積分容量、

Cy,Cz…積分容量、 SW1,SW2,SW3,SW3a,SW3b,SW4,SW4a,SW4b,SW5,SW5a,SW5b,SW6,SW6a,SW6b…スイッチ、 V1…入力電圧(入力信号)、 V2…出力電圧(出力信号)

【技術分野】

【0001】

本発明は、スイッチトキャパシター積分回路、フィルター回路、物理量測定装置、及び電子機器等に関する。

【背景技術】

【0002】

従来より、角速度等の物理量を測定するセンサー回路(広義には、物理量測定装置)は、カメラ機器の手振れ補正、ナビゲーションやデッドレコニング等の位置情報検出、及びモーションアナライザー等の身体運動の検出等に用いられる。このようなセンサー回路には、極めて低いカットオフ周波数を有するフィルター回路が内蔵される。

【0003】

例えば特許文献1〜特許文献3には、スイッチトキャパシター回路により構成され、極めて低いカットオフ周波数を有するフィルター回路が開示されている。特許文献1〜特許文献3に開示されたフィルター回路によれば、演算増幅器の入力容量と積分容量の比を大きくすることなく、極めて低いカットオフ周波数を有するフィルター回路を高精度に実現することができる。

【先行技術文献】

【特許文献】

【0004】

【特許文献1】特開2009−200618号公報

【特許文献2】特開2010−177734号公報

【特許文献3】特開2010−177791号公報

【発明の開示】

【発明が解決しようとする課題】

【0005】

ところで、センサー回路により角速度を検出するために用いる圧電素子(例えば、振動子)においては、駆動方向の共振周波数及びコリオリ力による振動を検出する検出方向の共振周波数について、互いの干渉を避けるために差を設けている。ところが、外乱の影響等により、この共振周波数の差(離調周波数)に相当する振動が圧電素子に加わると、不要な信号となる離調周波数の角速度信号が出力されてしまう。このような不要な信号を抑制するためには、離調周波数を十分大きくすることが考えられるが、駆動方向と検出方向の振動周波数が離れ、共振による感度増大の効果が得られなくなるという問題がある。そのため、この種の不要な信号は、ローパスフィルター回路により抑制する必要が生じる。この場合、ローパスフィルター回路は、できるだけ面積が小さく、消費電流が小さいことが望まれる。

【0006】

本発明は、以上のような技術的課題に鑑みてなされたものである。本発明の幾つかの態様によれば、面積が小さく、消費電流を大幅に低減することができるスイッチトキャパシター積分回路、フィルター回路、物理量測定装置、及び電子機器等を提供することができる。

【課題を解決するための手段】

【0007】

(1)本発明の第1の態様は、スイッチトキャパシター積分回路が、第1の容量を有し、第1の期間において入力信号に対応した電荷を前記第1の容量に充電する第1の電圧電荷変換回路と、第2の容量を有し、第2の期間において前記第1の容量に充電された電荷の一部を前記第2の容量に充電し、前記第2の容量に充電された電荷の一部を転送する第1の電荷積分回路とを含む。

【0008】

本態様においては、第1の容量に入力信号に対応した電荷を充電し、第1の容量に充電された電荷の一部を第2の容量に充電し、第2の容量に充電された電荷の一部を転送する。これにより、演算増幅器を用いることなくスイッチトキャパシター積分回路を提供することができるようになり、面積が小さく、消費電流を大幅に低減することができるようになる。

【0009】

(2)本発明の第2の態様に係るスイッチトキャパシター積分回路は、第1の態様において、入力容量と、第1の演算増幅器と、前記第1の演算増幅器の反転入力端子及び出力端子の間に挿入される第1の積分容量とを有する第1の積分器を含み、前記第2の期間において前記第1の容量に充電された電荷の一部を前記入力容量に充電し、第3の期間において前記入力容量に充電された電荷を前記第1の積分容量に転送する。

【0010】

本態様によれば、第1の積分器を設け、第1の容量に充電された電荷の一部を入力容量に充電し、入力容量に充電された電荷を第1の積分容量に転送するようにしたので、1つの演算増幅器を用いて2重正相積分を行うスイッチトキャパシター積分回路を提供することができるようになる。これにより、面積が小さく、消費電流を大幅に低減するスイッチトキャパシター積分回路を提供することができるようになる。

【0011】

(3)本発明の第3の態様に係るスイッチトキャパシター積分回路では、第2の態様において、前記第2の期間は、前記第1の期間と逆相の期間であり、前記第3の期間は、前記第1の期間と同相の期間である。

【0012】

本態様によれば、2相クロックによりスイッチ動作を行うスイッチを用いて構成される上記のスイッチトキャパシター積分回路を提供することができるようになる。従って、面積が小さく、消費電流を大幅に低減するスイッチトキャパシター積分回路を簡素な構成で提供することができるようになる。

【0013】

(4)本発明の第4の態様に係るスイッチトキャパシター積分回路では、第1の態様において、入力容量と、第2の演算増幅器と、前記第2の演算増幅器の反転入力端子及び出力端子の間に挿入される第2の積分容量とを有する第2の積分器を含み、第3の期間において前記第2の容量に充電された電荷を前記入力容量及び前記第2の積分容量に転送し、第4の期間において前記入力容量に充電された電荷を放電する。

【0014】

本態様によれば、第2の積分器を設け、第1の容量に充電された電荷の一部を入力容量に充電し、入力容量に充電された電荷を第2の積分容量に転送するようにしたので、1つの演算増幅器を用いて2重逆相積分を行うスイッチトキャパシター積分回路を提供することができるようになる。これにより、面積が小さく、消費電流を大幅に低減するスイッチトキャパシター積分回路を提供することができるようになる。

【0015】

(5)本発明の第5の態様に係るスイッチトキャパシター積分回路では、第1の態様において、入力容量と、第3の演算増幅器と、前記第3の演算増幅器の反転入力端子及び出力端子の間に挿入される第3の積分容量とを有する第3の積分器を含み、第3の期間において前記第2の容量に充電された電荷を前記入力容量に充電し、第4の期間において前記入力容量に充電された電荷を前記第3の積分容量に転送する。

【0016】

本態様によれば、第3の積分器を設け、第1の容量に充電された電荷の一部を入力容量に充電し、入力容量に充電された電荷を第1の積分容量に転送するようにしたので、1つの演算増幅器を用いて2重正相積分を行うスイッチトキャパシター積分回路を提供することができるようになる。これにより、面積が小さく、消費電流を大幅に低減するスイッチトキャパシター積分回路を提供することができるようになる。

【0017】

(6)本発明の第6の態様に係るスイッチトキャパシター積分回路では、第3の態様又は第4の態様において、前記第2の期間は、前記第1の期間と逆相の期間であり、前記第3の期間は、前記第1の期間と同相の期間であり、前記第4の期間は、前記第2の期間と同相の期間である。

【0018】

本態様によれば、2相クロックによりスイッチ動作を行うスイッチを用いて構成され、2重積分を行う上記のスイッチトキャパシター積分回路を提供することができるようになる。従って、面積が小さく、消費電流を大幅に低減するスイッチトキャパシター積分回路を簡素な構成で提供することができるようになる。

【0019】

(7)本発明の第7の態様に係るスイッチトキャパシター積分回路では、第2の態様乃至第6の態様のいずれかにおいて、前記第1の容量の容量値、前記第2の容量の容量値、及び前記入力容量の容量値は、整数比である。

【0020】

本態様によれば、上記の効果に加えて、第1の容量の容量値、第2の容量の容量値、及び入力容量の各々の寄生容量の影響を補償することができ、寄生容量の影響を最小限に抑えることができるようになる。

【0021】

(8)本発明の第8の態様は、フィルター回路が、第3の態様のスイッチトキャパシター積分回路と、帰還入力容量と、第3の容量を有し、前記第1の期間において前記第1の演算増幅器の出力信号に対応した電荷を前記第3の容量に充電する第2の電圧電荷変換回路と、第4の容量を有し、前記第2の期間において前記第3の容量に充電された電荷の一部を前記第4の容量に充電し、前記第4の容量に充電された電荷の一部を転送する第2の電荷積分回路とを含み、前記第1の期間において、前記第4の容量に充電された電荷を前記帰還入力容量及び前記第1の積分容量に転送し、前記第2の期間において前記帰還入力容量に充電された電荷を放電する。

【0022】

本態様によれば、1つの演算増幅器を用いて2次のローパスフィルターを構成することができるようになり、面積が小さく、消費電流を大幅に低減するスイッチトキャパシター積分回路を提供することができるようになる。

【0023】

(9)本発明の第9の態様は、フィルター回路が、第4の態様のスイッチトキャパシター積分回路と、帰還入力容量と、第3の容量を有し、前記第2の期間において前記第3の演算増幅器の出力信号に対応した電荷を前記第3の容量に充電する第2の電圧電荷変換回路と、第4の容量を有し、前記第1の期間において前記第3の容量に充電された電荷の一部を前記第4の容量に充電し、前記第4の容量に充電された電荷の一部を転送する第2の電荷積分回路とを含み、前記第2の期間において、前記第4の容量に充電された電荷を前記帰還入力容量及び前記第3の積分容量に転送し、前記第1の期間において前記帰還入力容量に充電された電荷を放電する。

【0024】

本態様によれば、1つの演算増幅器を用いて2次のローパスフィルターを構成することができるようになり、面積が小さく、消費電流を大幅に低減するスイッチトキャパシター積分回路を提供することができるようになる。

【0025】

(10)本発明の第10の態様は、フィルター回路が、第8の態様のフィルター回路を有する第1のフィルター回路と、前記第1のフィルター回路の出力に縦続接続され、第9の態様のフィルター回路を有する第2のフィルター回路とを含む。

【0026】

本態様によれば、最大で2つの演算増幅器を用いて4次のローパスフィルターを構成することができるようになり、面積が小さく、消費電流を大幅に低減するスイッチトキャパシター積分回路を提供することができるようになる。

【0027】

(11)本発明の第11の態様に係るフィルター回路は、第10の態様において、前記第1のフィルター回路を構成する前記第1の演算増幅器と、前記第2のフィルター回路を構成する前記第2の演算増幅器とが時分割で使用されるように構成される。

【0028】

本態様によれば、1つの演算増幅器を用いて4次のローパスフィルターを構成することができるようになり、面積が小さく、消費電流を大幅に低減するスイッチトキャパシター積分回路を提供することができるようになる。

【0029】

(12)本発明の第12の態様に係るフィルター回路は、第8の態様又は第9の態様のフィルター回路を含むn(nは3以上の整数)次のフィルター回路である。

【0030】

本態様によれば、できるだけ少ない数の演算増幅器を用いてフィルターを構成することができるようになり、面積が小さく、消費電流を大幅に低減するスイッチトキャパシター積分回路を提供することができるようになる。

【0031】

(13)本発明の第13の態様は、物理量測定装置が、振動子と、前記振動子と発振ループを形成し、該振動子に駆動振動を励振する駆動回路と、上記のいずれか記載のフィルター回路を有し、前記振動子に励振される駆動振動及び測定すべき物理量に応じて検出信号を出力する検出回路とを含む。

【0032】

本態様によれば、面積が小さく、消費電流を大幅に低減した物理量測定装置を提供することができるようになる。

【0033】

(14)本発明の第14の態様は、電子機器が、上記記載の物理量測定装置を含む。

【0034】

本態様によれば、物理量を測定する機能を有する電子機器の小型化及び低消費電力化に寄与することができるようになる。

【0035】

(15)本発明の第15の態様は、電子機器が、上記のいずれか記載のスイッチトキャパシター積分回路を含む。

【0036】

本態様によれば、電子機器の小型化及び低消費電力化に寄与することができるようになる。

【図面の簡単な説明】

【0037】

【図1】本発明の一実施形態に係る2重正相積分の構成例の回路図。

【図2】図2(A)は、第1の期間における2重正相積分回路の等価回路を示す図。図2(B)は、第2の期間における2重正相積分回路の等価回路を示す図。

【図3】式(4)の前半の有損失積分を表す部分をz関数で表した場合とs関数で近似した場合の関係の説明図。

【図4】一般的な2重正相積分回路のシグナルフローの一例を示す図。

【図5】図1の2重正相積分回路の寄生容量の説明図。

【図6】本発明の一実施形態に係る2重逆相積分回路の構成例の回路図。

【図7】一般的な2重逆相積分回路のシグナルフローの一例を示す図。

【図8】本発明の一実施形態に係る2重正相積分回路の他の構成例の回路図。

【図9】一般的な2次LPFのシグナルフローの一例を示す図。

【図10】本発明の一実施形態に係る2次LPFの構成例の回路図。

【図11】図10の2次LPFの周波数特性の計算結果の一例を示す図。

【図12】本発明の一実施形態に係る2次LPFの他の構成例の回路図。

【図13】図12の2次LPFの周波数特性の計算結果の一例を示す図。

【図14】本発明の一実施形態に係る4次LPFの構成例の回路図。

【図15】図14の4次LPFの周波数特性の計算結果の一例を示す図。

【図16】1つの演算増幅器を時分割使用したときの4次LPFの構成例の回路図。

【図17】本発明の一実施形態に係る3次LPFの構成例の回路図。

【図18】図17の3次LPFのシグナルフローを示す図。

【図19】図18の3次LPFの周波数特性の計算結果の一例を示す図。

【図20】1つの演算増幅器を時分割使用したときの3次LPFの構成例の回路図。

【図21】本実施形態におけるセンサー回路の構成例のブロック図。

【図22】本実施形態における電子機器の構成例のブロック図。

【発明を実施するための形態】

【0038】

以下、本発明の実施の形態について図面を用いて詳細に説明する。なお、以下に説明する実施の形態は、特許請求の範囲に記載された本発明の内容を不当に限定するものではない。また以下で説明される構成のすべてが本発明の課題を解決するために必須の構成要件であるとは限らない。

【0039】

1. スイッチトキャパシター(Switched Capacitor:SC)積分回路

1.1 2重正相積分回路

図1に、本発明の一実施形態に係るSC積分回路としての2重正相積分の構成例の回路図を示す。

【0040】

2重正相積分回路10は、第1の電圧電荷変換回路20と、第1の電荷積分回路30と、第1のSC積分器(第1の積分器)40とを備えている。第1の電圧電荷積分回路20及び第1の電荷積分回路30は、SC積分回路を構成し、有損失積分を行う。第1のSC積分器40は、演算増幅器を備え、無損失積分を行う。

【0041】

第1の電圧電荷積分回路20は、最小容量値をC1としたときに容量値がa×C1(aは正の整数)の第1の容量CAを有し、第1の期間T1において入力電圧V1(入力信号)に対応した電荷を第1の容量CAに充電する。第2の電荷積分回路30は、最小容量値をC1としたときに容量値がb×C1(bは正の整数)の第2の容量CBを有する。第2の電荷積分回路30は、第2の期間T2において第1の容量CAに充電された電荷の一部を第2の容量CBに充電し、第2の容量CBに充電された電荷の一部を第1のSC積分器40に転送することができる。ここで、第2の期間T2は、第1の期間T1に続く期間である。

【0042】

このような2重正相積分回路10において、第1の電圧電荷変換回路20は、入力電圧V1が入力される入力端と、第1の容量CAの一端との間に挿入されるスイッチSW1を備えることができる。第1の容量CAの他端は接地され、スイッチSW1がオンしたとき、第1の容量CAの両端に入力電圧V1が印加される。また、第1の電荷積分回路30は、第1の容量CAの一端と第2の容量CBの一端との間に挿入されるスイッチSW2を備えることができる。第2の容量CBの他端は接地され、スイッチSW2がオンしたとき、第1の容量CAの一端と第2の容量CBの一端とが電気的に接続される。

【0043】

ここで、スイッチSW1,SW2は、それぞれ2相クロックのいずれか一方によりオンオフ制御される。図1では、各スイッチには、「1」と表記されるスイッチと、「2」と表記されるスイッチの2種類がある。「1」と表記されるスイッチは、第1のクロックCLK1で動作するスイッチ(第1のフェーズスイッチ)であり、第1の期間T1でオンとなる。「2」と表記されるスイッチは、第2のクロックCLK2で動作するスイッチ(第2のフェーズスイッチ)であり、第1の期間T1と逆相の第2の期間T2でオンとなる。

【0044】

第1のSC積分器40は、容量値がc×C1(cは正の整数)の入力容量CCと、第1の演算増幅器AMP1と、第1の演算増幅器AMP1の反転入力端子及び出力端子の間に挿入され容量値がC2である第1の積分容量CDとを備えている。第1のSC積分器40は、第2の期間T2において第1の容量CAに充電された電荷の一部を入力容量CCに充電し、第3の期間T3において入力容量CCに充電された電荷を第1の積分容量CDに転送する。ここで、第3の期間T3は、第2の期間T2に続く期間である。

【0045】

このような第1のSC積分器40は、スイッチSW3,SW4,SW5,SW6を備えることができる。スイッチSW3は、第1の電荷積分回路30の第2の容量CBの一端と入力容量CCの一端との間に挿入される。スイッチSW4は、入力容量CCの一端と接地電位との間に挿入される。スイッチSW5は、入力容量CCの他端と接地電位との間に挿入される。スイッチSW6は、入力容量CCの他端と第1の演算増幅器AMP1の反転入力端子との間に挿入される。

【0046】

ここで、第3の期間T3が、第1の期間T1と同相の期間であるものとすると、スイッチSW4,SW6を第1のフェーズスイッチとし、スイッチSW3,SW5を第2のフェーズスイッチとすることができる。そのため、図1では、スイッチSW4,SW6を「1」と表記し、スイッチSW3,SW5を「2」と表記している。即ち、第1のSC積分器40は、クロール型のSC積分器である。

【0047】

図2(A)、図2(B)に、図1の2重正相積分10の動作説明図を示す。図2(A)は、第1の期間T1における2重正相積分回路10の等価回路を表す。図2(B)は、第2の期間T2における2重正相積分回路10の等価回路を表す。

【0048】

第2の容量CBの一端のノードの電圧Vx、第1の積分容量CDに電荷が転送される時刻をnとすると、式(1)、式(2)が成り立つ。式(1)及び式(2)では、図1で説明した容量値を用いている。

【数1】

【数2】

【0049】

式(1)についてz関数のVx(z)、式(2)についてz関数のV2(z)を求めると、式(3)のようになる。

【数3】

【0050】

式(3)より、2重正相積分回路10の伝達関数は、式(4)のように求められる。

【数4】

【0051】

式(4)において、前半のaz−1/2/(a+b+c−bz−1)は有損失積分であることを表し、後半のcC1z−1/2/C2(1−z−1)は無損失積分であることを表す。

【0052】

ここで、式(4)をs変数で表すことを考える。式(4)の前半の有損失積分を表す部分は、次のように変形することができる。

【数5】

【0053】

式(5)において、ωT/2≪1とすると、cos(ωT/2)は1に近似することができ、sin(ωT/2)は(ωT/2)に近似することができる。従って、式(5)は、次式のように表すことができる。

【数6】

【0054】

この結果、式(4)についてs変数を用いた場合は、次式のように表すことができる。

【数7】

【0055】

図3に、式(4)の前半の有損失積分を表す部分をz関数で表した場合とs関数で近似した場合の関係の説明図を示す。図3は、横軸に周波数、縦軸にゲインを表し、一例としてa=1、b=79、c=1としたときのz関数及びs関数の関係を表している。

【0056】

図3に示すように、10kHz以上の周波数帯域からz関数とs関数とで誤差が大きくなるものの、低周波数帯域では、z関数とs関数との誤差はほとんど無視することができる。即ち、図3は、低周波数帯域において式(5)、式(6)のようにs変数で表すことの妥当性を示している。

【0057】

ここで、2重正相積分回路のシグナルフローについて考える。

図4に、一般的な2重正相積分回路のシグナルフローの一例を示す。図4では、図1と同様に、入力電圧V1、出力電圧V2として表記している。

【0058】

図4と式(7)とを比較すると、図4のα,k1,k2は、次のように当てはめることができる。

【数8】

【0059】

従って、図1の構成によれば、1つの演算増幅器を用いたSC回路により2重積分回路を構成することができ、面積が小さく、消費電流を大幅に低減することができるSC積分回路を提供することができる。

【0060】

また、図1の構成によれば、第1の容量CAの容量値、第2の容量CBの容量値、及び入力容量CCの容量値が整数比となるように構成することで、第1の容量CA、第2の容量CB及び入力容量CCの各々の寄生容量の影響を補償することができる。これにより、寄生容量の影響を最小限に抑えることができる。

【0061】

図5に、図1の2重正相積分回路10の寄生容量の説明図を示す。図5において、図1と同様の部分には同一符号を付し、適宜説明を省略する。

【0062】

ここでは、容量Cを形成したときに寄生容量Cpが寄生すると考えることができる。(第1の容量CAの容量値):(第2の容量CBの容量値):(入力容量CCの容量値)=a:b:cであるため、第1の容量CAの一端が接続されるノードには、寄生容量Cpa=a×Cpが寄生する。同様に、第2の容量CBの一端が接続されるノードには、寄生容量Cpb=b×Cpが寄生する。また、入力容量CCの一端が接続されるノードには、寄生容量Cpc=c×Cpが寄生する。

【0063】

寄生容量Cpa,Cpb,Cpcを考慮した場合、式(3)は、次式のように表すことができるが、分子と分母で寄生容量分が相殺されるため、2重正相積分回路10の伝達関数は、式(4)と同じものとなる。即ち、第1の容量CAの容量値、第2の容量CBの容量値、及び入力容量CCの容量値が整数比となるように構成することで、式(9)に示すように寄生容量の影響が相殺され、寄生容量の影響を補償することができる。

【数9】

【0064】

1.2 2重逆相積分回路

図1では、2重正相積分回路を示したが、2重逆相積分回路についても同様である。

図6に、本発明の一実施形態に係るSC積分回路としての2重逆相積分回路の構成例の回路図を示す。

【0065】

2重逆相積分回路10aは、第2の電圧電荷変換回路20aと、第2の電荷積分回路30aと、第2のSC積分器(第2の積分器)40aとを備えている。2重逆相積分回路10aが2重正相積分回路10と異なる主な点は、第1のSC積分器40に代えて設けられる第2のSC積分器40aがバタフライ型のSC積分器である点である。第2の電圧電荷積分回路20a及び第2の電荷積分回路30aは、SC積分回路を構成し、有損失積分を行う。第2のSC積分器40aは、演算増幅器を備え、無損失積分を行う。

【0066】

第2の電圧電荷変換回路20aが第1の電圧電荷変換回路20と異なる点は、第1の容量CAaの容量値であり、第1の電圧電荷変換回路20と同様の動作を行う。第2の電圧電荷変換回路20aは、最小容量値をC12としたときに容量値がd×C12(dは正の整数)の第1の容量CAaを有する。第2の電荷積分回路30aが第1の電荷積分回路30と異なる点は、第2の容量CBaの容量値であり、第1の電荷積分回路30と同様の動作を行う。第2の電荷積分回路30aは、最小容量値をC12としたときに容量値がe×C12(eは正の整数)の第2の容量CBaを有する。

【0067】

第2のSC積分器40aは、容量値がf×C12(fは正の整数)の入力容量CCaと、第2の演算増幅器AMP2と、第2の演算増幅器AMP2の反転入力端子及び出力端子の間に挿入され容量値がC22である第2の積分容量CDaとを備えている。第2のSC積分器40aは、第3の期間T3において第2の容量CBaに充電された電荷を入力容量CCa及び第2の積分容量CDaに転送する。具体的には、第3の期間T3では、第2の容量CBaに充電された電荷が入力容量CCaに転送された結果、該入力容量CCaにその電荷量分だけ第2の積分容量CDaに転送する。その後、第2のSC積分器40aは、第4の期間T4において入力容量CCaに充電された電荷を放電する。ここで、第3の期間T3は、第2の期間T2に続く期間であり、第4の期間T4は、第3の期間T3に続く期間である。

【0068】

このような第2のSC積分器40aは、スイッチSW3a,SW4a,SW5a,SW6aを備えることができる。スイッチSW3aは、第2の電荷積分回路30aの第2の容量CBaの一端と入力容量CCaの一端との間に挿入される。スイッチSW4aは、入力容量CCaの一端と接地電位との間に挿入される。スイッチSW5aは、入力容量CCaの他端と接地電位との間に挿入される。スイッチSW6aは、入力容量CCaの他端と第2の演算増幅器AMP2の反転入力端子との間に挿入される。

【0069】

ここで、第3の期間T3が、第1の期間T1と同相の期間であり、第4の期間T4が第2の期間T2と同相の期間であるものとする。このとき、スイッチSW3a,SW6aを第1のフェーズスイッチとし、スイッチSW4a,SW5aを第2のフェーズスイッチとすることができる。そのため、図6では、スイッチSW3a,SW6aを「1」と表記し、スイッチSW4a,SW5aを「2」と表記している。即ち、第2のSC積分器40aは、バタフライ型のSC積分器である。

【0070】

2重逆相積分回路10aについて、2重正相積分回路10と同様に、伝達関数を求めると、次式のようになる。

【数10】

【0071】

式(10)について、式(5)及び式(6)と同様にs変数で表すと、次式のようになる。

【数11】

【0072】

式(11)において、分母にsTe2を含む部分が有損失積分を表す部分であり、分母がC22Tsを含む部分が無損失積分を表す部分である。

【0073】

図7に、一般的な2重逆相積分回路のシグナルフローの一例を示す。図7では、図4と同様に、入力電圧V1、出力電圧V2として表記している

【0074】

図7と式(11)とを比較すると、図7のβ,k1,k2は、次のように当てはめることができる。

【数12】

【0075】

従って、図6の構成によれば、図1と同様に、1つの演算増幅器を用いたSC回路により2重積分回路を構成することができ、面積が小さく、消費電流を大幅に低減することができるSC積分回路を提供することができる。また、図6の構成においても、第1の容量CAaの容量値、第2の容量CBaの容量値、及び入力容量CCaの容量値が整数比となるように構成することで、第1の容量CAa、第2の容量CBa及び入力容量CCaの各々の寄生容量の影響を補償することができる。

【0076】

1.3 他の2重正相積分回路

図1では、第1の演算増幅器AMP1を含む第1のSC積分器40が第1の期間T1において積分動作を行う2重正相積分回路を示したが、電荷積分回路の後段に接続されるSC積分器が第2の期間T2において積分動作を行ってもよい。

【0077】

図8に、本発明の一実施形態に係るSC積分回路としての2重正相積分回路の他の構成例の回路図を示す。

【0078】

2重正相積分回路10bは、第3の電圧電荷変換回路20bと、第3の電荷積分回路30bと、第3のSC積分器(第3の積分器)40bとを備えている。2重正相積分回路10bが2重正相積分回路10と異なる主な点は、第1のSC積分器40に代えて設けられる第3のSC積分器40bが第2の期間T2で積分動作を行うクロール型のSC積分器である点である。第3の電圧電荷積分回路20b及び第3の電荷積分回路30bは、SC積分回路を構成し、有損失積分を行う。第3のSC積分器40bは、演算増幅器を備え、無損失積分を行う。

【0079】

第3の電圧電荷変換回路20bが第1の電圧電荷変換回路20と異なる点は、第1の容量CAbの容量値であり、第1の電圧電荷変換回路20と同様の動作を行う。第3の電圧電荷変換回路20bは、最小容量値をC21としたときに容量値がa´×C21(a´は正の整数)の第1の容量CAbを有する。第3の電荷積分回路30bが第1の電荷積分回路30と異なる点は、第2の容量CBbの容量値であり、第1の電荷積分回路30と同様の動作を行う。第3の電荷積分回路30bは、最小容量値をC21としたときに容量値がb´×C21(b´は正の整数)の第2の容量CBbを有する。

【0080】

第3のSC積分器40bは、容量値がc´×C21(c´は正の整数)の入力容量CCbと、第3の演算増幅器AMP3と、第3の演算増幅器AMP3の反転入力端子及び出力端子の間に挿入され容量値がC2´である第3の積分容量CDbとを備えている。第3のSC積分器40bは、第3の期間T3において第2の容量CBbに充電された電荷を入力容量CCbに充電し、第4の期間T4において入力容量CCbに充電された電荷を第3の積分容量CDbに転送する。ここで、第3の期間T3は、第2の期間T2に続く期間であり、第4の期間T4は、第3の期間T3に続く期間である。

【0081】

このような第3のSC積分器40bは、スイッチSW3b,SW4b,SW5b,SW6bを備えることができる。スイッチSW3bは、第3の電荷積分回路30bの第2の容量CBbの一端と入力容量CCbの一端との間に挿入される。スイッチSW4bは、入力容量CCbの一端と接地電位との間に挿入される。スイッチSW5bは、入力容量CCbの他端と接地電位との間に挿入される。スイッチSW6bは、入力容量CCbの他端と第3の演算増幅器AMP3の反転入力端子との間に挿入される。

【0082】

ここで、第3の期間T3が、第1の期間T1と同相の期間であり、第4の期間T4が第2の期間T2と同相の期間であるものとする。このとき、スイッチSW3b,SW5bを第1のフェーズスイッチとし、スイッチSW4b,SW6bを第2のフェーズスイッチとすることができる。そのため、図8では、スイッチSW3b,SW5bを「1」と表記し、スイッチSW4b,SW6bを「2」と表記している。

【0083】

2重正相積分回路10bについて、2重正相積分回路10と同様に、伝達関数を求めると、次式のようになる。

【数13】

【0084】

式(13)について、式(5)及び式(6)と同様にs変数を用いて表すと、次式のようになる。

【数14】

【0085】

式(14)において、分母にsTb´2を含む部分が有損失積分を表す部分であり、分母がC2´Tsを含む部分が無損失積分を表す部分である。

【0086】

一般的な2重正相積分回路のシグナルフローを表す図4と式(14)とを比較すると、図4のα,k1,k2は、次のように当てはめることができる。

【数15】

【0087】

従って、図8の構成によれば、図1と同様に、1つの演算増幅器を用いたSC回路により2重積分回路を構成することができ、面積が小さく、消費電流を大幅に低減することができるSC積分回路を提供することができる。また、図8の構成においても、第1の容量CAbの容量値、第2の容量CBbの容量値、及び入力容量CCbの容量値が整数比となるように構成することで、第1の容量CAb、第2の容量CBb及び入力容量CCbの各々の寄生容量の影響を補償することができる。

【0088】

2. フィルター回路

2.1 2次ローパスフィルター

一般的な2次ローパスフィルター(Low Pass Filter:以下、LPF)(広義にはフィルター回路)は、図4の2重正相積分回路のシグナルフローと図7の2重逆相積分回路のシグナルフローとを用いて次のように表すことができる。

【0089】

図9に、一般的な2次LPFのシグナルフローの一例を示す。図9において、図4又は図7と同様の部分には同一符号を付し、適宜説明を省略する。

【0090】

図9のシグナルフローから、次式のような関係が成り立つ。

【数16】

【0091】

式(16)について伝達関数を求めると、次式のようになる。

【数17】

【0092】

一方、2次LPFの一般的な伝達関数T(s)は、直流ゲインをK、Q値をQ、カットオフ角周波数(cutoff angular frequency)をω0とすると、次式のように表すことができる。

【数18】

【0093】

式(17)と式(18)とを係数比較することで、α,k1,k2をK,Q,ω0,βで表すことができる。

【数19】

【0094】

図10に、本発明の一実施形態に係る2次LPFの構成例の回路図を示す。図10において、図1又は図6と同様の部分には同一符号を付し、適宜説明を省略する。

【0095】

2次LPF100は、図1に示す2重正相積分回路10と、帰還入力容量と、第2の電圧電荷変換回路20aと、第2の電荷積分回路30aとを備える2次バタワースLPFである。帰還入力容量は、図6の入力容量CCaに相当する。そして、2重正相積分回路10の出力信号が、第2の電圧電荷変換回路20a、第2の電荷積分回路30a及び帰還入力容量を介して、第2の2重正相積分回路10を構成する第1の演算増幅器AMP1の反転入力端子に帰還される。

【0096】

第2の電圧電荷変換回路20aは、第3の容量を有し、第1の期間T1において第1の演算増幅器AMP1の出力信号に対応した電荷を第3の容量に充電する。第3の容量は、図6の第1の容量CAaに対応し、図10では第3の容量をCAa(容量値d×C11)と表記している。第2の電荷積分回路30aは、第4の容量を有し、第2の期間T2において第3の容量(CAa)に充電された電荷の一部を第4の容量に充電し、第4の容量に充電された電荷の一部を帰還入力容量に転送する。第4の容量は、図6の第2の容量CBaに対応し、図10では第4の容量をCBa(容量値e×C11)と表記している。そして、2次LPF100は、第1の期間T1において、第4の容量(CBa)に充電された電荷を帰還入力容量(CCa)及び第1の積分容量CDに転送し、第2の期間T2において帰還入力容量(CCa)に充電された電荷を放電する。ここで、帰還入力容量の容量値は、f×C11であるものとする。このような2次LPF100は、図6と同様のスイッチを備え、図10では、図6と同様の符号を付している。

【0097】

図10の構成において、k1,k2はQやカットオフ周波数によって決まるため、式(19)、式(8)、及び式(12)から各素子の値を決めることができる。a=b=1としたとき、次のようになる。

【数20】

【0098】

同様に、d=f=1としたとき、次のようになる。

【数21】

【0099】

ここで、低周波数帯域では1/(ω0T)≫1であるため、K=1のときC1,C11が最小になる可能性があり、β=1/2として最小容量を1に正規化すると、次のように各素子の値を決定することができる。

【数22】

【0100】

図11に、図10の2次LPF100の周波数特性の計算結果の一例を示す。図11は、横軸に周波数、縦軸にゲインをとり、計算結果を実線で示し、シミュレーション結果を点で示している。

【0101】

ここでは、K=0[dB]、ω0=2π×200[rad/s]、T=1/5000[s]、Q=2−1/2、最小容量を0.1pFとすると、aC1=0.1pF、bC1=5.5pF、cC1=0.1pF、dC11=0.1pF、eC11=5.6pF、fC11=0.1pF、C2=2.8pFとしている。この結果、1つの演算増幅器を用いて、−40[dB/DEC]で減衰する2次LPFを構成することができる。しかも、総容量値が14.3pF、最小容量値と最大容量値との比である素子値の広がりを56(=5.6/0.1)に抑えた2次LPFを提供することができるようになる。従って、面積が小さく、消費電流を大幅に低減することができるフィルター回路を提供することができるようになる。

【0102】

2.2 他の2次LPF

図10では、第1の期間T1において動作する演算増幅器を1つ用いて2次LPFを構成する例を説明したが、第2の期間T2において動作する演算増幅器を1つ用いて2次LPFを構成することができる。

【0103】

図12に、本発明の一実施形態に係る2次LPFの他の構成例の回路図を示す。図12において、図6又は図8と同様の部分には同一符号を付し、適宜説明を省略する。

【0104】

2次LPF100aは、図8に示す2重正相積分回路10bと、帰還入力容量と、第2の電圧電荷変換回路20aと、第2の電荷積分回路30aとを備える2次バタワースLPFである。帰還入力容量は、図6の入力容量CCaに相当する。2重正相積分回路10bの出力信号が、第2の電圧電荷変換回路20a、第2の電荷積分回路30a及び帰還入力容量を介して、2重正相積分回路10bを構成する第3の演算増幅器AMP3の反転入力端子に帰還される。

【0105】

即ち、第2の電圧電荷変換回路20aは、第3の容量を有し、第2の期間T2において第3の演算増幅器AMP3の出力信号に対応した電荷を第3の容量に充電する。第3の容量は、図6の第1の容量CAaに対応し、図12では第3の容量をCAa(容量値d´×C11´)と表記している。第2の電荷積分回路30aは、第4の容量を有し、第1の期間T1において第3の容量(CAa)に充電された電荷の一部を第4の容量に充電し、第4の容量に充電された電荷の一部を転送する。第4の容量は、図6の第2の容量CBaに対応し、図12では第4の容量をCBa(容量値e´×C11´)と表記している。そして、2次LPF100aは、第2の期間T2において、第4の容量(CBa)に充電された電荷を帰還入力容量(CCa、容量値f´×C11´)及び第3の積分容量CDbに転送する。この2次LPF100aは、第1の期間T1において帰還入力容量(CCa)に充電された電荷を放電する。このような2次LPF100aは、図6と同様のスイッチを備え、図12では、図6と同様の符号を付している。なお、図12では、第2の電圧電荷変換回路20a、第2の電荷積分回路30aや帰還入力容量に接続されるスイッチの構成は、図10と同様であるが、各々が逆相のスイッチに入れ替わっている。

【0106】

図12の構成においても、図10と同様に、次のように各素子の値を決定することができる。以下の式は、式(22)と同じ値となる。

【数23】

【0107】

図13に、図12の2次LPF100aの周波数特性の計算結果の一例を示す。図13は、横軸に周波数、縦軸にゲインをとり、計算結果を実線で示し、シミュレーション結果を点で示している。

【0108】

ここでは、図11と同じ条件で計算した結果、図10と同じ素子値となる。従って、図12の構成においても、1つの演算増幅器を用いて、−40[dB/DEC]で減衰する2次LPFを構成することができる。しかも、総容量値が14.3pF、素子値の広がりを56に抑えた2次LPFを提供することができるようになる。従って、面積が小さく、消費電流を大幅に低減することができるフィルター回路を提供することができるようになる。

【0109】

2.3 4次LPF

2.3.1 原理構成

図10の2次LPF100の出力に、図12の2次LPF100aを縦続接続することで、4次LPFを構成することができる。

【0110】

図14に、本発明の一実施形態に係る4次LPFの構成例の回路図を示す。図14において、図10又は図12と同様の部分には同一符号を付し、適宜説明を省略する。

【0111】

4次LPF200は、第1のフィルター回路として図10の2次LPF100と、第2のフィルター回路として図12の2次LPF100aとを備える4次バタワースLPFである。ここで、2次LPF100aは、2次LPF100の出力に縦続接続される。

【0112】

4次LPF200は、例えば2次LPF100のQ値を「1.3065」、2次LPF100aのQ値を「0.541196」とすることで実現することができる。このとき、2次LPF100の各素子の値、2次LPF100aの各素子の値は、式(22)、式(23)により決定される。

【0113】

図15に、図14の4次LPF200の周波数特性の計算結果の一例を示す。図15は、横軸に周波数、縦軸にゲインをとり、計算結果を実線で示し、シミュレーション結果を点で示している。

【0114】

ここでは、K=0[dB]、ω0=2π×200[rad/s]、T=1/5000[s]、2次LPF100のQ=1.3065、2次LPF100aのQ=0.541196、最小容量を0.1pFとする。このとき、aC1=0.1pF、bC1=10.3pF、cC1=0.1pF、dC11=0.1pF、eC11=10.4pF、fC11=0.1pF、C2=1.5pFとなる。同様に、a´C1´=0.1pF、b´C1´=4.2pF、c´C1´=0.1pF、d´C11´=0.1pF、e´C11´=4.3pF、f´C11´=0.1pF、C2´=3.7pFとなる。この結果、2つの演算増幅器を用いて、−80[dB/DEC]で減衰する4次LPFを構成することができる。しかも、総容量値が35.2pF、素子値の広がりを104(=10.4/0.1)に抑えた4次LPFを提供することができるようになる。従って、面積が小さく、消費電流を大幅に低減することができるフィルター回路を提供することができるようになる。

【0115】

2.3.2 時分割使用構成

図14に示す4次LPF200では、2次LPF100を構成する第1の演算増幅器AMP1が第1の期間T1において積分動作を行い、2次LPF100aを構成する第3の演算増幅器AMP3が第2の期間T2において積分動作を行う。そこで、1つの演算増幅器を時分割使用して、第1の期間T1では第1の演算増幅器AMP1として機能させ、第2の期間T2では第3の演算増幅器AMP3として機能させることで、1つの演算増幅器を用いて4次LPFを提供することができる。

【0116】

図16に、1つの演算増幅器を時分割使用したときの4次LPFの構成例の回路図を示す。図16において、図14と同様の部分には同一符号を付し、適宜説明を省略する。

【0117】

4次LPF200aが図14の4次LPF200と異なる点は、演算増幅器が1つで構成された点と、第1の積分容量CDの両端に第1のフェーズスイッチが設けられ、且つ第3の積分容量CDbの両端に第2のフェーズスイッチが設けられた点である。更に、4次LPF200aの出力部に第2のフェーズスイッチが設けられている。

【0118】

これにより、4次LPF200aによれば、1つの演算増幅器を用いて4次LPFを提供することができるようになる。また、出力部にスイッチを設けるようにしたので、正確な4次LPFの処理後の出力電圧V3を取り出すことができるようになる。

【0119】

2.4 3次LPF

2.4.1 原理構成

4次LPFに限らず3次LPFについても、上記の2次LPFを用いることで構成することができる。

【0120】

図17に、本発明の一実施形態に係る3次LPFの構成例の回路図を示す。図17において、図10と同様の部分には同一符号を付し、適宜説明を省略する。

【0121】

3次LPF300は、図10の2次LPF100と、1次LPF310とを備える3次バタワースLPFである。ここで、1次LPF310は、2次LPF100の出力に縦続接続される。1次LPF310は、公知の1次LPFとすることができる。例えば、1次LPF310は、演算増幅器AMP4と、演算増幅器AMP4の反転入力端子と出力端子との間に挿入される積分容量Cyと、第2の期間T2において積分容量Cyと並列に接続される積分容量Czと、入力容量Cxとを備えることができる。入力容量Cxは、第1の期間T1において2次LPF100の出力電圧V2に対応した電荷を充電する。そして、第2の期間T2において、入力容量Cxに充電された電荷が、積分容量Cy,Czに転送される。なお、積分容量Czに充電された電荷は、第1の期間T1において放電される。

【0122】

図18に、図17の3次LPF300のシグナルフローを示す。図18において、図9と同様の部分には同一符号を付し、適宜説明を省略する。

【0123】

この場合も係数比較を行うことで、図18に示すように、k1,k2,k3,αを、Q,ω0,βを用いて各々表すことができる。

【0124】

図19に、図18の3次LPF300の周波数特性の計算結果の一例を示す。図19は、横軸に周波数、縦軸にゲインをとり、計算結果を実線で示し、シミュレーション結果を点で示している。

【0125】

ここで、K=0[dB]、ω0=2π×200[rad/s]、T=1/5000[s]、Q=1、最小容量を0.1pFとする。このとき、aC1=0.1pF、bC1=7.9pF、cC1=0.1pF、dC11=0.1pF、eC11=8.0pF、fC11=0.1pF、C2=2.0pF、Cx=0.1pF、Cy=3.9pF、Cz=0.1pFとすることができる。この結果、2つの演算増幅器を用いて、−60[dB/DEC]で減衰する3次LPFを構成することができる。しかも、総容量値が22.4pF、素子値の広がりを80(=8.0/0.1)に抑えた3次LPFを提供することができるようになる。従って、面積が小さく、消費電流を大幅に低減することができるフィルター回路を提供することができるようになる。

【0126】

2.4.2 時分割使用構成

図18に示す3次LPF300では、2次LPF100を構成する第1の演算増幅器AMP1が第1の期間T1において積分動作を行い、1次LPF310を構成する演算増幅器AMP4が第2の期間T2において積分動作を行う。そこで、1つの演算増幅器を時分割使用して、第1の期間T1では第1の演算増幅器AMP1として機能させ、第2の期間T2では演算増幅器AMP4として機能させることで、1つの演算増幅器を用いて3次LPFを提供することができる。

【0127】

図20に、1つの演算増幅器を時分割使用したときの3次LPFの構成例の回路図を示す。図20において、図17と同様の部分には同一符号を付し、適宜説明を省略する。

【0128】

3次LPF300aが図17の3次LPF300と異なる点は、演算増幅器が1つで構成された点と、積分容量Cyの両端に第2のフェーズスイッチが設けられた点である。更に、3次LPF300aの出力部に第2のフェーズスイッチが設けられている。

【0129】

これにより、3次LPF300aによれば、1つの演算増幅器を用いて3次LPFを提供することができるようになる。また、出力部にスイッチを設けるようにしたので、正確な3次LPFの処理後の出力電圧V3を取り出すことができるようになる。

【0130】

3. 物理量測定装置

上記で説明した2次LPF、3次LPF、又は4次LPFは、センサー回路に適用することにより、高精度なセンシングを行う物理量測定装置を提供することができるようになる。

【0131】

図21に、上記の2次LPF、3次LPF、又は4次LPFのいずれかが適用されたセンサー回路の構成例を示す。なお、この回路構成は一例であり、例えば回路の細部の構成が変形される場合もあり得る。

【0132】

センサー回路400は、角速度を測定対象の物理量とする物理量測定装置である。センサー回路400は、駆動回路(駆動装置)500と、検出回路(検出装置)600とを備えている。このセンサー回路400は、圧電材料で形成され、駆動振動片及び検出振動片を有する振動片(振動子、広義には圧電素子)510を含む。

【0133】

駆動回路500は、駆動振動片に設けられた駆動電極512a,512bを介して駆動振動片を発振ループ内に設け、駆動振動片(広義には振動子)を励振させる。駆動回路500は、電流電圧変換器520、オートゲインコントロール(Auto Gain Control:以下、AGC)回路530、帯域通過フィルター(Band Pass Filter:以下、BPF)540を備えている。更に、駆動回路500は、ゲインコントロールアンプ(Gain Control Amplifier:以下、GCA)550、2値化回路560を備えている。

【0134】

駆動振動片の駆動電極512aは、電流電圧変換器520の入力に電気的に接続され、電流電圧変換器520の出力は、AGC回路530及びBPF540に入力される。BPF540は、発振ループ内の発振信号の位相調整回路として機能し、BPF540の出力は、GCA550及び2値化回路560に入力される。AGC回路530は、電流電圧変換器520の出力に基づいて、GCA550のゲインを制御する。GCA550の出力は、駆動振動片の駆動電極512bに電気的に接続される。2値化回路560は、発振ループ内の発振信号を2値化し、参照信号として検出回路600に出力する。なお、図21では、駆動回路500の内部に振動片510の駆動振動片を設けるものとして説明したが、駆動回路500の外部に振動片510の駆動振動片が設けられていてもよい。

【0135】

検出回路600は、交流増幅回路610と、同期検波回路620と、直流増幅器630と、LPF640とを備えている。LPF640は、上記の2次LPF、3次LPF、又は4次LPFである。交流増幅回路610は、第1の電流電圧変換器612と、第2の電流電圧変換器614と、交流増幅器616と、BPF618とを含む。

【0136】

駆動回路500では、上記の構成の発振ループ内のゲインが「1」より大きい状態で発振スタートする。この時点では、駆動振動片への入力は雑音のみであるが、この雑音は、目的とする駆動振動の固有共振周波数を含む幅広い周波数の波動を含む。振動片510の駆動振動片の周波数フィルター作用によって、目的とする固有共振周波数の波動を多く含む信号が出力され、この信号が電流電圧変換器5210において電圧値に変換される。AGC回路530は、この電圧値に基づいてGCA550のゲインを制御することで発振ループ内の発振振幅を制御する。発振ループ内でこうした操作が繰り返されることにより、目的とする固有共振周波数の信号の割合が高くなる。そして、GCA550のゲイン制御によって、次第に発振ループを信号が1周する間の利得(ループゲイン)が「1」となり、この状態で駆動振動片が安定発振する。

【0137】

駆動振動片を励振させて安定発振状態になり、振動片510を所与の方向に回転させると、コリオリ力が振動片510に作用し、検出振動片が屈曲振動する。検出振動片には検出電極514a,514b,516a,516bが設けられる。検出電極514b,516bにはアナログ接地電位が供給され、検出電極514a,516aは、交流増幅回路610の第1の電流電圧変換器612及び第2の電流電圧変換器614に接続される。検出回路600は、検出電極514a,516aからの互いに極性が異なる検出信号を交流増幅した後、駆動回路500からの参照信号を用いて同期検波して、LPF640で検出信号OUTを出力する。

【0138】

以上のように、センサー回路400は、振動片510と、駆動回路500と、検出回路600とを備えることができる。駆動回路500は、振動片510と発振ループを形成し、該振動片に駆動振動を励振する。検出回路600は、上記のいずれかのフィルター回路を有し振動片510に励振される駆動振動及び測定すべき物理量に応じて検出信号を出力する。

【0139】

4. 電子機器

上記のセンサー回路は、次のような電子機器に搭載することができる。このような電子機器によれば、所望の信号伝達関数で動作し、且つ高精度なセンシングを容易に実現できるようになる。

【0140】

図22に、本実施形態における電子機器のハードウェア構成例のブロック図を示す。

【0141】

電子機器700は、センサー回路400と、A/D変換回路710と、クロック生成回路720と、中央演算処理装置等の処理部730と、メモリー740と、操作部750と、表示部760とを備えている。電子機器700を構成する各部は、バス(BUS)によって相互に接続されている。なお、A/D変換回路710は、処理部730に内蔵されていてもよい。

【0142】

例えば、処理部730は、メモリー740から読み込んだプログラムに従って処理を実行し、センサー回路400で検出された検出信号の振幅又は感度に応じてA/D変換回路710で変換されたディジタル値を用いて積分を行う。こうすることで、角速度及び回転角度を算出する。そして、処理部730は、算出した角速度又は回転角度に対応した処理を実行し、該処理に対応した表示データを生成し、表示部760に表示させる処理を行う。

【0143】

以上、本発明に係るSC積分回路、フィルター回路、物理量測定装置及び電子機器を上記の実施形態に基づいて説明したが、本発明は上記の実施形態に限定されるものではない。本発明は、その要旨を逸脱しない範囲において種々の態様において実施することが可能であり、例えば次のような変形も可能である。

【0144】

(1)上記の実施形態では、フィルター回路として、図10、図12、図14、図16、図17、又は図20を例に説明したが、本発明はこれらに限定されるものではない。

【0145】

(2)上記の実施形態では、フィルター回路として、2次LPF、3次LPF又は4次LPFを例に説明したが、図10又は図12の2次LPFを備えるn(nは3以上の整数)次のLPFに適用することができる。

【0146】

(3)上記の実施形態では、検出回路600が備えるLPF640として、上記の実施形態における2次LPF、3次LPF又は4次LPFを採用するものとして説明したが、本発明は、これに限定されるものではない。検出回路600が備えるLPF640は、例えば図10又は図12の2次LPFを備えるn(nは3以上の整数)次のLPFを採用することができる。

【0147】

(4)上記の実施形態では、電子機器が、上記のLPFが適用される例を説明したが、本発明はこれに限定されるものではない。本発明に係る電子機器が、上記のSC積分回路としての2重積分回路(2重正相積分回路、2重逆相積分回路)を備えていてもよい。

【符号の説明】

【0148】

10,10b…2重正相積分回路、 10a…2重逆相積分回路、

20…第1の電圧電荷変換回路、 20a…第2の電圧電荷変換回路、

20b…第3の電圧電荷変換回路、 30…第1の電荷積分回路、

30a…第2の電荷積分回路、 30b…第3の電荷積分回路、

40…第1のSC積分器、 40a…第2のSC積分器、 40b…第3のSC積分器、

100,100a…2次LPF、 200,200a…4次LPF、

300,300a…3次LPF、 400…センサー回路、

500…駆動回路(駆動装置)、 510…振動片(振動子)、

512a,512b…駆動電極、

514a,514b,516a,516b…検出電極、 520…電流電圧変換器、

530…AGC回路、 540,618…BPF、 550…GCA、

560…2値化回路、 600…検出回路(検出装置)、 610…交流増幅回路、

612…第1の電流電圧変換器、 614…第2の電流電圧変換器、

616…交流増幅器、 620…同期検波回路、 630…直流増幅器、

640…LPF、 700…電子機器、 710…A/D変換回路、

720…クロック生成回路、 730…処理部、 740…メモリー、

750…操作部、 760…表示部、 AMP…演算増幅器、

AMP1…第1の演算増幅器、 AMP2…第2の演算増幅器、

AMP3…第3の演算増幅器、 CA,CAa,CAb…第1の容量、

CB,CBa,CBb…第2の容量、 CC,CCa,CCb,Cx…入力容量、

CD…第1の積分容量、 CDa…第2の積分容量、 CDb…第3の積分容量、

Cy,Cz…積分容量、 SW1,SW2,SW3,SW3a,SW3b,SW4,SW4a,SW4b,SW5,SW5a,SW5b,SW6,SW6a,SW6b…スイッチ、 V1…入力電圧(入力信号)、 V2…出力電圧(出力信号)

【特許請求の範囲】

【請求項1】

第1の容量を有し、第1の期間において入力信号に対応した電荷を前記第1の容量に充電する第1の電圧電荷変換回路と、

第2の容量を有し、第2の期間において前記第1の容量に充電された電荷の一部を前記第2の容量に充電し、前記第2の容量に充電された電荷の一部を転送する第1の電荷積分回路とを含むことを特徴とするスイッチトキャパシター積分回路。

【請求項2】

請求項1において、

入力容量と、

第1の演算増幅器と、

前記第1の演算増幅器の反転入力端子及び出力端子の間に挿入される第1の積分容量とを有する第1の積分器を含み、

前記第2の期間において前記第1の容量に充電された電荷の一部を前記入力容量に充電し、第3の期間において前記入力容量に充電された電荷を前記第1の積分容量に転送することを特徴とするスイッチトキャパシター積分回路。

【請求項3】

請求項2において、

前記第2の期間は、前記第1の期間と逆相の期間であり、

前記第3の期間は、前記第1の期間と同相の期間であることを特徴とするスイッチトキャパシター積分回路。

【請求項4】

請求項1において、

入力容量と、

第2の演算増幅器と、

前記第2の演算増幅器の反転入力端子及び出力端子の間に挿入される第2の積分容量とを有する第2の積分器を含み、

第3の期間において前記第2の容量に充電された電荷を前記入力容量及び前記第2の積分容量に転送し、第4の期間において前記入力容量に充電された電荷を放電することを特徴とするスイッチトキャパシター積分回路。

【請求項5】

請求項1において、

入力容量と、

第3の演算増幅器と、

前記第3の演算増幅器の反転入力端子及び出力端子の間に挿入される第3の積分容量とを有する第3の積分器を含み、

第3の期間において前記第2の容量に充電された電荷を前記入力容量に充電し、第4の期間において前記入力容量に充電された電荷を前記第3の積分容量に転送することを特徴とするスイッチトキャパシター積分回路。

【請求項6】

請求項3又は4において、

前記第2の期間は、前記第1の期間と逆相の期間であり、

前記第3の期間は、前記第1の期間と同相の期間であり、

前記第4の期間は、前記第2の期間と同相の期間であることを特徴とするスイッチトキャパシター積分回路。

【請求項7】

請求項2乃至6のいずれかにおいて、

前記第1の容量の容量値、前記第2の容量の容量値、及び前記入力容量の容量値は、整数比であることを特徴とするスイッチトキャパシター積分回路。

【請求項8】

請求項3記載のスイッチトキャパシター積分回路と、

帰還入力容量と、

第3の容量を有し、前記第1の期間において前記第1の演算増幅器の出力信号に対応した電荷を前記第3の容量に充電する第2の電圧電荷変換回路と、

第4の容量を有し、前記第2の期間において前記第3の容量に充電された電荷の一部を前記第4の容量に充電し、前記第4の容量に充電された電荷の一部を転送する第2の電荷積分回路とを含み、

前記第1の期間において、前記第4の容量に充電された電荷を前記帰還入力容量及び前記第1の積分容量に転送し、前記第2の期間において前記帰還入力容量に充電された電荷を放電することを特徴とするフィルター回路。

【請求項9】

請求項4記載のスイッチトキャパシター積分回路と、

帰還入力容量と、

第3の容量を有し、前記第2の期間において前記第3の演算増幅器の出力信号に対応した電荷を前記第3の容量に充電する第2の電圧電荷変換回路と、

第4の容量を有し、前記第1の期間において前記第3の容量に充電された電荷の一部を前記第4の容量に充電し、前記第4の容量に充電された電荷の一部を転送する第2の電荷積分回路とを含み、

前記第2の期間において、前記第4の容量に充電された電荷を前記帰還入力容量及び前記第3の積分容量に転送し、前記第1の期間において前記帰還入力容量に充電された電荷を放電することを特徴とするフィルター回路。

【請求項10】

請求項8記載のフィルター回路を有する第1のフィルター回路と、

前記第1のフィルター回路の出力に縦続接続され、請求項9記載のフィルター回路を有する第2のフィルター回路とを含むことを特徴とするフィルター回路。

【請求項11】

請求項10において、

前記第1のフィルター回路を構成する前記第1の演算増幅器と、前記第2のフィルター回路を構成する前記第2の演算増幅器とが時分割で使用されるように構成されることを特徴とするフィルター回路。

【請求項12】

請求項8又は9記載のフィルター回路を含むことを特徴とするn(nは3以上の整数)次のフィルター回路。

【請求項13】

振動子と、

前記振動子と発振ループを形成し、該振動子に駆動振動を励振する駆動回路と、

請求項8乃至12のいずれか記載のフィルター回路を有し、前記振動子に励振される駆動振動及び測定すべき物理量に応じて検出信号を出力する検出回路とを含むことを特徴とする物理量測定装置。

【請求項14】

請求項13記載の物理量測定装置を含むことを特徴とする電子機器。

【請求項15】

請求項1乃至7のいずれか記載のスイッチトキャパシター積分回路を含むことを特徴とする電子機器。

【請求項1】

第1の容量を有し、第1の期間において入力信号に対応した電荷を前記第1の容量に充電する第1の電圧電荷変換回路と、

第2の容量を有し、第2の期間において前記第1の容量に充電された電荷の一部を前記第2の容量に充電し、前記第2の容量に充電された電荷の一部を転送する第1の電荷積分回路とを含むことを特徴とするスイッチトキャパシター積分回路。

【請求項2】

請求項1において、

入力容量と、

第1の演算増幅器と、

前記第1の演算増幅器の反転入力端子及び出力端子の間に挿入される第1の積分容量とを有する第1の積分器を含み、

前記第2の期間において前記第1の容量に充電された電荷の一部を前記入力容量に充電し、第3の期間において前記入力容量に充電された電荷を前記第1の積分容量に転送することを特徴とするスイッチトキャパシター積分回路。

【請求項3】

請求項2において、

前記第2の期間は、前記第1の期間と逆相の期間であり、

前記第3の期間は、前記第1の期間と同相の期間であることを特徴とするスイッチトキャパシター積分回路。

【請求項4】

請求項1において、

入力容量と、

第2の演算増幅器と、

前記第2の演算増幅器の反転入力端子及び出力端子の間に挿入される第2の積分容量とを有する第2の積分器を含み、

第3の期間において前記第2の容量に充電された電荷を前記入力容量及び前記第2の積分容量に転送し、第4の期間において前記入力容量に充電された電荷を放電することを特徴とするスイッチトキャパシター積分回路。

【請求項5】

請求項1において、

入力容量と、

第3の演算増幅器と、

前記第3の演算増幅器の反転入力端子及び出力端子の間に挿入される第3の積分容量とを有する第3の積分器を含み、

第3の期間において前記第2の容量に充電された電荷を前記入力容量に充電し、第4の期間において前記入力容量に充電された電荷を前記第3の積分容量に転送することを特徴とするスイッチトキャパシター積分回路。

【請求項6】

請求項3又は4において、

前記第2の期間は、前記第1の期間と逆相の期間であり、

前記第3の期間は、前記第1の期間と同相の期間であり、

前記第4の期間は、前記第2の期間と同相の期間であることを特徴とするスイッチトキャパシター積分回路。

【請求項7】

請求項2乃至6のいずれかにおいて、

前記第1の容量の容量値、前記第2の容量の容量値、及び前記入力容量の容量値は、整数比であることを特徴とするスイッチトキャパシター積分回路。

【請求項8】

請求項3記載のスイッチトキャパシター積分回路と、

帰還入力容量と、

第3の容量を有し、前記第1の期間において前記第1の演算増幅器の出力信号に対応した電荷を前記第3の容量に充電する第2の電圧電荷変換回路と、

第4の容量を有し、前記第2の期間において前記第3の容量に充電された電荷の一部を前記第4の容量に充電し、前記第4の容量に充電された電荷の一部を転送する第2の電荷積分回路とを含み、

前記第1の期間において、前記第4の容量に充電された電荷を前記帰還入力容量及び前記第1の積分容量に転送し、前記第2の期間において前記帰還入力容量に充電された電荷を放電することを特徴とするフィルター回路。

【請求項9】

請求項4記載のスイッチトキャパシター積分回路と、

帰還入力容量と、

第3の容量を有し、前記第2の期間において前記第3の演算増幅器の出力信号に対応した電荷を前記第3の容量に充電する第2の電圧電荷変換回路と、

第4の容量を有し、前記第1の期間において前記第3の容量に充電された電荷の一部を前記第4の容量に充電し、前記第4の容量に充電された電荷の一部を転送する第2の電荷積分回路とを含み、

前記第2の期間において、前記第4の容量に充電された電荷を前記帰還入力容量及び前記第3の積分容量に転送し、前記第1の期間において前記帰還入力容量に充電された電荷を放電することを特徴とするフィルター回路。

【請求項10】

請求項8記載のフィルター回路を有する第1のフィルター回路と、

前記第1のフィルター回路の出力に縦続接続され、請求項9記載のフィルター回路を有する第2のフィルター回路とを含むことを特徴とするフィルター回路。

【請求項11】

請求項10において、

前記第1のフィルター回路を構成する前記第1の演算増幅器と、前記第2のフィルター回路を構成する前記第2の演算増幅器とが時分割で使用されるように構成されることを特徴とするフィルター回路。

【請求項12】

請求項8又は9記載のフィルター回路を含むことを特徴とするn(nは3以上の整数)次のフィルター回路。

【請求項13】

振動子と、

前記振動子と発振ループを形成し、該振動子に駆動振動を励振する駆動回路と、

請求項8乃至12のいずれか記載のフィルター回路を有し、前記振動子に励振される駆動振動及び測定すべき物理量に応じて検出信号を出力する検出回路とを含むことを特徴とする物理量測定装置。

【請求項14】

請求項13記載の物理量測定装置を含むことを特徴とする電子機器。

【請求項15】

請求項1乃至7のいずれか記載のスイッチトキャパシター積分回路を含むことを特徴とする電子機器。

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【図14】

【図15】

【図16】

【図17】

【図18】

【図19】

【図20】

【図21】

【図22】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【図14】

【図15】

【図16】

【図17】

【図18】

【図19】

【図20】

【図21】

【図22】

【公開番号】特開2013−21426(P2013−21426A)

【公開日】平成25年1月31日(2013.1.31)

【国際特許分類】

【出願番号】特願2011−151531(P2011−151531)

【出願日】平成23年7月8日(2011.7.8)

【出願人】(000002369)セイコーエプソン株式会社 (51,324)

【出願人】(304021417)国立大学法人東京工業大学 (1,821)

【Fターム(参考)】

【公開日】平成25年1月31日(2013.1.31)

【国際特許分類】

【出願日】平成23年7月8日(2011.7.8)

【出願人】(000002369)セイコーエプソン株式会社 (51,324)

【出願人】(304021417)国立大学法人東京工業大学 (1,821)

【Fターム(参考)】

[ Back to top ]