スイッチングアンプ及びそのスイッチングアンプのレベルシフト回路

【課題】所定の振幅範囲でレベルが変化するPWM信号から振幅範囲の異なるPWM信号に変換するレベルシフト回路の簡単化を図る。

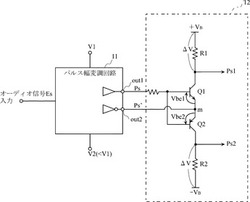

【解決手段】スイッチングアンプはオーディオ信号EsをPWM信号に変換して出力するパルス幅変調回路11の後段にシフトレベル回路12が設けられる。パルス幅変調回路11はPWM信号PsとPWM信号Psに対して逆相関係のPWM信号Ps’を出力する出力端子out1,out2を有する。シフトレベル回路12を抵抗R1、P型トランジスタQ1、N型トランジスタQ2および抵抗R2がこの順で直列接続された回路で構成し、この回路の両端を電源電圧+VB,−VBが入力される一対の電源端子に接続し、トランジスタQ1,Q2のベースにパルス幅変調回路11のout1を接続し、トランジスタQ1,Q2の接続点mにパルス幅変調回路11のout2を接続する構成とした。

【解決手段】スイッチングアンプはオーディオ信号EsをPWM信号に変換して出力するパルス幅変調回路11の後段にシフトレベル回路12が設けられる。パルス幅変調回路11はPWM信号PsとPWM信号Psに対して逆相関係のPWM信号Ps’を出力する出力端子out1,out2を有する。シフトレベル回路12を抵抗R1、P型トランジスタQ1、N型トランジスタQ2および抵抗R2がこの順で直列接続された回路で構成し、この回路の両端を電源電圧+VB,−VBが入力される一対の電源端子に接続し、トランジスタQ1,Q2のベースにパルス幅変調回路11のout1を接続し、トランジスタQ1,Q2の接続点mにパルス幅変調回路11のout2を接続する構成とした。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、オーディオ信号をPWM信号に変換し、そのPWM信号を増幅するスイッチングアンプとそのスイッチングアンプに含まれるレベルシフト回路に関するものである。

【背景技術】

【0002】

従来、音声信号を増幅する音響機器としてスイッチングアンプが知られている。スイッチングアンプは、音声信号をPWM信号に変換した後、そのPWM信号をスピーカの出力レベルに増幅する機器である。

【0003】

図4は、一般的なスイッチングアンプの構成を示すブロック図である。スイッチングアンプ100には、パルス幅変調回路101、レベルシフト回路102、ドライバ103および出力回路104が含まれている。図5は、スイッチングアンプ100の各部の出力波形を示す。

【0004】

パルス幅変調回路101は、図5(a)に示す入力信号(オーディオ信号)をパルス幅変調し、図5(b)に示すPWM信号を出力する。なお、図5(b)〜(e)のパルス波形は、時間軸を拡大したものであり、同図(a)の時間軸とはスケールが異なっている。

【0005】

レベルシフト回路102は、PWM信号Psから当該PWM信号Psのレベル変化の範囲と異なるレベル変化の範囲を有する2つのパルス信号を生成する回路である。レベルシフト回路102を必要とするのは、後述する出力回路104に含まれる2つのスイッチ回路SW1,SW2が互いに異なるタイプの半導体スイッチング素子で構成されるとともに、各スイッチ回路SW1,SW2をオン・オフ動作させるための駆動電圧の変化範囲がパルス幅変調回路101から出力されるPWM信号Psのレベル変化の範囲と異なるため、スイッチ回路SW1,SW2を駆動するためのパルス信号をそれぞれ生成する必要があるからである。

【0006】

レベルシフト回路102に供給される電源電圧を±VBの一対の電源電圧であるとし、出力回路104における上側のスイッチ回路SW1に対するパルス信号をハイサイドPWM信号Ps1とし、下側のスイッチ回路SW2に対するパルス信号をローサイドPWM信号Ps2とすると、レベルシフト回路102は、図5(c)に示すように、PWM信号Psのレベル変化の範囲V1〜V2を+VB〜(+VB−ΔV)に変更したハイサイドPWM信号Ps1を生成するとともに、同図(d)に示すように、PWM信号Psのレベル変化の範囲V1〜V2を(−VB+ΔV)〜−VBに変更したローサイドPWM信号Ps2を生成する。なお、ハイサイドPWM信号Ps1およびローサイドPWM信号Ps2はPWM信号Psに対して同期した関係になっている。

【0007】

ドライバ回路103は、レベルシフト回路102から出力されるハイサイドPWM信号Ps1およびローサイドPWM信号Ps2に基づいて、出力回路104内のスイッチ回路SW1とスイッチ回路SW2をオン・オフ動作させるためのドライブ信号を生成する回路である。スイッチ回路SW1に対するドライブ信号(以下、「ハイサイドドライブ信号」という。)は、ドライバ回路103に入力される信号に同期してスイッチ回路SW1に電圧を印加するパルス信号であり、ハイサイドPWM信号Ps1に対して出力電流量を増幅した信号である。同様に、スイッチ回路SW2に対するドライブ信号(以下、「ローサイドドライブ信号」という。)はドライバ回路103に入力される信号に同期してスイッチ回路SW2に電圧を印加するパルス信号で、ローサイドPWM信号Ps2に対して出力電流量を増幅した信号である。

【0008】

従って、スイッチSW1,SW2を駆動するための電圧パルス信号でみると、ハイサイドドライブ信号の波形はハイサイドPWM信号Ps1の波形(図5(c)参照)と同じであり、ローサイドドライブ信号の波形はローサイドPWM信号Ps2の波形(図5(d)参照)と同じである。

【0009】

出力回路104は、極性の反転した2つの直流電源+VB,−VBが入力される一対の電源端子の間に直列に接続された種類の異なる半導体スイッチング素子からなる2つのスイッチ回路SW1とスイッチ回路SW2を有し、スイッチ回路SW1とスイッチ回路SW2の接続点Nから、図5(e)に示すように、パルス幅変調回路101で生成されたPWM信号Psに対してレベル変化の範囲を+VB〜−VBの範囲に増幅したPWM信号Psoutを出力する回路である。例えば、スイッチ回路SW1にはPチャネルMOSFET(Metal Oxide Semiconductor Field Effect Transistor)が用いられ、スイッチ回路SW2にはNチャネルMOSFETが用いられる。出力回路104から出力されるPWM信号Psoutは、ローパスフィルタからなるフィルタ回路105によって高周波成分が除去され(アナログのオーディオ信号に戻され)た後、スピーカSPに入力され、当該スピーカSPから音声出力される。

【0010】

上述したように、スイッチングアンプでは、パルス幅変調回路101の後段にレベルシフト回路102を設けてPWM信号Psのレベル変化の範囲とは異なるレベル変化の範囲を有するハイサイドPWM信号Ps1とローサイドPWM信号Ps2とを生成する必要がある。

【0011】

図6は、パルス幅変調回路101の後段に設けられるレベルシフト回路102の具体回路の一例を示す図である。

【0012】

同図に示すレベルシフト回路101は、直流電源+VBが入力される電源端子と極性の反転した直流電源−VBが入力される電源端子との間に抵抗R1、npn型トランジスタQ1、pnp型トランジスタQ2および抵抗R2をこの順に直列に接続するとともに、トランジスタQ1,Q2の接続点mにVm=(V1+V2)/2の電源回路102aを接続し、トランジスタQ1,Q2の両ベースに抵抗を介してパルス幅変調回路101の出力端子out1から出力されるPWM信号Psが入力され、トランジスタQ1およびトランジスタQ2の各コレクタからそれぞれハイサイドPWM信号Ps1とローサイドPWM信号Ps2が出力される構成となっている。

【0013】

PWM信号PsがハイレベルV1のとき(図5(b)のTONの期間参照)は、トランジスタQ1のベース電圧が当該トランジスタQ1のベース・エミッタ間の電圧Vbe1より大きくなるが、トランジスタQ2のベース電圧は当該トランジスタQ2のベース・エミッタ間の電圧Vbe2よりも小さくならないので、トランジスタQ1,Q2のオン・オフ関係は、(Q1,Q2)=(ON,OFF)となる。従って、トランジスタQ1のコレクタ電圧は電源電圧+VBから抵抗R1の電圧降下分ΔVだけ低下した電圧(+VB−ΔV)となり、トランジスタQ2のコレクタ電圧は電源電圧−VBとなる。

【0014】

逆に、PWM信号PsがローレベルV2のとき(図5(b)のTOFFの期間参照)は、トランジスタQ2のベース電圧がベース・エミッタ間の電圧Vbe2より小さくなるが、トランジスタQ1のベース電圧はベース・エミッタ間の電圧Vbe1よりも大きくならないので、トランジスタQ1,Q2のオン・オフ関係は、(Q1,Q2)=(OFF,ON)となる。従って、トランジスタQ1のコレクタ電圧は電源電圧+VBとなり、トランジスタQ2のコレクタ電圧は電源電圧−VBから抵抗R2の電圧降下分ΔVだけ上昇した電圧(−VB+ΔV)となる。

【先行技術文献】

【特許文献】

【0015】

【特許文献1】特開2009−65612号公報

【発明の概要】

【発明が解決しようとする課題】

【0016】

図6に示すレベルシフト回路102は、PWM信号Psのレベル変化の中点電圧(V1+V2)/2を基準レベルとし、PWM信号Psのレベルが(基準レベル+Vbe1)以上の範囲にあるか、(基準レベル−Vbe2)以下の範囲にあるかによって、トランジスタQ1,Q2のオン・オフの状態を交互に切り換える構成であるので、例えば、|+Vbe1|=|−Vbe2|=Vbeとすると、PWM信号Psのレベル変化の幅は2Vbe以上でなければ、トランジスタQ1,Q2のオン・オフの状態を正常に切り換えることができなくなるという問題がある。

【0017】

例えば、Vbeを0.6vとすると、PWM信号Psのレベルの変化幅が1.2vよりも大きくなければ、トランジスタQ1,Q2のオン・オフの状態を正常に切り換えることができなくなる。従って、パルス幅変調回路101の駆動電源には、(V1−V2)>1.2vの条件を満たさなければならないという制約が掛かることになり、V1,V2を低電圧化することができないという問題がある。

【0018】

また、トランジスタQ1とトランジスタQ2との接続点mに基準レベルを設定するための電源回路102aを設けているので、この電源回路102aに含まれる抵抗成分rや容量成分Cの影響を受け、図7に示すように、トランジスタQ1,Q2のオン・オフの状態が切り換わったときのハイサイドPWM信号Ps1およびローサイドPWM信号Ps2のレベル変化が緩慢になるという問題がある。

【0019】

すなわち、レベルシフト回路102に入力されるPWM信号Psは、パルスの立上がりおよび立下りのエッジ部分が略直角となる理想的な矩形波となっている。しかし、ハイサイドPWM信号Ps1は、立下がりタイミングにおいて、+VBから(+VB−ΔV)に立ち下がるまでに微小時間を要し、図7に示すように、立下り波形が傾斜した波形となる。また、ハイサイドPWM信号Ps1は、立上がりタイミングにおいて、(+VB−ΔV)から+VBに立ち上がるまでに微小時間を要し、図7に示すように、立下り波形が傾斜した波形となる。

【0020】

同様に、ローサイドPWM信号Ps2は、立下がりタイミングにおいて、(−VB+ΔV)から−VBに立ち下がるまでに微小時間を要し、図7に示すように、立下り波形が傾斜した波形となる。また、ローサイドPWM信号Ps2は、立上がりタイミングにおいて、−VBから(−VB+ΔV)に立ち上がるまでに微小時間を要し、図7に示すように、立下り波形が傾斜した波形となる。

【0021】

本発明は、上記の課題に鑑みてなされたものであり、ハイサイドPWM信号Ps1およびローサイドPWM信号Ps2の波形の立上り、立下りの遷移時間を短くすることができるとともに、回路の簡単化を図ることができるレベルシフト回路およびそのレベルシフト回路を備えたスイッチングアンプを提供することを目的とする。

【課題を解決するための手段】

【0022】

上記課題を解決するため、本発明では、次の技術的手段を講じている。

【0023】

本発明の第1の側面によって提供されるレベルシフト回路は、オーディオ信号に基づいて所定の振幅範囲でレベルが変化する第1のPWM信号と前記第1のPWM信号に対して逆相関係の第2のPWM信号を生成するパルス幅変調回路の後段に設けられ、前記所定の振幅範囲の上限値よりも高い第1のレベル値を基準にして所定の範囲でレベルが変化する第1のパルス信号と、前記所定の振幅範囲の下限値よりも低い第2のレベル値を基準にして前記所定の範囲でレベルが変化する第2のパルス信号とを生成するレベルシフト回路であって、前記第1のレベル値の電圧と前記第2のレベル値の電圧とが入力される一対の電圧入力端子間に、抵抗とN型半導体スイッチの第1の直列回路と、P型半導体スイッチと抵抗の第2の直列回路とを直列に接続した回路を有し、前記N型半導体スイッチおよび前記P型半導体スイッチの制御電極に前記パルス幅変調回路から出力される前記第1のPWM信号が入力され、前記N型半導体スイッチと前記P型半導体スイッチとの前記制御電極以外の電極の接続点に前記パルス幅変調回路から出力される前記第2のPWM信号が入力されることを特徴とする(請求項1)。

【0024】

本発明の第2の側面によって提供されるスイッチングアンプは、請求項1に記載のレベルシフト回路と、前記レベルシフト回路から出力される第1および第2のパルス信号に基づいて、前記所定の振幅範囲の上限値よりも高い第3のレベルと前記所定の振幅範囲の下限値よりも低い第3のレベルとの範囲でレベルが変化するスピーカ駆動用のPWM信号を生成する出力回路とを備えたことを特徴とする(請求項2)。

【0025】

好ましい実施の形態においては、前記出力回路は、前記第1のレベルの電源電圧と前記第3のレベルの電源電圧が入力される一対の電源端子間に、前記第1のパルス信号によってオン・オフ動作が制御されるP型半導体スイッチと前記第2のパルス信号によってオン・オフ動作が制御されるN型半導体スイッチとの直列回路が接続され、前記P型半導体スイッチと前記N型半導体スイッチの接続点から前記スピーカ駆動用のPWM信号を出力する回路からなる(請求項3)。

【発明の効果】

【0026】

本発明によれば、レベルシフト回路を一対の電圧入力端子間に、抵抗とN型半導体スイッチの第1の直列回路と、P型半導体スイッチと抵抗の第2の直列回路とを直列に接続した回路構成とし、N型半導体スイッチおよびP型半導体スイッチの制御電極にパルス幅変調回路から出力されるPWM信号を入力し、N型半導体スイッチとP型半導体スイッチとの接続点にPWM信号に対して逆相関係の第2のPWM信号を入力する構成としたので、PWM信号のレベルが変化する振幅範囲をV1〜V2とすると、N型半導体スイッチおよびP型半導体スイッチにはオン・オフさせるための信号として振幅がΔVs=V1−V2のパルス信号が入力されることになる。

【0027】

従来の構成では、N型半導体スイッチとP型半導体スイッチとの接続点にV1〜V2の中点電圧、すなわち(V1+V2)/2の電圧が入力されるので、例えばN型半導体スイッチをオン・オフさせるためのパルス信号の基準レベルに対する電圧はV1−(V1+V2)/2−Vbeである。一方、本発明によれば、N型半導体スイッチをオン・オフさせるためのパルス信号の基準レベルに対する電圧がV1−V2−Vbeとなる。N型半導体スイッチの制御電極に電圧V1が供給されるとき、基準レベルには電圧V2が供給されるからである。従って、V1−V2−Vbe>V1−(V1+V2)/2−Vbeであるので、同一の電圧V1,V2に対して、例えばN型半導体スイッチをオンオフ動作させるためのパルス信号の基準レベルに対する電圧を大きくすることができる。なお、P型半導体スイッチについても同様である。その結果、パルス幅変調回路の電源電圧V1,V2の低電圧化を図ることができる。

【0028】

また、従来のように、N型半導体スイッチとP型半導体スイッチとの接続点に中点電圧を供給するための電源回路を必要としないので、その分、レベルシフト回路の構成が簡単になる。また、その電源回路に含まれる容量成分や抵抗成分の影響を受けて第1および第2のパルス信号の立上がり/立下がりが緩やかに変化するということがなく、パルス信号の波形の立上がり、立下がりの遷移時間を短くすることができる。

【0029】

本発明のその他の特徴および利点は、添付図面を参照して以下に行う詳細な説明によって、より明らかとなろう。

【図面の簡単な説明】

【0030】

【図1】本発明に係るスイッチングアンプの特徴的な構成の部分を示す図である。

【図2】図1に示すレベルシフト回路のPWM信号の波形とハイサイドPWM信号およびローサイドPWM信号の波形との関係を示す図である。

【図3】図1に示すレベルシフト回路に組み合わされるパルス幅変調回路の具体回路の一例を示す図である。

【図4】一般的なスイッチングアンプの構成を示すブロック図図である。

【図5】図4に示すスイッチングアンプのパルス幅変調回路、レベルシフト回路および出力回路の入出力信号の波形の一例を示す図である。

【図6】パルス幅変調回路の後段に設けられるレベルシフト回路の具体回路の一例を示す図である。

【図7】図6に示すレベルシフト回路のPWM信号の波形とハイサイドPWM信号およびローサイドPWM信号の波形との関係を示す図である。

【発明を実施するための形態】

【0031】

本発明に係るスイッチングアンプは、図6に示す従来のレベルシフト回路102において、トランジスタQ1,Q2の接続点mへの電圧Vmの与え方を改良した点に特徴がある。具体的には、パルス幅変調回路からPWM信号Psと逆相の関係にあるPWM信号Ps’を出力する出力端子を追加し、その出力端子をトランジスタQ1,Q2の接続点mと接続するようにした構成に特徴がある。

【0032】

図1は、本発明に係るスイッチングアンプの特徴的な構成の部分を示す図で、図6に対応する図である。図1に示すパルス幅変調回路11とレベルシフト回路12は、図6に示すパルス幅変調回路101とレベルシフト回路102にそれぞれ対応している。パルス変調回路11の構成は、パルス変調回路101に対してPWM信号Psを出力する出力端子out1の他にPWM信号Psと逆相の関係にあるPWM信号Ps’を出力する出力端子out2を有する点が異なり、レベルシフト回路12の構成は、レベルシフト回路102に対して電源回路102aを除いた点が異なり、レベルシフト回路102のトランジスタQ1とトランジスタQ2の接続点mはパルス変調回路11のPWM信号Ps’の出力端子out2に接続されている。

【0033】

図1に示すレベルシフト回路12によれば、接続点mの電圧Vmは固定されておらず、トランジスタQ1およびトランジスタQ2のベース電圧の変化に応じて相対的に変化する。パルス変調回路11の電源電圧をV1,V2とすると、トランジスタQ1およびトランジスタQ2のベースには、図5(b)に示すPWM信号Psが入力され、接続点mにはPWM信号Psと逆相の関係にあるPWM信号Ps’が入力されるから、トランジスタQ1およびトランジスタQ2のベース電圧がV1のとき、接続点mの電圧VmはV2となり、トランジスタQ1およびトランジスタQ2のベース電圧がV2のとき、接続点mの電圧VmはV1となる。

【0034】

すなわち、トランジスタQ1,Q2のエミッタ(基準レベル)に対するベースの電圧は、PWM信号Psのレベルの変化に応じてV1−V2とV2−V1との間で交互に切り換わることになるので、トランジスタQ1,Q2のベース・エミッタ電圧(導通開始電圧)をVbeとすると、パルス変調回路11の電源電圧V1,V2は、V1−V2≧Vbe、V2−V1≦−Vbeを満たせば、トランジスタQ1,Q2のオン・オフの状態を正常に切り換えることができる。言い換えると、同一の電圧V1,V2であっても、トランジスタQ1のエミッタ基準のベース電圧を従来よりも大きくすることができ、トランジスタQ2のエミッタ基準のベース電圧を従来よりも小さくすることができる。従って、従来のスイッチングアンプ100に比べてパルス変調回路1の電源電圧V1,V2の低電圧化を図ることができる。

【0035】

また、レベルシフト回路12の接続点mには電源回路102aが設けられていないので、従来のレベルシフト回路102のように電源回路102aに含まれる抵抗成分rや容量成分C(図6参照)の影響を受けて、トランジスタQ1,Q2のオン・オフの状態が切り換わったときのハイサイドPWM信号Ps1およびローサイドPWM信号Ps2のレベル変化が緩やかになり遷移時間が長くなるという問題を解決することができる。すなわち、レベルシフト回路12では、ハイサイドPWM信号Ps1とローサイドPWM信号Ps2の波形は、図2に示すようになる。ハイサイドPWM信号Ps1では、立下がりタイミングtbにおいて+VBから(+VB−ΔV)に急峻に立ち下がり、立上がりタイミングtaにおいて(+VB−ΔV)から+VBに急峻に立ち上がることができる。同様に、ローサイドPWM信号Ps2では、立下がりタイミングtbにおいて(−VB+ΔV)から−VBに急峻に立ち下がり、立上がりタイミングtaにおいて−VBから(−VB+ΔV)に急峻に立ち上がることができる。

【0036】

また、レベルシフト回路12では、電源回路102aがなくなる分、従来のレベルシフト回路102よりも回路を簡単化することができる。

【0037】

図3は、図1に示すレベルシフト回路12に組み合わされるパルス幅変調回路11の具体回路の一例を示す図である。図3におけるレベルシフト回路12の具体回路の構成は、図1に示すものと同じであるので、説明は省略する。

【0038】

図3に示すパルス幅変調回路11は、特開2007−329698号公報に記載の差動増幅回路111と非安定マルチバイブレータを用いた積分型パルス幅変調回路112(以下、単に「変調回路」という。)で構成されている。差動増幅回路11Aは、特性の等しい2つのトランジスタTr1,Tr2のエミッタを抵抗を介して相互に接続し、その接続点にトランジスタTr3を用いた定電流回路111aを接続した構成の周知の差動増幅回路である。一方のトランジスタTr1のベースにオーディオ信号Esが入力され、他方のトランジスタTr2のベースは接地されている。トランジスタTr1,Tr2の各コレクタからはトランジスタTr1のベース電圧(Es)とトランジスタTr2のベース電圧(0)の差電圧(Es−0)を増幅した電圧が出力される。

【0039】

変調回路112は、抵抗からなるバイアス電流源112aと、バイアス電流源112aに接続された差動増幅回路112bと、差動増幅回路112bに接続されたパルス発生回路112cとによって構成されている。差動増幅回路112bは、エミッタが抵抗を介して接続された一対のトランジスタTr3とトランジスタTr4を有し、トランジスタTr3でベースに入力される差動増幅回路111のトランジスタTr1のコレクタ電圧e1が変換コンダクタンスGoによってコレクタ電流I1に変換され、トランジスタTr4でベースに入力される差動増幅回路111のトランジスタTr2のコレクタ電圧e2が変換コンダクタンスGoによってコレクタ電流I2に変換される。

【0040】

なお、変換コンダクタンスGoは、トランジスタTr3,Tr4のエミッタ抵抗をReとすると、Go≒1/(2・Re)であり、電量I1,I2は、バイアス電流源112aから差動増幅回路112bに供給されるバイアス電流を2IBとすると、I1=IB−Go・(e1−e2)、I2=IB+Go・(e1−e2)である。

【0041】

パルス発生回路112cは、電流I1,I2によってコンデンサC1,C2をそれぞれ所定の閾値電圧Vthまで充電し、その充電時間T1,T2をパルス幅とするパルス信号を生成する回路である。トランジスタTr3,Tr4のコレクタに接続されたダイオードD1,D2および電源Vbからなる回路はコンデンサC1,C2の充電電圧がVthになると、その蓄積電荷を放電させる回路である。

【0042】

コンデンサC1,C2が閾値電圧Vthまで充電される時間をそれぞれT1,T2とすると、I1・T1=C・Vth、I2・T2=C・Vthの関係がそれぞれ成立するので、充電時間T1,T2は、それぞれT1=C・Vth/I1、T2=C・Vth/I2となる。

【0043】

コンデンサC1,C2が交互に充放電を繰り返すと、コンデンサC1,C2の充放電に応じてレベルが変化するパルス信号がNOR回路NOR1,NOR2からそれぞれ出力される。コンデンサC1,C2は交互に充放電を繰り返すので、NOR回路NOR1から出力されるパルス信号とNOR回路NOR1から出力されるパルス信号とは互いに位相が逆になっている。従って、NOR回路NOR1から出力されるパルス信号をPWM信号Psとすると、NOR回路NOR2から出力されるパルス信号はPWM信号Ps’となる。

【0044】

そして、PWM信号Psは、抵抗を介してレベルシフト回路12のトランジスタQ1,Q2のベースに入力され、PWM信号Ps’は、レベルシフト回路12のトランジスタQ1,Q2の接続点mに入力される。

【0045】

図3に示すように、パルス幅変調回路11を差動増幅回路111と非安定マルチバイブレータを用いた変調回路112で構成することにより、パルス幅変調回路11から簡単にPWM信号Psとこれと逆相関係にあるPWM信号Ps’を出力させることができる。

【0046】

また、図3に示すパルス幅変調回路11は、回路構成が簡単なので、スイッチングアンプ全体の回路構成の簡単化に寄与する。なお、パルス幅変調回路11の具体回路は、図3に示すものに限られるものではなく、例えば、特開2008−206128号公報に記載される、基準クロックから充電開始タイミングと放電開始タイミングの制御信号を生成し、これらの制御信号によって2つのコンデンサの充放電制御用のスイッチをそれぞれ制御する方式のパルス幅変調回路を適用してもよい。

【0047】

また、上記実施形態では、パルス幅変調回路11にPWM信号Ps’の出力端子out1を設けていたが、レベルシフト回路12にPWM信号Psの位相を反転させる回路を設け、レベルシフト回路12内でPWM信号PsからPWM信号Ps’を生成するようにしてもよい。

【0048】

なお、上記実施形態では、レベルシフト回路12の半導体スイッチング素子Q1,Q2をトランジスタで構成していたが、FETで構成してもよい。また、抵抗R1,R2に代えてΔVの電圧降下を生じさせる素子若しくは回路を用いてもよい。

【符号の説明】

【0049】

1 スイッチングアンプ

11 PWM幅変調回路

111 差動増幅器

112 変調回路

12 レベルシフト回路

13 出力回路

SP スピーカ

R1,R2 抵抗

Q1 npn型トランジスタ

Q2 pnp型トランジスタ

Q3 PチャネルFET

Q4 NチャネルFET

【技術分野】

【0001】

本発明は、オーディオ信号をPWM信号に変換し、そのPWM信号を増幅するスイッチングアンプとそのスイッチングアンプに含まれるレベルシフト回路に関するものである。

【背景技術】

【0002】

従来、音声信号を増幅する音響機器としてスイッチングアンプが知られている。スイッチングアンプは、音声信号をPWM信号に変換した後、そのPWM信号をスピーカの出力レベルに増幅する機器である。

【0003】

図4は、一般的なスイッチングアンプの構成を示すブロック図である。スイッチングアンプ100には、パルス幅変調回路101、レベルシフト回路102、ドライバ103および出力回路104が含まれている。図5は、スイッチングアンプ100の各部の出力波形を示す。

【0004】

パルス幅変調回路101は、図5(a)に示す入力信号(オーディオ信号)をパルス幅変調し、図5(b)に示すPWM信号を出力する。なお、図5(b)〜(e)のパルス波形は、時間軸を拡大したものであり、同図(a)の時間軸とはスケールが異なっている。

【0005】

レベルシフト回路102は、PWM信号Psから当該PWM信号Psのレベル変化の範囲と異なるレベル変化の範囲を有する2つのパルス信号を生成する回路である。レベルシフト回路102を必要とするのは、後述する出力回路104に含まれる2つのスイッチ回路SW1,SW2が互いに異なるタイプの半導体スイッチング素子で構成されるとともに、各スイッチ回路SW1,SW2をオン・オフ動作させるための駆動電圧の変化範囲がパルス幅変調回路101から出力されるPWM信号Psのレベル変化の範囲と異なるため、スイッチ回路SW1,SW2を駆動するためのパルス信号をそれぞれ生成する必要があるからである。

【0006】

レベルシフト回路102に供給される電源電圧を±VBの一対の電源電圧であるとし、出力回路104における上側のスイッチ回路SW1に対するパルス信号をハイサイドPWM信号Ps1とし、下側のスイッチ回路SW2に対するパルス信号をローサイドPWM信号Ps2とすると、レベルシフト回路102は、図5(c)に示すように、PWM信号Psのレベル変化の範囲V1〜V2を+VB〜(+VB−ΔV)に変更したハイサイドPWM信号Ps1を生成するとともに、同図(d)に示すように、PWM信号Psのレベル変化の範囲V1〜V2を(−VB+ΔV)〜−VBに変更したローサイドPWM信号Ps2を生成する。なお、ハイサイドPWM信号Ps1およびローサイドPWM信号Ps2はPWM信号Psに対して同期した関係になっている。

【0007】

ドライバ回路103は、レベルシフト回路102から出力されるハイサイドPWM信号Ps1およびローサイドPWM信号Ps2に基づいて、出力回路104内のスイッチ回路SW1とスイッチ回路SW2をオン・オフ動作させるためのドライブ信号を生成する回路である。スイッチ回路SW1に対するドライブ信号(以下、「ハイサイドドライブ信号」という。)は、ドライバ回路103に入力される信号に同期してスイッチ回路SW1に電圧を印加するパルス信号であり、ハイサイドPWM信号Ps1に対して出力電流量を増幅した信号である。同様に、スイッチ回路SW2に対するドライブ信号(以下、「ローサイドドライブ信号」という。)はドライバ回路103に入力される信号に同期してスイッチ回路SW2に電圧を印加するパルス信号で、ローサイドPWM信号Ps2に対して出力電流量を増幅した信号である。

【0008】

従って、スイッチSW1,SW2を駆動するための電圧パルス信号でみると、ハイサイドドライブ信号の波形はハイサイドPWM信号Ps1の波形(図5(c)参照)と同じであり、ローサイドドライブ信号の波形はローサイドPWM信号Ps2の波形(図5(d)参照)と同じである。

【0009】

出力回路104は、極性の反転した2つの直流電源+VB,−VBが入力される一対の電源端子の間に直列に接続された種類の異なる半導体スイッチング素子からなる2つのスイッチ回路SW1とスイッチ回路SW2を有し、スイッチ回路SW1とスイッチ回路SW2の接続点Nから、図5(e)に示すように、パルス幅変調回路101で生成されたPWM信号Psに対してレベル変化の範囲を+VB〜−VBの範囲に増幅したPWM信号Psoutを出力する回路である。例えば、スイッチ回路SW1にはPチャネルMOSFET(Metal Oxide Semiconductor Field Effect Transistor)が用いられ、スイッチ回路SW2にはNチャネルMOSFETが用いられる。出力回路104から出力されるPWM信号Psoutは、ローパスフィルタからなるフィルタ回路105によって高周波成分が除去され(アナログのオーディオ信号に戻され)た後、スピーカSPに入力され、当該スピーカSPから音声出力される。

【0010】

上述したように、スイッチングアンプでは、パルス幅変調回路101の後段にレベルシフト回路102を設けてPWM信号Psのレベル変化の範囲とは異なるレベル変化の範囲を有するハイサイドPWM信号Ps1とローサイドPWM信号Ps2とを生成する必要がある。

【0011】

図6は、パルス幅変調回路101の後段に設けられるレベルシフト回路102の具体回路の一例を示す図である。

【0012】

同図に示すレベルシフト回路101は、直流電源+VBが入力される電源端子と極性の反転した直流電源−VBが入力される電源端子との間に抵抗R1、npn型トランジスタQ1、pnp型トランジスタQ2および抵抗R2をこの順に直列に接続するとともに、トランジスタQ1,Q2の接続点mにVm=(V1+V2)/2の電源回路102aを接続し、トランジスタQ1,Q2の両ベースに抵抗を介してパルス幅変調回路101の出力端子out1から出力されるPWM信号Psが入力され、トランジスタQ1およびトランジスタQ2の各コレクタからそれぞれハイサイドPWM信号Ps1とローサイドPWM信号Ps2が出力される構成となっている。

【0013】

PWM信号PsがハイレベルV1のとき(図5(b)のTONの期間参照)は、トランジスタQ1のベース電圧が当該トランジスタQ1のベース・エミッタ間の電圧Vbe1より大きくなるが、トランジスタQ2のベース電圧は当該トランジスタQ2のベース・エミッタ間の電圧Vbe2よりも小さくならないので、トランジスタQ1,Q2のオン・オフ関係は、(Q1,Q2)=(ON,OFF)となる。従って、トランジスタQ1のコレクタ電圧は電源電圧+VBから抵抗R1の電圧降下分ΔVだけ低下した電圧(+VB−ΔV)となり、トランジスタQ2のコレクタ電圧は電源電圧−VBとなる。

【0014】

逆に、PWM信号PsがローレベルV2のとき(図5(b)のTOFFの期間参照)は、トランジスタQ2のベース電圧がベース・エミッタ間の電圧Vbe2より小さくなるが、トランジスタQ1のベース電圧はベース・エミッタ間の電圧Vbe1よりも大きくならないので、トランジスタQ1,Q2のオン・オフ関係は、(Q1,Q2)=(OFF,ON)となる。従って、トランジスタQ1のコレクタ電圧は電源電圧+VBとなり、トランジスタQ2のコレクタ電圧は電源電圧−VBから抵抗R2の電圧降下分ΔVだけ上昇した電圧(−VB+ΔV)となる。

【先行技術文献】

【特許文献】

【0015】

【特許文献1】特開2009−65612号公報

【発明の概要】

【発明が解決しようとする課題】

【0016】

図6に示すレベルシフト回路102は、PWM信号Psのレベル変化の中点電圧(V1+V2)/2を基準レベルとし、PWM信号Psのレベルが(基準レベル+Vbe1)以上の範囲にあるか、(基準レベル−Vbe2)以下の範囲にあるかによって、トランジスタQ1,Q2のオン・オフの状態を交互に切り換える構成であるので、例えば、|+Vbe1|=|−Vbe2|=Vbeとすると、PWM信号Psのレベル変化の幅は2Vbe以上でなければ、トランジスタQ1,Q2のオン・オフの状態を正常に切り換えることができなくなるという問題がある。

【0017】

例えば、Vbeを0.6vとすると、PWM信号Psのレベルの変化幅が1.2vよりも大きくなければ、トランジスタQ1,Q2のオン・オフの状態を正常に切り換えることができなくなる。従って、パルス幅変調回路101の駆動電源には、(V1−V2)>1.2vの条件を満たさなければならないという制約が掛かることになり、V1,V2を低電圧化することができないという問題がある。

【0018】

また、トランジスタQ1とトランジスタQ2との接続点mに基準レベルを設定するための電源回路102aを設けているので、この電源回路102aに含まれる抵抗成分rや容量成分Cの影響を受け、図7に示すように、トランジスタQ1,Q2のオン・オフの状態が切り換わったときのハイサイドPWM信号Ps1およびローサイドPWM信号Ps2のレベル変化が緩慢になるという問題がある。

【0019】

すなわち、レベルシフト回路102に入力されるPWM信号Psは、パルスの立上がりおよび立下りのエッジ部分が略直角となる理想的な矩形波となっている。しかし、ハイサイドPWM信号Ps1は、立下がりタイミングにおいて、+VBから(+VB−ΔV)に立ち下がるまでに微小時間を要し、図7に示すように、立下り波形が傾斜した波形となる。また、ハイサイドPWM信号Ps1は、立上がりタイミングにおいて、(+VB−ΔV)から+VBに立ち上がるまでに微小時間を要し、図7に示すように、立下り波形が傾斜した波形となる。

【0020】

同様に、ローサイドPWM信号Ps2は、立下がりタイミングにおいて、(−VB+ΔV)から−VBに立ち下がるまでに微小時間を要し、図7に示すように、立下り波形が傾斜した波形となる。また、ローサイドPWM信号Ps2は、立上がりタイミングにおいて、−VBから(−VB+ΔV)に立ち上がるまでに微小時間を要し、図7に示すように、立下り波形が傾斜した波形となる。

【0021】

本発明は、上記の課題に鑑みてなされたものであり、ハイサイドPWM信号Ps1およびローサイドPWM信号Ps2の波形の立上り、立下りの遷移時間を短くすることができるとともに、回路の簡単化を図ることができるレベルシフト回路およびそのレベルシフト回路を備えたスイッチングアンプを提供することを目的とする。

【課題を解決するための手段】

【0022】

上記課題を解決するため、本発明では、次の技術的手段を講じている。

【0023】

本発明の第1の側面によって提供されるレベルシフト回路は、オーディオ信号に基づいて所定の振幅範囲でレベルが変化する第1のPWM信号と前記第1のPWM信号に対して逆相関係の第2のPWM信号を生成するパルス幅変調回路の後段に設けられ、前記所定の振幅範囲の上限値よりも高い第1のレベル値を基準にして所定の範囲でレベルが変化する第1のパルス信号と、前記所定の振幅範囲の下限値よりも低い第2のレベル値を基準にして前記所定の範囲でレベルが変化する第2のパルス信号とを生成するレベルシフト回路であって、前記第1のレベル値の電圧と前記第2のレベル値の電圧とが入力される一対の電圧入力端子間に、抵抗とN型半導体スイッチの第1の直列回路と、P型半導体スイッチと抵抗の第2の直列回路とを直列に接続した回路を有し、前記N型半導体スイッチおよび前記P型半導体スイッチの制御電極に前記パルス幅変調回路から出力される前記第1のPWM信号が入力され、前記N型半導体スイッチと前記P型半導体スイッチとの前記制御電極以外の電極の接続点に前記パルス幅変調回路から出力される前記第2のPWM信号が入力されることを特徴とする(請求項1)。

【0024】

本発明の第2の側面によって提供されるスイッチングアンプは、請求項1に記載のレベルシフト回路と、前記レベルシフト回路から出力される第1および第2のパルス信号に基づいて、前記所定の振幅範囲の上限値よりも高い第3のレベルと前記所定の振幅範囲の下限値よりも低い第3のレベルとの範囲でレベルが変化するスピーカ駆動用のPWM信号を生成する出力回路とを備えたことを特徴とする(請求項2)。

【0025】

好ましい実施の形態においては、前記出力回路は、前記第1のレベルの電源電圧と前記第3のレベルの電源電圧が入力される一対の電源端子間に、前記第1のパルス信号によってオン・オフ動作が制御されるP型半導体スイッチと前記第2のパルス信号によってオン・オフ動作が制御されるN型半導体スイッチとの直列回路が接続され、前記P型半導体スイッチと前記N型半導体スイッチの接続点から前記スピーカ駆動用のPWM信号を出力する回路からなる(請求項3)。

【発明の効果】

【0026】

本発明によれば、レベルシフト回路を一対の電圧入力端子間に、抵抗とN型半導体スイッチの第1の直列回路と、P型半導体スイッチと抵抗の第2の直列回路とを直列に接続した回路構成とし、N型半導体スイッチおよびP型半導体スイッチの制御電極にパルス幅変調回路から出力されるPWM信号を入力し、N型半導体スイッチとP型半導体スイッチとの接続点にPWM信号に対して逆相関係の第2のPWM信号を入力する構成としたので、PWM信号のレベルが変化する振幅範囲をV1〜V2とすると、N型半導体スイッチおよびP型半導体スイッチにはオン・オフさせるための信号として振幅がΔVs=V1−V2のパルス信号が入力されることになる。

【0027】

従来の構成では、N型半導体スイッチとP型半導体スイッチとの接続点にV1〜V2の中点電圧、すなわち(V1+V2)/2の電圧が入力されるので、例えばN型半導体スイッチをオン・オフさせるためのパルス信号の基準レベルに対する電圧はV1−(V1+V2)/2−Vbeである。一方、本発明によれば、N型半導体スイッチをオン・オフさせるためのパルス信号の基準レベルに対する電圧がV1−V2−Vbeとなる。N型半導体スイッチの制御電極に電圧V1が供給されるとき、基準レベルには電圧V2が供給されるからである。従って、V1−V2−Vbe>V1−(V1+V2)/2−Vbeであるので、同一の電圧V1,V2に対して、例えばN型半導体スイッチをオンオフ動作させるためのパルス信号の基準レベルに対する電圧を大きくすることができる。なお、P型半導体スイッチについても同様である。その結果、パルス幅変調回路の電源電圧V1,V2の低電圧化を図ることができる。

【0028】

また、従来のように、N型半導体スイッチとP型半導体スイッチとの接続点に中点電圧を供給するための電源回路を必要としないので、その分、レベルシフト回路の構成が簡単になる。また、その電源回路に含まれる容量成分や抵抗成分の影響を受けて第1および第2のパルス信号の立上がり/立下がりが緩やかに変化するということがなく、パルス信号の波形の立上がり、立下がりの遷移時間を短くすることができる。

【0029】

本発明のその他の特徴および利点は、添付図面を参照して以下に行う詳細な説明によって、より明らかとなろう。

【図面の簡単な説明】

【0030】

【図1】本発明に係るスイッチングアンプの特徴的な構成の部分を示す図である。

【図2】図1に示すレベルシフト回路のPWM信号の波形とハイサイドPWM信号およびローサイドPWM信号の波形との関係を示す図である。

【図3】図1に示すレベルシフト回路に組み合わされるパルス幅変調回路の具体回路の一例を示す図である。

【図4】一般的なスイッチングアンプの構成を示すブロック図図である。

【図5】図4に示すスイッチングアンプのパルス幅変調回路、レベルシフト回路および出力回路の入出力信号の波形の一例を示す図である。

【図6】パルス幅変調回路の後段に設けられるレベルシフト回路の具体回路の一例を示す図である。

【図7】図6に示すレベルシフト回路のPWM信号の波形とハイサイドPWM信号およびローサイドPWM信号の波形との関係を示す図である。

【発明を実施するための形態】

【0031】

本発明に係るスイッチングアンプは、図6に示す従来のレベルシフト回路102において、トランジスタQ1,Q2の接続点mへの電圧Vmの与え方を改良した点に特徴がある。具体的には、パルス幅変調回路からPWM信号Psと逆相の関係にあるPWM信号Ps’を出力する出力端子を追加し、その出力端子をトランジスタQ1,Q2の接続点mと接続するようにした構成に特徴がある。

【0032】

図1は、本発明に係るスイッチングアンプの特徴的な構成の部分を示す図で、図6に対応する図である。図1に示すパルス幅変調回路11とレベルシフト回路12は、図6に示すパルス幅変調回路101とレベルシフト回路102にそれぞれ対応している。パルス変調回路11の構成は、パルス変調回路101に対してPWM信号Psを出力する出力端子out1の他にPWM信号Psと逆相の関係にあるPWM信号Ps’を出力する出力端子out2を有する点が異なり、レベルシフト回路12の構成は、レベルシフト回路102に対して電源回路102aを除いた点が異なり、レベルシフト回路102のトランジスタQ1とトランジスタQ2の接続点mはパルス変調回路11のPWM信号Ps’の出力端子out2に接続されている。

【0033】

図1に示すレベルシフト回路12によれば、接続点mの電圧Vmは固定されておらず、トランジスタQ1およびトランジスタQ2のベース電圧の変化に応じて相対的に変化する。パルス変調回路11の電源電圧をV1,V2とすると、トランジスタQ1およびトランジスタQ2のベースには、図5(b)に示すPWM信号Psが入力され、接続点mにはPWM信号Psと逆相の関係にあるPWM信号Ps’が入力されるから、トランジスタQ1およびトランジスタQ2のベース電圧がV1のとき、接続点mの電圧VmはV2となり、トランジスタQ1およびトランジスタQ2のベース電圧がV2のとき、接続点mの電圧VmはV1となる。

【0034】

すなわち、トランジスタQ1,Q2のエミッタ(基準レベル)に対するベースの電圧は、PWM信号Psのレベルの変化に応じてV1−V2とV2−V1との間で交互に切り換わることになるので、トランジスタQ1,Q2のベース・エミッタ電圧(導通開始電圧)をVbeとすると、パルス変調回路11の電源電圧V1,V2は、V1−V2≧Vbe、V2−V1≦−Vbeを満たせば、トランジスタQ1,Q2のオン・オフの状態を正常に切り換えることができる。言い換えると、同一の電圧V1,V2であっても、トランジスタQ1のエミッタ基準のベース電圧を従来よりも大きくすることができ、トランジスタQ2のエミッタ基準のベース電圧を従来よりも小さくすることができる。従って、従来のスイッチングアンプ100に比べてパルス変調回路1の電源電圧V1,V2の低電圧化を図ることができる。

【0035】

また、レベルシフト回路12の接続点mには電源回路102aが設けられていないので、従来のレベルシフト回路102のように電源回路102aに含まれる抵抗成分rや容量成分C(図6参照)の影響を受けて、トランジスタQ1,Q2のオン・オフの状態が切り換わったときのハイサイドPWM信号Ps1およびローサイドPWM信号Ps2のレベル変化が緩やかになり遷移時間が長くなるという問題を解決することができる。すなわち、レベルシフト回路12では、ハイサイドPWM信号Ps1とローサイドPWM信号Ps2の波形は、図2に示すようになる。ハイサイドPWM信号Ps1では、立下がりタイミングtbにおいて+VBから(+VB−ΔV)に急峻に立ち下がり、立上がりタイミングtaにおいて(+VB−ΔV)から+VBに急峻に立ち上がることができる。同様に、ローサイドPWM信号Ps2では、立下がりタイミングtbにおいて(−VB+ΔV)から−VBに急峻に立ち下がり、立上がりタイミングtaにおいて−VBから(−VB+ΔV)に急峻に立ち上がることができる。

【0036】

また、レベルシフト回路12では、電源回路102aがなくなる分、従来のレベルシフト回路102よりも回路を簡単化することができる。

【0037】

図3は、図1に示すレベルシフト回路12に組み合わされるパルス幅変調回路11の具体回路の一例を示す図である。図3におけるレベルシフト回路12の具体回路の構成は、図1に示すものと同じであるので、説明は省略する。

【0038】

図3に示すパルス幅変調回路11は、特開2007−329698号公報に記載の差動増幅回路111と非安定マルチバイブレータを用いた積分型パルス幅変調回路112(以下、単に「変調回路」という。)で構成されている。差動増幅回路11Aは、特性の等しい2つのトランジスタTr1,Tr2のエミッタを抵抗を介して相互に接続し、その接続点にトランジスタTr3を用いた定電流回路111aを接続した構成の周知の差動増幅回路である。一方のトランジスタTr1のベースにオーディオ信号Esが入力され、他方のトランジスタTr2のベースは接地されている。トランジスタTr1,Tr2の各コレクタからはトランジスタTr1のベース電圧(Es)とトランジスタTr2のベース電圧(0)の差電圧(Es−0)を増幅した電圧が出力される。

【0039】

変調回路112は、抵抗からなるバイアス電流源112aと、バイアス電流源112aに接続された差動増幅回路112bと、差動増幅回路112bに接続されたパルス発生回路112cとによって構成されている。差動増幅回路112bは、エミッタが抵抗を介して接続された一対のトランジスタTr3とトランジスタTr4を有し、トランジスタTr3でベースに入力される差動増幅回路111のトランジスタTr1のコレクタ電圧e1が変換コンダクタンスGoによってコレクタ電流I1に変換され、トランジスタTr4でベースに入力される差動増幅回路111のトランジスタTr2のコレクタ電圧e2が変換コンダクタンスGoによってコレクタ電流I2に変換される。

【0040】

なお、変換コンダクタンスGoは、トランジスタTr3,Tr4のエミッタ抵抗をReとすると、Go≒1/(2・Re)であり、電量I1,I2は、バイアス電流源112aから差動増幅回路112bに供給されるバイアス電流を2IBとすると、I1=IB−Go・(e1−e2)、I2=IB+Go・(e1−e2)である。

【0041】

パルス発生回路112cは、電流I1,I2によってコンデンサC1,C2をそれぞれ所定の閾値電圧Vthまで充電し、その充電時間T1,T2をパルス幅とするパルス信号を生成する回路である。トランジスタTr3,Tr4のコレクタに接続されたダイオードD1,D2および電源Vbからなる回路はコンデンサC1,C2の充電電圧がVthになると、その蓄積電荷を放電させる回路である。

【0042】

コンデンサC1,C2が閾値電圧Vthまで充電される時間をそれぞれT1,T2とすると、I1・T1=C・Vth、I2・T2=C・Vthの関係がそれぞれ成立するので、充電時間T1,T2は、それぞれT1=C・Vth/I1、T2=C・Vth/I2となる。

【0043】

コンデンサC1,C2が交互に充放電を繰り返すと、コンデンサC1,C2の充放電に応じてレベルが変化するパルス信号がNOR回路NOR1,NOR2からそれぞれ出力される。コンデンサC1,C2は交互に充放電を繰り返すので、NOR回路NOR1から出力されるパルス信号とNOR回路NOR1から出力されるパルス信号とは互いに位相が逆になっている。従って、NOR回路NOR1から出力されるパルス信号をPWM信号Psとすると、NOR回路NOR2から出力されるパルス信号はPWM信号Ps’となる。

【0044】

そして、PWM信号Psは、抵抗を介してレベルシフト回路12のトランジスタQ1,Q2のベースに入力され、PWM信号Ps’は、レベルシフト回路12のトランジスタQ1,Q2の接続点mに入力される。

【0045】

図3に示すように、パルス幅変調回路11を差動増幅回路111と非安定マルチバイブレータを用いた変調回路112で構成することにより、パルス幅変調回路11から簡単にPWM信号Psとこれと逆相関係にあるPWM信号Ps’を出力させることができる。

【0046】

また、図3に示すパルス幅変調回路11は、回路構成が簡単なので、スイッチングアンプ全体の回路構成の簡単化に寄与する。なお、パルス幅変調回路11の具体回路は、図3に示すものに限られるものではなく、例えば、特開2008−206128号公報に記載される、基準クロックから充電開始タイミングと放電開始タイミングの制御信号を生成し、これらの制御信号によって2つのコンデンサの充放電制御用のスイッチをそれぞれ制御する方式のパルス幅変調回路を適用してもよい。

【0047】

また、上記実施形態では、パルス幅変調回路11にPWM信号Ps’の出力端子out1を設けていたが、レベルシフト回路12にPWM信号Psの位相を反転させる回路を設け、レベルシフト回路12内でPWM信号PsからPWM信号Ps’を生成するようにしてもよい。

【0048】

なお、上記実施形態では、レベルシフト回路12の半導体スイッチング素子Q1,Q2をトランジスタで構成していたが、FETで構成してもよい。また、抵抗R1,R2に代えてΔVの電圧降下を生じさせる素子若しくは回路を用いてもよい。

【符号の説明】

【0049】

1 スイッチングアンプ

11 PWM幅変調回路

111 差動増幅器

112 変調回路

12 レベルシフト回路

13 出力回路

SP スピーカ

R1,R2 抵抗

Q1 npn型トランジスタ

Q2 pnp型トランジスタ

Q3 PチャネルFET

Q4 NチャネルFET

【特許請求の範囲】

【請求項1】

オーディオ信号に基づいて所定の振幅範囲でレベルが変化する第1のPWM信号と前記第1のPWM信号に対して逆相関係の第2のPWM信号を生成するパルス幅変調回路の後段に設けられ、前記所定の振幅範囲の上限値よりも高い第1のレベル値を基準にして所定の範囲でレベルが変化する第1のパルス信号と、前記所定の振幅範囲の下限値よりも低い第2のレベル値を基準にして前記所定の範囲でレベルが変化する第2のパルス信号とを生成するレベルシフト回路であって、

前記第1のレベル値の電圧と前記第2のレベル値の電圧とが入力される一対の電圧入力端子間に、前記所定の範囲に相当するレベル変化を生じさせる回路とN型半導体スイッチの第1の直列回路と、P型半導体スイッチと前記所定の範囲に相当するレベル変化を生じさせる回路の第2の直列回路とを直列に接続した回路を有し、前記N型半導体スイッチおよび前記P型半導体スイッチの制御電極に前記パルス幅変調回路から出力される前記第1のPWM信号が入力され、前記N型半導体スイッチと前記P型半導体スイッチとの前記制御電極以外の電極の接続点に前記パルス幅変調回路から出力される前記第2のPWM信号が入力される、ことを特徴とするレベルシフト回路。

【請求項2】

請求項1に記載のレベルシフト回路と、

前記レベルシフト回路から出力される第1および第2のパルス信号に基づいて、前記所定の振幅範囲の上限値よりも高い第3のレベルと前記所定の振幅範囲の下限値よりも低い第3のレベルとの範囲でレベルが変化するスピーカ駆動用のPWM信号を生成する出力回路と、を備えたことを特徴とするスイッチングアンプ。

【請求項3】

前記出力回路は、前記第1のレベルの電源電圧と前記第3のレベルの電源電圧が入力される一対の電源端子間に、前記第1のパルス信号によってオン・オフ動作が制御されるP型半導体スイッチと前記第2のパルス信号によってオン・オフ動作が制御されるN型半導体スイッチとの直列回路が接続され、前記P型半導体スイッチと前記N型半導体スイッチの接続点から前記スピーカ駆動用のPWM信号を出力する回路からなる、請求項2に記載のスイッチングアンプ。

【請求項1】

オーディオ信号に基づいて所定の振幅範囲でレベルが変化する第1のPWM信号と前記第1のPWM信号に対して逆相関係の第2のPWM信号を生成するパルス幅変調回路の後段に設けられ、前記所定の振幅範囲の上限値よりも高い第1のレベル値を基準にして所定の範囲でレベルが変化する第1のパルス信号と、前記所定の振幅範囲の下限値よりも低い第2のレベル値を基準にして前記所定の範囲でレベルが変化する第2のパルス信号とを生成するレベルシフト回路であって、

前記第1のレベル値の電圧と前記第2のレベル値の電圧とが入力される一対の電圧入力端子間に、前記所定の範囲に相当するレベル変化を生じさせる回路とN型半導体スイッチの第1の直列回路と、P型半導体スイッチと前記所定の範囲に相当するレベル変化を生じさせる回路の第2の直列回路とを直列に接続した回路を有し、前記N型半導体スイッチおよび前記P型半導体スイッチの制御電極に前記パルス幅変調回路から出力される前記第1のPWM信号が入力され、前記N型半導体スイッチと前記P型半導体スイッチとの前記制御電極以外の電極の接続点に前記パルス幅変調回路から出力される前記第2のPWM信号が入力される、ことを特徴とするレベルシフト回路。

【請求項2】

請求項1に記載のレベルシフト回路と、

前記レベルシフト回路から出力される第1および第2のパルス信号に基づいて、前記所定の振幅範囲の上限値よりも高い第3のレベルと前記所定の振幅範囲の下限値よりも低い第3のレベルとの範囲でレベルが変化するスピーカ駆動用のPWM信号を生成する出力回路と、を備えたことを特徴とするスイッチングアンプ。

【請求項3】

前記出力回路は、前記第1のレベルの電源電圧と前記第3のレベルの電源電圧が入力される一対の電源端子間に、前記第1のパルス信号によってオン・オフ動作が制御されるP型半導体スイッチと前記第2のパルス信号によってオン・オフ動作が制御されるN型半導体スイッチとの直列回路が接続され、前記P型半導体スイッチと前記N型半導体スイッチの接続点から前記スピーカ駆動用のPWM信号を出力する回路からなる、請求項2に記載のスイッチングアンプ。

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【公開番号】特開2010−263474(P2010−263474A)

【公開日】平成22年11月18日(2010.11.18)

【国際特許分類】

【出願番号】特願2009−113587(P2009−113587)

【出願日】平成21年5月8日(2009.5.8)

【出願人】(000000273)オンキヨー株式会社 (502)

【Fターム(参考)】

【公開日】平成22年11月18日(2010.11.18)

【国際特許分類】

【出願日】平成21年5月8日(2009.5.8)

【出願人】(000000273)オンキヨー株式会社 (502)

【Fターム(参考)】

[ Back to top ]