スイッチング回路、及びトランジスタの駆動回路

【課題】トランジスタのゲート電位をスレショルド電位未満に維持するための構成を備えるスイッチング回路において、ゲート電位の立ち上がりの遅延を抑制すること等。

【解決手段】電圧制御される主トランジスタと、グランド端子に接続され、前記主トランジスタのゲートスレショルド電圧よりもオン時ドレインーソース間電圧が低い副トランジスタと、第1の抵抗が設けられ、電源装置に接続される端子と前記主トランジスタのゲートとを接続する第1の電力ラインと、前記主トランジスタのゲートから前記副トランジスタへ流れる電流を選択的に許容する第2の電力ラインと、第2の抵抗が設けられ、前記端子と前記副トランジスタとを接続する第3の電力ラインと、を有し、前記第2の抵抗の抵抗値は、前記主トランジスタの容量と前記第1の抵抗の抵抗値の積を前記副トランジスタの容量で除した値よりも小さい値である、スイッチング回路。

【解決手段】電圧制御される主トランジスタと、グランド端子に接続され、前記主トランジスタのゲートスレショルド電圧よりもオン時ドレインーソース間電圧が低い副トランジスタと、第1の抵抗が設けられ、電源装置に接続される端子と前記主トランジスタのゲートとを接続する第1の電力ラインと、前記主トランジスタのゲートから前記副トランジスタへ流れる電流を選択的に許容する第2の電力ラインと、第2の抵抗が設けられ、前記端子と前記副トランジスタとを接続する第3の電力ラインと、を有し、前記第2の抵抗の抵抗値は、前記主トランジスタの容量と前記第1の抵抗の抵抗値の積を前記副トランジスタの容量で除した値よりも小さい値である、スイッチング回路。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、電圧制御型トランジスタのゲートに電圧を印加して動作させるスイッチング回路、及びその一部を構成するトランジスタの駆動回路に関する。

【背景技術】

【0002】

近年、インバータの一部を構成する半導体装置において、電圧制御型のトランジスタ、特にIGBT(Insulated Gate Bipolar Transistor)やMOSFET(Metal Oxide Semiconductor Field Effect Transistor)が広く用いられている。これらのトランジスタは、電源にスイッチや電圧調整用の抵抗を介してゲートが接続され、スイッチの駆動によりゲート電位がスレショルド電位以上となったときにコレクタ−エミッタ間(又はソース−ドレイン間)に電流(以下、主電流と称する)が流れるように動作する。逆に、主電流を流さないように制御する際には、スイッチの駆動により抵抗を介してゲートを低電位の端子(一般的にはグランド端子)に接続し、ゲート電位がスレショルド電位未満となるようにする。

【0003】

これらのトランジスタにおいて、主電流が変化する際に(特に、インバータの上下アームのトランジスタのオンオフが切り替わる際に)、電流の一部がゲートに流れ込むという現象が知られている。上記の構成では、ゲートに流れ込んだ電流は抵抗を介してグランド端子に流れることとなり、このゲートに流れ込んだ電流が大きいときには、スイッチをグランド端子側にしているにも拘わらず、ゲート電位がスレショルド電位以上のまま維持されてしまうという問題が生じる。この結果、インバータの同一アームのトランジスタが同時にオンするアーム短絡等が発生し、トランジスタが破壊される場合がある。このため、所望のタイミングで、ゲート電位を迅速にスレショルド電位未満にする仕組みを有することが望ましい。

【0004】

係る問題点に配慮した半導体装置の保護回路についての発明が開示されている(例えば、特許文献1参照)。この保護回路は、主電流の増加に応じて上昇する検出電圧がしきい電圧を超えたときに、自動的に主トランジスタのゲートをエミッタに接続するように構成されており、これによって、主電流の増加時に主トランジスタのゲート電位が強制的にスレショルド電位未満になるように制御している。

【特許文献1】特開平10−145206号公報

【発明の開示】

【発明が解決しようとする課題】

【0005】

しかしながら、上記従来の特許文献1に記載の保護回路は、主トランジスタのゲートをエミッタに接続するためのトランジスタ(以下、オフ保持用トランジスタと称する)が主トランジスタと並列に電源装置に接続された構成である。従って、オフ保持用トランジスタのドレイン−ソース間容量に起因して、電圧印加開始から主トランジスタのゲート電位がスレショルド電位に達するまでの時間が長くなるという問題が生じる。この時間が長くなると、半導体装置全体性の応答性が悪くなるだけでなく、主トランジスタの発熱が大きくなり、十分な放熱性を確保しなければならないこととなる。このために、主トランジスタのサイズを大きくしたり、定格電流を下げたりするものとすると、装置のコスト増や性能低下を招くため、好ましくない。また、この時間がオフ保持用トランジスタのドレイン−ソース間容量に依存するため、回路全体の設計が煩わしくなるという問題も生じる。

【0006】

本発明はこのような課題を解決するためのものであり、トランジスタのゲート電位をスレショルド電位未満に維持するための構成を備えるスイッチング回路において、ゲート電位の立ち上がりの遅延を抑制することを、主たる目的とする。

【課題を解決するための手段】

【0007】

上記目的を達成するための本発明の第1の態様は、

電圧制御される主トランジスタと、

グランド端子に接続され、前記主トランジスタのゲートスレショルド電圧よりもオン時ドレインーソース間電圧が低い副トランジスタと、

第1の抵抗が設けられ、電源装置に接続される端子と前記主トランジスタのゲートとを接続する第1の電力ラインと、

前記主トランジスタのゲートから前記副トランジスタへ流れる電流を選択的に許容する第2の電力ラインと、

第2の抵抗が設けられ、前記端子と前記副トランジスタとを接続する第3の電力ラインと、を有し、

前記第2の抵抗の抵抗値は、前記主トランジスタの容量と前記第1の抵抗の抵抗値の積を前記副トランジスタの容量で除した値よりも小さい値である、

スイッチング回路である。

【0008】

この本発明の第1の態様によれば、従来の、トランジスタのゲート電位をスレショルド電位未満に維持するための構成を備えるもの比して、ゲート電位の立ち上がりの遅延を抑制することができる。

【0009】

本発明の第2の態様は、

電圧制御される主トランジスタと、

グランド端子に接続され、前記主トランジスタのゲートスレショルド電圧よりもオン時ドレインーソース間電圧が低い副トランジスタと、

第1の抵抗が設けられ、電源装置に接続される端子と前記主トランジスタのゲートとを接続する第1の電力ラインと、

前記主トランジスタのゲートから前記副トランジスタへ流れる電流を選択的に許容する第2の電力ラインと、

第2の抵抗が設けられ、前記端子と前記副トランジスタとを接続する第3の電力ラインと、を有し、

前記第2の抵抗の抵抗値は、前記第1の抵抗の抵抗値よりも小さい値である、

スイッチング回路である。

【0010】

この本発明の第2の態様によれば、従来の、トランジスタのゲート電位をスレショルド電位未満に維持するための構成を備えるもの比して、ゲート電位の立ち上がりの遅延を抑制することができる。

【0011】

本発明の第1又は第2の態様において、前記第3の電力ラインは、前記第2の端子から前記副トランジスタへ流れる電流を選択的に許容するものとすると、好適である。

【0012】

本発明の第3の態様は、

主トランジスタを電圧制御するためのトランジスタの駆動回路であって、

グランド端子に接続された副トランジスタと、

第1の抵抗が設けられ、電源装置に接続される端子と前記主トランジスタのゲートとを接続する第1の電力ラインと、

前記主トランジスタのゲートから前記副トランジスタへ流れる電流を選択的に許容する第2の電力ラインと、

第2の抵抗が設けられ、前記端子と前記副トランジスタとを接続する第3の電力ラインと、

を有するトランジスタの駆動回路である。

【発明の効果】

【0013】

本発明によれば、トランジスタのゲート電位をスレショルド電位未満に維持するための構成を備えるスイッチング回路において、ゲート電位の立ち上がりの遅延を抑制することができる。

【発明を実施するための最良の形態】

【0014】

以下、本発明を実施するための最良の形態について、添付図面を参照しながら実施例を挙げて説明する。

【実施例】

【0015】

以下、本発明の一実施例に係るスイッチング回路1について説明する。

【0016】

[構成]

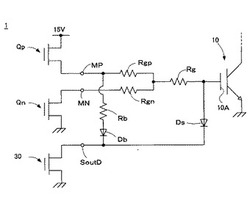

図1は、スイッチング回路1の全体構成の一例を示す図である。スイッチング回路1は、主要な構成として、電圧制御されるIGBT(Insulated Gate Bipolar Transistor)10と、抵抗Rg、Rgp、Rgn、Rb、ダイオードDs、Db、端子MP、MN、SoutD、及びこれらを接続する電力線と、トランジスタ30と、を備える。なお、IGBT10が、特許請求の範囲における「主トランジスタ」に相当し、トランジスタ30が、特許請求の範囲における「副トランジスタ」に相当する。また、スイッチング回路1からIGBT10を除いたものが、特許請求の範囲における「トランジスタの駆動回路」に相当する。

【0017】

IGBT10は、MOSFET(Metal Oxide Semiconductor Field Effect Transistor)をゲート部に組み込んだバイポーラトランジスタであり、ゲート10Aの電位(ゲート電位)がスレショルド電位(例えば、3[V]等)以上となったときに、コレクタ−エミッタ間に電流を流すように動作する。なお、主トランジスタはIGBTに限定されず、MOSFET等、他の種類の電圧制御型トランジスタが用いられてもよい。

【0018】

端子MPには、例えば定格電圧が15[V]であるバッテリ等の電源の正極が、スイッチング素子Qpを介して接続される。また、端子MNには、バッテリ等の電源の負極及びグランド端子(0[V])が、スイッチング素子Qnを介して接続される。スイッチング素子Qp、Qnは、いずれか一方のみがオンとなるように、図示しない制御装置によって制御される。

【0019】

端子SoutDには、電源の負極及びグランド端子がトランジスタ30を介して接続される。トランジスタ30は、例えばMOSFETであり、IGBT10のコレクタ−エミッタ間に流れる電流(以下、主電流と称する)が大きく変化したときにオンとなるように、図示しない制御装置によって制御される。また、これに限らず、スイッチング素子Qp、Qnのオンオフと同期して定期的にオンとなるように制御されてもよい。

【0020】

端子MPからゲート10Aに至る電力線(特許請求の範囲における「第1の電力ライン」に相当する)には、抵抗Rgp、Rgが順に設けられている。

【0021】

ゲート10Aから端子SoutDに至る電力線(特許請求の範囲における「第2の電力ライン」に相当する)には、ダイオードDsが設けられており、出力端子MGから端子SoutDへ流れる電流を選択的に許容するようになっている。

【0022】

端子MPから端子SoutDに至る電力線(特許請求の範囲における「第3の電力ライン」に相当する)には、抵抗Rb及びダイオードDbが設けられており、端子MPから端子SoutDへ流れる電流を選択的に許容するようになっている。

【0023】

また、端子MPからゲート10Aに至る電力線における抵抗Rgpと抵抗Rgの間から分岐して端子MNに至る電力線には、抵抗Rgnが設けられている。

【0024】

抵抗Rbの抵抗値は、抵抗RgとRgpの抵抗値の和にIGBT10のゲート−エミッタ間容量Csを乗じた値をトランジスタ30のドレイン−ソース間容量Cmで除した値よりも小さい値である。この意義については後述する。

【0025】

[従来からの問題点]

ここで、従来の装置において生じる問題点について説明する。図2は、従来の半導体装置の構成を簡略化して示す図である。この半導体装置では、主トランジスタのゲート電位をグランド電位に強制的に低下させるための副トランジスタが、主トランジスタと並列に電源装置に接続されている。電源装置とこれらのトランジスタの間には。抵抗Rjが設けられている。

【0026】

係る構成では、電源装置がオンとなってから主トランジスタのゲート電位がスレショルド電位以上となるまでの時間が、副トランジスタの容量(副トランジスタがMOSFETであればドレイン−ソース容量)Csjに依存し、副トランジスタを備えない場合に比して長くなってしまう。図3は、係る様子を示す図である。本図において、主トランジスタの容量をCmjと表記した。この結果、半導体装置全体性の応答性が悪くなるだけでなく、主トランジスタの発熱が大きくなり、十分な放熱性を確保しなければならないこととなる。このために、主トランジスタのサイズを大きくしたり、定格電流を下げたりすることが考えられるが、装置のコスト増や性能低下を招くため、好ましくない。また、この時間がオフ保持用トランジスタのドレイン−ソース間容量に依存するため、回路全体の設計が煩わしくなるという問題も生じる。

【0027】

[スイッチング回路1の動作]

これに対し、本実施例のスイッチング回路1では、スイッチング素子Qpがオンとなってから最も早く電位が立ち上がる端子MPから端子SoutDに至る電力線に、抵抗Rbを設けているため、トランジスタ30のドレイン電位が上昇するのと並行してゲート10Aのゲート電位が上昇することとなる。従って、従来の構成に比して、ゲート電位の立ち上がりの遅延を抑制することができる。また、従来の構成に抵抗やダイオードを追加したのみであるため、消費電力が増大しない。なお、IGBT10のコレクタ−エミッタ間に流れる主電流が変化する際にゲートに流れ込むと見込まれる電流によりゲート10Aのゲート電位がスレショルド電圧を超えることがないように、十分小さい等価抵抗のトランジスタ30を用いている。

【0028】

また、スイッチング回路1は、ゲート10Aとトランジスタ30との間にダイオードDsを備えている。これにより、トランジスタ30に供給されるべき電流がゲート10Aに回ってゲート10Aの電位を上昇させるのを防止している。従って、ゲート10Aの電位の立ち上がりはIGBT10のゲート−エミッタ間容量Cm及び抵抗Rgp、Rgに依存することとなり、回路全体の設計を容易にすることができる。

【0029】

更に、スイッチング回路1は、抵抗Rbの抵抗値を、抵抗RgとRgpの抵抗値の和にIGBT10のゲート−エミッタ間容量Cmを乗じた値をトランジスタ30のドレイン−ソース間容量Csで除した値よりも小さい値としている。これにより、トランジスタ30のドレイン電位は、ゲート10Aの電位よりも早く立ち上がることとなる。従って、ゲート10Aの電位が先に立ち上がることによりゲート10Aからトランジスタ30に電流が流れ、ゲート10Aの電位が不安定になる(例えば、振動等を生じる)という不都合が生じるのを回避している。

【0030】

図4は、これらの構成により実現される、IGBT10のゲート電位、及びトランジスタ30のドレイン電位の特性を示す図である。

【0031】

なお、ダイオードDbは、トランジスタ30がオフの状態でスイッチング素子Qpがオフ、Qnがオンとなった場合(通常時のIGBT10オフ動作時)において、ゲート10Aから流れる電流が、抵抗Rg、及びRgnを通って端子MNに至るようにするためのものである。ダイオードDbが存在しない場合、ゲート10AからダイオードDs、抵抗Rb、Rgp、Rgnを順に通って端子MNに至る電力径路が存在するため、ゲート10Aの電位を低下させる際の応答を最適化するための回路全体の設計(実際には抵抗比の決定等)が困難なものとなる。ダイオードDbを備えることにより、抵抗Rg,Rgp、Rgnの比率等を最適に決定するのが容易となるのである。

【0032】

[利用例]

スイッチング回路1は、例えば図5に示す如きインバータ50の一部として用いられる。インバータ50は、3本のアーム51、52、53を有し、各アームにIGBT10が2個取り付けられている。各アームにおけるIGBT10は、一方がオンであれば他方がオフとなるように、図示しない制御装置によって制御される。そして、各アームに取り付けられたIGBT10が、例えば120度の位相ズレをもってオンオフ制御され、モータ60が回転制御される。この際に、IGBT10には上記の如くゲート10Aの電位を所望のタイミングで迅速に低下させるための構成が接続されているため、同一アームのトランジスタが同時にオンするアーム短絡等が発生することが防止される。

【0033】

[まとめ]

以上説明した本実施例のスイッチング回路1によれば、端子MPから端子SoutDに至る電力線に抵抗Rbを設けているため、トランジスタ30のドレイン電位が上昇するのと並行してゲート10Aのゲート電位が上昇する。従って、従来の構成に比して、消費電力を余り上昇させることなく、ゲート電位の立ち上がりの遅延を抑制することができる。

【0034】

また、ゲート10Aとトランジスタ30との間にダイオードDsを備えているため、ゲート10Aの電位の立ち上がりが抵抗Rgp、Rgに依存することとなり、回路全体の設計を容易にすることができる。更に、抵抗Rbの抵抗値を、抵抗RgとRgpの抵抗値の和にIGBT10のゲート−エミッタ間容量を乗じた値をトランジスタ30のドレイン−ソース間容量で除した値よりも小さい値としているため、ゲート10Aの電位が先に立ち上がることによりゲート10Aからトランジスタ30に電流が流れ、ゲート10Aの電位が不安定になるという不都合が生じるのを回避することができる。

【0035】

[変形例]

以上、本発明を実施するための最良の形態について実施例を用いて説明したが、本発明はこうした実施例に何等限定されるものではなく、本発明の要旨を逸脱しない範囲内において種々の変形及び置換を加えることができる。

【0036】

例えば、抵抗Rbの抵抗値を、抵抗RgとRgpの抵抗値の和にIGBT10のゲート−エミッタ間容量を乗じた値をトランジスタ30のドレイン−ソース間容量で除した値よりも小さい値とするものとしたが、より簡易な制約を課してもよい。例えば、IGBT10のゲート−エミッタ間容量Cmが、トランジスタ30のドレイン−ソース間容量Cs以上である装置に適用することを前提とすれば、単に、抵抗Rbの抵抗値を、抵抗RgとRgpの抵抗値の和よりも小さい値とするものとしてもよい。

【0037】

また、図6に示す如く、抵抗RgpとRgnを区別せず、ゲート10Aのオン制御時の電力径路とオフ制御時の電力径路を共用するものとしてもよい。この場合、端子MPとMNを区別する必要はない。

【0038】

また、図7に示す如く、ゲート10Aから端子SoutDに至る電力線の途中にバッファ70を設けてもよい。本図の構成は、出力端子MGから端子SoutDに流れる電流が比較的大きい場合に適用されると好適である。バッファ70は、トランジスタ72と、抵抗Rebと、を備える。トランジスタ72は、トランジスタ30と同様、IGBT10のコレクタ−エミッタ間に流れる主電流が変化する際にゲートに流れ込むと見込まれる電流によりゲート10Aのゲート電位がスレショルド電圧を超えることがないように、十分小さい抵抗を用いている。トランジスタ72は、エミッタ−ベース間に一定以上の電位差が発生するとオン状態となるように動作する。抵抗Rebは、トランジスタ30がオフ状態となったときにトランジスタ72のベース−エミッタ間の電位差を0[V]にするために設けられている。係る構成によれば、出力端子MGから端子SoutDに流れる電流が比較的大きい場合にも対応することができる。

【産業上の利用可能性】

【0039】

本発明は、自動車製造業や自動車部品製造業等に利用可能である。

【図面の簡単な説明】

【0040】

【図1】本発明の一実施例に係るスイッチング回路1の全体構成の一例を示す図である。

【図2】従来の半導体装置の構成を簡略化して示す図である。

【図3】主トランジスタのゲート電位がスレショルド電位以上となるまでの時間が、副トランジスタの容量に依存して、副トランジスタを備えない場合に比して長くなってしまう様子を示す図である。

【図4】本実施例の構成により実現される、IGBT10のゲート電位、及びトランジスタ30のドレイン電位の特性を示す図である。

【図5】スイッチング回路1が好適に適用されるインバータ50の構成例である。

【図6】抵抗RgpとRgnを区別せず、ゲート10Aのオン制御時の電力径路とオフ制御時の電力径路を共用する場合の構成例である。

【図7】ゲート10Aから端子SoutDに至る電力線の途中にバッファ70を設けた場合の構成例である。

【符号の説明】

【0041】

1 スイッチング回路

10 IGBT

10A ゲート

30、72 トランジスタ

50 インバータ

51、52、53 アーム

60 モータ

70 バッファ

Ds、Db ダイオード

Qp、Qn スイッチング素子

Rg、Rgp、Rgn、Rb、Rj、Reb 抵抗

MP、MN、SoutD 端子

MG 出力端子

【技術分野】

【0001】

本発明は、電圧制御型トランジスタのゲートに電圧を印加して動作させるスイッチング回路、及びその一部を構成するトランジスタの駆動回路に関する。

【背景技術】

【0002】

近年、インバータの一部を構成する半導体装置において、電圧制御型のトランジスタ、特にIGBT(Insulated Gate Bipolar Transistor)やMOSFET(Metal Oxide Semiconductor Field Effect Transistor)が広く用いられている。これらのトランジスタは、電源にスイッチや電圧調整用の抵抗を介してゲートが接続され、スイッチの駆動によりゲート電位がスレショルド電位以上となったときにコレクタ−エミッタ間(又はソース−ドレイン間)に電流(以下、主電流と称する)が流れるように動作する。逆に、主電流を流さないように制御する際には、スイッチの駆動により抵抗を介してゲートを低電位の端子(一般的にはグランド端子)に接続し、ゲート電位がスレショルド電位未満となるようにする。

【0003】

これらのトランジスタにおいて、主電流が変化する際に(特に、インバータの上下アームのトランジスタのオンオフが切り替わる際に)、電流の一部がゲートに流れ込むという現象が知られている。上記の構成では、ゲートに流れ込んだ電流は抵抗を介してグランド端子に流れることとなり、このゲートに流れ込んだ電流が大きいときには、スイッチをグランド端子側にしているにも拘わらず、ゲート電位がスレショルド電位以上のまま維持されてしまうという問題が生じる。この結果、インバータの同一アームのトランジスタが同時にオンするアーム短絡等が発生し、トランジスタが破壊される場合がある。このため、所望のタイミングで、ゲート電位を迅速にスレショルド電位未満にする仕組みを有することが望ましい。

【0004】

係る問題点に配慮した半導体装置の保護回路についての発明が開示されている(例えば、特許文献1参照)。この保護回路は、主電流の増加に応じて上昇する検出電圧がしきい電圧を超えたときに、自動的に主トランジスタのゲートをエミッタに接続するように構成されており、これによって、主電流の増加時に主トランジスタのゲート電位が強制的にスレショルド電位未満になるように制御している。

【特許文献1】特開平10−145206号公報

【発明の開示】

【発明が解決しようとする課題】

【0005】

しかしながら、上記従来の特許文献1に記載の保護回路は、主トランジスタのゲートをエミッタに接続するためのトランジスタ(以下、オフ保持用トランジスタと称する)が主トランジスタと並列に電源装置に接続された構成である。従って、オフ保持用トランジスタのドレイン−ソース間容量に起因して、電圧印加開始から主トランジスタのゲート電位がスレショルド電位に達するまでの時間が長くなるという問題が生じる。この時間が長くなると、半導体装置全体性の応答性が悪くなるだけでなく、主トランジスタの発熱が大きくなり、十分な放熱性を確保しなければならないこととなる。このために、主トランジスタのサイズを大きくしたり、定格電流を下げたりするものとすると、装置のコスト増や性能低下を招くため、好ましくない。また、この時間がオフ保持用トランジスタのドレイン−ソース間容量に依存するため、回路全体の設計が煩わしくなるという問題も生じる。

【0006】

本発明はこのような課題を解決するためのものであり、トランジスタのゲート電位をスレショルド電位未満に維持するための構成を備えるスイッチング回路において、ゲート電位の立ち上がりの遅延を抑制することを、主たる目的とする。

【課題を解決するための手段】

【0007】

上記目的を達成するための本発明の第1の態様は、

電圧制御される主トランジスタと、

グランド端子に接続され、前記主トランジスタのゲートスレショルド電圧よりもオン時ドレインーソース間電圧が低い副トランジスタと、

第1の抵抗が設けられ、電源装置に接続される端子と前記主トランジスタのゲートとを接続する第1の電力ラインと、

前記主トランジスタのゲートから前記副トランジスタへ流れる電流を選択的に許容する第2の電力ラインと、

第2の抵抗が設けられ、前記端子と前記副トランジスタとを接続する第3の電力ラインと、を有し、

前記第2の抵抗の抵抗値は、前記主トランジスタの容量と前記第1の抵抗の抵抗値の積を前記副トランジスタの容量で除した値よりも小さい値である、

スイッチング回路である。

【0008】

この本発明の第1の態様によれば、従来の、トランジスタのゲート電位をスレショルド電位未満に維持するための構成を備えるもの比して、ゲート電位の立ち上がりの遅延を抑制することができる。

【0009】

本発明の第2の態様は、

電圧制御される主トランジスタと、

グランド端子に接続され、前記主トランジスタのゲートスレショルド電圧よりもオン時ドレインーソース間電圧が低い副トランジスタと、

第1の抵抗が設けられ、電源装置に接続される端子と前記主トランジスタのゲートとを接続する第1の電力ラインと、

前記主トランジスタのゲートから前記副トランジスタへ流れる電流を選択的に許容する第2の電力ラインと、

第2の抵抗が設けられ、前記端子と前記副トランジスタとを接続する第3の電力ラインと、を有し、

前記第2の抵抗の抵抗値は、前記第1の抵抗の抵抗値よりも小さい値である、

スイッチング回路である。

【0010】

この本発明の第2の態様によれば、従来の、トランジスタのゲート電位をスレショルド電位未満に維持するための構成を備えるもの比して、ゲート電位の立ち上がりの遅延を抑制することができる。

【0011】

本発明の第1又は第2の態様において、前記第3の電力ラインは、前記第2の端子から前記副トランジスタへ流れる電流を選択的に許容するものとすると、好適である。

【0012】

本発明の第3の態様は、

主トランジスタを電圧制御するためのトランジスタの駆動回路であって、

グランド端子に接続された副トランジスタと、

第1の抵抗が設けられ、電源装置に接続される端子と前記主トランジスタのゲートとを接続する第1の電力ラインと、

前記主トランジスタのゲートから前記副トランジスタへ流れる電流を選択的に許容する第2の電力ラインと、

第2の抵抗が設けられ、前記端子と前記副トランジスタとを接続する第3の電力ラインと、

を有するトランジスタの駆動回路である。

【発明の効果】

【0013】

本発明によれば、トランジスタのゲート電位をスレショルド電位未満に維持するための構成を備えるスイッチング回路において、ゲート電位の立ち上がりの遅延を抑制することができる。

【発明を実施するための最良の形態】

【0014】

以下、本発明を実施するための最良の形態について、添付図面を参照しながら実施例を挙げて説明する。

【実施例】

【0015】

以下、本発明の一実施例に係るスイッチング回路1について説明する。

【0016】

[構成]

図1は、スイッチング回路1の全体構成の一例を示す図である。スイッチング回路1は、主要な構成として、電圧制御されるIGBT(Insulated Gate Bipolar Transistor)10と、抵抗Rg、Rgp、Rgn、Rb、ダイオードDs、Db、端子MP、MN、SoutD、及びこれらを接続する電力線と、トランジスタ30と、を備える。なお、IGBT10が、特許請求の範囲における「主トランジスタ」に相当し、トランジスタ30が、特許請求の範囲における「副トランジスタ」に相当する。また、スイッチング回路1からIGBT10を除いたものが、特許請求の範囲における「トランジスタの駆動回路」に相当する。

【0017】

IGBT10は、MOSFET(Metal Oxide Semiconductor Field Effect Transistor)をゲート部に組み込んだバイポーラトランジスタであり、ゲート10Aの電位(ゲート電位)がスレショルド電位(例えば、3[V]等)以上となったときに、コレクタ−エミッタ間に電流を流すように動作する。なお、主トランジスタはIGBTに限定されず、MOSFET等、他の種類の電圧制御型トランジスタが用いられてもよい。

【0018】

端子MPには、例えば定格電圧が15[V]であるバッテリ等の電源の正極が、スイッチング素子Qpを介して接続される。また、端子MNには、バッテリ等の電源の負極及びグランド端子(0[V])が、スイッチング素子Qnを介して接続される。スイッチング素子Qp、Qnは、いずれか一方のみがオンとなるように、図示しない制御装置によって制御される。

【0019】

端子SoutDには、電源の負極及びグランド端子がトランジスタ30を介して接続される。トランジスタ30は、例えばMOSFETであり、IGBT10のコレクタ−エミッタ間に流れる電流(以下、主電流と称する)が大きく変化したときにオンとなるように、図示しない制御装置によって制御される。また、これに限らず、スイッチング素子Qp、Qnのオンオフと同期して定期的にオンとなるように制御されてもよい。

【0020】

端子MPからゲート10Aに至る電力線(特許請求の範囲における「第1の電力ライン」に相当する)には、抵抗Rgp、Rgが順に設けられている。

【0021】

ゲート10Aから端子SoutDに至る電力線(特許請求の範囲における「第2の電力ライン」に相当する)には、ダイオードDsが設けられており、出力端子MGから端子SoutDへ流れる電流を選択的に許容するようになっている。

【0022】

端子MPから端子SoutDに至る電力線(特許請求の範囲における「第3の電力ライン」に相当する)には、抵抗Rb及びダイオードDbが設けられており、端子MPから端子SoutDへ流れる電流を選択的に許容するようになっている。

【0023】

また、端子MPからゲート10Aに至る電力線における抵抗Rgpと抵抗Rgの間から分岐して端子MNに至る電力線には、抵抗Rgnが設けられている。

【0024】

抵抗Rbの抵抗値は、抵抗RgとRgpの抵抗値の和にIGBT10のゲート−エミッタ間容量Csを乗じた値をトランジスタ30のドレイン−ソース間容量Cmで除した値よりも小さい値である。この意義については後述する。

【0025】

[従来からの問題点]

ここで、従来の装置において生じる問題点について説明する。図2は、従来の半導体装置の構成を簡略化して示す図である。この半導体装置では、主トランジスタのゲート電位をグランド電位に強制的に低下させるための副トランジスタが、主トランジスタと並列に電源装置に接続されている。電源装置とこれらのトランジスタの間には。抵抗Rjが設けられている。

【0026】

係る構成では、電源装置がオンとなってから主トランジスタのゲート電位がスレショルド電位以上となるまでの時間が、副トランジスタの容量(副トランジスタがMOSFETであればドレイン−ソース容量)Csjに依存し、副トランジスタを備えない場合に比して長くなってしまう。図3は、係る様子を示す図である。本図において、主トランジスタの容量をCmjと表記した。この結果、半導体装置全体性の応答性が悪くなるだけでなく、主トランジスタの発熱が大きくなり、十分な放熱性を確保しなければならないこととなる。このために、主トランジスタのサイズを大きくしたり、定格電流を下げたりすることが考えられるが、装置のコスト増や性能低下を招くため、好ましくない。また、この時間がオフ保持用トランジスタのドレイン−ソース間容量に依存するため、回路全体の設計が煩わしくなるという問題も生じる。

【0027】

[スイッチング回路1の動作]

これに対し、本実施例のスイッチング回路1では、スイッチング素子Qpがオンとなってから最も早く電位が立ち上がる端子MPから端子SoutDに至る電力線に、抵抗Rbを設けているため、トランジスタ30のドレイン電位が上昇するのと並行してゲート10Aのゲート電位が上昇することとなる。従って、従来の構成に比して、ゲート電位の立ち上がりの遅延を抑制することができる。また、従来の構成に抵抗やダイオードを追加したのみであるため、消費電力が増大しない。なお、IGBT10のコレクタ−エミッタ間に流れる主電流が変化する際にゲートに流れ込むと見込まれる電流によりゲート10Aのゲート電位がスレショルド電圧を超えることがないように、十分小さい等価抵抗のトランジスタ30を用いている。

【0028】

また、スイッチング回路1は、ゲート10Aとトランジスタ30との間にダイオードDsを備えている。これにより、トランジスタ30に供給されるべき電流がゲート10Aに回ってゲート10Aの電位を上昇させるのを防止している。従って、ゲート10Aの電位の立ち上がりはIGBT10のゲート−エミッタ間容量Cm及び抵抗Rgp、Rgに依存することとなり、回路全体の設計を容易にすることができる。

【0029】

更に、スイッチング回路1は、抵抗Rbの抵抗値を、抵抗RgとRgpの抵抗値の和にIGBT10のゲート−エミッタ間容量Cmを乗じた値をトランジスタ30のドレイン−ソース間容量Csで除した値よりも小さい値としている。これにより、トランジスタ30のドレイン電位は、ゲート10Aの電位よりも早く立ち上がることとなる。従って、ゲート10Aの電位が先に立ち上がることによりゲート10Aからトランジスタ30に電流が流れ、ゲート10Aの電位が不安定になる(例えば、振動等を生じる)という不都合が生じるのを回避している。

【0030】

図4は、これらの構成により実現される、IGBT10のゲート電位、及びトランジスタ30のドレイン電位の特性を示す図である。

【0031】

なお、ダイオードDbは、トランジスタ30がオフの状態でスイッチング素子Qpがオフ、Qnがオンとなった場合(通常時のIGBT10オフ動作時)において、ゲート10Aから流れる電流が、抵抗Rg、及びRgnを通って端子MNに至るようにするためのものである。ダイオードDbが存在しない場合、ゲート10AからダイオードDs、抵抗Rb、Rgp、Rgnを順に通って端子MNに至る電力径路が存在するため、ゲート10Aの電位を低下させる際の応答を最適化するための回路全体の設計(実際には抵抗比の決定等)が困難なものとなる。ダイオードDbを備えることにより、抵抗Rg,Rgp、Rgnの比率等を最適に決定するのが容易となるのである。

【0032】

[利用例]

スイッチング回路1は、例えば図5に示す如きインバータ50の一部として用いられる。インバータ50は、3本のアーム51、52、53を有し、各アームにIGBT10が2個取り付けられている。各アームにおけるIGBT10は、一方がオンであれば他方がオフとなるように、図示しない制御装置によって制御される。そして、各アームに取り付けられたIGBT10が、例えば120度の位相ズレをもってオンオフ制御され、モータ60が回転制御される。この際に、IGBT10には上記の如くゲート10Aの電位を所望のタイミングで迅速に低下させるための構成が接続されているため、同一アームのトランジスタが同時にオンするアーム短絡等が発生することが防止される。

【0033】

[まとめ]

以上説明した本実施例のスイッチング回路1によれば、端子MPから端子SoutDに至る電力線に抵抗Rbを設けているため、トランジスタ30のドレイン電位が上昇するのと並行してゲート10Aのゲート電位が上昇する。従って、従来の構成に比して、消費電力を余り上昇させることなく、ゲート電位の立ち上がりの遅延を抑制することができる。

【0034】

また、ゲート10Aとトランジスタ30との間にダイオードDsを備えているため、ゲート10Aの電位の立ち上がりが抵抗Rgp、Rgに依存することとなり、回路全体の設計を容易にすることができる。更に、抵抗Rbの抵抗値を、抵抗RgとRgpの抵抗値の和にIGBT10のゲート−エミッタ間容量を乗じた値をトランジスタ30のドレイン−ソース間容量で除した値よりも小さい値としているため、ゲート10Aの電位が先に立ち上がることによりゲート10Aからトランジスタ30に電流が流れ、ゲート10Aの電位が不安定になるという不都合が生じるのを回避することができる。

【0035】

[変形例]

以上、本発明を実施するための最良の形態について実施例を用いて説明したが、本発明はこうした実施例に何等限定されるものではなく、本発明の要旨を逸脱しない範囲内において種々の変形及び置換を加えることができる。

【0036】

例えば、抵抗Rbの抵抗値を、抵抗RgとRgpの抵抗値の和にIGBT10のゲート−エミッタ間容量を乗じた値をトランジスタ30のドレイン−ソース間容量で除した値よりも小さい値とするものとしたが、より簡易な制約を課してもよい。例えば、IGBT10のゲート−エミッタ間容量Cmが、トランジスタ30のドレイン−ソース間容量Cs以上である装置に適用することを前提とすれば、単に、抵抗Rbの抵抗値を、抵抗RgとRgpの抵抗値の和よりも小さい値とするものとしてもよい。

【0037】

また、図6に示す如く、抵抗RgpとRgnを区別せず、ゲート10Aのオン制御時の電力径路とオフ制御時の電力径路を共用するものとしてもよい。この場合、端子MPとMNを区別する必要はない。

【0038】

また、図7に示す如く、ゲート10Aから端子SoutDに至る電力線の途中にバッファ70を設けてもよい。本図の構成は、出力端子MGから端子SoutDに流れる電流が比較的大きい場合に適用されると好適である。バッファ70は、トランジスタ72と、抵抗Rebと、を備える。トランジスタ72は、トランジスタ30と同様、IGBT10のコレクタ−エミッタ間に流れる主電流が変化する際にゲートに流れ込むと見込まれる電流によりゲート10Aのゲート電位がスレショルド電圧を超えることがないように、十分小さい抵抗を用いている。トランジスタ72は、エミッタ−ベース間に一定以上の電位差が発生するとオン状態となるように動作する。抵抗Rebは、トランジスタ30がオフ状態となったときにトランジスタ72のベース−エミッタ間の電位差を0[V]にするために設けられている。係る構成によれば、出力端子MGから端子SoutDに流れる電流が比較的大きい場合にも対応することができる。

【産業上の利用可能性】

【0039】

本発明は、自動車製造業や自動車部品製造業等に利用可能である。

【図面の簡単な説明】

【0040】

【図1】本発明の一実施例に係るスイッチング回路1の全体構成の一例を示す図である。

【図2】従来の半導体装置の構成を簡略化して示す図である。

【図3】主トランジスタのゲート電位がスレショルド電位以上となるまでの時間が、副トランジスタの容量に依存して、副トランジスタを備えない場合に比して長くなってしまう様子を示す図である。

【図4】本実施例の構成により実現される、IGBT10のゲート電位、及びトランジスタ30のドレイン電位の特性を示す図である。

【図5】スイッチング回路1が好適に適用されるインバータ50の構成例である。

【図6】抵抗RgpとRgnを区別せず、ゲート10Aのオン制御時の電力径路とオフ制御時の電力径路を共用する場合の構成例である。

【図7】ゲート10Aから端子SoutDに至る電力線の途中にバッファ70を設けた場合の構成例である。

【符号の説明】

【0041】

1 スイッチング回路

10 IGBT

10A ゲート

30、72 トランジスタ

50 インバータ

51、52、53 アーム

60 モータ

70 バッファ

Ds、Db ダイオード

Qp、Qn スイッチング素子

Rg、Rgp、Rgn、Rb、Rj、Reb 抵抗

MP、MN、SoutD 端子

MG 出力端子

【特許請求の範囲】

【請求項1】

電圧制御される主トランジスタと、

グランド端子に接続され、前記主トランジスタのゲートスレショルド電圧よりもオン時ドレインーソース間電圧が低い副トランジスタと、

第1の抵抗が設けられ、電源装置に接続される端子と前記主トランジスタのゲートとを接続する第1の電力ラインと、

前記主トランジスタのゲートから前記副トランジスタへ流れる電流を選択的に許容する第2の電力ラインと、

第2の抵抗が設けられ、前記端子と前記副トランジスタとを接続する第3の電力ラインと、を有し、

前記第2の抵抗の抵抗値は、前記主トランジスタの容量と前記第1の抵抗の抵抗値の積を前記副トランジスタの容量で除した値よりも小さい値である、

スイッチング回路。

【請求項2】

電圧制御される主トランジスタと、

グランド端子に接続され、前記主トランジスタのゲートスレショルド電圧よりもオン時ドレインーソース間電圧が低い副トランジスタと、

第1の抵抗が設けられ、電源装置に接続される端子と前記主トランジスタのゲートとを接続する第1の電力ラインと、

前記主トランジスタのゲートから前記副トランジスタへ流れる電流を選択的に許容する第2の電力ラインと、

第2の抵抗が設けられ、前記端子と前記副トランジスタとを接続する第3の電力ラインと、を有し、

前記第2の抵抗の抵抗値は、前記第1の抵抗の抵抗値よりも小さい値である、

スイッチング回路。

【請求項3】

前記第3の電力ラインは、前記端子から前記副トランジスタへ流れる電流を選択的に許容する、

請求項1又は2に記載のスイッチング回路。

【請求項4】

主トランジスタを電圧制御するためのトランジスタの駆動回路であって、

グランド端子に接続された副トランジスタと、

第1の抵抗が設けられ、電源装置に接続される端子と前記主トランジスタのゲートとを接続する第1の電力ラインと、

前記主トランジスタのゲートから前記副トランジスタへ流れる電流を選択的に許容する第2の電力ラインと、

第2の抵抗が設けられ、前記端子と前記副トランジスタとを接続する第3の電力ラインと、

を有するトランジスタの駆動回路。

【請求項1】

電圧制御される主トランジスタと、

グランド端子に接続され、前記主トランジスタのゲートスレショルド電圧よりもオン時ドレインーソース間電圧が低い副トランジスタと、

第1の抵抗が設けられ、電源装置に接続される端子と前記主トランジスタのゲートとを接続する第1の電力ラインと、

前記主トランジスタのゲートから前記副トランジスタへ流れる電流を選択的に許容する第2の電力ラインと、

第2の抵抗が設けられ、前記端子と前記副トランジスタとを接続する第3の電力ラインと、を有し、

前記第2の抵抗の抵抗値は、前記主トランジスタの容量と前記第1の抵抗の抵抗値の積を前記副トランジスタの容量で除した値よりも小さい値である、

スイッチング回路。

【請求項2】

電圧制御される主トランジスタと、

グランド端子に接続され、前記主トランジスタのゲートスレショルド電圧よりもオン時ドレインーソース間電圧が低い副トランジスタと、

第1の抵抗が設けられ、電源装置に接続される端子と前記主トランジスタのゲートとを接続する第1の電力ラインと、

前記主トランジスタのゲートから前記副トランジスタへ流れる電流を選択的に許容する第2の電力ラインと、

第2の抵抗が設けられ、前記端子と前記副トランジスタとを接続する第3の電力ラインと、を有し、

前記第2の抵抗の抵抗値は、前記第1の抵抗の抵抗値よりも小さい値である、

スイッチング回路。

【請求項3】

前記第3の電力ラインは、前記端子から前記副トランジスタへ流れる電流を選択的に許容する、

請求項1又は2に記載のスイッチング回路。

【請求項4】

主トランジスタを電圧制御するためのトランジスタの駆動回路であって、

グランド端子に接続された副トランジスタと、

第1の抵抗が設けられ、電源装置に接続される端子と前記主トランジスタのゲートとを接続する第1の電力ラインと、

前記主トランジスタのゲートから前記副トランジスタへ流れる電流を選択的に許容する第2の電力ラインと、

第2の抵抗が設けられ、前記端子と前記副トランジスタとを接続する第3の電力ラインと、

を有するトランジスタの駆動回路。

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【公開番号】特開2009−290287(P2009−290287A)

【公開日】平成21年12月10日(2009.12.10)

【国際特許分類】

【出願番号】特願2008−137999(P2008−137999)

【出願日】平成20年5月27日(2008.5.27)

【出願人】(000003207)トヨタ自動車株式会社 (59,920)

【Fターム(参考)】

【公開日】平成21年12月10日(2009.12.10)

【国際特許分類】

【出願日】平成20年5月27日(2008.5.27)

【出願人】(000003207)トヨタ自動車株式会社 (59,920)

【Fターム(参考)】

[ Back to top ]