スイッチング回路及び半導体モジュール

【課題】スイッチング制御する制御回路の負担を軽減するスイッチング回路を提供する。

【解決手段】第1のスイッチング素子の制御電極と第1のスイッチング素子をスイッチング制御する制御回路との間に接続される抵抗と、第1のスイッチング素子の制御電極と第1のスイッチング素子の低電位側電極との間に接続される第1のコンデンサと、第1のコンデンサと直列に接続される第2のスイッチング素子とを備え、第2のスイッチング素子の高電位側電極は、第1のスイッチング素子の制御電極に電気的に接続され、第2のスイッチング素子の低電位側電極は第1のスイッチング素子の低電位側電力端子に電気的に接続され、第2のスイッチング素子の制御電極は、抵抗と制御回路の間に接続されている。

【解決手段】第1のスイッチング素子の制御電極と第1のスイッチング素子をスイッチング制御する制御回路との間に接続される抵抗と、第1のスイッチング素子の制御電極と第1のスイッチング素子の低電位側電極との間に接続される第1のコンデンサと、第1のコンデンサと直列に接続される第2のスイッチング素子とを備え、第2のスイッチング素子の高電位側電極は、第1のスイッチング素子の制御電極に電気的に接続され、第2のスイッチング素子の低電位側電極は第1のスイッチング素子の低電位側電力端子に電気的に接続され、第2のスイッチング素子の制御電極は、抵抗と制御回路の間に接続されている。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、スイッチング回路及び半導体モジュールに関するものである。

【背景技術】

【0002】

SiCデバイスを用いたインバータ回路において、主スイッチング素子である接合電界効果トランジスタのゲートとソース間にコンデンサを挿入し、ドレイン−ソース間電圧上昇時におけるゲート-ソース間の電圧上昇変化を抑制し、誤点弧を防止するものが知られている(非特許文献1)。

【先行技術文献】

【非特許文献】

【0003】

【非特許文献1】Robin Kelley, SemiSouth, USA、「Optimized Gate Driver for Enhancement-Mode SiC JFET Used in 480VAV SMPS and 1kV PV-Inverters」PCIM Europe 2009 12-14 May 2009, Nuremberg

【発明の概要】

【発明が解決しようとする課題】

【0004】

しかしながら、主スイッチング素子をスイッチング制御する際に、当該コンデンサを充放電する充放電電流をゲート駆動回路から供給しなければならないため、ゲート駆動回路の負担が大きくなる、という問題があった。

【0005】

本発明が解決しようとする課題は、スイッチング制御する制御回路の負担を軽減するスイッチング回路を提供することである。

【課題を解決するための手段】

【0006】

本発明は、第1のスイッチング素子の制御電極と第1のスイッチング素子の低電位側電極との間に、第2のスイッチング素子とコンデンサとを直列に接続し、第2のスイッチング素子の高電位側電極を第1スイッチング素子の制御電極に、第2のスイッチング素子の低電位側電極を第1スイッチング素子の低電位電極端子に電気的に接続することによって上記課題を解決する。

【発明の効果】

【0007】

本発明によれば、第1のスイッチング素子のスイッチング制御において、スイッチング毎に当該コンデンサを充放電させることなく、第1のスイッチング素子の誤点弧を防ぐことができるため、スイッチング制御する制御回路の負担を軽減することができる。

【図面の簡単な説明】

【0008】

【図1】本発明の実施形態に係るスイッチング回路を含む直流−三相交流変換装置を示すブロック図である。

【図2】図1の上アーム回路及び下アーム回路の回路図である。

【図3】比較例の上アーム回路及び下アーム回路の回路図である。

【図4】比較例の上アーム回路及び下アーム回路における、電圧及び電流の時間特性を示すグラフである。

【図5】図2の上アーム回路及び下アーム回路における、電圧及び電流の時間特性を示すグラフである。

【図6】図2の上アーム回路のうち、ゲート駆動回路及びゲートインピーダンスを省略した回路図である。

【図7】図6のゲート抵抗、スイッチング素子及びコンデンサをモジュール化した半導体モジュールの平面図である。

【図8】本発明の実施形態に係るスイッチング回路である、上アーム回路及び下アーム回路の回路図である。

【図9】図8の上アーム回路のうち、ゲート駆動回路及びゲートインピーダンスを省略した回路図である。

【図10】図9のゲート抵抗、スイッチング素子及びコンデンサをモジュール化した半導体モジュールの平面図である。

【発明を実施するための形態】

【0009】

以下、本発明の実施形態を図面に基づいて説明する。

【0010】

《第1実施形態》

図1は、本発明の実施形態に係るスイッチング回路を含む直流−三相交流変換装置を示すブロック図である。詳細な図示は省略するが、本例のスイッチング回路を含む電力変換器は、交流無停電電源装置や誘導機を回転させる汎用インバータ装置等に適用される。

【0011】

本例のスイッチング回路を含む直流−三相交流変換装置は、三相の交流負荷103と、直流電源101と、当該直流電源101の直流電力を交流電力に変換するインバータ100とを備える。

【0012】

直流電源101は、例えば太陽電池、燃料電池、PFCコンバータ、またはリチウムイオン電池などの二次電池で構成されている。なお、交流負荷103が回生作用する場合、交流負荷103の交流電力が、インバータ100により直流に変換され、直流電源101に入力される。

【0013】

インバータ100は、上アーム回路1041、1043、1045と、下アーム回路1042、1044、1046と、平滑用のコンデンサ102と、コントローラ105とを有し、直流電源101の直流電力を交流電力に変換して、交流負荷103に供給する。上アーム回路1041、1043、1045は、パワーデバイスとしてのスイッチング素子Q1、Q3、Q5とダイオードD1、D3、D5とをそれぞれ並列に接続した回路を主要な構成とし、下アーム回路1042、1044、1046は、同じくパワーデバイスとしてのスイッチング素子Q2、Q4、Q6とダイオードD2、D4、D6とをそれぞれ並列に接続した回路を主要な構成とする。本例では、2つのスイッチング素子Q1〜Q6を直列に接続した3対の回路が、電源線P及び電源線Nとの間に接続されることにより、直流電源101に並列に接続され、各対のスイッチング素子を接続する各接続点と交流負荷103の三相入力部とがそれぞれ電気的に接続されている。スイッチング素子Q1〜Q6には、ワイドギャップ半導体デバイス(SiCデバイス、GaNデバイス、ダイヤモンドデバイス)またはSiデバイスであって、例えば、接合型電界効果トランジスタ(JFET)、MOSFET、又は、絶縁ゲートパイポーラトランジスタ(IGBT)が用いられる。各ダイオードD1〜D6には、例えばFRD(Fast Recovery Diode)、SBD(Schottky Barrier Diode)などが用いられる。

【0014】

図1に示す例でいえば、上アーム回路1041と下アーム回路1042、上アーム回路1043と下アーム回路1044、上アーム回路1045と下アーム回路1046がそれぞれ対になって直列に接続され、上アーム回路1041と下アーム回路1042との接続点と交流負荷103のU相、上アーム回路1043と下アーム回路1044との接続点と交流負荷103のV相、上アーム回路1045と下アーム回路1046との接続点と交流負荷103のW相がそれぞれ接続されている。上アーム回路及び下アーム回路1041〜1046は、コントローラ105により制御され、高周波でスイッチングされる。コントローラ105は、上アーム回路1041及び下アーム回路1042を交互にオン及びオフにして、オン時間比率を増減させて、インバータ100からの出力を制御する。

【0015】

上アーム回路1041はスイッチング素子Q1、ダイオードD1、後述するゲート駆動回路で構成され、スイッチング素子Q1のドレイン電極はダイオードD1のカソード端子に接続され、スイッチング素子Q1のソース電極はダイオードD1のアノード端子に接続されている。スイッチング素子Q1のゲート電極は後述するゲート駆動回路を介してコントローラ105に接続されている。他の上アーム回路及び下アーム回路1042〜1046の各端子も同様にコントローラ105に接続されている。

【0016】

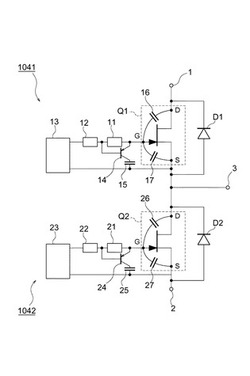

次に、図2を用いて、本例のスイッチング回路に相当する上アーム回路1041と下アーム回路1042の詳細な回路構成を説明する。図2は、図1のインバータ100からU相を抜き出した回路の回路図である。なお、上アーム回路1043と下アーム回路1044の回路構成、及び、上アーム回路1045及び下アーム回路1046の回路構成は、上アーム回路1041と下アーム回路1042の回路構成と同様であるため、説明を省略する。

【0017】

上アーム回路1041は、スイッチング素子Q1と、ダイオードD1と、ゲート抵抗11と、ゲートインピーダンス12と、ゲート駆動回路13と、スイッチング素子14と、コンデンサ15とを備えている。下アーム回路1042は、スイッチング素子Q2と、ダイオードD2と、ゲート抵抗21と、ゲートインピーダンス22と、ゲート駆動回路23と、スイッチング素子24と、コンデンサ25とを備える。スイッチング素子Q1は、ドレイン−ゲート間に帰還容量16と、ゲート−ソース間に入力容量17とを有する。スイッチング素子Q2は、ドレイン−ゲート間に帰還容量26と、ゲート−ソース間に入力容量27とを有する。帰還容量16、26及び入力容量17、27は、スイッチング素子Q1及びスイッチング素子Q2のそれぞれの内部に存在する寄生容量である。

【0018】

陽極端子1は直流電源101の正極側に接続され、陰極端子2は直流電源101の負極側に接続されている。交流端子3は、スイッチング素子Q1のソース電極とスイッチング素子Q2のドレイン電極との接続点から引き出され、交流負荷103のU相に接続されている。

【0019】

スイッチング素子Q1の三端子のうち、高電位側電極であるドレイン電極は陽極端子1に接続され、低電位側電極であるソース電極は交流端子3及びスイッチング素子Q2のドレイン電極に接続され、制御電極であるゲート電極はゲート抵抗11に接続されている。ゲート抵抗11は、スイッチング素子Q1における寄生振動を防止するための抵抗であり、一端をスイッチング素子Q1のゲート電極に接続されている。ゲートインピーダンス12は、ゲート駆動回路13の内部インピーダンス及び配線のインピーダンスに相当し、インダクタンスを主成分とするインピーダンスである。ゲートインピーダンス12は、一端をゲート抵抗11の他端に、他端をゲート駆動回路13に接続されている。

【0020】

ゲート駆動回路13は、コントローラ105からの制御信号に基づき、ゲート電圧をゲート電極に入力し、スイッチング素子Q1をスイッチング制御する駆動回路である。ゲート駆動回路13は、ゲートインピーダンス12及び交流端子3に接続されている。

【0021】

スイッチング素子14は、PNPトランジスタであり、エミッタ電極をスイッチング素子Q1のゲート電極とゲート抵抗11の一端との間に接続され、コレクタ電極をコンデンサ15の一端に接続され、ベース電極をゲート抵抗11の他端とゲートインピーダンス12の一端との間に接続されている。コンデンサ15は、一端をスイッチング素子14のコレクタ電極に接続され、他端をスイッチング素子Q1のソース電極に接続されている。すなわち、スイッチング素子14及びコンデンサ15は直列に接続され、スイッチング素子14とコンデンサ15との直列回路が、スイッチング素子のゲート−ソース間に電気的に接続されている。

【0022】

スイッチング素子Q2の三端子のうち、高電位側電極であるドレイン電極はスイッチング素子Q1のソース電極及び交流端子に接続され、低電位側電極であるソース電極は陰極電極2に接続され、制御電極であるゲート電極はゲート抵抗21に接続されている。ゲート抵抗21は、スイッチング素子Q2における寄生振動を防止するための抵抗であり、一端をスイッチング素子Q2のゲート電極に接続されている。ゲートインピーダンス22は、ゲート駆動回路23の内部インピーダンス及び配線のインピーダンスに相当し、インダクタンスを主成分とするインピーダンスである。ゲートインピーダンス22は、一端をゲート抵抗21の他端に、他端をゲート駆動回路に接続されている。

【0023】

ゲート駆動回路23は、コントローラ105からの制御信号に基づき、ゲート電圧をゲート電極に入力し、スイッチング素子Q2をスイッチング制御する駆動回路である。ゲート駆動回路23は、ゲートインピーダンス22及び陰極端子2に接続されている。

【0024】

スイッチング素子24は、PNPトランジスタであり、エミッタ電極をスイッチング素子Q2のゲート電極とゲート抵抗21の一端との間に接続され、コレクタ電極をコンデンサ25の一端に接続され、ベース電極をゲート抵抗21の他端とゲートインピーダンス22の一端との間に接続されている。コンデンサ25は、一端をスイッチング素子24のコレクタ電極に接続され、他端をスイッチング素子Q2のソース電極に接続されている。すなわち、スイッチング素子24及びコンデンサ25は直列に接続され、スイッチング素子24とコンデンサ25との直列回路が、スイッチング素子のゲート−ソース間に接続されている。

【0025】

ゲート駆動回路13、23は、図1のコントローラ105からの制御信号がON指令のときに陽極電圧、OFF指令のときに陰極電圧を出力する。

【0026】

スイッチング素子Q1、Q2は、ゲート−ソース間の電圧が閾値電圧以上になるとオンの状態になり、ドレイン−ソース間が通電され、ゲート−ソース間の電圧が当該閾値電圧未満であればオフの状態で、ドレイン−ソース間は遮断される。閾値電圧は、スイッチング素子Q1、Q2のオン及びオフを切り替える、デバイスの固有の電圧であり、ゲート駆動回路13、23からは、ON指令のとき閾値電圧よりも十分高い陽極電圧、OFF指令のとき閾値電圧よりも十分低い陰極電圧が供給される。すなわち、スイッチング素子Q1、Q2のゲート−ソース間が、閾値電圧よりも高い電圧から低い電圧に切り替わると、スイッチング素子Q1、Q2はオンからオフに反転(ターンオフ)する。

【0027】

ここで、スイッチング素子Q1〜Q6における誤点弧について、図3及び図4を用いて説明する。図3は比較例のスイッチング回路の回路図を示し、図4は比較例のスイッチング回路における、ゲート駆動回路13の出力電圧、ゲート駆動回路23の出力電圧、スイッチング素子Q1のゲート−ソース間の電圧、スイッチング素子Q2のゲート−ソース間の電圧、スイッチング素子Q1のドレイン−ソース間の電圧、スイッチング素子Q1のドレイン電流、スイッチング素子Q2のドレイン−ソース間の電圧、及び、スイッチング素子Q2のドレイン電流のタイムチャートを示している。なお、交流端子3に出力される負荷電流は正(交流端子から電流が出力される方向)とする。

【0028】

図3に示すように、比較例に係るスイッチング回路では、本例のようなスイッチング素子14及びコンデンサ15の直列回路が、スイッチング素子Q1、Q2のゲート−ソース間に接続されていない。図4に示すように、ゲート駆動回路13は時間T1から時間T2までをオン期間とする陽極パルスを出力し、ゲート駆動回路23は時間T3までと時間T4以降をオン期間とする陽極パルスを出力する。時間T1で陽極パルスがゲート駆動回路13から出力されると、入力容量17の充電に伴って、スイッチング素子Q1のゲート−ソース間の電圧は徐々に上昇する。このとき、ゲート駆動回路23の出力およびスイッチング素子Q2のゲート−ソース間電圧は陰極になっている。

【0029】

スイッチング素子Q1のゲート−ソース間の電圧は、時間Taの時点で閾値電圧に達するため、スイッチング素子Q1がオフからオン(ターンオン)になり、スイッチング素子Q1のドレイン電流が流れ始め、スイッチング素子Q1のドレイン−ソース間電圧は下がる。またスイッチング素子Q1のドレイン−ソース間の電圧下降に伴い、スイッチング素子Q2のドレイン−ソース間電圧が上昇する。

【0030】

時間Taの時点で、スイッチング素子Q2のドレイン−ソース間の電圧上昇(dv/dt)による電流は、帰還容量26及び入力容量27を接続する経路に流れ出す。そのため、スイッチング素子Q2のゲート−ソース間の電圧が上昇する。このスイッチング素子Q2のゲート−ソース間の上昇電圧は、スイッチング素子Q2のドレイン−ソース間の電圧の上昇速度(dv/dt)が大きいほど高くなり、帰還容量26の容量を入力容量27の容量で除した値(帰還容量26の容量/入力容量27の容量)が大きいほど、高くなる。そして時間Tbの時点で、スイッチング素子Q2のゲート−ソース間の電圧が閾値電圧より高くなり、スイッチング素子Q2が誤ってターンオンされる。この時、スイッチング素子Q1はオンであるため、陽極端子1と陰極端子2との間が短絡し、スイッチング素子Q1及びスイッチング素子Q2に過大な電気的ストレスが加わる。特に、スイッチング素子Q1〜Q6に、SiCデバイスを用いた場合には、他の半導体デバイス(Siデバイスなど)を用いた場合と比較して、動作が高速であり電圧の上昇速度(dv/dt)が大きく、また帰還容量16、26の容量も大きい。そのため、上記のような誤点弧が起こりやすい。

【0031】

誤点弧を防ぐための回路構成として、スイッチング素子Q1〜Q6のゲート−ソース間にコンデンサを追加接続することで、見かけ上のゲート−ソース間の容量(入力容量)を増やす回路構成が知られている。帰還容量26の容量を入力容量27の容量で除した値(帰還容量26の容量/入力容量27の容量)が小さくなり、誤点弧が生じにくくなる。しかし、当該回路構成では、スイッチング毎に追加されたコンデンサを充放電する必要があるため、ゲート駆動回路13、23の負担が増加する、という課題がある。また、コンデンサを追加することで、スイッチング制御時のゲート信号の波形の変化が鈍くなり、スイッチング素子Q1〜Q6のスイッチング速度が遅くなるため、スイッチング動作の時間遅れが大きくなったり、スイッチング損失が増加したりする、という課題もある。

【0032】

また、誤点弧を防ぐための他の回路構成として、スイッチング素子Q1〜Q6のゲート−ソース間に、PNPトランジスタのみを接続し、スイッチング素子Q1〜Q6のゲート−ソース間の電圧が上昇した時に、当該PNPトランジスタをオンにすることで、ゲート−ソース間の電圧をゼロ相当にして、スイッチング素子Q1〜Q6の誤点弧を防ぐ回路構成が知られている(特開2003−324966号公報を参照)。しかし、当該回路構成において、スイッチング素子Q1〜Q6に、閾値電圧が低いまたは負電圧である半導体デバイスを用いた場合には、PNPトランジスタがオンであっても、PNPトランジスタの電圧降下分だけゲート−ソース間電圧が上昇し、スイッチング素子Q1〜Q6が誤ってターンオンしてしまう。すなわち、当該回路構成は、閾値電圧が低い、または負電圧とするワイドギャップ半導体のスイッチング回路には適用することができない。

【0033】

本例は、上記のように、スイッチング素子Q1〜Q6のゲート−ソース間に、PNPトランジスタであるスイッチング素子14、24とコンデンサ15、25との直列回路を接続し、スイッチング素子14、24のベース電極を、ゲート抵抗11、21とゲート駆動回路13、23との間に接続している。これにより、スイッチング素子Q1のターンオンに伴い、スイッチング素子Q2のゲート−ソース間の電圧が上昇した場合、スイッチング素子24がオンになり、コンデンサ25がスイッチング素子Q2のゲート−ソース間に接続される。コンデンサ25の充電電圧により、スイッチング素子Q2のゲート−ソース間の電圧上昇を抑えつつ、スイッチング素子Q2のゲート−ソース間に負バイアスをかけることができるため、スイッチング素子Q2が誤ってターンオンすることを防ぐことができる。

【0034】

次に、図5を用いて、本例のスイッチング回路の動作を説明する。図5は本例のスイッチング回路における、ゲート駆動回路13の出力電圧、ゲート駆動回路23の出力電圧、スイッチング素子Q1のゲート−ソース間の電圧、スイッチング素子Q2のゲート−ソース間の電圧、スイッチング素子Q1のドレイン−ソース間の電圧、上アーム回路1041の電流、スイッチング素子Q2のドレイン−ソース間の電圧、及び、下アーム回路1042の電流のタイムチャートを示し、図4のタイムチャートと対応している。ゲート駆動回路13、23から出力される陽極パルスのタイミングは、図4に示すタイミングと同じため、説明を省略する。

【0035】

時間T1でゲート駆動回路13より陽極パルスが出力されると、スイッチング素子Q1のゲート−ソース間の電圧は上昇する。時間Taの時点で、スイッチング素子Q1のゲート−ソース間の電圧は閾値電圧に達し、スイッチング素子Q1はターンオンする。このとき、スイッチング素子Q1のドレイン電流が流れ始め、スイッチング素子Q1のドレイン−ソース間電圧は下がる。スイッチング素子Q1のドレイン−ソース間の電圧下降に伴い、スイッチング素子Q2のドレイン−ソース間電圧が上昇する。このとき、ゲート駆動回路23からは、負バイアスの電圧が出力されている。

【0036】

時間Ta以降、スイッチング素子Q2のドレイン−ソース間の電圧上昇(dv/dt)による電流は、帰還容量26及び入力容量27を接続する経路に流れ出し、これによりスイッチング素子Q2のゲート−ソース間電圧が上昇する。また本例では、スイッチング素子Q2のゲート電極から、スイッチング素子24のエミッタ電極及びベース電極を介して、ゲートインピーダンス22までの経路が形成されており、Q2のゲート−ソース間電圧上昇による電流が当該経路に流れ、スイッチング素子24がオンになる。スイッチング素子24がオンになると、スイッチング素子Q2のゲート−ソース間には、コンデンサ25が並列に接続されることになる。そのため、スイッチング素子Q2のゲート−ソース間の電圧上昇は抑制され、時間Tbの時点でピークになるスイッチング素子Q2のゲート−ソース間の電圧は閾値電圧より低く維持され、スイッチング素子Q2の誤点弧を防ぐことができる。一連の動作において、コンデンサ25の端子電圧変化は小さいため、コンデンサ25の電流がゲート駆動回路23の負担になることはほとんどない。

【0037】

次に、図6及び図7を用いて、本例のスイッチング回路を組み込んだ半導体モジュール200を説明する。図6は上アーム回路1041から、ゲート駆動回路13及びゲートインピーダンス12を除いた回路図であり、図7は半導体モジュール200の平面図である。なお、他の上アーム回路1043、1045及び下アーム回路1042、1044、1046に含まれる素子も、同様にモジュール化されているが、上アーム回路1041のモジュール化と同様であるため、説明を省略する。

【0038】

本例の半導体モジュール200は、ゲート抵抗11、スイッチング素子14及びコンデンサ15をモジュール化したものである。スイッチング素子Q1及びダイオードD1は、基板(図示しない)上に形成された、電極Aを含む配線上に実装されている。また、スイッチング素子Q1及びダイオードD1は、電極Bを含む配線と電気的に接続されている。半導体モジュール200において、ゲート抵抗11、スイッチング素子14及びコンデンサ15は、電極C及び電極Dをそれぞれ含む配線上に実装され、また各素子間を接続する配線に実装されることで、モジュール化されている。また、半導体モジュール200と、スイッチング素子Q1のゲート電極及びソース電極が、接続されている。これにより、本例のスイッチング回路を有さないインバータに接続する際には、インバータ回路基板に、本例の半導体モジュール200を実装し、回路を構成する素子と接続すれば、本例のスイッチング回路を含むインバータを実現することができる。

【0039】

上記のように、本例は、スイッチング素子Q1〜Q6のゲート電極とソース電極との間に、コンデンサ15、25とスイッチング素子14、24とを直列にして接続し、スイッチング素子14、25のエミッタ電極をスイッチング素子Q1〜Q6のゲート電極に、スイッチング素子14、24のコレクタ電極をスイッチング素子Q1〜Q6のソース電極に、スイッチング素子14、24のベース電極をゲート抵抗11、21とゲート駆動回路13、23との間に、それぞれ電気的に接続する。これにより、一方のスイッチング素子Q1〜Q6のターンオンに伴う、他方のスイッチング素子Q1〜Q6のゲート−ソース間の電圧上昇において、ゲート電極からの電流が、スイッチング素子14、24のエミッタ−ベース間を通り、ゲート駆動回路13、23に流れる。そして、スイッチング素子14、24がオンになり、コンデンサ15、25と導通させることで、入力容量が大きくなるため、スイッチング素子Q1〜Q6のゲート−ソース間の電圧上昇を抑制し、スイッチング素子Q1〜Q6の誤点弧を防ぐことができる。

【0040】

また本例において、コンデンサ15、25は、スイッチング素子Q1〜Q6のゲート−ソース間にバイアス電圧をかけることで誤点弧を防ぐように接続されているため、ゲート駆動回路13、23によるスイッチング制御毎に、コンデンサ15、25を放電させる必要がない。そのため、本例は、スイッチング制御毎に、コンデンサ15、25を充放電しなくてもよいため、ゲート駆動回路13、23の負担を軽減し、ゲート駆動回路13、23の出力波形も鈍らず、スイッチング動作の遅れが発生することを防ぎ、スイッチング速度の低下を防ぐことができる。

【0041】

また本例は、スイッチング素子Q1〜Q6に、ゲート−ソース間の閾値電圧を負電圧とするワイドギャップ半導体デバイスを用いた場合において、一方のスイッチング素子Q1〜Q6のターンオンに伴い、他方のスイッチング素子Q1〜Q6のゲート−ソース間の電圧が上昇し、スイッチング素子14、24がオンになる。かかる場合に、本例は、コンデンサ15、25をスイッチング素子14、25に直列に接続しているため、コンデンサ15、25により負側へバイアス電圧が加わり、スイッチング素子Q1〜Q6のゲート−ソース間の電圧を、閾値電圧未満に維持することができる。これにより、ゲート−ソース間の閾値電圧が低い、または閾値電圧を負電圧とするワイドギャップ半導体デバイスを用いた場合でも、スイッチング素子Q1〜Q6の誤点弧を防ぐことができる。

【0042】

また本例は、スイッチング回路を半導体モジュール200に組み込むことでモジュール化されている。これにより、追加部品を設けることなく、本例のスイッチング回路を、従来の電力変換器へ実装することができる。

【0043】

なお本例は、スイッチング素子Q1〜Q6にバイポーラトランジスタを用いて、コレクタ電極を高電位側電極に、エミッタ電極を低電位側電極に、ベース電極を制御電極になるよう接続してもよい。また、スイッチング素子14、24に、Pチャネル電界効果トランジスタを用いて、ソース電極を高電位側電極に、ドレイン電極を低電位側電極に、ゲート電極を制御電極になるよう接続してもよい。

【0044】

言い換えると、本例は、スイッチング素子Q1〜Q6のゲート電極又はベース電極と当該スイッチング素子Q1〜Q6を制御する駆動回路との間に接続される抵抗と、当該スイッチング素子Q1〜Q6のゲート電極又はベース電極と当該スイッチング素子Q1〜Q6のソース電極又はエミッタ電極との間に接続されるコンデンサ15、25と、コンデンサ15、25に直列に接続されるスイッチング素子14、24とを備え、スイッチング素子14、24のエミッタ端子又はソース端子はスイッチング素子Q1〜Q6のゲート電極又はベース電極に電気的に接続され、スイッチング素子14、24のコレクタ端子又はドレイン端子はスイッチング素子Q1〜Q6のソース電極又はエミッタ電極に電気的に接続され、スイッチング素子14、24のベース電極又はゲート電極は、当該抵抗と当該制御回路の間に接続され、スイッチング素子14、24は、PNPトランジスタ又はPチャネル電界効果トランジスタとしてもよい。

【0045】

また本例は、スイッチング素子14、24のベース電極を、ゲート抵抗11、21の他端とゲートインピーダンス12、22の一端との間に接続したが、ゲートインピーダンス12、22の他端とゲート駆動回路13、23との間に接続してもよく、ゲート抵抗11、21の他端とゲート駆動回路13、23との間に接続すればよい。

【0046】

また、本例は、コンデンサ15、25をスイッチング素子14、24のコレクタ電極に接続するが、コンデンサ15、25の一端をスイッチング素子14、24のエミッタ端子に接続し、コンデンサ15、25の他端をスイッチング素子Q1〜Q6のゲート端子に接続してもよい。

【0047】

また本例において、半導体モジュール200に含まれるゲート抵抗11、21、スイッチング素子14、24及びコンデンサ15、25の全ての回路素子、又は、一部の回路素子をICとして集積化してもよく、あるいは、スイッチング素子Q1〜Q6の中に組み込んでもよい。

【0048】

上記スイッチング素子Q1〜Q6が本発明の「第1のスイッチング素子」に相当し、スイッチング素子14、24が「第2のスイッチング素子」に、コンデンサ15、25が「第1のコンデンサ」に、ゲート駆動回路13、23が「制御回路」に相当し、ゲート抵抗11が「抵抗」に相当する。

【0049】

《第2実施形態》

図8は、発明の他の実施形態に係るスイッチング回路を含むインバータからU相を抜き出した回路の回路図である。本例では上述した第1実施形態に対して、コンデンサ18及びコンデンサ28を接続する点が異なる。これ以外の構成は上述した第1実施形態と同じであるため、その記載を援用する。

【0050】

本例のスイッチング回路は、スイッチング素子14のベース−コレクタ間にコンデンサ18を接続し、スイッチング素子24のベース−コレクタ間にコンデンサ28を接続している。コンデンサ18の容量はコンデンサ15の容量より小さく、コンデンサ28の容量はコンデンサ25の容量より小さい。

【0051】

スイッチング素子Q1がオンになり、スイッチング素子Q2のゲート−ソース間の電圧が上昇すると、ゲート電極からの電流が、スイッチング素子24のエミッタ−ベース間を通り、コンデンサ28に流れる。そして、スイッチング素子24がオンになり、スイッチング素子Q2のゲート−ソース間で、スイッチング素子24とコンデンサ25との直列回路が通電し、スイッチング素子Q2のゲート−ソース間の電圧上昇が抑制される。本例では、スイッチング素子24のベース電流を、ゲートインピーダンス22ではなく、コンデンサ28に流すため、ベース電流に対するゲートインピーダンス22からの影響を受けにくくすることができる。

【0052】

次に、図9及び図10を用いて、本例のスイッチング回路を組み込んだ半導体モジュール200を説明する。図9は上アーム回路1041から、ゲート駆動回路13及びゲートインピーダンス12を除いた回路図であり、図10は半導体モジュールの平面図である。なお、他の上アーム回路1043、1045及び下アーム回路1042、1044、1046に含まれる素子も、同様にモジュール化されているが、上アーム回路1041のモジュール化と同様であるため、説明を省略する。

【0053】

本例の半導体モジュール200は、ゲート抵抗11、スイッチング素子14、コンデンサ15及びコンデンサ18をモジュール化したものである。半導体モジュール200において、ゲート抵抗11、スイッチング素子14、コンデンサ15及びコンデンサ18は、電極C及び電極Dをそれぞれ含む配線上に実装され、また各素子間を接続する配線に実装されることで、モジュール化されている。これにより、本例のスイッチング回路を有さないインバータに接続する際には、インバータ回路基板に、本例の半導体モジュール200を実装し、回路を構成する素子と接続すれば、本例のスイッチング回路を含むインバータを実現することができる。

【0054】

上記のように、本例は、スイッチング素子14、24のベース電極とコレクタ電極との間に、コンデンサ15、25の容量より小さい容量であるコンデンサ18、28を接続する。これにより、スイッチング素子14、24のベース電流が、ゲートインピーダンス12、22により影響を受けることを防ぐことができる。

【0055】

上記コンデンサ18、28が「第2のコンデンサ」に相当する。

【符号の説明】

【0056】

100…インバータ

101…直流電源

102…コンデンサ

103…交流負荷

1041、1043、1045…上アーム回路

1042、1044、1046…下アーム回路

105…コントローラ

Q1〜Q6…スイッチング素子

D1〜D6…ダイオード

11、21…ゲート抵抗

12、22…ゲートインピーダンス

13、23…ゲート駆動回路

14、24…スイッチング素子

15、18、25、28…コンデンサ

1…陽極端子

2…陰極端子

3…交流端子

200…半導体モジュール

【技術分野】

【0001】

本発明は、スイッチング回路及び半導体モジュールに関するものである。

【背景技術】

【0002】

SiCデバイスを用いたインバータ回路において、主スイッチング素子である接合電界効果トランジスタのゲートとソース間にコンデンサを挿入し、ドレイン−ソース間電圧上昇時におけるゲート-ソース間の電圧上昇変化を抑制し、誤点弧を防止するものが知られている(非特許文献1)。

【先行技術文献】

【非特許文献】

【0003】

【非特許文献1】Robin Kelley, SemiSouth, USA、「Optimized Gate Driver for Enhancement-Mode SiC JFET Used in 480VAV SMPS and 1kV PV-Inverters」PCIM Europe 2009 12-14 May 2009, Nuremberg

【発明の概要】

【発明が解決しようとする課題】

【0004】

しかしながら、主スイッチング素子をスイッチング制御する際に、当該コンデンサを充放電する充放電電流をゲート駆動回路から供給しなければならないため、ゲート駆動回路の負担が大きくなる、という問題があった。

【0005】

本発明が解決しようとする課題は、スイッチング制御する制御回路の負担を軽減するスイッチング回路を提供することである。

【課題を解決するための手段】

【0006】

本発明は、第1のスイッチング素子の制御電極と第1のスイッチング素子の低電位側電極との間に、第2のスイッチング素子とコンデンサとを直列に接続し、第2のスイッチング素子の高電位側電極を第1スイッチング素子の制御電極に、第2のスイッチング素子の低電位側電極を第1スイッチング素子の低電位電極端子に電気的に接続することによって上記課題を解決する。

【発明の効果】

【0007】

本発明によれば、第1のスイッチング素子のスイッチング制御において、スイッチング毎に当該コンデンサを充放電させることなく、第1のスイッチング素子の誤点弧を防ぐことができるため、スイッチング制御する制御回路の負担を軽減することができる。

【図面の簡単な説明】

【0008】

【図1】本発明の実施形態に係るスイッチング回路を含む直流−三相交流変換装置を示すブロック図である。

【図2】図1の上アーム回路及び下アーム回路の回路図である。

【図3】比較例の上アーム回路及び下アーム回路の回路図である。

【図4】比較例の上アーム回路及び下アーム回路における、電圧及び電流の時間特性を示すグラフである。

【図5】図2の上アーム回路及び下アーム回路における、電圧及び電流の時間特性を示すグラフである。

【図6】図2の上アーム回路のうち、ゲート駆動回路及びゲートインピーダンスを省略した回路図である。

【図7】図6のゲート抵抗、スイッチング素子及びコンデンサをモジュール化した半導体モジュールの平面図である。

【図8】本発明の実施形態に係るスイッチング回路である、上アーム回路及び下アーム回路の回路図である。

【図9】図8の上アーム回路のうち、ゲート駆動回路及びゲートインピーダンスを省略した回路図である。

【図10】図9のゲート抵抗、スイッチング素子及びコンデンサをモジュール化した半導体モジュールの平面図である。

【発明を実施するための形態】

【0009】

以下、本発明の実施形態を図面に基づいて説明する。

【0010】

《第1実施形態》

図1は、本発明の実施形態に係るスイッチング回路を含む直流−三相交流変換装置を示すブロック図である。詳細な図示は省略するが、本例のスイッチング回路を含む電力変換器は、交流無停電電源装置や誘導機を回転させる汎用インバータ装置等に適用される。

【0011】

本例のスイッチング回路を含む直流−三相交流変換装置は、三相の交流負荷103と、直流電源101と、当該直流電源101の直流電力を交流電力に変換するインバータ100とを備える。

【0012】

直流電源101は、例えば太陽電池、燃料電池、PFCコンバータ、またはリチウムイオン電池などの二次電池で構成されている。なお、交流負荷103が回生作用する場合、交流負荷103の交流電力が、インバータ100により直流に変換され、直流電源101に入力される。

【0013】

インバータ100は、上アーム回路1041、1043、1045と、下アーム回路1042、1044、1046と、平滑用のコンデンサ102と、コントローラ105とを有し、直流電源101の直流電力を交流電力に変換して、交流負荷103に供給する。上アーム回路1041、1043、1045は、パワーデバイスとしてのスイッチング素子Q1、Q3、Q5とダイオードD1、D3、D5とをそれぞれ並列に接続した回路を主要な構成とし、下アーム回路1042、1044、1046は、同じくパワーデバイスとしてのスイッチング素子Q2、Q4、Q6とダイオードD2、D4、D6とをそれぞれ並列に接続した回路を主要な構成とする。本例では、2つのスイッチング素子Q1〜Q6を直列に接続した3対の回路が、電源線P及び電源線Nとの間に接続されることにより、直流電源101に並列に接続され、各対のスイッチング素子を接続する各接続点と交流負荷103の三相入力部とがそれぞれ電気的に接続されている。スイッチング素子Q1〜Q6には、ワイドギャップ半導体デバイス(SiCデバイス、GaNデバイス、ダイヤモンドデバイス)またはSiデバイスであって、例えば、接合型電界効果トランジスタ(JFET)、MOSFET、又は、絶縁ゲートパイポーラトランジスタ(IGBT)が用いられる。各ダイオードD1〜D6には、例えばFRD(Fast Recovery Diode)、SBD(Schottky Barrier Diode)などが用いられる。

【0014】

図1に示す例でいえば、上アーム回路1041と下アーム回路1042、上アーム回路1043と下アーム回路1044、上アーム回路1045と下アーム回路1046がそれぞれ対になって直列に接続され、上アーム回路1041と下アーム回路1042との接続点と交流負荷103のU相、上アーム回路1043と下アーム回路1044との接続点と交流負荷103のV相、上アーム回路1045と下アーム回路1046との接続点と交流負荷103のW相がそれぞれ接続されている。上アーム回路及び下アーム回路1041〜1046は、コントローラ105により制御され、高周波でスイッチングされる。コントローラ105は、上アーム回路1041及び下アーム回路1042を交互にオン及びオフにして、オン時間比率を増減させて、インバータ100からの出力を制御する。

【0015】

上アーム回路1041はスイッチング素子Q1、ダイオードD1、後述するゲート駆動回路で構成され、スイッチング素子Q1のドレイン電極はダイオードD1のカソード端子に接続され、スイッチング素子Q1のソース電極はダイオードD1のアノード端子に接続されている。スイッチング素子Q1のゲート電極は後述するゲート駆動回路を介してコントローラ105に接続されている。他の上アーム回路及び下アーム回路1042〜1046の各端子も同様にコントローラ105に接続されている。

【0016】

次に、図2を用いて、本例のスイッチング回路に相当する上アーム回路1041と下アーム回路1042の詳細な回路構成を説明する。図2は、図1のインバータ100からU相を抜き出した回路の回路図である。なお、上アーム回路1043と下アーム回路1044の回路構成、及び、上アーム回路1045及び下アーム回路1046の回路構成は、上アーム回路1041と下アーム回路1042の回路構成と同様であるため、説明を省略する。

【0017】

上アーム回路1041は、スイッチング素子Q1と、ダイオードD1と、ゲート抵抗11と、ゲートインピーダンス12と、ゲート駆動回路13と、スイッチング素子14と、コンデンサ15とを備えている。下アーム回路1042は、スイッチング素子Q2と、ダイオードD2と、ゲート抵抗21と、ゲートインピーダンス22と、ゲート駆動回路23と、スイッチング素子24と、コンデンサ25とを備える。スイッチング素子Q1は、ドレイン−ゲート間に帰還容量16と、ゲート−ソース間に入力容量17とを有する。スイッチング素子Q2は、ドレイン−ゲート間に帰還容量26と、ゲート−ソース間に入力容量27とを有する。帰還容量16、26及び入力容量17、27は、スイッチング素子Q1及びスイッチング素子Q2のそれぞれの内部に存在する寄生容量である。

【0018】

陽極端子1は直流電源101の正極側に接続され、陰極端子2は直流電源101の負極側に接続されている。交流端子3は、スイッチング素子Q1のソース電極とスイッチング素子Q2のドレイン電極との接続点から引き出され、交流負荷103のU相に接続されている。

【0019】

スイッチング素子Q1の三端子のうち、高電位側電極であるドレイン電極は陽極端子1に接続され、低電位側電極であるソース電極は交流端子3及びスイッチング素子Q2のドレイン電極に接続され、制御電極であるゲート電極はゲート抵抗11に接続されている。ゲート抵抗11は、スイッチング素子Q1における寄生振動を防止するための抵抗であり、一端をスイッチング素子Q1のゲート電極に接続されている。ゲートインピーダンス12は、ゲート駆動回路13の内部インピーダンス及び配線のインピーダンスに相当し、インダクタンスを主成分とするインピーダンスである。ゲートインピーダンス12は、一端をゲート抵抗11の他端に、他端をゲート駆動回路13に接続されている。

【0020】

ゲート駆動回路13は、コントローラ105からの制御信号に基づき、ゲート電圧をゲート電極に入力し、スイッチング素子Q1をスイッチング制御する駆動回路である。ゲート駆動回路13は、ゲートインピーダンス12及び交流端子3に接続されている。

【0021】

スイッチング素子14は、PNPトランジスタであり、エミッタ電極をスイッチング素子Q1のゲート電極とゲート抵抗11の一端との間に接続され、コレクタ電極をコンデンサ15の一端に接続され、ベース電極をゲート抵抗11の他端とゲートインピーダンス12の一端との間に接続されている。コンデンサ15は、一端をスイッチング素子14のコレクタ電極に接続され、他端をスイッチング素子Q1のソース電極に接続されている。すなわち、スイッチング素子14及びコンデンサ15は直列に接続され、スイッチング素子14とコンデンサ15との直列回路が、スイッチング素子のゲート−ソース間に電気的に接続されている。

【0022】

スイッチング素子Q2の三端子のうち、高電位側電極であるドレイン電極はスイッチング素子Q1のソース電極及び交流端子に接続され、低電位側電極であるソース電極は陰極電極2に接続され、制御電極であるゲート電極はゲート抵抗21に接続されている。ゲート抵抗21は、スイッチング素子Q2における寄生振動を防止するための抵抗であり、一端をスイッチング素子Q2のゲート電極に接続されている。ゲートインピーダンス22は、ゲート駆動回路23の内部インピーダンス及び配線のインピーダンスに相当し、インダクタンスを主成分とするインピーダンスである。ゲートインピーダンス22は、一端をゲート抵抗21の他端に、他端をゲート駆動回路に接続されている。

【0023】

ゲート駆動回路23は、コントローラ105からの制御信号に基づき、ゲート電圧をゲート電極に入力し、スイッチング素子Q2をスイッチング制御する駆動回路である。ゲート駆動回路23は、ゲートインピーダンス22及び陰極端子2に接続されている。

【0024】

スイッチング素子24は、PNPトランジスタであり、エミッタ電極をスイッチング素子Q2のゲート電極とゲート抵抗21の一端との間に接続され、コレクタ電極をコンデンサ25の一端に接続され、ベース電極をゲート抵抗21の他端とゲートインピーダンス22の一端との間に接続されている。コンデンサ25は、一端をスイッチング素子24のコレクタ電極に接続され、他端をスイッチング素子Q2のソース電極に接続されている。すなわち、スイッチング素子24及びコンデンサ25は直列に接続され、スイッチング素子24とコンデンサ25との直列回路が、スイッチング素子のゲート−ソース間に接続されている。

【0025】

ゲート駆動回路13、23は、図1のコントローラ105からの制御信号がON指令のときに陽極電圧、OFF指令のときに陰極電圧を出力する。

【0026】

スイッチング素子Q1、Q2は、ゲート−ソース間の電圧が閾値電圧以上になるとオンの状態になり、ドレイン−ソース間が通電され、ゲート−ソース間の電圧が当該閾値電圧未満であればオフの状態で、ドレイン−ソース間は遮断される。閾値電圧は、スイッチング素子Q1、Q2のオン及びオフを切り替える、デバイスの固有の電圧であり、ゲート駆動回路13、23からは、ON指令のとき閾値電圧よりも十分高い陽極電圧、OFF指令のとき閾値電圧よりも十分低い陰極電圧が供給される。すなわち、スイッチング素子Q1、Q2のゲート−ソース間が、閾値電圧よりも高い電圧から低い電圧に切り替わると、スイッチング素子Q1、Q2はオンからオフに反転(ターンオフ)する。

【0027】

ここで、スイッチング素子Q1〜Q6における誤点弧について、図3及び図4を用いて説明する。図3は比較例のスイッチング回路の回路図を示し、図4は比較例のスイッチング回路における、ゲート駆動回路13の出力電圧、ゲート駆動回路23の出力電圧、スイッチング素子Q1のゲート−ソース間の電圧、スイッチング素子Q2のゲート−ソース間の電圧、スイッチング素子Q1のドレイン−ソース間の電圧、スイッチング素子Q1のドレイン電流、スイッチング素子Q2のドレイン−ソース間の電圧、及び、スイッチング素子Q2のドレイン電流のタイムチャートを示している。なお、交流端子3に出力される負荷電流は正(交流端子から電流が出力される方向)とする。

【0028】

図3に示すように、比較例に係るスイッチング回路では、本例のようなスイッチング素子14及びコンデンサ15の直列回路が、スイッチング素子Q1、Q2のゲート−ソース間に接続されていない。図4に示すように、ゲート駆動回路13は時間T1から時間T2までをオン期間とする陽極パルスを出力し、ゲート駆動回路23は時間T3までと時間T4以降をオン期間とする陽極パルスを出力する。時間T1で陽極パルスがゲート駆動回路13から出力されると、入力容量17の充電に伴って、スイッチング素子Q1のゲート−ソース間の電圧は徐々に上昇する。このとき、ゲート駆動回路23の出力およびスイッチング素子Q2のゲート−ソース間電圧は陰極になっている。

【0029】

スイッチング素子Q1のゲート−ソース間の電圧は、時間Taの時点で閾値電圧に達するため、スイッチング素子Q1がオフからオン(ターンオン)になり、スイッチング素子Q1のドレイン電流が流れ始め、スイッチング素子Q1のドレイン−ソース間電圧は下がる。またスイッチング素子Q1のドレイン−ソース間の電圧下降に伴い、スイッチング素子Q2のドレイン−ソース間電圧が上昇する。

【0030】

時間Taの時点で、スイッチング素子Q2のドレイン−ソース間の電圧上昇(dv/dt)による電流は、帰還容量26及び入力容量27を接続する経路に流れ出す。そのため、スイッチング素子Q2のゲート−ソース間の電圧が上昇する。このスイッチング素子Q2のゲート−ソース間の上昇電圧は、スイッチング素子Q2のドレイン−ソース間の電圧の上昇速度(dv/dt)が大きいほど高くなり、帰還容量26の容量を入力容量27の容量で除した値(帰還容量26の容量/入力容量27の容量)が大きいほど、高くなる。そして時間Tbの時点で、スイッチング素子Q2のゲート−ソース間の電圧が閾値電圧より高くなり、スイッチング素子Q2が誤ってターンオンされる。この時、スイッチング素子Q1はオンであるため、陽極端子1と陰極端子2との間が短絡し、スイッチング素子Q1及びスイッチング素子Q2に過大な電気的ストレスが加わる。特に、スイッチング素子Q1〜Q6に、SiCデバイスを用いた場合には、他の半導体デバイス(Siデバイスなど)を用いた場合と比較して、動作が高速であり電圧の上昇速度(dv/dt)が大きく、また帰還容量16、26の容量も大きい。そのため、上記のような誤点弧が起こりやすい。

【0031】

誤点弧を防ぐための回路構成として、スイッチング素子Q1〜Q6のゲート−ソース間にコンデンサを追加接続することで、見かけ上のゲート−ソース間の容量(入力容量)を増やす回路構成が知られている。帰還容量26の容量を入力容量27の容量で除した値(帰還容量26の容量/入力容量27の容量)が小さくなり、誤点弧が生じにくくなる。しかし、当該回路構成では、スイッチング毎に追加されたコンデンサを充放電する必要があるため、ゲート駆動回路13、23の負担が増加する、という課題がある。また、コンデンサを追加することで、スイッチング制御時のゲート信号の波形の変化が鈍くなり、スイッチング素子Q1〜Q6のスイッチング速度が遅くなるため、スイッチング動作の時間遅れが大きくなったり、スイッチング損失が増加したりする、という課題もある。

【0032】

また、誤点弧を防ぐための他の回路構成として、スイッチング素子Q1〜Q6のゲート−ソース間に、PNPトランジスタのみを接続し、スイッチング素子Q1〜Q6のゲート−ソース間の電圧が上昇した時に、当該PNPトランジスタをオンにすることで、ゲート−ソース間の電圧をゼロ相当にして、スイッチング素子Q1〜Q6の誤点弧を防ぐ回路構成が知られている(特開2003−324966号公報を参照)。しかし、当該回路構成において、スイッチング素子Q1〜Q6に、閾値電圧が低いまたは負電圧である半導体デバイスを用いた場合には、PNPトランジスタがオンであっても、PNPトランジスタの電圧降下分だけゲート−ソース間電圧が上昇し、スイッチング素子Q1〜Q6が誤ってターンオンしてしまう。すなわち、当該回路構成は、閾値電圧が低い、または負電圧とするワイドギャップ半導体のスイッチング回路には適用することができない。

【0033】

本例は、上記のように、スイッチング素子Q1〜Q6のゲート−ソース間に、PNPトランジスタであるスイッチング素子14、24とコンデンサ15、25との直列回路を接続し、スイッチング素子14、24のベース電極を、ゲート抵抗11、21とゲート駆動回路13、23との間に接続している。これにより、スイッチング素子Q1のターンオンに伴い、スイッチング素子Q2のゲート−ソース間の電圧が上昇した場合、スイッチング素子24がオンになり、コンデンサ25がスイッチング素子Q2のゲート−ソース間に接続される。コンデンサ25の充電電圧により、スイッチング素子Q2のゲート−ソース間の電圧上昇を抑えつつ、スイッチング素子Q2のゲート−ソース間に負バイアスをかけることができるため、スイッチング素子Q2が誤ってターンオンすることを防ぐことができる。

【0034】

次に、図5を用いて、本例のスイッチング回路の動作を説明する。図5は本例のスイッチング回路における、ゲート駆動回路13の出力電圧、ゲート駆動回路23の出力電圧、スイッチング素子Q1のゲート−ソース間の電圧、スイッチング素子Q2のゲート−ソース間の電圧、スイッチング素子Q1のドレイン−ソース間の電圧、上アーム回路1041の電流、スイッチング素子Q2のドレイン−ソース間の電圧、及び、下アーム回路1042の電流のタイムチャートを示し、図4のタイムチャートと対応している。ゲート駆動回路13、23から出力される陽極パルスのタイミングは、図4に示すタイミングと同じため、説明を省略する。

【0035】

時間T1でゲート駆動回路13より陽極パルスが出力されると、スイッチング素子Q1のゲート−ソース間の電圧は上昇する。時間Taの時点で、スイッチング素子Q1のゲート−ソース間の電圧は閾値電圧に達し、スイッチング素子Q1はターンオンする。このとき、スイッチング素子Q1のドレイン電流が流れ始め、スイッチング素子Q1のドレイン−ソース間電圧は下がる。スイッチング素子Q1のドレイン−ソース間の電圧下降に伴い、スイッチング素子Q2のドレイン−ソース間電圧が上昇する。このとき、ゲート駆動回路23からは、負バイアスの電圧が出力されている。

【0036】

時間Ta以降、スイッチング素子Q2のドレイン−ソース間の電圧上昇(dv/dt)による電流は、帰還容量26及び入力容量27を接続する経路に流れ出し、これによりスイッチング素子Q2のゲート−ソース間電圧が上昇する。また本例では、スイッチング素子Q2のゲート電極から、スイッチング素子24のエミッタ電極及びベース電極を介して、ゲートインピーダンス22までの経路が形成されており、Q2のゲート−ソース間電圧上昇による電流が当該経路に流れ、スイッチング素子24がオンになる。スイッチング素子24がオンになると、スイッチング素子Q2のゲート−ソース間には、コンデンサ25が並列に接続されることになる。そのため、スイッチング素子Q2のゲート−ソース間の電圧上昇は抑制され、時間Tbの時点でピークになるスイッチング素子Q2のゲート−ソース間の電圧は閾値電圧より低く維持され、スイッチング素子Q2の誤点弧を防ぐことができる。一連の動作において、コンデンサ25の端子電圧変化は小さいため、コンデンサ25の電流がゲート駆動回路23の負担になることはほとんどない。

【0037】

次に、図6及び図7を用いて、本例のスイッチング回路を組み込んだ半導体モジュール200を説明する。図6は上アーム回路1041から、ゲート駆動回路13及びゲートインピーダンス12を除いた回路図であり、図7は半導体モジュール200の平面図である。なお、他の上アーム回路1043、1045及び下アーム回路1042、1044、1046に含まれる素子も、同様にモジュール化されているが、上アーム回路1041のモジュール化と同様であるため、説明を省略する。

【0038】

本例の半導体モジュール200は、ゲート抵抗11、スイッチング素子14及びコンデンサ15をモジュール化したものである。スイッチング素子Q1及びダイオードD1は、基板(図示しない)上に形成された、電極Aを含む配線上に実装されている。また、スイッチング素子Q1及びダイオードD1は、電極Bを含む配線と電気的に接続されている。半導体モジュール200において、ゲート抵抗11、スイッチング素子14及びコンデンサ15は、電極C及び電極Dをそれぞれ含む配線上に実装され、また各素子間を接続する配線に実装されることで、モジュール化されている。また、半導体モジュール200と、スイッチング素子Q1のゲート電極及びソース電極が、接続されている。これにより、本例のスイッチング回路を有さないインバータに接続する際には、インバータ回路基板に、本例の半導体モジュール200を実装し、回路を構成する素子と接続すれば、本例のスイッチング回路を含むインバータを実現することができる。

【0039】

上記のように、本例は、スイッチング素子Q1〜Q6のゲート電極とソース電極との間に、コンデンサ15、25とスイッチング素子14、24とを直列にして接続し、スイッチング素子14、25のエミッタ電極をスイッチング素子Q1〜Q6のゲート電極に、スイッチング素子14、24のコレクタ電極をスイッチング素子Q1〜Q6のソース電極に、スイッチング素子14、24のベース電極をゲート抵抗11、21とゲート駆動回路13、23との間に、それぞれ電気的に接続する。これにより、一方のスイッチング素子Q1〜Q6のターンオンに伴う、他方のスイッチング素子Q1〜Q6のゲート−ソース間の電圧上昇において、ゲート電極からの電流が、スイッチング素子14、24のエミッタ−ベース間を通り、ゲート駆動回路13、23に流れる。そして、スイッチング素子14、24がオンになり、コンデンサ15、25と導通させることで、入力容量が大きくなるため、スイッチング素子Q1〜Q6のゲート−ソース間の電圧上昇を抑制し、スイッチング素子Q1〜Q6の誤点弧を防ぐことができる。

【0040】

また本例において、コンデンサ15、25は、スイッチング素子Q1〜Q6のゲート−ソース間にバイアス電圧をかけることで誤点弧を防ぐように接続されているため、ゲート駆動回路13、23によるスイッチング制御毎に、コンデンサ15、25を放電させる必要がない。そのため、本例は、スイッチング制御毎に、コンデンサ15、25を充放電しなくてもよいため、ゲート駆動回路13、23の負担を軽減し、ゲート駆動回路13、23の出力波形も鈍らず、スイッチング動作の遅れが発生することを防ぎ、スイッチング速度の低下を防ぐことができる。

【0041】

また本例は、スイッチング素子Q1〜Q6に、ゲート−ソース間の閾値電圧を負電圧とするワイドギャップ半導体デバイスを用いた場合において、一方のスイッチング素子Q1〜Q6のターンオンに伴い、他方のスイッチング素子Q1〜Q6のゲート−ソース間の電圧が上昇し、スイッチング素子14、24がオンになる。かかる場合に、本例は、コンデンサ15、25をスイッチング素子14、25に直列に接続しているため、コンデンサ15、25により負側へバイアス電圧が加わり、スイッチング素子Q1〜Q6のゲート−ソース間の電圧を、閾値電圧未満に維持することができる。これにより、ゲート−ソース間の閾値電圧が低い、または閾値電圧を負電圧とするワイドギャップ半導体デバイスを用いた場合でも、スイッチング素子Q1〜Q6の誤点弧を防ぐことができる。

【0042】

また本例は、スイッチング回路を半導体モジュール200に組み込むことでモジュール化されている。これにより、追加部品を設けることなく、本例のスイッチング回路を、従来の電力変換器へ実装することができる。

【0043】

なお本例は、スイッチング素子Q1〜Q6にバイポーラトランジスタを用いて、コレクタ電極を高電位側電極に、エミッタ電極を低電位側電極に、ベース電極を制御電極になるよう接続してもよい。また、スイッチング素子14、24に、Pチャネル電界効果トランジスタを用いて、ソース電極を高電位側電極に、ドレイン電極を低電位側電極に、ゲート電極を制御電極になるよう接続してもよい。

【0044】

言い換えると、本例は、スイッチング素子Q1〜Q6のゲート電極又はベース電極と当該スイッチング素子Q1〜Q6を制御する駆動回路との間に接続される抵抗と、当該スイッチング素子Q1〜Q6のゲート電極又はベース電極と当該スイッチング素子Q1〜Q6のソース電極又はエミッタ電極との間に接続されるコンデンサ15、25と、コンデンサ15、25に直列に接続されるスイッチング素子14、24とを備え、スイッチング素子14、24のエミッタ端子又はソース端子はスイッチング素子Q1〜Q6のゲート電極又はベース電極に電気的に接続され、スイッチング素子14、24のコレクタ端子又はドレイン端子はスイッチング素子Q1〜Q6のソース電極又はエミッタ電極に電気的に接続され、スイッチング素子14、24のベース電極又はゲート電極は、当該抵抗と当該制御回路の間に接続され、スイッチング素子14、24は、PNPトランジスタ又はPチャネル電界効果トランジスタとしてもよい。

【0045】

また本例は、スイッチング素子14、24のベース電極を、ゲート抵抗11、21の他端とゲートインピーダンス12、22の一端との間に接続したが、ゲートインピーダンス12、22の他端とゲート駆動回路13、23との間に接続してもよく、ゲート抵抗11、21の他端とゲート駆動回路13、23との間に接続すればよい。

【0046】

また、本例は、コンデンサ15、25をスイッチング素子14、24のコレクタ電極に接続するが、コンデンサ15、25の一端をスイッチング素子14、24のエミッタ端子に接続し、コンデンサ15、25の他端をスイッチング素子Q1〜Q6のゲート端子に接続してもよい。

【0047】

また本例において、半導体モジュール200に含まれるゲート抵抗11、21、スイッチング素子14、24及びコンデンサ15、25の全ての回路素子、又は、一部の回路素子をICとして集積化してもよく、あるいは、スイッチング素子Q1〜Q6の中に組み込んでもよい。

【0048】

上記スイッチング素子Q1〜Q6が本発明の「第1のスイッチング素子」に相当し、スイッチング素子14、24が「第2のスイッチング素子」に、コンデンサ15、25が「第1のコンデンサ」に、ゲート駆動回路13、23が「制御回路」に相当し、ゲート抵抗11が「抵抗」に相当する。

【0049】

《第2実施形態》

図8は、発明の他の実施形態に係るスイッチング回路を含むインバータからU相を抜き出した回路の回路図である。本例では上述した第1実施形態に対して、コンデンサ18及びコンデンサ28を接続する点が異なる。これ以外の構成は上述した第1実施形態と同じであるため、その記載を援用する。

【0050】

本例のスイッチング回路は、スイッチング素子14のベース−コレクタ間にコンデンサ18を接続し、スイッチング素子24のベース−コレクタ間にコンデンサ28を接続している。コンデンサ18の容量はコンデンサ15の容量より小さく、コンデンサ28の容量はコンデンサ25の容量より小さい。

【0051】

スイッチング素子Q1がオンになり、スイッチング素子Q2のゲート−ソース間の電圧が上昇すると、ゲート電極からの電流が、スイッチング素子24のエミッタ−ベース間を通り、コンデンサ28に流れる。そして、スイッチング素子24がオンになり、スイッチング素子Q2のゲート−ソース間で、スイッチング素子24とコンデンサ25との直列回路が通電し、スイッチング素子Q2のゲート−ソース間の電圧上昇が抑制される。本例では、スイッチング素子24のベース電流を、ゲートインピーダンス22ではなく、コンデンサ28に流すため、ベース電流に対するゲートインピーダンス22からの影響を受けにくくすることができる。

【0052】

次に、図9及び図10を用いて、本例のスイッチング回路を組み込んだ半導体モジュール200を説明する。図9は上アーム回路1041から、ゲート駆動回路13及びゲートインピーダンス12を除いた回路図であり、図10は半導体モジュールの平面図である。なお、他の上アーム回路1043、1045及び下アーム回路1042、1044、1046に含まれる素子も、同様にモジュール化されているが、上アーム回路1041のモジュール化と同様であるため、説明を省略する。

【0053】

本例の半導体モジュール200は、ゲート抵抗11、スイッチング素子14、コンデンサ15及びコンデンサ18をモジュール化したものである。半導体モジュール200において、ゲート抵抗11、スイッチング素子14、コンデンサ15及びコンデンサ18は、電極C及び電極Dをそれぞれ含む配線上に実装され、また各素子間を接続する配線に実装されることで、モジュール化されている。これにより、本例のスイッチング回路を有さないインバータに接続する際には、インバータ回路基板に、本例の半導体モジュール200を実装し、回路を構成する素子と接続すれば、本例のスイッチング回路を含むインバータを実現することができる。

【0054】

上記のように、本例は、スイッチング素子14、24のベース電極とコレクタ電極との間に、コンデンサ15、25の容量より小さい容量であるコンデンサ18、28を接続する。これにより、スイッチング素子14、24のベース電流が、ゲートインピーダンス12、22により影響を受けることを防ぐことができる。

【0055】

上記コンデンサ18、28が「第2のコンデンサ」に相当する。

【符号の説明】

【0056】

100…インバータ

101…直流電源

102…コンデンサ

103…交流負荷

1041、1043、1045…上アーム回路

1042、1044、1046…下アーム回路

105…コントローラ

Q1〜Q6…スイッチング素子

D1〜D6…ダイオード

11、21…ゲート抵抗

12、22…ゲートインピーダンス

13、23…ゲート駆動回路

14、24…スイッチング素子

15、18、25、28…コンデンサ

1…陽極端子

2…陰極端子

3…交流端子

200…半導体モジュール

【特許請求の範囲】

【請求項1】

第1のスイッチング素子の制御電極と前記第1のスイッチング素子をスイッチング制御する制御回路との間に接続される抵抗と、

前記第1のスイッチング素子の制御電極と前記第1のスイッチング素子の低電位側電極との間に接続される第1のコンデンサと、

前記第1のコンデンサと直列に接続される第2のスイッチング素子とを備え、

前記第2のスイッチング素子の高電位側電極は、前記第1のスイッチング素子の制御電極に電気的に接続され、

前記第2のスイッチング素子の低電位側電極は前記第1のスイッチング素子の低電位側電力端子に電気的に接続され、

前記第2のスイッチング素子の制御電極は、前記抵抗と前記制御回路の間に接続されている

ことを特徴とするスイッチング回路。

【請求項2】

前記第2のスイッチング素子の制御電極と、前記第1のスイッチング素子の低電位側電極との間に接続され、前記第1のコンデンサの容量より小さい容量である第2のコンデンサをさらに備える

ことを特徴とする請求項1記載のスイッチング回路。

【請求項3】

前記第1のスイッチング素子は、

高電位側電極をドレイン電極とし低電位側電極をソース電極とするワイドギャップ半導体デバイス、又は、高電位側電極をコレクタ電極とし低電位側電極をエミッタ電極とするワイドギャップ半導体デバイスであり、

前記第2のスイッチング素子は、

高電位側電極をエミッタ電極とし低電位側電極をコレクタ電極とするPNPトランジスタ、又は、高電位側電極をソース電極とし低電位側電極をドレイン電極とするPチャネル電界効果トランジスタである

ことを特徴とする請求項1又は2記載のスイッチング回路。

【請求項4】

前記第1のスイッチング素子のオン及びオフを切り替える閾値電圧が負電圧である

ことを特徴とする請求項1〜3のいずれか一項に記載のスイッチング回路。

【請求項5】

前記第1のスイッチング素子は、パワーデバイスである

ことを特徴とする請求項1〜4のいずれか一項に記載のスイッチング回路。

【請求項6】

請求項1〜5のいずれか一項に記載のスイッチング回路を組み込んだ半導体モジュール。

【請求項1】

第1のスイッチング素子の制御電極と前記第1のスイッチング素子をスイッチング制御する制御回路との間に接続される抵抗と、

前記第1のスイッチング素子の制御電極と前記第1のスイッチング素子の低電位側電極との間に接続される第1のコンデンサと、

前記第1のコンデンサと直列に接続される第2のスイッチング素子とを備え、

前記第2のスイッチング素子の高電位側電極は、前記第1のスイッチング素子の制御電極に電気的に接続され、

前記第2のスイッチング素子の低電位側電極は前記第1のスイッチング素子の低電位側電力端子に電気的に接続され、

前記第2のスイッチング素子の制御電極は、前記抵抗と前記制御回路の間に接続されている

ことを特徴とするスイッチング回路。

【請求項2】

前記第2のスイッチング素子の制御電極と、前記第1のスイッチング素子の低電位側電極との間に接続され、前記第1のコンデンサの容量より小さい容量である第2のコンデンサをさらに備える

ことを特徴とする請求項1記載のスイッチング回路。

【請求項3】

前記第1のスイッチング素子は、

高電位側電極をドレイン電極とし低電位側電極をソース電極とするワイドギャップ半導体デバイス、又は、高電位側電極をコレクタ電極とし低電位側電極をエミッタ電極とするワイドギャップ半導体デバイスであり、

前記第2のスイッチング素子は、

高電位側電極をエミッタ電極とし低電位側電極をコレクタ電極とするPNPトランジスタ、又は、高電位側電極をソース電極とし低電位側電極をドレイン電極とするPチャネル電界効果トランジスタである

ことを特徴とする請求項1又は2記載のスイッチング回路。

【請求項4】

前記第1のスイッチング素子のオン及びオフを切り替える閾値電圧が負電圧である

ことを特徴とする請求項1〜3のいずれか一項に記載のスイッチング回路。

【請求項5】

前記第1のスイッチング素子は、パワーデバイスである

ことを特徴とする請求項1〜4のいずれか一項に記載のスイッチング回路。

【請求項6】

請求項1〜5のいずれか一項に記載のスイッチング回路を組み込んだ半導体モジュール。

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【公開番号】特開2012−239061(P2012−239061A)

【公開日】平成24年12月6日(2012.12.6)

【国際特許分類】

【出願番号】特願2011−107171(P2011−107171)

【出願日】平成23年5月12日(2011.5.12)

【国等の委託研究の成果に係る記載事項】(出願人による申告)平成21年度、新エネルギー・産業技術総合開発機構からの委託研究「次世代パワーエレクトロニクス技術開発」、産業技術力強化法第19条の適用を受ける特許出願

【出願人】(000003997)日産自動車株式会社 (16,386)

【出願人】(000106276)サンケン電気株式会社 (982)

【出願人】(000005234)富士電機株式会社 (3,146)

【Fターム(参考)】

【公開日】平成24年12月6日(2012.12.6)

【国際特許分類】

【出願日】平成23年5月12日(2011.5.12)

【国等の委託研究の成果に係る記載事項】(出願人による申告)平成21年度、新エネルギー・産業技術総合開発機構からの委託研究「次世代パワーエレクトロニクス技術開発」、産業技術力強化法第19条の適用を受ける特許出願

【出願人】(000003997)日産自動車株式会社 (16,386)

【出願人】(000106276)サンケン電気株式会社 (982)

【出願人】(000005234)富士電機株式会社 (3,146)

【Fターム(参考)】

[ Back to top ]