スイッチング回路及びDC−DCコンバータ

【課題】スイッチングノイズの低減と動作効率の向上を図り、併せてスイッチ素子の破壊を防止したスイッチング回路及びDC−DCコンバータを提供する。

【解決手段】実施形態によれば、ハイサイドスイッチと、ローサイドスイッチと、駆動回路と、を備えたスイッチング回路が提供される。前記ハイサイドスイッチは、電源端子と出力端子との間に接続されている。前記ローサイドスイッチは、前記出力端子と接地端子との間に接続されている。前記駆動回路は、制御信号に応じて、前記ハイサイドスイッチ及び前記ローサイドスイッチのいずれか一方のスイッチをオフし、第1の期間の間第1の電圧を他方のスイッチの制御端子に供給して前記他方のスイッチをオンさせ、前記第1の期間経過後において前記他方のスイッチの制御端子に前記第1の電圧よりも高い第2の電圧を供給することを特徴とする。

【解決手段】実施形態によれば、ハイサイドスイッチと、ローサイドスイッチと、駆動回路と、を備えたスイッチング回路が提供される。前記ハイサイドスイッチは、電源端子と出力端子との間に接続されている。前記ローサイドスイッチは、前記出力端子と接地端子との間に接続されている。前記駆動回路は、制御信号に応じて、前記ハイサイドスイッチ及び前記ローサイドスイッチのいずれか一方のスイッチをオフし、第1の期間の間第1の電圧を他方のスイッチの制御端子に供給して前記他方のスイッチをオンさせ、前記第1の期間経過後において前記他方のスイッチの制御端子に前記第1の電圧よりも高い第2の電圧を供給することを特徴とする。

【発明の詳細な説明】

【技術分野】

【0001】

本発明の実施形態は、スイッチング回路及びDC−DCコンバータに関する。

【背景技術】

【0002】

スイッチング回路は、誘導性負荷の駆動する出力回路として広く用いられている。例えば、降圧型DC−DCコンバータにおいては、ハイサイドスイッチとローサイドスイッチとで構成されたスイッチング回路を用いて、インダクタを駆動する。

ハイサイドスイッチがオフのときは、ローサイドスイッチに電流が流れる。そして、ローサイドスイッチがオフし、ハイサイドスイッチがオンに変化したとき、ローサイドスイッチの寄生ダイオードの回復電流がハイサイドスイッチに流れる。そのため、スイッチングの高速化や低オン抵抗な素子を使用して効率を向上させようとすると、回復電流も大きくなり、スイッチングノイズの発生や動作効率の低下要因となる。また、低オン抵抗な素子は、出力端子の短絡時に破壊の恐れもある。

【先行技術文献】

【特許文献】

【0003】

【特許文献1】特開2009−148043号公報

【発明の概要】

【発明が解決しようとする課題】

【0004】

本発明の実施形態は、スイッチングノイズの低減と動作効率の向上を図り、併せてスイッチ素子の破壊を防止したスイッチング回路及びDC−DCコンバータを提供する。

【課題を解決するための手段】

【0005】

実施形態によれば、ハイサイドスイッチと、ローサイドスイッチと、駆動回路と、を備えたスイッチング回路が提供される。前記ハイサイドスイッチは、電源端子と出力端子との間に接続されている。前記ローサイドスイッチは、前記出力端子と接地端子との間に接続されている。前記駆動回路は、制御信号に応じて、前記ハイサイドスイッチ及び前記ローサイドスイッチのいずれか一方のスイッチをオフし、第1の期間の間第1の電圧を他方のスイッチの制御端子に供給して前記他方のスイッチをオンさせ、前記第1の期間経過後において前記他方のスイッチの前記制御端子に前記第1の電圧よりも高い第2の電圧を供給することを特徴とする。

【図面の簡単な説明】

【0006】

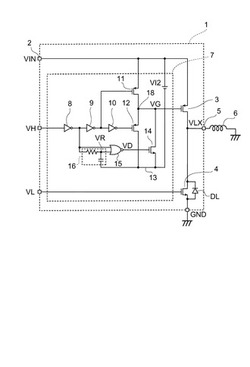

【図1】第1の実施形態に係るスイッチング回路の構成を例示する回路図。

【図2】図1に表したスイッチング回路の主要な信号のタイミングチャートであり、(a)はハイサイド制御信号VH、(b)はローサイド制御信号VL、(c)は信号VR、(d)は信号VD、(e)はゲート電圧VG、(f)は出力電圧VLX、(g)はハイサイド電流IHを表す。

【図3】ゲート・ソース間電圧Vgsとオン抵抗Ronとの関係を表す特性図。

【図4】ハイサイドスイッチの状態を表す特性図であり、(a)はオン抵抗Ron、(b)はハイサイド電流IHを表す。

【図5】第2の実施形態に係るスイッチング回路の構成を例示する回路図。

【図6】図5に表したスイッチング回路の主要な信号のタイミングチャートであり、(a)はハイサイド制御信号VH、(b)はローサイド制御信号VL、(c)は信号VR、(d)は信号VD、(e)はゲート電圧VG、(f)は出力電圧VLX、(g)は短絡検出信号VS、(h)はハイサイド電流IHを表す。

【図7】第2の実施形態に係るスイッチング回路の他の構成を例示する回路図。

【図8】図7に表したスイッチング回路の主要な信号のタイミングチャートであり、(a)はハイサイド制御信号VH、(b)はローサイド制御信号VL、(c)は信号VR、(d)は信号VD、(e)はゲート電圧VG、(f)は出力電圧VLX、(g)は短絡検出信号VSを表す。

【図9】第3の実施形態に係るDC−DCコンバータの構成を例示する回路図。

【図10】図9に表したDC−DCコンバータの主要な信号のタイミングチャートであり、(a)はハイサイド制御信号VH、(b)はローサイド制御信号VL、(c)はゲート電圧VG、(d)はスイッチング回路の出力電圧VLX、(e)はハイサイド電流IH、(f)はローサイド電流IL、(g)はインダクタ電流ILLを表す。

【図11】図9に表したDC−DCコンバータの主要な信号の他のタイミングチャートであり、(a)はハイサイド制御信号VH、(b)はローサイド制御信号VL、(c)はゲート電圧VG、(d)はスイッチング回路の出力電圧VLX、(e)はハイサイド電流IH、(f)はローサイド電流IL、(g)はインダクタ電流ILLを表す。

【発明を実施するための形態】

【0007】

以下、本発明の実施形態について図面を参照して詳細に説明する。なお、本願明細書と各図において、既出の図に関して前述したものと同様の要素には同一の符号を付して詳細な説明は適宜省略する。

【0008】

(第1の実施形態)

図1は、第1の実施形態に係るスイッチング回路の構成を例示する回路図である。

スイッチング回路1においては、電源端子2と出力端子との間にハイサイドスイッチ3が接続されている。出力端子5と接地端子GNDとの間にローサイドスイッチ4が接続されている。ハイサイドスイッチ3とローサイドスイッチ4とは、直列に接続されている。出力端子5には、誘導性負荷6が接続されている。

【0009】

ハイサイドスイッチ3とローサイドスイッチ4とを制御する信号は、駆動回路7で生成される。駆動回路7は、外部から入力されたハイサイド制御信号VH及びローサイド制御信号VLに応じて、ハイサイドスイッチ3及びローサイドスイッチ4をそれぞれオンまたはオフする。

【0010】

ハイサイドスイッチ3がオンでローサイドスイッチがオフのとき、出力端子5は、電源端子2と電気的に接続される。このとき、出力端子5の電圧、すなわち出力電圧VLXは、電源端子2に供給される電源電圧VINになる。そして、誘導性負荷6に電流が流れ、電源端子2を介して電源からエネルギーが供給される。

【0011】

ハイサイドスイッチ3がオフでローサイドスイッチがオンのとき、出力端子5は、接地端子GNDと電気的に接続される。このとき、出力電圧VLXは、0Vになる。誘導性負荷6には、回生電流が流れ、エネルギーが減少していく。

【0012】

スイッチング回路1は、ハイサイド制御信号VH、ローサイド制御信号VLに応じて、誘導性負荷6を駆動する。なお、図1においては、誘導性負荷6として、インダクタを例示しているが、例えば、DC−DCコンバータのインダクタや、モータなどのアクチュエータでもよい。

【0013】

次に各部について説明する。

ハイサイドスイッチ3は、PチャンネルMOSFET(以下、PMOS)であり、ソースは、電源端子2に接続され、ドレインは、出力端子5に接続されている。また、ハイサイドスイッチ3のゲート(制御端子)18は、駆動回路7に接続される。ハイサイドスイッチ3には、図示しない寄生ダイオードが含まれる。

【0014】

ローサイドスイッチ4は、NチャンネルMOSFET(以下、NMOS)であり、ソースは、接地端子GNDに接続され、ドレインは、出力端子5に接続されている。また、ローサイドスイッチ4のゲートは、駆動回路7に接続される。ローサイドスイッチ4には、寄生ダイオードDLが含まれる。

【0015】

駆動回路7においては、ハイサイド制御信号VHは、否定回路(INV)8、9、10を介して、第1のトランジスタ11、第2のトランジスタ12に入力される。第1及び第2のトランジスタ11、12は、PMOSで構成され、電源端子2と内部電源線13との間に直列に接続されている。

【0016】

第1のトランジスタ11のソースは、電源端子2に接続され、ドレインは、制御端子18に接続されている。第1のトランジスタ11のゲートは、INV9の出力に接続されている。第2のトランジスタ12のソースは、制御端子18に接続され、ドレインは、内部電源線13に接続されている。第2のトランジスタ12のゲートは、INV10の出力に接続されている。

【0017】

また、第3のトランジスタ14は、第2のトランジスタ12と並列に接続されている。第3のトランジスタ14は、NMOSで構成され、ドレインは、制御端子18に接続され、ソースは内部電源線13に接続されている。第3のトランジスタ14のゲートは、論理和の否定回路(NOR)15の出力に接続されている。

【0018】

NOR15は、INV8の出力と、INV8の出力を遅延回路16で遅延させた信号VRと、の論理和(信号VD)を生成する。なお、遅延回路16は、抵抗とコンデンサとで構成されている。信号VDは、INV8の出力の立ち上がりはそのままで、立ち下がりだけを遅延させ、さらに反転させた信号である。なお、遅延時間は、図2及び図4において説明するように、ローサイドスイッチ4の寄生ダイオードDLの逆方向回復時間Trrとほぼ等しい第1の期間T1に設定される。

【0019】

内部電源線13には、電源端子2に対して、−VI2の電圧が供給されている。INV8、9、10などの駆動回路7の内部の各論理回路には、内部電源電圧としてVI2が供給されている。駆動回路7の内部の各論理回路は、内部電源線13の電位を基準として動作する。

【0020】

上記のとおり、第1のトランジスタ11、第2のトランジスタ12及び第3のトランジスタ14は、制御端子18に接続されている。図2において説明するように、駆動回路7は、ハイサイド制御信号VH、出力電圧VLXに応じて、ハイサイドスイッチ3のゲート電圧(制御端子の電圧)VGを制御する。また、駆動回路7は、ローサイド制御信号VLをそのままの論理でローサイドスイッチ4のゲートに出力する。

【0021】

次にスイッチング回路1の動作について説明する。

図2は、図1に表したスイッチング回路の主要な信号のタイミングチャートであり、(a)はハイサイド制御信号VH、(b)はローサイド制御信号VL、(c)は信号VR、(d)は信号VD、(e)はゲート電圧VG、(f)は出力電圧VLX、(g)はハイサイド電流IHを表す。

【0022】

なお、図2(b)においては、ローサイドスイッチ4がオンまたはオフに制御されていることを、それぞれON、OFFで表している。また、図2(e)においては、ハイサイドスイッチ3がオンまたはオフに制御されていることを、それぞれON、OFFで表している。

【0023】

図2においては、ハイサイド制御信号VHとして、ハイレベルとローレベルとを周期的に繰り返す矩形波を入力した場合を例示している(図2(a))。また、ローサイド制御信号VLは、ハイサイド制御信号VHを反転した信号である(図2(b))。なお、ハイサイドスイッチ3とローサイドスイッチ4とが同時にオンになることを避けるために設けられるデッドタイムは、省略している。

【0024】

ハイサイド制御信号VHがローレベル、ローサイド制御信号VLがハイレベルのとき(図2(a)、(b))、ハイサイドスイッチ3はオフ、ローサイドスイッチ4はオンである。このとき、出力電圧VLXはローレベルである(図2(f))。また、信号VDは、ローレベルである(図2(d))。また、ローサイドスイッチ4には、誘導性負荷6の回生電流が流れている。

【0025】

ハイサイド制御信号VHがローレベルからハイレベルに変化すると(図2(a))、ローサイド制御信号VLはハイレベルからローレベルに変化する(図2(b))。ローサイドスイッチ4はオフになり、ローサイドスイッチ4を流れていた回生電流は、寄生ダイオードDLを流れる。

信号VDは、ハイサイド制御信号VHに対して第1の期間T1だけ遅延しているため、ローレベルである(図2(d))。

【0026】

第1のトランジスタ11はオフ、第2のトランジスタ12はオン、第3のトランジスタ14はオフになる。第2のトランジスタ12はソースフォロワ出力のため、ハイサイドスイッチ3のゲート電圧VGは、内部電源線13の電位よりも第2のトランジスタ12のしきい値電圧Vthだけ高い第1の電圧V1になる(図2(e))。なお、図2(e)においては、電源端子2の電位VINを基準にして、ゲート電圧VGを表している。

【0027】

ここで、第1の電圧V1は、内部電源電圧VI2よりも低く設定されている。ハイサイドスイッチ3のオン抵抗Ronは、内部電源電圧VI2を供給した場合よりも大きい値になっている。そのため、寄生ダイオードDLの逆方向電流はオン抵抗Ronに制限され、ハイサイドスイッチ3の電流IHとして流れる(図2(g)の一点鎖線Rで囲んだ部分)。

【0028】

遅延回路16の出力の信号VRは、時定数に従って低下する(図2(c))。第1の期間T1において、信号VRは、NOR15の論理しきい電圧よりも低下する。信号VDは、ハイレベルに変化する(図2(d))。信号VDは、ハイサイド制御信号VHの立上がりを第1の期間T1だけ遅延させた信号になる。

【0029】

ハイサイド制御信号VHがハイレベルに変化してから第1の期間T1経過後、信号VDは、ハイレベルになる。このとき、出力電圧VLXは、ハイレベルである(図2(f)の一点鎖線Pで囲んだ部分)。

【0030】

第3のトランジスタ14は、オンになり、ゲート電圧VGは、第2の電圧V2=−VI2になる。出力電圧VLXは、電源電圧VINまで上昇する(図2(f))。このとき、寄生ダイオードDLの逆方向回復時間Trrとほぼ等しい第1の期間T1を経過しているため、寄生ダイオードDLの逆方向回復電流はすでに減少している。ハイサイドスイッチ3の電流IHは、ほぼ直線的に上昇していく(図2(g))。

【0031】

ハイサイド制御信号VHがローレベル、ローサイド制御信号VLがハイレベルに変化すると、ハイサイドスイッチ3はオフ、ローサイドスイッチ4はオンに切り替えられる。次サイクル以降、同様の動作が繰り返される。

【0032】

このように、駆動回路7は、ハイサイド制御信号VHがローレベル、ローサイド制御信号VLがハイレベルのとき、ハイサイドスイッチ3をオフ、ローサイドスイッチ4をオンに切り替える。このとき、ローサイドスイッチ4に誘導性負荷6の回生電流が流れる。

【0033】

また、ハイサイド制御信号VHがハイレベル、ローサイド制御信号VLがローレベルに変化したとき、ローサイドスイッチ4をオフに切り替える。同時に、ハイサイドスイッチ3の制御端子に第1の期間T1の間は、第1の電圧V1を供給する。このとき、ハイサイドスイッチ3の電流IHは、オン抵抗Ronに制限されたローサイドスイッチ4の寄生ダイオードDLの逆方向回復電流が流れることになる。

【0034】

そして、第1の期間経過後は、第1の電圧V1よりも高い第2の電圧V2として電源電圧VINを供給してハイサイドスイッチ3をオンに切り替える。このときのハイサイドスイッチ3のオン抵抗は、第1の期間T1における値よりも小さくなっている。

【0035】

スイッチング回路1においては、ハイサイドスイッチ3がオフからオンに変化するときの第1の期間T1の間ゲート駆動電圧を低くすることにより、寄生ダイオードDLの逆方向回復電流が抑制される。そして第1の期間T1の経過後、寄生ダイオードDLに流れる電流がなくなるころに、ハイサイドスイッチ3のゲート駆動電圧が高くなり、オン抵抗をより小さくする。

【0036】

なお、第1の期間T1の間に、出力端子5と接地端子GNDとが短絡した場合でも、ハイサイドスイッチ3を流れる電流IHは、比較的高いオン抵抗により制限された値になる。

【0037】

図3は、ゲート・ソース間電圧Vgsとオン抵抗Ronとの関係を表す特性図である。

図3においては、ハイサイドスイッチ3のゲート・ソース間電圧Vgsを横軸、オン抵抗Ronを縦軸にとり、オン抵抗Ronのゲート・ソース間電圧Vgs依存性を表している。なお、各電圧は絶対値を表している。

【0038】

しきい値電圧Vth以上のゲート・ソース間電圧Vgsに対して、オン抵抗Ronは単調に低下する。ゲート電圧VGは、電源端子2の電位VINを基準にしているため、ゲート電圧VGは、ハイサイドスイッチ3のゲート・ソース間電圧Vgsと等しい。ゲート電圧VGが第1の電圧V1のとき、オン抵抗はRon1である。ゲート電圧が第2の電圧V2(=VI2)のとき、オン抵抗はRon2である。ここで、|Vgs1|<|Vgs2|、Ron1>Ron2になっている。

【0039】

図4は、ハイサイドスイッチの状態を表す特性図であり、(a)はオン抵抗Ron、(b)はハイサイド電流IHを表す。

図4(a)においては、横軸に時間t、縦軸にオン抵抗Ronをとり、ハイサイドスイッチ3のオン抵抗Ronの時間変化を表している。図4(b)においては、横軸に時間t、縦軸にハイサイドスイッチ3の電流IHをとり、電流IHの時間変化を表している。

【0040】

時間t=0でハイサイド制御信号VHがローレベルからハイレベルに変化した場合において、第1の期間T1の間、オン抵抗Ronは、Ron1になる。第1の期間T1経過後、オン抵抗Ronは、Ron1よりも小さいRon2になる。

【0041】

ハイサイドスイッチ3の電流IHは、第1の期間T1の間、比較的大きいオン抵抗Ron1のために、オン抵抗Ron2の場合に流れる寄生ダイオードDLの逆方向回復電流Irrよりも小さい値に制限されている。

したがって、スイッチングノイズが低減され、動作効率が向上する。

【0042】

なお、図4(b)においては、第1の期間T1が寄生ダイオードDLの逆方向回復時間Trrと等しい場合の電流IHを例示している。しかし、第1の期間T1は、寄生ダイオードDLの逆方向回復時間Trrと等しくなくてもよい。

【0043】

例えば、第1の期間T1は、寄生ダイオードDLの逆方向回復時間Trr以下に設定してもよい。この場合、第1の期間T1の間は、比較的大きいオン抵抗Ron1により電流IHは制限され、第1の期間T1経過後も逆方向回復時間Trrまでは、寄生ダイオードDLの逆方向回復電流Irrが流れることになる。

【0044】

しかし、第1の期間T1を設定せず、時間t=0でオン抵抗をRon2の小さい値に設定した場合と比較すると、流れる逆方向回復電流Irrは小さくなる。そのため、第1の期間T1を設定しない場合と比較して、スイッチングノイズが低減され、動作効率が向上する。また、第1の期間T1を逆方向回復時間Trrと等しく設定した場合と比較して、オン抵抗の小さい期間が長くなるため、動作効率が向上する。

【0045】

また、第1の期間T1は、寄生ダイオードDLの逆方向回復時間Trrよりも大きく設定してもよい。この場合、逆方向回復時間Trr経過後も第1の期間T1が経過するまでの間は、比較的大きいオン抵抗Ron1に保たれることになる。しかし、第1の期間T1が、ハイサイド制御信号VHがハイレベルである期間、すなわちハイサイドスイッチ3がオンしている期間と比較して十分短ければ、動作効率の低下はわずかである。

【0046】

なお、図1に表したスイッチング回路1においては、第1のトランジスタ11及び第2のトランジスタ12は、PMOS、第3のトランジスタ14は、NMOSでそれぞれ構成されている。しかし、第1のトランジスタ11及び第2のトランジスタ12は、NMOS、第3のトランジスタ14は、PMOSでそれぞれ構成されてもよい。

【0047】

(第2の実施形態)

図5は、第2の実施形態に係るスイッチング回路の構成を例示する回路図である。

スイッチング回路1aにおいては、ハイサイドスイッチ3、ローサイドスイッチ4、駆動回路7aを備える。スイッチング回路1aは、図1に表したスイッチング回路1の駆動回路7を駆動回路7aに置き換えた構成である。また、駆動回路7aは、図1に表した駆動回路7のINV8を論理積の否定回路(NAND)22に置き換え、さらに短絡検出回路17を追加した構成である。これ以外については、図1に表したスイッチング回路1と同様である。

【0048】

駆動回路7aにおいては、ハイサイド制御信号VHは、NAND22、INV9、10を介して、第1のトランジスタ11、第2のトランジスタ12に入力される。第1及び第2のトランジスタ11、12は、PMOSで構成され、電源端子2と内部電源線13との間に直列に接続されている。

【0049】

第1のトランジスタ11のソースは、電源端子2に接続され、ドレインは、制御端子18に接続されている。第1のトランジスタ11のゲートは、INV9の出力に接続されている。第2のトランジスタ12のソースは、制御端子18に接続され、ドレインは、内部電源線13に接続されている。第2のトランジスタ12のゲートは、INV10の出力に接続されている。

【0050】

また、第3のトランジスタ14は、第2のトランジスタ12と並列に接続されている。第3のトランジスタ14は、NMOSで構成され、ドレインは、制御端子18に接続され、ソースは内部電源線13に接続されている。第3のトランジスタ14のゲートは、NOR15の出力に接続されている。

【0051】

NOR15は、NAND22の出力と、NAND22の出力を遅延回路16で遅延させた信号VRと、の論理和(信号VD)を生成する。なお、遅延回路16は、抵抗とコンデンサとで構成されている。信号VDは、NAND8の出力の立ち上がりはそのままで、立ち下がりだけを遅延させ、さらに反転させた信号である。なお、遅延時間は、ローサイドスイッチ4の寄生ダイオードDLの逆方向回復時間Trrとほぼ等しい第1の期間T1に設定される。

【0052】

また、短絡検出回路17は、出力端子5と接地端子GNDとの短絡を検出する。図5においては、短絡検出回路17は、D型フリップフロップ(DFF)で構成されている。DFFのクロック端子CKには、信号VDが入力され、DFFの入力端子Dには出力電圧VLXが入力される。DFFの出力端子Qに短絡検出信号VSが出力される。なお、短絡検出回路17のDFFは、信号VDの立ち上がりエッジでクロックされる。

【0053】

NAND22は、ハイサイド制御信号VHと短絡検出信号VSとの論理積の否定を生成する。なお、図6において説明するように、NAND22は、短絡検出信号VSで、ハイサイド制御信号VHをマスクしている。また、短絡検出回路17を構成するDFFは、初期状態として、短絡を検出しない状態、すなわちハイレベルを出力する状態にセットされる。なお、DFFを外部からセットして初期状態に戻せるように、スイッチング回路1aにセット端子を設けてもよい。

【0054】

内部電源線13には、電源端子2に対して、−VI2の電圧が供給されている。NAND22、INV9、10などの駆動回路7の内部の各論理回路には、内部電源電圧としてVI2が供給されている。駆動回路7aの内部の各論理回路は、内部電源線13の電位を基準として動作する。

【0055】

上記のとおり、第1のトランジスタ11、第2のトランジスタ12及び第3のトランジスタ14は、制御端子18に接続されている。駆動回路7aは、ハイサイド制御信号VH、出力電圧VLXに応じて、ハイサイドスイッチ3のゲート電圧(制御端子の電圧)VGを制御する。また、駆動回路7aは、ローサイド制御信号VLをそのままの論理でローサイドスイッチ4のゲートに出力する。

【0056】

次にスイッチング回路1の動作について説明する。

図6は、図5に表したスイッチング回路の主要な信号のタイミングチャートであり、(a)はハイサイド制御信号VH、(b)はローサイド制御信号VL、(c)は信号VR、(d)は信号VD、(e)はゲート電圧VG、(f)は出力電圧VLX、(g)は短絡検出信号VS、(h)はハイサイド電流IHを表す。

【0057】

なお、図6(b)においては、ローサイドスイッチ4がオンまたはオフに制御されていることを、それぞれON、OFFで表している。また、図6(e)においては、ハイサイドスイッチ3がオンまたはオフに制御されていることを、それぞれON、OFFで表している。

【0058】

図6においては、ハイサイド制御信号VHとして、ハイレベルとローレベルとを周期的に繰り返す矩形波を入力した場合を例示している(図6(a))。また、ローサイド制御信号VLは、ハイサイド制御信号VHを反転した信号である(図6(b))。なお、ハイサイドスイッチ3とローサイドスイッチ4とが同時にオンになることを避けるために設けられるデッドタイムは、省略している。

【0059】

ハイサイド制御信号VHがローレベル、ローサイド制御信号VLがハイレベルのとき(図6(a)、(b))、ハイサイドスイッチ3はオフ、ローサイドスイッチ4はオンである。このとき、出力電圧VLXはローレベルである(図6(f))。また、信号VDは、ローレベルである(図6(d))。また、ローサイドスイッチ4には、誘導性負荷6の回生電流が流れている。

【0060】

ローサイド制御信号VLがハイレベルからローレベルに変化すると(図6(b))、ハイサイド制御信号VHはローレベルからハイレベルに変化する(図6(a))。ローサイドスイッチ4はオフになり、ローサイドスイッチ4を流れていた回生電流は、寄生ダイオードDLを流れる。

【0061】

信号VDは、ハイサイド制御信号VHに対して第1の期間T1だけ遅延しているため、ローレベルである(図6(d))。従って、短絡検出信号VSは、出力電圧VLXによらずハイレベルになる(図6(g))。

【0062】

第1のトランジスタ11はオフ、第2のトランジスタ12はオン、第3のトランジスタ14はオフになる。第2のトランジスタ12はソースフォロワ出力のため、ハイサイドスイッチ3のゲート電圧VGは、内部電源線13の電位よりも第2のトランジスタ12のしきい値電圧Vthだけ高い第1の電圧V1になる(図6(e))。なお、図6(e)においては、電源端子2の電位VINを基準にして、ゲート電圧VGを表している。

【0063】

ここで、第1の電圧V1は、内部電源電圧VI2よりも低く設定されている。ハイサイドスイッチ3のオン抵抗Ronは、内部電源電圧VI2を供給した場合よりも大きい値になっている。そのため、寄生ダイオードDLの逆方向電流はオン抵抗Ronに制限され、ハイサイドスイッチ3の電流IHとして流れる(図6(h)の一点鎖線Rで囲んだ部分)。

【0064】

遅延回路16の出力の信号VRは、時定数に従って低下する(図6(c))。第1の期間T1において、信号VRは、NOR15の論理しきい電圧よりも低下する。信号VDは、ハイレベルに変化する(図6(d))。信号VDは、ハイサイド制御信号VHの立上がりを第1の期間T1だけ遅延させた信号になる。

【0065】

ハイサイド制御信号VHがローレベルに変化してから第1の期間T1経過後、信号VDは、ハイレベルになり(図6(d))、短絡検出回路17のDFFがクロックされる。このとき、出力電圧VLXは、ハイレベルである(図6(f)の一点鎖線Pで囲んだ部分)。そのため、短絡検出回路17は、短絡を検出せず、短絡検出信号VSはハイレベルのままである(図6(g))。

【0066】

第3のトランジスタ14は、オンになり、ゲート電圧VGは、第2の電圧V2=−VI2になる。出力電圧VLXは、電源電圧VINまで上昇する(図6(f))。このとき、寄生ダイオードDLの逆方向回復時間Trrとほぼ等しい第1の期間T1を経過しているため、寄生ダイオードDLの逆方向回復電流はすでに減少している。ハイサイドスイッチ3の電流IHは、ほぼ直線的に上昇していく(図6(h))。

【0067】

ハイサイド制御信号VHがローレベル、ローサイド制御信号VLがハイレベルに変化すると、ハイサイドスイッチ3はオフ、ローサイドスイッチ4はオンに切り替えられる。次サイクル以降、同様の動作が繰り返される。

【0068】

また、第1の期間T1の経過時に、出力電圧VLXがローレベルの場合(図6(f)の一点破線Qで囲んだ部分)、短絡検出回路17は、短絡を検出し短絡検出信号VSとしてローレベルを出力する(図6(g))。

【0069】

NAND22にローレベルの短絡検出信号VSが入力され、NAND22は、ハイレベルを出力する。信号VDは、ローレベルになる。第1のトランジスタ11はオン、第2のトランジスタ12はオフ、第3のトランジスタ14はオフになる。

したがって、ハイサイドスイッチ3は、オフに切り替えられ、ハイサイドスイッチ3の電流IHは0になる(図6(h))。

【0070】

このように、駆動回路7aは、ハイサイド制御信号VHがローレベル、ローサイド制御信号VLがハイレベルのとき、ハイサイドスイッチ3をオフ、ローサイドスイッチ4をオンに切り替える。このとき、ローサイドスイッチ4に誘導性負荷6の回生電流が流れる。

【0071】

また、ハイサイド制御信号VHがハイレベル、ローサイド制御信号VLがローレベルに変化したとき、ローサイドスイッチ4をオフに切り替える。同時に、ハイサイドスイッチ3に第1の期間T1の間は、第1の電圧V1を供給する。このとき、ハイサイドスイッチ3の電流IHは、オン抵抗Ron=Ron1に制限されたローサイドスイッチ4の寄生ダイオードDLの逆方向回復電流が流れることになる。

【0072】

そして、第1の期間経過後は、第1の電圧V1よりも高い第2の電圧V2として電源電圧VINを供給してハイサイドスイッチ3をオンに切り替える。このときのハイサイドスイッチ3のオン抵抗Ron=Ron2は、第1の期間T1における値よりも小さくなっている。

【0073】

スイッチング回路1aにおいては、ハイサイドスイッチ3がオフからオンに変化するときの第1の期間T1の間ゲート駆動電圧を低くすることにより、寄生ダイオードDLの逆方向回復電流が抑制される。そして第1の期間T1の経過後、寄生ダイオードDLに流れる電流がなくなるころに、ハイサイドスイッチ3のゲート駆動電圧が高くなり、オン抵抗をより小さくする。

【0074】

また、ハイサイド制御信号VHがローレベルからハイレベルに変化してから第1の期間T1の経過後に、出力端子5の出力電圧VLXがローレベルのままの場合、短絡検出信号VSがローレベルになる。NAND22は、ハイレベルを出力して、ハイサイドスイッチ3をオフさせる。ハイサイドスイッチ3に過電流が連続的に流れるのを防ぎ、破壊を防止する。

なお、第1の期間T1の間に、出力端子5と接地端子GNDとが短絡した場合でも、ハイサイドスイッチ3を流れる電流IHは、比較的高いオン抵抗Ron=Ron1により制限された値になる。

【0075】

図7は、第2の実施形態に係るスイッチング回路の他の構成を例示する回路図である。

図7に表したように、スイッチング回路1bは、ハイサイドスイッチ3、ローサイドスイッチ4、駆動回路7bを備える。スイッチング回路1bは、図5に表したスイッチング回路1aの駆動回路7aを駆動回路7bに置き換えた構成である。ローサイドスイッチ4のゲート(制御端子)18に第1の電圧V1及び第2の電圧V2が供給される点以外、ハイサイドスイッチ3、ローサイドスイッチ4については、スイッチング回路1aと同様である。

【0076】

駆動回路7bにおいては、ローサイド制御信号VLは、論理積回路(AND)19、INV9、10を介して、第1のトランジスタ11、第2のトランジスタ12に入力される。第1及び第2のトランジスタ11、12は、NMOSで構成され、内部電源線13と接地端子GNDとの間に直列に接続されている。

【0077】

第1のトランジスタ11のソースは、接地端子GNDに接続され、ドレインは、ローサイドスイッチ4のゲート(制御端子)18に接続されている。第1のトランジスタ11のゲートは、INV9の出力に接続されている。第2のトランジスタ12のソースは、制御端子18に接続され、ドレインは、内部電源線13に接続されている。第2のトランジスタ12のゲートは、INV10の出力に接続されている。

【0078】

また、第3のトランジスタ14は、第2のトランジスタ12と並列に接続されている。第3のトランジスタ14は、PMOSで構成され、ドレインは、制御端子18に接続され、ソースは内部電源線13に接続されている。第3のトランジスタ14のゲートは、NAND20の出力に接続されている。

【0079】

NAND20は、AND19の出力と、AND19の出力を遅延回路16で遅延させた信号VRと、の論理積の否定(信号VD)を生成する。なお、遅延回路16は、抵抗とコンデンサとで構成されている。信号VDは、AND19の出力の立ち下がりはそのままで、立ち上がりだけを遅延させ、さらに反転させた信号である。なお、遅延時間は、図2及び図4において説明したように、例えば、第1の期間T1に設定することができる。

【0080】

また、短絡検出回路17aは、出力端子5と電源端子2との短絡を検出する。図7においては、短絡検出回路17aは、D型フリップフロップ(DFF)で構成されている。DFFのクロック端子CKには、信号VDが入力され、DFFの入力端子Dには出力電圧VLXが入力される。DFFの出力端子Qに短絡検出信号VSが出力される。なお、短絡検出回路17aのDFFは、信号VDの立ち下がりエッジでクロックされる。

【0081】

AND19は、ローサイド制御信号VLと短絡検出信号VSの否定との論理積を生成する。なお、図8において説明するように、AND19は、短絡検出信号VSの否定で、ローサイド制御信号VLをマスクしている。また、短絡検出回路17aを構成するDFFは、初期状態として、短絡を検出しない状態、すなわちローレベルを出力する状態にリセットされる。なお、DFFを外部からリセットして初期状態に戻せるように、スイッチング回路1bにリセット端子を設けてもよい。

【0082】

内部電源線13には、接地端子GNDに対して、VI1の電圧が供給されている。AND19、INV9、10などの駆動回路7bの内部の各論理回路には、電源電圧としてVI1が供給されている。駆動回路7bの内部の各論理回路は、接地端子GNDを基準として動作する。

【0083】

上記のとおり、第1のトランジスタ11、第2のトランジスタ12及び第3のトランジスタ14は、制御端子18に接続されている。図8において説明するように、駆動回路7bは、ローサイド制御信号VL、出力電圧VLXに応じてローサイドスイッチ4のゲート電圧VGを制御する。また、駆動回路7bは、ハイサイド制御信号VHをINV21で反転してハイサイドスイッチ3のゲートに出力する。

【0084】

次にスイッチング回路1aの動作について説明する。

図8は、図7に表したスイッチング回路の主要な信号のタイミングチャートであり、(a)はハイサイド制御信号VH、(b)はローサイド制御信号VL、(c)は信号VR、(d)は信号VD、(e)はゲート電圧VG、(f)は出力電圧VLX、(g)は短絡検出信号VSを表す。

【0085】

図8においては、ローサイド制御信号VLとして、ハイレベルとローレベルとを周期的に繰り返す矩形波を入力した場合を例示している(図8(b))。また、ハイサイド制御信号VHは、ローサイド制御信号VLを反転した信号である(図8(a))。なお、ハイサイドスイッチ3とローサイドスイッチ4とが同時にオンになることを避けるために設けられるデッドタイムは、省略している。

【0086】

なお、図8(a)においては、ハイサイドスイッチ3がオンまたはオフに制御されていることを、それぞれON、OFFで表している。また、図8(e)においては、ローサイドスイッチ4がオンまたはオフに制御されていることを、それぞれON、OFFで表している。

【0087】

ハイサイド制御信号VHがハイレベル、ローサイド制御信号VLがローレベルのとき(図8(a)、(b))、ハイサイドスイッチ3はオン、ローサイドスイッチ4はオフである。このとき、出力電圧VLXはハイレベルである(図8(f))。また、信号VDは、ハイレベルである(図8(d))。

【0088】

ハイサイド制御信号VHがハイレベルからローレベルに変化すると(図8(a))、ローサイド制御信号VLはローレベルからハイレベルに変化する(図8(b))。ハイサイドスイッチ3はオフになる。

【0089】

信号VDは、ローサイド制御信号VLに対して第1の期間T1だけ遅延しているため、ハイレベルである(図8(d))。したがって、短絡検出信号VSは、出力電圧VLXによらずローレベルである(図8(g))。

【0090】

第1のトランジスタ11はオフ、第2のトランジスタ12はオン、第3のトランジスタ14はオフになる。第2のトランジスタ12はソースフォロワ出力のため、ローサイドスイッチ4のゲート電圧VGは、第2のトランジスタ12のしきい値電圧Vthだけ内部電源電圧VI1よりも低い第1の電圧V1になる(図8(e))。なお、図8(e)においては、接地電位の0Vを基準にして、ゲート電圧VGを表している。

【0091】

ここで、第1の電圧V1は、内部電源電圧VI1よりも低く設定されている。ローサイドスイッチ4のオン抵抗Ronは、内部電源電圧VI1を供給した場合よりも大きい値になっている。そのため、ローサイドスイッチ4の電流Ilは、オン抵抗Ronに制限される。

【0092】

遅延回路16の出力の信号VRは、時定数に従って上昇する(図8(c))。第1の期間T1において、信号VRは、NOR15の論理しきい電圧よりも高くなる。信号VDは、ローレベルに変化する(図8(d))。信号VDは、ローサイド制御信号VLの立上がりを第1の期間T1だけ遅延させ、さらに反転させた信号になる。

【0093】

ローサイド制御信号VLがハイレベルに変化してから第1の期間T1経過後、信号VDは、ローレベルになり(図8(d))、短絡検出回路17aのDFFがクロックされる。このとき、出力電圧VLXは、ローレベルである(図8(f)の一点鎖線Pで囲んだ部分)。そのため、短絡検出回路17aは、短絡を検出せず、短絡検出信号VSはローレベルのままである(図8(h))。

【0094】

第3のトランジスタ14は、オンになり、出力電圧VLXは、接地電位0Vまで低下する(図8(f))。

ローサイド制御信号VLがローレベル、ハイサイド制御信号VHがハイレベルに変化すると、ローサイドスイッチ4はオフ、ハイサイドスイッチ3はオンに切り替えられる。次サイクル以降、同様の動作が繰り返される。

【0095】

また、第1の期間T1の経過時に、出力電圧VLXがハイレベルの場合(図8(f)の一点破線Qで囲んだ部分)、短絡検出回路17aは、短絡を検出してハイレベルを出力する(図8(h))。

【0096】

AND19にハイレベルの短絡検出信号VSが入力され、AND19は、ローレベルを出力する。信号VDは、ハイレベルになる。第1のトランジスタ11はオン、第2のトランジスタ12はオフ、第3のトランジスタ14はオフになる。

したがって、ローサイドスイッチ4は、オフに切り替えられる。

【0097】

このように、駆動回路7bは、ハイサイド制御信号VHがハイレベル、ローサイド制御信号VLがローレベルのとき、ハイサイドスイッチ3をオン、ローサイドスイッチ4をオフに切り替える。

【0098】

また、ハイサイド制御信号VHがローレベル、ローサイド制御信号VLがハイレベルに変化したとき、ハイサイドスイッチ3をオフに切り替える。同時に、ローサイドスイッチ4に第1の期間T1の間は、第1の電圧V1を供給する。このとき、ローサイドスイッチ4の電流ILは、オン抵抗Ron=Ron1に制限される。

【0099】

そして、第1の期間経過後は、第1の電圧V1よりも高い第2の電圧V2として内部電源電圧VI1を供給してローサイドスイッチ4をオンに切り替える。このときのローサイドスイッチ4のオン抵抗Ron=Ron2は、第1の期間T1における値Ron1よりも小さくなっている。

【0100】

スイッチング回路1bにおいては、ローサイドスイッチ4がオフからオンに変化するときの第1の期間T1の間、ゲート駆動電圧を低くすることにより、ローサイドスイッチ4の電流を制限している。そのため、出力端子5が電源端子2と短絡した場合でも、ローサイドスイッチ4に過電流が流れるのを防ぎ、破壊を防止すことができる。

【0101】

また、ローサイド制御信号VLがローレベルからハイレベルに変化してから第1の期間T1の経過後に、出力端子5の出力電圧VLXがハイレベルのままの場合、短絡検出信号VSがハイレベルになる。AND19は、ローレベルを出力して、ローサイドスイッチ4をオフさせる。そのため、ローサイドスイッチ4に過電流が連続的に流れるのを防ぎ、破壊を防止する。

【0102】

なお、図1、図5、図7にそれぞれ表したスイッチング回路1、1a、1bにおいては、ハイサイドスイッチ3は、PMOS、ローサイドスイッチ4は、NMOSでそれぞれ構成されている。しかし、ハイサイドスイッチ3、ローサイドスイッチ4は、ともにNMOS、PMOSでもよい。

【0103】

また、図7に表したスイッチング回路1bにおいては、第1のトランジスタ11及び第2のトランジスタ12は、NMOS、第3のトランジスタ14は、PMOSでそれぞれ構成されている。しかし、第1のトランジスタ11及び第2のトランジスタ12は、PMOS、第3のトランジスタ14は、NMOSでそれぞれ構成されてもよい。

【0104】

また、図1、図5にそれぞれ表したスイッチング回路1、1aにおいては、内部電源線13に内部電源電圧−VI2を供給している。しかし、内部電源電圧−VI2を供給せず、内部電源線13は、接地端子GNDに接続されていてもよい。

また、図7に表したスイッチング回路1bにおいては、内部電源線13に内部電源電圧VI1を供給している。しかし、内部電源電圧VI1を供給せず、内部電源線13は、電源端子2に接続されていてもよい。

【0105】

(第3の実施形態)

図9は、第3の実施形態に係るDC−DCコンバータの構成を例示する回路図である。

図9に表したように、DC−DCコンバータ30においては、スイッチング回路1aに、スイッチング回路1aを制御する制御回路31が追加されている。スイッチング回路1aについては、図5に表したスイッチング回路1aと同様である。

【0106】

また、DC−DCコンバータ32においては、スイッチング回路1aの出力端子5に、インダクタ33の一端が接続されている。インダクタ33の他端と接地端子GNDとの間に、帰還抵抗34と35とが直列に接続されている。さらに、平滑コンデンサ36が、インダクタ33の他端と接地端子GNDとの間に接続されている。

帰還抵抗34、35は、インダクタ33の他端の出力電圧VOUTを分圧した電圧VFBを制御回路31に帰還する。

【0107】

制御回路31は、スイッチング回路1にハイサイド制御信号VH、ローサイド制御信号VLを出力する。制御回路31は、インダクタ33の他端の出力電圧VOUTに応じて、スイッチング回路1aを制御する。

【0108】

図10は、図9に表したDC−DCコンバータの主要な信号のタイミングチャートであり、(a)はハイサイド制御信号VH、(b)はローサイド制御信号VL、(c)はゲート電圧VG、(d)はスイッチング回路の出力電圧VLX、(e)はハイサイド電流IH、(f)はローサイド電流IL、(g)はインダクタ電流ILLを表す。

【0109】

なお、図10(b)においては、ローサイドスイッチ4がオンまたはオフに制御されていることを、それぞれON、OFFで表している。また、図10(c)においては、ハイサイドスイッチ3がオンまたはオフに制御されていることを、それぞれON、OFFで表している。また、ハイサイドスイッチ3とローサイドスイッチ4とが同時にオンになることを避けるために、デッドタイムTdが設けられている。

【0110】

ハイサイド制御信号VHがローレベル、ローサイド制御信号VLがハイレベルのとき(図10(a)、(b))、ハイサイドスイッチ3のゲート電圧VGは、ハイレベルである(図10(c))。ハイサイドスイッチ3はオフ、ローサイドスイッチ4はオンである。このとき、スイッチング回路1aの出力電圧(出力端子5の電圧)VLXは、ローレベルである(図10(d))。ローサイドスイッチ4には、インダクタ33の電流ILLと等しい回生電流ILが流れている(図10(f)、(g))。

【0111】

制御回路31がハイサイド制御信号VHをローレベルからハイレベル、ローサイド制御信号VLをハイレベルからローレベルに切り替えると(図2(a)、(b))、ローサイドスイッチ4はオフになる。ローサイドスイッチ4を流れていた回生電流ILは、寄生ダイオードDLを流れる。

【0112】

また、ゲート電圧VGは、第1の期間T1の間、第1の電圧V1になる(図10(c))。ここで、第1の電圧V1は、図2において説明したように、内部電源電圧VI2よりも低く設定されている。ハイサイドスイッチ3のオン抵抗Ron=Ron1は、内部電源電圧VI2を供給した場合よりも大きい値になっている。そのため、寄生ダイオードDLの逆方向電流はオン抵抗Ron=Ron1に制限され、ハイサイドスイッチ3の電流IHとして流れる(図10(e)の一点鎖線Rで囲んだ部分)。インダクタ33の電流ILLは増加していく(図10(g))。

【0113】

ハイサイド制御信号VHがハイレベルに変化してから第1の期間T1経過後、出力電圧VLXは、ハイレベルであるため(図10(d)の一点鎖線Pで囲んだ部分)、短絡検出回路17は、短絡を検出せず、ゲート電圧VGは、第2の電圧V2=−VI2になる(図10(c))。スイッチング回路1aの出力電圧VLXは、電源電圧VINまで上昇する(図10(d))。

【0114】

このとき、寄生ダイオードDLの逆方向回復時間Trrとほぼ等しい第1の期間T1を経過しているため、寄生ダイオードDLの逆方向回復電流はすでに減少している。ハイサイドスイッチ3の電流IH及びインダクタ33の電流ILLは、ほぼ直線的に上昇していく(図10(e)、(g))。

【0115】

制御回路31がハイサイド制御信号VHをローレベル、ローサイド制御信号VLをハイレベルに変化させと、ハイサイドスイッチ3はオフ、ローサイドスイッチ4はオンに切り替えられる。ローサイドスイッチ4には、インダクタ33の回生電流ILLが流れる(図10(f)、(g))。次サイクル以降、同様の動作が繰り返される。

【0116】

また、第1の期間T1の経過時に、出力電圧VLXがローレベルの場合(図10(d)の一点破線Qで囲んだ部分)、短絡検出回路17は、短絡を検出して、ゲート電圧VGは、ハイレベルになる(図10(c))。ハイサイドスイッチ3は、オフに切り替えられ、ハイサイドスイッチ3の電流IHは0になる(図10(e))。

【0117】

このように、DC−DCコンバータ32においては、ハイサイド制御信号VHがローレベル、ローサイド制御信号VLがハイレベルのとき、ハイサイドスイッチ3をオフ、ローサイドスイッチ4をオンに切り替える。このとき、ローサイドスイッチ4にインダクタ33の電流ILLに等しい回生電流ILが流れる。

【0118】

また、ハイサイド制御信号VHがハイレベル、ローサイド制御信号VLがローレベルに変化したとき、ローサイドスイッチ4をオフに切り替える。同時に、ハイサイドスイッチ3を第1の期間T1の間は、第1の電圧V1を供給してオンに切り替える。このとき、ハイサイドスイッチ3の電流IHは、オン抵抗Ron=Ron1に制限されたローサイドスイッチ4の寄生ダイオードDLの逆方向回復電流が流れることになる。

【0119】

そして、第1の期間経過後は、第1の電圧V1よりも高い第2の電圧V2として電源電圧VINを供給する。このときのハイサイドスイッチ3のオン抵抗Ron=Ron2は、第1の期間T1における値よりも小さくなっている。

【0120】

DC−DCコンバータ32においては、ハイサイドスイッチ3がオフからオンに変化するときの第1の期間T1の間ゲート駆動電圧を低くすることにより、寄生ダイオードDLの逆方向回復電流が抑制される。そして第1の期間T1の経過後、寄生ダイオードDLに流れる電流がなくなるころに、ハイサイドスイッチ3のゲート駆動電圧が高くなり、オン抵抗をより小さくする。

【0121】

また、ハイサイド制御信号VHがローレベルからハイレベルに変化してから第1の期間T1の経過後に、出力端子5の出力電圧VLXがローレベルのままの場合、短絡が検出され、ゲート駆動電圧にハイレベルを出力して、ハイサイドスイッチ3をオフさせる。ハイサイドスイッチ3に過電流が連続的に流れるのを防ぎ、破壊を防止する。

なお、第1の期間T1の間に、出力端子5と接地端子GNDとが短絡した場合でも、ハイサイドスイッチ3を流れる電流IHは、比較的高いオン抵抗により制限された値になる。

【0122】

図9においては、スイッチング回路1aを用いたDC−DCコンバータ32の構成を例示した。しかし、スイッチング回路1、1bを用いてDC−DCコンバータを構成することもできる。すなわち、図9に表したスイッチング回路1aを、図1に表したスイッチング回路1または図7に表したスイッチング回路1bに置き換えた構成である。

【0123】

図11は、図9に表したDC−DCコンバータの主要な信号の他のタイミングチャートであり、(a)はハイサイド制御信号VH、(b)はローサイド制御信号VL、(c)はゲート電圧VG、(d)はスイッチング回路の出力電圧VLX、(e)はハイサイド電流IH、(f)はローサイド電流IL、(g)はインダクタ電流ILLを表す。

【0124】

図11においては、スイッチング回路1bを用いたDC−DCコンバータの主要な信号を表している。

なお、図11(a)においては、ハイサイドスイッチ3がオンまたはオフに制御されていることを、それぞれON、OFFで表している。また、図11(c)においては、ローサイドスイッチ4がオンまたはオフに制御されていることを、それぞれON、OFFで表している。また、ハイサイドスイッチ3とローサイドスイッチ4とが同時にオンになることを避けるために、デッドタイムTdが設けられている。

【0125】

ハイサイド制御信号VHがローレベル、ローサイド制御信号VLがハイレベルのとき(図11(a)、(b))、ローサイドスイッチ4のゲート電圧VGは、ローレベルである(図11(c))。ハイサイドスイッチ3はオン、ローサイドスイッチ4はオフである。このとき、スイッチング回路1bの出力電圧(出力端子5の電圧)VLXは、ハイレベルである(図11(d))。ローサイドスイッチ4には、インダクタ33の電流ILLと等しい回生電流ILが流れている(図11(f)、(g))。

【0126】

制御回路31がハイサイド制御信号VHをハイレベルからローレベル、ローサイド制御信号VLをローレベルからハイレベルに切り替えると(図2(a)、(b))、ハイサイドスイッチ3はオフになる。

【0127】

ローサイドスイッチ4のゲート電圧VGは、第1の期間T1の間、第1の電圧V1になる(図11(c))。ここで、第1の電圧V1は、図8において説明したように、内部電源電圧VI1よりも低く設定されている。ローサイドスイッチ4のオン抵抗Ronは、内部電源電圧VI1を供給した場合よりも大きい値になっている。そのため、ローサイドスイッチ4の電流ILは、オン抵抗Ron=Ron1に制限される(図11(f))。インダクタ33の電流ILLは減少していく(図10(g))。

【0128】

ローサイド制御信号VLがハイレベルに変化してから第1の期間T1経過後、出力電圧VLXは、ローレベルであるため(図11(d)の一点鎖線Pで囲んだ部分)、短絡は検出されず、ゲート電圧VGは、第2の電圧V2=VI1になる(図11(c))。スイッチング回路1bの出力電圧VLXは、接地端子GNDの電位0Vまで低下する(図11(d))。

ローサイドスイッチ4の電流IL及びインダクタ33の電流ILLは、ほぼ直線的に減少していく(図11(f)、(g))。

【0129】

制御回路31がハイサイド制御信号VHをハイレベル、ローサイド制御信号VLをローレベルに変化させと、ハイサイドスイッチ3はオン、ローサイドスイッチ4はオフに切り替えられる。ハイサイドスイッチ3には、ローサイドスイッチ4の寄生ダイオードDLの逆方向回復電流Irrにより電流IHが流れる(図10(e))。次サイクル以降、同様の動作が繰り返される。

【0130】

また、第1の期間T1の経過時に、出力電圧VLXがハイレベルの場合(図11(d)の一点破線Qで囲んだ部分)、短絡が検出されてゲート電圧VGは、ローレベルになる(図11(c))。ローサイドスイッチ4は、オフに切り替えられ、ローサイドスイッチ4の電流ILは0になる(図10(f))。

【0131】

このように、スイッチング回路1bを用いた場合、ハイサイド制御信号VHがハイレベル、ローサイド制御信号VLがローレベルのとき、ハイサイドスイッチ3をオン、ローサイドスイッチ4をオフに切り替える。このとき、ハイサイドスイッチ3にローサイドスイッチ4の寄生ダイオードDLの逆方向回復電流Irrにより電流IHが流れる。

【0132】

また、ハイサイド制御信号VHがローレベル、ローサイド制御信号VLがハイレベルに変化したとき、ハイサイドスイッチ3をオフに切り替える。同時に、ローサイドスイッチ4に第1の期間T1の間は、第1の電圧V1を供給する。このとき、ローサイドスイッチ4の電流ILは、オン抵抗Ron=Ron1に制限される。

【0133】

そして、第1の期間経過後は、第1の電圧V1よりも高い第2の電圧V2として内部電源電圧VI1を供給してローサイドスイッチ4をオンに切り替える。このときのローサイドスイッチ4のオン抵抗Ron=Ron2は、第1の期間T1における値よりも小さくなっている。

【0134】

このように、ローサイドスイッチ4がオフからオンに変化するときの第1の期間T1の間ゲート駆動電圧を低くすることにより、ローサイドスイッチ4を流れる電流を制限することができる。そして第1の期間T1の経過後、ローサイドスイッチ4のゲート駆動電圧が高くなり、オン抵抗をより小さくする。

【0135】

そのため、ローサイド制御信号VLがローレベルからハイレベルに変化してから第1の期間T1の経過後に、出力端子5の出力電圧VLXがハイレベルの場合、短絡が検出され、ゲート駆動電圧にローレベルを出力して、ローサイドスイッチ4をオフさせる。ローサイドスイッチ4に過電流が連続的に流れるのを防ぎ、破壊を防止する。

なお、第1の期間T1の間に、出力端子5と電源端子2とが短絡した場合でも、ローサイドスイッチ4を流れる電流ILは、比較的高いオン抵抗により制限された値になる。

【0136】

なお、スイッチング回路1、1a、1bを用いたDC−DCコンバータについて説明した。しかし、スイッチング回路としては、図1に表したスイッチング回路1または図5に表したスイッチング回路1aにおいて、内部電源線13を接地端子GNDに接続してもよい。図7に表したスイッチング回路1bにおいて、内部電源線13を電源端子2に接続してもよい。

【0137】

本発明のいくつかの実施形態を説明したが、これらの実施形態は、例として提示したものであり、発明の範囲を限定することは意図していない。これら新規な実施形態は、その他の様々な形態で実施されることが可能であり、発明の要旨を逸脱しない範囲で、種々の省略、置き換え、変更を行うことができる。これら実施形態やその変形は、発明の範囲や要旨に含まれるとともに、特許請求の範囲に記載された発明とその均等の範囲に含まれる。

【符号の説明】

【0138】

1、1a、1b…スイッチング回路、 2…電源端子、 3…ローサイドスイッチ、 4…ローサイドスイッチ、 5…出力端子(接続点)、 6…誘導性負荷、 7、7a、7b…駆動回路、 8、9、10…否定回路(INV)、 11…第1のトランジスタ、 12…第2のトランジスタ、 13…内部電源線、 14…第3のトランジスタ、 16…遅延回路、 17、17a、17b…短絡検出回路、 18…制御端子、 20、22…論理積の否定回路(NAND)、 30、32…DC−DCコンバータ、 31…制御回路、 33…インダクタ、 34…帰還抵抗、 36…平滑コンデンサ

【技術分野】

【0001】

本発明の実施形態は、スイッチング回路及びDC−DCコンバータに関する。

【背景技術】

【0002】

スイッチング回路は、誘導性負荷の駆動する出力回路として広く用いられている。例えば、降圧型DC−DCコンバータにおいては、ハイサイドスイッチとローサイドスイッチとで構成されたスイッチング回路を用いて、インダクタを駆動する。

ハイサイドスイッチがオフのときは、ローサイドスイッチに電流が流れる。そして、ローサイドスイッチがオフし、ハイサイドスイッチがオンに変化したとき、ローサイドスイッチの寄生ダイオードの回復電流がハイサイドスイッチに流れる。そのため、スイッチングの高速化や低オン抵抗な素子を使用して効率を向上させようとすると、回復電流も大きくなり、スイッチングノイズの発生や動作効率の低下要因となる。また、低オン抵抗な素子は、出力端子の短絡時に破壊の恐れもある。

【先行技術文献】

【特許文献】

【0003】

【特許文献1】特開2009−148043号公報

【発明の概要】

【発明が解決しようとする課題】

【0004】

本発明の実施形態は、スイッチングノイズの低減と動作効率の向上を図り、併せてスイッチ素子の破壊を防止したスイッチング回路及びDC−DCコンバータを提供する。

【課題を解決するための手段】

【0005】

実施形態によれば、ハイサイドスイッチと、ローサイドスイッチと、駆動回路と、を備えたスイッチング回路が提供される。前記ハイサイドスイッチは、電源端子と出力端子との間に接続されている。前記ローサイドスイッチは、前記出力端子と接地端子との間に接続されている。前記駆動回路は、制御信号に応じて、前記ハイサイドスイッチ及び前記ローサイドスイッチのいずれか一方のスイッチをオフし、第1の期間の間第1の電圧を他方のスイッチの制御端子に供給して前記他方のスイッチをオンさせ、前記第1の期間経過後において前記他方のスイッチの前記制御端子に前記第1の電圧よりも高い第2の電圧を供給することを特徴とする。

【図面の簡単な説明】

【0006】

【図1】第1の実施形態に係るスイッチング回路の構成を例示する回路図。

【図2】図1に表したスイッチング回路の主要な信号のタイミングチャートであり、(a)はハイサイド制御信号VH、(b)はローサイド制御信号VL、(c)は信号VR、(d)は信号VD、(e)はゲート電圧VG、(f)は出力電圧VLX、(g)はハイサイド電流IHを表す。

【図3】ゲート・ソース間電圧Vgsとオン抵抗Ronとの関係を表す特性図。

【図4】ハイサイドスイッチの状態を表す特性図であり、(a)はオン抵抗Ron、(b)はハイサイド電流IHを表す。

【図5】第2の実施形態に係るスイッチング回路の構成を例示する回路図。

【図6】図5に表したスイッチング回路の主要な信号のタイミングチャートであり、(a)はハイサイド制御信号VH、(b)はローサイド制御信号VL、(c)は信号VR、(d)は信号VD、(e)はゲート電圧VG、(f)は出力電圧VLX、(g)は短絡検出信号VS、(h)はハイサイド電流IHを表す。

【図7】第2の実施形態に係るスイッチング回路の他の構成を例示する回路図。

【図8】図7に表したスイッチング回路の主要な信号のタイミングチャートであり、(a)はハイサイド制御信号VH、(b)はローサイド制御信号VL、(c)は信号VR、(d)は信号VD、(e)はゲート電圧VG、(f)は出力電圧VLX、(g)は短絡検出信号VSを表す。

【図9】第3の実施形態に係るDC−DCコンバータの構成を例示する回路図。

【図10】図9に表したDC−DCコンバータの主要な信号のタイミングチャートであり、(a)はハイサイド制御信号VH、(b)はローサイド制御信号VL、(c)はゲート電圧VG、(d)はスイッチング回路の出力電圧VLX、(e)はハイサイド電流IH、(f)はローサイド電流IL、(g)はインダクタ電流ILLを表す。

【図11】図9に表したDC−DCコンバータの主要な信号の他のタイミングチャートであり、(a)はハイサイド制御信号VH、(b)はローサイド制御信号VL、(c)はゲート電圧VG、(d)はスイッチング回路の出力電圧VLX、(e)はハイサイド電流IH、(f)はローサイド電流IL、(g)はインダクタ電流ILLを表す。

【発明を実施するための形態】

【0007】

以下、本発明の実施形態について図面を参照して詳細に説明する。なお、本願明細書と各図において、既出の図に関して前述したものと同様の要素には同一の符号を付して詳細な説明は適宜省略する。

【0008】

(第1の実施形態)

図1は、第1の実施形態に係るスイッチング回路の構成を例示する回路図である。

スイッチング回路1においては、電源端子2と出力端子との間にハイサイドスイッチ3が接続されている。出力端子5と接地端子GNDとの間にローサイドスイッチ4が接続されている。ハイサイドスイッチ3とローサイドスイッチ4とは、直列に接続されている。出力端子5には、誘導性負荷6が接続されている。

【0009】

ハイサイドスイッチ3とローサイドスイッチ4とを制御する信号は、駆動回路7で生成される。駆動回路7は、外部から入力されたハイサイド制御信号VH及びローサイド制御信号VLに応じて、ハイサイドスイッチ3及びローサイドスイッチ4をそれぞれオンまたはオフする。

【0010】

ハイサイドスイッチ3がオンでローサイドスイッチがオフのとき、出力端子5は、電源端子2と電気的に接続される。このとき、出力端子5の電圧、すなわち出力電圧VLXは、電源端子2に供給される電源電圧VINになる。そして、誘導性負荷6に電流が流れ、電源端子2を介して電源からエネルギーが供給される。

【0011】

ハイサイドスイッチ3がオフでローサイドスイッチがオンのとき、出力端子5は、接地端子GNDと電気的に接続される。このとき、出力電圧VLXは、0Vになる。誘導性負荷6には、回生電流が流れ、エネルギーが減少していく。

【0012】

スイッチング回路1は、ハイサイド制御信号VH、ローサイド制御信号VLに応じて、誘導性負荷6を駆動する。なお、図1においては、誘導性負荷6として、インダクタを例示しているが、例えば、DC−DCコンバータのインダクタや、モータなどのアクチュエータでもよい。

【0013】

次に各部について説明する。

ハイサイドスイッチ3は、PチャンネルMOSFET(以下、PMOS)であり、ソースは、電源端子2に接続され、ドレインは、出力端子5に接続されている。また、ハイサイドスイッチ3のゲート(制御端子)18は、駆動回路7に接続される。ハイサイドスイッチ3には、図示しない寄生ダイオードが含まれる。

【0014】

ローサイドスイッチ4は、NチャンネルMOSFET(以下、NMOS)であり、ソースは、接地端子GNDに接続され、ドレインは、出力端子5に接続されている。また、ローサイドスイッチ4のゲートは、駆動回路7に接続される。ローサイドスイッチ4には、寄生ダイオードDLが含まれる。

【0015】

駆動回路7においては、ハイサイド制御信号VHは、否定回路(INV)8、9、10を介して、第1のトランジスタ11、第2のトランジスタ12に入力される。第1及び第2のトランジスタ11、12は、PMOSで構成され、電源端子2と内部電源線13との間に直列に接続されている。

【0016】

第1のトランジスタ11のソースは、電源端子2に接続され、ドレインは、制御端子18に接続されている。第1のトランジスタ11のゲートは、INV9の出力に接続されている。第2のトランジスタ12のソースは、制御端子18に接続され、ドレインは、内部電源線13に接続されている。第2のトランジスタ12のゲートは、INV10の出力に接続されている。

【0017】

また、第3のトランジスタ14は、第2のトランジスタ12と並列に接続されている。第3のトランジスタ14は、NMOSで構成され、ドレインは、制御端子18に接続され、ソースは内部電源線13に接続されている。第3のトランジスタ14のゲートは、論理和の否定回路(NOR)15の出力に接続されている。

【0018】

NOR15は、INV8の出力と、INV8の出力を遅延回路16で遅延させた信号VRと、の論理和(信号VD)を生成する。なお、遅延回路16は、抵抗とコンデンサとで構成されている。信号VDは、INV8の出力の立ち上がりはそのままで、立ち下がりだけを遅延させ、さらに反転させた信号である。なお、遅延時間は、図2及び図4において説明するように、ローサイドスイッチ4の寄生ダイオードDLの逆方向回復時間Trrとほぼ等しい第1の期間T1に設定される。

【0019】

内部電源線13には、電源端子2に対して、−VI2の電圧が供給されている。INV8、9、10などの駆動回路7の内部の各論理回路には、内部電源電圧としてVI2が供給されている。駆動回路7の内部の各論理回路は、内部電源線13の電位を基準として動作する。

【0020】

上記のとおり、第1のトランジスタ11、第2のトランジスタ12及び第3のトランジスタ14は、制御端子18に接続されている。図2において説明するように、駆動回路7は、ハイサイド制御信号VH、出力電圧VLXに応じて、ハイサイドスイッチ3のゲート電圧(制御端子の電圧)VGを制御する。また、駆動回路7は、ローサイド制御信号VLをそのままの論理でローサイドスイッチ4のゲートに出力する。

【0021】

次にスイッチング回路1の動作について説明する。

図2は、図1に表したスイッチング回路の主要な信号のタイミングチャートであり、(a)はハイサイド制御信号VH、(b)はローサイド制御信号VL、(c)は信号VR、(d)は信号VD、(e)はゲート電圧VG、(f)は出力電圧VLX、(g)はハイサイド電流IHを表す。

【0022】

なお、図2(b)においては、ローサイドスイッチ4がオンまたはオフに制御されていることを、それぞれON、OFFで表している。また、図2(e)においては、ハイサイドスイッチ3がオンまたはオフに制御されていることを、それぞれON、OFFで表している。

【0023】

図2においては、ハイサイド制御信号VHとして、ハイレベルとローレベルとを周期的に繰り返す矩形波を入力した場合を例示している(図2(a))。また、ローサイド制御信号VLは、ハイサイド制御信号VHを反転した信号である(図2(b))。なお、ハイサイドスイッチ3とローサイドスイッチ4とが同時にオンになることを避けるために設けられるデッドタイムは、省略している。

【0024】

ハイサイド制御信号VHがローレベル、ローサイド制御信号VLがハイレベルのとき(図2(a)、(b))、ハイサイドスイッチ3はオフ、ローサイドスイッチ4はオンである。このとき、出力電圧VLXはローレベルである(図2(f))。また、信号VDは、ローレベルである(図2(d))。また、ローサイドスイッチ4には、誘導性負荷6の回生電流が流れている。

【0025】

ハイサイド制御信号VHがローレベルからハイレベルに変化すると(図2(a))、ローサイド制御信号VLはハイレベルからローレベルに変化する(図2(b))。ローサイドスイッチ4はオフになり、ローサイドスイッチ4を流れていた回生電流は、寄生ダイオードDLを流れる。

信号VDは、ハイサイド制御信号VHに対して第1の期間T1だけ遅延しているため、ローレベルである(図2(d))。

【0026】

第1のトランジスタ11はオフ、第2のトランジスタ12はオン、第3のトランジスタ14はオフになる。第2のトランジスタ12はソースフォロワ出力のため、ハイサイドスイッチ3のゲート電圧VGは、内部電源線13の電位よりも第2のトランジスタ12のしきい値電圧Vthだけ高い第1の電圧V1になる(図2(e))。なお、図2(e)においては、電源端子2の電位VINを基準にして、ゲート電圧VGを表している。

【0027】

ここで、第1の電圧V1は、内部電源電圧VI2よりも低く設定されている。ハイサイドスイッチ3のオン抵抗Ronは、内部電源電圧VI2を供給した場合よりも大きい値になっている。そのため、寄生ダイオードDLの逆方向電流はオン抵抗Ronに制限され、ハイサイドスイッチ3の電流IHとして流れる(図2(g)の一点鎖線Rで囲んだ部分)。

【0028】

遅延回路16の出力の信号VRは、時定数に従って低下する(図2(c))。第1の期間T1において、信号VRは、NOR15の論理しきい電圧よりも低下する。信号VDは、ハイレベルに変化する(図2(d))。信号VDは、ハイサイド制御信号VHの立上がりを第1の期間T1だけ遅延させた信号になる。

【0029】

ハイサイド制御信号VHがハイレベルに変化してから第1の期間T1経過後、信号VDは、ハイレベルになる。このとき、出力電圧VLXは、ハイレベルである(図2(f)の一点鎖線Pで囲んだ部分)。

【0030】

第3のトランジスタ14は、オンになり、ゲート電圧VGは、第2の電圧V2=−VI2になる。出力電圧VLXは、電源電圧VINまで上昇する(図2(f))。このとき、寄生ダイオードDLの逆方向回復時間Trrとほぼ等しい第1の期間T1を経過しているため、寄生ダイオードDLの逆方向回復電流はすでに減少している。ハイサイドスイッチ3の電流IHは、ほぼ直線的に上昇していく(図2(g))。

【0031】

ハイサイド制御信号VHがローレベル、ローサイド制御信号VLがハイレベルに変化すると、ハイサイドスイッチ3はオフ、ローサイドスイッチ4はオンに切り替えられる。次サイクル以降、同様の動作が繰り返される。

【0032】

このように、駆動回路7は、ハイサイド制御信号VHがローレベル、ローサイド制御信号VLがハイレベルのとき、ハイサイドスイッチ3をオフ、ローサイドスイッチ4をオンに切り替える。このとき、ローサイドスイッチ4に誘導性負荷6の回生電流が流れる。

【0033】

また、ハイサイド制御信号VHがハイレベル、ローサイド制御信号VLがローレベルに変化したとき、ローサイドスイッチ4をオフに切り替える。同時に、ハイサイドスイッチ3の制御端子に第1の期間T1の間は、第1の電圧V1を供給する。このとき、ハイサイドスイッチ3の電流IHは、オン抵抗Ronに制限されたローサイドスイッチ4の寄生ダイオードDLの逆方向回復電流が流れることになる。

【0034】

そして、第1の期間経過後は、第1の電圧V1よりも高い第2の電圧V2として電源電圧VINを供給してハイサイドスイッチ3をオンに切り替える。このときのハイサイドスイッチ3のオン抵抗は、第1の期間T1における値よりも小さくなっている。

【0035】

スイッチング回路1においては、ハイサイドスイッチ3がオフからオンに変化するときの第1の期間T1の間ゲート駆動電圧を低くすることにより、寄生ダイオードDLの逆方向回復電流が抑制される。そして第1の期間T1の経過後、寄生ダイオードDLに流れる電流がなくなるころに、ハイサイドスイッチ3のゲート駆動電圧が高くなり、オン抵抗をより小さくする。

【0036】

なお、第1の期間T1の間に、出力端子5と接地端子GNDとが短絡した場合でも、ハイサイドスイッチ3を流れる電流IHは、比較的高いオン抵抗により制限された値になる。

【0037】

図3は、ゲート・ソース間電圧Vgsとオン抵抗Ronとの関係を表す特性図である。

図3においては、ハイサイドスイッチ3のゲート・ソース間電圧Vgsを横軸、オン抵抗Ronを縦軸にとり、オン抵抗Ronのゲート・ソース間電圧Vgs依存性を表している。なお、各電圧は絶対値を表している。

【0038】

しきい値電圧Vth以上のゲート・ソース間電圧Vgsに対して、オン抵抗Ronは単調に低下する。ゲート電圧VGは、電源端子2の電位VINを基準にしているため、ゲート電圧VGは、ハイサイドスイッチ3のゲート・ソース間電圧Vgsと等しい。ゲート電圧VGが第1の電圧V1のとき、オン抵抗はRon1である。ゲート電圧が第2の電圧V2(=VI2)のとき、オン抵抗はRon2である。ここで、|Vgs1|<|Vgs2|、Ron1>Ron2になっている。

【0039】

図4は、ハイサイドスイッチの状態を表す特性図であり、(a)はオン抵抗Ron、(b)はハイサイド電流IHを表す。

図4(a)においては、横軸に時間t、縦軸にオン抵抗Ronをとり、ハイサイドスイッチ3のオン抵抗Ronの時間変化を表している。図4(b)においては、横軸に時間t、縦軸にハイサイドスイッチ3の電流IHをとり、電流IHの時間変化を表している。

【0040】

時間t=0でハイサイド制御信号VHがローレベルからハイレベルに変化した場合において、第1の期間T1の間、オン抵抗Ronは、Ron1になる。第1の期間T1経過後、オン抵抗Ronは、Ron1よりも小さいRon2になる。

【0041】

ハイサイドスイッチ3の電流IHは、第1の期間T1の間、比較的大きいオン抵抗Ron1のために、オン抵抗Ron2の場合に流れる寄生ダイオードDLの逆方向回復電流Irrよりも小さい値に制限されている。

したがって、スイッチングノイズが低減され、動作効率が向上する。

【0042】

なお、図4(b)においては、第1の期間T1が寄生ダイオードDLの逆方向回復時間Trrと等しい場合の電流IHを例示している。しかし、第1の期間T1は、寄生ダイオードDLの逆方向回復時間Trrと等しくなくてもよい。

【0043】

例えば、第1の期間T1は、寄生ダイオードDLの逆方向回復時間Trr以下に設定してもよい。この場合、第1の期間T1の間は、比較的大きいオン抵抗Ron1により電流IHは制限され、第1の期間T1経過後も逆方向回復時間Trrまでは、寄生ダイオードDLの逆方向回復電流Irrが流れることになる。

【0044】

しかし、第1の期間T1を設定せず、時間t=0でオン抵抗をRon2の小さい値に設定した場合と比較すると、流れる逆方向回復電流Irrは小さくなる。そのため、第1の期間T1を設定しない場合と比較して、スイッチングノイズが低減され、動作効率が向上する。また、第1の期間T1を逆方向回復時間Trrと等しく設定した場合と比較して、オン抵抗の小さい期間が長くなるため、動作効率が向上する。

【0045】

また、第1の期間T1は、寄生ダイオードDLの逆方向回復時間Trrよりも大きく設定してもよい。この場合、逆方向回復時間Trr経過後も第1の期間T1が経過するまでの間は、比較的大きいオン抵抗Ron1に保たれることになる。しかし、第1の期間T1が、ハイサイド制御信号VHがハイレベルである期間、すなわちハイサイドスイッチ3がオンしている期間と比較して十分短ければ、動作効率の低下はわずかである。

【0046】

なお、図1に表したスイッチング回路1においては、第1のトランジスタ11及び第2のトランジスタ12は、PMOS、第3のトランジスタ14は、NMOSでそれぞれ構成されている。しかし、第1のトランジスタ11及び第2のトランジスタ12は、NMOS、第3のトランジスタ14は、PMOSでそれぞれ構成されてもよい。

【0047】

(第2の実施形態)

図5は、第2の実施形態に係るスイッチング回路の構成を例示する回路図である。

スイッチング回路1aにおいては、ハイサイドスイッチ3、ローサイドスイッチ4、駆動回路7aを備える。スイッチング回路1aは、図1に表したスイッチング回路1の駆動回路7を駆動回路7aに置き換えた構成である。また、駆動回路7aは、図1に表した駆動回路7のINV8を論理積の否定回路(NAND)22に置き換え、さらに短絡検出回路17を追加した構成である。これ以外については、図1に表したスイッチング回路1と同様である。

【0048】

駆動回路7aにおいては、ハイサイド制御信号VHは、NAND22、INV9、10を介して、第1のトランジスタ11、第2のトランジスタ12に入力される。第1及び第2のトランジスタ11、12は、PMOSで構成され、電源端子2と内部電源線13との間に直列に接続されている。

【0049】

第1のトランジスタ11のソースは、電源端子2に接続され、ドレインは、制御端子18に接続されている。第1のトランジスタ11のゲートは、INV9の出力に接続されている。第2のトランジスタ12のソースは、制御端子18に接続され、ドレインは、内部電源線13に接続されている。第2のトランジスタ12のゲートは、INV10の出力に接続されている。

【0050】

また、第3のトランジスタ14は、第2のトランジスタ12と並列に接続されている。第3のトランジスタ14は、NMOSで構成され、ドレインは、制御端子18に接続され、ソースは内部電源線13に接続されている。第3のトランジスタ14のゲートは、NOR15の出力に接続されている。

【0051】

NOR15は、NAND22の出力と、NAND22の出力を遅延回路16で遅延させた信号VRと、の論理和(信号VD)を生成する。なお、遅延回路16は、抵抗とコンデンサとで構成されている。信号VDは、NAND8の出力の立ち上がりはそのままで、立ち下がりだけを遅延させ、さらに反転させた信号である。なお、遅延時間は、ローサイドスイッチ4の寄生ダイオードDLの逆方向回復時間Trrとほぼ等しい第1の期間T1に設定される。

【0052】

また、短絡検出回路17は、出力端子5と接地端子GNDとの短絡を検出する。図5においては、短絡検出回路17は、D型フリップフロップ(DFF)で構成されている。DFFのクロック端子CKには、信号VDが入力され、DFFの入力端子Dには出力電圧VLXが入力される。DFFの出力端子Qに短絡検出信号VSが出力される。なお、短絡検出回路17のDFFは、信号VDの立ち上がりエッジでクロックされる。

【0053】

NAND22は、ハイサイド制御信号VHと短絡検出信号VSとの論理積の否定を生成する。なお、図6において説明するように、NAND22は、短絡検出信号VSで、ハイサイド制御信号VHをマスクしている。また、短絡検出回路17を構成するDFFは、初期状態として、短絡を検出しない状態、すなわちハイレベルを出力する状態にセットされる。なお、DFFを外部からセットして初期状態に戻せるように、スイッチング回路1aにセット端子を設けてもよい。

【0054】

内部電源線13には、電源端子2に対して、−VI2の電圧が供給されている。NAND22、INV9、10などの駆動回路7の内部の各論理回路には、内部電源電圧としてVI2が供給されている。駆動回路7aの内部の各論理回路は、内部電源線13の電位を基準として動作する。

【0055】

上記のとおり、第1のトランジスタ11、第2のトランジスタ12及び第3のトランジスタ14は、制御端子18に接続されている。駆動回路7aは、ハイサイド制御信号VH、出力電圧VLXに応じて、ハイサイドスイッチ3のゲート電圧(制御端子の電圧)VGを制御する。また、駆動回路7aは、ローサイド制御信号VLをそのままの論理でローサイドスイッチ4のゲートに出力する。

【0056】

次にスイッチング回路1の動作について説明する。

図6は、図5に表したスイッチング回路の主要な信号のタイミングチャートであり、(a)はハイサイド制御信号VH、(b)はローサイド制御信号VL、(c)は信号VR、(d)は信号VD、(e)はゲート電圧VG、(f)は出力電圧VLX、(g)は短絡検出信号VS、(h)はハイサイド電流IHを表す。

【0057】

なお、図6(b)においては、ローサイドスイッチ4がオンまたはオフに制御されていることを、それぞれON、OFFで表している。また、図6(e)においては、ハイサイドスイッチ3がオンまたはオフに制御されていることを、それぞれON、OFFで表している。

【0058】

図6においては、ハイサイド制御信号VHとして、ハイレベルとローレベルとを周期的に繰り返す矩形波を入力した場合を例示している(図6(a))。また、ローサイド制御信号VLは、ハイサイド制御信号VHを反転した信号である(図6(b))。なお、ハイサイドスイッチ3とローサイドスイッチ4とが同時にオンになることを避けるために設けられるデッドタイムは、省略している。

【0059】

ハイサイド制御信号VHがローレベル、ローサイド制御信号VLがハイレベルのとき(図6(a)、(b))、ハイサイドスイッチ3はオフ、ローサイドスイッチ4はオンである。このとき、出力電圧VLXはローレベルである(図6(f))。また、信号VDは、ローレベルである(図6(d))。また、ローサイドスイッチ4には、誘導性負荷6の回生電流が流れている。

【0060】

ローサイド制御信号VLがハイレベルからローレベルに変化すると(図6(b))、ハイサイド制御信号VHはローレベルからハイレベルに変化する(図6(a))。ローサイドスイッチ4はオフになり、ローサイドスイッチ4を流れていた回生電流は、寄生ダイオードDLを流れる。

【0061】

信号VDは、ハイサイド制御信号VHに対して第1の期間T1だけ遅延しているため、ローレベルである(図6(d))。従って、短絡検出信号VSは、出力電圧VLXによらずハイレベルになる(図6(g))。

【0062】

第1のトランジスタ11はオフ、第2のトランジスタ12はオン、第3のトランジスタ14はオフになる。第2のトランジスタ12はソースフォロワ出力のため、ハイサイドスイッチ3のゲート電圧VGは、内部電源線13の電位よりも第2のトランジスタ12のしきい値電圧Vthだけ高い第1の電圧V1になる(図6(e))。なお、図6(e)においては、電源端子2の電位VINを基準にして、ゲート電圧VGを表している。

【0063】

ここで、第1の電圧V1は、内部電源電圧VI2よりも低く設定されている。ハイサイドスイッチ3のオン抵抗Ronは、内部電源電圧VI2を供給した場合よりも大きい値になっている。そのため、寄生ダイオードDLの逆方向電流はオン抵抗Ronに制限され、ハイサイドスイッチ3の電流IHとして流れる(図6(h)の一点鎖線Rで囲んだ部分)。

【0064】

遅延回路16の出力の信号VRは、時定数に従って低下する(図6(c))。第1の期間T1において、信号VRは、NOR15の論理しきい電圧よりも低下する。信号VDは、ハイレベルに変化する(図6(d))。信号VDは、ハイサイド制御信号VHの立上がりを第1の期間T1だけ遅延させた信号になる。

【0065】

ハイサイド制御信号VHがローレベルに変化してから第1の期間T1経過後、信号VDは、ハイレベルになり(図6(d))、短絡検出回路17のDFFがクロックされる。このとき、出力電圧VLXは、ハイレベルである(図6(f)の一点鎖線Pで囲んだ部分)。そのため、短絡検出回路17は、短絡を検出せず、短絡検出信号VSはハイレベルのままである(図6(g))。

【0066】

第3のトランジスタ14は、オンになり、ゲート電圧VGは、第2の電圧V2=−VI2になる。出力電圧VLXは、電源電圧VINまで上昇する(図6(f))。このとき、寄生ダイオードDLの逆方向回復時間Trrとほぼ等しい第1の期間T1を経過しているため、寄生ダイオードDLの逆方向回復電流はすでに減少している。ハイサイドスイッチ3の電流IHは、ほぼ直線的に上昇していく(図6(h))。

【0067】

ハイサイド制御信号VHがローレベル、ローサイド制御信号VLがハイレベルに変化すると、ハイサイドスイッチ3はオフ、ローサイドスイッチ4はオンに切り替えられる。次サイクル以降、同様の動作が繰り返される。

【0068】

また、第1の期間T1の経過時に、出力電圧VLXがローレベルの場合(図6(f)の一点破線Qで囲んだ部分)、短絡検出回路17は、短絡を検出し短絡検出信号VSとしてローレベルを出力する(図6(g))。

【0069】

NAND22にローレベルの短絡検出信号VSが入力され、NAND22は、ハイレベルを出力する。信号VDは、ローレベルになる。第1のトランジスタ11はオン、第2のトランジスタ12はオフ、第3のトランジスタ14はオフになる。

したがって、ハイサイドスイッチ3は、オフに切り替えられ、ハイサイドスイッチ3の電流IHは0になる(図6(h))。

【0070】

このように、駆動回路7aは、ハイサイド制御信号VHがローレベル、ローサイド制御信号VLがハイレベルのとき、ハイサイドスイッチ3をオフ、ローサイドスイッチ4をオンに切り替える。このとき、ローサイドスイッチ4に誘導性負荷6の回生電流が流れる。

【0071】

また、ハイサイド制御信号VHがハイレベル、ローサイド制御信号VLがローレベルに変化したとき、ローサイドスイッチ4をオフに切り替える。同時に、ハイサイドスイッチ3に第1の期間T1の間は、第1の電圧V1を供給する。このとき、ハイサイドスイッチ3の電流IHは、オン抵抗Ron=Ron1に制限されたローサイドスイッチ4の寄生ダイオードDLの逆方向回復電流が流れることになる。

【0072】

そして、第1の期間経過後は、第1の電圧V1よりも高い第2の電圧V2として電源電圧VINを供給してハイサイドスイッチ3をオンに切り替える。このときのハイサイドスイッチ3のオン抵抗Ron=Ron2は、第1の期間T1における値よりも小さくなっている。

【0073】

スイッチング回路1aにおいては、ハイサイドスイッチ3がオフからオンに変化するときの第1の期間T1の間ゲート駆動電圧を低くすることにより、寄生ダイオードDLの逆方向回復電流が抑制される。そして第1の期間T1の経過後、寄生ダイオードDLに流れる電流がなくなるころに、ハイサイドスイッチ3のゲート駆動電圧が高くなり、オン抵抗をより小さくする。

【0074】

また、ハイサイド制御信号VHがローレベルからハイレベルに変化してから第1の期間T1の経過後に、出力端子5の出力電圧VLXがローレベルのままの場合、短絡検出信号VSがローレベルになる。NAND22は、ハイレベルを出力して、ハイサイドスイッチ3をオフさせる。ハイサイドスイッチ3に過電流が連続的に流れるのを防ぎ、破壊を防止する。

なお、第1の期間T1の間に、出力端子5と接地端子GNDとが短絡した場合でも、ハイサイドスイッチ3を流れる電流IHは、比較的高いオン抵抗Ron=Ron1により制限された値になる。

【0075】

図7は、第2の実施形態に係るスイッチング回路の他の構成を例示する回路図である。

図7に表したように、スイッチング回路1bは、ハイサイドスイッチ3、ローサイドスイッチ4、駆動回路7bを備える。スイッチング回路1bは、図5に表したスイッチング回路1aの駆動回路7aを駆動回路7bに置き換えた構成である。ローサイドスイッチ4のゲート(制御端子)18に第1の電圧V1及び第2の電圧V2が供給される点以外、ハイサイドスイッチ3、ローサイドスイッチ4については、スイッチング回路1aと同様である。

【0076】

駆動回路7bにおいては、ローサイド制御信号VLは、論理積回路(AND)19、INV9、10を介して、第1のトランジスタ11、第2のトランジスタ12に入力される。第1及び第2のトランジスタ11、12は、NMOSで構成され、内部電源線13と接地端子GNDとの間に直列に接続されている。

【0077】

第1のトランジスタ11のソースは、接地端子GNDに接続され、ドレインは、ローサイドスイッチ4のゲート(制御端子)18に接続されている。第1のトランジスタ11のゲートは、INV9の出力に接続されている。第2のトランジスタ12のソースは、制御端子18に接続され、ドレインは、内部電源線13に接続されている。第2のトランジスタ12のゲートは、INV10の出力に接続されている。

【0078】

また、第3のトランジスタ14は、第2のトランジスタ12と並列に接続されている。第3のトランジスタ14は、PMOSで構成され、ドレインは、制御端子18に接続され、ソースは内部電源線13に接続されている。第3のトランジスタ14のゲートは、NAND20の出力に接続されている。

【0079】

NAND20は、AND19の出力と、AND19の出力を遅延回路16で遅延させた信号VRと、の論理積の否定(信号VD)を生成する。なお、遅延回路16は、抵抗とコンデンサとで構成されている。信号VDは、AND19の出力の立ち下がりはそのままで、立ち上がりだけを遅延させ、さらに反転させた信号である。なお、遅延時間は、図2及び図4において説明したように、例えば、第1の期間T1に設定することができる。

【0080】

また、短絡検出回路17aは、出力端子5と電源端子2との短絡を検出する。図7においては、短絡検出回路17aは、D型フリップフロップ(DFF)で構成されている。DFFのクロック端子CKには、信号VDが入力され、DFFの入力端子Dには出力電圧VLXが入力される。DFFの出力端子Qに短絡検出信号VSが出力される。なお、短絡検出回路17aのDFFは、信号VDの立ち下がりエッジでクロックされる。

【0081】

AND19は、ローサイド制御信号VLと短絡検出信号VSの否定との論理積を生成する。なお、図8において説明するように、AND19は、短絡検出信号VSの否定で、ローサイド制御信号VLをマスクしている。また、短絡検出回路17aを構成するDFFは、初期状態として、短絡を検出しない状態、すなわちローレベルを出力する状態にリセットされる。なお、DFFを外部からリセットして初期状態に戻せるように、スイッチング回路1bにリセット端子を設けてもよい。

【0082】

内部電源線13には、接地端子GNDに対して、VI1の電圧が供給されている。AND19、INV9、10などの駆動回路7bの内部の各論理回路には、電源電圧としてVI1が供給されている。駆動回路7bの内部の各論理回路は、接地端子GNDを基準として動作する。

【0083】

上記のとおり、第1のトランジスタ11、第2のトランジスタ12及び第3のトランジスタ14は、制御端子18に接続されている。図8において説明するように、駆動回路7bは、ローサイド制御信号VL、出力電圧VLXに応じてローサイドスイッチ4のゲート電圧VGを制御する。また、駆動回路7bは、ハイサイド制御信号VHをINV21で反転してハイサイドスイッチ3のゲートに出力する。

【0084】

次にスイッチング回路1aの動作について説明する。

図8は、図7に表したスイッチング回路の主要な信号のタイミングチャートであり、(a)はハイサイド制御信号VH、(b)はローサイド制御信号VL、(c)は信号VR、(d)は信号VD、(e)はゲート電圧VG、(f)は出力電圧VLX、(g)は短絡検出信号VSを表す。

【0085】

図8においては、ローサイド制御信号VLとして、ハイレベルとローレベルとを周期的に繰り返す矩形波を入力した場合を例示している(図8(b))。また、ハイサイド制御信号VHは、ローサイド制御信号VLを反転した信号である(図8(a))。なお、ハイサイドスイッチ3とローサイドスイッチ4とが同時にオンになることを避けるために設けられるデッドタイムは、省略している。

【0086】

なお、図8(a)においては、ハイサイドスイッチ3がオンまたはオフに制御されていることを、それぞれON、OFFで表している。また、図8(e)においては、ローサイドスイッチ4がオンまたはオフに制御されていることを、それぞれON、OFFで表している。

【0087】

ハイサイド制御信号VHがハイレベル、ローサイド制御信号VLがローレベルのとき(図8(a)、(b))、ハイサイドスイッチ3はオン、ローサイドスイッチ4はオフである。このとき、出力電圧VLXはハイレベルである(図8(f))。また、信号VDは、ハイレベルである(図8(d))。

【0088】

ハイサイド制御信号VHがハイレベルからローレベルに変化すると(図8(a))、ローサイド制御信号VLはローレベルからハイレベルに変化する(図8(b))。ハイサイドスイッチ3はオフになる。

【0089】

信号VDは、ローサイド制御信号VLに対して第1の期間T1だけ遅延しているため、ハイレベルである(図8(d))。したがって、短絡検出信号VSは、出力電圧VLXによらずローレベルである(図8(g))。

【0090】

第1のトランジスタ11はオフ、第2のトランジスタ12はオン、第3のトランジスタ14はオフになる。第2のトランジスタ12はソースフォロワ出力のため、ローサイドスイッチ4のゲート電圧VGは、第2のトランジスタ12のしきい値電圧Vthだけ内部電源電圧VI1よりも低い第1の電圧V1になる(図8(e))。なお、図8(e)においては、接地電位の0Vを基準にして、ゲート電圧VGを表している。

【0091】

ここで、第1の電圧V1は、内部電源電圧VI1よりも低く設定されている。ローサイドスイッチ4のオン抵抗Ronは、内部電源電圧VI1を供給した場合よりも大きい値になっている。そのため、ローサイドスイッチ4の電流Ilは、オン抵抗Ronに制限される。

【0092】

遅延回路16の出力の信号VRは、時定数に従って上昇する(図8(c))。第1の期間T1において、信号VRは、NOR15の論理しきい電圧よりも高くなる。信号VDは、ローレベルに変化する(図8(d))。信号VDは、ローサイド制御信号VLの立上がりを第1の期間T1だけ遅延させ、さらに反転させた信号になる。

【0093】

ローサイド制御信号VLがハイレベルに変化してから第1の期間T1経過後、信号VDは、ローレベルになり(図8(d))、短絡検出回路17aのDFFがクロックされる。このとき、出力電圧VLXは、ローレベルである(図8(f)の一点鎖線Pで囲んだ部分)。そのため、短絡検出回路17aは、短絡を検出せず、短絡検出信号VSはローレベルのままである(図8(h))。

【0094】

第3のトランジスタ14は、オンになり、出力電圧VLXは、接地電位0Vまで低下する(図8(f))。

ローサイド制御信号VLがローレベル、ハイサイド制御信号VHがハイレベルに変化すると、ローサイドスイッチ4はオフ、ハイサイドスイッチ3はオンに切り替えられる。次サイクル以降、同様の動作が繰り返される。

【0095】

また、第1の期間T1の経過時に、出力電圧VLXがハイレベルの場合(図8(f)の一点破線Qで囲んだ部分)、短絡検出回路17aは、短絡を検出してハイレベルを出力する(図8(h))。

【0096】

AND19にハイレベルの短絡検出信号VSが入力され、AND19は、ローレベルを出力する。信号VDは、ハイレベルになる。第1のトランジスタ11はオン、第2のトランジスタ12はオフ、第3のトランジスタ14はオフになる。

したがって、ローサイドスイッチ4は、オフに切り替えられる。

【0097】

このように、駆動回路7bは、ハイサイド制御信号VHがハイレベル、ローサイド制御信号VLがローレベルのとき、ハイサイドスイッチ3をオン、ローサイドスイッチ4をオフに切り替える。

【0098】

また、ハイサイド制御信号VHがローレベル、ローサイド制御信号VLがハイレベルに変化したとき、ハイサイドスイッチ3をオフに切り替える。同時に、ローサイドスイッチ4に第1の期間T1の間は、第1の電圧V1を供給する。このとき、ローサイドスイッチ4の電流ILは、オン抵抗Ron=Ron1に制限される。

【0099】

そして、第1の期間経過後は、第1の電圧V1よりも高い第2の電圧V2として内部電源電圧VI1を供給してローサイドスイッチ4をオンに切り替える。このときのローサイドスイッチ4のオン抵抗Ron=Ron2は、第1の期間T1における値Ron1よりも小さくなっている。

【0100】

スイッチング回路1bにおいては、ローサイドスイッチ4がオフからオンに変化するときの第1の期間T1の間、ゲート駆動電圧を低くすることにより、ローサイドスイッチ4の電流を制限している。そのため、出力端子5が電源端子2と短絡した場合でも、ローサイドスイッチ4に過電流が流れるのを防ぎ、破壊を防止すことができる。

【0101】

また、ローサイド制御信号VLがローレベルからハイレベルに変化してから第1の期間T1の経過後に、出力端子5の出力電圧VLXがハイレベルのままの場合、短絡検出信号VSがハイレベルになる。AND19は、ローレベルを出力して、ローサイドスイッチ4をオフさせる。そのため、ローサイドスイッチ4に過電流が連続的に流れるのを防ぎ、破壊を防止する。

【0102】

なお、図1、図5、図7にそれぞれ表したスイッチング回路1、1a、1bにおいては、ハイサイドスイッチ3は、PMOS、ローサイドスイッチ4は、NMOSでそれぞれ構成されている。しかし、ハイサイドスイッチ3、ローサイドスイッチ4は、ともにNMOS、PMOSでもよい。

【0103】

また、図7に表したスイッチング回路1bにおいては、第1のトランジスタ11及び第2のトランジスタ12は、NMOS、第3のトランジスタ14は、PMOSでそれぞれ構成されている。しかし、第1のトランジスタ11及び第2のトランジスタ12は、PMOS、第3のトランジスタ14は、NMOSでそれぞれ構成されてもよい。

【0104】

また、図1、図5にそれぞれ表したスイッチング回路1、1aにおいては、内部電源線13に内部電源電圧−VI2を供給している。しかし、内部電源電圧−VI2を供給せず、内部電源線13は、接地端子GNDに接続されていてもよい。

また、図7に表したスイッチング回路1bにおいては、内部電源線13に内部電源電圧VI1を供給している。しかし、内部電源電圧VI1を供給せず、内部電源線13は、電源端子2に接続されていてもよい。

【0105】

(第3の実施形態)

図9は、第3の実施形態に係るDC−DCコンバータの構成を例示する回路図である。

図9に表したように、DC−DCコンバータ30においては、スイッチング回路1aに、スイッチング回路1aを制御する制御回路31が追加されている。スイッチング回路1aについては、図5に表したスイッチング回路1aと同様である。

【0106】

また、DC−DCコンバータ32においては、スイッチング回路1aの出力端子5に、インダクタ33の一端が接続されている。インダクタ33の他端と接地端子GNDとの間に、帰還抵抗34と35とが直列に接続されている。さらに、平滑コンデンサ36が、インダクタ33の他端と接地端子GNDとの間に接続されている。

帰還抵抗34、35は、インダクタ33の他端の出力電圧VOUTを分圧した電圧VFBを制御回路31に帰還する。

【0107】

制御回路31は、スイッチング回路1にハイサイド制御信号VH、ローサイド制御信号VLを出力する。制御回路31は、インダクタ33の他端の出力電圧VOUTに応じて、スイッチング回路1aを制御する。

【0108】

図10は、図9に表したDC−DCコンバータの主要な信号のタイミングチャートであり、(a)はハイサイド制御信号VH、(b)はローサイド制御信号VL、(c)はゲート電圧VG、(d)はスイッチング回路の出力電圧VLX、(e)はハイサイド電流IH、(f)はローサイド電流IL、(g)はインダクタ電流ILLを表す。

【0109】

なお、図10(b)においては、ローサイドスイッチ4がオンまたはオフに制御されていることを、それぞれON、OFFで表している。また、図10(c)においては、ハイサイドスイッチ3がオンまたはオフに制御されていることを、それぞれON、OFFで表している。また、ハイサイドスイッチ3とローサイドスイッチ4とが同時にオンになることを避けるために、デッドタイムTdが設けられている。

【0110】

ハイサイド制御信号VHがローレベル、ローサイド制御信号VLがハイレベルのとき(図10(a)、(b))、ハイサイドスイッチ3のゲート電圧VGは、ハイレベルである(図10(c))。ハイサイドスイッチ3はオフ、ローサイドスイッチ4はオンである。このとき、スイッチング回路1aの出力電圧(出力端子5の電圧)VLXは、ローレベルである(図10(d))。ローサイドスイッチ4には、インダクタ33の電流ILLと等しい回生電流ILが流れている(図10(f)、(g))。

【0111】

制御回路31がハイサイド制御信号VHをローレベルからハイレベル、ローサイド制御信号VLをハイレベルからローレベルに切り替えると(図2(a)、(b))、ローサイドスイッチ4はオフになる。ローサイドスイッチ4を流れていた回生電流ILは、寄生ダイオードDLを流れる。

【0112】

また、ゲート電圧VGは、第1の期間T1の間、第1の電圧V1になる(図10(c))。ここで、第1の電圧V1は、図2において説明したように、内部電源電圧VI2よりも低く設定されている。ハイサイドスイッチ3のオン抵抗Ron=Ron1は、内部電源電圧VI2を供給した場合よりも大きい値になっている。そのため、寄生ダイオードDLの逆方向電流はオン抵抗Ron=Ron1に制限され、ハイサイドスイッチ3の電流IHとして流れる(図10(e)の一点鎖線Rで囲んだ部分)。インダクタ33の電流ILLは増加していく(図10(g))。

【0113】

ハイサイド制御信号VHがハイレベルに変化してから第1の期間T1経過後、出力電圧VLXは、ハイレベルであるため(図10(d)の一点鎖線Pで囲んだ部分)、短絡検出回路17は、短絡を検出せず、ゲート電圧VGは、第2の電圧V2=−VI2になる(図10(c))。スイッチング回路1aの出力電圧VLXは、電源電圧VINまで上昇する(図10(d))。

【0114】

このとき、寄生ダイオードDLの逆方向回復時間Trrとほぼ等しい第1の期間T1を経過しているため、寄生ダイオードDLの逆方向回復電流はすでに減少している。ハイサイドスイッチ3の電流IH及びインダクタ33の電流ILLは、ほぼ直線的に上昇していく(図10(e)、(g))。

【0115】

制御回路31がハイサイド制御信号VHをローレベル、ローサイド制御信号VLをハイレベルに変化させと、ハイサイドスイッチ3はオフ、ローサイドスイッチ4はオンに切り替えられる。ローサイドスイッチ4には、インダクタ33の回生電流ILLが流れる(図10(f)、(g))。次サイクル以降、同様の動作が繰り返される。

【0116】

また、第1の期間T1の経過時に、出力電圧VLXがローレベルの場合(図10(d)の一点破線Qで囲んだ部分)、短絡検出回路17は、短絡を検出して、ゲート電圧VGは、ハイレベルになる(図10(c))。ハイサイドスイッチ3は、オフに切り替えられ、ハイサイドスイッチ3の電流IHは0になる(図10(e))。

【0117】

このように、DC−DCコンバータ32においては、ハイサイド制御信号VHがローレベル、ローサイド制御信号VLがハイレベルのとき、ハイサイドスイッチ3をオフ、ローサイドスイッチ4をオンに切り替える。このとき、ローサイドスイッチ4にインダクタ33の電流ILLに等しい回生電流ILが流れる。

【0118】

また、ハイサイド制御信号VHがハイレベル、ローサイド制御信号VLがローレベルに変化したとき、ローサイドスイッチ4をオフに切り替える。同時に、ハイサイドスイッチ3を第1の期間T1の間は、第1の電圧V1を供給してオンに切り替える。このとき、ハイサイドスイッチ3の電流IHは、オン抵抗Ron=Ron1に制限されたローサイドスイッチ4の寄生ダイオードDLの逆方向回復電流が流れることになる。

【0119】

そして、第1の期間経過後は、第1の電圧V1よりも高い第2の電圧V2として電源電圧VINを供給する。このときのハイサイドスイッチ3のオン抵抗Ron=Ron2は、第1の期間T1における値よりも小さくなっている。

【0120】

DC−DCコンバータ32においては、ハイサイドスイッチ3がオフからオンに変化するときの第1の期間T1の間ゲート駆動電圧を低くすることにより、寄生ダイオードDLの逆方向回復電流が抑制される。そして第1の期間T1の経過後、寄生ダイオードDLに流れる電流がなくなるころに、ハイサイドスイッチ3のゲート駆動電圧が高くなり、オン抵抗をより小さくする。

【0121】

また、ハイサイド制御信号VHがローレベルからハイレベルに変化してから第1の期間T1の経過後に、出力端子5の出力電圧VLXがローレベルのままの場合、短絡が検出され、ゲート駆動電圧にハイレベルを出力して、ハイサイドスイッチ3をオフさせる。ハイサイドスイッチ3に過電流が連続的に流れるのを防ぎ、破壊を防止する。

なお、第1の期間T1の間に、出力端子5と接地端子GNDとが短絡した場合でも、ハイサイドスイッチ3を流れる電流IHは、比較的高いオン抵抗により制限された値になる。

【0122】

図9においては、スイッチング回路1aを用いたDC−DCコンバータ32の構成を例示した。しかし、スイッチング回路1、1bを用いてDC−DCコンバータを構成することもできる。すなわち、図9に表したスイッチング回路1aを、図1に表したスイッチング回路1または図7に表したスイッチング回路1bに置き換えた構成である。

【0123】

図11は、図9に表したDC−DCコンバータの主要な信号の他のタイミングチャートであり、(a)はハイサイド制御信号VH、(b)はローサイド制御信号VL、(c)はゲート電圧VG、(d)はスイッチング回路の出力電圧VLX、(e)はハイサイド電流IH、(f)はローサイド電流IL、(g)はインダクタ電流ILLを表す。

【0124】

図11においては、スイッチング回路1bを用いたDC−DCコンバータの主要な信号を表している。

なお、図11(a)においては、ハイサイドスイッチ3がオンまたはオフに制御されていることを、それぞれON、OFFで表している。また、図11(c)においては、ローサイドスイッチ4がオンまたはオフに制御されていることを、それぞれON、OFFで表している。また、ハイサイドスイッチ3とローサイドスイッチ4とが同時にオンになることを避けるために、デッドタイムTdが設けられている。

【0125】

ハイサイド制御信号VHがローレベル、ローサイド制御信号VLがハイレベルのとき(図11(a)、(b))、ローサイドスイッチ4のゲート電圧VGは、ローレベルである(図11(c))。ハイサイドスイッチ3はオン、ローサイドスイッチ4はオフである。このとき、スイッチング回路1bの出力電圧(出力端子5の電圧)VLXは、ハイレベルである(図11(d))。ローサイドスイッチ4には、インダクタ33の電流ILLと等しい回生電流ILが流れている(図11(f)、(g))。

【0126】

制御回路31がハイサイド制御信号VHをハイレベルからローレベル、ローサイド制御信号VLをローレベルからハイレベルに切り替えると(図2(a)、(b))、ハイサイドスイッチ3はオフになる。

【0127】

ローサイドスイッチ4のゲート電圧VGは、第1の期間T1の間、第1の電圧V1になる(図11(c))。ここで、第1の電圧V1は、図8において説明したように、内部電源電圧VI1よりも低く設定されている。ローサイドスイッチ4のオン抵抗Ronは、内部電源電圧VI1を供給した場合よりも大きい値になっている。そのため、ローサイドスイッチ4の電流ILは、オン抵抗Ron=Ron1に制限される(図11(f))。インダクタ33の電流ILLは減少していく(図10(g))。

【0128】

ローサイド制御信号VLがハイレベルに変化してから第1の期間T1経過後、出力電圧VLXは、ローレベルであるため(図11(d)の一点鎖線Pで囲んだ部分)、短絡は検出されず、ゲート電圧VGは、第2の電圧V2=VI1になる(図11(c))。スイッチング回路1bの出力電圧VLXは、接地端子GNDの電位0Vまで低下する(図11(d))。

ローサイドスイッチ4の電流IL及びインダクタ33の電流ILLは、ほぼ直線的に減少していく(図11(f)、(g))。

【0129】

制御回路31がハイサイド制御信号VHをハイレベル、ローサイド制御信号VLをローレベルに変化させと、ハイサイドスイッチ3はオン、ローサイドスイッチ4はオフに切り替えられる。ハイサイドスイッチ3には、ローサイドスイッチ4の寄生ダイオードDLの逆方向回復電流Irrにより電流IHが流れる(図10(e))。次サイクル以降、同様の動作が繰り返される。

【0130】

また、第1の期間T1の経過時に、出力電圧VLXがハイレベルの場合(図11(d)の一点破線Qで囲んだ部分)、短絡が検出されてゲート電圧VGは、ローレベルになる(図11(c))。ローサイドスイッチ4は、オフに切り替えられ、ローサイドスイッチ4の電流ILは0になる(図10(f))。

【0131】

このように、スイッチング回路1bを用いた場合、ハイサイド制御信号VHがハイレベル、ローサイド制御信号VLがローレベルのとき、ハイサイドスイッチ3をオン、ローサイドスイッチ4をオフに切り替える。このとき、ハイサイドスイッチ3にローサイドスイッチ4の寄生ダイオードDLの逆方向回復電流Irrにより電流IHが流れる。

【0132】

また、ハイサイド制御信号VHがローレベル、ローサイド制御信号VLがハイレベルに変化したとき、ハイサイドスイッチ3をオフに切り替える。同時に、ローサイドスイッチ4に第1の期間T1の間は、第1の電圧V1を供給する。このとき、ローサイドスイッチ4の電流ILは、オン抵抗Ron=Ron1に制限される。

【0133】

そして、第1の期間経過後は、第1の電圧V1よりも高い第2の電圧V2として内部電源電圧VI1を供給してローサイドスイッチ4をオンに切り替える。このときのローサイドスイッチ4のオン抵抗Ron=Ron2は、第1の期間T1における値よりも小さくなっている。

【0134】

このように、ローサイドスイッチ4がオフからオンに変化するときの第1の期間T1の間ゲート駆動電圧を低くすることにより、ローサイドスイッチ4を流れる電流を制限することができる。そして第1の期間T1の経過後、ローサイドスイッチ4のゲート駆動電圧が高くなり、オン抵抗をより小さくする。

【0135】

そのため、ローサイド制御信号VLがローレベルからハイレベルに変化してから第1の期間T1の経過後に、出力端子5の出力電圧VLXがハイレベルの場合、短絡が検出され、ゲート駆動電圧にローレベルを出力して、ローサイドスイッチ4をオフさせる。ローサイドスイッチ4に過電流が連続的に流れるのを防ぎ、破壊を防止する。

なお、第1の期間T1の間に、出力端子5と電源端子2とが短絡した場合でも、ローサイドスイッチ4を流れる電流ILは、比較的高いオン抵抗により制限された値になる。

【0136】

なお、スイッチング回路1、1a、1bを用いたDC−DCコンバータについて説明した。しかし、スイッチング回路としては、図1に表したスイッチング回路1または図5に表したスイッチング回路1aにおいて、内部電源線13を接地端子GNDに接続してもよい。図7に表したスイッチング回路1bにおいて、内部電源線13を電源端子2に接続してもよい。

【0137】

本発明のいくつかの実施形態を説明したが、これらの実施形態は、例として提示したものであり、発明の範囲を限定することは意図していない。これら新規な実施形態は、その他の様々な形態で実施されることが可能であり、発明の要旨を逸脱しない範囲で、種々の省略、置き換え、変更を行うことができる。これら実施形態やその変形は、発明の範囲や要旨に含まれるとともに、特許請求の範囲に記載された発明とその均等の範囲に含まれる。

【符号の説明】

【0138】

1、1a、1b…スイッチング回路、 2…電源端子、 3…ローサイドスイッチ、 4…ローサイドスイッチ、 5…出力端子(接続点)、 6…誘導性負荷、 7、7a、7b…駆動回路、 8、9、10…否定回路(INV)、 11…第1のトランジスタ、 12…第2のトランジスタ、 13…内部電源線、 14…第3のトランジスタ、 16…遅延回路、 17、17a、17b…短絡検出回路、 18…制御端子、 20、22…論理積の否定回路(NAND)、 30、32…DC−DCコンバータ、 31…制御回路、 33…インダクタ、 34…帰還抵抗、 36…平滑コンデンサ

【特許請求の範囲】

【請求項1】

電源端子と出力端子との間に接続されたハイサイドスイッチと、

前記出力端子と接地端子との間に接続されたローサイドスイッチと、

制御信号に応じて、前記ハイサイドスイッチ及び前記ローサイドスイッチのいずれか一方のスイッチをオフし、第1の期間の間第1の電圧を他方のスイッチの制御端子に供給して前記他方のスイッチをオンさせ、前記第1の期間経過後に前記他方のスイッチの前記制御端子に前記第1の電圧よりも高い第2の電圧を供給する駆動回路と、

を備えたことを特徴とするスイッチング回路。

【請求項2】

前記駆動回路は、前記第1の期間経過後において前記出力端子の短絡を検出したときは前記他方をオフに切り替え、前記出力端子の短絡を検出しないときは前記他方に前記第2の電圧を供給することを特徴とする請求項1記載のスイッチング回路。

【請求項3】

前記第1の期間は、前記ハイサイドスイッチ及び前記ローサイドスイッチのいずれかの寄生ダイオードの逆方向回復時間以下であることを特徴とする請求項1または2に記載のスイッチング回路。

【請求項4】

前記第1の期間は、前記ハイサイドスイッチ及び前記ローサイドスイッチのいずれかの寄生ダイオードの逆方向回復時間以上であることを特徴とする請求項1または2に記載のスイッチング回路。

【請求項5】

前記駆動回路は、前記第1の電圧を前記ハイサイドスイッチに供給し、前記第1の期間経過後に前記出力端子と前記接地端子との短絡を検出したとき前記ハイサイドスイッチをオフに切り替えることを特徴とする請求項2〜4のいずれか1つに記載のスイッチング回路。

【請求項6】

前記駆動回路は、前記第1の電圧を前記ローサイドスイッチに供給し、前記第1の期間経過後に前記出力端子と前記電源端子との短絡を検出したとき前記ローサイドスイッチをオフに切り替えることを特徴とする請求項2〜4のいずれか1つに記載のスイッチング回路。

【請求項7】

請求項1〜6のいずれか1つに記載のスイッチング回路と、

入力された電圧に応じて制御信号を出力して前記スイッチング回路を制御する制御回路と、

を備えたことを特徴とするDC−DCコンバータ。

【請求項8】

前記出力端子に一端が接続されたインダクタと、

前記インダクタの他端と接地端子との間に接続され、前記制御回路に電圧を帰還する帰還抵抗と、

をさらに備えたことを特徴とする請求項7記載のDC−DCコンバータ。

【請求項1】

電源端子と出力端子との間に接続されたハイサイドスイッチと、

前記出力端子と接地端子との間に接続されたローサイドスイッチと、

制御信号に応じて、前記ハイサイドスイッチ及び前記ローサイドスイッチのいずれか一方のスイッチをオフし、第1の期間の間第1の電圧を他方のスイッチの制御端子に供給して前記他方のスイッチをオンさせ、前記第1の期間経過後に前記他方のスイッチの前記制御端子に前記第1の電圧よりも高い第2の電圧を供給する駆動回路と、

を備えたことを特徴とするスイッチング回路。

【請求項2】

前記駆動回路は、前記第1の期間経過後において前記出力端子の短絡を検出したときは前記他方をオフに切り替え、前記出力端子の短絡を検出しないときは前記他方に前記第2の電圧を供給することを特徴とする請求項1記載のスイッチング回路。

【請求項3】

前記第1の期間は、前記ハイサイドスイッチ及び前記ローサイドスイッチのいずれかの寄生ダイオードの逆方向回復時間以下であることを特徴とする請求項1または2に記載のスイッチング回路。

【請求項4】

前記第1の期間は、前記ハイサイドスイッチ及び前記ローサイドスイッチのいずれかの寄生ダイオードの逆方向回復時間以上であることを特徴とする請求項1または2に記載のスイッチング回路。

【請求項5】

前記駆動回路は、前記第1の電圧を前記ハイサイドスイッチに供給し、前記第1の期間経過後に前記出力端子と前記接地端子との短絡を検出したとき前記ハイサイドスイッチをオフに切り替えることを特徴とする請求項2〜4のいずれか1つに記載のスイッチング回路。

【請求項6】

前記駆動回路は、前記第1の電圧を前記ローサイドスイッチに供給し、前記第1の期間経過後に前記出力端子と前記電源端子との短絡を検出したとき前記ローサイドスイッチをオフに切り替えることを特徴とする請求項2〜4のいずれか1つに記載のスイッチング回路。

【請求項7】

請求項1〜6のいずれか1つに記載のスイッチング回路と、

入力された電圧に応じて制御信号を出力して前記スイッチング回路を制御する制御回路と、

を備えたことを特徴とするDC−DCコンバータ。

【請求項8】

前記出力端子に一端が接続されたインダクタと、

前記インダクタの他端と接地端子との間に接続され、前記制御回路に電圧を帰還する帰還抵抗と、

をさらに備えたことを特徴とする請求項7記載のDC−DCコンバータ。

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【公開番号】特開2012−200083(P2012−200083A)

【公開日】平成24年10月18日(2012.10.18)

【国際特許分類】

【出願番号】特願2011−62756(P2011−62756)

【出願日】平成23年3月22日(2011.3.22)

【出願人】(000003078)株式会社東芝 (54,554)

【Fターム(参考)】

【公開日】平成24年10月18日(2012.10.18)

【国際特許分類】

【出願日】平成23年3月22日(2011.3.22)

【出願人】(000003078)株式会社東芝 (54,554)

【Fターム(参考)】

[ Back to top ]