スイッチング素子の駆動回路

【課題】パワースイッチング素子S#*がオン状態であるときとオフ状態であるときとの双方においてそのゲートの電圧を適切に検出することが困難なこと。

【解決手段】パワースイッチング素子S#*のゲートおよびエミッタ間は、ゲート電圧が低下することをトリガとして、オフ保持用スイッチング素子40によって短絡される。オフ保持用スイッチング素子40は、集積回路(ドライブIC20)によってオン操作される。パワースイッチング素子S#*のゲートに電圧を印加する電源28,30はそれぞれ端子電圧が相違し、ゲート電圧が上昇することで端子電圧の低い電源30から端子電圧の高い電源28へと切り替える。パワースイッチング素子S#*がオフ状態であるときには端子T1の電圧を、また、オン状態であるときには端子T2の電圧を、それぞれゲート電圧として検出する。

【解決手段】パワースイッチング素子S#*のゲートおよびエミッタ間は、ゲート電圧が低下することをトリガとして、オフ保持用スイッチング素子40によって短絡される。オフ保持用スイッチング素子40は、集積回路(ドライブIC20)によってオン操作される。パワースイッチング素子S#*のゲートに電圧を印加する電源28,30はそれぞれ端子電圧が相違し、ゲート電圧が上昇することで端子電圧の低い電源30から端子電圧の高い電源28へと切り替える。パワースイッチング素子S#*がオフ状態であるときには端子T1の電圧を、また、オン状態であるときには端子T2の電圧を、それぞれゲート電圧として検出する。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、電圧制御形のスイッチング素子である駆動対象スイッチング素子をオン状態とするためのオン操作用回路と前記駆動対象スイッチング素子をオフ状態とするためのオフ操作用回路とを備え、これらを操作することで前記駆動対象スイッチング素子をオン・オフ操作するスイッチング素子の駆動回路に関する。

【背景技術】

【0002】

この種の駆動回路としては、例えば下記特許文献1に見られるように、絶縁ゲートバイポーラトランジスタ(IGBT)のゲートの放電処理の後、これをオフ状態に保つため、専用のスイッチング素子を用いてゲートとエミッタとを短絡させるものも提案されている。詳しくは、駆動回路の一部を集積回路として、その入力端子の電圧に基づき同集積回路の外部に設けられた上記専用のスイッチング素子を操作することで上記短絡させる処理を行なっている。

【0003】

また、この種の駆動回路としては、例えば下記特許文献2に見られるように、絶縁ゲートバイポーラトランジスタ(IGBT)のオン操作に伴うゲート電圧の検出結果に基づき、ミラー期間が終了したと判断されることで、ゲート印加電圧を上昇させるものも提案されている。

【先行技術文献】

【特許文献】

【0004】

【特許文献1】特開2010−75007号公報

【特許文献2】特許第4432215号公報

【発明の概要】

【発明が解決しようとする課題】

【0005】

ところで、上記特許文献2に記載の駆動回路においても、ゲート印加電圧の検出結果を取得することが要求されるが、上記特許文献1に記載の上記短絡する処理を行なうために用いた集積回路の端子電圧は、ゲート電圧を表現するものとして不適切となる。

【0006】

本発明は、上記課題を解決するためになされたものであり、その目的は、電圧制御形のスイッチング素子がオン状態であるときとオフ状態であるときとの双方においてその導通制御端子の電圧を適切に検出して利用することのできるスイッチング素子の駆動回路を提供することにある。

【課題を解決するための手段】

【0007】

以下、上記課題を解決するための手段、およびその作用効果について記載する。

【0008】

請求項1記載の発明は、電圧制御形のスイッチング素子である駆動対象スイッチング素子をオン状態とするためのオン操作用回路と前記駆動対象スイッチング素子をオフ状態とするためのオフ操作用回路とを備え、これらを操作することで前記駆動対象スイッチング素子をオン・オフ操作するスイッチング素子の駆動回路において、前記オン操作用回路は、充電用抵抗体の設けられた充電経路を備え、前記オフ操作用回路は、前記充電用抵抗体とは別の放電用抵抗体の設けられた放電経路を備え、前記駆動対象スイッチング素子の導通制御端子は、前記充電用抵抗体および前記放電用抵抗体の接続点を介してこれらのそれぞれに接続されるものであり、前記駆動対象スイッチング素子のオン操作期間において該駆動対象スイッチング素子の導通制御端子の電圧の検出結果に基づき前記オン操作用回路の操作状態を変更する処理を行なうオン操作用変更処理手段と、前記駆動対象スイッチング素子のオフ操作期間において前記導通制御端子の電圧の検出結果に基づき前記オフ操作用回路の操作状態を変更する処理を行なうオフ操作用変更処理手段とを備え、前記オン操作用変更処理手段と前記オフ操作用変更処理手段とは、1チップ化された集積回路に内蔵されるものであり、前記充電用抵抗体と前記放電用抵抗体との双方が前記集積回路に対して外付けされており、前記オン操作用変更処理手段に入力される検出結果と前記オフ操作用変更処理手段に入力される検出結果とのそれぞれに、前記放電用抵抗体および前記集積回路の接続端子の電圧の検出結果と前記充電用抵抗体および前記集積回路の接続端子の電圧の検出結果とを割り振る割振手段を備えることを特徴とする。

【0009】

オン操作期間においては、充電用抵抗体に接続される集積回路の端子電圧よりも、放電用抵抗体に接続される集積回路の端子電圧の方が、導通制御端子の電圧を高精度に表現する。一方、オフ操作期間においては、放電用抵抗体に接続される集積回路の端子電圧よりも、充電用抵抗体に接続される集積回路の端子電圧の方が、導通制御端子の電圧を高精度に表現する。上記発明では、この点に鑑み、割振手段を備えることで、電圧制御形のスイッチング素子がオン状態であるときとオフ状態であるときとの双方においてその導通制御端子の電圧を適切に検出して利用することができる。

【0010】

請求項2記載の発明は、請求項1記載の発明において、前記オン操作用変更処理手段は、前記導通制御端子の電圧が上昇することで前記充電経路を介した前記駆動対象スイッチング素子をオン状態とするための電荷の充電速度を上昇させることを特徴とする。

【0011】

請求項3記載の発明は、請求項1または2記載の発明において、前記オフ操作用回路は、前記放電経路とは別に、前記駆動対象スイッチング素子の出力端子と前記導通制御端子とを短絡させる短絡用スイッチング素子をさらに備え、前記オフ操作用変更処理手段は、前記導通制御端子の電圧の低下が検出されることに基づき前記短絡用スイッチング素子をオン操作することを特徴とする。

【0012】

請求項4記載の発明は、請求項1〜3のいずれか1項に記載の発明において、前記オフ操作用変更処理手段は、前記導通制御端子の電圧の低下が検出されることに基づき前記放電経路を介した前記駆動対象スイッチング素子をオン状態とするための電荷の放電速度を上昇させることを特徴とする。

【0013】

請求項5記載の発明は、請求項1〜4のいずれか1項に記載の発明において、前記充電経路と前記放電経路との接続点と前記導通制御端子とは、共通の電気経路によって接続されており、前記共通の電気経路の抵抗値は、前記充電用抵抗体の抵抗値と前記放電用抵抗体の抵抗値との双方と比較して小さく設定されていることを特徴とする。

【0014】

集積回路の端子電圧を利用した導通制御端子の電圧の検出精度は、共通の電気経路の電圧降下が小さいほど高くなる。上記発明では、この点に鑑み、上記設定とした。

【図面の簡単な説明】

【0015】

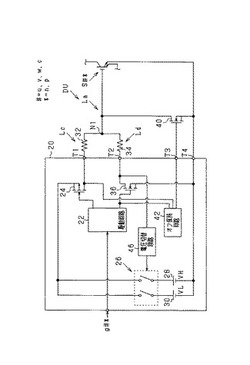

【図1】第1の実施形態にかかるシステム構成図。

【図2】同実施形態にかかるドライブユニットの構成を示す回路図。

【図3】同実施形態にかかるスイッチング素子の駆動処理の態様を示すタイムチャート。

【図4】第2の実施形態にかかるドライブユニットの構成を示す回路図。

【図5】同実施形態にかかるスイッチング素子の駆動処理の態様を示すタイムチャート。

【図6】第3の実施形態にかかるドライブユニットの構成を示す回路図。

【発明を実施するための形態】

【0016】

<第1の実施形態>

以下、本発明にかかる電力変換回路の駆動回路をハイブリッド車に適用した第1の実施形態について、図面を参照しつつ説明する。

【0017】

図1に、本実施形態にかかるモータジェネレータの制御システムの全体構成を示す。モータジェネレータ10は、インバータIVおよび昇圧コンバータCVを介して高電圧バッテリ12に接続されている。ここで、昇圧コンバータCVは、コンデンサ13と、コンデンサ13に並列接続された一対のパワースイッチング素子Scp,Scnと、一対のパワースイッチング素子Scp,Scnの接続点と高電圧バッテリ12の正極とを接続するリアクトルLとを備えている。そして、パワースイッチング素子Scp,Scnのオン・オフによって、高電圧バッテリ12の電圧(例えば「288V」)を所定の電圧(例えば「666V」)を上限として昇圧するものである。一方、インバータIVは、パワースイッチング素子Sup,Sunの直列接続体と、パワースイッチング素子Svp,Svnの直列接続体と、パワースイッチング素子Swp,Swnの直列接続体とを備えており、これら各直列接続体の接続点がモータジェネレータ10のU,V,W相にそれぞれ接続されている。これらパワースイッチング素子Sup,Sun,Svp,Svn,Swp,Swn,Scp,Scnとして、本実施形態では、絶縁ゲートバイポーラトランジスタ(IGBT)が用いられている。そして、これらにはそれぞれ、ダイオードDup,Dun,Dvp,Dvn,Dwp,Dwn,Dup,Dunが逆並列に接続されている。

【0018】

制御装置16は、低電圧バッテリ14を電源とする制御装置である。制御装置16は、モータジェネレータ10を制御対象とし、その制御量を所望に制御すべく、インバータIVやコンバータCVを操作する。詳しくは、コンバータCVのパワースイッチング素子Scp,Scnを操作すべく、操作信号gcp、gcnをドライブユニットDUに出力する。また、インバータIVのパワースイッチング素子Sup,Sun,Svp,Svn,Swp,Swnを操作すべく、操作信号gup,gun,gvp,gvn,gwp,gwnをドライブユニットDUに出力する。ここで、高電位側の操作信号gcp,gup,gvp,gwpと、対応する低電位側の操作信号gcn,gun,gvn,gwnとは、互いに相補的な信号となっている。換言すれば、高電位側のパワースイッチング素子Scp,Sup,Svp,Swpと、対応する低電位側のパワースイッチング素子Scn,Sun,Svn,Swnとは、交互にオン状態とされる。

【0019】

図2に、上記ドライブユニットDUの構成を示す。

【0020】

図示されるように、ドライブユニットDUは、1チップ化された半導体集積回路であるドライブIC20を備えている。ドライブIC20の端子T1は、ゲートの充電速度を調節するための充電用抵抗体32を介して、パワースイッチング素子S#*(#=u,v,w,c;*=n,p)のゲートに接続されている。一方、ドライブIC20は、パワースイッチング素子S#*をオン状態とすべく導通制御端子(ゲート)を充電するための電荷を供給する電源28,30を備えている。そして、電源28,30は、セレクタ26ならびに充電用スイッチング素子24の入力端子および出力端子を介して、端子T1に短絡接続される。

【0021】

また、ドライブIC20の端子T2は、ゲートの放電速度を調節するための放電用抵抗体34を介して、パワースイッチング素子S#*のゲートに接続されている。一方、ドライブIC20は、パワースイッチング素子S#*のエミッタに接続される端子T4と上記端子T2の間を開閉する放電用スイッチング素子36を備えており、これにより、端子T2と端子T4とが短絡接続される。

【0022】

具体的には、端子T1は、充電専用経路Lcと共通経路Laとを介してゲートに接続されており、端子T2は、放電専用経路Ldと共通経路Laとを介してゲートに接続されている。ここで、充電専用経路Lcと放電専用経路Ldとは接続点N1において接続されており、接続点N1とゲートとは共通経路Laによって短絡されている。また、充電専用経路Lcおよび放電専用経路Ldのそれぞれには、充電用抵抗体32および放電用抵抗体34のそれぞれが設けられており、これにより、充電専用経路Lcおよび放電専用経路Ldの抵抗値が共通経路Laの抵抗値よりも十分に大きくなっている。

【0023】

上記ドライブIC20は、パワースイッチング素子S#*を駆動する駆動回路22を備えている。駆動回路22では、図示しないフォトカプラ等の絶縁手段を介して、ドライブユニットDUに入力される上記操作信号g#*に基づき、充電用スイッチング素子24および放電用スイッチング素子36を相補的にオン・オフすることでパワースイッチング素子S#*を駆動する。すなわち、操作信号g#*が論理「H」となることで、パワースイッチング素子S#*をオン状態とする旨が指示される場合、充電用スイッチング素子24をオンして且つ放電用スイッチング素子36をオフすることで、パワースイッチング素子S#*のゲートに正の電荷を充電する。また、操作信号g#*が論理「L」となることで、パワースイッチング素子S#*をオフ状態とする旨が指示される場合、充電用スイッチング素子24をオフして且つ放電用スイッチング素子36をオンすることで、パワースイッチング素子S#*のゲートから正の電荷を放電させる。

【0024】

上記ドライブユニットDUは、パワースイッチング素子S#*をオン状態に切り替えるべくゲートを充電する処理期間において、ゲート印加電圧を上昇させゲート充電速度を上昇させる処理を行なう。すなわち、電源28の端子電圧VHを電源30の端子電圧VLよりも高く設定し、パワースイッチング素子S#*の出力端子および導通制御端子間の電圧(ゲートエミッタ間電圧:ゲート電圧Vge)がミラー期間の電圧よりも高くなることでゲート印加電圧を端子電圧VLから端子電圧VHに上昇させる。これにより、パワースイッチング素子S#*のオン状態への切り替えに伴いこれを流れる電流が増加する速度を制限してサージを抑制した後、速やかに印加電圧を上昇させることで損失の低減を図る。

【0025】

上記ドライブユニットDUは、さらに、パワースイッチング素子S#*のゲートおよびエミッタ間を短絡するためのNチャネルMOS型電界効果トランジスタ(オフ保持用スイッチング素子40)を備えている。オフ保持用スイッチング素子40は、パワースイッチング素子S#*のゲートおよびエミッタ間を低抵抗にて接続すべく、パワースイッチング素子S#*に極力近接して設けられている。そして、パワースイッチング素子S#*のゲートおよびエミッタ間を接続させる経路のうち、オフ保持用スイッチング素子40を備える経路のインピーダンスは、放電用抵抗体34を備える経路のインピーダンスよりも低くなるように設定されている。これは、上記操作信号g#*に応じてパワースイッチング素子S#*がオフ状態とされている際、パワースイッチング素子S#*の入力端子(コレクタ)や出力端子(エミッタ)とゲートとの間の寄生容量を介してゲートに高周波ノイズが重畳することでパワースイッチング素子S#*が誤ってオン状態となることを回避するためのものである。

【0026】

すなわち、高周波ノイズによって、パワースイッチング素子S#*のゲートから放電用抵抗体34側に電流が流れる場合、放電用抵抗体34の電圧降下によって、ゲートの電圧が上昇することで、パワースイッチング素子S#*がオン状態となるおそれがある。これに対し、オフ保持用スイッチング素子40を備える場合には、高周波ノイズに起因して、パワースイッチング素子S#*のゲートからオフ保持用スイッチング素子40に電流が流れることとなる。そして、この経路のインピーダンスが非常に小さいために、ゲート電圧の上昇量は無視でき、パワースイッチング素子S#*をオフ状態に保持することができる。

【0027】

上記オフ保持用スイッチング素子40のゲートは、端子T3を介して、ドライブIC20内のオフ保持回路42に接続されている。オフ保持回路42は、パワースイッチング素子S#*のゲート電圧が所定電圧となることで、オフ保持用スイッチング素子40をオン操作する処理を行うものである。また、オフ保持回路42は、駆動回路22から放電用スイッチング素子36のゲートに出力する信号をモニタし、放電用スイッチング素子36がオフ操作されることに同期してオフ保持用スイッチング素子40をオフ操作する処理を行うものでもある。

【0028】

ここで、本実施形態では、上記ゲートの充電速度の上昇処理と、オフ保持用スイッチング素子40の操作処理とのそれぞれで利用するゲート印加電圧をドライブIC20の印加電圧とすることで、ドライブICの端子数の低減を図る。ただし、この場合、これら2つの処理で共通の端子を利用することはできない。すなわち、端子T1と電源28,30とが短絡されていることに起因して、パワースイッチング素子S#*のオン操作処理時には、端子T1の電圧が電源28,30の電圧となるため、オン操作処理時には端子T1の電圧はゲート電圧Vgeを正確に表現したものとならない。一方、端子T2と端子T4とが短絡されていることに起因して、オフ操作処理時においては、端子T2の電圧が端子T4の電圧となるため、端子T2の電圧は、ゲート電圧Vgeを正確に表現したものとならない。ちなみに、充電用抵抗体32および放電用抵抗体34をドライブIC20に対して外付けしたのは、これらがゲートの充電速度や放電速度を調節する調節要素となるからである。

【0029】

本実施形態では、上記実情に鑑み、オン操作処理時においては端子T2の電圧をゲート電圧Vgeとして検出して且つ、オフ操作処理時においては端子T1の電圧をゲート電圧Vgeとして検出する。以下、こうしたゲート電圧Vgeの検出手法を利用して行われる上記ゲートの充電速度の上昇処理と、オフ保持用スイッチング素子40の操作処理とを示す。

【0030】

図3に、本実施形態にかかる上記2つの処理を示す。詳しくは、図3(a)は、充電用スイッチング素子24の状態の推移を示し、図3(b)は、放電用スイッチング素子36の状態の推移を示し、図3(c)は、ゲート電圧の状態の推移を示し、図3(d)は、端子T2の電圧の状態の推移を示し、図3(e)は、端子T1の電圧の状態の推移を示し、図3(f)は、ゲート印加電圧の推移を示し、図3(g)は、オフ保持用スイッチング素子40の操作状態の推移を示す。

【0031】

図示されるように、充電用スイッチング素子24がオン状態となっている期間においては、端子T2の電圧がゲート電圧Vgeを正確に表現したものとなる。このため、この電圧が閾値電圧VthHを上回ることで、ミラー期間の終了を高精度に検出することができ、ひいてはこれに基づきゲート印加電圧を端子電圧VLから端子電圧VHに上昇させる処理を行なうことができる。一方、放電用スイッチング素子36がオン状態となっている期間においては、端子T1の電圧がゲート電圧Vgeを正確に表現したものとなる。このため、この電圧が閾値電圧VthL(<VthH)を下回ることで、ミラー期間の終了を高精度に検出することができ、ひいてはこれに基づきオフ保持用スイッチング素子40のオン操作を行なうことができる。

【0032】

以上詳述した本実施形態によれば、以下の効果が得られるようになる。

【0033】

(1)オン操作処理時におけるゲート電圧Vgeを端子T2の電圧として検出して且つ、オフ操作処理時におけるゲート電圧Vgeを端子T1の電圧として検出した。これにより、オン操作処理時とオフ操作処理時との双方においてゲート電圧Vgeを高精度に検出しつつ、オン操作処理やオフ操作処理を行なうことができる。

【0034】

(2)充電専用経路Lcと放電専用経路Ldとの接続点N1とパワースイッチング素子S#*のゲートとの間を共通経路Laによって短絡した。これにより、端子T1,T2の電圧に基づくゲート電圧Vgeをいっそう高精度に行なうことができる。

<第2の実施形態>

以下、第2の実施形態について、先の第1の実施形態との相違点を中心に図面を参照しつつ説明する。

【0035】

図4に、本実施形態にかかるドライブユニットDUの回路構成を示す。なお、図4において、先の図2に示した部材に対応する部材については、便宜上同一の符号を付している。

【0036】

本実施形態では、ゲート充電速度を上昇させる処理として、充電専用経路Lcの抵抗値を低減する処理を行なう。これは、電源28を充電用スイッチング素子24a,24bのそれぞれを介して端子T1a,T1bに短絡し、端子T1a,T1bのそれぞれに充電用抵抗体32a,32bのそれぞれを接続することで可能となる。これにより、充電専用経路Lcは、充電用抵抗体32aを備える経路と充電用抵抗体32bを備える経路となる。

【0037】

また、本実施形態では、ゲート放電速度を上昇させる処理を行なう機能をも有する。これは、オフ操作処理によってミラー期間を経過した後であってもパワースイッチング素子S#*にテール電流が流れることに鑑み、このテール電流を極力低減するためのものである。こうした処理を、本実施形態では、放電専用経路Ldの抵抗値を低減する処理によって実現する。これは、端子T4を放電用スイッチング素子36a,36bのそれぞれを介して端子T2a,T2bに短絡し、端子T2a,T2bのそれぞれに放電用抵抗体34a,34bのそれぞれを接続することで可能となる。これにより、放電専用経路Ldは、放電用抵抗体34aを備える経路と放電用抵抗体34bを備える経路となる。

【0038】

上記充電用スイッチング素子24a,24bの操作や、放電用スイッチング素子36a,36bの操作は、コンパレータ60の出力に基づき駆動回路22によって行われる。すなわち、電源28の電圧を抵抗体50,52,54によって分圧することで閾値電圧VthH,VthLを生成するとともに、端子T2aの電圧と閾値電圧VthHとの大小を比較する手段と、端子T1aの電圧と閾値電圧VthLとの大小を比較する手段(コンパレータ60)を備える。詳しくは、コンパレータ60の一対の入力電圧を切り替えるべく、端子T1a,T2aの電圧を切り替えるセレクタ58と、閾値電圧VthH、VthLを切り替えるセレクタ56とを備えた。

【0039】

図5に、本実施形態にかかる上記2つの処理を示す。詳しくは、図5(a1)は、充電用スイッチング素子24aの状態の推移を示し、図5(a2)は、充電用スイッチング素子24bの状態の推移を示し、図5(b1)は、放電用スイッチング素子36aの状態の推移を示し、図5(b2)は、放電用スイッチング素子36bの状態の推移を示す。また、図5(c)は、ゲート電圧の状態の推移を示し、図5(d)は、端子T2aの電圧の状態の推移を示し、図5(e)は、端子T1aの電圧の状態の推移を示し、図5(f)は、セレクタ58の選択状態の推移を示し、図5(g)は、セレクタ56の選択状態の推移を示す。

【0040】

図示されるように、充電操作処理時(充電用スイッチング素子24aがオン状態とされる期間)においては、セレクタ58によって端子Bが選択されて且つセレクタ56によって端子Cが選択される。そして、端子T2aの電圧が閾値電圧VthHを上回ることで充電用スイッチング素子24bをオン状態に切り替え、充電専用経路Lcの抵抗値を低減し、充電速度を上昇させる。

【0041】

一方、オフ操作処理時(充電用スイッチング素子24aがオフ状態とされる期間)においては、セレクタ58によって端子Aが選択されて且つセレクタ56によって端子Dが選択される。そして、端子T1aの電圧が閾値電圧VthLを下回ることで放電用スイッチング素子36bをオン状態に切り替え、放電専用経路Ldの抵抗値を低減し、放電速度を上昇させる。

<第3の実施形態>

以下、第3の実施形態について、先の第2の実施形態との相違点を中心に図面を参照しつつ説明する。

【0042】

図6に、本実施形態にかかるドライブユニットDUの回路構成を示す。なお、図6において、先の図4に示した部材に対応する部材については、便宜上同一の符号を付している。

【0043】

本実施形態では、端子T2aの電圧と閾値電圧VthHとの大小比較を行なう手段(コンパレータ62)と、端子T1aの電圧と閾値電圧VthLとの大小比較を行なう手段(コンパレータ64)と、これらの出力を切り替える手段(セレクタ66)とを備える。これにより、駆動回路22では、セレクタ66の出力に基づき、上記第2の実施形態と同様の処理を行なうことができる。

<その他の実施形態>

なお、上記各実施形態は、以下のように変更して実施してもよい。

「オン操作用回路について」

ゲートの充電速度を上昇させるための回路としては、上記各実施形態において例示したものに限らない。例えば、充電用スイッチング素子をバイポーラトランジスタによって構成し、そのベース電流を操作するものであってもよい。

「オフ操作用回路について」

ゲートの放電速度を上昇させるための回路としては、上記第2、第3の実施形態において例示したものに限らない。例えば、放電用スイッチング素子36の出力端子の電位を低下させる手段を備えて構成してもよい。また例えば、放電用スイッチング素子をバイポーラトランジスタによって構成し、そのベース電流を操作するものであってもよい。

「オン操作用変更処理手段について」

ミラー期間の終了の検出手法としては、ゲート電圧が閾値電圧VthHを上回ることを検出するものに限らない。例えば、ゲート電圧の上昇速度を検出する(ゲート電圧の上昇速度が低下した後上昇することを検出する)ものであってもよい。

「オフ操作用変更処理手段について」

ミラー期間の終了の検出手法としては、ゲート電圧が閾値電圧VthLを下回ることを検出するものに限らない。例えば、ゲート電圧の低下速度を検出する(ゲート電圧の低下速度が低下した後上昇することを検出する)ものであってもよい。

【0044】

オフ保持用スイッチング素子40のオフ操作処理と、放電用スイッチング素子36a,36bを操作する処理との双方を、ゲート電圧に基づき行うものであってもよい。

「割振手段について」

上記第2,3の実施形態において、オン操作期間において端子T2bの電圧を用いてもよい。上記第2,3の実施形態において、オフ操作期間において端子T1bの電圧を用いてもよい。

【0045】

また、上記第1の実施形態においても、閾値電圧VthHと端子T2の電圧との大小を比較する比較手段と、閾値電圧VthLと端子T1の電圧との大小を比較する比較手段とを備え、これら比較手段を同一のハードウェアにして入力信号を変更するか、別のハードウェアにして出力信号を選択する手段を備えるかしてもよい。この場合、比較手段の出力が入力される手段(駆動回路22)がオフ保持用スイッチング素子40を操作する処理と、充電速度を上昇させる処理とを行えばよい。

「ゲート抵抗について」

共通経路Laに抵抗体を備えてもよい。ただし、この場合であっても、充電用抵抗体32の抵抗値と放電用抵抗体34の抵抗値との双方よりも小さくすることが望ましい。この際、共通経路Laの抵抗値を上記双方の抵抗値と比較して小さくすればするほど、ゲート電圧の検出精度を高めることができる。

【0046】

放電用スイッチング素子36の出力端子とスイッチング素子S#*の出力端子との間に抵抗体を備えてもよい。この場合であっても、放電用抵抗体34をドライブI20に対して外付けしている場合等にあっては、オフ操作期間におけるゲート電圧の検出精度を上げるうえで端子T1の電圧を用いることが望ましい。

【0047】

充電用スイッチング素子24の入力端子とスイッチング素子S#*をオンとするための電荷の供給源との間に抵抗体を備えてもよい。この場合であっても、充電用抵抗体32をドライブIC20に対して外付けしている場合等にあっては、オン操作期間におけるゲート電圧の検出精度を上げるうえで端子T2の電圧を用いることが望ましい。

「そのほか」

・駆動対象スイッチング素子によって構成される電力変換回路としては、車載回転機とバッテリとの間に接続されるインバータIVやコンバータCVに限らない。例えば、車載高電圧バッテリの電力を低電圧バッテリに供給すべく、高電圧バッテリの電圧を降圧するDCDCコンバータであってもよい。

【0048】

・駆動対象スイッチング素子としては、IGBTに限らず、例えばMOS型電界効果トランジスタであってもよい。

【符号の説明】

【0049】

20…ドライブIC、36…放電用スイッチング素子、34…放電用抵抗体、40…オフ保持用スイッチング素子(短絡用スイッチング素子の一実施形態)、42…オフ保持回路、S#*…パワースイッチング素子、IV…インバータ(電力変換回路の一実施形態)、CV…コンバータ(電力変換回路の一実施形態)。

【技術分野】

【0001】

本発明は、電圧制御形のスイッチング素子である駆動対象スイッチング素子をオン状態とするためのオン操作用回路と前記駆動対象スイッチング素子をオフ状態とするためのオフ操作用回路とを備え、これらを操作することで前記駆動対象スイッチング素子をオン・オフ操作するスイッチング素子の駆動回路に関する。

【背景技術】

【0002】

この種の駆動回路としては、例えば下記特許文献1に見られるように、絶縁ゲートバイポーラトランジスタ(IGBT)のゲートの放電処理の後、これをオフ状態に保つため、専用のスイッチング素子を用いてゲートとエミッタとを短絡させるものも提案されている。詳しくは、駆動回路の一部を集積回路として、その入力端子の電圧に基づき同集積回路の外部に設けられた上記専用のスイッチング素子を操作することで上記短絡させる処理を行なっている。

【0003】

また、この種の駆動回路としては、例えば下記特許文献2に見られるように、絶縁ゲートバイポーラトランジスタ(IGBT)のオン操作に伴うゲート電圧の検出結果に基づき、ミラー期間が終了したと判断されることで、ゲート印加電圧を上昇させるものも提案されている。

【先行技術文献】

【特許文献】

【0004】

【特許文献1】特開2010−75007号公報

【特許文献2】特許第4432215号公報

【発明の概要】

【発明が解決しようとする課題】

【0005】

ところで、上記特許文献2に記載の駆動回路においても、ゲート印加電圧の検出結果を取得することが要求されるが、上記特許文献1に記載の上記短絡する処理を行なうために用いた集積回路の端子電圧は、ゲート電圧を表現するものとして不適切となる。

【0006】

本発明は、上記課題を解決するためになされたものであり、その目的は、電圧制御形のスイッチング素子がオン状態であるときとオフ状態であるときとの双方においてその導通制御端子の電圧を適切に検出して利用することのできるスイッチング素子の駆動回路を提供することにある。

【課題を解決するための手段】

【0007】

以下、上記課題を解決するための手段、およびその作用効果について記載する。

【0008】

請求項1記載の発明は、電圧制御形のスイッチング素子である駆動対象スイッチング素子をオン状態とするためのオン操作用回路と前記駆動対象スイッチング素子をオフ状態とするためのオフ操作用回路とを備え、これらを操作することで前記駆動対象スイッチング素子をオン・オフ操作するスイッチング素子の駆動回路において、前記オン操作用回路は、充電用抵抗体の設けられた充電経路を備え、前記オフ操作用回路は、前記充電用抵抗体とは別の放電用抵抗体の設けられた放電経路を備え、前記駆動対象スイッチング素子の導通制御端子は、前記充電用抵抗体および前記放電用抵抗体の接続点を介してこれらのそれぞれに接続されるものであり、前記駆動対象スイッチング素子のオン操作期間において該駆動対象スイッチング素子の導通制御端子の電圧の検出結果に基づき前記オン操作用回路の操作状態を変更する処理を行なうオン操作用変更処理手段と、前記駆動対象スイッチング素子のオフ操作期間において前記導通制御端子の電圧の検出結果に基づき前記オフ操作用回路の操作状態を変更する処理を行なうオフ操作用変更処理手段とを備え、前記オン操作用変更処理手段と前記オフ操作用変更処理手段とは、1チップ化された集積回路に内蔵されるものであり、前記充電用抵抗体と前記放電用抵抗体との双方が前記集積回路に対して外付けされており、前記オン操作用変更処理手段に入力される検出結果と前記オフ操作用変更処理手段に入力される検出結果とのそれぞれに、前記放電用抵抗体および前記集積回路の接続端子の電圧の検出結果と前記充電用抵抗体および前記集積回路の接続端子の電圧の検出結果とを割り振る割振手段を備えることを特徴とする。

【0009】

オン操作期間においては、充電用抵抗体に接続される集積回路の端子電圧よりも、放電用抵抗体に接続される集積回路の端子電圧の方が、導通制御端子の電圧を高精度に表現する。一方、オフ操作期間においては、放電用抵抗体に接続される集積回路の端子電圧よりも、充電用抵抗体に接続される集積回路の端子電圧の方が、導通制御端子の電圧を高精度に表現する。上記発明では、この点に鑑み、割振手段を備えることで、電圧制御形のスイッチング素子がオン状態であるときとオフ状態であるときとの双方においてその導通制御端子の電圧を適切に検出して利用することができる。

【0010】

請求項2記載の発明は、請求項1記載の発明において、前記オン操作用変更処理手段は、前記導通制御端子の電圧が上昇することで前記充電経路を介した前記駆動対象スイッチング素子をオン状態とするための電荷の充電速度を上昇させることを特徴とする。

【0011】

請求項3記載の発明は、請求項1または2記載の発明において、前記オフ操作用回路は、前記放電経路とは別に、前記駆動対象スイッチング素子の出力端子と前記導通制御端子とを短絡させる短絡用スイッチング素子をさらに備え、前記オフ操作用変更処理手段は、前記導通制御端子の電圧の低下が検出されることに基づき前記短絡用スイッチング素子をオン操作することを特徴とする。

【0012】

請求項4記載の発明は、請求項1〜3のいずれか1項に記載の発明において、前記オフ操作用変更処理手段は、前記導通制御端子の電圧の低下が検出されることに基づき前記放電経路を介した前記駆動対象スイッチング素子をオン状態とするための電荷の放電速度を上昇させることを特徴とする。

【0013】

請求項5記載の発明は、請求項1〜4のいずれか1項に記載の発明において、前記充電経路と前記放電経路との接続点と前記導通制御端子とは、共通の電気経路によって接続されており、前記共通の電気経路の抵抗値は、前記充電用抵抗体の抵抗値と前記放電用抵抗体の抵抗値との双方と比較して小さく設定されていることを特徴とする。

【0014】

集積回路の端子電圧を利用した導通制御端子の電圧の検出精度は、共通の電気経路の電圧降下が小さいほど高くなる。上記発明では、この点に鑑み、上記設定とした。

【図面の簡単な説明】

【0015】

【図1】第1の実施形態にかかるシステム構成図。

【図2】同実施形態にかかるドライブユニットの構成を示す回路図。

【図3】同実施形態にかかるスイッチング素子の駆動処理の態様を示すタイムチャート。

【図4】第2の実施形態にかかるドライブユニットの構成を示す回路図。

【図5】同実施形態にかかるスイッチング素子の駆動処理の態様を示すタイムチャート。

【図6】第3の実施形態にかかるドライブユニットの構成を示す回路図。

【発明を実施するための形態】

【0016】

<第1の実施形態>

以下、本発明にかかる電力変換回路の駆動回路をハイブリッド車に適用した第1の実施形態について、図面を参照しつつ説明する。

【0017】

図1に、本実施形態にかかるモータジェネレータの制御システムの全体構成を示す。モータジェネレータ10は、インバータIVおよび昇圧コンバータCVを介して高電圧バッテリ12に接続されている。ここで、昇圧コンバータCVは、コンデンサ13と、コンデンサ13に並列接続された一対のパワースイッチング素子Scp,Scnと、一対のパワースイッチング素子Scp,Scnの接続点と高電圧バッテリ12の正極とを接続するリアクトルLとを備えている。そして、パワースイッチング素子Scp,Scnのオン・オフによって、高電圧バッテリ12の電圧(例えば「288V」)を所定の電圧(例えば「666V」)を上限として昇圧するものである。一方、インバータIVは、パワースイッチング素子Sup,Sunの直列接続体と、パワースイッチング素子Svp,Svnの直列接続体と、パワースイッチング素子Swp,Swnの直列接続体とを備えており、これら各直列接続体の接続点がモータジェネレータ10のU,V,W相にそれぞれ接続されている。これらパワースイッチング素子Sup,Sun,Svp,Svn,Swp,Swn,Scp,Scnとして、本実施形態では、絶縁ゲートバイポーラトランジスタ(IGBT)が用いられている。そして、これらにはそれぞれ、ダイオードDup,Dun,Dvp,Dvn,Dwp,Dwn,Dup,Dunが逆並列に接続されている。

【0018】

制御装置16は、低電圧バッテリ14を電源とする制御装置である。制御装置16は、モータジェネレータ10を制御対象とし、その制御量を所望に制御すべく、インバータIVやコンバータCVを操作する。詳しくは、コンバータCVのパワースイッチング素子Scp,Scnを操作すべく、操作信号gcp、gcnをドライブユニットDUに出力する。また、インバータIVのパワースイッチング素子Sup,Sun,Svp,Svn,Swp,Swnを操作すべく、操作信号gup,gun,gvp,gvn,gwp,gwnをドライブユニットDUに出力する。ここで、高電位側の操作信号gcp,gup,gvp,gwpと、対応する低電位側の操作信号gcn,gun,gvn,gwnとは、互いに相補的な信号となっている。換言すれば、高電位側のパワースイッチング素子Scp,Sup,Svp,Swpと、対応する低電位側のパワースイッチング素子Scn,Sun,Svn,Swnとは、交互にオン状態とされる。

【0019】

図2に、上記ドライブユニットDUの構成を示す。

【0020】

図示されるように、ドライブユニットDUは、1チップ化された半導体集積回路であるドライブIC20を備えている。ドライブIC20の端子T1は、ゲートの充電速度を調節するための充電用抵抗体32を介して、パワースイッチング素子S#*(#=u,v,w,c;*=n,p)のゲートに接続されている。一方、ドライブIC20は、パワースイッチング素子S#*をオン状態とすべく導通制御端子(ゲート)を充電するための電荷を供給する電源28,30を備えている。そして、電源28,30は、セレクタ26ならびに充電用スイッチング素子24の入力端子および出力端子を介して、端子T1に短絡接続される。

【0021】

また、ドライブIC20の端子T2は、ゲートの放電速度を調節するための放電用抵抗体34を介して、パワースイッチング素子S#*のゲートに接続されている。一方、ドライブIC20は、パワースイッチング素子S#*のエミッタに接続される端子T4と上記端子T2の間を開閉する放電用スイッチング素子36を備えており、これにより、端子T2と端子T4とが短絡接続される。

【0022】

具体的には、端子T1は、充電専用経路Lcと共通経路Laとを介してゲートに接続されており、端子T2は、放電専用経路Ldと共通経路Laとを介してゲートに接続されている。ここで、充電専用経路Lcと放電専用経路Ldとは接続点N1において接続されており、接続点N1とゲートとは共通経路Laによって短絡されている。また、充電専用経路Lcおよび放電専用経路Ldのそれぞれには、充電用抵抗体32および放電用抵抗体34のそれぞれが設けられており、これにより、充電専用経路Lcおよび放電専用経路Ldの抵抗値が共通経路Laの抵抗値よりも十分に大きくなっている。

【0023】

上記ドライブIC20は、パワースイッチング素子S#*を駆動する駆動回路22を備えている。駆動回路22では、図示しないフォトカプラ等の絶縁手段を介して、ドライブユニットDUに入力される上記操作信号g#*に基づき、充電用スイッチング素子24および放電用スイッチング素子36を相補的にオン・オフすることでパワースイッチング素子S#*を駆動する。すなわち、操作信号g#*が論理「H」となることで、パワースイッチング素子S#*をオン状態とする旨が指示される場合、充電用スイッチング素子24をオンして且つ放電用スイッチング素子36をオフすることで、パワースイッチング素子S#*のゲートに正の電荷を充電する。また、操作信号g#*が論理「L」となることで、パワースイッチング素子S#*をオフ状態とする旨が指示される場合、充電用スイッチング素子24をオフして且つ放電用スイッチング素子36をオンすることで、パワースイッチング素子S#*のゲートから正の電荷を放電させる。

【0024】

上記ドライブユニットDUは、パワースイッチング素子S#*をオン状態に切り替えるべくゲートを充電する処理期間において、ゲート印加電圧を上昇させゲート充電速度を上昇させる処理を行なう。すなわち、電源28の端子電圧VHを電源30の端子電圧VLよりも高く設定し、パワースイッチング素子S#*の出力端子および導通制御端子間の電圧(ゲートエミッタ間電圧:ゲート電圧Vge)がミラー期間の電圧よりも高くなることでゲート印加電圧を端子電圧VLから端子電圧VHに上昇させる。これにより、パワースイッチング素子S#*のオン状態への切り替えに伴いこれを流れる電流が増加する速度を制限してサージを抑制した後、速やかに印加電圧を上昇させることで損失の低減を図る。

【0025】

上記ドライブユニットDUは、さらに、パワースイッチング素子S#*のゲートおよびエミッタ間を短絡するためのNチャネルMOS型電界効果トランジスタ(オフ保持用スイッチング素子40)を備えている。オフ保持用スイッチング素子40は、パワースイッチング素子S#*のゲートおよびエミッタ間を低抵抗にて接続すべく、パワースイッチング素子S#*に極力近接して設けられている。そして、パワースイッチング素子S#*のゲートおよびエミッタ間を接続させる経路のうち、オフ保持用スイッチング素子40を備える経路のインピーダンスは、放電用抵抗体34を備える経路のインピーダンスよりも低くなるように設定されている。これは、上記操作信号g#*に応じてパワースイッチング素子S#*がオフ状態とされている際、パワースイッチング素子S#*の入力端子(コレクタ)や出力端子(エミッタ)とゲートとの間の寄生容量を介してゲートに高周波ノイズが重畳することでパワースイッチング素子S#*が誤ってオン状態となることを回避するためのものである。

【0026】

すなわち、高周波ノイズによって、パワースイッチング素子S#*のゲートから放電用抵抗体34側に電流が流れる場合、放電用抵抗体34の電圧降下によって、ゲートの電圧が上昇することで、パワースイッチング素子S#*がオン状態となるおそれがある。これに対し、オフ保持用スイッチング素子40を備える場合には、高周波ノイズに起因して、パワースイッチング素子S#*のゲートからオフ保持用スイッチング素子40に電流が流れることとなる。そして、この経路のインピーダンスが非常に小さいために、ゲート電圧の上昇量は無視でき、パワースイッチング素子S#*をオフ状態に保持することができる。

【0027】

上記オフ保持用スイッチング素子40のゲートは、端子T3を介して、ドライブIC20内のオフ保持回路42に接続されている。オフ保持回路42は、パワースイッチング素子S#*のゲート電圧が所定電圧となることで、オフ保持用スイッチング素子40をオン操作する処理を行うものである。また、オフ保持回路42は、駆動回路22から放電用スイッチング素子36のゲートに出力する信号をモニタし、放電用スイッチング素子36がオフ操作されることに同期してオフ保持用スイッチング素子40をオフ操作する処理を行うものでもある。

【0028】

ここで、本実施形態では、上記ゲートの充電速度の上昇処理と、オフ保持用スイッチング素子40の操作処理とのそれぞれで利用するゲート印加電圧をドライブIC20の印加電圧とすることで、ドライブICの端子数の低減を図る。ただし、この場合、これら2つの処理で共通の端子を利用することはできない。すなわち、端子T1と電源28,30とが短絡されていることに起因して、パワースイッチング素子S#*のオン操作処理時には、端子T1の電圧が電源28,30の電圧となるため、オン操作処理時には端子T1の電圧はゲート電圧Vgeを正確に表現したものとならない。一方、端子T2と端子T4とが短絡されていることに起因して、オフ操作処理時においては、端子T2の電圧が端子T4の電圧となるため、端子T2の電圧は、ゲート電圧Vgeを正確に表現したものとならない。ちなみに、充電用抵抗体32および放電用抵抗体34をドライブIC20に対して外付けしたのは、これらがゲートの充電速度や放電速度を調節する調節要素となるからである。

【0029】

本実施形態では、上記実情に鑑み、オン操作処理時においては端子T2の電圧をゲート電圧Vgeとして検出して且つ、オフ操作処理時においては端子T1の電圧をゲート電圧Vgeとして検出する。以下、こうしたゲート電圧Vgeの検出手法を利用して行われる上記ゲートの充電速度の上昇処理と、オフ保持用スイッチング素子40の操作処理とを示す。

【0030】

図3に、本実施形態にかかる上記2つの処理を示す。詳しくは、図3(a)は、充電用スイッチング素子24の状態の推移を示し、図3(b)は、放電用スイッチング素子36の状態の推移を示し、図3(c)は、ゲート電圧の状態の推移を示し、図3(d)は、端子T2の電圧の状態の推移を示し、図3(e)は、端子T1の電圧の状態の推移を示し、図3(f)は、ゲート印加電圧の推移を示し、図3(g)は、オフ保持用スイッチング素子40の操作状態の推移を示す。

【0031】

図示されるように、充電用スイッチング素子24がオン状態となっている期間においては、端子T2の電圧がゲート電圧Vgeを正確に表現したものとなる。このため、この電圧が閾値電圧VthHを上回ることで、ミラー期間の終了を高精度に検出することができ、ひいてはこれに基づきゲート印加電圧を端子電圧VLから端子電圧VHに上昇させる処理を行なうことができる。一方、放電用スイッチング素子36がオン状態となっている期間においては、端子T1の電圧がゲート電圧Vgeを正確に表現したものとなる。このため、この電圧が閾値電圧VthL(<VthH)を下回ることで、ミラー期間の終了を高精度に検出することができ、ひいてはこれに基づきオフ保持用スイッチング素子40のオン操作を行なうことができる。

【0032】

以上詳述した本実施形態によれば、以下の効果が得られるようになる。

【0033】

(1)オン操作処理時におけるゲート電圧Vgeを端子T2の電圧として検出して且つ、オフ操作処理時におけるゲート電圧Vgeを端子T1の電圧として検出した。これにより、オン操作処理時とオフ操作処理時との双方においてゲート電圧Vgeを高精度に検出しつつ、オン操作処理やオフ操作処理を行なうことができる。

【0034】

(2)充電専用経路Lcと放電専用経路Ldとの接続点N1とパワースイッチング素子S#*のゲートとの間を共通経路Laによって短絡した。これにより、端子T1,T2の電圧に基づくゲート電圧Vgeをいっそう高精度に行なうことができる。

<第2の実施形態>

以下、第2の実施形態について、先の第1の実施形態との相違点を中心に図面を参照しつつ説明する。

【0035】

図4に、本実施形態にかかるドライブユニットDUの回路構成を示す。なお、図4において、先の図2に示した部材に対応する部材については、便宜上同一の符号を付している。

【0036】

本実施形態では、ゲート充電速度を上昇させる処理として、充電専用経路Lcの抵抗値を低減する処理を行なう。これは、電源28を充電用スイッチング素子24a,24bのそれぞれを介して端子T1a,T1bに短絡し、端子T1a,T1bのそれぞれに充電用抵抗体32a,32bのそれぞれを接続することで可能となる。これにより、充電専用経路Lcは、充電用抵抗体32aを備える経路と充電用抵抗体32bを備える経路となる。

【0037】

また、本実施形態では、ゲート放電速度を上昇させる処理を行なう機能をも有する。これは、オフ操作処理によってミラー期間を経過した後であってもパワースイッチング素子S#*にテール電流が流れることに鑑み、このテール電流を極力低減するためのものである。こうした処理を、本実施形態では、放電専用経路Ldの抵抗値を低減する処理によって実現する。これは、端子T4を放電用スイッチング素子36a,36bのそれぞれを介して端子T2a,T2bに短絡し、端子T2a,T2bのそれぞれに放電用抵抗体34a,34bのそれぞれを接続することで可能となる。これにより、放電専用経路Ldは、放電用抵抗体34aを備える経路と放電用抵抗体34bを備える経路となる。

【0038】

上記充電用スイッチング素子24a,24bの操作や、放電用スイッチング素子36a,36bの操作は、コンパレータ60の出力に基づき駆動回路22によって行われる。すなわち、電源28の電圧を抵抗体50,52,54によって分圧することで閾値電圧VthH,VthLを生成するとともに、端子T2aの電圧と閾値電圧VthHとの大小を比較する手段と、端子T1aの電圧と閾値電圧VthLとの大小を比較する手段(コンパレータ60)を備える。詳しくは、コンパレータ60の一対の入力電圧を切り替えるべく、端子T1a,T2aの電圧を切り替えるセレクタ58と、閾値電圧VthH、VthLを切り替えるセレクタ56とを備えた。

【0039】

図5に、本実施形態にかかる上記2つの処理を示す。詳しくは、図5(a1)は、充電用スイッチング素子24aの状態の推移を示し、図5(a2)は、充電用スイッチング素子24bの状態の推移を示し、図5(b1)は、放電用スイッチング素子36aの状態の推移を示し、図5(b2)は、放電用スイッチング素子36bの状態の推移を示す。また、図5(c)は、ゲート電圧の状態の推移を示し、図5(d)は、端子T2aの電圧の状態の推移を示し、図5(e)は、端子T1aの電圧の状態の推移を示し、図5(f)は、セレクタ58の選択状態の推移を示し、図5(g)は、セレクタ56の選択状態の推移を示す。

【0040】

図示されるように、充電操作処理時(充電用スイッチング素子24aがオン状態とされる期間)においては、セレクタ58によって端子Bが選択されて且つセレクタ56によって端子Cが選択される。そして、端子T2aの電圧が閾値電圧VthHを上回ることで充電用スイッチング素子24bをオン状態に切り替え、充電専用経路Lcの抵抗値を低減し、充電速度を上昇させる。

【0041】

一方、オフ操作処理時(充電用スイッチング素子24aがオフ状態とされる期間)においては、セレクタ58によって端子Aが選択されて且つセレクタ56によって端子Dが選択される。そして、端子T1aの電圧が閾値電圧VthLを下回ることで放電用スイッチング素子36bをオン状態に切り替え、放電専用経路Ldの抵抗値を低減し、放電速度を上昇させる。

<第3の実施形態>

以下、第3の実施形態について、先の第2の実施形態との相違点を中心に図面を参照しつつ説明する。

【0042】

図6に、本実施形態にかかるドライブユニットDUの回路構成を示す。なお、図6において、先の図4に示した部材に対応する部材については、便宜上同一の符号を付している。

【0043】

本実施形態では、端子T2aの電圧と閾値電圧VthHとの大小比較を行なう手段(コンパレータ62)と、端子T1aの電圧と閾値電圧VthLとの大小比較を行なう手段(コンパレータ64)と、これらの出力を切り替える手段(セレクタ66)とを備える。これにより、駆動回路22では、セレクタ66の出力に基づき、上記第2の実施形態と同様の処理を行なうことができる。

<その他の実施形態>

なお、上記各実施形態は、以下のように変更して実施してもよい。

「オン操作用回路について」

ゲートの充電速度を上昇させるための回路としては、上記各実施形態において例示したものに限らない。例えば、充電用スイッチング素子をバイポーラトランジスタによって構成し、そのベース電流を操作するものであってもよい。

「オフ操作用回路について」

ゲートの放電速度を上昇させるための回路としては、上記第2、第3の実施形態において例示したものに限らない。例えば、放電用スイッチング素子36の出力端子の電位を低下させる手段を備えて構成してもよい。また例えば、放電用スイッチング素子をバイポーラトランジスタによって構成し、そのベース電流を操作するものであってもよい。

「オン操作用変更処理手段について」

ミラー期間の終了の検出手法としては、ゲート電圧が閾値電圧VthHを上回ることを検出するものに限らない。例えば、ゲート電圧の上昇速度を検出する(ゲート電圧の上昇速度が低下した後上昇することを検出する)ものであってもよい。

「オフ操作用変更処理手段について」

ミラー期間の終了の検出手法としては、ゲート電圧が閾値電圧VthLを下回ることを検出するものに限らない。例えば、ゲート電圧の低下速度を検出する(ゲート電圧の低下速度が低下した後上昇することを検出する)ものであってもよい。

【0044】

オフ保持用スイッチング素子40のオフ操作処理と、放電用スイッチング素子36a,36bを操作する処理との双方を、ゲート電圧に基づき行うものであってもよい。

「割振手段について」

上記第2,3の実施形態において、オン操作期間において端子T2bの電圧を用いてもよい。上記第2,3の実施形態において、オフ操作期間において端子T1bの電圧を用いてもよい。

【0045】

また、上記第1の実施形態においても、閾値電圧VthHと端子T2の電圧との大小を比較する比較手段と、閾値電圧VthLと端子T1の電圧との大小を比較する比較手段とを備え、これら比較手段を同一のハードウェアにして入力信号を変更するか、別のハードウェアにして出力信号を選択する手段を備えるかしてもよい。この場合、比較手段の出力が入力される手段(駆動回路22)がオフ保持用スイッチング素子40を操作する処理と、充電速度を上昇させる処理とを行えばよい。

「ゲート抵抗について」

共通経路Laに抵抗体を備えてもよい。ただし、この場合であっても、充電用抵抗体32の抵抗値と放電用抵抗体34の抵抗値との双方よりも小さくすることが望ましい。この際、共通経路Laの抵抗値を上記双方の抵抗値と比較して小さくすればするほど、ゲート電圧の検出精度を高めることができる。

【0046】

放電用スイッチング素子36の出力端子とスイッチング素子S#*の出力端子との間に抵抗体を備えてもよい。この場合であっても、放電用抵抗体34をドライブI20に対して外付けしている場合等にあっては、オフ操作期間におけるゲート電圧の検出精度を上げるうえで端子T1の電圧を用いることが望ましい。

【0047】

充電用スイッチング素子24の入力端子とスイッチング素子S#*をオンとするための電荷の供給源との間に抵抗体を備えてもよい。この場合であっても、充電用抵抗体32をドライブIC20に対して外付けしている場合等にあっては、オン操作期間におけるゲート電圧の検出精度を上げるうえで端子T2の電圧を用いることが望ましい。

「そのほか」

・駆動対象スイッチング素子によって構成される電力変換回路としては、車載回転機とバッテリとの間に接続されるインバータIVやコンバータCVに限らない。例えば、車載高電圧バッテリの電力を低電圧バッテリに供給すべく、高電圧バッテリの電圧を降圧するDCDCコンバータであってもよい。

【0048】

・駆動対象スイッチング素子としては、IGBTに限らず、例えばMOS型電界効果トランジスタであってもよい。

【符号の説明】

【0049】

20…ドライブIC、36…放電用スイッチング素子、34…放電用抵抗体、40…オフ保持用スイッチング素子(短絡用スイッチング素子の一実施形態)、42…オフ保持回路、S#*…パワースイッチング素子、IV…インバータ(電力変換回路の一実施形態)、CV…コンバータ(電力変換回路の一実施形態)。

【特許請求の範囲】

【請求項1】

電圧制御形のスイッチング素子である駆動対象スイッチング素子をオン状態とするためのオン操作用回路と前記駆動対象スイッチング素子をオフ状態とするためのオフ操作用回路とを備え、これらを操作することで前記駆動対象スイッチング素子をオン・オフ操作するスイッチング素子の駆動回路において、

前記オン操作用回路は、充電用抵抗体の設けられた充電経路を備え、

前記オフ操作用回路は、前記充電用抵抗体とは別の放電用抵抗体の設けられた放電経路を備え、

前記駆動対象スイッチング素子の導通制御端子は、前記充電用抵抗体および前記放電用抵抗体の接続点を介してこれらのそれぞれに接続されるものであり、

前記駆動対象スイッチング素子のオン操作期間において該駆動対象スイッチング素子の導通制御端子の電圧の検出結果に基づき前記オン操作用回路の操作状態を変更する処理を行なうオン操作用変更処理手段と、

前記駆動対象スイッチング素子のオフ操作期間において前記導通制御端子の電圧の検出結果に基づき前記オフ操作用回路の操作状態を変更する処理を行なうオフ操作用変更処理手段とを備え、

前記オン操作用変更処理手段と前記オフ操作用変更処理手段とは、1チップ化された集積回路に内蔵されるものであり、

前記充電用抵抗体と前記放電用抵抗体との双方が前記集積回路に対して外付けされており、

前記オン操作用変更処理手段に入力される検出結果と前記オフ操作用変更処理手段に入力される検出結果とのそれぞれに、前記放電用抵抗体および前記集積回路の接続端子の電圧の検出結果と前記充電用抵抗体および前記集積回路の接続端子の電圧の検出結果とを割り振る割振手段を備えることを特徴とするスイッチング素子の駆動回路。

【請求項2】

前記オン操作用変更処理手段は、前記導通制御端子の電圧が上昇することで前記充電経路を介した前記駆動対象スイッチング素子をオン状態とするための電荷の充電速度を上昇させることを特徴とする請求項1記載のスイッチング素子の駆動回路。

【請求項3】

前記オフ操作用回路は、前記放電経路とは別に、前記駆動対象スイッチング素子の出力端子と前記導通制御端子とを短絡させる短絡用スイッチング素子をさらに備え、

前記オフ操作用変更処理手段は、前記導通制御端子の電圧の低下が検出されることに基づき前記短絡用スイッチング素子をオン操作することを特徴とする請求項1または2記載のスイッチング素子の駆動回路。

【請求項4】

前記オフ操作用変更処理手段は、前記導通制御端子の電圧の低下が検出されることに基づき前記放電経路を介した前記駆動対象スイッチング素子をオン状態とするための電荷の放電速度を上昇させることを特徴とする請求項1〜3のいずれか1項に記載のスイッチング素子の駆動回路。

【請求項5】

前記充電経路と前記放電経路との接続点と前記導通制御端子とは、共通の電気経路によって接続されており、

前記共通の電気経路の抵抗値は、前記充電用抵抗体の抵抗値と前記放電用抵抗体の抵抗値との双方と比較して小さく設定されていることを特徴とする請求項1〜4のいずれか1項に記載のスイッチング素子の駆動回路。

【請求項1】

電圧制御形のスイッチング素子である駆動対象スイッチング素子をオン状態とするためのオン操作用回路と前記駆動対象スイッチング素子をオフ状態とするためのオフ操作用回路とを備え、これらを操作することで前記駆動対象スイッチング素子をオン・オフ操作するスイッチング素子の駆動回路において、

前記オン操作用回路は、充電用抵抗体の設けられた充電経路を備え、

前記オフ操作用回路は、前記充電用抵抗体とは別の放電用抵抗体の設けられた放電経路を備え、

前記駆動対象スイッチング素子の導通制御端子は、前記充電用抵抗体および前記放電用抵抗体の接続点を介してこれらのそれぞれに接続されるものであり、

前記駆動対象スイッチング素子のオン操作期間において該駆動対象スイッチング素子の導通制御端子の電圧の検出結果に基づき前記オン操作用回路の操作状態を変更する処理を行なうオン操作用変更処理手段と、

前記駆動対象スイッチング素子のオフ操作期間において前記導通制御端子の電圧の検出結果に基づき前記オフ操作用回路の操作状態を変更する処理を行なうオフ操作用変更処理手段とを備え、

前記オン操作用変更処理手段と前記オフ操作用変更処理手段とは、1チップ化された集積回路に内蔵されるものであり、

前記充電用抵抗体と前記放電用抵抗体との双方が前記集積回路に対して外付けされており、

前記オン操作用変更処理手段に入力される検出結果と前記オフ操作用変更処理手段に入力される検出結果とのそれぞれに、前記放電用抵抗体および前記集積回路の接続端子の電圧の検出結果と前記充電用抵抗体および前記集積回路の接続端子の電圧の検出結果とを割り振る割振手段を備えることを特徴とするスイッチング素子の駆動回路。

【請求項2】

前記オン操作用変更処理手段は、前記導通制御端子の電圧が上昇することで前記充電経路を介した前記駆動対象スイッチング素子をオン状態とするための電荷の充電速度を上昇させることを特徴とする請求項1記載のスイッチング素子の駆動回路。

【請求項3】

前記オフ操作用回路は、前記放電経路とは別に、前記駆動対象スイッチング素子の出力端子と前記導通制御端子とを短絡させる短絡用スイッチング素子をさらに備え、

前記オフ操作用変更処理手段は、前記導通制御端子の電圧の低下が検出されることに基づき前記短絡用スイッチング素子をオン操作することを特徴とする請求項1または2記載のスイッチング素子の駆動回路。

【請求項4】

前記オフ操作用変更処理手段は、前記導通制御端子の電圧の低下が検出されることに基づき前記放電経路を介した前記駆動対象スイッチング素子をオン状態とするための電荷の放電速度を上昇させることを特徴とする請求項1〜3のいずれか1項に記載のスイッチング素子の駆動回路。

【請求項5】

前記充電経路と前記放電経路との接続点と前記導通制御端子とは、共通の電気経路によって接続されており、

前記共通の電気経路の抵抗値は、前記充電用抵抗体の抵抗値と前記放電用抵抗体の抵抗値との双方と比較して小さく設定されていることを特徴とする請求項1〜4のいずれか1項に記載のスイッチング素子の駆動回路。

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図2】

【図3】

【図4】

【図5】

【図6】

【公開番号】特開2012−16110(P2012−16110A)

【公開日】平成24年1月19日(2012.1.19)

【国際特許分類】

【出願番号】特願2010−148591(P2010−148591)

【出願日】平成22年6月30日(2010.6.30)

【出願人】(000004260)株式会社デンソー (27,639)

【Fターム(参考)】

【公開日】平成24年1月19日(2012.1.19)

【国際特許分類】

【出願日】平成22年6月30日(2010.6.30)

【出願人】(000004260)株式会社デンソー (27,639)

【Fターム(参考)】

[ Back to top ]