スイッチング素子の駆動回路

【課題】ドライブIC20の駆動対象が1つである場合、端子T6,T7がショートする異常によって、過電流保護機能が働かなくなるおそれがあること。

【解決手段】ドライブIC20は、駆動対象を2つのスイッチング素子とすることが可能であるが、ここでは単一のスイッチング素子S*#を駆動する。この際、スイッチング素子S*#を流れる電流と相関を有する微小電流によって生じる抵抗体50の電圧降下量(電圧Vsd)は、端子T6,T7の双方に入力される。ドライブIC20では、これら端子T6,T7の電圧と基準電源56の基準電圧との大小比較に基づき、スイッチング素子S*#に過電流が流れているか否かを判断する。

【解決手段】ドライブIC20は、駆動対象を2つのスイッチング素子とすることが可能であるが、ここでは単一のスイッチング素子S*#を駆動する。この際、スイッチング素子S*#を流れる電流と相関を有する微小電流によって生じる抵抗体50の電圧降下量(電圧Vsd)は、端子T6,T7の双方に入力される。ドライブIC20では、これら端子T6,T7の電圧と基準電源56の基準電圧との大小比較に基づき、スイッチング素子S*#に過電流が流れているか否かを判断する。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、駆動対象スイッチング素子の駆動制御を行うスイッチング素子の駆動回路に関する。

【背景技術】

【0002】

この種の駆動回路としては、例えば下記特許文献1に見られるように、絶縁ゲートバイポーラトランジスタ(IGBT)のエミッタ及びゲート間に、ゲートの電圧を所定電圧にクランプするためのツェナーダイオードとトランジスタとを接続し、IGBTのコレクタ電流の検出値(電圧信号)が閾値電圧よりも大きくなる場合にトランジスタをオン状態とするものも提案されている。これにより、IGBTのコレクタ電流がその信頼性の低下を招きかねない値となると判断される場合に、ゲートの電圧を規定値にクランプすることができ、ひいてはコレクタ電流を制限することができる。

【0003】

また、近年、車載インバータ等の電力変換回路にあっては、大電流を扱う関係上、複数のスイッチング素子を並列に設ける(パラ接続する)ことで、扱うことのできる電流量を倍増させることも提案され、実用化されている。このようにパラ接続を利用する場合、上記コレクタ電流の検出についても各スイッチング素子毎に行なわれることがある。

【0004】

一方、上記スイッチング素子の駆動制御を行ったり、上記ゲート電圧をクランプする手段等を集積回路によって構成することが周知である。ここで、上記パラ接続を利用する場合、集積回路に、上記コレクタ電流の検出値のそれぞれを入力する複数の端子を設けることとなる。

【0005】

ところで、上記集積回路を汎用性のあるものとするうえでは、上記パラ接続を想定して集積回路を構成しておき、パラ接続を利用しない場合にもこの集積回路を利用することが考えられる。この場合、上記コレクタ電流の検出値が入力される端子のなかに利用されないものが生じる。これに対しては、利用されない端子については、下記特許文献2に記載されているように、接地しておく(IGBTのエミッタと同電位としておく)ことが考えられる。これにより、この端子の電圧が閾値電圧よりも大きくなることがないため、上記ゲート電圧をクランプする機能が働くこともない。

【先行技術文献】

【特許文献】

【0006】

【特許文献1】特許第3558324号公報

【特許文献2】特開平11−87909号公報

【発明の概要】

【発明が解決しようとする課題】

【0007】

ただし、上記態様にてパラ接続を利用しないにもかかわらずパラ接続を想定した集積回路が用いられる場合、上記コレクタ電流の検出値が入力される複数の端子間が何らかの理由でショートする異常時において、コレクタ電流の検出値が実際に入力される端子の電位も接地に固定されるおそれがある。そしてこの場合、コレクタ電流が過度に大きくなる異常時においてもゲート電圧をクランプさせることができない。

【0008】

本発明は、上記課題を解決する過程でなされたものであり、その目的は、汎用性のある集積回路を用いつつも、駆動対象スイッチング素子の駆動制御の信頼性を向上させることのできるスイッチング素子の駆動回路を提供することにある。

【課題を解決するための手段】

【0009】

以下、上記課題を解決するための手段、およびその作用効果について記載する。

【0010】

請求項1記載の発明は、駆動対象スイッチング素子の駆動状態を検出して検出結果に応じた電圧信号を出力する検出手段と、該検出手段の出力する電圧信号を検出結果入力端子を介して取り込み、該電圧信号を参照しつつ前記駆動対象スイッチング素子の駆動制御を行う集積回路とを備え、前記集積回路は、前記検出結果入力端子を複数備えて且つ、前記検出結果入力端子のうち少なくとも2つに同一の電圧信号を入力すべくこれらが互いに接続されていることを特徴とする。

【0011】

上記発明では、検出結果入力端子を冗長設計することで、1の集積回路が駆動することのできる駆動対象スイッチング素子の数を変更することができ、ひいては集積回路を汎用性のあるものとすることができる。しかも、1の集積回路が実際に駆動する駆動対象スイッチング素子の数が駆動可能な最大数よりも小さくなることであまった検出結果入力端子を利用される検出結果入力端子に接続することで、このあまった検出結果入力端子には利用されるものと同様の電圧信号が入力されることとなる。このため、これらがショートする異常事態が生じたとしても、駆動対象スイッチング素子の駆動制御に支障が生じることがない。

【0012】

請求項2記載の発明は、請求項1記載の発明において、前記集積回路は、前記検出結果入力端子に入力される電圧信号に基づき、前記駆動対象スイッチング素子の駆動に異常が生じているか否かを判断する判断手段と、前記判断手段によって異常が生じていると判断される場合、前記駆動対象スイッチング素子の駆動を制限する制限手段とを備えることを特徴とする。

【0013】

上記発明は、電圧信号に基づき駆動対象スイッチング素子の駆動に異常が生じているか否かを判断し、異常が生じている場合には駆動を制限するものである。このため、検出結果入力端子のなかに利用されないものがあって且つこれと利用されるものとがショートすることで、利用される端子から入力される電圧信号が不適切な値となる場合には、異常であるにもかかわらず駆動を制限することができなくなるおそれがある。このため、複数の検出結果入力端子を互いに接続する手法の利用価値が特に大きい。

【0014】

請求項3記載の発明は、請求項2記載の発明において、前記検出手段の出力する電圧信号は、前記駆動対象スイッチング素子を流れる電流と正の相関を有するものであり、前記判断手段は、前記検出結果入力端子から入力される電圧信号が閾値電圧よりも大きい場合、前記駆動対象スイッチング素子に異常が生じていると判断することを特徴とする。

【0015】

請求項4記載の発明は、請求項1または2記載の発明において、前記駆動対象スイッチング素子は、電圧制御形のスイッチング素子であり、前記検出手段の出力する電圧信号は、前記駆動対象スイッチング素子の電流の流通経路の一対の端部のいずれか一方および開閉制御端子間の電位差であることを特徴とする

請求項5記載の発明は、請求項2記載の発明において、前記検出手段は、前記集積回路の外部に設けられた定電流源と、前記駆動対象スイッチング素子の付近に配置された感温ダイオードとを備えて構成され、前記判断手段は、前記感温ダイオードのアノード電圧が閾値電圧以下である場合、前記駆動対象スイッチング素子に異常が生じていると判断することを特徴とする。

【0016】

請求項6記載の発明は、請求項1〜5のいずれか1項に記載の発明において、前記集積回路は、前記検出結果入力端子が前記電圧信号の入力のための信号線に接続されないオープン状態においてその電位を固定する手段を内部に備えないことを特徴とする。

【0017】

上記発明では、検出結果入力端子の電位を固定する手段を内部に備えないため、複数の検出結果入力端子同士を接続する場合としない場合とで、電圧信号の検出値の変化を抑制する設定が容易となる。

【図面の簡単な説明】

【0018】

【図1】第1の実施形態にかかるシステム構成図。

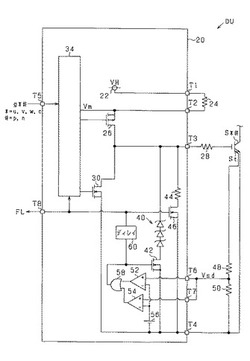

【図2】同実施形態にかかるドライブユニットの回路構成を示す回路図。

【図3】第2の実施形態にかかるドライブユニットの回路構成を示す回路図。

【図4】第3の実施形態にかかるドライブユニットの回路構成を示す回路図。

【発明を実施するための形態】

【0019】

<第1の実施形態>

以下、本発明にかかるスイッチング素子の駆動回路を車載主機に接続される電力変換回路に適用した第1の実施形態について、図面を参照しつつ説明する。

【0020】

図1に、本実施形態にかかる制御システムの全体構成を示す。モータジェネレータ10は、車載主機であり、図示しない駆動輪に機械的に連結されている。モータジェネレータ10は、インバータINVおよび昇圧コンバータCNVを介して高電圧バッテリ12に接続されている。ここで、昇圧コンバータCNVは、コンデンサCと、コンデンサCに並列接続された一対のスイッチング素子Scp,Scnと、一対のスイッチング素子Scp,Scnの接続点と高電圧バッテリ12の正極とを接続するリアクトルLとを備えている。そして、スイッチング素子Scp,Scnのオン・オフによって、高電圧バッテリ12の電圧(例えば百V以上)を所定の電圧(例えば「666V」)を上限として昇圧するものである。一方、インバータINVは、スイッチング素子Sup,Sunの直列接続体と、スイッチング素子Svp,Svnの直列接続体と、スイッチング素子Swp,Swnの直列接続体とを備えており、これら各直列接続体の接続点がモータジェネレータ10のU,V,W相にそれぞれ接続されている。これらスイッチング素子S*#(*=u,v,w,c;#=p,n)として、本実施形態では、絶縁ゲートバイポーラトランジスタ(IGBT)が用いられている。そして、これらにはそれぞれ、ダイオードD*#が逆並列に接続されている。

【0021】

制御装置18は、低電圧バッテリ16を電源とする制御装置である。制御装置18は、モータジェネレータ10を制御対象とし、その制御量を所望に制御すべく、インバータINVや昇圧コンバータCNVを操作する。詳しくは、昇圧コンバータCNVのスイッチング素子Scp,Scnを操作すべく、操作信号gcp、gcnをドライブユニットDUに出力する。また、インバータINVのスイッチング素子Sup,Sun,Svp,Svn,Swp,Swnを操作すべく、操作信号gup,gun,gvp,gvn,gwp,gwnをドライブユニットDUに出力する。ここで、高電位側の操作信号g*pと、対応する低電位側の操作信号g*nとは、互いに相補的な信号となっている。換言すれば、高電位側のスイッチング素子S*pと、対応する低電位側のスイッチング素子S*nとは、交互にオン状態とされる。

【0022】

ここで、高電圧バッテリ12を備える高電圧システムと低電圧バッテリ16を備える低電圧システムとは、互いに絶縁されており、これらの間の信号の授受は、例えばフォトカプラ等の絶縁素子を備えるインターフェース14を介して行われる。

【0023】

図2に、上記ドライブユニットDUの構成を示す。

【0024】

図示されるように、ドライブユニットDUは、1チップ化された半導体集積回路であるドライブIC20を備えている。ドライブIC20は、端子電圧VHを有する直流電圧源22を備え、直流電圧源22の端子は、端子T1、定電流用抵抗体24、端子T2、PチャネルMOS電界効果トランジスタ(定電流用スイッチング素子26)、端子T3、およびゲート抵抗28を介してスイッチング素子S*#の開閉制御端子(ゲート)に接続されている。

【0025】

一方、端子T3は、NチャネルMOS電界効果トランジスタ(放電用スイッチング素子30)を介して端子T4に接続されている。そして、端子T4は、スイッチング素子S*#の出力端子(エミッタ)に接続されている。

【0026】

上記定電流用スイッチング素子26および放電用スイッチング素子30は、ドライブIC20内の駆動制御部34によって操作される。すなわち、駆動制御部34では、端子T5を介して入力される上記操作信号g*#に基づき、定電流用スイッチング素子26と放電用スイッチング素子30とを交互にオン・オフすることでスイッチング素子S*#を駆動する。詳しくは、操作信号g*#がオン操作指令となることで、放電用スイッチング素子30をオフして且つ定電流用スイッチング素子26をオンする。一方、操作信号g*#がオフ操作指令となることで、定電流用スイッチング素子26をオフして且つ放電用スイッチング素子30をオンする。

【0027】

ここで、定電流用スイッチング素子26をオン操作する期間においては、その開閉制御端子(ゲート)への印加電圧を、定電流用抵抗体24の電圧降下量(端子T2の電圧Vm)を規定値に制御するために操作する。これにより、定電流用抵抗体24を流れる電流量を一定値とすることができ、ひいてはスイッチング素子S*#のゲート充電処理を定電流制御にて行うことができる。なお、定電流用スイッチング素子26を用いた定電流制御によれば、スイッチング素子S*#のゲート電圧は、端子電圧VHに収束する。ゲート電圧が収束値へと近づくと、定電流制御の制御性が低下する。これは、ゲート電圧Vgeが端子電圧VHから定電流用抵抗体24の電圧降下量と定電流用スイッチング素子26の電圧降下量の最小値とを減算した値以上となると、定電流用スイッチング素子26のゲート電圧の操作によっては、定電流用抵抗体24の電圧降下量を規定値に制御することができなくなるためである。このため、端子電圧VHは、スイッチング素子S*#の正常駆動時においてスイッチング素子S*#を流れる電流の最大値を飽和電流とするゲート電圧までは、定電流制御の制御性が低下しない値に設定されている。

【0028】

上記端子T3は、また、ツェナーダイオード40およびクランプ用スイッチング素子42の直列接続体を介して端子T4に接続されている。ここで、ツェナーダイオード40のブレークダウン電圧は、スイッチング素子S*#に過度の電流が流れない程度にスイッチング素子S*#のゲート電圧を制限するものである。

【0029】

上記端子T3は、さらに、ソフト遮断用抵抗体44およびソフト遮断用スイッチング素子46を介して端子T4に接続されている。

【0030】

一方、上記スイッチング素子S*#は、その入力端子(コレクタ)および出力端子(エミッタ)間に流れる電流(コレクタ電流)と相関を有する微少電流を出力するセンス端子Stを備えている。そして、センス端子Stは、抵抗体48,50の直列接続体を介してエミッタに電気的に接続されている。これにより、センス端子Stから出力される電流によって抵抗体50に電圧降下が生じるため、抵抗体50による電圧降下量を、スイッチング素子S*#の入力端子および出力端子間を流れる電流と相関を有する電気的な状態量とすることができる。

【0031】

上記抵抗体50による電圧降下量(抵抗体48,50の接続点の電圧Vsd)は、端子T6を介して、コンパレータ52の非反転入力端子に取り込まれるとともに、端子T7を介してコンパレータ54の非反転入力端子に取り込まれる。一方、コンパレータ52,54の反転入力端子には、基準電源56の基準電圧Vrefが印加されている。これにより、コレクタ電流が過電流閾値Ith以上となることで、コンパレータ52,54の出力信号が論理「L」から論理「H」に反転する。コンパレータ52,54の出力する論理「H」の信号は、OR回路58を介してクランプ用スイッチング素子42に印加されるとともに、ディレイ60に取り込まれる。ディレイ60は、入力信号が所定時間に渡って論理「H」となることで、フェール信号FLを出力する。フェール信号FLは、スイッチング素子S*#を強制的にオフ状態とすべく、ソフト遮断用スイッチング素子46をオン操作したり、定電流用スイッチング素子26および放電用スイッチング素子30の駆動を停止させるべく駆動制御部34に指令するものである。

【0032】

こうした構成によれば、スイッチング素子S*#に過電流が流れる場合には、まずクランプ用スイッチング素子42のオン操作に伴ってツェナーダイオード40がオン状態とされることで、スイッチング素子S*#のゲート電圧が低下する。これにより、スイッチング素子S*#を流れる電流を制限することができる。そしてその後、過電流が所定時間継続する場合には、ソフト遮断用スイッチング素子46がオン状態とされることから、スイッチング素子S*#が強制的にオフとされる。

【0033】

これにより、コレクタ電流が過電流閾値Ith以上となる状態が所定時間以上継続することで、ソフト遮断用スイッチング素子46がオンとされ、ソフト遮断用抵抗体44およびゲート抵抗28を介して、スイッチング素子S*#のゲートの電荷が放電される。ここで、ソフト遮断用抵抗体44は、放電経路の抵抗値を高抵抗とするためのものである。これは、コレクタ電流が過大である状況下にあっては、スイッチング素子S*#をオン状態からオフ状態へと切り替える速度、換言すればコレクタおよびエミッタ間の遮断速度を大きくすると、サージが過大となるおそれがあることに鑑みたものである。このため、コレクタ電流が過電流閾値Ith以上となると判断される状況下にあっては、ゲート抵抗28および放電用スイッチング素子30を備える放電経路よりも抵抗値の大きい経路によってスイッチング素子S*#のゲートを放電させる。

【0034】

なお、上記クランプ用スイッチング素子42およびツェナーダイオード40を備えるクランプ回路によるクランプ電圧を、本実施形態では、スイッチング素子S*#を流れる電流を規定値(≧過電流閾値Ith)以下に制限する値に設定する。また、フェール信号FLは、端子T8を介して低電圧システム(制御装置18)に出力される。このフェール信号FLによって、先の図1に示すフェール処理部14aでは、インバータINVや昇圧コンバータCNVをシャットダウンする。ちなみに、フェール処理部14aの構成は、例えば特開2009−60358号公報の図3に記載のものとすればよい。

【0035】

本実施形態にかかるドライブIC20は、駆動対象とするスイッチング素子S*#を1つまたは2つとするものである。そして、駆動対象となるスイッチング素子S*#を単一とするか2つとするかに応じて、端子T3から出力される電流量(ゲート充電速度)を調節すべく、抵抗体24がドライブIC20に対して外付けされ、その抵抗値が調節される。また、端子T3から入力される電流量(ゲート放電速度)を調節すべく、ゲート抵抗28がドライブIC20に対して外付けされ、その抵抗値が調節される。また、端子T3に接続されるスイッチング素子S*#の数が2つである場合に対処すべく、電圧Vsdを取り込む一対の入力端子T6,T7を備える。そして、端子T6,T7の少なくとも一方で過電流閾値Ithを上回ると判断される場合に、スイッチング素子S*#を流れる電流を制限する。

【0036】

ただし、端子T3に接続されるスイッチング素子S*#のゲートが単一である場合、端子T6,T7のいずれか一方は本来使用されないものである。ここで、たとえば端子T7を接地(スイッチング素子S*#のエミッタ)に接続するなら、コンパレータ54が論理「H」に反転することもない。ただしこの場合、端子T6,T7間がショートする異常が生じる場合には、抵抗体50の電圧降下量(電圧Vsd)が過電流閾値Ithに対応するものであったとしても、コンパレータ52が論理「L」を出力し続けることとなる。

【0037】

これに対し、本実施形態では、端子T6,T7を同電位とすべくこれらをショートさせる(低インピーダンスで接続する)。これにより、端子T6,T7の双方に、単一のスイッチング素子S*#のコレクタ電流の検出電圧信号(電圧Vsd)を印加することができるため、上述した事態を回避することができる。

【0038】

以上詳述した本実施形態によれば、以下の効果が得られるようになる。

【0039】

(1)ドライブIC20についての同一の物理量の検出結果を入力する検出結果入力端子(端子T6,T7)を同電位とすべく、これらをショートさせた。これにより、これらの間でショートが生じる異常事態が生じたとしても、スイッチング素子S*#の駆動制御に支障が生じることがない。

【0040】

(2)検出結果入力端子(T6,T7)が電圧信号の入力のための信号線に接続されないオープン状態においてその電位を固定する手段を内部に備えないようにした。この場合、たとえば端子T6,T7を抵抗体を介して端子T4にプルダウンするなどして電位固定手段を備える場合と比較して、端子T6,T7をショートさせる場合とさせない場合とで、電圧Vsdの検出値が変化しないため、電圧Vsdの検出精度が低下する事態を回避することができる。

<第2の実施形態>

以下、第2の実施形態について、先の第1の実施形態との相違点を中心に図面を参照しつつ説明する。

【0041】

図3に、上記ドライブユニットDUの構成を示す。なお、図3において、先の図2に示した部材に対応するものについては、便宜上同一のステップ番号を付している。

【0042】

本実施形態では、直流電圧源22の端子電圧VLを、スイッチング素子S*#の信頼性を低下させるおそれのある電流の下限値を飽和電流とするゲート電圧よりも低く設定する。そして、これとは別に端子電圧VLよりも大きい端子電圧VHを有する直流電圧源32を備え、直流電圧源32を、定電圧用スイッチング素子33、端子T9を介してゲート抵抗28に接続する。これにより、スイッチング素子S*#をオン状態に切り替えるに際しては、そのゲートをまず定電流制御によって充電する。そして、ミラー期間を過ぎることと規定時間が経過することとの論理積が真となることを条件に、定電流用スイッチング素子26をオフして且つ、定電圧用スイッチング素子33をオンしてスイッチング素子S*#のゲートに端子電圧VHを印加する。これは、スイッチング素子S*#のオン状態への切り替えに際してスイッチング素子S*#に過度に大きい電流が流れることを回避するためのものである。

【0043】

すなわち、オン状態への切り替えに際して過度に大きい電流が流れる場合、上記クランプ用スイッチング素子42の応答が間にあわない懸念がある。これに対し、本実施形態では、定電圧用スイッチング素子33をオン操作するまでは直流電圧源22の端子電圧VLによってスイッチング素子S*#に流れる電流を制限することができる。なお、上記規定時間は、クランプ用スイッチング素子42の反応に要する時間以上に設定されている。

【0044】

上記ミラー期間が過ぎるか否かは、端子T10,T11を介して取り込まれるスイッチング素子S*#のゲートおよびエミッタ間電圧(ゲート電圧)に基づき判断される。ここで、一対の端子T10,T11を備えたのは、ドライブIC20が駆動可能なスイッチング素子を2つまでとすることと対応している。また、一対の端子T10,T11をショートさせたのは、本実施形態では、実際の駆動対象を単一のスイッチング素子S*#としたためである。

<第3の実施形態>

以下、第3の実施形態について、先の第1の実施形態との相違点を中心に図面を参照しつつ説明する。

【0045】

図4に、上記ドライブユニットDUの構成を示す。なお、図4において、先の図2に示した部材に対応するものについては、便宜上同一のステップ番号を付している。

【0046】

図示されるように、本実施形態では、スイッチング素子S*#の温度を検出する感温ダイオードSDを備える。感温ダイオードSDは、ドライブIC20に対して外付けされた直流電圧源70からの電荷が定電流源72を介して供給されるものである。感温ダイオードSDのカソードは端子T4に接続されており、アノードは、端子T12,T13に接続されている。これにより、感温ダイオードSDによる温度検出結果である電圧信号が端子T12,T13に印加されることとなる。

【0047】

端子T12,T13の電圧は、最小値算出回路74を介して異常判断部76に取り込まれる。すなわち、端子T12,T13の電圧のうち小さい方が異常判断部76に取り込まれる。異常判断部76では、感温ダイオードSDによって検出される温度がスイッチング素子S*#の信頼性の低下を招くほど過度に高い値であるか否かを判断し、過度に高いと判断される場合、フェール信号FLを出力する。ここで、最小値算出回路74を用いたのは、感温ダイオードSDのアノード電圧が温度と負の相関を有することに鑑み、ドライブIC20の駆動対象が2つである場合に、温度の高い方を用いて異常の有無を判断するためである。

【0048】

ここで、本実施形態では、駆動対象を2つとすることができるドライブIC20を用いて単一のスイッチング素子S*#が駆動されるため、端子T12,T13を同電位とすべくこれらをショートさせた。なお、本実施形態において、定電流源72をドライブIC20に対して外付けしたのは、端子T12,T13をショートさせることで、感温ダイオードSDのアノード電圧と温度との対応関係が変化することを回避するためである。すなわち、定電流源72をドライブIC20内において、端子T12,T13のそれぞれに設ける場合には、端子T12,T13をショートさせて1つの感温ダイオードSDに接続する場合と、端子T12,T13のそれぞれを各別の感温ダイオードSDに接続する場合とで、感温ダイオードSDのアノード電圧と温度との関係が相違することとなる。

<その他の実施形態>

なお、上記各実施形態は、以下のように変更して実施してもよい。

【0049】

「制限手段について」

上記第1の実施形態において、ツェナーダイオード40およびクランプ用スイッチング素子42を備えるクランプ回路と、ソフト遮断用スイッチング素子46と、駆動制御部34にオフ操作指令を出力する手段との全てを備える代わりに少なくとも1つを備えるものであってもよい。またこれに代えて、たとえば放電用スイッチング素子30を強制的にオン操作する手段としてもよい。

【0050】

「判断手段について」

上記第2の実施形態において、定電流制御時における端子T3および端子T10間の電位差や端子T3および端子T11間の電位差に基づき、定電流制御の異常の有無を判断するものであってもよい。これは、ゲート抵抗28に定電流が流れる場合、そのゲート抵抗28における電圧降下量は、一定値となることに鑑みたものである。

【0051】

また、「ゲート電圧の利用手法について」の欄も参照のこと。

【0052】

「検出手段について」

上記実施形態において例示したものに限らないことについては、「判断手段について」の欄に記載したとおりである。

【0053】

「集積回路内において端子の電位を固定する手段について」

上記各実施形態ではこれを備えないことを前提としたがこれに限らない。たとえば上記第3の実施形態において、直流電圧源70および定電流源72をドライブIC20内に備える場合には、端子T13に感温ダイオードSDを接続しないオープン状態において、端子T13の電位は直流電圧源70によって固定されるものと考えられる。ただし、この場合であっても、端子T12,T13がショートする場合には、感温ダイオードSDに流れる電流量が倍増することから感温ダイオードSDの出力電圧と温度との対応関係が想定外のものとなる。このため、上記第3の実施形態(図4)に例示したように端子T12および端子T13を接続することが有効である。ただし、この場合、感温ダイオードSDに流れる電流がパラ接続の有無で変化しないように、集積回路内の定電流源の電流を外部から操作可能とする。

【0054】

またたとえば、上記第1の実施形態において、ドライブIC20内において端子T6,T7を抵抗体を介して端子T4に接続する場合であっても、その抵抗値によっては、端子T6,T7をショートさせることによる電圧Vsdの検出値の変化を無視しうると考えられる。また、この場合、端子T6,T7と抵抗体48,50の接続点との間にそれぞれ抵抗体を設けることで上記検出値の変化を抑制してもよい。

【0055】

「検出結果入力端子同士の接続」

これらの接続手法としては、これらをショートするものに限らず、たとえば同一の抵抗値を有する抵抗体を介してそれぞれを検出手段(たとえば図3の抵抗体48,50の接続点)に接続するものであってもよい。

【0056】

「感温ダイオードSDのアノード電圧の利用手法について」

異常判断に利用されるものに限らず、たとえば制御装置18に出力される温度情報の取得手段として利用されるものであってもよい。

【0057】

「ゲート電圧の利用手法について」

上記第2の実施形態において利用したものに限らず、たとえばオン操作処理から規定時間経過時のゲート電圧が低いことに基づき、ゲートの駆動に異常が生じていることを判断するために利用してもよい。

【0058】

「1の集積回路によって駆動対象とされる駆動対象スイッチング素子の数について」

1つまたは2つに限らず、3つ以上の場合にも対処可能なものであってもよい。この場合、実際に駆動対象とされるスイッチング素子の数が1つであるなら、残りのそれぞれに対応する検出結果入力端子の全てを駆動対象とされるスイッチング素子に対応する検出結果入力端子に接続する。またたとえば、3つ以上に対処可能であって且つ実際に駆動対象とされるスイッチング素子の数が対処可能数よりも1つ少ない場合、残りの1つに対応する検出結果入力端子を駆動対象とされるスイッチング素子に対応する検出結果入力端子のいずれかに接続する。

【0059】

「駆動対象スイッチング素子について」

駆動対象スイッチング素子としては、IGBTに限らず、たとえばパワーMOS電界効果トランジスタ等であってもよい。この際、Nチャネルにも限らず、Pチャネルであってもよい。ただしこの場合、電流の流通経路の一対の端部のうちのいずれか一方の電位(ソース電位)に対して開閉制御端子の電位(ゲート電位)を低下させることでオン状態となるため、ゲートに「負」の電荷を充電することで駆動対象スイッチング素子がオン状態となる。

【0060】

「駆動対象スイッチング素子によって構成される電力変換回路について」

電力変換回路としては、回転機の端子を直流電源の正極および負極のそれぞれに選択的に接続する高電位側のスイッチング素子および低電位側のスイッチング素子を備える直流交流変換回路(インバータINV)や、高電位側のスイッチング素子および低電位側のスイッチング素子を備えるコンバータCNVに限らない。たとえば、高電圧バッテリ12の電圧を降圧して低電圧バッテリ16に印加する降圧コンバータであってもよい。ちなみに、この場合であっても、高電位側のスイッチング素子および低電位側のスイッチング素子の直列接続体を備える場合には、過電流保護機能の利用価値が大きくなる。

【0061】

「そのほか」

・スイッチング素子S*#をオン状態とするための電荷の充電処理としては、定電流制御を行なうものに限らず、たとえばスイッチング素子S*#の開閉制御端子と直流電圧源とを備えるループ経路に流れる充電電流を線形素子としての抵抗体によって制限することで充電処理を行なってもよい。

【0062】

・スイッチング素子S*#をオン状態とするための電荷の放電処理を、定電流制御によって行なってもよい。

【0063】

・上記第1の実施形態において、端子T4およびT6間の電圧や端子T4および端子T7間の電圧を差動増幅回路によって変換したものをコンパレータ52,54に入力するようにしてもよい。

【0064】

・モータジェネレータ10としては、車載主機に限らず、たとえばシリーズハイブリッド車に搭載される発電機であってもよい。

【符号の説明】

【0065】

20…ドライブIC(集積回路の一実施形態)、S*#…スイッチング素子(駆動対象スイッチング素子の一実施形態)、T6,T7…端子(検出結果入力端子の一実施形態)。

【技術分野】

【0001】

本発明は、駆動対象スイッチング素子の駆動制御を行うスイッチング素子の駆動回路に関する。

【背景技術】

【0002】

この種の駆動回路としては、例えば下記特許文献1に見られるように、絶縁ゲートバイポーラトランジスタ(IGBT)のエミッタ及びゲート間に、ゲートの電圧を所定電圧にクランプするためのツェナーダイオードとトランジスタとを接続し、IGBTのコレクタ電流の検出値(電圧信号)が閾値電圧よりも大きくなる場合にトランジスタをオン状態とするものも提案されている。これにより、IGBTのコレクタ電流がその信頼性の低下を招きかねない値となると判断される場合に、ゲートの電圧を規定値にクランプすることができ、ひいてはコレクタ電流を制限することができる。

【0003】

また、近年、車載インバータ等の電力変換回路にあっては、大電流を扱う関係上、複数のスイッチング素子を並列に設ける(パラ接続する)ことで、扱うことのできる電流量を倍増させることも提案され、実用化されている。このようにパラ接続を利用する場合、上記コレクタ電流の検出についても各スイッチング素子毎に行なわれることがある。

【0004】

一方、上記スイッチング素子の駆動制御を行ったり、上記ゲート電圧をクランプする手段等を集積回路によって構成することが周知である。ここで、上記パラ接続を利用する場合、集積回路に、上記コレクタ電流の検出値のそれぞれを入力する複数の端子を設けることとなる。

【0005】

ところで、上記集積回路を汎用性のあるものとするうえでは、上記パラ接続を想定して集積回路を構成しておき、パラ接続を利用しない場合にもこの集積回路を利用することが考えられる。この場合、上記コレクタ電流の検出値が入力される端子のなかに利用されないものが生じる。これに対しては、利用されない端子については、下記特許文献2に記載されているように、接地しておく(IGBTのエミッタと同電位としておく)ことが考えられる。これにより、この端子の電圧が閾値電圧よりも大きくなることがないため、上記ゲート電圧をクランプする機能が働くこともない。

【先行技術文献】

【特許文献】

【0006】

【特許文献1】特許第3558324号公報

【特許文献2】特開平11−87909号公報

【発明の概要】

【発明が解決しようとする課題】

【0007】

ただし、上記態様にてパラ接続を利用しないにもかかわらずパラ接続を想定した集積回路が用いられる場合、上記コレクタ電流の検出値が入力される複数の端子間が何らかの理由でショートする異常時において、コレクタ電流の検出値が実際に入力される端子の電位も接地に固定されるおそれがある。そしてこの場合、コレクタ電流が過度に大きくなる異常時においてもゲート電圧をクランプさせることができない。

【0008】

本発明は、上記課題を解決する過程でなされたものであり、その目的は、汎用性のある集積回路を用いつつも、駆動対象スイッチング素子の駆動制御の信頼性を向上させることのできるスイッチング素子の駆動回路を提供することにある。

【課題を解決するための手段】

【0009】

以下、上記課題を解決するための手段、およびその作用効果について記載する。

【0010】

請求項1記載の発明は、駆動対象スイッチング素子の駆動状態を検出して検出結果に応じた電圧信号を出力する検出手段と、該検出手段の出力する電圧信号を検出結果入力端子を介して取り込み、該電圧信号を参照しつつ前記駆動対象スイッチング素子の駆動制御を行う集積回路とを備え、前記集積回路は、前記検出結果入力端子を複数備えて且つ、前記検出結果入力端子のうち少なくとも2つに同一の電圧信号を入力すべくこれらが互いに接続されていることを特徴とする。

【0011】

上記発明では、検出結果入力端子を冗長設計することで、1の集積回路が駆動することのできる駆動対象スイッチング素子の数を変更することができ、ひいては集積回路を汎用性のあるものとすることができる。しかも、1の集積回路が実際に駆動する駆動対象スイッチング素子の数が駆動可能な最大数よりも小さくなることであまった検出結果入力端子を利用される検出結果入力端子に接続することで、このあまった検出結果入力端子には利用されるものと同様の電圧信号が入力されることとなる。このため、これらがショートする異常事態が生じたとしても、駆動対象スイッチング素子の駆動制御に支障が生じることがない。

【0012】

請求項2記載の発明は、請求項1記載の発明において、前記集積回路は、前記検出結果入力端子に入力される電圧信号に基づき、前記駆動対象スイッチング素子の駆動に異常が生じているか否かを判断する判断手段と、前記判断手段によって異常が生じていると判断される場合、前記駆動対象スイッチング素子の駆動を制限する制限手段とを備えることを特徴とする。

【0013】

上記発明は、電圧信号に基づき駆動対象スイッチング素子の駆動に異常が生じているか否かを判断し、異常が生じている場合には駆動を制限するものである。このため、検出結果入力端子のなかに利用されないものがあって且つこれと利用されるものとがショートすることで、利用される端子から入力される電圧信号が不適切な値となる場合には、異常であるにもかかわらず駆動を制限することができなくなるおそれがある。このため、複数の検出結果入力端子を互いに接続する手法の利用価値が特に大きい。

【0014】

請求項3記載の発明は、請求項2記載の発明において、前記検出手段の出力する電圧信号は、前記駆動対象スイッチング素子を流れる電流と正の相関を有するものであり、前記判断手段は、前記検出結果入力端子から入力される電圧信号が閾値電圧よりも大きい場合、前記駆動対象スイッチング素子に異常が生じていると判断することを特徴とする。

【0015】

請求項4記載の発明は、請求項1または2記載の発明において、前記駆動対象スイッチング素子は、電圧制御形のスイッチング素子であり、前記検出手段の出力する電圧信号は、前記駆動対象スイッチング素子の電流の流通経路の一対の端部のいずれか一方および開閉制御端子間の電位差であることを特徴とする

請求項5記載の発明は、請求項2記載の発明において、前記検出手段は、前記集積回路の外部に設けられた定電流源と、前記駆動対象スイッチング素子の付近に配置された感温ダイオードとを備えて構成され、前記判断手段は、前記感温ダイオードのアノード電圧が閾値電圧以下である場合、前記駆動対象スイッチング素子に異常が生じていると判断することを特徴とする。

【0016】

請求項6記載の発明は、請求項1〜5のいずれか1項に記載の発明において、前記集積回路は、前記検出結果入力端子が前記電圧信号の入力のための信号線に接続されないオープン状態においてその電位を固定する手段を内部に備えないことを特徴とする。

【0017】

上記発明では、検出結果入力端子の電位を固定する手段を内部に備えないため、複数の検出結果入力端子同士を接続する場合としない場合とで、電圧信号の検出値の変化を抑制する設定が容易となる。

【図面の簡単な説明】

【0018】

【図1】第1の実施形態にかかるシステム構成図。

【図2】同実施形態にかかるドライブユニットの回路構成を示す回路図。

【図3】第2の実施形態にかかるドライブユニットの回路構成を示す回路図。

【図4】第3の実施形態にかかるドライブユニットの回路構成を示す回路図。

【発明を実施するための形態】

【0019】

<第1の実施形態>

以下、本発明にかかるスイッチング素子の駆動回路を車載主機に接続される電力変換回路に適用した第1の実施形態について、図面を参照しつつ説明する。

【0020】

図1に、本実施形態にかかる制御システムの全体構成を示す。モータジェネレータ10は、車載主機であり、図示しない駆動輪に機械的に連結されている。モータジェネレータ10は、インバータINVおよび昇圧コンバータCNVを介して高電圧バッテリ12に接続されている。ここで、昇圧コンバータCNVは、コンデンサCと、コンデンサCに並列接続された一対のスイッチング素子Scp,Scnと、一対のスイッチング素子Scp,Scnの接続点と高電圧バッテリ12の正極とを接続するリアクトルLとを備えている。そして、スイッチング素子Scp,Scnのオン・オフによって、高電圧バッテリ12の電圧(例えば百V以上)を所定の電圧(例えば「666V」)を上限として昇圧するものである。一方、インバータINVは、スイッチング素子Sup,Sunの直列接続体と、スイッチング素子Svp,Svnの直列接続体と、スイッチング素子Swp,Swnの直列接続体とを備えており、これら各直列接続体の接続点がモータジェネレータ10のU,V,W相にそれぞれ接続されている。これらスイッチング素子S*#(*=u,v,w,c;#=p,n)として、本実施形態では、絶縁ゲートバイポーラトランジスタ(IGBT)が用いられている。そして、これらにはそれぞれ、ダイオードD*#が逆並列に接続されている。

【0021】

制御装置18は、低電圧バッテリ16を電源とする制御装置である。制御装置18は、モータジェネレータ10を制御対象とし、その制御量を所望に制御すべく、インバータINVや昇圧コンバータCNVを操作する。詳しくは、昇圧コンバータCNVのスイッチング素子Scp,Scnを操作すべく、操作信号gcp、gcnをドライブユニットDUに出力する。また、インバータINVのスイッチング素子Sup,Sun,Svp,Svn,Swp,Swnを操作すべく、操作信号gup,gun,gvp,gvn,gwp,gwnをドライブユニットDUに出力する。ここで、高電位側の操作信号g*pと、対応する低電位側の操作信号g*nとは、互いに相補的な信号となっている。換言すれば、高電位側のスイッチング素子S*pと、対応する低電位側のスイッチング素子S*nとは、交互にオン状態とされる。

【0022】

ここで、高電圧バッテリ12を備える高電圧システムと低電圧バッテリ16を備える低電圧システムとは、互いに絶縁されており、これらの間の信号の授受は、例えばフォトカプラ等の絶縁素子を備えるインターフェース14を介して行われる。

【0023】

図2に、上記ドライブユニットDUの構成を示す。

【0024】

図示されるように、ドライブユニットDUは、1チップ化された半導体集積回路であるドライブIC20を備えている。ドライブIC20は、端子電圧VHを有する直流電圧源22を備え、直流電圧源22の端子は、端子T1、定電流用抵抗体24、端子T2、PチャネルMOS電界効果トランジスタ(定電流用スイッチング素子26)、端子T3、およびゲート抵抗28を介してスイッチング素子S*#の開閉制御端子(ゲート)に接続されている。

【0025】

一方、端子T3は、NチャネルMOS電界効果トランジスタ(放電用スイッチング素子30)を介して端子T4に接続されている。そして、端子T4は、スイッチング素子S*#の出力端子(エミッタ)に接続されている。

【0026】

上記定電流用スイッチング素子26および放電用スイッチング素子30は、ドライブIC20内の駆動制御部34によって操作される。すなわち、駆動制御部34では、端子T5を介して入力される上記操作信号g*#に基づき、定電流用スイッチング素子26と放電用スイッチング素子30とを交互にオン・オフすることでスイッチング素子S*#を駆動する。詳しくは、操作信号g*#がオン操作指令となることで、放電用スイッチング素子30をオフして且つ定電流用スイッチング素子26をオンする。一方、操作信号g*#がオフ操作指令となることで、定電流用スイッチング素子26をオフして且つ放電用スイッチング素子30をオンする。

【0027】

ここで、定電流用スイッチング素子26をオン操作する期間においては、その開閉制御端子(ゲート)への印加電圧を、定電流用抵抗体24の電圧降下量(端子T2の電圧Vm)を規定値に制御するために操作する。これにより、定電流用抵抗体24を流れる電流量を一定値とすることができ、ひいてはスイッチング素子S*#のゲート充電処理を定電流制御にて行うことができる。なお、定電流用スイッチング素子26を用いた定電流制御によれば、スイッチング素子S*#のゲート電圧は、端子電圧VHに収束する。ゲート電圧が収束値へと近づくと、定電流制御の制御性が低下する。これは、ゲート電圧Vgeが端子電圧VHから定電流用抵抗体24の電圧降下量と定電流用スイッチング素子26の電圧降下量の最小値とを減算した値以上となると、定電流用スイッチング素子26のゲート電圧の操作によっては、定電流用抵抗体24の電圧降下量を規定値に制御することができなくなるためである。このため、端子電圧VHは、スイッチング素子S*#の正常駆動時においてスイッチング素子S*#を流れる電流の最大値を飽和電流とするゲート電圧までは、定電流制御の制御性が低下しない値に設定されている。

【0028】

上記端子T3は、また、ツェナーダイオード40およびクランプ用スイッチング素子42の直列接続体を介して端子T4に接続されている。ここで、ツェナーダイオード40のブレークダウン電圧は、スイッチング素子S*#に過度の電流が流れない程度にスイッチング素子S*#のゲート電圧を制限するものである。

【0029】

上記端子T3は、さらに、ソフト遮断用抵抗体44およびソフト遮断用スイッチング素子46を介して端子T4に接続されている。

【0030】

一方、上記スイッチング素子S*#は、その入力端子(コレクタ)および出力端子(エミッタ)間に流れる電流(コレクタ電流)と相関を有する微少電流を出力するセンス端子Stを備えている。そして、センス端子Stは、抵抗体48,50の直列接続体を介してエミッタに電気的に接続されている。これにより、センス端子Stから出力される電流によって抵抗体50に電圧降下が生じるため、抵抗体50による電圧降下量を、スイッチング素子S*#の入力端子および出力端子間を流れる電流と相関を有する電気的な状態量とすることができる。

【0031】

上記抵抗体50による電圧降下量(抵抗体48,50の接続点の電圧Vsd)は、端子T6を介して、コンパレータ52の非反転入力端子に取り込まれるとともに、端子T7を介してコンパレータ54の非反転入力端子に取り込まれる。一方、コンパレータ52,54の反転入力端子には、基準電源56の基準電圧Vrefが印加されている。これにより、コレクタ電流が過電流閾値Ith以上となることで、コンパレータ52,54の出力信号が論理「L」から論理「H」に反転する。コンパレータ52,54の出力する論理「H」の信号は、OR回路58を介してクランプ用スイッチング素子42に印加されるとともに、ディレイ60に取り込まれる。ディレイ60は、入力信号が所定時間に渡って論理「H」となることで、フェール信号FLを出力する。フェール信号FLは、スイッチング素子S*#を強制的にオフ状態とすべく、ソフト遮断用スイッチング素子46をオン操作したり、定電流用スイッチング素子26および放電用スイッチング素子30の駆動を停止させるべく駆動制御部34に指令するものである。

【0032】

こうした構成によれば、スイッチング素子S*#に過電流が流れる場合には、まずクランプ用スイッチング素子42のオン操作に伴ってツェナーダイオード40がオン状態とされることで、スイッチング素子S*#のゲート電圧が低下する。これにより、スイッチング素子S*#を流れる電流を制限することができる。そしてその後、過電流が所定時間継続する場合には、ソフト遮断用スイッチング素子46がオン状態とされることから、スイッチング素子S*#が強制的にオフとされる。

【0033】

これにより、コレクタ電流が過電流閾値Ith以上となる状態が所定時間以上継続することで、ソフト遮断用スイッチング素子46がオンとされ、ソフト遮断用抵抗体44およびゲート抵抗28を介して、スイッチング素子S*#のゲートの電荷が放電される。ここで、ソフト遮断用抵抗体44は、放電経路の抵抗値を高抵抗とするためのものである。これは、コレクタ電流が過大である状況下にあっては、スイッチング素子S*#をオン状態からオフ状態へと切り替える速度、換言すればコレクタおよびエミッタ間の遮断速度を大きくすると、サージが過大となるおそれがあることに鑑みたものである。このため、コレクタ電流が過電流閾値Ith以上となると判断される状況下にあっては、ゲート抵抗28および放電用スイッチング素子30を備える放電経路よりも抵抗値の大きい経路によってスイッチング素子S*#のゲートを放電させる。

【0034】

なお、上記クランプ用スイッチング素子42およびツェナーダイオード40を備えるクランプ回路によるクランプ電圧を、本実施形態では、スイッチング素子S*#を流れる電流を規定値(≧過電流閾値Ith)以下に制限する値に設定する。また、フェール信号FLは、端子T8を介して低電圧システム(制御装置18)に出力される。このフェール信号FLによって、先の図1に示すフェール処理部14aでは、インバータINVや昇圧コンバータCNVをシャットダウンする。ちなみに、フェール処理部14aの構成は、例えば特開2009−60358号公報の図3に記載のものとすればよい。

【0035】

本実施形態にかかるドライブIC20は、駆動対象とするスイッチング素子S*#を1つまたは2つとするものである。そして、駆動対象となるスイッチング素子S*#を単一とするか2つとするかに応じて、端子T3から出力される電流量(ゲート充電速度)を調節すべく、抵抗体24がドライブIC20に対して外付けされ、その抵抗値が調節される。また、端子T3から入力される電流量(ゲート放電速度)を調節すべく、ゲート抵抗28がドライブIC20に対して外付けされ、その抵抗値が調節される。また、端子T3に接続されるスイッチング素子S*#の数が2つである場合に対処すべく、電圧Vsdを取り込む一対の入力端子T6,T7を備える。そして、端子T6,T7の少なくとも一方で過電流閾値Ithを上回ると判断される場合に、スイッチング素子S*#を流れる電流を制限する。

【0036】

ただし、端子T3に接続されるスイッチング素子S*#のゲートが単一である場合、端子T6,T7のいずれか一方は本来使用されないものである。ここで、たとえば端子T7を接地(スイッチング素子S*#のエミッタ)に接続するなら、コンパレータ54が論理「H」に反転することもない。ただしこの場合、端子T6,T7間がショートする異常が生じる場合には、抵抗体50の電圧降下量(電圧Vsd)が過電流閾値Ithに対応するものであったとしても、コンパレータ52が論理「L」を出力し続けることとなる。

【0037】

これに対し、本実施形態では、端子T6,T7を同電位とすべくこれらをショートさせる(低インピーダンスで接続する)。これにより、端子T6,T7の双方に、単一のスイッチング素子S*#のコレクタ電流の検出電圧信号(電圧Vsd)を印加することができるため、上述した事態を回避することができる。

【0038】

以上詳述した本実施形態によれば、以下の効果が得られるようになる。

【0039】

(1)ドライブIC20についての同一の物理量の検出結果を入力する検出結果入力端子(端子T6,T7)を同電位とすべく、これらをショートさせた。これにより、これらの間でショートが生じる異常事態が生じたとしても、スイッチング素子S*#の駆動制御に支障が生じることがない。

【0040】

(2)検出結果入力端子(T6,T7)が電圧信号の入力のための信号線に接続されないオープン状態においてその電位を固定する手段を内部に備えないようにした。この場合、たとえば端子T6,T7を抵抗体を介して端子T4にプルダウンするなどして電位固定手段を備える場合と比較して、端子T6,T7をショートさせる場合とさせない場合とで、電圧Vsdの検出値が変化しないため、電圧Vsdの検出精度が低下する事態を回避することができる。

<第2の実施形態>

以下、第2の実施形態について、先の第1の実施形態との相違点を中心に図面を参照しつつ説明する。

【0041】

図3に、上記ドライブユニットDUの構成を示す。なお、図3において、先の図2に示した部材に対応するものについては、便宜上同一のステップ番号を付している。

【0042】

本実施形態では、直流電圧源22の端子電圧VLを、スイッチング素子S*#の信頼性を低下させるおそれのある電流の下限値を飽和電流とするゲート電圧よりも低く設定する。そして、これとは別に端子電圧VLよりも大きい端子電圧VHを有する直流電圧源32を備え、直流電圧源32を、定電圧用スイッチング素子33、端子T9を介してゲート抵抗28に接続する。これにより、スイッチング素子S*#をオン状態に切り替えるに際しては、そのゲートをまず定電流制御によって充電する。そして、ミラー期間を過ぎることと規定時間が経過することとの論理積が真となることを条件に、定電流用スイッチング素子26をオフして且つ、定電圧用スイッチング素子33をオンしてスイッチング素子S*#のゲートに端子電圧VHを印加する。これは、スイッチング素子S*#のオン状態への切り替えに際してスイッチング素子S*#に過度に大きい電流が流れることを回避するためのものである。

【0043】

すなわち、オン状態への切り替えに際して過度に大きい電流が流れる場合、上記クランプ用スイッチング素子42の応答が間にあわない懸念がある。これに対し、本実施形態では、定電圧用スイッチング素子33をオン操作するまでは直流電圧源22の端子電圧VLによってスイッチング素子S*#に流れる電流を制限することができる。なお、上記規定時間は、クランプ用スイッチング素子42の反応に要する時間以上に設定されている。

【0044】

上記ミラー期間が過ぎるか否かは、端子T10,T11を介して取り込まれるスイッチング素子S*#のゲートおよびエミッタ間電圧(ゲート電圧)に基づき判断される。ここで、一対の端子T10,T11を備えたのは、ドライブIC20が駆動可能なスイッチング素子を2つまでとすることと対応している。また、一対の端子T10,T11をショートさせたのは、本実施形態では、実際の駆動対象を単一のスイッチング素子S*#としたためである。

<第3の実施形態>

以下、第3の実施形態について、先の第1の実施形態との相違点を中心に図面を参照しつつ説明する。

【0045】

図4に、上記ドライブユニットDUの構成を示す。なお、図4において、先の図2に示した部材に対応するものについては、便宜上同一のステップ番号を付している。

【0046】

図示されるように、本実施形態では、スイッチング素子S*#の温度を検出する感温ダイオードSDを備える。感温ダイオードSDは、ドライブIC20に対して外付けされた直流電圧源70からの電荷が定電流源72を介して供給されるものである。感温ダイオードSDのカソードは端子T4に接続されており、アノードは、端子T12,T13に接続されている。これにより、感温ダイオードSDによる温度検出結果である電圧信号が端子T12,T13に印加されることとなる。

【0047】

端子T12,T13の電圧は、最小値算出回路74を介して異常判断部76に取り込まれる。すなわち、端子T12,T13の電圧のうち小さい方が異常判断部76に取り込まれる。異常判断部76では、感温ダイオードSDによって検出される温度がスイッチング素子S*#の信頼性の低下を招くほど過度に高い値であるか否かを判断し、過度に高いと判断される場合、フェール信号FLを出力する。ここで、最小値算出回路74を用いたのは、感温ダイオードSDのアノード電圧が温度と負の相関を有することに鑑み、ドライブIC20の駆動対象が2つである場合に、温度の高い方を用いて異常の有無を判断するためである。

【0048】

ここで、本実施形態では、駆動対象を2つとすることができるドライブIC20を用いて単一のスイッチング素子S*#が駆動されるため、端子T12,T13を同電位とすべくこれらをショートさせた。なお、本実施形態において、定電流源72をドライブIC20に対して外付けしたのは、端子T12,T13をショートさせることで、感温ダイオードSDのアノード電圧と温度との対応関係が変化することを回避するためである。すなわち、定電流源72をドライブIC20内において、端子T12,T13のそれぞれに設ける場合には、端子T12,T13をショートさせて1つの感温ダイオードSDに接続する場合と、端子T12,T13のそれぞれを各別の感温ダイオードSDに接続する場合とで、感温ダイオードSDのアノード電圧と温度との関係が相違することとなる。

<その他の実施形態>

なお、上記各実施形態は、以下のように変更して実施してもよい。

【0049】

「制限手段について」

上記第1の実施形態において、ツェナーダイオード40およびクランプ用スイッチング素子42を備えるクランプ回路と、ソフト遮断用スイッチング素子46と、駆動制御部34にオフ操作指令を出力する手段との全てを備える代わりに少なくとも1つを備えるものであってもよい。またこれに代えて、たとえば放電用スイッチング素子30を強制的にオン操作する手段としてもよい。

【0050】

「判断手段について」

上記第2の実施形態において、定電流制御時における端子T3および端子T10間の電位差や端子T3および端子T11間の電位差に基づき、定電流制御の異常の有無を判断するものであってもよい。これは、ゲート抵抗28に定電流が流れる場合、そのゲート抵抗28における電圧降下量は、一定値となることに鑑みたものである。

【0051】

また、「ゲート電圧の利用手法について」の欄も参照のこと。

【0052】

「検出手段について」

上記実施形態において例示したものに限らないことについては、「判断手段について」の欄に記載したとおりである。

【0053】

「集積回路内において端子の電位を固定する手段について」

上記各実施形態ではこれを備えないことを前提としたがこれに限らない。たとえば上記第3の実施形態において、直流電圧源70および定電流源72をドライブIC20内に備える場合には、端子T13に感温ダイオードSDを接続しないオープン状態において、端子T13の電位は直流電圧源70によって固定されるものと考えられる。ただし、この場合であっても、端子T12,T13がショートする場合には、感温ダイオードSDに流れる電流量が倍増することから感温ダイオードSDの出力電圧と温度との対応関係が想定外のものとなる。このため、上記第3の実施形態(図4)に例示したように端子T12および端子T13を接続することが有効である。ただし、この場合、感温ダイオードSDに流れる電流がパラ接続の有無で変化しないように、集積回路内の定電流源の電流を外部から操作可能とする。

【0054】

またたとえば、上記第1の実施形態において、ドライブIC20内において端子T6,T7を抵抗体を介して端子T4に接続する場合であっても、その抵抗値によっては、端子T6,T7をショートさせることによる電圧Vsdの検出値の変化を無視しうると考えられる。また、この場合、端子T6,T7と抵抗体48,50の接続点との間にそれぞれ抵抗体を設けることで上記検出値の変化を抑制してもよい。

【0055】

「検出結果入力端子同士の接続」

これらの接続手法としては、これらをショートするものに限らず、たとえば同一の抵抗値を有する抵抗体を介してそれぞれを検出手段(たとえば図3の抵抗体48,50の接続点)に接続するものであってもよい。

【0056】

「感温ダイオードSDのアノード電圧の利用手法について」

異常判断に利用されるものに限らず、たとえば制御装置18に出力される温度情報の取得手段として利用されるものであってもよい。

【0057】

「ゲート電圧の利用手法について」

上記第2の実施形態において利用したものに限らず、たとえばオン操作処理から規定時間経過時のゲート電圧が低いことに基づき、ゲートの駆動に異常が生じていることを判断するために利用してもよい。

【0058】

「1の集積回路によって駆動対象とされる駆動対象スイッチング素子の数について」

1つまたは2つに限らず、3つ以上の場合にも対処可能なものであってもよい。この場合、実際に駆動対象とされるスイッチング素子の数が1つであるなら、残りのそれぞれに対応する検出結果入力端子の全てを駆動対象とされるスイッチング素子に対応する検出結果入力端子に接続する。またたとえば、3つ以上に対処可能であって且つ実際に駆動対象とされるスイッチング素子の数が対処可能数よりも1つ少ない場合、残りの1つに対応する検出結果入力端子を駆動対象とされるスイッチング素子に対応する検出結果入力端子のいずれかに接続する。

【0059】

「駆動対象スイッチング素子について」

駆動対象スイッチング素子としては、IGBTに限らず、たとえばパワーMOS電界効果トランジスタ等であってもよい。この際、Nチャネルにも限らず、Pチャネルであってもよい。ただしこの場合、電流の流通経路の一対の端部のうちのいずれか一方の電位(ソース電位)に対して開閉制御端子の電位(ゲート電位)を低下させることでオン状態となるため、ゲートに「負」の電荷を充電することで駆動対象スイッチング素子がオン状態となる。

【0060】

「駆動対象スイッチング素子によって構成される電力変換回路について」

電力変換回路としては、回転機の端子を直流電源の正極および負極のそれぞれに選択的に接続する高電位側のスイッチング素子および低電位側のスイッチング素子を備える直流交流変換回路(インバータINV)や、高電位側のスイッチング素子および低電位側のスイッチング素子を備えるコンバータCNVに限らない。たとえば、高電圧バッテリ12の電圧を降圧して低電圧バッテリ16に印加する降圧コンバータであってもよい。ちなみに、この場合であっても、高電位側のスイッチング素子および低電位側のスイッチング素子の直列接続体を備える場合には、過電流保護機能の利用価値が大きくなる。

【0061】

「そのほか」

・スイッチング素子S*#をオン状態とするための電荷の充電処理としては、定電流制御を行なうものに限らず、たとえばスイッチング素子S*#の開閉制御端子と直流電圧源とを備えるループ経路に流れる充電電流を線形素子としての抵抗体によって制限することで充電処理を行なってもよい。

【0062】

・スイッチング素子S*#をオン状態とするための電荷の放電処理を、定電流制御によって行なってもよい。

【0063】

・上記第1の実施形態において、端子T4およびT6間の電圧や端子T4および端子T7間の電圧を差動増幅回路によって変換したものをコンパレータ52,54に入力するようにしてもよい。

【0064】

・モータジェネレータ10としては、車載主機に限らず、たとえばシリーズハイブリッド車に搭載される発電機であってもよい。

【符号の説明】

【0065】

20…ドライブIC(集積回路の一実施形態)、S*#…スイッチング素子(駆動対象スイッチング素子の一実施形態)、T6,T7…端子(検出結果入力端子の一実施形態)。

【特許請求の範囲】

【請求項1】

駆動対象スイッチング素子の駆動状態を検出して検出結果に応じた電圧信号を出力する検出手段と、

該検出手段の出力する電圧信号を検出結果入力端子を介して取り込み、該電圧信号を参照しつつ前記駆動対象スイッチング素子の駆動制御を行う集積回路とを備え、

前記集積回路は、前記検出結果入力端子を複数備えて且つ、

前記検出結果入力端子のうち少なくとも2つに同一の電圧信号を入力すべくこれらが互いに接続されていることを特徴とするスイッチング素子の駆動回路。

【請求項2】

前記集積回路は、前記検出結果入力端子に入力される電圧信号に基づき、前記駆動対象スイッチング素子の駆動に異常が生じているか否かを判断する判断手段と、

前記判断手段によって異常が生じていると判断される場合、前記駆動対象スイッチング素子の駆動を制限する制限手段とを備えることを特徴とする請求項1記載のスイッチング素子の駆動回路。

【請求項3】

前記検出手段の出力する電圧信号は、前記駆動対象スイッチング素子を流れる電流と正の相関を有するものであり、

前記判断手段は、前記検出結果入力端子から入力される電圧信号が閾値電圧よりも大きい場合、前記駆動対象スイッチング素子に異常が生じていると判断することを特徴とする請求項2記載のスイッチング素子の駆動回路。

【請求項4】

前記駆動対象スイッチング素子は、電圧制御形のスイッチング素子であり、

前記検出手段の出力する電圧信号は、前記駆動対象スイッチング素子の電流の流通経路の一対の端部のいずれか一方および開閉制御端子間の電位差であることを特徴とする請求項1または2記載のスイッチング素子の駆動回路。

【請求項5】

前記検出手段は、前記集積回路の外部に設けられた定電流源と、前記駆動対象スイッチング素子の付近に配置された感温ダイオードとを備えて構成され、

前記判断手段は、前記感温ダイオードのアノード電圧が閾値電圧以下である場合、前記駆動対象スイッチング素子に異常が生じていると判断することを特徴とする請求項2記載のスイッチング素子の駆動回路。

【請求項6】

前記集積回路は、前記検出結果入力端子が前記電圧信号の入力のための信号線に接続されないオープン状態においてその電位を固定する手段を内部に備えないことを特徴とする請求項1〜5のいずれか1項に記載のスイッチング素子の駆動回路。

【請求項1】

駆動対象スイッチング素子の駆動状態を検出して検出結果に応じた電圧信号を出力する検出手段と、

該検出手段の出力する電圧信号を検出結果入力端子を介して取り込み、該電圧信号を参照しつつ前記駆動対象スイッチング素子の駆動制御を行う集積回路とを備え、

前記集積回路は、前記検出結果入力端子を複数備えて且つ、

前記検出結果入力端子のうち少なくとも2つに同一の電圧信号を入力すべくこれらが互いに接続されていることを特徴とするスイッチング素子の駆動回路。

【請求項2】

前記集積回路は、前記検出結果入力端子に入力される電圧信号に基づき、前記駆動対象スイッチング素子の駆動に異常が生じているか否かを判断する判断手段と、

前記判断手段によって異常が生じていると判断される場合、前記駆動対象スイッチング素子の駆動を制限する制限手段とを備えることを特徴とする請求項1記載のスイッチング素子の駆動回路。

【請求項3】

前記検出手段の出力する電圧信号は、前記駆動対象スイッチング素子を流れる電流と正の相関を有するものであり、

前記判断手段は、前記検出結果入力端子から入力される電圧信号が閾値電圧よりも大きい場合、前記駆動対象スイッチング素子に異常が生じていると判断することを特徴とする請求項2記載のスイッチング素子の駆動回路。

【請求項4】

前記駆動対象スイッチング素子は、電圧制御形のスイッチング素子であり、

前記検出手段の出力する電圧信号は、前記駆動対象スイッチング素子の電流の流通経路の一対の端部のいずれか一方および開閉制御端子間の電位差であることを特徴とする請求項1または2記載のスイッチング素子の駆動回路。

【請求項5】

前記検出手段は、前記集積回路の外部に設けられた定電流源と、前記駆動対象スイッチング素子の付近に配置された感温ダイオードとを備えて構成され、

前記判断手段は、前記感温ダイオードのアノード電圧が閾値電圧以下である場合、前記駆動対象スイッチング素子に異常が生じていると判断することを特徴とする請求項2記載のスイッチング素子の駆動回路。

【請求項6】

前記集積回路は、前記検出結果入力端子が前記電圧信号の入力のための信号線に接続されないオープン状態においてその電位を固定する手段を内部に備えないことを特徴とする請求項1〜5のいずれか1項に記載のスイッチング素子の駆動回路。

【図1】

【図2】

【図3】

【図4】

【図2】

【図3】

【図4】

【公開番号】特開2012−178951(P2012−178951A)

【公開日】平成24年9月13日(2012.9.13)

【国際特許分類】

【出願番号】特願2011−41650(P2011−41650)

【出願日】平成23年2月28日(2011.2.28)

【出願人】(000004260)株式会社デンソー (27,639)

【Fターム(参考)】

【公開日】平成24年9月13日(2012.9.13)

【国際特許分類】

【出願日】平成23年2月28日(2011.2.28)

【出願人】(000004260)株式会社デンソー (27,639)

【Fターム(参考)】

[ Back to top ]