スイッチング素子の駆動回路

【課題】誤動作を防止することによって従来よりも信頼性を高めた、スイッチング素子の駆動回路を提供する。

【解決手段】スイッチング素子Q5の駆動回路HVICにおいて、論理回路U15は、内部状態に応じて高電位側のスイッチング素子Q5をオン/オフに切替えるための制御信号を出力する。第1の抵抗部RP1は、第3の電源ノードVBと第1のノードND1との間に設けられる。第2の抵抗部R2は、第1のノードND1と第2のノードND2との間に設けられる。第1の制御用スイッチング素子Q1は、第2のノードND2と第1の電源ノードGNDとの間に設けられ、第1のパルス信号PLS1を受けたときに導通する。第1の比較部U4は、第1のノードND1の電位が第1の閾値以下の場合に活性状態となる第1の信号Sonを出力する。第1および第2の抵抗部RP1,R2の少なくとも一方の抵抗値は、上記の制御信号の変化に基づいたタイミングで変化する。

【解決手段】スイッチング素子Q5の駆動回路HVICにおいて、論理回路U15は、内部状態に応じて高電位側のスイッチング素子Q5をオン/オフに切替えるための制御信号を出力する。第1の抵抗部RP1は、第3の電源ノードVBと第1のノードND1との間に設けられる。第2の抵抗部R2は、第1のノードND1と第2のノードND2との間に設けられる。第1の制御用スイッチング素子Q1は、第2のノードND2と第1の電源ノードGNDとの間に設けられ、第1のパルス信号PLS1を受けたときに導通する。第1の比較部U4は、第1のノードND1の電位が第1の閾値以下の場合に活性状態となる第1の信号Sonを出力する。第1および第2の抵抗部RP1,R2の少なくとも一方の抵抗値は、上記の制御信号の変化に基づいたタイミングで変化する。

【発明の詳細な説明】

【技術分野】

【0001】

この発明は半導体スイッチング素子の制御電極を駆動するための駆動回路に関する。

【背景技術】

【0002】

PWM(Pulse Width Modulation)インバータなどの電力変換装置には、直流電源の正極と負極との2つの半導体スイッチング素子が直列(いわゆるトーテムポール型)に接続されたアームが複数設けられる。各アームの高電位側のスイッチング素子を駆動する回路として近年、トランスやフォトカプラによる絶縁を行なわない、いわゆるレベルシフト回路が使用される。

【0003】

たとえば、特開2000−252809号公報(特許文献1)は、この種のレベルシフト回路の構成例を開示する。同文献によると、レベルシフト回路は、第1、第2の2つの可制御半導体素子と、直流電源と、第1、第2の2つの負荷抵抗と、ロジック回路と、信号無効化手段とを備える。各可制御半導体素子は、電位の基準となる電極が共通電位に接続され、この電位基準電極と制御電極との間に導通用信号を入力する期間、電位基準電極と主電極との間が導通状態となる。直流電源は、一極が共通電位と所定の高電位との間で変動する外部回路の所定の部位に接続され、この二電位間の電圧より低い電圧を持つ。第1、第2の2つの負荷抵抗は、この直流電源の他極に一端が接続され、他端がそれぞれ第1、第2の可制御半導体素子の主電極に接続される。ロジック回路は、上記の直流電源のもとで作動する。第1、第2の可制御半導体素子の制御電極には、それぞれにタイミングを異にしてパルス状の導通用信号が入力される。このときの可制御半導体素子の導通によって第1、第2の負荷抵抗に生ずるパルス状の電圧降下が信号としてロジック回路に伝えられる。信号無効化手段は、第1、第2の負荷抵抗に同時にパルス状の電圧降下が生じたときは、この電圧降下の信号をロジック回路へ伝えることを防止する。具体的に、信号無効化手段は、ロジック回路へ伝える第1の負荷抵抗の電圧降下の信号を、第2の負荷抵抗の電圧降下に基づき生成したマスク用信号によってマスクし、同じくロジック回路へ伝える第2の負荷抵抗の電圧降下の信号を、第1の負荷抵抗の電圧降下に基づき生成したマスク用信号によってマスクする。

【先行技術文献】

【特許文献】

【0004】

【特許文献1】特開2000−252809号公報

【発明の概要】

【発明が解決しようとする課題】

【0005】

上記文献のレベルシフト回路を含む駆動回路を用いて、高電位側のスイッチング素子を駆動してオフからオンに遷移させる場合あるいは低電位側のスイッチング素子を駆動してオンからオフに遷移させる場合、トーテムポールの中点電位が上昇する。このとき、各可制御半導体素子の主電極と基板(共通電位)との間の接合容量(寄生容量)を充電することになり、第1、第2の2つの負荷抵抗に寄生容量を充電する充電電流が流れる。この結果、第1、第2の負荷抵抗に同時に電圧降下が生じることになる。通常、製造上のばらつきなどによって第1、第2の可制御半導体素子の寄生容量にずれがあるので、第1、第2の負荷抵抗による電圧降下量にもずれが生じることになる。電圧降下量のずれが大きいと上記の信号無効化手段によるマスクが働かないので、ロジック回路に誤信号が伝えられる可能性がある。

【0006】

この発明の目的は、誤動作を防止することによって従来よりも信頼性を高めた、スイッチング素子の駆動回路を提供することである。

【課題を解決するための手段】

【0007】

この発明は一局面において、第1の電源ノードとそれより高電位に設定される第2の電源ノードとの間に直列に接続された2つのスイッチング素子のうち高電位側のスイッチング素子の駆動回路であって、第3の電源ノードと、論理回路と、第1および第2の抵抗部と、第1の制御用スイッチング素子と、第1の比較部とを備える。第3の電源ノードは、2つのスイッチング素子の接続ノードの電位よりも高電位に設定される。論理回路は、内部状態として第1および第2の状態を有し、内部状態に応じて高電位側のスイッチング素子をオン状態またはオフ状態に切替えるために、第1および第2の状態にそれぞれ対応して第1および第2の論理レベルに切替わる制御信号を出力する。第1の抵抗部は、第3の電源ノードと第1のノードとの間に設けられる。第2の抵抗部は、第1のノードと第2のノードとの間に設けられる。第1の制御用スイッチング素子は、第2のノードと第1の電源ノードとの間に設けられ、第1のパルス信号を受けたときに導通する。第1の比較部は、第1のパルス信号に応じて論理回路を第1の状態から第2の状態に切替えるために、第1のノードの電位が第1の閾値以下の場合に活性状態となる第1の信号を出力する。第1および第2の抵抗部の少なくとも一方の抵抗値は、少なくとも制御信号の変化に基づいたタイミングで変化する。

【発明の効果】

【0008】

この発明の一局面によるスイッチング素子の駆動回路によれば、第1および第2の抵抗部の少なくとも一方の抵抗値を、少なくとも制御信号の変化に基づいたタイミングで変化させることによって、誤動作を防止することができるので従来よりも信頼性を高めることができる。

【図面の簡単な説明】

【0009】

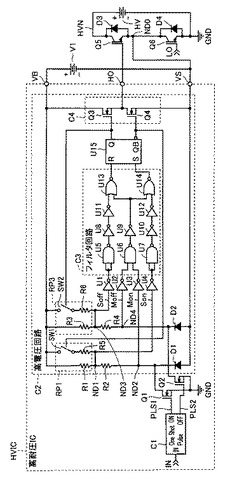

【図1】この発明の実施の形態1によるスイッチング素子の駆動回路(高耐圧IC)HVICの構成を示す回路図である。

【図2】図1の駆動回路HVICがHブリッジの高電位側スイッチング素子Q5に接続された場合を示す図である。

【図3】図1の駆動回路HVICの動作を示すタイミング図である。

【図4】図1の駆動回路HVICの変形例を示す回路図である。

【図5】この発明の実施の形態2によるスイッチング素子の駆動回路HVICbの構成を示す回路図である。

【図6】図1の駆動回路HVICの動作と図5の駆動回路HVICbの動作とを対比して示すタイミング図である。

【図7】図5の駆動回路HVICbにおいて、低電位側スイッチング素子Q6がターンオフする場合のタイミング図である。

【図8】この発明の実施の形態3によるスイッチング素子の駆動回路HVICcの構成を示す回路図である。

【図9】図8に示す定電流源I1の構成の一例を示す回路図である。

【図10】図8の駆動回路HVICcの動作を示すタイミング図である。

【図11】この発明の実施の形態4によるスイッチング素子の駆動回路HVICdの構成を示す回路図である。

【図12】図11の駆動回路HVICdの動作を示すタイミング図である。

【図13】この発明の実施の形態5によるスイッチング素子の駆動回路HVICeの構成を示す回路図である。

【図14】図13の駆動回路HVICeの動作を示すタイミング図である。

【図15】この発明の実施の形態6によるスイッチング素子の駆動回路HVICfの構成を示す回路図である。

【図16】図13の駆動回路HVICeの動作と図15の駆動回路HVICfの動作とを対比して示すタイミング図である。

【図17】図15の駆動回路HVICfにおいて、低電位側スイッチング素子Q6がターンオフする場合のタイミング図である。

【発明を実施するための形態】

【0010】

以下、この発明の実施の形態について図面を参照して詳しく説明する。なお、同一または相当する部分には同一の参照符号を付して、その説明を繰返さない。

【0011】

<実施の形態1>

[駆動回路HVICの構成]

図1は、この発明の実施の形態1によるスイッチング素子の駆動回路(高耐圧IC)HVICの構成を示す回路図である。

【0012】

図1を参照して、駆動回路HVICは、入力信号INに応じてトーテムポール接続された高電位側スイッチング素子Q5をオン状態およびオフ状態に駆動するための集積回路(IC:Integrated Circuit)である。高電位側スイッチング素子Q5および低電位側スイッチング素子Q6は、高電圧電源HVが接続される高電位側電源ノードHVNと低電位側電源ノード(接地ノード)GNDとの間に直列に接続される。図1には、高電位側スイッチング素子Q5および低電位側スイッチング素子Q6の一例としてIGBT(Insulated Gate Bipolar Transistor)が示される。

【0013】

高電位側スイッチング素子(IGBT)Q5のコレクタとエミッタとの間には高電位側フリーホイールダイオードD3が逆バイアス方向に接続される。低電位側スイッチング素子(IGBT)Q6のコレクタとエミッタとの間には低電位側フリーホイールダイオードD4が逆バイアス方向に接続される。高電位側スイッチング素子Q5と低電位側スイッチング素子Q6との接続ノードND0は、駆動回路HVICの仮想接地ノードVSに接続される。高電位側スイッチング素子Q5の制御電極(IGBTのゲート)は、駆動回路HVICの信号出力ノードHOに接続される。駆動回路HVICの電源ノードVBと仮想接地ノードVSの間には直流電源V1が接続される。低電位側スイッチング素子Q6の制御電極は、低電位側用の駆動回路の信号出力ノードLOと接続される。

【0014】

駆動回路HVICは、ワンショットパルス発生回路C1と、NMOS(Negative channel Metal Oxide Semiconductor)トランジスタQ1,Q2(制御用スイッチング素子)と、高電圧回路部C2とを含む。ワンショットパルス発生回路C1は、入力信号INの立上がりエッジに同期して高電位側スイッチング素子Q5をオン状態にするためのパルス信号PLS1を生成して出力し、入力信号INの立下がりエッジに同期して高電位側スイッチング素子Q5をオフ状態にするためのパルス信号PLS2を生成して出力する。

【0015】

NMOSトランジスタQ1は、高電圧回路部C2のノードND2と接地ノードGNDとの間に接続され、ワンショットパルス発生回路C1からパルス信号PLS1をゲートに受けることによって導通する。これによって高電圧回路部C2にパルス信号PLS1が伝達される。NMOSトランジスタQ2は、高電圧回路部C2のノードND4と接地ノードGNDとの間に接続され、ワンショットパルス発生回路C1からパルス信号PLS2をゲートに受けることによって導通する。これによって高電圧回路部C2にパルス信号PLS2が伝達される。

【0016】

ワンショットパルス発生回路C1によってパルス信号PLS1,PLS2をNMOSトランジスタQ1,Q2のゲートに供給する理由は、NMOSトランジスタQ1,Q2の負荷抵抗として用いられている抵抗素子R1〜R4の電流消費を抑えるためである。入力信号がパルス信号であるので、入力信号を保持するためにRSフリップフロップU15が高電圧回路部C2に設けられている。

【0017】

高電圧回路部C2は、抵抗素子R1〜R4と、クランプ用のダイオードD1,D2と、インバータU1〜U4と、フィルタ回路C3と、RSフリップフロップU15と、出力段回路C4とを含む。

【0018】

抵抗素子R1,R2は、この順番で電源ノードVBとノードND2との間に直列に接続される(以下、抵抗素子R1,R2の接続ノードをノードND1と称する)。NMOSトランジスタQ1がパルス信号PLS1を受けて導通すると、抵抗素子R1,R2およびNMOSトランジスタQ1を介して電源ノードVBから接地ノードGNDに電流が流れる。これによって抵抗素子R1,R2に生じたパルス状の電圧降下が、ノードND1,ND2

での電位変化として検出される。

【0019】

同様に抵抗素子R3,R4は、この順番で電源ノードVBとノードND4との間に直列に接続される(以下、抵抗素子R3,R4の接続ノードをノードND3と称する)。NMOSトランジスタQ2がパルス信号PLS2を受けて導通すると、抵抗素子R3,R4およびNMOSトランジスタQ2を介して電源ノードVBから接地ノードGNDに電流が流れる。これによって抵抗素子R3,R4に生じたパルス状の電圧降下が、ノードND3,ND4での電位変化として検出される。

【0020】

ノードND1の電位変化は高電位側スイッチング素子Q5をオン状態にするためのオン信号Sonとして用いられる。ノードND3の電位変化は高電位側スイッチング素子Q5をオフ状態にするためのオフ信号Soffとして用いられる。ノードND2の電位変化は、オフ信号Soffをマスクするためのマスク信号Monとして用いられる。ノードND4の電位変化はオン信号Sonをマスクするためのマスク信号Moffとして用いられる。

【0021】

ダイオードD1は、抵抗素子R1,R2に過大な電流が流れないように、仮想接地ノードVSとノードND2との間に、仮想接地ノードVS側がアノードとなるように接続される。ダイオードD2は、抵抗素子R3,R4に過大な電流が流れないように、仮想接地ノードVSとノードND4との間に、仮想接地ノードVS側がアノードとなるように接続される。

【0022】

インバータU1〜U4は直流電源V1によって駆動される。インバータU4は、ノードND1からオン信号Sonを受けて、オン信号SonがインバータU4の閾値以下になるとハイレベル(Hレベルとも記載する)の信号を出力する、インバータU3は、ノードND2からマスク信号Monを受けて、マスク信号MonがインバータU3の閾値以下になるとHレベルの信号を出力する。インバータU1は、ノードND3からオフ信号Soffを受けて、オフ信号SoffがインバータU1の閾値以下になるとHレベルの信号を出力する。インバータU2は、ノードND4からマスク信号Moffを受けて、マスク信号MoffがインバータU2の閾値以下になるとHレベルの信号を出力する。以下の説明では、インバータU1〜U4の閾値は全て等しいとする。

【0023】

フィルタ回路C3は、NAND回路U5〜U7と、インバータU8〜U12と、NOR回路U13,U14とを含む。これらの各要素およびRSフリップフロップU15は直流電源V1によって駆動される。

【0024】

NAND回路U7は、インバータU4の出力の論理レベルを反転するNOT回路(インバータ)として用いられる。NAND回路U7の出力はインバータU10,U12を介して、NOR回路U14の第1の入力ノードに入力される。したがって、NOR回路U14の第1の入力ノードには、オン信号SonがインバータU4の閾値以下となったとき、ローレベル(Lレベルとも記載する)の信号が入力される。

【0025】

NAND回路U5は、インバータU1の出力の論理レベルを反転するNOT回路(インバータ)として用いられる。NAND回路U5の出力はインバータU8,U11を介して、NOR回路U13の第1の入力ノードに入力される。したがって、NOR回路U13の第1の入力ノードには、オフ信号SoffがインバータU1の閾値以下となったとき、Lレベルの信号が入力される。

【0026】

NAND回路U6は、インバータU2およびU3の出力を受ける。NAND回路U6の出力は、インバータU9を介してNOR回路U13,U14の各第2の入力ノードに入力される。したがって、NOR回路U13,U14の各第2の入力ノードには、マスク信号MonがインバータU3の閾値以下となりかつマスク信号MoffがインバータU2の閾値以下となったときに、Hレベルの信号が入力される。

【0027】

NOR回路U14の出力はRSフリップフロップU15のセット端子(S)に入力され、NOR回路U13の出力はRSフリップフロップU15のリセット端子(R)に入力される。したがって、RSフリップフロップU15のセット端子(S)には、オン信号SonがインバータU4の閾値以下となりかつマスク信号MoffがインバータU2の閾値を超えていれば、Hレベルの信号が入力される。RSフリップフロップU15のリセット端子(R)には、オフ信号SoffがインバータU1の閾値以下となりかつマスク信号MonがインバータU3の閾値を超えていれば、Hレベルの信号が入力される。

【0028】

出力段回路C4は、NMOSトランジスタQ3,Q4を含む。NMOSトランジスタQ3,Q4は、この順で電源ノードVBと仮想接地ノードVSとの間に直列に接続される。NMOSトランジスタQ3のゲートはRSフリップフロップU15の出力端子(Q)と接続され、NMOSトランジスタQ4のゲートはRSフリップフロップU15の反転出力端子(QB)と接続される。NMOSトランジスタQ3,Q4の接続ノードは信号出力ノードHOを介して、高電位側スイッチング素子Q5の制御電極(IGBTのゲート)に接続される。したがって、RSフリップフロップU15がセットされた状態のとき、高電位側スイッチング素子Q5がオン状態になり、RSフリップフロップU15がリセットされた状態のとき、高電位側スイッチング素子Q5がオフ状態になる。

【0029】

高電圧回路部C2は、さらに、抵抗素子R5,R6と、スイッチSW1,SW2とを含む。

【0030】

抵抗素子R5は、電源ノードVBとノードND1との間に抵抗素子R1と並列に設けられる。スイッチSW1(制御用スイッチング素子)は、電源ノードVBとノードND1との間に抵抗素子R5と直列に設けられる。スイッチSW1は、RSフリップフロップU15の反転出力端子(QB)の出力信号がHレベルになったときオン状態になる。

【0031】

抵抗素子R6は、電源ノードVBとノードND3との間に抵抗素子R3と並列に設けられる。スイッチSW2(制御用スイッチング素子)は、電源ノードVBとノードND3との間に抵抗素子R6と直列に設けられる。スイッチSW2は、RSフリップフロップU15の出力端子(Q)の出力信号がHレベルになったときオン状態になる。

【0032】

スイッチSW1,SW2として、たとえば、PMOS(Positive channel Metal Oxide Semiconductor)トランジスタやNMOSトランジスタを用いることができる。PMOSトランジスタを用いる場合は、RSフリップフロップU15の出力端子(Q)または反転出力端子(QB)とPMOSトランジスタのゲートとの間にインバータが設けられる。

【0033】

図1において、抵抗素子R1,R5とスイッチSW1とによって抵抗部RP1が構成される。抵抗部RP1の抵抗値は、RSフリップフロップU15の反転出力端子(QB)の論理レベルに応じて変化する。抵抗素子R3,R6とスイッチSW2とによって抵抗部RP3が構成される。抵抗部RP3の抵抗値は、RSフリップフロップU15の出力端子(Q)の論理レベルに応じて変化する。図1の駆動回路HVICでは、このような抵抗値の変化する抵抗部RP1,RP3をNMOSトランジスタQ1,Q2の負荷抵抗として用いることによって、駆動回路HVICの誤動作を防止することができる。

【0034】

[誤動作のメカニズム]

抵抗部RP1,RP3の動作を説明するのに先立って、抵抗部RP1,RP3に代えて抵抗素子R1,R3が設けられている場合(すなわち、抵抗素子R5,R6およびスイッチSW1,SW2が設けられていない場合)に、駆動回路HVICに誤動作が生じる理由について説明する。

【0035】

図2は、図1の駆動回路HVICがHブリッジの高電位側スイッチング素子Q5に接続された場合を示す図である。図2を参照して、高電位側電源ノードHVNと接地ノードGNDとの間には、さらに、高電位側スイッチング素子Q5bと低電位側スイッチング素子Q6bがこの順で直列に接続される。スイッチング素子Q5b,Q6bとそれぞれ逆並列にフリーホイールダイオードD3b,D4bが設けられる。スイッチング素子Q5,Q6の接続ノードND0と、スイッチング素子Q5b,Q6bの接続ノードND0bとの間に誘導性の負荷L1が接続される。図2において、スイッチング素子Q5,Q6,Q5b,Q6bはIGBTである。

【0036】

図2において、トランジスタQ5b,Q6がオン状態、トランジスタQ5,Q6bがオフ状態であったとする。この状態から、トランジスタQ6がオフ状態になると、オン状態のトランジスタQ5b、負荷L1、およびダイオードD3を介してフリーホイール電流が流れる。この結果、ノードND0(仮想接地ノードVS)の電位が上昇する(言い換えると、仮想接地ノードVSに正のdV/dtが印加される)。電源ノードVBの電位は仮想接地ノードVSの電位に直流電源V1の電圧を加算した値に等しいので、仮想接地ノードVSの電位が上昇すると電源ノードVBの電位も同じ電圧変化率で上昇する。

【0037】

トランジスタQ5b,Q6がオフ状態、トランジスタQ5,Q6bがオン状態の場合にも同様のことが生じる。この状態から、トランジスタQ6bがオフ状態になると、ノードND0(すなわち、仮想接地ノードVS)の電位が上昇する(すなわち、仮想接地ノードVSに正のdV/dtが印加される)場合がある。3相インバータの場合も上記と同様に、仮想接地ノードVSの電位が上昇する(すなわち、仮想接地ノードVSに正のdV/dtが印加される)場合がある。

【0038】

再び図1を参照して、駆動回路HVICの信号出力ノードHOがLレベルの状態で、ノードLOの電位がHレベルからLレベルに変化したことによって、低電位側スイッチング素子Q6がオン状態からオフ状態に変化したとする。このとき、仮想接地ノードVSの電位および電源ノードVBの電位は低電位側スイッチング素子Q6のスイッチングスピードに応じて上昇する。この結果、NMOSトランジスタQ1,Q2のドレインと基板間の接合容量(寄生容量)が充電されることになるので、抵抗素子R1,R2および抵抗素子R3,R4に寄生容量の充電電流が流れる。この充電電流による電圧降下によって、次段のインバータU1〜U4の入力電位(Son,Mon,Soff,Moff)は低下する。ここで、オン信号用のNMOSトランジスタQ1の寄生容量のほうがオフ信号用のNMOSトランジスタQ2の寄生容量よりも大きければ、ノードND1,ND2の電位(すなわち、オン信号Sonおよびマスク信号Mon)のほうがノードND3,ND4の電位(すなわち、オフ信号Soffおよびマスク信号Moff)よりも低下することになる。この結果、マスク信号MoffがインバータU2の閾値よりも低下する前にオン信号SonがインバータU4の閾値よりも低下すれば、RSフリップフロップU15のセット端子(S)にHレベルの信号が入力され、これによって、高電位側スイッチング素子Q5はオフ状態からオン状態へと誤動作することになる。

【0039】

[駆動回路HVICの動作]

図3は、図1の駆動回路HVICの動作を示すタイミング図である。図3では、上から順に、低電位側スイッチング素子Q6のゲート駆動信号の波形(LO)、仮想接地ノードVS(電源ノードVB)の電圧変化、オン信号Son、マスク信号Mon、オフ信号Soff、およびマスク信号Moffの電圧波形、インバータU2、U1,U3,U4の各出力電圧波形、RSフリップフロップU15の反転出力端子(QB)、出力端子(Q)、リセット端子(R)、およびセット端子(S)の各電圧波形、ならびに駆動回路HVICの信号出力ノードHOの電圧波形が示される。以下、図1、図3を参照して図1の抵抗部RP1,RP3の機能について説明する。

【0040】

図3において、初期状態ではRSフリップフロップU15はリセットされた状態であり、その出力端子(Q)はLレベルであり、反転出力端子(QB)はHレベルである。この結果、駆動回路HVICの信号出力ノードHOはLレベルになり、抵抗部RP1のスイッチSW1はオン状態になり、抵抗部RP3のスイッチSW2はオフ状態になる。スイッチSW1がオン状態であるので、抵抗部RP1の抵抗値(電源ノードVBとノードND1との間の抵抗値)は、抵抗素子R1とR5との並列合成抵抗(R1//R5と記載する)となり、スイッチSW1がオフ状態の場合の抵抗値(抵抗素子R1の抵抗値)より小さい。一方、抵抗部RP3の抵抗値(電源ノードVBとノードND3との間の抵抗値)は、スイッチSW2がオフ状態であるので抵抗素子R3の抵抗値であり、抵抗素子R3とR6との並列合成抵抗(R3//R6と記載する)よりも大きい。

【0041】

時刻t1で低電位側スイッチング素子Q6用のゲート駆動回路の信号出力ノードLOがHレベルからLレベルに切替わる。これによって、仮想接地ノードVSの電位が低電位側スイッチング素子Q6のスイッチングスピードに応じて上昇するので、NMOSトランジスタQ1,Q2のドレインと基板との間の接合容量(寄生容量)が充電される。このとき、抵抗部RP1(電源ノードVBとノードND1との間)の抵抗値(R1//R5)と、抵抗部RP3(電源ノードVBとノードND3との間)の抵抗値(R3)との違いによって電圧降下量が異なるので、ノードND3,ND4の電位(Soff,Moff)はノードND1,ND2の電位(Son,Mon)よりも低くなる。

【0042】

このため、時刻t2でマスク信号Moffが最初にインバータU2の閾値TH以下となる。これによって、インバータU2の出力がHレベルに切替わる。次に時刻t3でオフ信号SoffがインバータU1の閾値TH以下となることによって、インバータU1の出力がHレベルに切替わる。次に時刻t4でマスク信号MonがインバータU3の閾値TH以下となることによって、インバータU3の出力がHレベルに切替わる。次に時刻t5でオン信号SonがインバータU4の閾値TH以下となることによって、インバータU4の出力がHレベルに切替わる。時刻t3からt4の間で、RSフリップフロップU15のリセット端子(R)への入力がHレベルになるが、RSフリップフロップU15は元々リセットされた状態であるので出力端子(Q)および反転出力端子(QB)の論理レベルは変化しない。この結果、駆動回路HVICの信号出力ノードHOはLレベルを維持し、駆動回路HVICは正常な動作を行なうことができる。

【0043】

次の時刻t6で、ダイオードD1,D2が導通し、ノードND1〜ND4の電位(Son,Mon,Soff,Moff)は一定値にクランプされる。次の時刻t7で仮想接地ノードVSの電位上昇が0になるので、ノードND1〜ND4の電位(Son,Soff,Mon,Moff)は元の電位(電源ノードVBの電位)に戻る。

【0044】

[変形例]

図4は、図1の駆動回路HVICの変形例を示す回路図である。この変形例では、図4(A)に示すように電源ノードVBと接地ノードGNDとの間に、抵抗素子R1、抵抗部RP2、およびMOSトランジスタQ1がこの順で直列に設けられる。さらに、図4(B)に示すように電源ノードVBと接地ノードGNDとの間に、抵抗素子R3、抵抗部RP4、およびMOSトランジスタQ2がこの順で直列に設けられる。

【0045】

図4(A)を参照して、抵抗部RP2は、ノードND1,ND2間に設けられた抵抗素子R2と、ノードND2とNMOSトランジスタQ1のドレイン(ノードND7)との間に設けられた抵抗素子R7と、抵抗素子R7と並列に設けられたスイッチSW1とを含む。スイッチSW1は、RSフリップフロップU15の出力端子(Q)がHレベルのときオン状態になり、Lレベルのときオフ状態になる。したがって、RSフリップフロップU15がセット状態の場合には、NMOSトランジスタQ1の寄生容量による充電電流が抵抗素子R7を流れずにスイッチSW1を介してバイパスされる。一方、RSフリップフロップU15がリセット状態の場合には、NMOSトランジスタQ1の寄生容量による充電電流が抵抗素子R7を流れるので、ノードND1,ND2の電位の低下がセット状態の場合に比べて減少する。この結果、誤動作を防止することができる。

【0046】

図4(B)を参照して、抵抗部RP3は、ノードND3,ND4間に設けられた抵抗素子R3と、ノードND4とNMOSトランジスタQ2のドレイン(ノードND8)との間に設けられた抵抗素子R8と、抵抗素子R8と並列に設けられたスイッチSW2とを含む。スイッチSW2は、RSフリップフロップU15の反転出力端子(QB)がHレベルのときオン状態になり、Lレベルのときオフ状態になる。したがって、RSフリップフロップU15がリセット状態の場合には、NMOSトランジスタQ2の寄生容量による充電電流が抵抗素子R8を流れずにスイッチSW2を介してバイパスされる。一方、RSフリップフロップU15がセット状態の場合には、NMOSトランジスタQ2の寄生容量による充電電流が抵抗素子R8を流れるので、ノードND3,ND4の電位の低下がセット状態の場合に比べて減少する。この結果、誤動作を防止することができる。

【0047】

以上をまとめると、電源ノードVBとオン信号Sonが検出されるノードND1との間に抵抗部RP1が設けられ、ノードND1とNMOSトランジスタQ1との間に抵抗部RP2が設けられる。そして、RSフリップフロップU15がリセット状態(高電位側スイッチング素子Q5がオフ状態)の場合にはセット状態(高電位側スイッチング素子Q5がオン状態)の場合に比べて、抵抗部RP1の抵抗値に対する抵抗部RP2の抵抗値の比率が増加するように、抵抗部RP1,RP2の少なくとも一方の抵抗値が変化する。これによって、高電位側のスイッチング素子Q5がオフ状態からオン状態に誤動作するのを防止できる。

【0048】

同様に、電源ノードVBとオフ信号Soffが検出されるノードND3との間に抵抗部RP3が設けられ、ノードND3とNMOSトランジスタQ2との間に抵抗部RP4が設けられる。そして、RSフリップフロップU15がセット状態(高電位側スイッチング素子Q5がオン状態)の場合にはリセット状態(高電位側スイッチング素子Q5がオフ状態)の場合に比べて、抵抗部RP3の抵抗値に対する抵抗部RP4の抵抗値の比率が増加するように、抵抗部RP3,RP4の少なくとも一方の抵抗値が変化する。これによって、高電位側のスイッチング素子Q5がオン状態からオフ状態に誤動作するのを防止できる。

【0049】

<実施の形態2>

図1に示す実施の形態1による駆動回路HVICでは、スイッチSW1およびSW2のいずれかが常時オン状態になっている。このため、パルス信号PLS1がNMOSトランジスタQ1に入力されたときにRSフリップフロップU15のセット端子(S)に入力される信号のパルス幅や、パルス信号PLS2がNMOSトランジスタQ2に入力されたときにRSフリップフロップU15のリセット端子(R)に入力される信号のパルス幅が、従来よりも短くなる。この結果、従来よりもノイズ耐量が低下するという問題がある。

【0050】

実施の形態2による駆動回路HVICbでは、仮想接地ノードVSの電位が上昇した場合のみスイッチSW1,SW2が導通状態になるように、スイッチSW1,SW2の制御シーケンスをマスク信号Mon,Moffを用いたものに変更する。これによってノイズ耐量の低下を防止することができる。以下、具体的に説明する。

【0051】

図5は、この発明の実施の形態2によるスイッチング素子の駆動回路HVICbの構成を示す回路図である。

【0052】

図5の高電圧回路部C2bに設けられた抵抗部RP1bは、AND回路U16をさらに含む点で図1の抵抗部RP1と異なる。AND回路U16は、RSフリップフロップU15の反転出力端子(QB)の出力とインバータU2の出力とを受け、両方の出力ともHレベルのときにHレベルの信号をスイッチSW1に供給する。スイッチSW1は、AND回路U16から受けた信号がHレベルのとき導通する。

【0053】

図5の高電圧回路部C2bに設けられた抵抗部RP3bは、AND回路U17をさらに含む点で図1の抵抗部RP3と異なる。AND回路U17は、RSフリップフロップU15の出力端子(Q)の出力とインバータU3の出力とを受け、両方の出力ともHレベルのときにHレベルの信号をスイッチSW2に供給する。スイッチSW2は、AND回路U17から受けた信号がHレベルのとき導通する。

【0054】

図5のその他の点は図1の場合と同じであるので、同一または相当する部分には同一の参照符号を付して説明を繰返さない。

【0055】

図6は、図1の駆動回路HVICの動作と図5の駆動回路HVICbの動作とを対比して示すタイミング図である。図6の左側のグラフには高電位側スイッチング素子Q5をターンオンさせる場合の駆動回路HVIC(実施の形態1)の各部の電圧波形が示される。図6の右側のグラフには同じ場合の駆動回路HVICb(実施の形態2)の各部の電圧波形が示される。左右のそれぞれのグラフにおいて、上から順に、ワンショットパルス発生回路C1の入力信号INおよび出力パルス信号PLS1,PLS2の各電圧波形、オン信号Son、マスク信号Mon、オフ信号Soff、およびマスク信号Moffの電圧波形、インバータU3、U4,U2,U1の各出力電圧波形、RSフリップフロップU15の出力端子(Q)および反転出力端子(QB)の電圧波形、スイッチSW2,SW1のオン/オフの状態、RSフリップフロップU15のセット端子(S)およびリセット端子(R)の各電圧波形ならびに駆動回路HVIC,HVICbの信号出力ノードHOの電圧波形が示される。

【0056】

まず、図1および図6の左側のグラフを参照して、実施の形態1による駆動回路HVICの場合について説明する。この場合、初期状態では、ワンショットパルス発生回路C1の入力信号INがLレベルである。このとき、RSフリップフロップU15はリセットされた状態であるので、出力端子(Q)はLレベルであり、反転出力端子(QB)はHレベルである。図1の駆動回路HVICの場合には、スイッチSW1がオン状態になっているため、抵抗部RP1(ノードND1と電源ノードVBとの間)の抵抗値は抵抗素子R1の抵抗値と抵抗素子R5の抵抗値との並列合成抵抗(R1//R5)になる。

【0057】

時刻t1に入力信号INがHレベルに切替わることによってワンショットパルス発生回路C1からパルス信号PLS1(パルス幅は時刻t1から時刻t4まで)が出力される。この結果、ノードND1,ND2の電位(Son,Mon)が低下する。

【0058】

次の時刻t2に、ノードND2の電位(マスク信号Mon)がインバータU3の閾値TH以下となるので、インバータU3の出力がHレベルに切替わる。

【0059】

次の時刻t3に、ノードND1の電位(オン信号Son)がインバータU4の閾値TH以下となるので、インバータU4の出力がHレベルに切替わる。これによって、RSフリップフロップU15のセット端子(S)の入力がHレベルになるので、RSフリップフロップU15の出力端子(Q)がHレベルに切替わり、反転出力端子(QB)がLレベルに切替わり、駆動回路HVICの信号出力ノードHOがHレベルに切替わる。さらに、RSフリップフロップU15の出力端子(Q)および反転出力端子(QB)の電圧変化に伴ってスイッチSW1がオフ状態になり、スイッチSW2がオン状態になる。スイッチSW1がオフ状態になると、抵抗部RP1(ノードND1と電源ノードVBとの間)の抵抗値は抵抗素子R1の抵抗値に増大するので、時刻t3以前よりも急峻にオン信号Sonおよびマスク信号Monが低下する。

【0060】

次の時刻t4で、NMOSトランジスタQ1のゲート入力(PLS2)が0Vに戻るので、ノードND1,ND2の電位(Son,Mon)が元の電位(電源ノードVBの電位)に戻る。この結果、インバータU3,U4の出力がLレベルに切替わり、RSフリップフロップU15へのセット端子(S)への入力がLレベルに戻る。

【0061】

次に、図1および図6の右側のグラフを参照して、実施の形態2による駆動回路HVICbの場合について説明する。この場合、初期状態では、スイッチSW1がオフ状態である点を除いて左側のグラフと同じである。スイッチSW1はRSフリップフロップU15の反転出力端子(QB)の出力とインバータU2との出力によって制御される。初期状態では反転出力端子(QB)はHレベルであるが、インバータU2の出力がLレベルであるので、スイッチSW1はオフ状態となっている。この結果、抵抗部RP1b(ノードND1と電源ノードVBとの間)の抵抗値は抵抗素子R1の抵抗値に等しい。

【0062】

時刻t11で、入力信号INがHレベルに切替わることによってワンショットパルス発生回路C1からパルス信号PLS1(パルス幅は時刻t11から時刻t14まで)が出力される。この結果、ノードND1,ND2の電位(Son,Mon)が低下する。このときの電位低下の速度は、図6の左側のグラフに比べてノードVB,ND1間の抵抗値が増大したために速くなる。

【0063】

時刻t12で、ノードND2の電位(マスク信号Mon)がインバータU3の閾値TH以下となるので、インバータU3の出力がHレベルに切替わる。

【0064】

次の時刻t13で、ノードND1の電位(オン信号Son)がインバータU4の閾値TH以下となるので、インバータU4の出力がHレベルに切替わる。これによって、RSフリップフロップU15のセット端子(S)の入力がHレベルになるので、RSフリップフロップU15の出力端子(Q)がHレベルに切替わり、反転出力端子(QB)がLレベルに切替わり、駆動回路HVICbの信号出力ノードHOがHレベルに切替わる。このとき、インバータU3の出力がHレベルであるので、スイッチSW2がオン状態になる。

【0065】

次の時刻t14で、NMOSトランジスタQ1のゲート入力(PLS2)が0Vに戻るので、ノードND1,ND2の電位(Son,Mon)が元の電位(電源ノードVBの電位)に戻る。この結果、インバータU3,U4の出力がLレベルに切替わり、RSフリップフロップU15へのセット端子(S)への入力がLレベルに戻り、スイッチSW2がオフ状態に戻る。

【0066】

RSフリップフロップU15のセット端子(S)に入力される信号のパルス幅を、実施の形態1の場合(時刻t3から時刻t4まで)と実施の形態2の場合(時刻t13から時刻t14まで)とを比較する。そうすると、実施の形態2の場合のパルス幅(時刻t13から時刻t14まで)は、実施の形態1の場合のパルス幅(時刻t3から時刻t4まで)に比べて長くなる。この結果、実施の形態2の場合のノイズ耐量は実施の形態1の場合に比べて改善する。

【0067】

図7は、図5の駆動回路HVICbにおいて、低電位側スイッチング素子Q6がターンオフする場合のタイミング図である。図7では、上から順に、低電位側スイッチング素子Q6のゲート駆動信号の波形(LO)、仮想接地ノードVS(電源ノードVB)の電圧変化、オン信号Son、マスク信号Mon、オフ信号Soff、およびマスク信号Moffの電圧波形、インバータU2、U1,U3,U4の各出力電圧波形、RSフリップフロップU15の反転出力端子(QB)および出力端子(Q)の各電圧波形、スイッチSW1,SW2のオン/オフの状態、RSフリップフロップU15のリセット端子(R)およびセット端子(S)の各電圧波形ならびに駆動回路HVICbの信号出力ノードHOの電圧波形が示される。

【0068】

図7において、初期状態ではRSフリップフロップU15はリセット状態にあり、その出力端子(Q)はLレベルであり、反転出力端子(QB)はHレベルである。この結果、駆動回路HVICbの信号出力ノードHOはLレベルになり、抵抗部RP3のスイッチSW2はオフ状態になる。抵抗部RP1のスイッチSW1は、インバータU2の出力がLレベルであるのでオフ状態になる。よって、抵抗部RP1b(電源ノードVBとノードND1との間)の抵抗値は、抵抗素子R1の抵抗値に等しくなり、抵抗部RP3b(電源ノードVBとノードND3との間)の抵抗値は、抵抗素子R3の抵抗値に等しくなる。

【0069】

時刻t1で低電位側スイッチング素子Q6用のゲート駆動回路の信号出力ノードLOがHレベルからLレベルに切替わる。これによって、仮想接地ノードVSの電位が低電位側スイッチング素子Q6のスイッチングスピードに応じて上昇するので、NMOSトランジスタQ1,Q2のドレインと基板との間の接合容量(寄生容量)が充電される。このとき、抵抗素子R1,R2の抵抗値と抵抗素子R3,R4の抵抗値とがそれぞれ等しく、かつ、NMOSトランジスタQ1,Q2の寄生容量が互いに等しければ、ノードND1の電位(オン信号Son)とノードND3の電位(オフ信号Soff)は同じ速度で低下し、ノードND2の電位(マスク信号Mon)とノードND4の電位(マスク信号Moff)は同じ速度で低下する。

【0070】

次の時刻t2で、マスク信号Mon,Moffが閾値TH以下となるので、インバータU2,U3の出力がHレベルに切替わる。RSフリップフロップU15の反転出力端子(QB)がHレベルでありかつインバータU2の出力がHレベルであるので、スイッチSW1がオン状態になる。この結果、抵抗部RP1b(ノードND1と電源ノードVBとの間)の抵抗値は抵抗素子R1の抵抗値と抵抗素子R5の抵抗値との並列合成抵抗(R1//R5)になる。この結果、時刻t2以降、オン信号Sonおよびマスク信号Monは、オフ信号Soffおよびマスク信号Moffに比べてより緩やかに低下する。

【0071】

次の時刻t3で、オフ信号Soffが閾値TH以下となるので、インバータU1の出力がHレベルに切替わる。マスク信号Monが既に閾値TH以下となっているので、RSフリップフロップU15のリセット端子(R)の入力はLレベルのままである。

【0072】

次の時刻t4で、オン信号SonがインバータU4の閾値TH以下となることによって

、インバータU4の出力がHレベルに切替わる。マスク信号Moffが既に閾値TH以下となっているので、RSフリップフロップU15のセット端子(S)の入力はLレベルのままである。

【0073】

次の時刻t5で、ダイオードD1,D2が導通し、ノードND1〜ND4の電位(Son,Mon,Soff,Moff)は一定値にクランプされる。次の時刻t6で仮想接地ノードVSの電位上昇が0になるので、ノードND1〜ND4の電位(Son,Soff,Mon,Moff)は元の電位(電源ノードVBの電位)に戻る。

【0074】

以上のように、駆動回路HVICbの仮想接地ノードVSの電位が上昇した場合でも信号出力ノードHOはLレベルを維持し、駆動回路HVICbは正常な動作を行なうことができる。

【0075】

<実施の形態3>

図8は、この発明の実施の形態3によるスイッチング素子の駆動回路HVICcの構成を示す回路図である。

【0076】

図8の高電圧回路部C2cは、図1の抵抗素子R5,R6およびスイッチSW1,SW2に代えて定電流供給部CS1,CS2が設けられている点で図1の高電圧回路部C2と異なる。

【0077】

具体的に、定電流供給部CS1は、電源ノードVBとノードND1との間に抵抗素子R1と並列に設けられた定電流源I1と、定電流源I1とノードND1との間に定電流源I1と直列に設けられたスイッチSW1とを含む。スイッチSW1は、RSフリップフロップU15の出力端子(Q)の出力を受け、出力端子(Q)がHレベルのときに導通する。したがって、定電流源I1は、高電位側スイッチング素子Q5がオン状態(RSフリップフロップU15はセット状態)のときに、抵抗素子R2を介してオン信号Sonを生成するためのNMOSトランジスタQ1に電流を供給する。

【0078】

定電流供給部CS2は、電源ノードVBとノードND3との間に抵抗素子R3と並列に設けられた定電流源I2と、定電流源I2とノードND3との間に定電流源I2と直列に設けられたスイッチSW2とを含む。スイッチSW2は、RSフリップフロップU15の反転出力端子(QB)の出力を受け、出力端子(QB)がHレベルのときに導通する。定電流源I2は、高電位側スイッチング素子Q5がオフ状態(RSフリップフロップU15はリセット状態)のときに、抵抗素子R4を介してオフ信号Soffを生成するためのNMOSトランジスタQ2に電流を供給する。図8のその他の点は図1と同じであるので、同一または相当する部分には同一の参照符号を付して説明を繰返さない。なお、図8において、抵抗素子R1〜R4の各々を複数の抵抗素子が直列および/または並列に接続されたものに置換することができる。この明細書では、抵抗素子が1個の場合と複数の場合とを含めて抵抗部と称する。

【0079】

図9は、図8に示す定電流源I1の構成の一例を示す回路図である。定電流源I2の構成は定電流源I1の構成と同じであるので、図9には定電流源I1の構成が代表として示される。

【0080】

図9を参照して、定電流源I1は、NMOSトランジスタQ101と、PMOSトランジスタQ102,Q103と、抵抗素子R101と、参照電源VREFと、差動増幅器U101とを含む。差動増幅器U101は、電源ノードVBと仮想接地ノードVSとの間の電圧(図8の直流電源V1)によって動作する。PMOSトランジスタQ103、NMOSトランジスタQ101、および抵抗素子R101は、この順で電源ノードVBと仮想接地ノードVSとの間に直列に接続される。PMOSトランジスタQ102,Q103はカレントミラーを構成する。参照電源VREFの負極は仮想接地ノードVSに接続され、正極は差動増幅器U101の非反転入力端子に接続される。差動増幅器U101の反転入力端子はNMOSトランジスタQ101のソース(ノードND101)に接続され、差動増幅器U101の出力端子はNMOSトランジスタQ101のゲートに接続される。

【0081】

以上の構成によって、NMOSトランジスタQ101には参照電源VREFの電圧に応じた参照電流が流れる。この参照電流は、PMOSトランジスタQ103とカレントミラーを構成するPMOSトランジスタQ102によってコピーされ、スイッチSW1を介して抵抗素子R3およびNMOSトランジスタQ1に供給される。

【0082】

図10は、図8の駆動回路HVICcの動作を示すタイミング図である。図10では、上から順に、低電位側スイッチング素子Q6のゲート駆動信号の波形(LO)、仮想接地ノードVS(電源ノードVB)の電圧変化、オン信号Son、マスク信号Mon、オフ信号Soff、およびマスク信号Moffの電圧波形、インバータU2、U1,U3,U4の各出力電圧波形、RSフリップフロップU15の反転出力端子(QB)、出力端子(Q)、リセット端子(R)、およびセット端子(S)の各電圧波形、ならびに駆動回路HVICcの信号出力ノードHOの電圧波形が示される。以下、図8、図10を参照して図8の定電流供給部CS1,CS2の機能について説明する。

【0083】

図10において、初期状態ではRSフリップフロップU15はリセットされた状態にあり、その出力端子(Q)はLレベルであり、反転出力端子(QB)はHレベルである。この結果、駆動回路HVICcの信号出力ノードHOはLレベルになり、定電流供給部CS1のスイッチSW1はオフ状態になり、定電流供給部CS2のスイッチSW2はオン状態になる。

【0084】

時刻t1で低電位側スイッチング素子Q6用のゲート駆動回路の信号出力ノードLOがHレベルからLレベルに切替わる。これによって、仮想接地ノードVSの電位が低電位側スイッチング素子Q6のスイッチングスピードに応じて上昇するので、NMOSトランジスタQ1,Q2のドレインと基板との間の接合容量(寄生容量)が充電される。このとき、スイッチSW2がオン状態であるので、抵抗素子R2を流れる充電電流に比べて抵抗素子R4には定電流源I2による電流の分だけ多くの充電電流が流れる。この結果、ノードND3,ND4の電位(オフ信号Soffおよびマスク信号Moff)は、ノードND1,ND2の電位(オン信号Sonおよびマスク信号Mon)よりも低下する。

【0085】

このため、次の時刻t2でマスク信号Moffが最初にインバータU2の閾値TH以下となる。これによって、インバータU2の出力がHレベルに切替わる。

【0086】

次の時刻t3でオフ信号SoffがインバータU1の閾値TH以下となることによって、インバータU1の出力がHレベルに切替わる。次の時刻t4でマスク信号MonがインバータU3の閾値TH以下となることによって、インバータU3の出力がHレベルに切替わる。

【0087】

時刻t3からt4の間で、RSフリップフロップU15のリセット端子(R)への入力がHレベルになるが、RSフリップフロップU15は元々リセットされた状態であるので出力端子(Q)および反転出力端子(QB)の論理レベルは変化しない。この結果、駆動回路HVICcの信号出力ノードHOはLレベルを維持し、駆動回路HVICcは正常な動作を行なうことができる。

【0088】

次の時刻t5でオン信号SonがインバータU4の閾値TH以下となることによって、インバータU4の出力がHレベルに切替わる。

【0089】

次の時刻t6で、ダイオードD1,D2が導通し、ノードND1〜ND4の電位(Son,Mon,Soff,Moff)は一定値にクランプされる。次の時刻t7で仮想接地ノードVSの電位上昇が0になるので、ノードND1〜ND4の電位(Son,Soff,Mon,Moff)は元の電位(電源ノードVBの電位)に戻る。

【0090】

実施の形態1,2の駆動回路HVIC,HVICbでは、定電流源I1,I2の代わりに抵抗素子R5,R6が設けられていた。抵抗素子R5,R6を使用する場合には、仮想接地ノードVSの電位の変化率(dV/dt)に依存して、オン信号Sonとオフ信号Soffとの電位差やマスク信号Mon,Moff間の電位差が変化する。これに対して実施の形態3の場合には、オン信号Sonとオフ信号Soffとの電位差およぼマスク信号Mon,Moff間の電位差を仮想接地ノードVSの電位の変化率(dV/dt)に依存せず発生させることができる。このため、実施の形態3の場合には、実施の形態1,2の場合に比べてより信頼性高い駆動回路を実現することができる。

【0091】

その他のメリットとして、定電流源I1,I2を使用することによって、実施の形態1の駆動回路HVICと比べてスイッチSW1,SW2のオン/オフのタイミングが逆になる。このため、次にワンショットパルス発生回路C1からパルス信号が入力されるNMOSトランジスタに接続された負荷の抵抗値が変化しないので、設計が容易となる。

【0092】

上記では、定電流源I1,I2による電流は、それぞれノードND1,ND3に注入されていたが、必ずしもこれには限らない。たとえば、ノードND1,ND2間に抵抗素子R2と直列にさらに抵抗素子を設け、これらの抵抗素子の接続ノードに定電流源I1による電流を注入するようにしてもよい。あるいは、電源ノードVBとノードND1との間に抵抗素子R1と直列にさらに抵抗素子を設け、これらの抵抗素子の接続ノードに定電流源I1による電流を注入するようにしてもよい。すなわち、ノードND1とNMOSトランジスタQ1との間に1または複数の抵抗素子からなる抵抗部が設けられている場合に、これらの抵抗素子の少なくとも1つを介してNMOSトランジスタQ1に電流が供給されるようにすればよい。定電流源I2の場合も同様である。

【0093】

<実施の形態4>

図11は、この発明の実施の形態4によるスイッチング素子の駆動回路HVICdの構成を示す回路図である。

【0094】

図11の高電圧回路部C2dに設けられた定電流供給部CS1bは、AND回路U16をさらに含む点で図8の定電流供給部CS1と異なる。AND回路U16は、RSフリップフロップU15の出力端子(Q)の出力とインバータU3の出力とを受け、両方の出力ともHレベルのときにHレベルの信号をスイッチSW1に供給する。スイッチSW1は、AND回路U16から受けた信号がHレベルのとき導通する。

【0095】

図11の高電圧回路部C2dに設けられた定電流供給部CS2bは、AND回路U17をさらに含む点で図8の定電流供給部CS2と異なる。AND回路U17は、RSフリップフロップU15の反転出力端子(QB)の出力とインバータU2の出力とを受け、両方の出力ともHレベルのときにHレベルの信号をスイッチSW2に供給する。スイッチSW2は、AND回路U17から受けた信号がHレベルのとき導通する。

【0096】

AND回路U16、U17を設けたことによって、パルス信号PLS1,PLS2を受けて高電位側スイッチング素子Q5をオン状態およびオフ状態に切替えるとき、および仮想接地ノードVSの電位が上昇しているときのみに定電流源I1,I2を動作させるので、駆動回路の消費電力を低減させることができる。図11のその他の点は図8の場合と同じであるので、同一または相当する部分には同一の参照符号を付して説明を繰返さない。

【0097】

図12は、図11の駆動回路HVICdの動作を示すタイミング図である。図12では、上から順に、低電位側スイッチング素子Q6のゲート駆動信号の波形(LO)、仮想接地ノードVS(電源ノードVB)の電圧変化、オン信号Son、マスク信号Mon、オフ信号Soff、およびマスク信号Moffの電圧波形、インバータU2、U1,U3,U4の各出力電圧波形、RSフリップフロップU15の反転出力端子(QB)および出力端子(Q)の各電圧波形、スイッチSW2,SW1のオン/オフの状態、RSフリップフロップU15のリセット端子(R)およびセット端子(S)の各電圧波形ならびに駆動回路HVICdの信号出力ノードHOの電圧波形が示される。

【0098】

図12において、初期状態ではRSフリップフロップU15はリセット状態にあり、その出力端子(Q)はLレベルであり、反転出力端子(QB)はHレベルである。この結果、駆動回路HVICdの信号出力ノードHOはLレベルになり、定電流供給部CS1bのスイッチSW1はオフ状態になる。定電流供給部CS2bのスイッチSW2は、インバータU2の出力がLレベルであるのでオフ状態になる。

【0099】

時刻t1で低電位側スイッチング素子Q6用のゲート駆動回路の信号出力ノードLOがHレベルからLレベルに切替わる。これによって、仮想接地ノードVSの電位が低電位側スイッチング素子Q6のスイッチングスピードに応じて上昇するので、NMOSトランジスタQ1,Q2のドレインと基板との間の接合容量(寄生容量)が充電される。このとき、スイッチSW1,SW2がオフ状態であるので、定電流源I1,I2による電流供給は行われない。したがって、抵抗素子R1,R2の抵抗値と抵抗素子R3,R4の抵抗値とがそれぞれ等しく、かつ、NMOSトランジスタQ1,Q2の寄生容量が互いに等しければ、ノードND1の電位(オン信号Son)とノードND3の電位(オフ信号Soff)は同じ速度で低下し、ノードND2の電位(マスク信号Mon)とノードND4の電位(マスク信号Moff)は同じ速度で低下する。

【0100】

次の時刻t2で、マスク信号Mon,Moffが閾値TH以下となるので、インバータU2,U3の出力がHレベルに切替わる。RSフリップフロップU15の反転出力端子(QB)がHレベルでありかつインバータU2の出力がHレベルであるので、スイッチSW2がオン状態になる。この結果、抵抗素子R4を介してオフ信号用のNMOSトランジスタQ2に定電流源I2から充電電流が供給されるので、時刻t2以降、オフ信号Soffおよびマスク信号Moffはオン信号Sonおよびマスク信号Monに比べてより早く低下する。

【0101】

次の時刻t3で、オフ信号Soffが閾値TH以下となるので、インバータU1の出力がHレベルに切替わる。マスク信号Monが既に閾値TH以下となっているので、RSフリップフロップU15のリセット端子(R)の入力はLレベルのままである。

【0102】

次の時刻t4で、オン信号SonがインバータU4の閾値TH以下となることによって、インバータU4の出力がHレベルに切替わる。マスク信号Moffが既に閾値TH以下となっているので、RSフリップフロップU15のセット端子(S)の入力はLレベルのままである。

【0103】

次の時刻t5で、ダイオードD1,D2が導通し、ノードND1〜ND4の電位(Son,Mon,Soff,Moff)は一定値にクランプされる。次の時刻t6で仮想接地ノードVSの電位上昇が0になるので、ノードND1〜ND4の電位(Son,Soff,Mon,Moff)は元の電位(電源ノードVBの電位)に戻る。

【0104】

以上のように、駆動回路HVICdの仮想接地ノードVSの電位が上昇した場合でも信号出力ノードHOはLレベルを維持し、駆動回路HVICdは正常な動作を行なうことができる。

【0105】

<実施の形態5>

図13は、この発明の実施の形態5によるスイッチング素子の駆動回路HVICeの構成を示す回路図である。

【0106】

図13の高電圧回路部C2eは、図1の抵抗素子R5,R6およびスイッチSW1,SW2に代えて、閾値変化部THC1,THC2が設けられている点で図1の高電圧回路部C2と異なる。

【0107】

具体的に、閾値変化部THC1は、インバータU3の出力ノードと仮想接地ノードVSとの間に設けられたNMOSトランジスタQ9と、インバータU4の出力ノードと仮想接地ノードVSとの間に設けられたNMOSトランジスタQ10とを含む。NMOSトランジスタQ9,Q10のゲートは、RSフリップフロップU15の反転出力端子(QB)に接続される。

【0108】

閾値変化部THC2は、インバータU1の出力ノードと仮想接地ノードVSとの間に設けられたNMOSトランジスタQ7と、インバータU2の出力ノードと仮想接地ノードVSとの間に設けられたNMOSトランジスタQ8とを含む。NMOSトランジスタQ7,Q8のゲートは、RSフリップフロップU15の出力端子(Q)に接続される。

【0109】

図13においてインバータU1〜U4はCMOSインバータである。すなわち、各インバータの出力ノードと電源ノードVBとの間にPMOSトランジスタが設けられ、各インバータの出力ノードと仮想接地ノードVSとの間にNMOSトランジスタが設けられる。これらのPMOSトランジスタおよびNMOSトランジスタのゲートが、ノードND1〜ND4のうち対応のノードと接続される。

【0110】

インバータU1〜U4の各々は、出力ノードに接続された対応のNMOSトランジスタ(Q7〜Q10)がオン状態の場合には、入力信号レベルが十分に低下しないと出力がHレベルに変化しない。すなわち、出力ノードに接続された対応のNMOSトランジスタがオン状態の場合には、インバータの閾値が低下した状態になる。したがって、NMOSトランジスタQ7〜Q10のオン/オフを制御することによって、それぞれ対応するインバータU1〜U4の閾値を制御することができる。

【0111】

図13のその他の点は図1と同じであるので、同一または相当する部分には同一の参照符号を付して説明を繰返さない。なお、図13において、抵抗素子R1〜R4の各々を複数の抵抗素子が直列および/または並列に接続されたものに置換することができる。この明細書では、抵抗素子が1個の場合と複数の場合とを含めて抵抗部と称する。

【0112】

図14は、図13の駆動回路HVICeの動作を示すタイミング図である。図14では、上から順に、低電位側スイッチング素子Q6のゲート駆動信号の波形(LO)、仮想接地ノードVS(電源ノードVB)の電圧変化、オン信号Son、マスク信号Mon、オフ信号Soff、およびマスク信号Moffの電圧波形、インバータU2、U1,U3,U4の各出力電圧波形、RSフリップフロップU15の反転出力端子(QB)、出力端子(Q)、リセット端子(R)、およびセット端子(S)の各電圧波形ならびに駆動回路HVICeの信号出力ノードHOの電圧波形が示される。

【0113】

図14において、初期状態ではRSフリップフロップU15はリセット状態にあり、その出力端子(Q)はLレベルであり、反転出力端子(QB)はHレベルである。この結果、駆動回路HVICeの信号出力ノードHOはLレベルになり、閾値変化部THC1のNMOSトランジスタQ9,Q10はオン状態になり、閾値変化部THC2のNMOSトランジスタQ7,Q8はオフ状態になる。これによって、インバータU3,U4の閾値TH2は、インバータU1,U2の閾値TH1よりも低下する。

【0114】

時刻t1で低電位側スイッチング素子Q6用のゲート駆動回路の信号出力ノードLOがHレベルからLレベルに切替わる。これによって、仮想接地ノードVSの電位が低電位側スイッチング素子Q6のスイッチングスピードに応じて上昇するので、NMOSトランジスタQ1,Q2のドレインと基板との間の接合容量(寄生容量)が充電される。このとき、抵抗素子R1,R2の抵抗値と抵抗素子R3,R4の抵抗値とがそれぞれ等しく、かつ、NMOSトランジスタQ1,Q2の寄生容量が互いに等しければ、ノードND1の電位(オン信号Son)とノードND3の電位(オフ信号Soff)は同じ速度で低下し、ノードND2の電位(マスク信号Mon)とノードND4の電位(マスク信号Moff)は同じ速度で低下する。

【0115】

次の時刻t2で、マスク信号MoffがインバータU2の閾値TH1以下となるので、インバータU2の出力がHレベルに切替わる。

【0116】

次の時刻t3で、オフ信号SoffがインバータU1の閾値TH1以下となるので、インバータU1の出力がHレベルに切替わる。この結果、RSフリップフロップU15のリセット端子(R)の入力信号がHレベルに切替わる。RSフリップフロップU15は既にリセットされた状態であるので、出力端子Qおよび反転出力端子QBは、それぞれLレベルおよびHレベルのままで変化しない。

【0117】

次の時刻t4で、マスク信号MonがインバータU3の閾値TH2以下となるので、インバータU3の出力がHレベルに切替わる。これによって、オフ信号Soffがマスクされるので、RSフリップフロップU15のリセット端子(R)の入力信号がLレベルに切替わる。

【0118】

次の時刻t5で、オン信号SonがインバータU4の閾値TH2以下となるので、インバータU4の出力がHレベルに切替わる。

【0119】

次の時刻t5で、ダイオードD1,D2が導通し、ノードND1〜ND4の電位(Son,Mon,Soff,Moff)は一定値にクランプされる。次の時刻t6で仮想接地ノードVSの電位上昇が0になるので、ノードND1〜ND4の電位(Son,Soff,Mon,Moff)は元の電位(電源ノードVBの電位)に戻る。

【0120】

以上のように、駆動回路HVICeの仮想接地ノードVSの電位が上昇した場合でも信号出力ノードHOはLレベルを維持し、駆動回路HVICeは正常な動作を行なうことができる。

【0121】

実施の形態1,2の駆動回路HVIC,HVICbでは、抵抗値が変化する抵抗部RP1,RP2がNMOSトランジスタQ1,Q2の負荷抵抗として設けられていた。このように負荷抵抗の抵抗値を変化させる場合には、仮想接地ノードVSの電位の変化率(dV/dt)に依存して、オン信号Sonとオフ信号Soffとの電位差やマスク信号Mon,Moff間の電位差が変化する。これに対して実施の形態5の場合には、オン信号Son、オフ信号Soff、およびマスク信号Mon,Moffと比較される閾値を変化させているので、インバータU1〜U4の出力が切替わるタイミングを仮想接地ノードVSの電位の変化率(dV/dt)に依存せず制御することができる。このため、実施の形態5の場合には、実施の形態1,2の場合に比べて設計が容易であり、より信頼性高い駆動回路を実現することができる。

【0122】

<実施の形態6>

図15は、この発明の実施の形態6によるスイッチング素子の駆動回路HVICfの構成を示す回路図である。

【0123】

図15の高電圧回路部C2fに設けられた閾値変化部THC1bは、AND回路U16をさらに含む点で図13の閾値変化部THC1と異なる。AND回路U16は、RSフリップフロップU15の反転出力端子(QB)の出力とインバータU2の出力とを受け、両方の出力ともHレベルのときにHレベルの信号をNMOSトランジスタQ9,Q10のゲートに出力する。

【0124】

図15の高電圧回路部C2fに設けられた閾値変化部THC2bは、AND回路U17をさらに含む点で図13の閾値変化部THC2と異なる。AND回路U17は、RSフリップフロップU15の出力端子(Q)の出力とインバータU3の出力とを受け、両方の出力ともHレベルのときにHレベルの信号をNMOSトランジスタQ7,Q8のゲートに出力する。図15のその他の点は図13の場合と同じであるので、同一または相当する部分には同一の参照符号を付して説明を繰返さない。

【0125】

図16は、図13の駆動回路HVICeの動作と図15の駆動回路HVICfの動作とを対比して示すタイミング図である。図16の左側のグラフには高電位側スイッチング素子Q5をターンオンさせる場合の駆動回路HVICe(実施の形態5)の各部の電圧波形が示される。図16の右側のグラフには同じ場合の駆動回路HVICf(実施の形態6)の各部の電圧波形が示される。左右のそれぞれのグラフにおいて、上から順に、ワンショットパルス発生回路C1の入力信号INおよび出力パルス信号PLS1,PLS2の各電圧波形、オン信号Son、マスク信号Mon、オフ信号Soff、およびマスク信号Moffの電圧波形、インバータU3、U4,U2,U1の各出力電圧波形、RSフリップフロップU15の出力端子(Q)および反転出力端子(QB)の電圧波形、NMOSトランジスタQ7,Q8のオン/オフの状態、NMOSトランジスタQ9,Q10のオン/オフの状態、RSフリップフロップU15のおよびセット端子(S)およびリセット端子(R)の各電圧波形ならびに駆動回路HVICe,HVICfの信号出力ノードHOの電圧波形が示される。

【0126】

まず、図13および図16の左側のグラフを参照して、実施の形態5による駆動回路HVICeの場合について説明する。この場合、初期状態では、ワンショットパルス発生回路C1の入力信号INがLレベルである。このとき、RSフリップフロップU15はリセットされた状態であるので、出力端子(Q)はLレベルであり、反転出力端子(QB)はHレベルである。図13の駆動回路HVICeの場合には、NMOSトランジスタQ9,Q10がオン状態になっているため、インバータU3,U4の閾値TH2がインバータU1,U2の閾値TH1よりも低下する。

【0127】

時刻t1に入力信号INがHレベルに切替わることによってワンショットパルス発生回路C1からパルス信号PLS1(パルス幅は時刻t1から時刻t4まで)が出力される。この結果、ノードND1,ND2の電位(Son,Mon)が低下する。

【0128】

次の時刻t2に、ノードND2の電位(マスク信号Mon)がインバータU3の閾値TH2以下となるので、インバータU3の出力がHレベルに切替わる。

【0129】

次の時刻t3に、ノードND1の電位(オン信号Son)がインバータU4の閾値TH2以下となるので、インバータU4の出力がHレベルに切替わる。これによって、RSフリップフロップU15のセット端子(S)の入力がHレベルになるので、RSフリップフロップU15の出力端子(Q)がHレベルに切替わり、反転出力端子(QB)がLレベルに切替わり、駆動回路HVICeの信号出力ノードHOがHレベルに切替わる。さらに、RSフリップフロップU15の出力端子(Q)および反転出力端子(QB)の電圧変化に伴ってNMOSトランジスタQ7,Q8がオン状態になり、NMOSトランジスタQ9,Q10がオフ状態になる。

【0130】

次の時刻t4で、NMOSトランジスタQ1のゲート入力(PLS1)が0Vに戻るので、ノードND1,ND2の電位(Son,Mon)が元の電位(電源ノードVBの電位)に戻る。この結果、インバータU3,U4の出力がLレベルに切替わり、RSフリップフロップU15へのセット端子(S)への入力がLレベルに戻る。

【0131】

次に、図13および図16の右側のグラフを参照して、実施の形態6による駆動回路HVICfの場合について説明する。この場合、初期状態では、NMOSトランジスタQ9,Q10がオフ状態である点を除いて左側のグラフと同じである。NMOSトランジスタQ9,Q10はRSフリップフロップU15の反転出力端子(QB)の出力とインバータU2との出力によって制御されるため、初期状態では反転出力端子(QB)はHレベルであるが、インバータU2がLレベルであるので、NMOSトランジスタQ9,Q10がオフ状態となっている。この結果、インバータU3,U4の閾値はTH1であり、TH2に低下していない。

【0132】

時刻t11に入力信号INがHレベルに切替わることによってワンショットパルス発生回路C1からパルス信号PLS1(パルス幅は時刻t11から時刻t14まで)が出力される。この結果、ノードND1,ND2の電位(Son,Mon)が低下する。

【0133】

次の時刻t12で、ノードND2の電位(マスク信号Mon)がインバータU3の閾値TH1以下となるので(ただし、TH1>TH2)、インバータU3の出力がHレベルに切替わる。

【0134】

次の時刻t13に、ノードND1の電位(オン信号Son)がインバータU4の閾値TH1以下となるので、インバータU4の出力がHレベルに切替わる。これによって、RSフリップフロップU15のセット端子(S)の入力がHレベルになるので、RSフリップフロップU15の出力端子(Q)がHレベルに切替わり、反転出力端子(QB)がLレベルに切替わり、駆動回路HVICfの信号出力ノードHOがHレベルに切替わる。このとき、インバータU3の出力がHレベルであるので、NMOSトランジスタQ7,Q8がオン状態になる。

【0135】

次の時刻t14で、NMOSトランジスタQ1のゲート入力(PLS1)が0Vに戻るので、ノードND1,ND2の電位(Son,Mon)が元の電位(電源ノードVBの電位)に戻る。この結果、インバータU3,U4の出力がLレベルに切替わり、RSフリップフロップU15へのセット端子(S)への入力がLレベルに戻り、トランジスタQ7,Q8がオフ状態なる。

【0136】

RSフリップフロップU15のセット端子(S)に入力される信号のパルス幅を、実施の形態5の場合(時刻t3から時刻t4まで)と実施の形態6の場合(時刻t13から時刻t14まで)とを比較する。そうすると、実施の形態6の場合のパルス幅(時刻t13から時刻t14まで)は、実施の形態5の場合のパルス幅(時刻t3から時刻t4まで)に比べて長くなる。この結果、実施の形態6の場合のノイズ耐量は実施の形態5の場合に比べて改善する。

【0137】

図17は、図15の駆動回路HVICfにおいて、低電位側スイッチング素子Q6がターンオフする場合のタイミング図である。

図17では、上から順に、低電位側スイッチング素子Q6のゲート駆動信号の波形(LO)、仮想接地ノードVS(電源ノードVB)の電圧変化、オン信号Son、マスク信号Mon、オフ信号Soff、およびマスク信号Moffの電圧波形、インバータU2、U1,U3,U4の各出力電圧波形、RSフリップフロップU15の反転出力端子(QB)および出力端子(Q)の各電圧波形、NMOSトランジスタQ9,Q10のオン/オフの状態、NMOSトランジスタQ7,Q8のオン/オフの状態、RSフリップフロップU15のリセット端子(R)およびセット端子(S)の各電圧波形ならびに駆動回路HVICfの信号出力ノードHOの電圧波形が示される。

【0138】

図17において、初期状態ではRSフリップフロップU15はリセット状態にあり、その出力端子(Q)はLレベルであり、反転出力端子(QB)はHレベルである。この結果、駆動回路HVICfの信号出力ノードHOはLレベルになる。インバータU2,U3の出力はLレベルであるので、NMOSトランジスタQ7〜Q10のいずれもオフ状態になる。インバータU1〜U4の閾値は比較的高いTH1になる(TH1>TH2とする)。

【0139】

時刻t1で低電位側スイッチング素子Q6用のゲート駆動回路の信号出力ノードLOがHレベルからLレベルに切替わる。これによって、仮想接地ノードVSの電位が低電位側スイッチング素子Q6のスイッチングスピードに応じて上昇するので、NMOSトランジスタQ1,Q2のドレインと基板との間の接合容量(寄生容量)が充電される。このとき、抵抗素子R1,R2の抵抗値と抵抗素子R3,R4の抵抗値とがそれぞれ等しく、かつ、NMOSトランジスタQ1,Q2の寄生容量が互いに等しければ、ノードND1の電位(オン信号Son)とノードND3の電位(オフ信号Soff)は同じ速度で低下し、ノードND2の電位(マスク信号Mon)とノードND4の電位(マスク信号Moff)は同じ速度で低下する。

【0140】

次の時刻t2で、マスク信号MoffがインバータU2の閾値TH1以下となるので、インバータU2の出力がHレベルに切替わる。これによって、NMOSトランジスタQ9,Q10がオン状態になるので、インバータU3,U4の閾値をTH1からTH2に低下させる。

【0141】

次の時刻t3で、オフ信号SoffがインバータU1の閾値TH1以下となるので、インバータU1の出力がHレベルに切替わる。この結果、RSフリップフロップU15のリセット端子(R)の入力信号がHレベルに切替わる。RSフリップフロップU15は既にリセットされた状態であるので、出力端子Qおよび反転出力端子QBは、それぞれLレベルおよびHレベルのままで変化しない。

【0142】

次の時刻t4で、マスク信号MonがインバータU3の閾値TH2以下となるので、インバータU3の出力がHレベルに切替わる。これによって、オフ信号Soffがマスクされるので、RSフリップフロップU15のリセット端子(R)の入力信号がLレベルに切替わる。

【0143】

次の時刻t5で、オン信号SonがインバータU4の閾値TH2以下となるので、インバータU4の出力がHレベルに切替わる。

【0144】

次の時刻t5で、ダイオードD1,D2が導通し、ノードND1〜ND4の電位(Son,Mon,Soff,Moff)は一定値にクランプされる。次の時刻t6で仮想接地ノードVSの電位上昇が0になるので、ノードND1〜ND4の電位(Son,Soff,Mon,Moff)は元の電位(電源ノードVBの電位)に戻る。

【0145】

以上のように、駆動回路HVICfの仮想接地ノードVSの電位が上昇した場合でも信号出力ノードHOはLレベルを維持し、駆動回路HVICfは正常な動作を行なうことができる。

【0146】

今回開示された実施の形態はすべての点で例示であって制限的なものでないと考えられるべきである。この発明の範囲は上記した説明ではなくて請求の範囲によって示され、請求の範囲と均等の意味および範囲内でのすべての変更が含まれることが意図される。

【符号の説明】

【0147】

C1 ワンショットパルス発生回路、CS1,CS2,CS1b,CS2b 定電流供給部、GND 接地ノード、HO 信号出力ノード(高電位側)、HV 高電圧電源、HVIC,HVICb〜HVICf 駆動回路、HVN 高電位側電源ノード、I1,I2 定電流源、LO 信号出力ノード(低電位側)、Moff,Mon マスク信号、ND1〜ND4 ノード、PLS1,PLS2 パルス信号、Q1,Q2 NMOSトランジスタ(制御用スイッチング素子)、Q5 高電位側スイッチング素子、Q6 低電位側スイッチング素子、R1〜R6 抵抗素子、RP1〜RP4,RP1b,RP2b 抵抗部、SW1,SW2 スイッチ、Soff オフ信号、Son オン信号、TH,TH1,TH2 閾値、THC1,THC2,THC1b,THC2b 閾値変化部、U15 フリップフロップ、V1 直流電源、VB 電源ノード、VS 仮想接地ノード。

【技術分野】

【0001】

この発明は半導体スイッチング素子の制御電極を駆動するための駆動回路に関する。

【背景技術】

【0002】

PWM(Pulse Width Modulation)インバータなどの電力変換装置には、直流電源の正極と負極との2つの半導体スイッチング素子が直列(いわゆるトーテムポール型)に接続されたアームが複数設けられる。各アームの高電位側のスイッチング素子を駆動する回路として近年、トランスやフォトカプラによる絶縁を行なわない、いわゆるレベルシフト回路が使用される。

【0003】

たとえば、特開2000−252809号公報(特許文献1)は、この種のレベルシフト回路の構成例を開示する。同文献によると、レベルシフト回路は、第1、第2の2つの可制御半導体素子と、直流電源と、第1、第2の2つの負荷抵抗と、ロジック回路と、信号無効化手段とを備える。各可制御半導体素子は、電位の基準となる電極が共通電位に接続され、この電位基準電極と制御電極との間に導通用信号を入力する期間、電位基準電極と主電極との間が導通状態となる。直流電源は、一極が共通電位と所定の高電位との間で変動する外部回路の所定の部位に接続され、この二電位間の電圧より低い電圧を持つ。第1、第2の2つの負荷抵抗は、この直流電源の他極に一端が接続され、他端がそれぞれ第1、第2の可制御半導体素子の主電極に接続される。ロジック回路は、上記の直流電源のもとで作動する。第1、第2の可制御半導体素子の制御電極には、それぞれにタイミングを異にしてパルス状の導通用信号が入力される。このときの可制御半導体素子の導通によって第1、第2の負荷抵抗に生ずるパルス状の電圧降下が信号としてロジック回路に伝えられる。信号無効化手段は、第1、第2の負荷抵抗に同時にパルス状の電圧降下が生じたときは、この電圧降下の信号をロジック回路へ伝えることを防止する。具体的に、信号無効化手段は、ロジック回路へ伝える第1の負荷抵抗の電圧降下の信号を、第2の負荷抵抗の電圧降下に基づき生成したマスク用信号によってマスクし、同じくロジック回路へ伝える第2の負荷抵抗の電圧降下の信号を、第1の負荷抵抗の電圧降下に基づき生成したマスク用信号によってマスクする。

【先行技術文献】

【特許文献】

【0004】

【特許文献1】特開2000−252809号公報

【発明の概要】

【発明が解決しようとする課題】

【0005】

上記文献のレベルシフト回路を含む駆動回路を用いて、高電位側のスイッチング素子を駆動してオフからオンに遷移させる場合あるいは低電位側のスイッチング素子を駆動してオンからオフに遷移させる場合、トーテムポールの中点電位が上昇する。このとき、各可制御半導体素子の主電極と基板(共通電位)との間の接合容量(寄生容量)を充電することになり、第1、第2の2つの負荷抵抗に寄生容量を充電する充電電流が流れる。この結果、第1、第2の負荷抵抗に同時に電圧降下が生じることになる。通常、製造上のばらつきなどによって第1、第2の可制御半導体素子の寄生容量にずれがあるので、第1、第2の負荷抵抗による電圧降下量にもずれが生じることになる。電圧降下量のずれが大きいと上記の信号無効化手段によるマスクが働かないので、ロジック回路に誤信号が伝えられる可能性がある。

【0006】

この発明の目的は、誤動作を防止することによって従来よりも信頼性を高めた、スイッチング素子の駆動回路を提供することである。

【課題を解決するための手段】

【0007】

この発明は一局面において、第1の電源ノードとそれより高電位に設定される第2の電源ノードとの間に直列に接続された2つのスイッチング素子のうち高電位側のスイッチング素子の駆動回路であって、第3の電源ノードと、論理回路と、第1および第2の抵抗部と、第1の制御用スイッチング素子と、第1の比較部とを備える。第3の電源ノードは、2つのスイッチング素子の接続ノードの電位よりも高電位に設定される。論理回路は、内部状態として第1および第2の状態を有し、内部状態に応じて高電位側のスイッチング素子をオン状態またはオフ状態に切替えるために、第1および第2の状態にそれぞれ対応して第1および第2の論理レベルに切替わる制御信号を出力する。第1の抵抗部は、第3の電源ノードと第1のノードとの間に設けられる。第2の抵抗部は、第1のノードと第2のノードとの間に設けられる。第1の制御用スイッチング素子は、第2のノードと第1の電源ノードとの間に設けられ、第1のパルス信号を受けたときに導通する。第1の比較部は、第1のパルス信号に応じて論理回路を第1の状態から第2の状態に切替えるために、第1のノードの電位が第1の閾値以下の場合に活性状態となる第1の信号を出力する。第1および第2の抵抗部の少なくとも一方の抵抗値は、少なくとも制御信号の変化に基づいたタイミングで変化する。

【発明の効果】

【0008】

この発明の一局面によるスイッチング素子の駆動回路によれば、第1および第2の抵抗部の少なくとも一方の抵抗値を、少なくとも制御信号の変化に基づいたタイミングで変化させることによって、誤動作を防止することができるので従来よりも信頼性を高めることができる。

【図面の簡単な説明】

【0009】

【図1】この発明の実施の形態1によるスイッチング素子の駆動回路(高耐圧IC)HVICの構成を示す回路図である。

【図2】図1の駆動回路HVICがHブリッジの高電位側スイッチング素子Q5に接続された場合を示す図である。

【図3】図1の駆動回路HVICの動作を示すタイミング図である。

【図4】図1の駆動回路HVICの変形例を示す回路図である。

【図5】この発明の実施の形態2によるスイッチング素子の駆動回路HVICbの構成を示す回路図である。

【図6】図1の駆動回路HVICの動作と図5の駆動回路HVICbの動作とを対比して示すタイミング図である。

【図7】図5の駆動回路HVICbにおいて、低電位側スイッチング素子Q6がターンオフする場合のタイミング図である。

【図8】この発明の実施の形態3によるスイッチング素子の駆動回路HVICcの構成を示す回路図である。

【図9】図8に示す定電流源I1の構成の一例を示す回路図である。

【図10】図8の駆動回路HVICcの動作を示すタイミング図である。

【図11】この発明の実施の形態4によるスイッチング素子の駆動回路HVICdの構成を示す回路図である。

【図12】図11の駆動回路HVICdの動作を示すタイミング図である。

【図13】この発明の実施の形態5によるスイッチング素子の駆動回路HVICeの構成を示す回路図である。

【図14】図13の駆動回路HVICeの動作を示すタイミング図である。

【図15】この発明の実施の形態6によるスイッチング素子の駆動回路HVICfの構成を示す回路図である。

【図16】図13の駆動回路HVICeの動作と図15の駆動回路HVICfの動作とを対比して示すタイミング図である。

【図17】図15の駆動回路HVICfにおいて、低電位側スイッチング素子Q6がターンオフする場合のタイミング図である。

【発明を実施するための形態】

【0010】

以下、この発明の実施の形態について図面を参照して詳しく説明する。なお、同一または相当する部分には同一の参照符号を付して、その説明を繰返さない。

【0011】

<実施の形態1>

[駆動回路HVICの構成]

図1は、この発明の実施の形態1によるスイッチング素子の駆動回路(高耐圧IC)HVICの構成を示す回路図である。

【0012】

図1を参照して、駆動回路HVICは、入力信号INに応じてトーテムポール接続された高電位側スイッチング素子Q5をオン状態およびオフ状態に駆動するための集積回路(IC:Integrated Circuit)である。高電位側スイッチング素子Q5および低電位側スイッチング素子Q6は、高電圧電源HVが接続される高電位側電源ノードHVNと低電位側電源ノード(接地ノード)GNDとの間に直列に接続される。図1には、高電位側スイッチング素子Q5および低電位側スイッチング素子Q6の一例としてIGBT(Insulated Gate Bipolar Transistor)が示される。

【0013】

高電位側スイッチング素子(IGBT)Q5のコレクタとエミッタとの間には高電位側フリーホイールダイオードD3が逆バイアス方向に接続される。低電位側スイッチング素子(IGBT)Q6のコレクタとエミッタとの間には低電位側フリーホイールダイオードD4が逆バイアス方向に接続される。高電位側スイッチング素子Q5と低電位側スイッチング素子Q6との接続ノードND0は、駆動回路HVICの仮想接地ノードVSに接続される。高電位側スイッチング素子Q5の制御電極(IGBTのゲート)は、駆動回路HVICの信号出力ノードHOに接続される。駆動回路HVICの電源ノードVBと仮想接地ノードVSの間には直流電源V1が接続される。低電位側スイッチング素子Q6の制御電極は、低電位側用の駆動回路の信号出力ノードLOと接続される。

【0014】

駆動回路HVICは、ワンショットパルス発生回路C1と、NMOS(Negative channel Metal Oxide Semiconductor)トランジスタQ1,Q2(制御用スイッチング素子)と、高電圧回路部C2とを含む。ワンショットパルス発生回路C1は、入力信号INの立上がりエッジに同期して高電位側スイッチング素子Q5をオン状態にするためのパルス信号PLS1を生成して出力し、入力信号INの立下がりエッジに同期して高電位側スイッチング素子Q5をオフ状態にするためのパルス信号PLS2を生成して出力する。

【0015】

NMOSトランジスタQ1は、高電圧回路部C2のノードND2と接地ノードGNDとの間に接続され、ワンショットパルス発生回路C1からパルス信号PLS1をゲートに受けることによって導通する。これによって高電圧回路部C2にパルス信号PLS1が伝達される。NMOSトランジスタQ2は、高電圧回路部C2のノードND4と接地ノードGNDとの間に接続され、ワンショットパルス発生回路C1からパルス信号PLS2をゲートに受けることによって導通する。これによって高電圧回路部C2にパルス信号PLS2が伝達される。

【0016】

ワンショットパルス発生回路C1によってパルス信号PLS1,PLS2をNMOSトランジスタQ1,Q2のゲートに供給する理由は、NMOSトランジスタQ1,Q2の負荷抵抗として用いられている抵抗素子R1〜R4の電流消費を抑えるためである。入力信号がパルス信号であるので、入力信号を保持するためにRSフリップフロップU15が高電圧回路部C2に設けられている。

【0017】

高電圧回路部C2は、抵抗素子R1〜R4と、クランプ用のダイオードD1,D2と、インバータU1〜U4と、フィルタ回路C3と、RSフリップフロップU15と、出力段回路C4とを含む。

【0018】

抵抗素子R1,R2は、この順番で電源ノードVBとノードND2との間に直列に接続される(以下、抵抗素子R1,R2の接続ノードをノードND1と称する)。NMOSトランジスタQ1がパルス信号PLS1を受けて導通すると、抵抗素子R1,R2およびNMOSトランジスタQ1を介して電源ノードVBから接地ノードGNDに電流が流れる。これによって抵抗素子R1,R2に生じたパルス状の電圧降下が、ノードND1,ND2

での電位変化として検出される。

【0019】

同様に抵抗素子R3,R4は、この順番で電源ノードVBとノードND4との間に直列に接続される(以下、抵抗素子R3,R4の接続ノードをノードND3と称する)。NMOSトランジスタQ2がパルス信号PLS2を受けて導通すると、抵抗素子R3,R4およびNMOSトランジスタQ2を介して電源ノードVBから接地ノードGNDに電流が流れる。これによって抵抗素子R3,R4に生じたパルス状の電圧降下が、ノードND3,ND4での電位変化として検出される。

【0020】

ノードND1の電位変化は高電位側スイッチング素子Q5をオン状態にするためのオン信号Sonとして用いられる。ノードND3の電位変化は高電位側スイッチング素子Q5をオフ状態にするためのオフ信号Soffとして用いられる。ノードND2の電位変化は、オフ信号Soffをマスクするためのマスク信号Monとして用いられる。ノードND4の電位変化はオン信号Sonをマスクするためのマスク信号Moffとして用いられる。

【0021】

ダイオードD1は、抵抗素子R1,R2に過大な電流が流れないように、仮想接地ノードVSとノードND2との間に、仮想接地ノードVS側がアノードとなるように接続される。ダイオードD2は、抵抗素子R3,R4に過大な電流が流れないように、仮想接地ノードVSとノードND4との間に、仮想接地ノードVS側がアノードとなるように接続される。

【0022】

インバータU1〜U4は直流電源V1によって駆動される。インバータU4は、ノードND1からオン信号Sonを受けて、オン信号SonがインバータU4の閾値以下になるとハイレベル(Hレベルとも記載する)の信号を出力する、インバータU3は、ノードND2からマスク信号Monを受けて、マスク信号MonがインバータU3の閾値以下になるとHレベルの信号を出力する。インバータU1は、ノードND3からオフ信号Soffを受けて、オフ信号SoffがインバータU1の閾値以下になるとHレベルの信号を出力する。インバータU2は、ノードND4からマスク信号Moffを受けて、マスク信号MoffがインバータU2の閾値以下になるとHレベルの信号を出力する。以下の説明では、インバータU1〜U4の閾値は全て等しいとする。

【0023】

フィルタ回路C3は、NAND回路U5〜U7と、インバータU8〜U12と、NOR回路U13,U14とを含む。これらの各要素およびRSフリップフロップU15は直流電源V1によって駆動される。

【0024】

NAND回路U7は、インバータU4の出力の論理レベルを反転するNOT回路(インバータ)として用いられる。NAND回路U7の出力はインバータU10,U12を介して、NOR回路U14の第1の入力ノードに入力される。したがって、NOR回路U14の第1の入力ノードには、オン信号SonがインバータU4の閾値以下となったとき、ローレベル(Lレベルとも記載する)の信号が入力される。

【0025】

NAND回路U5は、インバータU1の出力の論理レベルを反転するNOT回路(インバータ)として用いられる。NAND回路U5の出力はインバータU8,U11を介して、NOR回路U13の第1の入力ノードに入力される。したがって、NOR回路U13の第1の入力ノードには、オフ信号SoffがインバータU1の閾値以下となったとき、Lレベルの信号が入力される。

【0026】

NAND回路U6は、インバータU2およびU3の出力を受ける。NAND回路U6の出力は、インバータU9を介してNOR回路U13,U14の各第2の入力ノードに入力される。したがって、NOR回路U13,U14の各第2の入力ノードには、マスク信号MonがインバータU3の閾値以下となりかつマスク信号MoffがインバータU2の閾値以下となったときに、Hレベルの信号が入力される。

【0027】

NOR回路U14の出力はRSフリップフロップU15のセット端子(S)に入力され、NOR回路U13の出力はRSフリップフロップU15のリセット端子(R)に入力される。したがって、RSフリップフロップU15のセット端子(S)には、オン信号SonがインバータU4の閾値以下となりかつマスク信号MoffがインバータU2の閾値を超えていれば、Hレベルの信号が入力される。RSフリップフロップU15のリセット端子(R)には、オフ信号SoffがインバータU1の閾値以下となりかつマスク信号MonがインバータU3の閾値を超えていれば、Hレベルの信号が入力される。

【0028】

出力段回路C4は、NMOSトランジスタQ3,Q4を含む。NMOSトランジスタQ3,Q4は、この順で電源ノードVBと仮想接地ノードVSとの間に直列に接続される。NMOSトランジスタQ3のゲートはRSフリップフロップU15の出力端子(Q)と接続され、NMOSトランジスタQ4のゲートはRSフリップフロップU15の反転出力端子(QB)と接続される。NMOSトランジスタQ3,Q4の接続ノードは信号出力ノードHOを介して、高電位側スイッチング素子Q5の制御電極(IGBTのゲート)に接続される。したがって、RSフリップフロップU15がセットされた状態のとき、高電位側スイッチング素子Q5がオン状態になり、RSフリップフロップU15がリセットされた状態のとき、高電位側スイッチング素子Q5がオフ状態になる。

【0029】

高電圧回路部C2は、さらに、抵抗素子R5,R6と、スイッチSW1,SW2とを含む。

【0030】

抵抗素子R5は、電源ノードVBとノードND1との間に抵抗素子R1と並列に設けられる。スイッチSW1(制御用スイッチング素子)は、電源ノードVBとノードND1との間に抵抗素子R5と直列に設けられる。スイッチSW1は、RSフリップフロップU15の反転出力端子(QB)の出力信号がHレベルになったときオン状態になる。

【0031】

抵抗素子R6は、電源ノードVBとノードND3との間に抵抗素子R3と並列に設けられる。スイッチSW2(制御用スイッチング素子)は、電源ノードVBとノードND3との間に抵抗素子R6と直列に設けられる。スイッチSW2は、RSフリップフロップU15の出力端子(Q)の出力信号がHレベルになったときオン状態になる。

【0032】

スイッチSW1,SW2として、たとえば、PMOS(Positive channel Metal Oxide Semiconductor)トランジスタやNMOSトランジスタを用いることができる。PMOSトランジスタを用いる場合は、RSフリップフロップU15の出力端子(Q)または反転出力端子(QB)とPMOSトランジスタのゲートとの間にインバータが設けられる。

【0033】

図1において、抵抗素子R1,R5とスイッチSW1とによって抵抗部RP1が構成される。抵抗部RP1の抵抗値は、RSフリップフロップU15の反転出力端子(QB)の論理レベルに応じて変化する。抵抗素子R3,R6とスイッチSW2とによって抵抗部RP3が構成される。抵抗部RP3の抵抗値は、RSフリップフロップU15の出力端子(Q)の論理レベルに応じて変化する。図1の駆動回路HVICでは、このような抵抗値の変化する抵抗部RP1,RP3をNMOSトランジスタQ1,Q2の負荷抵抗として用いることによって、駆動回路HVICの誤動作を防止することができる。

【0034】

[誤動作のメカニズム]

抵抗部RP1,RP3の動作を説明するのに先立って、抵抗部RP1,RP3に代えて抵抗素子R1,R3が設けられている場合(すなわち、抵抗素子R5,R6およびスイッチSW1,SW2が設けられていない場合)に、駆動回路HVICに誤動作が生じる理由について説明する。

【0035】

図2は、図1の駆動回路HVICがHブリッジの高電位側スイッチング素子Q5に接続された場合を示す図である。図2を参照して、高電位側電源ノードHVNと接地ノードGNDとの間には、さらに、高電位側スイッチング素子Q5bと低電位側スイッチング素子Q6bがこの順で直列に接続される。スイッチング素子Q5b,Q6bとそれぞれ逆並列にフリーホイールダイオードD3b,D4bが設けられる。スイッチング素子Q5,Q6の接続ノードND0と、スイッチング素子Q5b,Q6bの接続ノードND0bとの間に誘導性の負荷L1が接続される。図2において、スイッチング素子Q5,Q6,Q5b,Q6bはIGBTである。

【0036】

図2において、トランジスタQ5b,Q6がオン状態、トランジスタQ5,Q6bがオフ状態であったとする。この状態から、トランジスタQ6がオフ状態になると、オン状態のトランジスタQ5b、負荷L1、およびダイオードD3を介してフリーホイール電流が流れる。この結果、ノードND0(仮想接地ノードVS)の電位が上昇する(言い換えると、仮想接地ノードVSに正のdV/dtが印加される)。電源ノードVBの電位は仮想接地ノードVSの電位に直流電源V1の電圧を加算した値に等しいので、仮想接地ノードVSの電位が上昇すると電源ノードVBの電位も同じ電圧変化率で上昇する。

【0037】

トランジスタQ5b,Q6がオフ状態、トランジスタQ5,Q6bがオン状態の場合にも同様のことが生じる。この状態から、トランジスタQ6bがオフ状態になると、ノードND0(すなわち、仮想接地ノードVS)の電位が上昇する(すなわち、仮想接地ノードVSに正のdV/dtが印加される)場合がある。3相インバータの場合も上記と同様に、仮想接地ノードVSの電位が上昇する(すなわち、仮想接地ノードVSに正のdV/dtが印加される)場合がある。

【0038】

再び図1を参照して、駆動回路HVICの信号出力ノードHOがLレベルの状態で、ノードLOの電位がHレベルからLレベルに変化したことによって、低電位側スイッチング素子Q6がオン状態からオフ状態に変化したとする。このとき、仮想接地ノードVSの電位および電源ノードVBの電位は低電位側スイッチング素子Q6のスイッチングスピードに応じて上昇する。この結果、NMOSトランジスタQ1,Q2のドレインと基板間の接合容量(寄生容量)が充電されることになるので、抵抗素子R1,R2および抵抗素子R3,R4に寄生容量の充電電流が流れる。この充電電流による電圧降下によって、次段のインバータU1〜U4の入力電位(Son,Mon,Soff,Moff)は低下する。ここで、オン信号用のNMOSトランジスタQ1の寄生容量のほうがオフ信号用のNMOSトランジスタQ2の寄生容量よりも大きければ、ノードND1,ND2の電位(すなわち、オン信号Sonおよびマスク信号Mon)のほうがノードND3,ND4の電位(すなわち、オフ信号Soffおよびマスク信号Moff)よりも低下することになる。この結果、マスク信号MoffがインバータU2の閾値よりも低下する前にオン信号SonがインバータU4の閾値よりも低下すれば、RSフリップフロップU15のセット端子(S)にHレベルの信号が入力され、これによって、高電位側スイッチング素子Q5はオフ状態からオン状態へと誤動作することになる。

【0039】

[駆動回路HVICの動作]

図3は、図1の駆動回路HVICの動作を示すタイミング図である。図3では、上から順に、低電位側スイッチング素子Q6のゲート駆動信号の波形(LO)、仮想接地ノードVS(電源ノードVB)の電圧変化、オン信号Son、マスク信号Mon、オフ信号Soff、およびマスク信号Moffの電圧波形、インバータU2、U1,U3,U4の各出力電圧波形、RSフリップフロップU15の反転出力端子(QB)、出力端子(Q)、リセット端子(R)、およびセット端子(S)の各電圧波形、ならびに駆動回路HVICの信号出力ノードHOの電圧波形が示される。以下、図1、図3を参照して図1の抵抗部RP1,RP3の機能について説明する。

【0040】

図3において、初期状態ではRSフリップフロップU15はリセットされた状態であり、その出力端子(Q)はLレベルであり、反転出力端子(QB)はHレベルである。この結果、駆動回路HVICの信号出力ノードHOはLレベルになり、抵抗部RP1のスイッチSW1はオン状態になり、抵抗部RP3のスイッチSW2はオフ状態になる。スイッチSW1がオン状態であるので、抵抗部RP1の抵抗値(電源ノードVBとノードND1との間の抵抗値)は、抵抗素子R1とR5との並列合成抵抗(R1//R5と記載する)となり、スイッチSW1がオフ状態の場合の抵抗値(抵抗素子R1の抵抗値)より小さい。一方、抵抗部RP3の抵抗値(電源ノードVBとノードND3との間の抵抗値)は、スイッチSW2がオフ状態であるので抵抗素子R3の抵抗値であり、抵抗素子R3とR6との並列合成抵抗(R3//R6と記載する)よりも大きい。

【0041】

時刻t1で低電位側スイッチング素子Q6用のゲート駆動回路の信号出力ノードLOがHレベルからLレベルに切替わる。これによって、仮想接地ノードVSの電位が低電位側スイッチング素子Q6のスイッチングスピードに応じて上昇するので、NMOSトランジスタQ1,Q2のドレインと基板との間の接合容量(寄生容量)が充電される。このとき、抵抗部RP1(電源ノードVBとノードND1との間)の抵抗値(R1//R5)と、抵抗部RP3(電源ノードVBとノードND3との間)の抵抗値(R3)との違いによって電圧降下量が異なるので、ノードND3,ND4の電位(Soff,Moff)はノードND1,ND2の電位(Son,Mon)よりも低くなる。

【0042】

このため、時刻t2でマスク信号Moffが最初にインバータU2の閾値TH以下となる。これによって、インバータU2の出力がHレベルに切替わる。次に時刻t3でオフ信号SoffがインバータU1の閾値TH以下となることによって、インバータU1の出力がHレベルに切替わる。次に時刻t4でマスク信号MonがインバータU3の閾値TH以下となることによって、インバータU3の出力がHレベルに切替わる。次に時刻t5でオン信号SonがインバータU4の閾値TH以下となることによって、インバータU4の出力がHレベルに切替わる。時刻t3からt4の間で、RSフリップフロップU15のリセット端子(R)への入力がHレベルになるが、RSフリップフロップU15は元々リセットされた状態であるので出力端子(Q)および反転出力端子(QB)の論理レベルは変化しない。この結果、駆動回路HVICの信号出力ノードHOはLレベルを維持し、駆動回路HVICは正常な動作を行なうことができる。

【0043】

次の時刻t6で、ダイオードD1,D2が導通し、ノードND1〜ND4の電位(Son,Mon,Soff,Moff)は一定値にクランプされる。次の時刻t7で仮想接地ノードVSの電位上昇が0になるので、ノードND1〜ND4の電位(Son,Soff,Mon,Moff)は元の電位(電源ノードVBの電位)に戻る。

【0044】

[変形例]

図4は、図1の駆動回路HVICの変形例を示す回路図である。この変形例では、図4(A)に示すように電源ノードVBと接地ノードGNDとの間に、抵抗素子R1、抵抗部RP2、およびMOSトランジスタQ1がこの順で直列に設けられる。さらに、図4(B)に示すように電源ノードVBと接地ノードGNDとの間に、抵抗素子R3、抵抗部RP4、およびMOSトランジスタQ2がこの順で直列に設けられる。

【0045】

図4(A)を参照して、抵抗部RP2は、ノードND1,ND2間に設けられた抵抗素子R2と、ノードND2とNMOSトランジスタQ1のドレイン(ノードND7)との間に設けられた抵抗素子R7と、抵抗素子R7と並列に設けられたスイッチSW1とを含む。スイッチSW1は、RSフリップフロップU15の出力端子(Q)がHレベルのときオン状態になり、Lレベルのときオフ状態になる。したがって、RSフリップフロップU15がセット状態の場合には、NMOSトランジスタQ1の寄生容量による充電電流が抵抗素子R7を流れずにスイッチSW1を介してバイパスされる。一方、RSフリップフロップU15がリセット状態の場合には、NMOSトランジスタQ1の寄生容量による充電電流が抵抗素子R7を流れるので、ノードND1,ND2の電位の低下がセット状態の場合に比べて減少する。この結果、誤動作を防止することができる。

【0046】

図4(B)を参照して、抵抗部RP3は、ノードND3,ND4間に設けられた抵抗素子R3と、ノードND4とNMOSトランジスタQ2のドレイン(ノードND8)との間に設けられた抵抗素子R8と、抵抗素子R8と並列に設けられたスイッチSW2とを含む。スイッチSW2は、RSフリップフロップU15の反転出力端子(QB)がHレベルのときオン状態になり、Lレベルのときオフ状態になる。したがって、RSフリップフロップU15がリセット状態の場合には、NMOSトランジスタQ2の寄生容量による充電電流が抵抗素子R8を流れずにスイッチSW2を介してバイパスされる。一方、RSフリップフロップU15がセット状態の場合には、NMOSトランジスタQ2の寄生容量による充電電流が抵抗素子R8を流れるので、ノードND3,ND4の電位の低下がセット状態の場合に比べて減少する。この結果、誤動作を防止することができる。

【0047】

以上をまとめると、電源ノードVBとオン信号Sonが検出されるノードND1との間に抵抗部RP1が設けられ、ノードND1とNMOSトランジスタQ1との間に抵抗部RP2が設けられる。そして、RSフリップフロップU15がリセット状態(高電位側スイッチング素子Q5がオフ状態)の場合にはセット状態(高電位側スイッチング素子Q5がオン状態)の場合に比べて、抵抗部RP1の抵抗値に対する抵抗部RP2の抵抗値の比率が増加するように、抵抗部RP1,RP2の少なくとも一方の抵抗値が変化する。これによって、高電位側のスイッチング素子Q5がオフ状態からオン状態に誤動作するのを防止できる。

【0048】

同様に、電源ノードVBとオフ信号Soffが検出されるノードND3との間に抵抗部RP3が設けられ、ノードND3とNMOSトランジスタQ2との間に抵抗部RP4が設けられる。そして、RSフリップフロップU15がセット状態(高電位側スイッチング素子Q5がオン状態)の場合にはリセット状態(高電位側スイッチング素子Q5がオフ状態)の場合に比べて、抵抗部RP3の抵抗値に対する抵抗部RP4の抵抗値の比率が増加するように、抵抗部RP3,RP4の少なくとも一方の抵抗値が変化する。これによって、高電位側のスイッチング素子Q5がオン状態からオフ状態に誤動作するのを防止できる。

【0049】

<実施の形態2>

図1に示す実施の形態1による駆動回路HVICでは、スイッチSW1およびSW2のいずれかが常時オン状態になっている。このため、パルス信号PLS1がNMOSトランジスタQ1に入力されたときにRSフリップフロップU15のセット端子(S)に入力される信号のパルス幅や、パルス信号PLS2がNMOSトランジスタQ2に入力されたときにRSフリップフロップU15のリセット端子(R)に入力される信号のパルス幅が、従来よりも短くなる。この結果、従来よりもノイズ耐量が低下するという問題がある。

【0050】

実施の形態2による駆動回路HVICbでは、仮想接地ノードVSの電位が上昇した場合のみスイッチSW1,SW2が導通状態になるように、スイッチSW1,SW2の制御シーケンスをマスク信号Mon,Moffを用いたものに変更する。これによってノイズ耐量の低下を防止することができる。以下、具体的に説明する。

【0051】

図5は、この発明の実施の形態2によるスイッチング素子の駆動回路HVICbの構成を示す回路図である。

【0052】

図5の高電圧回路部C2bに設けられた抵抗部RP1bは、AND回路U16をさらに含む点で図1の抵抗部RP1と異なる。AND回路U16は、RSフリップフロップU15の反転出力端子(QB)の出力とインバータU2の出力とを受け、両方の出力ともHレベルのときにHレベルの信号をスイッチSW1に供給する。スイッチSW1は、AND回路U16から受けた信号がHレベルのとき導通する。

【0053】

図5の高電圧回路部C2bに設けられた抵抗部RP3bは、AND回路U17をさらに含む点で図1の抵抗部RP3と異なる。AND回路U17は、RSフリップフロップU15の出力端子(Q)の出力とインバータU3の出力とを受け、両方の出力ともHレベルのときにHレベルの信号をスイッチSW2に供給する。スイッチSW2は、AND回路U17から受けた信号がHレベルのとき導通する。

【0054】

図5のその他の点は図1の場合と同じであるので、同一または相当する部分には同一の参照符号を付して説明を繰返さない。

【0055】

図6は、図1の駆動回路HVICの動作と図5の駆動回路HVICbの動作とを対比して示すタイミング図である。図6の左側のグラフには高電位側スイッチング素子Q5をターンオンさせる場合の駆動回路HVIC(実施の形態1)の各部の電圧波形が示される。図6の右側のグラフには同じ場合の駆動回路HVICb(実施の形態2)の各部の電圧波形が示される。左右のそれぞれのグラフにおいて、上から順に、ワンショットパルス発生回路C1の入力信号INおよび出力パルス信号PLS1,PLS2の各電圧波形、オン信号Son、マスク信号Mon、オフ信号Soff、およびマスク信号Moffの電圧波形、インバータU3、U4,U2,U1の各出力電圧波形、RSフリップフロップU15の出力端子(Q)および反転出力端子(QB)の電圧波形、スイッチSW2,SW1のオン/オフの状態、RSフリップフロップU15のセット端子(S)およびリセット端子(R)の各電圧波形ならびに駆動回路HVIC,HVICbの信号出力ノードHOの電圧波形が示される。

【0056】

まず、図1および図6の左側のグラフを参照して、実施の形態1による駆動回路HVICの場合について説明する。この場合、初期状態では、ワンショットパルス発生回路C1の入力信号INがLレベルである。このとき、RSフリップフロップU15はリセットされた状態であるので、出力端子(Q)はLレベルであり、反転出力端子(QB)はHレベルである。図1の駆動回路HVICの場合には、スイッチSW1がオン状態になっているため、抵抗部RP1(ノードND1と電源ノードVBとの間)の抵抗値は抵抗素子R1の抵抗値と抵抗素子R5の抵抗値との並列合成抵抗(R1//R5)になる。

【0057】

時刻t1に入力信号INがHレベルに切替わることによってワンショットパルス発生回路C1からパルス信号PLS1(パルス幅は時刻t1から時刻t4まで)が出力される。この結果、ノードND1,ND2の電位(Son,Mon)が低下する。

【0058】

次の時刻t2に、ノードND2の電位(マスク信号Mon)がインバータU3の閾値TH以下となるので、インバータU3の出力がHレベルに切替わる。

【0059】

次の時刻t3に、ノードND1の電位(オン信号Son)がインバータU4の閾値TH以下となるので、インバータU4の出力がHレベルに切替わる。これによって、RSフリップフロップU15のセット端子(S)の入力がHレベルになるので、RSフリップフロップU15の出力端子(Q)がHレベルに切替わり、反転出力端子(QB)がLレベルに切替わり、駆動回路HVICの信号出力ノードHOがHレベルに切替わる。さらに、RSフリップフロップU15の出力端子(Q)および反転出力端子(QB)の電圧変化に伴ってスイッチSW1がオフ状態になり、スイッチSW2がオン状態になる。スイッチSW1がオフ状態になると、抵抗部RP1(ノードND1と電源ノードVBとの間)の抵抗値は抵抗素子R1の抵抗値に増大するので、時刻t3以前よりも急峻にオン信号Sonおよびマスク信号Monが低下する。

【0060】

次の時刻t4で、NMOSトランジスタQ1のゲート入力(PLS2)が0Vに戻るので、ノードND1,ND2の電位(Son,Mon)が元の電位(電源ノードVBの電位)に戻る。この結果、インバータU3,U4の出力がLレベルに切替わり、RSフリップフロップU15へのセット端子(S)への入力がLレベルに戻る。

【0061】

次に、図1および図6の右側のグラフを参照して、実施の形態2による駆動回路HVICbの場合について説明する。この場合、初期状態では、スイッチSW1がオフ状態である点を除いて左側のグラフと同じである。スイッチSW1はRSフリップフロップU15の反転出力端子(QB)の出力とインバータU2との出力によって制御される。初期状態では反転出力端子(QB)はHレベルであるが、インバータU2の出力がLレベルであるので、スイッチSW1はオフ状態となっている。この結果、抵抗部RP1b(ノードND1と電源ノードVBとの間)の抵抗値は抵抗素子R1の抵抗値に等しい。

【0062】

時刻t11で、入力信号INがHレベルに切替わることによってワンショットパルス発生回路C1からパルス信号PLS1(パルス幅は時刻t11から時刻t14まで)が出力される。この結果、ノードND1,ND2の電位(Son,Mon)が低下する。このときの電位低下の速度は、図6の左側のグラフに比べてノードVB,ND1間の抵抗値が増大したために速くなる。

【0063】

時刻t12で、ノードND2の電位(マスク信号Mon)がインバータU3の閾値TH以下となるので、インバータU3の出力がHレベルに切替わる。

【0064】

次の時刻t13で、ノードND1の電位(オン信号Son)がインバータU4の閾値TH以下となるので、インバータU4の出力がHレベルに切替わる。これによって、RSフリップフロップU15のセット端子(S)の入力がHレベルになるので、RSフリップフロップU15の出力端子(Q)がHレベルに切替わり、反転出力端子(QB)がLレベルに切替わり、駆動回路HVICbの信号出力ノードHOがHレベルに切替わる。このとき、インバータU3の出力がHレベルであるので、スイッチSW2がオン状態になる。

【0065】

次の時刻t14で、NMOSトランジスタQ1のゲート入力(PLS2)が0Vに戻るので、ノードND1,ND2の電位(Son,Mon)が元の電位(電源ノードVBの電位)に戻る。この結果、インバータU3,U4の出力がLレベルに切替わり、RSフリップフロップU15へのセット端子(S)への入力がLレベルに戻り、スイッチSW2がオフ状態に戻る。

【0066】

RSフリップフロップU15のセット端子(S)に入力される信号のパルス幅を、実施の形態1の場合(時刻t3から時刻t4まで)と実施の形態2の場合(時刻t13から時刻t14まで)とを比較する。そうすると、実施の形態2の場合のパルス幅(時刻t13から時刻t14まで)は、実施の形態1の場合のパルス幅(時刻t3から時刻t4まで)に比べて長くなる。この結果、実施の形態2の場合のノイズ耐量は実施の形態1の場合に比べて改善する。

【0067】

図7は、図5の駆動回路HVICbにおいて、低電位側スイッチング素子Q6がターンオフする場合のタイミング図である。図7では、上から順に、低電位側スイッチング素子Q6のゲート駆動信号の波形(LO)、仮想接地ノードVS(電源ノードVB)の電圧変化、オン信号Son、マスク信号Mon、オフ信号Soff、およびマスク信号Moffの電圧波形、インバータU2、U1,U3,U4の各出力電圧波形、RSフリップフロップU15の反転出力端子(QB)および出力端子(Q)の各電圧波形、スイッチSW1,SW2のオン/オフの状態、RSフリップフロップU15のリセット端子(R)およびセット端子(S)の各電圧波形ならびに駆動回路HVICbの信号出力ノードHOの電圧波形が示される。

【0068】

図7において、初期状態ではRSフリップフロップU15はリセット状態にあり、その出力端子(Q)はLレベルであり、反転出力端子(QB)はHレベルである。この結果、駆動回路HVICbの信号出力ノードHOはLレベルになり、抵抗部RP3のスイッチSW2はオフ状態になる。抵抗部RP1のスイッチSW1は、インバータU2の出力がLレベルであるのでオフ状態になる。よって、抵抗部RP1b(電源ノードVBとノードND1との間)の抵抗値は、抵抗素子R1の抵抗値に等しくなり、抵抗部RP3b(電源ノードVBとノードND3との間)の抵抗値は、抵抗素子R3の抵抗値に等しくなる。

【0069】

時刻t1で低電位側スイッチング素子Q6用のゲート駆動回路の信号出力ノードLOがHレベルからLレベルに切替わる。これによって、仮想接地ノードVSの電位が低電位側スイッチング素子Q6のスイッチングスピードに応じて上昇するので、NMOSトランジスタQ1,Q2のドレインと基板との間の接合容量(寄生容量)が充電される。このとき、抵抗素子R1,R2の抵抗値と抵抗素子R3,R4の抵抗値とがそれぞれ等しく、かつ、NMOSトランジスタQ1,Q2の寄生容量が互いに等しければ、ノードND1の電位(オン信号Son)とノードND3の電位(オフ信号Soff)は同じ速度で低下し、ノードND2の電位(マスク信号Mon)とノードND4の電位(マスク信号Moff)は同じ速度で低下する。

【0070】

次の時刻t2で、マスク信号Mon,Moffが閾値TH以下となるので、インバータU2,U3の出力がHレベルに切替わる。RSフリップフロップU15の反転出力端子(QB)がHレベルでありかつインバータU2の出力がHレベルであるので、スイッチSW1がオン状態になる。この結果、抵抗部RP1b(ノードND1と電源ノードVBとの間)の抵抗値は抵抗素子R1の抵抗値と抵抗素子R5の抵抗値との並列合成抵抗(R1//R5)になる。この結果、時刻t2以降、オン信号Sonおよびマスク信号Monは、オフ信号Soffおよびマスク信号Moffに比べてより緩やかに低下する。

【0071】

次の時刻t3で、オフ信号Soffが閾値TH以下となるので、インバータU1の出力がHレベルに切替わる。マスク信号Monが既に閾値TH以下となっているので、RSフリップフロップU15のリセット端子(R)の入力はLレベルのままである。

【0072】

次の時刻t4で、オン信号SonがインバータU4の閾値TH以下となることによって

、インバータU4の出力がHレベルに切替わる。マスク信号Moffが既に閾値TH以下となっているので、RSフリップフロップU15のセット端子(S)の入力はLレベルのままである。

【0073】

次の時刻t5で、ダイオードD1,D2が導通し、ノードND1〜ND4の電位(Son,Mon,Soff,Moff)は一定値にクランプされる。次の時刻t6で仮想接地ノードVSの電位上昇が0になるので、ノードND1〜ND4の電位(Son,Soff,Mon,Moff)は元の電位(電源ノードVBの電位)に戻る。

【0074】

以上のように、駆動回路HVICbの仮想接地ノードVSの電位が上昇した場合でも信号出力ノードHOはLレベルを維持し、駆動回路HVICbは正常な動作を行なうことができる。

【0075】

<実施の形態3>

図8は、この発明の実施の形態3によるスイッチング素子の駆動回路HVICcの構成を示す回路図である。

【0076】

図8の高電圧回路部C2cは、図1の抵抗素子R5,R6およびスイッチSW1,SW2に代えて定電流供給部CS1,CS2が設けられている点で図1の高電圧回路部C2と異なる。

【0077】

具体的に、定電流供給部CS1は、電源ノードVBとノードND1との間に抵抗素子R1と並列に設けられた定電流源I1と、定電流源I1とノードND1との間に定電流源I1と直列に設けられたスイッチSW1とを含む。スイッチSW1は、RSフリップフロップU15の出力端子(Q)の出力を受け、出力端子(Q)がHレベルのときに導通する。したがって、定電流源I1は、高電位側スイッチング素子Q5がオン状態(RSフリップフロップU15はセット状態)のときに、抵抗素子R2を介してオン信号Sonを生成するためのNMOSトランジスタQ1に電流を供給する。

【0078】

定電流供給部CS2は、電源ノードVBとノードND3との間に抵抗素子R3と並列に設けられた定電流源I2と、定電流源I2とノードND3との間に定電流源I2と直列に設けられたスイッチSW2とを含む。スイッチSW2は、RSフリップフロップU15の反転出力端子(QB)の出力を受け、出力端子(QB)がHレベルのときに導通する。定電流源I2は、高電位側スイッチング素子Q5がオフ状態(RSフリップフロップU15はリセット状態)のときに、抵抗素子R4を介してオフ信号Soffを生成するためのNMOSトランジスタQ2に電流を供給する。図8のその他の点は図1と同じであるので、同一または相当する部分には同一の参照符号を付して説明を繰返さない。なお、図8において、抵抗素子R1〜R4の各々を複数の抵抗素子が直列および/または並列に接続されたものに置換することができる。この明細書では、抵抗素子が1個の場合と複数の場合とを含めて抵抗部と称する。

【0079】

図9は、図8に示す定電流源I1の構成の一例を示す回路図である。定電流源I2の構成は定電流源I1の構成と同じであるので、図9には定電流源I1の構成が代表として示される。

【0080】

図9を参照して、定電流源I1は、NMOSトランジスタQ101と、PMOSトランジスタQ102,Q103と、抵抗素子R101と、参照電源VREFと、差動増幅器U101とを含む。差動増幅器U101は、電源ノードVBと仮想接地ノードVSとの間の電圧(図8の直流電源V1)によって動作する。PMOSトランジスタQ103、NMOSトランジスタQ101、および抵抗素子R101は、この順で電源ノードVBと仮想接地ノードVSとの間に直列に接続される。PMOSトランジスタQ102,Q103はカレントミラーを構成する。参照電源VREFの負極は仮想接地ノードVSに接続され、正極は差動増幅器U101の非反転入力端子に接続される。差動増幅器U101の反転入力端子はNMOSトランジスタQ101のソース(ノードND101)に接続され、差動増幅器U101の出力端子はNMOSトランジスタQ101のゲートに接続される。

【0081】

以上の構成によって、NMOSトランジスタQ101には参照電源VREFの電圧に応じた参照電流が流れる。この参照電流は、PMOSトランジスタQ103とカレントミラーを構成するPMOSトランジスタQ102によってコピーされ、スイッチSW1を介して抵抗素子R3およびNMOSトランジスタQ1に供給される。

【0082】

図10は、図8の駆動回路HVICcの動作を示すタイミング図である。図10では、上から順に、低電位側スイッチング素子Q6のゲート駆動信号の波形(LO)、仮想接地ノードVS(電源ノードVB)の電圧変化、オン信号Son、マスク信号Mon、オフ信号Soff、およびマスク信号Moffの電圧波形、インバータU2、U1,U3,U4の各出力電圧波形、RSフリップフロップU15の反転出力端子(QB)、出力端子(Q)、リセット端子(R)、およびセット端子(S)の各電圧波形、ならびに駆動回路HVICcの信号出力ノードHOの電圧波形が示される。以下、図8、図10を参照して図8の定電流供給部CS1,CS2の機能について説明する。

【0083】

図10において、初期状態ではRSフリップフロップU15はリセットされた状態にあり、その出力端子(Q)はLレベルであり、反転出力端子(QB)はHレベルである。この結果、駆動回路HVICcの信号出力ノードHOはLレベルになり、定電流供給部CS1のスイッチSW1はオフ状態になり、定電流供給部CS2のスイッチSW2はオン状態になる。

【0084】

時刻t1で低電位側スイッチング素子Q6用のゲート駆動回路の信号出力ノードLOがHレベルからLレベルに切替わる。これによって、仮想接地ノードVSの電位が低電位側スイッチング素子Q6のスイッチングスピードに応じて上昇するので、NMOSトランジスタQ1,Q2のドレインと基板との間の接合容量(寄生容量)が充電される。このとき、スイッチSW2がオン状態であるので、抵抗素子R2を流れる充電電流に比べて抵抗素子R4には定電流源I2による電流の分だけ多くの充電電流が流れる。この結果、ノードND3,ND4の電位(オフ信号Soffおよびマスク信号Moff)は、ノードND1,ND2の電位(オン信号Sonおよびマスク信号Mon)よりも低下する。

【0085】

このため、次の時刻t2でマスク信号Moffが最初にインバータU2の閾値TH以下となる。これによって、インバータU2の出力がHレベルに切替わる。

【0086】

次の時刻t3でオフ信号SoffがインバータU1の閾値TH以下となることによって、インバータU1の出力がHレベルに切替わる。次の時刻t4でマスク信号MonがインバータU3の閾値TH以下となることによって、インバータU3の出力がHレベルに切替わる。

【0087】

時刻t3からt4の間で、RSフリップフロップU15のリセット端子(R)への入力がHレベルになるが、RSフリップフロップU15は元々リセットされた状態であるので出力端子(Q)および反転出力端子(QB)の論理レベルは変化しない。この結果、駆動回路HVICcの信号出力ノードHOはLレベルを維持し、駆動回路HVICcは正常な動作を行なうことができる。

【0088】

次の時刻t5でオン信号SonがインバータU4の閾値TH以下となることによって、インバータU4の出力がHレベルに切替わる。

【0089】

次の時刻t6で、ダイオードD1,D2が導通し、ノードND1〜ND4の電位(Son,Mon,Soff,Moff)は一定値にクランプされる。次の時刻t7で仮想接地ノードVSの電位上昇が0になるので、ノードND1〜ND4の電位(Son,Soff,Mon,Moff)は元の電位(電源ノードVBの電位)に戻る。

【0090】

実施の形態1,2の駆動回路HVIC,HVICbでは、定電流源I1,I2の代わりに抵抗素子R5,R6が設けられていた。抵抗素子R5,R6を使用する場合には、仮想接地ノードVSの電位の変化率(dV/dt)に依存して、オン信号Sonとオフ信号Soffとの電位差やマスク信号Mon,Moff間の電位差が変化する。これに対して実施の形態3の場合には、オン信号Sonとオフ信号Soffとの電位差およぼマスク信号Mon,Moff間の電位差を仮想接地ノードVSの電位の変化率(dV/dt)に依存せず発生させることができる。このため、実施の形態3の場合には、実施の形態1,2の場合に比べてより信頼性高い駆動回路を実現することができる。

【0091】

その他のメリットとして、定電流源I1,I2を使用することによって、実施の形態1の駆動回路HVICと比べてスイッチSW1,SW2のオン/オフのタイミングが逆になる。このため、次にワンショットパルス発生回路C1からパルス信号が入力されるNMOSトランジスタに接続された負荷の抵抗値が変化しないので、設計が容易となる。

【0092】

上記では、定電流源I1,I2による電流は、それぞれノードND1,ND3に注入されていたが、必ずしもこれには限らない。たとえば、ノードND1,ND2間に抵抗素子R2と直列にさらに抵抗素子を設け、これらの抵抗素子の接続ノードに定電流源I1による電流を注入するようにしてもよい。あるいは、電源ノードVBとノードND1との間に抵抗素子R1と直列にさらに抵抗素子を設け、これらの抵抗素子の接続ノードに定電流源I1による電流を注入するようにしてもよい。すなわち、ノードND1とNMOSトランジスタQ1との間に1または複数の抵抗素子からなる抵抗部が設けられている場合に、これらの抵抗素子の少なくとも1つを介してNMOSトランジスタQ1に電流が供給されるようにすればよい。定電流源I2の場合も同様である。

【0093】

<実施の形態4>

図11は、この発明の実施の形態4によるスイッチング素子の駆動回路HVICdの構成を示す回路図である。

【0094】

図11の高電圧回路部C2dに設けられた定電流供給部CS1bは、AND回路U16をさらに含む点で図8の定電流供給部CS1と異なる。AND回路U16は、RSフリップフロップU15の出力端子(Q)の出力とインバータU3の出力とを受け、両方の出力ともHレベルのときにHレベルの信号をスイッチSW1に供給する。スイッチSW1は、AND回路U16から受けた信号がHレベルのとき導通する。

【0095】

図11の高電圧回路部C2dに設けられた定電流供給部CS2bは、AND回路U17をさらに含む点で図8の定電流供給部CS2と異なる。AND回路U17は、RSフリップフロップU15の反転出力端子(QB)の出力とインバータU2の出力とを受け、両方の出力ともHレベルのときにHレベルの信号をスイッチSW2に供給する。スイッチSW2は、AND回路U17から受けた信号がHレベルのとき導通する。

【0096】

AND回路U16、U17を設けたことによって、パルス信号PLS1,PLS2を受けて高電位側スイッチング素子Q5をオン状態およびオフ状態に切替えるとき、および仮想接地ノードVSの電位が上昇しているときのみに定電流源I1,I2を動作させるので、駆動回路の消費電力を低減させることができる。図11のその他の点は図8の場合と同じであるので、同一または相当する部分には同一の参照符号を付して説明を繰返さない。

【0097】

図12は、図11の駆動回路HVICdの動作を示すタイミング図である。図12では、上から順に、低電位側スイッチング素子Q6のゲート駆動信号の波形(LO)、仮想接地ノードVS(電源ノードVB)の電圧変化、オン信号Son、マスク信号Mon、オフ信号Soff、およびマスク信号Moffの電圧波形、インバータU2、U1,U3,U4の各出力電圧波形、RSフリップフロップU15の反転出力端子(QB)および出力端子(Q)の各電圧波形、スイッチSW2,SW1のオン/オフの状態、RSフリップフロップU15のリセット端子(R)およびセット端子(S)の各電圧波形ならびに駆動回路HVICdの信号出力ノードHOの電圧波形が示される。

【0098】

図12において、初期状態ではRSフリップフロップU15はリセット状態にあり、その出力端子(Q)はLレベルであり、反転出力端子(QB)はHレベルである。この結果、駆動回路HVICdの信号出力ノードHOはLレベルになり、定電流供給部CS1bのスイッチSW1はオフ状態になる。定電流供給部CS2bのスイッチSW2は、インバータU2の出力がLレベルであるのでオフ状態になる。

【0099】

時刻t1で低電位側スイッチング素子Q6用のゲート駆動回路の信号出力ノードLOがHレベルからLレベルに切替わる。これによって、仮想接地ノードVSの電位が低電位側スイッチング素子Q6のスイッチングスピードに応じて上昇するので、NMOSトランジスタQ1,Q2のドレインと基板との間の接合容量(寄生容量)が充電される。このとき、スイッチSW1,SW2がオフ状態であるので、定電流源I1,I2による電流供給は行われない。したがって、抵抗素子R1,R2の抵抗値と抵抗素子R3,R4の抵抗値とがそれぞれ等しく、かつ、NMOSトランジスタQ1,Q2の寄生容量が互いに等しければ、ノードND1の電位(オン信号Son)とノードND3の電位(オフ信号Soff)は同じ速度で低下し、ノードND2の電位(マスク信号Mon)とノードND4の電位(マスク信号Moff)は同じ速度で低下する。

【0100】

次の時刻t2で、マスク信号Mon,Moffが閾値TH以下となるので、インバータU2,U3の出力がHレベルに切替わる。RSフリップフロップU15の反転出力端子(QB)がHレベルでありかつインバータU2の出力がHレベルであるので、スイッチSW2がオン状態になる。この結果、抵抗素子R4を介してオフ信号用のNMOSトランジスタQ2に定電流源I2から充電電流が供給されるので、時刻t2以降、オフ信号Soffおよびマスク信号Moffはオン信号Sonおよびマスク信号Monに比べてより早く低下する。

【0101】

次の時刻t3で、オフ信号Soffが閾値TH以下となるので、インバータU1の出力がHレベルに切替わる。マスク信号Monが既に閾値TH以下となっているので、RSフリップフロップU15のリセット端子(R)の入力はLレベルのままである。

【0102】

次の時刻t4で、オン信号SonがインバータU4の閾値TH以下となることによって、インバータU4の出力がHレベルに切替わる。マスク信号Moffが既に閾値TH以下となっているので、RSフリップフロップU15のセット端子(S)の入力はLレベルのままである。

【0103】

次の時刻t5で、ダイオードD1,D2が導通し、ノードND1〜ND4の電位(Son,Mon,Soff,Moff)は一定値にクランプされる。次の時刻t6で仮想接地ノードVSの電位上昇が0になるので、ノードND1〜ND4の電位(Son,Soff,Mon,Moff)は元の電位(電源ノードVBの電位)に戻る。

【0104】

以上のように、駆動回路HVICdの仮想接地ノードVSの電位が上昇した場合でも信号出力ノードHOはLレベルを維持し、駆動回路HVICdは正常な動作を行なうことができる。

【0105】

<実施の形態5>

図13は、この発明の実施の形態5によるスイッチング素子の駆動回路HVICeの構成を示す回路図である。

【0106】

図13の高電圧回路部C2eは、図1の抵抗素子R5,R6およびスイッチSW1,SW2に代えて、閾値変化部THC1,THC2が設けられている点で図1の高電圧回路部C2と異なる。

【0107】

具体的に、閾値変化部THC1は、インバータU3の出力ノードと仮想接地ノードVSとの間に設けられたNMOSトランジスタQ9と、インバータU4の出力ノードと仮想接地ノードVSとの間に設けられたNMOSトランジスタQ10とを含む。NMOSトランジスタQ9,Q10のゲートは、RSフリップフロップU15の反転出力端子(QB)に接続される。

【0108】

閾値変化部THC2は、インバータU1の出力ノードと仮想接地ノードVSとの間に設けられたNMOSトランジスタQ7と、インバータU2の出力ノードと仮想接地ノードVSとの間に設けられたNMOSトランジスタQ8とを含む。NMOSトランジスタQ7,Q8のゲートは、RSフリップフロップU15の出力端子(Q)に接続される。

【0109】

図13においてインバータU1〜U4はCMOSインバータである。すなわち、各インバータの出力ノードと電源ノードVBとの間にPMOSトランジスタが設けられ、各インバータの出力ノードと仮想接地ノードVSとの間にNMOSトランジスタが設けられる。これらのPMOSトランジスタおよびNMOSトランジスタのゲートが、ノードND1〜ND4のうち対応のノードと接続される。

【0110】

インバータU1〜U4の各々は、出力ノードに接続された対応のNMOSトランジスタ(Q7〜Q10)がオン状態の場合には、入力信号レベルが十分に低下しないと出力がHレベルに変化しない。すなわち、出力ノードに接続された対応のNMOSトランジスタがオン状態の場合には、インバータの閾値が低下した状態になる。したがって、NMOSトランジスタQ7〜Q10のオン/オフを制御することによって、それぞれ対応するインバータU1〜U4の閾値を制御することができる。

【0111】

図13のその他の点は図1と同じであるので、同一または相当する部分には同一の参照符号を付して説明を繰返さない。なお、図13において、抵抗素子R1〜R4の各々を複数の抵抗素子が直列および/または並列に接続されたものに置換することができる。この明細書では、抵抗素子が1個の場合と複数の場合とを含めて抵抗部と称する。

【0112】

図14は、図13の駆動回路HVICeの動作を示すタイミング図である。図14では、上から順に、低電位側スイッチング素子Q6のゲート駆動信号の波形(LO)、仮想接地ノードVS(電源ノードVB)の電圧変化、オン信号Son、マスク信号Mon、オフ信号Soff、およびマスク信号Moffの電圧波形、インバータU2、U1,U3,U4の各出力電圧波形、RSフリップフロップU15の反転出力端子(QB)、出力端子(Q)、リセット端子(R)、およびセット端子(S)の各電圧波形ならびに駆動回路HVICeの信号出力ノードHOの電圧波形が示される。

【0113】

図14において、初期状態ではRSフリップフロップU15はリセット状態にあり、その出力端子(Q)はLレベルであり、反転出力端子(QB)はHレベルである。この結果、駆動回路HVICeの信号出力ノードHOはLレベルになり、閾値変化部THC1のNMOSトランジスタQ9,Q10はオン状態になり、閾値変化部THC2のNMOSトランジスタQ7,Q8はオフ状態になる。これによって、インバータU3,U4の閾値TH2は、インバータU1,U2の閾値TH1よりも低下する。

【0114】

時刻t1で低電位側スイッチング素子Q6用のゲート駆動回路の信号出力ノードLOがHレベルからLレベルに切替わる。これによって、仮想接地ノードVSの電位が低電位側スイッチング素子Q6のスイッチングスピードに応じて上昇するので、NMOSトランジスタQ1,Q2のドレインと基板との間の接合容量(寄生容量)が充電される。このとき、抵抗素子R1,R2の抵抗値と抵抗素子R3,R4の抵抗値とがそれぞれ等しく、かつ、NMOSトランジスタQ1,Q2の寄生容量が互いに等しければ、ノードND1の電位(オン信号Son)とノードND3の電位(オフ信号Soff)は同じ速度で低下し、ノードND2の電位(マスク信号Mon)とノードND4の電位(マスク信号Moff)は同じ速度で低下する。

【0115】

次の時刻t2で、マスク信号MoffがインバータU2の閾値TH1以下となるので、インバータU2の出力がHレベルに切替わる。

【0116】

次の時刻t3で、オフ信号SoffがインバータU1の閾値TH1以下となるので、インバータU1の出力がHレベルに切替わる。この結果、RSフリップフロップU15のリセット端子(R)の入力信号がHレベルに切替わる。RSフリップフロップU15は既にリセットされた状態であるので、出力端子Qおよび反転出力端子QBは、それぞれLレベルおよびHレベルのままで変化しない。

【0117】

次の時刻t4で、マスク信号MonがインバータU3の閾値TH2以下となるので、インバータU3の出力がHレベルに切替わる。これによって、オフ信号Soffがマスクされるので、RSフリップフロップU15のリセット端子(R)の入力信号がLレベルに切替わる。

【0118】

次の時刻t5で、オン信号SonがインバータU4の閾値TH2以下となるので、インバータU4の出力がHレベルに切替わる。

【0119】

次の時刻t5で、ダイオードD1,D2が導通し、ノードND1〜ND4の電位(Son,Mon,Soff,Moff)は一定値にクランプされる。次の時刻t6で仮想接地ノードVSの電位上昇が0になるので、ノードND1〜ND4の電位(Son,Soff,Mon,Moff)は元の電位(電源ノードVBの電位)に戻る。

【0120】

以上のように、駆動回路HVICeの仮想接地ノードVSの電位が上昇した場合でも信号出力ノードHOはLレベルを維持し、駆動回路HVICeは正常な動作を行なうことができる。

【0121】

実施の形態1,2の駆動回路HVIC,HVICbでは、抵抗値が変化する抵抗部RP1,RP2がNMOSトランジスタQ1,Q2の負荷抵抗として設けられていた。このように負荷抵抗の抵抗値を変化させる場合には、仮想接地ノードVSの電位の変化率(dV/dt)に依存して、オン信号Sonとオフ信号Soffとの電位差やマスク信号Mon,Moff間の電位差が変化する。これに対して実施の形態5の場合には、オン信号Son、オフ信号Soff、およびマスク信号Mon,Moffと比較される閾値を変化させているので、インバータU1〜U4の出力が切替わるタイミングを仮想接地ノードVSの電位の変化率(dV/dt)に依存せず制御することができる。このため、実施の形態5の場合には、実施の形態1,2の場合に比べて設計が容易であり、より信頼性高い駆動回路を実現することができる。

【0122】

<実施の形態6>

図15は、この発明の実施の形態6によるスイッチング素子の駆動回路HVICfの構成を示す回路図である。

【0123】

図15の高電圧回路部C2fに設けられた閾値変化部THC1bは、AND回路U16をさらに含む点で図13の閾値変化部THC1と異なる。AND回路U16は、RSフリップフロップU15の反転出力端子(QB)の出力とインバータU2の出力とを受け、両方の出力ともHレベルのときにHレベルの信号をNMOSトランジスタQ9,Q10のゲートに出力する。

【0124】

図15の高電圧回路部C2fに設けられた閾値変化部THC2bは、AND回路U17をさらに含む点で図13の閾値変化部THC2と異なる。AND回路U17は、RSフリップフロップU15の出力端子(Q)の出力とインバータU3の出力とを受け、両方の出力ともHレベルのときにHレベルの信号をNMOSトランジスタQ7,Q8のゲートに出力する。図15のその他の点は図13の場合と同じであるので、同一または相当する部分には同一の参照符号を付して説明を繰返さない。

【0125】

図16は、図13の駆動回路HVICeの動作と図15の駆動回路HVICfの動作とを対比して示すタイミング図である。図16の左側のグラフには高電位側スイッチング素子Q5をターンオンさせる場合の駆動回路HVICe(実施の形態5)の各部の電圧波形が示される。図16の右側のグラフには同じ場合の駆動回路HVICf(実施の形態6)の各部の電圧波形が示される。左右のそれぞれのグラフにおいて、上から順に、ワンショットパルス発生回路C1の入力信号INおよび出力パルス信号PLS1,PLS2の各電圧波形、オン信号Son、マスク信号Mon、オフ信号Soff、およびマスク信号Moffの電圧波形、インバータU3、U4,U2,U1の各出力電圧波形、RSフリップフロップU15の出力端子(Q)および反転出力端子(QB)の電圧波形、NMOSトランジスタQ7,Q8のオン/オフの状態、NMOSトランジスタQ9,Q10のオン/オフの状態、RSフリップフロップU15のおよびセット端子(S)およびリセット端子(R)の各電圧波形ならびに駆動回路HVICe,HVICfの信号出力ノードHOの電圧波形が示される。

【0126】

まず、図13および図16の左側のグラフを参照して、実施の形態5による駆動回路HVICeの場合について説明する。この場合、初期状態では、ワンショットパルス発生回路C1の入力信号INがLレベルである。このとき、RSフリップフロップU15はリセットされた状態であるので、出力端子(Q)はLレベルであり、反転出力端子(QB)はHレベルである。図13の駆動回路HVICeの場合には、NMOSトランジスタQ9,Q10がオン状態になっているため、インバータU3,U4の閾値TH2がインバータU1,U2の閾値TH1よりも低下する。

【0127】

時刻t1に入力信号INがHレベルに切替わることによってワンショットパルス発生回路C1からパルス信号PLS1(パルス幅は時刻t1から時刻t4まで)が出力される。この結果、ノードND1,ND2の電位(Son,Mon)が低下する。

【0128】

次の時刻t2に、ノードND2の電位(マスク信号Mon)がインバータU3の閾値TH2以下となるので、インバータU3の出力がHレベルに切替わる。

【0129】

次の時刻t3に、ノードND1の電位(オン信号Son)がインバータU4の閾値TH2以下となるので、インバータU4の出力がHレベルに切替わる。これによって、RSフリップフロップU15のセット端子(S)の入力がHレベルになるので、RSフリップフロップU15の出力端子(Q)がHレベルに切替わり、反転出力端子(QB)がLレベルに切替わり、駆動回路HVICeの信号出力ノードHOがHレベルに切替わる。さらに、RSフリップフロップU15の出力端子(Q)および反転出力端子(QB)の電圧変化に伴ってNMOSトランジスタQ7,Q8がオン状態になり、NMOSトランジスタQ9,Q10がオフ状態になる。

【0130】

次の時刻t4で、NMOSトランジスタQ1のゲート入力(PLS1)が0Vに戻るので、ノードND1,ND2の電位(Son,Mon)が元の電位(電源ノードVBの電位)に戻る。この結果、インバータU3,U4の出力がLレベルに切替わり、RSフリップフロップU15へのセット端子(S)への入力がLレベルに戻る。

【0131】

次に、図13および図16の右側のグラフを参照して、実施の形態6による駆動回路HVICfの場合について説明する。この場合、初期状態では、NMOSトランジスタQ9,Q10がオフ状態である点を除いて左側のグラフと同じである。NMOSトランジスタQ9,Q10はRSフリップフロップU15の反転出力端子(QB)の出力とインバータU2との出力によって制御されるため、初期状態では反転出力端子(QB)はHレベルであるが、インバータU2がLレベルであるので、NMOSトランジスタQ9,Q10がオフ状態となっている。この結果、インバータU3,U4の閾値はTH1であり、TH2に低下していない。

【0132】

時刻t11に入力信号INがHレベルに切替わることによってワンショットパルス発生回路C1からパルス信号PLS1(パルス幅は時刻t11から時刻t14まで)が出力される。この結果、ノードND1,ND2の電位(Son,Mon)が低下する。

【0133】

次の時刻t12で、ノードND2の電位(マスク信号Mon)がインバータU3の閾値TH1以下となるので(ただし、TH1>TH2)、インバータU3の出力がHレベルに切替わる。

【0134】

次の時刻t13に、ノードND1の電位(オン信号Son)がインバータU4の閾値TH1以下となるので、インバータU4の出力がHレベルに切替わる。これによって、RSフリップフロップU15のセット端子(S)の入力がHレベルになるので、RSフリップフロップU15の出力端子(Q)がHレベルに切替わり、反転出力端子(QB)がLレベルに切替わり、駆動回路HVICfの信号出力ノードHOがHレベルに切替わる。このとき、インバータU3の出力がHレベルであるので、NMOSトランジスタQ7,Q8がオン状態になる。

【0135】

次の時刻t14で、NMOSトランジスタQ1のゲート入力(PLS1)が0Vに戻るので、ノードND1,ND2の電位(Son,Mon)が元の電位(電源ノードVBの電位)に戻る。この結果、インバータU3,U4の出力がLレベルに切替わり、RSフリップフロップU15へのセット端子(S)への入力がLレベルに戻り、トランジスタQ7,Q8がオフ状態なる。

【0136】

RSフリップフロップU15のセット端子(S)に入力される信号のパルス幅を、実施の形態5の場合(時刻t3から時刻t4まで)と実施の形態6の場合(時刻t13から時刻t14まで)とを比較する。そうすると、実施の形態6の場合のパルス幅(時刻t13から時刻t14まで)は、実施の形態5の場合のパルス幅(時刻t3から時刻t4まで)に比べて長くなる。この結果、実施の形態6の場合のノイズ耐量は実施の形態5の場合に比べて改善する。

【0137】

図17は、図15の駆動回路HVICfにおいて、低電位側スイッチング素子Q6がターンオフする場合のタイミング図である。

図17では、上から順に、低電位側スイッチング素子Q6のゲート駆動信号の波形(LO)、仮想接地ノードVS(電源ノードVB)の電圧変化、オン信号Son、マスク信号Mon、オフ信号Soff、およびマスク信号Moffの電圧波形、インバータU2、U1,U3,U4の各出力電圧波形、RSフリップフロップU15の反転出力端子(QB)および出力端子(Q)の各電圧波形、NMOSトランジスタQ9,Q10のオン/オフの状態、NMOSトランジスタQ7,Q8のオン/オフの状態、RSフリップフロップU15のリセット端子(R)およびセット端子(S)の各電圧波形ならびに駆動回路HVICfの信号出力ノードHOの電圧波形が示される。

【0138】

図17において、初期状態ではRSフリップフロップU15はリセット状態にあり、その出力端子(Q)はLレベルであり、反転出力端子(QB)はHレベルである。この結果、駆動回路HVICfの信号出力ノードHOはLレベルになる。インバータU2,U3の出力はLレベルであるので、NMOSトランジスタQ7〜Q10のいずれもオフ状態になる。インバータU1〜U4の閾値は比較的高いTH1になる(TH1>TH2とする)。

【0139】

時刻t1で低電位側スイッチング素子Q6用のゲート駆動回路の信号出力ノードLOがHレベルからLレベルに切替わる。これによって、仮想接地ノードVSの電位が低電位側スイッチング素子Q6のスイッチングスピードに応じて上昇するので、NMOSトランジスタQ1,Q2のドレインと基板との間の接合容量(寄生容量)が充電される。このとき、抵抗素子R1,R2の抵抗値と抵抗素子R3,R4の抵抗値とがそれぞれ等しく、かつ、NMOSトランジスタQ1,Q2の寄生容量が互いに等しければ、ノードND1の電位(オン信号Son)とノードND3の電位(オフ信号Soff)は同じ速度で低下し、ノードND2の電位(マスク信号Mon)とノードND4の電位(マスク信号Moff)は同じ速度で低下する。

【0140】

次の時刻t2で、マスク信号MoffがインバータU2の閾値TH1以下となるので、インバータU2の出力がHレベルに切替わる。これによって、NMOSトランジスタQ9,Q10がオン状態になるので、インバータU3,U4の閾値をTH1からTH2に低下させる。

【0141】

次の時刻t3で、オフ信号SoffがインバータU1の閾値TH1以下となるので、インバータU1の出力がHレベルに切替わる。この結果、RSフリップフロップU15のリセット端子(R)の入力信号がHレベルに切替わる。RSフリップフロップU15は既にリセットされた状態であるので、出力端子Qおよび反転出力端子QBは、それぞれLレベルおよびHレベルのままで変化しない。

【0142】

次の時刻t4で、マスク信号MonがインバータU3の閾値TH2以下となるので、インバータU3の出力がHレベルに切替わる。これによって、オフ信号Soffがマスクされるので、RSフリップフロップU15のリセット端子(R)の入力信号がLレベルに切替わる。

【0143】

次の時刻t5で、オン信号SonがインバータU4の閾値TH2以下となるので、インバータU4の出力がHレベルに切替わる。

【0144】

次の時刻t5で、ダイオードD1,D2が導通し、ノードND1〜ND4の電位(Son,Mon,Soff,Moff)は一定値にクランプされる。次の時刻t6で仮想接地ノードVSの電位上昇が0になるので、ノードND1〜ND4の電位(Son,Soff,Mon,Moff)は元の電位(電源ノードVBの電位)に戻る。

【0145】

以上のように、駆動回路HVICfの仮想接地ノードVSの電位が上昇した場合でも信号出力ノードHOはLレベルを維持し、駆動回路HVICfは正常な動作を行なうことができる。

【0146】

今回開示された実施の形態はすべての点で例示であって制限的なものでないと考えられるべきである。この発明の範囲は上記した説明ではなくて請求の範囲によって示され、請求の範囲と均等の意味および範囲内でのすべての変更が含まれることが意図される。

【符号の説明】

【0147】

C1 ワンショットパルス発生回路、CS1,CS2,CS1b,CS2b 定電流供給部、GND 接地ノード、HO 信号出力ノード(高電位側)、HV 高電圧電源、HVIC,HVICb〜HVICf 駆動回路、HVN 高電位側電源ノード、I1,I2 定電流源、LO 信号出力ノード(低電位側)、Moff,Mon マスク信号、ND1〜ND4 ノード、PLS1,PLS2 パルス信号、Q1,Q2 NMOSトランジスタ(制御用スイッチング素子)、Q5 高電位側スイッチング素子、Q6 低電位側スイッチング素子、R1〜R6 抵抗素子、RP1〜RP4,RP1b,RP2b 抵抗部、SW1,SW2 スイッチ、Soff オフ信号、Son オン信号、TH,TH1,TH2 閾値、THC1,THC2,THC1b,THC2b 閾値変化部、U15 フリップフロップ、V1 直流電源、VB 電源ノード、VS 仮想接地ノード。

【特許請求の範囲】

【請求項1】

第1の電源ノードとそれより高電位に設定される第2の電源ノードとの間に直列に接続された2つのスイッチング素子のうち高電位側のスイッチング素子の駆動回路であって、

前記2つのスイッチング素子の接続ノードの電位よりも高電位に設定される第3の電源ノードと、

内部状態として第1および第2の状態を有し、前記内部状態に応じて前記高電位側のスイッチング素子をオン状態またはオフ状態に切替えるために、前記第1および第2の状態にそれぞれ対応して第1および第2の論理レベルに切替わる制御信号を出力する論理回路と、

前記第3の電源ノードと第1のノードとの間に設けられた第1の抵抗部と、

前記第1のノードと第2のノードとの間に設けられた第2の抵抗部と、

前記第2のノードと前記第1の電源ノードとの間に設けられ、第1のパルス信号を受けたときに導通する第1の制御用スイッチング素子と、

前記第1のパルス信号に応じて前記論理回路を前記第1の状態から前記第2の状態に切替えるために、前記第1のノードの電位が第1の閾値以下の場合に活性状態となる第1の信号を出力する第1の比較部とを備え、

前記第1および第2の抵抗部の少なくとも一方の抵抗値は、少なくとも前記制御信号の変化に基づいたタイミングで変化する、スイッチング素子の駆動回路。

【請求項2】

前記第3の電源ノードと第3のノードとの間に設けられた第3の抵抗部と、

前記第3のノードと第4のノードとの間に設けられた第4の抵抗部と、

前記第4のノードと前記第1の電源ノードとの間に設けられ、前記第1のパルス信号とタイミングの異なる第2のパルス信号を受けたときに導通する第2の制御用スイッチング素子と、

前記第2のパルス信号に応じて前記論理回路を前記第2の状態から前記第1の状態に切替えるために、前記第3のノードの電位が第2の閾値以下の場合に活性状態となる第2の信号を出力する第2の比較部と、

前記第4のノードの電位が第3の閾値以下の場合に活性状態になる第3の信号を出力する第3の比較部とをさらに備え、

前記第1および第2の抵抗部の少なくとも一方の抵抗値は、前記制御信号が前記第1の論理レベルでありかつ前記第3の信号が活性状態の場合に、前記制御信号が前記第2の論理レベルの場合に比べて前記第1の抵抗部の抵抗値に対する前記第2の抵抗部の抵抗値の比率が増加するように変化する、請求項1に記載のスイッチング素子の駆動回路。

【請求項3】

前記第1および第2の抵抗部の少なくとも一方の抵抗値は、前記制御信号が前記第1の論理レベルの場合に、前記制御信号が前記第2の論理レベルの場合に比べて前記第1の抵抗部の抵抗値に対する前記第2の抵抗部の抵抗値の比率が増加するように変化する、請求項1に記載のスイッチング素子の駆動回路。

【請求項4】

前記第1の抵抗部は、

前記第3の電源ノードと前記第1のノードとの間に設けられた第1の抵抗素子と、

前記第3の電源ノードと前記第1のノードとの間に前記第1の抵抗素子と並列に設けられた第2の抵抗素子と、

前記第3の電源ノードと前記第1のノードとの間に前記第2の抵抗素子と直列に設けられ、前記制御信号が前記第1の論理レベルでありかつ前記第3の信号が活性状態の場合に導通する第3の制御用スイッチング素子とを含む、請求項2に記載のスイッチング素子の駆動回路。

【請求項5】

前記第1の抵抗部は、

前記第3の電源ノードと前記第1のノードとの間に設けられた第1の抵抗素子と、

前記第3の電源ノードと前記第1のノードとの間に前記第1の抵抗素子と並列に設けられた第2の抵抗素子と、

前記第3の電源ノードと前記第1のノードとの間に前記第2の抵抗素子と直列に設けられ、前記制御信号が前記第1の論理レベルの場合に導通する第3の制御用スイッチング素子とを含む、請求項3に記載のスイッチング素子の駆動回路。

【請求項6】

第1の電源ノードとそれより高電位に設定される第2の電源ノードとの間に直列に接続された2つのスイッチング素子のうち高電位側のスイッチング素子の駆動回路であって、

前記2つのスイッチング素子の接続ノードの電位よりも高電位に設定される第3の電源ノードと、

内部状態として第1および第2の状態を有し、前記内部状態に応じて前記高電位側のスイッチング素子をオン状態またはオフ状態に切替えるために、前記第1および第2の状態にそれぞれ対応して第1および第2の論理レベルに切替わる制御信号をそれぞれ出力する論理回路と、

前記第3の電源ノードと第1のノードとの間に設けられた第1の抵抗部と、

前記第1のノードと第2のノードとの間に設けられた第2の抵抗部と、

前記第2のノードと前記第1の電源ノードとの間に設けられ、第1のパルス信号を受けたときに導通する第1の制御用スイッチング素子と、

前記第1のパルス信号に応じて前記論理回路を前記第1の状態から前記第2の状態に切替えるために、前記第1のノードの電位が第1の閾値以下の場合に活性状態となる第1の信号を出力する第1の比較部と、

少なくとも前記制御信号の変化に基づいたタイミングで、前記第2の抵抗部を構成する1または複数の抵抗素子の少なくとも1つを介して前記第1の制御用スイッチング素子に定電流を供給可能な定電流供給部とを備える、スイッチング素子の駆動回路。

【請求項7】

前記第2のノードの電位が第2の閾値以下の場合に活性状態になる第2の信号を出力する第2の比較部とをさらに備え、

前記定電流供給部は、前記制御信号が前記第2の論理レベルでありかつ前記第2の信号が活性状態の場合に、前記第2の抵抗部を構成する1または複数の抵抗素子の少なくとも1つを介して前記第1の制御用スイッチング素子に定電流を供給可能である、請求項6に記載のスイッチング素子の駆動回路。

【請求項8】

前記定電流供給部は、前記制御信号が前記第2の論理レベルの場合に、前記第2の抵抗部を構成する1または複数の抵抗素子の少なくとも1つを介して前記第1の制御用スイッチング素子に定電流を供給可能である、請求項6に記載のスイッチング素子の駆動回路。

【請求項9】

前記定電流供給部は、

前記第3の電源ノードと前記第1のノードとの間に前記第1の抵抗部と並列に設けられた定電流源と、

前記定電流源と前記第1のノードとの間に前記定電流源と直列に設けられ、前記制御信号が前記第2の論理レベルでありかつ前記第2の信号が活性状態の場合に導通する第2の制御用スイッチング素子とを含む、請求項7に記載のスイッチング素子の駆動回路。

【請求項10】

前記定電流供給部は、

前記第3の電源ノードと前記第1のノードとの間に前記第1の抵抗部と並列に設けられた定電流源と、

前記定電流源と前記第1のノードとの間に前記定電流源と直列に設けられ、前記制御信号が前記第2の論理レベルの場合に導通する第2の制御用スイッチング素子とを含む、請求項8に記載のスイッチング素子の駆動回路。

【請求項11】

第1の電源ノードとそれより高電位に設定される第2の電源ノードとの間に直列に接続された2つのスイッチング素子のうち高電位側のスイッチング素子の駆動回路であって、

前記2つのスイッチング素子の接続ノードの電位よりも高電位に設定される第3の電源ノードと、

内部状態として第1および第2の状態を有し、前記内部状態に応じて前記高電位側のスイッチング素子をオン状態またはオフ状態に切替えるために、前記第1および第2の状態にそれぞれ対応して第1および第2の論理レベルに切替わる制御信号をそれぞれ出力する第1の論理回路と、

前記第3の電源ノードと第1のノードとの間に設けられた第1の抵抗部と、

前記第1のノードと前記第1の電源ノードとの間に設けられ、第1のパルス信号を受けたときに導通する第1の制御用スイッチング素子と、

前記第1のパルス信号に応じて前記第1の論理回路を前記第1の状態から前記第2の状態に切替えるために、前記第1のノードの電位が第1の閾値以下の場合に活性状態となる第1の信号を出力する第1の比較部と、

少なくとも前記制御信号の変化に基づいたタイミングで、前記第1の閾値の大きさを変化させる閾値変化部とを備える、スイッチング素子の駆動回路。

【請求項12】

前記第3の電源ノードと第2のノードとの間に設けられた第2の抵抗部と、

前記第2のノードと第3のノードとの間に設けられた第3の抵抗部と、

前記第3のノードと前記第1の電源ノードとの間に設けられ、前記第1のパルス信号とタイミングの異なる第2のパルス信号を受けたときに導通する第2の制御用スイッチング素子と、

前記第2のパルス信号に応じて前記第1の論理回路を前記第2の状態から前記第1の状態に切替えるために、前記第2のノードの電位が第2の閾値以下の場合に活性状態となる第2の信号を出力する第2の比較部と、

前記第3のノードの電位が第3の閾値以下の場合に活性状態になる第3の信号を出力する第3の比較部とをさらに備え、

前記閾値変化部は、前記制御信号が前記第1の論理レベルでありかつ前記第3の信号が活性状態の場合に、前記制御信号が前記第2の論理レベルの場合に比べて前記第1の閾値の大きさを減少させる、請求項11に記載のスイッチング素子の駆動回路。

【請求項13】

前記閾値変化部は、前記制御信号が前記第1の論理レベルの場合に、前記制御信号が前記第2の論理レベルの場合に比べて前記第1の閾値の大きさを減少させる、請求項11に記載のスイッチング素子の駆動回路。

【請求項14】

前記第1の比較部は、前記第3の電源ノードと前記接続ノードとの間に供給された電圧で動作するMOSインバータであり、

前記閾値変化部は、

前記第1の比較部の出力ノードと前記接続ノードとの間に設けられたMOSトランジスタと、

前記制御信号が前記第1の論理レベルでありかつ前記第3の信号が活性状態の場合に、前記MOSトランジスタをオン状態にする信号を前記MOSトランジスタのゲートに供給する第2の論理回路とを含む、請求項12に記載のスイッチング素子の駆動回路。

【請求項15】

前記第1の比較部は、前記第3の電源ノードと前記接続ノードとの間に供給された電圧で動作するMOSインバータであり、

前記閾値変化部は、前記第1の比較部の出力ノードと前記接続ノードとの間に設けられ、前記制御信号が前記第1の論理レベルの場合にオン状態になるMOSトランジスタを含む、請求項13に記載のスイッチング素子の駆動回路。

【請求項1】

第1の電源ノードとそれより高電位に設定される第2の電源ノードとの間に直列に接続された2つのスイッチング素子のうち高電位側のスイッチング素子の駆動回路であって、

前記2つのスイッチング素子の接続ノードの電位よりも高電位に設定される第3の電源ノードと、

内部状態として第1および第2の状態を有し、前記内部状態に応じて前記高電位側のスイッチング素子をオン状態またはオフ状態に切替えるために、前記第1および第2の状態にそれぞれ対応して第1および第2の論理レベルに切替わる制御信号を出力する論理回路と、

前記第3の電源ノードと第1のノードとの間に設けられた第1の抵抗部と、

前記第1のノードと第2のノードとの間に設けられた第2の抵抗部と、

前記第2のノードと前記第1の電源ノードとの間に設けられ、第1のパルス信号を受けたときに導通する第1の制御用スイッチング素子と、

前記第1のパルス信号に応じて前記論理回路を前記第1の状態から前記第2の状態に切替えるために、前記第1のノードの電位が第1の閾値以下の場合に活性状態となる第1の信号を出力する第1の比較部とを備え、

前記第1および第2の抵抗部の少なくとも一方の抵抗値は、少なくとも前記制御信号の変化に基づいたタイミングで変化する、スイッチング素子の駆動回路。

【請求項2】

前記第3の電源ノードと第3のノードとの間に設けられた第3の抵抗部と、

前記第3のノードと第4のノードとの間に設けられた第4の抵抗部と、

前記第4のノードと前記第1の電源ノードとの間に設けられ、前記第1のパルス信号とタイミングの異なる第2のパルス信号を受けたときに導通する第2の制御用スイッチング素子と、

前記第2のパルス信号に応じて前記論理回路を前記第2の状態から前記第1の状態に切替えるために、前記第3のノードの電位が第2の閾値以下の場合に活性状態となる第2の信号を出力する第2の比較部と、

前記第4のノードの電位が第3の閾値以下の場合に活性状態になる第3の信号を出力する第3の比較部とをさらに備え、

前記第1および第2の抵抗部の少なくとも一方の抵抗値は、前記制御信号が前記第1の論理レベルでありかつ前記第3の信号が活性状態の場合に、前記制御信号が前記第2の論理レベルの場合に比べて前記第1の抵抗部の抵抗値に対する前記第2の抵抗部の抵抗値の比率が増加するように変化する、請求項1に記載のスイッチング素子の駆動回路。

【請求項3】

前記第1および第2の抵抗部の少なくとも一方の抵抗値は、前記制御信号が前記第1の論理レベルの場合に、前記制御信号が前記第2の論理レベルの場合に比べて前記第1の抵抗部の抵抗値に対する前記第2の抵抗部の抵抗値の比率が増加するように変化する、請求項1に記載のスイッチング素子の駆動回路。

【請求項4】

前記第1の抵抗部は、

前記第3の電源ノードと前記第1のノードとの間に設けられた第1の抵抗素子と、

前記第3の電源ノードと前記第1のノードとの間に前記第1の抵抗素子と並列に設けられた第2の抵抗素子と、

前記第3の電源ノードと前記第1のノードとの間に前記第2の抵抗素子と直列に設けられ、前記制御信号が前記第1の論理レベルでありかつ前記第3の信号が活性状態の場合に導通する第3の制御用スイッチング素子とを含む、請求項2に記載のスイッチング素子の駆動回路。

【請求項5】

前記第1の抵抗部は、

前記第3の電源ノードと前記第1のノードとの間に設けられた第1の抵抗素子と、

前記第3の電源ノードと前記第1のノードとの間に前記第1の抵抗素子と並列に設けられた第2の抵抗素子と、

前記第3の電源ノードと前記第1のノードとの間に前記第2の抵抗素子と直列に設けられ、前記制御信号が前記第1の論理レベルの場合に導通する第3の制御用スイッチング素子とを含む、請求項3に記載のスイッチング素子の駆動回路。

【請求項6】

第1の電源ノードとそれより高電位に設定される第2の電源ノードとの間に直列に接続された2つのスイッチング素子のうち高電位側のスイッチング素子の駆動回路であって、

前記2つのスイッチング素子の接続ノードの電位よりも高電位に設定される第3の電源ノードと、

内部状態として第1および第2の状態を有し、前記内部状態に応じて前記高電位側のスイッチング素子をオン状態またはオフ状態に切替えるために、前記第1および第2の状態にそれぞれ対応して第1および第2の論理レベルに切替わる制御信号をそれぞれ出力する論理回路と、

前記第3の電源ノードと第1のノードとの間に設けられた第1の抵抗部と、

前記第1のノードと第2のノードとの間に設けられた第2の抵抗部と、

前記第2のノードと前記第1の電源ノードとの間に設けられ、第1のパルス信号を受けたときに導通する第1の制御用スイッチング素子と、

前記第1のパルス信号に応じて前記論理回路を前記第1の状態から前記第2の状態に切替えるために、前記第1のノードの電位が第1の閾値以下の場合に活性状態となる第1の信号を出力する第1の比較部と、

少なくとも前記制御信号の変化に基づいたタイミングで、前記第2の抵抗部を構成する1または複数の抵抗素子の少なくとも1つを介して前記第1の制御用スイッチング素子に定電流を供給可能な定電流供給部とを備える、スイッチング素子の駆動回路。

【請求項7】

前記第2のノードの電位が第2の閾値以下の場合に活性状態になる第2の信号を出力する第2の比較部とをさらに備え、

前記定電流供給部は、前記制御信号が前記第2の論理レベルでありかつ前記第2の信号が活性状態の場合に、前記第2の抵抗部を構成する1または複数の抵抗素子の少なくとも1つを介して前記第1の制御用スイッチング素子に定電流を供給可能である、請求項6に記載のスイッチング素子の駆動回路。

【請求項8】

前記定電流供給部は、前記制御信号が前記第2の論理レベルの場合に、前記第2の抵抗部を構成する1または複数の抵抗素子の少なくとも1つを介して前記第1の制御用スイッチング素子に定電流を供給可能である、請求項6に記載のスイッチング素子の駆動回路。

【請求項9】

前記定電流供給部は、

前記第3の電源ノードと前記第1のノードとの間に前記第1の抵抗部と並列に設けられた定電流源と、

前記定電流源と前記第1のノードとの間に前記定電流源と直列に設けられ、前記制御信号が前記第2の論理レベルでありかつ前記第2の信号が活性状態の場合に導通する第2の制御用スイッチング素子とを含む、請求項7に記載のスイッチング素子の駆動回路。

【請求項10】

前記定電流供給部は、

前記第3の電源ノードと前記第1のノードとの間に前記第1の抵抗部と並列に設けられた定電流源と、

前記定電流源と前記第1のノードとの間に前記定電流源と直列に設けられ、前記制御信号が前記第2の論理レベルの場合に導通する第2の制御用スイッチング素子とを含む、請求項8に記載のスイッチング素子の駆動回路。

【請求項11】

第1の電源ノードとそれより高電位に設定される第2の電源ノードとの間に直列に接続された2つのスイッチング素子のうち高電位側のスイッチング素子の駆動回路であって、

前記2つのスイッチング素子の接続ノードの電位よりも高電位に設定される第3の電源ノードと、

内部状態として第1および第2の状態を有し、前記内部状態に応じて前記高電位側のスイッチング素子をオン状態またはオフ状態に切替えるために、前記第1および第2の状態にそれぞれ対応して第1および第2の論理レベルに切替わる制御信号をそれぞれ出力する第1の論理回路と、

前記第3の電源ノードと第1のノードとの間に設けられた第1の抵抗部と、

前記第1のノードと前記第1の電源ノードとの間に設けられ、第1のパルス信号を受けたときに導通する第1の制御用スイッチング素子と、

前記第1のパルス信号に応じて前記第1の論理回路を前記第1の状態から前記第2の状態に切替えるために、前記第1のノードの電位が第1の閾値以下の場合に活性状態となる第1の信号を出力する第1の比較部と、

少なくとも前記制御信号の変化に基づいたタイミングで、前記第1の閾値の大きさを変化させる閾値変化部とを備える、スイッチング素子の駆動回路。

【請求項12】

前記第3の電源ノードと第2のノードとの間に設けられた第2の抵抗部と、

前記第2のノードと第3のノードとの間に設けられた第3の抵抗部と、

前記第3のノードと前記第1の電源ノードとの間に設けられ、前記第1のパルス信号とタイミングの異なる第2のパルス信号を受けたときに導通する第2の制御用スイッチング素子と、

前記第2のパルス信号に応じて前記第1の論理回路を前記第2の状態から前記第1の状態に切替えるために、前記第2のノードの電位が第2の閾値以下の場合に活性状態となる第2の信号を出力する第2の比較部と、

前記第3のノードの電位が第3の閾値以下の場合に活性状態になる第3の信号を出力する第3の比較部とをさらに備え、

前記閾値変化部は、前記制御信号が前記第1の論理レベルでありかつ前記第3の信号が活性状態の場合に、前記制御信号が前記第2の論理レベルの場合に比べて前記第1の閾値の大きさを減少させる、請求項11に記載のスイッチング素子の駆動回路。

【請求項13】

前記閾値変化部は、前記制御信号が前記第1の論理レベルの場合に、前記制御信号が前記第2の論理レベルの場合に比べて前記第1の閾値の大きさを減少させる、請求項11に記載のスイッチング素子の駆動回路。

【請求項14】

前記第1の比較部は、前記第3の電源ノードと前記接続ノードとの間に供給された電圧で動作するMOSインバータであり、

前記閾値変化部は、

前記第1の比較部の出力ノードと前記接続ノードとの間に設けられたMOSトランジスタと、

前記制御信号が前記第1の論理レベルでありかつ前記第3の信号が活性状態の場合に、前記MOSトランジスタをオン状態にする信号を前記MOSトランジスタのゲートに供給する第2の論理回路とを含む、請求項12に記載のスイッチング素子の駆動回路。

【請求項15】

前記第1の比較部は、前記第3の電源ノードと前記接続ノードとの間に供給された電圧で動作するMOSインバータであり、

前記閾値変化部は、前記第1の比較部の出力ノードと前記接続ノードとの間に設けられ、前記制御信号が前記第1の論理レベルの場合にオン状態になるMOSトランジスタを含む、請求項13に記載のスイッチング素子の駆動回路。

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【図14】

【図15】

【図16】

【図17】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【図14】

【図15】

【図16】

【図17】

【公開番号】特開2012−75267(P2012−75267A)

【公開日】平成24年4月12日(2012.4.12)

【国際特許分類】

【出願番号】特願2010−218943(P2010−218943)

【出願日】平成22年9月29日(2010.9.29)

【出願人】(000006013)三菱電機株式会社 (33,312)

【Fターム(参考)】

【公開日】平成24年4月12日(2012.4.12)

【国際特許分類】

【出願日】平成22年9月29日(2010.9.29)

【出願人】(000006013)三菱電機株式会社 (33,312)

【Fターム(参考)】

[ Back to top ]