スイッチング素子の駆動回路

【課題】固定が容易で且つ設置スペースを削減できるようにしたスイッチング素子の駆動回路を提供する。

【解決手段】多層配線板8の下面が主電流経路6上に搭載する搭載面とされているため、その多層配線板8の搭載面を平坦面にすることができる。したがって、主電流配線6は、その上面が平坦な設置面として形成されていれば、単に多層配線板8の搭載面を主電流配線6の上面に配置することで設置できる。これにより、コイルLを容易に固定でき設置スペースを削減できる。

【解決手段】多層配線板8の下面が主電流経路6上に搭載する搭載面とされているため、その多層配線板8の搭載面を平坦面にすることができる。したがって、主電流配線6は、その上面が平坦な設置面として形成されていれば、単に多層配線板8の搭載面を主電流配線6の上面に配置することで設置できる。これにより、コイルLを容易に固定でき設置スペースを削減できる。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、スイッチング素子の駆動回路に関する。

【背景技術】

【0002】

スイッチング素子の駆動回路は、スイッチング素子の制御端子に印加する電圧を制御することでスイッチング素子をオンオフする。この場合、スイッチング素子のオンオフ時間を決定する主要因は寄生容量に応じた充放電時間である。

【0003】

寄生容量の充電時間は、駆動回路からスイッチング素子の制御端子に流れ込む電流値の大小に応じて決定される。したがって、充電時間を短縮するためには、制御端子に流れ込む電流値を増加すると良い。この種の技術は例えば特許文献1に記載されている。この特許文献1には、スイッチング素子の制御端子の印加電圧を強制的に電源電圧に近づける構成が開示されている。

【0004】

すなわち、従来の駆動回路は、スイッチング素子の制御端子から寄生容量に流れる電流値を増すことでスイッチング動作の高速化を図っている。しかし、この場合には駆動回路の電流供給能力を増加しなければならない。この問題の解決を図るため、特許文献2では、スイッチング素子の主電流が流れる電流経路の周囲にインダクタを設け、このインダクタに発生する誘導起電圧をスイッチング素子の制御端子の印加電圧に重畳している。このように動作させることで、駆動回路の電流供給能力を増加させることなく、スイッチング素子を高速動作できることが提案されている。

【先行技術文献】

【特許文献】

【0005】

【特許文献1】特開2006−25071号公報

【特許文献2】特開2008−235997号公報

【発明の概要】

【発明が解決しようとする課題】

【0006】

特許文献2記載の技術を実用化するには、主電流経路に対しインダクタをどのように配置するかが課題となる。特許文献2記載の技術においては、リング状のフェライトコアとこのリング状コアに巻回されたコイルを用いているが、コアがリング状に成形されているため固定が困難となる。しかも、主電流経路の周囲にコアを設置しているため配置スペースを多く必要とする。

【0007】

コイルの固定が容易で且つ設置スペースを削減できるようにしたスイッチング素子の駆動回路を提供する。

【課題を解決するための手段】

【0008】

請求項1記載の発明によれば、スイッチング素子は信号源から与えられるパルス信号に応じてオンオフ制御され主電流が流れる。主電流配線は平坦面を備え、基板にはコイルが配設され平坦面を備えている。基板内のコイルにはスイッチング素子の主電流に応じて生じる磁束が鎖交するため、当該磁束に応じた誘導起電圧が発生する。コイルは信号源のパルス信号を入力すると、誘導起電圧を重畳してスイッチング素子の制御端子に与える。

【0009】

この場合、主電流配線と基板の平坦面間が密着面となっているため、設置スペースを削減できる。しかも、基板と主電流配線の間の密着面が互いに平坦面であるため容易に固定できる。また、例えばフェライトコアなどのコアを必要としないためコストも安くなる。請求項2記載の発明のように、基板内のコイルはゲート抵抗と直列接続されていると良い。

【0010】

請求項3記載の発明によれば、基板内のコイルの巻回端部間の長さが主電流配線の配線幅以下の長さになっており主電流配線の配線幅内に設置されているため、主電流配線に流れる電流に応じて発生する磁束をコイルに多く鎖交させることができ、逆に主電流配線以外の電流経路に通電する電流に応じて発生する磁束をコイルに出来る限り鎖交させないようにできる。したがって、コイルによる検出精度を高めることができると共に耐ノイズ性を向上できる。

【0011】

請求項4記載の発明のように、多層配線板の複数の各層に形成された配線パターンと各層の配線パターンをループ状に結合するビアを組合わせてコイルを形成すると良い。するとコイルを多層配線板内に組込むことができる。

【0012】

請求項5記載の発明によれば、基板内のコイルは、多層配線板内に互いに逆方向ループ状に巻回された部分コイルを複数直列接続して構成されているため、外乱ノイズに対する耐性を高めることができる。

【0013】

請求項6記載の発明によれば、第1部分コイルが第1層と第3層の配線パターンをビアによって構造的に接続して構成されると共に、第2部分コイルが第2層と第4層の配線パターンをビアにより構造的に接続して構成されているため、第1および第2部分コイル間の磁束鎖交領域をオーバーラップして設けることができ、外乱ノイズに対する耐性を高めることができる。

【0014】

請求項7記載の発明によれば、多層配線板はコイルと共に主電流配線を組み込んで構成されるため、コイルと主電流配線を多層配線板に共に実装できるようになり、コイルと主電流配線を別々に実装する手間がなくなる。

【0015】

請求項8記載の発明によれば、制御端子接続配線パターンと主電流配線は同一基板に形成されており、これらの配線間にスリットが設けられているため、これらの配線間の容量結合を抑制できる。

【0016】

請求項9記載の発明によれば、基板内のコイルに誘導起電圧が過大に生じたときに当該誘導起電圧をツェナーダイオードによって所定電圧でクランプできる。

【図面の簡単な説明】

【0017】

【図1】第1実施形態についてスイッチング素子の駆動回路の一例を示す回路図

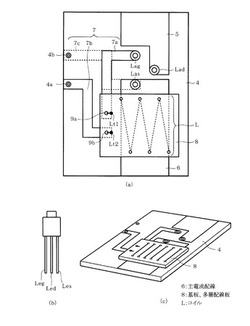

【図2】(a)は要部の構造を概略的に示す平面図、(b)はディスクリートタイプのスイッチング素子の構造例、(c)は要部の構造を概略的に示す斜視図

【図3】多層配線板内の各層の配線パターンを概略的に示す平面図

【図4】多層配線板の構造を概略的に示す縦断面図

【図5】主電流配線の周囲に発生する磁束の方向の説明図

【図6】多層配線板内のコイルに鎖交する磁束のイメージ図

【図7】コイルと主電流配線の配置関係を示す平面図

【図8】(a)はスイッチング素子のオン動作を概略的に説明するタイミングチャート、(b)はコイルの寄生成分を考慮した等価回路

【図9】第2実施形態を示す図3相当図

【図10】第3実施形態について図2(a)に示す基板の平面図

【図11】第4実施形態について示す図1相当図

【図12】第5実施形態について多層配線板の層構造を示す分解斜視図

【図13】第6実施形態について示す図2(c)の一部相当図(コイルと主電流配線の配置関係を示す斜視図)

【発明を実施するための形態】

【0018】

(第1実施形態)

以下、第1実施形態について図1〜図8を参照しながら説明する。

図1は、スイッチング素子の駆動回路例を示している。この図1に示すように、スイッチング素子M1は、例えばNチャネル型のMOSトランジスタを用いて構成され、誘導性負荷2と直列接続されている。誘導性負荷2には還流ダイオードDが並列接続されている。

【0019】

これらのスイッチング素子M1と誘導性負荷2との直列接続回路には、直流電圧E1が与えられている。直流電圧E1はこの直列接続回路の主電源電圧である。このスイッチング素子M1のゲート端子(制御端子)M1gには信号源Sおよび駆動回路1が構成されている。

【0020】

信号源Sは、直流電圧源E2の正負両側端子間に直列接続された制御スイッチSW1およびSW2を備えておりパルス信号を出力する。駆動回路1は、この信号源Sに加えてゲート抵抗RgおよびコイルLを組み合わせて構成され、スイッチング素子M1のゲートにパルス信号(例えばPWM信号)を印加することによりスイッチング素子M1をオンオフ駆動する。なお、駆動回路1には信号源Sを構成要件として含んでも含まなくても良い。

【0021】

コイルLは、後述する多層配線板8内に構成され、スイッチング素子M1のソース端子(出力端子)M1sに流れる主電流の電流経路3の周辺に設置され、電流経路3の通電電流の電磁誘導作用により当該通電電流の変化に応じた誘導起電圧を発生する。

【0022】

コイルLの一端子Lt1はスイッチング素子M1のゲート端子M1gに接続され、他端子Lt2はゲート抵抗Rgの信号出力側に接続されている。

図2(a)は、スイッチング素子とコイルの接続部分を含む要部を平面図で示している。また、図2(b)はディスクリートタイプのスイッチング素子構造を示している。また、図2(c)は、主電流通電基板に対する多層配線板の設置例を斜視図によって示している。

【0023】

主電流通電基板4は、例えばガラスエポキシ製の樹脂を基材として構成され、図2(a)に示すように、この基材上に銅箔などの金属によって配線パターン5〜7が形成されている。主電流通電基板4の表面にはドレイン電流通電用の主電流配線(配線パターン)5が形成され、ソース電流通電用の主電流配線(配線パターン)6が形成されている。また、主電流通電基板4の表面および裏面には、ゲート電圧印加用配線(配線パターン)7が、各主電流配線5、6の配線幅よりも幅の狭いパターンによって形成されている。

【0024】

このゲート電圧印加用配線7は、複数の配線7a〜7cを含む。配線7aは、その一端にゲート接続用のランドLagが構成され、他端にはコイルLとの接続端子が設けられている。配線7aは、その一部がソース電流通電用の主電流配線6の電流通電方向(図2(a)の上下方向)と同一方向に延伸し、当該主電流配線6と平行に形成されている。

【0025】

配線7aは、その他端が多層配線板8内に構成されるコイルLの接続端子9aと半田により接続されており、これにより配線7aはコイルLの一端子Lt1と電気的に接続されている。多層配線板8内の構造および配置位置については後述する。配線7bは、その一端がコイルLの接続端子9bと半田により接続されており、これによりコイルLの他端子Lt2と電気的に接続されている。配線7bの他端には、主電流通電基板4の辺部内側に配置されたゲート抵抗Rg接続用のランド4aが構成されている。

【0026】

配線7cは、主電流通電基板4の裏面に配置されるもので、その一端にはランドLasが構成されると共に、その他端には主電流通電基板4の辺部に位置してランド4bが構成されている。ランドLasは主電流配線6のパターン端部にも設けられ、ランドLasはスルーホールにより表面および裏面が貫通して接続されている。これにより、ソース電流通電用の主電流配線6と配線7cとが電気的に接続されている。主電流配線5は、そのパターン端部にドレイン接続用のランドLadが構成され、ドレイン接続用のランドLadにはスルーホールが設けられている。

【0027】

図2(b)は、スイッチング素子のパッケージ構造例を示している。スイッチング素子M1は、例えばTO(Transistor Outline)系パッケージ等の内部に電気的に構成され、複数本のリード端子Leg(ゲート)、Led(ドレイン)、Les(ソース)がパッケージの外方に延出して構成され、これらのリード端子Leg,Led,Lesが、図2(a)に示す主電流通電基板4の各ランドLag,Lad,Lasに構成されたスルーホールにそれぞれ挿通され半田付けされることによって固定される。

【0028】

図2(a)および図2(c)に示すように、主電流通電基板4の主電流配線6上には多層配線板8が搭載されている。この多層配線板8は、図1に示すコイルLが金属配線により内部に構成されている。

【0029】

図3(a)〜図3(d)は、多層配線板の各層の金属配線パターンおよびビアを模式的に示している。多層配線板8の第1層8a〜第4層8dは、それぞれガラスエポキシ樹脂を基材としてそれぞれ平板状をなして構成され、それぞれこの基材の上面に金属による配線パターンを形成して構成されている。

【0030】

第1層8aの下面が平坦面に成形されており、主電流配線6(主電流通電基板4)の上面に搭載する搭載面となる。これらの第1層8a〜第4層8d間は、多層配線板8の接続端子9aおよび9b側(図3の左側)からその反対側(図3の右側)にかけてジグザグに配置されたスルーホール(ビアに相当)H1〜H6を通じて連接されている。また、接続端子9aおよび9bが構成されており、接続端子9aおよび9bは第1層8a〜第4層8d間を貫通するスルーホールにより連接されている。

【0031】

図3(a)に示すように、第1層8aの表面においては、金属配線10が、スルーホールH1およびH2間、H3およびH4間、H5およびH6間を連結している。また、図3(c)に示す第3層8cの表面においては、金属配線10が、接続端子9aおよびスルーホールH6間を連結している。

【0032】

さらに、図3(d)に示すように、第4層8dの表面においては、金属配線10が、接続端子9bおよびスルーホールH1間、スルーホールH2およびH3間、並びに、スルーホールH4およびH5間を連結している。

【0033】

すると、電流の通電経路は、接続端子9a→スルーホールH6→第1層8aのH6およびH5間の金属配線10→スルーホールH5→第4層8dのH5およびH4間の金属配線10→スルーホールH4→…→スルーホールH1→第4層8dのH1および接続端子9b間の金属配線10、を通じて構成される。

【0034】

したがって、金属配線10およびスルーホールH1〜H6によってループ状に電流経路を形成することでコイルLを構成できる。コイルLの一端子Lt1は接続端子9aに接続され、他端子Lt2は接続端子9bに接続される。説明を容易化するため、コイルLの配線を3回巻回した例を示しているが、実用的には感度を向上するため3を超える巻数のコイルLを用いても良い。また、逆に設置スペースの削減のため、3未満の巻数のコイルLを用いても良い。

【0035】

図4は、主電流配線上に搭載された多層配線板の断面構造を理解し易いように模式的に示している。図4に示すように、主電流配線6上には多層配線板8が密着して搭載されている。多層配線板8の第1層(最下層)8aはガラスエポキシ樹脂を基材として構成されているが、これらの第1層8aと主電流配線6との間には、ソルダーレジスト等による回路パターン保護のため絶縁膜が設けられている。これにより、主電流配線6と多層配線板8との間の絶縁性が保たれている。また、絶縁性を強化するためポリイミドなどの薄い絶縁層を別途設けても良い。

【0036】

図4に示すように、コイルLは、各層8a〜8dの金属配線10およびスルーホールH1〜H6に囲われてループ状に結合して構成されている。図5に示すように、電流が主電流配線6に流れると、この主電流配線6の周囲に磁束φが発生し、多層配線板8内に構成されたコイルLの開口面Laに鎖交する。すると、コイルLは誘導起電圧を発生する。

【0037】

図6は、多層配線板内のコイルの開口面に鎖交する磁束のイメージを図4に対応して示している。磁束の鎖交方向は、図6の掲載面の垂直方向となるが、コイルLの開口面Laが大きければ磁束φの鎖交数も増加するため、電流変動に応じた誘導起電圧の感度を高めることができる。

【0038】

したがって、多層配線板8は4層構造のものを適用したが、これに限られるものではなく、磁束が通過するための面積を増加する場合、5層以上の多層配線板を用いても良い。逆に、主電流配線6の周囲のスペースを有効活用するためには多層配線板8を薄くすると良く、この観点では多層配線板8を2層の両面基板、または、3層多層基板で構成し、この内部にコイルLを配設すると良い。すなわち、多層配線板8の層数は適宜選定すると良い。

【0039】

図7は、コイルと主電流配線の配置関係を平面図により概略的に示している。前述したように、コイルLは多層配線板8内に3回(複数)以上巻回されていると良いが、このコイルLの巻回端部間の長さlは主電流配線6の配線幅Wと一致またはそれ未満の長さであり、また、平面的に配線幅W内に収めて設置されていると良い。

【0040】

図2等には省略しているが、主電流通電基板4には他の回路(図示せず)が搭載される。この他の回路に流れる電流に応じた磁束φがコイルLに鎖交しにくくなる。これにより、他の配線の通電電流の影響を極力抑制できる。また、コイルLのコイル幅wと主電流配線6の配線幅Wとの関係はどちらが長くても良いしほぼ同一長としても良い。

【0041】

上記構成の動作について説明する。図8(a)は、スイッチング素子をオフからオンにするときの要部の電圧、電流波形をタイミングチャートにより示しており、図8(b)は、その等価回路を示している。

【0042】

図8(b)の等価回路に示すように、コイルLには寄生容量Cp1、寄生容量Cp2、寄生インダクタLpが図示形態で存在する。制御スイッチSW1をオンすると共に制御スイッチSW2をオフすることで、図8(a)に示すように、駆動回路1が電圧源E2からステップ状のゲート電圧Vdrをスイッチング素子M1の制御端子(MOSFETのゲート)に印加すると、スイッチング素子M1のゲート入力容量には電荷が充電され、スイッチング素子M1のゲートソース間電圧が徐々に増加する(図8(a)のA区間)。この間、スイッチング素子M1の出力電流(ソース電流Is(≒ドレイン電流Id))はほとんど流れない。

【0043】

その後、スイッチング素子M1のゲートソース間電圧Vgsが閾値電圧Vthを上回ると、ソース電流Is(≒ドレイン電流Id)が増加し始める。このため、当該ソース電流Isの変化量dIs/dtに依存した誘導起電圧Kp×dIs/dtが正方向に重畳される(図8(a)のB区間)。すると、ソース電流Is,ドレイン電流Idの上昇度を増すことができる。これにより、スイッチング素子M1を高速スイッチングできる。

【0044】

<本実施形態のまとめ>

本実施形態では、多層配線板8の下面が主電流経路6上に搭載する搭載面とされているため、その多層配線板8の搭載面を平坦面にすることができる。したがって、主電流配線6(主電流通電基板4)は、その上面が平坦な設置面として形成されていれば、単に多層配線板8の搭載面を主電流配線6の上面に配置することで密着して設置できる。これにより、主電流配線6の周囲に設置スペースを多く必要としない。多層配線板8を主電流配線6(主電流通電基板4)上に配置できるため、コイルLに多くの磁束を鎖交させることができる。

【0045】

コイルLは、その巻回端部間の長さlが主電流配線6の配線幅W以下の長さであり、主電流配線6の配線幅W内に設置されているため、主電流配線6に流れる電流に応じて発生する磁束を多くコイルLに鎖交させることができ、逆に主電流配線6以外の電流経路に通電する電流に応じて発生する磁束を出来る限り鎖交させないようにできる。したがって、コイルLによる検出精度を高めることができ耐ノイズ性を向上できる。

【0046】

コイルLが、多層配線板8の複数の各層8a〜8dに形成された金属配線(配線パターン)10と、この金属配線10をループ状に結合するスルーホールH1〜H6を組み合わせて構成されるため、コイルLを多層配線板8内にコンパクトに組込むことができる。これによりコイルLを安価に構成できる。また、鉄心コア、フェライトコアなどが不要となり低コスト化を実現できる。

【0047】

製法上においても巻き加工を不要にできるため低コスト化を実現できる。なお、主電流配線6の上面はソルダーレジストなどの絶縁材によりコーティングされているため、コイルLと主電流配線6等との間の絶縁性を保持できる。

【0048】

(第2実施形態)

図9は、第2実施形態を示すもので、前述実施形態と異なるところは、多層配線板内に互いに逆方向ループ状に巻回された部分コイルを複数直列接続して構成しているところにある。前述実施形態と同一または類似の機能を有する部分には同一符号を付して説明を省略し、以下、異なる部分について説明する。

【0049】

図9(a)〜図9(d)は、多層配線板内の各層の配線パターンおよび接続状態を示すもので、前述実施形態の図3に代えて示している。

図9(a)〜図9(d)に示すように、接続端子11aおよび11bが、接続端子9aおよび9bにそれぞれ隣接して構成されており、これらの接続端子11aおよび11bは第1層8a〜第4層8dを貫通するスルーホールによって連接されている。

【0050】

図9(a)〜図9(d)に示すように、スルーホールH1〜H6は、前述実施形態と同様にジグザグに配置されており、第1層8aおよび第3層8cにおいて金属配線10が各スルーホールH1〜H6を順に連結しているが、本実施形態ではこれに加えてスルーホールH1〜H6に対してスルーホールH7をさらにジグザグに配置し、金属配線10が当該スルーホールH7と接続端子9aとを連結している。また、金属配線10がスルーホールH1と接続端子11bとを連結している。

【0051】

すると、電流の通電経路は、接続端子9a→スルーホールH7→第3層8cのH7およびH6間の金属配線10→スルーホールH6→第1層8aのH6およびH5間の金属配線10→スルーホールH5→第3層8cのH5およびH4間の金属配線10→スルーホールH4→…→スルーホールH1→第3層8cのH1および接続端子11b間の金属配線10、を通じて構成される。

【0052】

したがって、図9(a)に示す第1層8aと図9(c)に示す第3層8cとの間で所定の一方向(図9中の左側から見た場合、時計回り方向:右巻き)に巻回された部分コイルL1を構成できる。

【0053】

図9(a)〜図9(d)に示すように、多層配線板8の各層8a〜8dは、多層配線板8の接続端子9aおよび9b側(図9の左側)からその反対側(図9の右側)にかけて平面的にジグザグに配置されたスルーホールH8〜H15を通じてそれぞれ連接されている。

【0054】

第2層8bでは、金属配線10が、スルーホールH8およびH9間、H10およびH11間、H12およびH13間、H14およびH15間を連結しており、第4層8dでは、金属配線10がスルーホールH9およびH10間、H11およびH12間、H13およびH14間、スルーホールH15および接続端子11a間を連結している。

【0055】

すると、電流の通電経路は、接続端子11a→第4層8dの接続端子11aおよびスルーホールH15間の金属配線10→スルーホールH15→第2層8bのH15およびH14間の金属配線10→スルーホールH14→第4層8dのH14およびH13間の金属配線10→スルーホールH13→…→スルーホールH8→スルーホールH8および接続端子9b間の金属配線10、を通じて形成される。

【0056】

したがって、図9(b)に示す第2層8bと図9(d)に示す第4層8dとの間で、前記の一方向とは逆方向(図9中の左側から見た場合、反時計回り方向:左巻き)に巻回された部分コイルL2を構成できる。

【0057】

実装時には、接続端子11aおよび11b間を連結して短絡することで部分コイルL1およびL2を直列接続した状態でコイルを構成できる。

本実施形態においては、部分コイルL1と部分コイルL2とが直列接続して構成されている。また、部分コイルL1と部分コイルL2とが互いに逆方向に巻回して構成されているため、外乱ノイズに対する耐性を高めることができる。また、部分コイルL1が第1層8a−第3層8c間、部分コイルL2が第2層8b−第4層8d間にそれぞれ構成されているため、部分コイルL1−L2間の磁束鎖交領域をオーバーラップして設けることができ、外乱ノイズに対する耐性を高めることができる。

【0058】

部分コイルL1を第1層8a−第3層8c間、部分コイルL2を第2層8b−第4層8d間、に構成した実施形態を示したが、部分コイルL1を第1層8a−第2層8b間、部分コイルL2を第3層8c−第4層8d間に構成しても良い。

【0059】

(第3実施形態)

図10は、第3実施形態を示すもので、前述実施形態と異なるところは、配線7(制御端子接続配線パターン)と主電流配線6との間にスリットが設けられているところにある。前述実施形態と同一又は類似部分については同一又は類似の符号を付して説明を省略し、以下、異なる部分について説明を行う。

【0060】

図10は、主電流通電基板の一例を示している。この図10には、図2(a)に示した多層配線板8の構成を除いて示している。

図10に示すように、スリット12が、主電流配線6の電流経路の脇に位置して当該主電流配線6に沿って形成されている。このスリット12は、ソース電流Isが流れる主電流配線6と、配線7aおよび7bとの間に形成されている。このスリット12は、ソースリード端子Lesの接続用のランドLasと配線7aとの間にも形成される。これにより、ゲート電圧印加用配線7と主電流配線6との間の容量結合を抑制できる。

【0061】

特に、ゲート電圧印加用配線7の配線7a〜7cの一部または全部が主電流配線6と並走している場合、容量結合によってゲート印加電圧Vginにノイズが重畳する虞がある。このため、本実施形態では、スリット12を設けて絶縁することでノイズの影響を極力抑制できる。

【0062】

(第4実施形態)

図11は、第4実施形態を示すもので、前述実施形態と異なるところは、コイルに生じる誘導起電圧をクランプするためのツェナーダイオードを設けたところにある。図11に示すように、コイルLの一端子Lt1および他端子Lt2間には、ツェナーダイオードD1およびD2が互いに逆方向に接続されている。すると、コイルLに誘導起電圧が過大に生じたときに当該過電圧を所定電圧でクランプできる。

【0063】

(第5実施形態)

図12は、第5実施形態を示すもので、前述実施形態と異なるところは、コイルと共に主電流配線が多層配線板に組み込まれた状態で構成されているところにある。

【0064】

図12は、多層配線板の層構造を分解斜視図によって示している。この多層配線板13は5層構造となっており、図12中の下から第1層13a、第2層13b、第3層13c、第4層13dおよび第5層13eの5層構造となっている。ここで、第2層13b〜第5層13eの各層には、図9(a)〜図9(d)に示す第1層8a〜第4層8dの各層とそれぞれ同様の配線パターン(金属配線10、スルーホールH1〜H15)が形成されている。第1層13aには、主電流通電基板4に形成された配線パターン(主電流配線5,6、ゲート電流印加用配線7)と同様のパターンが形成されている。

【0065】

したがって、第1層13a〜第5層13eが多層配線板13に一体化されていると、コイルL(部分コイルL1、L2)と主電流配線6を多層配線板13に共に実装できるようになり、コイルLと主電流配線6を別々に実装する手間がなくなる。

【0066】

(第6実施形態)

図13は、第6実施形態を示すもので、前述実施形態と異なるところは、コイルを主電流配線に埋め込んだところにある。

【0067】

前述の実施形態では、主電流配線5、6を主電流通電基板4上の銅箔により形成した実施形態を示したが、これに限られるものではない。すなわち、図13に示すように、前述実施形態の主電流配線5,6に代えて所定厚さの導電板14を構成し、その一部に凹部14aを成形し、この凹部14aの上に多層配線板8を搭載しても良い。

【0068】

導電板14の凹部14aの下面が多層配線板8の搭載面となる。この導電板14の凹部14aはその凹面が平坦面に構成されており、多層配線板8が凹部14aの下面上に搭載される。コイルLの誘導起電圧は配線15を接続することで取得できる。このような形態であっても、導電板14の通電電流に応じて発生する磁束を多層配線板8内のコイルLに鎖交させることができる。

【0069】

(他の実施形態)

本発明は、前記の実施形態に限定されるものではなく、例えば、以下に示す変形又は拡張が可能である。

コイルLの巻数、コイル幅wは適宜変更しても良い。

ソース電流Is用の主電流配線6の上に多層配線板8を密着して搭載することで、ソース電流Isに応じた誘導起電圧をゲート印加電圧Vginに重畳させる実施形態を示したが、これに限られるものではなく、例えば、ドレイン電流Id用の主電流配線5の上に多層配線板8を密着して搭載し、ドレイン電流Idに応じた誘導起電圧をゲート印加電圧Vginに重畳させるようにしても良い。

【0070】

多層配線板8の複数層構造を全て貫通するスルーホールH1〜H6と金属配線10を用いてコイルLを構成した実施形態を示したが、多層配線層8の層間(例えば第1層8aおよび第2層8b間、第2層8bおよび第3層8c間、第3層8cおよび第4層8d間)のうち何れかを結合するビアを用いてコイルLを構成しても良い。

【0071】

誘導性負荷2を駆動するための駆動回路1に適用したが、特にこれに限られるものではなく、DCDCコンバータなどスイッチング素子M1を具備した回路を駆動する駆動回路に適用できる。

【符号の説明】

【0072】

図面中、1は駆動回路、2は誘導性負荷、3は電流経路、4は主電流通電基板、6は主電流配線、7はゲート電圧印加用配線(制御端子接続配線パターン)、8は多層配線板(基板)、8aは第1層、8bは第2層、8cは第3層、8dは第4層、9a、9bは接続端子、10は金属配線(配線パターン)、11a、11bは接続端子、12はスリット、13は多層配線板、13aは第1層、13bは第2層、13cは第3層、13dは第4層、13eは第5層、14は導電板(主電流配線)、15は配線、Lはコイル、L1は部分コイル(第1部分コイル)、L2は部分コイル(第2部分コイル)、M1はスイッチング素子、Sは信号源、Rgはゲート抵抗を示す。

【技術分野】

【0001】

本発明は、スイッチング素子の駆動回路に関する。

【背景技術】

【0002】

スイッチング素子の駆動回路は、スイッチング素子の制御端子に印加する電圧を制御することでスイッチング素子をオンオフする。この場合、スイッチング素子のオンオフ時間を決定する主要因は寄生容量に応じた充放電時間である。

【0003】

寄生容量の充電時間は、駆動回路からスイッチング素子の制御端子に流れ込む電流値の大小に応じて決定される。したがって、充電時間を短縮するためには、制御端子に流れ込む電流値を増加すると良い。この種の技術は例えば特許文献1に記載されている。この特許文献1には、スイッチング素子の制御端子の印加電圧を強制的に電源電圧に近づける構成が開示されている。

【0004】

すなわち、従来の駆動回路は、スイッチング素子の制御端子から寄生容量に流れる電流値を増すことでスイッチング動作の高速化を図っている。しかし、この場合には駆動回路の電流供給能力を増加しなければならない。この問題の解決を図るため、特許文献2では、スイッチング素子の主電流が流れる電流経路の周囲にインダクタを設け、このインダクタに発生する誘導起電圧をスイッチング素子の制御端子の印加電圧に重畳している。このように動作させることで、駆動回路の電流供給能力を増加させることなく、スイッチング素子を高速動作できることが提案されている。

【先行技術文献】

【特許文献】

【0005】

【特許文献1】特開2006−25071号公報

【特許文献2】特開2008−235997号公報

【発明の概要】

【発明が解決しようとする課題】

【0006】

特許文献2記載の技術を実用化するには、主電流経路に対しインダクタをどのように配置するかが課題となる。特許文献2記載の技術においては、リング状のフェライトコアとこのリング状コアに巻回されたコイルを用いているが、コアがリング状に成形されているため固定が困難となる。しかも、主電流経路の周囲にコアを設置しているため配置スペースを多く必要とする。

【0007】

コイルの固定が容易で且つ設置スペースを削減できるようにしたスイッチング素子の駆動回路を提供する。

【課題を解決するための手段】

【0008】

請求項1記載の発明によれば、スイッチング素子は信号源から与えられるパルス信号に応じてオンオフ制御され主電流が流れる。主電流配線は平坦面を備え、基板にはコイルが配設され平坦面を備えている。基板内のコイルにはスイッチング素子の主電流に応じて生じる磁束が鎖交するため、当該磁束に応じた誘導起電圧が発生する。コイルは信号源のパルス信号を入力すると、誘導起電圧を重畳してスイッチング素子の制御端子に与える。

【0009】

この場合、主電流配線と基板の平坦面間が密着面となっているため、設置スペースを削減できる。しかも、基板と主電流配線の間の密着面が互いに平坦面であるため容易に固定できる。また、例えばフェライトコアなどのコアを必要としないためコストも安くなる。請求項2記載の発明のように、基板内のコイルはゲート抵抗と直列接続されていると良い。

【0010】

請求項3記載の発明によれば、基板内のコイルの巻回端部間の長さが主電流配線の配線幅以下の長さになっており主電流配線の配線幅内に設置されているため、主電流配線に流れる電流に応じて発生する磁束をコイルに多く鎖交させることができ、逆に主電流配線以外の電流経路に通電する電流に応じて発生する磁束をコイルに出来る限り鎖交させないようにできる。したがって、コイルによる検出精度を高めることができると共に耐ノイズ性を向上できる。

【0011】

請求項4記載の発明のように、多層配線板の複数の各層に形成された配線パターンと各層の配線パターンをループ状に結合するビアを組合わせてコイルを形成すると良い。するとコイルを多層配線板内に組込むことができる。

【0012】

請求項5記載の発明によれば、基板内のコイルは、多層配線板内に互いに逆方向ループ状に巻回された部分コイルを複数直列接続して構成されているため、外乱ノイズに対する耐性を高めることができる。

【0013】

請求項6記載の発明によれば、第1部分コイルが第1層と第3層の配線パターンをビアによって構造的に接続して構成されると共に、第2部分コイルが第2層と第4層の配線パターンをビアにより構造的に接続して構成されているため、第1および第2部分コイル間の磁束鎖交領域をオーバーラップして設けることができ、外乱ノイズに対する耐性を高めることができる。

【0014】

請求項7記載の発明によれば、多層配線板はコイルと共に主電流配線を組み込んで構成されるため、コイルと主電流配線を多層配線板に共に実装できるようになり、コイルと主電流配線を別々に実装する手間がなくなる。

【0015】

請求項8記載の発明によれば、制御端子接続配線パターンと主電流配線は同一基板に形成されており、これらの配線間にスリットが設けられているため、これらの配線間の容量結合を抑制できる。

【0016】

請求項9記載の発明によれば、基板内のコイルに誘導起電圧が過大に生じたときに当該誘導起電圧をツェナーダイオードによって所定電圧でクランプできる。

【図面の簡単な説明】

【0017】

【図1】第1実施形態についてスイッチング素子の駆動回路の一例を示す回路図

【図2】(a)は要部の構造を概略的に示す平面図、(b)はディスクリートタイプのスイッチング素子の構造例、(c)は要部の構造を概略的に示す斜視図

【図3】多層配線板内の各層の配線パターンを概略的に示す平面図

【図4】多層配線板の構造を概略的に示す縦断面図

【図5】主電流配線の周囲に発生する磁束の方向の説明図

【図6】多層配線板内のコイルに鎖交する磁束のイメージ図

【図7】コイルと主電流配線の配置関係を示す平面図

【図8】(a)はスイッチング素子のオン動作を概略的に説明するタイミングチャート、(b)はコイルの寄生成分を考慮した等価回路

【図9】第2実施形態を示す図3相当図

【図10】第3実施形態について図2(a)に示す基板の平面図

【図11】第4実施形態について示す図1相当図

【図12】第5実施形態について多層配線板の層構造を示す分解斜視図

【図13】第6実施形態について示す図2(c)の一部相当図(コイルと主電流配線の配置関係を示す斜視図)

【発明を実施するための形態】

【0018】

(第1実施形態)

以下、第1実施形態について図1〜図8を参照しながら説明する。

図1は、スイッチング素子の駆動回路例を示している。この図1に示すように、スイッチング素子M1は、例えばNチャネル型のMOSトランジスタを用いて構成され、誘導性負荷2と直列接続されている。誘導性負荷2には還流ダイオードDが並列接続されている。

【0019】

これらのスイッチング素子M1と誘導性負荷2との直列接続回路には、直流電圧E1が与えられている。直流電圧E1はこの直列接続回路の主電源電圧である。このスイッチング素子M1のゲート端子(制御端子)M1gには信号源Sおよび駆動回路1が構成されている。

【0020】

信号源Sは、直流電圧源E2の正負両側端子間に直列接続された制御スイッチSW1およびSW2を備えておりパルス信号を出力する。駆動回路1は、この信号源Sに加えてゲート抵抗RgおよびコイルLを組み合わせて構成され、スイッチング素子M1のゲートにパルス信号(例えばPWM信号)を印加することによりスイッチング素子M1をオンオフ駆動する。なお、駆動回路1には信号源Sを構成要件として含んでも含まなくても良い。

【0021】

コイルLは、後述する多層配線板8内に構成され、スイッチング素子M1のソース端子(出力端子)M1sに流れる主電流の電流経路3の周辺に設置され、電流経路3の通電電流の電磁誘導作用により当該通電電流の変化に応じた誘導起電圧を発生する。

【0022】

コイルLの一端子Lt1はスイッチング素子M1のゲート端子M1gに接続され、他端子Lt2はゲート抵抗Rgの信号出力側に接続されている。

図2(a)は、スイッチング素子とコイルの接続部分を含む要部を平面図で示している。また、図2(b)はディスクリートタイプのスイッチング素子構造を示している。また、図2(c)は、主電流通電基板に対する多層配線板の設置例を斜視図によって示している。

【0023】

主電流通電基板4は、例えばガラスエポキシ製の樹脂を基材として構成され、図2(a)に示すように、この基材上に銅箔などの金属によって配線パターン5〜7が形成されている。主電流通電基板4の表面にはドレイン電流通電用の主電流配線(配線パターン)5が形成され、ソース電流通電用の主電流配線(配線パターン)6が形成されている。また、主電流通電基板4の表面および裏面には、ゲート電圧印加用配線(配線パターン)7が、各主電流配線5、6の配線幅よりも幅の狭いパターンによって形成されている。

【0024】

このゲート電圧印加用配線7は、複数の配線7a〜7cを含む。配線7aは、その一端にゲート接続用のランドLagが構成され、他端にはコイルLとの接続端子が設けられている。配線7aは、その一部がソース電流通電用の主電流配線6の電流通電方向(図2(a)の上下方向)と同一方向に延伸し、当該主電流配線6と平行に形成されている。

【0025】

配線7aは、その他端が多層配線板8内に構成されるコイルLの接続端子9aと半田により接続されており、これにより配線7aはコイルLの一端子Lt1と電気的に接続されている。多層配線板8内の構造および配置位置については後述する。配線7bは、その一端がコイルLの接続端子9bと半田により接続されており、これによりコイルLの他端子Lt2と電気的に接続されている。配線7bの他端には、主電流通電基板4の辺部内側に配置されたゲート抵抗Rg接続用のランド4aが構成されている。

【0026】

配線7cは、主電流通電基板4の裏面に配置されるもので、その一端にはランドLasが構成されると共に、その他端には主電流通電基板4の辺部に位置してランド4bが構成されている。ランドLasは主電流配線6のパターン端部にも設けられ、ランドLasはスルーホールにより表面および裏面が貫通して接続されている。これにより、ソース電流通電用の主電流配線6と配線7cとが電気的に接続されている。主電流配線5は、そのパターン端部にドレイン接続用のランドLadが構成され、ドレイン接続用のランドLadにはスルーホールが設けられている。

【0027】

図2(b)は、スイッチング素子のパッケージ構造例を示している。スイッチング素子M1は、例えばTO(Transistor Outline)系パッケージ等の内部に電気的に構成され、複数本のリード端子Leg(ゲート)、Led(ドレイン)、Les(ソース)がパッケージの外方に延出して構成され、これらのリード端子Leg,Led,Lesが、図2(a)に示す主電流通電基板4の各ランドLag,Lad,Lasに構成されたスルーホールにそれぞれ挿通され半田付けされることによって固定される。

【0028】

図2(a)および図2(c)に示すように、主電流通電基板4の主電流配線6上には多層配線板8が搭載されている。この多層配線板8は、図1に示すコイルLが金属配線により内部に構成されている。

【0029】

図3(a)〜図3(d)は、多層配線板の各層の金属配線パターンおよびビアを模式的に示している。多層配線板8の第1層8a〜第4層8dは、それぞれガラスエポキシ樹脂を基材としてそれぞれ平板状をなして構成され、それぞれこの基材の上面に金属による配線パターンを形成して構成されている。

【0030】

第1層8aの下面が平坦面に成形されており、主電流配線6(主電流通電基板4)の上面に搭載する搭載面となる。これらの第1層8a〜第4層8d間は、多層配線板8の接続端子9aおよび9b側(図3の左側)からその反対側(図3の右側)にかけてジグザグに配置されたスルーホール(ビアに相当)H1〜H6を通じて連接されている。また、接続端子9aおよび9bが構成されており、接続端子9aおよび9bは第1層8a〜第4層8d間を貫通するスルーホールにより連接されている。

【0031】

図3(a)に示すように、第1層8aの表面においては、金属配線10が、スルーホールH1およびH2間、H3およびH4間、H5およびH6間を連結している。また、図3(c)に示す第3層8cの表面においては、金属配線10が、接続端子9aおよびスルーホールH6間を連結している。

【0032】

さらに、図3(d)に示すように、第4層8dの表面においては、金属配線10が、接続端子9bおよびスルーホールH1間、スルーホールH2およびH3間、並びに、スルーホールH4およびH5間を連結している。

【0033】

すると、電流の通電経路は、接続端子9a→スルーホールH6→第1層8aのH6およびH5間の金属配線10→スルーホールH5→第4層8dのH5およびH4間の金属配線10→スルーホールH4→…→スルーホールH1→第4層8dのH1および接続端子9b間の金属配線10、を通じて構成される。

【0034】

したがって、金属配線10およびスルーホールH1〜H6によってループ状に電流経路を形成することでコイルLを構成できる。コイルLの一端子Lt1は接続端子9aに接続され、他端子Lt2は接続端子9bに接続される。説明を容易化するため、コイルLの配線を3回巻回した例を示しているが、実用的には感度を向上するため3を超える巻数のコイルLを用いても良い。また、逆に設置スペースの削減のため、3未満の巻数のコイルLを用いても良い。

【0035】

図4は、主電流配線上に搭載された多層配線板の断面構造を理解し易いように模式的に示している。図4に示すように、主電流配線6上には多層配線板8が密着して搭載されている。多層配線板8の第1層(最下層)8aはガラスエポキシ樹脂を基材として構成されているが、これらの第1層8aと主電流配線6との間には、ソルダーレジスト等による回路パターン保護のため絶縁膜が設けられている。これにより、主電流配線6と多層配線板8との間の絶縁性が保たれている。また、絶縁性を強化するためポリイミドなどの薄い絶縁層を別途設けても良い。

【0036】

図4に示すように、コイルLは、各層8a〜8dの金属配線10およびスルーホールH1〜H6に囲われてループ状に結合して構成されている。図5に示すように、電流が主電流配線6に流れると、この主電流配線6の周囲に磁束φが発生し、多層配線板8内に構成されたコイルLの開口面Laに鎖交する。すると、コイルLは誘導起電圧を発生する。

【0037】

図6は、多層配線板内のコイルの開口面に鎖交する磁束のイメージを図4に対応して示している。磁束の鎖交方向は、図6の掲載面の垂直方向となるが、コイルLの開口面Laが大きければ磁束φの鎖交数も増加するため、電流変動に応じた誘導起電圧の感度を高めることができる。

【0038】

したがって、多層配線板8は4層構造のものを適用したが、これに限られるものではなく、磁束が通過するための面積を増加する場合、5層以上の多層配線板を用いても良い。逆に、主電流配線6の周囲のスペースを有効活用するためには多層配線板8を薄くすると良く、この観点では多層配線板8を2層の両面基板、または、3層多層基板で構成し、この内部にコイルLを配設すると良い。すなわち、多層配線板8の層数は適宜選定すると良い。

【0039】

図7は、コイルと主電流配線の配置関係を平面図により概略的に示している。前述したように、コイルLは多層配線板8内に3回(複数)以上巻回されていると良いが、このコイルLの巻回端部間の長さlは主電流配線6の配線幅Wと一致またはそれ未満の長さであり、また、平面的に配線幅W内に収めて設置されていると良い。

【0040】

図2等には省略しているが、主電流通電基板4には他の回路(図示せず)が搭載される。この他の回路に流れる電流に応じた磁束φがコイルLに鎖交しにくくなる。これにより、他の配線の通電電流の影響を極力抑制できる。また、コイルLのコイル幅wと主電流配線6の配線幅Wとの関係はどちらが長くても良いしほぼ同一長としても良い。

【0041】

上記構成の動作について説明する。図8(a)は、スイッチング素子をオフからオンにするときの要部の電圧、電流波形をタイミングチャートにより示しており、図8(b)は、その等価回路を示している。

【0042】

図8(b)の等価回路に示すように、コイルLには寄生容量Cp1、寄生容量Cp2、寄生インダクタLpが図示形態で存在する。制御スイッチSW1をオンすると共に制御スイッチSW2をオフすることで、図8(a)に示すように、駆動回路1が電圧源E2からステップ状のゲート電圧Vdrをスイッチング素子M1の制御端子(MOSFETのゲート)に印加すると、スイッチング素子M1のゲート入力容量には電荷が充電され、スイッチング素子M1のゲートソース間電圧が徐々に増加する(図8(a)のA区間)。この間、スイッチング素子M1の出力電流(ソース電流Is(≒ドレイン電流Id))はほとんど流れない。

【0043】

その後、スイッチング素子M1のゲートソース間電圧Vgsが閾値電圧Vthを上回ると、ソース電流Is(≒ドレイン電流Id)が増加し始める。このため、当該ソース電流Isの変化量dIs/dtに依存した誘導起電圧Kp×dIs/dtが正方向に重畳される(図8(a)のB区間)。すると、ソース電流Is,ドレイン電流Idの上昇度を増すことができる。これにより、スイッチング素子M1を高速スイッチングできる。

【0044】

<本実施形態のまとめ>

本実施形態では、多層配線板8の下面が主電流経路6上に搭載する搭載面とされているため、その多層配線板8の搭載面を平坦面にすることができる。したがって、主電流配線6(主電流通電基板4)は、その上面が平坦な設置面として形成されていれば、単に多層配線板8の搭載面を主電流配線6の上面に配置することで密着して設置できる。これにより、主電流配線6の周囲に設置スペースを多く必要としない。多層配線板8を主電流配線6(主電流通電基板4)上に配置できるため、コイルLに多くの磁束を鎖交させることができる。

【0045】

コイルLは、その巻回端部間の長さlが主電流配線6の配線幅W以下の長さであり、主電流配線6の配線幅W内に設置されているため、主電流配線6に流れる電流に応じて発生する磁束を多くコイルLに鎖交させることができ、逆に主電流配線6以外の電流経路に通電する電流に応じて発生する磁束を出来る限り鎖交させないようにできる。したがって、コイルLによる検出精度を高めることができ耐ノイズ性を向上できる。

【0046】

コイルLが、多層配線板8の複数の各層8a〜8dに形成された金属配線(配線パターン)10と、この金属配線10をループ状に結合するスルーホールH1〜H6を組み合わせて構成されるため、コイルLを多層配線板8内にコンパクトに組込むことができる。これによりコイルLを安価に構成できる。また、鉄心コア、フェライトコアなどが不要となり低コスト化を実現できる。

【0047】

製法上においても巻き加工を不要にできるため低コスト化を実現できる。なお、主電流配線6の上面はソルダーレジストなどの絶縁材によりコーティングされているため、コイルLと主電流配線6等との間の絶縁性を保持できる。

【0048】

(第2実施形態)

図9は、第2実施形態を示すもので、前述実施形態と異なるところは、多層配線板内に互いに逆方向ループ状に巻回された部分コイルを複数直列接続して構成しているところにある。前述実施形態と同一または類似の機能を有する部分には同一符号を付して説明を省略し、以下、異なる部分について説明する。

【0049】

図9(a)〜図9(d)は、多層配線板内の各層の配線パターンおよび接続状態を示すもので、前述実施形態の図3に代えて示している。

図9(a)〜図9(d)に示すように、接続端子11aおよび11bが、接続端子9aおよび9bにそれぞれ隣接して構成されており、これらの接続端子11aおよび11bは第1層8a〜第4層8dを貫通するスルーホールによって連接されている。

【0050】

図9(a)〜図9(d)に示すように、スルーホールH1〜H6は、前述実施形態と同様にジグザグに配置されており、第1層8aおよび第3層8cにおいて金属配線10が各スルーホールH1〜H6を順に連結しているが、本実施形態ではこれに加えてスルーホールH1〜H6に対してスルーホールH7をさらにジグザグに配置し、金属配線10が当該スルーホールH7と接続端子9aとを連結している。また、金属配線10がスルーホールH1と接続端子11bとを連結している。

【0051】

すると、電流の通電経路は、接続端子9a→スルーホールH7→第3層8cのH7およびH6間の金属配線10→スルーホールH6→第1層8aのH6およびH5間の金属配線10→スルーホールH5→第3層8cのH5およびH4間の金属配線10→スルーホールH4→…→スルーホールH1→第3層8cのH1および接続端子11b間の金属配線10、を通じて構成される。

【0052】

したがって、図9(a)に示す第1層8aと図9(c)に示す第3層8cとの間で所定の一方向(図9中の左側から見た場合、時計回り方向:右巻き)に巻回された部分コイルL1を構成できる。

【0053】

図9(a)〜図9(d)に示すように、多層配線板8の各層8a〜8dは、多層配線板8の接続端子9aおよび9b側(図9の左側)からその反対側(図9の右側)にかけて平面的にジグザグに配置されたスルーホールH8〜H15を通じてそれぞれ連接されている。

【0054】

第2層8bでは、金属配線10が、スルーホールH8およびH9間、H10およびH11間、H12およびH13間、H14およびH15間を連結しており、第4層8dでは、金属配線10がスルーホールH9およびH10間、H11およびH12間、H13およびH14間、スルーホールH15および接続端子11a間を連結している。

【0055】

すると、電流の通電経路は、接続端子11a→第4層8dの接続端子11aおよびスルーホールH15間の金属配線10→スルーホールH15→第2層8bのH15およびH14間の金属配線10→スルーホールH14→第4層8dのH14およびH13間の金属配線10→スルーホールH13→…→スルーホールH8→スルーホールH8および接続端子9b間の金属配線10、を通じて形成される。

【0056】

したがって、図9(b)に示す第2層8bと図9(d)に示す第4層8dとの間で、前記の一方向とは逆方向(図9中の左側から見た場合、反時計回り方向:左巻き)に巻回された部分コイルL2を構成できる。

【0057】

実装時には、接続端子11aおよび11b間を連結して短絡することで部分コイルL1およびL2を直列接続した状態でコイルを構成できる。

本実施形態においては、部分コイルL1と部分コイルL2とが直列接続して構成されている。また、部分コイルL1と部分コイルL2とが互いに逆方向に巻回して構成されているため、外乱ノイズに対する耐性を高めることができる。また、部分コイルL1が第1層8a−第3層8c間、部分コイルL2が第2層8b−第4層8d間にそれぞれ構成されているため、部分コイルL1−L2間の磁束鎖交領域をオーバーラップして設けることができ、外乱ノイズに対する耐性を高めることができる。

【0058】

部分コイルL1を第1層8a−第3層8c間、部分コイルL2を第2層8b−第4層8d間、に構成した実施形態を示したが、部分コイルL1を第1層8a−第2層8b間、部分コイルL2を第3層8c−第4層8d間に構成しても良い。

【0059】

(第3実施形態)

図10は、第3実施形態を示すもので、前述実施形態と異なるところは、配線7(制御端子接続配線パターン)と主電流配線6との間にスリットが設けられているところにある。前述実施形態と同一又は類似部分については同一又は類似の符号を付して説明を省略し、以下、異なる部分について説明を行う。

【0060】

図10は、主電流通電基板の一例を示している。この図10には、図2(a)に示した多層配線板8の構成を除いて示している。

図10に示すように、スリット12が、主電流配線6の電流経路の脇に位置して当該主電流配線6に沿って形成されている。このスリット12は、ソース電流Isが流れる主電流配線6と、配線7aおよび7bとの間に形成されている。このスリット12は、ソースリード端子Lesの接続用のランドLasと配線7aとの間にも形成される。これにより、ゲート電圧印加用配線7と主電流配線6との間の容量結合を抑制できる。

【0061】

特に、ゲート電圧印加用配線7の配線7a〜7cの一部または全部が主電流配線6と並走している場合、容量結合によってゲート印加電圧Vginにノイズが重畳する虞がある。このため、本実施形態では、スリット12を設けて絶縁することでノイズの影響を極力抑制できる。

【0062】

(第4実施形態)

図11は、第4実施形態を示すもので、前述実施形態と異なるところは、コイルに生じる誘導起電圧をクランプするためのツェナーダイオードを設けたところにある。図11に示すように、コイルLの一端子Lt1および他端子Lt2間には、ツェナーダイオードD1およびD2が互いに逆方向に接続されている。すると、コイルLに誘導起電圧が過大に生じたときに当該過電圧を所定電圧でクランプできる。

【0063】

(第5実施形態)

図12は、第5実施形態を示すもので、前述実施形態と異なるところは、コイルと共に主電流配線が多層配線板に組み込まれた状態で構成されているところにある。

【0064】

図12は、多層配線板の層構造を分解斜視図によって示している。この多層配線板13は5層構造となっており、図12中の下から第1層13a、第2層13b、第3層13c、第4層13dおよび第5層13eの5層構造となっている。ここで、第2層13b〜第5層13eの各層には、図9(a)〜図9(d)に示す第1層8a〜第4層8dの各層とそれぞれ同様の配線パターン(金属配線10、スルーホールH1〜H15)が形成されている。第1層13aには、主電流通電基板4に形成された配線パターン(主電流配線5,6、ゲート電流印加用配線7)と同様のパターンが形成されている。

【0065】

したがって、第1層13a〜第5層13eが多層配線板13に一体化されていると、コイルL(部分コイルL1、L2)と主電流配線6を多層配線板13に共に実装できるようになり、コイルLと主電流配線6を別々に実装する手間がなくなる。

【0066】

(第6実施形態)

図13は、第6実施形態を示すもので、前述実施形態と異なるところは、コイルを主電流配線に埋め込んだところにある。

【0067】

前述の実施形態では、主電流配線5、6を主電流通電基板4上の銅箔により形成した実施形態を示したが、これに限られるものではない。すなわち、図13に示すように、前述実施形態の主電流配線5,6に代えて所定厚さの導電板14を構成し、その一部に凹部14aを成形し、この凹部14aの上に多層配線板8を搭載しても良い。

【0068】

導電板14の凹部14aの下面が多層配線板8の搭載面となる。この導電板14の凹部14aはその凹面が平坦面に構成されており、多層配線板8が凹部14aの下面上に搭載される。コイルLの誘導起電圧は配線15を接続することで取得できる。このような形態であっても、導電板14の通電電流に応じて発生する磁束を多層配線板8内のコイルLに鎖交させることができる。

【0069】

(他の実施形態)

本発明は、前記の実施形態に限定されるものではなく、例えば、以下に示す変形又は拡張が可能である。

コイルLの巻数、コイル幅wは適宜変更しても良い。

ソース電流Is用の主電流配線6の上に多層配線板8を密着して搭載することで、ソース電流Isに応じた誘導起電圧をゲート印加電圧Vginに重畳させる実施形態を示したが、これに限られるものではなく、例えば、ドレイン電流Id用の主電流配線5の上に多層配線板8を密着して搭載し、ドレイン電流Idに応じた誘導起電圧をゲート印加電圧Vginに重畳させるようにしても良い。

【0070】

多層配線板8の複数層構造を全て貫通するスルーホールH1〜H6と金属配線10を用いてコイルLを構成した実施形態を示したが、多層配線層8の層間(例えば第1層8aおよび第2層8b間、第2層8bおよび第3層8c間、第3層8cおよび第4層8d間)のうち何れかを結合するビアを用いてコイルLを構成しても良い。

【0071】

誘導性負荷2を駆動するための駆動回路1に適用したが、特にこれに限られるものではなく、DCDCコンバータなどスイッチング素子M1を具備した回路を駆動する駆動回路に適用できる。

【符号の説明】

【0072】

図面中、1は駆動回路、2は誘導性負荷、3は電流経路、4は主電流通電基板、6は主電流配線、7はゲート電圧印加用配線(制御端子接続配線パターン)、8は多層配線板(基板)、8aは第1層、8bは第2層、8cは第3層、8dは第4層、9a、9bは接続端子、10は金属配線(配線パターン)、11a、11bは接続端子、12はスリット、13は多層配線板、13aは第1層、13bは第2層、13cは第3層、13dは第4層、13eは第5層、14は導電板(主電流配線)、15は配線、Lはコイル、L1は部分コイル(第1部分コイル)、L2は部分コイル(第2部分コイル)、M1はスイッチング素子、Sは信号源、Rgはゲート抵抗を示す。

【特許請求の範囲】

【請求項1】

信号源から与えられるパルス信号に応じてオンオフ制御され主電流が流れるスイッチング素子と、

平坦面を備え前記スイッチング素子の主電流を通電する主電流配線と、

前記主電流配線に搭載する搭載面が平坦面に構成され、コイルが内部に配設された基板と、を備え、

前記基板内のコイルは、前記スイッチング素子の主電流に応じて生じる磁束と鎖交するように配設されると共に、前記信号源のパルス信号を入力して前記スイッチング素子の制御端子に与えるように電気的に接続されていることを特徴とするスイッチング素子の駆動回路。

【請求項2】

前記スイッチング素子の制御端子に電気的に接続されたゲート抵抗を備え、

前記基板内のコイルは、前記ゲート抵抗と直列接続されていることを特徴とする請求項1記載のスイッチング素子の駆動回路。

【請求項3】

前記基板内のコイルは、その巻回端部間が前記主電流配線の配線幅以下の長さであり、当該主電流配線の配線幅内に設置されていることを特徴とする請求項1または2記載のスイッチング素子の駆動回路。

【請求項4】

前記基板は多層配線板を備えて構成され、

前記基板内のコイルは、前記多層配線板の複数の各層に形成された配線パターンと当該各層の配線パターンをループ状に結合するビアとを組み合わせて形成されることを特徴とする請求項1ないし3の何れかに記載のスイッチング素子の駆動回路。

【請求項5】

前記基板内のコイルは、前記多層配線板内に互いに逆方向ループ状に巻回された部分コイルを複数直列接続して構成されることを特徴とする請求項4記載のスイッチング素子の駆動回路。

【請求項6】

前記多層配線板は、第1層、第2層、第3層および第4層を順に備え、

前記基板内のコイルは、前記多層配線板内の第1層と第3層にそれぞれ形成された配線パターンをビアによって構造的に接続した第1部分コイルと、前記第1部分コイルとは逆方向に巻回され前記多層配線板内の第2層と第4層にそれぞれ形成された配線パターンをビアによって構造的に接続した第2部分コイルとを備えたことを特徴とする請求項5記載のスイッチング素子の駆動回路。

【請求項7】

前記多層配線板は、前記コイルと共に前記主電流配線を組み込んで構成されることを特徴とする請求項4ないし6の何れかに記載のスイッチング素子の駆動回路。

【請求項8】

前記スイッチング素子の制御端子に接続すると共に前記主電流配線が形成された主電流通電基板と同一基板に形成された制御端子接続配線パターンを備え、

前記制御端子接続配線パターンと前記主電流配線との間にスリットが設けられていることを特徴とする請求項1ないし7の何れかに記載のスイッチング素子の駆動回路。

【請求項9】

前記基板内のコイルに生じる誘導起電圧をクランプするツェナーダイオードを備えたことを特徴とする請求項1ないし8の何れかに記載のスイッチング素子の駆動回路。

【請求項10】

前記信号源を備えたことを特徴とする請求項1ないし9の何れかに記載のスイッチング素子の駆動回路。

【請求項1】

信号源から与えられるパルス信号に応じてオンオフ制御され主電流が流れるスイッチング素子と、

平坦面を備え前記スイッチング素子の主電流を通電する主電流配線と、

前記主電流配線に搭載する搭載面が平坦面に構成され、コイルが内部に配設された基板と、を備え、

前記基板内のコイルは、前記スイッチング素子の主電流に応じて生じる磁束と鎖交するように配設されると共に、前記信号源のパルス信号を入力して前記スイッチング素子の制御端子に与えるように電気的に接続されていることを特徴とするスイッチング素子の駆動回路。

【請求項2】

前記スイッチング素子の制御端子に電気的に接続されたゲート抵抗を備え、

前記基板内のコイルは、前記ゲート抵抗と直列接続されていることを特徴とする請求項1記載のスイッチング素子の駆動回路。

【請求項3】

前記基板内のコイルは、その巻回端部間が前記主電流配線の配線幅以下の長さであり、当該主電流配線の配線幅内に設置されていることを特徴とする請求項1または2記載のスイッチング素子の駆動回路。

【請求項4】

前記基板は多層配線板を備えて構成され、

前記基板内のコイルは、前記多層配線板の複数の各層に形成された配線パターンと当該各層の配線パターンをループ状に結合するビアとを組み合わせて形成されることを特徴とする請求項1ないし3の何れかに記載のスイッチング素子の駆動回路。

【請求項5】

前記基板内のコイルは、前記多層配線板内に互いに逆方向ループ状に巻回された部分コイルを複数直列接続して構成されることを特徴とする請求項4記載のスイッチング素子の駆動回路。

【請求項6】

前記多層配線板は、第1層、第2層、第3層および第4層を順に備え、

前記基板内のコイルは、前記多層配線板内の第1層と第3層にそれぞれ形成された配線パターンをビアによって構造的に接続した第1部分コイルと、前記第1部分コイルとは逆方向に巻回され前記多層配線板内の第2層と第4層にそれぞれ形成された配線パターンをビアによって構造的に接続した第2部分コイルとを備えたことを特徴とする請求項5記載のスイッチング素子の駆動回路。

【請求項7】

前記多層配線板は、前記コイルと共に前記主電流配線を組み込んで構成されることを特徴とする請求項4ないし6の何れかに記載のスイッチング素子の駆動回路。

【請求項8】

前記スイッチング素子の制御端子に接続すると共に前記主電流配線が形成された主電流通電基板と同一基板に形成された制御端子接続配線パターンを備え、

前記制御端子接続配線パターンと前記主電流配線との間にスリットが設けられていることを特徴とする請求項1ないし7の何れかに記載のスイッチング素子の駆動回路。

【請求項9】

前記基板内のコイルに生じる誘導起電圧をクランプするツェナーダイオードを備えたことを特徴とする請求項1ないし8の何れかに記載のスイッチング素子の駆動回路。

【請求項10】

前記信号源を備えたことを特徴とする請求項1ないし9の何れかに記載のスイッチング素子の駆動回路。

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【公開番号】特開2013−110684(P2013−110684A)

【公開日】平成25年6月6日(2013.6.6)

【国際特許分類】

【出願番号】特願2011−256147(P2011−256147)

【出願日】平成23年11月24日(2011.11.24)

【出願人】(000004260)株式会社デンソー (27,639)

【Fターム(参考)】

【公開日】平成25年6月6日(2013.6.6)

【国際特許分類】

【出願日】平成23年11月24日(2011.11.24)

【出願人】(000004260)株式会社デンソー (27,639)

【Fターム(参考)】

[ Back to top ]