スイッチング素子の駆動装置

【課題】第1スイッチング素子22および第1抵抗体24を介してパワースイッチング素子Swのゲートと電源20とを接続して且つ、第2スイッチング素子28および第2抵抗体26を介してゲートとエミッタとを接続する駆動装置において、ゲート電圧の設定ができないこと。

【解決手段】操作信号gがパワースイッチング素子Swをオン操作する指令に切り替わることで、第1スイッチング素子22および第2スイッチング素子28の双方のオン状態を実現する。これにより、ゲート印加電圧は、第1抵抗体24および第2抵抗体26によって電源20が分圧された電圧Vcとなる。その後、ミラー期間が終了することで、第2スイッチング素子28をオフ状態に切り替え、ゲート印加電圧を電源20の電圧Vcにする。

【解決手段】操作信号gがパワースイッチング素子Swをオン操作する指令に切り替わることで、第1スイッチング素子22および第2スイッチング素子28の双方のオン状態を実現する。これにより、ゲート印加電圧は、第1抵抗体24および第2抵抗体26によって電源20が分圧された電圧Vcとなる。その後、ミラー期間が終了することで、第2スイッチング素子28をオフ状態に切り替え、ゲート印加電圧を電源20の電圧Vcにする。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、電圧制御形のスイッチング素子の導通制御端子を高電圧印加手段に接続して且つ受動素子および第1開閉手段を備える第1経路と、前記導通制御端子を低電圧印加手段に接続して且つ受動素子および第2開閉手段を備える第2経路とを備え、前記第1開閉手段および前記第2開閉手段を操作することで前記スイッチング素子を駆動するスイッチング素子の駆動装置に関する。

【背景技術】

【0002】

この種の駆動装置としては、例えば下記特許文献1に見られるように、インバータを構成するIGBTをオンさせるべくゲートに印加するための電圧を生成する一対の電源を備えるものも提案されている。これにより、IGBTのオン操作に際しては、まず一対の電源のうち低電圧のものを用いてゲートに電圧を印加し、IGBTをオンさせる。次に、一対の電源のうち高電圧のものを用いてゲートの印加電圧を上昇させる。これにより、上下アームの短絡が生じる場合に、IGBTのオン操作に伴って過電流が流れることを好適に回避することができる。また、過電流が流れるおそれがない場合には、ゲート電圧の上昇によって導通損失を迅速に低減させることができる。

【先行技術文献】

【特許文献】

【0003】

【特許文献1】特開2009−71956号公報

【発明の概要】

【発明が解決しようとする課題】

【0004】

ただし、上記装置の場合、一対の電源のうち電圧の高い方を用いてゲートに電圧を印加する際に電圧の高い方から低い方に電流が流れるという問題がある。これに対し、上記装置では、ダイオードを備えることで上記電流の流れを回避するようにしているが、この場合、ダイオードの電圧降下量の変動によって、ゲート電圧が安定しないという問題がある。さらに、上記装置の場合、一対の電源を備える必要があり、回路規模の増大やコストアップを招くおそれもある。

【0005】

本発明は、上記課題を解決するためになされたものであり、その目的は、電圧制御形のスイッチング素子の導通制御端子を高電圧印加手段に接続して且つ受動素子および第1開閉手段を備える第1経路と、前記導通制御端子を低電圧印加手段に接続して且つ受動素子および第2開閉手段を備える第2経路とを備え、前記第1開閉手段および前記第2開閉手段を操作することで前記スイッチング素子を駆動するに際し、導通制御端子への印加電圧をより適切に可変設定することのできるスイッチング素子の駆動装置を提供することにある。

【課題を解決するための手段】

【0006】

以下、上記課題を解決するための手段、およびその作用効果について記載する。

【0007】

請求項1記載の発明は、電圧制御形のスイッチング素子の導通制御端子を高電圧印加手段に接続して且つ受動素子および第1開閉手段を備える第1経路と、前記導通制御端子を低電圧印加手段に接続して且つ受動素子および第2開閉手段を備える第2経路とを備え、前記第1開閉手段および前記第2開閉手段を操作することで前記スイッチング素子を駆動するスイッチング素子の駆動装置において、前記スイッチング素子のスイッチング状態の切り替えに際し、前記第1開閉手段および前記第2開閉手段の双方の閉状態からいずれか一方が閉且つ他方が開となる状態へと切り替える切替手段を備え、前記いずれか一方は、前記高電圧印加手段および前記低電圧印加手段のうちの前記スイッチング状態の切り替えによって実現されるスイッチング状態とするための電圧を前記導通制御端子に印加する方と前記導通制御端子とを接続するための手段であることを特徴とする。

【0008】

上記発明では、第1開閉手段および第2開閉手段の双方の閉状態といずれか一方が閉且つ他方が開となる状態とで、導通制御端子に対する印加電圧を相違させることができる。このため、切替手段による処理によって、導通制御端子への印加電圧をより適切に可変設定することができる。

【0009】

請求項2記載の発明は、請求項1記載の発明において、前記第1開閉手段および前記第2開閉手段の双方が閉状態とされる際の前記導通制御端子の電圧の収束値が、前記スイッチング素子のミラー電圧よりも前記高電圧印加手段の印加電圧および前記低電圧印加手段の印加電圧のうちの前記スイッチング状態の切り替えによって実現されるスイッチング状態とするための電圧側にあることを特徴とする。

【0010】

上記発明では、スイッチング状態の切り替えに際し、ミラー期間に移行した後と前とで、導通制御端子に印加する電圧を相違させることが可能となる。

【0011】

請求項3記載の発明は、請求項1または2記載の発明において、前記切替手段は、前記スイッチング状態をオフ状態からオン状態に切り替える際に前記切り替えを行うものであり、前記第1開閉手段および前記第2開閉手段の双方が閉状態とされる際の前記導通制御端子の電圧の収束値が前記スイッチング素子のミラー電圧よりも前記オン状態時の電圧側にあることを特徴とする。

【0012】

上記発明では、スイッチング状態をオン状態に切り替えるに際し、ミラー期間に移行した後と前とで、導通制御端子に印加する電圧を相違させることが可能となる。

【0013】

請求項4記載の発明は、請求項3記載の発明において、前記切替手段は、前記スイッチング素子のミラー期間以降に前記切り替えを行うことを特徴とする。

【0014】

請求項5記載の発明は、請求項1〜4のいずれか1項に記載の発明において、前記切替手段は、前記スイッチング素子の操作信号がスイッチング状態の切り替えを指示するタイミングに対して遅延したタイミングを指示する遅延信号を生成する遅延信号生成手段を備え、前記遅延信号に基づき前記切り替えを行うことを特徴とする。

【0015】

上記発明では、切り替え処理を行うべく遅延信号を参照することで、切り替え処理を適切なタイミングにて行うことができる。

【0016】

請求項6記載の発明は、請求項5記載の発明において、前記遅延信号生成手段は、前記操作信号を入力として前記遅延信号を生成することを特徴とする。

【0017】

上記発明では、遅延信号を適切に生成することができる。

【0018】

請求項7記載の発明は、請求項6記載の発明において、前記切替手段は、前記スイッチング状態をオフ状態からオン状態に切り替える際に前記第1開閉手段および前記第2開閉手段の双方の閉状態から前記第1開閉手段が閉且つ前記第2開閉手段が開となる状態への切り替えを行うものであり、前記スイッチング素子を流れる電流が過度に大きくなるか否かを判断する過電流判断手段を更に備え、前記遅延信号は、前記スイッチング素子をオン状態に切り替えるに際しての前記遅延したタイミングを指示するものであり、前記遅延信号による遅延時間は、前記過電流判断手段による過電流の判断に要する時間以上に設定されることを特徴とする。

【0019】

スイッチング素子の出力端子が低電位の部材と異常な低インピーダンスで接続される場合等にあっては、スイッチング素子をオンした瞬間に過電流が流れる。ただし、この過電流が流れたことが過電流判断手段によって判断されるまでには、ある程度の処理時間(過電流判断手段による過電流の判断に要する時間)が必要となる。そして、この判断以前において第1開閉手段が閉状態であって且つ第2開閉手段が開状態となる状態に切り替えてしまうと、スイッチング素子を流れる電流が更に増大し、スイッチング素子の信頼性を低下させるおそれがある。上記発明では、この点に鑑み、遅延信号の遅延時間を上記設定とする。

【0020】

請求項8記載の発明は、請求項7記載の発明において、前記過電流判断手段により前記スイッチング素子を流れる電流が過度に大きくなると判断される場合、前記切替手段による前記切り替えを禁止する禁止手段を更に備えることを特徴とする。

【0021】

上記発明では、過電流が流れる場合に切り替えを禁止することで、スイッチング素子を流れる電流が更に増加することを回避することができる。

【0022】

請求項9記載の発明は、請求項5〜8のいずれか1項に記載の発明において、前記遅延信号は、前記スイッチング素子をオン状態に切り替えるに際しての前記遅延したタイミングを指示するものであり、前記遅延したタイミングまでの遅延時間は、前記スイッチング素子のオン状態への切替指令タイミングから前記スイッチング素子のミラー期間のうちの該ミラー期間の終了前のタイミングとなるまでに要すると想定される時間に設定されることを特徴とする。

【0023】

上記発明によれば、スイッチング素子の損失を低減することができる。

【0024】

請求項10記載の発明は、請求項5〜8のいずれか1項に記載の発明において、前記遅延信号は、前記スイッチング素子をオン状態に切り替えるに際しての前記遅延したタイミングを指示するものであり、前記遅延したタイミングまでの遅延時間は、前記スイッチング素子のオン状態への切替指令タイミングから前記スイッチング素子のミラー期間の終了タイミングとなるまでに要すると想定される時間に設定されることを特徴とする。

【0025】

スイッチング素子を流れる電流の変化速度が大きい場合、電流の流通経路に存在するインダクタ(寄生インダクタ等)によって、大きなサージが生じることとなる。このサージを低減する上では、ミラー期間の終了までにおける導通制御端子の電圧の変化速度を抑制することが望ましい。ただし、導通制御端子の電圧の変化速度が小さい場合には、スイッチング状態の切り替えに際しての損失が増大する。上記発明では、この点に鑑み、スイッチング素子のミラー期間の終了とともに切り替え処理を行うことで、サージを抑制しつつも損失を極力低減することができる。

【0026】

請求項11記載の発明は、請求項1〜4のいずれか1項に記載の発明において、前記切替手段は、前記スイッチング素子のミラー期間の終了を検出する終了検出手段を備え、前記ミラー期間の終了が検出されることで前記切り替えを行うことを特徴とする。

【0027】

スイッチング素子を流れる電流の変化速度が大きい場合、電流の流通経路に存在するインダクタ(寄生インダクタ等)によって、大きなサージが生じることとなる。このサージを低減する上では、ミラー期間の終了までにおける導通制御端子の電圧の変化速度を抑制することが望ましい。ただし、導通制御端子の電圧の変化速度が小さい場合には、スイッチング状態の切り替えに際しての損失が増大する。上記発明では、この点に鑑み、スイッチング素子のミラー期間の終了が検出されることで切り替え処理を行うことで、サージを抑制しつつも損失を極力低減することが可能となる。

【0028】

請求項12記載の発明は、請求項5〜10のいずれか1項に記載の発明において、前記切替手段は、前記スイッチング素子のミラー期間の終了を検出する終了検出手段を備え、前記遅延信号によって規定された遅延時間が経過して且つ前記ミラー期間の終了が検出されることで前記切り替えを行うことを特徴とする。

【0029】

スイッチング素子を流れる電流の変化速度が大きい場合、電流の流通経路に存在するインダクタ(寄生インダクタ等)によって、大きなサージが生じることとなる。このサージを低減する上では、ミラー期間の終了までにおける導通制御端子の電圧の変化速度を抑制することが望ましい。ただし、導通制御端子の電圧の変化速度が小さい場合には、スイッチング状態の切り替えに際しての損失が増大する。上記発明では、この点に鑑み、スイッチング素子のミラー期間の終了が検出されることに基づき切り替え処理を行うことで、サージを抑制しつつも損失を極力低減することができる。

【0030】

請求項13記載の発明は、請求項11または12記載の発明において、前記終了検出手段は、前記導通制御端子の電圧と終了判定電圧とを比較する比較手段を備え、該比較手段の比較結果を前記ミラー期間の終了の有無の検出結果を示す信号とすることを特徴とする。

【0031】

請求項14記載の発明は、請求項13記載の発明において、前記スイッチング素子の温度を検出する温度検出手段を備え、前記終了検出手段は、前記温度検出手段によって検出される温度に応じて前記終了判定電圧を可変設定することを特徴とする。

【0032】

ミラー期間における導通制御端子の電圧は、温度依存性を有する。上記発明では、この点に鑑み、終了判定電圧を、現在の温度においてミラー期間の電圧として想定される値に応じて設定することが可能となる。

【0033】

請求項15記載の発明は、請求項11または12記載の発明において、前記終了検出手段は、前記導通制御端子の電圧の変化を検出する手段を備え、該変化が検出されることに基づき前記ミラー期間の終了を検出することを特徴とする。

【0034】

ミラー期間においては、導通制御端子の電圧の変化速度が大きく低下する。このため、ミラー期間の終了時には、導通制御端子の電圧の変化速度が大きく増大することとなる。上記発明では、この点に着目し、ミラー期間の終了を検出する。

【0035】

請求項16記載の発明は、請求項1〜15のいずれか1項に記載の発明において、前記第1経路が備える受動素子は、抵抗体を含むことを特徴とする。

【0036】

請求項17記載の発明は、請求項1〜16のいずれか1項に記載の発明において、前記第2経路が備える受動素子は、抵抗体を含むことを特徴とする。

【0037】

請求項18記載の発明は、請求項17記載の発明において、前記第1経路が備える受動素子は、抵抗体からなり、前記第2経路が備える受動素子は、抵抗体からなることを特徴とする。

【0038】

上記発明では、第1経路および第2経路を簡素な構成とすることができる。

【0039】

請求項19記載の発明は、請求項17記載の発明において、前記第1経路が備える受動素子は、抵抗体からなり、前記第2経路が備える受動素子は、抵抗体とコンデンサとの並列接続体からなることを特徴とする。

【0040】

上記発明において、前記高電圧印加手段と前記導通制御端子との接続によってオン状態とされて且つスイッチング状態をオフ状態からオン状態へと切り替えるに際して切替手段を用いる場合、第1開閉手段および第2開閉手段の双方が閉状態である際の導通制御端子の電圧の変化速度はコンデンサによって制限される。このため、第1経路が備える抵抗体の抵抗値を極力小さくすることができ、ひいては第1開閉手段が閉状態であって且つ第2開閉手段が開状態とされる状態に切り替えられた際の導通制御端子の電圧の上昇速度を極力大きくすることができる。

【0041】

請求項20記載の発明は、請求項1〜15のいずれか1項に記載の発明において、前記第1経路が備える受動素子は、抵抗体とコンデンサとの並列接続体からなり、前記第2経路が備える受動素子は、抵抗体とコンデンサとの並列接続体からなることを特徴とする。

【0042】

請求項21記載の発明は、請求項20記載の発明において、前記スイッチング素子は、前記高電圧印加手段と前記導通制御端子との接続によってオン状態とされるものであり、前記切替手段は、前記スイッチング状態をオフ状態からオン状態に切り替える際に前記切り替えを行うものであり、前記第1経路のコンデンサと前記第2経路のコンデンサとの直列接続体によって前記高電圧印加手段と前記低電圧印加手段との間の電圧を分圧した値が前記スイッチング素子のミラー電圧よりも低く、且つ前記第1経路の抵抗体と前記第2経路の抵抗体とによって前記高電圧印加手段と前記低電圧印加手段との間の電圧を分圧した値が前記スイッチング素子のミラー電圧よりも高いことを特徴とする。

【0043】

上記発明では、ミラー電圧となるまでに要する時間を低減することができる。

【0044】

請求項22記載の発明は、請求項1記載の発明において、前記切替手段は、前記スイッチング状態をオン状態からオフ状態に切り替える際に前記切り替えを行うものであり、前記第1開閉手段および前記第2開閉手段の双方が閉状態とされる際の前記導通制御端子の電圧の収束値が前記スイッチング素子のミラー電圧よりも前記オフ状態とする電圧側であることを特徴とする。

【0045】

上記発明では、スイッチング状態をオフ状態に切り替えるに際し、ミラー期間を移行した後と前とで、導通制御端子に印加する電圧を相違させることが可能となる。

【0046】

請求項23記載の発明は、請求項22記載の発明において、前記切替手段は、前記スイッチング素子のミラー期間以降に前記切り替えを行うことを特徴とする。

【0047】

請求項24記載の発明は、請求項1〜23のいずれか1項に記載の発明において、前記スイッチング素子は、高電位側のスイッチング素子および低電位側のスイッチング素子の直列接続体を備える電力変換回路における前記直列接続体を構成するスイッチング素子であることを特徴とする。

【0048】

上記発明では、高電位側のスイッチング素子および低電位側のスイッチング素子の双方がオン状態となる事態が生じた場合に、これらに過度の電流が流れるおそれがある。ただし、この場合であっても、第1開閉手段および第2開閉手段の双方がオン状態となる状態であれば、電流量を制限することができる。このため、上記発明は、切替手段の利用価値が特に大きい。

【図面の簡単な説明】

【0049】

【図1】第1の実施形態にかかるシステム構成図。

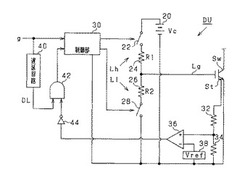

【図2】同実施形態にかかるドライブユニットの回路構成を示す回路図。

【図3】同実施形態にかかる遅延回路の回路構成例を示す回路図。

【図4】同実施形態にかかるパワースイッチング素子のオン操作態様を示すタイムチャート。

【図5】第2の実施形態にかかるパワースイッチング素子のオン操作態様を示すタイムチャート。

【図6】第3の実施形態にかかるパワースイッチング素子のオン操作態様を示すタイムチャート。

【図7】第4の実施形態にかかるドライブユニットの回路構成を示す回路図。

【図8】同実施形態にかかるパワースイッチング素子のオン操作態様を示すタイムチャート。

【図9】第5の実施形態にかかるドライブユニットの回路構成を示す回路図。

【図10】第6の実施形態にかかるドライブユニットの回路構成を示す回路図。

【図11】同実施形態にかかるパワースイッチング素子のオン操作態様を示すタイムチャート。

【図12】第7の実施形態にかかるドライブユニットの回路構成を示す回路図。

【図13】同実施形態にかかるパワースイッチング素子のオン操作態様を示すタイムチャート。

【図14】第8の実施形態にかかるドライブユニットの回路構成を示す回路図。

【図15】同実施形態にかかるパワースイッチング素子のオン操作態様を示すタイムチャート。

【図16】第9の実施形態にかかるドライブユニットの回路構成を示す回路図。

【図17】同実施形態にかかるパワースイッチング素子のオン操作態様を示すタイムチャート。

【図18】第10の同実施形態にかかるパワースイッチング素子のオン操作態様を示すタイムチャート。

【発明を実施するための形態】

【0050】

(第1の実施形態)

以下、本発明にかかるパワースイッチング素子の駆動装置をハイブリッド車に適用した第1の実施形態について、図面を参照しつつ説明する。

【0051】

図1に、本実施形態のシステム構成を示す。図示されるように、車載主機としてのモータジェネレータ10は、インバータIVおよびコンバータCVを介して高電圧バッテリ12に接続されている。インバータIVは、高電位側のパワースイッチング素子Swpおよび低電位側のパワースイッチング素子Swnの直列接続体が3つ並列接続されて構成されている。そして、これら各パワースイッチング素子Swpおよびパワースイッチング素子Swnの接続点が、モータジェネレータ10の各相にそれぞれ接続されている。また、コンバータCVは、コンデンサCと、高電位側のパワースイッチング素子Swpおよび低電位側のパワースイッチング素子Swnの直列接続体と、パワースイッチング素子Swpおよびパワースイッチング素子Swnの接続点と高電圧バッテリ12とを接続するリアクトルLとを備えている。

【0052】

上記高電位側のパワースイッチング素子Swpおよび低電位側のパワースイッチング素子Swnのそれぞれの入出力端子間(コレクタおよびエミッタ間)には、高電位側のフリーホイールダイオードFDpおよび低電位側のフリーホイールダイオードFDnのカソードおよびアノードが接続されている。特に、本実施形態では、高電位側のパワースイッチング素子Swpおよび高電位側のフリーホイールダイオードFDpは互いに同一の半導体基板に隣接して形成されており、低電位側のパワースイッチング素子Swnおよび低電位側のフリーホイールダイオードFDnは互いに同一の半導体基板に隣接して形成されている。こうした半導体デバイスとしては、例えば「モータ制御用RC−IGBT 高橋秀樹、他2名 7(315) 三菱電機技報、VOl81、NO.5,2007」に記載されているものがある。

【0053】

上記インバータIVを構成するパワースイッチング素子Swp,Swnの導通制御端子(ゲート)には、いずれもドライブユニットDUが接続されている。これにより、パワースイッチング素子Swp,Swnは、ドライブユニットDUを介して、低電圧バッテリ14を電源とする制御装置16によって駆動される。制御装置16は、図示しない各種センサの検出値等に基づき、インバータIVのU相、V相、およびW相のそれぞれについてのパワースイッチング素子Swpを操作する操作信号gup,gvp,gwpと、パワースイッチング素子Swnを操作する操作信号gun,gvn,gwnとを生成し出力する。また、コンバータCVのパワースイッチング素子Swp、Swnを操作する操作信号gcp,gcnを生成し出力する。これにより、パワースイッチング素子Swp,Swnは、ドライブユニットDUを介して制御装置16により操作される。

【0054】

なお、インバータIVやコンバータCVを備える高電圧システムと、制御装置16を備える低電圧システムとは、図示しないフォトカプラ等の絶縁手段によって絶縁されており、上記操作信号は、絶縁手段を介して高電圧システムに出力される。

【0055】

上記パワースイッチング素子Swp,Swnは、いずれも絶縁ゲートバイポーラトランジスタ(IGBT)にて構成されている。また、パワースイッチング素子Swp,Swnは、その入力端子および出力端子間に流れる電流と相関を有する微少電流を出力するセンス端子Stを備えている。

【0056】

図2に、本実施形態にかかるドライブユニットDUの回路構成を示す。なお、以下では、パワースイッチング素子Swp、Swnを総括する場合、パワースイッチング素子Swと記載し、フリーホイールダイオードFDp,FDnを総括する場合、フリーホイールダイオードFDと記載する。また、上記操作信号gup,gvp,gwp,gcp,gun,gvn,gwn,gcnを総括する場合、操作信号gと記載する。

【0057】

図示されるように、ドライブユニットDUは、パワースイッチング素子Swをオンさせるべく出力端子(エミッタ)よりも所定の電圧Vcだけ高い高電圧を印加するための電源20を備えている。なお、図では、電源20をバッテリの記号にて示してあるが、実際には、この電源20は、フローティング電源を構成するコンデンサ等であってもよい。電源20の高電圧は、第1スイッチング素子22および線形素子としての第1抵抗体24を備える高電圧経路Lhおよび共通経路Lgを介してパワースイッチング素子Swの導通制御端子(ゲート)に印加される。また、ゲートの電荷は、共通経路Lgと、線形素子としての第2抵抗体26および第2スイッチング素子28を備える低電圧経路Llを介して放電される。ここで、ゲートは、共通経路Lgおよび低電圧経路Llを介してパワースイッチング素子Swのエミッタに接続されている。

【0058】

一方、制御部30は、操作信号gを入力とし、これに基づき第1スイッチング素子22および第2スイッチング素子28を操作することで、パワースイッチング素子Swを駆動する。詳しくは、本実施形態では、操作信号gがオン操作指令となることで、まず第1スイッチング素子22および第2スイッチング素子28の双方をオン操作することで、パワースイッチング素子Swを充電した後、所定の遅延時間が経過することで、第2スイッチング素子28をオフする。これにより、スイッチング状態のオフ状態からオン状態への切り替え途中においてゲート印加電圧を上昇させることができる。この所定の遅延時間は、遅延回路40によって設定される。遅延回路40は、操作信号gを入力とし、操作信号gによってオン操作への切り替え指示がなされるタイミングに対して所定の遅延時間遅延したタイミングを指示する遅延信号DLを生成する回路である。この回路としては、例えば図3に示すものとすればよい。

【0059】

図3(a)は、抵抗体40bおよびコンデンサ40aによって構成される遅延回路であり、入力信号としての操作信号gが論理「H」となることでコンデンサ40aの電圧が漸増し、論理「H」に対応する電圧値へと所定の遅延時間が経過することで移行する。また、図3(b)は、図3(a)の構成において、出力側から入力側へと進む方向を順方向とするダイオード40cが抵抗体40bに並列接続されるものである。この構成によれば、操作信号gが論理「H」に変化してから遅延回路40の出力信号が論理「H」に変化するまでには遅延が生じるものの、操作信号gが論理「L」に変化してから遅延回路40の出力信号が論理「L」に変化するまでには殆ど遅延が生じない。また、図3(c)は、抵抗体40bおよびコンデンサ40aの直列接続体の両端に電源40fの電圧を印加し、上記コンデンサ40aを迂回するようにスイッチング素子40dを設けて且つ、そのゲートにインバータ40eによる操作信号gの論理反転信号を印加するものである。この構成によっても、操作信号gが論理「H」に変化してから遅延回路40の出力信号が論理「H」に変化するまでには遅延が生じるものの、操作信号gが論理「L」に変化してから遅延回路40の出力信号が論理「L」に変化するまでには殆ど遅延が生じない。

【0060】

上記遅延回路40の遅延時間は、スイッチング状態のオフ状態からオン状態への移行期間のうちゲート電圧の上昇速度が一旦大きく低下する期間(ミラー期間)が終了するまでに要する時間より長く設定される。ただし、本実施形態では、遅延時間の経過後であっても、パワースイッチング素子Swに過電流が流れる場合には、第2スイッチング素子28をオフ操作しない。これを実現する構成は以下である。

【0061】

パワースイッチング素子Swのセンス端子Stとエミッタとの間には、抵抗体32,34の直列接続体が接続されており、その接続点には、コンパレータ36の非反転入力端子が接続されている。また、コンパレータ36の反転入力端子には、基準電源38の基準電圧Vrefが印加されている。ここで、基準電圧Vrefは、パワースイッチング素子Swに流れる電流が過度に大きいと判断される下限値(閾値電流)に応じて設定されるものである。これにより、コンパレータ36では、センス端子Stの出力電流による抵抗体32,34の電圧降下を利用して、パワースイッチング素子Swを流れる電流が閾値電流であるか否かを判断することができる。

【0062】

コンパレータ36の出力信号は、インバータ44によって論理反転された後、AND回路42に取り込まれる。AND回路42は、遅延回路40の出力する遅延信号DLと、インバータ44の出力する信号との論理積信号を生成し、制御部30に出力する。そして制御部30では、AND回路42の出力信号が論理「H」となることで第2スイッチング素子28をオフ操作する。これにより、制御部30では、操作信号gがオン操作を指令するタイミングから所定の遅延時間経過することと、パワースイッチング素子Swに閾値電流以上の電流が流れていないこととの論理積が真である場合に第2スイッチング素子28をオフ操作する。

【0063】

図4に、本実施形態にかかるパワースイッチング素子Swの駆動処理について、正常時の場合(ケース1)と過電流が検出される場合(ケース2)とを比較しつつ示す。詳しくは、図4(a)に、ゲート電圧Vgeの推移を示し、図4(b)に、第1スイッチング素子22の操作状態の推移を示し、図4(c)に、第2スイッチング素子28の操作状態の推移を示し、図4(d)に、コンパレータ36の出力信号の推移を示し、図4(e)に、遅延信号DLの推移を示す。

【0064】

図示されるように、操作信号gがオン操作指令に切り替わることで、第1スイッチング素子22および第2スイッチング素子28をオン操作する。これにより、ゲートの電圧は、第1抵抗体24および第2抵抗体26による電圧Vcの分圧値「R2・Vc/(R1+R2)」に収束する。この分圧値は、パワースイッチング素子Swがオン状態に切り替わる閾値電圧Vth以上に設定される。このため、ケース1の場合には、ゲート電圧が閾値電圧Vthに達することでミラー期間に移行し、ゲートの電圧の上昇速度がミラー期間以前と比較して一旦無視できるほど小さくなり、その後、ミラー期間の経過後において分圧値に収束する。その後、遅延時間Tdの経過に伴って、第2スイッチング素子28がオフ操作されることで、ゲート電圧Vgeは、電圧Vcまで上昇する。

【0065】

一方、ケース2の場合には、ゲート電圧Vgeは、上記分圧値まで一気に上昇する。そして場合、コンパレータ36の出力信号が論理「H」となり、過電流の検出がなされるため、遅延時間Tdが経過しても第2スイッチング素子28をオフ操作しない。なお、上記遅延時間Tdは、コンパレータ36を備えて構成される過電流判断手段による過電流の判断に要する時間Tiよりも長く設定される。また、過電流の判断のための閾値電流は、ゲート電圧が上記分圧値となる際にパワースイッチング素子Swを流れることのできる最大電流以下に設定される。

【0066】

これにより、過電流が流れる場合には、ゲート電圧を上記分圧値に制限することで、パワースイッチング素子Swに流れる電流を制限することができる。ちなみに、ゲート電圧が電圧Vcとなる場合にパワースイッチング素子Swに流すことのできる最大電流は、パワースイッチング素子Swの信頼性を維持できない大電流であり、特に上記閾値電流よりも十分に大きい。それにもかかわらずゲート印加電圧を電圧Vcまで上昇させるのは、パワースイッチング素子Swをオン状態とする際の導通損失がゲート電圧Vgeが大きいほど小さくなるためである。ただし、ゲート印加電圧を電圧Vcに一気に上昇させる場合には、過電流が流れる異常な状況下において、パワースイッチング素子Swに流れる電流が過度に大きくなる(ゲート電圧が電圧Vcとなる場合にパワースイッチング素子Swに流すことのできる最大電流となる)期間が存在する。これは、過電流判断手段の動作速度に限界があるためである。このため、パワースイッチング素子Swとして、過電流判断手段によって過電流が流れると判断され、フェールセーフ処理がなされるまでの期間、少なくとも上記大電流に耐えうるものを選択する必要が生じ、ひいてはパワースイッチング素子Swの大型化を招く。

【0067】

特に、パワースイッチング素子SwおよびフリーホイールダイオードFDが互いに同一の半導体基板に隣接して形成されるものにあっては、パワースイッチング素子Swの導通損失が大きくなりやすいため、エミッタおよびコレクタ間の厚さを低減することが望まれるが、この場合、熱に対する耐性が低下するため、パワースイッチング素子Swに流せる許容電流が低減する。このため、上記フェールセーフ処理がなされるまでの時間大電流に耐えうるものを選択する場合、パワースイッチング素子Swの表面積を大きくする要求が特に大きくなる。

【0068】

以上詳述した本実施形態によれば、以下の効果が得られるようになる。

【0069】

(1)パワースイッチング素子Swのオン状態への切り替えに際し、第1スイッチング素子22および第2スイッチング素子28の双方のオン状態から第1スイッチング素子22がオン且つ第2スイッチング素子28がオフとなる状態へと切り替えた。これにより、ゲート印加電圧を段階的に変化させることができる。特に、第1スイッチング素子22および第2スイッチング素子28の双方が閉状態となる期間におけるゲート電圧Vgeを、第1抵抗体24および第2抵抗体26の抵抗値の精度によって高精度に制御することができる。

【0070】

(2)第1スイッチング素子22および第2スイッチング素子28の双方をオン状態とする場合のゲート電圧Vgeの収束値を、パワースイッチング素子Swがオン状態となる電圧Vth(ミラー電圧)よりも高く設定した。これにより、スイッチング状態をオン状態に切り替えるに際し、ミラー期間に移行した後と前とで、ゲート印加電圧を相違させることが可能となる。

【0071】

(3)パワースイッチング素子Swのミラー期間以降に、第1スイッチング素子22および第2スイッチング素子28の双方のオン状態から第1スイッチング素子22がオン且つ第2スイッチング素子28がオフとなる状態へと切り替えた。これにより、スイッチング状態をオン状態に切り替えるに際し、ミラー期間に移行した後と前とで、ゲート印加電圧を相違させることが可能となる。

【0072】

(4)パワースイッチング素子Swの操作信号gがオン状態への切り替えを指示するタイミングに対して遅延したタイミングを指示する遅延信号DLを生成する遅延回路40を備え、遅延信号DLに基づき第1スイッチング素子22および第2スイッチング素子28の双方のオン状態から第1スイッチング素子22がオン且つ第2スイッチング素子28がオフとなる状態へと切り替えた。これにより、切り替え処理を適切なタイミングにて行うことができる。

【0073】

(5)遅延回路40を、操作信号gを入力として遅延信号DLを生成する回路とした。これにより、遅延信号DLを適切に生成することができる。

【0074】

(6)遅延信号DLによる遅延時間Tdを、過電流判断手段(コンパレータ36等)による過電流の判断に要する時間以上に設定した。これにより、過電流の有無の判断を待って、第1スイッチング素子22および第2スイッチング素子28の双方のオン状態から第1スイッチング素子22がオン且つ第2スイッチング素子28がオフとなる状態へと切り替えることができる。

【0075】

(7)過電流が検出される場合、第1スイッチング素子22および第2スイッチング素子28の双方のオン状態から第1スイッチング素子22がオン且つ第2スイッチング素子28がオフとなる状態への切り替えを禁止した。これにより、パワースイッチング素子Swを流れる電流が更に増加することを回避することができる。

【0076】

(8)高電圧経路Lhが備える受動素子が抵抗体(第1抵抗体24)からなり、低電圧経路Llが備える受動素子が抵抗体(第2抵抗体26)からなるようにした。これにより、高電圧経路Lhや低電圧経路Llを簡素な構成とすることができる。

【0077】

(9)ドライブユニットDUの駆動対象を、高電位側のパワースイッチング素子Swpおよび低電位側のパワースイッチング素子Swnの直列接続体を備える電力変換回路(インバータIV)における上記直列接続体を構成するパワースイッチング素子Swp,Swnとした。この場合、高電位側のパワースイッチング素子Swpおよび低電位側のパワースイッチング素子Swnの双方がオン状態となる事態が生じた場合に、これらに過度の電流が流れるおそれがあるため、上記切り替え処理の利用価値が特に大きい。

【0078】

(第2の実施形態)

以下、第2の実施形態について、先の第1の実施形態との相違点を中心に図面を参照しつつ説明する。

【0079】

本実施形態では、パワースイッチング素子Swのミラー期間の途中で、第1スイッチング素子22および第2スイッチング素子28の双方のオン状態から第1スイッチング素子22がオン且つ第2スイッチング素子28がオフとなる状態へと切り替える。これにより、パワースイッチング素子Swに電流が流れることによる損失の低減を図る。すなわち、ミラー期間の終了後、第1抵抗体24および第2抵抗体26による電圧Vcの分圧値によって定まる電圧「R2・Vc/(R1+R2)」にゲート電圧Vgeが収束すると、ミラー期間の終了後においてゲート印加電圧を電圧Vcとした場合と比較して損失が大きくなる。このため、ミラー期間の途中で上記切り替えを行なうことで、ミラー期間の終了後、ゲート電圧Vgeは、電圧Vcに向けて速やかに上昇することとなり、損失を低減することができる。

【0080】

図5に、本実施形態にかかるパワースイッチング素子Swの駆動処理(特に、正常時)を示す。なお、図5(a)〜図5(d)は、先の図4(a)〜図4(d)に対応している。図に示すミラー期間においてはゲート電圧Vgeの上昇速度は、ミラー期間前やミラー期間後と比較して無視しうるほど小さいが、実際には、図中下方に拡大して示すように、ゲート電圧Vgeは上昇している。そして、その上昇速度は、第1スイッチング素子22および第2スイッチング素子28の双方のオン状態から第1スイッチング素子22がオン且つ第2スイッチング素子28がオフとなる状態へと切り替えることで大きくなる。

【0081】

なお、上記切り替えタイミングの設定は、遅延回路40の回路時定数の調節等によって行なうことができる。

【0082】

以上説明した本実施形態によれば、先の第1の実施形態の上記(1)、(2)、(4)〜(9)の各効果に加えて、更に以下の効果が得られるようになる。

【0083】

(10)遅延信号DLによる遅延時間Tdを、パワースイッチング素子Swのオン状態への切替指令タイミングからミラー期間のうちのミラー期間の終了前のタイミングとなるまでに要すると想定される時間に設定した。これにより、パワースイッチング素子Swの損失を低減することができる。

【0084】

(第3の実施形態)

以下、第3の実施形態について、先の第1の実施形態との相違点を中心に図面を参照しつつ説明する。

【0085】

本実施形態では、パワースイッチング素子Swのミラー期間の終了タイミングにおいて、第1スイッチング素子22および第2スイッチング素子28の双方のオン状態から第1スイッチング素子22がオン且つ第2スイッチング素子28がオフとなる状態へと切り替える。これにより、サージの増大を抑制しつつも、パワースイッチング素子Swに電流が流れることによる損失の低減を図る。図6に、本実施形態にかかるパワースイッチング素子Swの駆動処理(特に、正常時)を示す。なお、図6(a)〜図6(d)は、先の図4(a)〜図4(d)に対応している。

【0086】

すなわち、上記第2の実施形態では、先の図5に示したように、第1スイッチング素子22および第2スイッチング素子28の双方のオン状態から第1スイッチング素子22がオン且つ第2スイッチング素子28がオフとなる状態へと切り替えることで、ゲート電圧Vgeの上昇速度が大きくなる。これにより、パワースイッチング素子Swを流れる電流の変化速度が増大し、ひいてはサージが大きくなるおそれがある。これに対し、上記切り替えをミラー期間の終了時とすることで、サージの抑制を図りつつもパワースイッチング素子Swの損失を極力低減する。

【0087】

なお、上記切り替えタイミングの設定は、遅延回路40の回路時定数の調節等によって行なうことができる。

【0088】

以上説明した本実施形態によれば、先の第1の実施形態の上記(1)、(2)、(4)〜(9)の各効果に加えて、更に以下の効果が得られるようになる。

【0089】

(11)遅延信号DLの遅延時間Tdを、パワースイッチング素子Swのオン操作指令タイミングからミラー期間の終了タイミングとなるまでに要すると想定される時間に設定した。これにより、サージを抑制しつつも損失を極力低減することができる。

【0090】

(第4の実施形態)

以下、第4の実施形態について、先の第1の実施形態との相違点を中心に図面を参照しつつ説明する。

【0091】

図7に、本実施形態にかかるドライブユニットDUの回路構成を示す。なお、図7において、先の図2に示した部材に対応する部材については、便宜上同一の符号を付している。

【0092】

本実施形態では、ゲート電圧Vgeを入力としてミラー期間の終了を判断し、これに基づき第1スイッチング素子22および第2スイッチング素子28の双方のオン状態から第1スイッチング素子22がオン且つ第2スイッチング素子28がオフとなる状態への切り替えを行なう。すなわち、本実施形態では、コンパレータ50を備え、その非反転入力端子にゲート電圧Vgeを印加し、反転入力端子に、電源52により、パワースイッチング素子Swがオンする際の電圧Vthよりもわずかに高い終了検出電圧Vmを印加する。そして、AND回路42は、遅延信号DLとインバータ44の出力信号と、コンパレータ50の出力信号の論理積信号を生成して制御部30に出力する。これにより、制御部30では、操作信号gがオン指令に切り替わるタイミングから遅延時間Tdが経過することと、過電流が検出されていないことと、ゲート電圧Vgeが上記終了検出電圧Vm以上となることとの論理積が真となることで、上記切り替えを行なう。ここで、遅延時間Tdは、操作信号gがオン操作指令に切り替わるタイミングからパワースイッチング素子Swに過電流が流れた場合にその旨がコンパレータ36等を備えて構成される過電流判断手段によって検出されるまでに要する時間Td以上であって且つ、ミラー期間の終了までに要する時間よりも短い時間に設定される。

【0093】

図8に、本実施形態にかかるパワースイッチング素子Swの駆動処理について、正常時の場合(ケース1)と過電流が検出される場合(ケース2)とを比較しつつ示す。なお、図8(a)〜図8(d)は、先の図4(a)〜図4(d)に対応しており、また図8(e)は、遅延信号DLの推移を示す。

【0094】

図示されるように、正常時においては、ミラー期間が終了し、ゲート電圧Vgeが終了検出電圧Vm以上となることで、第1スイッチング素子22および第2スイッチング素子28の双方のオン状態から第1スイッチング素子22がオン且つ第2スイッチング素子28がオフとなる状態への切り替えがなされる。これに対し、過電流が流れる場合には、上記切り替えはなされず、パワースイッチング素子Swを流れる電流は、第1スイッチング素子22および第2スイッチング素子28の双方のオン状態におけるゲート電圧Vgeの収束値によって流すことのできる電流に制限される。

【0095】

なお、遅延時間Tdは、操作信号gがオン操作指令に切り替わるタイミングからパワースイッチング素子Swに過電流が流れた場合にその旨がコンパレータ36等を備えて構成される過電流判断手段によって検出されるまでに要する時間Ti以上であって且つ、ミラー期間の終了までに要する時間よりも短い時間に設定される。

【0096】

以上説明した本実施形態によれば、先の第1の実施形態の上記(1)、(2)、(4)〜(9)の各効果に加えて、更に以下の効果が得られるようになる。

【0097】

(12)パワースイッチング素子Swのミラー期間の終了を検出し、ミラー期間の終了が検出されることで上記切り替えを行った。これにより、サージを抑制しつつも損失を極力低減することができる。

【0098】

(13)遅延信号DLによって規定された遅延時間Tdが経過して且つミラー期間の終了が検出されることで上記切り替えを行った。これにより、パワースイッチング素子Swがオン状態に切り替わることで過電流が流れる状況下、過電流が流れたと判断される以前にゲート電圧Vgeが上記終了検出電圧Vm以上となったとしても、上記切替がなされることを回避することができる。

【0099】

(第5の実施形態)

以下、第5の実施形態について、先の第4の実施形態との相違点を中心に図面を参照しつつ説明する。

【0100】

本実施形態では、ミラー期間の終了を判断するための終了検出電圧Vmをパワースイッチング素子Swの温度に応じて可変設定する。これは、パワースイッチング素子Swがオン状態に切り替わる電圧Vthが温度に応じて変動することに鑑みた設定である。

【0101】

図9に、本実施形態にかかるドライブユニットDUの回路構成を示す。なお、図9において、先の図7に示した部材に対応する部材については、便宜上同一の符号を付している。図示されるように、電源52aは、パワースイッチング素子Sw付近に配置されてその温度を検出する感温ダイオードSDによる温度検出信号に基づき終了検出電圧Vmを可変設定する。これにより、終了検出電圧Vmは、パワースイッチング素子Swの温度検出値によってパワースイッチング素子Swが実際にオン状態に切り替わると想定される値よりもわずかに大きい値に設定されることとなる。

【0102】

以上説明した本実施形態によれば、先の第1の実施形態の上記(1)、(2)、(4)〜(9)の各効果に加えて、更に以下の効果が得られるようになる。

【0103】

(14)パワースイッチング素子Swの温度に応じて終了検出電圧Vmを可変設定した。これにより、現在の温度においてミラー期間のゲート電圧Vgeとして想定される値に応じて終了検出電圧Vmを設定することができる。

【0104】

(第6の実施形態)

以下、第6の実施形態について、先の第4の実施形態との相違点を中心に図面を参照しつつ説明する。

【0105】

本実施形態では、ゲート電圧Vgeの変化の検出に基づきミラー期間の終了を検出する。

【0106】

図10に、本実施形態にかかるドライブユニットDUの回路構成を示す。なお、図10において、先の図2に示した部材に対応する部材については、便宜上同一の符号を付している。図示されるように、本実施形態では、ゲート電圧Vgeを入力として、これを微分する微分回路64を備える。この微分回路64は、例えばRC回路等によって構成することができる。そして、微分回路64の出力(ゲート電圧Vgeの変化速度)は、コンパレータ60の非反転入力端子に印加され、またコンパレータ60の反転入力端子には、電源62の電圧Vdが印加される。ここで、電圧Vdは、ミラー期間以外の微分回路64の出力値と、ミラー期間の微分回路64の出力値とで、コンパレータ60の出力値を相違させることのできる値に設定する。そして、AND回路42は、遅延信号DLと、インバータ44の出力信号と、コンパレータ60の出力信号との論理積信号を制御部30に出力する。これにより、制御部30では、操作信号gがオン操作指令に切り替わるタイミングから遅延時間Tdが経過することと、過電流が流れていないことと、ゲート電圧Vgeの上昇速度が所定以上となることとの論理積が真となることで、第1スイッチング素子22および第2スイッチング素子28の双方のオン状態から第1スイッチング素子がオン且つ第2スイッチング素子28がオフとなる状態へと切り替える処理を行なう。なお、遅延信号DLによって規定される遅延時間Tdは、操作信号gがオン操作指令に切り替わるタイミングからミラー期間に移行するタイミングまでに要する時間以上であって且つミラー期間の終了タイミングまでに要する時間以下に設定される。

【0107】

図11に、本実施形態にかかるパワースイッチング素子Swの駆動処理を示す。なお、図11(a)〜図11(d)は、先の図4(a)〜図4(d)に対応しており、また図11(e)は、遅延信号DLの推移を示す。

【0108】

図示されるように、操作信号gがオン操作指令に切り替わり、第1スイッチング素子22および第2スイッチング素子28がオン状態となることで、ゲート電圧Vgeが上昇していく。これにより、コンパレータ60は、ゲート電圧Vgeの変化速度がミラー期間によるものよりも大きい旨の信号を出力するものの、この場合には、遅延信号DLによって指定される遅延時間Tdが経過しないため、上記切り替えはなされない。その後、ミラー期間の途中で遅延信号DLによって指定される遅延時間Tdが経過するものの、この際には、ゲート電圧Vgeの変化速度がミラー期間によるものである旨の信号をコンパレータ60が出力するため、上記切り替えはなされない。その後、ゲート電圧Vgeの変化速度がミラー期間によるものよりも大きい旨の信号をコンパレータ60が出力することで、上記切替がなされる。

【0109】

以上説明した本実施形態によれば、先の第1の実施形態の上記(1)、(2)、(4)〜(9)の各効果に加えて、更に以下の効果が得られるようになる。

【0110】

(15)ゲート電圧Vgeの変化が検出されることに基づきミラー期間の終了を検出した。これにより、ミラー期間の終了を的確に検出することができる。

【0111】

(第7の実施形態)

以下、第7の実施形態について、先の第1の実施形態との相違点を中心に図面を参照しつつ説明する。

【0112】

図12に、本実施形態にかかるドライブユニットDUの回路構成を示す。なお、図10において、先の図2に示した部材に対応する部材については、便宜上同一の符号を付している。図示されるように、本実施形態では、高電圧経路と低電圧経路とを複数備える。すなわち、高電圧経路として、第1スイッチング素子22aおよび第1抵抗体24aを備える高電圧経路Lhaと、第1スイッチング素子22bおよび第1抵抗体24bを備える高電圧経路Lhbとを備える。また、低電圧経路として、第2スイッチング素子28aおよび第2抵抗体26aを備える低電圧経路Llaと、第2スイッチング素子28bおよび第2抵抗体26bを備える低電圧経路Llaとを備える。ここで、第1抵抗体24a(抵抗値R1)および第2抵抗体26a(抵抗値R2)による電圧Vcの分圧値「Vc・R2/(R1+R2)」よりも、第1抵抗体24b(抵抗値R3)および第2抵抗体26b(抵抗値R4)による電圧Vcの分圧値「Vc・R4/(R3+R4)」の方が低く設定されている。詳しくは、パワースイッチング素子Swがオン状態に切り替わる閾値電圧Vthが上記一対の分圧値の間となるように設定されている。そして、第1抵抗体24aの抵抗値R1と第2抵抗体26aの抵抗値R2との和が、第1抵抗体24bの抵抗値R3と第2抵抗体26bの抵抗値R4との和よりも大きくなるように設定されている。これは、第1スイッチング素子22bおよび第2スイッチング素子28bの双方がオン状態となる場合の方が第1スイッチング素子22aおよび第2スイッチング素子28aの双方がオン状態となる場合よりもゲートの充電速度を大きくするための設定である。

【0113】

図13に、本実施形態にかかるパワースイッチング素子Swの駆動処理を示す。詳しくは、図13(a)に、ゲート電圧Vgeの推移を示し、図13(b)に、第1スイッチング素子22aの操作状態の推移を示し、図13(c)に、第2スイッチング素子28aの操作状態の推移を示し、図13(d)に、第1スイッチング素子22bの操作状態の推移を示し、図13(e)に、第2スイッチング素子28bの操作状態の推移を示す。

【0114】

図示されるように、操作信号gがオン操作指令に切り替えられると、第1スイッチング素子22bおよび第2スイッチング素子28bの双方がオン状態とされることで、ゲート電圧Vgeは、迅速に、第1抵抗体24bおよび第2抵抗体26bによる電圧Vcの分圧値まで上昇する。そして、ゲート電圧Vgeがこの分圧値に収束した後、第1スイッチング素子22bおよび第2スイッチング素子28bの双方のオン状態から第1スイッチング素子22aおよび第2スイッチング素子28aの双方のオン状態に切り替えられる。これにより、ゲートの充電速度を低下させた状態でミラー期間に移行させる。そして、ミラー期間の終了後、第1スイッチング素子22aがオンかつ第2スイッチング素子28aがオフとなる状態に切り替える。

【0115】

なお、第1スイッチング素子22bおよび第2スイッチング素子28bの双方のオン状態からこれら双方のオフ状態への切り替えは、上記遅延回路40と同様の構成を有する遅延回路の遅延信号に基づき行なえばよい。また、第1スイッチング素子22aおよび第2スイッチング素子28aの双方のオン状態への切り替えも、この遅延信号に基づき行なうことができる。さらに、第1スイッチング素子22aがオンかつ第2スイッチング素子28aがオフとなる状態への切り替えは、上記第1の実施形態の遅延回路40を用いて行なうことができる。

【0116】

以上説明した本実施形態によれば、先の第1の実施形態の上記(1)、(2)、(4)〜(9)の各効果に加えて、更に以下の効果が得られるようになる。

【0117】

(16)第1抵抗体24aおよび第2抵抗体26aによる電圧Vcの分圧値「Vc・R2/(R1+R2)」が閾値電圧Vthより大きく且つ、第1抵抗体24bおよび第2抵抗体26bによる電圧Vcの分圧値「Vc・R4/(R3+R4)」が閾値電圧Vthよりも小さくして且つ、「R1+R2>R3+R4」とした。これにより、上記分圧値「Vc・R4/(R3+R4)」までゲート電圧Vgeを迅速に上昇させることができる。特に、この分圧値が、パワースイッチング素子Swがオン状態に切り替わる閾値電圧Vthよりも低いため、スイッチング状態の切替速度を上昇させつつもサージの増大を好適に回避することができる。

【0118】

(第8の実施形態)

以下、第8の実施形態について、先の第1の実施形態との相違点を中心に図面を参照しつつ説明する。

【0119】

図14に、本実施形態にかかるドライブユニットDUの回路構成を示す。なお、図14において、先の図2に示した部材に対応する部材については、便宜上同一の符号を付している。

【0120】

図示されるように、本実施形態では、第2抵抗体26にコンデンサ70を並列接続する。これにより、第1スイッチング素子22および第2スイッチング素子28の双方のオン状態時において、ゲート電圧Vgeの上昇速度をコンデンサ70の静電容量C1によって制御することができる。このため、第1抵抗体24の抵抗値R1を十分に小さい値に設定することができる。

【0121】

図15に、本実施形態にかかるパワースイッチング素子Swの駆動処理を示す。なお、図15(a)〜図15(c)は、先の図2(a)〜図2(c)に対応している。

【0122】

図示されるように、第1スイッチング素子22および第2スイッチング素子28の双方のオン状態から第1スイッチング素子22がオン且つ第2スイッチング素子28がオフとなる状態に切り替えることで、ゲート電圧Vgeを電圧Vcに急上昇させることができる。そして、この際の上昇速度を、第1スイッチング素子22および第2スイッチング素子28の双方のオン状態となる際のゲート電圧Vgeの上昇速度と比較して十分に大きくすることができる。このため、ミラー期間等におけるゲート電圧Vgeの上昇速度を抑制することによりサージを抑制しつつ、ミラー期間終了後におけるゲート電圧Vgeの上昇速度を大きくすることにより損失を低減することができる。

【0123】

以上説明した本実施形態によれば、先の第1の実施形態の上記(1)、(2)、(4)〜(9)の各効果に加えて、更に以下の効果が得られるようになる。

【0124】

(17)第2抵抗体26にコンデンサ70を並列接続した。これにより、コンデンサ70によって第1スイッチング素子22および第2スイッチング素子28の双方のオン状態となる際のゲート電圧Vgeの上昇速度を制限しつつも、第1抵抗体24の抵抗値を極力小さくして第1スイッチング素子22がオン且つ第2スイッチング素子28がオフとなる状態におけるゲート電圧Vgeの上昇速度を十分大きくすることができる。

【0125】

(第9の実施形態)

以下、第9の実施形態について、先の第8の実施形態との相違点を中心に図面を参照しつつ説明する。

【0126】

図16に、本実施形態にかかるドライブユニットDUの回路構成を示す。なお、図16において、先の図14に示した部材に対応する部材については、便宜上同一の符号を付している。

【0127】

図示されるように、本実施形態では、第1抵抗体24にコンデンサ72を並列接続する。ここで、コンデンサ70、72の静電容量C1,C2は、コンデンサ70,72による電圧Vcの分圧値「Vc・C2/(C1+C2)」がパワースイッチング素子Swをオン状態とする閾値電圧Vthよりも低くなるように設定している。

【0128】

図17に、本実施形態にかかるパワースイッチング素子Swの駆動処理を示す。なお、図17(a)〜図17(c)は、先の図2(a)〜図2(c)に対応している。

【0129】

図示されるように、操作信号gがオン操作指令となり第1スイッチング素子22および第2スイッチング素子28の双方がオン状態とされることで、ゲート電圧Vgeは、コンデンサ70,72による上記分圧値まで急速に上昇する。その後、第1抵抗体24および第2抵抗体26による分圧値まで上昇するが、その速度は、上記第8の実施形態と同様、コンデンサ70の静電容量等によって制限される。このため、ミラー期間におけるゲートの充電速度を制限することができる。そして、第1スイッチング素子22および第2スイッチング素子28の双方のオン状態から第1スイッチング素子22がオン且つ第2スイッチング素子28がオフとなる状態に切り替えることで、ゲート電圧Vgeを電圧Vcに急上昇させることができる。

【0130】

以上説明した本実施形態によれば、先の第8の実施形態の上記各効果に加えて、更に以下の効果が得られるようになる。

【0131】

(18)第1抵抗体24にコンデンサ72を並列接続して且つ第2抵抗体26にコンデンサ70を並列接続し、これらコンデンサ70,72による電圧Vcの分圧値を閾値電圧Vthよりも小さく設定した。これにより、操作信号gがオン操作指令に切り替わってからミラー期間となるまでの時間を短縮することができる。

【0132】

(第10の実施形態)

以下、第10の実施形態について、先の第1の実施形態との相違点を中心に図面を参照しつつ説明する。

【0133】

本実施形態では、パワースイッチング素子Swをオフする際にゲート印加電圧を2段階に変化させるために先の図2に示した第1スイッチング素子22、第1抵抗体24、第2抵抗体26、第2スイッチング素子28を利用する。ただし、第1抵抗体24および第2抵抗体26による電圧Vcの分圧値は、パワースイッチング素子Swをオフ状態に切り替える閾値電圧Vthよりも低く設定する。これは、パワースイッチング素子Swがオフするまでの期間においてパワースイッチング素子Swを流れる電流の変化速度が過度に大きくならないようにするための設定である。

【0134】

図18に、本実施形態にかかるパワースイッチング素子Swの駆動処理を示す。なお、図18(a)〜図18(c)は、先の図2(a)〜図2(c)に対応している。

【0135】

図示されるように、本実施形態では、操作信号gがオフ操作指令に切り替わることで、第1スイッチング素子22および第2スイッチング素子28の双方をオン状態とし、ゲート印加電圧を、第1抵抗体24および第2抵抗体26による電圧Vcの分圧値「Vc・R2/(R1+R2)」とする。これにより、ゲート電圧Vgeが低下し、ミラー期間を経て上記分圧値に収束する。その後、第1スイッチング素子22がオフ且つ第2スイッチング素子28がオンとなる状態に移行させることで、ゲート電圧Vgeをゼロまで低下させる。

【0136】

(その他の実施形態)

なお、上記各実施形態は、以下のように変更して実施してもよい。

<遅延信号生成手段について>

遅延信号生成手段としては、操作信号gを入力とし、これを遅延させる手段に限らない。例えば、操作信号gがオン指令信号となることをトリガとして計時動作を行うタイマを備え、タイマの値が閾値を超えるタイミングを指定するものであってもよい。

<切替手段について>

切替手段としては、遅延回路40を備えて構成されるものに限らない。例えば、先の第4、5の実施形態において遅延回路40を省いて構成してもよい。また、先の第6の実施形態において、遅延回路40を省き、操作信号gがオン指令信号となってからコンパレータ60の出力が2度論理「H」となることに基づき、ミラー期間の終了を検出する手段を構成してもよい。

<過電流判断手段について>

過電流判断手段としては、パワースイッチング素子Swのセンス端子Stの微少電流によるシャント抵抗の電圧降下量と基準電圧Vrefとを比較することで過電流の有無を判断する手段に限らない。例えば、パワースイッチング素子Swの入力端子および出力端子間の電圧降下量をパワースイッチング素子Swを流れる電流と相関を有するパラメータとして用いて、この値と閾値とを比較することで過電流の有無を判断する手段であってもよい。

<導通制御端子と高電圧印加手段とを接続する第1経路について>

第1経路としては、単一のスイッチング素子によって開閉される1つの経路、または2つのスイッチング素子のそれぞれによって開閉される合計2つの経路に限らない。例えば3つ以上のスイッチング素子のそれぞれによって開閉される合計3つ以上の経路であってもよい。ここで、例えばオン状態への切り替えに3つ以上の経路を利用する場合には、ミラー期間の終了後において、複数の経路を利用して導通制御端子に高電圧印加手段の電圧を印加すればよい。

【0137】

また、第1経路としては、受動素子として抵抗体やコンデンサを備えるものに限らない。例えばインダクタをさらに備えるものであってもよい。

<導通制御端子と低電圧印加手段とを接続する第2経路について>

第2経路としては、単一のスイッチング素子によって開閉される1つの経路、または2つのスイッチング素子のそれぞれによって開閉される合計2つの経路に限らない。例えば3つ以上のスイッチング素子のそれぞれによって開閉される合計3つ以上の経路であってもよい。ここで、例えばオフ状態への切り替えに3つ以上の経路を用いる場合には、ミラー期間の終了後において、複数の経路を用いて導通制御端子に低電圧印加手段の電圧を印加すればよい。また、例えばオン状態への切り替えに第1経路および第2経路としてそれぞれ3つ以上の経路を利用する場合には、ミラー期間前において、複数の経路を利用して導通制御端子に高電圧印加手段の電圧を印加すればよい。具体的には、例えば先の第7の実施形態において、高電圧経路Lhbおよび低電圧経路Llbの直列接続体を1つ追加し、オン指令タイミングにおいてこれら一対の直列接続体をオンし、その後、高電圧経路Lhaおよび低電圧経路Llaを用いればよい。これにより、ミラー期間に移行する前までの期間をいっそう短縮することができる。

【0138】

また、第2経路としては、受動素子として抵抗体やコンデンサを備えるものに限らない。例えばインダクタをさらに備えるものであってもよい。

<第1経路と第2経路との共通部分について>

第1経路と第2経路との共通部分(図1の共通経路Lg)に、ゲート抵抗を備えてもよい。また、共通部分を有しなくてもよい。

<オフ状態への切り替えについて>

オフ状態への切り替えについては、上記第10の実施形態にて例示したものに限らない。例えば、上記第2〜第9の実施形態の構成を、パワースイッチング素子Swのオフ状態への切り替え処理用に設定してもよい。

<駆動対象となるスイッチング素子について>

駆動対象となるIGBTとしては、これに逆並列に接続される態様にてこれと同一半導体基板に併設されたフリーホイールダイオードが設けられた半導体デバイスを構成するものに限らない。また、IGBTにも限らず、例えば、スーパージャンクションMOS電界効果トランジスタや、シリコンカーバイト(SiC)にて構成されるMOS電界効果トランジスタ等の電界効果トランジスタであってもよい。なお、MOS電界効果トランジスタを駆動対象として採用する場合、Nチャネルのトランジスタに限らず、Pチャネルのトランジスタであってもよい。

【0139】

また、駆動対象となるパワースイッチング素子としては、インバータIVやコンバータCVを構成するものにも限らない。この際、高電位側のパワースイッチング素子Swpおよび低電位側のパワースイッチング素子Swnの直列接続体を備える構成にも限らない。

【符号の説明】

【0140】

22…第1スイッチング素子、24…第1抵抗体、26…第2抵抗体、28…第2スイッチング素子、Sw…パワースイッチング素子。

【技術分野】

【0001】

本発明は、電圧制御形のスイッチング素子の導通制御端子を高電圧印加手段に接続して且つ受動素子および第1開閉手段を備える第1経路と、前記導通制御端子を低電圧印加手段に接続して且つ受動素子および第2開閉手段を備える第2経路とを備え、前記第1開閉手段および前記第2開閉手段を操作することで前記スイッチング素子を駆動するスイッチング素子の駆動装置に関する。

【背景技術】

【0002】

この種の駆動装置としては、例えば下記特許文献1に見られるように、インバータを構成するIGBTをオンさせるべくゲートに印加するための電圧を生成する一対の電源を備えるものも提案されている。これにより、IGBTのオン操作に際しては、まず一対の電源のうち低電圧のものを用いてゲートに電圧を印加し、IGBTをオンさせる。次に、一対の電源のうち高電圧のものを用いてゲートの印加電圧を上昇させる。これにより、上下アームの短絡が生じる場合に、IGBTのオン操作に伴って過電流が流れることを好適に回避することができる。また、過電流が流れるおそれがない場合には、ゲート電圧の上昇によって導通損失を迅速に低減させることができる。

【先行技術文献】

【特許文献】

【0003】

【特許文献1】特開2009−71956号公報

【発明の概要】

【発明が解決しようとする課題】

【0004】

ただし、上記装置の場合、一対の電源のうち電圧の高い方を用いてゲートに電圧を印加する際に電圧の高い方から低い方に電流が流れるという問題がある。これに対し、上記装置では、ダイオードを備えることで上記電流の流れを回避するようにしているが、この場合、ダイオードの電圧降下量の変動によって、ゲート電圧が安定しないという問題がある。さらに、上記装置の場合、一対の電源を備える必要があり、回路規模の増大やコストアップを招くおそれもある。

【0005】

本発明は、上記課題を解決するためになされたものであり、その目的は、電圧制御形のスイッチング素子の導通制御端子を高電圧印加手段に接続して且つ受動素子および第1開閉手段を備える第1経路と、前記導通制御端子を低電圧印加手段に接続して且つ受動素子および第2開閉手段を備える第2経路とを備え、前記第1開閉手段および前記第2開閉手段を操作することで前記スイッチング素子を駆動するに際し、導通制御端子への印加電圧をより適切に可変設定することのできるスイッチング素子の駆動装置を提供することにある。

【課題を解決するための手段】

【0006】

以下、上記課題を解決するための手段、およびその作用効果について記載する。

【0007】

請求項1記載の発明は、電圧制御形のスイッチング素子の導通制御端子を高電圧印加手段に接続して且つ受動素子および第1開閉手段を備える第1経路と、前記導通制御端子を低電圧印加手段に接続して且つ受動素子および第2開閉手段を備える第2経路とを備え、前記第1開閉手段および前記第2開閉手段を操作することで前記スイッチング素子を駆動するスイッチング素子の駆動装置において、前記スイッチング素子のスイッチング状態の切り替えに際し、前記第1開閉手段および前記第2開閉手段の双方の閉状態からいずれか一方が閉且つ他方が開となる状態へと切り替える切替手段を備え、前記いずれか一方は、前記高電圧印加手段および前記低電圧印加手段のうちの前記スイッチング状態の切り替えによって実現されるスイッチング状態とするための電圧を前記導通制御端子に印加する方と前記導通制御端子とを接続するための手段であることを特徴とする。

【0008】

上記発明では、第1開閉手段および第2開閉手段の双方の閉状態といずれか一方が閉且つ他方が開となる状態とで、導通制御端子に対する印加電圧を相違させることができる。このため、切替手段による処理によって、導通制御端子への印加電圧をより適切に可変設定することができる。

【0009】

請求項2記載の発明は、請求項1記載の発明において、前記第1開閉手段および前記第2開閉手段の双方が閉状態とされる際の前記導通制御端子の電圧の収束値が、前記スイッチング素子のミラー電圧よりも前記高電圧印加手段の印加電圧および前記低電圧印加手段の印加電圧のうちの前記スイッチング状態の切り替えによって実現されるスイッチング状態とするための電圧側にあることを特徴とする。

【0010】

上記発明では、スイッチング状態の切り替えに際し、ミラー期間に移行した後と前とで、導通制御端子に印加する電圧を相違させることが可能となる。

【0011】

請求項3記載の発明は、請求項1または2記載の発明において、前記切替手段は、前記スイッチング状態をオフ状態からオン状態に切り替える際に前記切り替えを行うものであり、前記第1開閉手段および前記第2開閉手段の双方が閉状態とされる際の前記導通制御端子の電圧の収束値が前記スイッチング素子のミラー電圧よりも前記オン状態時の電圧側にあることを特徴とする。

【0012】

上記発明では、スイッチング状態をオン状態に切り替えるに際し、ミラー期間に移行した後と前とで、導通制御端子に印加する電圧を相違させることが可能となる。

【0013】

請求項4記載の発明は、請求項3記載の発明において、前記切替手段は、前記スイッチング素子のミラー期間以降に前記切り替えを行うことを特徴とする。

【0014】

請求項5記載の発明は、請求項1〜4のいずれか1項に記載の発明において、前記切替手段は、前記スイッチング素子の操作信号がスイッチング状態の切り替えを指示するタイミングに対して遅延したタイミングを指示する遅延信号を生成する遅延信号生成手段を備え、前記遅延信号に基づき前記切り替えを行うことを特徴とする。

【0015】

上記発明では、切り替え処理を行うべく遅延信号を参照することで、切り替え処理を適切なタイミングにて行うことができる。

【0016】

請求項6記載の発明は、請求項5記載の発明において、前記遅延信号生成手段は、前記操作信号を入力として前記遅延信号を生成することを特徴とする。

【0017】

上記発明では、遅延信号を適切に生成することができる。

【0018】

請求項7記載の発明は、請求項6記載の発明において、前記切替手段は、前記スイッチング状態をオフ状態からオン状態に切り替える際に前記第1開閉手段および前記第2開閉手段の双方の閉状態から前記第1開閉手段が閉且つ前記第2開閉手段が開となる状態への切り替えを行うものであり、前記スイッチング素子を流れる電流が過度に大きくなるか否かを判断する過電流判断手段を更に備え、前記遅延信号は、前記スイッチング素子をオン状態に切り替えるに際しての前記遅延したタイミングを指示するものであり、前記遅延信号による遅延時間は、前記過電流判断手段による過電流の判断に要する時間以上に設定されることを特徴とする。

【0019】

スイッチング素子の出力端子が低電位の部材と異常な低インピーダンスで接続される場合等にあっては、スイッチング素子をオンした瞬間に過電流が流れる。ただし、この過電流が流れたことが過電流判断手段によって判断されるまでには、ある程度の処理時間(過電流判断手段による過電流の判断に要する時間)が必要となる。そして、この判断以前において第1開閉手段が閉状態であって且つ第2開閉手段が開状態となる状態に切り替えてしまうと、スイッチング素子を流れる電流が更に増大し、スイッチング素子の信頼性を低下させるおそれがある。上記発明では、この点に鑑み、遅延信号の遅延時間を上記設定とする。

【0020】

請求項8記載の発明は、請求項7記載の発明において、前記過電流判断手段により前記スイッチング素子を流れる電流が過度に大きくなると判断される場合、前記切替手段による前記切り替えを禁止する禁止手段を更に備えることを特徴とする。

【0021】

上記発明では、過電流が流れる場合に切り替えを禁止することで、スイッチング素子を流れる電流が更に増加することを回避することができる。

【0022】

請求項9記載の発明は、請求項5〜8のいずれか1項に記載の発明において、前記遅延信号は、前記スイッチング素子をオン状態に切り替えるに際しての前記遅延したタイミングを指示するものであり、前記遅延したタイミングまでの遅延時間は、前記スイッチング素子のオン状態への切替指令タイミングから前記スイッチング素子のミラー期間のうちの該ミラー期間の終了前のタイミングとなるまでに要すると想定される時間に設定されることを特徴とする。

【0023】

上記発明によれば、スイッチング素子の損失を低減することができる。

【0024】

請求項10記載の発明は、請求項5〜8のいずれか1項に記載の発明において、前記遅延信号は、前記スイッチング素子をオン状態に切り替えるに際しての前記遅延したタイミングを指示するものであり、前記遅延したタイミングまでの遅延時間は、前記スイッチング素子のオン状態への切替指令タイミングから前記スイッチング素子のミラー期間の終了タイミングとなるまでに要すると想定される時間に設定されることを特徴とする。

【0025】

スイッチング素子を流れる電流の変化速度が大きい場合、電流の流通経路に存在するインダクタ(寄生インダクタ等)によって、大きなサージが生じることとなる。このサージを低減する上では、ミラー期間の終了までにおける導通制御端子の電圧の変化速度を抑制することが望ましい。ただし、導通制御端子の電圧の変化速度が小さい場合には、スイッチング状態の切り替えに際しての損失が増大する。上記発明では、この点に鑑み、スイッチング素子のミラー期間の終了とともに切り替え処理を行うことで、サージを抑制しつつも損失を極力低減することができる。

【0026】

請求項11記載の発明は、請求項1〜4のいずれか1項に記載の発明において、前記切替手段は、前記スイッチング素子のミラー期間の終了を検出する終了検出手段を備え、前記ミラー期間の終了が検出されることで前記切り替えを行うことを特徴とする。

【0027】

スイッチング素子を流れる電流の変化速度が大きい場合、電流の流通経路に存在するインダクタ(寄生インダクタ等)によって、大きなサージが生じることとなる。このサージを低減する上では、ミラー期間の終了までにおける導通制御端子の電圧の変化速度を抑制することが望ましい。ただし、導通制御端子の電圧の変化速度が小さい場合には、スイッチング状態の切り替えに際しての損失が増大する。上記発明では、この点に鑑み、スイッチング素子のミラー期間の終了が検出されることで切り替え処理を行うことで、サージを抑制しつつも損失を極力低減することが可能となる。

【0028】

請求項12記載の発明は、請求項5〜10のいずれか1項に記載の発明において、前記切替手段は、前記スイッチング素子のミラー期間の終了を検出する終了検出手段を備え、前記遅延信号によって規定された遅延時間が経過して且つ前記ミラー期間の終了が検出されることで前記切り替えを行うことを特徴とする。

【0029】

スイッチング素子を流れる電流の変化速度が大きい場合、電流の流通経路に存在するインダクタ(寄生インダクタ等)によって、大きなサージが生じることとなる。このサージを低減する上では、ミラー期間の終了までにおける導通制御端子の電圧の変化速度を抑制することが望ましい。ただし、導通制御端子の電圧の変化速度が小さい場合には、スイッチング状態の切り替えに際しての損失が増大する。上記発明では、この点に鑑み、スイッチング素子のミラー期間の終了が検出されることに基づき切り替え処理を行うことで、サージを抑制しつつも損失を極力低減することができる。

【0030】

請求項13記載の発明は、請求項11または12記載の発明において、前記終了検出手段は、前記導通制御端子の電圧と終了判定電圧とを比較する比較手段を備え、該比較手段の比較結果を前記ミラー期間の終了の有無の検出結果を示す信号とすることを特徴とする。

【0031】

請求項14記載の発明は、請求項13記載の発明において、前記スイッチング素子の温度を検出する温度検出手段を備え、前記終了検出手段は、前記温度検出手段によって検出される温度に応じて前記終了判定電圧を可変設定することを特徴とする。

【0032】

ミラー期間における導通制御端子の電圧は、温度依存性を有する。上記発明では、この点に鑑み、終了判定電圧を、現在の温度においてミラー期間の電圧として想定される値に応じて設定することが可能となる。

【0033】

請求項15記載の発明は、請求項11または12記載の発明において、前記終了検出手段は、前記導通制御端子の電圧の変化を検出する手段を備え、該変化が検出されることに基づき前記ミラー期間の終了を検出することを特徴とする。

【0034】

ミラー期間においては、導通制御端子の電圧の変化速度が大きく低下する。このため、ミラー期間の終了時には、導通制御端子の電圧の変化速度が大きく増大することとなる。上記発明では、この点に着目し、ミラー期間の終了を検出する。

【0035】

請求項16記載の発明は、請求項1〜15のいずれか1項に記載の発明において、前記第1経路が備える受動素子は、抵抗体を含むことを特徴とする。

【0036】

請求項17記載の発明は、請求項1〜16のいずれか1項に記載の発明において、前記第2経路が備える受動素子は、抵抗体を含むことを特徴とする。

【0037】

請求項18記載の発明は、請求項17記載の発明において、前記第1経路が備える受動素子は、抵抗体からなり、前記第2経路が備える受動素子は、抵抗体からなることを特徴とする。

【0038】

上記発明では、第1経路および第2経路を簡素な構成とすることができる。

【0039】

請求項19記載の発明は、請求項17記載の発明において、前記第1経路が備える受動素子は、抵抗体からなり、前記第2経路が備える受動素子は、抵抗体とコンデンサとの並列接続体からなることを特徴とする。

【0040】

上記発明において、前記高電圧印加手段と前記導通制御端子との接続によってオン状態とされて且つスイッチング状態をオフ状態からオン状態へと切り替えるに際して切替手段を用いる場合、第1開閉手段および第2開閉手段の双方が閉状態である際の導通制御端子の電圧の変化速度はコンデンサによって制限される。このため、第1経路が備える抵抗体の抵抗値を極力小さくすることができ、ひいては第1開閉手段が閉状態であって且つ第2開閉手段が開状態とされる状態に切り替えられた際の導通制御端子の電圧の上昇速度を極力大きくすることができる。

【0041】

請求項20記載の発明は、請求項1〜15のいずれか1項に記載の発明において、前記第1経路が備える受動素子は、抵抗体とコンデンサとの並列接続体からなり、前記第2経路が備える受動素子は、抵抗体とコンデンサとの並列接続体からなることを特徴とする。

【0042】

請求項21記載の発明は、請求項20記載の発明において、前記スイッチング素子は、前記高電圧印加手段と前記導通制御端子との接続によってオン状態とされるものであり、前記切替手段は、前記スイッチング状態をオフ状態からオン状態に切り替える際に前記切り替えを行うものであり、前記第1経路のコンデンサと前記第2経路のコンデンサとの直列接続体によって前記高電圧印加手段と前記低電圧印加手段との間の電圧を分圧した値が前記スイッチング素子のミラー電圧よりも低く、且つ前記第1経路の抵抗体と前記第2経路の抵抗体とによって前記高電圧印加手段と前記低電圧印加手段との間の電圧を分圧した値が前記スイッチング素子のミラー電圧よりも高いことを特徴とする。

【0043】

上記発明では、ミラー電圧となるまでに要する時間を低減することができる。

【0044】

請求項22記載の発明は、請求項1記載の発明において、前記切替手段は、前記スイッチング状態をオン状態からオフ状態に切り替える際に前記切り替えを行うものであり、前記第1開閉手段および前記第2開閉手段の双方が閉状態とされる際の前記導通制御端子の電圧の収束値が前記スイッチング素子のミラー電圧よりも前記オフ状態とする電圧側であることを特徴とする。

【0045】

上記発明では、スイッチング状態をオフ状態に切り替えるに際し、ミラー期間を移行した後と前とで、導通制御端子に印加する電圧を相違させることが可能となる。

【0046】

請求項23記載の発明は、請求項22記載の発明において、前記切替手段は、前記スイッチング素子のミラー期間以降に前記切り替えを行うことを特徴とする。

【0047】

請求項24記載の発明は、請求項1〜23のいずれか1項に記載の発明において、前記スイッチング素子は、高電位側のスイッチング素子および低電位側のスイッチング素子の直列接続体を備える電力変換回路における前記直列接続体を構成するスイッチング素子であることを特徴とする。

【0048】

上記発明では、高電位側のスイッチング素子および低電位側のスイッチング素子の双方がオン状態となる事態が生じた場合に、これらに過度の電流が流れるおそれがある。ただし、この場合であっても、第1開閉手段および第2開閉手段の双方がオン状態となる状態であれば、電流量を制限することができる。このため、上記発明は、切替手段の利用価値が特に大きい。

【図面の簡単な説明】

【0049】

【図1】第1の実施形態にかかるシステム構成図。

【図2】同実施形態にかかるドライブユニットの回路構成を示す回路図。

【図3】同実施形態にかかる遅延回路の回路構成例を示す回路図。

【図4】同実施形態にかかるパワースイッチング素子のオン操作態様を示すタイムチャート。

【図5】第2の実施形態にかかるパワースイッチング素子のオン操作態様を示すタイムチャート。

【図6】第3の実施形態にかかるパワースイッチング素子のオン操作態様を示すタイムチャート。

【図7】第4の実施形態にかかるドライブユニットの回路構成を示す回路図。

【図8】同実施形態にかかるパワースイッチング素子のオン操作態様を示すタイムチャート。

【図9】第5の実施形態にかかるドライブユニットの回路構成を示す回路図。

【図10】第6の実施形態にかかるドライブユニットの回路構成を示す回路図。

【図11】同実施形態にかかるパワースイッチング素子のオン操作態様を示すタイムチャート。

【図12】第7の実施形態にかかるドライブユニットの回路構成を示す回路図。

【図13】同実施形態にかかるパワースイッチング素子のオン操作態様を示すタイムチャート。

【図14】第8の実施形態にかかるドライブユニットの回路構成を示す回路図。

【図15】同実施形態にかかるパワースイッチング素子のオン操作態様を示すタイムチャート。

【図16】第9の実施形態にかかるドライブユニットの回路構成を示す回路図。

【図17】同実施形態にかかるパワースイッチング素子のオン操作態様を示すタイムチャート。

【図18】第10の同実施形態にかかるパワースイッチング素子のオン操作態様を示すタイムチャート。

【発明を実施するための形態】

【0050】

(第1の実施形態)

以下、本発明にかかるパワースイッチング素子の駆動装置をハイブリッド車に適用した第1の実施形態について、図面を参照しつつ説明する。

【0051】

図1に、本実施形態のシステム構成を示す。図示されるように、車載主機としてのモータジェネレータ10は、インバータIVおよびコンバータCVを介して高電圧バッテリ12に接続されている。インバータIVは、高電位側のパワースイッチング素子Swpおよび低電位側のパワースイッチング素子Swnの直列接続体が3つ並列接続されて構成されている。そして、これら各パワースイッチング素子Swpおよびパワースイッチング素子Swnの接続点が、モータジェネレータ10の各相にそれぞれ接続されている。また、コンバータCVは、コンデンサCと、高電位側のパワースイッチング素子Swpおよび低電位側のパワースイッチング素子Swnの直列接続体と、パワースイッチング素子Swpおよびパワースイッチング素子Swnの接続点と高電圧バッテリ12とを接続するリアクトルLとを備えている。

【0052】

上記高電位側のパワースイッチング素子Swpおよび低電位側のパワースイッチング素子Swnのそれぞれの入出力端子間(コレクタおよびエミッタ間)には、高電位側のフリーホイールダイオードFDpおよび低電位側のフリーホイールダイオードFDnのカソードおよびアノードが接続されている。特に、本実施形態では、高電位側のパワースイッチング素子Swpおよび高電位側のフリーホイールダイオードFDpは互いに同一の半導体基板に隣接して形成されており、低電位側のパワースイッチング素子Swnおよび低電位側のフリーホイールダイオードFDnは互いに同一の半導体基板に隣接して形成されている。こうした半導体デバイスとしては、例えば「モータ制御用RC−IGBT 高橋秀樹、他2名 7(315) 三菱電機技報、VOl81、NO.5,2007」に記載されているものがある。

【0053】

上記インバータIVを構成するパワースイッチング素子Swp,Swnの導通制御端子(ゲート)には、いずれもドライブユニットDUが接続されている。これにより、パワースイッチング素子Swp,Swnは、ドライブユニットDUを介して、低電圧バッテリ14を電源とする制御装置16によって駆動される。制御装置16は、図示しない各種センサの検出値等に基づき、インバータIVのU相、V相、およびW相のそれぞれについてのパワースイッチング素子Swpを操作する操作信号gup,gvp,gwpと、パワースイッチング素子Swnを操作する操作信号gun,gvn,gwnとを生成し出力する。また、コンバータCVのパワースイッチング素子Swp、Swnを操作する操作信号gcp,gcnを生成し出力する。これにより、パワースイッチング素子Swp,Swnは、ドライブユニットDUを介して制御装置16により操作される。

【0054】

なお、インバータIVやコンバータCVを備える高電圧システムと、制御装置16を備える低電圧システムとは、図示しないフォトカプラ等の絶縁手段によって絶縁されており、上記操作信号は、絶縁手段を介して高電圧システムに出力される。

【0055】

上記パワースイッチング素子Swp,Swnは、いずれも絶縁ゲートバイポーラトランジスタ(IGBT)にて構成されている。また、パワースイッチング素子Swp,Swnは、その入力端子および出力端子間に流れる電流と相関を有する微少電流を出力するセンス端子Stを備えている。

【0056】

図2に、本実施形態にかかるドライブユニットDUの回路構成を示す。なお、以下では、パワースイッチング素子Swp、Swnを総括する場合、パワースイッチング素子Swと記載し、フリーホイールダイオードFDp,FDnを総括する場合、フリーホイールダイオードFDと記載する。また、上記操作信号gup,gvp,gwp,gcp,gun,gvn,gwn,gcnを総括する場合、操作信号gと記載する。

【0057】

図示されるように、ドライブユニットDUは、パワースイッチング素子Swをオンさせるべく出力端子(エミッタ)よりも所定の電圧Vcだけ高い高電圧を印加するための電源20を備えている。なお、図では、電源20をバッテリの記号にて示してあるが、実際には、この電源20は、フローティング電源を構成するコンデンサ等であってもよい。電源20の高電圧は、第1スイッチング素子22および線形素子としての第1抵抗体24を備える高電圧経路Lhおよび共通経路Lgを介してパワースイッチング素子Swの導通制御端子(ゲート)に印加される。また、ゲートの電荷は、共通経路Lgと、線形素子としての第2抵抗体26および第2スイッチング素子28を備える低電圧経路Llを介して放電される。ここで、ゲートは、共通経路Lgおよび低電圧経路Llを介してパワースイッチング素子Swのエミッタに接続されている。

【0058】

一方、制御部30は、操作信号gを入力とし、これに基づき第1スイッチング素子22および第2スイッチング素子28を操作することで、パワースイッチング素子Swを駆動する。詳しくは、本実施形態では、操作信号gがオン操作指令となることで、まず第1スイッチング素子22および第2スイッチング素子28の双方をオン操作することで、パワースイッチング素子Swを充電した後、所定の遅延時間が経過することで、第2スイッチング素子28をオフする。これにより、スイッチング状態のオフ状態からオン状態への切り替え途中においてゲート印加電圧を上昇させることができる。この所定の遅延時間は、遅延回路40によって設定される。遅延回路40は、操作信号gを入力とし、操作信号gによってオン操作への切り替え指示がなされるタイミングに対して所定の遅延時間遅延したタイミングを指示する遅延信号DLを生成する回路である。この回路としては、例えば図3に示すものとすればよい。

【0059】

図3(a)は、抵抗体40bおよびコンデンサ40aによって構成される遅延回路であり、入力信号としての操作信号gが論理「H」となることでコンデンサ40aの電圧が漸増し、論理「H」に対応する電圧値へと所定の遅延時間が経過することで移行する。また、図3(b)は、図3(a)の構成において、出力側から入力側へと進む方向を順方向とするダイオード40cが抵抗体40bに並列接続されるものである。この構成によれば、操作信号gが論理「H」に変化してから遅延回路40の出力信号が論理「H」に変化するまでには遅延が生じるものの、操作信号gが論理「L」に変化してから遅延回路40の出力信号が論理「L」に変化するまでには殆ど遅延が生じない。また、図3(c)は、抵抗体40bおよびコンデンサ40aの直列接続体の両端に電源40fの電圧を印加し、上記コンデンサ40aを迂回するようにスイッチング素子40dを設けて且つ、そのゲートにインバータ40eによる操作信号gの論理反転信号を印加するものである。この構成によっても、操作信号gが論理「H」に変化してから遅延回路40の出力信号が論理「H」に変化するまでには遅延が生じるものの、操作信号gが論理「L」に変化してから遅延回路40の出力信号が論理「L」に変化するまでには殆ど遅延が生じない。

【0060】

上記遅延回路40の遅延時間は、スイッチング状態のオフ状態からオン状態への移行期間のうちゲート電圧の上昇速度が一旦大きく低下する期間(ミラー期間)が終了するまでに要する時間より長く設定される。ただし、本実施形態では、遅延時間の経過後であっても、パワースイッチング素子Swに過電流が流れる場合には、第2スイッチング素子28をオフ操作しない。これを実現する構成は以下である。

【0061】

パワースイッチング素子Swのセンス端子Stとエミッタとの間には、抵抗体32,34の直列接続体が接続されており、その接続点には、コンパレータ36の非反転入力端子が接続されている。また、コンパレータ36の反転入力端子には、基準電源38の基準電圧Vrefが印加されている。ここで、基準電圧Vrefは、パワースイッチング素子Swに流れる電流が過度に大きいと判断される下限値(閾値電流)に応じて設定されるものである。これにより、コンパレータ36では、センス端子Stの出力電流による抵抗体32,34の電圧降下を利用して、パワースイッチング素子Swを流れる電流が閾値電流であるか否かを判断することができる。

【0062】

コンパレータ36の出力信号は、インバータ44によって論理反転された後、AND回路42に取り込まれる。AND回路42は、遅延回路40の出力する遅延信号DLと、インバータ44の出力する信号との論理積信号を生成し、制御部30に出力する。そして制御部30では、AND回路42の出力信号が論理「H」となることで第2スイッチング素子28をオフ操作する。これにより、制御部30では、操作信号gがオン操作を指令するタイミングから所定の遅延時間経過することと、パワースイッチング素子Swに閾値電流以上の電流が流れていないこととの論理積が真である場合に第2スイッチング素子28をオフ操作する。

【0063】

図4に、本実施形態にかかるパワースイッチング素子Swの駆動処理について、正常時の場合(ケース1)と過電流が検出される場合(ケース2)とを比較しつつ示す。詳しくは、図4(a)に、ゲート電圧Vgeの推移を示し、図4(b)に、第1スイッチング素子22の操作状態の推移を示し、図4(c)に、第2スイッチング素子28の操作状態の推移を示し、図4(d)に、コンパレータ36の出力信号の推移を示し、図4(e)に、遅延信号DLの推移を示す。

【0064】

図示されるように、操作信号gがオン操作指令に切り替わることで、第1スイッチング素子22および第2スイッチング素子28をオン操作する。これにより、ゲートの電圧は、第1抵抗体24および第2抵抗体26による電圧Vcの分圧値「R2・Vc/(R1+R2)」に収束する。この分圧値は、パワースイッチング素子Swがオン状態に切り替わる閾値電圧Vth以上に設定される。このため、ケース1の場合には、ゲート電圧が閾値電圧Vthに達することでミラー期間に移行し、ゲートの電圧の上昇速度がミラー期間以前と比較して一旦無視できるほど小さくなり、その後、ミラー期間の経過後において分圧値に収束する。その後、遅延時間Tdの経過に伴って、第2スイッチング素子28がオフ操作されることで、ゲート電圧Vgeは、電圧Vcまで上昇する。

【0065】

一方、ケース2の場合には、ゲート電圧Vgeは、上記分圧値まで一気に上昇する。そして場合、コンパレータ36の出力信号が論理「H」となり、過電流の検出がなされるため、遅延時間Tdが経過しても第2スイッチング素子28をオフ操作しない。なお、上記遅延時間Tdは、コンパレータ36を備えて構成される過電流判断手段による過電流の判断に要する時間Tiよりも長く設定される。また、過電流の判断のための閾値電流は、ゲート電圧が上記分圧値となる際にパワースイッチング素子Swを流れることのできる最大電流以下に設定される。

【0066】

これにより、過電流が流れる場合には、ゲート電圧を上記分圧値に制限することで、パワースイッチング素子Swに流れる電流を制限することができる。ちなみに、ゲート電圧が電圧Vcとなる場合にパワースイッチング素子Swに流すことのできる最大電流は、パワースイッチング素子Swの信頼性を維持できない大電流であり、特に上記閾値電流よりも十分に大きい。それにもかかわらずゲート印加電圧を電圧Vcまで上昇させるのは、パワースイッチング素子Swをオン状態とする際の導通損失がゲート電圧Vgeが大きいほど小さくなるためである。ただし、ゲート印加電圧を電圧Vcに一気に上昇させる場合には、過電流が流れる異常な状況下において、パワースイッチング素子Swに流れる電流が過度に大きくなる(ゲート電圧が電圧Vcとなる場合にパワースイッチング素子Swに流すことのできる最大電流となる)期間が存在する。これは、過電流判断手段の動作速度に限界があるためである。このため、パワースイッチング素子Swとして、過電流判断手段によって過電流が流れると判断され、フェールセーフ処理がなされるまでの期間、少なくとも上記大電流に耐えうるものを選択する必要が生じ、ひいてはパワースイッチング素子Swの大型化を招く。

【0067】

特に、パワースイッチング素子SwおよびフリーホイールダイオードFDが互いに同一の半導体基板に隣接して形成されるものにあっては、パワースイッチング素子Swの導通損失が大きくなりやすいため、エミッタおよびコレクタ間の厚さを低減することが望まれるが、この場合、熱に対する耐性が低下するため、パワースイッチング素子Swに流せる許容電流が低減する。このため、上記フェールセーフ処理がなされるまでの時間大電流に耐えうるものを選択する場合、パワースイッチング素子Swの表面積を大きくする要求が特に大きくなる。

【0068】

以上詳述した本実施形態によれば、以下の効果が得られるようになる。

【0069】

(1)パワースイッチング素子Swのオン状態への切り替えに際し、第1スイッチング素子22および第2スイッチング素子28の双方のオン状態から第1スイッチング素子22がオン且つ第2スイッチング素子28がオフとなる状態へと切り替えた。これにより、ゲート印加電圧を段階的に変化させることができる。特に、第1スイッチング素子22および第2スイッチング素子28の双方が閉状態となる期間におけるゲート電圧Vgeを、第1抵抗体24および第2抵抗体26の抵抗値の精度によって高精度に制御することができる。

【0070】

(2)第1スイッチング素子22および第2スイッチング素子28の双方をオン状態とする場合のゲート電圧Vgeの収束値を、パワースイッチング素子Swがオン状態となる電圧Vth(ミラー電圧)よりも高く設定した。これにより、スイッチング状態をオン状態に切り替えるに際し、ミラー期間に移行した後と前とで、ゲート印加電圧を相違させることが可能となる。

【0071】

(3)パワースイッチング素子Swのミラー期間以降に、第1スイッチング素子22および第2スイッチング素子28の双方のオン状態から第1スイッチング素子22がオン且つ第2スイッチング素子28がオフとなる状態へと切り替えた。これにより、スイッチング状態をオン状態に切り替えるに際し、ミラー期間に移行した後と前とで、ゲート印加電圧を相違させることが可能となる。

【0072】

(4)パワースイッチング素子Swの操作信号gがオン状態への切り替えを指示するタイミングに対して遅延したタイミングを指示する遅延信号DLを生成する遅延回路40を備え、遅延信号DLに基づき第1スイッチング素子22および第2スイッチング素子28の双方のオン状態から第1スイッチング素子22がオン且つ第2スイッチング素子28がオフとなる状態へと切り替えた。これにより、切り替え処理を適切なタイミングにて行うことができる。

【0073】

(5)遅延回路40を、操作信号gを入力として遅延信号DLを生成する回路とした。これにより、遅延信号DLを適切に生成することができる。

【0074】

(6)遅延信号DLによる遅延時間Tdを、過電流判断手段(コンパレータ36等)による過電流の判断に要する時間以上に設定した。これにより、過電流の有無の判断を待って、第1スイッチング素子22および第2スイッチング素子28の双方のオン状態から第1スイッチング素子22がオン且つ第2スイッチング素子28がオフとなる状態へと切り替えることができる。

【0075】

(7)過電流が検出される場合、第1スイッチング素子22および第2スイッチング素子28の双方のオン状態から第1スイッチング素子22がオン且つ第2スイッチング素子28がオフとなる状態への切り替えを禁止した。これにより、パワースイッチング素子Swを流れる電流が更に増加することを回避することができる。

【0076】

(8)高電圧経路Lhが備える受動素子が抵抗体(第1抵抗体24)からなり、低電圧経路Llが備える受動素子が抵抗体(第2抵抗体26)からなるようにした。これにより、高電圧経路Lhや低電圧経路Llを簡素な構成とすることができる。

【0077】

(9)ドライブユニットDUの駆動対象を、高電位側のパワースイッチング素子Swpおよび低電位側のパワースイッチング素子Swnの直列接続体を備える電力変換回路(インバータIV)における上記直列接続体を構成するパワースイッチング素子Swp,Swnとした。この場合、高電位側のパワースイッチング素子Swpおよび低電位側のパワースイッチング素子Swnの双方がオン状態となる事態が生じた場合に、これらに過度の電流が流れるおそれがあるため、上記切り替え処理の利用価値が特に大きい。

【0078】

(第2の実施形態)

以下、第2の実施形態について、先の第1の実施形態との相違点を中心に図面を参照しつつ説明する。

【0079】

本実施形態では、パワースイッチング素子Swのミラー期間の途中で、第1スイッチング素子22および第2スイッチング素子28の双方のオン状態から第1スイッチング素子22がオン且つ第2スイッチング素子28がオフとなる状態へと切り替える。これにより、パワースイッチング素子Swに電流が流れることによる損失の低減を図る。すなわち、ミラー期間の終了後、第1抵抗体24および第2抵抗体26による電圧Vcの分圧値によって定まる電圧「R2・Vc/(R1+R2)」にゲート電圧Vgeが収束すると、ミラー期間の終了後においてゲート印加電圧を電圧Vcとした場合と比較して損失が大きくなる。このため、ミラー期間の途中で上記切り替えを行なうことで、ミラー期間の終了後、ゲート電圧Vgeは、電圧Vcに向けて速やかに上昇することとなり、損失を低減することができる。

【0080】

図5に、本実施形態にかかるパワースイッチング素子Swの駆動処理(特に、正常時)を示す。なお、図5(a)〜図5(d)は、先の図4(a)〜図4(d)に対応している。図に示すミラー期間においてはゲート電圧Vgeの上昇速度は、ミラー期間前やミラー期間後と比較して無視しうるほど小さいが、実際には、図中下方に拡大して示すように、ゲート電圧Vgeは上昇している。そして、その上昇速度は、第1スイッチング素子22および第2スイッチング素子28の双方のオン状態から第1スイッチング素子22がオン且つ第2スイッチング素子28がオフとなる状態へと切り替えることで大きくなる。

【0081】

なお、上記切り替えタイミングの設定は、遅延回路40の回路時定数の調節等によって行なうことができる。

【0082】

以上説明した本実施形態によれば、先の第1の実施形態の上記(1)、(2)、(4)〜(9)の各効果に加えて、更に以下の効果が得られるようになる。

【0083】

(10)遅延信号DLによる遅延時間Tdを、パワースイッチング素子Swのオン状態への切替指令タイミングからミラー期間のうちのミラー期間の終了前のタイミングとなるまでに要すると想定される時間に設定した。これにより、パワースイッチング素子Swの損失を低減することができる。

【0084】

(第3の実施形態)

以下、第3の実施形態について、先の第1の実施形態との相違点を中心に図面を参照しつつ説明する。

【0085】

本実施形態では、パワースイッチング素子Swのミラー期間の終了タイミングにおいて、第1スイッチング素子22および第2スイッチング素子28の双方のオン状態から第1スイッチング素子22がオン且つ第2スイッチング素子28がオフとなる状態へと切り替える。これにより、サージの増大を抑制しつつも、パワースイッチング素子Swに電流が流れることによる損失の低減を図る。図6に、本実施形態にかかるパワースイッチング素子Swの駆動処理(特に、正常時)を示す。なお、図6(a)〜図6(d)は、先の図4(a)〜図4(d)に対応している。

【0086】

すなわち、上記第2の実施形態では、先の図5に示したように、第1スイッチング素子22および第2スイッチング素子28の双方のオン状態から第1スイッチング素子22がオン且つ第2スイッチング素子28がオフとなる状態へと切り替えることで、ゲート電圧Vgeの上昇速度が大きくなる。これにより、パワースイッチング素子Swを流れる電流の変化速度が増大し、ひいてはサージが大きくなるおそれがある。これに対し、上記切り替えをミラー期間の終了時とすることで、サージの抑制を図りつつもパワースイッチング素子Swの損失を極力低減する。

【0087】

なお、上記切り替えタイミングの設定は、遅延回路40の回路時定数の調節等によって行なうことができる。

【0088】

以上説明した本実施形態によれば、先の第1の実施形態の上記(1)、(2)、(4)〜(9)の各効果に加えて、更に以下の効果が得られるようになる。

【0089】

(11)遅延信号DLの遅延時間Tdを、パワースイッチング素子Swのオン操作指令タイミングからミラー期間の終了タイミングとなるまでに要すると想定される時間に設定した。これにより、サージを抑制しつつも損失を極力低減することができる。

【0090】

(第4の実施形態)

以下、第4の実施形態について、先の第1の実施形態との相違点を中心に図面を参照しつつ説明する。

【0091】

図7に、本実施形態にかかるドライブユニットDUの回路構成を示す。なお、図7において、先の図2に示した部材に対応する部材については、便宜上同一の符号を付している。

【0092】

本実施形態では、ゲート電圧Vgeを入力としてミラー期間の終了を判断し、これに基づき第1スイッチング素子22および第2スイッチング素子28の双方のオン状態から第1スイッチング素子22がオン且つ第2スイッチング素子28がオフとなる状態への切り替えを行なう。すなわち、本実施形態では、コンパレータ50を備え、その非反転入力端子にゲート電圧Vgeを印加し、反転入力端子に、電源52により、パワースイッチング素子Swがオンする際の電圧Vthよりもわずかに高い終了検出電圧Vmを印加する。そして、AND回路42は、遅延信号DLとインバータ44の出力信号と、コンパレータ50の出力信号の論理積信号を生成して制御部30に出力する。これにより、制御部30では、操作信号gがオン指令に切り替わるタイミングから遅延時間Tdが経過することと、過電流が検出されていないことと、ゲート電圧Vgeが上記終了検出電圧Vm以上となることとの論理積が真となることで、上記切り替えを行なう。ここで、遅延時間Tdは、操作信号gがオン操作指令に切り替わるタイミングからパワースイッチング素子Swに過電流が流れた場合にその旨がコンパレータ36等を備えて構成される過電流判断手段によって検出されるまでに要する時間Td以上であって且つ、ミラー期間の終了までに要する時間よりも短い時間に設定される。

【0093】

図8に、本実施形態にかかるパワースイッチング素子Swの駆動処理について、正常時の場合(ケース1)と過電流が検出される場合(ケース2)とを比較しつつ示す。なお、図8(a)〜図8(d)は、先の図4(a)〜図4(d)に対応しており、また図8(e)は、遅延信号DLの推移を示す。

【0094】

図示されるように、正常時においては、ミラー期間が終了し、ゲート電圧Vgeが終了検出電圧Vm以上となることで、第1スイッチング素子22および第2スイッチング素子28の双方のオン状態から第1スイッチング素子22がオン且つ第2スイッチング素子28がオフとなる状態への切り替えがなされる。これに対し、過電流が流れる場合には、上記切り替えはなされず、パワースイッチング素子Swを流れる電流は、第1スイッチング素子22および第2スイッチング素子28の双方のオン状態におけるゲート電圧Vgeの収束値によって流すことのできる電流に制限される。

【0095】

なお、遅延時間Tdは、操作信号gがオン操作指令に切り替わるタイミングからパワースイッチング素子Swに過電流が流れた場合にその旨がコンパレータ36等を備えて構成される過電流判断手段によって検出されるまでに要する時間Ti以上であって且つ、ミラー期間の終了までに要する時間よりも短い時間に設定される。

【0096】

以上説明した本実施形態によれば、先の第1の実施形態の上記(1)、(2)、(4)〜(9)の各効果に加えて、更に以下の効果が得られるようになる。

【0097】

(12)パワースイッチング素子Swのミラー期間の終了を検出し、ミラー期間の終了が検出されることで上記切り替えを行った。これにより、サージを抑制しつつも損失を極力低減することができる。

【0098】

(13)遅延信号DLによって規定された遅延時間Tdが経過して且つミラー期間の終了が検出されることで上記切り替えを行った。これにより、パワースイッチング素子Swがオン状態に切り替わることで過電流が流れる状況下、過電流が流れたと判断される以前にゲート電圧Vgeが上記終了検出電圧Vm以上となったとしても、上記切替がなされることを回避することができる。

【0099】

(第5の実施形態)

以下、第5の実施形態について、先の第4の実施形態との相違点を中心に図面を参照しつつ説明する。

【0100】

本実施形態では、ミラー期間の終了を判断するための終了検出電圧Vmをパワースイッチング素子Swの温度に応じて可変設定する。これは、パワースイッチング素子Swがオン状態に切り替わる電圧Vthが温度に応じて変動することに鑑みた設定である。

【0101】

図9に、本実施形態にかかるドライブユニットDUの回路構成を示す。なお、図9において、先の図7に示した部材に対応する部材については、便宜上同一の符号を付している。図示されるように、電源52aは、パワースイッチング素子Sw付近に配置されてその温度を検出する感温ダイオードSDによる温度検出信号に基づき終了検出電圧Vmを可変設定する。これにより、終了検出電圧Vmは、パワースイッチング素子Swの温度検出値によってパワースイッチング素子Swが実際にオン状態に切り替わると想定される値よりもわずかに大きい値に設定されることとなる。

【0102】

以上説明した本実施形態によれば、先の第1の実施形態の上記(1)、(2)、(4)〜(9)の各効果に加えて、更に以下の効果が得られるようになる。

【0103】

(14)パワースイッチング素子Swの温度に応じて終了検出電圧Vmを可変設定した。これにより、現在の温度においてミラー期間のゲート電圧Vgeとして想定される値に応じて終了検出電圧Vmを設定することができる。

【0104】

(第6の実施形態)

以下、第6の実施形態について、先の第4の実施形態との相違点を中心に図面を参照しつつ説明する。

【0105】

本実施形態では、ゲート電圧Vgeの変化の検出に基づきミラー期間の終了を検出する。

【0106】

図10に、本実施形態にかかるドライブユニットDUの回路構成を示す。なお、図10において、先の図2に示した部材に対応する部材については、便宜上同一の符号を付している。図示されるように、本実施形態では、ゲート電圧Vgeを入力として、これを微分する微分回路64を備える。この微分回路64は、例えばRC回路等によって構成することができる。そして、微分回路64の出力(ゲート電圧Vgeの変化速度)は、コンパレータ60の非反転入力端子に印加され、またコンパレータ60の反転入力端子には、電源62の電圧Vdが印加される。ここで、電圧Vdは、ミラー期間以外の微分回路64の出力値と、ミラー期間の微分回路64の出力値とで、コンパレータ60の出力値を相違させることのできる値に設定する。そして、AND回路42は、遅延信号DLと、インバータ44の出力信号と、コンパレータ60の出力信号との論理積信号を制御部30に出力する。これにより、制御部30では、操作信号gがオン操作指令に切り替わるタイミングから遅延時間Tdが経過することと、過電流が流れていないことと、ゲート電圧Vgeの上昇速度が所定以上となることとの論理積が真となることで、第1スイッチング素子22および第2スイッチング素子28の双方のオン状態から第1スイッチング素子がオン且つ第2スイッチング素子28がオフとなる状態へと切り替える処理を行なう。なお、遅延信号DLによって規定される遅延時間Tdは、操作信号gがオン操作指令に切り替わるタイミングからミラー期間に移行するタイミングまでに要する時間以上であって且つミラー期間の終了タイミングまでに要する時間以下に設定される。

【0107】

図11に、本実施形態にかかるパワースイッチング素子Swの駆動処理を示す。なお、図11(a)〜図11(d)は、先の図4(a)〜図4(d)に対応しており、また図11(e)は、遅延信号DLの推移を示す。

【0108】

図示されるように、操作信号gがオン操作指令に切り替わり、第1スイッチング素子22および第2スイッチング素子28がオン状態となることで、ゲート電圧Vgeが上昇していく。これにより、コンパレータ60は、ゲート電圧Vgeの変化速度がミラー期間によるものよりも大きい旨の信号を出力するものの、この場合には、遅延信号DLによって指定される遅延時間Tdが経過しないため、上記切り替えはなされない。その後、ミラー期間の途中で遅延信号DLによって指定される遅延時間Tdが経過するものの、この際には、ゲート電圧Vgeの変化速度がミラー期間によるものである旨の信号をコンパレータ60が出力するため、上記切り替えはなされない。その後、ゲート電圧Vgeの変化速度がミラー期間によるものよりも大きい旨の信号をコンパレータ60が出力することで、上記切替がなされる。

【0109】

以上説明した本実施形態によれば、先の第1の実施形態の上記(1)、(2)、(4)〜(9)の各効果に加えて、更に以下の効果が得られるようになる。

【0110】

(15)ゲート電圧Vgeの変化が検出されることに基づきミラー期間の終了を検出した。これにより、ミラー期間の終了を的確に検出することができる。

【0111】

(第7の実施形態)

以下、第7の実施形態について、先の第1の実施形態との相違点を中心に図面を参照しつつ説明する。

【0112】

図12に、本実施形態にかかるドライブユニットDUの回路構成を示す。なお、図10において、先の図2に示した部材に対応する部材については、便宜上同一の符号を付している。図示されるように、本実施形態では、高電圧経路と低電圧経路とを複数備える。すなわち、高電圧経路として、第1スイッチング素子22aおよび第1抵抗体24aを備える高電圧経路Lhaと、第1スイッチング素子22bおよび第1抵抗体24bを備える高電圧経路Lhbとを備える。また、低電圧経路として、第2スイッチング素子28aおよび第2抵抗体26aを備える低電圧経路Llaと、第2スイッチング素子28bおよび第2抵抗体26bを備える低電圧経路Llaとを備える。ここで、第1抵抗体24a(抵抗値R1)および第2抵抗体26a(抵抗値R2)による電圧Vcの分圧値「Vc・R2/(R1+R2)」よりも、第1抵抗体24b(抵抗値R3)および第2抵抗体26b(抵抗値R4)による電圧Vcの分圧値「Vc・R4/(R3+R4)」の方が低く設定されている。詳しくは、パワースイッチング素子Swがオン状態に切り替わる閾値電圧Vthが上記一対の分圧値の間となるように設定されている。そして、第1抵抗体24aの抵抗値R1と第2抵抗体26aの抵抗値R2との和が、第1抵抗体24bの抵抗値R3と第2抵抗体26bの抵抗値R4との和よりも大きくなるように設定されている。これは、第1スイッチング素子22bおよび第2スイッチング素子28bの双方がオン状態となる場合の方が第1スイッチング素子22aおよび第2スイッチング素子28aの双方がオン状態となる場合よりもゲートの充電速度を大きくするための設定である。

【0113】

図13に、本実施形態にかかるパワースイッチング素子Swの駆動処理を示す。詳しくは、図13(a)に、ゲート電圧Vgeの推移を示し、図13(b)に、第1スイッチング素子22aの操作状態の推移を示し、図13(c)に、第2スイッチング素子28aの操作状態の推移を示し、図13(d)に、第1スイッチング素子22bの操作状態の推移を示し、図13(e)に、第2スイッチング素子28bの操作状態の推移を示す。

【0114】

図示されるように、操作信号gがオン操作指令に切り替えられると、第1スイッチング素子22bおよび第2スイッチング素子28bの双方がオン状態とされることで、ゲート電圧Vgeは、迅速に、第1抵抗体24bおよび第2抵抗体26bによる電圧Vcの分圧値まで上昇する。そして、ゲート電圧Vgeがこの分圧値に収束した後、第1スイッチング素子22bおよび第2スイッチング素子28bの双方のオン状態から第1スイッチング素子22aおよび第2スイッチング素子28aの双方のオン状態に切り替えられる。これにより、ゲートの充電速度を低下させた状態でミラー期間に移行させる。そして、ミラー期間の終了後、第1スイッチング素子22aがオンかつ第2スイッチング素子28aがオフとなる状態に切り替える。

【0115】

なお、第1スイッチング素子22bおよび第2スイッチング素子28bの双方のオン状態からこれら双方のオフ状態への切り替えは、上記遅延回路40と同様の構成を有する遅延回路の遅延信号に基づき行なえばよい。また、第1スイッチング素子22aおよび第2スイッチング素子28aの双方のオン状態への切り替えも、この遅延信号に基づき行なうことができる。さらに、第1スイッチング素子22aがオンかつ第2スイッチング素子28aがオフとなる状態への切り替えは、上記第1の実施形態の遅延回路40を用いて行なうことができる。

【0116】

以上説明した本実施形態によれば、先の第1の実施形態の上記(1)、(2)、(4)〜(9)の各効果に加えて、更に以下の効果が得られるようになる。

【0117】

(16)第1抵抗体24aおよび第2抵抗体26aによる電圧Vcの分圧値「Vc・R2/(R1+R2)」が閾値電圧Vthより大きく且つ、第1抵抗体24bおよび第2抵抗体26bによる電圧Vcの分圧値「Vc・R4/(R3+R4)」が閾値電圧Vthよりも小さくして且つ、「R1+R2>R3+R4」とした。これにより、上記分圧値「Vc・R4/(R3+R4)」までゲート電圧Vgeを迅速に上昇させることができる。特に、この分圧値が、パワースイッチング素子Swがオン状態に切り替わる閾値電圧Vthよりも低いため、スイッチング状態の切替速度を上昇させつつもサージの増大を好適に回避することができる。

【0118】

(第8の実施形態)

以下、第8の実施形態について、先の第1の実施形態との相違点を中心に図面を参照しつつ説明する。

【0119】

図14に、本実施形態にかかるドライブユニットDUの回路構成を示す。なお、図14において、先の図2に示した部材に対応する部材については、便宜上同一の符号を付している。

【0120】

図示されるように、本実施形態では、第2抵抗体26にコンデンサ70を並列接続する。これにより、第1スイッチング素子22および第2スイッチング素子28の双方のオン状態時において、ゲート電圧Vgeの上昇速度をコンデンサ70の静電容量C1によって制御することができる。このため、第1抵抗体24の抵抗値R1を十分に小さい値に設定することができる。

【0121】

図15に、本実施形態にかかるパワースイッチング素子Swの駆動処理を示す。なお、図15(a)〜図15(c)は、先の図2(a)〜図2(c)に対応している。

【0122】

図示されるように、第1スイッチング素子22および第2スイッチング素子28の双方のオン状態から第1スイッチング素子22がオン且つ第2スイッチング素子28がオフとなる状態に切り替えることで、ゲート電圧Vgeを電圧Vcに急上昇させることができる。そして、この際の上昇速度を、第1スイッチング素子22および第2スイッチング素子28の双方のオン状態となる際のゲート電圧Vgeの上昇速度と比較して十分に大きくすることができる。このため、ミラー期間等におけるゲート電圧Vgeの上昇速度を抑制することによりサージを抑制しつつ、ミラー期間終了後におけるゲート電圧Vgeの上昇速度を大きくすることにより損失を低減することができる。

【0123】

以上説明した本実施形態によれば、先の第1の実施形態の上記(1)、(2)、(4)〜(9)の各効果に加えて、更に以下の効果が得られるようになる。

【0124】

(17)第2抵抗体26にコンデンサ70を並列接続した。これにより、コンデンサ70によって第1スイッチング素子22および第2スイッチング素子28の双方のオン状態となる際のゲート電圧Vgeの上昇速度を制限しつつも、第1抵抗体24の抵抗値を極力小さくして第1スイッチング素子22がオン且つ第2スイッチング素子28がオフとなる状態におけるゲート電圧Vgeの上昇速度を十分大きくすることができる。

【0125】

(第9の実施形態)

以下、第9の実施形態について、先の第8の実施形態との相違点を中心に図面を参照しつつ説明する。

【0126】

図16に、本実施形態にかかるドライブユニットDUの回路構成を示す。なお、図16において、先の図14に示した部材に対応する部材については、便宜上同一の符号を付している。

【0127】

図示されるように、本実施形態では、第1抵抗体24にコンデンサ72を並列接続する。ここで、コンデンサ70、72の静電容量C1,C2は、コンデンサ70,72による電圧Vcの分圧値「Vc・C2/(C1+C2)」がパワースイッチング素子Swをオン状態とする閾値電圧Vthよりも低くなるように設定している。

【0128】

図17に、本実施形態にかかるパワースイッチング素子Swの駆動処理を示す。なお、図17(a)〜図17(c)は、先の図2(a)〜図2(c)に対応している。

【0129】

図示されるように、操作信号gがオン操作指令となり第1スイッチング素子22および第2スイッチング素子28の双方がオン状態とされることで、ゲート電圧Vgeは、コンデンサ70,72による上記分圧値まで急速に上昇する。その後、第1抵抗体24および第2抵抗体26による分圧値まで上昇するが、その速度は、上記第8の実施形態と同様、コンデンサ70の静電容量等によって制限される。このため、ミラー期間におけるゲートの充電速度を制限することができる。そして、第1スイッチング素子22および第2スイッチング素子28の双方のオン状態から第1スイッチング素子22がオン且つ第2スイッチング素子28がオフとなる状態に切り替えることで、ゲート電圧Vgeを電圧Vcに急上昇させることができる。

【0130】

以上説明した本実施形態によれば、先の第8の実施形態の上記各効果に加えて、更に以下の効果が得られるようになる。

【0131】

(18)第1抵抗体24にコンデンサ72を並列接続して且つ第2抵抗体26にコンデンサ70を並列接続し、これらコンデンサ70,72による電圧Vcの分圧値を閾値電圧Vthよりも小さく設定した。これにより、操作信号gがオン操作指令に切り替わってからミラー期間となるまでの時間を短縮することができる。

【0132】

(第10の実施形態)

以下、第10の実施形態について、先の第1の実施形態との相違点を中心に図面を参照しつつ説明する。

【0133】

本実施形態では、パワースイッチング素子Swをオフする際にゲート印加電圧を2段階に変化させるために先の図2に示した第1スイッチング素子22、第1抵抗体24、第2抵抗体26、第2スイッチング素子28を利用する。ただし、第1抵抗体24および第2抵抗体26による電圧Vcの分圧値は、パワースイッチング素子Swをオフ状態に切り替える閾値電圧Vthよりも低く設定する。これは、パワースイッチング素子Swがオフするまでの期間においてパワースイッチング素子Swを流れる電流の変化速度が過度に大きくならないようにするための設定である。

【0134】

図18に、本実施形態にかかるパワースイッチング素子Swの駆動処理を示す。なお、図18(a)〜図18(c)は、先の図2(a)〜図2(c)に対応している。

【0135】

図示されるように、本実施形態では、操作信号gがオフ操作指令に切り替わることで、第1スイッチング素子22および第2スイッチング素子28の双方をオン状態とし、ゲート印加電圧を、第1抵抗体24および第2抵抗体26による電圧Vcの分圧値「Vc・R2/(R1+R2)」とする。これにより、ゲート電圧Vgeが低下し、ミラー期間を経て上記分圧値に収束する。その後、第1スイッチング素子22がオフ且つ第2スイッチング素子28がオンとなる状態に移行させることで、ゲート電圧Vgeをゼロまで低下させる。

【0136】

(その他の実施形態)

なお、上記各実施形態は、以下のように変更して実施してもよい。

<遅延信号生成手段について>

遅延信号生成手段としては、操作信号gを入力とし、これを遅延させる手段に限らない。例えば、操作信号gがオン指令信号となることをトリガとして計時動作を行うタイマを備え、タイマの値が閾値を超えるタイミングを指定するものであってもよい。

<切替手段について>

切替手段としては、遅延回路40を備えて構成されるものに限らない。例えば、先の第4、5の実施形態において遅延回路40を省いて構成してもよい。また、先の第6の実施形態において、遅延回路40を省き、操作信号gがオン指令信号となってからコンパレータ60の出力が2度論理「H」となることに基づき、ミラー期間の終了を検出する手段を構成してもよい。

<過電流判断手段について>

過電流判断手段としては、パワースイッチング素子Swのセンス端子Stの微少電流によるシャント抵抗の電圧降下量と基準電圧Vrefとを比較することで過電流の有無を判断する手段に限らない。例えば、パワースイッチング素子Swの入力端子および出力端子間の電圧降下量をパワースイッチング素子Swを流れる電流と相関を有するパラメータとして用いて、この値と閾値とを比較することで過電流の有無を判断する手段であってもよい。

<導通制御端子と高電圧印加手段とを接続する第1経路について>

第1経路としては、単一のスイッチング素子によって開閉される1つの経路、または2つのスイッチング素子のそれぞれによって開閉される合計2つの経路に限らない。例えば3つ以上のスイッチング素子のそれぞれによって開閉される合計3つ以上の経路であってもよい。ここで、例えばオン状態への切り替えに3つ以上の経路を利用する場合には、ミラー期間の終了後において、複数の経路を利用して導通制御端子に高電圧印加手段の電圧を印加すればよい。

【0137】

また、第1経路としては、受動素子として抵抗体やコンデンサを備えるものに限らない。例えばインダクタをさらに備えるものであってもよい。

<導通制御端子と低電圧印加手段とを接続する第2経路について>

第2経路としては、単一のスイッチング素子によって開閉される1つの経路、または2つのスイッチング素子のそれぞれによって開閉される合計2つの経路に限らない。例えば3つ以上のスイッチング素子のそれぞれによって開閉される合計3つ以上の経路であってもよい。ここで、例えばオフ状態への切り替えに3つ以上の経路を用いる場合には、ミラー期間の終了後において、複数の経路を用いて導通制御端子に低電圧印加手段の電圧を印加すればよい。また、例えばオン状態への切り替えに第1経路および第2経路としてそれぞれ3つ以上の経路を利用する場合には、ミラー期間前において、複数の経路を利用して導通制御端子に高電圧印加手段の電圧を印加すればよい。具体的には、例えば先の第7の実施形態において、高電圧経路Lhbおよび低電圧経路Llbの直列接続体を1つ追加し、オン指令タイミングにおいてこれら一対の直列接続体をオンし、その後、高電圧経路Lhaおよび低電圧経路Llaを用いればよい。これにより、ミラー期間に移行する前までの期間をいっそう短縮することができる。

【0138】

また、第2経路としては、受動素子として抵抗体やコンデンサを備えるものに限らない。例えばインダクタをさらに備えるものであってもよい。

<第1経路と第2経路との共通部分について>

第1経路と第2経路との共通部分(図1の共通経路Lg)に、ゲート抵抗を備えてもよい。また、共通部分を有しなくてもよい。

<オフ状態への切り替えについて>

オフ状態への切り替えについては、上記第10の実施形態にて例示したものに限らない。例えば、上記第2〜第9の実施形態の構成を、パワースイッチング素子Swのオフ状態への切り替え処理用に設定してもよい。

<駆動対象となるスイッチング素子について>

駆動対象となるIGBTとしては、これに逆並列に接続される態様にてこれと同一半導体基板に併設されたフリーホイールダイオードが設けられた半導体デバイスを構成するものに限らない。また、IGBTにも限らず、例えば、スーパージャンクションMOS電界効果トランジスタや、シリコンカーバイト(SiC)にて構成されるMOS電界効果トランジスタ等の電界効果トランジスタであってもよい。なお、MOS電界効果トランジスタを駆動対象として採用する場合、Nチャネルのトランジスタに限らず、Pチャネルのトランジスタであってもよい。

【0139】

また、駆動対象となるパワースイッチング素子としては、インバータIVやコンバータCVを構成するものにも限らない。この際、高電位側のパワースイッチング素子Swpおよび低電位側のパワースイッチング素子Swnの直列接続体を備える構成にも限らない。

【符号の説明】

【0140】

22…第1スイッチング素子、24…第1抵抗体、26…第2抵抗体、28…第2スイッチング素子、Sw…パワースイッチング素子。

【特許請求の範囲】

【請求項1】

電圧制御形のスイッチング素子の導通制御端子を高電圧印加手段に接続して且つ受動素子および第1開閉手段を備える第1経路と、前記導通制御端子を低電圧印加手段に接続して且つ受動素子および第2開閉手段を備える第2経路とを備え、前記第1開閉手段および前記第2開閉手段を操作することで前記スイッチング素子を駆動するスイッチング素子の駆動装置において、

前記スイッチング素子のスイッチング状態の切り替えに際し、前記第1開閉手段および前記第2開閉手段の双方の閉状態からいずれか一方が閉且つ他方が開となる状態へと切り替える切替手段を備え、

前記いずれか一方は、前記高電圧印加手段および前記低電圧印加手段のうちの前記スイッチング状態の切り替えによって実現されるスイッチング状態とするための電圧を前記導通制御端子に印加する方と前記導通制御端子とを接続するための手段であることを特徴とするスイッチング素子の駆動装置。

【請求項2】

前記第1開閉手段および前記第2開閉手段の双方が閉状態とされる際の前記導通制御端子の電圧の収束値が、前記スイッチング素子のミラー電圧よりも前記高電圧印加手段の印加電圧および前記低電圧印加手段の印加電圧のうちの前記スイッチング状態の切り替えによって実現されるスイッチング状態とするための電圧側にあることを特徴とする請求項1記載のスイッチング素子の駆動装置。

【請求項3】

前記切替手段は、前記スイッチング状態をオフ状態からオン状態に切り替える際に前記切り替えを行うものであり、

前記第1開閉手段および前記第2開閉手段の双方が閉状態とされる際の前記導通制御端子の電圧の収束値が前記スイッチング素子のミラー電圧よりも前記オン状態時の電圧側にあることを特徴とする請求項1または2記載のスイッチング素子の駆動装置。

【請求項4】

前記切替手段は、前記スイッチング素子のミラー期間以降に前記切り替えを行うことを特徴とする請求項3記載のスイッチング素子の駆動装置。

【請求項5】

前記切替手段は、前記スイッチング素子の操作信号がスイッチング状態の切り替えを指示するタイミングに対して遅延したタイミングを指示する遅延信号を生成する遅延信号生成手段を備え、前記遅延信号に基づき前記切り替えを行うことを特徴とする請求項1〜4のいずれか1項に記載のスイッチング素子の駆動装置。

【請求項6】

前記遅延信号生成手段は、前記操作信号を入力として前記遅延信号を生成することを特徴とする請求項5記載のスイッチング素子の駆動装置。

【請求項7】

前記切替手段は、前記スイッチング状態をオフ状態からオン状態に切り替える際に前記第1開閉手段および前記第2開閉手段の双方の閉状態から前記第1開閉手段が閉且つ前記第2開閉手段が開となる状態への切り替えを行うものであり、

前記スイッチング素子を流れる電流が過度に大きくなるか否かを判断する過電流判断手段を更に備え、

前記遅延信号は、前記スイッチング素子をオン状態に切り替えるに際しての前記遅延したタイミングを指示するものであり、

前記遅延信号による遅延時間は、前記過電流判断手段による過電流の判断に要する時間以上に設定されることを特徴とする請求項6記載のスイッチング素子の駆動装置。

【請求項8】

前記過電流判断手段により前記スイッチング素子を流れる電流が過度に大きくなると判断される場合、前記切替手段による前記切り替えを禁止する禁止手段を更に備えることを特徴とする請求項7記載のスイッチング素子の駆動装置。

【請求項9】

前記遅延信号は、前記スイッチング素子をオン状態に切り替えるに際しての前記遅延したタイミングを指示するものであり、

前記遅延したタイミングまでの遅延時間は、前記スイッチング素子のオン状態への切替指令タイミングから前記スイッチング素子のミラー期間のうちの該ミラー期間の終了前のタイミングとなるまでに要すると想定される時間に設定されることを特徴とする請求項5〜8のいずれか1項に記載のスイッチング素子の駆動装置。

【請求項10】

前記遅延信号は、前記スイッチング素子をオン状態に切り替えるに際しての前記遅延したタイミングを指示するものであり、

前記遅延したタイミングまでの遅延時間は、前記スイッチング素子のオン状態への切替指令タイミングから前記スイッチング素子のミラー期間の終了タイミングとなるまでに要すると想定される時間に設定されることを特徴とする請求項5〜8のいずれか1項に記載のスイッチング素子の駆動装置。

【請求項11】

前記切替手段は、前記スイッチング素子のミラー期間の終了を検出する終了検出手段を備え、前記ミラー期間の終了が検出されることで前記切り替えを行うことを特徴とする請求項1〜4のいずれか1項に記載のスイッチング素子の駆動装置。

【請求項12】

前記切替手段は、前記スイッチング素子のミラー期間の終了を検出する終了検出手段を備え、前記遅延信号によって規定された遅延時間が経過して且つ前記ミラー期間の終了が検出されることで前記切り替えを行うことを特徴とする請求項5〜10のいずれか1項に記載のスイッチング素子の駆動装置。

【請求項13】

前記終了検出手段は、前記導通制御端子の電圧と終了判定電圧とを比較する比較手段を備え、該比較手段の比較結果を前記ミラー期間の終了の有無の検出結果を示す信号とすることを特徴とする請求項11または12記載のスイッチング素子の駆動装置。

【請求項14】

前記スイッチング素子の温度を検出する温度検出手段を備え、

前記終了検出手段は、前記温度検出手段によって検出される温度に応じて前記終了判定電圧を可変設定することを特徴とする請求項13記載のスイッチング素子の駆動装置。

【請求項15】

前記終了検出手段は、前記導通制御端子の電圧の変化を検出する手段を備え、該変化が検出されることに基づき前記ミラー期間の終了を検出することを特徴とする請求項11または12記載のスイッチング素子の駆動装置。

【請求項16】

前記第1経路が備える受動素子は、抵抗体を含むことを特徴とする請求項1〜15のいずれか1項に記載のスイッチング素子の駆動装置。

【請求項17】

前記第2経路が備える受動素子は、抵抗体を含むことを特徴とする請求項1〜16のいずれか1項に記載のスイッチング素子の駆動装置。

【請求項18】

前記第1経路が備える受動素子は、抵抗体からなり、

前記第2経路が備える受動素子は、抵抗体からなることを特徴とする請求項17記載のスイッチング素子の駆動装置。

【請求項19】

前記第1経路が備える受動素子は、抵抗体からなり、

前記第2経路が備える受動素子は、抵抗体とコンデンサとの並列接続体からなることを特徴とする請求項17記載のスイッチング素子の駆動装置。

【請求項20】

前記第1経路が備える受動素子は、抵抗体とコンデンサとの並列接続体からなり、

前記第2経路が備える受動素子は、抵抗体とコンデンサとの並列接続体からなることを特徴とする請求項1〜15のいずれか1項に記載のスイッチング素子の駆動装置。

【請求項21】

前記スイッチング素子は、前記高電圧印加手段と前記導通制御端子との接続によってオン状態とされるものであり、

前記切替手段は、前記スイッチング状態をオフ状態からオン状態に切り替える際に前記切り替えを行うものであり、

前記第1経路のコンデンサと前記第2経路のコンデンサとの直列接続体によって前記高電圧印加手段と前記低電圧印加手段との間の電圧を分圧した値が前記スイッチング素子のミラー電圧よりも低く、且つ前記第1経路の抵抗体と前記第2経路の抵抗体とによって前記高電圧印加手段と前記低電圧印加手段との間の電圧を分圧した値が前記スイッチング素子のミラー電圧よりも高いことを特徴とする請求項20記載のスイッチング素子の駆動装置。

【請求項22】

前記切替手段は、前記スイッチング状態をオン状態からオフ状態に切り替える際に前記切り替えを行うものであり、

前記第1開閉手段および前記第2開閉手段の双方が閉状態とされる際の前記導通制御端子の電圧の収束値が前記スイッチング素子のミラー電圧よりも前記オフ状態とする電圧側であることを特徴とする請求項1記載のスイッチング素子の駆動装置。

【請求項23】

前記切替手段は、前記スイッチング素子のミラー期間以降に前記切り替えを行うことを特徴とする請求項22記載のスイッチング素子の駆動装置。

【請求項24】

前記スイッチング素子は、高電位側のスイッチング素子および低電位側のスイッチング素子の直列接続体を備える電力変換回路における前記直列接続体を構成するスイッチング素子であることを特徴とする請求項1〜23のいずれか1項に記載のスイッチング素子の駆動装置。

【請求項1】

電圧制御形のスイッチング素子の導通制御端子を高電圧印加手段に接続して且つ受動素子および第1開閉手段を備える第1経路と、前記導通制御端子を低電圧印加手段に接続して且つ受動素子および第2開閉手段を備える第2経路とを備え、前記第1開閉手段および前記第2開閉手段を操作することで前記スイッチング素子を駆動するスイッチング素子の駆動装置において、

前記スイッチング素子のスイッチング状態の切り替えに際し、前記第1開閉手段および前記第2開閉手段の双方の閉状態からいずれか一方が閉且つ他方が開となる状態へと切り替える切替手段を備え、

前記いずれか一方は、前記高電圧印加手段および前記低電圧印加手段のうちの前記スイッチング状態の切り替えによって実現されるスイッチング状態とするための電圧を前記導通制御端子に印加する方と前記導通制御端子とを接続するための手段であることを特徴とするスイッチング素子の駆動装置。

【請求項2】

前記第1開閉手段および前記第2開閉手段の双方が閉状態とされる際の前記導通制御端子の電圧の収束値が、前記スイッチング素子のミラー電圧よりも前記高電圧印加手段の印加電圧および前記低電圧印加手段の印加電圧のうちの前記スイッチング状態の切り替えによって実現されるスイッチング状態とするための電圧側にあることを特徴とする請求項1記載のスイッチング素子の駆動装置。

【請求項3】

前記切替手段は、前記スイッチング状態をオフ状態からオン状態に切り替える際に前記切り替えを行うものであり、

前記第1開閉手段および前記第2開閉手段の双方が閉状態とされる際の前記導通制御端子の電圧の収束値が前記スイッチング素子のミラー電圧よりも前記オン状態時の電圧側にあることを特徴とする請求項1または2記載のスイッチング素子の駆動装置。

【請求項4】

前記切替手段は、前記スイッチング素子のミラー期間以降に前記切り替えを行うことを特徴とする請求項3記載のスイッチング素子の駆動装置。

【請求項5】

前記切替手段は、前記スイッチング素子の操作信号がスイッチング状態の切り替えを指示するタイミングに対して遅延したタイミングを指示する遅延信号を生成する遅延信号生成手段を備え、前記遅延信号に基づき前記切り替えを行うことを特徴とする請求項1〜4のいずれか1項に記載のスイッチング素子の駆動装置。

【請求項6】

前記遅延信号生成手段は、前記操作信号を入力として前記遅延信号を生成することを特徴とする請求項5記載のスイッチング素子の駆動装置。

【請求項7】

前記切替手段は、前記スイッチング状態をオフ状態からオン状態に切り替える際に前記第1開閉手段および前記第2開閉手段の双方の閉状態から前記第1開閉手段が閉且つ前記第2開閉手段が開となる状態への切り替えを行うものであり、

前記スイッチング素子を流れる電流が過度に大きくなるか否かを判断する過電流判断手段を更に備え、

前記遅延信号は、前記スイッチング素子をオン状態に切り替えるに際しての前記遅延したタイミングを指示するものであり、

前記遅延信号による遅延時間は、前記過電流判断手段による過電流の判断に要する時間以上に設定されることを特徴とする請求項6記載のスイッチング素子の駆動装置。

【請求項8】

前記過電流判断手段により前記スイッチング素子を流れる電流が過度に大きくなると判断される場合、前記切替手段による前記切り替えを禁止する禁止手段を更に備えることを特徴とする請求項7記載のスイッチング素子の駆動装置。

【請求項9】

前記遅延信号は、前記スイッチング素子をオン状態に切り替えるに際しての前記遅延したタイミングを指示するものであり、

前記遅延したタイミングまでの遅延時間は、前記スイッチング素子のオン状態への切替指令タイミングから前記スイッチング素子のミラー期間のうちの該ミラー期間の終了前のタイミングとなるまでに要すると想定される時間に設定されることを特徴とする請求項5〜8のいずれか1項に記載のスイッチング素子の駆動装置。

【請求項10】

前記遅延信号は、前記スイッチング素子をオン状態に切り替えるに際しての前記遅延したタイミングを指示するものであり、

前記遅延したタイミングまでの遅延時間は、前記スイッチング素子のオン状態への切替指令タイミングから前記スイッチング素子のミラー期間の終了タイミングとなるまでに要すると想定される時間に設定されることを特徴とする請求項5〜8のいずれか1項に記載のスイッチング素子の駆動装置。

【請求項11】

前記切替手段は、前記スイッチング素子のミラー期間の終了を検出する終了検出手段を備え、前記ミラー期間の終了が検出されることで前記切り替えを行うことを特徴とする請求項1〜4のいずれか1項に記載のスイッチング素子の駆動装置。

【請求項12】

前記切替手段は、前記スイッチング素子のミラー期間の終了を検出する終了検出手段を備え、前記遅延信号によって規定された遅延時間が経過して且つ前記ミラー期間の終了が検出されることで前記切り替えを行うことを特徴とする請求項5〜10のいずれか1項に記載のスイッチング素子の駆動装置。

【請求項13】

前記終了検出手段は、前記導通制御端子の電圧と終了判定電圧とを比較する比較手段を備え、該比較手段の比較結果を前記ミラー期間の終了の有無の検出結果を示す信号とすることを特徴とする請求項11または12記載のスイッチング素子の駆動装置。

【請求項14】

前記スイッチング素子の温度を検出する温度検出手段を備え、

前記終了検出手段は、前記温度検出手段によって検出される温度に応じて前記終了判定電圧を可変設定することを特徴とする請求項13記載のスイッチング素子の駆動装置。

【請求項15】

前記終了検出手段は、前記導通制御端子の電圧の変化を検出する手段を備え、該変化が検出されることに基づき前記ミラー期間の終了を検出することを特徴とする請求項11または12記載のスイッチング素子の駆動装置。

【請求項16】

前記第1経路が備える受動素子は、抵抗体を含むことを特徴とする請求項1〜15のいずれか1項に記載のスイッチング素子の駆動装置。

【請求項17】

前記第2経路が備える受動素子は、抵抗体を含むことを特徴とする請求項1〜16のいずれか1項に記載のスイッチング素子の駆動装置。

【請求項18】

前記第1経路が備える受動素子は、抵抗体からなり、

前記第2経路が備える受動素子は、抵抗体からなることを特徴とする請求項17記載のスイッチング素子の駆動装置。

【請求項19】

前記第1経路が備える受動素子は、抵抗体からなり、

前記第2経路が備える受動素子は、抵抗体とコンデンサとの並列接続体からなることを特徴とする請求項17記載のスイッチング素子の駆動装置。

【請求項20】

前記第1経路が備える受動素子は、抵抗体とコンデンサとの並列接続体からなり、

前記第2経路が備える受動素子は、抵抗体とコンデンサとの並列接続体からなることを特徴とする請求項1〜15のいずれか1項に記載のスイッチング素子の駆動装置。

【請求項21】

前記スイッチング素子は、前記高電圧印加手段と前記導通制御端子との接続によってオン状態とされるものであり、

前記切替手段は、前記スイッチング状態をオフ状態からオン状態に切り替える際に前記切り替えを行うものであり、

前記第1経路のコンデンサと前記第2経路のコンデンサとの直列接続体によって前記高電圧印加手段と前記低電圧印加手段との間の電圧を分圧した値が前記スイッチング素子のミラー電圧よりも低く、且つ前記第1経路の抵抗体と前記第2経路の抵抗体とによって前記高電圧印加手段と前記低電圧印加手段との間の電圧を分圧した値が前記スイッチング素子のミラー電圧よりも高いことを特徴とする請求項20記載のスイッチング素子の駆動装置。

【請求項22】

前記切替手段は、前記スイッチング状態をオン状態からオフ状態に切り替える際に前記切り替えを行うものであり、

前記第1開閉手段および前記第2開閉手段の双方が閉状態とされる際の前記導通制御端子の電圧の収束値が前記スイッチング素子のミラー電圧よりも前記オフ状態とする電圧側であることを特徴とする請求項1記載のスイッチング素子の駆動装置。

【請求項23】

前記切替手段は、前記スイッチング素子のミラー期間以降に前記切り替えを行うことを特徴とする請求項22記載のスイッチング素子の駆動装置。

【請求項24】

前記スイッチング素子は、高電位側のスイッチング素子および低電位側のスイッチング素子の直列接続体を備える電力変換回路における前記直列接続体を構成するスイッチング素子であることを特徴とする請求項1〜23のいずれか1項に記載のスイッチング素子の駆動装置。

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【図14】

【図15】

【図16】

【図17】

【図18】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【図14】

【図15】

【図16】

【図17】

【図18】

【公開番号】特開2011−120418(P2011−120418A)

【公開日】平成23年6月16日(2011.6.16)

【国際特許分類】

【出願番号】特願2009−277517(P2009−277517)

【出願日】平成21年12月7日(2009.12.7)

【出願人】(000004260)株式会社デンソー (27,639)

【Fターム(参考)】

【公開日】平成23年6月16日(2011.6.16)

【国際特許分類】

【出願日】平成21年12月7日(2009.12.7)

【出願人】(000004260)株式会社デンソー (27,639)

【Fターム(参考)】

[ Back to top ]