スイッチング装置、スイッチングモジュール

【課題】本発明は、サージ電圧の低減及び発生ノイズの低減を可能とするスイッチング装置、スイッチングモジュールを提供することを目的とする。

【解決手段】本発明にかかるスイッチング装置は、スイッチング素子1と、エミッタ電極100と、エミッタ電極100を外部の主配線に接続するための主配線用エミッタ端子4と、エミッタ電極100と主配線用エミッタ端子4との間の主電流経路に介在する、複数の制御用エミッタ端子5、制御用エミッタ端子6、制御用エミッタ端子7と、隣接する制御用エミッタ端子間の主電流経路に介挿されたインダクタンス8、インダクタンス9とを備えることを特徴とする。

【解決手段】本発明にかかるスイッチング装置は、スイッチング素子1と、エミッタ電極100と、エミッタ電極100を外部の主配線に接続するための主配線用エミッタ端子4と、エミッタ電極100と主配線用エミッタ端子4との間の主電流経路に介在する、複数の制御用エミッタ端子5、制御用エミッタ端子6、制御用エミッタ端子7と、隣接する制御用エミッタ端子間の主電流経路に介挿されたインダクタンス8、インダクタンス9とを備えることを特徴とする。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、スイッチング装置、スイッチングモジュールの回路構造に関するものである。

【背景技術】

【0002】

従来のスイッチング装置は、特許文献1に示すように、スイッチング制御のためのエミッタ端子が1本備えられていた。

【0003】

このため、ON/OFFスイッチング過渡時のdi/dt(dv/dt)制御は、ゲート−エミッタ電圧VGE又は外付けゲート−エミッタ間ゲート抵抗RGの大小により行っていた。

【先行技術文献】

【特許文献】

【0004】

【特許文献1】特開平10−229671号公報

【発明の概要】

【発明が解決しようとする課題】

【0005】

インバータ回路に組み込まれた従来スイッチング装置においては、ターンオフ過渡時に遮断した電流のdi/dtと、主配線のインダクタンスとにより、大きなサージ電圧が発生する。そして、発生したサージ電圧がスイッチング素子の定格電圧を超える場合には、素子破壊が生ずるという問題があった。

【0006】

また、ターンオン過渡時においても、リカバリサージ電圧がスイッチング素子の定格電圧を超えることにより、素子破壊が生ずる可能性があった。

【0007】

さらに、ターンオン及びターンオフ過渡時のdi/dt(dv/dt)が大きいため、発生ノイズが大きくなるという問題点があった。

【0008】

本発明は、上記のような問題点を解消するためになされたもので、サージ電圧の低減及び発生ノイズの低減を可能とするスイッチング装置、スイッチングモジュールを提供することを目的とする。

【課題を解決するための手段】

【0009】

本発明にかかるスイッチング装置は、制御端子及び電流電極を有するスイッチング素子と、前記電流電極を外部の主配線に接続するための主配線用電流端子と、前記電流電極と前記主配線用電流端子との間の主電流経路に介在する、複数の制御用電流端子と、隣接する前記制御用電流端子間の前記主電流経路に介挿されたインダクタンスとを備えることを特徴とする。

【0010】

また、本発明にかかるスイッチングモジュールは、上記のスイッチング装置を複数備えることを特徴とする。

【発明の効果】

【0011】

本発明にかかるスイッチング装置によれば、制御端子及び電流電極を有するスイッチング素子と、前記電流電極を外部の主配線に接続するための主配線用電流端子と、前記電流電極と前記主配線用電流端子との間の主電流経路に介在する、複数の制御用電流端子と、隣接する前記制御用電流端子間の前記主電流経路に介挿されたインダクタンスとを備えることにより、適切な特性の制御用エミッタ端子に切り替えて使用し、スイッチング過渡時のdi/dt(dv/dt)を可変させることができ、サージ電圧の低減及び発生ノイズの低減を実現することが可能となる。

【0012】

また、本発明にかかるスイッチングモジュールによれば、上記のスイッチング装置を複数備えることにより、サージ電圧の低減及び発生ノイズの低減を、モジュール内において実現することが可能となる。

【図面の簡単な説明】

【0013】

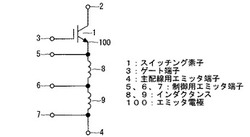

【図1】本発明の実施の形態1を示すスイッチング装置回路図である。

【図2】本発明の実施の形態1の、スイッチング装置とドライバ回路との接続を示す回路図である。

【図3】本発明の実施の形態2を示すスイッチング装置回路図である。

【図4】本発明の実施の形態2を示すスイッチング装置回路図である。

【図5】本発明の実施の形態2を示すスイッチング装置回路図である。

【発明を実施するための形態】

【0014】

<A.実施の形態1>

<A−1.構成>

図1に、本発明にかかるスイッチング装置の回路図を示す。図においてスイッチング素子1は例えばIGBTである。スイッチング装置は前記スイッチング素子1と、複数の制御用エミッタ端子5、制御用エミッタ端子6、制御用エミッタ端子7を有する。

【0015】

図示した、個々の制御用エミッタ端子5、制御用エミッタ端子6、制御用エミッタ端子7は、それぞれスイッチング素子1のエミッタ電極100との間のインダクタンスが異なる値となるようにスイッチング装置の内部配線に接続される。スイッチング装置内部では、個別のインダクタンス8、インダクタンス9が接続されている。

【0016】

具体的には、スイッチング素子1は、コレクタ端子2、制御端子としてのゲート端子3及び電流電極としてのエミッタ電極100を有し、さらに、前記エミッタ電極100側において、インダクタンス8、インダクタンス9を介して、主配線用電流端子としての主配線用エミッタ端子4を有している。

【0017】

エミッタ電極100と、主配線に接続するための主配線用エミッタ端子4とを結ぶ経路は主電流経路である。前記主電流経路上において、複数の制御用電流端子としての制御用エミッタ端子5、制御用エミッタ端子6、制御用エミッタ端子7が介在している。

【0018】

さらに前記主電流経路には、制御用エミッタ端子5、制御用エミッタ端子6、制御用エミッタ端子7の間にそれぞれ位置するインダクタンス8、インダクタンス9が備えられる。

【0019】

図2は、スイッチング装置とドライバ回路間の接続の一例を示す、スイッチング装置の回路図である。

【0020】

図2において、スイッチング素子1のゲート端子3は、ドライブ回路10に接続される。また、制御用エミッタ端子5、制御用エミッタ端子6は、切替えスイッチ11、切替えスイッチ12をそれぞれ介し、ドライブ回路10に接続される。なお切替えスイッチは、制御用エミッタ端子が備わる経路のうちのいずれかに備えられる場合であってもよい。

【0021】

ドライブ回路10は、ゲート端子3からスイッチング素子1にかかる電圧を制御し、スイッチング素子1を駆動する。切替えスイッチ11、切替えスイッチ12は、半導体スイッチを用いて実現可能である。切替えスイッチ11、切替えスイッチ12の制御機能は、ドライブ回路10に含むことも可能であるが、図示しない制御回路に含むことも可能である。図2では、切替えスイッチに対する制御信号線の図示を省略している。なお、制御用エミッタ端子7もドライブ回路10に接続される。

【0022】

主電流経路に流れる電流が時間的に変化する際に、主配線用エミッタ端子4と制御用エミッタ端子間のインダクタンス8、インダクタンス9に、電圧が発生する。発生した電圧により、負帰還としての効果が生ずることが一般に知られている。

【0023】

本発明は、異なるインダクタンスをもつ複数の制御用エミッタ端子5、制御用エミッタ端子6、制御用エミッタ端子7を使い分けることで、スイッチング過渡時の負帰還の効果を可変する。このようなスイッチング素子を備えるスイッチング装置、及び複数のスイッチング素子を備えるスイッチングモジュール等においても、同様に効果を発揮することができる。

【0024】

さらに、図2の切替えスイッチ11、切替えスイッチ12により、通常の電流遮断時と、過電流又は短絡保護の際の過大な電流遮断時とで制御用エミッタ端子5、制御用エミッタ端子6、制御用エミッタ端子7を使い分け、サージ電圧低減・発生ノイズ低減が可能となる。

【0025】

<A−2.効果>

本発明にかかる実施の形態1によれば、スイッチング装置において、制御端子及び電流電極を有するスイッチング素子と、電流電極としてのエミッタ電極100と、エミッタ電極100を外部の主配線に接続するための主配線用電流端子としての主配線用エミッタ端子4と、エミッタ電極100と主配線用エミッタ端子4との間の主電流経路に介在する、複数の制御用電流端子としての制御用エミッタ端子5、制御用エミッタ端子6、制御用エミッタ端子7と、隣接する制御用エミッタ端子5、制御用エミッタ端子6、制御用エミッタ端子7間の主電流経路に介挿されたインダクタンス8、インダクタンス9とを備えることで、適切な特性の制御用エミッタ端子に切り替えて使用し、スイッチング過渡時のdi/dt(dv/dt)を可変させることができ、サージ電圧の低減及び発生ノイズの低減を実現することが可能となる。

【0026】

また、本発明にかかる実施の形態1によれば、スイッチング装置において、スイッチング素子の制御端子としてのゲート端子3及び複数の制御用電流端子としての制御用エミッタ端子5、制御用エミッタ端子6、制御用エミッタ端子7に接続され、スイッチング素子を駆動するドライブ回路10と、ドライブ回路10と複数の制御用エミッタ端子5、制御用エミッタ端子6、制御用エミッタ端子7との間の少なくとも1つに介挿された切替えスイッチ11、切替えスイッチ12とをさらに備えることで、適切な特性の制御用エミッタ端子に切り替えて使用し、スイッチング過渡時のdi/dt(dv/dt)を可変させることができる。

【0027】

また、本発明にかかる実施の形態1によれば、スイッチング装置において、切替えスイッチ11、切替えスイッチ12の切替えにより、主電流経路のインダクタンスが異なることで、インダクタンスを適切に変更し、スイッチング過渡時のdi/dt(dv/dt)を可変させることができる。

【0028】

また、本発明にかかる実施の形態1によれば、スイッチングモジュールにおいて、上記のスイッチング装置を複数備えることで、サージ電圧の低減及び発生ノイズの低減を、モジュール内において実現することが可能となる。

【0029】

<B.実施の形態2>

<B−1.構成>

図3では、制御用エミッタ端子6、制御用エミッタ端子7と主電流経路との間に、制限抵抗13、制限抵抗14が備えられている。ここで制限抵抗とは、ゲート端子3に流出入するゲート電流を制限する抵抗であり、制御用エミッタ端子のうちのいずれかと主電流経路との間に備えられる場合であってもよい。また制限抵抗は、図2に示す構成においても適用可能である。

【0030】

制限抵抗13、制限抵抗14を備えることにより、負帰還によるdi/dt(dv/dt)可変だけでなく、制限抵抗による効果を加えることが可能となる。具体的には、ゲート端子3に流出入する電流(ゲート電流)値を調整することで、ゲート端子3が充放電される速度が調整される。小さい抵抗値ならば、ゲート電流は大きく、ゲート端子3の充放電は早くなる。このため、素子のターンオン・ターンオフ過渡時のdi/dt(dv/dt)が高くなる。大きい抵抗値ならば、ゲート電流は小さく、ゲート端子3の充放電は遅くなる。このため、素子のターンオン・ターンオフ過渡時のdi/dt(dv/dt)が低くなる。

【0031】

また図4に示すように、制御用エミッタ端子5、制御用エミッタ端子6と主電流経路との間に、制御エミッタ端子を切り替えるダイオード15、ダイオード16を備えることも可能である。ここでダイオードは、制御用エミッタ端子のうちのいずれかと主電流経路との間に備えられる場合であってもよい。

【0032】

当該ダイオード15、ダイオード16を備えることにより、例えば図2に示すドライブ回路と接続した際、外付けの切替えスイッチ11、切替えスイッチ12を介さずに、ターンオン/ターンオフ毎に制御用エミッタ端子を切替え可能となる。

【0033】

なお、図5に示すように、制限抵抗14と、ダイオード15、ダイオード16とを組み合わせた構成とすることも可能である。

【0034】

なお、実施の形態1、2においては、制御用エミッタ端子は2〜3本であるが、必要に応じ、その本数を変更することは可能である。また、制限抵抗、ダイオードの数、配置位置についても、適宜変更可能である。

【0035】

また、本発明の説明にあたってはIGBT素子を例に挙げ説明したが、本発明は、FET素子等、ゲート電圧において駆動する素子には適用可能である。なおFET素子を用いる場合には、エミッタ電極はソース電極に、主配線用エミッタ端子は主配線用ソース端子に、制御用エミッタ端子は制御用ソース端子に、それぞれ読み替える。

【0036】

また本発明は、Si素子を用いる場合に限らず、SiC素子を用いる場合にも適用可能である。SiC素子のスイッチング素子は一般に、Si素子に比べて高速動作するので、スイッチング過渡時のサージ電圧及び発生ノイズが大きくなりがちである。よって、SiC素子のスイッチング素子を用いる場合には、本発明のサージ電圧の低減及び発生ノイズの低減が特に有効である。

【0037】

また本発明は、複数の素子を搭載したIPM(Intelligent Power Module)等のモジュールにおいて、適用可能である。

【0038】

<B−2.効果>

本発明にかかる実施の形態2によれば、スイッチング装置において、複数の制御用電流端子としての制御用エミッタ端子5、制御用エミッタ端子6、制御用エミッタ端子7の少なくとも1つと主電流経路との間に、ダイオード15、ダイオード16をさらに備えることで、ターンオン又はターンオフのうちの一方の、スイッチング過渡時のdi/dt(dv/dt)を負帰還により可変させることができ、サージ電圧の低減及び発生ノイズの低減を実現することが可能となる。

【0039】

また、本発明にかかる実施の形態2によれば、スイッチング装置において、複数の制御用電流端子としての制御用エミッタ端子5、制御用エミッタ端子6、制御用エミッタ端子7の少なくとも1つと主電流経路との間に、制限抵抗13、制限抵抗14をさらに備えることで、抵抗によりdi/dt(dv/dt)を可変させることができ、サージ電圧の低減及び発生ノイズの低減を実現することが可能となる。

【符号の説明】

【0040】

1 スイッチング素子、2 コレクタ端子、3 ゲート端子、4 主配線用エミッタ端子、5〜7 制御用エミッタ端子、8,9 インダクタンス、10 ドライブ回路、11,12 切替えスイッチ、13,14 制限抵抗、15,16 ダイオード、100 エミッタ電極。

【技術分野】

【0001】

本発明は、スイッチング装置、スイッチングモジュールの回路構造に関するものである。

【背景技術】

【0002】

従来のスイッチング装置は、特許文献1に示すように、スイッチング制御のためのエミッタ端子が1本備えられていた。

【0003】

このため、ON/OFFスイッチング過渡時のdi/dt(dv/dt)制御は、ゲート−エミッタ電圧VGE又は外付けゲート−エミッタ間ゲート抵抗RGの大小により行っていた。

【先行技術文献】

【特許文献】

【0004】

【特許文献1】特開平10−229671号公報

【発明の概要】

【発明が解決しようとする課題】

【0005】

インバータ回路に組み込まれた従来スイッチング装置においては、ターンオフ過渡時に遮断した電流のdi/dtと、主配線のインダクタンスとにより、大きなサージ電圧が発生する。そして、発生したサージ電圧がスイッチング素子の定格電圧を超える場合には、素子破壊が生ずるという問題があった。

【0006】

また、ターンオン過渡時においても、リカバリサージ電圧がスイッチング素子の定格電圧を超えることにより、素子破壊が生ずる可能性があった。

【0007】

さらに、ターンオン及びターンオフ過渡時のdi/dt(dv/dt)が大きいため、発生ノイズが大きくなるという問題点があった。

【0008】

本発明は、上記のような問題点を解消するためになされたもので、サージ電圧の低減及び発生ノイズの低減を可能とするスイッチング装置、スイッチングモジュールを提供することを目的とする。

【課題を解決するための手段】

【0009】

本発明にかかるスイッチング装置は、制御端子及び電流電極を有するスイッチング素子と、前記電流電極を外部の主配線に接続するための主配線用電流端子と、前記電流電極と前記主配線用電流端子との間の主電流経路に介在する、複数の制御用電流端子と、隣接する前記制御用電流端子間の前記主電流経路に介挿されたインダクタンスとを備えることを特徴とする。

【0010】

また、本発明にかかるスイッチングモジュールは、上記のスイッチング装置を複数備えることを特徴とする。

【発明の効果】

【0011】

本発明にかかるスイッチング装置によれば、制御端子及び電流電極を有するスイッチング素子と、前記電流電極を外部の主配線に接続するための主配線用電流端子と、前記電流電極と前記主配線用電流端子との間の主電流経路に介在する、複数の制御用電流端子と、隣接する前記制御用電流端子間の前記主電流経路に介挿されたインダクタンスとを備えることにより、適切な特性の制御用エミッタ端子に切り替えて使用し、スイッチング過渡時のdi/dt(dv/dt)を可変させることができ、サージ電圧の低減及び発生ノイズの低減を実現することが可能となる。

【0012】

また、本発明にかかるスイッチングモジュールによれば、上記のスイッチング装置を複数備えることにより、サージ電圧の低減及び発生ノイズの低減を、モジュール内において実現することが可能となる。

【図面の簡単な説明】

【0013】

【図1】本発明の実施の形態1を示すスイッチング装置回路図である。

【図2】本発明の実施の形態1の、スイッチング装置とドライバ回路との接続を示す回路図である。

【図3】本発明の実施の形態2を示すスイッチング装置回路図である。

【図4】本発明の実施の形態2を示すスイッチング装置回路図である。

【図5】本発明の実施の形態2を示すスイッチング装置回路図である。

【発明を実施するための形態】

【0014】

<A.実施の形態1>

<A−1.構成>

図1に、本発明にかかるスイッチング装置の回路図を示す。図においてスイッチング素子1は例えばIGBTである。スイッチング装置は前記スイッチング素子1と、複数の制御用エミッタ端子5、制御用エミッタ端子6、制御用エミッタ端子7を有する。

【0015】

図示した、個々の制御用エミッタ端子5、制御用エミッタ端子6、制御用エミッタ端子7は、それぞれスイッチング素子1のエミッタ電極100との間のインダクタンスが異なる値となるようにスイッチング装置の内部配線に接続される。スイッチング装置内部では、個別のインダクタンス8、インダクタンス9が接続されている。

【0016】

具体的には、スイッチング素子1は、コレクタ端子2、制御端子としてのゲート端子3及び電流電極としてのエミッタ電極100を有し、さらに、前記エミッタ電極100側において、インダクタンス8、インダクタンス9を介して、主配線用電流端子としての主配線用エミッタ端子4を有している。

【0017】

エミッタ電極100と、主配線に接続するための主配線用エミッタ端子4とを結ぶ経路は主電流経路である。前記主電流経路上において、複数の制御用電流端子としての制御用エミッタ端子5、制御用エミッタ端子6、制御用エミッタ端子7が介在している。

【0018】

さらに前記主電流経路には、制御用エミッタ端子5、制御用エミッタ端子6、制御用エミッタ端子7の間にそれぞれ位置するインダクタンス8、インダクタンス9が備えられる。

【0019】

図2は、スイッチング装置とドライバ回路間の接続の一例を示す、スイッチング装置の回路図である。

【0020】

図2において、スイッチング素子1のゲート端子3は、ドライブ回路10に接続される。また、制御用エミッタ端子5、制御用エミッタ端子6は、切替えスイッチ11、切替えスイッチ12をそれぞれ介し、ドライブ回路10に接続される。なお切替えスイッチは、制御用エミッタ端子が備わる経路のうちのいずれかに備えられる場合であってもよい。

【0021】

ドライブ回路10は、ゲート端子3からスイッチング素子1にかかる電圧を制御し、スイッチング素子1を駆動する。切替えスイッチ11、切替えスイッチ12は、半導体スイッチを用いて実現可能である。切替えスイッチ11、切替えスイッチ12の制御機能は、ドライブ回路10に含むことも可能であるが、図示しない制御回路に含むことも可能である。図2では、切替えスイッチに対する制御信号線の図示を省略している。なお、制御用エミッタ端子7もドライブ回路10に接続される。

【0022】

主電流経路に流れる電流が時間的に変化する際に、主配線用エミッタ端子4と制御用エミッタ端子間のインダクタンス8、インダクタンス9に、電圧が発生する。発生した電圧により、負帰還としての効果が生ずることが一般に知られている。

【0023】

本発明は、異なるインダクタンスをもつ複数の制御用エミッタ端子5、制御用エミッタ端子6、制御用エミッタ端子7を使い分けることで、スイッチング過渡時の負帰還の効果を可変する。このようなスイッチング素子を備えるスイッチング装置、及び複数のスイッチング素子を備えるスイッチングモジュール等においても、同様に効果を発揮することができる。

【0024】

さらに、図2の切替えスイッチ11、切替えスイッチ12により、通常の電流遮断時と、過電流又は短絡保護の際の過大な電流遮断時とで制御用エミッタ端子5、制御用エミッタ端子6、制御用エミッタ端子7を使い分け、サージ電圧低減・発生ノイズ低減が可能となる。

【0025】

<A−2.効果>

本発明にかかる実施の形態1によれば、スイッチング装置において、制御端子及び電流電極を有するスイッチング素子と、電流電極としてのエミッタ電極100と、エミッタ電極100を外部の主配線に接続するための主配線用電流端子としての主配線用エミッタ端子4と、エミッタ電極100と主配線用エミッタ端子4との間の主電流経路に介在する、複数の制御用電流端子としての制御用エミッタ端子5、制御用エミッタ端子6、制御用エミッタ端子7と、隣接する制御用エミッタ端子5、制御用エミッタ端子6、制御用エミッタ端子7間の主電流経路に介挿されたインダクタンス8、インダクタンス9とを備えることで、適切な特性の制御用エミッタ端子に切り替えて使用し、スイッチング過渡時のdi/dt(dv/dt)を可変させることができ、サージ電圧の低減及び発生ノイズの低減を実現することが可能となる。

【0026】

また、本発明にかかる実施の形態1によれば、スイッチング装置において、スイッチング素子の制御端子としてのゲート端子3及び複数の制御用電流端子としての制御用エミッタ端子5、制御用エミッタ端子6、制御用エミッタ端子7に接続され、スイッチング素子を駆動するドライブ回路10と、ドライブ回路10と複数の制御用エミッタ端子5、制御用エミッタ端子6、制御用エミッタ端子7との間の少なくとも1つに介挿された切替えスイッチ11、切替えスイッチ12とをさらに備えることで、適切な特性の制御用エミッタ端子に切り替えて使用し、スイッチング過渡時のdi/dt(dv/dt)を可変させることができる。

【0027】

また、本発明にかかる実施の形態1によれば、スイッチング装置において、切替えスイッチ11、切替えスイッチ12の切替えにより、主電流経路のインダクタンスが異なることで、インダクタンスを適切に変更し、スイッチング過渡時のdi/dt(dv/dt)を可変させることができる。

【0028】

また、本発明にかかる実施の形態1によれば、スイッチングモジュールにおいて、上記のスイッチング装置を複数備えることで、サージ電圧の低減及び発生ノイズの低減を、モジュール内において実現することが可能となる。

【0029】

<B.実施の形態2>

<B−1.構成>

図3では、制御用エミッタ端子6、制御用エミッタ端子7と主電流経路との間に、制限抵抗13、制限抵抗14が備えられている。ここで制限抵抗とは、ゲート端子3に流出入するゲート電流を制限する抵抗であり、制御用エミッタ端子のうちのいずれかと主電流経路との間に備えられる場合であってもよい。また制限抵抗は、図2に示す構成においても適用可能である。

【0030】

制限抵抗13、制限抵抗14を備えることにより、負帰還によるdi/dt(dv/dt)可変だけでなく、制限抵抗による効果を加えることが可能となる。具体的には、ゲート端子3に流出入する電流(ゲート電流)値を調整することで、ゲート端子3が充放電される速度が調整される。小さい抵抗値ならば、ゲート電流は大きく、ゲート端子3の充放電は早くなる。このため、素子のターンオン・ターンオフ過渡時のdi/dt(dv/dt)が高くなる。大きい抵抗値ならば、ゲート電流は小さく、ゲート端子3の充放電は遅くなる。このため、素子のターンオン・ターンオフ過渡時のdi/dt(dv/dt)が低くなる。

【0031】

また図4に示すように、制御用エミッタ端子5、制御用エミッタ端子6と主電流経路との間に、制御エミッタ端子を切り替えるダイオード15、ダイオード16を備えることも可能である。ここでダイオードは、制御用エミッタ端子のうちのいずれかと主電流経路との間に備えられる場合であってもよい。

【0032】

当該ダイオード15、ダイオード16を備えることにより、例えば図2に示すドライブ回路と接続した際、外付けの切替えスイッチ11、切替えスイッチ12を介さずに、ターンオン/ターンオフ毎に制御用エミッタ端子を切替え可能となる。

【0033】

なお、図5に示すように、制限抵抗14と、ダイオード15、ダイオード16とを組み合わせた構成とすることも可能である。

【0034】

なお、実施の形態1、2においては、制御用エミッタ端子は2〜3本であるが、必要に応じ、その本数を変更することは可能である。また、制限抵抗、ダイオードの数、配置位置についても、適宜変更可能である。

【0035】

また、本発明の説明にあたってはIGBT素子を例に挙げ説明したが、本発明は、FET素子等、ゲート電圧において駆動する素子には適用可能である。なおFET素子を用いる場合には、エミッタ電極はソース電極に、主配線用エミッタ端子は主配線用ソース端子に、制御用エミッタ端子は制御用ソース端子に、それぞれ読み替える。

【0036】

また本発明は、Si素子を用いる場合に限らず、SiC素子を用いる場合にも適用可能である。SiC素子のスイッチング素子は一般に、Si素子に比べて高速動作するので、スイッチング過渡時のサージ電圧及び発生ノイズが大きくなりがちである。よって、SiC素子のスイッチング素子を用いる場合には、本発明のサージ電圧の低減及び発生ノイズの低減が特に有効である。

【0037】

また本発明は、複数の素子を搭載したIPM(Intelligent Power Module)等のモジュールにおいて、適用可能である。

【0038】

<B−2.効果>

本発明にかかる実施の形態2によれば、スイッチング装置において、複数の制御用電流端子としての制御用エミッタ端子5、制御用エミッタ端子6、制御用エミッタ端子7の少なくとも1つと主電流経路との間に、ダイオード15、ダイオード16をさらに備えることで、ターンオン又はターンオフのうちの一方の、スイッチング過渡時のdi/dt(dv/dt)を負帰還により可変させることができ、サージ電圧の低減及び発生ノイズの低減を実現することが可能となる。

【0039】

また、本発明にかかる実施の形態2によれば、スイッチング装置において、複数の制御用電流端子としての制御用エミッタ端子5、制御用エミッタ端子6、制御用エミッタ端子7の少なくとも1つと主電流経路との間に、制限抵抗13、制限抵抗14をさらに備えることで、抵抗によりdi/dt(dv/dt)を可変させることができ、サージ電圧の低減及び発生ノイズの低減を実現することが可能となる。

【符号の説明】

【0040】

1 スイッチング素子、2 コレクタ端子、3 ゲート端子、4 主配線用エミッタ端子、5〜7 制御用エミッタ端子、8,9 インダクタンス、10 ドライブ回路、11,12 切替えスイッチ、13,14 制限抵抗、15,16 ダイオード、100 エミッタ電極。

【特許請求の範囲】

【請求項1】

制御端子及び電流電極を有するスイッチング素子と、

前記電流電極を外部の主配線に接続するための主配線用電流端子と、

前記電流電極と前記主配線用電流端子との間の主電流経路に介在する、複数の制御用電流端子と、

隣接する前記制御用電流端子間の前記主電流経路に介挿されたインダクタンスとを備えることを特徴とする、

スイッチング装置。

【請求項2】

複数の前記制御用電流端子の少なくとも1つと前記主電流経路との間に、ダイオードをさらに備えることを特徴とする、

請求項1に記載のスイッチング装置。

【請求項3】

複数の前記制御用電流端子の少なくとも1つと前記主電流経路との間に、制限抵抗をさらに備えることを特徴とする、

請求項1又は2に記載のスイッチング装置。

【請求項4】

前記制御端子及び複数の前記制御用電流端子に接続され、前記スイッチング素子を駆動するドライブ回路と、

前記ドライブ回路と複数の前記制御用電流端子との間の少なくとも1つに介挿された切替えスイッチとをさらに備えることを特徴とする、

請求項1〜3のいずれかに記載のスイッチング装置。

【請求項5】

前記切替えスイッチの切替えにより、前記主電流経路のインダクタンスが異なることを特徴とする、

請求項4に記載のスイッチング装置。

【請求項6】

前記スイッチング素子はSiC素子であることを特徴とする、

請求項1〜5のいずれかに記載のスイッチング装置。

【請求項7】

請求項1〜6のいずれかに記載のスイッチング装置を複数備えることを特徴とする、

スイッチングモジュール。

【請求項1】

制御端子及び電流電極を有するスイッチング素子と、

前記電流電極を外部の主配線に接続するための主配線用電流端子と、

前記電流電極と前記主配線用電流端子との間の主電流経路に介在する、複数の制御用電流端子と、

隣接する前記制御用電流端子間の前記主電流経路に介挿されたインダクタンスとを備えることを特徴とする、

スイッチング装置。

【請求項2】

複数の前記制御用電流端子の少なくとも1つと前記主電流経路との間に、ダイオードをさらに備えることを特徴とする、

請求項1に記載のスイッチング装置。

【請求項3】

複数の前記制御用電流端子の少なくとも1つと前記主電流経路との間に、制限抵抗をさらに備えることを特徴とする、

請求項1又は2に記載のスイッチング装置。

【請求項4】

前記制御端子及び複数の前記制御用電流端子に接続され、前記スイッチング素子を駆動するドライブ回路と、

前記ドライブ回路と複数の前記制御用電流端子との間の少なくとも1つに介挿された切替えスイッチとをさらに備えることを特徴とする、

請求項1〜3のいずれかに記載のスイッチング装置。

【請求項5】

前記切替えスイッチの切替えにより、前記主電流経路のインダクタンスが異なることを特徴とする、

請求項4に記載のスイッチング装置。

【請求項6】

前記スイッチング素子はSiC素子であることを特徴とする、

請求項1〜5のいずれかに記載のスイッチング装置。

【請求項7】

請求項1〜6のいずれかに記載のスイッチング装置を複数備えることを特徴とする、

スイッチングモジュール。

【図1】

【図2】

【図3】

【図4】

【図5】

【図2】

【図3】

【図4】

【図5】

【公開番号】特開2012−222932(P2012−222932A)

【公開日】平成24年11月12日(2012.11.12)

【国際特許分類】

【出願番号】特願2011−85336(P2011−85336)

【出願日】平成23年4月7日(2011.4.7)

【出願人】(000006013)三菱電機株式会社 (33,312)

【Fターム(参考)】

【公開日】平成24年11月12日(2012.11.12)

【国際特許分類】

【出願日】平成23年4月7日(2011.4.7)

【出願人】(000006013)三菱電機株式会社 (33,312)

【Fターム(参考)】

[ Back to top ]