スイッチング装置

【課題】抵抗素子と容量素子との並列回路が半導体スイッチング素子のコレクタ−ゲート間に設けられている構成において、容量素子が過充電されないように放電経路を確保することができる、スイッチング装置の提供を目的とする。

【解決手段】半導体スイッチング素子Q1のスイッチング装置であって、半導体スイッチング素子Q1のコレクタ−ゲート間に設けられ、並列接続された抵抗素子R1と容量素子C1とを有する並列回路と、前記並列回路と前記コレクタとの間に設けられ、前記コレクタ側の向きに自身に印加される電圧が第1の基準値を超えると前記並列回路側の向きに電流を流すツェナーダイオードZ1,Z2と、前記並列回路と前記コレクタとの間に設けられ、前記並列回路側の向きに自身に印加される電圧が第2の基準値を超えると前記コレクタ側の向きに電流を流すツェナーダイオードZ3とを備えることを特徴とする、スイッチング装置。

【解決手段】半導体スイッチング素子Q1のスイッチング装置であって、半導体スイッチング素子Q1のコレクタ−ゲート間に設けられ、並列接続された抵抗素子R1と容量素子C1とを有する並列回路と、前記並列回路と前記コレクタとの間に設けられ、前記コレクタ側の向きに自身に印加される電圧が第1の基準値を超えると前記並列回路側の向きに電流を流すツェナーダイオードZ1,Z2と、前記並列回路と前記コレクタとの間に設けられ、前記並列回路側の向きに自身に印加される電圧が第2の基準値を超えると前記コレクタ側の向きに電流を流すツェナーダイオードZ3とを備えることを特徴とする、スイッチング装置。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、半導体スイッチング素子のスイッチング装置に関する。

【背景技術】

【0002】

従来技術として、コレクタとエミッタとゲートとを有する電力半導体コンポーネントをサージ電圧から保護する装置が知られている(例えば、特許文献1参照)。この保護装置は、図9(a)に示されるように、直列に接続されたn+N個のツェナーダイオードZ1からZn+Nを含む主枝路1と、主枝路1のN個のツェナーダイオードZn+1からZn+Nに並列に接続されたコンデンサ5を含む二次枝路2と、二次枝路2のコンデンサ5に並列に接続された抵抗器8を含む追加枝路3とを備えるものである。また、主枝路1は、n+N個のツェナーダイオードZ1からZn+Nに直列に接続された抵抗器6とそれらのn+N個のツェナーダイオードと逆向きの保護ダイオード7とを含んでいる。

【0003】

特許文献1の開示内容によると、主枝路1のN個のツェナーダイオードZn+1からZn+Nに並列にコンデンサ5を接続することによって、静的閾値電圧Vstatic(=(n+N)×Vz)と動的閾値電圧Vdynamic(=n×Vz)とを設けて、IGBTのオフ時にVceが動的閾値電圧Vdynamicへの到達によってサージ電圧を制限することを図っているとともに、IGBTが短絡などにより不飽和状態になった場合であっても、コンデンサ5に並列接続された抵抗器8を介して不飽和期間中にコンデンサ5を放電可能にすることによって、正常動作時と同様に、IGBTのオフ時のサージ電圧を動的閾値Vdynamicで制限することを図っている。

【特許文献1】特開2003−199325号公報

【発明の開示】

【発明が解決しようとする課題】

【0004】

ところで、図9(a)の保護ダイオード7は、一般に、ゲート側からコレクタ側に電流が回り込むことによる誤作動を防止する逆流防止ダイオードであることが知られている。しかしながら、図9(b)に示されるように、逆流防止ダイオードDをコンデンサCに対してコレクタ側に設けた構成では、コレクタに印加される電圧が高くなることによりコンデンサCに過電圧が印加されても、逆流防止ダイオードDの存在によって、放電抵抗Rを介してのみしか過充電分を放電できない。

【0005】

そこで、本発明は、抵抗素子と容量素子との並列回路が半導体スイッチング素子のコレクタ−ゲート間に設けられている構成において、当該容量素子が過充電されないように放電経路を確保することができる、スイッチング装置の提供を目的とする。

【課題を解決するための手段】

【0006】

上記目的を達成するため、第1の発明に係るスイッチング装置は、

半導体スイッチング素子を備え、

前記半導体スイッチング素子のスイッチング装置であって、

前記半導体スイッチング素子のコレクタ−ゲート間に設けられ、並列接続された抵抗素子と容量素子とを有する並列回路と、

前記並列回路と前記コレクタとの間に設けられ、前記コレクタ側の向きに自身に印加される電圧が第1の基準値を超えると前記並列回路側の向きに電流を流す第1の電流制限素子と、

前記並列回路と前記コレクタとの間に設けられ、前記並列回路側の向きに自身に印加される電圧が第2の基準値を超えると前記コレクタ側の向きに電流を流す第2の電流制限素子とを備えることを特徴とする。

【0007】

第2の発明は、第1の発明に係るスイッチング装置であって、

前記第2の基準値は、前記半導体スイッチング素子のコレクタの電圧上昇により前記並列回路の耐圧が超えないように設定されることを特徴とする。

【0008】

第3の発明は、第1又は第2の発明に係るスイッチング装置であって、

前記半導体スイッチング素子は、該半導体スイッチング素子のコレクタの電圧が変動し得るインバータ又はコンバータのスイッチング素子であることを特徴とする。

【0009】

第4の発明は、第1から第3のいずれか一の発明に係るスイッチング装置であって、

前記第2の電流制限素子は、ツェナーダイオードであることを特徴とする。

【0010】

第5の発明は、第1から第3のいずれか一の発明に係るスイッチング装置であって、

前記第2の電流制限素子は、バリスタであることを特徴とする。

【0011】

また、上記目的を達成するため、第6の発明に係るスイッチング装置は、

コレクタ−ゲート間に設けられ、並列接続された抵抗素子と容量素子とを有する並列回路と、

前記並列回路と前記コレクタとの間に設けられ、前記コレクタ側の向きに自身に印加される電圧が第1の基準値を超えると前記並列回路側の向きに電流を流す第1の電流制限素子と、

前記並列回路と前記コレクタとの間に設けられ、前記並列回路側の向きに自身に印加される電圧が第2の基準値を超えると前記コレクタ側の向きに電流を流す第2の電流制限素子と、を備える複数の半導体スイッチング素子を有し、

第1の半導体スイッチング素子のエミッタと第2の半導体スイッチング素子のコレクタとを接続した構成が含まれることを特徴とする。

【0012】

第7の発明は、第6の発明に係るスイッチング装置であって、

前記第2の基準値は、前記半導体スイッチング素子のコレクタの電圧上昇により前記並列回路の耐圧が超えないように設定されることを特徴とする。

【0013】

第8の発明は、第6又は第7の発明に係るスイッチング装置であって、

前記第1の半導体スイッチング素子は、該第1の半導体スイッチング素子のコレクタの電圧が変動し得るインバータ又はコンバータの上アーム素子であり、

前記第2の半導体スイッチング素子は、該第2の半導体スイッチング素子のコレクタの電圧が変動し得るインバータ又はコンバータの下アーム素子であることを特徴とする。

【0014】

第9の発明は、第6から第8のいずれか一の発明に係るスイッチング装置であって、

前記第2の電流制限素子は、ツェナーダイオードであることを特徴とする。

【0015】

第10の発明は、第6から第8のいずれか一の発明に係るスイッチング装置であって、

前記第2の電流制限素子は、バリスタであることを特徴とする。

【発明の効果】

【0016】

本発明によれば、抵抗素子と容量素子との並列回路が半導体スイッチング素子のコレクタ−ゲート間に設けられている構成において、当該容量素子が過充電されないように放電経路を確保することができる。

【発明を実施するための最良の形態】

【0017】

以下、図面を参照して、本発明を実施するための最良の形態の説明を行う。図1は、本発明に係るスイッチング装置の一実施形態であるモータ/ジェネレータ駆動システム100の概略構成図である。モータ/ジェネレータ駆動システム100は、直流電源の車載のバッテリ10と、バッテリ10の出力電圧を昇圧するDC−DCコンバータ20と、DC−DCコンバータ20による昇圧後の出力電圧(以下、「昇圧電圧」という)を安定させる平滑コンデンサ30と、DC−DCコンバータ20による昇圧電圧を三相交流に変換してブラシレスDCモータなどのモータ50を制御するインバータ40とを有している。なお、インバータ40は、ジェネレータ60によって発電された電力を制御するものでもよい。また、DC−DCコンバータ20は、インバータ40側からの入力電圧を降圧変換してその降圧電圧をバッテリ10側に出力するものでもよい。

【0018】

DC−DCコンバータ20は、スイッチングレギュレータなどの電圧変換制御回路によって、バッテリ10側の電圧を昇圧変換してインバータ40側に昇圧電圧を出力する(又は、インバータ40側の電圧を降圧変換してバッテリ10側に降圧電圧を出力する)。この昇圧電圧(インバータ40側の電圧)が、インバータ40内の、上アーム側のスイッチング素子と下アーム側のスイッチング素子とが接続された各相の直列回路の両端に印加される。電圧変換制御回路は、例えば、ダイオードD13をコレクタ−エミッタ間に並列に備える上アーム側のスイッチング素子Q13と、ダイオードD14をコレクタ−エミッタ間に並列に備える下アーム側のスイッチング素子Q14と、一端を素子Q13と素子Q14との接続点に接続され他端をバッテリ10の出力電位に接続されるリアクトル25と、素子Q13を駆動する駆動回路C13と、素子Q14を駆動する駆動回路C14とを備える。昇圧変換動作及び降圧変換動作は、周知のため、説明を省略する。

【0019】

DC−DCコンバータ20の正極端子22pは正側配線70pを介してインバータ40の正極入力端子41pに接続される。また、DC−DCコンバータ20の負極端子22nは負側配線70nを介してインバータ40の負極入力端子41nに接続される。

【0020】

インバータ40は、モータ50の制御回路46と、ジェネレータ60の制御回路47とを有する。制御回路46は、U相のスイッチング素子Q1(Q2)をスイッチングさせる駆動信号を出力する駆動回路C1(C2)と、V相のスイッチング素子Q3(Q4)をスイッチングさせる駆動信号を出力する駆動回路部C3(C4)と、W相のスイッチング素子Q5(Q6)をスイッチングさせる駆動信号を出力する駆動回路C5(C6)とを有する。制御回路46は、三相(U,V,W)の駆動信号(例えば、PWM信号)に従い各スイッチング素子のオン/オフを制御することによって、DC−DCコンバータ20による昇圧後の直流電力を交流電力に変換してモータ50を駆動する。すなわち、モータ50の三相巻線に制御回路46によって三相交流電流を流すと回転磁界が発生することを利用して、モータ50の回転が制御される。ジェネレータ60の制御回路47は、制御回路46と制御方法が異なるだけであって、制御回路46と同様の構成であるので、その説明を省略する。

【0021】

なお、スイッチング素子Q1〜Q14は、NチャンネルIGBT,NチャンネルMOSFET,npn型バイポーラトランジスタ等の半導体から構成される素子である。

【0022】

スイッチング素子Q1,3,5は、インバータ40の正極入力端子41pの電源電圧に短絡するハイサイドのスイッチング素子であり、スイッチング素子Q2,4,6は、インバータ40の負極入力端子41nのグランド電圧(基準電圧)に短絡するローサイドのスイッチング素子である。各スイッチング素子Q1〜6には、ダイオードが並列に接続(又は、内蔵)される。各ダイオードD1〜6は、グランドから電源電圧への方向(エミッタからコレクタへの方向)を順方向とする(電源電圧側がカソードとなる)。スイッチング素子Q13,Q14も同様である。

【0023】

スイッチング素子Q1とQ2との接続点Puは、インバータ40のU相出力端子42uを介して、モータ50のU相コイルに接続される。スイッチング素子Q3とQ4との接続点Pvは、インバータ40のV相出力端子42vを介して、モータ50のV相コイルに接続される。スイッチング素子Q5とQ6との接続点Pwは、インバータ40のW相出力端子42wを介して、モータ50のW相コイルに接続される。

【0024】

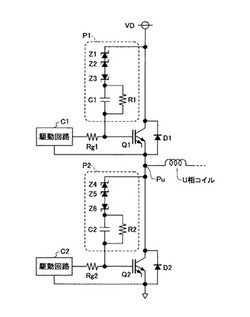

図2は、インバータ40のU相の制御回路の詳細構成図である。インバータ40の他相の制御回路についても同様の構成のため、その説明は省略する。DC−DCコンバータ20の電圧変換制御回路についても、同様の構成でもよい。

【0025】

スイッチング素子Q1は、直流電源の電源電圧VD(正極入力端子41pの電源電圧に相当)に短絡するハイサイドのスイッチング素子であり、スイッチング素子Q2は、グランド電圧(基準電圧)に短絡するローサイドのスイッチング素子である。スイッチング素子Q1,Q2のそれぞれのコレクタ−エミッタ間にはダイオードD1,D2が並列に接続(又は、内蔵)される。ダイオードD1,D2は、グランドから電源電圧への方向(エミッタからコレクタへの方向)を順方向とするフリーホイールダイオードである。スイッチング素子Q1のエミッタとQ2のコレクタとの接続点Puは、モータ50のU相コイルに接続される。

【0026】

また、ゲート駆動回路C1は、スイッチング素子Q1をスイッチングさせる駆動信号を出力し、ゲート抵抗Rg1を介して、スイッチング素子Q1をオン/オフさせる。同様に、ゲート駆動回路C2は、スイッチング素子Q2をスイッチングさせる駆動信号を出力し、ゲート抵抗Rg2を介して、スイッチングQ2をオン/オフさせる。

【0027】

スイッチング素子Q1(Q2)のコレクタ−ゲート間には、高耐圧ツェナーダイオードZ1,Z2(Z4,Z5)と、逆流及び過充電防止用ツェナーダイオードZ3(Z6)と、高耐圧コンデンサC1(C2)と放電用抵抗R1(R2)との並列回路とを備える。

【0028】

スイッチング素子Q1(Q2)のコレクタ−エミッタ間にサージが発生し、コレクタ−エミッタ間電圧Vceが直列接続されたツェナーZ1,Z2(Z4,Z5)の降伏電圧(ツェナー電圧)によって設定され得る切替閾値Vthを超えると、ツェナーZ1,Z2がオンして、ツェナーダイオードZ3(Z6)を介して、コンデンサC1(C2)の充電が始まる。スイッチング素子の駆動時にゲートからコレクタへ電流が流れるのを防止するツェナーダイオードZ3(Z6)は、サージ電圧が発生するコレクタ側との間にツェナーZ1,Z2(Z4,Z5)が存在するため、高耐圧品でなくてもよい(例えば、20V耐圧)。Z1等の高耐圧ツェナーダイオードの段数は、切替閾値Vthをどのような値に設定するかによって、決められる。例えば、切替閾値Vthを550Vに設定するならば、図2に示されるように、ツェナー電圧270Vの高耐圧ツェナーダイオード2段とダイオード1段とを直列に接続すればよい。このオーダーの耐圧であれば、小型の表面実装パッケージを利用することができる。このような製品は、市場に多品種流通しているので、豊富なツェナー電圧値を選択することができ、実機でのサージ電圧の調整作業も容易となる。

【0029】

切替閾値Vthの温度特性については、例えば、コレクタ−エミッタ間電圧の絶対最大定格Vces=1300V程度のIGBTでは、Vcesの温度係数が約+0.5〜0.6V/℃である。一方、Vthを550V付近に設定すれば、270Vツェナーの温度係数が約+0.25V/℃であるため、2段直列にすると約+0.5V/℃となる。したがって、ほぼVcesとVthの温度特性がそろうため、全温度範囲で安定した動作が可能となる。

【0030】

高耐圧コンデンサC1(C2)の耐圧は、高耐圧ツェナーZ1,Z2(Z4,Z5)と直列接続となるため、低く抑えることが可能となる。例えば、電源電圧VD(=650V)、コレクタ−エミッタ間に発生し得るサージ電圧が1000V以下、切替閾値Vth(=550V)とすれば、高耐圧コンデンサC1(C2)にかかる電圧は通常動作時でも最大で450Vになる。40%増しのマージンをみて630V耐圧品を使用したとしても、高耐圧ツェナーZ1,Z2(Z4,Z5)がない場合に比べ約半分の耐圧品を使用することができるようになる。コンデンサC1(C2)はスイッチング素子Q1(Q2)のコレクタ−ゲート間に接続されているため、ミラー効果が有効に働き、pFオーダーの小容量値(例えば、1000pF)にて十分な効果が得られる。つまり、コレクタ−エミッタ間電圧Vceが切替閾値Vth以上になると、等価的にスイッチング素子Q1(Q2)の帰還容量が増加するため、オフサージ電圧を抑制することができる。このオーダーの耐圧、容量値であれば、高周波特性に優れた小型のチップ積層セラミックコンデンサが使用できるようになる。また、チップ積層セラミックコンデンサは、市場に多品種流通しているため、豊富な定数が選択でき、実機でのサージ電圧調整作業も容易になる。

【0031】

放電用抵抗R1(R2)は、コンデンサC1(C2)に充電された電荷を放電するためのものである。スイッチング素子Q1(Q2)のコレクタ−エミッタ間に次のサージが発生する時(例えば、半導体スイッチング素子Q1(Q2)が次回ターンオフする時)までに、コンデンサC1(C2)の電圧が下限電圧(=VD−Vth)まで下がるような放電用抵抗R1(R2)が設定されるとよい(なお、下限電圧(=VD−Vth)は、ツェナーダイオードZ3(Z6)のダイオードドロップ分は除いている)。したがって、放電用抵抗R1(R2)の抵抗値は、kΩからMΩオーダー(例えば、1kΩ以上1MΩ以下)であればよい。

【0032】

放電用抵抗R1(R2)の抵抗値を高く設定することによって、切替閾値Vthを電源電圧VDより低く設定することができる。高抵抗値にすることによってツェナーZ1,Z2(Z4,Z5)を介してコレクタ側から常時流れる電流は微小となるため、発熱は無視できるからである。したがって、切替閾値Vthは、電源電圧VDより低くも高くも設定できるので、回路定数を広範囲に調整することができる。

【0033】

図3は、オフサージ電圧を抑制する場合のタイミングチャートを示す。Pはスイッチング素子Qの損失(P=Vce×Ice)であり、Vceはコレクタ−エミッタ間電圧、Iceはコレクタ電流、Ptonはターンオン時のスイッチング損失、Ptoffはターンオフ時のスイッチング損失を示す。点線波形は図2の保護回路P1(P2)を有する場合の波形を示し、実線波形は図2の保護回路P1(P2)を有しない場合の波形を示す。スイッチング素子Q1(Q2)がターンオフ時において、Vceが切替閾値Vth以下のときには保護回路P1(P2)の有無で差がない。しかしながら、Vceが切替閾値Vthを超えると、ツェナーZ1,Z2(Z4,Z5)がオンして、ツェナーダイオードZ3(Z6)を介して、コンデンサC1の充電が始まる。コンデンサC1はスイッチング素子Q1(Q2)のコレクタ−ゲート間に接続されているため、ミラー効果が有効に働き、pFオーダーの小容量値にて十分な効果が得られる。つまり、VceがVth以上になると、スイッチング素子Q1(Q2)のゲート−コレクタ間の寄生容量にコンデンサC1(C2)が並列接続されることにより、等価的にスイッチング素子Q1(Q2)の帰還容量が増加するため、オフサージ電圧を抑制することができる。

【0034】

図4は、スイッチング損失を抑制する場合のタイミングチャートを示す。点線波形は図2の保護回路P1(P2)を有する場合の波形を示し、実線波形は図2の保護回路P1(P2)を有しない場合の波形を示す。スイッチング損失を低減する場合は、ゲート抵抗Rg1(Rg2)の抵抗値を下げることによって、Vceの立ち上がりを高速化することによって損失を低減することができる。

【0035】

また、Rg1,Rg2の抵抗値を調整することによって、オフサージ電圧を抑えつつ、スイッチング損失を低減することも可能である。つまり、オフサージ電圧とスイッチング損失の抑制というトレードオフ特性を改善することができる。

【0036】

図5は、高耐圧コンデンサC1,C2の容量値を1000pFとした場合のオフサージ電圧の波形を示した図である。図5に示されるように、保護回路P1(P2)を有しない場合の実線波形に比べ、保護回路P1(P2)を有する場合の点線波形のほうが、ターンオフ時のサージ電圧を低減することができる。

【0037】

なお、図2の回路構成の制御応答は、高耐圧ツェナーZ1,Z2(Z4,Z5)のスイッチング時間(オフからオンまでの時間)が支配的である。ノイズリミッタやサージ吸収用ダイオードとして使用されることも多い高耐圧ツェナーのスイッチング時間は十分無視できる値であるため、制御遅れによりサージ電圧が増大するというおそれはなく、スイッチング周波数の高周波化にも容易に対応することができる。

【0038】

ところで、図1に示されるように、電源電圧VDはDC−DCコンバータ20と平滑コンデンサ30などによって略一定値に制御されているところ、モータ50の回生やジェネレータ60の発電やDC−DCコンバータ20の故障などによって、電源電圧VDが急激に変動する場合がある。DC−DCコンバータ20の出力経路やモータ50の回生電力の回収経路やジェネレータ50の発電電力の回収経路が電源電圧VDに接続されているからである。特に、DC−DCコンバータ20等のこれらの複数の制御装置が電源電圧VDに接続されていると、電源電圧VDの変動要因となり得る現象が重複して発生することによって、想定以上に電源電圧VDが急増したり急減したりするおそれがある。また、スイッチング素子Q1がオン状態のときに電源電圧VDが急変すれば、接続点Puの電圧(スイッチング素子Q2のコレクタ電圧)も急変することになる。

【0039】

電源電圧VDが増加すると、図2に示されるように、ツェナーダイオードZ1,Z2(Z4,Z5)とツェナーダイオードZ3(Z6)を介して、コンデンサC1(C2)に電圧(=VD−降伏電圧−ダイオード順方向電圧)が印加されることになる。しかしながら、ツェナーダイオードZ3(Z6)のツェナー電圧をコンデンサC1(C2)及び抵抗R1(R2)の耐圧を超えないように設定することによって、コンデンサC1(C2)が過充電や過電圧になる前に、放電用抵抗R1(R2)を通る放電経路とツェナーダイオードZ3(Z6)を通る放電経路の2つの経路でのコンデンサC1(C2)の放電が可能となる。コンデンサC1(C2)からの放電電力は、スイッチング素子Q1がオフ状態であっても、正極入力端子41pを介して、平滑コンデンサ30やDC−DCコンバータ20に供給される。

【0040】

ツェナーダイオードZ3(Z6)のツェナー電圧は、コンデンサC1(C2)の耐圧値より小さい値に設定するとよい。例えば、コンデンサC1(C2)の耐圧が630Vの場合、その耐圧値より小さい560Vのツェナー電圧を有するツェナーダイオードをZ3(Z6)として選定すればよい。また、ツェナーダイオードZ3(Z6)のツェナー電圧は、スイッチング素子Q1(Q2)をオンにするためゲート電圧を印加するときに放電用抵抗R1(R2)を介してゲート側からコレクタ側に電流が流れないように、スイッチング素子Q1(Q2)をオンにするためのゲート電圧より大きい値に設定するとよい。

【0041】

このように、ツェナーダイオードZ3(Z6)を通る放電経路が新たに形成されることによって、放電用抵抗R1(R2)に流れる電流が減少するため、消費電力が抑えられ、放電用抵抗R1(R2)の定格を下げることができる。また、過充電や過電圧によるコンデンサC1(C2)や放電用抵抗R1(R2)のショート等の故障を防ぐことができる。逆に、ツェナーダイオードZ3(Z6)のツェナー電圧に応じて、コンデンサC1(C2)や放電用抵抗R1(R2)の耐圧等の定格を下げるなどの調整をすることも可能になる。もちろん、インバータ40やDC−DCコンバータ20における他の上下アームの放電抵抗についても同様のことが言える。

【0042】

したがって、上述の実施例によれば、電源電圧VDが上昇しても、放電経路を確保して、放電用抵抗の消費電力の抑制や過充電によるコンデンサの破壊などを防止することができる。すなわち、コンデンサで受け入れた大電圧がツェナーダイオードZ3(Z6)の閾値を超える電圧であればコレクタ側に戻され得るので、放電用抵抗に流れる電流の減少やコンデンサの過電圧の低減を図ることができる。

【0043】

以上、本発明の好ましい実施例について詳説したが、本発明は、上述した実施例に制限されることはなく、本発明の範囲を逸脱することなく、上述した実施例に種々の変形及び置換を加えることができる。

【0044】

図6は、高耐圧ツェナーダイオードZ1,Z2(Z4、Z5)及びツェナーダイオードZ3(Z6)との代わりに、バリスタV1(V2)を使った場合の構成図である。この場合も、上述の図2の場合と同様の効果が得られる。バリスタも積層セラミック製のチップ部品が多品種で流通しているため、サージ電圧の調整も容易となる。バリスタは、非直線性抵抗素子であって、印加電圧が高くなると急激にその電気抵抗が小さくなる性質を有する。抵抗値が急激に下がるときの電圧をバリスタ電圧という。

【0045】

図7は、スイッチング素子Q1のゲートエミッタ間にプルダウン抵抗Rpdを追加した場合の回路である。高耐圧ツェナーダイオードZ1,Z2の寄生容量値が、コンデンサC1に対して無視できない場合には、例えば、スイッチング素子Q1のゲートエミッタ間にプルダウン抵抗Rpdを追加するなどによって、ゲインを調整することもできる。つまり、スイッチング素子Q1のゲートに流れ込む電流の一部をRpdで分流することにより、ツェナーダイオードZ1,Z2の寄生容量の影響を解消することができる。

【0046】

図8は、スイッチング素子Q1のゲートの直前に抵抗Rlpfを追加した場合の回路である。抵抗Rlpfとスイッチング素子Q1のゲート容量とによってローパスフィルタを形成することができるので、高周波成分のノイズをカットすることができ、回路をより安定動作させることができる。

【図面の簡単な説明】

【0047】

【図1】本発明に係るスイッチング装置の一実施形態であるモータ/ジェネレータ駆動システム100の概略構成図である。

【図2】インバータ40のU相の制御回路の詳細構成図である。

【図3】オフサージ電圧を抑制する場合のタイミングチャートを示す。

【図4】スイッチング損失を抑制する場合のタイミングチャートを示す。

【図5】高耐圧コンデンサC1,C2の容量値を1000pFとした場合のオフサージ電圧の波形を示した図である。

【図6】高耐圧ツェナーダイオードZ1,Z2(Z4、Z5)及びツェナーダイオードZ3(Z6)との代わりに、バリスタV1(V2)を使った場合の構成図である。

【図7】スイッチング素子Q1のゲートエミッタ間にプルダウン抵抗Rpdを追加した場合の回路である。

【図8】スイッチング素子Q1のゲートの直前に抵抗Rlpfを追加した場合の回路である。

【図9】保護回路の一例である。

【符号の説明】

【0048】

Z1,Z2,Z4,Z5 高耐圧ツェナーダイオード

Z3,Z6 逆流及び過充電防止用ツェナーダイオード

C1,C2 コンデンサ

R1,R2 放電用抵抗

Q1〜Q14 スイッチング素子

P1,P2 保護回路

VD 電源電圧

V1,V2 バリスタ

【技術分野】

【0001】

本発明は、半導体スイッチング素子のスイッチング装置に関する。

【背景技術】

【0002】

従来技術として、コレクタとエミッタとゲートとを有する電力半導体コンポーネントをサージ電圧から保護する装置が知られている(例えば、特許文献1参照)。この保護装置は、図9(a)に示されるように、直列に接続されたn+N個のツェナーダイオードZ1からZn+Nを含む主枝路1と、主枝路1のN個のツェナーダイオードZn+1からZn+Nに並列に接続されたコンデンサ5を含む二次枝路2と、二次枝路2のコンデンサ5に並列に接続された抵抗器8を含む追加枝路3とを備えるものである。また、主枝路1は、n+N個のツェナーダイオードZ1からZn+Nに直列に接続された抵抗器6とそれらのn+N個のツェナーダイオードと逆向きの保護ダイオード7とを含んでいる。

【0003】

特許文献1の開示内容によると、主枝路1のN個のツェナーダイオードZn+1からZn+Nに並列にコンデンサ5を接続することによって、静的閾値電圧Vstatic(=(n+N)×Vz)と動的閾値電圧Vdynamic(=n×Vz)とを設けて、IGBTのオフ時にVceが動的閾値電圧Vdynamicへの到達によってサージ電圧を制限することを図っているとともに、IGBTが短絡などにより不飽和状態になった場合であっても、コンデンサ5に並列接続された抵抗器8を介して不飽和期間中にコンデンサ5を放電可能にすることによって、正常動作時と同様に、IGBTのオフ時のサージ電圧を動的閾値Vdynamicで制限することを図っている。

【特許文献1】特開2003−199325号公報

【発明の開示】

【発明が解決しようとする課題】

【0004】

ところで、図9(a)の保護ダイオード7は、一般に、ゲート側からコレクタ側に電流が回り込むことによる誤作動を防止する逆流防止ダイオードであることが知られている。しかしながら、図9(b)に示されるように、逆流防止ダイオードDをコンデンサCに対してコレクタ側に設けた構成では、コレクタに印加される電圧が高くなることによりコンデンサCに過電圧が印加されても、逆流防止ダイオードDの存在によって、放電抵抗Rを介してのみしか過充電分を放電できない。

【0005】

そこで、本発明は、抵抗素子と容量素子との並列回路が半導体スイッチング素子のコレクタ−ゲート間に設けられている構成において、当該容量素子が過充電されないように放電経路を確保することができる、スイッチング装置の提供を目的とする。

【課題を解決するための手段】

【0006】

上記目的を達成するため、第1の発明に係るスイッチング装置は、

半導体スイッチング素子を備え、

前記半導体スイッチング素子のスイッチング装置であって、

前記半導体スイッチング素子のコレクタ−ゲート間に設けられ、並列接続された抵抗素子と容量素子とを有する並列回路と、

前記並列回路と前記コレクタとの間に設けられ、前記コレクタ側の向きに自身に印加される電圧が第1の基準値を超えると前記並列回路側の向きに電流を流す第1の電流制限素子と、

前記並列回路と前記コレクタとの間に設けられ、前記並列回路側の向きに自身に印加される電圧が第2の基準値を超えると前記コレクタ側の向きに電流を流す第2の電流制限素子とを備えることを特徴とする。

【0007】

第2の発明は、第1の発明に係るスイッチング装置であって、

前記第2の基準値は、前記半導体スイッチング素子のコレクタの電圧上昇により前記並列回路の耐圧が超えないように設定されることを特徴とする。

【0008】

第3の発明は、第1又は第2の発明に係るスイッチング装置であって、

前記半導体スイッチング素子は、該半導体スイッチング素子のコレクタの電圧が変動し得るインバータ又はコンバータのスイッチング素子であることを特徴とする。

【0009】

第4の発明は、第1から第3のいずれか一の発明に係るスイッチング装置であって、

前記第2の電流制限素子は、ツェナーダイオードであることを特徴とする。

【0010】

第5の発明は、第1から第3のいずれか一の発明に係るスイッチング装置であって、

前記第2の電流制限素子は、バリスタであることを特徴とする。

【0011】

また、上記目的を達成するため、第6の発明に係るスイッチング装置は、

コレクタ−ゲート間に設けられ、並列接続された抵抗素子と容量素子とを有する並列回路と、

前記並列回路と前記コレクタとの間に設けられ、前記コレクタ側の向きに自身に印加される電圧が第1の基準値を超えると前記並列回路側の向きに電流を流す第1の電流制限素子と、

前記並列回路と前記コレクタとの間に設けられ、前記並列回路側の向きに自身に印加される電圧が第2の基準値を超えると前記コレクタ側の向きに電流を流す第2の電流制限素子と、を備える複数の半導体スイッチング素子を有し、

第1の半導体スイッチング素子のエミッタと第2の半導体スイッチング素子のコレクタとを接続した構成が含まれることを特徴とする。

【0012】

第7の発明は、第6の発明に係るスイッチング装置であって、

前記第2の基準値は、前記半導体スイッチング素子のコレクタの電圧上昇により前記並列回路の耐圧が超えないように設定されることを特徴とする。

【0013】

第8の発明は、第6又は第7の発明に係るスイッチング装置であって、

前記第1の半導体スイッチング素子は、該第1の半導体スイッチング素子のコレクタの電圧が変動し得るインバータ又はコンバータの上アーム素子であり、

前記第2の半導体スイッチング素子は、該第2の半導体スイッチング素子のコレクタの電圧が変動し得るインバータ又はコンバータの下アーム素子であることを特徴とする。

【0014】

第9の発明は、第6から第8のいずれか一の発明に係るスイッチング装置であって、

前記第2の電流制限素子は、ツェナーダイオードであることを特徴とする。

【0015】

第10の発明は、第6から第8のいずれか一の発明に係るスイッチング装置であって、

前記第2の電流制限素子は、バリスタであることを特徴とする。

【発明の効果】

【0016】

本発明によれば、抵抗素子と容量素子との並列回路が半導体スイッチング素子のコレクタ−ゲート間に設けられている構成において、当該容量素子が過充電されないように放電経路を確保することができる。

【発明を実施するための最良の形態】

【0017】

以下、図面を参照して、本発明を実施するための最良の形態の説明を行う。図1は、本発明に係るスイッチング装置の一実施形態であるモータ/ジェネレータ駆動システム100の概略構成図である。モータ/ジェネレータ駆動システム100は、直流電源の車載のバッテリ10と、バッテリ10の出力電圧を昇圧するDC−DCコンバータ20と、DC−DCコンバータ20による昇圧後の出力電圧(以下、「昇圧電圧」という)を安定させる平滑コンデンサ30と、DC−DCコンバータ20による昇圧電圧を三相交流に変換してブラシレスDCモータなどのモータ50を制御するインバータ40とを有している。なお、インバータ40は、ジェネレータ60によって発電された電力を制御するものでもよい。また、DC−DCコンバータ20は、インバータ40側からの入力電圧を降圧変換してその降圧電圧をバッテリ10側に出力するものでもよい。

【0018】

DC−DCコンバータ20は、スイッチングレギュレータなどの電圧変換制御回路によって、バッテリ10側の電圧を昇圧変換してインバータ40側に昇圧電圧を出力する(又は、インバータ40側の電圧を降圧変換してバッテリ10側に降圧電圧を出力する)。この昇圧電圧(インバータ40側の電圧)が、インバータ40内の、上アーム側のスイッチング素子と下アーム側のスイッチング素子とが接続された各相の直列回路の両端に印加される。電圧変換制御回路は、例えば、ダイオードD13をコレクタ−エミッタ間に並列に備える上アーム側のスイッチング素子Q13と、ダイオードD14をコレクタ−エミッタ間に並列に備える下アーム側のスイッチング素子Q14と、一端を素子Q13と素子Q14との接続点に接続され他端をバッテリ10の出力電位に接続されるリアクトル25と、素子Q13を駆動する駆動回路C13と、素子Q14を駆動する駆動回路C14とを備える。昇圧変換動作及び降圧変換動作は、周知のため、説明を省略する。

【0019】

DC−DCコンバータ20の正極端子22pは正側配線70pを介してインバータ40の正極入力端子41pに接続される。また、DC−DCコンバータ20の負極端子22nは負側配線70nを介してインバータ40の負極入力端子41nに接続される。

【0020】

インバータ40は、モータ50の制御回路46と、ジェネレータ60の制御回路47とを有する。制御回路46は、U相のスイッチング素子Q1(Q2)をスイッチングさせる駆動信号を出力する駆動回路C1(C2)と、V相のスイッチング素子Q3(Q4)をスイッチングさせる駆動信号を出力する駆動回路部C3(C4)と、W相のスイッチング素子Q5(Q6)をスイッチングさせる駆動信号を出力する駆動回路C5(C6)とを有する。制御回路46は、三相(U,V,W)の駆動信号(例えば、PWM信号)に従い各スイッチング素子のオン/オフを制御することによって、DC−DCコンバータ20による昇圧後の直流電力を交流電力に変換してモータ50を駆動する。すなわち、モータ50の三相巻線に制御回路46によって三相交流電流を流すと回転磁界が発生することを利用して、モータ50の回転が制御される。ジェネレータ60の制御回路47は、制御回路46と制御方法が異なるだけであって、制御回路46と同様の構成であるので、その説明を省略する。

【0021】

なお、スイッチング素子Q1〜Q14は、NチャンネルIGBT,NチャンネルMOSFET,npn型バイポーラトランジスタ等の半導体から構成される素子である。

【0022】

スイッチング素子Q1,3,5は、インバータ40の正極入力端子41pの電源電圧に短絡するハイサイドのスイッチング素子であり、スイッチング素子Q2,4,6は、インバータ40の負極入力端子41nのグランド電圧(基準電圧)に短絡するローサイドのスイッチング素子である。各スイッチング素子Q1〜6には、ダイオードが並列に接続(又は、内蔵)される。各ダイオードD1〜6は、グランドから電源電圧への方向(エミッタからコレクタへの方向)を順方向とする(電源電圧側がカソードとなる)。スイッチング素子Q13,Q14も同様である。

【0023】

スイッチング素子Q1とQ2との接続点Puは、インバータ40のU相出力端子42uを介して、モータ50のU相コイルに接続される。スイッチング素子Q3とQ4との接続点Pvは、インバータ40のV相出力端子42vを介して、モータ50のV相コイルに接続される。スイッチング素子Q5とQ6との接続点Pwは、インバータ40のW相出力端子42wを介して、モータ50のW相コイルに接続される。

【0024】

図2は、インバータ40のU相の制御回路の詳細構成図である。インバータ40の他相の制御回路についても同様の構成のため、その説明は省略する。DC−DCコンバータ20の電圧変換制御回路についても、同様の構成でもよい。

【0025】

スイッチング素子Q1は、直流電源の電源電圧VD(正極入力端子41pの電源電圧に相当)に短絡するハイサイドのスイッチング素子であり、スイッチング素子Q2は、グランド電圧(基準電圧)に短絡するローサイドのスイッチング素子である。スイッチング素子Q1,Q2のそれぞれのコレクタ−エミッタ間にはダイオードD1,D2が並列に接続(又は、内蔵)される。ダイオードD1,D2は、グランドから電源電圧への方向(エミッタからコレクタへの方向)を順方向とするフリーホイールダイオードである。スイッチング素子Q1のエミッタとQ2のコレクタとの接続点Puは、モータ50のU相コイルに接続される。

【0026】

また、ゲート駆動回路C1は、スイッチング素子Q1をスイッチングさせる駆動信号を出力し、ゲート抵抗Rg1を介して、スイッチング素子Q1をオン/オフさせる。同様に、ゲート駆動回路C2は、スイッチング素子Q2をスイッチングさせる駆動信号を出力し、ゲート抵抗Rg2を介して、スイッチングQ2をオン/オフさせる。

【0027】

スイッチング素子Q1(Q2)のコレクタ−ゲート間には、高耐圧ツェナーダイオードZ1,Z2(Z4,Z5)と、逆流及び過充電防止用ツェナーダイオードZ3(Z6)と、高耐圧コンデンサC1(C2)と放電用抵抗R1(R2)との並列回路とを備える。

【0028】

スイッチング素子Q1(Q2)のコレクタ−エミッタ間にサージが発生し、コレクタ−エミッタ間電圧Vceが直列接続されたツェナーZ1,Z2(Z4,Z5)の降伏電圧(ツェナー電圧)によって設定され得る切替閾値Vthを超えると、ツェナーZ1,Z2がオンして、ツェナーダイオードZ3(Z6)を介して、コンデンサC1(C2)の充電が始まる。スイッチング素子の駆動時にゲートからコレクタへ電流が流れるのを防止するツェナーダイオードZ3(Z6)は、サージ電圧が発生するコレクタ側との間にツェナーZ1,Z2(Z4,Z5)が存在するため、高耐圧品でなくてもよい(例えば、20V耐圧)。Z1等の高耐圧ツェナーダイオードの段数は、切替閾値Vthをどのような値に設定するかによって、決められる。例えば、切替閾値Vthを550Vに設定するならば、図2に示されるように、ツェナー電圧270Vの高耐圧ツェナーダイオード2段とダイオード1段とを直列に接続すればよい。このオーダーの耐圧であれば、小型の表面実装パッケージを利用することができる。このような製品は、市場に多品種流通しているので、豊富なツェナー電圧値を選択することができ、実機でのサージ電圧の調整作業も容易となる。

【0029】

切替閾値Vthの温度特性については、例えば、コレクタ−エミッタ間電圧の絶対最大定格Vces=1300V程度のIGBTでは、Vcesの温度係数が約+0.5〜0.6V/℃である。一方、Vthを550V付近に設定すれば、270Vツェナーの温度係数が約+0.25V/℃であるため、2段直列にすると約+0.5V/℃となる。したがって、ほぼVcesとVthの温度特性がそろうため、全温度範囲で安定した動作が可能となる。

【0030】

高耐圧コンデンサC1(C2)の耐圧は、高耐圧ツェナーZ1,Z2(Z4,Z5)と直列接続となるため、低く抑えることが可能となる。例えば、電源電圧VD(=650V)、コレクタ−エミッタ間に発生し得るサージ電圧が1000V以下、切替閾値Vth(=550V)とすれば、高耐圧コンデンサC1(C2)にかかる電圧は通常動作時でも最大で450Vになる。40%増しのマージンをみて630V耐圧品を使用したとしても、高耐圧ツェナーZ1,Z2(Z4,Z5)がない場合に比べ約半分の耐圧品を使用することができるようになる。コンデンサC1(C2)はスイッチング素子Q1(Q2)のコレクタ−ゲート間に接続されているため、ミラー効果が有効に働き、pFオーダーの小容量値(例えば、1000pF)にて十分な効果が得られる。つまり、コレクタ−エミッタ間電圧Vceが切替閾値Vth以上になると、等価的にスイッチング素子Q1(Q2)の帰還容量が増加するため、オフサージ電圧を抑制することができる。このオーダーの耐圧、容量値であれば、高周波特性に優れた小型のチップ積層セラミックコンデンサが使用できるようになる。また、チップ積層セラミックコンデンサは、市場に多品種流通しているため、豊富な定数が選択でき、実機でのサージ電圧調整作業も容易になる。

【0031】

放電用抵抗R1(R2)は、コンデンサC1(C2)に充電された電荷を放電するためのものである。スイッチング素子Q1(Q2)のコレクタ−エミッタ間に次のサージが発生する時(例えば、半導体スイッチング素子Q1(Q2)が次回ターンオフする時)までに、コンデンサC1(C2)の電圧が下限電圧(=VD−Vth)まで下がるような放電用抵抗R1(R2)が設定されるとよい(なお、下限電圧(=VD−Vth)は、ツェナーダイオードZ3(Z6)のダイオードドロップ分は除いている)。したがって、放電用抵抗R1(R2)の抵抗値は、kΩからMΩオーダー(例えば、1kΩ以上1MΩ以下)であればよい。

【0032】

放電用抵抗R1(R2)の抵抗値を高く設定することによって、切替閾値Vthを電源電圧VDより低く設定することができる。高抵抗値にすることによってツェナーZ1,Z2(Z4,Z5)を介してコレクタ側から常時流れる電流は微小となるため、発熱は無視できるからである。したがって、切替閾値Vthは、電源電圧VDより低くも高くも設定できるので、回路定数を広範囲に調整することができる。

【0033】

図3は、オフサージ電圧を抑制する場合のタイミングチャートを示す。Pはスイッチング素子Qの損失(P=Vce×Ice)であり、Vceはコレクタ−エミッタ間電圧、Iceはコレクタ電流、Ptonはターンオン時のスイッチング損失、Ptoffはターンオフ時のスイッチング損失を示す。点線波形は図2の保護回路P1(P2)を有する場合の波形を示し、実線波形は図2の保護回路P1(P2)を有しない場合の波形を示す。スイッチング素子Q1(Q2)がターンオフ時において、Vceが切替閾値Vth以下のときには保護回路P1(P2)の有無で差がない。しかしながら、Vceが切替閾値Vthを超えると、ツェナーZ1,Z2(Z4,Z5)がオンして、ツェナーダイオードZ3(Z6)を介して、コンデンサC1の充電が始まる。コンデンサC1はスイッチング素子Q1(Q2)のコレクタ−ゲート間に接続されているため、ミラー効果が有効に働き、pFオーダーの小容量値にて十分な効果が得られる。つまり、VceがVth以上になると、スイッチング素子Q1(Q2)のゲート−コレクタ間の寄生容量にコンデンサC1(C2)が並列接続されることにより、等価的にスイッチング素子Q1(Q2)の帰還容量が増加するため、オフサージ電圧を抑制することができる。

【0034】

図4は、スイッチング損失を抑制する場合のタイミングチャートを示す。点線波形は図2の保護回路P1(P2)を有する場合の波形を示し、実線波形は図2の保護回路P1(P2)を有しない場合の波形を示す。スイッチング損失を低減する場合は、ゲート抵抗Rg1(Rg2)の抵抗値を下げることによって、Vceの立ち上がりを高速化することによって損失を低減することができる。

【0035】

また、Rg1,Rg2の抵抗値を調整することによって、オフサージ電圧を抑えつつ、スイッチング損失を低減することも可能である。つまり、オフサージ電圧とスイッチング損失の抑制というトレードオフ特性を改善することができる。

【0036】

図5は、高耐圧コンデンサC1,C2の容量値を1000pFとした場合のオフサージ電圧の波形を示した図である。図5に示されるように、保護回路P1(P2)を有しない場合の実線波形に比べ、保護回路P1(P2)を有する場合の点線波形のほうが、ターンオフ時のサージ電圧を低減することができる。

【0037】

なお、図2の回路構成の制御応答は、高耐圧ツェナーZ1,Z2(Z4,Z5)のスイッチング時間(オフからオンまでの時間)が支配的である。ノイズリミッタやサージ吸収用ダイオードとして使用されることも多い高耐圧ツェナーのスイッチング時間は十分無視できる値であるため、制御遅れによりサージ電圧が増大するというおそれはなく、スイッチング周波数の高周波化にも容易に対応することができる。

【0038】

ところで、図1に示されるように、電源電圧VDはDC−DCコンバータ20と平滑コンデンサ30などによって略一定値に制御されているところ、モータ50の回生やジェネレータ60の発電やDC−DCコンバータ20の故障などによって、電源電圧VDが急激に変動する場合がある。DC−DCコンバータ20の出力経路やモータ50の回生電力の回収経路やジェネレータ50の発電電力の回収経路が電源電圧VDに接続されているからである。特に、DC−DCコンバータ20等のこれらの複数の制御装置が電源電圧VDに接続されていると、電源電圧VDの変動要因となり得る現象が重複して発生することによって、想定以上に電源電圧VDが急増したり急減したりするおそれがある。また、スイッチング素子Q1がオン状態のときに電源電圧VDが急変すれば、接続点Puの電圧(スイッチング素子Q2のコレクタ電圧)も急変することになる。

【0039】

電源電圧VDが増加すると、図2に示されるように、ツェナーダイオードZ1,Z2(Z4,Z5)とツェナーダイオードZ3(Z6)を介して、コンデンサC1(C2)に電圧(=VD−降伏電圧−ダイオード順方向電圧)が印加されることになる。しかしながら、ツェナーダイオードZ3(Z6)のツェナー電圧をコンデンサC1(C2)及び抵抗R1(R2)の耐圧を超えないように設定することによって、コンデンサC1(C2)が過充電や過電圧になる前に、放電用抵抗R1(R2)を通る放電経路とツェナーダイオードZ3(Z6)を通る放電経路の2つの経路でのコンデンサC1(C2)の放電が可能となる。コンデンサC1(C2)からの放電電力は、スイッチング素子Q1がオフ状態であっても、正極入力端子41pを介して、平滑コンデンサ30やDC−DCコンバータ20に供給される。

【0040】

ツェナーダイオードZ3(Z6)のツェナー電圧は、コンデンサC1(C2)の耐圧値より小さい値に設定するとよい。例えば、コンデンサC1(C2)の耐圧が630Vの場合、その耐圧値より小さい560Vのツェナー電圧を有するツェナーダイオードをZ3(Z6)として選定すればよい。また、ツェナーダイオードZ3(Z6)のツェナー電圧は、スイッチング素子Q1(Q2)をオンにするためゲート電圧を印加するときに放電用抵抗R1(R2)を介してゲート側からコレクタ側に電流が流れないように、スイッチング素子Q1(Q2)をオンにするためのゲート電圧より大きい値に設定するとよい。

【0041】

このように、ツェナーダイオードZ3(Z6)を通る放電経路が新たに形成されることによって、放電用抵抗R1(R2)に流れる電流が減少するため、消費電力が抑えられ、放電用抵抗R1(R2)の定格を下げることができる。また、過充電や過電圧によるコンデンサC1(C2)や放電用抵抗R1(R2)のショート等の故障を防ぐことができる。逆に、ツェナーダイオードZ3(Z6)のツェナー電圧に応じて、コンデンサC1(C2)や放電用抵抗R1(R2)の耐圧等の定格を下げるなどの調整をすることも可能になる。もちろん、インバータ40やDC−DCコンバータ20における他の上下アームの放電抵抗についても同様のことが言える。

【0042】

したがって、上述の実施例によれば、電源電圧VDが上昇しても、放電経路を確保して、放電用抵抗の消費電力の抑制や過充電によるコンデンサの破壊などを防止することができる。すなわち、コンデンサで受け入れた大電圧がツェナーダイオードZ3(Z6)の閾値を超える電圧であればコレクタ側に戻され得るので、放電用抵抗に流れる電流の減少やコンデンサの過電圧の低減を図ることができる。

【0043】

以上、本発明の好ましい実施例について詳説したが、本発明は、上述した実施例に制限されることはなく、本発明の範囲を逸脱することなく、上述した実施例に種々の変形及び置換を加えることができる。

【0044】

図6は、高耐圧ツェナーダイオードZ1,Z2(Z4、Z5)及びツェナーダイオードZ3(Z6)との代わりに、バリスタV1(V2)を使った場合の構成図である。この場合も、上述の図2の場合と同様の効果が得られる。バリスタも積層セラミック製のチップ部品が多品種で流通しているため、サージ電圧の調整も容易となる。バリスタは、非直線性抵抗素子であって、印加電圧が高くなると急激にその電気抵抗が小さくなる性質を有する。抵抗値が急激に下がるときの電圧をバリスタ電圧という。

【0045】

図7は、スイッチング素子Q1のゲートエミッタ間にプルダウン抵抗Rpdを追加した場合の回路である。高耐圧ツェナーダイオードZ1,Z2の寄生容量値が、コンデンサC1に対して無視できない場合には、例えば、スイッチング素子Q1のゲートエミッタ間にプルダウン抵抗Rpdを追加するなどによって、ゲインを調整することもできる。つまり、スイッチング素子Q1のゲートに流れ込む電流の一部をRpdで分流することにより、ツェナーダイオードZ1,Z2の寄生容量の影響を解消することができる。

【0046】

図8は、スイッチング素子Q1のゲートの直前に抵抗Rlpfを追加した場合の回路である。抵抗Rlpfとスイッチング素子Q1のゲート容量とによってローパスフィルタを形成することができるので、高周波成分のノイズをカットすることができ、回路をより安定動作させることができる。

【図面の簡単な説明】

【0047】

【図1】本発明に係るスイッチング装置の一実施形態であるモータ/ジェネレータ駆動システム100の概略構成図である。

【図2】インバータ40のU相の制御回路の詳細構成図である。

【図3】オフサージ電圧を抑制する場合のタイミングチャートを示す。

【図4】スイッチング損失を抑制する場合のタイミングチャートを示す。

【図5】高耐圧コンデンサC1,C2の容量値を1000pFとした場合のオフサージ電圧の波形を示した図である。

【図6】高耐圧ツェナーダイオードZ1,Z2(Z4、Z5)及びツェナーダイオードZ3(Z6)との代わりに、バリスタV1(V2)を使った場合の構成図である。

【図7】スイッチング素子Q1のゲートエミッタ間にプルダウン抵抗Rpdを追加した場合の回路である。

【図8】スイッチング素子Q1のゲートの直前に抵抗Rlpfを追加した場合の回路である。

【図9】保護回路の一例である。

【符号の説明】

【0048】

Z1,Z2,Z4,Z5 高耐圧ツェナーダイオード

Z3,Z6 逆流及び過充電防止用ツェナーダイオード

C1,C2 コンデンサ

R1,R2 放電用抵抗

Q1〜Q14 スイッチング素子

P1,P2 保護回路

VD 電源電圧

V1,V2 バリスタ

【特許請求の範囲】

【請求項1】

半導体スイッチング素子を備え、

前記半導体スイッチング素子のスイッチング装置であって、

前記半導体スイッチング素子のコレクタ−ゲート間に設けられ、並列接続された抵抗素子と容量素子とを有する並列回路と、

前記並列回路と前記コレクタとの間に設けられ、前記コレクタ側の向きに自身に印加される電圧が第1の基準値を超えると前記並列回路側の向きに電流を流す第1の電流制限素子と、

前記並列回路と前記コレクタとの間に設けられ、前記並列回路側の向きに自身に印加される電圧が第2の基準値を超えると前記コレクタ側の向きに電流を流す第2の電流制限素子とを備えることを特徴とする、スイッチング装置。

【請求項2】

前記第2の基準値は、前記半導体スイッチング素子のコレクタの電圧上昇により前記並列回路の耐圧が超えないように設定される、請求項1に記載のスイッチング装置。

【請求項3】

前記半導体スイッチング素子は、該半導体スイッチング素子のコレクタの電圧が変動し得るインバータ又はコンバータのスイッチング素子である、請求項1又は2に記載のスイッチング装置。

【請求項4】

前記第2の電流制限素子は、ツェナーダイオードである、請求項1から3のいずれか一項に記載のスイッチング装置。

【請求項5】

前記第2の電流制限素子は、バリスタである、請求項1から3のいずれか一項に記載のスイッチング装置。

【請求項6】

コレクタ−ゲート間に設けられ、並列接続された抵抗素子と容量素子とを有する並列回路と、

前記並列回路と前記コレクタとの間に設けられ、前記コレクタ側の向きに自身に印加される電圧が第1の基準値を超えると前記並列回路側の向きに電流を流す第1の電流制限素子と、

前記並列回路と前記コレクタとの間に設けられ、前記並列回路側の向きに自身に印加される電圧が第2の基準値を超えると前記コレクタ側の向きに電流を流す第2の電流制限素子と、を備える複数の半導体スイッチング素子を有し、

第1の半導体スイッチング素子のエミッタと第2の半導体スイッチング素子のコレクタとを接続した構成が含まれる、スイッチング装置。

【請求項7】

前記第2の基準値は、前記半導体スイッチング素子のコレクタの電圧上昇により前記並列回路の耐圧が超えないように設定される、請求項6に記載のスイッチング装置。

【請求項8】

前記第1の半導体スイッチング素子は、該第1の半導体スイッチング素子のコレクタの電圧が変動し得るインバータ又はコンバータの上アーム素子であり、

前記第2の半導体スイッチング素子は、該第2の半導体スイッチング素子のコレクタの電圧が変動し得るインバータ又はコンバータの下アーム素子である、請求項6又は7に記載のスイッチング装置。

【請求項9】

前記第2の電流制限素子は、ツェナーダイオードである、請求項6から8のいずれか一項に記載のスイッチング装置。

【請求項10】

前記第2の電流制限素子は、バリスタである、請求項6から8のいずれか一項に記載のスイッチング装置。

【請求項1】

半導体スイッチング素子を備え、

前記半導体スイッチング素子のスイッチング装置であって、

前記半導体スイッチング素子のコレクタ−ゲート間に設けられ、並列接続された抵抗素子と容量素子とを有する並列回路と、

前記並列回路と前記コレクタとの間に設けられ、前記コレクタ側の向きに自身に印加される電圧が第1の基準値を超えると前記並列回路側の向きに電流を流す第1の電流制限素子と、

前記並列回路と前記コレクタとの間に設けられ、前記並列回路側の向きに自身に印加される電圧が第2の基準値を超えると前記コレクタ側の向きに電流を流す第2の電流制限素子とを備えることを特徴とする、スイッチング装置。

【請求項2】

前記第2の基準値は、前記半導体スイッチング素子のコレクタの電圧上昇により前記並列回路の耐圧が超えないように設定される、請求項1に記載のスイッチング装置。

【請求項3】

前記半導体スイッチング素子は、該半導体スイッチング素子のコレクタの電圧が変動し得るインバータ又はコンバータのスイッチング素子である、請求項1又は2に記載のスイッチング装置。

【請求項4】

前記第2の電流制限素子は、ツェナーダイオードである、請求項1から3のいずれか一項に記載のスイッチング装置。

【請求項5】

前記第2の電流制限素子は、バリスタである、請求項1から3のいずれか一項に記載のスイッチング装置。

【請求項6】

コレクタ−ゲート間に設けられ、並列接続された抵抗素子と容量素子とを有する並列回路と、

前記並列回路と前記コレクタとの間に設けられ、前記コレクタ側の向きに自身に印加される電圧が第1の基準値を超えると前記並列回路側の向きに電流を流す第1の電流制限素子と、

前記並列回路と前記コレクタとの間に設けられ、前記並列回路側の向きに自身に印加される電圧が第2の基準値を超えると前記コレクタ側の向きに電流を流す第2の電流制限素子と、を備える複数の半導体スイッチング素子を有し、

第1の半導体スイッチング素子のエミッタと第2の半導体スイッチング素子のコレクタとを接続した構成が含まれる、スイッチング装置。

【請求項7】

前記第2の基準値は、前記半導体スイッチング素子のコレクタの電圧上昇により前記並列回路の耐圧が超えないように設定される、請求項6に記載のスイッチング装置。

【請求項8】

前記第1の半導体スイッチング素子は、該第1の半導体スイッチング素子のコレクタの電圧が変動し得るインバータ又はコンバータの上アーム素子であり、

前記第2の半導体スイッチング素子は、該第2の半導体スイッチング素子のコレクタの電圧が変動し得るインバータ又はコンバータの下アーム素子である、請求項6又は7に記載のスイッチング装置。

【請求項9】

前記第2の電流制限素子は、ツェナーダイオードである、請求項6から8のいずれか一項に記載のスイッチング装置。

【請求項10】

前記第2の電流制限素子は、バリスタである、請求項6から8のいずれか一項に記載のスイッチング装置。

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【公開番号】特開2009−131035(P2009−131035A)

【公開日】平成21年6月11日(2009.6.11)

【国際特許分類】

【出願番号】特願2007−302925(P2007−302925)

【出願日】平成19年11月22日(2007.11.22)

【出願人】(000003207)トヨタ自動車株式会社 (59,920)

【Fターム(参考)】

【公開日】平成21年6月11日(2009.6.11)

【国際特許分類】

【出願日】平成19年11月22日(2007.11.22)

【出願人】(000003207)トヨタ自動車株式会社 (59,920)

【Fターム(参考)】

[ Back to top ]