スイッチング電源とその駆動方法

【課題】 効率を高めた高周波送信機用のスイッチング電源を提供すること。

【解決手段】 実施形態によれば、入力信号の波形に基づき送信増幅器をエンベロープトラッキング駆動するスイッチング電源は、入力信号が一時側に入力されるトランスと、このトランスの二次側に接続されるスイッチング部とを具備する。スイッチング部は、ゲートおよびソースが上記トランスの二次側に接続されるFETと、カソードが上記ゲートに接続されるショットキーダイオードと、ショットキーダイオードに逆極性で直列接続されカソードが上記ソースに接続されるツェナーダイオードと、このツェナーダイオードに並列接続されるコンデンサとを備える。

【解決手段】 実施形態によれば、入力信号の波形に基づき送信増幅器をエンベロープトラッキング駆動するスイッチング電源は、入力信号が一時側に入力されるトランスと、このトランスの二次側に接続されるスイッチング部とを具備する。スイッチング部は、ゲートおよびソースが上記トランスの二次側に接続されるFETと、カソードが上記ゲートに接続されるショットキーダイオードと、ショットキーダイオードに逆極性で直列接続されカソードが上記ソースに接続されるツェナーダイオードと、このツェナーダイオードに並列接続されるコンデンサとを備える。

【発明の詳細な説明】

【技術分野】

【0001】

本発明の実施形態は、CDMA(Code Division Multiple Access)やOFDM(Orthogonal Frequency Division Multiplex)等のマイクロ波通信に用いられるスイッチング電源とその駆動方法に関する。

【背景技術】

【0002】

CDMAやOFDMは、携帯電話のような広帯域サービス及び高速な移動環境下においても通信を可能にする通信方式として多様なシステムに利用されている。この種の変調方式には変調波のPAPR(Peak to Average Power Ratio)が大きいという特性がある。このためCDMAやOFDM変調方式を利用したシステムでは、送信電力増幅器の非線形歪みが生じ、送信信号が劣化してしまう。この非線形歪みは、増幅器をPAPR以上のバックオフ領域で動作させることで低減することが可能である。しかしながらこの方法では増幅器の効率が低下するという新たな問題が発生する。

【0003】

そこで、増幅器の低歪み動作及び高効率動作の両方を実現する技術としてエンベロープトラッキングが提案されている。エンベロープトラッキングは、時間的にダイナミックにレベル変動するOFDM波の包絡線(エンベロープ)を検波し、それに応じて増幅器のドレイン電圧をコントロールする技術である。対象とされる送信信号の包絡線の帯域幅は例えば10MHz前後、電源のスイッチング周波数は数100MHz、電源電圧のピークは数10Vオーダである。

【先行技術文献】

【特許文献】

【0004】

【特許文献1】特許第4456569号公報

【発明の概要】

【発明が解決しようとする課題】

【0005】

例えば大容量蓄電池の充電器用のスイッチング素子にはFETが使用され、大電力化、数MHz(メガヘルツ)オーダでの高速スイッチングが実現されている。この種の高速スイッチング電源回路にはPチャネル、Nチャネルトランジスタが用いられるが、100MHz以上の高速スイッチングに追従可能なPチャネルトランジスタは知られていない。

【0006】

NチャネルのSi高速MOSFETだけを使う方式があるが、数100MHzの高速スイッチングには追従しない。マイクロ波帯電力増幅用のNチャネルGaAsFETは数100MHzのスイッチング周波数に追従し高電流も流せるが、数10Vの電圧振幅は得られない。近年、電源用としてNチャネルGaNFETが開発されているが、数10Vの電圧振幅は得られても数100MHzのスイッチング周波数には追従しない。いずれにせよ、これらの素子をエンベロープトラッキング技術に応用して超高速のスイッチング周波数および大振幅の出力を実現するには技術的な困難を伴う。

目的は、効率を高めた高周波送信機用のスイッチング電源とその駆動方法を提供することにある。

【課題を解決するための手段】

【0007】

実施形態によれば、入力信号の波形に基づき送信増幅器をエンベロープトラッキング駆動するスイッチング電源は、入力信号が一時側に入力されるトランスと、このトランスの二次側に接続されるスイッチング部とを具備する。スイッチング部は、ゲートおよびソースが上記トランスの二次側に接続されるFETと、カソードが上記ゲートに接続されるショットキーダイオードと、ショットキーダイオードに逆極性で直列接続されカソードが上記ソースに接続されるツェナーダイオードと、このツェナーダイオードに並列接続されるコンデンサとを備える。

【図面の簡単な説明】

【0008】

【図1】実施形態に係わるFETスイッチング電源を備える高周波送信機を示すブロック図。

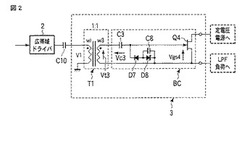

【図2】図1に示されるFETスイッチング電源3の第1の実施形態を示す回路図。

【図3】基本FETスイッチ回路BCにおける各部の動作波形を示す図。

【図4】FETスイッチング電源3の第2の実施形態を示す回路図。

【図5】図4に示されるFETスイッチング電源3における各部の電圧波形を示す図。

【図6】電源電圧の印加タイミングを制御可能な回路の一例を示す図。

【図7】FETスイッチング電源3の第3の実施形態を示す回路図。

【図8】FETスイッチング電源3の第4の実施形態を示す回路図。

【発明を実施するための形態】

【0009】

図1は、実施形態に係わるFETスイッチング電源を備える高周波送信機を示すブロック図である。図1において、高周波送信機Sは、パワーアンプ(PA)1、広帯域ドライバ2、FETスイッチング電源3、検波器4、波形変換部5およびローパスフィルタ(LPF)6を備えて無線電波を送信する。広帯域ドライバ2は、波形変換部5で生成されたスイッチング信号をFETスイッチング電源3に出力する。FETスイッチング電源3は既定の電源電圧でスイッチングされる電力をPA1に供給する。すなわち、送信する無線電波のエンベロープ(包絡線)信号に対応する電源電圧がFETスイッチング電源3からPA1に供給される。この形式の増幅器はいわゆるエンベロープトラッキングアンプである。

【0010】

無線電波として送信される送信信号は、PA1および検波器4に入力される。検波器4は送信信号を包絡線検波する。これにより得られた包絡線波形は波形変換部5でΔΣ変換などを経てスイッチング信号に変換される。包絡線の帯域幅は10MHz前後、スイッチング周波数は数100MHzである。送信信号のPAPRが大きく、平均レベルに有る時間が長く変動が大きい場合にも、PA1およびFETスイッチング電源3は安定して動作することが要求される。以下、スイッチング電源の複数の実施形態につき説明する。

【0011】

[第1の実施形態]

図2は、図1に示されるFETスイッチング電源3の第1の実施形態を示す回路図である。この回路は実施形態における基本的なFETスイッチ回路であり、広帯域ドライバ2からのスイッチング信号を巻線比1:1のパルストランスT1に入力してフローティングさせたものである。パルストランスT1の二次側出力は基本FETスイッチング回路BCに入力される。

【0012】

図2において、広帯域ドライバ2からのパルス状のスイッチング信号は、コンデンサC10を介して直流カットされ、パルストランスT1(以下、トランスT1と称する)に入力される。トランスT1のコイル(巻線)の巻き始めを(・)で示す。二次巻線W3の(・)マーク側の出力端子はコンデンサC3を介してNチャネルFETQ4のゲートに接続される。二次巻線W3の他方の出力端子はFETQ4のソースに接続される。二次巻線W3の(・)マークの端子から電圧Vt3のパルスが出力されるが、トランスの出力電圧の平均は0ボルトなので、パルスデューティに応じて正と負のピーク電圧が変動する。

【0013】

基本FETスイッチ回路BCにおいて、FETQ4として、ショットキー接合のゲートを持つノーマリーオン動作のNチャネルGaAsFETを用いた場合の動作を説明する。FETQ4はノーマリーオンなのでゲート−ソース間電圧Vgs4が0ボルトでもオン抵抗が低く、ゲートがショットキー接合なのでVgs4>0で順方向ゲート電流が流れる。

【0014】

FETQ4のゲートにショットキーダイオード(以下ダイオードと称する)D7のカソードが接続される。ダイオードD7のアノードはFETQ4のVgs4に印加するパルスの電圧振幅を設定するツェナーダイオードD8のアノードに接続される。ツェナーダイオードD8のカソードはFETQ4のソースに接続される。

【0015】

ツェナーダイオードD8にはコンデンサC8が並列接続される。コンデンサC8は、ダイオードD7が逆バイアスになったとき電圧を保持し、ダイオードD7が順バイアスなったときに速やかに電荷を供給する。従ってFETQ4の順方向ゲート電流とD7の順方向電流とが平衡する電圧で、Vgs4に印加されるパルスの直流レベルが固定される。その結果、コンデンサC3にVgs4とVt3との差の電圧Vc3が生じる。

【0016】

FETQ4はノーマリーオンなので順方向ゲート電流が少しでも流れる正のVgs4でドレイン−ソース間のオン抵抗が低くなり、オフ時に完全にピンチオフするようにダイオードD8でパルス電圧振幅を設定する。よってドレインに電源を接続し、ソースに負荷を接続すれば、スイッチング動作の損失を低減できる。

【0017】

図3は、基本FETスイッチ回路BCにおける各部の動作波形を示す図である。図2の回路において、例えばT1の二次巻線W3の電圧Vt3が5Vp−pでデューティ比(DF)が90%である場合、トランスT1の出力電圧に直流成分が無いので、図3(a)に示すようにVt3は+0.5V〜−4.5Vとなる。また、FETQ4のゲート・ソース間電圧Vgs4の立ち上がり電圧Vf4が+1Vである場合には、ゲート・ソース間電圧Vgs4は図3(b)に示すように+1V〜−4Vとなる。従って、図3(c)に示すようにC3の電圧はVc3=−0.5Vとなる。

一方、DFが10%の場合は図3(d)に示すように電圧Vt3は+4.5V〜−0.5V、ゲート・ソース間電圧Vgs4は図3(e)に示すように+1V〜−4Vとなり、C3の電圧は図3(f)に示すようにVc3=+3.5Vとなる。

【0018】

図2に示されるスイッチング回路は、DFが増加している時は高速応答するダイオードD7の順方向電流でC3を放電し、DFが減少している時はFETQ4の順方向ゲート電流でコンデンサC3を充電するので、包絡線の10MHz前後に安定して追従することができる。

【0019】

次に、基本FETスイッチ回路BCにおいて、FETQ4として、電源用のNチャネルGaNFETを用いた場合の動作を説明する。この種のトランジスタは電源用として用いることができる。

電源用GaNFETは耐圧が高いが、マイクロ波帯電力増幅用よりも応答速度が一桁以上遅く、数100MHzの高速スイッチングさせるためにはスピードアップ処理が必要である。また、ゲートがショットキー接合でノーマリーオフであるので、順方向ゲート電流が流れる正のゲート・ソース間電圧Vgsを印加しなければオン抵抗が下がらない。

【0020】

FETQ4がオンの間、その順方向ゲート電流を保持するためにはコンデンサC3の容量を大きくしなければならない。しかしながら包絡線の10MHz前後に追従させようとすると、FETQ4のゲート電流やダイオードD7の順方向電流が過大になり破損するほどの電荷量になってしまう問題がある。つまり、既存のFETや回路方式は、高周波信号増幅器のスイッチング電源としては振幅が得られない。あるいは、振幅に耐えるものは応答速度が得られない。

【0021】

第1の実施形態に係わるFETスイッチング電源は、高電圧をスイッチングする終段のGaNFETと、そのスピードアップ回路と、複数のGaAsFETを用いたドライバアンプと、ドライバアンプをフローティングするためのパルストランスとを備える。これにより高速かつ大振幅の高周波スイッチング電源を実現することができる。このスイッチング電源を用いることにより、送信信号の包絡線に対応した電源電圧をPA1に供給するエンベロープトラッキングアンプの効率を高めることが可能になる。

【0022】

[第2の実施形態]

図4は、図1に示されるFETスイッチング電源3の第2の実施形態を示す回路図である図4のFETスイッチング回路3は、入力信号に対して同極性となる二次巻線W2、二次巻線W3および逆極性となる二次巻線W1から信号を出力するパルストランスT1aを備える。パルストランスT1aの二次側には3つの基本FETスイッチング回路BC1〜BC3が接続される。このうちBC3が図2の基本FETスイッチング回路BCに対応する。BC1およびBC2もBC3と同様の構成であり、BC1のFETに符合Q2を、BC2のFETに符合Q3を付して示す。BC1はパルストランスT1aに対して逆相で接続され、BC2およびBC3は同相で接続される。

【0023】

BC1のFETQ2のソースはFETQ3のドレインに接続され、FETQ3のソースはFETQ1のソースに接続される。FETQ2のソースとFETQ3のドレインとの接続点XCは、抵抗R1とコンデンサC4が並列接続されたスピードアップ回路を介して、FETQ1のゲートにスイッチング信号を出力する。FETQ1のドレインは電圧Vddの電源PS1に接続され、FETQ1のソースはアノード接地のショットキーダイオードD1のカソードに接続される。

【0024】

このほか、FETスイッチング回路3は、PA1に電力を供給する電圧Vddの直流電源PS1、およびFETQ1をオンにする電荷を供給する電圧Vpを出力するドライブ回路用電源PS2を備える。以上の構成において、0Vのローレベルから電源電圧Vddのハイレベルまでの大振幅かつスイッチングされた電圧が、FETQ1のゲートへ入力されるスイッチング信号と同じ極性でFETQ1のソースからLPF6(図示せず)出力される。

【0025】

基本FETスイッチング回路BC1〜BC3のFETQ2〜Q4として、ショットキー接合のゲートを持つノーマリーオン動作のNチャネルGaAsFETを用いた場合の動作を説明する。FETQ1はショットキー接合のゲートを持つノーマリーオフ動作の電源用Nチャネル型GaNFETとする。

【0026】

FETQ1は、ON時のオン抵抗を低くするために順方向ゲート電流を流す必要があるので、その電荷をFETQ1がオフ時に、電圧Vpのバイアス用のDC電源(ドライブ回路用電源)PS2からショットキーダイオードD2を介して、他方がFETQ1のソースに接続されたコンデンサC5に供給する。コンデンサC5はFETQ1のソースに対して基本FETスイッチング回路BC1のFETQ2のドレイン電圧をVpに保つ。FETQ1は耐圧が高いが応答速度が遅いので、スピードアップ回路として抵抗R1、R2、コンデンサC4および基本FETスイッチング回路BC3を備える。

なお図4において、符合XAはFETQ1のソース接続点、XBはFETQ2のドレイン接続点、XCはFETQ2のソース接続点である。

【0027】

図5は、図4に示されるFETスイッチング電源3における各部の電圧波形を示す図である。接続点XAはFETQ1がONの時にVddボルト、OFFの時に0ボルトになる(図5(a))。接続点XBは電圧Vpに充電されたコンデンサC5を介して接続点XAに接続されているので、FETQ1がONの時に(Vdd+Vp)ボルト、OFFの時にVpボルトになる(図5(b))。接続点XCはFETQ1がONの時に(Vdd+Vp)ボルト、OFFの時に0ボルトとなり、この電圧がスピードアップ回路に入力される(図5(c))。

【0028】

スピードアップ回路の端子○1と端子○2との間には、基本FETスイッチング回路BC3のFETQ4のドレインとソースがそれぞれ接続される。FETQ1のソースの電圧XAに対する○1の電圧XCは、FETQ1がオン時にVpボルト、オフ時の0ボルトとなる。FETQ1がオフ時にFETQ4で○1と○2が短絡されるので、低抵抗の抵抗R2を介してコンデンサC4は放電して0ボルトになる。

【0029】

FETQ1がオン時はFETQ4が開放なので、オフ→オン直後はFETQ1の入力容量Ci1とコンデンサC4とでVpが分圧されるが、スピードアップのためにコンデンサC4の容量は入力容量Ci1の容量より大きく設定するので、FETQ1のゲート・ソース間電圧Vgs1はほぼVpになる。この瞬間のFETQ1の非線形な順方向ゲート電流を高く設定することにより、コンデンサC4の充電時間を短くする。

【0030】

定常状態の順方向ゲート電流をIgf1、ゲート・ソース間電圧Vgs1をVf1とするとコンデンサC4の電圧はR1・Igf1=Vp−Vf1になる(図5(d))。FETQ1がオン→オフ直後はC4がCi1より大きいのでほぼゲート・ソース間電圧Vgs1=Vf1−Vpになり、FETQ1がオフになる時間よりは遅い時定数でR2とFETQ4を介してコンデンサC4の電荷が放電して0ボルトになる。この放電の時定数は、抵抗R2の値をr2、コンデンサC4の値をc4とすると(c4・r2)で概算できるので、パルス幅より短い時間に設定する。また、定常状態で許容される順方向ゲート電流をIgf1maxとし、抵抗R1の値をr1とすれば、r1>(Vp−Vf1)/Igf1maxとして許容電流を超えないようにr1の値を設定する。

【0031】

この実施形態における各値は、一例として最大電流10A、Vdd=50V、Vp=5V、Vf1=2.5V、Igf1=20mA,Ci1=300pF、r1=150Ω>125Ωとする。そして、抵抗R2とコンデンサC1〜C8等の値は使用するスイッチング周波数と包絡線の帯域幅に基づいて最適化するようにする。

【0032】

次に、電源投入時の過渡状態について説明する。スイッチング信号が入力されていない時はコンデンサC1〜C3の電圧やFETQ2〜FETQ4のVgs2〜Vgs4は0ボルトで、ノーマリーオンのFETQ2〜FETQ4はオン状態なので、FETQ2とFETQ3を経由する貫通電流は流れ続ける。ここではFETQ1のVf1がVp等の電源電圧と比べて十分低いとして説明を簡単にする。

【0033】

この状態で先に電源Vpをオンにすると、ダイオードD2、FETQ2、FETQ3、および負荷を経由してVp/RL(負荷抵抗)が流れる。この状態でのFETQ2とFETQ3のソースとドレインおよび負荷にかかる電圧は全てVpなので、コンデンサC5の電圧は0ボルトで、FETQ1はドレインがソースとして働きオン状態になり、Vddの電源がオフ時に開放となる場合は約Vpに充電してFETQ1はオフになる。

【0034】

この状態でVddを印加するとFETQ1はオフ状態になるが、負荷にかかる電圧などはVpのままである。逆にVddを先に印加してもFETQ1はオフ状態のままで電流は流れないが、次にVpを印加すると先にVpを印加した時と同じ状態になる。この状態でスイッチング信号を入力すると、FETQ3はFETQ1オフ時にオンになるのでFETQ1はオフになるが、FETQ1オン時にFETQ2がオンしてもC5が0ボルトなのでFETQ1はオンにならない。しかし、FETQ2とFETQ3のどちらか一方がオフ状態で貫通電流が流れるのはオン/オフ切替時の一瞬なので、負荷での電圧が下がりC5を充電し始めやがて正常動作に入る。以上からこの実施形態では、ダイオードD2、FETQ2、FETQ3の最大許容電流を約Vp/RL(負荷抵抗)とした場合の電流より高くする。

【0035】

なお、電源電圧を印加する前にスイッチング信号を入力して、コンデンサC1〜C3を充電してFETQ2〜FETQ4をオン/オフさせて、FETQ2とFETQ3を経由する貫通電流が流れ続けないようにしてから、電源電圧を印加するようにすれば良い。このようなシーケンスで回路を駆動することで、ダイオードD2の最大許容電流はVp/負荷抵抗より低くできる。また、FETQ2、FETQ3の最大許容電流も低くできる場合がある。

【0036】

図6は、電源電圧の印加タイミングを制御可能な回路の一例を示す図である。図6において図4と共通する部分には同じ符号を付して示すか省略し、ここでは異なる部分についてのみ説明する。

図6に示すように、トランスT1の一次巻線wiに電源供給制限部PXを接続する。電源供給制限部PXはスイッチング信号の有無を監視するセンサ部81を備える。なおセンサ部81は二次巻線側に接続してもよい。センサ部81は入力される信号を検波し、検波波形が既定レベル以上になるとスイッチング信号有りと判断する。そうすると電源PS1、PS2への一次電力をオンにする電源制御信号をスイッチ部PPの制御端子に入力する。

【0037】

スイッチ部PPは電源PS2の1次側に挿入され、オンにする制御信号に従って入力される電源PS1、PS2への電力をオンにする。このスイッチ部PPは、このオン信号により起動される内部タイマ、もしくは積分回路等により所定の時間遅れてONになる遅延部DLを備える。これによりオンにする制御信号が入力されたのち、電源PS2に電力が供給される。なお、このスイッチ部PPは、電源PS2の二次側に挿入され出力Vdd、Vpの供給開始タイミングを遅らせるものであっても良い。このようにFETQ2とFETQ3とを経由する貫通電流が流れ続けないシーケンス、タイミング制御をしてから、電源電圧を印加するようにしてもよい。以上のようにこの実施形態によっても、応答速度と振幅を確保することが可能なスイッチング回路を実現することができる。

【0038】

[第3の実施形態]

図7は、図1に示されるFETスイッチング電源3の第3の実施形態を示す回路図である。図7において図4と共通する部分には同じ符号を付して示し、ここでは異なる部分についてのみ説明する。図7において、FETQ1のソースにショットキーダイオードD9のアノードを接続し、ドレインにカソードを接続するようにした。これにより、負荷の異常などによる異常電圧からFETQ1を保護することができる。

【0039】

[第4の実施形態]

図8は、図1に示されるFETスイッチング電源3の第4の実施形態を示す回路図である。図8において図7と共通する部分には同じ符号を付して示し、ここでは異なる部分についてのみ説明する。

図8において、ダイオードD1のカソード○3、アノード○4にそれぞれFETQ5のドレイン○3、ソース○4が接続される。FETQ5のゲートには、FETQ1のゲートと逆極性のスイッチング信号が入力される。このFETQ5は、ショットキー接合のゲートを持つNチャネル型のノーマリーオフ型FETである。この逆極性の信号は基本FETスイッチ回路BC1と同様に生成される。

【0040】

図7においては、FETQ1がオフ時にダイオードD1に流れる電流とダイオードD1の順方向電圧降下の積が損失となる。このダイオードD1における電圧降下による損失を防ぐため、図8においては、オン抵抗が低いFETQ5をダイオードD1に並列接続することにより電圧降下を小さく抑えて損失を減少させるようにしている。

【0041】

なお、FETQ5はフローティングさせる必要はない。よって遅延回路などでパルストランスT1bの入力信号のタイミングを遅らせ、FETQ1のゲートに入力されるスイッチング信号のタイミングと合わせた逆極性の信号を生成しても良い。また、パルストランスを逆極性、すなわち入力信号に対してW1の二次巻線を同極性、W2の二次巻線とW3の二次巻線を逆極性にしても同様な効果が得られる。

【0042】

以上説明したようにこれらの実施形態によれば、高効率な高周波送信機用の高速・大振幅スイッチング電源およびスイッチング方法を提供することができる。

本発明のいくつかの実施形態を説明したが、これらの実施形態は、例として提示したものであり、発明の範囲を限定することは意図していない。これら新規な実施形態は、その他の様々な形態で実施されることが可能であり、発明の要旨を逸脱しない範囲で、種々の省略、置き換え、変更を行うことができる。これら実施形態やその変形は、発明の範囲や要旨に含まれるとともに、特許請求の範囲に記載された発明とその均等の範囲に含まれる。

【符号の説明】

【0043】

S…高周波送信機、1…パワーアンプ(PA)、2…広帯域ドライバ、3…FETスイッチング電源、4…検波器、5…波形変換部、6…ローパスフィルタ(LPF)、T1…パルストランス、BC…基本FETスイッチング回路、C1〜C8,C10…コンデンサ、Q1〜Q4…NチャネルFET、D1,D2,D7…ショットキーダイオード、D8…ツェナーダイオード、T1a…パルストランス、BC1〜BC3…基本FETスイッチング回路、PS1…電源、PS2…ドライブ回路用電源、R1,R2…抵抗、PX…電源供給制限部、81…センサ部、PP…スイッチ部、DL…遅延部

【技術分野】

【0001】

本発明の実施形態は、CDMA(Code Division Multiple Access)やOFDM(Orthogonal Frequency Division Multiplex)等のマイクロ波通信に用いられるスイッチング電源とその駆動方法に関する。

【背景技術】

【0002】

CDMAやOFDMは、携帯電話のような広帯域サービス及び高速な移動環境下においても通信を可能にする通信方式として多様なシステムに利用されている。この種の変調方式には変調波のPAPR(Peak to Average Power Ratio)が大きいという特性がある。このためCDMAやOFDM変調方式を利用したシステムでは、送信電力増幅器の非線形歪みが生じ、送信信号が劣化してしまう。この非線形歪みは、増幅器をPAPR以上のバックオフ領域で動作させることで低減することが可能である。しかしながらこの方法では増幅器の効率が低下するという新たな問題が発生する。

【0003】

そこで、増幅器の低歪み動作及び高効率動作の両方を実現する技術としてエンベロープトラッキングが提案されている。エンベロープトラッキングは、時間的にダイナミックにレベル変動するOFDM波の包絡線(エンベロープ)を検波し、それに応じて増幅器のドレイン電圧をコントロールする技術である。対象とされる送信信号の包絡線の帯域幅は例えば10MHz前後、電源のスイッチング周波数は数100MHz、電源電圧のピークは数10Vオーダである。

【先行技術文献】

【特許文献】

【0004】

【特許文献1】特許第4456569号公報

【発明の概要】

【発明が解決しようとする課題】

【0005】

例えば大容量蓄電池の充電器用のスイッチング素子にはFETが使用され、大電力化、数MHz(メガヘルツ)オーダでの高速スイッチングが実現されている。この種の高速スイッチング電源回路にはPチャネル、Nチャネルトランジスタが用いられるが、100MHz以上の高速スイッチングに追従可能なPチャネルトランジスタは知られていない。

【0006】

NチャネルのSi高速MOSFETだけを使う方式があるが、数100MHzの高速スイッチングには追従しない。マイクロ波帯電力増幅用のNチャネルGaAsFETは数100MHzのスイッチング周波数に追従し高電流も流せるが、数10Vの電圧振幅は得られない。近年、電源用としてNチャネルGaNFETが開発されているが、数10Vの電圧振幅は得られても数100MHzのスイッチング周波数には追従しない。いずれにせよ、これらの素子をエンベロープトラッキング技術に応用して超高速のスイッチング周波数および大振幅の出力を実現するには技術的な困難を伴う。

目的は、効率を高めた高周波送信機用のスイッチング電源とその駆動方法を提供することにある。

【課題を解決するための手段】

【0007】

実施形態によれば、入力信号の波形に基づき送信増幅器をエンベロープトラッキング駆動するスイッチング電源は、入力信号が一時側に入力されるトランスと、このトランスの二次側に接続されるスイッチング部とを具備する。スイッチング部は、ゲートおよびソースが上記トランスの二次側に接続されるFETと、カソードが上記ゲートに接続されるショットキーダイオードと、ショットキーダイオードに逆極性で直列接続されカソードが上記ソースに接続されるツェナーダイオードと、このツェナーダイオードに並列接続されるコンデンサとを備える。

【図面の簡単な説明】

【0008】

【図1】実施形態に係わるFETスイッチング電源を備える高周波送信機を示すブロック図。

【図2】図1に示されるFETスイッチング電源3の第1の実施形態を示す回路図。

【図3】基本FETスイッチ回路BCにおける各部の動作波形を示す図。

【図4】FETスイッチング電源3の第2の実施形態を示す回路図。

【図5】図4に示されるFETスイッチング電源3における各部の電圧波形を示す図。

【図6】電源電圧の印加タイミングを制御可能な回路の一例を示す図。

【図7】FETスイッチング電源3の第3の実施形態を示す回路図。

【図8】FETスイッチング電源3の第4の実施形態を示す回路図。

【発明を実施するための形態】

【0009】

図1は、実施形態に係わるFETスイッチング電源を備える高周波送信機を示すブロック図である。図1において、高周波送信機Sは、パワーアンプ(PA)1、広帯域ドライバ2、FETスイッチング電源3、検波器4、波形変換部5およびローパスフィルタ(LPF)6を備えて無線電波を送信する。広帯域ドライバ2は、波形変換部5で生成されたスイッチング信号をFETスイッチング電源3に出力する。FETスイッチング電源3は既定の電源電圧でスイッチングされる電力をPA1に供給する。すなわち、送信する無線電波のエンベロープ(包絡線)信号に対応する電源電圧がFETスイッチング電源3からPA1に供給される。この形式の増幅器はいわゆるエンベロープトラッキングアンプである。

【0010】

無線電波として送信される送信信号は、PA1および検波器4に入力される。検波器4は送信信号を包絡線検波する。これにより得られた包絡線波形は波形変換部5でΔΣ変換などを経てスイッチング信号に変換される。包絡線の帯域幅は10MHz前後、スイッチング周波数は数100MHzである。送信信号のPAPRが大きく、平均レベルに有る時間が長く変動が大きい場合にも、PA1およびFETスイッチング電源3は安定して動作することが要求される。以下、スイッチング電源の複数の実施形態につき説明する。

【0011】

[第1の実施形態]

図2は、図1に示されるFETスイッチング電源3の第1の実施形態を示す回路図である。この回路は実施形態における基本的なFETスイッチ回路であり、広帯域ドライバ2からのスイッチング信号を巻線比1:1のパルストランスT1に入力してフローティングさせたものである。パルストランスT1の二次側出力は基本FETスイッチング回路BCに入力される。

【0012】

図2において、広帯域ドライバ2からのパルス状のスイッチング信号は、コンデンサC10を介して直流カットされ、パルストランスT1(以下、トランスT1と称する)に入力される。トランスT1のコイル(巻線)の巻き始めを(・)で示す。二次巻線W3の(・)マーク側の出力端子はコンデンサC3を介してNチャネルFETQ4のゲートに接続される。二次巻線W3の他方の出力端子はFETQ4のソースに接続される。二次巻線W3の(・)マークの端子から電圧Vt3のパルスが出力されるが、トランスの出力電圧の平均は0ボルトなので、パルスデューティに応じて正と負のピーク電圧が変動する。

【0013】

基本FETスイッチ回路BCにおいて、FETQ4として、ショットキー接合のゲートを持つノーマリーオン動作のNチャネルGaAsFETを用いた場合の動作を説明する。FETQ4はノーマリーオンなのでゲート−ソース間電圧Vgs4が0ボルトでもオン抵抗が低く、ゲートがショットキー接合なのでVgs4>0で順方向ゲート電流が流れる。

【0014】

FETQ4のゲートにショットキーダイオード(以下ダイオードと称する)D7のカソードが接続される。ダイオードD7のアノードはFETQ4のVgs4に印加するパルスの電圧振幅を設定するツェナーダイオードD8のアノードに接続される。ツェナーダイオードD8のカソードはFETQ4のソースに接続される。

【0015】

ツェナーダイオードD8にはコンデンサC8が並列接続される。コンデンサC8は、ダイオードD7が逆バイアスになったとき電圧を保持し、ダイオードD7が順バイアスなったときに速やかに電荷を供給する。従ってFETQ4の順方向ゲート電流とD7の順方向電流とが平衡する電圧で、Vgs4に印加されるパルスの直流レベルが固定される。その結果、コンデンサC3にVgs4とVt3との差の電圧Vc3が生じる。

【0016】

FETQ4はノーマリーオンなので順方向ゲート電流が少しでも流れる正のVgs4でドレイン−ソース間のオン抵抗が低くなり、オフ時に完全にピンチオフするようにダイオードD8でパルス電圧振幅を設定する。よってドレインに電源を接続し、ソースに負荷を接続すれば、スイッチング動作の損失を低減できる。

【0017】

図3は、基本FETスイッチ回路BCにおける各部の動作波形を示す図である。図2の回路において、例えばT1の二次巻線W3の電圧Vt3が5Vp−pでデューティ比(DF)が90%である場合、トランスT1の出力電圧に直流成分が無いので、図3(a)に示すようにVt3は+0.5V〜−4.5Vとなる。また、FETQ4のゲート・ソース間電圧Vgs4の立ち上がり電圧Vf4が+1Vである場合には、ゲート・ソース間電圧Vgs4は図3(b)に示すように+1V〜−4Vとなる。従って、図3(c)に示すようにC3の電圧はVc3=−0.5Vとなる。

一方、DFが10%の場合は図3(d)に示すように電圧Vt3は+4.5V〜−0.5V、ゲート・ソース間電圧Vgs4は図3(e)に示すように+1V〜−4Vとなり、C3の電圧は図3(f)に示すようにVc3=+3.5Vとなる。

【0018】

図2に示されるスイッチング回路は、DFが増加している時は高速応答するダイオードD7の順方向電流でC3を放電し、DFが減少している時はFETQ4の順方向ゲート電流でコンデンサC3を充電するので、包絡線の10MHz前後に安定して追従することができる。

【0019】

次に、基本FETスイッチ回路BCにおいて、FETQ4として、電源用のNチャネルGaNFETを用いた場合の動作を説明する。この種のトランジスタは電源用として用いることができる。

電源用GaNFETは耐圧が高いが、マイクロ波帯電力増幅用よりも応答速度が一桁以上遅く、数100MHzの高速スイッチングさせるためにはスピードアップ処理が必要である。また、ゲートがショットキー接合でノーマリーオフであるので、順方向ゲート電流が流れる正のゲート・ソース間電圧Vgsを印加しなければオン抵抗が下がらない。

【0020】

FETQ4がオンの間、その順方向ゲート電流を保持するためにはコンデンサC3の容量を大きくしなければならない。しかしながら包絡線の10MHz前後に追従させようとすると、FETQ4のゲート電流やダイオードD7の順方向電流が過大になり破損するほどの電荷量になってしまう問題がある。つまり、既存のFETや回路方式は、高周波信号増幅器のスイッチング電源としては振幅が得られない。あるいは、振幅に耐えるものは応答速度が得られない。

【0021】

第1の実施形態に係わるFETスイッチング電源は、高電圧をスイッチングする終段のGaNFETと、そのスピードアップ回路と、複数のGaAsFETを用いたドライバアンプと、ドライバアンプをフローティングするためのパルストランスとを備える。これにより高速かつ大振幅の高周波スイッチング電源を実現することができる。このスイッチング電源を用いることにより、送信信号の包絡線に対応した電源電圧をPA1に供給するエンベロープトラッキングアンプの効率を高めることが可能になる。

【0022】

[第2の実施形態]

図4は、図1に示されるFETスイッチング電源3の第2の実施形態を示す回路図である図4のFETスイッチング回路3は、入力信号に対して同極性となる二次巻線W2、二次巻線W3および逆極性となる二次巻線W1から信号を出力するパルストランスT1aを備える。パルストランスT1aの二次側には3つの基本FETスイッチング回路BC1〜BC3が接続される。このうちBC3が図2の基本FETスイッチング回路BCに対応する。BC1およびBC2もBC3と同様の構成であり、BC1のFETに符合Q2を、BC2のFETに符合Q3を付して示す。BC1はパルストランスT1aに対して逆相で接続され、BC2およびBC3は同相で接続される。

【0023】

BC1のFETQ2のソースはFETQ3のドレインに接続され、FETQ3のソースはFETQ1のソースに接続される。FETQ2のソースとFETQ3のドレインとの接続点XCは、抵抗R1とコンデンサC4が並列接続されたスピードアップ回路を介して、FETQ1のゲートにスイッチング信号を出力する。FETQ1のドレインは電圧Vddの電源PS1に接続され、FETQ1のソースはアノード接地のショットキーダイオードD1のカソードに接続される。

【0024】

このほか、FETスイッチング回路3は、PA1に電力を供給する電圧Vddの直流電源PS1、およびFETQ1をオンにする電荷を供給する電圧Vpを出力するドライブ回路用電源PS2を備える。以上の構成において、0Vのローレベルから電源電圧Vddのハイレベルまでの大振幅かつスイッチングされた電圧が、FETQ1のゲートへ入力されるスイッチング信号と同じ極性でFETQ1のソースからLPF6(図示せず)出力される。

【0025】

基本FETスイッチング回路BC1〜BC3のFETQ2〜Q4として、ショットキー接合のゲートを持つノーマリーオン動作のNチャネルGaAsFETを用いた場合の動作を説明する。FETQ1はショットキー接合のゲートを持つノーマリーオフ動作の電源用Nチャネル型GaNFETとする。

【0026】

FETQ1は、ON時のオン抵抗を低くするために順方向ゲート電流を流す必要があるので、その電荷をFETQ1がオフ時に、電圧Vpのバイアス用のDC電源(ドライブ回路用電源)PS2からショットキーダイオードD2を介して、他方がFETQ1のソースに接続されたコンデンサC5に供給する。コンデンサC5はFETQ1のソースに対して基本FETスイッチング回路BC1のFETQ2のドレイン電圧をVpに保つ。FETQ1は耐圧が高いが応答速度が遅いので、スピードアップ回路として抵抗R1、R2、コンデンサC4および基本FETスイッチング回路BC3を備える。

なお図4において、符合XAはFETQ1のソース接続点、XBはFETQ2のドレイン接続点、XCはFETQ2のソース接続点である。

【0027】

図5は、図4に示されるFETスイッチング電源3における各部の電圧波形を示す図である。接続点XAはFETQ1がONの時にVddボルト、OFFの時に0ボルトになる(図5(a))。接続点XBは電圧Vpに充電されたコンデンサC5を介して接続点XAに接続されているので、FETQ1がONの時に(Vdd+Vp)ボルト、OFFの時にVpボルトになる(図5(b))。接続点XCはFETQ1がONの時に(Vdd+Vp)ボルト、OFFの時に0ボルトとなり、この電圧がスピードアップ回路に入力される(図5(c))。

【0028】

スピードアップ回路の端子○1と端子○2との間には、基本FETスイッチング回路BC3のFETQ4のドレインとソースがそれぞれ接続される。FETQ1のソースの電圧XAに対する○1の電圧XCは、FETQ1がオン時にVpボルト、オフ時の0ボルトとなる。FETQ1がオフ時にFETQ4で○1と○2が短絡されるので、低抵抗の抵抗R2を介してコンデンサC4は放電して0ボルトになる。

【0029】

FETQ1がオン時はFETQ4が開放なので、オフ→オン直後はFETQ1の入力容量Ci1とコンデンサC4とでVpが分圧されるが、スピードアップのためにコンデンサC4の容量は入力容量Ci1の容量より大きく設定するので、FETQ1のゲート・ソース間電圧Vgs1はほぼVpになる。この瞬間のFETQ1の非線形な順方向ゲート電流を高く設定することにより、コンデンサC4の充電時間を短くする。

【0030】

定常状態の順方向ゲート電流をIgf1、ゲート・ソース間電圧Vgs1をVf1とするとコンデンサC4の電圧はR1・Igf1=Vp−Vf1になる(図5(d))。FETQ1がオン→オフ直後はC4がCi1より大きいのでほぼゲート・ソース間電圧Vgs1=Vf1−Vpになり、FETQ1がオフになる時間よりは遅い時定数でR2とFETQ4を介してコンデンサC4の電荷が放電して0ボルトになる。この放電の時定数は、抵抗R2の値をr2、コンデンサC4の値をc4とすると(c4・r2)で概算できるので、パルス幅より短い時間に設定する。また、定常状態で許容される順方向ゲート電流をIgf1maxとし、抵抗R1の値をr1とすれば、r1>(Vp−Vf1)/Igf1maxとして許容電流を超えないようにr1の値を設定する。

【0031】

この実施形態における各値は、一例として最大電流10A、Vdd=50V、Vp=5V、Vf1=2.5V、Igf1=20mA,Ci1=300pF、r1=150Ω>125Ωとする。そして、抵抗R2とコンデンサC1〜C8等の値は使用するスイッチング周波数と包絡線の帯域幅に基づいて最適化するようにする。

【0032】

次に、電源投入時の過渡状態について説明する。スイッチング信号が入力されていない時はコンデンサC1〜C3の電圧やFETQ2〜FETQ4のVgs2〜Vgs4は0ボルトで、ノーマリーオンのFETQ2〜FETQ4はオン状態なので、FETQ2とFETQ3を経由する貫通電流は流れ続ける。ここではFETQ1のVf1がVp等の電源電圧と比べて十分低いとして説明を簡単にする。

【0033】

この状態で先に電源Vpをオンにすると、ダイオードD2、FETQ2、FETQ3、および負荷を経由してVp/RL(負荷抵抗)が流れる。この状態でのFETQ2とFETQ3のソースとドレインおよび負荷にかかる電圧は全てVpなので、コンデンサC5の電圧は0ボルトで、FETQ1はドレインがソースとして働きオン状態になり、Vddの電源がオフ時に開放となる場合は約Vpに充電してFETQ1はオフになる。

【0034】

この状態でVddを印加するとFETQ1はオフ状態になるが、負荷にかかる電圧などはVpのままである。逆にVddを先に印加してもFETQ1はオフ状態のままで電流は流れないが、次にVpを印加すると先にVpを印加した時と同じ状態になる。この状態でスイッチング信号を入力すると、FETQ3はFETQ1オフ時にオンになるのでFETQ1はオフになるが、FETQ1オン時にFETQ2がオンしてもC5が0ボルトなのでFETQ1はオンにならない。しかし、FETQ2とFETQ3のどちらか一方がオフ状態で貫通電流が流れるのはオン/オフ切替時の一瞬なので、負荷での電圧が下がりC5を充電し始めやがて正常動作に入る。以上からこの実施形態では、ダイオードD2、FETQ2、FETQ3の最大許容電流を約Vp/RL(負荷抵抗)とした場合の電流より高くする。

【0035】

なお、電源電圧を印加する前にスイッチング信号を入力して、コンデンサC1〜C3を充電してFETQ2〜FETQ4をオン/オフさせて、FETQ2とFETQ3を経由する貫通電流が流れ続けないようにしてから、電源電圧を印加するようにすれば良い。このようなシーケンスで回路を駆動することで、ダイオードD2の最大許容電流はVp/負荷抵抗より低くできる。また、FETQ2、FETQ3の最大許容電流も低くできる場合がある。

【0036】

図6は、電源電圧の印加タイミングを制御可能な回路の一例を示す図である。図6において図4と共通する部分には同じ符号を付して示すか省略し、ここでは異なる部分についてのみ説明する。

図6に示すように、トランスT1の一次巻線wiに電源供給制限部PXを接続する。電源供給制限部PXはスイッチング信号の有無を監視するセンサ部81を備える。なおセンサ部81は二次巻線側に接続してもよい。センサ部81は入力される信号を検波し、検波波形が既定レベル以上になるとスイッチング信号有りと判断する。そうすると電源PS1、PS2への一次電力をオンにする電源制御信号をスイッチ部PPの制御端子に入力する。

【0037】

スイッチ部PPは電源PS2の1次側に挿入され、オンにする制御信号に従って入力される電源PS1、PS2への電力をオンにする。このスイッチ部PPは、このオン信号により起動される内部タイマ、もしくは積分回路等により所定の時間遅れてONになる遅延部DLを備える。これによりオンにする制御信号が入力されたのち、電源PS2に電力が供給される。なお、このスイッチ部PPは、電源PS2の二次側に挿入され出力Vdd、Vpの供給開始タイミングを遅らせるものであっても良い。このようにFETQ2とFETQ3とを経由する貫通電流が流れ続けないシーケンス、タイミング制御をしてから、電源電圧を印加するようにしてもよい。以上のようにこの実施形態によっても、応答速度と振幅を確保することが可能なスイッチング回路を実現することができる。

【0038】

[第3の実施形態]

図7は、図1に示されるFETスイッチング電源3の第3の実施形態を示す回路図である。図7において図4と共通する部分には同じ符号を付して示し、ここでは異なる部分についてのみ説明する。図7において、FETQ1のソースにショットキーダイオードD9のアノードを接続し、ドレインにカソードを接続するようにした。これにより、負荷の異常などによる異常電圧からFETQ1を保護することができる。

【0039】

[第4の実施形態]

図8は、図1に示されるFETスイッチング電源3の第4の実施形態を示す回路図である。図8において図7と共通する部分には同じ符号を付して示し、ここでは異なる部分についてのみ説明する。

図8において、ダイオードD1のカソード○3、アノード○4にそれぞれFETQ5のドレイン○3、ソース○4が接続される。FETQ5のゲートには、FETQ1のゲートと逆極性のスイッチング信号が入力される。このFETQ5は、ショットキー接合のゲートを持つNチャネル型のノーマリーオフ型FETである。この逆極性の信号は基本FETスイッチ回路BC1と同様に生成される。

【0040】

図7においては、FETQ1がオフ時にダイオードD1に流れる電流とダイオードD1の順方向電圧降下の積が損失となる。このダイオードD1における電圧降下による損失を防ぐため、図8においては、オン抵抗が低いFETQ5をダイオードD1に並列接続することにより電圧降下を小さく抑えて損失を減少させるようにしている。

【0041】

なお、FETQ5はフローティングさせる必要はない。よって遅延回路などでパルストランスT1bの入力信号のタイミングを遅らせ、FETQ1のゲートに入力されるスイッチング信号のタイミングと合わせた逆極性の信号を生成しても良い。また、パルストランスを逆極性、すなわち入力信号に対してW1の二次巻線を同極性、W2の二次巻線とW3の二次巻線を逆極性にしても同様な効果が得られる。

【0042】

以上説明したようにこれらの実施形態によれば、高効率な高周波送信機用の高速・大振幅スイッチング電源およびスイッチング方法を提供することができる。

本発明のいくつかの実施形態を説明したが、これらの実施形態は、例として提示したものであり、発明の範囲を限定することは意図していない。これら新規な実施形態は、その他の様々な形態で実施されることが可能であり、発明の要旨を逸脱しない範囲で、種々の省略、置き換え、変更を行うことができる。これら実施形態やその変形は、発明の範囲や要旨に含まれるとともに、特許請求の範囲に記載された発明とその均等の範囲に含まれる。

【符号の説明】

【0043】

S…高周波送信機、1…パワーアンプ(PA)、2…広帯域ドライバ、3…FETスイッチング電源、4…検波器、5…波形変換部、6…ローパスフィルタ(LPF)、T1…パルストランス、BC…基本FETスイッチング回路、C1〜C8,C10…コンデンサ、Q1〜Q4…NチャネルFET、D1,D2,D7…ショットキーダイオード、D8…ツェナーダイオード、T1a…パルストランス、BC1〜BC3…基本FETスイッチング回路、PS1…電源、PS2…ドライブ回路用電源、R1,R2…抵抗、PX…電源供給制限部、81…センサ部、PP…スイッチ部、DL…遅延部

【特許請求の範囲】

【請求項1】

入力信号の波形に基づき送信増幅器をエンベロープトラッキング駆動するスイッチング電源において、

前記入力信号が一時側に入力されるトランスと、

前記トランスの二次側に接続されるスイッチング部とを具備し、

前記スイッチング部は、

ゲートおよびソースが前記トランスの二次側に接続されるFETと、

カソードが前記ゲートに接続されるショットキーダイオードと、

前記ショットキーダイオードに逆極性で直列接続されカソードが前記ソースに接続されるツェナーダイオードと、

前記ツェナーダイオードに並列接続されるコンデンサと、

を備える、スイッチング電源。

【請求項2】

前記FETは、ショットキー接合のゲートを持つノーマリーオン動作のNチャネルGaAsFETである、請求項1に記載のスイッチング電源。

【請求項3】

入力信号の波形に基づき送信増幅器をエンベロープトラッキング駆動するスイッチング電源において、

前記入力信号が一時側に入力されるトランスと、

前記トランスの二次側に接続される第1乃至第3のスイッチング部と、

並列接続される抵抗およびコンデンサを備えるスピードアップ回路と、

アノード接地のショットキーダイオードと、

ゲートが前記抵抗に接続されソースが前記ショットキーダイオードのカソードに接続される電源用FETとを具備し、

前記第1乃至第3のスイッチング部は、

ゲートおよびソースが前記トランスの二次側に接続される回路内FETと、

カソードが前記回路内FETのゲートに接続される回路内ショットキーダイオードと、

前記回路内ショットキーダイオードに逆極性で直列接続されカソードが前記回路内FETのソースに接続されるツェナーダイオードと、

前記ツェナーダイオードに並列接続されるコンデンサと、

をそれぞれ備え、

前記第1のスイッチング部の回路内FETのソースと、前記第2のスイッチング部の回路内FETのドレインと、前記抵抗とを接続し、

前記第3のスイッチング部の回路内FETのドレインおよびソースを、前記スピードアップ回路に並列接続した、スイッチング電源。

【請求項4】

前記電源用FETは、ショットキー接合のゲートを持つノーマリーオフ動作のNチャネル型GaNFETであり、

前記回路内FETは、それぞれショットキー接合のゲートを持つノーマリーオン動作のNチャネルGaAsFETである、請求項3に記載のスイッチング電源。

【請求項5】

前記第2および第3のスイッチング部は前記一次側と同相で接続され、前記第1のスイッチング部は前記一次側と逆相で接続される、請求項3に記載のスイッチング電源。

【請求項6】

さらに、前記電源用FETのソースにアノードが接続され、当該電源用FETのドレインにカソードが接続される電源用FET用ショットキーダイオードを具備する、請求項3に記載のスイッチング電源。

【請求項7】

さらに、少なくとも前記第1のスイッチング部の回路内FETと前記第2のスイッチング部の回路内FETとを駆動するための電源を発生する電源部と、

前記入力信号を検波して既定レベル以上の検波波形を検出するセンサ部と、

前記センサ部の検出結果に基づいて前記電源部を制御して、前記第1のスイッチング部の回路内FETと前記第2のスイッチング部の回路内FETとを経由する貫通電流を抑圧する制御部とを具備する、請求項3に記載のスイッチング電源。

【請求項8】

入力信号の波形に基づき送信増幅器をエンベロープトラッキング駆動するスイッチング電源の駆動方法において、

前記スイッチング電源は、

前記入力信号が一時側に入力されるトランスと、

前記トランスの二次側に接続されるスイッチング部とを具備し、

前記スイッチング部において、

FETのゲートおよびソースを前記トランスの二次側に接続し、

ショットキーダイオードのカソードを前記ゲートに接続し、

前記ショットキーダイオードに逆極性で直列接続されるツェナーダイオードのカソードを前記ソースに接続し、

コンデンサを前記ツェナーダイオードに並列接続する、

駆動方法。

【請求項9】

前記FETは、ショットキー接合のゲートを持つノーマリーオン動作のNチャネルGaAsFETである、請求項8に記載の駆動方法。

【請求項10】

入力信号の波形に基づき送信増幅器をエンベロープトラッキング駆動するスイッチング電源の駆動方法において、

前記スイッチング電源は、

前記入力信号が一時側に入力されるトランスと、

前記トランスの二次側に接続される第1乃至第3のスイッチング部と、

並列接続される抵抗およびコンデンサを備えるスピードアップ回路と、

アノード接地のショットキーダイオードと、

ゲートが前記抵抗に接続されソースが前記ショットキーダイオードのカソードに接続される電源用FETとを具備し、

前記第1乃至第3のスイッチング部のそれぞれにおいて、

回路内FETのゲートおよびソースを前記トランスの二次側に接続し、

回路内ショットキーダイオードのカソードを前記回路内FETのゲートに接続し、

前記回路内ショットキーダイオードに逆極性で直列接続されるツェナーダイオードのカソードを前記回路内FETのソースに接続し、

コンデンサを前記ツェナーダイオードに並列接続し、

前記第1のスイッチング部の回路内FETのソースと、前記第2のスイッチング部の回路内FETのドレインと、前記抵抗とを接続し、

前記第3のスイッチング部の回路内FETのドレインおよびソースを、前記スピードアップ回路に並列接続した、駆動方法。

【請求項11】

前記電源用FETは、ショットキー接合のゲートを持つノーマリーオフ動作のNチャネル型GaNFETであり、

前記回路内FETは、それぞれショットキー接合のゲートを持つノーマリーオン動作のNチャネルGaAsFETである、請求項10に記載の駆動方法。

【請求項12】

前記第2および第3のスイッチング部を前記一次側と同相で接続し、前記第1のスイッチング部を前記一次側と逆相で接続した、請求項10に記載の駆動方法。

【請求項13】

さらに、電源用FET用ショットキーダイオードのアノードを前記電源用FETのソースに接続し、カソードを当該電源用FETのドレインに接続した、請求項10に記載の駆動方法。

【請求項14】

前記スイッチング電源は、

さらに、少なくとも前記第1のスイッチング部の回路内FETと前記第2のスイッチング部の回路内FETとを駆動するための電源を発生する電源部を具備し、

前記入力信号を検波して既定レベル以上の検波波形を検出し、

前記検出結果に基づいて前記電源部を制御して、前記第1のスイッチング部の回路内FETと前記第2のスイッチング部の回路内FETとを経由する貫通電流を抑圧する、請求項10に記載の駆動方法。

【請求項1】

入力信号の波形に基づき送信増幅器をエンベロープトラッキング駆動するスイッチング電源において、

前記入力信号が一時側に入力されるトランスと、

前記トランスの二次側に接続されるスイッチング部とを具備し、

前記スイッチング部は、

ゲートおよびソースが前記トランスの二次側に接続されるFETと、

カソードが前記ゲートに接続されるショットキーダイオードと、

前記ショットキーダイオードに逆極性で直列接続されカソードが前記ソースに接続されるツェナーダイオードと、

前記ツェナーダイオードに並列接続されるコンデンサと、

を備える、スイッチング電源。

【請求項2】

前記FETは、ショットキー接合のゲートを持つノーマリーオン動作のNチャネルGaAsFETである、請求項1に記載のスイッチング電源。

【請求項3】

入力信号の波形に基づき送信増幅器をエンベロープトラッキング駆動するスイッチング電源において、

前記入力信号が一時側に入力されるトランスと、

前記トランスの二次側に接続される第1乃至第3のスイッチング部と、

並列接続される抵抗およびコンデンサを備えるスピードアップ回路と、

アノード接地のショットキーダイオードと、

ゲートが前記抵抗に接続されソースが前記ショットキーダイオードのカソードに接続される電源用FETとを具備し、

前記第1乃至第3のスイッチング部は、

ゲートおよびソースが前記トランスの二次側に接続される回路内FETと、

カソードが前記回路内FETのゲートに接続される回路内ショットキーダイオードと、

前記回路内ショットキーダイオードに逆極性で直列接続されカソードが前記回路内FETのソースに接続されるツェナーダイオードと、

前記ツェナーダイオードに並列接続されるコンデンサと、

をそれぞれ備え、

前記第1のスイッチング部の回路内FETのソースと、前記第2のスイッチング部の回路内FETのドレインと、前記抵抗とを接続し、

前記第3のスイッチング部の回路内FETのドレインおよびソースを、前記スピードアップ回路に並列接続した、スイッチング電源。

【請求項4】

前記電源用FETは、ショットキー接合のゲートを持つノーマリーオフ動作のNチャネル型GaNFETであり、

前記回路内FETは、それぞれショットキー接合のゲートを持つノーマリーオン動作のNチャネルGaAsFETである、請求項3に記載のスイッチング電源。

【請求項5】

前記第2および第3のスイッチング部は前記一次側と同相で接続され、前記第1のスイッチング部は前記一次側と逆相で接続される、請求項3に記載のスイッチング電源。

【請求項6】

さらに、前記電源用FETのソースにアノードが接続され、当該電源用FETのドレインにカソードが接続される電源用FET用ショットキーダイオードを具備する、請求項3に記載のスイッチング電源。

【請求項7】

さらに、少なくとも前記第1のスイッチング部の回路内FETと前記第2のスイッチング部の回路内FETとを駆動するための電源を発生する電源部と、

前記入力信号を検波して既定レベル以上の検波波形を検出するセンサ部と、

前記センサ部の検出結果に基づいて前記電源部を制御して、前記第1のスイッチング部の回路内FETと前記第2のスイッチング部の回路内FETとを経由する貫通電流を抑圧する制御部とを具備する、請求項3に記載のスイッチング電源。

【請求項8】

入力信号の波形に基づき送信増幅器をエンベロープトラッキング駆動するスイッチング電源の駆動方法において、

前記スイッチング電源は、

前記入力信号が一時側に入力されるトランスと、

前記トランスの二次側に接続されるスイッチング部とを具備し、

前記スイッチング部において、

FETのゲートおよびソースを前記トランスの二次側に接続し、

ショットキーダイオードのカソードを前記ゲートに接続し、

前記ショットキーダイオードに逆極性で直列接続されるツェナーダイオードのカソードを前記ソースに接続し、

コンデンサを前記ツェナーダイオードに並列接続する、

駆動方法。

【請求項9】

前記FETは、ショットキー接合のゲートを持つノーマリーオン動作のNチャネルGaAsFETである、請求項8に記載の駆動方法。

【請求項10】

入力信号の波形に基づき送信増幅器をエンベロープトラッキング駆動するスイッチング電源の駆動方法において、

前記スイッチング電源は、

前記入力信号が一時側に入力されるトランスと、

前記トランスの二次側に接続される第1乃至第3のスイッチング部と、

並列接続される抵抗およびコンデンサを備えるスピードアップ回路と、

アノード接地のショットキーダイオードと、

ゲートが前記抵抗に接続されソースが前記ショットキーダイオードのカソードに接続される電源用FETとを具備し、

前記第1乃至第3のスイッチング部のそれぞれにおいて、

回路内FETのゲートおよびソースを前記トランスの二次側に接続し、

回路内ショットキーダイオードのカソードを前記回路内FETのゲートに接続し、

前記回路内ショットキーダイオードに逆極性で直列接続されるツェナーダイオードのカソードを前記回路内FETのソースに接続し、

コンデンサを前記ツェナーダイオードに並列接続し、

前記第1のスイッチング部の回路内FETのソースと、前記第2のスイッチング部の回路内FETのドレインと、前記抵抗とを接続し、

前記第3のスイッチング部の回路内FETのドレインおよびソースを、前記スピードアップ回路に並列接続した、駆動方法。

【請求項11】

前記電源用FETは、ショットキー接合のゲートを持つノーマリーオフ動作のNチャネル型GaNFETであり、

前記回路内FETは、それぞれショットキー接合のゲートを持つノーマリーオン動作のNチャネルGaAsFETである、請求項10に記載の駆動方法。

【請求項12】

前記第2および第3のスイッチング部を前記一次側と同相で接続し、前記第1のスイッチング部を前記一次側と逆相で接続した、請求項10に記載の駆動方法。

【請求項13】

さらに、電源用FET用ショットキーダイオードのアノードを前記電源用FETのソースに接続し、カソードを当該電源用FETのドレインに接続した、請求項10に記載の駆動方法。

【請求項14】

前記スイッチング電源は、

さらに、少なくとも前記第1のスイッチング部の回路内FETと前記第2のスイッチング部の回路内FETとを駆動するための電源を発生する電源部を具備し、

前記入力信号を検波して既定レベル以上の検波波形を検出し、

前記検出結果に基づいて前記電源部を制御して、前記第1のスイッチング部の回路内FETと前記第2のスイッチング部の回路内FETとを経由する貫通電流を抑圧する、請求項10に記載の駆動方法。

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【公開番号】特開2012−186563(P2012−186563A)

【公開日】平成24年9月27日(2012.9.27)

【国際特許分類】

【出願番号】特願2011−46901(P2011−46901)

【出願日】平成23年3月3日(2011.3.3)

【出願人】(000003078)株式会社東芝 (54,554)

【Fターム(参考)】

【公開日】平成24年9月27日(2012.9.27)

【国際特許分類】

【出願日】平成23年3月3日(2011.3.3)

【出願人】(000003078)株式会社東芝 (54,554)

【Fターム(参考)】

[ Back to top ]