スイッチング電源及び画像形成装置

【課題】 スイッチング電源の一次側の電流検出抵抗によって生じる逆起電力によりスイッチング素子が発熱する。

【解決手段】 スイッチング手段に接続され、スイッチング手段に流れる電流を検出する電流検出抵抗に並列に接続され、電流検出抵抗によって生じるスイッチング手段の発熱を低減するスイッチング電源。

【解決手段】 スイッチング手段に接続され、スイッチング手段に流れる電流を検出する電流検出抵抗に並列に接続され、電流検出抵抗によって生じるスイッチング手段の発熱を低減するスイッチング電源。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は電子機器に電力を供給するスイッチング電源に関する。

【背景技術】

【0002】

従来のスイッチング電源について図8、図9を用いて説明する。図8において、一次電解コンデンサC1に充電された直流電圧Vinは、トランスT1の一次巻線を介して、スイッチング素子であるFET1のドレイン端子に供給される。FET1のソース端子は、電流検出抵抗Risを介して、一次電解コンデンサC1に接続される。トランスT1の二次巻線は、二次整流ダイオードD3を介して、二次電解コンデンサC2に供給される。二次電解コンデンサC2に充電される直流電圧Voutがスイッチング電源の出力電圧となる。さらに、直流電圧Voutは、抵抗R3と抵抗R4によって分圧され、シャントレギュレータIC2のREF端子に供給される。シャントレギュレータIC2のカソード端子には、フォトカプラPC−FBのLEDが接続される。フォトカプラPC−FBのフォトトランジスタは、PWMコントロールモジュールIC1に接続される。フォトカプラPC−FBのフォトトランジスタのコレクタ電圧が、スイッチング電源の出力電圧Voutのフィードバック信号(FB信号ともいう)である。FB信号は、PWMコントロールモジュールIC1内で抵抗R1でプルアップされ、PWMアンプAMP1の反転入力端子に接続される。PWMアンプAMP1の非反転入力端子には、三角波発生回路から三角波信号(OSC信号ともいう)が供給される。

【0003】

図9において、時刻t0のように、OSC信号の電圧が、FB信号の電圧よりも高い場合、PWMアンプAMP1の出力はHレベルとなる。PWMアンプAMP1の出力は、論理和回路ORの入力端子に供給される。論理和回路ORの他の入力端子には、フリップフロップ回路FFのQ出力が供給されている。t0においてフリップフロップFFのQ出力は、後述のとおりLowレベル(Lレベルともいう)である。よって、論理和回路ORの出力レベルはHighレベル(Hレベル)となる。論理和回路ORの出力は、スイッチング素子としてのPチャネルMOS FETであるFET2、及びNチャネルMOS FETであるFET3からなる出力バッファ回路に供給される。従って、PWMコントロールモジュールIC1の出力信号(OUT信号ともいう)は、Lレベルとなる。OUT信号はFET1のゲート端子に供給される。よってFET1はオフする。

【0004】

時刻t1において、OSC信号の電圧がFB信号の電圧よりも低くなると、PWMアンプAMP1の出力はLレベル、論理和回路ORの出力はLレベル、OUT信号はHレベルとなり、FET1がオンする。すると、FET1にドレイン電流Idが流れる。時刻t2において、再度、OSC信号の電圧が、FB信号の電圧よりも高くなると、PWMアンプAMP1の出力はHレベル、論理和回路ORの出力はHレベル、OUT信号はLレベルとなり、FET1がオフする。すると、Idが停止する。

【0005】

さて、時刻t3以降において、スイッチング電源の出力電流Ioutが増加すると、出力電圧Voutがわずかに低下する。すると、シャントレギュレータIC2はPC−FBのLEDに流れる電流を減少させる。これにより、FB信号が上昇し、FET1のオン時間(オンパルス幅ともいう)t4〜t5の時間が広がる。すると、出力電圧Voutはわずかに上昇する。

【0006】

以上のように、PWMコントロールモジュールIC1は、FET1のオン時間を制御(PWM制御)して、出力電圧をVoutを安定化させる。

【0007】

ところで、このようなスイッチング電源は、通常、過負荷保護機能を有する。具体的な過負荷保護回路は、FET1のソース端子に接続された電流検出抵抗Risによって、FET1のドレイン電流Idを検出し、ドレイン電流Idがあらかじめ規定された値Vref÷Risとなった場合、FET1をオフする。これにより、スイッチング電源の負荷電流を規定値Ip以下に制限することができる。

【0008】

以下、この動作を説明する。FET1のドレイン電流Idは、電流検出抵抗Risによって電圧変換され、電流検出信号ISとして、PWMコントロールモジュールIC1内のカレントセンスアンプAMP2の非反転入力端子に供給される。一方、カレントセンスアンプAMP2の反転入力端子には、定電圧源Vrefが接続されている。時刻t0〜t8のように、ドレイン電流Idの値がVref÷Risよりも小さい場合、電流検出信号IS信号の電圧はVrefよりも小さくなり、アンプAMP2の出力はLレベルとなる。アンプAMP2の出力は、フリップフロップFFのS入力端子に供給されている。

【0009】

一方、フリップフロップFFのR入力端子には、OSC信号が供給されている。フリップフロップFFは、OSC信号の頂点でリセットされる構成である。OSC信号の頂点にあたる時刻t1、t4、t6、t8でフリップフロップFFがリセットされる。この間、フリップフロップFFのS入力端子はLレベルであるから、フリップフロップFFのQ出力はHレベルとなる。フリップフロップFFのQ出力はORに供給されている。よって、時刻t0〜t8までの間は、FET1のスイッチング動作に影響を与えない。時刻t9でドレイン電流Idの値がVref÷Risに達すると、電流検出信号IS信号の電圧がVrefを超え、アンプAMP2の出力がHレベルとなる。すると、フリップフロップFFのQ端子はHレベル、ORの出力はHレベル、OUT信号はLレベルとなり、FET1がオフする。時刻t10においてフリップフロップFFがリセットされ、FET1が再度オンするものの、ドレインIdがVref÷Risに達した時点(t11)で、FET1がオフされる。以上のように、ドレイン電流Idはあらかじめ規定された値Vref÷Risで制限される。よって、スイッチング電源の出力電流Ioutも、あらかじめ規定された値Ip以下に制限されることとなる。以上の従来の構成に類似するものが特許文献1に開示されている。

【先行技術文献】

【特許文献】

【0010】

【特許文献1】特開2004−312901号公報

【発明の概要】

【発明が解決しようとする課題】

【0011】

しかし、上記のスイッチング電源には、以下に説明するような課題がある。

FET1のドレイン電流Idは、三角形状の間欠波形となる。従って、電流検出抵抗Risに流れる電流も、同様に三角形状の間欠波形となる。よって、通常、電流検出抵抗Risには耐パルス性の高い抵抗が採用される。例えば、図10(A)に示すように、ワイヤ状の金属素体をコイル状に巻いた巻線抵抗や、図10(B)に示すように、筒状の抵抗皮膜に螺旋状のスリットを設けた皮膜抵抗が採用されることが多い。

【0012】

ところで、これらの抵抗は、そのコイル状の構造から、インダクタンスLisを持つ。図11、および図12を用いて、電流検出抵抗RisがインダクタンスLisを持つ場合の動作について説明する。

【0013】

時刻t21において、FET1のゲート−ソース間電圧Vgsが上昇し、ゲート閾値電圧Vthを超えると、ドレイン電流Idが流れ始め、次第に上昇していく。この電流は、電流検出抵抗RisのインダクタンスLisにも流れる。時刻t22において、ゲート−ソース間電圧Vgsが下降してゲート閾値電圧Vthを下回ると、ドレインIdは急速に低下していく。すると、インダクタンスLisに逆起電力Vsが発生する。この逆起電力Vsは、FET1のソース端子側がマイナス、PWMコントロールモジュールIC1のGND端子側がプラスの極性となる。PWMコントロールモジュールIC1内のFET3には、ボディダイオードD1が存在する。よって逆起電力(逆起電圧)Vsは、図12中の破線で示すとおり、IC1のGND端子→ボディダイオードD1→FET1のゲート端子のルートで、FET1のゲート−ソース間に印加される。すると、図12中の時刻t23のように、FET1のゲート−ソース間電圧Vgsが閾値電圧Vthを超え、FET1が再度オンしてドレイン電流Idが流れ出す。このとき、FET1のドレイン−ソース間電圧Vdsは、非常に高い状態にあるため、FET1が発熱して、場合によってはFET1が破壊に至るという課題がある。

【0014】

本発明は上記課題を鑑み、電流検出抵抗のインダクタンスによる逆起電力によるスイッチング素子の発熱を低減することを目的とする。

【課題を解決するための手段】

【0015】

上記課題を解決するための本発明のスイッチング電源は、トランスの一次側を駆動するスイッチング手段と、前記スイッチング手段に接続され、前記スイッチング手段に流れる電流を検出する電流検出手段と、前記電流検出手段に並列に接続され、前記電流検出抵抗のインダクタンスによって生じる起電力を低減する電力低減手段とを有することを特徴とする。

【発明の効果】

【0016】

本発明によれば。電流検出抵抗のインダクタンスの影響によるスイッチング手段の発熱を低減できる。

【図面の簡単な説明】

【0017】

【図1】実施例1の回路図

【図2】実施例1の回路の動作波形図

【図3】実施例2の回路図

【図4】実施例2の回路の動作波形図

【図5】実施例2の変形例を示す回路図

【図6】実施例3の回路図

【図7】実施例3の回路の動作波形図

【図8】従来のスイッチング電源回路図

【図9】従来のスイッチング電源回路の動作波形図

【図10】電流検出抵抗の構成を示す図

【図11】従来の回路図

【図12】従来の回路の動作波形図

【図13】スイッチング電源の適用例

【発明を実施するための形態】

【0018】

次に、上述した課題を解決するための本発明の具体的な構成について、以下に実施例に基づき説明する。なお、以下に示す実施例は一例であって、この発明の技術的範囲をそれらのみに限定する趣旨のものではない。

【0019】

(実施例1)

図1、図2を用いて本発明の実施例1のスイッチング電源について説明する。実施例1は、電流検出抵抗Risと並列に、ダイオードDclを接続し、電流検出抵抗のインダクタンスLisで発生する逆起電力(逆起電圧)をDclの順方向電圧Vfでクランプすることにより、FET1が再度オンすることを防ぐことを特徴とする。つまり、ダイオードDclが起電力低減回路として機能する。なお、この電流検出抵抗は、上記で説明したワイヤ状の金属素体をコイル状に巻いた巻線抵抗もしくは筒状の抵抗皮膜に螺旋状のスリットを設けた皮膜抵抗である(図10参照)。

【0020】

図1は、上記の図8における主要部を抜粋した図を用いて示している。基本構成は図8と同様であり、トランスの一次側(一次巻線)をスイッチング素子で所定の周波数で駆動することによりトランスの二次側(二次巻線)から電圧を出力するスイッチング電源を前提としている。なお、図8と共通する個所については同じ符号で示している。図1におけるダイオードDclが図8の構成に対して追加されている点が異なる。

【0021】

図2は、実施例1におけるスイッチング素子であるFET1のドレイン−ソース間電圧とドレイン電流とゲート−ソース間電圧の動作波形を示している。図2の時刻t31において、FET1のゲート−ソース間電圧Vgsが上昇し、ゲート閾値電圧Vthを超えると、ドレイン電流Idが流れ始め、次第に上昇していく。このドレイン電流Idは、電流検出RisのインダクタンスLisにも流れる。時刻t32において、ドレイン−ソース間電圧Vgsが下降してゲート閾値電圧Vthを下回ると、ドレイン電流Idは急速に低下していく。すると、インダクタンスLisに逆起電力Vsが発生する。この逆起電力Vsは、FET1のソース端子側がマイナス、PWMコントロールモジュールIC1のGND端子側がプラスの極性となる。

【0022】

ここで、実施例1では電流検出抵抗Risに対して並列にダイオードDclが接続されている。このときダイオードDclの順方向の電圧降下Vfは、FET1のゲート閾値電圧Vthよりも小さい。従って、発生した逆起電力Vsは、図2中の破線で示すとおり、ダイオードDclの順方向の電圧降下Vfでクランプされることになる。つまり、時刻t32〜t34の間、FET1のゲート−ソース間電圧Vgsも、ダイオードDclのVfでクランプされることとなり、FET1の閾値電圧Vthを超えることはない。

【0023】

以上、説明したように、実施例1では、電流検出抵抗(巻線抵抗)に並列にダイオードを接続し、そのダイオードの順方向の電圧降下をFET1のゲート閾値電圧Vthより小さい値にする。これにより、FET1が電流検出抵抗の逆起電力によって、再度オンしてFET1にドレイン電流Idが流れ出すことがなくなるため、FET1の発熱を低減することができる。FET1の発熱が低減されれば、発熱によって生じる破壊する等の故障の発生を抑制できる。

【0024】

(実施例2)

次に、図3と図4を用いて実施例2の構成と動作を説明する。実施例2の特徴は、電流検出抵抗Risと並列に、コンデンサCclを接続する点である。

これにより、電流検出抵抗のインダクタンスLisの逆起電力Vsを低減して、FET1の再オンを防ぐことが特徴である。つまり、コンデンサCclが起電力低減回路として機能する。この電流検出抵抗は、上記で説明したワイヤ状の金属素体をコイル状に巻いた巻線抵抗もしくは筒状の抵抗皮膜に螺旋状のスリットを設けた皮膜抵抗である(図10参照)。

【0025】

図3は、上記の図8の主要部を抜粋した図を用いて示している。基本構成は図8と同様であり、トランスの一次側(一次巻線)をスイッチング素子で所定の周波数で駆動することによりトランスの二次側(二次巻線)から電圧を出力するスイッチング電源を前提としている。図8と共通する個所については同じ符号で示している。図3におけるコンデンサCclが図8の構成に対して追加されている点が異なる。

【0026】

図4は、実施例2におけるスイッチング素子であるFET1のドレイン−ソース間電圧とドレイン電流とゲート−ソース間電圧の動作波形を示している。時刻t41において、FET1のゲート−ソース間電圧Vgsが上昇し、ゲート−ソース間電圧Vgsがゲート閾値電圧Vthを超えると、ドレイン電流Idが流れ始め、次第に上昇していく。このドレイン電流Idは、電流検出抵抗RisのインダクタンスLisにも流れる。時刻t42において、ゲート−ソース間電圧Vgsが下降してゲート閾値電圧Vthを下回ると、ドレイン電流Idは急速に低下していく。すると、電流検出抵抗RisのインダクタンスLisに逆起電力Vsが発生する。この逆起電力Vsは、FET1のソース端子側がマイナス、PWMコントロールモジュールIC1のGND端子側がプラスの極性となる。

【0027】

実施例2の構成では、電流検出抵抗Risには、コンデンサCclが接続されている。インダクタンスLisに発生した逆起電力Vsによって、コンデンサCclに蓄えられるエネルギと、それまでインダクタンスLisに流れていたドレイン電流Idpによって、インダクタンスLisに蓄えられるエネルギは等しくなる。つまり、概ね、以下の式(1)が成り立つことになる。

【0028】

【数1】

【0029】

上式(1)をVsについて解くと、Vsは、以下の式(2)で示される。

【0030】

【数2】

【0031】

時刻t42〜t43の期間、FET1のゲート−ソース間電圧Vgsは、このVsまで上昇することとなる。ここで、実施例2ではコンデンサCclの静電容量は、以下の式(3)を満たすように設定している。

【0032】

【数3】

【0033】

このように設定することで、Vsは、ゲート閾値電圧Vthを超えることはない。

【0034】

以上、説明したように、実施例2では、電流検出抵抗(巻線抵抗)に並列にダイオードを接続し、そのダイオードの順方向の電圧降下をFET1のゲート閾値電圧Vthより小さい値にする。これにより、FET1が電流検出抵抗の逆起電力によって、再度オンしてFET1にドレイン電流Idが流れ出すことがなくなるため、FET1の発熱を低減することができる。FET1の発熱が低減されれば、発熱によって生じる破壊する等の故障の発生を抑制できる。

【0035】

なお、実施例2の変形例として図5に示すように、コンデンサCclに、さらに抵抗Rclを直列に接続する構成でも同様の効果を得ることができる。この場合は、コンデンサCclと抵抗Rclで生成する回路の電圧値を閾値電圧Vthより低い値にすればよい。

【0036】

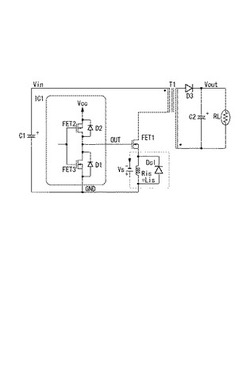

(実施例3)

次に、図6と図7を用いて実施例3の構成及び動作を説明する。実施例3は、DC/DCコンバータに適用した例である。実施例1と同様、電流検出抵抗Risと並列にダイオードDclを接続し、電流検出抵抗のインダクタンスLisで発生する逆起電力をDclの順方向の電圧降下Vfでクランプし、FET1が再度オンすることを防ぐものである。この電流検出抵抗は、上記で説明したワイヤ状の金属素体をコイル状に巻いた巻線抵抗もしくは筒状の抵抗皮膜に螺旋状のスリットを設けた皮膜抵抗である(図10参照)。

【0037】

まず、図6を用いてDC/DCコンバータの回路構成を説明する。なお、上記の図8のトランスの一次側の回路構成と同様の個所は省略または同符号を示している。図6において一次電解コンデンサC1に充電された直流電圧Vinは、電流検出抵抗Risを介して、FET1のソース端子に供給される。FET1のドレイン端子は、入力電圧Vinをスイッチングしてパルス電圧を生成する。

【0038】

FET1によって生成されたパルス電圧は、ダイオードD3とインダクタL1、と二次電解コンデンサC2によって平滑化され、出力電圧Voutとして負荷抵抗RLに供給される。FET1のゲート端子には、PWMコントロールモジュールIC1よりOUT信号が供給されている。PWMコントロールモジュールIC1はFET1のスイッチングをPWM信号によって制御して、出力電圧Voutを安定化させる。これが実施例のDC/DCコンバータの構成である。

【0039】

次に、以上の回路の動作波形を図7に示す。時刻t51で、FET1のゲート−ソース間電圧Vgsが低下し、ゲート閾値電圧Vthを下回ると、FET1にドレイン電流Idが流れる。このドレイン電流Idは、電流検出抵抗RisのインダクタンスLisにも流れる。時刻t52において、ゲート−ソース間電圧Vgsが上昇しゲート閾値電圧Vthを上回ると、ドレインIdは急速に低下していく。すると、電流検出抵抗RisのインダクタンスLisに逆起電力Vsが発生する。この逆起電力Vsは、入力電圧Vinの側がマイナス、FET1のソース端子側がプラスの極性となる。

【0040】

実施例3では、電流検出抵抗Risに並列にダイオードDclが接続されている。このときダイオードDclの順方向の電圧降下Vfは、FET1のゲート閾値電圧Vthよりも小さく設定されている。すると、逆起電力Vsは、図7中の破線で示すとおり、ダイオードDclの順方向の電圧降下Vfでクランプされる。よって、時刻t52からt53の間、FET1のゲート−ソース間電圧Vgsも、このダイオードの電圧降下Vfでクランプされることとなり、ゲート閾値電圧Vthを下回ることはない。

【0041】

以上、説明したように、実施例3では、電流検出抵抗(巻線抵抗)に並列にダイオードを接続し、そのダイオードの順方向の電圧降下をFET1のゲート閾値電圧Vthより小さい値にする。これにより、FET1が電流検出抵抗の逆起電力によって、再度オンしてFET1にドレイン電流Idが流れ出すことがなくなるため、FET1の発熱を低減することができる。FET1の発熱が低減されれば、発熱によって生じる破壊する等の故障の発生を抑制できる。

【0042】

<スイッチング電源の適用例>

上記の実施例で説明したスイッチング電源装置を、例えばレーザビームプリンタ、複写機、ファクシミリ等の画像形成装置における低電圧電源として適用することができる。以下にその適用例を説明する。スイッチング電源は、画像形成装置における制御部としてのコントローラへの電力供給、また、用紙を搬送する搬送ローラの駆動部としてのモータへの電力供給のための電源として適用される。

【0043】

図13(A)に画像形成装置の一例であるレーザビームプリンタの概略構成を示す。レーザビームプリンタ200は、画像形成部210として潜像が形成される像担持体としての感光ドラム211、感光ドラムに形成された潜像をトナーで現像する現像部212を備えている。そして感光ドラム211に現像されたトナー像をカセット216から供給された記録媒体としてのシート(不図示)に転写して、シートに転写したトナー像を定着器214で定着してトレイ215に排出する。また、図13(B)画像形成装置の制御部としてのコントローラと駆動部としてのモータへの電源からの電力供給ラインを示す。前述の電流共振電源は、このような画像形成動作を制御するCPU310有するコントローラへ300の電力供給、また、画像形成のための駆動部としてのモータ312及びモータ313に電力を供給する低圧電源として適用できる。供給する電力としては、コントローラ300へは3.3V、モータへは24Vを供給する。例えばモータ312はシートを搬送する搬送ローラを駆動するモータ、モータ313は定着器214を駆動するモータである。このような画像形成装置の低電圧電源として、上記のスイッチング電源装置を適用した場合でも、上記実施例と同様、低電圧電源のスイッチング素子の温度上昇を低減し、安定した電圧を供給することができ、画像形成装置を安定して動作することができる。なお、上記実施例で説明したスイッチング電源は、ここで示した画像形成装置に限らず他の電子機器の低電圧電源としても適用可能である。

【符号の説明】

【0044】

C1 一次電解コンデンサ

C2 二次次電解コンデンサ

FET1、FET2、FET3 FIELD EFFECT TRANSISTOR(電解効果トランジスタ)

T1 トランス

D1、D2、D3、Dcl ダイオード

Ris 電流検出抵抗

RL 負荷抵抗

IC1 PWMコントロールモジュール

【技術分野】

【0001】

本発明は電子機器に電力を供給するスイッチング電源に関する。

【背景技術】

【0002】

従来のスイッチング電源について図8、図9を用いて説明する。図8において、一次電解コンデンサC1に充電された直流電圧Vinは、トランスT1の一次巻線を介して、スイッチング素子であるFET1のドレイン端子に供給される。FET1のソース端子は、電流検出抵抗Risを介して、一次電解コンデンサC1に接続される。トランスT1の二次巻線は、二次整流ダイオードD3を介して、二次電解コンデンサC2に供給される。二次電解コンデンサC2に充電される直流電圧Voutがスイッチング電源の出力電圧となる。さらに、直流電圧Voutは、抵抗R3と抵抗R4によって分圧され、シャントレギュレータIC2のREF端子に供給される。シャントレギュレータIC2のカソード端子には、フォトカプラPC−FBのLEDが接続される。フォトカプラPC−FBのフォトトランジスタは、PWMコントロールモジュールIC1に接続される。フォトカプラPC−FBのフォトトランジスタのコレクタ電圧が、スイッチング電源の出力電圧Voutのフィードバック信号(FB信号ともいう)である。FB信号は、PWMコントロールモジュールIC1内で抵抗R1でプルアップされ、PWMアンプAMP1の反転入力端子に接続される。PWMアンプAMP1の非反転入力端子には、三角波発生回路から三角波信号(OSC信号ともいう)が供給される。

【0003】

図9において、時刻t0のように、OSC信号の電圧が、FB信号の電圧よりも高い場合、PWMアンプAMP1の出力はHレベルとなる。PWMアンプAMP1の出力は、論理和回路ORの入力端子に供給される。論理和回路ORの他の入力端子には、フリップフロップ回路FFのQ出力が供給されている。t0においてフリップフロップFFのQ出力は、後述のとおりLowレベル(Lレベルともいう)である。よって、論理和回路ORの出力レベルはHighレベル(Hレベル)となる。論理和回路ORの出力は、スイッチング素子としてのPチャネルMOS FETであるFET2、及びNチャネルMOS FETであるFET3からなる出力バッファ回路に供給される。従って、PWMコントロールモジュールIC1の出力信号(OUT信号ともいう)は、Lレベルとなる。OUT信号はFET1のゲート端子に供給される。よってFET1はオフする。

【0004】

時刻t1において、OSC信号の電圧がFB信号の電圧よりも低くなると、PWMアンプAMP1の出力はLレベル、論理和回路ORの出力はLレベル、OUT信号はHレベルとなり、FET1がオンする。すると、FET1にドレイン電流Idが流れる。時刻t2において、再度、OSC信号の電圧が、FB信号の電圧よりも高くなると、PWMアンプAMP1の出力はHレベル、論理和回路ORの出力はHレベル、OUT信号はLレベルとなり、FET1がオフする。すると、Idが停止する。

【0005】

さて、時刻t3以降において、スイッチング電源の出力電流Ioutが増加すると、出力電圧Voutがわずかに低下する。すると、シャントレギュレータIC2はPC−FBのLEDに流れる電流を減少させる。これにより、FB信号が上昇し、FET1のオン時間(オンパルス幅ともいう)t4〜t5の時間が広がる。すると、出力電圧Voutはわずかに上昇する。

【0006】

以上のように、PWMコントロールモジュールIC1は、FET1のオン時間を制御(PWM制御)して、出力電圧をVoutを安定化させる。

【0007】

ところで、このようなスイッチング電源は、通常、過負荷保護機能を有する。具体的な過負荷保護回路は、FET1のソース端子に接続された電流検出抵抗Risによって、FET1のドレイン電流Idを検出し、ドレイン電流Idがあらかじめ規定された値Vref÷Risとなった場合、FET1をオフする。これにより、スイッチング電源の負荷電流を規定値Ip以下に制限することができる。

【0008】

以下、この動作を説明する。FET1のドレイン電流Idは、電流検出抵抗Risによって電圧変換され、電流検出信号ISとして、PWMコントロールモジュールIC1内のカレントセンスアンプAMP2の非反転入力端子に供給される。一方、カレントセンスアンプAMP2の反転入力端子には、定電圧源Vrefが接続されている。時刻t0〜t8のように、ドレイン電流Idの値がVref÷Risよりも小さい場合、電流検出信号IS信号の電圧はVrefよりも小さくなり、アンプAMP2の出力はLレベルとなる。アンプAMP2の出力は、フリップフロップFFのS入力端子に供給されている。

【0009】

一方、フリップフロップFFのR入力端子には、OSC信号が供給されている。フリップフロップFFは、OSC信号の頂点でリセットされる構成である。OSC信号の頂点にあたる時刻t1、t4、t6、t8でフリップフロップFFがリセットされる。この間、フリップフロップFFのS入力端子はLレベルであるから、フリップフロップFFのQ出力はHレベルとなる。フリップフロップFFのQ出力はORに供給されている。よって、時刻t0〜t8までの間は、FET1のスイッチング動作に影響を与えない。時刻t9でドレイン電流Idの値がVref÷Risに達すると、電流検出信号IS信号の電圧がVrefを超え、アンプAMP2の出力がHレベルとなる。すると、フリップフロップFFのQ端子はHレベル、ORの出力はHレベル、OUT信号はLレベルとなり、FET1がオフする。時刻t10においてフリップフロップFFがリセットされ、FET1が再度オンするものの、ドレインIdがVref÷Risに達した時点(t11)で、FET1がオフされる。以上のように、ドレイン電流Idはあらかじめ規定された値Vref÷Risで制限される。よって、スイッチング電源の出力電流Ioutも、あらかじめ規定された値Ip以下に制限されることとなる。以上の従来の構成に類似するものが特許文献1に開示されている。

【先行技術文献】

【特許文献】

【0010】

【特許文献1】特開2004−312901号公報

【発明の概要】

【発明が解決しようとする課題】

【0011】

しかし、上記のスイッチング電源には、以下に説明するような課題がある。

FET1のドレイン電流Idは、三角形状の間欠波形となる。従って、電流検出抵抗Risに流れる電流も、同様に三角形状の間欠波形となる。よって、通常、電流検出抵抗Risには耐パルス性の高い抵抗が採用される。例えば、図10(A)に示すように、ワイヤ状の金属素体をコイル状に巻いた巻線抵抗や、図10(B)に示すように、筒状の抵抗皮膜に螺旋状のスリットを設けた皮膜抵抗が採用されることが多い。

【0012】

ところで、これらの抵抗は、そのコイル状の構造から、インダクタンスLisを持つ。図11、および図12を用いて、電流検出抵抗RisがインダクタンスLisを持つ場合の動作について説明する。

【0013】

時刻t21において、FET1のゲート−ソース間電圧Vgsが上昇し、ゲート閾値電圧Vthを超えると、ドレイン電流Idが流れ始め、次第に上昇していく。この電流は、電流検出抵抗RisのインダクタンスLisにも流れる。時刻t22において、ゲート−ソース間電圧Vgsが下降してゲート閾値電圧Vthを下回ると、ドレインIdは急速に低下していく。すると、インダクタンスLisに逆起電力Vsが発生する。この逆起電力Vsは、FET1のソース端子側がマイナス、PWMコントロールモジュールIC1のGND端子側がプラスの極性となる。PWMコントロールモジュールIC1内のFET3には、ボディダイオードD1が存在する。よって逆起電力(逆起電圧)Vsは、図12中の破線で示すとおり、IC1のGND端子→ボディダイオードD1→FET1のゲート端子のルートで、FET1のゲート−ソース間に印加される。すると、図12中の時刻t23のように、FET1のゲート−ソース間電圧Vgsが閾値電圧Vthを超え、FET1が再度オンしてドレイン電流Idが流れ出す。このとき、FET1のドレイン−ソース間電圧Vdsは、非常に高い状態にあるため、FET1が発熱して、場合によってはFET1が破壊に至るという課題がある。

【0014】

本発明は上記課題を鑑み、電流検出抵抗のインダクタンスによる逆起電力によるスイッチング素子の発熱を低減することを目的とする。

【課題を解決するための手段】

【0015】

上記課題を解決するための本発明のスイッチング電源は、トランスの一次側を駆動するスイッチング手段と、前記スイッチング手段に接続され、前記スイッチング手段に流れる電流を検出する電流検出手段と、前記電流検出手段に並列に接続され、前記電流検出抵抗のインダクタンスによって生じる起電力を低減する電力低減手段とを有することを特徴とする。

【発明の効果】

【0016】

本発明によれば。電流検出抵抗のインダクタンスの影響によるスイッチング手段の発熱を低減できる。

【図面の簡単な説明】

【0017】

【図1】実施例1の回路図

【図2】実施例1の回路の動作波形図

【図3】実施例2の回路図

【図4】実施例2の回路の動作波形図

【図5】実施例2の変形例を示す回路図

【図6】実施例3の回路図

【図7】実施例3の回路の動作波形図

【図8】従来のスイッチング電源回路図

【図9】従来のスイッチング電源回路の動作波形図

【図10】電流検出抵抗の構成を示す図

【図11】従来の回路図

【図12】従来の回路の動作波形図

【図13】スイッチング電源の適用例

【発明を実施するための形態】

【0018】

次に、上述した課題を解決するための本発明の具体的な構成について、以下に実施例に基づき説明する。なお、以下に示す実施例は一例であって、この発明の技術的範囲をそれらのみに限定する趣旨のものではない。

【0019】

(実施例1)

図1、図2を用いて本発明の実施例1のスイッチング電源について説明する。実施例1は、電流検出抵抗Risと並列に、ダイオードDclを接続し、電流検出抵抗のインダクタンスLisで発生する逆起電力(逆起電圧)をDclの順方向電圧Vfでクランプすることにより、FET1が再度オンすることを防ぐことを特徴とする。つまり、ダイオードDclが起電力低減回路として機能する。なお、この電流検出抵抗は、上記で説明したワイヤ状の金属素体をコイル状に巻いた巻線抵抗もしくは筒状の抵抗皮膜に螺旋状のスリットを設けた皮膜抵抗である(図10参照)。

【0020】

図1は、上記の図8における主要部を抜粋した図を用いて示している。基本構成は図8と同様であり、トランスの一次側(一次巻線)をスイッチング素子で所定の周波数で駆動することによりトランスの二次側(二次巻線)から電圧を出力するスイッチング電源を前提としている。なお、図8と共通する個所については同じ符号で示している。図1におけるダイオードDclが図8の構成に対して追加されている点が異なる。

【0021】

図2は、実施例1におけるスイッチング素子であるFET1のドレイン−ソース間電圧とドレイン電流とゲート−ソース間電圧の動作波形を示している。図2の時刻t31において、FET1のゲート−ソース間電圧Vgsが上昇し、ゲート閾値電圧Vthを超えると、ドレイン電流Idが流れ始め、次第に上昇していく。このドレイン電流Idは、電流検出RisのインダクタンスLisにも流れる。時刻t32において、ドレイン−ソース間電圧Vgsが下降してゲート閾値電圧Vthを下回ると、ドレイン電流Idは急速に低下していく。すると、インダクタンスLisに逆起電力Vsが発生する。この逆起電力Vsは、FET1のソース端子側がマイナス、PWMコントロールモジュールIC1のGND端子側がプラスの極性となる。

【0022】

ここで、実施例1では電流検出抵抗Risに対して並列にダイオードDclが接続されている。このときダイオードDclの順方向の電圧降下Vfは、FET1のゲート閾値電圧Vthよりも小さい。従って、発生した逆起電力Vsは、図2中の破線で示すとおり、ダイオードDclの順方向の電圧降下Vfでクランプされることになる。つまり、時刻t32〜t34の間、FET1のゲート−ソース間電圧Vgsも、ダイオードDclのVfでクランプされることとなり、FET1の閾値電圧Vthを超えることはない。

【0023】

以上、説明したように、実施例1では、電流検出抵抗(巻線抵抗)に並列にダイオードを接続し、そのダイオードの順方向の電圧降下をFET1のゲート閾値電圧Vthより小さい値にする。これにより、FET1が電流検出抵抗の逆起電力によって、再度オンしてFET1にドレイン電流Idが流れ出すことがなくなるため、FET1の発熱を低減することができる。FET1の発熱が低減されれば、発熱によって生じる破壊する等の故障の発生を抑制できる。

【0024】

(実施例2)

次に、図3と図4を用いて実施例2の構成と動作を説明する。実施例2の特徴は、電流検出抵抗Risと並列に、コンデンサCclを接続する点である。

これにより、電流検出抵抗のインダクタンスLisの逆起電力Vsを低減して、FET1の再オンを防ぐことが特徴である。つまり、コンデンサCclが起電力低減回路として機能する。この電流検出抵抗は、上記で説明したワイヤ状の金属素体をコイル状に巻いた巻線抵抗もしくは筒状の抵抗皮膜に螺旋状のスリットを設けた皮膜抵抗である(図10参照)。

【0025】

図3は、上記の図8の主要部を抜粋した図を用いて示している。基本構成は図8と同様であり、トランスの一次側(一次巻線)をスイッチング素子で所定の周波数で駆動することによりトランスの二次側(二次巻線)から電圧を出力するスイッチング電源を前提としている。図8と共通する個所については同じ符号で示している。図3におけるコンデンサCclが図8の構成に対して追加されている点が異なる。

【0026】

図4は、実施例2におけるスイッチング素子であるFET1のドレイン−ソース間電圧とドレイン電流とゲート−ソース間電圧の動作波形を示している。時刻t41において、FET1のゲート−ソース間電圧Vgsが上昇し、ゲート−ソース間電圧Vgsがゲート閾値電圧Vthを超えると、ドレイン電流Idが流れ始め、次第に上昇していく。このドレイン電流Idは、電流検出抵抗RisのインダクタンスLisにも流れる。時刻t42において、ゲート−ソース間電圧Vgsが下降してゲート閾値電圧Vthを下回ると、ドレイン電流Idは急速に低下していく。すると、電流検出抵抗RisのインダクタンスLisに逆起電力Vsが発生する。この逆起電力Vsは、FET1のソース端子側がマイナス、PWMコントロールモジュールIC1のGND端子側がプラスの極性となる。

【0027】

実施例2の構成では、電流検出抵抗Risには、コンデンサCclが接続されている。インダクタンスLisに発生した逆起電力Vsによって、コンデンサCclに蓄えられるエネルギと、それまでインダクタンスLisに流れていたドレイン電流Idpによって、インダクタンスLisに蓄えられるエネルギは等しくなる。つまり、概ね、以下の式(1)が成り立つことになる。

【0028】

【数1】

【0029】

上式(1)をVsについて解くと、Vsは、以下の式(2)で示される。

【0030】

【数2】

【0031】

時刻t42〜t43の期間、FET1のゲート−ソース間電圧Vgsは、このVsまで上昇することとなる。ここで、実施例2ではコンデンサCclの静電容量は、以下の式(3)を満たすように設定している。

【0032】

【数3】

【0033】

このように設定することで、Vsは、ゲート閾値電圧Vthを超えることはない。

【0034】

以上、説明したように、実施例2では、電流検出抵抗(巻線抵抗)に並列にダイオードを接続し、そのダイオードの順方向の電圧降下をFET1のゲート閾値電圧Vthより小さい値にする。これにより、FET1が電流検出抵抗の逆起電力によって、再度オンしてFET1にドレイン電流Idが流れ出すことがなくなるため、FET1の発熱を低減することができる。FET1の発熱が低減されれば、発熱によって生じる破壊する等の故障の発生を抑制できる。

【0035】

なお、実施例2の変形例として図5に示すように、コンデンサCclに、さらに抵抗Rclを直列に接続する構成でも同様の効果を得ることができる。この場合は、コンデンサCclと抵抗Rclで生成する回路の電圧値を閾値電圧Vthより低い値にすればよい。

【0036】

(実施例3)

次に、図6と図7を用いて実施例3の構成及び動作を説明する。実施例3は、DC/DCコンバータに適用した例である。実施例1と同様、電流検出抵抗Risと並列にダイオードDclを接続し、電流検出抵抗のインダクタンスLisで発生する逆起電力をDclの順方向の電圧降下Vfでクランプし、FET1が再度オンすることを防ぐものである。この電流検出抵抗は、上記で説明したワイヤ状の金属素体をコイル状に巻いた巻線抵抗もしくは筒状の抵抗皮膜に螺旋状のスリットを設けた皮膜抵抗である(図10参照)。

【0037】

まず、図6を用いてDC/DCコンバータの回路構成を説明する。なお、上記の図8のトランスの一次側の回路構成と同様の個所は省略または同符号を示している。図6において一次電解コンデンサC1に充電された直流電圧Vinは、電流検出抵抗Risを介して、FET1のソース端子に供給される。FET1のドレイン端子は、入力電圧Vinをスイッチングしてパルス電圧を生成する。

【0038】

FET1によって生成されたパルス電圧は、ダイオードD3とインダクタL1、と二次電解コンデンサC2によって平滑化され、出力電圧Voutとして負荷抵抗RLに供給される。FET1のゲート端子には、PWMコントロールモジュールIC1よりOUT信号が供給されている。PWMコントロールモジュールIC1はFET1のスイッチングをPWM信号によって制御して、出力電圧Voutを安定化させる。これが実施例のDC/DCコンバータの構成である。

【0039】

次に、以上の回路の動作波形を図7に示す。時刻t51で、FET1のゲート−ソース間電圧Vgsが低下し、ゲート閾値電圧Vthを下回ると、FET1にドレイン電流Idが流れる。このドレイン電流Idは、電流検出抵抗RisのインダクタンスLisにも流れる。時刻t52において、ゲート−ソース間電圧Vgsが上昇しゲート閾値電圧Vthを上回ると、ドレインIdは急速に低下していく。すると、電流検出抵抗RisのインダクタンスLisに逆起電力Vsが発生する。この逆起電力Vsは、入力電圧Vinの側がマイナス、FET1のソース端子側がプラスの極性となる。

【0040】

実施例3では、電流検出抵抗Risに並列にダイオードDclが接続されている。このときダイオードDclの順方向の電圧降下Vfは、FET1のゲート閾値電圧Vthよりも小さく設定されている。すると、逆起電力Vsは、図7中の破線で示すとおり、ダイオードDclの順方向の電圧降下Vfでクランプされる。よって、時刻t52からt53の間、FET1のゲート−ソース間電圧Vgsも、このダイオードの電圧降下Vfでクランプされることとなり、ゲート閾値電圧Vthを下回ることはない。

【0041】

以上、説明したように、実施例3では、電流検出抵抗(巻線抵抗)に並列にダイオードを接続し、そのダイオードの順方向の電圧降下をFET1のゲート閾値電圧Vthより小さい値にする。これにより、FET1が電流検出抵抗の逆起電力によって、再度オンしてFET1にドレイン電流Idが流れ出すことがなくなるため、FET1の発熱を低減することができる。FET1の発熱が低減されれば、発熱によって生じる破壊する等の故障の発生を抑制できる。

【0042】

<スイッチング電源の適用例>

上記の実施例で説明したスイッチング電源装置を、例えばレーザビームプリンタ、複写機、ファクシミリ等の画像形成装置における低電圧電源として適用することができる。以下にその適用例を説明する。スイッチング電源は、画像形成装置における制御部としてのコントローラへの電力供給、また、用紙を搬送する搬送ローラの駆動部としてのモータへの電力供給のための電源として適用される。

【0043】

図13(A)に画像形成装置の一例であるレーザビームプリンタの概略構成を示す。レーザビームプリンタ200は、画像形成部210として潜像が形成される像担持体としての感光ドラム211、感光ドラムに形成された潜像をトナーで現像する現像部212を備えている。そして感光ドラム211に現像されたトナー像をカセット216から供給された記録媒体としてのシート(不図示)に転写して、シートに転写したトナー像を定着器214で定着してトレイ215に排出する。また、図13(B)画像形成装置の制御部としてのコントローラと駆動部としてのモータへの電源からの電力供給ラインを示す。前述の電流共振電源は、このような画像形成動作を制御するCPU310有するコントローラへ300の電力供給、また、画像形成のための駆動部としてのモータ312及びモータ313に電力を供給する低圧電源として適用できる。供給する電力としては、コントローラ300へは3.3V、モータへは24Vを供給する。例えばモータ312はシートを搬送する搬送ローラを駆動するモータ、モータ313は定着器214を駆動するモータである。このような画像形成装置の低電圧電源として、上記のスイッチング電源装置を適用した場合でも、上記実施例と同様、低電圧電源のスイッチング素子の温度上昇を低減し、安定した電圧を供給することができ、画像形成装置を安定して動作することができる。なお、上記実施例で説明したスイッチング電源は、ここで示した画像形成装置に限らず他の電子機器の低電圧電源としても適用可能である。

【符号の説明】

【0044】

C1 一次電解コンデンサ

C2 二次次電解コンデンサ

FET1、FET2、FET3 FIELD EFFECT TRANSISTOR(電解効果トランジスタ)

T1 トランス

D1、D2、D3、Dcl ダイオード

Ris 電流検出抵抗

RL 負荷抵抗

IC1 PWMコントロールモジュール

【特許請求の範囲】

【請求項1】

トランスの一次側を駆動するスイッチング手段と、

前記スイッチング手段に接続され、前記スイッチング手段に流れる電流を検出する電流検出手段と、

前記電流検出手段に並列に接続され、前記電流検出手段のインダクタンスによって生じる起電力を低減する電力低減手段と

を有することを特徴とするスイッチング電源。

【請求項2】

前記電力低減手段は、ダイオードであることを特徴とする請求項1に記載のスイッチング電源。

【請求項3】

前記ダイオードの順方向の電圧を前記スイッチング手段がオンするための閾値電圧より低い電圧に設定することを特徴とする請求項2に記載のスイッチング電源。

【請求項4】

前記電力低減手段は、コンデンサであることを特徴とする請求項1に記載のスイッチング電源。

【請求項5】

前記電力低減手段は、コンデンサと抵抗を直列に接続した回路であることを特徴とする請求項1に記載のスイッチング電源。

【請求項6】

前記電流検出手段とは、巻線抵抗もしくは皮膜抵抗であることを特徴とする請求項1乃至5のいずれかの項に記載のスイッチング電源。

【請求項7】

画像形成手段と、

前記画像形成手段の動作を制御する制御手段と、

前記制御手段に電力を供給するスイッチング電源と、を備え、

前記スイッチング電源は、

トランスの一次巻線を駆動するスイッチング手段と、

前記スイッチング手段に接続され、前記スイッチング手段に流れる電流を検出する電流検出手段と、

前記電流検出手段に並列に接続され、前記電流検出手段のインダクタンスによって生じる起電力を低減する電力低減手段と

を有することを特徴とする画像形成装置。

【請求項1】

トランスの一次側を駆動するスイッチング手段と、

前記スイッチング手段に接続され、前記スイッチング手段に流れる電流を検出する電流検出手段と、

前記電流検出手段に並列に接続され、前記電流検出手段のインダクタンスによって生じる起電力を低減する電力低減手段と

を有することを特徴とするスイッチング電源。

【請求項2】

前記電力低減手段は、ダイオードであることを特徴とする請求項1に記載のスイッチング電源。

【請求項3】

前記ダイオードの順方向の電圧を前記スイッチング手段がオンするための閾値電圧より低い電圧に設定することを特徴とする請求項2に記載のスイッチング電源。

【請求項4】

前記電力低減手段は、コンデンサであることを特徴とする請求項1に記載のスイッチング電源。

【請求項5】

前記電力低減手段は、コンデンサと抵抗を直列に接続した回路であることを特徴とする請求項1に記載のスイッチング電源。

【請求項6】

前記電流検出手段とは、巻線抵抗もしくは皮膜抵抗であることを特徴とする請求項1乃至5のいずれかの項に記載のスイッチング電源。

【請求項7】

画像形成手段と、

前記画像形成手段の動作を制御する制御手段と、

前記制御手段に電力を供給するスイッチング電源と、を備え、

前記スイッチング電源は、

トランスの一次巻線を駆動するスイッチング手段と、

前記スイッチング手段に接続され、前記スイッチング手段に流れる電流を検出する電流検出手段と、

前記電流検出手段に並列に接続され、前記電流検出手段のインダクタンスによって生じる起電力を低減する電力低減手段と

を有することを特徴とする画像形成装置。

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【公開番号】特開2012−161191(P2012−161191A)

【公開日】平成24年8月23日(2012.8.23)

【国際特許分類】

【出願番号】特願2011−20140(P2011−20140)

【出願日】平成23年2月1日(2011.2.1)

【出願人】(000001007)キヤノン株式会社 (59,756)

【Fターム(参考)】

【公開日】平成24年8月23日(2012.8.23)

【国際特許分類】

【出願日】平成23年2月1日(2011.2.1)

【出願人】(000001007)キヤノン株式会社 (59,756)

【Fターム(参考)】

[ Back to top ]