スイッチング電源用の信号伝達トランス及びスイッチング電源装置

【課題】インダクタンス及び結合度の調整が容易なスイッチング電源装置用の信号伝達トランス、及びそれを用いた安全性の高いスイッチング電源装置を提供する。

【解決手段】信号伝達トランス22は、回路素子を実装してスイッチング電源回路が構成される多層基板50内の導体層52に形成された同心状のコイルパターン52(3)〜52(6)を備える。コイルパターン52(3)〜52(6)を挟む外側の導体層52に設けられ、少なくともコイルパターン52(3)〜52(6)の最内周の1ターン及びその内側領域を閉鎖するよう形成された一対の閉鎖パターン52(2),52(7)を備える。コイルパターン52(3)〜52(6)の何れかに電流が流れると、最内周の1ターンの内側領域に発生する磁束の一部が、閉鎖パターンに吸収される。閉鎖パターン52(2),52(7)は、安定電位に接続されている。

【解決手段】信号伝達トランス22は、回路素子を実装してスイッチング電源回路が構成される多層基板50内の導体層52に形成された同心状のコイルパターン52(3)〜52(6)を備える。コイルパターン52(3)〜52(6)を挟む外側の導体層52に設けられ、少なくともコイルパターン52(3)〜52(6)の最内周の1ターン及びその内側領域を閉鎖するよう形成された一対の閉鎖パターン52(2),52(7)を備える。コイルパターン52(3)〜52(6)の何れかに電流が流れると、最内周の1ターンの内側領域に発生する磁束の一部が、閉鎖パターンに吸収される。閉鎖パターン52(2),52(7)は、安定電位に接続されている。

【発明の詳細な説明】

【技術分野】

【0001】

この発明は、回路素子を実装してスイッチング電源回路が構成される多層基板内に形成されたコイルパターンを使用したスイッチング電源用の信号伝達トランス、及びスイッチング電源装置に関する。

【背景技術】

【0002】

スイッチング電源装置では、電力伝送用の主トランスの他に、スイッチング用のトランジスタ素子の駆動パルスや各種の交流信号を伝達する信号伝達トランスが用いられている。近年、電源回路の高密度実装の要請により、絶縁用のボビンを省略することによって小型化を図ったトランスが用いられるようになった。

【0003】

従来、この種のトランスとして、例えば特許文献1に開示されているように、多層基板内に外部から絶縁された複数のコイルパターンを同心状に積層形成し、コイルパターンの最内周の内側を貫通する挿入穴に磁心を挿入して成るプリントコイル形トランスがある。このプリントコイル形トランスは、発生電圧の低い補助コイルが2分割され、補助コイル以外のコイルパターンを挟み込むように外側の層に配置され、その一端が一次側に接地されており、この構造により、補助コイルが静電ノイズを低減するシールド層としての役割も果たす。

【0004】

また、特許文献2に開示されているスイッチング電源装置は、表面に回路素子が実装される多層基板内に外部から絶縁されたコイルパターンが積層して形成されたシートコイルトランスが設けられ、各層の間を絶縁する絶縁シートとして、コイルのインダクタンスを高くするための磁性粉が混合された絶縁シートが用いられている。このシートコイルトランスは、磁性コアの取り付けを省略することができるので、スイッチング電源装置の組み立てが容易で、他の回路素子の実装スペースも確保しやすい。

【0005】

その他、特許文献3に開示されているように、信号伝達トランスを使用した絶縁型DC−DCコンバータであって、入力及び出力巻線を有するメイントランス、入力巻線に接続された主スイッチ素子、主スイッチ素子を駆動するPWM制御回路、出力巻線に接続されたトランス巻線駆動方式の同期整流回路、及び同期整流回路が出力する整流電圧を平滑する平滑回路を備えたシングルエンディッドフォワード方式の絶縁型DC−DCコンバータがある。この絶縁型DC−DCコンバータは、信号伝達トランス(ドライブトランス)の一次巻線が、PWM制御回路のパルス出力端子と主スイッチ素子の駆動端子との接続点に直列に挿入され、同じく二次巻線が、転流側の同期整流素子の駆動端子を短絡可能な駆動スイッチ素子の駆動端子に接続されている。この構成により、PWM制御回路から主スイッチ素子をターンオンさせる駆動パルスが出力されると、主スイッチ素子がターンオンする前に、信号伝達トランスを通じてタイミング信号が駆動スイッチ素子に伝達され、駆動スイッチ素子がターンオンすることによって転流側の同期整流素子がターンオフする。この動作により、主スイッチ素子、整流側及び転流側の同期整流素子が同時にオンして短絡電流が流れる不具合を回避することができる。

【先行技術文献】

【特許文献】

【0006】

【特許文献1】特開平7−142269号公報

【特許文献2】特開平9−182432号公報

【特許文献3】特開2000−262051号公報

【発明の概要】

【発明が解決しようとする課題】

【0007】

しかし、特許文献1の磁気デバイスは、多層基板に磁性コアを組み付ける作業が煩雑で手間がかかる。特許文献2のシートコイルトランスは、磁性粉が混合された絶縁シートを用いた特殊な多層基板を使用しなければならない。従って、いずれの場合もコストが高くなるという問題があった。

【0008】

また、特許文献1,2の構造は、コイルのインダクタンスや各コイル間の結合度を高くするのに適した構造である。しかし、スイッチング電源装置に使用される信号伝達トランスは、回路動作上の役割や伝達する信号の種類によっては、高いインダクタンスや高い結合度が必要なく、かえって低い方がよい場合も少なくない。従って、特許文献1,2の磁気デバイス及びシートコイルトランスの構造は、インダクタンスや結合度の調整可能な範囲が狭く、信号伝達トランスとして使いにくいものである。

【0009】

特許文献3のスイッチング電源装置に使用される信号伝達トランスの構造は、磁性コアを備え、インダクタンスを低くするために巻数を少なくすることが望ましい旨が記載されている。従って、この信号伝達トランスも、インダクタンスや結合度の調整可能な範囲が狭く、最適化のための調整が容易ではない。

【0010】

この発明は、上記背景技術に鑑みて成されたものであり、インダクタンス及び結合度の調整が容易で安価なスイッチング電源装置用の信号伝達トランス、及び当該信号伝達トランスを使用した安全性の高いスイッチング電源装置を提供することを目的とする。

【課題を解決するための手段】

【0011】

この発明は、回路素子を実装してスイッチング電源回路が構成される多層基板内の導体層に形成された同心状の複数のコイルパターンと、前記複数のコイルパターンを挟む外側の導体層により形成され、少なくとも前記コイルパターンの最内周の1ターン及びその内側領域を閉鎖するよう形成された一対の閉鎖パターンとを備え、前記コイルパターンに電流が流れたとき、前記最内周の1ターンの内側領域に発生する磁束の一部が、前記閉鎖パターンに吸収されるスイッチング電源装置用の信号伝達トランスである。

【0012】

前記閉鎖パターンは、複数の小パターンの集合体であってもよい。また、前記閉鎖パターンが安定電位に接続されていることが好ましい。また、前記閉鎖パターンが、回路素子が実装される最外層を除く内側の層に形成されていてもよい。

【0013】

またこの発明は、上記の信号伝達トランスを備え、入力電源に直列接続され、入力電圧を所定のスイッチング周期で断続する主スイッチング素子と、パルス出力端子が前記主スイッチング素子の駆動端子に接続され、前記パルス出力端子ら出力する矩形波状の駆動パルスによって前記主スイッチング素子のオン・オフを制御する主スイッチング素子制御回路とを備え、前記信号伝達トランスの前記一次巻線が、前記主スイッチング素子制御回路の前記パルス出力端子と前記主スイッチング素子の前記駆動端子との接続点に直列に挿入され、前記信号伝達トランスは、前記一次巻線側に前記駆動パルスが入力されることによって前記二次巻線にタイミング信号パルスを発生し、前記主スイッチング素子制御回路とグランド電位の異なる制御回路に伝達し、前記制御回路は、前記タイミング信号パルスを利用した同期制御を行うスイッチング電源装置である。

【0014】

さらに、この発明は、入力電源に直列接続され、入力電圧を所定のスイッチング周期で断続する主スイッチング素子と、パルス出力端子が前記主スイッチング素子の駆動端子に接続され、前記パルス出力端子から出力する矩形波状の駆動パルスによって前記主スイッチング素子のオン・オフを制御する主スイッチング素子制御回路と、前記主スイッチング素子と直列に接続され前記主スイッチング素子の断続によって発生する断続電圧が両端に印加される入力巻線と、前記断続電圧を変圧した交流電圧が発生する出力巻線とを有する主トランスと、前記出力巻線に接続され、前記出力巻線に発生する電圧を整流する一又は二以上の同期整流FETを有し、各ゲート端子が前記トランスの前記出力巻線又はその他の巻線を用いたトランス巻線駆動方式により駆動される同期整流回路と、前記同期整流回路の出力に接続され、整流された電圧を平滑して直流の出力電圧を出力する平滑回路と、前記同期整流FETごとに設けられ、当該ゲート・ソース端子間を短絡・開放可能な補助FETと、対応する前記補助FETのゲート閾値電圧よりも高い電源電圧を出力する一又は二以上の直流電源と、前記直流電源と対応する前記補助FETのゲート端子との間に接続され、当該補助FETのゲート・ソース端子間を当該電源電圧にプルアップするプルアップ抵抗と、前記プルアップ抵抗ごとに設けられ、当該プルアップ抵抗が接続されている前記補助FETのゲート・ソース端子間を短絡・開放可能なタイミングトランジスタ素子と、前記信号トランスとを備え、前記信号伝達トランスは一又は二以上の前記二次巻線を有し、前記一次巻線が、前記主スイッチング素子制御回路の前記パルス出力端子と前記主スイッチング素子の前記駆動端子との接続点に直列に挿入され、前記タイミングトランジスタ素子の駆動端子に、対応する前記二次巻線が接続され、前記タイミングトランジスタ素子は、前記信号伝達トランスの前記一次巻線側に前記駆動パルスが入力されることにより、当該駆動端子に接続された前記二次巻線に発生するタイミング信号パルスを受けてオン・オフし、前記タイミングトランジスタ素子のオフの期間、前記補助FETのゲート・ソース間の入力容量が前記プルアップ抵抗を介して流れ込む前記直流電源からの電流によって充電され、前記プルアップ抵抗は、前記タイミングトランジスタ素子のオフが前記スイッチング周期よりも長い所定の時間を超えて継続したとき、前記補助FETのゲート・ソース端子間の電圧が前記ゲート閾値電圧を超えるように、前記充電電流を制限するスイッチング電源装置である。

【発明の効果】

【0015】

この発明のスイッチング電源装置用の信号伝達トランスは、多層基板内に形成され、磁性コアを取り付けることなく安価に構成することができる。また、コイルパターンのレイアウト(巻数、渦巻きの形状など)を変更する以外にも、各コイルパターン間の絶縁部材の厚み、及びコイルパターンと閉鎖パターンとの間の絶縁部材の厚み等を適宜調節することにより、インダクタンス及び各コイルパターン同士の結合度を広範囲に変更、調整することができる。しかも、多層基板は、金型や数値制御された各種装置を用いて高い寸法精度で製作されるので、最適化されたインダクタンス及び結合度をばらつきなく実現することができる。閉鎖パターンは、コイルパターンの最内周の内側領域を通る磁束が多層基板の外部に漏洩するのを防止すると共に、外来の磁束が信号伝達トランスに鎖交して干渉するのを防止する磁気シールドとしても働く。さらに、閉鎖パターンを安定電位に接地することによって、静電シールドとしての効果も得られる。

【0016】

また、この発明のスイッチング電源装置は、信号伝達トランスの一次巻線が、主スイッチング素子制御回路のパルス出力端子と主スイッチング素子の駆動端子との接続点に直列に挿入され、二次巻線からごく短いパルス幅のタイミング信号を出力する動作を行うので、上記の構造を備えた信号伝達トランスを使用することによって、主スイッチング素子と同期整流素子とのオン・オフのタイミング制御を容易に行うことができる。しかも、インダクタンス及び結合度のバランス設計により、主スイッチング素子の駆動端子電圧の立ち上がり又は立ち下がりスピードを急峻にすることができるので、主スイッチング素子のクロス損失を最小限に抑えることができる。

【図面の簡単な説明】

【0017】

【図1】この発明のスイッチング電源装置の第一実施形態を示すブロック図である。

【図2】第一実施形態のスイッチング電源装置の具体的な構成を示す回路図である。

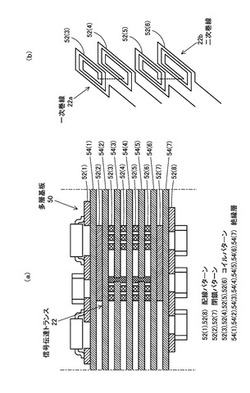

【図3】この発明の第一実施形態の信号伝達トランスの構造を示す断面図(a)、コイルパターンのレイアウトを示す模式図(b)である。

【図4】信号伝達トランスの第二実施形態の構造を示す断面図(a)、コイルパターンのレイアウトを示す模式図(b)である。

【図5】信号伝達トランスの第三実施形態の構造を示す断面図(a)、コイルパターンのレイアウトを示す模式図(b)である。

【図6】第一実施形態のスイッチング電源装置の変形例を説明する回路図(a),(b)である。

【発明を実施するための形態】

【0018】

以下、この発明のスイッチング電源装置用の信号伝達トランス及びスイッチング電源装置の第一実施形態態について、図1〜図3に基づいて説明する。第一実施形態のスイッチング電源装置10は、図1のブロック図に示すように、主スイッチング素子12、主スイッチング素子制御回路14、主トランス16、同期整流回路18、平滑回路20及び信号伝達トランス22を備えている。ブロックで記載した同期整流回路18及び平滑回路20を具体的な回路で表わすと、図2のようになる。以下、図2の回路図を用いてスイッチング電源装置10の構成と動作を説明する。

【0019】

主スイッチング素子12は、NチャネルのMOS形FETであり、入力電源24に直列接続され、入力電圧を所定のスイッチング周期Tで断続する。主スイッチング素子制御回路14は、パルス出力端子14aが主スイッチング素子12のゲート端子12gに接続され、パルス出力端子14aから矩形波状の駆動パルスV14aを出力し、主スイッチング素子12のオン・オフを制御する。

【0020】

主トランス16は、入力巻線16a、出力巻線16b及び補助巻線16cを備え、互いに密に結合している。入力巻線16aは、主スイッチング素子12と直列に接続され、両端に主スイッチング素子12のオン・オフによって発生する断続電圧が印加される。そして、出力巻線16bと補助巻線16cに、入力巻線16aに印加された断続電圧と略相似形の電圧が発生する。ここで、図2のトランス16に付したドットは、各巻線の極性を示している。

【0021】

同期整流回路18は、2つの同期整流FETである整流側FET26及び転流側FET28を備えている。整流側FET26はNチャネルのMOS型FETであり、ドレイン端子が出力巻線16bのドットのない一端に接続され、ゲート端子が駆動コンデンサ30を介して出力巻線16bのドットのある一端に接続されている。整流側FET26のゲート・ソース端子間に接続されている抵抗32は、図示しないゲート入力容量の放電抵抗である。

【0022】

転流側FET28もNチャネルのMOS型FETであり、ドレイン端子が出力巻線16bのドットのある一端に接続され、ソース端子が整流側FET26のソース端子に接続されている。転流側FET28のゲート・ソース端子間に接続されている抵抗34は、図示しないゲート入力容量の放電抵抗である。転流側FET28のゲート端子は駆動コンデンサ35aを介して駆動ツェナーダイオード35bのカソード端子に接続され、駆動ツェナーダイオード35bのアノード端子が補助巻線16cのドットのない一端に接続され、さらに、補助巻線16cのドットのある一端が転流側FET28のソース端子に接続されている。

【0023】

同期整流回路18は、以上の構成により、整流側及び転流側FET26,28のゲート端子が、出力巻線16b及び補助巻線16cを用いたトランス巻線駆動方式によって駆動され、整流側FET26が主スイッチング素子12と同位相で、転流側FET28が主スイッチング素子12と相補的にそれぞれがオン・オフし、出力巻線16bの発生電圧を適正に整流することができる。

【0024】

さらに、この同期整流回路18には、後述する異常発振の不具合を回避するための異常発振防止回路36が付加されている。異常発振防止回路36は、整流側及び転流側FET26,28のゲート・ソース端子間を短絡・開放可能に自己のドレイン及びソース端子がそれぞれ接続された第一及び第二補助FET38,40を備えている。第一及び第二補助FET38,40のゲート端子は互いに接続され、プルアップ抵抗42を介して直流電源44にプルアップされている。直流電源44は、例えば、出力巻線16b又は補助巻線16cに発生する電圧を利用して直流の電源電圧を生成する簡易式の電圧源であり、第一及び第二補助FET38,40のゲート閾値電圧よりも高い電源電圧を出力する。さらに、第一及び第二補助FET38,40のゲート・ソース端子間を短絡・開放可能に自己のドレイン及びソース端子が接続されたタイミングFET46が設けられている。タイミングFET46はタイミングトランジスタ素子であり、ここではNチャネルのMOS型FETが使用されているが、バイポーラトランジスタに置き換えることも可能である。

【0025】

第一及び第二補助FET38,40のゲート端子電圧V38gは、タイミングFET46がターンオフした時から上昇し始める。プルアップ抵抗42は、直流電源44が第一及び第二補助FET38,40の図示しないゲート入力容量を充電する電流を制限する働きをし、ゲート入力容量との時定数により、電圧V38gの上昇速度を決定する。プルアップ抵抗42の抵抗値は、スイッチング周期Tよりも長い時間(例えば、スイッチング周期Tの2〜5倍程度の時間)が経過した後で、電圧V38gがゲート閾値電圧に達するように、比較的大きな値に設定されている。異常発振防止回路36の詳細な動作は、後で説明する。

【0026】

平滑回路20は、平滑インダクタ20a及び平滑コンデンサ20bで成るローパスフィルタであり、同期整流回路18が出力する整流電圧を平滑して直流の出力電圧を生成し、後段の負荷48に電力を供給する。

【0027】

信号伝達トランス22は、一次巻線22aと二次巻線22bを備えている。図2のドットは各巻線の極性を示しており、一次巻線22aが、主スイッチング素子制御回路14のパルス出力端子14aと主スイッチング素子12のゲート端子12gとの接続点に直列に挿入され、ドットのある一端がパルス出力端子14aに接続されている。二次巻線22bは、ドットのある一端が異常発振防止回路36のタイミングFET46のゲート端子に接続され、ドットのない一端がソース端子に接続されている。

【0028】

信号伝達トランス22は、図3に示すように、主スイッチング素子12やその他の回路素子が実装された多層基板50内に設けられ、異なる導体層に一次巻線22aと二次巻線22bが形成され、それらが積層されて互いに磁気結合した空芯トランスの構造になっている。ここでは、一次及び二次巻線22a,22bの巻数が同じであり、インダクタンスが50〜100nH、結合度が約0.2〜0.3程度に設定されている。信号伝達トランス22の詳細な構造については、後で詳しく説明する。

【0029】

次に、スイッチング電源装置10の動作について説明する。スイッチング電源装置10は、異常発振防止回路36及び信号伝達トランス22が設けられていないとすれば、トランス巻線駆動方式の同期整流回路を備えたシングルエンディッドフォワード型の一般的なスイッチング電源装置である。そして、スイッチング電源装置10に入力電源24が投入され、出力電圧及び出力電流を負荷48に安定供給する動作(以下、定常動作と称する。)を行うときは、異常発振防止回路36は動作しない。従って、定常動作中の電力変換動作は従来と同様であり、ここでは説明を省略する。

【0030】

異常発振防止回路36及び信号伝達トランス22は、入力電源24が停止したとき等に生じる異常発振の不具合を回避するための回路であり、定常動作中は異常発振の不具合が発生し得ないので、異常発振防止回路36の機能を停止させている。具体的には、以下の動作により、第一及び第二補助FET38,40がオフ状態に保持される。

【0031】

主スイッチング素子制御回路14が出力する駆動パルスV14aがローレベルからハイレベルに転じた時、主スイッチング素子12の図示しないゲート入力容量を充電する電流が、一次巻線22aを通じて流れる。これにより一次巻線22a側に所定の信号が入力され、二次巻線22bから出力されるタイミング信号がタイミングFET46のゲート・ソース端子間に伝達される。二次巻線22bはドットのある端子が高電位となるので、ゲート端子電圧V46gが瞬時にゲート閾値電圧を超え、タイミングFET46がオンし、第一及び第二補助FETのゲート入力容量が急速放電され、ゲート端子電圧V38gがリセットされる。

【0032】

その後、主スイッチング素子12のゲート端子電圧V12gが駆動パルスV14aのハイレベル電圧に向かって上昇する。信号伝達トランス22は、一次巻線22aのインダクタンスが非常に小さく、二次巻線22bとの結合度もさほど高くないことから、主スイッチング素子12のゲート入力容量の充電電流がほとんど制限されず、ゲート端子電圧V12gは、駆動パルスV14aが上昇する傾きにほぼ近い急峻な傾きで上昇し、ゲート閾値電圧を超えて主スイッチング素子12がオンする。また、ゲート端子電圧V12gが短時間のうちに駆動パルス電圧V14aに達し、二次巻線22bから出力されるタイミング信号もなくなり、タイミングFET46がオフに転じる。すると、第一及び第二補助FET38,40のゲート入力容量が開放され、直流電源44からプルアップ抵抗42を通じて充電電流が流れ込み、ゲート端子電圧V38gが上昇し始める。ゲート端子電圧V38gの上昇速度は当該ゲート入力容量とプルアップ抵抗42の時定数によって制限され、非常に緩やかに上昇する。

【0033】

その後、主スイッチング素子駆動回路14の駆動パルスV14aがハイレベルからローレベルに転じた時、主スイッチング素子12のゲート入力容量を放電する電流が、一次巻線22aを通じて流れる。これにより、一次巻線22aの側に所定の信号が入力され、二次巻線22bから出力されるタイミング信号がタイミングFET46のゲート・ソース端子間に伝達される。二次巻線22bは、ドットのない端子が高電位となるので、ゲート端子電圧V46gが負方向に低下する。しかし、タイミングFET46は、当該タイミング信号を受ける前から既にオフしており、ゲート端子電圧V38gの上昇に対して影響しない。

【0034】

その後、先に駆動パルスV14aがハイレベルに転じてからスイッチング周期Tが経過した時点で、駆動パルスV14aが再度ハイレベルに転じ、ゲート端子電圧V38gがリセットされる。

【0035】

ゲート端子電圧V38gの上昇速度はプルアップ抵抗42等の時定数によって規定され、ゲート端子電圧V38gがリセットされた後、スイッチング周期Tよりも長い時間(例えば、スイッチング周期Tの2〜5倍程度の時間)が経過しないとゲート閾値電圧を超えない。従って、上記の動作を繰り返す定常動作中は、第一及び第二補助FET38,40がオフ状態に保持され、異常発振防止回路36は動作しない。

【0036】

次に、スイッチング電源装置10が定常動作している最中に入力電源24が遮断される等し、主スイッチング素子駆動回路14の駆動パルスV14aが停止したときの動作(以下、電源停止動作と称する)について説明する。まず、図2に示すスイッチング電源装置10の構成から異常発振防止回路36が設けられていない場合に生じる異常発振の不具合について説明する。

【0037】

スイッチング電源装置10の定常動作中に、主スイッチング素子12がオン、整流側FET26がオン、転流側FET28がオフの状態で駆動パルスV14aが停止した場合を考える。駆動パルスV14aが停止(ローレベルに転じてローレベルを保持)すると、主スイッチング素子12がオンからオフに転じ、一次巻線16aが開放される。すると、主スイッチング素子12のオンの間に主トランス16に蓄積された励磁エネルギーの放出が始まり、出力巻線16bと補助巻線16cの両端に、ドットのない一端が高電位となる方向にフライバック電圧が発生する。このフライバック電圧により、整流側FET26がオフに転じ、転流側FET28がオンに転じる。転流側FET28がオンすると、平滑コンデンサ20bの蓄積電荷を放出する電流が、平滑コンデンサ20b、転流側FET28、平滑インダクタ20aの経路に流れ、平滑インダクタ20aに励磁エネルギーが蓄積される。

【0038】

主トランス16の励磁エネルギーの放出が終了すると、出力巻線16bと補助巻線16cの電圧は低下するが、整流側FET26のオフと転流側FET28のオンが継続する。その後、転流側FET28のゲート入力容量の蓄積電荷が抵抗34によって徐々に放電され、ゲート端子電圧V28gがゲート閾値電圧に低下したところで、転流側FET28がオフし始める。すると、転流側FET28のオンの間に平滑インダクタ20aに蓄積された励磁エネルギーの放出が始まり、平滑インダクタ20aの両端に、平滑コンデンサ20b側の一端が高電位となる方向にフライバック電圧が発生する。このフライバック電圧により、出力巻線16bと補助巻線16cの両端に、ドットのある一端が高電位となる方向に電圧が発生し、整流側FET26がオンに転じると共に転流側FET28も完全にオフする。整流側FET26がオンすると、平滑コンデンサ20aの蓄積電荷と平滑インダクタの励磁エネルギーを放出する電流が、平滑コンデンサ20b、出力巻線16b、整流側FET26、平滑インダクタ20aの経路に流れ、主トランス16に励磁エネルギーが蓄積される。この電流は、出力巻線16bと密に結合している入力巻線16aから、入力電源24(又は、図示しない入力コンデンサ)、主スイッチング素子12の内部に寄生する図示しないドレイン・ソース間ダイオード、という経路にも流れる。

【0039】

その後、整流側FET26のゲート入力容量の蓄積電荷が抵抗32によって徐々に放電され、ゲート端子電圧V26gがゲート閾値電圧まで低下したところで整流側FET26がオフし始める。すると、整流側FET26のオンの間に主トランス16に蓄積された励磁エネルギーの放出が始まり、出力巻線16bと補助巻線16cの両端に、ドットのない一端が高電位となる方向にフライバック電圧が発生し、転流側FET28がオンに転じると共に整流側FET26も完全にオフする。以下、整流側FET26と転流側FET28が相補的にオン・オフする自励式の異常発振が発生する。

【0040】

異常発振の周期は、スイッチング周期Tよりも長くなるのが一般的である(例えば、スイッチング周期Tの5倍〜10倍程度)。また、主トランス16と平滑インダクタ20aに流れる電流の大きさを制限する回路素子もない。従って、異常発振が発生すると、この電流により主トランス16や平滑インダクタ20aが磁気飽和し、それによってさらに大きな電流が発生し、整流側及び転流側FET26,28に過大な電気ストレスが加わって破損するおそれがある。

【0041】

スイッチング電源回路10は、異常発振防止回路36を設けることによって異常発振の不具合が回避されている。スイッチング電源装置10の定常動作中、駆動パルスV14aが停止すると、信号伝達トランス22の二次巻線22bからタイミング信号が出力されないので、タイミングFET46がオフを継続し、第一及び第二補助FET38,40のゲート電圧V38gがリセットされることなく、直流電源44からの充電によって上昇し続ける。そして、スイッチング周期Tの2〜5倍程度の時間(異常発振の周期よりも短い時間)が経過したところでゲート電圧V38gがゲート閾値電圧を超え、第一及び第二補助FET38,40がオンに転じてそのまま保持される。そして、整流側及び転流側FET26,28は、ゲート・ソース端子間が共に短絡されるので、オフに固定されることになる。従って、整流側及び転流側FET26,28は、主トランス16や平滑インダクタ20aの動作によらず、確実にオフに固定されるので、上記のような自励式の異常発振が発生することがない。

【0042】

なお、異常発振防止回路36は、駆動パルスV14aがハイレベルに転じる時のタイミング信号を利用してゲート電圧V38gのリセットを行っているが、駆動パルスV14aがローレベルに転じる時のタイミング信号を利用する構成に変更しても、同様の作用効果を得ることができる。後者の構成を選択するときは、二次巻線22bがタイミングFET46のゲート・ソース端子間に接続される極性を反対にすればよい。従って、各回路素子の部品配置や回路パターンのレイアウトを検討する際に、前者と後者のうちの都合のよい方を選択することができる。

【0043】

スイッチング電源装置10が上記の理想的な動作を行うためには、信号伝達トランス22の特性が重要である。定常動作中は、主スイッチング素子12のゲート端子電圧V12gを急峻に上昇させ、ターンオン時のクロス損失を小さく抑えなくてはならないので、信号伝達トランス22は、インダクタンスを低くすることが好ましい。その一方で、定常動作中、スイッチング周期TごとにタイミングFET46をオンさせて異常発振防止回路36の機能を停止させるため、タイミングFET46がオンするのに十分なタイミング信号を二次巻線22bに発生させなくてはならないので、一定以上の結合が必要である。

【0044】

この信号伝達トランス22は、一次及び二次巻線22a,22bを同じ巻数とし、各インダクタンスを50〜100nH、結合度を約0.2〜0.3に設定することによって、上記2つの条件を両立させている。ただし、これらの数値は一例にすぎず、駆動パルスV14aのハイレベルの電圧値、主スイッチング素子12のゲート入力容量及びゲート閾値電圧、タイミングFET46のゲート入力容量及びゲート閾値電圧、スイッチング周期Tなどが異なると、信号伝達トランス22のインダクタンスと結合度の最適値も異なってくる。従って、信号伝達トランス22は、インダクタンスと結合度の調整、変更が容易な構造であることが望ましい。

【0045】

信号伝達トランス22の構造は、図3に示すように、表面にスイッチング素子12等の回路素子が実装される多層基板50の中に形成されている。多層基板50は、銅などで成る導体層52と、樹脂やガラス繊維等の絶縁部材で成る絶縁層54とを備え、8つの導体層52の間に7つの絶縁層54(図3の上側から順番に54(1)〜54(7))を交互に挟んで積層された一般的なプリント基板である。

【0046】

図3の上側から数えて3番目と4番目の導体層52には、コイルパターン52(3),52(4)が形成され、5番目と6番目の導体層52に、コイルパターン52(5),52(6)が形成され、2番目と7番目の導体層52には、閉鎖パターン52(2),52(7)が形成され、1番目と8番目の導体層52に、回路素子の実装及び配線を行う配線パターン52(1),52(8)が形成されている。

【0047】

コイルパターン52(3),52(4)は、渦巻き状に形成された平面コイルであり、図3(b)に示すように、最内周の1ターンの端部同士が絶縁層54(3)に設けたスルーホールを通じて一体に接続され、一次巻線22aとなる。また、コイルパターン52(3),52(4)も、渦巻き状に形成された平面コイルであり、図3(b)に示すように、最内周の1ターンの端部同士が絶縁層54(5)に設けたスルーホールを通じて一体に接続され、二次巻線22bとなる。4つのコイルパターン52(3)〜52(6)は、最内周の1ターンの内側領域の形状が等しく、最外周の1ターンの外周縁の形状もほぼ等しく、互いに重なり合うように同心状に配置されている。

【0048】

閉鎖パターン52(2),52(7)は、少なくともコイルパターン52(3),52(6)の最内周の1ターン及びその内側領域を閉鎖する導体パターンであり、ここでは、最外周の外周縁の内側領域を覆う大きさに形成されている。従って、一次巻線22aであるコイルパターン52(3),52(4)に電流が流れ最内周の1ターンの内側領域を通る磁束が発生すると、その磁束の一部が閉鎖パターン52(2),52(7)を厚み方向に通過し、渦電流損失となって吸収される。

【0049】

配線パターン52(1),52(8)は、閉鎖パターン52(2),52(7)と重なる領域にも自由に形成することができる。また、閉鎖パターン52(2)は、絶縁層54(1)に設けた図示しないスルーホールを通して配線パターン52(1)の安定電位の部分に接続されている。同様に、閉鎖パターン52(7)も、絶縁層54(7)に設けた図示しないスルーホールを通して配線パターン52(8)の安定電位の部分に接続されている。安定電位とは交流的に安定な電位のことであり、例えば、図2における主スイッチング素子12のソース端子の電位や、主トランス16の入力巻線16aのドットのある一端の電位である。

【0050】

信号伝達トランス22のインダクタンスは、一次及び二次巻線22a,22bの巻数によって調整することができ、巻数を少なくすればインダクタンスが小さくなる。しかし、あまり少なくすると、2つの巻線間の結合度が確保できない。この信号伝達トランス22は、巻数以外のパラメータを変更することによって、インダクタンスと結合度を容易に調整することができる。

【0051】

閉鎖パターン52(2),52(7)は、コイルパターン52(3),52(4)に電流が流れたとき、その内側領域に発生する磁束の一部を吸収すると共に、コイルパターン52(5),52(6)に鎖交する磁束の量を減らす働きをする。すなわち、閉鎖パターン52(2),52(7)が存在すると、インダクタンスが低下すると共に、結合度も低下することになる。閉鎖パターン52(2),52(7)による磁束の吸収量は、閉鎖パターン52(2),52(7)の厚みを変更することによって調整できる。また、閉鎖パターン52(2)とコイルパターン52(3)との間の絶縁層54(2)の厚みを変更することによって、絶縁層54(2)の内部を面方向に通過する磁束の量、すなわち閉鎖パターン52(2),52(7)に吸収されない磁束の量を調整できる。閉鎖パターン52(7)とコイルパターン52(6)との間の絶縁層54(6)の厚みについても同様である。このように、上記の各パラメータを変化させることによって、インダクタンスと結合度を広範囲に調整、変更することができる。

【0052】

インダクタンスと結合度を調整する手段は他にもあり、例えば、絶縁層54(3),54(4),54(5),54(6)の厚みを変更したり、平面コイル内の1ターン毎の間隔を変更したり、各コイルパターンの最内周の内側領域の面積を増減したりすることによって、ある程度の調整が可能である。

【0053】

以上説明したように、第一実施形態のスイッチング電源装置10は、電源停止時に異常発振防止回路36が動作することによって、異常発振による不具合を確実に回避することができ、安全である。さらに、定常動作時、信号伝達トランス22は、一次巻線22aが主スイッチング素子制御回路14のパルス出力端子14aと主スイッチング素子12のゲート端子12gとの接続点に直列に挿入され、ごく短いパルス幅のタイミング信号を二次巻線22bに伝達する動作を行う。従って、信号伝達トランス22のインダクタンスと結合度を最適化することにより、主スイッチング素子12のゲート端子電圧V12gの立ち上がりを急峻にし、主スイッチング素子のクロス損失の最小限に抑えることができる。

【0054】

また、信号伝達トランス22は、多層基板50の内部に形成され、磁性コアが不要なので安価に構成することができ、信号伝達トランス22と重なる位置に他の回路素子を配置することにより、スイッチング電源装置の小型化にも寄与できる。さらに、コイルパターン52(3)〜52(6)の巻数などを変更する以外に、各コイルパターン間の絶縁層54(3)〜54(5)の厚み、及びコイルパターン52(3),52(6)と閉鎖パターン52(2),52(7)の間の絶縁層54(2),54(6)の厚み等のパラメータを調節することにより、インダクタンスと結合度を広範囲に変化させることができるので、最適化が容易である。しかも、多層基板50は、金型や数値制御された各種装置を用いて高い寸法精度で製作されるので、最適化されたインダクタンス及び結合度をばらつきなく実現することができる。従って、スイッチング電源装置10の信号伝達トランス22等の用途に非常に適している。

【0055】

閉鎖パターン52(2),52(7)は、コイルパターン52(3)〜52(6)の最内周の内側領域を通過する磁束が多層基板50の外部に漏洩するのを防止すると共に、外来の磁束が信号伝達トランス22に鎖交して干渉するのを防止する磁気シールドの働きをする。さらに、閉鎖パターンが安定電位に接地されているので静電シールドとしても働く。

【0056】

次に、この発明の信号伝達トランスの第二実施形態について、図4に基づいて説明する。この実施形態の信号伝達トランス58は、一次及び二次巻線58a,58bを備え、上記スイッチング電源装置10の信号伝達トランス22と同様に使用可能なトランスである。

【0057】

多層基板60は、銅などから成る導体層62と、樹脂やガラス繊維等の絶縁部材で成る絶縁層64とを備え、6つの導体層52の間に5つの絶縁層64(図4の上側から順番に64(1)〜64(5))を交互に挟んで積層された一般的なプリント基板である。

【0058】

図4の上側から数えて3番目の導体層62に一次巻線58aであるコイルパターン62(3−1)及び二次巻線58bであるコイルパターン62(3−2)が形成され、4番目の導体層62に、引出パターン62(4−1),62(4−2)が形成され、2番目と5番目の導体層62に閉鎖パターン62(2),62(5)が形成され、さらに、1番目と6番目の導体層62に回路素子の実装及び配線を行う配線パターン62(1),62(6)が形成されている。

【0059】

コイルパターン62(3−1),62(3−2)は、図4(b)に示すように、互いに平行に渦巻き状に形成された平面コイルであり、最内周の1ターンの端部が絶縁層64(3)に設けたスルーホールを通じて引出パターン62(4−1),62(4−2)に接続され、外側に引き出されている。

【0060】

閉鎖パターン62(2),62(5)は、少なくともコイルパターン62(3−1),62(3−2)の最内周の1ターン及びその内側領域を閉鎖する導体パターンであり、ここでは、最外周の外周縁の内側領域を覆う大きさに形成されている。従って、一次巻線58aであるコイルパターン62(3−1)に電流が流れて最内周の1ターンの内側領域を通る磁束が発生すると、その磁束の一部が閉鎖パターン62(2),62(5)を厚み方向に通過し、渦電流損失となって吸収される。

【0061】

このように、第二実施形態の信号伝達トランス58は、一次及び二次巻線58a,58bを2つの導体層62で構成したという点で、上記の信号伝達トランス22と異なり、その他の構成は同様である。この信号伝達トランス58は上記の信号伝達トランス22と同様の作用効果を得ることができ、特に、信号伝達トランス22が4つの導体層52で一次及び二次巻線22a,22bを構成しているのに比べると、層数の少ない安価な多層基板を使用できるという利点がある。

【0062】

この発明の第三実施形態の信号伝達トランス66は、図5に示すように、さらに層数の少ない多層基板に構成されている。信号伝達トランス66は、一次及び二次巻線66a,66bを備え、上記の信号伝達トランス22,58と同様に使用可能なトランスである。

【0063】

多層基板68は、銅などで成る導体層70と、樹脂やガラス繊維等の絶縁部材で成る絶縁層72とを備え、4つの導体層70の間に3つの絶縁層72(図5の上側から順番に72(1)〜72(3))を交互に挟んで積層された一般的なプリント基板である。

【0064】

図5の上側から数えて1番目の導体層70に回路素子の実装及び配線を行う配線パターン70(1)が形成され、3番目の導体層70に、一次巻線66aであるコイルパターン70(3−1)と二次巻線66bであるコイルパターン70(3−2)が形成され、4番目の導体層70に、引出パターン70(4−1),70(4−2)、閉鎖パターン70(4−3)、及び図示しない配線パターンが形成されている。

【0065】

コイルパターン70(3−1),70(3−2)は、図5(b)に示すように、互いに平行に渦巻き状に形成された平面コイルであり、最内周の1ターンの端部が絶縁層72(3)に設けたスルーホールを通じて引出パターン70(4−1),70(4−2)に接続され、外側に引き出されている。閉鎖パターン70(4−3)は、少なくともコイルパターン70(3−1),70(3−2)の最内周の1ターン及びその内側領域を閉鎖する一又は二以上に分離した導体パターンであり、引出パターン70(4−1),70(4−2)を避けて設けられている。

【0066】

第三実施形態の信号伝達トランス66は、一次及び二次巻線66a,66bを2つの導体層70で構成したという点で、上記の信号伝達トランス22と異なる。さらに、一方の閉鎖パターン70(4−3)、引出パターン70(4−1),70(4−2)、及び配線パターンを同じの導体層70に設けたという点で、上記の信号伝達トランス60と異なる。その他の構成は同様である。

【0067】

この信号伝達トランス66は、上記の信号伝達トランス22,58と同様の作用効果を得ることができ、特に、上記の信号伝達トランス22が4つの導体層52で一次及び二次巻線22a,22bを構成しているのに比べると、格段に層数の少ない安価な多層基板を使用できるという利点がある。

【0068】

なお、この発明のスイッチング電源装置は、上記実施形態に限定されるものではない。図2のスイッチング電源装置10は、トランス巻線駆動方式の同期整流回路を備えたシングルエンディッドフォワード型のスイッチング電源装置であるが、インバータ型式がシングルエンディッドフォワード型と異なるスイッチング電源装置にも適用することができる。シングルエンディッドフォワード型のスイッチング電源装置10の場合、同期整流素子が2つ(整流側及び転流側FET26,28)なので、異常発振防止回路36は、同期整流素子ごとに1つずつ(補助FET38,40)設けられている。例えば、インバータ型式がフライバック型の場合、同期整流素子が1つなので補助FETは1つで足りる。また、インバータ型式がブリッジ型で主トランスの出力巻線電圧を全波整流する場合、同期整流素子が4つなので、補助FETを4つ設ければよい。何れの場合も、スイッチング電源10と同様に、電源停止時の異常動作の不具合を容易かつ確実に回避することができる。

【0069】

また、図2のスイッチング電源装置10の場合、信号伝達トランス22の二次巻線22bから出力されるタイミング信号が、異常発振防止回路36をリセットする同期制御に使用されているが、その他の様々な同期制御に使用することができる。例えば、背景技術の特許文献3に記載された絶縁型DC−DCコンバータのように、トランス巻線駆動方式で駆動される転流側FETのターンオフのタイミングを制御し、転流側FETと主スイッチング素子とが同時にオンするのを防止する同期制御に、このタイミング信号を使用することができる。また、主トランスの一次巻線と並列にアクティブクランプ用コンデンサを断続する直列スイッチング素子を備えたスイッチング電源装置において、直列スイッチング素子のターンオフ又はターンオフのタイミングを制御し、直列スイッチング素子と主スイッチング素子が同時にオンするのを防止する同期制御に、このタイミング信号を使用することも可能である。ここで例示した何れの同期制御においても、信号伝達トランスのインダクタンスと結合度を最適化する必要があり、この発明の信号伝達トランスを使用すれば最適化が容易であり、量産時のばらつきも非常に小さく抑えることができる。

【0070】

また、図6(a),(b)に示すように、一次巻線22aと並列にダイオード74を接続することによって、タイミング信号の選択が可能になる。例えば、図6(a)のように、ダイオード74のカソードを主スイッチング素子12側にして並列接続した場合、駆動パルスV14aがローレベルに転じた時のタイミング信号のみ二次巻線22bから出力される。反対に、図6(b)のように、ダイオード74のアノードを主スイッチング素子12側にして並列接続した場合は、駆動パルスV14aがハイレベルに転じた時のタイミング信号のみ出力される。また、ダイオード74を接続しない場合は、駆動パルスV14aがローレベルに転じた時とハイレベルに転じた時の両方のタイミング信号が出力される。何れのタイミング信号を使用するかは自由であり、タイミング信号を受ける制御回路の目的や回路構成によって選択すればよい。例えば、図2のスイッチング電源装置10の場合を考えると、異常発振防止回路36をリセットする動作に必要なのは、駆動パルスV14aがハイレベルに転じた時のタイミング信号であり、ローレベルに転じた時のタイミング信号は使用していない。そればかりか、タイミングFET46のゲート・ソース端子間に逆電圧ストレスを加えるおそれのある不要な信号と言える。従って、図6(b)のように、ダイオード74のアノードを主スイッチング素子12の側に接続することによって、不要なタイミング信号の発生を防止することができる。

【0071】

また、この発明の信号伝達トランスも上記実施形態に限定されるものではない。上記の信号伝達トランス22,58,66の閉鎖パターンは、何れもコイルパターンの最外周の1ターン及びその内側の領域を覆うように設けられているが、少なくとも、最内周の1ターン及びその内側領域を覆うものであればよい。閉鎖パターンが小さいと、その外側にあるコイル部分からの磁束が漏れ出すのでシールド効果がやや低下するものの、インダクタンスと結合度の変更、調整には支障がない。また、閉鎖パターンの領域内を引出パターンや他の配線パターンが横切って閉鎖パターンが二以上の小パターンに分離している場合、閉鎖パターンを静電シールドとして使用するに際し、全ての小パターンを同一の安定電位に接続してもよいし、小パターンごとに異なる安定電位に接続しても構わない。

【0072】

また、コイルパターンは渦巻き状の平面コイルであればよく、巻き形状は、円形、四角形、楕円形など自由であり、巻数、パターン幅、パターン間隔等も特に限定されない。また、複数の二次巻線を設け、多出力型の信号伝達トランスを構成することも可能である。

【符号の説明】

【0073】

10 スイッチング電源装置

12 主スイッチング素子

14 主スイッチング素子制御回路

14a パルス出力端子

16 主トランス

16a 入力巻線

16b 出力巻線

16c 補助巻線

18 同期整流回路

20 平滑回路

22,58,66 信号伝達トランス

22a,58a,66a 一次巻線

22b,58b,66b 二次巻線

26 整流側FET

28 転流側FET

36 異常発振防止回路

38 第一補助FET

40 第二補助FET

42 プルアップ抵抗

44 直流電源

46 タイミングFET

50 多層基板

52 導体層

52(1),52(8) 配線パターン

52(2),52(7) 閉鎖パターン

52(3),52(4),52(5),52(6), コイルパターン

54,54(1)〜54(7) 絶縁層

60 多層基板

62 導体層

62(1),62(6) 配線パターン

62(2),62(5) 閉鎖パターン

62(3−1),62(3−2) コイルパターン

62(4−1),62(4−2) 引出パターン

64,64(1)〜64(5) 絶縁層

68 多層基板

70 導体層

70(1) 配線パターン

70(2),70(4−3) 閉鎖パターン

70(3−1),70(3−2) コイルパターン

70(4−1),70(4−2) 引出パターン

72,72(1)〜72(3) 絶縁層

【技術分野】

【0001】

この発明は、回路素子を実装してスイッチング電源回路が構成される多層基板内に形成されたコイルパターンを使用したスイッチング電源用の信号伝達トランス、及びスイッチング電源装置に関する。

【背景技術】

【0002】

スイッチング電源装置では、電力伝送用の主トランスの他に、スイッチング用のトランジスタ素子の駆動パルスや各種の交流信号を伝達する信号伝達トランスが用いられている。近年、電源回路の高密度実装の要請により、絶縁用のボビンを省略することによって小型化を図ったトランスが用いられるようになった。

【0003】

従来、この種のトランスとして、例えば特許文献1に開示されているように、多層基板内に外部から絶縁された複数のコイルパターンを同心状に積層形成し、コイルパターンの最内周の内側を貫通する挿入穴に磁心を挿入して成るプリントコイル形トランスがある。このプリントコイル形トランスは、発生電圧の低い補助コイルが2分割され、補助コイル以外のコイルパターンを挟み込むように外側の層に配置され、その一端が一次側に接地されており、この構造により、補助コイルが静電ノイズを低減するシールド層としての役割も果たす。

【0004】

また、特許文献2に開示されているスイッチング電源装置は、表面に回路素子が実装される多層基板内に外部から絶縁されたコイルパターンが積層して形成されたシートコイルトランスが設けられ、各層の間を絶縁する絶縁シートとして、コイルのインダクタンスを高くするための磁性粉が混合された絶縁シートが用いられている。このシートコイルトランスは、磁性コアの取り付けを省略することができるので、スイッチング電源装置の組み立てが容易で、他の回路素子の実装スペースも確保しやすい。

【0005】

その他、特許文献3に開示されているように、信号伝達トランスを使用した絶縁型DC−DCコンバータであって、入力及び出力巻線を有するメイントランス、入力巻線に接続された主スイッチ素子、主スイッチ素子を駆動するPWM制御回路、出力巻線に接続されたトランス巻線駆動方式の同期整流回路、及び同期整流回路が出力する整流電圧を平滑する平滑回路を備えたシングルエンディッドフォワード方式の絶縁型DC−DCコンバータがある。この絶縁型DC−DCコンバータは、信号伝達トランス(ドライブトランス)の一次巻線が、PWM制御回路のパルス出力端子と主スイッチ素子の駆動端子との接続点に直列に挿入され、同じく二次巻線が、転流側の同期整流素子の駆動端子を短絡可能な駆動スイッチ素子の駆動端子に接続されている。この構成により、PWM制御回路から主スイッチ素子をターンオンさせる駆動パルスが出力されると、主スイッチ素子がターンオンする前に、信号伝達トランスを通じてタイミング信号が駆動スイッチ素子に伝達され、駆動スイッチ素子がターンオンすることによって転流側の同期整流素子がターンオフする。この動作により、主スイッチ素子、整流側及び転流側の同期整流素子が同時にオンして短絡電流が流れる不具合を回避することができる。

【先行技術文献】

【特許文献】

【0006】

【特許文献1】特開平7−142269号公報

【特許文献2】特開平9−182432号公報

【特許文献3】特開2000−262051号公報

【発明の概要】

【発明が解決しようとする課題】

【0007】

しかし、特許文献1の磁気デバイスは、多層基板に磁性コアを組み付ける作業が煩雑で手間がかかる。特許文献2のシートコイルトランスは、磁性粉が混合された絶縁シートを用いた特殊な多層基板を使用しなければならない。従って、いずれの場合もコストが高くなるという問題があった。

【0008】

また、特許文献1,2の構造は、コイルのインダクタンスや各コイル間の結合度を高くするのに適した構造である。しかし、スイッチング電源装置に使用される信号伝達トランスは、回路動作上の役割や伝達する信号の種類によっては、高いインダクタンスや高い結合度が必要なく、かえって低い方がよい場合も少なくない。従って、特許文献1,2の磁気デバイス及びシートコイルトランスの構造は、インダクタンスや結合度の調整可能な範囲が狭く、信号伝達トランスとして使いにくいものである。

【0009】

特許文献3のスイッチング電源装置に使用される信号伝達トランスの構造は、磁性コアを備え、インダクタンスを低くするために巻数を少なくすることが望ましい旨が記載されている。従って、この信号伝達トランスも、インダクタンスや結合度の調整可能な範囲が狭く、最適化のための調整が容易ではない。

【0010】

この発明は、上記背景技術に鑑みて成されたものであり、インダクタンス及び結合度の調整が容易で安価なスイッチング電源装置用の信号伝達トランス、及び当該信号伝達トランスを使用した安全性の高いスイッチング電源装置を提供することを目的とする。

【課題を解決するための手段】

【0011】

この発明は、回路素子を実装してスイッチング電源回路が構成される多層基板内の導体層に形成された同心状の複数のコイルパターンと、前記複数のコイルパターンを挟む外側の導体層により形成され、少なくとも前記コイルパターンの最内周の1ターン及びその内側領域を閉鎖するよう形成された一対の閉鎖パターンとを備え、前記コイルパターンに電流が流れたとき、前記最内周の1ターンの内側領域に発生する磁束の一部が、前記閉鎖パターンに吸収されるスイッチング電源装置用の信号伝達トランスである。

【0012】

前記閉鎖パターンは、複数の小パターンの集合体であってもよい。また、前記閉鎖パターンが安定電位に接続されていることが好ましい。また、前記閉鎖パターンが、回路素子が実装される最外層を除く内側の層に形成されていてもよい。

【0013】

またこの発明は、上記の信号伝達トランスを備え、入力電源に直列接続され、入力電圧を所定のスイッチング周期で断続する主スイッチング素子と、パルス出力端子が前記主スイッチング素子の駆動端子に接続され、前記パルス出力端子ら出力する矩形波状の駆動パルスによって前記主スイッチング素子のオン・オフを制御する主スイッチング素子制御回路とを備え、前記信号伝達トランスの前記一次巻線が、前記主スイッチング素子制御回路の前記パルス出力端子と前記主スイッチング素子の前記駆動端子との接続点に直列に挿入され、前記信号伝達トランスは、前記一次巻線側に前記駆動パルスが入力されることによって前記二次巻線にタイミング信号パルスを発生し、前記主スイッチング素子制御回路とグランド電位の異なる制御回路に伝達し、前記制御回路は、前記タイミング信号パルスを利用した同期制御を行うスイッチング電源装置である。

【0014】

さらに、この発明は、入力電源に直列接続され、入力電圧を所定のスイッチング周期で断続する主スイッチング素子と、パルス出力端子が前記主スイッチング素子の駆動端子に接続され、前記パルス出力端子から出力する矩形波状の駆動パルスによって前記主スイッチング素子のオン・オフを制御する主スイッチング素子制御回路と、前記主スイッチング素子と直列に接続され前記主スイッチング素子の断続によって発生する断続電圧が両端に印加される入力巻線と、前記断続電圧を変圧した交流電圧が発生する出力巻線とを有する主トランスと、前記出力巻線に接続され、前記出力巻線に発生する電圧を整流する一又は二以上の同期整流FETを有し、各ゲート端子が前記トランスの前記出力巻線又はその他の巻線を用いたトランス巻線駆動方式により駆動される同期整流回路と、前記同期整流回路の出力に接続され、整流された電圧を平滑して直流の出力電圧を出力する平滑回路と、前記同期整流FETごとに設けられ、当該ゲート・ソース端子間を短絡・開放可能な補助FETと、対応する前記補助FETのゲート閾値電圧よりも高い電源電圧を出力する一又は二以上の直流電源と、前記直流電源と対応する前記補助FETのゲート端子との間に接続され、当該補助FETのゲート・ソース端子間を当該電源電圧にプルアップするプルアップ抵抗と、前記プルアップ抵抗ごとに設けられ、当該プルアップ抵抗が接続されている前記補助FETのゲート・ソース端子間を短絡・開放可能なタイミングトランジスタ素子と、前記信号トランスとを備え、前記信号伝達トランスは一又は二以上の前記二次巻線を有し、前記一次巻線が、前記主スイッチング素子制御回路の前記パルス出力端子と前記主スイッチング素子の前記駆動端子との接続点に直列に挿入され、前記タイミングトランジスタ素子の駆動端子に、対応する前記二次巻線が接続され、前記タイミングトランジスタ素子は、前記信号伝達トランスの前記一次巻線側に前記駆動パルスが入力されることにより、当該駆動端子に接続された前記二次巻線に発生するタイミング信号パルスを受けてオン・オフし、前記タイミングトランジスタ素子のオフの期間、前記補助FETのゲート・ソース間の入力容量が前記プルアップ抵抗を介して流れ込む前記直流電源からの電流によって充電され、前記プルアップ抵抗は、前記タイミングトランジスタ素子のオフが前記スイッチング周期よりも長い所定の時間を超えて継続したとき、前記補助FETのゲート・ソース端子間の電圧が前記ゲート閾値電圧を超えるように、前記充電電流を制限するスイッチング電源装置である。

【発明の効果】

【0015】

この発明のスイッチング電源装置用の信号伝達トランスは、多層基板内に形成され、磁性コアを取り付けることなく安価に構成することができる。また、コイルパターンのレイアウト(巻数、渦巻きの形状など)を変更する以外にも、各コイルパターン間の絶縁部材の厚み、及びコイルパターンと閉鎖パターンとの間の絶縁部材の厚み等を適宜調節することにより、インダクタンス及び各コイルパターン同士の結合度を広範囲に変更、調整することができる。しかも、多層基板は、金型や数値制御された各種装置を用いて高い寸法精度で製作されるので、最適化されたインダクタンス及び結合度をばらつきなく実現することができる。閉鎖パターンは、コイルパターンの最内周の内側領域を通る磁束が多層基板の外部に漏洩するのを防止すると共に、外来の磁束が信号伝達トランスに鎖交して干渉するのを防止する磁気シールドとしても働く。さらに、閉鎖パターンを安定電位に接地することによって、静電シールドとしての効果も得られる。

【0016】

また、この発明のスイッチング電源装置は、信号伝達トランスの一次巻線が、主スイッチング素子制御回路のパルス出力端子と主スイッチング素子の駆動端子との接続点に直列に挿入され、二次巻線からごく短いパルス幅のタイミング信号を出力する動作を行うので、上記の構造を備えた信号伝達トランスを使用することによって、主スイッチング素子と同期整流素子とのオン・オフのタイミング制御を容易に行うことができる。しかも、インダクタンス及び結合度のバランス設計により、主スイッチング素子の駆動端子電圧の立ち上がり又は立ち下がりスピードを急峻にすることができるので、主スイッチング素子のクロス損失を最小限に抑えることができる。

【図面の簡単な説明】

【0017】

【図1】この発明のスイッチング電源装置の第一実施形態を示すブロック図である。

【図2】第一実施形態のスイッチング電源装置の具体的な構成を示す回路図である。

【図3】この発明の第一実施形態の信号伝達トランスの構造を示す断面図(a)、コイルパターンのレイアウトを示す模式図(b)である。

【図4】信号伝達トランスの第二実施形態の構造を示す断面図(a)、コイルパターンのレイアウトを示す模式図(b)である。

【図5】信号伝達トランスの第三実施形態の構造を示す断面図(a)、コイルパターンのレイアウトを示す模式図(b)である。

【図6】第一実施形態のスイッチング電源装置の変形例を説明する回路図(a),(b)である。

【発明を実施するための形態】

【0018】

以下、この発明のスイッチング電源装置用の信号伝達トランス及びスイッチング電源装置の第一実施形態態について、図1〜図3に基づいて説明する。第一実施形態のスイッチング電源装置10は、図1のブロック図に示すように、主スイッチング素子12、主スイッチング素子制御回路14、主トランス16、同期整流回路18、平滑回路20及び信号伝達トランス22を備えている。ブロックで記載した同期整流回路18及び平滑回路20を具体的な回路で表わすと、図2のようになる。以下、図2の回路図を用いてスイッチング電源装置10の構成と動作を説明する。

【0019】

主スイッチング素子12は、NチャネルのMOS形FETであり、入力電源24に直列接続され、入力電圧を所定のスイッチング周期Tで断続する。主スイッチング素子制御回路14は、パルス出力端子14aが主スイッチング素子12のゲート端子12gに接続され、パルス出力端子14aから矩形波状の駆動パルスV14aを出力し、主スイッチング素子12のオン・オフを制御する。

【0020】

主トランス16は、入力巻線16a、出力巻線16b及び補助巻線16cを備え、互いに密に結合している。入力巻線16aは、主スイッチング素子12と直列に接続され、両端に主スイッチング素子12のオン・オフによって発生する断続電圧が印加される。そして、出力巻線16bと補助巻線16cに、入力巻線16aに印加された断続電圧と略相似形の電圧が発生する。ここで、図2のトランス16に付したドットは、各巻線の極性を示している。

【0021】

同期整流回路18は、2つの同期整流FETである整流側FET26及び転流側FET28を備えている。整流側FET26はNチャネルのMOS型FETであり、ドレイン端子が出力巻線16bのドットのない一端に接続され、ゲート端子が駆動コンデンサ30を介して出力巻線16bのドットのある一端に接続されている。整流側FET26のゲート・ソース端子間に接続されている抵抗32は、図示しないゲート入力容量の放電抵抗である。

【0022】

転流側FET28もNチャネルのMOS型FETであり、ドレイン端子が出力巻線16bのドットのある一端に接続され、ソース端子が整流側FET26のソース端子に接続されている。転流側FET28のゲート・ソース端子間に接続されている抵抗34は、図示しないゲート入力容量の放電抵抗である。転流側FET28のゲート端子は駆動コンデンサ35aを介して駆動ツェナーダイオード35bのカソード端子に接続され、駆動ツェナーダイオード35bのアノード端子が補助巻線16cのドットのない一端に接続され、さらに、補助巻線16cのドットのある一端が転流側FET28のソース端子に接続されている。

【0023】

同期整流回路18は、以上の構成により、整流側及び転流側FET26,28のゲート端子が、出力巻線16b及び補助巻線16cを用いたトランス巻線駆動方式によって駆動され、整流側FET26が主スイッチング素子12と同位相で、転流側FET28が主スイッチング素子12と相補的にそれぞれがオン・オフし、出力巻線16bの発生電圧を適正に整流することができる。

【0024】

さらに、この同期整流回路18には、後述する異常発振の不具合を回避するための異常発振防止回路36が付加されている。異常発振防止回路36は、整流側及び転流側FET26,28のゲート・ソース端子間を短絡・開放可能に自己のドレイン及びソース端子がそれぞれ接続された第一及び第二補助FET38,40を備えている。第一及び第二補助FET38,40のゲート端子は互いに接続され、プルアップ抵抗42を介して直流電源44にプルアップされている。直流電源44は、例えば、出力巻線16b又は補助巻線16cに発生する電圧を利用して直流の電源電圧を生成する簡易式の電圧源であり、第一及び第二補助FET38,40のゲート閾値電圧よりも高い電源電圧を出力する。さらに、第一及び第二補助FET38,40のゲート・ソース端子間を短絡・開放可能に自己のドレイン及びソース端子が接続されたタイミングFET46が設けられている。タイミングFET46はタイミングトランジスタ素子であり、ここではNチャネルのMOS型FETが使用されているが、バイポーラトランジスタに置き換えることも可能である。

【0025】

第一及び第二補助FET38,40のゲート端子電圧V38gは、タイミングFET46がターンオフした時から上昇し始める。プルアップ抵抗42は、直流電源44が第一及び第二補助FET38,40の図示しないゲート入力容量を充電する電流を制限する働きをし、ゲート入力容量との時定数により、電圧V38gの上昇速度を決定する。プルアップ抵抗42の抵抗値は、スイッチング周期Tよりも長い時間(例えば、スイッチング周期Tの2〜5倍程度の時間)が経過した後で、電圧V38gがゲート閾値電圧に達するように、比較的大きな値に設定されている。異常発振防止回路36の詳細な動作は、後で説明する。

【0026】

平滑回路20は、平滑インダクタ20a及び平滑コンデンサ20bで成るローパスフィルタであり、同期整流回路18が出力する整流電圧を平滑して直流の出力電圧を生成し、後段の負荷48に電力を供給する。

【0027】

信号伝達トランス22は、一次巻線22aと二次巻線22bを備えている。図2のドットは各巻線の極性を示しており、一次巻線22aが、主スイッチング素子制御回路14のパルス出力端子14aと主スイッチング素子12のゲート端子12gとの接続点に直列に挿入され、ドットのある一端がパルス出力端子14aに接続されている。二次巻線22bは、ドットのある一端が異常発振防止回路36のタイミングFET46のゲート端子に接続され、ドットのない一端がソース端子に接続されている。

【0028】

信号伝達トランス22は、図3に示すように、主スイッチング素子12やその他の回路素子が実装された多層基板50内に設けられ、異なる導体層に一次巻線22aと二次巻線22bが形成され、それらが積層されて互いに磁気結合した空芯トランスの構造になっている。ここでは、一次及び二次巻線22a,22bの巻数が同じであり、インダクタンスが50〜100nH、結合度が約0.2〜0.3程度に設定されている。信号伝達トランス22の詳細な構造については、後で詳しく説明する。

【0029】

次に、スイッチング電源装置10の動作について説明する。スイッチング電源装置10は、異常発振防止回路36及び信号伝達トランス22が設けられていないとすれば、トランス巻線駆動方式の同期整流回路を備えたシングルエンディッドフォワード型の一般的なスイッチング電源装置である。そして、スイッチング電源装置10に入力電源24が投入され、出力電圧及び出力電流を負荷48に安定供給する動作(以下、定常動作と称する。)を行うときは、異常発振防止回路36は動作しない。従って、定常動作中の電力変換動作は従来と同様であり、ここでは説明を省略する。

【0030】

異常発振防止回路36及び信号伝達トランス22は、入力電源24が停止したとき等に生じる異常発振の不具合を回避するための回路であり、定常動作中は異常発振の不具合が発生し得ないので、異常発振防止回路36の機能を停止させている。具体的には、以下の動作により、第一及び第二補助FET38,40がオフ状態に保持される。

【0031】

主スイッチング素子制御回路14が出力する駆動パルスV14aがローレベルからハイレベルに転じた時、主スイッチング素子12の図示しないゲート入力容量を充電する電流が、一次巻線22aを通じて流れる。これにより一次巻線22a側に所定の信号が入力され、二次巻線22bから出力されるタイミング信号がタイミングFET46のゲート・ソース端子間に伝達される。二次巻線22bはドットのある端子が高電位となるので、ゲート端子電圧V46gが瞬時にゲート閾値電圧を超え、タイミングFET46がオンし、第一及び第二補助FETのゲート入力容量が急速放電され、ゲート端子電圧V38gがリセットされる。

【0032】

その後、主スイッチング素子12のゲート端子電圧V12gが駆動パルスV14aのハイレベル電圧に向かって上昇する。信号伝達トランス22は、一次巻線22aのインダクタンスが非常に小さく、二次巻線22bとの結合度もさほど高くないことから、主スイッチング素子12のゲート入力容量の充電電流がほとんど制限されず、ゲート端子電圧V12gは、駆動パルスV14aが上昇する傾きにほぼ近い急峻な傾きで上昇し、ゲート閾値電圧を超えて主スイッチング素子12がオンする。また、ゲート端子電圧V12gが短時間のうちに駆動パルス電圧V14aに達し、二次巻線22bから出力されるタイミング信号もなくなり、タイミングFET46がオフに転じる。すると、第一及び第二補助FET38,40のゲート入力容量が開放され、直流電源44からプルアップ抵抗42を通じて充電電流が流れ込み、ゲート端子電圧V38gが上昇し始める。ゲート端子電圧V38gの上昇速度は当該ゲート入力容量とプルアップ抵抗42の時定数によって制限され、非常に緩やかに上昇する。

【0033】

その後、主スイッチング素子駆動回路14の駆動パルスV14aがハイレベルからローレベルに転じた時、主スイッチング素子12のゲート入力容量を放電する電流が、一次巻線22aを通じて流れる。これにより、一次巻線22aの側に所定の信号が入力され、二次巻線22bから出力されるタイミング信号がタイミングFET46のゲート・ソース端子間に伝達される。二次巻線22bは、ドットのない端子が高電位となるので、ゲート端子電圧V46gが負方向に低下する。しかし、タイミングFET46は、当該タイミング信号を受ける前から既にオフしており、ゲート端子電圧V38gの上昇に対して影響しない。

【0034】

その後、先に駆動パルスV14aがハイレベルに転じてからスイッチング周期Tが経過した時点で、駆動パルスV14aが再度ハイレベルに転じ、ゲート端子電圧V38gがリセットされる。

【0035】

ゲート端子電圧V38gの上昇速度はプルアップ抵抗42等の時定数によって規定され、ゲート端子電圧V38gがリセットされた後、スイッチング周期Tよりも長い時間(例えば、スイッチング周期Tの2〜5倍程度の時間)が経過しないとゲート閾値電圧を超えない。従って、上記の動作を繰り返す定常動作中は、第一及び第二補助FET38,40がオフ状態に保持され、異常発振防止回路36は動作しない。

【0036】

次に、スイッチング電源装置10が定常動作している最中に入力電源24が遮断される等し、主スイッチング素子駆動回路14の駆動パルスV14aが停止したときの動作(以下、電源停止動作と称する)について説明する。まず、図2に示すスイッチング電源装置10の構成から異常発振防止回路36が設けられていない場合に生じる異常発振の不具合について説明する。

【0037】

スイッチング電源装置10の定常動作中に、主スイッチング素子12がオン、整流側FET26がオン、転流側FET28がオフの状態で駆動パルスV14aが停止した場合を考える。駆動パルスV14aが停止(ローレベルに転じてローレベルを保持)すると、主スイッチング素子12がオンからオフに転じ、一次巻線16aが開放される。すると、主スイッチング素子12のオンの間に主トランス16に蓄積された励磁エネルギーの放出が始まり、出力巻線16bと補助巻線16cの両端に、ドットのない一端が高電位となる方向にフライバック電圧が発生する。このフライバック電圧により、整流側FET26がオフに転じ、転流側FET28がオンに転じる。転流側FET28がオンすると、平滑コンデンサ20bの蓄積電荷を放出する電流が、平滑コンデンサ20b、転流側FET28、平滑インダクタ20aの経路に流れ、平滑インダクタ20aに励磁エネルギーが蓄積される。

【0038】

主トランス16の励磁エネルギーの放出が終了すると、出力巻線16bと補助巻線16cの電圧は低下するが、整流側FET26のオフと転流側FET28のオンが継続する。その後、転流側FET28のゲート入力容量の蓄積電荷が抵抗34によって徐々に放電され、ゲート端子電圧V28gがゲート閾値電圧に低下したところで、転流側FET28がオフし始める。すると、転流側FET28のオンの間に平滑インダクタ20aに蓄積された励磁エネルギーの放出が始まり、平滑インダクタ20aの両端に、平滑コンデンサ20b側の一端が高電位となる方向にフライバック電圧が発生する。このフライバック電圧により、出力巻線16bと補助巻線16cの両端に、ドットのある一端が高電位となる方向に電圧が発生し、整流側FET26がオンに転じると共に転流側FET28も完全にオフする。整流側FET26がオンすると、平滑コンデンサ20aの蓄積電荷と平滑インダクタの励磁エネルギーを放出する電流が、平滑コンデンサ20b、出力巻線16b、整流側FET26、平滑インダクタ20aの経路に流れ、主トランス16に励磁エネルギーが蓄積される。この電流は、出力巻線16bと密に結合している入力巻線16aから、入力電源24(又は、図示しない入力コンデンサ)、主スイッチング素子12の内部に寄生する図示しないドレイン・ソース間ダイオード、という経路にも流れる。

【0039】

その後、整流側FET26のゲート入力容量の蓄積電荷が抵抗32によって徐々に放電され、ゲート端子電圧V26gがゲート閾値電圧まで低下したところで整流側FET26がオフし始める。すると、整流側FET26のオンの間に主トランス16に蓄積された励磁エネルギーの放出が始まり、出力巻線16bと補助巻線16cの両端に、ドットのない一端が高電位となる方向にフライバック電圧が発生し、転流側FET28がオンに転じると共に整流側FET26も完全にオフする。以下、整流側FET26と転流側FET28が相補的にオン・オフする自励式の異常発振が発生する。

【0040】

異常発振の周期は、スイッチング周期Tよりも長くなるのが一般的である(例えば、スイッチング周期Tの5倍〜10倍程度)。また、主トランス16と平滑インダクタ20aに流れる電流の大きさを制限する回路素子もない。従って、異常発振が発生すると、この電流により主トランス16や平滑インダクタ20aが磁気飽和し、それによってさらに大きな電流が発生し、整流側及び転流側FET26,28に過大な電気ストレスが加わって破損するおそれがある。

【0041】

スイッチング電源回路10は、異常発振防止回路36を設けることによって異常発振の不具合が回避されている。スイッチング電源装置10の定常動作中、駆動パルスV14aが停止すると、信号伝達トランス22の二次巻線22bからタイミング信号が出力されないので、タイミングFET46がオフを継続し、第一及び第二補助FET38,40のゲート電圧V38gがリセットされることなく、直流電源44からの充電によって上昇し続ける。そして、スイッチング周期Tの2〜5倍程度の時間(異常発振の周期よりも短い時間)が経過したところでゲート電圧V38gがゲート閾値電圧を超え、第一及び第二補助FET38,40がオンに転じてそのまま保持される。そして、整流側及び転流側FET26,28は、ゲート・ソース端子間が共に短絡されるので、オフに固定されることになる。従って、整流側及び転流側FET26,28は、主トランス16や平滑インダクタ20aの動作によらず、確実にオフに固定されるので、上記のような自励式の異常発振が発生することがない。

【0042】

なお、異常発振防止回路36は、駆動パルスV14aがハイレベルに転じる時のタイミング信号を利用してゲート電圧V38gのリセットを行っているが、駆動パルスV14aがローレベルに転じる時のタイミング信号を利用する構成に変更しても、同様の作用効果を得ることができる。後者の構成を選択するときは、二次巻線22bがタイミングFET46のゲート・ソース端子間に接続される極性を反対にすればよい。従って、各回路素子の部品配置や回路パターンのレイアウトを検討する際に、前者と後者のうちの都合のよい方を選択することができる。

【0043】

スイッチング電源装置10が上記の理想的な動作を行うためには、信号伝達トランス22の特性が重要である。定常動作中は、主スイッチング素子12のゲート端子電圧V12gを急峻に上昇させ、ターンオン時のクロス損失を小さく抑えなくてはならないので、信号伝達トランス22は、インダクタンスを低くすることが好ましい。その一方で、定常動作中、スイッチング周期TごとにタイミングFET46をオンさせて異常発振防止回路36の機能を停止させるため、タイミングFET46がオンするのに十分なタイミング信号を二次巻線22bに発生させなくてはならないので、一定以上の結合が必要である。

【0044】

この信号伝達トランス22は、一次及び二次巻線22a,22bを同じ巻数とし、各インダクタンスを50〜100nH、結合度を約0.2〜0.3に設定することによって、上記2つの条件を両立させている。ただし、これらの数値は一例にすぎず、駆動パルスV14aのハイレベルの電圧値、主スイッチング素子12のゲート入力容量及びゲート閾値電圧、タイミングFET46のゲート入力容量及びゲート閾値電圧、スイッチング周期Tなどが異なると、信号伝達トランス22のインダクタンスと結合度の最適値も異なってくる。従って、信号伝達トランス22は、インダクタンスと結合度の調整、変更が容易な構造であることが望ましい。

【0045】

信号伝達トランス22の構造は、図3に示すように、表面にスイッチング素子12等の回路素子が実装される多層基板50の中に形成されている。多層基板50は、銅などで成る導体層52と、樹脂やガラス繊維等の絶縁部材で成る絶縁層54とを備え、8つの導体層52の間に7つの絶縁層54(図3の上側から順番に54(1)〜54(7))を交互に挟んで積層された一般的なプリント基板である。

【0046】

図3の上側から数えて3番目と4番目の導体層52には、コイルパターン52(3),52(4)が形成され、5番目と6番目の導体層52に、コイルパターン52(5),52(6)が形成され、2番目と7番目の導体層52には、閉鎖パターン52(2),52(7)が形成され、1番目と8番目の導体層52に、回路素子の実装及び配線を行う配線パターン52(1),52(8)が形成されている。

【0047】

コイルパターン52(3),52(4)は、渦巻き状に形成された平面コイルであり、図3(b)に示すように、最内周の1ターンの端部同士が絶縁層54(3)に設けたスルーホールを通じて一体に接続され、一次巻線22aとなる。また、コイルパターン52(3),52(4)も、渦巻き状に形成された平面コイルであり、図3(b)に示すように、最内周の1ターンの端部同士が絶縁層54(5)に設けたスルーホールを通じて一体に接続され、二次巻線22bとなる。4つのコイルパターン52(3)〜52(6)は、最内周の1ターンの内側領域の形状が等しく、最外周の1ターンの外周縁の形状もほぼ等しく、互いに重なり合うように同心状に配置されている。

【0048】

閉鎖パターン52(2),52(7)は、少なくともコイルパターン52(3),52(6)の最内周の1ターン及びその内側領域を閉鎖する導体パターンであり、ここでは、最外周の外周縁の内側領域を覆う大きさに形成されている。従って、一次巻線22aであるコイルパターン52(3),52(4)に電流が流れ最内周の1ターンの内側領域を通る磁束が発生すると、その磁束の一部が閉鎖パターン52(2),52(7)を厚み方向に通過し、渦電流損失となって吸収される。

【0049】

配線パターン52(1),52(8)は、閉鎖パターン52(2),52(7)と重なる領域にも自由に形成することができる。また、閉鎖パターン52(2)は、絶縁層54(1)に設けた図示しないスルーホールを通して配線パターン52(1)の安定電位の部分に接続されている。同様に、閉鎖パターン52(7)も、絶縁層54(7)に設けた図示しないスルーホールを通して配線パターン52(8)の安定電位の部分に接続されている。安定電位とは交流的に安定な電位のことであり、例えば、図2における主スイッチング素子12のソース端子の電位や、主トランス16の入力巻線16aのドットのある一端の電位である。

【0050】

信号伝達トランス22のインダクタンスは、一次及び二次巻線22a,22bの巻数によって調整することができ、巻数を少なくすればインダクタンスが小さくなる。しかし、あまり少なくすると、2つの巻線間の結合度が確保できない。この信号伝達トランス22は、巻数以外のパラメータを変更することによって、インダクタンスと結合度を容易に調整することができる。

【0051】

閉鎖パターン52(2),52(7)は、コイルパターン52(3),52(4)に電流が流れたとき、その内側領域に発生する磁束の一部を吸収すると共に、コイルパターン52(5),52(6)に鎖交する磁束の量を減らす働きをする。すなわち、閉鎖パターン52(2),52(7)が存在すると、インダクタンスが低下すると共に、結合度も低下することになる。閉鎖パターン52(2),52(7)による磁束の吸収量は、閉鎖パターン52(2),52(7)の厚みを変更することによって調整できる。また、閉鎖パターン52(2)とコイルパターン52(3)との間の絶縁層54(2)の厚みを変更することによって、絶縁層54(2)の内部を面方向に通過する磁束の量、すなわち閉鎖パターン52(2),52(7)に吸収されない磁束の量を調整できる。閉鎖パターン52(7)とコイルパターン52(6)との間の絶縁層54(6)の厚みについても同様である。このように、上記の各パラメータを変化させることによって、インダクタンスと結合度を広範囲に調整、変更することができる。

【0052】

インダクタンスと結合度を調整する手段は他にもあり、例えば、絶縁層54(3),54(4),54(5),54(6)の厚みを変更したり、平面コイル内の1ターン毎の間隔を変更したり、各コイルパターンの最内周の内側領域の面積を増減したりすることによって、ある程度の調整が可能である。

【0053】

以上説明したように、第一実施形態のスイッチング電源装置10は、電源停止時に異常発振防止回路36が動作することによって、異常発振による不具合を確実に回避することができ、安全である。さらに、定常動作時、信号伝達トランス22は、一次巻線22aが主スイッチング素子制御回路14のパルス出力端子14aと主スイッチング素子12のゲート端子12gとの接続点に直列に挿入され、ごく短いパルス幅のタイミング信号を二次巻線22bに伝達する動作を行う。従って、信号伝達トランス22のインダクタンスと結合度を最適化することにより、主スイッチング素子12のゲート端子電圧V12gの立ち上がりを急峻にし、主スイッチング素子のクロス損失の最小限に抑えることができる。

【0054】

また、信号伝達トランス22は、多層基板50の内部に形成され、磁性コアが不要なので安価に構成することができ、信号伝達トランス22と重なる位置に他の回路素子を配置することにより、スイッチング電源装置の小型化にも寄与できる。さらに、コイルパターン52(3)〜52(6)の巻数などを変更する以外に、各コイルパターン間の絶縁層54(3)〜54(5)の厚み、及びコイルパターン52(3),52(6)と閉鎖パターン52(2),52(7)の間の絶縁層54(2),54(6)の厚み等のパラメータを調節することにより、インダクタンスと結合度を広範囲に変化させることができるので、最適化が容易である。しかも、多層基板50は、金型や数値制御された各種装置を用いて高い寸法精度で製作されるので、最適化されたインダクタンス及び結合度をばらつきなく実現することができる。従って、スイッチング電源装置10の信号伝達トランス22等の用途に非常に適している。

【0055】

閉鎖パターン52(2),52(7)は、コイルパターン52(3)〜52(6)の最内周の内側領域を通過する磁束が多層基板50の外部に漏洩するのを防止すると共に、外来の磁束が信号伝達トランス22に鎖交して干渉するのを防止する磁気シールドの働きをする。さらに、閉鎖パターンが安定電位に接地されているので静電シールドとしても働く。

【0056】

次に、この発明の信号伝達トランスの第二実施形態について、図4に基づいて説明する。この実施形態の信号伝達トランス58は、一次及び二次巻線58a,58bを備え、上記スイッチング電源装置10の信号伝達トランス22と同様に使用可能なトランスである。

【0057】

多層基板60は、銅などから成る導体層62と、樹脂やガラス繊維等の絶縁部材で成る絶縁層64とを備え、6つの導体層52の間に5つの絶縁層64(図4の上側から順番に64(1)〜64(5))を交互に挟んで積層された一般的なプリント基板である。

【0058】

図4の上側から数えて3番目の導体層62に一次巻線58aであるコイルパターン62(3−1)及び二次巻線58bであるコイルパターン62(3−2)が形成され、4番目の導体層62に、引出パターン62(4−1),62(4−2)が形成され、2番目と5番目の導体層62に閉鎖パターン62(2),62(5)が形成され、さらに、1番目と6番目の導体層62に回路素子の実装及び配線を行う配線パターン62(1),62(6)が形成されている。

【0059】

コイルパターン62(3−1),62(3−2)は、図4(b)に示すように、互いに平行に渦巻き状に形成された平面コイルであり、最内周の1ターンの端部が絶縁層64(3)に設けたスルーホールを通じて引出パターン62(4−1),62(4−2)に接続され、外側に引き出されている。

【0060】

閉鎖パターン62(2),62(5)は、少なくともコイルパターン62(3−1),62(3−2)の最内周の1ターン及びその内側領域を閉鎖する導体パターンであり、ここでは、最外周の外周縁の内側領域を覆う大きさに形成されている。従って、一次巻線58aであるコイルパターン62(3−1)に電流が流れて最内周の1ターンの内側領域を通る磁束が発生すると、その磁束の一部が閉鎖パターン62(2),62(5)を厚み方向に通過し、渦電流損失となって吸収される。

【0061】

このように、第二実施形態の信号伝達トランス58は、一次及び二次巻線58a,58bを2つの導体層62で構成したという点で、上記の信号伝達トランス22と異なり、その他の構成は同様である。この信号伝達トランス58は上記の信号伝達トランス22と同様の作用効果を得ることができ、特に、信号伝達トランス22が4つの導体層52で一次及び二次巻線22a,22bを構成しているのに比べると、層数の少ない安価な多層基板を使用できるという利点がある。

【0062】

この発明の第三実施形態の信号伝達トランス66は、図5に示すように、さらに層数の少ない多層基板に構成されている。信号伝達トランス66は、一次及び二次巻線66a,66bを備え、上記の信号伝達トランス22,58と同様に使用可能なトランスである。

【0063】

多層基板68は、銅などで成る導体層70と、樹脂やガラス繊維等の絶縁部材で成る絶縁層72とを備え、4つの導体層70の間に3つの絶縁層72(図5の上側から順番に72(1)〜72(3))を交互に挟んで積層された一般的なプリント基板である。

【0064】

図5の上側から数えて1番目の導体層70に回路素子の実装及び配線を行う配線パターン70(1)が形成され、3番目の導体層70に、一次巻線66aであるコイルパターン70(3−1)と二次巻線66bであるコイルパターン70(3−2)が形成され、4番目の導体層70に、引出パターン70(4−1),70(4−2)、閉鎖パターン70(4−3)、及び図示しない配線パターンが形成されている。

【0065】

コイルパターン70(3−1),70(3−2)は、図5(b)に示すように、互いに平行に渦巻き状に形成された平面コイルであり、最内周の1ターンの端部が絶縁層72(3)に設けたスルーホールを通じて引出パターン70(4−1),70(4−2)に接続され、外側に引き出されている。閉鎖パターン70(4−3)は、少なくともコイルパターン70(3−1),70(3−2)の最内周の1ターン及びその内側領域を閉鎖する一又は二以上に分離した導体パターンであり、引出パターン70(4−1),70(4−2)を避けて設けられている。

【0066】

第三実施形態の信号伝達トランス66は、一次及び二次巻線66a,66bを2つの導体層70で構成したという点で、上記の信号伝達トランス22と異なる。さらに、一方の閉鎖パターン70(4−3)、引出パターン70(4−1),70(4−2)、及び配線パターンを同じの導体層70に設けたという点で、上記の信号伝達トランス60と異なる。その他の構成は同様である。

【0067】

この信号伝達トランス66は、上記の信号伝達トランス22,58と同様の作用効果を得ることができ、特に、上記の信号伝達トランス22が4つの導体層52で一次及び二次巻線22a,22bを構成しているのに比べると、格段に層数の少ない安価な多層基板を使用できるという利点がある。

【0068】

なお、この発明のスイッチング電源装置は、上記実施形態に限定されるものではない。図2のスイッチング電源装置10は、トランス巻線駆動方式の同期整流回路を備えたシングルエンディッドフォワード型のスイッチング電源装置であるが、インバータ型式がシングルエンディッドフォワード型と異なるスイッチング電源装置にも適用することができる。シングルエンディッドフォワード型のスイッチング電源装置10の場合、同期整流素子が2つ(整流側及び転流側FET26,28)なので、異常発振防止回路36は、同期整流素子ごとに1つずつ(補助FET38,40)設けられている。例えば、インバータ型式がフライバック型の場合、同期整流素子が1つなので補助FETは1つで足りる。また、インバータ型式がブリッジ型で主トランスの出力巻線電圧を全波整流する場合、同期整流素子が4つなので、補助FETを4つ設ければよい。何れの場合も、スイッチング電源10と同様に、電源停止時の異常動作の不具合を容易かつ確実に回避することができる。

【0069】

また、図2のスイッチング電源装置10の場合、信号伝達トランス22の二次巻線22bから出力されるタイミング信号が、異常発振防止回路36をリセットする同期制御に使用されているが、その他の様々な同期制御に使用することができる。例えば、背景技術の特許文献3に記載された絶縁型DC−DCコンバータのように、トランス巻線駆動方式で駆動される転流側FETのターンオフのタイミングを制御し、転流側FETと主スイッチング素子とが同時にオンするのを防止する同期制御に、このタイミング信号を使用することができる。また、主トランスの一次巻線と並列にアクティブクランプ用コンデンサを断続する直列スイッチング素子を備えたスイッチング電源装置において、直列スイッチング素子のターンオフ又はターンオフのタイミングを制御し、直列スイッチング素子と主スイッチング素子が同時にオンするのを防止する同期制御に、このタイミング信号を使用することも可能である。ここで例示した何れの同期制御においても、信号伝達トランスのインダクタンスと結合度を最適化する必要があり、この発明の信号伝達トランスを使用すれば最適化が容易であり、量産時のばらつきも非常に小さく抑えることができる。

【0070】

また、図6(a),(b)に示すように、一次巻線22aと並列にダイオード74を接続することによって、タイミング信号の選択が可能になる。例えば、図6(a)のように、ダイオード74のカソードを主スイッチング素子12側にして並列接続した場合、駆動パルスV14aがローレベルに転じた時のタイミング信号のみ二次巻線22bから出力される。反対に、図6(b)のように、ダイオード74のアノードを主スイッチング素子12側にして並列接続した場合は、駆動パルスV14aがハイレベルに転じた時のタイミング信号のみ出力される。また、ダイオード74を接続しない場合は、駆動パルスV14aがローレベルに転じた時とハイレベルに転じた時の両方のタイミング信号が出力される。何れのタイミング信号を使用するかは自由であり、タイミング信号を受ける制御回路の目的や回路構成によって選択すればよい。例えば、図2のスイッチング電源装置10の場合を考えると、異常発振防止回路36をリセットする動作に必要なのは、駆動パルスV14aがハイレベルに転じた時のタイミング信号であり、ローレベルに転じた時のタイミング信号は使用していない。そればかりか、タイミングFET46のゲート・ソース端子間に逆電圧ストレスを加えるおそれのある不要な信号と言える。従って、図6(b)のように、ダイオード74のアノードを主スイッチング素子12の側に接続することによって、不要なタイミング信号の発生を防止することができる。

【0071】

また、この発明の信号伝達トランスも上記実施形態に限定されるものではない。上記の信号伝達トランス22,58,66の閉鎖パターンは、何れもコイルパターンの最外周の1ターン及びその内側の領域を覆うように設けられているが、少なくとも、最内周の1ターン及びその内側領域を覆うものであればよい。閉鎖パターンが小さいと、その外側にあるコイル部分からの磁束が漏れ出すのでシールド効果がやや低下するものの、インダクタンスと結合度の変更、調整には支障がない。また、閉鎖パターンの領域内を引出パターンや他の配線パターンが横切って閉鎖パターンが二以上の小パターンに分離している場合、閉鎖パターンを静電シールドとして使用するに際し、全ての小パターンを同一の安定電位に接続してもよいし、小パターンごとに異なる安定電位に接続しても構わない。

【0072】

また、コイルパターンは渦巻き状の平面コイルであればよく、巻き形状は、円形、四角形、楕円形など自由であり、巻数、パターン幅、パターン間隔等も特に限定されない。また、複数の二次巻線を設け、多出力型の信号伝達トランスを構成することも可能である。

【符号の説明】

【0073】

10 スイッチング電源装置

12 主スイッチング素子

14 主スイッチング素子制御回路

14a パルス出力端子

16 主トランス

16a 入力巻線

16b 出力巻線

16c 補助巻線

18 同期整流回路

20 平滑回路

22,58,66 信号伝達トランス

22a,58a,66a 一次巻線

22b,58b,66b 二次巻線

26 整流側FET

28 転流側FET

36 異常発振防止回路

38 第一補助FET

40 第二補助FET

42 プルアップ抵抗

44 直流電源

46 タイミングFET

50 多層基板

52 導体層

52(1),52(8) 配線パターン

52(2),52(7) 閉鎖パターン

52(3),52(4),52(5),52(6), コイルパターン

54,54(1)〜54(7) 絶縁層

60 多層基板

62 導体層

62(1),62(6) 配線パターン

62(2),62(5) 閉鎖パターン

62(3−1),62(3−2) コイルパターン

62(4−1),62(4−2) 引出パターン

64,64(1)〜64(5) 絶縁層

68 多層基板

70 導体層

70(1) 配線パターン

70(2),70(4−3) 閉鎖パターン

70(3−1),70(3−2) コイルパターン

70(4−1),70(4−2) 引出パターン

72,72(1)〜72(3) 絶縁層

【特許請求の範囲】

【請求項1】

回路素子を実装してスイッチング電源回路が構成される多層基板内の導体層に形成された同心状の複数のコイルパターンと、

前記複数のコイルパターンを挟む外側の導体層により形成され、少なくとも前記コイルパターンの最内周の1ターン及びその内側領域を閉鎖するよう形成された一対の閉鎖パターンとを備え、

前記コイルパターンに電流が流れたとき、前記最内周の1ターンの内側領域に発生する磁束の一部が、前記閉鎖パターンに吸収されること特徴とするスイッチング電源装置用の信号伝達トランス。

【請求項2】

前記閉鎖パターンは、複数の小パターンが集合して成る請求項1記載のスイッチング電源装置用の信号伝達トランス。

【請求項3】

前記閉鎖パターンが安定電位に接続されている請求項1又は2記載のスイッチング電源装置用の信号伝達トランス。

【請求項4】

前記閉鎖パターンは、回路素子が実装される最外層を除く内側の層に形成されている請求項1又は2記載のスイッチング電源用の信号伝達トランス。

【請求項5】

請求項1乃至4のいずれか記載の信号伝達トランスと、

入力電源に直列接続され、入力電圧を所定のスイッチング周期で断続する主スイッチング素子と、

パルス出力端子が前記主スイッチング素子の駆動端子に接続され、前記パルス出力端子から出力する矩形波状の駆動パルスによって前記主スイッチング素子のオン・オフを制御する主スイッチング素子制御回路とを備え、

前記信号伝達トランスの前記一次巻線が、前記主スイッチング素子制御回路の前記パルス出力端子と前記主スイッチング素子の前記駆動端子との接続点に直列に挿入され、

前記信号伝達トランスは、前記一次巻線側に前記駆動パルスが入力されることによって前記二次巻線にタイミング信号パルスを発生し、前記主スイッチング素子制御回路とグランド電位の異なる制御回路に伝達し、

前記制御回路は、前記タイミング信号パルスを利用した同期制御を行うことを特徴とするスイッチング電源装置。

【請求項6】

請求項1乃至4のいずれか記載の信号伝達トランスと、

入力電源に直列接続され、入力電圧を所定のスイッチング周期で断続する主スイッチング素子と、

パルス出力端子が前記主スイッチング素子の駆動端子に接続され、前記パルス出力端子から出力する矩形波状の駆動パルスによって前記主スイッチング素子のオン・オフを制御する主スイッチング素子制御回路と、

前記主スイッチング素子と直列に接続され前記主スイッチング素子の断続によって発生する断続電圧が両端に印加される入力巻線と、前記断続電圧を変圧した交流電圧が発生する出力巻線とを有する主トランスと、

前記出力巻線に接続され、前記出力巻線に発生する電圧を整流する一又は二以上の同期整流FETを有し、各ゲート端子が前記トランスの前記出力巻線又はその他の巻線を用いたトランス巻線駆動方式により駆動される同期整流回路と、

前記同期整流回路の出力に接続され、整流された電圧を平滑して直流の出力電圧を出力する平滑回路と、

前記同期整流FETごとに設けられ、当該ゲート・ソース端子間を短絡・開放可能な補助FETと、

対応する前記補助FETのゲート閾値電圧よりも高い電源電圧を出力する直流電源と、

前記直流電源と対応する前記補助FETのゲート端子との間に接続され、当該補助FETのゲート・ソース端子間を当該電源電圧にプルアップするプルアップ抵抗と、

前記プルアップ抵抗ごとに設けられ、当該プルアップ抵抗が接続されている前記補助FETのゲート・ソース端子間を短絡・開放可能なタイミングトランジスタ素子とを備え、

前記信号伝達トランスは一又は二以上の二次巻線を有し、前記一次巻線が、前記主スイッチング素子制御回路の前記パルス出力端子と前記主スイッチング素子の前記駆動端子との接続点に直列に挿入され、前記タイミングトランジスタ素子の駆動端子に、対応する前記二次巻線が接続され、

前記タイミングトランジスタ素子は、前記信号伝達トランスの前記一次巻線側に前記駆動パルスが入力されることにより前記二次巻線に発生するタイミング信号パルスを受けてオン・オフし、

前記タイミングトランジスタ素子のオフの期間、前記補助FETのゲート・ソース間の入力容量が前記プルアップ抵抗を介して流れ込む前記直流電源からの電流によって充電され、

前記プルアップ抵抗は、前記タイミングトランジスタ素子のオフが前記スイッチング周期よりも長い所定の時間を超えて継続したとき、前記補助FETのゲート・ソース端子間の電圧が前記ゲート閾値電圧を超えるように、前記充電電流を制限することを特徴とするスイッチング電源装置。

【請求項1】

回路素子を実装してスイッチング電源回路が構成される多層基板内の導体層に形成された同心状の複数のコイルパターンと、

前記複数のコイルパターンを挟む外側の導体層により形成され、少なくとも前記コイルパターンの最内周の1ターン及びその内側領域を閉鎖するよう形成された一対の閉鎖パターンとを備え、

前記コイルパターンに電流が流れたとき、前記最内周の1ターンの内側領域に発生する磁束の一部が、前記閉鎖パターンに吸収されること特徴とするスイッチング電源装置用の信号伝達トランス。

【請求項2】

前記閉鎖パターンは、複数の小パターンが集合して成る請求項1記載のスイッチング電源装置用の信号伝達トランス。

【請求項3】

前記閉鎖パターンが安定電位に接続されている請求項1又は2記載のスイッチング電源装置用の信号伝達トランス。

【請求項4】

前記閉鎖パターンは、回路素子が実装される最外層を除く内側の層に形成されている請求項1又は2記載のスイッチング電源用の信号伝達トランス。

【請求項5】

請求項1乃至4のいずれか記載の信号伝達トランスと、

入力電源に直列接続され、入力電圧を所定のスイッチング周期で断続する主スイッチング素子と、

パルス出力端子が前記主スイッチング素子の駆動端子に接続され、前記パルス出力端子から出力する矩形波状の駆動パルスによって前記主スイッチング素子のオン・オフを制御する主スイッチング素子制御回路とを備え、

前記信号伝達トランスの前記一次巻線が、前記主スイッチング素子制御回路の前記パルス出力端子と前記主スイッチング素子の前記駆動端子との接続点に直列に挿入され、

前記信号伝達トランスは、前記一次巻線側に前記駆動パルスが入力されることによって前記二次巻線にタイミング信号パルスを発生し、前記主スイッチング素子制御回路とグランド電位の異なる制御回路に伝達し、

前記制御回路は、前記タイミング信号パルスを利用した同期制御を行うことを特徴とするスイッチング電源装置。

【請求項6】

請求項1乃至4のいずれか記載の信号伝達トランスと、

入力電源に直列接続され、入力電圧を所定のスイッチング周期で断続する主スイッチング素子と、

パルス出力端子が前記主スイッチング素子の駆動端子に接続され、前記パルス出力端子から出力する矩形波状の駆動パルスによって前記主スイッチング素子のオン・オフを制御する主スイッチング素子制御回路と、

前記主スイッチング素子と直列に接続され前記主スイッチング素子の断続によって発生する断続電圧が両端に印加される入力巻線と、前記断続電圧を変圧した交流電圧が発生する出力巻線とを有する主トランスと、

前記出力巻線に接続され、前記出力巻線に発生する電圧を整流する一又は二以上の同期整流FETを有し、各ゲート端子が前記トランスの前記出力巻線又はその他の巻線を用いたトランス巻線駆動方式により駆動される同期整流回路と、

前記同期整流回路の出力に接続され、整流された電圧を平滑して直流の出力電圧を出力する平滑回路と、

前記同期整流FETごとに設けられ、当該ゲート・ソース端子間を短絡・開放可能な補助FETと、

対応する前記補助FETのゲート閾値電圧よりも高い電源電圧を出力する直流電源と、

前記直流電源と対応する前記補助FETのゲート端子との間に接続され、当該補助FETのゲート・ソース端子間を当該電源電圧にプルアップするプルアップ抵抗と、

前記プルアップ抵抗ごとに設けられ、当該プルアップ抵抗が接続されている前記補助FETのゲート・ソース端子間を短絡・開放可能なタイミングトランジスタ素子とを備え、

前記信号伝達トランスは一又は二以上の二次巻線を有し、前記一次巻線が、前記主スイッチング素子制御回路の前記パルス出力端子と前記主スイッチング素子の前記駆動端子との接続点に直列に挿入され、前記タイミングトランジスタ素子の駆動端子に、対応する前記二次巻線が接続され、

前記タイミングトランジスタ素子は、前記信号伝達トランスの前記一次巻線側に前記駆動パルスが入力されることにより前記二次巻線に発生するタイミング信号パルスを受けてオン・オフし、

前記タイミングトランジスタ素子のオフの期間、前記補助FETのゲート・ソース間の入力容量が前記プルアップ抵抗を介して流れ込む前記直流電源からの電流によって充電され、

前記プルアップ抵抗は、前記タイミングトランジスタ素子のオフが前記スイッチング周期よりも長い所定の時間を超えて継続したとき、前記補助FETのゲート・ソース端子間の電圧が前記ゲート閾値電圧を超えるように、前記充電電流を制限することを特徴とするスイッチング電源装置。

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図2】

【図3】

【図4】

【図5】

【図6】

【公開番号】特開2013−81283(P2013−81283A)

【公開日】平成25年5月2日(2013.5.2)

【国際特許分類】

【出願番号】特願2011−219213(P2011−219213)

【出願日】平成23年10月3日(2011.10.3)

【出願人】(000103208)コーセル株式会社 (80)

【Fターム(参考)】

【公開日】平成25年5月2日(2013.5.2)

【国際特許分類】

【出願日】平成23年10月3日(2011.10.3)

【出願人】(000103208)コーセル株式会社 (80)

【Fターム(参考)】

[ Back to top ]