スイッチング電源装置

【課題】ダイオードブリッジを設けることなく、且つスイッチング制御回路を複雑化することなく、全体の電力損失を低減したスイッチング電源装置を構成する。

【解決手段】スイッチング素子Q1,Q2に流れる電流が正方向であるときの電流検出抵抗Rs1,Rs2の降下電圧が順方向となる向きにダイオードDs1,Ds2が接続されている。PFC制御IC30は、ダイオードDs1の出力電圧Vrs1が電流基準値に対応する値に達したときにスイッチング素子Q1をターンオフし、ダイオードDs2の出力電圧Vrs2が電流基準値に対応する値に達したときにスイッチング素子Q2をターンオフするので、正の半サイクルでスイッチング素子Q2はオン状態を保ち、負の半サイクルでスイッチング素子Q1はオン状態を保つ。そのため、スイッチング素子Q1,Q2のボディダイオードによる損失が低減される。

【解決手段】スイッチング素子Q1,Q2に流れる電流が正方向であるときの電流検出抵抗Rs1,Rs2の降下電圧が順方向となる向きにダイオードDs1,Ds2が接続されている。PFC制御IC30は、ダイオードDs1の出力電圧Vrs1が電流基準値に対応する値に達したときにスイッチング素子Q1をターンオフし、ダイオードDs2の出力電圧Vrs2が電流基準値に対応する値に達したときにスイッチング素子Q2をターンオフするので、正の半サイクルでスイッチング素子Q2はオン状態を保ち、負の半サイクルでスイッチング素子Q1はオン状態を保つ。そのため、スイッチング素子Q1,Q2のボディダイオードによる損失が低減される。

【発明の詳細な説明】

【技術分野】

【0001】

本発明はスイッチング電源装置に関し、特に整流ブリッジ回路を設けないブリッジレスPFCとして作用するスイッチング電源装置に関するものである。

【背景技術】

【0002】

商用交流電源が入力されて、スイッチング電源装置の力率を改善するPFCコンバータは、例えば特許文献2,3に開示されている。特許文献2,3のPFCコンバータは、商用交流電源を入力して全波整流するダイオードブリッジと、その全波整流電圧を入力する昇圧チョッパー回路とで構成されている。

【0003】

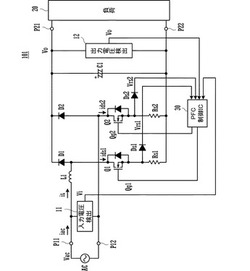

ここで、ダイオードブリッジと昇圧チョッパー回路とで構成されているPFCコンバータ動作するスイッチング電源装置の構成例を図1に示す。

図1に示すスイッチング電源装置において、商用交流電源ACの交流入力電圧Vacを整流するダイオードブリッジB1の出力両端には、インダクタL1とスイッチング素子Q1と電流検出抵抗Rsとからなる直列回路が接続されている。スイッチング素子Q1の両端には、ダイオードD1と平滑コンデンサC1とからなる直列回路が接続され、平滑コンデンサC1の両端には、負荷20が接続されている。スイッチング素子Q1は、PFC制御IC10のPWM制御によりオン/オフする。電流検出抵抗Rsは、ダイオードブリッジB1に流れる入力電流を検出する。

【0004】

PFC制御IC10は、ダイオードブリッジB1に流れる電流と入力電圧波形とを比較し、また出力電圧を参照して、それらに応じたデューティパルスをスイッチング素子Q1に与える。このような構成により、交流電源電流波形が交流電源電圧波形に相似形になり、且つ出力電圧が一定になるように制御されて、力率が改善される。

【0005】

一方、特許文献1に開示されているように、整流ブリッジ回路にスイッチング素子を組み込んだ回路も知られている。このように、ダイオードブリッジ回路を設けない構成であると、ダイオードブリッジ回路で損失が生じないので、その分の電力損失が低減できる、という利点がある。

【先行技術文献】

【特許文献】

【0006】

【特許文献1】特表2007−527687号公報

【特許文献2】特開平10−94246号公報

【特許文献3】特開2000−139079号公報

【発明の概要】

【発明が解決しようとする課題】

【0007】

しかし、整流ブリッジ回路にスイッチング素子を組み込んだ回路では、スイッチング素子の制御が単純ではなく、制御回路が複雑になる欠点がある。多く市販されているPFC制御ICは特許文献2,3のようにワンサイクル制御を行うものであり、これらのPFC制御ICでブリッジレスPFCのスイッチング素子を制御するのは困難であった。

【0008】

特許文献1のPFCコンバータでは、ワンサイクル制御回路によって二つのスイッチング素子を制御するようにしたものであるが、この構成では、スイッチング素子での損失が必ずしも小さくはないという課題がある。

【0009】

すなわち、二つのスイッチング素子に対して並列接続されているダイオード(ボディダイオード)は商用交流電源周期の半周期において常に導通することになるが、従来のワンサイクル制御を行うPFC制御ICを用いると、2つのスイッチング素子が同じようにオンオフしてしまう。そのため、ボディダイオードのみ通して通電される期間が生じ、ボディダイオードでの損失が大きくなる、という課題がある。

【0010】

この発明の目的は、ダイオードブリッジを設けることなく、且つスイッチング制御回路を複雑化することなく、全体の電力損失を低減したスイッチング電源装置を提供することにある。

【課題を解決するための手段】

【0011】

前記課題を解決するために、この発明のスイッチング電源装置は次のように構成する。

この発明のスイッチング電源装置は、

二つの出力端に対して並列に接続された、第1のスイッチング素子と第1の整流素子を含む第1の直列回路と、

前記二つの出力端に対して並列に接続された、第2のスイッチング素子と第2の整流素子を含む第2の直列回路と、

前記第1のスイッチング素子と前記第1の整流素子との接続点と交流入力電源の第1の入力端との間、若しくは前記第2のスイッチング素子と前記第2の整流素子との接続点と交流入力電源の第2の入力端との間、の何れか一方又は両方に挿入されたインダクタと、

前記二つの出力端に対して並列に接続された平滑回路と、

前記交流入力電源の第1の入力端と第2の入力端との間に入力される入力電圧を検出する入力電圧検出手段と、

前記二つの出力端に出力される出力電圧を検出する出力電圧検出手段と、

前記インダクタに流れる電流の平均値が前記入力電圧に対して相似形となるように前記第1のスイッチング素子及び前記第2のスイッチング素子を制御するスイッチング制御手段とを備え、

前記スイッチング制御手段は、前記出力電圧検出手段の検出信号を入力して、出力電圧を目標値に安定化する電圧補償手段と、前記入力電圧検出手段の検出信号を入力して、正弦波状の電流基準値を生成する手段と、前記第1のスイッチング素子に流れる電流検出信号に基づいてインダクタ電流を検出する第1のインダクタ電流検出手段と、前記第2のスイッチング素子に流れる電流検出信号に基づいてインダクタ電流を検出する第2のインダクタ電流検出手段と、前記電流基準値及び第1のインダクタ電流検出手段による検出値に基づいて第1のスイッチング素子のオンデューティを制御する第1のPWM制御手段と、前記電流基準値及び第2のインダクタ電流検出手段による検出値に基づいて第2のスイッチング素子のオンデューティを制御する第2のPWM制御手段と、を備えるとともに、

前記第1のインダクタ電流検出手段及び第2のインダクタ電流検出手段は、前記第1のスイッチング素子又は第2のスイッチング素子のうち、電流が正方向に流れるスイッチング素子の電流値を、当該スイッチング素子に流れる実際の電流値として(そのまま)検出し、電流が負方向に流れるスイッチング素子の電流値を、当該スイッチング素子に流れる実際の電流値より小さく(低く)検出することを特徴とする。

例えば、前記第1のインダクタ電流検出手段は、前記第1のスイッチング素子に直列接続された第1の電流検出抵抗と、前記第1のスイッチング素子に流れる電流が正方向であるときの前記第1の電流検出抵抗の降下電圧が順方向となる向きに接続された第1のダイオードを含み、

前記第2のインダクタ電流検出手段は、前記第2のスイッチング素子に直列接続された第2の電流検出抵抗と、前記第2のスイッチング素子に流れる電流が正方向であるときの前記第2の電流検出抵抗の降下電圧が順方向となる向きに接続された第2のダイオードを含んで構成される。

【0012】

また例えば、前記第1のインダクタ電流検出手段は、前記第1のスイッチング素子に接続された第1のカレントトランスと、前記第1のスイッチング素子に流れる電流が正方向であるときの前記第1のカレントトランスの出力電圧が順方向となる向きに接続された第1のダイオードとで構成され、

前記第2のインダクタ電流検出手段は、前記第2のスイッチング素子に接続された第2のカレントトランスと、前記第2のスイッチング素子に流れる電流が正方向であるときの前記第2のカレントトランスの出力電圧が順方向となる向きに接続された第2のダイオードとで構成される。

【0013】

また例えば、前記スイッチング制御手段は、インターリーブPFC用の制御ICで構成する。

【発明の効果】

【0014】

この発明によれば、スイッチング制御回路が複雑化することなくブリッジレスPFCコンバータを構成でき、しかもスイッチング素子のボディダイオードによる損失を低減したスイッチング電源装置が得られる。

【図面の簡単な説明】

【0015】

【図1】ダイオードブリッジと昇圧チョッパー回路とで構成されて、PFCコンバータ動作する従来のスイッチング電源装置の回路図である。

【図2】第1の実施形態に係るスイッチング電源装置101の回路図である。

【図3】スイッチング電源装置101のPFC制御ICの構成をブロック化して表した図である。

【図4】図2に示したスイッチング電源装置101の4つのタイミングでの電流経路を示す図である。

【図5】電流連続モードで制御が行われている状態におけるスイッチング電源装置101の電圧・電流の波形図であり、図5(A)は正の半サイクルでの波形、図5(B)は負の半サイクルでの波形である。

【図6】第2の実施形態に係るスイッチング電源装置102の回路図である。

【図7】電流連続モードで制御が行われている状態におけるスイッチング電源装置102の電圧・電流の波形図であり、図7(A)は正の半サイクルでの波形図、図7(B)は負の半サイクルでの波形図である。

【図8】従来のインターリーブ方式のスイッチング電源装置の回路図である。

【発明を実施するための形態】

【0016】

《第1の実施形態》

第1の実施形態に係るスイッチング電源装置について、図2〜図5を参照して説明する。

図2は第1の実施形態に係るスイッチング電源装置101の回路図である。図2において第1の入力端P11と第2の入力端P12に商用交流電源ACが接続され、交流入力電圧Vacが入力される。また、出力端P21,P22に負荷20が接続され、所定の直流電圧が負荷20へ出力される。

【0017】

負荷20は例えばDC−DCコンバータ及びそのDC−DCコンバータによって電源供給を受ける電子機器の回路である。

【0018】

このスイッチング電源装置101の入力段には、交流入力電圧Vacを全波整流するダイオードブリッジが設けられていない。

第1のスイッチング素子Q1と第1のダイオードD1(本発明に係る「第1の整流素子」)を含む第1の直列回路が、二つの出力端P21,P22に対して並列接続されている。また、第2のスイッチング素子Q2と第2のダイオードD2(本発明に係る「第2の整流素子」)を含む第2の直列回路が、二つの出力端P21,P22に対して並列接続されている。

【0019】

第1のスイッチング素子Q1と第1のダイオードD1との接続点と交流入力電源の第1の入力端P11との間にインダクタL1が挿入されている。インダクタは、第2のスイッチング素子Q2と第2のダイオードD2との接続点と交流入力電源の第2の入力端P12との間に挿入されていてもよい。また、両方のラインに挿入されていてもよい。

【0020】

第1の入力端P11と第2の入力端P12との間には、入力電圧を検出する入力電圧検出回路11が設けられている。この入力電圧検出回路11が本発明に係る「入力電圧検出手段」に相当する。

【0021】

二つの出力端P21,P22に対してコンデンサC1による平滑回路が並列接続されている。

出力端P21とP22との間には、出力電圧を検出する出力電圧検出回路12が設けられている。この出力電圧検出回路12が本発明に係る「出力電圧検出手段」に相当する。

【0022】

第1のスイッチング素子Q1には第1の電流検出抵抗Rs1が直列接続されている。また、第2のスイッチング素子Q2には第2の電流検出抵抗Rs2が直列接続されている。

【0023】

第1のスイッチング素子Q1に流れる電流が正方向であるときの第1の電流検出抵抗Rs1の降下電圧が順方向となる向きに第1のダイオードDs1が接続されている。また、第2のスイッチング素子Q2に流れる電流が正方向であるときの第2の電流検出抵抗Rs2の降下電圧が順方向となる向きに第2のダイオードDs2が接続されている。

【0024】

PFC制御IC30は、第1のスイッチング素子Q1及び第2のスイッチング素子Q2のゲートに対してゲート制御電圧を出力する。このPFC制御IC30が、本発明に係るスイッチング制御手段に相当する。

【0025】

図3は、前記スイッチング電源装置101のPFC制御ICの構成をブロック化して表した図である。

図3おいて、加算要素31は、出力電圧目標値Vrefに対する出力電圧検出値Voの誤差evを求める。出力電圧誤差増幅器32は、誤差evに対して所定の比例係数を乗じて電流基準振幅値Vmを求める。この出力電圧誤差増幅器32は、本発明に係る「電圧補償手段」に相当する。乗算器33は、電流基準振幅値Vmに対して入力電圧検出値Viを乗じて正弦波状の電流基準値irefを求める。この乗算器33が本発明に係る「正弦波状の電流基準値(信号)を生成する手段」に相当する。

【0026】

インダクタ電流検出器37Aは、電流検出信号Vrs1からインダクタ電流に対応する電圧を生成する。これは、時定数をもって減少する信号を生成することによりスイッチング素子Q1のオフ時にインダクタL1に流れる電流の波形を生成し、このインダクタ電流信号V(iL)1を生成する。

【0027】

同様に、インダクタ電流検出器37Bは、電流検出信号Vrs2からインダクタ電流に対応する電圧を生成する。これは、時定数をもって減少する信号を生成することによりスイッチング素子Q2のオフ時にインダクタL1に流れる電流の波形を生成し、このインダクタ電流信号V(iL)2を生成する。

【0028】

前記インダクタ電流検出器37A、図2中の電流検出抵抗Rs1、及びダイオードDs1で、本発明に係る「第1のインダクタ電流検出手段」を構成している。同様に、前記インダクタ電流検出器37B、図2中の電流検出抵抗Rs2、及びダイオードDs2で、本発明に係る「第2のインダクタ電流検出手段」を構成している。

【0029】

加算要素34Aは、電流基準値irefに対するインダクタ電流信号V(iL)1の差分である入力電流誤差値ei1を求める。入力電流誤差増幅器35Aは入力電流誤差値ei1を増幅してパルス生成器に対する変調信号D1を発生する。パルス生成器36Aは前記変調信号D1に基づいて、スイッチング素子Q1のゲート制御電圧Qg1を出力する。このパルス生成器36Aは、本発明に係る「第1のPWM制御手段」に相当する。

【0030】

加算要素34Bは、電流基準値irefに対するインダクタ電流信号V(iL)2の差分である入力電流誤差値ei2を求める。入力電流誤差増幅器35Bは入力電流誤差値ei2を増幅してパルス生成器に対する変調信号D2を発生する。パルス生成器36Bは前記変調信号D2に基づいて、スイッチング素子Q2のゲート制御電圧Qg2を出力する。このパルス生成器36Bは、本発明に係る「第2のPWM制御手段」に相当する。

【0031】

このように、PFC制御IC30は、入力電圧検出回路11、第1の電流検出抵抗Rs1、第2の電流検出抵抗Rs2及び出力電圧検出回路12の検出信号に基づいて、商用交流電源ACから入力される入力電流iacが交流入力電源電圧Vacに対して相似形になり、且つ出力電圧が一定になるようにスイッチング素子Q1,Q2をオン/オフ制御する。

【0032】

図4は、図2に示したスイッチング電源装置101の4つのタイミングでの電流経路を示す図である。

図4(A)は、交流入力電圧の正の半サイクルで、スイッチング素子Q1,Q2が共にオン状態であるときの電流経路、図4(B)は、交流入力電圧の正の半サイクルで、スイッチング素子Q1がオフ状態、スイッチング素子Q2がオン状態であるときの電流経路である。

【0033】

また、図4(C)は、交流入力電圧の負の半サイクルで、スイッチング素子Q1,Q2が共にオン状態であるときの電流経路、図4(D)は、交流入力電圧の負の半サイクルで、スイッチング素子Q2がオフ状態、スイッチング素子Q1がオン状態であるときの電流経路である。

【0034】

交流入力電圧の正の半サイクルで、Q1,Q2がオン状態であるとき、図4(A)に示す経路で電流が流れて、インダクタL1に励磁エネルギーが蓄積され、Q1がオフ状態であるとき、図4(B)に示す経路で電流が流れて、インダクタL1から励磁エネルギーが放出される。このとき、Q2のボディダイオードにも電流が流れるが、Q2がオン状態となることにより、大半はQ2を流れて、Q2のボディダイオードによる損失は小さい。

【0035】

同様に、交流入力電源の負の半サイクルで、Q1,Q2がオン状態であるとき、図4(C)に示す経路で電流が流れて、インダクタL1に励磁エネルギーが蓄積され、Q1がオフ状態であるとき、図4(D)に示すタイミングで、インダクタL1から励磁エネルギーが放出される。このとき、Q1のボディダイオードにも電流が流れるが、Q1がオン状態となることにより、大半はQ1を流れて、Q1のボディダイオードによる損失は小さい。

【0036】

図5(A),図5(B)は、電流連続モードで制御が行われている状態におけるスイッチング電源装置101の電圧・電流の波形図である。

図5(A)は商用交流電圧の正の半サイクルでの波形図、図5(B)は商用交流電圧の負の半サイクルでの波形図である。図中の信号名は図2中に示した信号名に対応している。

【0037】

先ず、交流入力電圧の正の半サイクルでの動作は次のとおりである。

図5(A)に表れているように、交流入力電圧の正の半サイクルで、スイッチング素子Q1のオン期間に、インダクタL1に励磁エネルギーが蓄積される。この期間に第1のダイオードDs1からの出力電圧である電流検出信号Vrs1の波形は、インダクタL1に流れる電流波形と相似形となる。電流検出信号Vrs1が、電流基準値を表す電圧V(iref)に達したとき、ゲート制御電圧Qg1がローレベルになってスイッチング素子Q1はターンオフされる。このことによってスイッチング素子Q1のオンデューティが制御される。

【0038】

一方、この期間に電流検出抵抗Rs2には逆方向に電流が流れるので、第2のダイオードDs2はオフのままであり、第2のダイオードDs2の出力電圧である電流検出信号Vrs2は0Vである。そのため、電流検出信号Vrs2は、電流基準値であるV(iref)に達することなく、ゲート制御電圧Qg2はハイレベルを保つ。なお、図5(A)においては、ゲート制御電圧Qg2が短時間だけローレベルになっているが、これはPFC制御ICの最大デューティの制限によるものである。

【0039】

交流入力電圧の正の半サイクルで、スイッチング素子Q1のオフ期間では、インダクタL1から励磁エネルギーが放出される。この期間は電流検出抵抗Rs1に電流が流れないので、第1のダイオードDs1の出力電圧である電流検出信号Vrs1は0Vである。一方、この期間の第2のダイオードDs2の出力電圧である電流検出信号Vrs2は、やはり0Vである。

【0040】

このように、スイッチング素子Q1がオンのときもオフのときも、スイッチング素子Q2はオン状態となる。そのため、既に述べたように、Q2のボディダイオードによる損失は小さい。

【0041】

次に、交流入力電圧の負の半サイクルでの動作は次のとおりである。

図5(B)に表れているように、交流入力電圧の負の半サイクルで、スイッチング素子Q2のオン期間に、インダクタL1に負方向の励磁エネルギーが蓄積される。この期間の第2のダイオードDs2の出力電圧である電流検出信号Vrs2の波形は、インダクタL1に流れる電流波形の極性を反転した波形と相似形となる。電流検出信号Vrs2が、電流基準値を表す電圧V(iref)に達したとき、ゲート制御電圧Qg2がローレベルになってスイッチング素子Q2はターンオフされる。このことによってスイッチング素子Q2のオンデューティが制御される。

【0042】

一方、この期間に電流検出抵抗Rs1には逆方向に電流が流れるので、第1のダイオードDs1はオフのままであり、第1のダイオードDs1の出力電圧である電流検出信号Vrs1は0Vである。そのため、電流検出信号Vrs1は、電流基準値であるV(iref)に達することなく、ゲート制御電圧Qg1はハイレベルを保つ。なお、図5(B)においては、PFC制御ICの最大デューティの制限により、ゲート制御電圧Qg1が短時間だけローレベルになっている。

【0043】

交流入力電圧の負の半サイクルで、スイッチング素子Q2のオフ期間では、インダクタL1から励磁エネルギーが放出される。この期間は電流検出抵抗Rs2に電流が流れないので、第2のダイオードDs2の出力電圧である電流検出信号Vrs2は0Vである。一方、この期間の第1のダイオードDs1の出力電圧である電流検出信号Vrs1は、やはり0Vである。

【0044】

このように、スイッチング素子Q2がオンのときもオフのときも、スイッチング素子Q1がオンとなる。そのため、既に述べたように、Q1のボディダイオードによる損失は小さい。

【0045】

《第2の実施形態》

第2の実施形態に係るスイッチング電源装置について、図6,図7を参照して説明する。

図6は第2の実施形態に係るスイッチング電源装置102の回路図である。第1の実施形態で図2に示したスイッチング電源装置101と異なるのは、スイッチング素子Q1,Q2のソースに電流検出抵抗ではなくカレントトランスCT1,CT2を挿入した点である。カレントトランスCT1の2次側には、スイッチング素子Q1に流れる電流が正方向であるときにカレントトランスCT1の出力電圧が順方向となる向きにダイオードDs1及び抵抗Rs1が接続されている。また、カレントトランスCT2の2次側には、スイッチング素子Q2に流れる電流が正方向であるときにカレントトランスCT2の出力電圧が順方向となる向きにダイオードDs2及び抵抗Rs2が接続されている。

【0046】

図7(A),図7(B)は、電流連続モードで制御が行われている状態におけるスイッチング電源装置102の電圧・電流の波形図である。

カレントトランスCT1,CT2は直流成分(低周波の成分)が2次側に現れないので、PFC制御IC30に入力される電流検出信号Vrs1,Vrs2の波形は、最低電圧が0V電圧にレベルシフトされた波形となる。

【0047】

交流入力電源の正の半サイクルでは、スイッチング素子Q1のオン期間の電流検出信号Vrs1の波形は、インダクタL1に流れる電流波形と相似形となり、電流基準値であるV(iref)に達したとき、ゲート制御電圧Qg1がローレベルになってスイッチング素子Q1はターンオフされる。このことによってスイッチング素子Q1のオンデューティが制御される。電流検出信号Vrs2は、カレントトランスCT2により直流成分がカットされるため、電流基準値を表す電圧V(iref)より常に下回ることになり、スイッチング素子Q2に対するゲート制御電圧Qg2はハイレベルを保つ。すなわち、スイッチング素子Q2はオン状態を保つ。スイッチング素子Q1のオフ期間には、インダクタ電流平均値検出器37Aにより時定数をもって減少する信号が生成される。スイッチング素子Q2は、電流検出信号Vrs2が電圧基準値を表す電圧V(iref)より常に下回ることになり、オン状態を保つ。

【0048】

このように、スイッチング素子Q1がオンのときもオフのときも、スイッチング素子Q2はオン状態となるため、Q2のボディダイオードによる損失は小さい。

【0049】

交流入力電源の負の半サイクルでは、スイッチング素子Q1とQ2が正の半サイクルと逆になり、電流検出信号Vrs1は電流基準値を表す電圧V(iref)より常に下回ることになり、スイッチング素子Q1に対するゲート制御電圧Qg1はハイレベルを保つ。すなわち、スイッチング素子Q1はオン状態を保つ。

【0050】

このように、スイッチング素子Q2がオンのときもオフのときも、スイッチング素子Q1がオンとなるため、Q1のボディダイオードによる損失は小さい。

【0051】

なお、図3に示したPFC制御ICは、元々インターリーブ方式用の制御ICとして市販されている(例えばテキサスインスツルメンツ製ICUCC28070 である)。ここで、インターリーブ方式のスイッチング電源装置の例を図8に示す。図8に示すスイッチング電源装置において、商用交流電源ACの交流入力電圧Vacを整流するダイオードブリッジB1の出力両端には、インダクタL11とスイッチング素子Q11とカレントトランスCT1とからなる直列回路、及びインダクタL12とスイッチング素子Q12とカレントトランスCT2とからなるもう一つの直列回路が接続されている。スイッチング素子Q11とインダクタL11との接続点と平滑コンデンサCoとの間にダイオードD11が接続され、スイッチング素子Q12とインダクタL12との接続点と平滑コンデンサCoとの間にダイオードD12が接続されている。平滑コンデンサCoの両端には負荷20が接続される。

【0052】

PFC制御IC30は、カレントトランスCT1,CT2の出力信号を受けて、スイッチング素子Q11,Q12を位相差180で交互に(インターリーブ方式で)オン/オフする。

【0053】

このようなインターリーブ方式用のPFC制御IC30には、図3に示したとおり、インダクタ電流を検出し、入力電流誤差に応じたパルス幅のゲート制御電圧を発生する回路を2系統備えている。

【0054】

本発明は、前記インターリーブ方式用のPFC制御ICを用い、スイッチング素子Q1,Q2のうち、電流が正方向に流れるスイッチング素子の電流値を、そのスイッチング素子に流れる実際の電流値としてそのまま検出し、電流が負方向に流れるスイッチング素子の電流値を、そのスイッチング素子に流れる実際の電流値より小さく(低く)検出するようにインダクタ電流検出手段を構成することで、スイッチング制御回路を複雑化することなくブリッジレスPFCコンバータを構成でき、しかもスイッチング素子のボディダイオードによる損失を低減したスイッチング電源装置が得られる。

【符号の説明】

【0055】

AC…商用交流電源

B1…ダイオードブリッジ

CT1,CT2…カレントトランス

D1,D2…ダイオード

Ds1…第1のダイオード

Ds2…第2のダイオード

ei1…入力電流誤差値

ei2…入力電流誤差値

L1…インダクタ

P11…第1の入力端

P12…第2の入力端

P21,P22…出力端

Q1…第1のスイッチング素子

Q2…第2のスイッチング素子

Qg1,Qg2…ゲート制御電圧

Rs1…第1の電流検出抵抗

Rs2…第2の電流検出抵抗

11…入力電圧検出回路

12…出力電圧検出回路

20…負荷

31…加算要素

32…出力電圧誤差増幅器

33…乗算器

34A,34B…加算要素

35A,35B…入力電流誤差増幅器

36A,36B…パルス生成器

37A,37B…インダクタ電流平均値検出器

101,102…スイッチング電源装置

【技術分野】

【0001】

本発明はスイッチング電源装置に関し、特に整流ブリッジ回路を設けないブリッジレスPFCとして作用するスイッチング電源装置に関するものである。

【背景技術】

【0002】

商用交流電源が入力されて、スイッチング電源装置の力率を改善するPFCコンバータは、例えば特許文献2,3に開示されている。特許文献2,3のPFCコンバータは、商用交流電源を入力して全波整流するダイオードブリッジと、その全波整流電圧を入力する昇圧チョッパー回路とで構成されている。

【0003】

ここで、ダイオードブリッジと昇圧チョッパー回路とで構成されているPFCコンバータ動作するスイッチング電源装置の構成例を図1に示す。

図1に示すスイッチング電源装置において、商用交流電源ACの交流入力電圧Vacを整流するダイオードブリッジB1の出力両端には、インダクタL1とスイッチング素子Q1と電流検出抵抗Rsとからなる直列回路が接続されている。スイッチング素子Q1の両端には、ダイオードD1と平滑コンデンサC1とからなる直列回路が接続され、平滑コンデンサC1の両端には、負荷20が接続されている。スイッチング素子Q1は、PFC制御IC10のPWM制御によりオン/オフする。電流検出抵抗Rsは、ダイオードブリッジB1に流れる入力電流を検出する。

【0004】

PFC制御IC10は、ダイオードブリッジB1に流れる電流と入力電圧波形とを比較し、また出力電圧を参照して、それらに応じたデューティパルスをスイッチング素子Q1に与える。このような構成により、交流電源電流波形が交流電源電圧波形に相似形になり、且つ出力電圧が一定になるように制御されて、力率が改善される。

【0005】

一方、特許文献1に開示されているように、整流ブリッジ回路にスイッチング素子を組み込んだ回路も知られている。このように、ダイオードブリッジ回路を設けない構成であると、ダイオードブリッジ回路で損失が生じないので、その分の電力損失が低減できる、という利点がある。

【先行技術文献】

【特許文献】

【0006】

【特許文献1】特表2007−527687号公報

【特許文献2】特開平10−94246号公報

【特許文献3】特開2000−139079号公報

【発明の概要】

【発明が解決しようとする課題】

【0007】

しかし、整流ブリッジ回路にスイッチング素子を組み込んだ回路では、スイッチング素子の制御が単純ではなく、制御回路が複雑になる欠点がある。多く市販されているPFC制御ICは特許文献2,3のようにワンサイクル制御を行うものであり、これらのPFC制御ICでブリッジレスPFCのスイッチング素子を制御するのは困難であった。

【0008】

特許文献1のPFCコンバータでは、ワンサイクル制御回路によって二つのスイッチング素子を制御するようにしたものであるが、この構成では、スイッチング素子での損失が必ずしも小さくはないという課題がある。

【0009】

すなわち、二つのスイッチング素子に対して並列接続されているダイオード(ボディダイオード)は商用交流電源周期の半周期において常に導通することになるが、従来のワンサイクル制御を行うPFC制御ICを用いると、2つのスイッチング素子が同じようにオンオフしてしまう。そのため、ボディダイオードのみ通して通電される期間が生じ、ボディダイオードでの損失が大きくなる、という課題がある。

【0010】

この発明の目的は、ダイオードブリッジを設けることなく、且つスイッチング制御回路を複雑化することなく、全体の電力損失を低減したスイッチング電源装置を提供することにある。

【課題を解決するための手段】

【0011】

前記課題を解決するために、この発明のスイッチング電源装置は次のように構成する。

この発明のスイッチング電源装置は、

二つの出力端に対して並列に接続された、第1のスイッチング素子と第1の整流素子を含む第1の直列回路と、

前記二つの出力端に対して並列に接続された、第2のスイッチング素子と第2の整流素子を含む第2の直列回路と、

前記第1のスイッチング素子と前記第1の整流素子との接続点と交流入力電源の第1の入力端との間、若しくは前記第2のスイッチング素子と前記第2の整流素子との接続点と交流入力電源の第2の入力端との間、の何れか一方又は両方に挿入されたインダクタと、

前記二つの出力端に対して並列に接続された平滑回路と、

前記交流入力電源の第1の入力端と第2の入力端との間に入力される入力電圧を検出する入力電圧検出手段と、

前記二つの出力端に出力される出力電圧を検出する出力電圧検出手段と、

前記インダクタに流れる電流の平均値が前記入力電圧に対して相似形となるように前記第1のスイッチング素子及び前記第2のスイッチング素子を制御するスイッチング制御手段とを備え、

前記スイッチング制御手段は、前記出力電圧検出手段の検出信号を入力して、出力電圧を目標値に安定化する電圧補償手段と、前記入力電圧検出手段の検出信号を入力して、正弦波状の電流基準値を生成する手段と、前記第1のスイッチング素子に流れる電流検出信号に基づいてインダクタ電流を検出する第1のインダクタ電流検出手段と、前記第2のスイッチング素子に流れる電流検出信号に基づいてインダクタ電流を検出する第2のインダクタ電流検出手段と、前記電流基準値及び第1のインダクタ電流検出手段による検出値に基づいて第1のスイッチング素子のオンデューティを制御する第1のPWM制御手段と、前記電流基準値及び第2のインダクタ電流検出手段による検出値に基づいて第2のスイッチング素子のオンデューティを制御する第2のPWM制御手段と、を備えるとともに、

前記第1のインダクタ電流検出手段及び第2のインダクタ電流検出手段は、前記第1のスイッチング素子又は第2のスイッチング素子のうち、電流が正方向に流れるスイッチング素子の電流値を、当該スイッチング素子に流れる実際の電流値として(そのまま)検出し、電流が負方向に流れるスイッチング素子の電流値を、当該スイッチング素子に流れる実際の電流値より小さく(低く)検出することを特徴とする。

例えば、前記第1のインダクタ電流検出手段は、前記第1のスイッチング素子に直列接続された第1の電流検出抵抗と、前記第1のスイッチング素子に流れる電流が正方向であるときの前記第1の電流検出抵抗の降下電圧が順方向となる向きに接続された第1のダイオードを含み、

前記第2のインダクタ電流検出手段は、前記第2のスイッチング素子に直列接続された第2の電流検出抵抗と、前記第2のスイッチング素子に流れる電流が正方向であるときの前記第2の電流検出抵抗の降下電圧が順方向となる向きに接続された第2のダイオードを含んで構成される。

【0012】

また例えば、前記第1のインダクタ電流検出手段は、前記第1のスイッチング素子に接続された第1のカレントトランスと、前記第1のスイッチング素子に流れる電流が正方向であるときの前記第1のカレントトランスの出力電圧が順方向となる向きに接続された第1のダイオードとで構成され、

前記第2のインダクタ電流検出手段は、前記第2のスイッチング素子に接続された第2のカレントトランスと、前記第2のスイッチング素子に流れる電流が正方向であるときの前記第2のカレントトランスの出力電圧が順方向となる向きに接続された第2のダイオードとで構成される。

【0013】

また例えば、前記スイッチング制御手段は、インターリーブPFC用の制御ICで構成する。

【発明の効果】

【0014】

この発明によれば、スイッチング制御回路が複雑化することなくブリッジレスPFCコンバータを構成でき、しかもスイッチング素子のボディダイオードによる損失を低減したスイッチング電源装置が得られる。

【図面の簡単な説明】

【0015】

【図1】ダイオードブリッジと昇圧チョッパー回路とで構成されて、PFCコンバータ動作する従来のスイッチング電源装置の回路図である。

【図2】第1の実施形態に係るスイッチング電源装置101の回路図である。

【図3】スイッチング電源装置101のPFC制御ICの構成をブロック化して表した図である。

【図4】図2に示したスイッチング電源装置101の4つのタイミングでの電流経路を示す図である。

【図5】電流連続モードで制御が行われている状態におけるスイッチング電源装置101の電圧・電流の波形図であり、図5(A)は正の半サイクルでの波形、図5(B)は負の半サイクルでの波形である。

【図6】第2の実施形態に係るスイッチング電源装置102の回路図である。

【図7】電流連続モードで制御が行われている状態におけるスイッチング電源装置102の電圧・電流の波形図であり、図7(A)は正の半サイクルでの波形図、図7(B)は負の半サイクルでの波形図である。

【図8】従来のインターリーブ方式のスイッチング電源装置の回路図である。

【発明を実施するための形態】

【0016】

《第1の実施形態》

第1の実施形態に係るスイッチング電源装置について、図2〜図5を参照して説明する。

図2は第1の実施形態に係るスイッチング電源装置101の回路図である。図2において第1の入力端P11と第2の入力端P12に商用交流電源ACが接続され、交流入力電圧Vacが入力される。また、出力端P21,P22に負荷20が接続され、所定の直流電圧が負荷20へ出力される。

【0017】

負荷20は例えばDC−DCコンバータ及びそのDC−DCコンバータによって電源供給を受ける電子機器の回路である。

【0018】

このスイッチング電源装置101の入力段には、交流入力電圧Vacを全波整流するダイオードブリッジが設けられていない。

第1のスイッチング素子Q1と第1のダイオードD1(本発明に係る「第1の整流素子」)を含む第1の直列回路が、二つの出力端P21,P22に対して並列接続されている。また、第2のスイッチング素子Q2と第2のダイオードD2(本発明に係る「第2の整流素子」)を含む第2の直列回路が、二つの出力端P21,P22に対して並列接続されている。

【0019】

第1のスイッチング素子Q1と第1のダイオードD1との接続点と交流入力電源の第1の入力端P11との間にインダクタL1が挿入されている。インダクタは、第2のスイッチング素子Q2と第2のダイオードD2との接続点と交流入力電源の第2の入力端P12との間に挿入されていてもよい。また、両方のラインに挿入されていてもよい。

【0020】

第1の入力端P11と第2の入力端P12との間には、入力電圧を検出する入力電圧検出回路11が設けられている。この入力電圧検出回路11が本発明に係る「入力電圧検出手段」に相当する。

【0021】

二つの出力端P21,P22に対してコンデンサC1による平滑回路が並列接続されている。

出力端P21とP22との間には、出力電圧を検出する出力電圧検出回路12が設けられている。この出力電圧検出回路12が本発明に係る「出力電圧検出手段」に相当する。

【0022】

第1のスイッチング素子Q1には第1の電流検出抵抗Rs1が直列接続されている。また、第2のスイッチング素子Q2には第2の電流検出抵抗Rs2が直列接続されている。

【0023】

第1のスイッチング素子Q1に流れる電流が正方向であるときの第1の電流検出抵抗Rs1の降下電圧が順方向となる向きに第1のダイオードDs1が接続されている。また、第2のスイッチング素子Q2に流れる電流が正方向であるときの第2の電流検出抵抗Rs2の降下電圧が順方向となる向きに第2のダイオードDs2が接続されている。

【0024】

PFC制御IC30は、第1のスイッチング素子Q1及び第2のスイッチング素子Q2のゲートに対してゲート制御電圧を出力する。このPFC制御IC30が、本発明に係るスイッチング制御手段に相当する。

【0025】

図3は、前記スイッチング電源装置101のPFC制御ICの構成をブロック化して表した図である。

図3おいて、加算要素31は、出力電圧目標値Vrefに対する出力電圧検出値Voの誤差evを求める。出力電圧誤差増幅器32は、誤差evに対して所定の比例係数を乗じて電流基準振幅値Vmを求める。この出力電圧誤差増幅器32は、本発明に係る「電圧補償手段」に相当する。乗算器33は、電流基準振幅値Vmに対して入力電圧検出値Viを乗じて正弦波状の電流基準値irefを求める。この乗算器33が本発明に係る「正弦波状の電流基準値(信号)を生成する手段」に相当する。

【0026】

インダクタ電流検出器37Aは、電流検出信号Vrs1からインダクタ電流に対応する電圧を生成する。これは、時定数をもって減少する信号を生成することによりスイッチング素子Q1のオフ時にインダクタL1に流れる電流の波形を生成し、このインダクタ電流信号V(iL)1を生成する。

【0027】

同様に、インダクタ電流検出器37Bは、電流検出信号Vrs2からインダクタ電流に対応する電圧を生成する。これは、時定数をもって減少する信号を生成することによりスイッチング素子Q2のオフ時にインダクタL1に流れる電流の波形を生成し、このインダクタ電流信号V(iL)2を生成する。

【0028】

前記インダクタ電流検出器37A、図2中の電流検出抵抗Rs1、及びダイオードDs1で、本発明に係る「第1のインダクタ電流検出手段」を構成している。同様に、前記インダクタ電流検出器37B、図2中の電流検出抵抗Rs2、及びダイオードDs2で、本発明に係る「第2のインダクタ電流検出手段」を構成している。

【0029】

加算要素34Aは、電流基準値irefに対するインダクタ電流信号V(iL)1の差分である入力電流誤差値ei1を求める。入力電流誤差増幅器35Aは入力電流誤差値ei1を増幅してパルス生成器に対する変調信号D1を発生する。パルス生成器36Aは前記変調信号D1に基づいて、スイッチング素子Q1のゲート制御電圧Qg1を出力する。このパルス生成器36Aは、本発明に係る「第1のPWM制御手段」に相当する。

【0030】

加算要素34Bは、電流基準値irefに対するインダクタ電流信号V(iL)2の差分である入力電流誤差値ei2を求める。入力電流誤差増幅器35Bは入力電流誤差値ei2を増幅してパルス生成器に対する変調信号D2を発生する。パルス生成器36Bは前記変調信号D2に基づいて、スイッチング素子Q2のゲート制御電圧Qg2を出力する。このパルス生成器36Bは、本発明に係る「第2のPWM制御手段」に相当する。

【0031】

このように、PFC制御IC30は、入力電圧検出回路11、第1の電流検出抵抗Rs1、第2の電流検出抵抗Rs2及び出力電圧検出回路12の検出信号に基づいて、商用交流電源ACから入力される入力電流iacが交流入力電源電圧Vacに対して相似形になり、且つ出力電圧が一定になるようにスイッチング素子Q1,Q2をオン/オフ制御する。

【0032】

図4は、図2に示したスイッチング電源装置101の4つのタイミングでの電流経路を示す図である。

図4(A)は、交流入力電圧の正の半サイクルで、スイッチング素子Q1,Q2が共にオン状態であるときの電流経路、図4(B)は、交流入力電圧の正の半サイクルで、スイッチング素子Q1がオフ状態、スイッチング素子Q2がオン状態であるときの電流経路である。

【0033】

また、図4(C)は、交流入力電圧の負の半サイクルで、スイッチング素子Q1,Q2が共にオン状態であるときの電流経路、図4(D)は、交流入力電圧の負の半サイクルで、スイッチング素子Q2がオフ状態、スイッチング素子Q1がオン状態であるときの電流経路である。

【0034】

交流入力電圧の正の半サイクルで、Q1,Q2がオン状態であるとき、図4(A)に示す経路で電流が流れて、インダクタL1に励磁エネルギーが蓄積され、Q1がオフ状態であるとき、図4(B)に示す経路で電流が流れて、インダクタL1から励磁エネルギーが放出される。このとき、Q2のボディダイオードにも電流が流れるが、Q2がオン状態となることにより、大半はQ2を流れて、Q2のボディダイオードによる損失は小さい。

【0035】

同様に、交流入力電源の負の半サイクルで、Q1,Q2がオン状態であるとき、図4(C)に示す経路で電流が流れて、インダクタL1に励磁エネルギーが蓄積され、Q1がオフ状態であるとき、図4(D)に示すタイミングで、インダクタL1から励磁エネルギーが放出される。このとき、Q1のボディダイオードにも電流が流れるが、Q1がオン状態となることにより、大半はQ1を流れて、Q1のボディダイオードによる損失は小さい。

【0036】

図5(A),図5(B)は、電流連続モードで制御が行われている状態におけるスイッチング電源装置101の電圧・電流の波形図である。

図5(A)は商用交流電圧の正の半サイクルでの波形図、図5(B)は商用交流電圧の負の半サイクルでの波形図である。図中の信号名は図2中に示した信号名に対応している。

【0037】

先ず、交流入力電圧の正の半サイクルでの動作は次のとおりである。

図5(A)に表れているように、交流入力電圧の正の半サイクルで、スイッチング素子Q1のオン期間に、インダクタL1に励磁エネルギーが蓄積される。この期間に第1のダイオードDs1からの出力電圧である電流検出信号Vrs1の波形は、インダクタL1に流れる電流波形と相似形となる。電流検出信号Vrs1が、電流基準値を表す電圧V(iref)に達したとき、ゲート制御電圧Qg1がローレベルになってスイッチング素子Q1はターンオフされる。このことによってスイッチング素子Q1のオンデューティが制御される。

【0038】

一方、この期間に電流検出抵抗Rs2には逆方向に電流が流れるので、第2のダイオードDs2はオフのままであり、第2のダイオードDs2の出力電圧である電流検出信号Vrs2は0Vである。そのため、電流検出信号Vrs2は、電流基準値であるV(iref)に達することなく、ゲート制御電圧Qg2はハイレベルを保つ。なお、図5(A)においては、ゲート制御電圧Qg2が短時間だけローレベルになっているが、これはPFC制御ICの最大デューティの制限によるものである。

【0039】

交流入力電圧の正の半サイクルで、スイッチング素子Q1のオフ期間では、インダクタL1から励磁エネルギーが放出される。この期間は電流検出抵抗Rs1に電流が流れないので、第1のダイオードDs1の出力電圧である電流検出信号Vrs1は0Vである。一方、この期間の第2のダイオードDs2の出力電圧である電流検出信号Vrs2は、やはり0Vである。

【0040】

このように、スイッチング素子Q1がオンのときもオフのときも、スイッチング素子Q2はオン状態となる。そのため、既に述べたように、Q2のボディダイオードによる損失は小さい。

【0041】

次に、交流入力電圧の負の半サイクルでの動作は次のとおりである。

図5(B)に表れているように、交流入力電圧の負の半サイクルで、スイッチング素子Q2のオン期間に、インダクタL1に負方向の励磁エネルギーが蓄積される。この期間の第2のダイオードDs2の出力電圧である電流検出信号Vrs2の波形は、インダクタL1に流れる電流波形の極性を反転した波形と相似形となる。電流検出信号Vrs2が、電流基準値を表す電圧V(iref)に達したとき、ゲート制御電圧Qg2がローレベルになってスイッチング素子Q2はターンオフされる。このことによってスイッチング素子Q2のオンデューティが制御される。

【0042】

一方、この期間に電流検出抵抗Rs1には逆方向に電流が流れるので、第1のダイオードDs1はオフのままであり、第1のダイオードDs1の出力電圧である電流検出信号Vrs1は0Vである。そのため、電流検出信号Vrs1は、電流基準値であるV(iref)に達することなく、ゲート制御電圧Qg1はハイレベルを保つ。なお、図5(B)においては、PFC制御ICの最大デューティの制限により、ゲート制御電圧Qg1が短時間だけローレベルになっている。

【0043】

交流入力電圧の負の半サイクルで、スイッチング素子Q2のオフ期間では、インダクタL1から励磁エネルギーが放出される。この期間は電流検出抵抗Rs2に電流が流れないので、第2のダイオードDs2の出力電圧である電流検出信号Vrs2は0Vである。一方、この期間の第1のダイオードDs1の出力電圧である電流検出信号Vrs1は、やはり0Vである。

【0044】

このように、スイッチング素子Q2がオンのときもオフのときも、スイッチング素子Q1がオンとなる。そのため、既に述べたように、Q1のボディダイオードによる損失は小さい。

【0045】

《第2の実施形態》

第2の実施形態に係るスイッチング電源装置について、図6,図7を参照して説明する。

図6は第2の実施形態に係るスイッチング電源装置102の回路図である。第1の実施形態で図2に示したスイッチング電源装置101と異なるのは、スイッチング素子Q1,Q2のソースに電流検出抵抗ではなくカレントトランスCT1,CT2を挿入した点である。カレントトランスCT1の2次側には、スイッチング素子Q1に流れる電流が正方向であるときにカレントトランスCT1の出力電圧が順方向となる向きにダイオードDs1及び抵抗Rs1が接続されている。また、カレントトランスCT2の2次側には、スイッチング素子Q2に流れる電流が正方向であるときにカレントトランスCT2の出力電圧が順方向となる向きにダイオードDs2及び抵抗Rs2が接続されている。

【0046】

図7(A),図7(B)は、電流連続モードで制御が行われている状態におけるスイッチング電源装置102の電圧・電流の波形図である。

カレントトランスCT1,CT2は直流成分(低周波の成分)が2次側に現れないので、PFC制御IC30に入力される電流検出信号Vrs1,Vrs2の波形は、最低電圧が0V電圧にレベルシフトされた波形となる。

【0047】

交流入力電源の正の半サイクルでは、スイッチング素子Q1のオン期間の電流検出信号Vrs1の波形は、インダクタL1に流れる電流波形と相似形となり、電流基準値であるV(iref)に達したとき、ゲート制御電圧Qg1がローレベルになってスイッチング素子Q1はターンオフされる。このことによってスイッチング素子Q1のオンデューティが制御される。電流検出信号Vrs2は、カレントトランスCT2により直流成分がカットされるため、電流基準値を表す電圧V(iref)より常に下回ることになり、スイッチング素子Q2に対するゲート制御電圧Qg2はハイレベルを保つ。すなわち、スイッチング素子Q2はオン状態を保つ。スイッチング素子Q1のオフ期間には、インダクタ電流平均値検出器37Aにより時定数をもって減少する信号が生成される。スイッチング素子Q2は、電流検出信号Vrs2が電圧基準値を表す電圧V(iref)より常に下回ることになり、オン状態を保つ。

【0048】

このように、スイッチング素子Q1がオンのときもオフのときも、スイッチング素子Q2はオン状態となるため、Q2のボディダイオードによる損失は小さい。

【0049】

交流入力電源の負の半サイクルでは、スイッチング素子Q1とQ2が正の半サイクルと逆になり、電流検出信号Vrs1は電流基準値を表す電圧V(iref)より常に下回ることになり、スイッチング素子Q1に対するゲート制御電圧Qg1はハイレベルを保つ。すなわち、スイッチング素子Q1はオン状態を保つ。

【0050】

このように、スイッチング素子Q2がオンのときもオフのときも、スイッチング素子Q1がオンとなるため、Q1のボディダイオードによる損失は小さい。

【0051】

なお、図3に示したPFC制御ICは、元々インターリーブ方式用の制御ICとして市販されている(例えばテキサスインスツルメンツ製ICUCC28070 である)。ここで、インターリーブ方式のスイッチング電源装置の例を図8に示す。図8に示すスイッチング電源装置において、商用交流電源ACの交流入力電圧Vacを整流するダイオードブリッジB1の出力両端には、インダクタL11とスイッチング素子Q11とカレントトランスCT1とからなる直列回路、及びインダクタL12とスイッチング素子Q12とカレントトランスCT2とからなるもう一つの直列回路が接続されている。スイッチング素子Q11とインダクタL11との接続点と平滑コンデンサCoとの間にダイオードD11が接続され、スイッチング素子Q12とインダクタL12との接続点と平滑コンデンサCoとの間にダイオードD12が接続されている。平滑コンデンサCoの両端には負荷20が接続される。

【0052】

PFC制御IC30は、カレントトランスCT1,CT2の出力信号を受けて、スイッチング素子Q11,Q12を位相差180で交互に(インターリーブ方式で)オン/オフする。

【0053】

このようなインターリーブ方式用のPFC制御IC30には、図3に示したとおり、インダクタ電流を検出し、入力電流誤差に応じたパルス幅のゲート制御電圧を発生する回路を2系統備えている。

【0054】

本発明は、前記インターリーブ方式用のPFC制御ICを用い、スイッチング素子Q1,Q2のうち、電流が正方向に流れるスイッチング素子の電流値を、そのスイッチング素子に流れる実際の電流値としてそのまま検出し、電流が負方向に流れるスイッチング素子の電流値を、そのスイッチング素子に流れる実際の電流値より小さく(低く)検出するようにインダクタ電流検出手段を構成することで、スイッチング制御回路を複雑化することなくブリッジレスPFCコンバータを構成でき、しかもスイッチング素子のボディダイオードによる損失を低減したスイッチング電源装置が得られる。

【符号の説明】

【0055】

AC…商用交流電源

B1…ダイオードブリッジ

CT1,CT2…カレントトランス

D1,D2…ダイオード

Ds1…第1のダイオード

Ds2…第2のダイオード

ei1…入力電流誤差値

ei2…入力電流誤差値

L1…インダクタ

P11…第1の入力端

P12…第2の入力端

P21,P22…出力端

Q1…第1のスイッチング素子

Q2…第2のスイッチング素子

Qg1,Qg2…ゲート制御電圧

Rs1…第1の電流検出抵抗

Rs2…第2の電流検出抵抗

11…入力電圧検出回路

12…出力電圧検出回路

20…負荷

31…加算要素

32…出力電圧誤差増幅器

33…乗算器

34A,34B…加算要素

35A,35B…入力電流誤差増幅器

36A,36B…パルス生成器

37A,37B…インダクタ電流平均値検出器

101,102…スイッチング電源装置

【特許請求の範囲】

【請求項1】

二つの出力端に対して並列に接続された、第1のスイッチング素子と第1の整流素子を含む第1の直列回路と、

前記二つの出力端に対して並列に接続された、第2のスイッチング素子と第2の整流素子を含む第2の直列回路と、

前記第1のスイッチング素子と前記第1の整流素子との接続点と交流入力電源の第1の入力端との間、若しくは前記第2のスイッチング素子と前記第2の整流素子との接続点と交流入力電源の第2の入力端との間、の何れか一方又は両方に挿入されたインダクタと、

前記二つの出力端に対して並列に接続された平滑回路と、

前記交流入力電源の第1の入力端と第2の入力端との間に入力される入力電圧を検出する入力電圧検出手段と、

前記二つの出力端に出力される出力電圧を検出する出力電圧検出手段と、

前記インダクタに流れる電流の平均値が前記入力電圧に対して相似形となるように前記第1のスイッチング素子及び前記第2のスイッチング素子を制御するスイッチング制御手段と、を備えたスイッチング電源装置であって、

前記スイッチング制御手段は、前記出力電圧検出手段の検出信号を入力して、出力電圧を目標値に安定化する電圧補償手段と、前記入力電圧検出手段の検出信号を入力して、正弦波状の電流基準値を生成する手段と、前記第1のスイッチング素子に流れる電流検出信号に基づいてインダクタ電流を検出する第1のインダクタ電流検出手段と、前記第2のスイッチング素子に流れる電流検出信号に基づいてインダクタ電流を検出する第2のインダクタ電流検出手段と、前記電流基準値及び第1のインダクタ電流検出手段による検出値に基づいて第1のスイッチング素子のオンデューティを制御する第1のPWM制御手段と、前記電流基準値及び第2のインダクタ電流検出手段による検出値に基づいて第2のスイッチング素子のオンデューティを制御する第2のPWM制御手段と、を備えるとともに、

前記第1のインダクタ電流検出手段及び第2のインダクタ電流検出手段は、前記第1のスイッチング素子又は第2のスイッチング素子のうち、電流が正方向に流れるスイッチング素子の電流値を、当該スイッチング素子に流れる実際の電流値として検出し、電流が負方向に流れるスイッチング素子の電流値を、当該スイッチング素子に流れる実際の電流値より小さく検出することを特徴とするスイッチング電源装置。

【請求項2】

前記第1のインダクタ電流検出手段は、前記第1のスイッチング素子に直列接続された第1の電流検出抵抗と、前記第1のスイッチング素子に流れる電流が正方向であるときの前記第1の電流検出抵抗の降下電圧が順方向となる向きに接続された第1のダイオードを含み、

前記第2のインダクタ電流検出手段は、前記第2のスイッチング素子に直列接続された第2の電流検出抵抗と、前記第2のスイッチング素子に流れる電流が正方向であるときの前記第2の電流検出抵抗の降下電圧が順方向となる向きに接続された第2のダイオードを含んで構成された、請求項1に記載のスイッチング電源装置。

【請求項3】

前記第1のインダクタ電流検出手段は、前記第1のスイッチング素子に接続された第1のカレントトランスと、前記第1のスイッチング素子に流れる電流が正方向であるときの前記第1のカレントトランスの出力電圧が順方向となる向きに接続された第1のダイオードとで構成され、

前記第2のインダクタ電流検出手段は、前記第2のスイッチング素子に接続された第2のカレントトランスと、前記第2のスイッチング素子に流れる電流が正方向であるときの前記第2のカレントトランスの出力電圧が順方向となる向きに接続された第2のダイオードとで構成された、請求項1に記載のスイッチング電源装置。

【請求項4】

前記スイッチング制御手段はインターリーブPFC用の制御ICで構成された、請求項1乃至3の何れかに記載のスイッチング電源装置。

【請求項1】

二つの出力端に対して並列に接続された、第1のスイッチング素子と第1の整流素子を含む第1の直列回路と、

前記二つの出力端に対して並列に接続された、第2のスイッチング素子と第2の整流素子を含む第2の直列回路と、

前記第1のスイッチング素子と前記第1の整流素子との接続点と交流入力電源の第1の入力端との間、若しくは前記第2のスイッチング素子と前記第2の整流素子との接続点と交流入力電源の第2の入力端との間、の何れか一方又は両方に挿入されたインダクタと、

前記二つの出力端に対して並列に接続された平滑回路と、

前記交流入力電源の第1の入力端と第2の入力端との間に入力される入力電圧を検出する入力電圧検出手段と、

前記二つの出力端に出力される出力電圧を検出する出力電圧検出手段と、

前記インダクタに流れる電流の平均値が前記入力電圧に対して相似形となるように前記第1のスイッチング素子及び前記第2のスイッチング素子を制御するスイッチング制御手段と、を備えたスイッチング電源装置であって、

前記スイッチング制御手段は、前記出力電圧検出手段の検出信号を入力して、出力電圧を目標値に安定化する電圧補償手段と、前記入力電圧検出手段の検出信号を入力して、正弦波状の電流基準値を生成する手段と、前記第1のスイッチング素子に流れる電流検出信号に基づいてインダクタ電流を検出する第1のインダクタ電流検出手段と、前記第2のスイッチング素子に流れる電流検出信号に基づいてインダクタ電流を検出する第2のインダクタ電流検出手段と、前記電流基準値及び第1のインダクタ電流検出手段による検出値に基づいて第1のスイッチング素子のオンデューティを制御する第1のPWM制御手段と、前記電流基準値及び第2のインダクタ電流検出手段による検出値に基づいて第2のスイッチング素子のオンデューティを制御する第2のPWM制御手段と、を備えるとともに、

前記第1のインダクタ電流検出手段及び第2のインダクタ電流検出手段は、前記第1のスイッチング素子又は第2のスイッチング素子のうち、電流が正方向に流れるスイッチング素子の電流値を、当該スイッチング素子に流れる実際の電流値として検出し、電流が負方向に流れるスイッチング素子の電流値を、当該スイッチング素子に流れる実際の電流値より小さく検出することを特徴とするスイッチング電源装置。

【請求項2】

前記第1のインダクタ電流検出手段は、前記第1のスイッチング素子に直列接続された第1の電流検出抵抗と、前記第1のスイッチング素子に流れる電流が正方向であるときの前記第1の電流検出抵抗の降下電圧が順方向となる向きに接続された第1のダイオードを含み、

前記第2のインダクタ電流検出手段は、前記第2のスイッチング素子に直列接続された第2の電流検出抵抗と、前記第2のスイッチング素子に流れる電流が正方向であるときの前記第2の電流検出抵抗の降下電圧が順方向となる向きに接続された第2のダイオードを含んで構成された、請求項1に記載のスイッチング電源装置。

【請求項3】

前記第1のインダクタ電流検出手段は、前記第1のスイッチング素子に接続された第1のカレントトランスと、前記第1のスイッチング素子に流れる電流が正方向であるときの前記第1のカレントトランスの出力電圧が順方向となる向きに接続された第1のダイオードとで構成され、

前記第2のインダクタ電流検出手段は、前記第2のスイッチング素子に接続された第2のカレントトランスと、前記第2のスイッチング素子に流れる電流が正方向であるときの前記第2のカレントトランスの出力電圧が順方向となる向きに接続された第2のダイオードとで構成された、請求項1に記載のスイッチング電源装置。

【請求項4】

前記スイッチング制御手段はインターリーブPFC用の制御ICで構成された、請求項1乃至3の何れかに記載のスイッチング電源装置。

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【公開番号】特開2011−152017(P2011−152017A)

【公開日】平成23年8月4日(2011.8.4)

【国際特許分類】

【出願番号】特願2010−13332(P2010−13332)

【出願日】平成22年1月25日(2010.1.25)

【出願人】(000006231)株式会社村田製作所 (3,635)

【Fターム(参考)】

【公開日】平成23年8月4日(2011.8.4)

【国際特許分類】

【出願日】平成22年1月25日(2010.1.25)

【出願人】(000006231)株式会社村田製作所 (3,635)

【Fターム(参考)】

[ Back to top ]