スイッチング電源装置

【課題】内部素子等の個体差等の影響を容易に吸収し、所望の静的負荷変動特性を精度よく実現することができるスイッチング電源装置を提供する。

【解決手段】間接出力電圧信号V3を出力する出力電圧検出回路38と、基準電圧信号V2を出力する基準電圧信号発生回路42と、基準電圧信号V2と間接出力電圧信号V3の差分を出力する誤差増幅器44を備える。誤差増幅器44の出力を基にパルス幅変調し、駆動パルスVg22を出力する主スイッチング素子駆動回路24を備える。スイッチング電流を検出し間接出力電流信号V1を出力する出力電流検出回路48を備える。間接出力電流信号V1をオン時比率D46で断続する補正量制御回路46を備える。基準電圧信号発生回路42は、補正量制御回路46を介して間接出力電流信号V1を受け、間接出力電流信号V1の波高値及びオン時比率D46に応じて基準電圧信号V2を補正する。

【解決手段】間接出力電圧信号V3を出力する出力電圧検出回路38と、基準電圧信号V2を出力する基準電圧信号発生回路42と、基準電圧信号V2と間接出力電圧信号V3の差分を出力する誤差増幅器44を備える。誤差増幅器44の出力を基にパルス幅変調し、駆動パルスVg22を出力する主スイッチング素子駆動回路24を備える。スイッチング電流を検出し間接出力電流信号V1を出力する出力電流検出回路48を備える。間接出力電流信号V1をオン時比率D46で断続する補正量制御回路46を備える。基準電圧信号発生回路42は、補正量制御回路46を介して間接出力電流信号V1を受け、間接出力電流信号V1の波高値及びオン時比率D46に応じて基準電圧信号V2を補正する。

【発明の詳細な説明】

【技術分野】

【0001】

この発明は、出力の静的負荷変動特性を補正する機能を備えたスイッチング電源装置に関する。

【背景技術】

【0002】

入出力間が主トランスで絶縁されたスイッチング電源装置の場合、例えば、整流平滑回路の平滑インダクタに設けた補助巻線、又は主トランスに設けた補助巻線に発生する電圧から出力電圧と相関のある電圧信号を生成し、その信号に基づいて出力電圧の制御を行う間接出力電圧制御方式が用いられる。間接出力電圧制御方式は、出力電圧を直接検出する制御方式と異なり、主トランスの二次側の電流経路に存在する整流素子の導通抵抗や配線パターンの抵抗に発生する電圧降下分は検出しない。従って、出力電流がゼロから定格電流まで変化したときの出力電圧の変動(静的負荷変動)が、直接出力電圧制御方式よりも二次側の電圧降下分だけ大きくなる。

【0003】

1つの負荷に複数台のスイッチング電源装置の出力を接続する並列運転を行うとき、特定のスイッチング電源装置に負担が集中しないように、各スイッチング電源装置の出力電流を均等化する電流バランス制御が必要になる。電流バランス制御には様々な方法があり、例えばドループ制御と呼ばれる方法は、各スイッチング電源装置が有する静的負荷変動を積極的に利用して出力電流の均等化を図る方法で、複雑な制御回路を設ける必要がないので、スイッチング電源装置の構成をシンプルにできるという利点がある。従って、間接出力電圧制御方式は、並列運転でドループ制御を行うタイプのスイッチング電源装置に適している。

【0004】

ドループ制御を行う場合、電流バランスの精度を高くするのが容易ではないという問題がある。例えば、各スイッチング電源装置の二次側の配線パターンを意図的に細くして静的負荷変動を大きくすれば、電流バランスの精度を向上させることができる。しかし、静的負荷変動を大きくしすぎると、負荷に一定の出力電圧を供給するというスイッチング電源装置の本来の機能を果たせない。そこで、近年、静的負荷変動を一定以下に抑えつつ、各スイッチング電源装置の静的負荷変動特性(出力電流−出力電圧特性)を精度よく一致させることによって電流バランスの精度を高くする、という観点から、出力電流に応じて出力電圧を補正する制御を行うスイッチング電源装置が提案されている。

【0005】

例えば、特許文献1に開示されているDC−DCコンバータは、主トランスに設けた電圧検出用コイルに発生する電圧から出力電圧と相関のある間接出力電圧信号を生成する電圧検出用回路と、直流電圧である基準電圧信号を出力する基準電源と、間接出力電圧信号と基準電圧信号とが入力されるエラーアンプを有し、2つの入力が等しくなるように主スイッチング素子をオン・オフ制御する制御回路を備えている。さらに、主スイッチング素子に流れるスイッチング電流を電圧変換する抵抗体を有し、抵抗体の出力であるスイッチング電流信号を間接出力電圧信号に重畳させ、出力電流の大きさに応じて出力電圧を上昇させる方向の補正を加える一次側電流検出回路を備えている。

【先行技術文献】

【特許文献】

【0006】

【特許文献1】特開2000−156975号公報

【発明の概要】

【発明が解決しようとする課題】

【0007】

しかし、特許文献1のDC−DCコンバータの場合、DC−DCコンバータを量産したとき、二次側の回路素子等の個体差により、静的負荷変動特性を精度よく一致させることが困難であるという問題がある。二次側の整流素子の導通抵抗やプリント基板の配線パターンの抵抗値は、同一型番の部品であっても、一定以上のやむを得ない個体差が存在するので、一次側電流検出回路による補正を加えないときの静的負荷変動特性に、ばらつきが生じる。従って、各製品の一次側電流検出回路を極力高精度な素子を用いて構成し、出力電圧の補正量を正確に一致させたとしても、補正後の静的負荷変動特性にばらつきが生じることは避けられない。

【0008】

また、このDC−DCコンバータは、入力電圧が変化すると、出力電圧の補正量も変化してしまうという問題がある。間接出力電圧信号に重畳させるスイッチング電流信号は、図12に示すように、一定のスイッチング周波数及び所定の時比率で断続する台形波状の電圧になる。通常、エラーアンプは、出力電圧制御の安定度を高める等の理由で高域遮断周波数がスイッチング周波数よりも十分低く設定される(例えば、スイッチング周波数が100kHzであれば、高域遮断周波数が数kHz〜数十kHz程度)。従って、エラーアンプは、スイッチング電流信号の直流成分である平均電圧にのみ応答し、概ねこの平均電圧によって出力電圧の補正量が決定される。

【0009】

入力電圧が低いときは、図12(a)に示すように、スイッチング電流が発生する時比率が大きいため、スイッチング電流信号の平均電圧が高くなり、出力電圧の補正量が大きくなる。一方、出力電流が同じでも、入力電圧が高いときは、図12(b)に示すように、スイッチング電流のピーク値はほぼ同じだが、時比率が小さいために平均電圧が低くなり、出力電圧の補正量が小さくなる。従って、例えば、並列運転時のドループ制御による電流バランス調整の精度を向上させるため、入力電圧が低いときに出力電圧の補正量を小さめ設定すると、入力電圧が高いときに出力電圧の補正量が小さくなり過ぎて、静的負荷変動が許容値を超えて大きくなるおそれがある。反対に、静的負荷変動を許容値以下に抑えるため、入力電圧が高いときに出力電圧の補正量を大きめに設定すると、入力電圧が低いときに出力電圧の補正量が大きくなり過ぎて、並列運転時のドループ制御の精度が悪くなって出力電流の均等化が図れなくなる。

【0010】

さらに、このDC−DCコンバータは、出力電圧の設定を変更したときも、出力電圧の補正量が変化してしまうという問題がある。例えば、同一の主トランスを用いてスイッチング電源装置を組み立て、基準電源の基準電圧信号を変更することによって、出力電圧を異なる電圧(例えば、3.3V、2.5V、2.0V等)に切り替える場合がある。出力電圧の設定が高いときは、図13(a)に示すように、スイッチング電流が発生する時比率が大きいため、スイッチング電流信号の平均電圧が高くなり、出力電圧の補正量が大きくなる。一方、入力電圧と出力電流が同じでも、出力電圧の設定が低いときは、図13(b)に示すように、スイッチング電流のピーク値はほぼ同じだが、時比率が小さいために平均電圧が低くなり、出力電圧の補正量が小さくなる。従って、出力電圧の設定を変更したときも、入力電圧が変化したときと同様の問題が発生する。

【0011】

この発明は、上記背景技術に鑑みて成されたものであり、内部素子等の個体差等の影響を容易に吸収し、所望の静的負荷変動特性を精度よく実現することができるスイッチング電源装置を提供することを目的とする。

【課題を解決するための手段】

【0012】

この発明は、入力電源と直列に接続され、所定のスイッチング周波数でオン・オフすることによって入力電圧を断続し交流電圧を発生させる主スイッチング素子と、前記交流電圧が印加される一次巻線及びそれに磁気結合した二次巻線を有する主トランスと、前記二次巻線に発生した交流電圧を直流の出力電圧に変換し、当該出力電圧及び出力電流を負荷に供給する整流平滑回路とを備え、さらに、前記出力電圧と相関のある電圧信号である間接出力電圧信号を出力する出力電圧検出回路と、所定の直流電圧である基準電圧信号を出力する基準電圧信号発生回路、及び前記基準電圧信号と前記間接出力電圧信号との差分を増幅して出力する誤差増幅器で構成されたフィードバック制御回路と、前記誤差増幅器が出力した誤差増幅信号に基づいてパルス幅変調を行い、前記間接出力電圧信号と前記基準電圧信号とが等しくなるように前記主スイッチング素子を駆動するパルス電圧を出力する主スイッチング素子駆動回路と、を備えたスイッチング電源装置であって、前記主スイッチング素子に流れるスイッチング電流を検出し、前記出力電流と相関のある電圧信号である間接出力電流信号を出力する出力電流検出回路と、所定の周波数及び時比率で前記間接出力電流信号を断続する補正量制御回路とを備え、前記出力電圧検出回路又は前記基準電圧信号発生回路は、前記補正量制御回路を介して前記間接出力電流信号を受け、当該間接出力電流信号の値及び前記間接出力電流信号を断続した前記時比率の値が大きいほど、より前記出力電圧が高くなる方向に補正した前記間接出力電圧信号又は前記基準電圧信号を出力するスイッチング電源装置である。

【0013】

前記補正量制御回路には、前記入力電圧の状態を示す入力電圧信号、又は前記出力電圧を安定化する目標値を示す出力電圧設定信号が入力され、前記補正量制御回路は、前記入力電圧が高いときほど、且つ、前記出力電圧の目標値が低いときほど、前記前記間接出力電流信号を断続する時比率を大きくする制御を行う。

【0014】

前記主スイッチング素子のスイッチング周波数と、前記補正量制御回路の断続周波数とが等しいことが好ましい。また、出力電圧検出回路は、前記整流平滑回路の平滑インダクタに設けた補助巻線、又は前記主トランスに設けた補助巻線に発生する電圧を検出する構成とすることが好ましい。さらには、前記整流平滑回路は、双方向に導通可能な整流素子によって同期整流を行う構成にすることが好ましい。

【0015】

また、前記出力電流検出回路は、前記主スイッチング素子のスイッチング電流が流れる経路に、一端を信号グランドに接続して設けられ、前記スイッチング電流を電圧変換して正のスイッチング電流信号を出力する電流検出抵抗と、第一上段抵抗、第一下段抵抗及び第一直流電源を有し、前記第一直流電源のマイナス出力側が前記信号グランドに接続され、同じくプラス出力側が前記第一上段抵抗の一端に接続され、前記第一上段抵抗の他端と前記電流検出抵抗の出力端との間に前記第一下段抵抗が接続され、前記第一下段抵抗の両端に、前記第一直流電源の直流電圧を当該二つの抵抗の抵抗比で分圧した電圧と略等しい分圧電圧を発生させる第一バイアス回路と、前記第一上段抵抗及び第一下段抵抗の中点と前記信号グランドとの間に接続された第一コンデンサとで構成され、前記第一コンデンサの出力端である前記第一上段抵抗側の一端から、前記正のスイッチング電流信号を脈流又は直流に平滑した電圧と前記第一バイアス回路の前記分圧電圧とを合算した前記間接出力電流信号を出力し、前記補正量制御回路は、ソース端子が前記第一コンデンサの出力端に接続されたnチャネルMOS型FETである第一断続スイッチ素子と、一端が前記第一断続スイッチ素子のドレイン端子に接続された補正抵抗と、前記第一断続スイッチ素子のゲート端子と前記信号グランドとの間に、前記間接出力電流信号及び前記基準電圧信号よりも高い波高値を有する矩形波であって、前記第一断続スイッチ素子をオン・オフさせる駆動パルスを出力するPWMパルス発振回路とで構成され、前記基準電圧信号発生回路は、マイナス出力側が信号グランドに接続された第二直流電源と、前記第二直流電源のプラス出力側に一端が接続された第二上段抵抗と、前記第二上段抵抗の他端に接続され他端が信号グランドに接続された第二下段抵抗とで成る第二バイアス回路と、前記第二下段抵抗と並列に接続された第二コンデンサとで構成され、前記第二コンデンサの出力端である前記第二上段抵抗側の一端に前記補正抵抗の他端が接続され、前記第二コンデンサの出力端から、前記第二直流電源を第二上段抵抗及び第二下段抵抗の抵抗比で分圧して前記第二下段抵抗に発生する分圧電圧と、前記補正量制御回路によって断続された前記間接出力電流信号を脈流又は直流に平滑した電圧とを合算した前記基準電圧信号を出力する。

【0016】

さらに、前記補正量制御回路は、前記補正抵抗と前記第二コンデンサとの接続点にnチャネルMOS型FETである第二断続スイッチ素子が挿入され、前記第二断続スイッチ素子のドレイン端子が前記補正抵抗の一端に接続され、ソース端子が前記第二コンデンサの出力端に接続され、ゲート端子が前記第一断続スイッチの前記ゲート端子に接続されている。

【0017】

前記第一バイアス回路及び第二バイアス回路は、前記出力電流がゼロのとき、前記第一又は第二断続スイッチ素子のオン・オフの時比率によらず、前記間接出力電流信号及び前記基準電圧信号が等しくなるように設けられていることが好ましい。また、前記第一バイアス回路及び第二バイアス回路の前記第一直流電源及び第二直流電源は、一つの直流電源が兼用されていることが好ましい。

【0018】

また、前記出力電流検出回路は、前記主スイッチング素子のスイッチング電流が流れる経路に、一端を信号グランドに接続して設けられ、前記スイッチング電流を電圧変換して負のスイッチング電流信号を出力する電流検出抵抗と、第一上段抵抗、第一下段抵抗及び第一直流電源を有し、前記第一直流電源のマイナス出力端が前記信号グランドに接続され、同じくプラス出力端が前記第一上段抵抗の一端に接続され、前記第一上段抵抗の他端と前記電流検出抵抗の出力端との間に前記第一下段抵抗が接続され、前記第一下段抵抗の両端に、前記第一直流電源の電圧を当該二つの抵抗の抵抗比で分圧した電圧と略等しい分圧電圧を発生させる第一バイアス回路と、前記第一上段抵抗及び第一下段抵抗の中点と前記信号グランドとの間に接続された第一コンデンサとで構成され、前記第一コンデンサの出力端である前記第一上段抵抗側の一端から、前記負のスイッチング電流信号を脈流又は直流に平滑した電圧と前記第一バイアス回路の前記分圧電圧とを合算した前記間接出力電流信号を出力し、前記補正量制御回路は、ソース端子が前記第一コンデンサの出力端に接続されたnチャネルMOS型FETである第一断続スイッチ素子と、一端が前記第一断続スイッチ素子のドレイン端子に接続された補正抵抗と、前記第一断続スイッチ素子のゲート端子と前記信号グランドとの間に、前記間接出力電流信号及び前記間接出力電圧信号よりも高い波高値を有する矩形波であって、前記第一断続スイッチ素子をオン・オフさせる駆動パルスを出力するPWMパルス発振回路とで構成され、前記出力電圧検出回路は、一端が前記補正抵抗の他端に接続され、他端が信号グランドに接続された第三コンデンサを備え、

前記第三コンデンサの出力端である前記補正抵抗側の一端から、前記出力電圧と相関のある電圧信号である前記間接出力電圧信号と、前記補正量制御回路によって断続された前記間接出力電流信号を脈流又は直流に平滑した電圧と合算した前記間接出力電圧信号を出力する。

【0019】

さらに、前記補正量制御回路は、前記補正抵抗と前記第三コンデンサとの接続点にnチャネルMOS型FETである第二断続スイッチ素子が挿入され、前記第二断続スイッチ素子のドレイン端子が前記補正抵抗の一端に接続され、ソース端子が前記第三コンデンサの出力端に接続され、ゲート端子が前記第一断続スイッチの前記ゲート端子に接続されている。

【0020】

前記第一バイアス回路及び前記出力電圧検出回路は、前記出力電流がゼロのとき、前記第一又は第二断続スイッチ素子のオン・オフの時比率によらず、前記間接出力電流信号及び前記間接出力電圧信号が等しくなるように設けられていることが好ましい。

【発明の効果】

【0021】

このスイッチング電源装置は、補正量制御回路が間接出力電流信号を断続する時比率を変化させることによって出力電圧の補正量を自在に変化させることができ、所望の静的負荷変動特性を精度よく実現することができる。例えば、補正量制御回路にデジタルプロセッサを組み込み、デジタルプロセッサに設定された演算式に基づいて断続の時比率を決定すれば、インテリジェント性の高い補正量制御回路を容易に構成することができる。

【0022】

また、補正制御回路の断続周波数と主スイッチング素子のスイッチング周波数を正確に一致させることによって、出力電圧に不要なビートノイズが発生するのを防止することができる。さらに、整流平滑回路を、双方向に導通可能な整流素子によって同期整流を行う構成にすれば、補正量制御回路が断続する時比率を決定する演算式を簡単化することができる。

【図面の簡単な説明】

【0023】

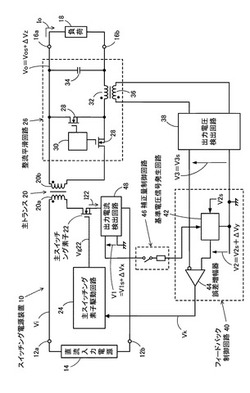

【図1】この発明のスイッチング電源装置の第一実施形態の構成を示すブロック図である。

【図2】第一実施形態のスイッチング電源装置の具体的な構成を示す回路図である。

【図3】第一実施形態のスイッチング電源装置のPWMパルス発振回路の動作を説明するタイムチャートである。

【図4】第一実施形態のスイッチング電源装置の、補正量制御回路による補正がないときの静的負荷変動特性のグラフ(a)、補正量制御回路による補正があるときの基準電圧信号V2のグラフ(b)及び静的負荷変動特性のグラフ(c)である。

【図5】補正量制御回路の変形例を用いた第一実施形態のスイッチング電源装置の回路図である。

【図6】図3の補正量制御回路の動作を説明する回路図(a)、等価回路(b)〜(d)である。

【図7】第一及び第二断続スイッチ素子の等価回路を示す図である。

【図8】図5の変形例に係る補正量制御回路の動作を説明する回路図(a)、各等価回路(b)〜(d)である。

【図9】この発明のスイッチング電源装置の第二実施形態の構成を示す回路図である。

【図10】第二実施形態のスイッチング電源装置のPWMパルス発振回路の動作を説明するタイムチャートである。

【図11】この発明のスイッチング電源装置の第三実施形態の構成を示す回路図である。

【図12】従来のスイッチング電源装置における、入力電圧に対するスイッチング電流信号及び平均電圧変化を説明するタイムチャート(a),(b)である。

【図13】従来のスイッチング電源装置における、出力電圧の設定に対するスイッチング電流信号及び平均電圧の変化を説明するタイムチャート(a),(b)である。

【発明を実施するための形態】

【0024】

以下、この発明のスイッチング電源装置の第一実施形態について、図1〜4に基づいて説明する。第一実施形態のスイッチング電源装置10は、図1のブロック図に示すように、シングルエンディッドフォワード方式の電力変換部を有し、入力端12a,12bに印加された直流入力電源14の入力電圧Viを直流の電圧Voに変換し、出力端16a,16bに接続された負荷18に出力電圧Voと出力電流Ioを供給する装置である。

【0025】

入力端12a,12bの間には、主トランス20の一次巻線20aと主スイッチング素子22の直列回路が接続されている。主スイッチング素子22は、ここではnチャネルMOS型FETであり、主スイッチング素子駆動回路24が出力する駆動パルスVg22によって駆動される。そして、入力電圧Viを、所定のスイッチング周波数f22及びオン時比率D22で断続し、一次巻線20aの両端に交流電圧を発生させる。

【0026】

主トランス20は、一次巻線20aと密に磁気結合した二次巻線20bを有し、二次巻線20bの両端に整流平滑回路26が接続されている。整流平滑回路26は、双方向に導通可能なnチャネルMOS型FETを用いた2つの整流素子28と、主スイッチング素子22のオン・オフと同期をとって整流素子28をオン・オフ駆動する同期整流駆動回路30と、ローパスフィルタを成す平滑インダクタ32及び平滑コンデンサ34とで構成され、二次巻線20bに発生する交流電圧を整流素子28で整流し、その整流電圧を平滑インダクタ32及び平滑コンデンサ34を通して平滑し、平滑コンデンサ32の両端を引き出した出力端16a,16bの間に出力電圧Voを発生させる。

【0027】

出力電圧Voを安定化する制御は、平滑インダクタ32に設けた補助巻線36、出力電圧検出回路38、フィードバック制御回路40及び主スイッチング素子駆動回路24によって行う。出力電圧検出回路38は、補助巻線36の両端に接続され、補助巻線36に発生する電圧から出力電圧Voと相関のある間接出力電圧信号V3を出力する。この実施形態では、後述する補正量制御回路46による補正が出力電圧検出回路38には加わらないので、出力電圧Voに略比例した直流の電圧V3sが間接出力電圧信号V3として出力される。

【0028】

フィードバック制御回路40は、基準電圧信号発生回路42と誤差増幅器44とで構成されている。基準電圧信号発生回路42は、直流電圧である基準電圧信号V2を出力する回路であり、後述する補正量制御回路46による補正分ΔVyと、一定の直流電圧V2sとを合算した電圧を基準電圧信号V2として出力する。

【0029】

誤差増幅器44は、反転入力端子に入力された間接出力電圧信号V3と、非反転入力端子に入力された基準電圧信号V2の差分を反転増幅し、主スイッチング素子駆動回路24に向けて誤差増幅信号Vkを出力する。主スイッチング素子駆動回路24は、誤差増幅信号Vkを基にパルス幅変調し、主スイッチング素子22をオン・オフさせるための駆動パルスVg22を出力する。このとき、駆動パルスVg22のハイレベルの時比率、すなわち主スイッチング素子22のオン時比率D22は、誤差増幅器44の動作により、間接出力電圧信号V3と基準電圧信号V2とが等しくなるように可変され、その結果、出力電圧Voが基準電圧信号V2に相当する所定の直流電圧に制御される。例えば、基準電圧信号V2が高めに変化すると、出力電圧Voが上昇する。

【0030】

さらに、スイッチング電源装置10は、基準電圧信号発生回路42が出力する基準電圧信号V2を出力電流Io等に応じて補正する動作を行うため、出力電流検出回路48及び補正量制御回路46を備えている。出力電流検出回路48は、主スイッチング素子22に流れるスイッチング電流I22を検出し、出力電流Ioと相関のある直流又は脈流の電圧信号である間接出力電流信号V1を出力する。補正量制御回路46は、出力電流検出回路48の出力と基準電圧発生回路42との間に設けられ、間接出力電流信号V1を所定の周波数f46及びオン時比率D46で断続する。

【0031】

基準電圧信号発生回路42が出力する基準電圧信号V2は、上述したように、一定の直流電圧V2sと補正量制御回路46による補正分ΔVyとを合算した電圧であり、出力電流検出回路48が出力する間接出力電流信号V1の波高値が大きいほど、また、補正量制御回路が導通するオン時比率D46が大きいほど、大きな補正分ΔVyを発生させる。詳しくは後の動作説明の中で述べる。

【0032】

次に、上記の出力電流検出回路48、補正量制御回路46、フィードバック制御回路40の基準電圧信号発生回路42、及び出力電圧検出回路38の具体的な回路構成について、図2の回路図に基づいて説明する。

【0033】

出力電流検出回路48は、電流検出抵抗50、第一バイアス回路52及び第一コンデンサ54で構成されている。電流検出抵抗50は、主スイッチング素子22のソース端子と信号グランドに接続される入力端12bとの間に設けられ、主スイッチング素子22側の一端から、スイッチング電流I22を電圧変換した正のスイッチング電流信号を出力する。第一バイアス回路52は、マイナス出力が信号グランドに接続されプラス出力から一定の直流電圧Vrを出力する直流電源56と、そのプラス出力に一端が接続された第一上段抵抗52aと、第一上段抵抗52aの他端と電流検出抵抗50の出力端との間に接続された第一下段抵抗52bとで構成されている。直流電源56は、第一バイアス回路52の第一直流電源であり、後述する第二バイアス回路66の第二直流電源としても使用される。また、2つの抵抗52a,52bは、電流検出抵抗50に比べて十分大きい抵抗値を有している。従って、第一下段抵抗52bの両端に、直流電圧Vrを2つの抵抗52a,52bの抵抗比で分圧した電圧と略等しい分圧電圧V1sが発生する。第一コンデンサ54は、2つの抵抗52a,52bの中点と信号グランドとの間に接続され、2つの抵抗52a,52bの中点側の一端から、電流検出抵抗50のスイッチング電流信号を脈流又は直流に平滑した正の電圧ΔVxと、第一バイアス回路52の分圧電圧V1sとを合算した間接出力電流信号V1を出力する。

【0034】

補正量制御回路46は、図2に示すように、第一断続スイッチ素子60、PWMパルス発振回路62及び補正抵抗64で構成されている。第一断続スイッチ素子60は、ソース端子が第一コンデンサ54の出力端に接続され、ドレイン端子が補正抵抗64の一端に接続されたnチャネルMOS型FETであり、PWMパルス発振回路62がゲート端子と信号グランドとの間に出力する駆動パルスVg60によってオン・オフ駆動される。

【0035】

PWMパルス発振回路62は、CLK発振回路62a、CPU62b、フラッシュメモリ62c及びパルス発生回路62dで構成されている。CLK発振回路62aは、第一断続スイッチ60の断続周波数f46よりも十分高い周波数のシステムクロックであるクロック信号Vckを出力する。CPU62bには、後述する第1及び第2レジスタ設定値R1,R2を算出する演算を行うことができるようにプログラムが設定されている。演算式に含まれている係数は、デフォルト設定されているものを除き、フラッシュメモリ62cから読み出す。また、CPU62bは、入力電圧Viの状態を示す入力電圧信号Virと、出力電圧Voの目標値を示す出力電圧設定信号Vorを外部から取得し、演算式にパラメータ入力する。

【0036】

パルス発生回路62dは、クロック信号Vckと第1及び第2レジスタ設定値R1,R2を受け、周波数がf46、ハイレベルの時比率がD46の駆動パルスVg60を生成する。例えば、図3に示すように、クロック信号Vckをカウントするカウンタに、第1レジスタ設定値R1として100カウント、第2レジスタ設定値R2として50カウントが付与された場合、カウンタのカウント数が第2レジスタ設定値R2に達するまでの間(1〜50カウントの間)は駆動パルスVg60をハイレベルに保持し、カウント数が第2レジスタ設定値を超え第1レジスタ設定値に達するまでの間(51〜100カウントの間)はローレベルに保持する。そして、100カウントを超えるとカウント数をリセットして1カウントに戻る。この動作を繰り返すことによって、周波数f46がクロック信号Vckの周波数fckの1/100で、ハイレベルの時比率D46が50%の駆動パルスVg60を発生させる。従って、CPU62bの演算処理の結果、第2レジスタ設定値R2が変更されると、時比率D46が0〜100%の範囲で変化することができる。駆動パルスVg60の波高値Vg60pについては後で述べる。

【0037】

補正抵抗64は、一端が第一断続スイッチ素子60のドレイン端子に、他端がフィードバック制御回路40の基準電圧信号発生回路42に接続され、第一断続スイッチ素子60に流れる電流を制限する働きをする。

【0038】

基準電圧信号発生回路42は、第二バイアス回路66と第二コンデンサ68とで構成されている。第二バイアス回路66は、マイナス出力が信号グランドに接続されプラス出力から一定の直流電圧Vrを出力する直流電源56と、そのプラス出力に一端が接続された第二上段抵抗66aと、第二上段抵抗66aの他端と信号グランドとの間に接続された第二下段抵抗66bとで構成されている。直流電源56は、第二バイアス回路66の第二直流電源であり、上述した第一バイアス回路52の第一直流電源としても使用されている。第二コンデンサ68は、第二下段抵抗66bの第二上段抵抗66a側の一端と信号グランドとの間に接続され、さらに、第二コンデンサ68の第二上段抵抗66a側の一端に、補正量制御回路46の補正抵抗64の他端が接続されている。従って、第二コンデンサ68は、第二上段抵抗66a側の一端から、直流電圧Vrを2つの抵抗66a,66bの抵抗比で分圧した分圧電圧V2sと、補正量制御回路46によって断続された間接出力電流信号V1を脈流又は直流に平滑した電圧ΔVyとを合算した基準電圧信号V2を出力する。

【0039】

なお、この実施形態では、第二上段抵抗66a及び第二下段抵抗66bの抵抗比が、第一バイアス回路52の第一上段抵抗52a及び第一下段抵抗52bの抵抗比と等しくなるように設定されている。従って、同じ直流電圧Vrを等しい抵抗比で分圧するので、基準電圧信号発生回路42の分圧電圧V2sは、出力電流検出回路48の分圧電圧V1sと等しい。また、第一断続スイッチ素子60は、ソースからドレインの向きに導通可能な図示しない寄生ダイオードを備えているが、間接出力電流信号V1のΔVx分が寄生ダイオードの順方向電圧を超えないように諸定数が設定されているので、寄生ダイオードが導通することはない。また、PWMパルス発振回路62が出力する駆動パルスVg60の波高値Vg60pは、第一断続スイッチ素子60を確実にオン・オフさせるため、間接出力電流信号V1及び基準電圧信号V2よりも十分高い電圧に設定されている。

【0040】

出力電圧検出回路38は、補助巻線36に接続されたダイオード70及び第三コンデンサ72で成るピークホールド回路と、第三コンデンサ72の両端に接続された放電抵抗74とで構成され、第三コンデンサ72の一端が信号グランドに接続され、正電圧が発生する側の一端が出力電圧検出回路38の出力端38aとなる。主スイッチング素子22がオフの期間、補助巻線36に出力電圧Voに略比例した波高値V3sの電圧が発生し、ダイオード70がそのタイミングで導通することによって第三コンデンサ72を充電する。従って、出力端38aには直流の電圧V3sが発生し、間接出力電圧信号V3として出力される。

【0041】

次に、スイッチング電源装置10の動作について説明する。まず、説明の便宜のため、スイッチング電源装置10の補正量制御回路46の第一断続スイッチ素子60が停止している状態(オン時比率D46=0%に固定されている状態)を考える。この場合、出力電圧Vo−出力電流Ioの関係、すなわち静的負荷変動特性は、式(1)のように表わされる。

【数1】

【0042】

ここで、Vosは、出力電圧Ioがゼロアンペアのときの出力電圧Vo(以下、Vosを無負荷出力電圧と称す。)であり、Rwは、二次側の出力電流Ioが流れる経路にある整流素子28の導通抵抗や配線パターンの抵抗分等の合成抵抗分であり、ΔVwは、抵抗分Rwに出力電流Ioが流れたときの電圧降下である。

【0043】

出力電圧検出回路38が出力する間接出力電圧信号V3は、フィードバック制御回路40及び主スイッチング素子駆動回路24の動作により、基準電圧信号V2(ここでは、分圧電圧V2s)と等しくなるように制御されるので、平滑インダクタ32の両端電圧は、出力電流Ioの大小によらず、無負荷出力電圧Vosに保持される。従って、図4(a)に実線で示すように、静的負荷変動特性は、出力電流Ioが大きくなるほど、出力電圧Voが右肩下がりで低下する特性となり、大きな静的負荷変動が発生する。

【0044】

次に、図4(b),(c)を用いて、補正量制御回路御46の第一断続スイッチ素子60が所定のオン時比率D46でオン・オフし、図4(c)の実線に示す所望の静的負荷変動特性を実現する動作を説明する。

【0045】

出力電流Ioがゼロのときは、スイッチング電流信号を平滑した電圧ΔVxがほぼゼロになるので、間接出力電流信号V1が分圧電圧V1sになる。分圧電圧V1sは、基準電圧発生回路42の分圧電圧V2sと等しいので、第一断続スイッチ素子60がオンしても、第一断続スイッチ素子60に電流が流れない。従って、オン時比率D46の大小にかかわらず補正分ΔVyがゼロになり、基準電圧信号V2が分圧電圧V2sとなる。従って、出力電圧Voは、補正量制御回路46が停止している図4(a)と同様に、無負荷出力電圧Vosに制御される。

【0046】

出力電流Ioが流れると、出力電流検出回路48にスイッチング電流信号を平滑した電圧ΔVxが発生し、間接出力電流信号V1が、分圧電圧V1sよりも電圧ΔVxだけ高くなる。従って、第一断続スイッチ素子60がオン・オフすることによって、間接出力電流信号V1の電圧ΔVxが断続的に第二コンデンサ68に送られ、その断続信号を脈流又は直流に平滑した補正分ΔVyが発生し、図4(b)に示すように、基準電圧信号V2が補正分ΔVyだけ補正される。基準電圧信号V2が補正分ΔVyだけ高くなると、誤差増幅器44は、間接出力電圧信号V3が補正分ΔVyだけ低いと認識し、誤差増幅信号Vkを変化させ、主スイッチング素子制御回路24が主スイッチング素子22のオン時比率D22を大きくし、図4(c)に示すように、出力電圧Voを電圧ΔVzだけ上昇させる。

【0047】

図4(b)に示すように、補正分ΔVyは、第一断続スイッチ素子60のオン時比率D46を一定値に固定した状態でも、出力電流Ioが増加するにつれて大きくなる。さらにオン時比率D46を変更すれば、補正分ΔVyが大きくなる傾きを変化させることができる。従って、オン時比率D46を調整することによって、補正分ΔVyを自在に可変することができ、所望の静的負荷変動特性を実現することができる。特に、オン時比率D46は、CPU62bとフラッシュメモリ62cを用いたデジタル演算処理によって決定するので、高いインテリジェント性を有し、様々なアプリケーションに対応できる。

【0048】

例えば、スイッチング電源装置10を工場で量産したとき、オン時比率D46を一律の値にデフォルト設定して組み立てた結果、無負荷出力電圧Vosのばらつきは許容値内であるが、製品個々の抵抗Rwのばらつきが大きいため、静的負荷変動特性の規格を逸脱する製品が発生したとする。この問題は、背景技術で説明した特許文献1のDC−DCコンバータでは対策が困難であるが、この実施形態のスイッチング電源装置10であれば、以下に説明する方法で容易に解決することができる。

【0049】

まず、組み立てた製品個々に行う通電試験において、オン時比率D46を0%に固定して動作させ、特定の出力電流Ioにおける電圧降下ΔVwを測定し、フラッシュメモリ62cに書き込む。式(1)から分かるように、電圧降下ΔVwは抵抗Rwに略比例するので、電圧降下ΔVwを測定すれば、抵抗Rwの個体差の的確に把握することができる。次に、CPU62bが、フラッシュメモリ62cから電圧降下ΔVwを読み取り、目標とする静的負荷変動特性を得るため、その特定の出力電流Ioにおいて必要な補正分ΔVyを算出し、その補正分ΔVyを得るためのオン時比率D46を算出し、さらに、その時比率D46を実現するための第2レジスタ設定値R2を算出する。そして、PWMパルス発振回路62が、CPU62bが算出した第2レジスタ設定値R2を受け、第一断続スイッチ素子60をオン・オフさせる駆動パルスVg60を発生する。すると、第一断続スイッチ素子60のオン・オフ動作によって最適な補正分ΔVyが基準電圧信号V2に重畳され、目標の静的負荷変動特性に非常に近い静的負荷変動特性を得ることができる。このように、製品の通電試験でソフト的な初期設定を行うだけで、各製品の静的負荷変動特性を、簡単に且つ精度よく一致させることができる。

【0050】

また、例えば、入力電圧Viの変動や出力電圧Voの設定の違いよって静的負荷変動特性が大きく変化し、「静的負荷変動が小さく、良好なドループ制御も可能なスイッチング電源装置10を実現することができない」という問題が発生することも考えられる(この問題は、上記の背景技術の中で、図12、図13を用いて説明した問題である)。しかし、この問題についても、CPU62bがオン時比率D46を算出する演算式に、外部から入力される入力電圧信号Vir及び出力電圧設定信号Vorをパラメータとして加えておくことによって、容易に解決することができる。

【0051】

図12、図13から分かるように、オン時比率D46を一定値に固定すると、入力電圧Viが低いときほど、また出力電圧Voの設定値が高いときほど、間接出力電流信号V1の電圧ΔVx成分が大きくなり、補正分ΔVyも大きくなり、その結果、補正による出力電圧Voの上昇電圧ΔVzが大きくなる。反対に、入力電圧Viが高いときほど、また出力電圧Voの設定値が低いときほど、間接出力電流信号V1の電圧ΔVx成分が小さくなり、補正分ΔVyも小さくなり、その結果、補正による出力電圧Voの上昇電圧ΔVzが小さくなる。従って、入力電圧Viと出力電圧Voの設定値が変化しても、一定の補正分ΔVyが得られるようにすれば、補正による出力電圧Voの上昇電圧ΔVzが一定になり、この問題を解決することができる。具体的には、CPU62bがオン時比率D46を算出する演算式に、スイッチング電源装置10の実際の動作状態をモニタした入力電圧信号Vir及び出力電圧設定信号Vorをパラメータとして加え、さらに、入力電圧Vi及び出力電圧Voの設定値が補正分ΔVyに与える影響をキャンセルする係数等を盛り込んでおけばよい。このように、入力電圧Viの状態及び出力電圧Voの設定を加味してオン時比率D46を算出する演算式を設定することによって、静的負荷変動が小さく、且つ良好なドループ制御も可能なスイッチング電源装置10を実現することができる。

【0052】

以上説明したように、スイッチング電源装置10は、補正量制御回路46が間接出力電流信号V1を断続するオン時比率D46を変化させることによって、補正による出力電圧Voの上昇電圧ΔVzを自在に変化させることができ、所望の静的負荷変動特性を精度よく実現することができる。特に、補正量制御回路にデジタルプロセッサを組み込み、デジタルプロセッサに設定された演算式に基づいて断続の時比率D46を決定することにより、インテリジェント性の高い補正量制御回路46を容易に構成することができる。

【0053】

また、ここでは、第一バイアス回路52が決定する分圧電圧V1sと第二バイアス回路66が決定する分圧電圧V2sとが等しくなるように設定されているので、図4(b)に示すように、オン時比率D46の値にかかわらず、出力電流Ioがゼロアンペアのときの補正分ΔVzをほぼゼロにすることができる。従って、入力電圧Vi及び出力電圧Voの設定値の情報を加味してオン時比率D46を算出する場合でも、設定する演算式を簡単化することができる。また、整流平滑回路26が、双方向に導通可能な整流素子28によって同期整流を行う構成なので、出力電流Ioとスイッチング電流I22を平滑したスイッチング電流信号ΔVxとの関係をほぼ線形な式で表わすことができ、オン時比率D46を算出する演算式を簡単化することができる。ただし、ダイオード整流等の構成であっても、それに応じた演算式を設定すれば、使用可能である。 さらに、第一及び第二バイアス回路52,66の第一及び第二直流電源が一つの直流電源56で兼用されているので、例えば、出力電圧Voの設定を3.3Vから2.0Vに切り替えるとき、直流電圧Vrを低い電圧値に変更するだけで対応することができる。また、この直流電圧Vrを、CPU62bに入力する出力電圧設定信号Vorとして使用することも可能である。

【0054】

次に、この実施形態の補正量制御回路46の変形例である補正量制御回路76について、図5〜図8に基づいて説明する。ここで、上記のスイッチング電源装置10と同様の構成は、同一の符号を付して説明を省略する。補正量制御回路76は、図5に示すように、上記補正量制御回路46の構成に加え、第二断続スイッチ素子78を設けたものであり、その他の構成は補正量制御回路46と同じである。

【0055】

第二断続スイッチ素子78は、第一断続スイッチ素子60と同一のnチャネルMOS型FETであり、補正抵抗64の第一断続スイッチ素子60が接続されていない側の一端にドレイン端子が接続され、第一断続スイッチ素子60のゲート端子に自身のゲート端子が接続され、基準電圧信号発生回路42の第二コンデンサ68の出力端にソース端子が接続されている。従って、補正量制御回路76は、第一及び第二断続スイッチ素子60,78を同位相でオン・オフさせることによって間接出力電流信号V1を断続する。

【0056】

補正量制御回路76は、特に、出力電流Ioがゼロアンペアのときの上記補正量制御回路46の動作を改善する効果がある。そこで、まず、図6を用いて上記補正量制御回路46の動作を説明し、それと対比しながら、変形例の補正量制御回路76の動作を説明する。

【0057】

図6(a)は、図2の回路図から、主要な部品である第一断続スイッチ素子60、パルス発生回路62d、補正抵抗64、誤差増幅器44、第一コンデンサ54及び第二コンデンサ68の部分を抜粋した回路図である。なお、パルス発生回路62dが出力する駆動パルスVg60の波高値Vg60pは、上述したように、間接出力電流信号V1及び基準電圧信号V2よりも十分高い電圧に設定されている。

【0058】

nチャネルMOS型FETである第一断続スイッチ素子60は、図7の等価回路に示すように、パルス発生回路62dが発生する駆動パルスVg60がハイレベルのときにオンするドレイン・ソース間のスイッチSW60、ドレイン・ソース間の寄生コンデンサCds60、ドレイン・ゲート間の寄生コンデンサCdg60及びゲート・ソース間の寄生コンデンサCgs60を用いて表わすことができる。そこで、図6(a)の回路図をスイッチSW60等に置き換えた図6(b)〜(d)に基づき、スイッチング電源装置10の出力電流Ioがゼロアンペアのときの動作を説明する。ここで、説明の便宜のため、図6(b)が開始する前の初期状態として、間接出力電流信号V1及び基準電圧信号V2が、互いに等しく分圧電圧V1s(=分圧電圧V2s)になっているとする。

【0059】

図6(b)は、駆動パルスVg60がゼロボルトから波高値Vg60pに向かって上昇している途中の動作を示しており、矢印で示すように、パルス発生回路62dを起点とする2つの経路に急峻な電流が流れる。スイッチSW60は、寄生コンデンサCgs60が充電され、その両端電圧が第一断続スイッチ素子60のオン閾値を超えたタイミングでオンに転じる。第一コンデンサ54の間接出力電流信号V1は、矢印で示す電流により、僅かに上昇する(以下、この電圧上昇分をΔVe1とする)。電圧上昇分ΔVe1は、寄生コンデンサCgs60,Cds60,Cgd60と第一コンデンサ54との容量比や波高値Vg60pに依存するので、図4(b),(c)で説明した理想的な動作を行うためには、第一コンデンサ54の容量を寄生コンデンサCgs60,Cds60,Cgd60よりも極めて大きな値に設定することによって電圧ΔVe1を小さく抑え、間接出力電流信号V1が分圧電圧V1sに保持されるようにすることが好ましい。しかし、静的負荷変動特性の補正を出力電流Ioに対してより高速に応答させるためには、第一コンデンサ54の容量をある程度小さい値に設定する必要がある。ここでは、第一コンデンサ54の容量が、ある程度の小さい値が設定されており、第一コンデンサ54の間接出力電流信号V1が分圧電圧V1sから電圧ΔVe1だけ僅かに上昇する。一方、第二コンデンサ68は、補正抵抗64の存在によってほとんど電流が流れず、基準電圧信号V2が分圧電圧V2s(=分圧電圧V1s)に保持される。

【0060】

図6(c)は、駆動パルスVg60が波高値Vg60pを維持し、スイッチSW60がオンしている期間の動作を示している。この状態では、寄生コンデンサCgs60,Cds60,Cgd60には電流が流れないが、矢印で示すように、第一コンデンサ54を起点とする補正抵抗64、第二コンデンサ68の経路に、電圧上昇分ΔVe1を緩やかに放電する電流が流れる。この電流により、第一コンデンサ54の間接出力電流信号V1が分圧電圧V1sに向かって低下し、第二コンデンサ68の基準電圧信号V2が分圧電圧V

2sから僅かに上昇する(以下、この電圧上昇分をΔVe2とする)。電圧上昇分ΔVe2は、駆動パルスVg60が波高値Vg60pを維持する時間、すなわち、スイッチSW60のオン時比率D46によって異なる値になる。従って、この期間中の間接出力電流信号V1及び基準電圧信号V2の状態は一律ではない。

【0061】

図6(d)は、駆動パルスVg60が波高値Vg60pからゼロボルトに向かって低下している途中の動作を示しており、矢印で示すように、第一コンデンサ54を起点とする2つの経路に急峻な電流が流れる。スイッチSW60は、寄生コンデンサCgs60が放電され、その両端電圧が第一断続スイッチ素子60のオン閾値未満になったタイミングでオフに転じる。第一コンデンサ54は、図6(c)の期間の電圧上昇分が急峻に放電され、間接出力電流信号V1が分圧電圧V1sまで瞬時に低下する。一方、第二コンデンサ68には、補正抵抗64の存在によりほとんど電流が流れない状態でスイッチSW60がオフするため、基準電圧信号V2は、図6(c)が終了したときの電圧、すなわち、分圧電圧V2s(=分圧電圧V1s)よりも電圧上昇分ΔVe2だけ高い電圧に保持される。

【0062】

このように、上記の補正量制御回路46は、静的負荷変動特性の補正を高速化する目的で第一コンデンサ54の容量を小さくした場合に、出力電流Ioがゼロアンペアであっても、間接出力電流信号V1及び基準電圧信号V2が分圧電圧V1s及びV2s(=分圧電圧V1s)に保持されず、電圧ΔVe1やΔVe2の分だけ変化する。しかも、電圧上昇分ΔVe2は、オン時比率D46の状態によって変動する不安定なものである。従って、電圧上昇分ΔVe1,ΔVe2は、図4(b),(c)で説明した「出力電流Ioの増加に対してのみ補正分ΔVyが比例して増加する」という理想的な動作の妨げになる不安定な誤差要因といえる。

【0063】

それに対して、変形例に係る補正量制御回路76の場合、第二断続スイッチ素子78が付加されているので、上記の補正量制御回路46とは動作が異なる。以下、補正量制御回路76の場合の動作を、図8に基づいて説明する。

【0064】

図8(a)は、図5の回路図から、主要な部品である第一断続スイッチ素子60、パルス発生回路62d、補正抵抗64、誤差増幅器44、第一コンデンサ54、第二コンデンサ68、及び第二断続スイッチ素子78の部分を抜粋した回路図である。上記と同様に、パルス発生回路62dが出力する駆動パルスVg60の波高値Vg60pは、間接出力電流信号V1及び基準電圧信号V2よりも十分高い電圧に設定されている。また、図8(b)〜(d)は、図8(a)の回路図をスイッチSW60,SW78等に置き換えた等価回路であり、これらの各等価回路を用いて、スイッチング電源装置10の出力電流Ioがゼロアンペアのときの動作を説明する。ここで、説明の便宜のため、図8(b)が開始する前の初期状態として、出力電流信号V1及び基準電圧信号V2が、互いに等しく分圧電圧V1s(=分圧電圧V2s)になっているとする。

【0065】

図8(b)は、駆動パルスVg60がゼロボルトから波高値Vg60pに向かって上昇している途中の動作を示しており、矢印で示すように、パルス発生回路62dを起点とする4つの経路に急峻な電流が流れる。スイッチSW60,SW78は、寄生コンデンサCgs60,Cgs78が充電され、それらの両端電圧が第一及び第二断続スイッチ素子60,78のオン閾値を超えたタイミングで、ほぼ同時にオンに転じる。第一コンデンサ54の間接出力電流信号V1は、矢印で示す電流により僅かに上昇する。この電圧上昇分は、上記補正量制御回路46と同様にΔVe1である。一方、この補正量制御回路76の場合、第二コンデンサ68にも矢印に示す電流が流れ、第一コンデンサ54と第二コンデンサ68が同じ容量の素子の場合、基準電圧信号V2が電圧ΔVe2(=ΔVe1)だけ上昇する。

【0066】

図8(c)は、駆動パルスVg60が波高値Vg60pを維持し、スイッチSW60,SW78がオンしている期間の動作を示している。この期間は、各コンデンサの電位バランスがとれているので、どの経路にも電流が流れず、間接出力電流信号V1及び基準電圧信号V2は、図8(b)が終了したときの電圧、すなわち、分圧電圧V1sよりもΔVe1だけ上昇した電圧に保持される。従って、この期間中の間接出力電流信号V1及び基準電圧信号V2は、スイッチSW60,SW78のオン時比率D46によらず一律である。

【0067】

図8(d)は、駆動パルスVg60が波高値Vg60pからゼロボルトに向かって低下している途中の動作を示しており、矢印で示すように、第一コンデンサ54を起点とする2つの経路と第二コンデンサ68を起点とする2つの経路とに急峻な電流が流れる。スイッチSW60,SW78は、寄生コンデンサCgs60,Cgs78が放電され、それぞれ両端電圧が第一及び第二断続スイッチ素子60,78のオン閾値未満になったタイミングで、ほぼ同時にオフに転じる。第一コンデンサ54は、電圧上昇分ΔVe1が急峻に放電され、上記補正量制御回路46と同様に、出力電流信号V1が分圧電圧V1sまで瞬時に低下する。一方、この補正量制御回路76の場合は、第二コンデンサ68の電圧上昇分ΔVe2(=ΔVe1)も同時に放電され、基準電圧信号V2が分圧電圧V2s(=分圧電圧V1s)まで瞬時に低下する。

【0068】

このように、変形例に係る補正量制御回路76は、第一コンデンサ54の容量を小さくした場合に、出力電流Ioがゼロアンペアであっても間接出力電流信号V1及び基準電圧信号V2が分圧電圧V2s(=分圧電圧V1s)に保持されず、電圧ΔVe1(=ΔVe2)だけ上昇する。しかし、電圧上昇分ΔVe1は、出力電流Ioやオン時比率D46の状態によらず、第一コンデンサ54(=第二コンデンサ68)と寄生コンデンサCgs60(=Cgs78)、Cgd60(=Cgd78)、Cds60(=Cds78)の関係で決定される一律で安定なものである。電圧ΔVe2の上昇は、出力電圧Voの上昇させることになるが、一律で安定な値であるため、容易にキャンセルすることができる。従って、電圧上昇分ΔVe1は、図4(b),(c)で説明した「出力電流Ioの増加に対してのみ補正分ΔVyが比例して増加する」という理想的な動作を実現することができる。

【0069】

次に、この発明のスイッチング電源装置の第二実施形態について、図9、図10に基づいて説明する。ここで、上記のスイッチング電源装置10と同様の構成は、同一の符号を付して説明を省略する。第二実施形態のスイッチング電源装置80は、図9に示すように、上記のスイッチング電源装置10のPWMパルス発振回路62を新たなパルス発生回路PWMパルス発振回路82に置き換えることによって、補正量制御回路46の断続周波数f46と主スイッチング素子22のスイッチング周波数f22とが一致する動作を行うものである。その他の構成は、上記のスイッチング電源装置10と同じである。

【0070】

PWMパルス発振回路82は、CLK発振回路62a、新たなCPU82b、フラッシュメモリ62c及び新たなパルス発生回路82dで構成されている。CLK発振回路62aは、第一断続スイッチ60の断続周波数f46よりも十分高い周波数のシステムクロックであるクロック信号Vckを出力する。CPU82bには、第1〜第3レジスタ設定値R1,R2,R3を算出する演算を行うことができるようにプログラムが設定されている。演算式に含まれている係数は、デフォルト設定されているものを除き、フラッシュメモリ62cから読み出す。また、CPU82bは、入力電圧信号Virと、出力電圧設定信号Vorを外部から取得し、演算式にパラメータ入力する。

【0071】

パルス発生回路82dは、クロック信号Vckと第1及び第2レジスタ設定値R1,R2に基づいて、周波数がf46でハイレベルの時比率がD46の駆動パルスVg60を生成すると共に、クロック信号Vckと第1及び第3レジスタ設定値R1,R3に基づいて、周波数がf46でハイレベルの時比率がD24の同期パルスV24を生成する。例えば、図10に示すように、クロック信号Vckをカウントするカウンタに、第1レジスタ設定値R1として100カウント、第2レジスタ設定値R2として30カウント、第3レジスタ設定値R2として60カウントが付与されているとする。駆動パルスVg60については、カウンタのカウント数が第2レジスタ設定値R2に達するまでの間(1〜30カウントの間)はハイレベルに保持し、カウント数が第2レジスタ設定値を超え第1レジスタ設定値に達するまでの間(31〜100カウントの間)はローレベルに保持する。そして、100カウントを超えるとカウント数をリセットして1カウントに戻る。この動作を繰り返すことによって、周波数f46がクロック信号Vckの周波数fckの1/100、ハイレベルの時比率D46が30%の駆動パルスVg60を発生させる。

【0072】

同期パルスV24についても同様に、カウンタのカウント数が第3レジスタ設定値R3に達するまでの間(1〜60カウントの間)はハイレベルに保持し、カウント数が第3レジスタ設定値を超え第1レジスタ設定値に達するまでの間(61〜100カウントの間)はローレベルに保持する。そして、100カウントを超えるとカウント数をリセットして1カウントに戻る。この動作を繰り返すことによって、周波数が駆動パルスVg60の周波数f46と同じで、ハイレベルの時比率D24が60%の同期パルスV24を発生させる。

【0073】

駆動パルスVg60は、上述したように、第一断続スイッチ素子60のゲート端子に向けて出力され、第一断続スイッチ素子60をオン・オフさせる。同期パルスV24は、図9に示すように、主スイッチング素子駆動回路24に向けて出力される。主スイッチング素子駆動回路24は、周波数f46の同期パルスV24を受け、主スイッチング素子22の駆動パルスVg22の1周期の開始のタイミングを同期させ、駆動パルスVg22の周波数f22を同期パルスV24の周波数f46と一致させる。この動作により、主スイッチング素子22のスイッチング周波数f22と補正量制御回路46の断続周波数f46とを一致させる。

【0074】

スイッチング電源装置80は、スイッチング周波数f22と断続周波数f46とを容易に、且つ正確に一致させることができるので、互いに異なる2つの周波数が干渉したときに生じる不要なビートノイズが発生する心配がない。

【0075】

また、同期パルスV24は、時比率D24という情報も有しており、時比率D24も様々な制御に利用することができる。例えば、スイッチング素子制御回路24が、特開平2010−125524号公報のフィードフォワード制御の構成になっている場合、主スイッチング素子22のオン時比率D22が変化し得る上限値を、同期パルスV24の時比率D24で規定することによって、主トランス20の磁気飽和を容易に回避することができる。

【0076】

次に、この発明のスイッチング電源装置の第三実施形態について、図11に基づいて説明する。ここで、上記のスイッチング電源装置10と同様の構成は、同一の符号を付して説明を省略する。第三実施形態のスイッチング電源装置84は、図11に示すように、上記のスイッチング電源装置10の出力電流検出回路48を新たな出力電流検出回路86に置き換え、さらに、補正量制御回路46の補正抵抗64の出力端の接続を、出力電圧検出回路38の出力端38aに変更したものである。その他の構成は、上記のスイッチング電源装置10と同じである。

【0077】

出力電流検出回路86は、電流検出抵抗50、第一バイアス回路52及び第一コンデンサ54で構成されている。電流検出抵抗50は、信号グランドである主スイッチング素子22のソース端子と直流入力電源14が接続される入力端12bとの間に設けられ、入力端12b側の一端から、スイッチング電流I22を電圧変換した負のスイッチング電流信号を出力する。第一バイアス回路52は、マイナス出力が信号グランドに接続されプラス出力から一定の直流電圧Vrを出力する直流電源56と、そのプラス出力に一端が接続された第一上段抵抗52aと、第一上段抵抗52aの他端と電流検出抵抗50の出力端との間に接続された第一下段抵抗52bとで構成されている。2つの抵抗52a,52bは、電流検出抵抗50に比べて十分大きい抵抗値を有している。従って、第一下段抵抗52bの両端に、直流電圧Vrを2つの抵抗52a,52bの抵抗比で分圧した電圧と略等しい分圧電圧V1sが発生する。第一コンデンサ54は、2つの抵抗52a,52bの中点と信号グランドとの間に接続され、2つの抵抗52a,52bの中点側の一端から、電流検出抵抗50のスイッチング電流信号を脈流又は直流に平滑した負の電圧(−ΔVx)と、第一バイアス回路52の分圧電圧V1sとを合算した間接出力電流信号V1を出力する。

【0078】

出力電圧検出回路38は、上述したように、補助巻線36に接続されたダイオード70及び第三コンデンサ72で成るピークホールド回路と、第三コンデンサ72の両端に接続された放電抵抗74とで構成されている。しかし、ここでは、補正量制御回路46の補正抵抗64の出力端が出力端38aに接続され、出力端38aには、出力電圧Voに略比例した直流の電圧V3sが発生と、補正量制御回路46によって断続された間接出力電流信号V1を脈流又は直流に平滑した電圧(−ΔVy)とを合算した間接出力電圧信号V3を出力する。

【0079】

基準電圧信号発生回路42は、上述したように第二バイアス回路66と第二コンデンサ68とで構成されているが、補正量制御回路46の補正抵抗64の出力端が接続されていない。従って、第二コンデンサ68の第二上段抵抗66a側の一端から出力される基準電圧信号V2は、直流電圧Vrを2つの抵抗66a,66bの抵抗比で分圧した一定の分圧電圧V2sである。

【0080】

誤差増幅器44は、上述したように、反転入力端子に入力された間接出力電圧信号V3と、非反転入力端子に入力された基準電圧信号V2の差分を反転増幅し、主スイッチング素子駆動回路24に向けて誤差増幅信号Vkを出力する。そして、主スイッチング素子駆動回路24は、誤差増幅信号Vkをパルス幅変調し、主スイッチング素子22をオン・オフさせるための駆動パルスVg22を出力する。出力電圧信号V3が低めに変化すると、主スイッチング素子22のオン時比率D22が大きくなり、出力電圧Voが上昇する。

【0081】

このスイッチング電源装置84は、主スイッチング素子22及び電流検出回路86の部品配置の都合等により、電流検出抵抗50の主スイッチング素子22側の一端が信号グランドに接続されているので、電流検出抵抗50が出力するスイッチング電流信号が負の電圧になる。従って、静的出力変動特性を補正するための補正分が(−ΔVy)になる。そこで、補正分(−ΔVy)が誤差増幅器44の反転入力端子の側に入力されるように、出力電圧信号V3に合算する構成に変更し、図4(b),(c)と同様の補正が行われるようにしたものである。このスイッチング電源装置84においても、上記スイッチング電源装置10と同様の作用効果を得ることができる。

【0082】

なお、この発明のスイッチング電源装置は、上記実施形態に限定されるものではない。出力電圧検出回路は、出力電圧を電源回路の一次側で間接的に検出できるものであればよく、例えば、平滑インダクタの補助巻線を利用し、特開2008−278639号公報に開示されているような高機能回路を使用してもよい。また、主トランスに設けた補助巻線に発生する電圧から出力電圧と相関のある電圧信号を生成する構成にしてもよい。

【0083】

また、上記の実施形態では、出力電流がゼロアンペアのとき、出力電流検出回路が出力する出力電流信号V1(=V1s)と、補正量制御回路が接続される基準電圧信号発生回路が出力する基準電圧信号V2(=V2s)とを等しくすることによって、補正量制御回路を断続させる時比率を決定する演算式を簡単化できることを説明したが、電圧V1sと電圧V2sとが異なる値であっても、それに応じた演算式を設定すれば、所望の静的負荷変動特性を精度よく実現することができることは言うまでもない。

【0084】

さらに、電力変換部の構成は、シングルエンディッドフォワード方式のほか、フライバック方式、プッシュプル方式、各種ブリッジ方式など自由に選択することができる。

【符号の説明】

【0085】

10,80,84 スイッチング電源装置

20 主トランス

20a 一次巻線

20b 二次巻線

22 主スイッチング素子

24 主スイッチング素子制御回路

26 整流平滑回路

32 平滑インダクタ

36 補助巻線36

38 出力電圧検出回路

40 フィードバック制御回路

42 基準電圧信号発生回路

44 誤差増幅器

46,76 補正量制御回路

48,86 出力電流検出回路

50 電流検出抵抗

52 第一バイアス回路

52a 第一上段抵抗

52b 第一下段抵抗

54 第一コンデンサ

56 直流電源

60 第一断続スイッチ素子

62,82 PWMパルス発振回路

62a CLK発振回路

62b,82b CPU

62c フラッシュメモリ

62d,82d パルス発生回路

64 補正抵抗

66 第二バイアス回路

66a 第二上段抵抗

66b 第二下段抵抗

68 第二コンデンサ

72 第三コンデンサ

78 第二断続スイッチ素子

【技術分野】

【0001】

この発明は、出力の静的負荷変動特性を補正する機能を備えたスイッチング電源装置に関する。

【背景技術】

【0002】

入出力間が主トランスで絶縁されたスイッチング電源装置の場合、例えば、整流平滑回路の平滑インダクタに設けた補助巻線、又は主トランスに設けた補助巻線に発生する電圧から出力電圧と相関のある電圧信号を生成し、その信号に基づいて出力電圧の制御を行う間接出力電圧制御方式が用いられる。間接出力電圧制御方式は、出力電圧を直接検出する制御方式と異なり、主トランスの二次側の電流経路に存在する整流素子の導通抵抗や配線パターンの抵抗に発生する電圧降下分は検出しない。従って、出力電流がゼロから定格電流まで変化したときの出力電圧の変動(静的負荷変動)が、直接出力電圧制御方式よりも二次側の電圧降下分だけ大きくなる。

【0003】

1つの負荷に複数台のスイッチング電源装置の出力を接続する並列運転を行うとき、特定のスイッチング電源装置に負担が集中しないように、各スイッチング電源装置の出力電流を均等化する電流バランス制御が必要になる。電流バランス制御には様々な方法があり、例えばドループ制御と呼ばれる方法は、各スイッチング電源装置が有する静的負荷変動を積極的に利用して出力電流の均等化を図る方法で、複雑な制御回路を設ける必要がないので、スイッチング電源装置の構成をシンプルにできるという利点がある。従って、間接出力電圧制御方式は、並列運転でドループ制御を行うタイプのスイッチング電源装置に適している。

【0004】

ドループ制御を行う場合、電流バランスの精度を高くするのが容易ではないという問題がある。例えば、各スイッチング電源装置の二次側の配線パターンを意図的に細くして静的負荷変動を大きくすれば、電流バランスの精度を向上させることができる。しかし、静的負荷変動を大きくしすぎると、負荷に一定の出力電圧を供給するというスイッチング電源装置の本来の機能を果たせない。そこで、近年、静的負荷変動を一定以下に抑えつつ、各スイッチング電源装置の静的負荷変動特性(出力電流−出力電圧特性)を精度よく一致させることによって電流バランスの精度を高くする、という観点から、出力電流に応じて出力電圧を補正する制御を行うスイッチング電源装置が提案されている。

【0005】

例えば、特許文献1に開示されているDC−DCコンバータは、主トランスに設けた電圧検出用コイルに発生する電圧から出力電圧と相関のある間接出力電圧信号を生成する電圧検出用回路と、直流電圧である基準電圧信号を出力する基準電源と、間接出力電圧信号と基準電圧信号とが入力されるエラーアンプを有し、2つの入力が等しくなるように主スイッチング素子をオン・オフ制御する制御回路を備えている。さらに、主スイッチング素子に流れるスイッチング電流を電圧変換する抵抗体を有し、抵抗体の出力であるスイッチング電流信号を間接出力電圧信号に重畳させ、出力電流の大きさに応じて出力電圧を上昇させる方向の補正を加える一次側電流検出回路を備えている。

【先行技術文献】

【特許文献】

【0006】

【特許文献1】特開2000−156975号公報

【発明の概要】

【発明が解決しようとする課題】

【0007】

しかし、特許文献1のDC−DCコンバータの場合、DC−DCコンバータを量産したとき、二次側の回路素子等の個体差により、静的負荷変動特性を精度よく一致させることが困難であるという問題がある。二次側の整流素子の導通抵抗やプリント基板の配線パターンの抵抗値は、同一型番の部品であっても、一定以上のやむを得ない個体差が存在するので、一次側電流検出回路による補正を加えないときの静的負荷変動特性に、ばらつきが生じる。従って、各製品の一次側電流検出回路を極力高精度な素子を用いて構成し、出力電圧の補正量を正確に一致させたとしても、補正後の静的負荷変動特性にばらつきが生じることは避けられない。

【0008】

また、このDC−DCコンバータは、入力電圧が変化すると、出力電圧の補正量も変化してしまうという問題がある。間接出力電圧信号に重畳させるスイッチング電流信号は、図12に示すように、一定のスイッチング周波数及び所定の時比率で断続する台形波状の電圧になる。通常、エラーアンプは、出力電圧制御の安定度を高める等の理由で高域遮断周波数がスイッチング周波数よりも十分低く設定される(例えば、スイッチング周波数が100kHzであれば、高域遮断周波数が数kHz〜数十kHz程度)。従って、エラーアンプは、スイッチング電流信号の直流成分である平均電圧にのみ応答し、概ねこの平均電圧によって出力電圧の補正量が決定される。

【0009】

入力電圧が低いときは、図12(a)に示すように、スイッチング電流が発生する時比率が大きいため、スイッチング電流信号の平均電圧が高くなり、出力電圧の補正量が大きくなる。一方、出力電流が同じでも、入力電圧が高いときは、図12(b)に示すように、スイッチング電流のピーク値はほぼ同じだが、時比率が小さいために平均電圧が低くなり、出力電圧の補正量が小さくなる。従って、例えば、並列運転時のドループ制御による電流バランス調整の精度を向上させるため、入力電圧が低いときに出力電圧の補正量を小さめ設定すると、入力電圧が高いときに出力電圧の補正量が小さくなり過ぎて、静的負荷変動が許容値を超えて大きくなるおそれがある。反対に、静的負荷変動を許容値以下に抑えるため、入力電圧が高いときに出力電圧の補正量を大きめに設定すると、入力電圧が低いときに出力電圧の補正量が大きくなり過ぎて、並列運転時のドループ制御の精度が悪くなって出力電流の均等化が図れなくなる。

【0010】

さらに、このDC−DCコンバータは、出力電圧の設定を変更したときも、出力電圧の補正量が変化してしまうという問題がある。例えば、同一の主トランスを用いてスイッチング電源装置を組み立て、基準電源の基準電圧信号を変更することによって、出力電圧を異なる電圧(例えば、3.3V、2.5V、2.0V等)に切り替える場合がある。出力電圧の設定が高いときは、図13(a)に示すように、スイッチング電流が発生する時比率が大きいため、スイッチング電流信号の平均電圧が高くなり、出力電圧の補正量が大きくなる。一方、入力電圧と出力電流が同じでも、出力電圧の設定が低いときは、図13(b)に示すように、スイッチング電流のピーク値はほぼ同じだが、時比率が小さいために平均電圧が低くなり、出力電圧の補正量が小さくなる。従って、出力電圧の設定を変更したときも、入力電圧が変化したときと同様の問題が発生する。

【0011】

この発明は、上記背景技術に鑑みて成されたものであり、内部素子等の個体差等の影響を容易に吸収し、所望の静的負荷変動特性を精度よく実現することができるスイッチング電源装置を提供することを目的とする。

【課題を解決するための手段】

【0012】

この発明は、入力電源と直列に接続され、所定のスイッチング周波数でオン・オフすることによって入力電圧を断続し交流電圧を発生させる主スイッチング素子と、前記交流電圧が印加される一次巻線及びそれに磁気結合した二次巻線を有する主トランスと、前記二次巻線に発生した交流電圧を直流の出力電圧に変換し、当該出力電圧及び出力電流を負荷に供給する整流平滑回路とを備え、さらに、前記出力電圧と相関のある電圧信号である間接出力電圧信号を出力する出力電圧検出回路と、所定の直流電圧である基準電圧信号を出力する基準電圧信号発生回路、及び前記基準電圧信号と前記間接出力電圧信号との差分を増幅して出力する誤差増幅器で構成されたフィードバック制御回路と、前記誤差増幅器が出力した誤差増幅信号に基づいてパルス幅変調を行い、前記間接出力電圧信号と前記基準電圧信号とが等しくなるように前記主スイッチング素子を駆動するパルス電圧を出力する主スイッチング素子駆動回路と、を備えたスイッチング電源装置であって、前記主スイッチング素子に流れるスイッチング電流を検出し、前記出力電流と相関のある電圧信号である間接出力電流信号を出力する出力電流検出回路と、所定の周波数及び時比率で前記間接出力電流信号を断続する補正量制御回路とを備え、前記出力電圧検出回路又は前記基準電圧信号発生回路は、前記補正量制御回路を介して前記間接出力電流信号を受け、当該間接出力電流信号の値及び前記間接出力電流信号を断続した前記時比率の値が大きいほど、より前記出力電圧が高くなる方向に補正した前記間接出力電圧信号又は前記基準電圧信号を出力するスイッチング電源装置である。

【0013】

前記補正量制御回路には、前記入力電圧の状態を示す入力電圧信号、又は前記出力電圧を安定化する目標値を示す出力電圧設定信号が入力され、前記補正量制御回路は、前記入力電圧が高いときほど、且つ、前記出力電圧の目標値が低いときほど、前記前記間接出力電流信号を断続する時比率を大きくする制御を行う。

【0014】

前記主スイッチング素子のスイッチング周波数と、前記補正量制御回路の断続周波数とが等しいことが好ましい。また、出力電圧検出回路は、前記整流平滑回路の平滑インダクタに設けた補助巻線、又は前記主トランスに設けた補助巻線に発生する電圧を検出する構成とすることが好ましい。さらには、前記整流平滑回路は、双方向に導通可能な整流素子によって同期整流を行う構成にすることが好ましい。

【0015】

また、前記出力電流検出回路は、前記主スイッチング素子のスイッチング電流が流れる経路に、一端を信号グランドに接続して設けられ、前記スイッチング電流を電圧変換して正のスイッチング電流信号を出力する電流検出抵抗と、第一上段抵抗、第一下段抵抗及び第一直流電源を有し、前記第一直流電源のマイナス出力側が前記信号グランドに接続され、同じくプラス出力側が前記第一上段抵抗の一端に接続され、前記第一上段抵抗の他端と前記電流検出抵抗の出力端との間に前記第一下段抵抗が接続され、前記第一下段抵抗の両端に、前記第一直流電源の直流電圧を当該二つの抵抗の抵抗比で分圧した電圧と略等しい分圧電圧を発生させる第一バイアス回路と、前記第一上段抵抗及び第一下段抵抗の中点と前記信号グランドとの間に接続された第一コンデンサとで構成され、前記第一コンデンサの出力端である前記第一上段抵抗側の一端から、前記正のスイッチング電流信号を脈流又は直流に平滑した電圧と前記第一バイアス回路の前記分圧電圧とを合算した前記間接出力電流信号を出力し、前記補正量制御回路は、ソース端子が前記第一コンデンサの出力端に接続されたnチャネルMOS型FETである第一断続スイッチ素子と、一端が前記第一断続スイッチ素子のドレイン端子に接続された補正抵抗と、前記第一断続スイッチ素子のゲート端子と前記信号グランドとの間に、前記間接出力電流信号及び前記基準電圧信号よりも高い波高値を有する矩形波であって、前記第一断続スイッチ素子をオン・オフさせる駆動パルスを出力するPWMパルス発振回路とで構成され、前記基準電圧信号発生回路は、マイナス出力側が信号グランドに接続された第二直流電源と、前記第二直流電源のプラス出力側に一端が接続された第二上段抵抗と、前記第二上段抵抗の他端に接続され他端が信号グランドに接続された第二下段抵抗とで成る第二バイアス回路と、前記第二下段抵抗と並列に接続された第二コンデンサとで構成され、前記第二コンデンサの出力端である前記第二上段抵抗側の一端に前記補正抵抗の他端が接続され、前記第二コンデンサの出力端から、前記第二直流電源を第二上段抵抗及び第二下段抵抗の抵抗比で分圧して前記第二下段抵抗に発生する分圧電圧と、前記補正量制御回路によって断続された前記間接出力電流信号を脈流又は直流に平滑した電圧とを合算した前記基準電圧信号を出力する。

【0016】

さらに、前記補正量制御回路は、前記補正抵抗と前記第二コンデンサとの接続点にnチャネルMOS型FETである第二断続スイッチ素子が挿入され、前記第二断続スイッチ素子のドレイン端子が前記補正抵抗の一端に接続され、ソース端子が前記第二コンデンサの出力端に接続され、ゲート端子が前記第一断続スイッチの前記ゲート端子に接続されている。

【0017】

前記第一バイアス回路及び第二バイアス回路は、前記出力電流がゼロのとき、前記第一又は第二断続スイッチ素子のオン・オフの時比率によらず、前記間接出力電流信号及び前記基準電圧信号が等しくなるように設けられていることが好ましい。また、前記第一バイアス回路及び第二バイアス回路の前記第一直流電源及び第二直流電源は、一つの直流電源が兼用されていることが好ましい。

【0018】

また、前記出力電流検出回路は、前記主スイッチング素子のスイッチング電流が流れる経路に、一端を信号グランドに接続して設けられ、前記スイッチング電流を電圧変換して負のスイッチング電流信号を出力する電流検出抵抗と、第一上段抵抗、第一下段抵抗及び第一直流電源を有し、前記第一直流電源のマイナス出力端が前記信号グランドに接続され、同じくプラス出力端が前記第一上段抵抗の一端に接続され、前記第一上段抵抗の他端と前記電流検出抵抗の出力端との間に前記第一下段抵抗が接続され、前記第一下段抵抗の両端に、前記第一直流電源の電圧を当該二つの抵抗の抵抗比で分圧した電圧と略等しい分圧電圧を発生させる第一バイアス回路と、前記第一上段抵抗及び第一下段抵抗の中点と前記信号グランドとの間に接続された第一コンデンサとで構成され、前記第一コンデンサの出力端である前記第一上段抵抗側の一端から、前記負のスイッチング電流信号を脈流又は直流に平滑した電圧と前記第一バイアス回路の前記分圧電圧とを合算した前記間接出力電流信号を出力し、前記補正量制御回路は、ソース端子が前記第一コンデンサの出力端に接続されたnチャネルMOS型FETである第一断続スイッチ素子と、一端が前記第一断続スイッチ素子のドレイン端子に接続された補正抵抗と、前記第一断続スイッチ素子のゲート端子と前記信号グランドとの間に、前記間接出力電流信号及び前記間接出力電圧信号よりも高い波高値を有する矩形波であって、前記第一断続スイッチ素子をオン・オフさせる駆動パルスを出力するPWMパルス発振回路とで構成され、前記出力電圧検出回路は、一端が前記補正抵抗の他端に接続され、他端が信号グランドに接続された第三コンデンサを備え、

前記第三コンデンサの出力端である前記補正抵抗側の一端から、前記出力電圧と相関のある電圧信号である前記間接出力電圧信号と、前記補正量制御回路によって断続された前記間接出力電流信号を脈流又は直流に平滑した電圧と合算した前記間接出力電圧信号を出力する。

【0019】

さらに、前記補正量制御回路は、前記補正抵抗と前記第三コンデンサとの接続点にnチャネルMOS型FETである第二断続スイッチ素子が挿入され、前記第二断続スイッチ素子のドレイン端子が前記補正抵抗の一端に接続され、ソース端子が前記第三コンデンサの出力端に接続され、ゲート端子が前記第一断続スイッチの前記ゲート端子に接続されている。

【0020】

前記第一バイアス回路及び前記出力電圧検出回路は、前記出力電流がゼロのとき、前記第一又は第二断続スイッチ素子のオン・オフの時比率によらず、前記間接出力電流信号及び前記間接出力電圧信号が等しくなるように設けられていることが好ましい。

【発明の効果】

【0021】

このスイッチング電源装置は、補正量制御回路が間接出力電流信号を断続する時比率を変化させることによって出力電圧の補正量を自在に変化させることができ、所望の静的負荷変動特性を精度よく実現することができる。例えば、補正量制御回路にデジタルプロセッサを組み込み、デジタルプロセッサに設定された演算式に基づいて断続の時比率を決定すれば、インテリジェント性の高い補正量制御回路を容易に構成することができる。

【0022】

また、補正制御回路の断続周波数と主スイッチング素子のスイッチング周波数を正確に一致させることによって、出力電圧に不要なビートノイズが発生するのを防止することができる。さらに、整流平滑回路を、双方向に導通可能な整流素子によって同期整流を行う構成にすれば、補正量制御回路が断続する時比率を決定する演算式を簡単化することができる。

【図面の簡単な説明】

【0023】

【図1】この発明のスイッチング電源装置の第一実施形態の構成を示すブロック図である。

【図2】第一実施形態のスイッチング電源装置の具体的な構成を示す回路図である。

【図3】第一実施形態のスイッチング電源装置のPWMパルス発振回路の動作を説明するタイムチャートである。

【図4】第一実施形態のスイッチング電源装置の、補正量制御回路による補正がないときの静的負荷変動特性のグラフ(a)、補正量制御回路による補正があるときの基準電圧信号V2のグラフ(b)及び静的負荷変動特性のグラフ(c)である。

【図5】補正量制御回路の変形例を用いた第一実施形態のスイッチング電源装置の回路図である。

【図6】図3の補正量制御回路の動作を説明する回路図(a)、等価回路(b)〜(d)である。

【図7】第一及び第二断続スイッチ素子の等価回路を示す図である。

【図8】図5の変形例に係る補正量制御回路の動作を説明する回路図(a)、各等価回路(b)〜(d)である。

【図9】この発明のスイッチング電源装置の第二実施形態の構成を示す回路図である。

【図10】第二実施形態のスイッチング電源装置のPWMパルス発振回路の動作を説明するタイムチャートである。

【図11】この発明のスイッチング電源装置の第三実施形態の構成を示す回路図である。

【図12】従来のスイッチング電源装置における、入力電圧に対するスイッチング電流信号及び平均電圧変化を説明するタイムチャート(a),(b)である。

【図13】従来のスイッチング電源装置における、出力電圧の設定に対するスイッチング電流信号及び平均電圧の変化を説明するタイムチャート(a),(b)である。

【発明を実施するための形態】

【0024】

以下、この発明のスイッチング電源装置の第一実施形態について、図1〜4に基づいて説明する。第一実施形態のスイッチング電源装置10は、図1のブロック図に示すように、シングルエンディッドフォワード方式の電力変換部を有し、入力端12a,12bに印加された直流入力電源14の入力電圧Viを直流の電圧Voに変換し、出力端16a,16bに接続された負荷18に出力電圧Voと出力電流Ioを供給する装置である。

【0025】

入力端12a,12bの間には、主トランス20の一次巻線20aと主スイッチング素子22の直列回路が接続されている。主スイッチング素子22は、ここではnチャネルMOS型FETであり、主スイッチング素子駆動回路24が出力する駆動パルスVg22によって駆動される。そして、入力電圧Viを、所定のスイッチング周波数f22及びオン時比率D22で断続し、一次巻線20aの両端に交流電圧を発生させる。

【0026】

主トランス20は、一次巻線20aと密に磁気結合した二次巻線20bを有し、二次巻線20bの両端に整流平滑回路26が接続されている。整流平滑回路26は、双方向に導通可能なnチャネルMOS型FETを用いた2つの整流素子28と、主スイッチング素子22のオン・オフと同期をとって整流素子28をオン・オフ駆動する同期整流駆動回路30と、ローパスフィルタを成す平滑インダクタ32及び平滑コンデンサ34とで構成され、二次巻線20bに発生する交流電圧を整流素子28で整流し、その整流電圧を平滑インダクタ32及び平滑コンデンサ34を通して平滑し、平滑コンデンサ32の両端を引き出した出力端16a,16bの間に出力電圧Voを発生させる。

【0027】

出力電圧Voを安定化する制御は、平滑インダクタ32に設けた補助巻線36、出力電圧検出回路38、フィードバック制御回路40及び主スイッチング素子駆動回路24によって行う。出力電圧検出回路38は、補助巻線36の両端に接続され、補助巻線36に発生する電圧から出力電圧Voと相関のある間接出力電圧信号V3を出力する。この実施形態では、後述する補正量制御回路46による補正が出力電圧検出回路38には加わらないので、出力電圧Voに略比例した直流の電圧V3sが間接出力電圧信号V3として出力される。

【0028】

フィードバック制御回路40は、基準電圧信号発生回路42と誤差増幅器44とで構成されている。基準電圧信号発生回路42は、直流電圧である基準電圧信号V2を出力する回路であり、後述する補正量制御回路46による補正分ΔVyと、一定の直流電圧V2sとを合算した電圧を基準電圧信号V2として出力する。

【0029】

誤差増幅器44は、反転入力端子に入力された間接出力電圧信号V3と、非反転入力端子に入力された基準電圧信号V2の差分を反転増幅し、主スイッチング素子駆動回路24に向けて誤差増幅信号Vkを出力する。主スイッチング素子駆動回路24は、誤差増幅信号Vkを基にパルス幅変調し、主スイッチング素子22をオン・オフさせるための駆動パルスVg22を出力する。このとき、駆動パルスVg22のハイレベルの時比率、すなわち主スイッチング素子22のオン時比率D22は、誤差増幅器44の動作により、間接出力電圧信号V3と基準電圧信号V2とが等しくなるように可変され、その結果、出力電圧Voが基準電圧信号V2に相当する所定の直流電圧に制御される。例えば、基準電圧信号V2が高めに変化すると、出力電圧Voが上昇する。

【0030】

さらに、スイッチング電源装置10は、基準電圧信号発生回路42が出力する基準電圧信号V2を出力電流Io等に応じて補正する動作を行うため、出力電流検出回路48及び補正量制御回路46を備えている。出力電流検出回路48は、主スイッチング素子22に流れるスイッチング電流I22を検出し、出力電流Ioと相関のある直流又は脈流の電圧信号である間接出力電流信号V1を出力する。補正量制御回路46は、出力電流検出回路48の出力と基準電圧発生回路42との間に設けられ、間接出力電流信号V1を所定の周波数f46及びオン時比率D46で断続する。

【0031】

基準電圧信号発生回路42が出力する基準電圧信号V2は、上述したように、一定の直流電圧V2sと補正量制御回路46による補正分ΔVyとを合算した電圧であり、出力電流検出回路48が出力する間接出力電流信号V1の波高値が大きいほど、また、補正量制御回路が導通するオン時比率D46が大きいほど、大きな補正分ΔVyを発生させる。詳しくは後の動作説明の中で述べる。

【0032】

次に、上記の出力電流検出回路48、補正量制御回路46、フィードバック制御回路40の基準電圧信号発生回路42、及び出力電圧検出回路38の具体的な回路構成について、図2の回路図に基づいて説明する。

【0033】

出力電流検出回路48は、電流検出抵抗50、第一バイアス回路52及び第一コンデンサ54で構成されている。電流検出抵抗50は、主スイッチング素子22のソース端子と信号グランドに接続される入力端12bとの間に設けられ、主スイッチング素子22側の一端から、スイッチング電流I22を電圧変換した正のスイッチング電流信号を出力する。第一バイアス回路52は、マイナス出力が信号グランドに接続されプラス出力から一定の直流電圧Vrを出力する直流電源56と、そのプラス出力に一端が接続された第一上段抵抗52aと、第一上段抵抗52aの他端と電流検出抵抗50の出力端との間に接続された第一下段抵抗52bとで構成されている。直流電源56は、第一バイアス回路52の第一直流電源であり、後述する第二バイアス回路66の第二直流電源としても使用される。また、2つの抵抗52a,52bは、電流検出抵抗50に比べて十分大きい抵抗値を有している。従って、第一下段抵抗52bの両端に、直流電圧Vrを2つの抵抗52a,52bの抵抗比で分圧した電圧と略等しい分圧電圧V1sが発生する。第一コンデンサ54は、2つの抵抗52a,52bの中点と信号グランドとの間に接続され、2つの抵抗52a,52bの中点側の一端から、電流検出抵抗50のスイッチング電流信号を脈流又は直流に平滑した正の電圧ΔVxと、第一バイアス回路52の分圧電圧V1sとを合算した間接出力電流信号V1を出力する。

【0034】

補正量制御回路46は、図2に示すように、第一断続スイッチ素子60、PWMパルス発振回路62及び補正抵抗64で構成されている。第一断続スイッチ素子60は、ソース端子が第一コンデンサ54の出力端に接続され、ドレイン端子が補正抵抗64の一端に接続されたnチャネルMOS型FETであり、PWMパルス発振回路62がゲート端子と信号グランドとの間に出力する駆動パルスVg60によってオン・オフ駆動される。

【0035】

PWMパルス発振回路62は、CLK発振回路62a、CPU62b、フラッシュメモリ62c及びパルス発生回路62dで構成されている。CLK発振回路62aは、第一断続スイッチ60の断続周波数f46よりも十分高い周波数のシステムクロックであるクロック信号Vckを出力する。CPU62bには、後述する第1及び第2レジスタ設定値R1,R2を算出する演算を行うことができるようにプログラムが設定されている。演算式に含まれている係数は、デフォルト設定されているものを除き、フラッシュメモリ62cから読み出す。また、CPU62bは、入力電圧Viの状態を示す入力電圧信号Virと、出力電圧Voの目標値を示す出力電圧設定信号Vorを外部から取得し、演算式にパラメータ入力する。

【0036】

パルス発生回路62dは、クロック信号Vckと第1及び第2レジスタ設定値R1,R2を受け、周波数がf46、ハイレベルの時比率がD46の駆動パルスVg60を生成する。例えば、図3に示すように、クロック信号Vckをカウントするカウンタに、第1レジスタ設定値R1として100カウント、第2レジスタ設定値R2として50カウントが付与された場合、カウンタのカウント数が第2レジスタ設定値R2に達するまでの間(1〜50カウントの間)は駆動パルスVg60をハイレベルに保持し、カウント数が第2レジスタ設定値を超え第1レジスタ設定値に達するまでの間(51〜100カウントの間)はローレベルに保持する。そして、100カウントを超えるとカウント数をリセットして1カウントに戻る。この動作を繰り返すことによって、周波数f46がクロック信号Vckの周波数fckの1/100で、ハイレベルの時比率D46が50%の駆動パルスVg60を発生させる。従って、CPU62bの演算処理の結果、第2レジスタ設定値R2が変更されると、時比率D46が0〜100%の範囲で変化することができる。駆動パルスVg60の波高値Vg60pについては後で述べる。

【0037】

補正抵抗64は、一端が第一断続スイッチ素子60のドレイン端子に、他端がフィードバック制御回路40の基準電圧信号発生回路42に接続され、第一断続スイッチ素子60に流れる電流を制限する働きをする。

【0038】

基準電圧信号発生回路42は、第二バイアス回路66と第二コンデンサ68とで構成されている。第二バイアス回路66は、マイナス出力が信号グランドに接続されプラス出力から一定の直流電圧Vrを出力する直流電源56と、そのプラス出力に一端が接続された第二上段抵抗66aと、第二上段抵抗66aの他端と信号グランドとの間に接続された第二下段抵抗66bとで構成されている。直流電源56は、第二バイアス回路66の第二直流電源であり、上述した第一バイアス回路52の第一直流電源としても使用されている。第二コンデンサ68は、第二下段抵抗66bの第二上段抵抗66a側の一端と信号グランドとの間に接続され、さらに、第二コンデンサ68の第二上段抵抗66a側の一端に、補正量制御回路46の補正抵抗64の他端が接続されている。従って、第二コンデンサ68は、第二上段抵抗66a側の一端から、直流電圧Vrを2つの抵抗66a,66bの抵抗比で分圧した分圧電圧V2sと、補正量制御回路46によって断続された間接出力電流信号V1を脈流又は直流に平滑した電圧ΔVyとを合算した基準電圧信号V2を出力する。

【0039】

なお、この実施形態では、第二上段抵抗66a及び第二下段抵抗66bの抵抗比が、第一バイアス回路52の第一上段抵抗52a及び第一下段抵抗52bの抵抗比と等しくなるように設定されている。従って、同じ直流電圧Vrを等しい抵抗比で分圧するので、基準電圧信号発生回路42の分圧電圧V2sは、出力電流検出回路48の分圧電圧V1sと等しい。また、第一断続スイッチ素子60は、ソースからドレインの向きに導通可能な図示しない寄生ダイオードを備えているが、間接出力電流信号V1のΔVx分が寄生ダイオードの順方向電圧を超えないように諸定数が設定されているので、寄生ダイオードが導通することはない。また、PWMパルス発振回路62が出力する駆動パルスVg60の波高値Vg60pは、第一断続スイッチ素子60を確実にオン・オフさせるため、間接出力電流信号V1及び基準電圧信号V2よりも十分高い電圧に設定されている。

【0040】

出力電圧検出回路38は、補助巻線36に接続されたダイオード70及び第三コンデンサ72で成るピークホールド回路と、第三コンデンサ72の両端に接続された放電抵抗74とで構成され、第三コンデンサ72の一端が信号グランドに接続され、正電圧が発生する側の一端が出力電圧検出回路38の出力端38aとなる。主スイッチング素子22がオフの期間、補助巻線36に出力電圧Voに略比例した波高値V3sの電圧が発生し、ダイオード70がそのタイミングで導通することによって第三コンデンサ72を充電する。従って、出力端38aには直流の電圧V3sが発生し、間接出力電圧信号V3として出力される。

【0041】

次に、スイッチング電源装置10の動作について説明する。まず、説明の便宜のため、スイッチング電源装置10の補正量制御回路46の第一断続スイッチ素子60が停止している状態(オン時比率D46=0%に固定されている状態)を考える。この場合、出力電圧Vo−出力電流Ioの関係、すなわち静的負荷変動特性は、式(1)のように表わされる。

【数1】

【0042】

ここで、Vosは、出力電圧Ioがゼロアンペアのときの出力電圧Vo(以下、Vosを無負荷出力電圧と称す。)であり、Rwは、二次側の出力電流Ioが流れる経路にある整流素子28の導通抵抗や配線パターンの抵抗分等の合成抵抗分であり、ΔVwは、抵抗分Rwに出力電流Ioが流れたときの電圧降下である。

【0043】

出力電圧検出回路38が出力する間接出力電圧信号V3は、フィードバック制御回路40及び主スイッチング素子駆動回路24の動作により、基準電圧信号V2(ここでは、分圧電圧V2s)と等しくなるように制御されるので、平滑インダクタ32の両端電圧は、出力電流Ioの大小によらず、無負荷出力電圧Vosに保持される。従って、図4(a)に実線で示すように、静的負荷変動特性は、出力電流Ioが大きくなるほど、出力電圧Voが右肩下がりで低下する特性となり、大きな静的負荷変動が発生する。

【0044】

次に、図4(b),(c)を用いて、補正量制御回路御46の第一断続スイッチ素子60が所定のオン時比率D46でオン・オフし、図4(c)の実線に示す所望の静的負荷変動特性を実現する動作を説明する。

【0045】

出力電流Ioがゼロのときは、スイッチング電流信号を平滑した電圧ΔVxがほぼゼロになるので、間接出力電流信号V1が分圧電圧V1sになる。分圧電圧V1sは、基準電圧発生回路42の分圧電圧V2sと等しいので、第一断続スイッチ素子60がオンしても、第一断続スイッチ素子60に電流が流れない。従って、オン時比率D46の大小にかかわらず補正分ΔVyがゼロになり、基準電圧信号V2が分圧電圧V2sとなる。従って、出力電圧Voは、補正量制御回路46が停止している図4(a)と同様に、無負荷出力電圧Vosに制御される。

【0046】

出力電流Ioが流れると、出力電流検出回路48にスイッチング電流信号を平滑した電圧ΔVxが発生し、間接出力電流信号V1が、分圧電圧V1sよりも電圧ΔVxだけ高くなる。従って、第一断続スイッチ素子60がオン・オフすることによって、間接出力電流信号V1の電圧ΔVxが断続的に第二コンデンサ68に送られ、その断続信号を脈流又は直流に平滑した補正分ΔVyが発生し、図4(b)に示すように、基準電圧信号V2が補正分ΔVyだけ補正される。基準電圧信号V2が補正分ΔVyだけ高くなると、誤差増幅器44は、間接出力電圧信号V3が補正分ΔVyだけ低いと認識し、誤差増幅信号Vkを変化させ、主スイッチング素子制御回路24が主スイッチング素子22のオン時比率D22を大きくし、図4(c)に示すように、出力電圧Voを電圧ΔVzだけ上昇させる。

【0047】

図4(b)に示すように、補正分ΔVyは、第一断続スイッチ素子60のオン時比率D46を一定値に固定した状態でも、出力電流Ioが増加するにつれて大きくなる。さらにオン時比率D46を変更すれば、補正分ΔVyが大きくなる傾きを変化させることができる。従って、オン時比率D46を調整することによって、補正分ΔVyを自在に可変することができ、所望の静的負荷変動特性を実現することができる。特に、オン時比率D46は、CPU62bとフラッシュメモリ62cを用いたデジタル演算処理によって決定するので、高いインテリジェント性を有し、様々なアプリケーションに対応できる。

【0048】

例えば、スイッチング電源装置10を工場で量産したとき、オン時比率D46を一律の値にデフォルト設定して組み立てた結果、無負荷出力電圧Vosのばらつきは許容値内であるが、製品個々の抵抗Rwのばらつきが大きいため、静的負荷変動特性の規格を逸脱する製品が発生したとする。この問題は、背景技術で説明した特許文献1のDC−DCコンバータでは対策が困難であるが、この実施形態のスイッチング電源装置10であれば、以下に説明する方法で容易に解決することができる。

【0049】

まず、組み立てた製品個々に行う通電試験において、オン時比率D46を0%に固定して動作させ、特定の出力電流Ioにおける電圧降下ΔVwを測定し、フラッシュメモリ62cに書き込む。式(1)から分かるように、電圧降下ΔVwは抵抗Rwに略比例するので、電圧降下ΔVwを測定すれば、抵抗Rwの個体差の的確に把握することができる。次に、CPU62bが、フラッシュメモリ62cから電圧降下ΔVwを読み取り、目標とする静的負荷変動特性を得るため、その特定の出力電流Ioにおいて必要な補正分ΔVyを算出し、その補正分ΔVyを得るためのオン時比率D46を算出し、さらに、その時比率D46を実現するための第2レジスタ設定値R2を算出する。そして、PWMパルス発振回路62が、CPU62bが算出した第2レジスタ設定値R2を受け、第一断続スイッチ素子60をオン・オフさせる駆動パルスVg60を発生する。すると、第一断続スイッチ素子60のオン・オフ動作によって最適な補正分ΔVyが基準電圧信号V2に重畳され、目標の静的負荷変動特性に非常に近い静的負荷変動特性を得ることができる。このように、製品の通電試験でソフト的な初期設定を行うだけで、各製品の静的負荷変動特性を、簡単に且つ精度よく一致させることができる。

【0050】

また、例えば、入力電圧Viの変動や出力電圧Voの設定の違いよって静的負荷変動特性が大きく変化し、「静的負荷変動が小さく、良好なドループ制御も可能なスイッチング電源装置10を実現することができない」という問題が発生することも考えられる(この問題は、上記の背景技術の中で、図12、図13を用いて説明した問題である)。しかし、この問題についても、CPU62bがオン時比率D46を算出する演算式に、外部から入力される入力電圧信号Vir及び出力電圧設定信号Vorをパラメータとして加えておくことによって、容易に解決することができる。

【0051】

図12、図13から分かるように、オン時比率D46を一定値に固定すると、入力電圧Viが低いときほど、また出力電圧Voの設定値が高いときほど、間接出力電流信号V1の電圧ΔVx成分が大きくなり、補正分ΔVyも大きくなり、その結果、補正による出力電圧Voの上昇電圧ΔVzが大きくなる。反対に、入力電圧Viが高いときほど、また出力電圧Voの設定値が低いときほど、間接出力電流信号V1の電圧ΔVx成分が小さくなり、補正分ΔVyも小さくなり、その結果、補正による出力電圧Voの上昇電圧ΔVzが小さくなる。従って、入力電圧Viと出力電圧Voの設定値が変化しても、一定の補正分ΔVyが得られるようにすれば、補正による出力電圧Voの上昇電圧ΔVzが一定になり、この問題を解決することができる。具体的には、CPU62bがオン時比率D46を算出する演算式に、スイッチング電源装置10の実際の動作状態をモニタした入力電圧信号Vir及び出力電圧設定信号Vorをパラメータとして加え、さらに、入力電圧Vi及び出力電圧Voの設定値が補正分ΔVyに与える影響をキャンセルする係数等を盛り込んでおけばよい。このように、入力電圧Viの状態及び出力電圧Voの設定を加味してオン時比率D46を算出する演算式を設定することによって、静的負荷変動が小さく、且つ良好なドループ制御も可能なスイッチング電源装置10を実現することができる。

【0052】

以上説明したように、スイッチング電源装置10は、補正量制御回路46が間接出力電流信号V1を断続するオン時比率D46を変化させることによって、補正による出力電圧Voの上昇電圧ΔVzを自在に変化させることができ、所望の静的負荷変動特性を精度よく実現することができる。特に、補正量制御回路にデジタルプロセッサを組み込み、デジタルプロセッサに設定された演算式に基づいて断続の時比率D46を決定することにより、インテリジェント性の高い補正量制御回路46を容易に構成することができる。

【0053】

また、ここでは、第一バイアス回路52が決定する分圧電圧V1sと第二バイアス回路66が決定する分圧電圧V2sとが等しくなるように設定されているので、図4(b)に示すように、オン時比率D46の値にかかわらず、出力電流Ioがゼロアンペアのときの補正分ΔVzをほぼゼロにすることができる。従って、入力電圧Vi及び出力電圧Voの設定値の情報を加味してオン時比率D46を算出する場合でも、設定する演算式を簡単化することができる。また、整流平滑回路26が、双方向に導通可能な整流素子28によって同期整流を行う構成なので、出力電流Ioとスイッチング電流I22を平滑したスイッチング電流信号ΔVxとの関係をほぼ線形な式で表わすことができ、オン時比率D46を算出する演算式を簡単化することができる。ただし、ダイオード整流等の構成であっても、それに応じた演算式を設定すれば、使用可能である。 さらに、第一及び第二バイアス回路52,66の第一及び第二直流電源が一つの直流電源56で兼用されているので、例えば、出力電圧Voの設定を3.3Vから2.0Vに切り替えるとき、直流電圧Vrを低い電圧値に変更するだけで対応することができる。また、この直流電圧Vrを、CPU62bに入力する出力電圧設定信号Vorとして使用することも可能である。

【0054】

次に、この実施形態の補正量制御回路46の変形例である補正量制御回路76について、図5〜図8に基づいて説明する。ここで、上記のスイッチング電源装置10と同様の構成は、同一の符号を付して説明を省略する。補正量制御回路76は、図5に示すように、上記補正量制御回路46の構成に加え、第二断続スイッチ素子78を設けたものであり、その他の構成は補正量制御回路46と同じである。

【0055】

第二断続スイッチ素子78は、第一断続スイッチ素子60と同一のnチャネルMOS型FETであり、補正抵抗64の第一断続スイッチ素子60が接続されていない側の一端にドレイン端子が接続され、第一断続スイッチ素子60のゲート端子に自身のゲート端子が接続され、基準電圧信号発生回路42の第二コンデンサ68の出力端にソース端子が接続されている。従って、補正量制御回路76は、第一及び第二断続スイッチ素子60,78を同位相でオン・オフさせることによって間接出力電流信号V1を断続する。

【0056】

補正量制御回路76は、特に、出力電流Ioがゼロアンペアのときの上記補正量制御回路46の動作を改善する効果がある。そこで、まず、図6を用いて上記補正量制御回路46の動作を説明し、それと対比しながら、変形例の補正量制御回路76の動作を説明する。

【0057】

図6(a)は、図2の回路図から、主要な部品である第一断続スイッチ素子60、パルス発生回路62d、補正抵抗64、誤差増幅器44、第一コンデンサ54及び第二コンデンサ68の部分を抜粋した回路図である。なお、パルス発生回路62dが出力する駆動パルスVg60の波高値Vg60pは、上述したように、間接出力電流信号V1及び基準電圧信号V2よりも十分高い電圧に設定されている。

【0058】

nチャネルMOS型FETである第一断続スイッチ素子60は、図7の等価回路に示すように、パルス発生回路62dが発生する駆動パルスVg60がハイレベルのときにオンするドレイン・ソース間のスイッチSW60、ドレイン・ソース間の寄生コンデンサCds60、ドレイン・ゲート間の寄生コンデンサCdg60及びゲート・ソース間の寄生コンデンサCgs60を用いて表わすことができる。そこで、図6(a)の回路図をスイッチSW60等に置き換えた図6(b)〜(d)に基づき、スイッチング電源装置10の出力電流Ioがゼロアンペアのときの動作を説明する。ここで、説明の便宜のため、図6(b)が開始する前の初期状態として、間接出力電流信号V1及び基準電圧信号V2が、互いに等しく分圧電圧V1s(=分圧電圧V2s)になっているとする。

【0059】

図6(b)は、駆動パルスVg60がゼロボルトから波高値Vg60pに向かって上昇している途中の動作を示しており、矢印で示すように、パルス発生回路62dを起点とする2つの経路に急峻な電流が流れる。スイッチSW60は、寄生コンデンサCgs60が充電され、その両端電圧が第一断続スイッチ素子60のオン閾値を超えたタイミングでオンに転じる。第一コンデンサ54の間接出力電流信号V1は、矢印で示す電流により、僅かに上昇する(以下、この電圧上昇分をΔVe1とする)。電圧上昇分ΔVe1は、寄生コンデンサCgs60,Cds60,Cgd60と第一コンデンサ54との容量比や波高値Vg60pに依存するので、図4(b),(c)で説明した理想的な動作を行うためには、第一コンデンサ54の容量を寄生コンデンサCgs60,Cds60,Cgd60よりも極めて大きな値に設定することによって電圧ΔVe1を小さく抑え、間接出力電流信号V1が分圧電圧V1sに保持されるようにすることが好ましい。しかし、静的負荷変動特性の補正を出力電流Ioに対してより高速に応答させるためには、第一コンデンサ54の容量をある程度小さい値に設定する必要がある。ここでは、第一コンデンサ54の容量が、ある程度の小さい値が設定されており、第一コンデンサ54の間接出力電流信号V1が分圧電圧V1sから電圧ΔVe1だけ僅かに上昇する。一方、第二コンデンサ68は、補正抵抗64の存在によってほとんど電流が流れず、基準電圧信号V2が分圧電圧V2s(=分圧電圧V1s)に保持される。

【0060】

図6(c)は、駆動パルスVg60が波高値Vg60pを維持し、スイッチSW60がオンしている期間の動作を示している。この状態では、寄生コンデンサCgs60,Cds60,Cgd60には電流が流れないが、矢印で示すように、第一コンデンサ54を起点とする補正抵抗64、第二コンデンサ68の経路に、電圧上昇分ΔVe1を緩やかに放電する電流が流れる。この電流により、第一コンデンサ54の間接出力電流信号V1が分圧電圧V1sに向かって低下し、第二コンデンサ68の基準電圧信号V2が分圧電圧V

2sから僅かに上昇する(以下、この電圧上昇分をΔVe2とする)。電圧上昇分ΔVe2は、駆動パルスVg60が波高値Vg60pを維持する時間、すなわち、スイッチSW60のオン時比率D46によって異なる値になる。従って、この期間中の間接出力電流信号V1及び基準電圧信号V2の状態は一律ではない。

【0061】

図6(d)は、駆動パルスVg60が波高値Vg60pからゼロボルトに向かって低下している途中の動作を示しており、矢印で示すように、第一コンデンサ54を起点とする2つの経路に急峻な電流が流れる。スイッチSW60は、寄生コンデンサCgs60が放電され、その両端電圧が第一断続スイッチ素子60のオン閾値未満になったタイミングでオフに転じる。第一コンデンサ54は、図6(c)の期間の電圧上昇分が急峻に放電され、間接出力電流信号V1が分圧電圧V1sまで瞬時に低下する。一方、第二コンデンサ68には、補正抵抗64の存在によりほとんど電流が流れない状態でスイッチSW60がオフするため、基準電圧信号V2は、図6(c)が終了したときの電圧、すなわち、分圧電圧V2s(=分圧電圧V1s)よりも電圧上昇分ΔVe2だけ高い電圧に保持される。

【0062】

このように、上記の補正量制御回路46は、静的負荷変動特性の補正を高速化する目的で第一コンデンサ54の容量を小さくした場合に、出力電流Ioがゼロアンペアであっても、間接出力電流信号V1及び基準電圧信号V2が分圧電圧V1s及びV2s(=分圧電圧V1s)に保持されず、電圧ΔVe1やΔVe2の分だけ変化する。しかも、電圧上昇分ΔVe2は、オン時比率D46の状態によって変動する不安定なものである。従って、電圧上昇分ΔVe1,ΔVe2は、図4(b),(c)で説明した「出力電流Ioの増加に対してのみ補正分ΔVyが比例して増加する」という理想的な動作の妨げになる不安定な誤差要因といえる。

【0063】

それに対して、変形例に係る補正量制御回路76の場合、第二断続スイッチ素子78が付加されているので、上記の補正量制御回路46とは動作が異なる。以下、補正量制御回路76の場合の動作を、図8に基づいて説明する。

【0064】

図8(a)は、図5の回路図から、主要な部品である第一断続スイッチ素子60、パルス発生回路62d、補正抵抗64、誤差増幅器44、第一コンデンサ54、第二コンデンサ68、及び第二断続スイッチ素子78の部分を抜粋した回路図である。上記と同様に、パルス発生回路62dが出力する駆動パルスVg60の波高値Vg60pは、間接出力電流信号V1及び基準電圧信号V2よりも十分高い電圧に設定されている。また、図8(b)〜(d)は、図8(a)の回路図をスイッチSW60,SW78等に置き換えた等価回路であり、これらの各等価回路を用いて、スイッチング電源装置10の出力電流Ioがゼロアンペアのときの動作を説明する。ここで、説明の便宜のため、図8(b)が開始する前の初期状態として、出力電流信号V1及び基準電圧信号V2が、互いに等しく分圧電圧V1s(=分圧電圧V2s)になっているとする。

【0065】

図8(b)は、駆動パルスVg60がゼロボルトから波高値Vg60pに向かって上昇している途中の動作を示しており、矢印で示すように、パルス発生回路62dを起点とする4つの経路に急峻な電流が流れる。スイッチSW60,SW78は、寄生コンデンサCgs60,Cgs78が充電され、それらの両端電圧が第一及び第二断続スイッチ素子60,78のオン閾値を超えたタイミングで、ほぼ同時にオンに転じる。第一コンデンサ54の間接出力電流信号V1は、矢印で示す電流により僅かに上昇する。この電圧上昇分は、上記補正量制御回路46と同様にΔVe1である。一方、この補正量制御回路76の場合、第二コンデンサ68にも矢印に示す電流が流れ、第一コンデンサ54と第二コンデンサ68が同じ容量の素子の場合、基準電圧信号V2が電圧ΔVe2(=ΔVe1)だけ上昇する。

【0066】

図8(c)は、駆動パルスVg60が波高値Vg60pを維持し、スイッチSW60,SW78がオンしている期間の動作を示している。この期間は、各コンデンサの電位バランスがとれているので、どの経路にも電流が流れず、間接出力電流信号V1及び基準電圧信号V2は、図8(b)が終了したときの電圧、すなわち、分圧電圧V1sよりもΔVe1だけ上昇した電圧に保持される。従って、この期間中の間接出力電流信号V1及び基準電圧信号V2は、スイッチSW60,SW78のオン時比率D46によらず一律である。

【0067】

図8(d)は、駆動パルスVg60が波高値Vg60pからゼロボルトに向かって低下している途中の動作を示しており、矢印で示すように、第一コンデンサ54を起点とする2つの経路と第二コンデンサ68を起点とする2つの経路とに急峻な電流が流れる。スイッチSW60,SW78は、寄生コンデンサCgs60,Cgs78が放電され、それぞれ両端電圧が第一及び第二断続スイッチ素子60,78のオン閾値未満になったタイミングで、ほぼ同時にオフに転じる。第一コンデンサ54は、電圧上昇分ΔVe1が急峻に放電され、上記補正量制御回路46と同様に、出力電流信号V1が分圧電圧V1sまで瞬時に低下する。一方、この補正量制御回路76の場合は、第二コンデンサ68の電圧上昇分ΔVe2(=ΔVe1)も同時に放電され、基準電圧信号V2が分圧電圧V2s(=分圧電圧V1s)まで瞬時に低下する。

【0068】

このように、変形例に係る補正量制御回路76は、第一コンデンサ54の容量を小さくした場合に、出力電流Ioがゼロアンペアであっても間接出力電流信号V1及び基準電圧信号V2が分圧電圧V2s(=分圧電圧V1s)に保持されず、電圧ΔVe1(=ΔVe2)だけ上昇する。しかし、電圧上昇分ΔVe1は、出力電流Ioやオン時比率D46の状態によらず、第一コンデンサ54(=第二コンデンサ68)と寄生コンデンサCgs60(=Cgs78)、Cgd60(=Cgd78)、Cds60(=Cds78)の関係で決定される一律で安定なものである。電圧ΔVe2の上昇は、出力電圧Voの上昇させることになるが、一律で安定な値であるため、容易にキャンセルすることができる。従って、電圧上昇分ΔVe1は、図4(b),(c)で説明した「出力電流Ioの増加に対してのみ補正分ΔVyが比例して増加する」という理想的な動作を実現することができる。

【0069】

次に、この発明のスイッチング電源装置の第二実施形態について、図9、図10に基づいて説明する。ここで、上記のスイッチング電源装置10と同様の構成は、同一の符号を付して説明を省略する。第二実施形態のスイッチング電源装置80は、図9に示すように、上記のスイッチング電源装置10のPWMパルス発振回路62を新たなパルス発生回路PWMパルス発振回路82に置き換えることによって、補正量制御回路46の断続周波数f46と主スイッチング素子22のスイッチング周波数f22とが一致する動作を行うものである。その他の構成は、上記のスイッチング電源装置10と同じである。

【0070】

PWMパルス発振回路82は、CLK発振回路62a、新たなCPU82b、フラッシュメモリ62c及び新たなパルス発生回路82dで構成されている。CLK発振回路62aは、第一断続スイッチ60の断続周波数f46よりも十分高い周波数のシステムクロックであるクロック信号Vckを出力する。CPU82bには、第1〜第3レジスタ設定値R1,R2,R3を算出する演算を行うことができるようにプログラムが設定されている。演算式に含まれている係数は、デフォルト設定されているものを除き、フラッシュメモリ62cから読み出す。また、CPU82bは、入力電圧信号Virと、出力電圧設定信号Vorを外部から取得し、演算式にパラメータ入力する。

【0071】

パルス発生回路82dは、クロック信号Vckと第1及び第2レジスタ設定値R1,R2に基づいて、周波数がf46でハイレベルの時比率がD46の駆動パルスVg60を生成すると共に、クロック信号Vckと第1及び第3レジスタ設定値R1,R3に基づいて、周波数がf46でハイレベルの時比率がD24の同期パルスV24を生成する。例えば、図10に示すように、クロック信号Vckをカウントするカウンタに、第1レジスタ設定値R1として100カウント、第2レジスタ設定値R2として30カウント、第3レジスタ設定値R2として60カウントが付与されているとする。駆動パルスVg60については、カウンタのカウント数が第2レジスタ設定値R2に達するまでの間(1〜30カウントの間)はハイレベルに保持し、カウント数が第2レジスタ設定値を超え第1レジスタ設定値に達するまでの間(31〜100カウントの間)はローレベルに保持する。そして、100カウントを超えるとカウント数をリセットして1カウントに戻る。この動作を繰り返すことによって、周波数f46がクロック信号Vckの周波数fckの1/100、ハイレベルの時比率D46が30%の駆動パルスVg60を発生させる。

【0072】

同期パルスV24についても同様に、カウンタのカウント数が第3レジスタ設定値R3に達するまでの間(1〜60カウントの間)はハイレベルに保持し、カウント数が第3レジスタ設定値を超え第1レジスタ設定値に達するまでの間(61〜100カウントの間)はローレベルに保持する。そして、100カウントを超えるとカウント数をリセットして1カウントに戻る。この動作を繰り返すことによって、周波数が駆動パルスVg60の周波数f46と同じで、ハイレベルの時比率D24が60%の同期パルスV24を発生させる。

【0073】

駆動パルスVg60は、上述したように、第一断続スイッチ素子60のゲート端子に向けて出力され、第一断続スイッチ素子60をオン・オフさせる。同期パルスV24は、図9に示すように、主スイッチング素子駆動回路24に向けて出力される。主スイッチング素子駆動回路24は、周波数f46の同期パルスV24を受け、主スイッチング素子22の駆動パルスVg22の1周期の開始のタイミングを同期させ、駆動パルスVg22の周波数f22を同期パルスV24の周波数f46と一致させる。この動作により、主スイッチング素子22のスイッチング周波数f22と補正量制御回路46の断続周波数f46とを一致させる。

【0074】

スイッチング電源装置80は、スイッチング周波数f22と断続周波数f46とを容易に、且つ正確に一致させることができるので、互いに異なる2つの周波数が干渉したときに生じる不要なビートノイズが発生する心配がない。

【0075】

また、同期パルスV24は、時比率D24という情報も有しており、時比率D24も様々な制御に利用することができる。例えば、スイッチング素子制御回路24が、特開平2010−125524号公報のフィードフォワード制御の構成になっている場合、主スイッチング素子22のオン時比率D22が変化し得る上限値を、同期パルスV24の時比率D24で規定することによって、主トランス20の磁気飽和を容易に回避することができる。

【0076】

次に、この発明のスイッチング電源装置の第三実施形態について、図11に基づいて説明する。ここで、上記のスイッチング電源装置10と同様の構成は、同一の符号を付して説明を省略する。第三実施形態のスイッチング電源装置84は、図11に示すように、上記のスイッチング電源装置10の出力電流検出回路48を新たな出力電流検出回路86に置き換え、さらに、補正量制御回路46の補正抵抗64の出力端の接続を、出力電圧検出回路38の出力端38aに変更したものである。その他の構成は、上記のスイッチング電源装置10と同じである。

【0077】

出力電流検出回路86は、電流検出抵抗50、第一バイアス回路52及び第一コンデンサ54で構成されている。電流検出抵抗50は、信号グランドである主スイッチング素子22のソース端子と直流入力電源14が接続される入力端12bとの間に設けられ、入力端12b側の一端から、スイッチング電流I22を電圧変換した負のスイッチング電流信号を出力する。第一バイアス回路52は、マイナス出力が信号グランドに接続されプラス出力から一定の直流電圧Vrを出力する直流電源56と、そのプラス出力に一端が接続された第一上段抵抗52aと、第一上段抵抗52aの他端と電流検出抵抗50の出力端との間に接続された第一下段抵抗52bとで構成されている。2つの抵抗52a,52bは、電流検出抵抗50に比べて十分大きい抵抗値を有している。従って、第一下段抵抗52bの両端に、直流電圧Vrを2つの抵抗52a,52bの抵抗比で分圧した電圧と略等しい分圧電圧V1sが発生する。第一コンデンサ54は、2つの抵抗52a,52bの中点と信号グランドとの間に接続され、2つの抵抗52a,52bの中点側の一端から、電流検出抵抗50のスイッチング電流信号を脈流又は直流に平滑した負の電圧(−ΔVx)と、第一バイアス回路52の分圧電圧V1sとを合算した間接出力電流信号V1を出力する。

【0078】

出力電圧検出回路38は、上述したように、補助巻線36に接続されたダイオード70及び第三コンデンサ72で成るピークホールド回路と、第三コンデンサ72の両端に接続された放電抵抗74とで構成されている。しかし、ここでは、補正量制御回路46の補正抵抗64の出力端が出力端38aに接続され、出力端38aには、出力電圧Voに略比例した直流の電圧V3sが発生と、補正量制御回路46によって断続された間接出力電流信号V1を脈流又は直流に平滑した電圧(−ΔVy)とを合算した間接出力電圧信号V3を出力する。

【0079】

基準電圧信号発生回路42は、上述したように第二バイアス回路66と第二コンデンサ68とで構成されているが、補正量制御回路46の補正抵抗64の出力端が接続されていない。従って、第二コンデンサ68の第二上段抵抗66a側の一端から出力される基準電圧信号V2は、直流電圧Vrを2つの抵抗66a,66bの抵抗比で分圧した一定の分圧電圧V2sである。

【0080】

誤差増幅器44は、上述したように、反転入力端子に入力された間接出力電圧信号V3と、非反転入力端子に入力された基準電圧信号V2の差分を反転増幅し、主スイッチング素子駆動回路24に向けて誤差増幅信号Vkを出力する。そして、主スイッチング素子駆動回路24は、誤差増幅信号Vkをパルス幅変調し、主スイッチング素子22をオン・オフさせるための駆動パルスVg22を出力する。出力電圧信号V3が低めに変化すると、主スイッチング素子22のオン時比率D22が大きくなり、出力電圧Voが上昇する。

【0081】

このスイッチング電源装置84は、主スイッチング素子22及び電流検出回路86の部品配置の都合等により、電流検出抵抗50の主スイッチング素子22側の一端が信号グランドに接続されているので、電流検出抵抗50が出力するスイッチング電流信号が負の電圧になる。従って、静的出力変動特性を補正するための補正分が(−ΔVy)になる。そこで、補正分(−ΔVy)が誤差増幅器44の反転入力端子の側に入力されるように、出力電圧信号V3に合算する構成に変更し、図4(b),(c)と同様の補正が行われるようにしたものである。このスイッチング電源装置84においても、上記スイッチング電源装置10と同様の作用効果を得ることができる。

【0082】

なお、この発明のスイッチング電源装置は、上記実施形態に限定されるものではない。出力電圧検出回路は、出力電圧を電源回路の一次側で間接的に検出できるものであればよく、例えば、平滑インダクタの補助巻線を利用し、特開2008−278639号公報に開示されているような高機能回路を使用してもよい。また、主トランスに設けた補助巻線に発生する電圧から出力電圧と相関のある電圧信号を生成する構成にしてもよい。

【0083】

また、上記の実施形態では、出力電流がゼロアンペアのとき、出力電流検出回路が出力する出力電流信号V1(=V1s)と、補正量制御回路が接続される基準電圧信号発生回路が出力する基準電圧信号V2(=V2s)とを等しくすることによって、補正量制御回路を断続させる時比率を決定する演算式を簡単化できることを説明したが、電圧V1sと電圧V2sとが異なる値であっても、それに応じた演算式を設定すれば、所望の静的負荷変動特性を精度よく実現することができることは言うまでもない。

【0084】

さらに、電力変換部の構成は、シングルエンディッドフォワード方式のほか、フライバック方式、プッシュプル方式、各種ブリッジ方式など自由に選択することができる。

【符号の説明】

【0085】

10,80,84 スイッチング電源装置

20 主トランス

20a 一次巻線

20b 二次巻線

22 主スイッチング素子

24 主スイッチング素子制御回路

26 整流平滑回路

32 平滑インダクタ

36 補助巻線36

38 出力電圧検出回路

40 フィードバック制御回路

42 基準電圧信号発生回路

44 誤差増幅器

46,76 補正量制御回路

48,86 出力電流検出回路

50 電流検出抵抗

52 第一バイアス回路

52a 第一上段抵抗

52b 第一下段抵抗

54 第一コンデンサ

56 直流電源

60 第一断続スイッチ素子

62,82 PWMパルス発振回路

62a CLK発振回路

62b,82b CPU

62c フラッシュメモリ

62d,82d パルス発生回路

64 補正抵抗

66 第二バイアス回路

66a 第二上段抵抗

66b 第二下段抵抗

68 第二コンデンサ

72 第三コンデンサ

78 第二断続スイッチ素子

【特許請求の範囲】

【請求項1】

入力電源と直列に接続され、所定のスイッチング周波数でオン・オフすることによって入力電圧を断続し交流電圧を発生させる主スイッチング素子と、

前記交流電圧が印加される一次巻線及びそれに磁気結合した二次巻線を有する主トランスと、

前記二次巻線に発生した交流電圧を直流の出力電圧に変換し、当該出力電圧及び出力電流を負荷に供給する整流平滑回路と、

前記出力電圧と相関のある電圧信号である間接出力電圧信号を出力する出力電圧検出回路と、

所定の直流電圧である基準電圧信号を出力する基準電圧信号発生回路、及び前記基準電圧信号と前記間接出力電圧信号との差分を増幅して出力する誤差増幅器で構成されたフィードバック制御回路と、

前記誤差増幅器が出力した誤差増幅信号に基づいてパルス幅変調を行い、前記間接出力電圧信号と前記基準電圧信号とが等しくなるように前記主スイッチング素子を駆動するパルス電圧を出力する主スイッチング素子駆動回路と、を備えたスイッチング電源装置において、

前記主スイッチング素子に流れるスイッチング電流を検出し、前記出力電流と相関のある電圧信号である間接出力電流信号を出力する出力電流検出回路と、

所定の周波数及び時比率で前記間接出力電流信号を断続する補正量制御回路とを備え、

前記出力電圧検出回路又は前記基準電圧信号発生回路は、前記補正量制御回路を介して前記間接出力電流信号を受け、当該間接出力電流信号の値及び前記間接出力電流信号を断続した前記時比率の値が大きいほど、より前記出力電圧が高くなる方向に補正した前記間接出力電圧信号又は前記基準電圧信号を出力することを特徴とするスイッチング電源装置。

【請求項2】

前記補正量制御回路には、前記入力電圧の状態を示す入力電圧信号、又は前記出力電圧を安定化する目標値を示す出力電圧設定信号が入力され、

前記補正量制御回路は、前記入力電圧が高いときほど、且つ、前記出力電圧の目標値が低いときほど、前記前記間接出力電流信号を断続する時比率を大きくする制御を行う請求項1記載のスイッチング電源装置。

【請求項3】

前記主スイッチング素子のスイッチング周波数と、前記補正量制御回路の断続周波数とが等しい請求項1記載のスイッチング電源装置。

【請求項4】

前記出力電圧検出回路は、前記整流平滑回路の平滑インダクタに設けた補助巻線、又は前記主トランスに設けた補助巻線に発生する電圧を検出し、前記出力電圧と相関のある電圧信号である間接出力電圧信号を出力する請求項1記載のスイッチング電源装置。

【請求項5】

前記整流平滑回路は、双方向に導通可能な整流素子によって同期整流を行う請求項1記載のスイッチング電源装置。

【請求項6】

前記出力電流検出回路は、

前記主スイッチング素子のスイッチング電流が流れる経路に、一端を信号グランドに接続して設けられ、前記スイッチング電流を電圧変換して正のスイッチング電流信号を出力する電流検出抵抗と、

第一上段抵抗、第一下段抵抗及び第一直流電源を有し、前記第一直流電源のマイナス出力側が前記信号グランドに接続され、同じくプラス出力側が前記第一上段抵抗の一端に接続され、前記第一上段抵抗の他端と前記電流検出抵抗の出力端との間に前記第一下段抵抗が接続され、前記第一下段抵抗の両端に、前記第一直流電源の直流電圧を当該二つの抵抗の抵抗比で分圧した電圧と略等しい分圧電圧を発生させる第一バイアス回路と、

前記第一上段抵抗及び第一下段抵抗の中点と前記信号グランドとの間に接続された第一コンデンサとで構成され、

前記第一コンデンサの出力端である前記第一上段抵抗側の一端から、前記正のスイッチング電流信号を脈流又は直流に平滑した電圧と前記第一バイアス回路の前記分圧電圧とを合算した前記間接出力電流信号を出力し、

前記補正量制御回路は、

ソース端子が前記第一コンデンサの出力端に接続されたnチャネルMOS型FETである第一断続スイッチ素子と、

一端が前記第一断続スイッチ素子のドレイン端子に接続された補正抵抗と、

前記第一断続スイッチ素子のゲート端子と前記信号グランドとの間に、前記間接出力電流信号及び前記基準電圧信号よりも高い波高値を有する矩形波であって、前記第一断続スイッチ素子をオン・オフさせる駆動パルスを出力するPWMパルス発振回路とで構成され、

前記基準電圧信号発生回路は、

マイナス出力側が信号グランドに接続された第二直流電源と、前記第二直流電源のプラス出力側に一端が接続された第二上段抵抗と、前記第二上段抵抗の他端に接続され他端が信号グランドに接続された第二下段抵抗とで成る第二バイアス回路と、

前記第二下段抵抗と並列に接続された第二コンデンサとで構成され、

前記第二コンデンサの出力端である前記第二上段抵抗側の一端に前記補正抵抗の他端が接続され、

前記第二コンデンサの出力端から、前記第二直流電源を第二上段抵抗及び第二下段抵抗の抵抗比で分圧して前記第二下段抵抗に発生する分圧電圧と、前記補正量制御回路によって断続された前記間接出力電流信号を脈流又は直流に平滑した電圧とを合算した前記基準電圧信号を出力する請求項1乃至5の何れか記載のスイッチング電源装置。

【請求項7】

前記補正量制御回路は、前記補正抵抗と前記第二コンデンサとの接続点にnチャネルMOS型FETである第二断続スイッチ素子が挿入され、

前記第二断続スイッチ素子のドレイン端子が前記補正抵抗の一端に接続され、ソース端子が前記第二コンデンサの出力端に接続され、ゲート端子が前記第一断続スイッチの前記ゲート端子に接続されている請求項6記載のスイッチング電源装置。

【請求項8】

前記第一バイアス回路及び第二バイアス回路は、前記出力電流がゼロのとき、前記第一又は第二断続スイッチ素子のオン・オフの時比率によらず、前記間接出力電流信号及び前記基準電圧信号が等しくなるように設けられている請求項6又は7記載のスイッチング電源装置。

【請求項9】

前記第一バイアス回路及び第二バイアス回路の前記第一直流電源及び第二直流電源は、一つの直流電源が兼用されている請求項8記載のスイッチング電源装置。

【請求項10】

前記出力電流検出回路は、

前記主スイッチング素子のスイッチング電流が流れる経路に、一端を信号グランドに接続して設けられ、前記スイッチング電流を電圧変換して負のスイッチング電流信号を出力する電流検出抵抗と、

第一上段抵抗、第一下段抵抗及び第一直流電源を有し、前記第一直流電源のマイナス出力端が前記信号グランドに接続され、同じくプラス出力端が前記第一上段抵抗の一端に接続され、前記第一上段抵抗の他端と前記電流検出抵抗の出力端との間に前記第一下段抵抗が接続され、前記第一下段抵抗の両端に、前記第一直流電源の電圧を当該二つの抵抗の抵抗比で分圧した電圧と略等しい分圧電圧を発生させる第一バイアス回路と、

前記第一上段抵抗及び第一下段抵抗の中点と前記信号グランドとの間に接続された第一コンデンサとで構成され、

前記第一コンデンサの出力端である前記第一上段抵抗側の一端から、前記負のスイッチング電流信号を脈流又は直流に平滑した電圧と前記第一バイアス回路の前記分圧電圧とを合算した前記間接出力電流信号を出力し、

前記補正量制御回路は、

ソース端子が前記第一コンデンサの出力端に接続されたnチャネルMOS型FETである第一断続スイッチ素子と、

一端が前記第一断続スイッチ素子のドレイン端子に接続された補正抵抗と、

前記第一断続スイッチ素子のゲート端子と前記信号グランドとの間に、前記間接出力電流信号及び前記間接出力電圧信号よりも高い波高値を有する矩形波であって、前記第一断続スイッチ素子をオン・オフさせる駆動パルスを出力するPWMパルス発振回路とで構成され、

前記出力電圧検出回路は、

一端が前記補正抵抗の他端に接続され、他端が信号グランドに接続された第三コンデンサを備え、

前記第三コンデンサの出力端である前記補正抵抗側の一端から、前記出力電圧と相関のある電圧信号である前記間接出力電圧信号と、前記補正量制御回路によって断続された前記間接出力電流信号を脈流又は直流に平滑した電圧と合算した前記間接出力電圧信号を出力する請求項1乃至5の何れか記載のスイッチング電源装置。

【請求項11】

前記補正量制御回路は、前記補正抵抗と前記第三コンデンサとの接続点にnチャネルMOS型FETである第二断続スイッチ素子が挿入され、

前記第二断続スイッチ素子のドレイン端子が前記補正抵抗の一端に接続され、ソース端子が前記第三コンデンサの出力端に接続され、ゲート端子が前記第一断続スイッチの前記ゲート端子に接続されている請求項10記載のスイッチング電源装置。

【請求項12】

前記第一バイアス回路及び前記出力電圧検出回路は、前記出力電流がゼロのとき、前記第一又は第二断続スイッチ素子のオン・オフの時比率によらず、前記間接出力電流信号及び前記間接出力電圧信号が等しくなるように設けられている請求項10又は11記載のスイッチング電源装置。

【請求項1】

入力電源と直列に接続され、所定のスイッチング周波数でオン・オフすることによって入力電圧を断続し交流電圧を発生させる主スイッチング素子と、

前記交流電圧が印加される一次巻線及びそれに磁気結合した二次巻線を有する主トランスと、

前記二次巻線に発生した交流電圧を直流の出力電圧に変換し、当該出力電圧及び出力電流を負荷に供給する整流平滑回路と、

前記出力電圧と相関のある電圧信号である間接出力電圧信号を出力する出力電圧検出回路と、

所定の直流電圧である基準電圧信号を出力する基準電圧信号発生回路、及び前記基準電圧信号と前記間接出力電圧信号との差分を増幅して出力する誤差増幅器で構成されたフィードバック制御回路と、

前記誤差増幅器が出力した誤差増幅信号に基づいてパルス幅変調を行い、前記間接出力電圧信号と前記基準電圧信号とが等しくなるように前記主スイッチング素子を駆動するパルス電圧を出力する主スイッチング素子駆動回路と、を備えたスイッチング電源装置において、

前記主スイッチング素子に流れるスイッチング電流を検出し、前記出力電流と相関のある電圧信号である間接出力電流信号を出力する出力電流検出回路と、

所定の周波数及び時比率で前記間接出力電流信号を断続する補正量制御回路とを備え、

前記出力電圧検出回路又は前記基準電圧信号発生回路は、前記補正量制御回路を介して前記間接出力電流信号を受け、当該間接出力電流信号の値及び前記間接出力電流信号を断続した前記時比率の値が大きいほど、より前記出力電圧が高くなる方向に補正した前記間接出力電圧信号又は前記基準電圧信号を出力することを特徴とするスイッチング電源装置。

【請求項2】

前記補正量制御回路には、前記入力電圧の状態を示す入力電圧信号、又は前記出力電圧を安定化する目標値を示す出力電圧設定信号が入力され、

前記補正量制御回路は、前記入力電圧が高いときほど、且つ、前記出力電圧の目標値が低いときほど、前記前記間接出力電流信号を断続する時比率を大きくする制御を行う請求項1記載のスイッチング電源装置。

【請求項3】

前記主スイッチング素子のスイッチング周波数と、前記補正量制御回路の断続周波数とが等しい請求項1記載のスイッチング電源装置。

【請求項4】

前記出力電圧検出回路は、前記整流平滑回路の平滑インダクタに設けた補助巻線、又は前記主トランスに設けた補助巻線に発生する電圧を検出し、前記出力電圧と相関のある電圧信号である間接出力電圧信号を出力する請求項1記載のスイッチング電源装置。

【請求項5】

前記整流平滑回路は、双方向に導通可能な整流素子によって同期整流を行う請求項1記載のスイッチング電源装置。

【請求項6】

前記出力電流検出回路は、

前記主スイッチング素子のスイッチング電流が流れる経路に、一端を信号グランドに接続して設けられ、前記スイッチング電流を電圧変換して正のスイッチング電流信号を出力する電流検出抵抗と、

第一上段抵抗、第一下段抵抗及び第一直流電源を有し、前記第一直流電源のマイナス出力側が前記信号グランドに接続され、同じくプラス出力側が前記第一上段抵抗の一端に接続され、前記第一上段抵抗の他端と前記電流検出抵抗の出力端との間に前記第一下段抵抗が接続され、前記第一下段抵抗の両端に、前記第一直流電源の直流電圧を当該二つの抵抗の抵抗比で分圧した電圧と略等しい分圧電圧を発生させる第一バイアス回路と、

前記第一上段抵抗及び第一下段抵抗の中点と前記信号グランドとの間に接続された第一コンデンサとで構成され、

前記第一コンデンサの出力端である前記第一上段抵抗側の一端から、前記正のスイッチング電流信号を脈流又は直流に平滑した電圧と前記第一バイアス回路の前記分圧電圧とを合算した前記間接出力電流信号を出力し、

前記補正量制御回路は、

ソース端子が前記第一コンデンサの出力端に接続されたnチャネルMOS型FETである第一断続スイッチ素子と、

一端が前記第一断続スイッチ素子のドレイン端子に接続された補正抵抗と、

前記第一断続スイッチ素子のゲート端子と前記信号グランドとの間に、前記間接出力電流信号及び前記基準電圧信号よりも高い波高値を有する矩形波であって、前記第一断続スイッチ素子をオン・オフさせる駆動パルスを出力するPWMパルス発振回路とで構成され、

前記基準電圧信号発生回路は、

マイナス出力側が信号グランドに接続された第二直流電源と、前記第二直流電源のプラス出力側に一端が接続された第二上段抵抗と、前記第二上段抵抗の他端に接続され他端が信号グランドに接続された第二下段抵抗とで成る第二バイアス回路と、

前記第二下段抵抗と並列に接続された第二コンデンサとで構成され、

前記第二コンデンサの出力端である前記第二上段抵抗側の一端に前記補正抵抗の他端が接続され、

前記第二コンデンサの出力端から、前記第二直流電源を第二上段抵抗及び第二下段抵抗の抵抗比で分圧して前記第二下段抵抗に発生する分圧電圧と、前記補正量制御回路によって断続された前記間接出力電流信号を脈流又は直流に平滑した電圧とを合算した前記基準電圧信号を出力する請求項1乃至5の何れか記載のスイッチング電源装置。

【請求項7】

前記補正量制御回路は、前記補正抵抗と前記第二コンデンサとの接続点にnチャネルMOS型FETである第二断続スイッチ素子が挿入され、

前記第二断続スイッチ素子のドレイン端子が前記補正抵抗の一端に接続され、ソース端子が前記第二コンデンサの出力端に接続され、ゲート端子が前記第一断続スイッチの前記ゲート端子に接続されている請求項6記載のスイッチング電源装置。

【請求項8】

前記第一バイアス回路及び第二バイアス回路は、前記出力電流がゼロのとき、前記第一又は第二断続スイッチ素子のオン・オフの時比率によらず、前記間接出力電流信号及び前記基準電圧信号が等しくなるように設けられている請求項6又は7記載のスイッチング電源装置。

【請求項9】

前記第一バイアス回路及び第二バイアス回路の前記第一直流電源及び第二直流電源は、一つの直流電源が兼用されている請求項8記載のスイッチング電源装置。

【請求項10】

前記出力電流検出回路は、

前記主スイッチング素子のスイッチング電流が流れる経路に、一端を信号グランドに接続して設けられ、前記スイッチング電流を電圧変換して負のスイッチング電流信号を出力する電流検出抵抗と、

第一上段抵抗、第一下段抵抗及び第一直流電源を有し、前記第一直流電源のマイナス出力端が前記信号グランドに接続され、同じくプラス出力端が前記第一上段抵抗の一端に接続され、前記第一上段抵抗の他端と前記電流検出抵抗の出力端との間に前記第一下段抵抗が接続され、前記第一下段抵抗の両端に、前記第一直流電源の電圧を当該二つの抵抗の抵抗比で分圧した電圧と略等しい分圧電圧を発生させる第一バイアス回路と、

前記第一上段抵抗及び第一下段抵抗の中点と前記信号グランドとの間に接続された第一コンデンサとで構成され、

前記第一コンデンサの出力端である前記第一上段抵抗側の一端から、前記負のスイッチング電流信号を脈流又は直流に平滑した電圧と前記第一バイアス回路の前記分圧電圧とを合算した前記間接出力電流信号を出力し、

前記補正量制御回路は、

ソース端子が前記第一コンデンサの出力端に接続されたnチャネルMOS型FETである第一断続スイッチ素子と、

一端が前記第一断続スイッチ素子のドレイン端子に接続された補正抵抗と、

前記第一断続スイッチ素子のゲート端子と前記信号グランドとの間に、前記間接出力電流信号及び前記間接出力電圧信号よりも高い波高値を有する矩形波であって、前記第一断続スイッチ素子をオン・オフさせる駆動パルスを出力するPWMパルス発振回路とで構成され、

前記出力電圧検出回路は、

一端が前記補正抵抗の他端に接続され、他端が信号グランドに接続された第三コンデンサを備え、

前記第三コンデンサの出力端である前記補正抵抗側の一端から、前記出力電圧と相関のある電圧信号である前記間接出力電圧信号と、前記補正量制御回路によって断続された前記間接出力電流信号を脈流又は直流に平滑した電圧と合算した前記間接出力電圧信号を出力する請求項1乃至5の何れか記載のスイッチング電源装置。

【請求項11】

前記補正量制御回路は、前記補正抵抗と前記第三コンデンサとの接続点にnチャネルMOS型FETである第二断続スイッチ素子が挿入され、

前記第二断続スイッチ素子のドレイン端子が前記補正抵抗の一端に接続され、ソース端子が前記第三コンデンサの出力端に接続され、ゲート端子が前記第一断続スイッチの前記ゲート端子に接続されている請求項10記載のスイッチング電源装置。

【請求項12】

前記第一バイアス回路及び前記出力電圧検出回路は、前記出力電流がゼロのとき、前記第一又は第二断続スイッチ素子のオン・オフの時比率によらず、前記間接出力電流信号及び前記間接出力電圧信号が等しくなるように設けられている請求項10又は11記載のスイッチング電源装置。

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【公開番号】特開2012−244772(P2012−244772A)

【公開日】平成24年12月10日(2012.12.10)

【国際特許分類】

【出願番号】特願2011−112551(P2011−112551)

【出願日】平成23年5月19日(2011.5.19)

【出願人】(000103208)コーセル株式会社 (80)

【Fターム(参考)】

【公開日】平成24年12月10日(2012.12.10)

【国際特許分類】

【出願日】平成23年5月19日(2011.5.19)

【出願人】(000103208)コーセル株式会社 (80)

【Fターム(参考)】

[ Back to top ]