スイッチング電源

【目的】軽負荷でかつ高スイッチング周波数の場合においてもPWM信号を生成するための信号が微小信号であることに起因する不安定動作要因のない電流モードのスイッチング電源を提供する。

【構成】この発明のスイッチング電源は、電流検出信号の立ち上がりの早い時期に加算スロープ信号を重畳させて、軽負荷でかつ高スイッチング周波数の場合でも合成信号Vsigがある程度大きくなるようにすることにより、これとバランスをとるエラーアンプERRAMPの出力FBも大きくする。これにより、電流モードであっても、エラーアンプERRAMPの出力であるフィードバック信号FBや合成信号Vsigが微小信号であることに起因する不安定動作要因を解消することができる。

【構成】この発明のスイッチング電源は、電流検出信号の立ち上がりの早い時期に加算スロープ信号を重畳させて、軽負荷でかつ高スイッチング周波数の場合でも合成信号Vsigがある程度大きくなるようにすることにより、これとバランスをとるエラーアンプERRAMPの出力FBも大きくする。これにより、電流モードであっても、エラーアンプERRAMPの出力であるフィードバック信号FBや合成信号Vsigが微小信号であることに起因する不安定動作要因を解消することができる。

【発明の詳細な説明】

【技術分野】

【0001】

この発明は、電流モードのスイッチング電源に関する。

【背景技術】

【0002】

図11に従来の電流モードのスイッチング電源の一例について、その回路ブロック図を示す。1はスイッチング電源の入力電圧VINが入力される入力端子、Mpはスイッチング素子であるPチャネルMOSトランジスタ、Mnは同期整流素子であるNチャネルMOSトランジスタであり、2つのトランジスタMp,Mnはそれぞれドライブ回路2,3により駆動されて交互にオン・オフする。トランジスタMp,Mnの接続点にはインダクタLと出力コンデンサCoの直列回路からなる平滑フィルタが接続されている。入力電圧VINに接続されたトランジスタMp,Mnを交互にオン・オフすることによりその接続点に発生する断続的な電圧をインダクタLと出力コンデンサCoからなる平滑フィルタにより平滑化し、所望の出力電圧VOUTを出力端子4から出力する。出力電圧VOUTは抵抗R1,R2により分圧されてエラーアンプ(誤差増幅器)ERRAMPの反転入力端子に入力される。エラーアンプERRAMPの非反転入力端子には基準電圧回路VREFから出力され目標電圧に対応する基準電圧VREF(便宜的に回路名と同じとする)が入力されている。また、エラーアンプERRAMPの出力端子と反転入力端子の間には抵抗RcとコンデンサCcの直列回路からなる位相補償回路が接続されている。この構成により、エラーアンプERRAMPは出力電圧と目標電圧との差に応じた誤差信号(エラーシグナル)を出力する。以下では、この誤差信号をフィードバック信号FBと呼ぶ。フィードバック信号FBはPWMコンパレータPWMCMPの反転入力端子に入力され、その出力信号はRSフリップフロップ5のリセット端子Rに入力される。RSフリップフロップ5のセット入力端子Sには入力端子6にからの信号OSCが入力されていて、フリップフロップ5は信号OSCにより所定期間毎にセットされてそのQ出力がH(ハイ)になる。

【0003】

スイッチング素子Mpに流れる電流は電流検出手段7により検出され、その電流検出信号はスロープ補償回路8から出力されるスロープ補償信号と加算回路9により和をとられてPWMコンパレータPWMCMPの非反転入力端子に入力されている。スロープ補償回路8も信号OSCにより所定期間毎に起動をかけられている。フリップフロップのQ出力はPWM信号としてドライブ回路2,3に入力され、フリップフロップのQ出力がHのときにスイッチング素子Mpがオン、フリップフロップのQ出力がL(ロー)のときに同期整流素子Mnがオンする。このように、スイッチング素子Mpに流れる電流を検出してスイッチング素子の制御を行う方式を電流モードという。電流モードのスイッチング電源では、スイッチング素子を50%以上のオンデューティ(時比率)で動作させた場合に、スイッチング周波数より低い周波数の発振が起こる、サブハーモニック発振という現象が知られている(例えば、特許文献1参照)。これを防止するのがスロープ補償回路8である。スロープ補償回路8から出力される単調増加のスロープ補償信号を電流検出信号に加算して電流検出信号の傾き(増加率)を上げることによりサブハーモニック発振を防止する。

図12に、電流検出手段7、スロープ補償回路8および加算回路9の構成例を示す。ドライブ回路2およびトランジスタMpは図11のものと同じものであり、Rsはスイッチング素子Mpに流れる電流を検出するためのセンス抵抗である。センス抵抗Rsの両端の電圧は、それぞれレベルシフト回路10,11によりレベルシフトされてトランスコンダクタンスアンプ12に入力される。レベルシフト回路10,11としては様々な様態を適用することができるが、簡易的な構成、例えば分圧回路であってもよい。トランスコンダクタンスアンプ12は2つの入力の差分に応じた電流を出力する。本発明の場合、トランスコンダクタンスアンプ12の出力はシンク電流であり、2つの入力の差分が大きいほど、すなわちスイッチング素子Mpに流れる電流が大きいほど大きな電流を吸い込む。トランスコンダクタンスアンプ12の出力であるシンク電流IsはPチャネルMOSトランジスタM1を介して電源VINから供給される。PチャネルMOSトランジスタM2とM1はカレントミラー回路を構成していて、PチャネルMOSトランジスタM2に流れる電流I1は、トランスコンダクタンスアンプ12の出力電流Isをコピーしたものになっている(電流Isに等しいか、比例したものになっている)。この電流I1がスイッチング素子Mpに流れる電流を検出した電流検出信号に相当する。

【0004】

定電流源I0とコンデンサC1は積分回路を構成していて、定電流源I0から供給される定電流(その値もI0と表わす)がコンデンサC1で積分されることにより、コンデンサC1の両端電圧(積分電圧)は直線的に上昇していく。信号OSCはこの回路の外部から与えられる定周期の信号であり、一定期間毎に所定時間幅のリセット信号をNチャネルMOSトランジスタM3のゲートに与える。NチャネルMOSトランジスタM3は、信号OSCがリセット信号Hを与えるとオンし、コンデンサC1の電荷を放電させてその積分電圧をリセットするリセットトランジスタである。コンデンサC1の積分電圧はNチャネルMOSトランジスタM4のゲートに印加されている。NチャネルMOSトランジスタM4はソースフォロワ回路として動作し、抵抗R3にV1=(コンデンサC1の積分電圧−NチャネルMOSトランジスタM4の閾値電圧)の電圧を加える。抵抗R3の抵抗値をR3とすると抵抗R3にはI2=V1/R3の電流が流れ、I2も直線的に上昇する信号となる。PチャネルMOSトランジスタM5とM6はカレントミラー回路を構成していて、PチャネルMOSトランジスタM6に流れる電流I3は、電流I2をコピーしたものになっている。この電流I3がスロープ補償信号に相当する。

電流I1とI3はともに抵抗Raに流れ、抵抗Raの抵抗値もRaとすると、これにより抵抗Raの両端電圧Vsig(抵抗Raの一端は基準電位のGNDであるので、他端のPチャネルMOSトランジスタM2,M6と接続される側の電圧Vsigと等しい)は、Vsig=Ra×(I1+I3)=Ra×I1+Ra×I3 となる。この電圧Vsigが電流検出信号とスロープ補償信号を合成した(和をとった)信号であり、スイッチング素子のオン・オフ制御を行うための信号となる。

【0005】

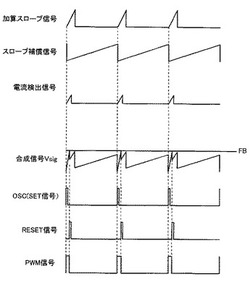

図13は上記の回路の動作を説明するためのタイミングチャートである。上から順に、スロープ補償回路8の出力であるスロープ補償信号(図12に示す電流I3に相当),電流検出信号(図12に示す電流I1に相当),電流検出信号とスロープ補償信号を加算した合成信号(図12に示す電圧信号Vsigに相当),信号OSC(Hの部分がRSフリップフロップ5をセット(SET)する信号となる),RSフリップフロップ5のリセット信号(PWMコンパレータPWMCMPの出力信号)およびPWM信号(RSフリップフロップ5のQ出力)である。信号OSCのHによりオンスロープ補償回路8がトリガーされてスロープ補償信号が立ち上がる(厳密には、信号OSCがLに戻り、コンデンサC1の積分電圧がNチャネルMOSトランジスタM4の閾値電圧を超えてから立ち上がる)とともに、RSフリップフロップ5がセットされてスイッチング素子Mpがオンし、電流検出信号も立ち上がる。加算回路9の出力である合成信号Vsigも立ち上がり、合成信号VsigがエラーアンプERRAMPの出力であるフィードバック信号FBに達すると、PWMコンパレータPWMCMPの出力信号がHとなってRSフリップフロップ5をリセットする。RSフリップフロップ5がリセットされるとPWM信号がLとなり、スイッチング素子Mpがオフして電流検出信号の値がゼロとなる。電流検出信号がゼロとなると、合成信号Vsigがスロープ補償信号だけを反映した信号となるとともに、RSフリップフロップ5のリセット信号が解除される。以上の動作を信号OSCの周期毎に繰り返して、所定の出力電圧VOUTを得るのである。

【特許文献1】特開2004−40856号公報

【発明の開示】

【発明が解決しようとする課題】

【0006】

電流モードのスイッチング電源においては、軽負荷(出力電流が小さい)でかつスイッチング周波数(すなわち上記の信号OSCの周波数)が高いとセンス抵抗Rsにより検出される電流検出信号が微小になる。この様子を図14に示す。図14に示す信号は図13のものと同じであるが、軽負荷でかつ高スイッチング周波数の場合について示すものである。スイッチング周波数が高くてスイッチング周期が短いと、そのスイッチング周期で立ち上がる合成信号Vsigとバランスをとる形となるため(バランスがとれていないとPWM波形のデューティが大きすぎるか小さすぎて出力電圧VOUTが変化し、結局バランスがとれるようになる)、スイッチング周期が長いときに比べ、エラーアンプERRAMPの出力FBは低下する。さらに、図14に示すように、軽負荷で出力コンデンサCoから外部に取り出される電荷が少ない(すなわち出力電流が小さい)と、出力電圧VOUTが増加するためエラーアンプERRAMPの出力であるフィードバック信号FBが一層小さくなる。このように、軽負荷でかつ高スイッチング周波数の場合はフィードバック新B号FBがゼロ近くまで減少し、鋸波である合成信号Vsigが立ち上がり始めて直ぐの、その値がまだ小さいときにPWMコンパレータPWMCMPが動作する(RSフリップフロップ5へのリセット信号を出力する)ので、図14に示すように誤パルスが出力され、不安定動作の要因となる。さらに、エラーアンプERRAMPの出力であるフィードバック信号FBが微小信号であるためノイズの影響を受けやすく、これも不安定動作の要因となる。

【0007】

また、特許文献1に開示されている、スロープ補償信号をスイッチング周期の途中から加算する方式では、軽負荷でかつ高スイッチング周波数の場合に関する上記の問題がさらに顕著になってしまう(合成信号Vsigの立ち上がりがさらに小さくなり、これとバランスをとるエラーアンプERRAMPの出力FBがさらに微小となる)。

この発明は、これらの課題を解決し、軽負荷でかつ高スイッチング周波数の場合においてもPWM信号を生成するたもの信号が微小信号であることに起因する不安定動作要因のない電流モードのスイッチング電源を提供することを目的とする。

【課題を解決するための手段】

【0008】

そこで、上記課題を解決するために、請求項1に係る発明は、スイッチング素子のオン・オフを制御して所定の電圧の出力を生成するスイッチング電源において、前記出力の電圧またはその分圧と基準電圧を比較してその差に応じた誤差信号を出力する誤差増幅器と、前記スイッチング素子に流れる電流を検出する電流検出手段と、前記スイッチング手段がオンする前にゼロリセットされ、前記スイッチング手段がオンすると増加を開始し、前記スイッチング素子のスイッチング周期より短い所定時間経過後に増加を停止する加算スロープ信号を生成する加算スロープ回路とを有し、前記電流検出手段の出力と前記加算スロープ信号を加算した和信号を求め、該和信号と前記誤差信号を比較して前記和信号が前記誤差信号に等しくなったときに前記スイッチング素子をオフにすることを特徴とする。

請求項2に係る発明は、請求項1に係る発明においてサブハーモニック発振を防ぐためのスロープ補償信号を生成するスロープ補償回路をさらに有し、前記和信号の替わりに前記和信号にさらに前記スロープ補償信号を加算した第2和信号を前記誤差信号と比較して、前記第2和信号が前記誤差信号に等しくなったときにスイッチング素子をオフにすることを特徴とする。

請求項3に係る発明は、請求項1に係る発明においてサブハーモニック発振を防ぐためのスロープ補償信号を生成するスロープ補償回路をさらに有し、前記誤差信号の替わりに前記誤差信号から前記スロープ補償信号を差し引いた差信号を前記和信号と比較して、前記和信号が前記差信号に等しくなったときにスイッチング素子をオフにすることを特徴とする。

【0009】

請求項4に係る発明は、請求項1ないし3のいずれか1つに係る発明において前記加算スロープ回路が定電流で充電されるコンデンサを有し、該コンデンサの両端電圧を前記加算スロープ信号とすることを特徴とする。

請求項5に係る発明は、請求項4に係る発明において前記定電流が前記スイッチング素子のスイッチング周波数に比例することを特徴とする。

請求項6に係る発明は、請求項1ないし3のいずれか1つに係る発明において前記加算スロープ信号の増加率が前記スイッチング素子のスイッチング周波数に比例することを特徴とする。

請求項7に係る発明は、請求項5または6に係る発明において前記所定時間が前記スイッチング素子のスイッチング周期に比例することを特徴とする。

請求項8に係る発明は、請求項1に係る発明において前記電流検出手段が前記スイッチング素子に接続された抵抗の両端電圧を検出するものであることを特徴とする。

【発明の効果】

【0010】

この発明のスイッチング電源は、電流検出信号の立ち上がりの早い時期に加算スロープ信号を重畳させて、軽負荷でかつ高スイッチング周波数の場合でも合成信号Vsigがある程度大きくなるようにすることにより、これとバランスをとるエラーアンプERRAMPの出力FBも大きくして、電流モードであっても、PWM信号を生成するための信号が微小信号であることに起因する不安定動作要因を解消することができる。

【発明を実施するための最良の形態】

【0011】

以下、図面を用いて本発明のスイッチング電源について説明する。

図1に、本発明のスイッチング電源に係る全体構成例を示す。図11と同じ部位には、同じ符号を付して詳細な説明を省略する。本実施例の図11に示すスイッチング電源との違いは、加算スロープ回路20を設け、その出力である加算スロープ信号を加算回路9への3つめの入力信号としたことにある。加算スロープ回路20は入力端子21からの信号Min.Pulseが入力され、信号Min.Pulseにより指示される期間、単調増加する信号を発生し、それを加算スロープ信号として加算回路9に入力する。信号Min.Pulseは信号OSC同じ周波数(すなわちスイッチング周波数と同じ周波数)で、かつ同期をとられた信号であり、信号OSCの新しい周期が開始すると加算スロープ回路20に加算スロープ信号の生成を指示する。

図2に加算スロープ回路20の第1の構成例を関連部分とともに示す。本図において、図12と同じ部位には、同じ符号を付して詳細な説明を省略する。図2において加算スロープ回路20は、NチャネルMOSトランジスタM7,M8,PチャネルMOSトランジスタM9,M10,定電流源I1,コンデンサC2および抵抗R4を有している。構成はスロープ補償回路8と同様であり、定電流源I1とコンデンサとC2が積分回路を構成し、NチャネルMOSトランジスタM7がそのリセットトランジスタとなっている。ワンショット回路21の出力である信号Min.PulseがLであるとリセットトランジスタM7がオフするので、その期間に定電流源からの定電流(その値もI1とする)がコンデンサC2(その容量値もC2とする)に積分され、時間をtとするとコンデンサC2の両端電圧はI1×t/C2となって直線的に立ち上がる。コンデンサC2による積分電圧はNチャネルMOSトランジスタM8のゲートに印加され、NチャネルMOSトランジスタM8はソースフォロワ回路として動作し、抵抗R4にV2=(コンデンサC2の積分電圧−NチャネルMOSトランジスタM8の閾値電圧)の電圧を加える。抵抗R4の抵抗値をR4とすると抵抗R4にはI4=V2/R4の電流が流れ、I4も直線的に上昇する信号となる。PチャネルMOSトランジスタM9とM10はカレントミラー回路を構成していて、PチャネルMOSトランジスタM10に流れる電流I5は、電流I4をコピーしたものになっている。この電流I5が加算スロープ信号に相当する。

【0012】

電流I5は電流I1,I3とともに抵抗Raに流れ、これにより合成信号Vsigは、Vsig=Ra×(I1+I3+I5)=Ra×I1+Ra×I3+Ra×I5 となる。

信号Min.PulseがHであるとリセットトランジスタM7がオンするので、加算スロープ信号I5がゼロとなり、加算スロープ信号は合成信号Vsigの生成に寄与しなくなる。また、ワンショット回路22には信号OSCが入力され、ワンショット回路22は信号OSCが立ち上がると所定期間Lとなりその後Hとなる信号を生成する。

図1,2の回路に係るタイミングチャートを図3,4に示す。図3はエラーアンプERRAMPの出力であるフィードバック信号FBが小さく、加算スロープ信号が増加しているときに合成信号Vsigとフィードバック信号FBが等しくなる場合であり、図4はフィードバック信号FBが大きく、加算スロープ信号の増加期間が終了してから合成信号Vsigとフィードバック信号FBが等しくなる場合である。

図3において、OSC信号がHになると、上述のようにスロープ補償回路8がトリガーされてスロープ補償信号が立ち上がるとともに、ワンショット回路22が所定期間Lとなる信号(Min.Pulse信号)を出力して加算スロープ信号も立ち上がる(増加を始める)。この所定期間の間は、加算スロープ信号,スロープ補償信号および電流検出信号の和が合成信号Vsigとなる(電流検出信号は、スイッチング素子がオフするとゼロになって合成信号Vsigに寄与しなくなる)。フィードバック信号FBが小さいので合成信号Vsigとフィードバック信号FBが上記所定期間のうちに等しくなってPWM信号が終了し(Lになり)、スイッチング素子Mpがオフするから電流検出信号もゼロになる。この場合、フィードバック信号FBが小さいといっても、ある程度傾斜の大きい加算スロープ信号が電流検出信号に重畳されて合成信号Vsigもある程度の大きさを有しているので、これとバランスをとる(合成信号Vsigと等しくなる点で適切な時比率を与える)フィードバック信号FBも従来より大きな値をとるようになるので、フィードバック信号FBや合成信号Vsigが微小信号であることに起因する不安定動作要因を解消することができる。

【0013】

図4は軽負荷ではない場合に相当し、フィードバック信号FBが従来でも大きくなる領域である。上記の所定期間が経過しても合成信号Vsigとフィードバック信号FBが等しくならないと、加算スロープ信号がゼロに戻り、以降はスロープ補償信号と電流検出信号の和が合成信号Vsigとなる。この合成信号Vsigがフィードバック信号FBに等しくなるとスイッチング素子Mpがオフし、電流検出信号がゼロになるから、以降は合成信号Vsigがスロープ補償信号だけを反映した信号となる。

図5に加算スロープ回路の第2の構成例を関連部分とともに示す。図5に示す回路は、図2の第1の加算スロープ回路20を第2の加算スロープ回路20’に置き換えたものである。第2の加算スロープ回路20’に対しては、ワンショット回路21の出力Min.Pulseではなく、信号OSCが直接入力される。第1の加算スロープ回路20に対する第2の加算スロープ回路20’の違いは、コンデンサC2に並列にツェナーダイオードZDを設けた点である。第2の加算スロープ回路20’はツェナーダイオードZDを除き、スロープ補償回路8と同様の構成・動作を行う。すなわち、第2の加算スロープ回路20’はスロープ補償回路8と同様に信号OSCでトリガーされて一定の傾きで増加する加算スロープ信号I5を生成する。加算スロープ信号I5の増加はスイッチング周期の最後まで続くものではなく、コンデンサC2の積分電圧(両端電圧)がツェナーダイオードZDのツェナー電圧Vzに達した時点でクランプされて増加は終了する。すなわち、コンデンサC2の積分電圧がVzでクランプされるので、電圧V2は以降(Vz−NチャネルMOSトランジスタM8の閾値電圧)の定電圧となり、これにより電流I4,I5も定電流となる。

【0014】

図1,5の回路に係るタイミングチャートを図6,7に示す(図1において、信号Min.Pulseが信号OSCに置き換えられているものとする)。図6,7は、図1,2に関する図3,4に対応するものであり、それぞれ、エラーアンプERRAMPの出力であるフィードバック信号FBが小さく、加算スロープ信号が増加しているときに合成信号Vsigとフィードバック信号FBが等しくなる場合、およびフィードバック信号FBが大きく、加算スロープ信号の増加期間が終了してから合成信号Vsigとフィードバック信号FBが等しくなる場合のタイミングチャートである。

図6においてOSC信号がHになると、上述の実施例と同様にスロープ補償回路8がトリガーされてスロープ補償信号が立ち上がるとともに、第2の加算スロープ回路20’もトリガーされて加算スロープ信号が立ち上がる(増加を始める)。コンデンサC2の積分電圧がツェナーダイオードZDのツェナー電圧Vzに達するまでは、加算スロープ信号,スロープ補償信号および電流検出信号の和が合成信号Vsigとなる(電流検出信号は、スイッチング素子がオフするとゼロになって合成信号Vsigに寄与しなくなる)。フィードバック信号FBが小さいので合成信号Vsigとフィードバック信号FBが、コンデンサC2の積分電圧がツェナーダイオードZDのツェナー電圧Vzに達する前に等しくなってPWM信号が終了し(Lになり)、スイッチング素子Mpがオフするから電流検出信号もゼロになる。この場合、フィードバック信号FBが小さいといっても、上述の実施例と同様にある程度傾斜の大きい加算スロープ信号が電流検出信号に重畳されて合成信号Vsigもある程度の大きさを有しているので、これとバランスをとるフィードバック信号FBも従来より大きな値をとり、フィードバック信号FBや合成信号Vsigが微小信号であることに起因する不安定動作要因を解消することができる。

【0015】

図7は軽負荷ではない場合に相当し、フィードバック信号FBが従来でも大きくなる領域である。コンデンサC2の積分電圧がツェナーダイオードZDのツェナー電圧Vzに達しても合成信号Vsigとフィードバック信号FBが等しくならないと、加算スロープ信号はコンデンサC2の積分電圧がツェナー電圧Vzに達した時点の値を保ち、以降はその一定値とスロープ補償信号と電流検出信号との和が合成信号Vsigとなる。この合成信号Vsigがフィードバック信号FBに等しくなるとスイッチング素子Mpがオフし、電流検出信号がゼロになるから、以降はスロープ補償信号と上記一定値の和の信号が合成信号Vsigとなる。

上述の実施例において、定電流源I1の定電流I1の大きさは信号OSCの周波数、すなわちスイッチング周波数に比例したものであるとよい。これは、スイッチング周波数が変化しうるものであり、スイッチング周波数もしくはスイッチング周期が変化しても定電流I1の値が一定であると、スイッチング周期が短い場合は加算スロープ信号の立ち上がりが遅すぎることになり、スイッチング周期が長い場合は加算スロープ信号の立ち上がりが速すぎることになって不具合が生じるからである。なお、スイッチング周波数は、負荷の軽重や入出力電圧の変化などによって変化させる場合がある。加算スロープ信号については、上記Min.Pulseのパルス幅をスイッチング周期に比例する時間として当該時間経過後に加算スロープ信号の大きさがスイッチング周波数によらず一定値になる、もしくはコンデンサC2の積分電圧がツェナー電圧Vzに達するまでの時間がスイッチング周期に比例したものになることが望ましい。このためには、定電流I1がスイッチング周期に反比例、すなわちスイッチング周波数に比例するものであればよい。

【0016】

スイッチング周波数に比例する定電流I1を与える回路の例を図8に示す。図8において、VCOは電圧制御発振器(Voltage Controlled Oscillator)であり、入力信号f_sigの電圧に比例した周波数の信号OSCを生成・出力する。また、図8の回路はオペアンプ(演算増幅器)OP1,PチャネルMOSトランジスタM11,M12および抵抗R5も有していて、この部分が定電流源I1に相当する。入力信号f_sigはオペアンプOP1の反転入力端子に入力され、オペアンプOP1の出力はPチャネルMOSトランジスタM11,M12のゲートに接続されている。出力はPチャネルMOSトランジスタM11のドレインは抵抗R5の一端およびオペアンプOP1の非反転入力端子に接続されている。この構成により、オペアンプOP1の反転入力端子と非反転入力端子は仮想短絡されるから、抵抗R5には入力信号f_sigの電圧が印加される。従い、抵抗R3には入力信号f_sigの電圧に比例した、すなわちスイッチング周波数に比例した電流I6が流れる。PチャネルMOSトランジスタM11とM12はカレントミラー回路を構成していて、PチャネルMOSトランジスタM12に流れる電流はPチャネルMOSトランジスタM11に流れる電流(すなわち抵抗R3に流れる電流)I6に等しい、もしくは比例したものになる。従い、PチャネルMOSトランジスタM12のドレインから供給される電流はスイッチング周波数に比例したものになり、これを定電流I1としてコンデンサC2で積分すればよい。

【0017】

図9に、電圧制御発振器VCOおよびスイッチング周期に比例したMin.Pulse信号のパルス幅を与える回路の構成例を示す。この回路では、定電流源I1の構成要素であるオペアンプ(演算増幅器)OP1,PチャネルMOSトランジスタM11および抵抗R5を、電圧制御発振器VCOが共有している。電圧制御発振器VCOはこの他に、PチャネルMOSトランジスタM13,M14,M17,NチャネルMOSトランジスタM15,M16,M18,コンデンサCt,ワンショット回路23,ヒステリシスコンパレータCMP1,コンパレータCMP2およびオア(OR)ゲート24を有している。PチャネルMOSトランジスタM13,M14はゲートが共通に接続されてカレントミラー回路を構成し、PチャネルMOSトランジスタM13に流れる電流I7およびPチャネルMOSトランジスタM14に流れる電流I8は、PチャネルMOSトランジスタM11に流れる電流I6に等しいか、もしくは比例したものになっている。PチャネルMOSトランジスタM13とNチャネルMOSトランジスタM15は直列に接続され、NチャネルMOSトランジスタM15とM16とがカレントミラー回路を構成しているから、NチャネルMOSトランジスタM16に流れる電流I9は電流I7に等しいか、もしくは比例するものになる。PチャネルMOSトランジスタM14,M17とNチャネルMOSトランジスタM18,M16は直列に接続され、PチャネルMOSトランジスタM17とNチャネルMOSトランジスタM18はヒステリシスコンパレータCMP1の出力V4により交互にオン・オフするので、PチャネルMOSトランジスタM17とNチャネルMOSトランジスタM18の接続点に接続されているコンデンサCtは、電流I8で充電される(PチャネルMOSトランジスタM17がオンしている場合)か、電流I9で放電される(NチャネルMOSトランジスタM18がオンしている場合)かのいずれかの状態となる。コンデンサCtの充電電圧V3は、ヒステリシスコンパレータCMP1により基準電圧Vref1,Vref2(Vref1<Vref2)と比較され、コンパレータCMP2により基準電圧Vref3(Vref1<Vref3<Vref2)と比較される。ヒステリシスコンパレータCMP1の出力V4とコンパレータCMP2の出力V5はオアゲート24によって論理和をとられて信号Min.Pulseになる。また、ヒステリシスコンパレータCMP1の出力V4はワンショット回路23に入力され、ワンショット回路23は信号V4の立下りでトリガーされて一定幅のHパルスを出力する。

【0018】

図9の回路の動作について、図10のタイミングチャートを用いて説明する。ヒステリシスコンパレータCMP1の出力V4がHであるとコンデンサCtの電荷が定電流I9によって放電されるため、コンデンサCtの積分電圧V3は直線的に減少する。電圧V3が基準電圧Vref1に達するとヒステリシスコンパレータCMP1の出力V4は反転してLとなるとともに、ヒステリシスコンパレータCMP1の基準電圧がVref1からVref2に切り替わる。ヒステリシスコンパレータCMP1の出力V4がLであるとコンデンサCtは定電流I8によって充電されるため、コンデンサCtの積分電圧V3は直線的に増加する。電圧V3が基準電圧Vref2に達するとヒステリシスコンパレータCMP1の出力V4は反転してHとなるとともに、ヒステリシスコンパレータCMP1の基準電圧がVref2からVref1に切り替わる。この動作を繰り返し、コンデンサCtの積分電圧V3はVref1とVref2の間で振動する三角波となる。

一方、コンパレータCMP2は、コンデンサCtの積分電圧V3と基準電圧Vref3との比較を行って、信号V5を出力する。信号V4と信号V5はオアゲート24によって論理和をとられて、信号OSCの立ち上がりからコンデンサCtの積分電圧V3が基準電圧Vref3に達するまでの期間Lとなる信号Min.Pulseとなる。信号V4がLとなっている時間をT1、信号V4がHとなっている時間をT2とすると、T1=K1×I6,T2=K2×I6(K1,K2は定数)となる。信号Min.Pulseのパルス幅(Lとなっている期間)をT0とすると、T0=T1×(Vref3−Vref1)/(Vref2−Vref1)となるから、T0とスイッチング周期(=T1+T2)の比は、T0/(T1+T2)=(K1/(K1+K2))×(Vref3−Vref1)/(Vref2−Vref1)となり、スイッチング周波数に依存しない一定値となる。

【0019】

また、本発明はスロープ補償を行わない場合でも有効である。この場合、上述の説明においてスロープ補償信号が常にゼロであると考えればよい。合成信号Vsigは加算スロープ信号と電流検出信号の和信号となる。これを第1の和信号と考えれば、上述の加算スロープ信号,スロープ補償信号および電流検出信号を加算した信号は第2和信号といえる。

さらに、スロープ補償信号を加算スロープ信号および電流検出信号と一緒に加算して上記和信号,第2和信号を求める実施例について説明してきたが、エラーアンプERRAMPの出力であるフィードバック信号FBからスロープ補償信号を差し引いたものと、加算スロープ信号と電流検出信号との和信号をPWMコンパレータPWMCMPで比較してPWM信号を生成するようにしてもよい。この場合も電流検出信号に加算スロープ信号が加算されて合成信号Vsigはある程度の大きさを有しているので、これとバランスをとる(合成信号Vsigと等しくなる点で適切な時比率を与える)信号(フィードバック信号FB−スロープ補償信号)も従来より大きな値をとるようになるので、PWM信号を生成するための信号が微小信号であることに起因する不安定動作要因を解消することができる。

【図面の簡単な説明】

【0020】

【図1】本発明のスイッチング電源に係る全体構成例を示す図である。

【図2】加算スロープ回路20の第1の構成例を関連部分とともに示す回路図である。

【図3】図1,2の回路に係るタイミングチャートである。

【図4】図1,2の回路に係る別のタイミングチャートである。

【図5】加算スロープ回路の第2の構成例を関連部分とともに示す回路図である。

【図6】図1,5の回路に係るタイミングチャートである。

【図7】図1,5の回路に係る別のタイミングチャートである。

【図8】スイッチング周波数に比例する定電流I1を与える回路例を示す図である。

【図9】電圧制御発振器VCOおよびスイッチング周期に比例したMin.Pulse信号のパルス幅を与える回路の構成例を示す図である。

【図10】図9の回路の動作について説明するためのタイミングチャートである。

【図11】従来の電流モードのスイッチング電源の一例を示す回路図である。

【図12】電流検出手段7、スロープ補償回路8および加算回路9の構成例を示す回路図である。

【図13】図11,12の回路の動作を説明するためのタイミングチャートである

【図14】軽負荷でかつスイッチング周波数が高いときにセンス抵抗Rsにより検出される電流検出信号が微小になる様子を示すための図である。

【符号の説明】

【0021】

1,6,21 入力端子

2,3 ドライブ回路

4 出力端子

5 RSフリップフロップ

7 電流検出手段

8 スロープ補償回路

9 加算回路

10,11 レベルシフト回路

12 トランスコンダクタンスアンプ

20 加算スロープ回路

22,23 ワンショット回路

24 オアゲート

C1,C2,Cc,Co,Ct コンデンサもしくはその容量値

CMP1 ヒステリシスコンパレータ

CMP2 コンパレータ

ERRAMP エラーアンプ(誤差増幅器)

I0,I1 定電流源もしくはその定電流値

I2〜I9 定電流

L インダクタ

R1〜R5,Ra,Rc,Rs 抵抗もしくはその抵抗値

VREF,Vref1〜Vref3 基準電圧源もしくは基準電圧値

VIN 入力電源もしくはその電圧

VOUT 出力もしくはその電圧

M1,M2,M5,M6,M9〜14,M17 PチャネルMOSトランジスタ

M3,M4,M7,M8,M15,M16,M18 チャネルMOSトランジスタ

Mn 同期整流素子(NチャネルMOSトランジスタ)

Mp スイッチング素子(PチャネルMOSトランジスタ)

OP1 オペアンプ(演算増幅器)

ZD ツェナーダイオード

【技術分野】

【0001】

この発明は、電流モードのスイッチング電源に関する。

【背景技術】

【0002】

図11に従来の電流モードのスイッチング電源の一例について、その回路ブロック図を示す。1はスイッチング電源の入力電圧VINが入力される入力端子、Mpはスイッチング素子であるPチャネルMOSトランジスタ、Mnは同期整流素子であるNチャネルMOSトランジスタであり、2つのトランジスタMp,Mnはそれぞれドライブ回路2,3により駆動されて交互にオン・オフする。トランジスタMp,Mnの接続点にはインダクタLと出力コンデンサCoの直列回路からなる平滑フィルタが接続されている。入力電圧VINに接続されたトランジスタMp,Mnを交互にオン・オフすることによりその接続点に発生する断続的な電圧をインダクタLと出力コンデンサCoからなる平滑フィルタにより平滑化し、所望の出力電圧VOUTを出力端子4から出力する。出力電圧VOUTは抵抗R1,R2により分圧されてエラーアンプ(誤差増幅器)ERRAMPの反転入力端子に入力される。エラーアンプERRAMPの非反転入力端子には基準電圧回路VREFから出力され目標電圧に対応する基準電圧VREF(便宜的に回路名と同じとする)が入力されている。また、エラーアンプERRAMPの出力端子と反転入力端子の間には抵抗RcとコンデンサCcの直列回路からなる位相補償回路が接続されている。この構成により、エラーアンプERRAMPは出力電圧と目標電圧との差に応じた誤差信号(エラーシグナル)を出力する。以下では、この誤差信号をフィードバック信号FBと呼ぶ。フィードバック信号FBはPWMコンパレータPWMCMPの反転入力端子に入力され、その出力信号はRSフリップフロップ5のリセット端子Rに入力される。RSフリップフロップ5のセット入力端子Sには入力端子6にからの信号OSCが入力されていて、フリップフロップ5は信号OSCにより所定期間毎にセットされてそのQ出力がH(ハイ)になる。

【0003】

スイッチング素子Mpに流れる電流は電流検出手段7により検出され、その電流検出信号はスロープ補償回路8から出力されるスロープ補償信号と加算回路9により和をとられてPWMコンパレータPWMCMPの非反転入力端子に入力されている。スロープ補償回路8も信号OSCにより所定期間毎に起動をかけられている。フリップフロップのQ出力はPWM信号としてドライブ回路2,3に入力され、フリップフロップのQ出力がHのときにスイッチング素子Mpがオン、フリップフロップのQ出力がL(ロー)のときに同期整流素子Mnがオンする。このように、スイッチング素子Mpに流れる電流を検出してスイッチング素子の制御を行う方式を電流モードという。電流モードのスイッチング電源では、スイッチング素子を50%以上のオンデューティ(時比率)で動作させた場合に、スイッチング周波数より低い周波数の発振が起こる、サブハーモニック発振という現象が知られている(例えば、特許文献1参照)。これを防止するのがスロープ補償回路8である。スロープ補償回路8から出力される単調増加のスロープ補償信号を電流検出信号に加算して電流検出信号の傾き(増加率)を上げることによりサブハーモニック発振を防止する。

図12に、電流検出手段7、スロープ補償回路8および加算回路9の構成例を示す。ドライブ回路2およびトランジスタMpは図11のものと同じものであり、Rsはスイッチング素子Mpに流れる電流を検出するためのセンス抵抗である。センス抵抗Rsの両端の電圧は、それぞれレベルシフト回路10,11によりレベルシフトされてトランスコンダクタンスアンプ12に入力される。レベルシフト回路10,11としては様々な様態を適用することができるが、簡易的な構成、例えば分圧回路であってもよい。トランスコンダクタンスアンプ12は2つの入力の差分に応じた電流を出力する。本発明の場合、トランスコンダクタンスアンプ12の出力はシンク電流であり、2つの入力の差分が大きいほど、すなわちスイッチング素子Mpに流れる電流が大きいほど大きな電流を吸い込む。トランスコンダクタンスアンプ12の出力であるシンク電流IsはPチャネルMOSトランジスタM1を介して電源VINから供給される。PチャネルMOSトランジスタM2とM1はカレントミラー回路を構成していて、PチャネルMOSトランジスタM2に流れる電流I1は、トランスコンダクタンスアンプ12の出力電流Isをコピーしたものになっている(電流Isに等しいか、比例したものになっている)。この電流I1がスイッチング素子Mpに流れる電流を検出した電流検出信号に相当する。

【0004】

定電流源I0とコンデンサC1は積分回路を構成していて、定電流源I0から供給される定電流(その値もI0と表わす)がコンデンサC1で積分されることにより、コンデンサC1の両端電圧(積分電圧)は直線的に上昇していく。信号OSCはこの回路の外部から与えられる定周期の信号であり、一定期間毎に所定時間幅のリセット信号をNチャネルMOSトランジスタM3のゲートに与える。NチャネルMOSトランジスタM3は、信号OSCがリセット信号Hを与えるとオンし、コンデンサC1の電荷を放電させてその積分電圧をリセットするリセットトランジスタである。コンデンサC1の積分電圧はNチャネルMOSトランジスタM4のゲートに印加されている。NチャネルMOSトランジスタM4はソースフォロワ回路として動作し、抵抗R3にV1=(コンデンサC1の積分電圧−NチャネルMOSトランジスタM4の閾値電圧)の電圧を加える。抵抗R3の抵抗値をR3とすると抵抗R3にはI2=V1/R3の電流が流れ、I2も直線的に上昇する信号となる。PチャネルMOSトランジスタM5とM6はカレントミラー回路を構成していて、PチャネルMOSトランジスタM6に流れる電流I3は、電流I2をコピーしたものになっている。この電流I3がスロープ補償信号に相当する。

電流I1とI3はともに抵抗Raに流れ、抵抗Raの抵抗値もRaとすると、これにより抵抗Raの両端電圧Vsig(抵抗Raの一端は基準電位のGNDであるので、他端のPチャネルMOSトランジスタM2,M6と接続される側の電圧Vsigと等しい)は、Vsig=Ra×(I1+I3)=Ra×I1+Ra×I3 となる。この電圧Vsigが電流検出信号とスロープ補償信号を合成した(和をとった)信号であり、スイッチング素子のオン・オフ制御を行うための信号となる。

【0005】

図13は上記の回路の動作を説明するためのタイミングチャートである。上から順に、スロープ補償回路8の出力であるスロープ補償信号(図12に示す電流I3に相当),電流検出信号(図12に示す電流I1に相当),電流検出信号とスロープ補償信号を加算した合成信号(図12に示す電圧信号Vsigに相当),信号OSC(Hの部分がRSフリップフロップ5をセット(SET)する信号となる),RSフリップフロップ5のリセット信号(PWMコンパレータPWMCMPの出力信号)およびPWM信号(RSフリップフロップ5のQ出力)である。信号OSCのHによりオンスロープ補償回路8がトリガーされてスロープ補償信号が立ち上がる(厳密には、信号OSCがLに戻り、コンデンサC1の積分電圧がNチャネルMOSトランジスタM4の閾値電圧を超えてから立ち上がる)とともに、RSフリップフロップ5がセットされてスイッチング素子Mpがオンし、電流検出信号も立ち上がる。加算回路9の出力である合成信号Vsigも立ち上がり、合成信号VsigがエラーアンプERRAMPの出力であるフィードバック信号FBに達すると、PWMコンパレータPWMCMPの出力信号がHとなってRSフリップフロップ5をリセットする。RSフリップフロップ5がリセットされるとPWM信号がLとなり、スイッチング素子Mpがオフして電流検出信号の値がゼロとなる。電流検出信号がゼロとなると、合成信号Vsigがスロープ補償信号だけを反映した信号となるとともに、RSフリップフロップ5のリセット信号が解除される。以上の動作を信号OSCの周期毎に繰り返して、所定の出力電圧VOUTを得るのである。

【特許文献1】特開2004−40856号公報

【発明の開示】

【発明が解決しようとする課題】

【0006】

電流モードのスイッチング電源においては、軽負荷(出力電流が小さい)でかつスイッチング周波数(すなわち上記の信号OSCの周波数)が高いとセンス抵抗Rsにより検出される電流検出信号が微小になる。この様子を図14に示す。図14に示す信号は図13のものと同じであるが、軽負荷でかつ高スイッチング周波数の場合について示すものである。スイッチング周波数が高くてスイッチング周期が短いと、そのスイッチング周期で立ち上がる合成信号Vsigとバランスをとる形となるため(バランスがとれていないとPWM波形のデューティが大きすぎるか小さすぎて出力電圧VOUTが変化し、結局バランスがとれるようになる)、スイッチング周期が長いときに比べ、エラーアンプERRAMPの出力FBは低下する。さらに、図14に示すように、軽負荷で出力コンデンサCoから外部に取り出される電荷が少ない(すなわち出力電流が小さい)と、出力電圧VOUTが増加するためエラーアンプERRAMPの出力であるフィードバック信号FBが一層小さくなる。このように、軽負荷でかつ高スイッチング周波数の場合はフィードバック新B号FBがゼロ近くまで減少し、鋸波である合成信号Vsigが立ち上がり始めて直ぐの、その値がまだ小さいときにPWMコンパレータPWMCMPが動作する(RSフリップフロップ5へのリセット信号を出力する)ので、図14に示すように誤パルスが出力され、不安定動作の要因となる。さらに、エラーアンプERRAMPの出力であるフィードバック信号FBが微小信号であるためノイズの影響を受けやすく、これも不安定動作の要因となる。

【0007】

また、特許文献1に開示されている、スロープ補償信号をスイッチング周期の途中から加算する方式では、軽負荷でかつ高スイッチング周波数の場合に関する上記の問題がさらに顕著になってしまう(合成信号Vsigの立ち上がりがさらに小さくなり、これとバランスをとるエラーアンプERRAMPの出力FBがさらに微小となる)。

この発明は、これらの課題を解決し、軽負荷でかつ高スイッチング周波数の場合においてもPWM信号を生成するたもの信号が微小信号であることに起因する不安定動作要因のない電流モードのスイッチング電源を提供することを目的とする。

【課題を解決するための手段】

【0008】

そこで、上記課題を解決するために、請求項1に係る発明は、スイッチング素子のオン・オフを制御して所定の電圧の出力を生成するスイッチング電源において、前記出力の電圧またはその分圧と基準電圧を比較してその差に応じた誤差信号を出力する誤差増幅器と、前記スイッチング素子に流れる電流を検出する電流検出手段と、前記スイッチング手段がオンする前にゼロリセットされ、前記スイッチング手段がオンすると増加を開始し、前記スイッチング素子のスイッチング周期より短い所定時間経過後に増加を停止する加算スロープ信号を生成する加算スロープ回路とを有し、前記電流検出手段の出力と前記加算スロープ信号を加算した和信号を求め、該和信号と前記誤差信号を比較して前記和信号が前記誤差信号に等しくなったときに前記スイッチング素子をオフにすることを特徴とする。

請求項2に係る発明は、請求項1に係る発明においてサブハーモニック発振を防ぐためのスロープ補償信号を生成するスロープ補償回路をさらに有し、前記和信号の替わりに前記和信号にさらに前記スロープ補償信号を加算した第2和信号を前記誤差信号と比較して、前記第2和信号が前記誤差信号に等しくなったときにスイッチング素子をオフにすることを特徴とする。

請求項3に係る発明は、請求項1に係る発明においてサブハーモニック発振を防ぐためのスロープ補償信号を生成するスロープ補償回路をさらに有し、前記誤差信号の替わりに前記誤差信号から前記スロープ補償信号を差し引いた差信号を前記和信号と比較して、前記和信号が前記差信号に等しくなったときにスイッチング素子をオフにすることを特徴とする。

【0009】

請求項4に係る発明は、請求項1ないし3のいずれか1つに係る発明において前記加算スロープ回路が定電流で充電されるコンデンサを有し、該コンデンサの両端電圧を前記加算スロープ信号とすることを特徴とする。

請求項5に係る発明は、請求項4に係る発明において前記定電流が前記スイッチング素子のスイッチング周波数に比例することを特徴とする。

請求項6に係る発明は、請求項1ないし3のいずれか1つに係る発明において前記加算スロープ信号の増加率が前記スイッチング素子のスイッチング周波数に比例することを特徴とする。

請求項7に係る発明は、請求項5または6に係る発明において前記所定時間が前記スイッチング素子のスイッチング周期に比例することを特徴とする。

請求項8に係る発明は、請求項1に係る発明において前記電流検出手段が前記スイッチング素子に接続された抵抗の両端電圧を検出するものであることを特徴とする。

【発明の効果】

【0010】

この発明のスイッチング電源は、電流検出信号の立ち上がりの早い時期に加算スロープ信号を重畳させて、軽負荷でかつ高スイッチング周波数の場合でも合成信号Vsigがある程度大きくなるようにすることにより、これとバランスをとるエラーアンプERRAMPの出力FBも大きくして、電流モードであっても、PWM信号を生成するための信号が微小信号であることに起因する不安定動作要因を解消することができる。

【発明を実施するための最良の形態】

【0011】

以下、図面を用いて本発明のスイッチング電源について説明する。

図1に、本発明のスイッチング電源に係る全体構成例を示す。図11と同じ部位には、同じ符号を付して詳細な説明を省略する。本実施例の図11に示すスイッチング電源との違いは、加算スロープ回路20を設け、その出力である加算スロープ信号を加算回路9への3つめの入力信号としたことにある。加算スロープ回路20は入力端子21からの信号Min.Pulseが入力され、信号Min.Pulseにより指示される期間、単調増加する信号を発生し、それを加算スロープ信号として加算回路9に入力する。信号Min.Pulseは信号OSC同じ周波数(すなわちスイッチング周波数と同じ周波数)で、かつ同期をとられた信号であり、信号OSCの新しい周期が開始すると加算スロープ回路20に加算スロープ信号の生成を指示する。

図2に加算スロープ回路20の第1の構成例を関連部分とともに示す。本図において、図12と同じ部位には、同じ符号を付して詳細な説明を省略する。図2において加算スロープ回路20は、NチャネルMOSトランジスタM7,M8,PチャネルMOSトランジスタM9,M10,定電流源I1,コンデンサC2および抵抗R4を有している。構成はスロープ補償回路8と同様であり、定電流源I1とコンデンサとC2が積分回路を構成し、NチャネルMOSトランジスタM7がそのリセットトランジスタとなっている。ワンショット回路21の出力である信号Min.PulseがLであるとリセットトランジスタM7がオフするので、その期間に定電流源からの定電流(その値もI1とする)がコンデンサC2(その容量値もC2とする)に積分され、時間をtとするとコンデンサC2の両端電圧はI1×t/C2となって直線的に立ち上がる。コンデンサC2による積分電圧はNチャネルMOSトランジスタM8のゲートに印加され、NチャネルMOSトランジスタM8はソースフォロワ回路として動作し、抵抗R4にV2=(コンデンサC2の積分電圧−NチャネルMOSトランジスタM8の閾値電圧)の電圧を加える。抵抗R4の抵抗値をR4とすると抵抗R4にはI4=V2/R4の電流が流れ、I4も直線的に上昇する信号となる。PチャネルMOSトランジスタM9とM10はカレントミラー回路を構成していて、PチャネルMOSトランジスタM10に流れる電流I5は、電流I4をコピーしたものになっている。この電流I5が加算スロープ信号に相当する。

【0012】

電流I5は電流I1,I3とともに抵抗Raに流れ、これにより合成信号Vsigは、Vsig=Ra×(I1+I3+I5)=Ra×I1+Ra×I3+Ra×I5 となる。

信号Min.PulseがHであるとリセットトランジスタM7がオンするので、加算スロープ信号I5がゼロとなり、加算スロープ信号は合成信号Vsigの生成に寄与しなくなる。また、ワンショット回路22には信号OSCが入力され、ワンショット回路22は信号OSCが立ち上がると所定期間Lとなりその後Hとなる信号を生成する。

図1,2の回路に係るタイミングチャートを図3,4に示す。図3はエラーアンプERRAMPの出力であるフィードバック信号FBが小さく、加算スロープ信号が増加しているときに合成信号Vsigとフィードバック信号FBが等しくなる場合であり、図4はフィードバック信号FBが大きく、加算スロープ信号の増加期間が終了してから合成信号Vsigとフィードバック信号FBが等しくなる場合である。

図3において、OSC信号がHになると、上述のようにスロープ補償回路8がトリガーされてスロープ補償信号が立ち上がるとともに、ワンショット回路22が所定期間Lとなる信号(Min.Pulse信号)を出力して加算スロープ信号も立ち上がる(増加を始める)。この所定期間の間は、加算スロープ信号,スロープ補償信号および電流検出信号の和が合成信号Vsigとなる(電流検出信号は、スイッチング素子がオフするとゼロになって合成信号Vsigに寄与しなくなる)。フィードバック信号FBが小さいので合成信号Vsigとフィードバック信号FBが上記所定期間のうちに等しくなってPWM信号が終了し(Lになり)、スイッチング素子Mpがオフするから電流検出信号もゼロになる。この場合、フィードバック信号FBが小さいといっても、ある程度傾斜の大きい加算スロープ信号が電流検出信号に重畳されて合成信号Vsigもある程度の大きさを有しているので、これとバランスをとる(合成信号Vsigと等しくなる点で適切な時比率を与える)フィードバック信号FBも従来より大きな値をとるようになるので、フィードバック信号FBや合成信号Vsigが微小信号であることに起因する不安定動作要因を解消することができる。

【0013】

図4は軽負荷ではない場合に相当し、フィードバック信号FBが従来でも大きくなる領域である。上記の所定期間が経過しても合成信号Vsigとフィードバック信号FBが等しくならないと、加算スロープ信号がゼロに戻り、以降はスロープ補償信号と電流検出信号の和が合成信号Vsigとなる。この合成信号Vsigがフィードバック信号FBに等しくなるとスイッチング素子Mpがオフし、電流検出信号がゼロになるから、以降は合成信号Vsigがスロープ補償信号だけを反映した信号となる。

図5に加算スロープ回路の第2の構成例を関連部分とともに示す。図5に示す回路は、図2の第1の加算スロープ回路20を第2の加算スロープ回路20’に置き換えたものである。第2の加算スロープ回路20’に対しては、ワンショット回路21の出力Min.Pulseではなく、信号OSCが直接入力される。第1の加算スロープ回路20に対する第2の加算スロープ回路20’の違いは、コンデンサC2に並列にツェナーダイオードZDを設けた点である。第2の加算スロープ回路20’はツェナーダイオードZDを除き、スロープ補償回路8と同様の構成・動作を行う。すなわち、第2の加算スロープ回路20’はスロープ補償回路8と同様に信号OSCでトリガーされて一定の傾きで増加する加算スロープ信号I5を生成する。加算スロープ信号I5の増加はスイッチング周期の最後まで続くものではなく、コンデンサC2の積分電圧(両端電圧)がツェナーダイオードZDのツェナー電圧Vzに達した時点でクランプされて増加は終了する。すなわち、コンデンサC2の積分電圧がVzでクランプされるので、電圧V2は以降(Vz−NチャネルMOSトランジスタM8の閾値電圧)の定電圧となり、これにより電流I4,I5も定電流となる。

【0014】

図1,5の回路に係るタイミングチャートを図6,7に示す(図1において、信号Min.Pulseが信号OSCに置き換えられているものとする)。図6,7は、図1,2に関する図3,4に対応するものであり、それぞれ、エラーアンプERRAMPの出力であるフィードバック信号FBが小さく、加算スロープ信号が増加しているときに合成信号Vsigとフィードバック信号FBが等しくなる場合、およびフィードバック信号FBが大きく、加算スロープ信号の増加期間が終了してから合成信号Vsigとフィードバック信号FBが等しくなる場合のタイミングチャートである。

図6においてOSC信号がHになると、上述の実施例と同様にスロープ補償回路8がトリガーされてスロープ補償信号が立ち上がるとともに、第2の加算スロープ回路20’もトリガーされて加算スロープ信号が立ち上がる(増加を始める)。コンデンサC2の積分電圧がツェナーダイオードZDのツェナー電圧Vzに達するまでは、加算スロープ信号,スロープ補償信号および電流検出信号の和が合成信号Vsigとなる(電流検出信号は、スイッチング素子がオフするとゼロになって合成信号Vsigに寄与しなくなる)。フィードバック信号FBが小さいので合成信号Vsigとフィードバック信号FBが、コンデンサC2の積分電圧がツェナーダイオードZDのツェナー電圧Vzに達する前に等しくなってPWM信号が終了し(Lになり)、スイッチング素子Mpがオフするから電流検出信号もゼロになる。この場合、フィードバック信号FBが小さいといっても、上述の実施例と同様にある程度傾斜の大きい加算スロープ信号が電流検出信号に重畳されて合成信号Vsigもある程度の大きさを有しているので、これとバランスをとるフィードバック信号FBも従来より大きな値をとり、フィードバック信号FBや合成信号Vsigが微小信号であることに起因する不安定動作要因を解消することができる。

【0015】

図7は軽負荷ではない場合に相当し、フィードバック信号FBが従来でも大きくなる領域である。コンデンサC2の積分電圧がツェナーダイオードZDのツェナー電圧Vzに達しても合成信号Vsigとフィードバック信号FBが等しくならないと、加算スロープ信号はコンデンサC2の積分電圧がツェナー電圧Vzに達した時点の値を保ち、以降はその一定値とスロープ補償信号と電流検出信号との和が合成信号Vsigとなる。この合成信号Vsigがフィードバック信号FBに等しくなるとスイッチング素子Mpがオフし、電流検出信号がゼロになるから、以降はスロープ補償信号と上記一定値の和の信号が合成信号Vsigとなる。

上述の実施例において、定電流源I1の定電流I1の大きさは信号OSCの周波数、すなわちスイッチング周波数に比例したものであるとよい。これは、スイッチング周波数が変化しうるものであり、スイッチング周波数もしくはスイッチング周期が変化しても定電流I1の値が一定であると、スイッチング周期が短い場合は加算スロープ信号の立ち上がりが遅すぎることになり、スイッチング周期が長い場合は加算スロープ信号の立ち上がりが速すぎることになって不具合が生じるからである。なお、スイッチング周波数は、負荷の軽重や入出力電圧の変化などによって変化させる場合がある。加算スロープ信号については、上記Min.Pulseのパルス幅をスイッチング周期に比例する時間として当該時間経過後に加算スロープ信号の大きさがスイッチング周波数によらず一定値になる、もしくはコンデンサC2の積分電圧がツェナー電圧Vzに達するまでの時間がスイッチング周期に比例したものになることが望ましい。このためには、定電流I1がスイッチング周期に反比例、すなわちスイッチング周波数に比例するものであればよい。

【0016】

スイッチング周波数に比例する定電流I1を与える回路の例を図8に示す。図8において、VCOは電圧制御発振器(Voltage Controlled Oscillator)であり、入力信号f_sigの電圧に比例した周波数の信号OSCを生成・出力する。また、図8の回路はオペアンプ(演算増幅器)OP1,PチャネルMOSトランジスタM11,M12および抵抗R5も有していて、この部分が定電流源I1に相当する。入力信号f_sigはオペアンプOP1の反転入力端子に入力され、オペアンプOP1の出力はPチャネルMOSトランジスタM11,M12のゲートに接続されている。出力はPチャネルMOSトランジスタM11のドレインは抵抗R5の一端およびオペアンプOP1の非反転入力端子に接続されている。この構成により、オペアンプOP1の反転入力端子と非反転入力端子は仮想短絡されるから、抵抗R5には入力信号f_sigの電圧が印加される。従い、抵抗R3には入力信号f_sigの電圧に比例した、すなわちスイッチング周波数に比例した電流I6が流れる。PチャネルMOSトランジスタM11とM12はカレントミラー回路を構成していて、PチャネルMOSトランジスタM12に流れる電流はPチャネルMOSトランジスタM11に流れる電流(すなわち抵抗R3に流れる電流)I6に等しい、もしくは比例したものになる。従い、PチャネルMOSトランジスタM12のドレインから供給される電流はスイッチング周波数に比例したものになり、これを定電流I1としてコンデンサC2で積分すればよい。

【0017】

図9に、電圧制御発振器VCOおよびスイッチング周期に比例したMin.Pulse信号のパルス幅を与える回路の構成例を示す。この回路では、定電流源I1の構成要素であるオペアンプ(演算増幅器)OP1,PチャネルMOSトランジスタM11および抵抗R5を、電圧制御発振器VCOが共有している。電圧制御発振器VCOはこの他に、PチャネルMOSトランジスタM13,M14,M17,NチャネルMOSトランジスタM15,M16,M18,コンデンサCt,ワンショット回路23,ヒステリシスコンパレータCMP1,コンパレータCMP2およびオア(OR)ゲート24を有している。PチャネルMOSトランジスタM13,M14はゲートが共通に接続されてカレントミラー回路を構成し、PチャネルMOSトランジスタM13に流れる電流I7およびPチャネルMOSトランジスタM14に流れる電流I8は、PチャネルMOSトランジスタM11に流れる電流I6に等しいか、もしくは比例したものになっている。PチャネルMOSトランジスタM13とNチャネルMOSトランジスタM15は直列に接続され、NチャネルMOSトランジスタM15とM16とがカレントミラー回路を構成しているから、NチャネルMOSトランジスタM16に流れる電流I9は電流I7に等しいか、もしくは比例するものになる。PチャネルMOSトランジスタM14,M17とNチャネルMOSトランジスタM18,M16は直列に接続され、PチャネルMOSトランジスタM17とNチャネルMOSトランジスタM18はヒステリシスコンパレータCMP1の出力V4により交互にオン・オフするので、PチャネルMOSトランジスタM17とNチャネルMOSトランジスタM18の接続点に接続されているコンデンサCtは、電流I8で充電される(PチャネルMOSトランジスタM17がオンしている場合)か、電流I9で放電される(NチャネルMOSトランジスタM18がオンしている場合)かのいずれかの状態となる。コンデンサCtの充電電圧V3は、ヒステリシスコンパレータCMP1により基準電圧Vref1,Vref2(Vref1<Vref2)と比較され、コンパレータCMP2により基準電圧Vref3(Vref1<Vref3<Vref2)と比較される。ヒステリシスコンパレータCMP1の出力V4とコンパレータCMP2の出力V5はオアゲート24によって論理和をとられて信号Min.Pulseになる。また、ヒステリシスコンパレータCMP1の出力V4はワンショット回路23に入力され、ワンショット回路23は信号V4の立下りでトリガーされて一定幅のHパルスを出力する。

【0018】

図9の回路の動作について、図10のタイミングチャートを用いて説明する。ヒステリシスコンパレータCMP1の出力V4がHであるとコンデンサCtの電荷が定電流I9によって放電されるため、コンデンサCtの積分電圧V3は直線的に減少する。電圧V3が基準電圧Vref1に達するとヒステリシスコンパレータCMP1の出力V4は反転してLとなるとともに、ヒステリシスコンパレータCMP1の基準電圧がVref1からVref2に切り替わる。ヒステリシスコンパレータCMP1の出力V4がLであるとコンデンサCtは定電流I8によって充電されるため、コンデンサCtの積分電圧V3は直線的に増加する。電圧V3が基準電圧Vref2に達するとヒステリシスコンパレータCMP1の出力V4は反転してHとなるとともに、ヒステリシスコンパレータCMP1の基準電圧がVref2からVref1に切り替わる。この動作を繰り返し、コンデンサCtの積分電圧V3はVref1とVref2の間で振動する三角波となる。

一方、コンパレータCMP2は、コンデンサCtの積分電圧V3と基準電圧Vref3との比較を行って、信号V5を出力する。信号V4と信号V5はオアゲート24によって論理和をとられて、信号OSCの立ち上がりからコンデンサCtの積分電圧V3が基準電圧Vref3に達するまでの期間Lとなる信号Min.Pulseとなる。信号V4がLとなっている時間をT1、信号V4がHとなっている時間をT2とすると、T1=K1×I6,T2=K2×I6(K1,K2は定数)となる。信号Min.Pulseのパルス幅(Lとなっている期間)をT0とすると、T0=T1×(Vref3−Vref1)/(Vref2−Vref1)となるから、T0とスイッチング周期(=T1+T2)の比は、T0/(T1+T2)=(K1/(K1+K2))×(Vref3−Vref1)/(Vref2−Vref1)となり、スイッチング周波数に依存しない一定値となる。

【0019】

また、本発明はスロープ補償を行わない場合でも有効である。この場合、上述の説明においてスロープ補償信号が常にゼロであると考えればよい。合成信号Vsigは加算スロープ信号と電流検出信号の和信号となる。これを第1の和信号と考えれば、上述の加算スロープ信号,スロープ補償信号および電流検出信号を加算した信号は第2和信号といえる。

さらに、スロープ補償信号を加算スロープ信号および電流検出信号と一緒に加算して上記和信号,第2和信号を求める実施例について説明してきたが、エラーアンプERRAMPの出力であるフィードバック信号FBからスロープ補償信号を差し引いたものと、加算スロープ信号と電流検出信号との和信号をPWMコンパレータPWMCMPで比較してPWM信号を生成するようにしてもよい。この場合も電流検出信号に加算スロープ信号が加算されて合成信号Vsigはある程度の大きさを有しているので、これとバランスをとる(合成信号Vsigと等しくなる点で適切な時比率を与える)信号(フィードバック信号FB−スロープ補償信号)も従来より大きな値をとるようになるので、PWM信号を生成するための信号が微小信号であることに起因する不安定動作要因を解消することができる。

【図面の簡単な説明】

【0020】

【図1】本発明のスイッチング電源に係る全体構成例を示す図である。

【図2】加算スロープ回路20の第1の構成例を関連部分とともに示す回路図である。

【図3】図1,2の回路に係るタイミングチャートである。

【図4】図1,2の回路に係る別のタイミングチャートである。

【図5】加算スロープ回路の第2の構成例を関連部分とともに示す回路図である。

【図6】図1,5の回路に係るタイミングチャートである。

【図7】図1,5の回路に係る別のタイミングチャートである。

【図8】スイッチング周波数に比例する定電流I1を与える回路例を示す図である。

【図9】電圧制御発振器VCOおよびスイッチング周期に比例したMin.Pulse信号のパルス幅を与える回路の構成例を示す図である。

【図10】図9の回路の動作について説明するためのタイミングチャートである。

【図11】従来の電流モードのスイッチング電源の一例を示す回路図である。

【図12】電流検出手段7、スロープ補償回路8および加算回路9の構成例を示す回路図である。

【図13】図11,12の回路の動作を説明するためのタイミングチャートである

【図14】軽負荷でかつスイッチング周波数が高いときにセンス抵抗Rsにより検出される電流検出信号が微小になる様子を示すための図である。

【符号の説明】

【0021】

1,6,21 入力端子

2,3 ドライブ回路

4 出力端子

5 RSフリップフロップ

7 電流検出手段

8 スロープ補償回路

9 加算回路

10,11 レベルシフト回路

12 トランスコンダクタンスアンプ

20 加算スロープ回路

22,23 ワンショット回路

24 オアゲート

C1,C2,Cc,Co,Ct コンデンサもしくはその容量値

CMP1 ヒステリシスコンパレータ

CMP2 コンパレータ

ERRAMP エラーアンプ(誤差増幅器)

I0,I1 定電流源もしくはその定電流値

I2〜I9 定電流

L インダクタ

R1〜R5,Ra,Rc,Rs 抵抗もしくはその抵抗値

VREF,Vref1〜Vref3 基準電圧源もしくは基準電圧値

VIN 入力電源もしくはその電圧

VOUT 出力もしくはその電圧

M1,M2,M5,M6,M9〜14,M17 PチャネルMOSトランジスタ

M3,M4,M7,M8,M15,M16,M18 チャネルMOSトランジスタ

Mn 同期整流素子(NチャネルMOSトランジスタ)

Mp スイッチング素子(PチャネルMOSトランジスタ)

OP1 オペアンプ(演算増幅器)

ZD ツェナーダイオード

【特許請求の範囲】

【請求項1】

スイッチング素子のオン・オフを制御して所定の電圧の出力を生成するスイッチング電源において、

前記出力の電圧またはその分圧と基準電圧を比較してその差に応じた誤差信号を出力する誤差増幅器と、

前記スイッチング素子に流れる電流を検出する電流検出手段と、

前記スイッチング手段がオンする前にゼロリセットされ、前記スイッチング手段がオンすると増加を開始し、前記スイッチング素子のスイッチング周期より短い所定時間経過後に増加を停止する加算スロープ信号を生成する加算スロープ回路とを有し、

前記電流検出手段の出力と前記加算スロープ信号を加算した和信号を求め、該和信号と前記誤差信号を比較して前記和信号が前記誤差信号に等しくなったときに前記スイッチング素子をオフにすることを特徴とするスイッチング電源。

【請求項2】

サブハーモニック発振を防ぐためのスロープ補償信号を生成するスロープ補償回路をさらに有し、前記和信号の替わりに前記和信号にさらに前記スロープ補償信号を加算した第2和信号を前記誤差信号と比較して、前記第2和信号が前記誤差信号に等しくなったときにスイッチング素子をオフにすることを特徴とする請求項1に記載のスイッチング電源。

【請求項3】

サブハーモニック発振を防ぐためのスロープ補償信号を生成するスロープ補償回路をさらに有し、前記誤差信号の替わりに前記誤差信号から前記スロープ補償信号を差し引いた差信号を前記和信号と比較して、前記和信号が前記差信号に等しくなったときにスイッチング素子をオフにすることを特徴とする請求項1に記載のスイッチング電源。

【請求項4】

前記加算スロープ回路が定電流で充電されるコンデンサを有し、該コンデンサの両端電圧を前記加算スロープ信号とすることを特徴とする請求項1ないし3のいずれか1項に記載のスイッチング電源。

【請求項5】

前記定電流が前記スイッチング素子のスイッチング周波数に比例することを特徴とする請求項4に記載のスイッチング電源。

【請求項6】

前記加算スロープ信号の増加率が前記スイッチング素子のスイッチング周波数に比例することを特徴とする請求項1ないし3のいずれか1項に記載のスイッチング電源。

【請求項7】

前記所定時間が前記スイッチング素子のスイッチング周期に比例することを特徴とすることを請求項5または6に記載のスイッチング電源。

【請求項8】

前記電流検出手段が前記スイッチング素子に接続された抵抗の両端電圧を検出するものであることを特徴とする請求項1に記載のスイッチング電源。

【請求項1】

スイッチング素子のオン・オフを制御して所定の電圧の出力を生成するスイッチング電源において、

前記出力の電圧またはその分圧と基準電圧を比較してその差に応じた誤差信号を出力する誤差増幅器と、

前記スイッチング素子に流れる電流を検出する電流検出手段と、

前記スイッチング手段がオンする前にゼロリセットされ、前記スイッチング手段がオンすると増加を開始し、前記スイッチング素子のスイッチング周期より短い所定時間経過後に増加を停止する加算スロープ信号を生成する加算スロープ回路とを有し、

前記電流検出手段の出力と前記加算スロープ信号を加算した和信号を求め、該和信号と前記誤差信号を比較して前記和信号が前記誤差信号に等しくなったときに前記スイッチング素子をオフにすることを特徴とするスイッチング電源。

【請求項2】

サブハーモニック発振を防ぐためのスロープ補償信号を生成するスロープ補償回路をさらに有し、前記和信号の替わりに前記和信号にさらに前記スロープ補償信号を加算した第2和信号を前記誤差信号と比較して、前記第2和信号が前記誤差信号に等しくなったときにスイッチング素子をオフにすることを特徴とする請求項1に記載のスイッチング電源。

【請求項3】

サブハーモニック発振を防ぐためのスロープ補償信号を生成するスロープ補償回路をさらに有し、前記誤差信号の替わりに前記誤差信号から前記スロープ補償信号を差し引いた差信号を前記和信号と比較して、前記和信号が前記差信号に等しくなったときにスイッチング素子をオフにすることを特徴とする請求項1に記載のスイッチング電源。

【請求項4】

前記加算スロープ回路が定電流で充電されるコンデンサを有し、該コンデンサの両端電圧を前記加算スロープ信号とすることを特徴とする請求項1ないし3のいずれか1項に記載のスイッチング電源。

【請求項5】

前記定電流が前記スイッチング素子のスイッチング周波数に比例することを特徴とする請求項4に記載のスイッチング電源。

【請求項6】

前記加算スロープ信号の増加率が前記スイッチング素子のスイッチング周波数に比例することを特徴とする請求項1ないし3のいずれか1項に記載のスイッチング電源。

【請求項7】

前記所定時間が前記スイッチング素子のスイッチング周期に比例することを特徴とすることを請求項5または6に記載のスイッチング電源。

【請求項8】

前記電流検出手段が前記スイッチング素子に接続された抵抗の両端電圧を検出するものであることを特徴とする請求項1に記載のスイッチング電源。

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【図14】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【図14】

【公開番号】特開2009−71978(P2009−71978A)

【公開日】平成21年4月2日(2009.4.2)

【国際特許分類】

【出願番号】特願2007−237791(P2007−237791)

【出願日】平成19年9月13日(2007.9.13)

【出願人】(503361248)富士電機デバイステクノロジー株式会社 (1,023)

【Fターム(参考)】

【公開日】平成21年4月2日(2009.4.2)

【国際特許分類】

【出願日】平成19年9月13日(2007.9.13)

【出願人】(503361248)富士電機デバイステクノロジー株式会社 (1,023)

【Fターム(参考)】

[ Back to top ]