スイッチング電源

【課題】 スイッチング電源の軽負荷状態におけるトランスの唸り音を低減する。

【解決手段】 スイッチング電源において、トランスの1次側に入力される電圧をスイッチングするスイッチング手段と、スイッチング手段のスイッチング動作を制御する制御手段と、を備え、トランスの1次側に流れる電流を電圧に変換して検出して前記制御手段に供給する検出手段が、スイッチング手段の動作状態に応じて、前記制御手段に供給する電圧を制御する。

【解決手段】 スイッチング電源において、トランスの1次側に入力される電圧をスイッチングするスイッチング手段と、スイッチング手段のスイッチング動作を制御する制御手段と、を備え、トランスの1次側に流れる電流を電圧に変換して検出して前記制御手段に供給する検出手段が、スイッチング手段の動作状態に応じて、前記制御手段に供給する電圧を制御する。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、直流電圧を出力するスイッチング電源に関する。

【背景技術】

【0002】

従来のフライバック方式のスイッチング電源において、トランスの1次側の電圧をスイッチングするスイッチング素子(例えば、FET等の素子)のスイッチング動作は、次のように制御される。例えば、トランスの2次側の電圧と、FETを流れる電流に対応する電圧と、FETのドレイン・ソース間の電圧とに基づいて、FETの動作(オン/オフ)が制御される。この動作の制御は、スイッチング動作制御用(専用)ICを使用して、2次側の電圧が第1の基準電圧を越え、且つ、FETのドレイン・ソース間の電圧が第2の基準電圧以下の条件で、FETをオンする。一方、FETを流れる電流に対応する電圧よりも2次側の電圧が低くなる条件で、FETをOFFする。このようなスイッチング電源において、軽負荷状態においてFETのオンする期間を短くすることで、軽負荷時の消費電力を低減させる工夫がなされている(特許文献1参照)。

【0003】

昨今、軽負荷状態における消費電力の低減は、スイッチング電源を搭載した機器の課題の1つとなっている。例えば、スイッチング電源を搭載した機器が、軽負荷状態(動作待機状態ともいう)であった場合の消費電力をより低減させれば、従来の機器に比べて消費電力をより低減した機器を提供することができる。特に、動作待機状態や非動作状態においては、機器の消費電力はスイッチング電源等の電力供給源が装置内で最も電力を消費している状態である場合が多い。従って、スイッチング電源の軽負荷状態における消費電力をより低減させる必要性が高まってきている。

【0004】

ここで、スイッチング電源の軽負荷状態における消費電力の低減を妨げる要因として、スイッチング素子であるFETのスイッチング損失が挙げられる。そこで、FETがオンしている間に流す電流量を増加させて、単位時間当たりのスイッチング回数を減らしてFETのスイッチング損失を低減させる方法が考えられる。

【先行技術文献】

【特許文献】

【0005】

【特許文献1】特開2000−148265号公報

【発明の概要】

【発明が解決しようとする課題】

【0006】

しかしながら、スイッチング素子がオンする期間に流す電流量を増やし、スイッチング回数を減らすとトランスから唸り音が発生するという課題が生じる。スイッチング回数を減らすことにより、スイッチング素子がONする期間に流す電流量が増えると、トランスの唸り音が大きくなる。つまり、軽負荷状態におけるスイッチング損失を低減しようとすると、トランスの唸り音が発生して、ユーザにとってはこの唸り音が耳障りな音として聞こえてしまう。なお、軽負荷状態では機器が非動作状態であることが多いため、ユーザに唸り音が聞こえやすい状態である。

【0007】

本発明は、上記課題に鑑みてなされたものであり、スイッチング電源の軽負荷状態におけるトランスの唸り音を低減することを目的とする。

【課題を解決するための手段】

【0008】

上記目的を達成するための本発明のスイッチング電源は、商用交流電源からの交流電圧を整流及び平滑した直流電圧をスイッチングして得られた電圧を変圧して出力するトランスを有し、前記トランスが出力した電圧を整流及び平滑した電圧を出力するスイッチング電源において、前記トランスの1次側に入力される電圧をスイッチングするスイッチング手段と、前記スイッチング手段のスイッチング動作を制御する制御手段と、を備え、前記トランスの1次側に流れる電流を電圧に変換して検出して前記制御手段に供給する検出手段と、前記検出手段は、前記スイッチング手段の動作状態に応じて、前記制御手段に供給する電圧を制御する。

【発明の効果】

【0009】

以上説明したように、本発明によれば、スイッチング電源において、軽負荷状態における、トランスから発生する唸り音を低減することができる。

【図面の簡単な説明】

【0010】

【図1】実施例1のスイッチング電源の回路図

【図2】実施例1における軽負荷状態の動作波形

【図3】実施例1における通常負荷状態の動作波形及びIS端子に入力される電圧波形

【図4】実施例1における過負荷状態のIS端子に入力される電圧波形

【図5】実施例2のスイッチング電源の回路図

【図6】実施例2におけるIS端子に入力される電圧波形電圧波形

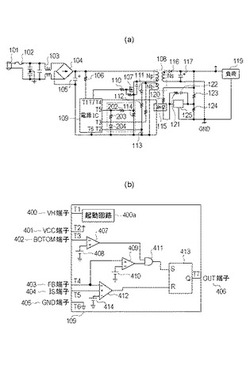

【図7】本発明のスイッチング電源の前提回路図及び電源ICの内部ブロック概要図

【図8】図7のスイッチング電源の動作波形

【図9】省電力化に対応したスイッチング電源の回路図

【図10】図7と図9の夫々の回路の間欠発振時の動作波形

【図11】過負荷検出時の負荷の差を説明する図

【図12】スイッチング損失を説明する図

【図13】トランス構成図

【図14】トランスを上からみた透視図

【図15】トランスの変形を示す図

【図16】トランスの固有振動している状態を示す図

【図17】電磁力によるコアの変形図

【図18】スイッチング電源の適用例を示す図

【発明を実施するための形態】

【0011】

次に、上述した課題を解決するための本発明の具体的な構成について、以下に実施例に基づき説明する。なお、以下に示す実施例は一例であって、この発明の技術的範囲をそれらのみに限定する趣旨のものではない。

【0012】

まず、本発明の前提となるスイッチング電源の軽負荷状態において、トランスの唸り音の発生のメカニズムについて以下に説明する。

【0013】

図13にトランス108の構造図を示す。また、図14はトランスを上面より透視した図である。図13及び図14において、301、302はフェライトコアであり、中央磁脚部にはギャップ(間隔)を設けている。303はコイルボビン、304は一次巻線、305は二次巻線、306は層間紙、307はテープである。トランス108を組み立てる場合、まずコイルボビン303に巻線と層間紙を巻いていく。次に、端子処理を行った後、コア301と302をボビンに通し、コア301と302を固定するために、その外周部にテープ307を巻く。次に、ワニスに含浸させる。一般的に、ワニスとしては不飽和ポリエステル樹脂、変性ポリエステル樹脂、アルキド樹脂等が用いられる。このようなワニスを入れた槽(に規定時間、端子を上にして浸す(ディップ)。その後はワニスを固化するため、数時間、高温度に保つ。このようにワニス含浸処理を行うことでコア301と302同士、コア(301及び302)とコイルボビン303、巻線304と305及び層間紙306にワニスが染み込み、固化して一体となる。

【0014】

しかし、ワニス含浸処理を施したトランス108には、ワニスの含侵具合にバラつきがある。例えば、中央磁脚までワニスが到達して対向する互いの中央磁脚同士が接着されている状態であればトランスの唸り音は小さくなる。逆に、中央磁脚までワニスが到達していない状態であると唸り音が大きくなる。また、外側磁脚同士がきちんと接着されていないと図15のように外側磁脚同士の擦れが発生して大きな唸り音が発生する。これは、トランス108を励磁して磁束が発生して電磁力が発生しているためである。この電磁力は中央磁脚に最も大きく働き、対向する互いの中央磁脚を吸いつける方向即ち図17(a)で示す矢印方向に発生する。電磁力を受けてトランス108は図17(a)のように変形する。スイッチ素子のターンオフにより磁束が減少すると、コアの弾性により復元力が働きトランス108は図18(b)のように変形する。トランスがこのように変形して動くことにより、外側磁脚同士は互いに振動し、擦れによる唸り音が発生する。図16のように、対向する外側磁脚同士をきちんと接着すれば唸り音は軽減されるが、接着されている場合でも接着された外側磁脚が1本の弾性体として振動するため、外側磁脚の固有振動による振動音が残る。つまり、外側磁脚同士を接着した場合でも唸り音を十分に減衰させることは難しい。

【0015】

また、昨今の機器は非動作時において、一層、省電力化が望まれており、スイッチング電源においても非動作時のような軽負荷状態でスイッチング回数を減らして消費電力を低減し、かつ、動作効率の向上を図ったものが増えている。この結果、上記のようなスイッチング電源のトランス108の駆動周波数が可聴周波数域となりトランスの唸り音が大きくなる可能性がある。また、スイッチング損失を低減するためスイッチング素子のオン期間に流す電流量を増やす傾向にあり、この場合、トランス108のコア301と302に働く電磁力が増大するため、図17に示すような振動による唸り音が大きくなる可能性がある。以上が、トランスからの唸り音発生のメカニズムである。

【0016】

次に、本発明の前提となるスイッチング電源の回路構成と動作について図7を用いて説明する。なお、ここで説明するスイッチング電源は一般にフライバック方式のスイッチング電源とも呼ばれる。

【0017】

図7(a)の回路図において、101は商用交流電源から電圧が入力されるインレット、102はヒューズ、103はコモンモードコイル、104は整流ダイオードブリッジ、105は1次平滑コンデンサ、106は電源IC(109)を起動させる起動抵抗である。また、107はトランス(108)の1次巻線Npに流れる電流を断続的に遮断するスイッチング素子である。本例ではMOS−FET(電界効果トランジスタ)を適用している(以下、FET107という)。108は1次巻線Np(1次側)と2次巻線Ns(2次側)を有するフライバックトランスであり、入力された直流電圧を変圧(変換)して出力する。109はFET107のオンオフ動作を制御する電源IC、110はスイッチングFETのゲートに流れる電流を制限するための抵抗、111はトランス108の補助巻線Nbに誘起された電圧を整流するためのダイオードである。112は抵抗、113はコンデンサであり、この抵抗112とコンデンサ113でフィルタ回路を構成している。114はトランス108に流れる電流を検出する電流検出回路の第1の抵抗である電流検出抵抗、115はシャントレギュレータ125の出力を電源IC109に伝達するフォトカプラ、116はトランス108の2次巻線Nsの電圧を整流するダイオード、117は平滑コンデンサである。そして、119はスイッチング電源に接続される負荷、120はフォトカプラに流す電流を制限する抵抗、121は抵抗、122はコンデンサであり、これらは位相保証回路である。また、123、124はレギュレーション抵抗、125はシャントレギュレータである。

【0018】

まず、スイッチング電源の通常動作(通常負荷状態)として、インレット101より入力された商用交流電源からの交流電圧は、整流ダイオードブリッジ104を介し、全波整流されて1次平滑コンデンサ105に直流電圧としてチャージされる。更に、この直流電圧は、起動抵抗106を介して電源IC109を起動させる。電源IC109が起動し、FET107が導通状態(オン状態)になると1次巻線Npに1次平滑コンデンサ105の直流電圧が印加され、補助巻線Nbに1次巻線Npと同極側を正とする電圧が誘起される。このとき2次巻線Nsにも電圧が誘起されるが、ダイオード116のアノード側を負とする電圧であるため2次側には電圧は伝達されない。従って1次巻線Npを流れる電流はトランス108の励磁電流だけで、トランス108には励磁電流の2乗に比例したエネルギーが蓄積される。この励磁電流は時間に比例して増大する。また、補助巻線Nbに誘起された電圧はダイオード111、抵抗112を介して、コンデンサ113を充電し電源IC109に対する電源となる。

【0019】

次に、FET107が非導通状態(オフ状態)になると、トランス108の各巻線には起動時と逆極性の電圧が誘起され、2次巻線Nsにはダイオード116のアノード側を正とする電圧が誘起される。そして、トランス108に蓄積されたエネルギーが、ダイオード116と平滑コンデンサ117で整流及び平滑され、直流電圧出力118となり負荷119に供給される。また、このようにトランス108が動作すると、トランスの補助巻線Nbにより生成された電圧が電源IC109の電源として供給されるようになる。これにより電源IC109は動作を継続することが可能となり、引き続きFETI07をスイッチング動作(オンオフ)させて、トランス108から継続的に安定した電圧を出力することが可能となる。

【0020】

また、直流電圧出力118の電圧値の制御は次のように行なわれる。まず、直流電圧出力118をレギュレーション抵抗123と124とで分圧した電圧がシャントレギュレータ125に入力される。そして、この入力される電圧に応じたフィードバック信号が生成されて、フォトカプラ115を介して電源IC109へ伝達(フィードバック)される。そして、このフィードバック信号に基づき電源IC109がFET107のオンオフ動作を制御することにより、安定した直流電圧を出力すること可能となる。なお、図7(a)の電源IC109には、夫々の端子に対してT1乃至T7の番号を付し、以下に説明する電源IC109の詳細な回路図の各端子との対応関係を示している。

【0021】

次に、上記で説明したスイッチング電源のスイッチング素子であるFET107と、このオンオフ動作を制御する電源IC109の詳細な動作を説明する。なお、ここでは、電源ICとして周波数非固定、デュティー非固定、電流制御モードの動作について説明する。この動作モードは一般的な電源ICの動作モードである。

【0022】

図7(b)に電源IC109の内部ブロックの概要図を示す。図7(b)において、400aは、電源IC109の起動回路、401は電源ICへ給電される電源電圧が入力されるVCC端子、402はBOTOM端子、403はFB端子、404はIS端子、405は電源ICのGND端子、406はOUT端子、407、409、412はコンパレータ、408と410は基準電圧、411はAND回路、413はRSフリップフロップ論理回路である。

【0023】

以下に、図7(b)の電源IC109のブロック図に示した主要部分の機能を説明する。

・VH端子400(T1)及び起動回路400a

起動抵抗106に接続されて起動時の電圧の入力部、及び電源ICを起動する回路。

・VCC端子401(T2)

補助巻線Nbで発生した電圧が入力される電源ICの電源となる電圧の入力部。

・BOTOM端子402(T3)

FET107のドレイン・ソース間の電圧Vdsをモニターする端子。

・FB端子403(T4)

フィードバック端子、直流電圧出力118の変動をフォトカプラ115を介し入力する端子。

・IS端子404(T5)

FET107に流れるドレイン電流Idをモニターする端子。

・GND端子405(T6)

電源ICのGND端子。

・OUT端子406(T7)

FET107のゲート端子に接続される端子。

・コンパレータ407

BOTOM端子402の電圧が基準電圧408を下回ると、AND回路411へHIGH信号を出力する。

・コンパレータ409

FB端子403の電圧が基準電圧408を上回ると、AND回路411へHIGH信号を出力する。

・AND回路411

コンパレータ407とコンパレータ409の出力を入力する。

・コンパレータ412

FB端子403とIS端子404から入力された電圧を比較し、IS端子404の電圧が高い場合にRSフリップフロップ論理回路409へHIGH信号を出力する。さらに、IS端子404から入力された電圧が基準電圧414よりも高くなった場合には、電源IC109の発振動作を停止させる。

・RSフリップフロップ論理回路

周知のRSフリップフロップ論理回路(詳細説明は省略)。

【0024】

このような電源ICにより制御されるスイッチング電源の動作波形を図9に示す。図7乃至図9を用いて、スイッチング電源の電源IC109、FET107、トランス108、ダイオード116の動作を以下に説明する。

【0025】

<図8のタイミング1>

図8のタイミング1は、FET107が導通状態(オン状態)になったばかりの状態である。この時、FET107のドレイン電流Idは直線的に増加する。FET107のドレイン電流Idにより、トランス108にエネルギーが蓄積される。また、ダイオード116を逆バイアスする電位であるため、ダイオード116には電流Ifが流れない状態である。従って、直流電圧出力118は下降している。更に、FB端子403の電圧はフォトカプラ115を介して徐々に上昇する。また、IS端子404の電圧もスイッチングFET107のドレイン電流Idの増加と同様に直線的に増加する。

【0026】

<図8のタイミング2>

図8のタイミング2の状態へ移るタイミングとなるのは、FB端子403の電圧よりもIS端子404の電圧が高い電圧となったタイミングである。このタイミングでRSフリップフロップ論理回路409のR端子がHIGH状態(以下、HIという)となり、RSフリップフロップ論理回路409のQ端子、つまり、電源IC109のOUT端子406がLOWとなり、FET107が、非導通状態(オフ状態)になる。このため、FET107のドレイン電流Idは流れなくなる。また、ダイオード116は正バイアスされて導通状態となり、トランス108に蓄積されたエネルギーがダイオード116の電流Ifとして流れ始めることにより直流電圧出力118は上昇する。このため、FB端子403の電圧はフォトカプラ115を介して徐々に下降する。また、IS端子404の電圧もFET107のドレイン電流Idの停止と同様のタイミングで停止する。

【0027】

<図8のタイミング3>

図8のタイミング3の状態へ移るタイミングは、BOTOM端子402の電圧が基準電圧408以下となり、かつ、FB端子403の電圧が、基準電圧410よりも高くなったタイミングである。この時、AND回路411から、RSフリップフロップ論理回路409のS端子にHIGH信号が入力されて、RSフリップフロップ論理回路409のQ端子、つまり、電源IC109のOUT端子406がHIとなり、FET107が導通状態(オン状態)になる。このタイミング3=タイミング1であり、引き続き、上記のタイミング1から一連の動作が繰り返される。

【0028】

以上説明したように、スイッチング電源(電源IC:周波数非固定、デュティー非固定、電流制御モードで動作)の一連のスイッチング動作が行なわれる。

【0029】

次に、スイッチング回数を減らして、FET107のスイッチング動作による損失を低減した構成及び動作について図9及び図10を用いて説明する。図9における電源IC109の構成は図7(a)と同様であるため省略している。図9の回路の軽負荷状態における動作を図10(b)に示し、比較例として図10(a)に図7(a)の回路の動作を示す。また、図9の回路において、図7(a)の回路と異なるのは、IS端子(T5)への入力ラインにダイオード201が接続されている点である。その他の構成は図7(a)と同様である。図9に示す回路では、このダイオード201により、IS端子に電圧が入力されるタイミングを制御することにより、以下に説明する図12(b)で示す動作を実現している。

【0030】

<図10(b)の期間A>

軽負荷状態において、電流検出抵抗114に発生する電圧がダイオード201の閾値電圧Vfを越えたポイントB0の時点から、IS端子404の電圧は一定の傾きで上昇を開始する。IS端子404の電圧が上昇してFB端子403の電圧と同じ電圧になったタイミングで、FET107は非導通状態(オフ状態)となる。このように、電流検出抵抗114に発生する電圧がダイオード201のVf分だけ低下することを利用して、FET107が導通状態から非導通状態(オンからオフ)となる時間を、図7(a)の動作である図10(a)で示すタイミングより長くしている。なお、図10(a)に比べて非導通状態(オフ状態)となる時間の比率は、ダイオード201の閾値電圧Vfによって決定される。例えば、図9の構成においてFET107のスイッチング回数を図7(a)に対して1/6にする場合は、以下で示す(式1)、(式2)によりダイオード201の閾値Vfを導くことができる。

【0031】

・図7(a)の場合

P1=1/2×L×I1^2 ・・・(式1)

P1:トランス108に蓄えられるエネルギー

L:トランス108のL値

I1:スイッチングFET107のドレインIdのピーク値

・図9の場合

P2=1/2×L×I2^2 ・・・(式2)

P2:トランス108に蓄えられるエネルギー

L:トランス108のL値

I2:スイッチングFET107のドレイン電流Idのピーク値

ここで、スイッチング回数を1/6にするためには、6×P1=P2であることから、I2=√6×I1となる。つまり、スイッチングFET107の導通時間も図7(a)と比較して、図10の場合は√6倍となることから、IS端子404のピーク電圧をVISとすると、1+Vf/VIS=√6であるため、Vf=(√6−1)×VISとなる。

【0032】

なお、図7の場合と図10(b)の場合における過負荷検出のタイミングの違いを図11に示す。この図に示すように、ダイオード201を設けたため、過負荷検出のタイミングに差が生じることがわかる。この差が大きくなると過負荷状態を誤検出する可能性がでてくる。

【0033】

<図10(b)の期間B>

タイミングBは、FET107が非導通状態(オフ状態)となった後、トランス108に蓄積したエネルギーをフライバック電流として、トランス108の2次側に流し出す期間を示している。なお、フライバック電流を流しきった後も、FB端子403の電圧が基準電圧410を越えない限り、AND回路411からの出力をHIにすることができないため、フリップフロップ論理回路409のS端子をHIにすることができない。従って、FET107が導通することができない。このように、フライバック電流を流しきった後も、FET107は非導通状態(オフ状態)を続けるようにスイッチング動作を制御して、直流電圧出力118が安定するように制御している。

【0034】

<図10(b)の期間C>

再び、FET107が導通状態(オン状態)となる期間を示す。FET107が導通する(オンする)には、FB端子403の電圧が基準電圧410を越え、かつ、BOTOM端子402の電圧が基準電圧408以下となる必要があり、フライバック電流を流しきった後は直流電圧出力118が下降していくので、FB端子403の電圧が徐々に上昇し、基準電圧410を越えるためFET107が導通状態(オン状態)となる。

【0035】

上記のとおり、FET107を導通状態になるタイミングは、BOTOM端子402の電圧が基準電圧408以下となり、かつ、FB端子403の電圧が基準電圧410よりも高くなったタイミングである。通常負荷状態であれば、FB端子電圧は基準電圧410よりも十分に高いため、BOTOM端子402の電圧が基準電圧408以下になるタイミングでFET107を導通状態にする。これに対して、軽負荷状態ではFB端子の電圧が低く、トランス108に蓄積したエネルギーがフライバック電流としてトランスの2次側に流れ出ている間に、FB端子が基準電圧410よりも低くなる。このため、フライバック電流を流しきった後、FB端子が基準電圧410よりも高くなるまではスイッチングFET107を導通状態にすることができない。このように、軽負荷時には、図10(b)示すとおり間欠発振する動作となる。

【0036】

以上説明したように、図9の回路によってスイッチング回数を減らし、図7(a)で示す回路よりも軽負荷状態における省電力化が可能となる。

【0037】

なお、FET107のスイッチング損失について図12に概要図を示した。この図に示すようにスイッチング損失とは、FET107がスイッチング動作時(オンオフ動作時)に発生する損失のことである。スイッチング動作時のFET107のドレイン・ソース間の電圧Vdsと、ドレイン電流Idを掛け合わせた電力で示される。このスイッチング損失は、上記の図10(a)の場合よりも、図10(b)の場合の方が低減される。

【0038】

以下、上記したスイッチング電源の構成及び動作を前提として、本発明の特徴的な構成及び動作についていくつかの実施例を示して詳細に説明する。

【0039】

(実施例1)

実施例1のスイッチング電源の回路を図1に示す。図1の回路は、上記の図7と基本構成は同様である。図1において、図7との違いは、電流検出回路部として電流検出抵抗114に対して、第2及び第3の抵抗である抵抗203と抵抗204とダイオード204を直列に接続した回路を並列に接続し、抵抗203と抵抗204の接続点が電源ICのIS端子404に接続される点である。

【0040】

図1の点線で囲んだ回路が本例の特徴部であり複数の抵抗とダイオードから構成される。具体的には、第1抵抗としての電流検出抵抗114、第2抵抗としての抵抗203、第3抵抗としての抵抗204、ダイオード204から構成される回路である。なお、その他の構成は図7と同様であるため詳細な説明は省略する。

【0041】

本例の図1の構成は、上記の図7の回路に比べて、軽負荷状態におけるトランス108の唸り音を低減することができる。また、唸り音の低減に加え、過電流の誤検出を防ぐことができる点も特徴である。以下に本例の回路動作について、〔1〕軽負荷状態の回路動作、〔2〕通常負荷状態の回路動作、〔3〕過負荷状態の回路動作の夫々について詳細に説明する。

【0042】

〔1〕軽負荷状態の回路動作

図1に示す回路における軽負荷状態(間欠発振)の動作波形を図2(a)、電源IC109のIS端子404の電圧波形(1回のスイッチングにおける電圧波形)を図2(b)に示す。FET107が導通して(オンして)、IS端子404の電圧は一定の傾きで上昇を開始する。IS端子404の電圧が上昇し、FB端子403の電圧と同じ電圧になったタイミングで、FET107は非導通状態(オフ状態)となる。軽負荷状態では、ダイオード204の順方向電圧Vfを越えないので、電流検出抵抗114により検出された電圧が、そのままIS端子404に入力される。ここで、電流検出抵抗114は、トランス108の唸り音を低減させるため、上記の図7の回路よりも高い抵抗値に設定している。これにより、図2(b)で示すとおり、軽負荷状態では上記の図7よりもスイッチング周期が短くなる(スイッチング周波数が高くなる)。その結果、トランス108に1度に流れる電流値が低下する。つまり、軽負荷状態においてFET107のスイッチング1回におけるトランス108に流れる電流値を図7の回路に比べて低下させることで、トランス108のコアの電磁力が弱くなりトランス108唸り音が低減できる。なお、軽負荷状態におけるIS端子404に入力される電圧をVIS、電流検出抵抗114により検出された電圧をVo、電流検出抵抗114の抵抗値をRIS、FET107に流れるドレイン電流をIdとすると、IS端子404の電圧VISは以下に示す(式3)で表される。

VIS=Vo=RIS×Id ・・・(式3)

【0043】

〔2〕通常負荷状態の回路動作

通常負荷状態の動作波形を図3(a)、IS端子404の電圧波形(1回のスイッチングにおける電圧波形)を図3(b)に示す。通常負荷状態においては、IS端子404の電圧がダイオード204のVfを越えたタイミング(ポイントB1)で傾きが変化する。0VからポイントB1までの電圧(IS端子404の電圧)は、軽負荷状態と同じ傾きで上昇するが、ポイントB1を超えると、分圧抵抗202と203によって決められた分圧比の傾きで増加するようになる(上昇率を切り換えて、傾きが緩やかになる)。ここで、IS端子404の電圧をVIS、電流検出抵抗114により検出された電圧をVo、電流検出抵抗114の抵抗値をRIS、FET107に流れるドレイン電流をId、分圧抵抗202と203の夫々の抵抗値をRa,Rb、ダイオード204の順方向電圧をVf、分圧抵抗202と203とダイオード204の直列回路に流れる電流をiとすると、IS端子404の電圧VISは以下に示す(式4)、(式5)、(式6)で表される。以下の(式4)乃至(式6)によれば、IS端子404の電圧VISがダイオード204の順方向電圧Vfと等しくなったタイミングがポイントB1であることがわかる。

RIS<<Ra,Rbに設定した場合、Id>>iより、

Vo≒Ra×Id・・・(式4)

VIS=Vo−Ra×i、VIS=Vf+Rb×iより、

VIS=((Ra×Vf)+(Rb×Vo))/(Ra+Rb)・・・(式5)

この時のポイントB1の境界条件は、上記(式4)において、VIS=Voとして、

VIS=((Ra×Vf)+(Rb×Vo))/(Ra+Rb)

=((Ra×Vf)+(Rb×VIS))/(Ra+Rb)

(Ra+Rb)×VIS=(Ra×Vf)+(Rb*VIS)・・・(式6)

つまり、VIS=Vfとなり、S端子404の電圧VISがダイオード204の順方向電圧Vfと等しくなったタイミングがポイントB1となる境界条件であることがわかる。

【0044】

〔3〕過負荷状態の回路動作

過負荷状態におけるIS端子404の電圧波形(1回のスイッチングにおける電圧波形)を図4に示す。ここで過負荷状態とは、出力電流が過剰に流れてしまう負荷状態を意味する。スイッチンン具電源としては、過負荷状態を正しく検出して電源IC109の発振動作を停止させる必要がある。IS端子404のピーク電圧が、コンパレータ412の基準電圧414よりも高くなった場合に、電源IC109は発振動作を停止させる。過負荷の検出動作に対しても、電流検出抵抗114によって検出された電圧から、ダイオード204の順方向電圧Vf分を差し引いた電圧を抵抗202と203によって分圧した電圧がIS端子404に入力される。この時の動作波形が図4である。上記の図7の回路と比べて、最終的な過負荷検出の値は同じになる。図4のポイントB2は、このポイントB2でIS端子404のピーク電圧がダイオード201の順方向電圧Vfを越えたことを意味する。このポイントB2から、抵抗202と203の分圧比によって定められた傾きでIS端子404の電圧が上昇していく(上昇率を切り換えて、傾きが緩やかになる)。

【0045】

このように、過負荷状態では、ダイオード204がオンすることで、電流検出抵抗114によって検出された電圧から、ダイオード204の順方向電圧Vf分を差し引いた電圧に対して、抵抗202と203によって分圧された電圧がIS端子404に入力される。これによりIS端子に入力される電圧の傾きが緩やかになり、図7の回路と同じタイミングで必要な負荷(上記の図7の場合と同じ負荷)で正しく過負荷を検出することが可能となる。この電圧の傾きは抵抗202と203の分圧比によって決まるため、ダイオード204の順方向電圧Vfを考慮し、抵抗202と203の分圧比を調整することにより設定することができる。なお、ダイオード204を設けない場合は、点線で示すように過負荷を検出するタイミングが大幅に遅れてしまい、過負荷状態が継続されることによる誤動作(素子の破壊等による)が発生する可能性が高まる。

【0046】

このような過負荷検出の構成は、電源ICとして、通常動作状態でスイッチング素子を停止するための端子と、過負荷を検出するための端子が共通化されているICを用いる場合に特に有効となる。なぜなら、このような電源ICに図1の回路を適用すると、通常動作状態において過負荷を検出する場合の負荷が高くなってしまうため、上記の図7の構成よりも過電流(過負荷)を保護するタイミングが遅れてしまう可能性がある。これでは、スイッチング素子(MOS−FET)や各種素子の定格(耐圧)を上げることになり、素子の大型化やコストアップにつながる。本例の図1の構成であれば、素子の定格を上げずに対応することができる。

【0047】

ここで、IS端子404の電圧をVIS、電流検出抵抗114により検出された電圧をVo、電流検出抵抗114の抵抗値をRIS、FET107に流れるドレイン電流をId、抵抗202と抵抗203の夫々の抵抗値をRa,Rbとし、ダイオード204の順方向電圧Vfにおける、抵抗202と203の夫々の抵抗値RaとRbを設定する方法を以下に説明する。

VIS=((Ra×Vf)+(Rb×Vo))/(Ra+Rb)・・・(式7)

Vo≒Ra×Id・・・(式8)

式(7)、式(8)より、

VIS=((Ra×Vf)+(Rb×Ra×Id))/(Ra+Rb)・・・(式9)

【0048】

上記の(式9)に、過負荷検出のためのドレイン電流値Idと、ダイオード204の順方向電圧Vf、IS端子404が電源ICの発振動作を停止させる電圧VISを入力すれば、必要な過負荷検出のための分圧抵抗202,203の夫々の抵抗値Ra,Rbの算出することができる。

【0049】

以上説明したように、本実施例のスイッチング電源によれば、軽負荷状態におけるトランスから発生する唸り音を低減することができる。さらに、過負荷(過電流)の誤検出を防ぐことができる。

【0050】

(実施例2)

実施例2のスイッチング電源の回路図を図5に示す。図5に示す回路は、上記の図7で示した回路と基本構成は同じである。図5と図7との違いは、電流検出回路部として、電流検出抵抗114と並列に第2と第3の抵抗である抵抗203,抵抗204、スイッチング素子205を直列に接続した回路を接続し、抵抗203と抵抗204の接続点が電源IC109のIS端子404に接続される点である。図5の点線で囲んだ回路が本例の特徴部であり複数の抵抗とスイッチング素子から構成される。具体的には、第1抵抗としての電流検出抵抗114、第2抵抗としての抵抗203、第3抵抗としての抵抗204、スイッチング素子205から構成される回路である。本例においても実施例1と同様に、上記の図7の回路に比べて、軽負荷状態におけるトランスの唸り音を低減することができる。また、唸り音の低減に加えて、過負荷(過電流)の誤検出を防ぐことができる点も特徴である。また、本例のスイッチング電源の動作は実施例1の図1の動作と同様になる。

【0051】

本例の図5の回路では、軽負荷状態においてスイッチング素子205をオフしておけば、電流検出抵抗114によって検出される電圧がそのままIS端子404に入力されるため、FET107に流れる電流が低減する。これにより、コアの電磁力が弱くなるためトランス108唸り音が低減される。

【0052】

ここで、IS端子404に入力される電圧をVIS、電流検出抵抗114により検出された電圧をVo、電流検出抵抗114の抵抗値をRIS、FET107に流れるドレイン電流をIdとすると、IS端子404の電圧VISは以下に示す式で表される。

VIS=Vo=RIS×Id ・・・(式10)

【0053】

過負荷状態においては、スイッチング素子205をオンしておくことで、電流検出抵抗114によって検出された電圧を、スイッチング素子205による電圧降下分を差し引いた電圧に対して抵抗202と203によって分圧された電圧がIS端子404に入力される。これによりIS端子404の電圧の上昇の傾きが緩やかになり、図7の回路と同じタイミングで必要な負荷(上記の図7の場合と同じ負荷)過負荷を検出することが可能となる。また、電圧VISの上昇の傾きは抵抗202と203の抵抗値の比によって決まる。スイッチング素子205による電圧降下分を考慮して、抵抗202と203の分圧比を調整すれば、上記の図7と同様の過負荷の検出が可能になる。

【0054】

ここで、IS端子404の電圧をVIS、電流検出抵抗114により検出された電圧をVo、電流検出抵抗114の抵抗値をRIS、FET107に流れるドレイン電流をId、抵抗202と203の夫々の抵抗値をRa,Rb、抵抗202と203に流れる電流をiとすると、IS端子404の電圧VISは以下に示す(式)で表される。

RIS<<Ra,Rbに設定した場合、Id>>iより、

Vo≒Ra×Id・・・(式11)

VIS=Vo−Ra×i、VIS=Rb×iより、

VIS=(Rb×Vo)/(Ra+Rb)・・・(式12)

【0055】

ここで、本例の実施例1との違いについて説明する。本例では、スイッチング素子205のオン/オフによってIS端子に入力される電圧の上昇率を切り換える構成である。スイッチング素子205のオン/オフによるIS端子404の検出電圧の差を図6に示す。本例では、抵抗203の下流にスイッチング素子205を設け、スイッチング素子205のオン/オフを制御する制御部206(トランス108の2次側)を設けている。これにより、制御部206により、スイッチング素子205のオン/オフを制御することで、分圧用の抵抗202と203の有効/無効を設定することが可能となる。軽負荷状態で装置が動作していない状況においては、制御部206によりスイッチング素子205をオフすることで、トランス108の唸り音を低減するモードで動作させる。通常動作状態等、負荷を必要とする装置の動作中の状況においては、制御部206によりスイッチング素子205をオンすることで分圧抵抗202と203を有効にして、上記の図7と同様の負荷で過負荷が検出されることになる。なお、スイッチング素子205としては、例えば、リレースイッチやMOS−FETを適用可能である。また、制御部206としてはスイッチング電源の搭載された装置の制御部としてのCPU又はASIC等を適用可能である。

【0056】

ここで、IS端子404の電圧をVIS、電流検出抵抗114により検出された電圧をVo、電流検出抵抗114の抵抗値をRIS、FET107に流れるドレイン電流をId、抵抗202と203の夫々の抵抗値をRa,Rbとし、ダイオード204の順方向電圧Vfにおける、分圧抵抗202と203の夫々の抵抗値Ra,Rbを設定する方法を以下に説明する。

VIS=(Rb×Vo)/(Ra+Rb)・・・(式12)

Vo≒Ra×Id・・・(式13)

(式12)、(式13)より、

VIS=(Rb×Ra×Id)/(Ra+Rb)・・・(式13)

上記の(式13)に、過負荷検出のためのドレイン電流値IdとIS端子404が電源ICの発振動作を停止させるための電圧値VISを入力することで、必要な過負荷検出の抵抗202と203の夫々の抵抗値RaとRbを算出することができる。

【0057】

以上説明したように、本実施例のスイッチング電源によれば、軽負荷状態におけるトランスから発生する唸り音を低減することができる。さらに、過電圧(過電流)の誤検出を防ぐことができる。

【0058】

なお、上記実施例1、2とは別の手段として、電流検出抵抗114のラインにカレントトランス等を用いて構成される電流検知回路を設ける方法も考えられる。その場合は、カレントトランスによって検知して出力される電圧と基準電圧とをコンパレータを用いて比較することによってスイッチング素子205のオン/オフを行うことになる。このような構成にすれば、CPUからの制御によらず、自動的にスイッチング素子205のオン/オフを制御することができる。

【0059】

(スイッチング電源の適用例)

次に、上記の実施例1,2で説明したスイッチング電源を、例えば、レーザビームプリンタ、複写機、ファクシミリ等の画像形成装置における低電圧電源に適用することができる。以下にその適用例を説明する。スイッチング電源は、画像形成装置における用紙を搬送する搬送ローラの駆動部であるモータや、その他、アクチュエータ類、コントローラへの電力供給のための電源として適用可能である。

【0060】

図18(a)に画像形成装置の一例であるレーザビームプリンタの概略構成を示す。レーザビームプリンタ200は、画像形成部210として潜像が形成される像担持体としての感光ドラム211、感光ドラムに形成された潜像をトナーで現像する現像部212を備えている。そして感光ドラム211に現像されたトナー像をカセット216から供給された記録媒体としてのシート(不図示)に転写して、シートに転写したトナー像を定着器214で定着してトレイ215に排出する。

【0061】

また、図18(b)画像形成装置の駆動部としてのモータやコントローラへの電源からの電力供給ラインを示す。上記のスイッチング電源は、このような画像形成動作を制御するCPU218有するコントローラへ217の電力供給、また、画像形成のための駆動部としてのモータ219及びモータ220に電力を供給する低圧電源として適用できる。供給する電力として、これらのモータには、例えば、24Vを供給する。例えばモータ219はシートを搬送する搬送ローラを駆動するモータ、モータ220は定着器214を駆動するモータである。また、コントローラ217には、例えば、スイッチング電源から5Vを供給する。

【0062】

レーザビームプリンタのような画像形成装置は、記録材に画像を形成している動作状態と、画像形成を実行しておらず、消費電力を低減するためにモータ等への電力の供給をオフする非動作状態(待機状態、省電力状態ともいう)とに切り換えることができる。例えば、画像形成装置が非動作状態に切り換えられた場合において、上記で説明したスイッチング電源装置を適用すれば、非動作状態における装置の消費電力をより低減することができる。また、過負荷(過電流)の誤検出を防止できる。なお、上記実施例1,2で説明したスイッチング電源は、ここで示した画像形成装置に限らず他の電子機器の低電圧電源としても適用可能である。

【符号の説明】

【0063】

101 インレット

104 整流ダイオードブリッジ

107 スイッチング素子(MOS−FET)

108 トランス

109 電源IC

114 抵抗(電流検出用)

202、203 抵抗(分圧用の抵抗)

204 ダイオード

【技術分野】

【0001】

本発明は、直流電圧を出力するスイッチング電源に関する。

【背景技術】

【0002】

従来のフライバック方式のスイッチング電源において、トランスの1次側の電圧をスイッチングするスイッチング素子(例えば、FET等の素子)のスイッチング動作は、次のように制御される。例えば、トランスの2次側の電圧と、FETを流れる電流に対応する電圧と、FETのドレイン・ソース間の電圧とに基づいて、FETの動作(オン/オフ)が制御される。この動作の制御は、スイッチング動作制御用(専用)ICを使用して、2次側の電圧が第1の基準電圧を越え、且つ、FETのドレイン・ソース間の電圧が第2の基準電圧以下の条件で、FETをオンする。一方、FETを流れる電流に対応する電圧よりも2次側の電圧が低くなる条件で、FETをOFFする。このようなスイッチング電源において、軽負荷状態においてFETのオンする期間を短くすることで、軽負荷時の消費電力を低減させる工夫がなされている(特許文献1参照)。

【0003】

昨今、軽負荷状態における消費電力の低減は、スイッチング電源を搭載した機器の課題の1つとなっている。例えば、スイッチング電源を搭載した機器が、軽負荷状態(動作待機状態ともいう)であった場合の消費電力をより低減させれば、従来の機器に比べて消費電力をより低減した機器を提供することができる。特に、動作待機状態や非動作状態においては、機器の消費電力はスイッチング電源等の電力供給源が装置内で最も電力を消費している状態である場合が多い。従って、スイッチング電源の軽負荷状態における消費電力をより低減させる必要性が高まってきている。

【0004】

ここで、スイッチング電源の軽負荷状態における消費電力の低減を妨げる要因として、スイッチング素子であるFETのスイッチング損失が挙げられる。そこで、FETがオンしている間に流す電流量を増加させて、単位時間当たりのスイッチング回数を減らしてFETのスイッチング損失を低減させる方法が考えられる。

【先行技術文献】

【特許文献】

【0005】

【特許文献1】特開2000−148265号公報

【発明の概要】

【発明が解決しようとする課題】

【0006】

しかしながら、スイッチング素子がオンする期間に流す電流量を増やし、スイッチング回数を減らすとトランスから唸り音が発生するという課題が生じる。スイッチング回数を減らすことにより、スイッチング素子がONする期間に流す電流量が増えると、トランスの唸り音が大きくなる。つまり、軽負荷状態におけるスイッチング損失を低減しようとすると、トランスの唸り音が発生して、ユーザにとってはこの唸り音が耳障りな音として聞こえてしまう。なお、軽負荷状態では機器が非動作状態であることが多いため、ユーザに唸り音が聞こえやすい状態である。

【0007】

本発明は、上記課題に鑑みてなされたものであり、スイッチング電源の軽負荷状態におけるトランスの唸り音を低減することを目的とする。

【課題を解決するための手段】

【0008】

上記目的を達成するための本発明のスイッチング電源は、商用交流電源からの交流電圧を整流及び平滑した直流電圧をスイッチングして得られた電圧を変圧して出力するトランスを有し、前記トランスが出力した電圧を整流及び平滑した電圧を出力するスイッチング電源において、前記トランスの1次側に入力される電圧をスイッチングするスイッチング手段と、前記スイッチング手段のスイッチング動作を制御する制御手段と、を備え、前記トランスの1次側に流れる電流を電圧に変換して検出して前記制御手段に供給する検出手段と、前記検出手段は、前記スイッチング手段の動作状態に応じて、前記制御手段に供給する電圧を制御する。

【発明の効果】

【0009】

以上説明したように、本発明によれば、スイッチング電源において、軽負荷状態における、トランスから発生する唸り音を低減することができる。

【図面の簡単な説明】

【0010】

【図1】実施例1のスイッチング電源の回路図

【図2】実施例1における軽負荷状態の動作波形

【図3】実施例1における通常負荷状態の動作波形及びIS端子に入力される電圧波形

【図4】実施例1における過負荷状態のIS端子に入力される電圧波形

【図5】実施例2のスイッチング電源の回路図

【図6】実施例2におけるIS端子に入力される電圧波形電圧波形

【図7】本発明のスイッチング電源の前提回路図及び電源ICの内部ブロック概要図

【図8】図7のスイッチング電源の動作波形

【図9】省電力化に対応したスイッチング電源の回路図

【図10】図7と図9の夫々の回路の間欠発振時の動作波形

【図11】過負荷検出時の負荷の差を説明する図

【図12】スイッチング損失を説明する図

【図13】トランス構成図

【図14】トランスを上からみた透視図

【図15】トランスの変形を示す図

【図16】トランスの固有振動している状態を示す図

【図17】電磁力によるコアの変形図

【図18】スイッチング電源の適用例を示す図

【発明を実施するための形態】

【0011】

次に、上述した課題を解決するための本発明の具体的な構成について、以下に実施例に基づき説明する。なお、以下に示す実施例は一例であって、この発明の技術的範囲をそれらのみに限定する趣旨のものではない。

【0012】

まず、本発明の前提となるスイッチング電源の軽負荷状態において、トランスの唸り音の発生のメカニズムについて以下に説明する。

【0013】

図13にトランス108の構造図を示す。また、図14はトランスを上面より透視した図である。図13及び図14において、301、302はフェライトコアであり、中央磁脚部にはギャップ(間隔)を設けている。303はコイルボビン、304は一次巻線、305は二次巻線、306は層間紙、307はテープである。トランス108を組み立てる場合、まずコイルボビン303に巻線と層間紙を巻いていく。次に、端子処理を行った後、コア301と302をボビンに通し、コア301と302を固定するために、その外周部にテープ307を巻く。次に、ワニスに含浸させる。一般的に、ワニスとしては不飽和ポリエステル樹脂、変性ポリエステル樹脂、アルキド樹脂等が用いられる。このようなワニスを入れた槽(に規定時間、端子を上にして浸す(ディップ)。その後はワニスを固化するため、数時間、高温度に保つ。このようにワニス含浸処理を行うことでコア301と302同士、コア(301及び302)とコイルボビン303、巻線304と305及び層間紙306にワニスが染み込み、固化して一体となる。

【0014】

しかし、ワニス含浸処理を施したトランス108には、ワニスの含侵具合にバラつきがある。例えば、中央磁脚までワニスが到達して対向する互いの中央磁脚同士が接着されている状態であればトランスの唸り音は小さくなる。逆に、中央磁脚までワニスが到達していない状態であると唸り音が大きくなる。また、外側磁脚同士がきちんと接着されていないと図15のように外側磁脚同士の擦れが発生して大きな唸り音が発生する。これは、トランス108を励磁して磁束が発生して電磁力が発生しているためである。この電磁力は中央磁脚に最も大きく働き、対向する互いの中央磁脚を吸いつける方向即ち図17(a)で示す矢印方向に発生する。電磁力を受けてトランス108は図17(a)のように変形する。スイッチ素子のターンオフにより磁束が減少すると、コアの弾性により復元力が働きトランス108は図18(b)のように変形する。トランスがこのように変形して動くことにより、外側磁脚同士は互いに振動し、擦れによる唸り音が発生する。図16のように、対向する外側磁脚同士をきちんと接着すれば唸り音は軽減されるが、接着されている場合でも接着された外側磁脚が1本の弾性体として振動するため、外側磁脚の固有振動による振動音が残る。つまり、外側磁脚同士を接着した場合でも唸り音を十分に減衰させることは難しい。

【0015】

また、昨今の機器は非動作時において、一層、省電力化が望まれており、スイッチング電源においても非動作時のような軽負荷状態でスイッチング回数を減らして消費電力を低減し、かつ、動作効率の向上を図ったものが増えている。この結果、上記のようなスイッチング電源のトランス108の駆動周波数が可聴周波数域となりトランスの唸り音が大きくなる可能性がある。また、スイッチング損失を低減するためスイッチング素子のオン期間に流す電流量を増やす傾向にあり、この場合、トランス108のコア301と302に働く電磁力が増大するため、図17に示すような振動による唸り音が大きくなる可能性がある。以上が、トランスからの唸り音発生のメカニズムである。

【0016】

次に、本発明の前提となるスイッチング電源の回路構成と動作について図7を用いて説明する。なお、ここで説明するスイッチング電源は一般にフライバック方式のスイッチング電源とも呼ばれる。

【0017】

図7(a)の回路図において、101は商用交流電源から電圧が入力されるインレット、102はヒューズ、103はコモンモードコイル、104は整流ダイオードブリッジ、105は1次平滑コンデンサ、106は電源IC(109)を起動させる起動抵抗である。また、107はトランス(108)の1次巻線Npに流れる電流を断続的に遮断するスイッチング素子である。本例ではMOS−FET(電界効果トランジスタ)を適用している(以下、FET107という)。108は1次巻線Np(1次側)と2次巻線Ns(2次側)を有するフライバックトランスであり、入力された直流電圧を変圧(変換)して出力する。109はFET107のオンオフ動作を制御する電源IC、110はスイッチングFETのゲートに流れる電流を制限するための抵抗、111はトランス108の補助巻線Nbに誘起された電圧を整流するためのダイオードである。112は抵抗、113はコンデンサであり、この抵抗112とコンデンサ113でフィルタ回路を構成している。114はトランス108に流れる電流を検出する電流検出回路の第1の抵抗である電流検出抵抗、115はシャントレギュレータ125の出力を電源IC109に伝達するフォトカプラ、116はトランス108の2次巻線Nsの電圧を整流するダイオード、117は平滑コンデンサである。そして、119はスイッチング電源に接続される負荷、120はフォトカプラに流す電流を制限する抵抗、121は抵抗、122はコンデンサであり、これらは位相保証回路である。また、123、124はレギュレーション抵抗、125はシャントレギュレータである。

【0018】

まず、スイッチング電源の通常動作(通常負荷状態)として、インレット101より入力された商用交流電源からの交流電圧は、整流ダイオードブリッジ104を介し、全波整流されて1次平滑コンデンサ105に直流電圧としてチャージされる。更に、この直流電圧は、起動抵抗106を介して電源IC109を起動させる。電源IC109が起動し、FET107が導通状態(オン状態)になると1次巻線Npに1次平滑コンデンサ105の直流電圧が印加され、補助巻線Nbに1次巻線Npと同極側を正とする電圧が誘起される。このとき2次巻線Nsにも電圧が誘起されるが、ダイオード116のアノード側を負とする電圧であるため2次側には電圧は伝達されない。従って1次巻線Npを流れる電流はトランス108の励磁電流だけで、トランス108には励磁電流の2乗に比例したエネルギーが蓄積される。この励磁電流は時間に比例して増大する。また、補助巻線Nbに誘起された電圧はダイオード111、抵抗112を介して、コンデンサ113を充電し電源IC109に対する電源となる。

【0019】

次に、FET107が非導通状態(オフ状態)になると、トランス108の各巻線には起動時と逆極性の電圧が誘起され、2次巻線Nsにはダイオード116のアノード側を正とする電圧が誘起される。そして、トランス108に蓄積されたエネルギーが、ダイオード116と平滑コンデンサ117で整流及び平滑され、直流電圧出力118となり負荷119に供給される。また、このようにトランス108が動作すると、トランスの補助巻線Nbにより生成された電圧が電源IC109の電源として供給されるようになる。これにより電源IC109は動作を継続することが可能となり、引き続きFETI07をスイッチング動作(オンオフ)させて、トランス108から継続的に安定した電圧を出力することが可能となる。

【0020】

また、直流電圧出力118の電圧値の制御は次のように行なわれる。まず、直流電圧出力118をレギュレーション抵抗123と124とで分圧した電圧がシャントレギュレータ125に入力される。そして、この入力される電圧に応じたフィードバック信号が生成されて、フォトカプラ115を介して電源IC109へ伝達(フィードバック)される。そして、このフィードバック信号に基づき電源IC109がFET107のオンオフ動作を制御することにより、安定した直流電圧を出力すること可能となる。なお、図7(a)の電源IC109には、夫々の端子に対してT1乃至T7の番号を付し、以下に説明する電源IC109の詳細な回路図の各端子との対応関係を示している。

【0021】

次に、上記で説明したスイッチング電源のスイッチング素子であるFET107と、このオンオフ動作を制御する電源IC109の詳細な動作を説明する。なお、ここでは、電源ICとして周波数非固定、デュティー非固定、電流制御モードの動作について説明する。この動作モードは一般的な電源ICの動作モードである。

【0022】

図7(b)に電源IC109の内部ブロックの概要図を示す。図7(b)において、400aは、電源IC109の起動回路、401は電源ICへ給電される電源電圧が入力されるVCC端子、402はBOTOM端子、403はFB端子、404はIS端子、405は電源ICのGND端子、406はOUT端子、407、409、412はコンパレータ、408と410は基準電圧、411はAND回路、413はRSフリップフロップ論理回路である。

【0023】

以下に、図7(b)の電源IC109のブロック図に示した主要部分の機能を説明する。

・VH端子400(T1)及び起動回路400a

起動抵抗106に接続されて起動時の電圧の入力部、及び電源ICを起動する回路。

・VCC端子401(T2)

補助巻線Nbで発生した電圧が入力される電源ICの電源となる電圧の入力部。

・BOTOM端子402(T3)

FET107のドレイン・ソース間の電圧Vdsをモニターする端子。

・FB端子403(T4)

フィードバック端子、直流電圧出力118の変動をフォトカプラ115を介し入力する端子。

・IS端子404(T5)

FET107に流れるドレイン電流Idをモニターする端子。

・GND端子405(T6)

電源ICのGND端子。

・OUT端子406(T7)

FET107のゲート端子に接続される端子。

・コンパレータ407

BOTOM端子402の電圧が基準電圧408を下回ると、AND回路411へHIGH信号を出力する。

・コンパレータ409

FB端子403の電圧が基準電圧408を上回ると、AND回路411へHIGH信号を出力する。

・AND回路411

コンパレータ407とコンパレータ409の出力を入力する。

・コンパレータ412

FB端子403とIS端子404から入力された電圧を比較し、IS端子404の電圧が高い場合にRSフリップフロップ論理回路409へHIGH信号を出力する。さらに、IS端子404から入力された電圧が基準電圧414よりも高くなった場合には、電源IC109の発振動作を停止させる。

・RSフリップフロップ論理回路

周知のRSフリップフロップ論理回路(詳細説明は省略)。

【0024】

このような電源ICにより制御されるスイッチング電源の動作波形を図9に示す。図7乃至図9を用いて、スイッチング電源の電源IC109、FET107、トランス108、ダイオード116の動作を以下に説明する。

【0025】

<図8のタイミング1>

図8のタイミング1は、FET107が導通状態(オン状態)になったばかりの状態である。この時、FET107のドレイン電流Idは直線的に増加する。FET107のドレイン電流Idにより、トランス108にエネルギーが蓄積される。また、ダイオード116を逆バイアスする電位であるため、ダイオード116には電流Ifが流れない状態である。従って、直流電圧出力118は下降している。更に、FB端子403の電圧はフォトカプラ115を介して徐々に上昇する。また、IS端子404の電圧もスイッチングFET107のドレイン電流Idの増加と同様に直線的に増加する。

【0026】

<図8のタイミング2>

図8のタイミング2の状態へ移るタイミングとなるのは、FB端子403の電圧よりもIS端子404の電圧が高い電圧となったタイミングである。このタイミングでRSフリップフロップ論理回路409のR端子がHIGH状態(以下、HIという)となり、RSフリップフロップ論理回路409のQ端子、つまり、電源IC109のOUT端子406がLOWとなり、FET107が、非導通状態(オフ状態)になる。このため、FET107のドレイン電流Idは流れなくなる。また、ダイオード116は正バイアスされて導通状態となり、トランス108に蓄積されたエネルギーがダイオード116の電流Ifとして流れ始めることにより直流電圧出力118は上昇する。このため、FB端子403の電圧はフォトカプラ115を介して徐々に下降する。また、IS端子404の電圧もFET107のドレイン電流Idの停止と同様のタイミングで停止する。

【0027】

<図8のタイミング3>

図8のタイミング3の状態へ移るタイミングは、BOTOM端子402の電圧が基準電圧408以下となり、かつ、FB端子403の電圧が、基準電圧410よりも高くなったタイミングである。この時、AND回路411から、RSフリップフロップ論理回路409のS端子にHIGH信号が入力されて、RSフリップフロップ論理回路409のQ端子、つまり、電源IC109のOUT端子406がHIとなり、FET107が導通状態(オン状態)になる。このタイミング3=タイミング1であり、引き続き、上記のタイミング1から一連の動作が繰り返される。

【0028】

以上説明したように、スイッチング電源(電源IC:周波数非固定、デュティー非固定、電流制御モードで動作)の一連のスイッチング動作が行なわれる。

【0029】

次に、スイッチング回数を減らして、FET107のスイッチング動作による損失を低減した構成及び動作について図9及び図10を用いて説明する。図9における電源IC109の構成は図7(a)と同様であるため省略している。図9の回路の軽負荷状態における動作を図10(b)に示し、比較例として図10(a)に図7(a)の回路の動作を示す。また、図9の回路において、図7(a)の回路と異なるのは、IS端子(T5)への入力ラインにダイオード201が接続されている点である。その他の構成は図7(a)と同様である。図9に示す回路では、このダイオード201により、IS端子に電圧が入力されるタイミングを制御することにより、以下に説明する図12(b)で示す動作を実現している。

【0030】

<図10(b)の期間A>

軽負荷状態において、電流検出抵抗114に発生する電圧がダイオード201の閾値電圧Vfを越えたポイントB0の時点から、IS端子404の電圧は一定の傾きで上昇を開始する。IS端子404の電圧が上昇してFB端子403の電圧と同じ電圧になったタイミングで、FET107は非導通状態(オフ状態)となる。このように、電流検出抵抗114に発生する電圧がダイオード201のVf分だけ低下することを利用して、FET107が導通状態から非導通状態(オンからオフ)となる時間を、図7(a)の動作である図10(a)で示すタイミングより長くしている。なお、図10(a)に比べて非導通状態(オフ状態)となる時間の比率は、ダイオード201の閾値電圧Vfによって決定される。例えば、図9の構成においてFET107のスイッチング回数を図7(a)に対して1/6にする場合は、以下で示す(式1)、(式2)によりダイオード201の閾値Vfを導くことができる。

【0031】

・図7(a)の場合

P1=1/2×L×I1^2 ・・・(式1)

P1:トランス108に蓄えられるエネルギー

L:トランス108のL値

I1:スイッチングFET107のドレインIdのピーク値

・図9の場合

P2=1/2×L×I2^2 ・・・(式2)

P2:トランス108に蓄えられるエネルギー

L:トランス108のL値

I2:スイッチングFET107のドレイン電流Idのピーク値

ここで、スイッチング回数を1/6にするためには、6×P1=P2であることから、I2=√6×I1となる。つまり、スイッチングFET107の導通時間も図7(a)と比較して、図10の場合は√6倍となることから、IS端子404のピーク電圧をVISとすると、1+Vf/VIS=√6であるため、Vf=(√6−1)×VISとなる。

【0032】

なお、図7の場合と図10(b)の場合における過負荷検出のタイミングの違いを図11に示す。この図に示すように、ダイオード201を設けたため、過負荷検出のタイミングに差が生じることがわかる。この差が大きくなると過負荷状態を誤検出する可能性がでてくる。

【0033】

<図10(b)の期間B>

タイミングBは、FET107が非導通状態(オフ状態)となった後、トランス108に蓄積したエネルギーをフライバック電流として、トランス108の2次側に流し出す期間を示している。なお、フライバック電流を流しきった後も、FB端子403の電圧が基準電圧410を越えない限り、AND回路411からの出力をHIにすることができないため、フリップフロップ論理回路409のS端子をHIにすることができない。従って、FET107が導通することができない。このように、フライバック電流を流しきった後も、FET107は非導通状態(オフ状態)を続けるようにスイッチング動作を制御して、直流電圧出力118が安定するように制御している。

【0034】

<図10(b)の期間C>

再び、FET107が導通状態(オン状態)となる期間を示す。FET107が導通する(オンする)には、FB端子403の電圧が基準電圧410を越え、かつ、BOTOM端子402の電圧が基準電圧408以下となる必要があり、フライバック電流を流しきった後は直流電圧出力118が下降していくので、FB端子403の電圧が徐々に上昇し、基準電圧410を越えるためFET107が導通状態(オン状態)となる。

【0035】

上記のとおり、FET107を導通状態になるタイミングは、BOTOM端子402の電圧が基準電圧408以下となり、かつ、FB端子403の電圧が基準電圧410よりも高くなったタイミングである。通常負荷状態であれば、FB端子電圧は基準電圧410よりも十分に高いため、BOTOM端子402の電圧が基準電圧408以下になるタイミングでFET107を導通状態にする。これに対して、軽負荷状態ではFB端子の電圧が低く、トランス108に蓄積したエネルギーがフライバック電流としてトランスの2次側に流れ出ている間に、FB端子が基準電圧410よりも低くなる。このため、フライバック電流を流しきった後、FB端子が基準電圧410よりも高くなるまではスイッチングFET107を導通状態にすることができない。このように、軽負荷時には、図10(b)示すとおり間欠発振する動作となる。

【0036】

以上説明したように、図9の回路によってスイッチング回数を減らし、図7(a)で示す回路よりも軽負荷状態における省電力化が可能となる。

【0037】

なお、FET107のスイッチング損失について図12に概要図を示した。この図に示すようにスイッチング損失とは、FET107がスイッチング動作時(オンオフ動作時)に発生する損失のことである。スイッチング動作時のFET107のドレイン・ソース間の電圧Vdsと、ドレイン電流Idを掛け合わせた電力で示される。このスイッチング損失は、上記の図10(a)の場合よりも、図10(b)の場合の方が低減される。

【0038】

以下、上記したスイッチング電源の構成及び動作を前提として、本発明の特徴的な構成及び動作についていくつかの実施例を示して詳細に説明する。

【0039】

(実施例1)

実施例1のスイッチング電源の回路を図1に示す。図1の回路は、上記の図7と基本構成は同様である。図1において、図7との違いは、電流検出回路部として電流検出抵抗114に対して、第2及び第3の抵抗である抵抗203と抵抗204とダイオード204を直列に接続した回路を並列に接続し、抵抗203と抵抗204の接続点が電源ICのIS端子404に接続される点である。

【0040】

図1の点線で囲んだ回路が本例の特徴部であり複数の抵抗とダイオードから構成される。具体的には、第1抵抗としての電流検出抵抗114、第2抵抗としての抵抗203、第3抵抗としての抵抗204、ダイオード204から構成される回路である。なお、その他の構成は図7と同様であるため詳細な説明は省略する。

【0041】

本例の図1の構成は、上記の図7の回路に比べて、軽負荷状態におけるトランス108の唸り音を低減することができる。また、唸り音の低減に加え、過電流の誤検出を防ぐことができる点も特徴である。以下に本例の回路動作について、〔1〕軽負荷状態の回路動作、〔2〕通常負荷状態の回路動作、〔3〕過負荷状態の回路動作の夫々について詳細に説明する。

【0042】

〔1〕軽負荷状態の回路動作

図1に示す回路における軽負荷状態(間欠発振)の動作波形を図2(a)、電源IC109のIS端子404の電圧波形(1回のスイッチングにおける電圧波形)を図2(b)に示す。FET107が導通して(オンして)、IS端子404の電圧は一定の傾きで上昇を開始する。IS端子404の電圧が上昇し、FB端子403の電圧と同じ電圧になったタイミングで、FET107は非導通状態(オフ状態)となる。軽負荷状態では、ダイオード204の順方向電圧Vfを越えないので、電流検出抵抗114により検出された電圧が、そのままIS端子404に入力される。ここで、電流検出抵抗114は、トランス108の唸り音を低減させるため、上記の図7の回路よりも高い抵抗値に設定している。これにより、図2(b)で示すとおり、軽負荷状態では上記の図7よりもスイッチング周期が短くなる(スイッチング周波数が高くなる)。その結果、トランス108に1度に流れる電流値が低下する。つまり、軽負荷状態においてFET107のスイッチング1回におけるトランス108に流れる電流値を図7の回路に比べて低下させることで、トランス108のコアの電磁力が弱くなりトランス108唸り音が低減できる。なお、軽負荷状態におけるIS端子404に入力される電圧をVIS、電流検出抵抗114により検出された電圧をVo、電流検出抵抗114の抵抗値をRIS、FET107に流れるドレイン電流をIdとすると、IS端子404の電圧VISは以下に示す(式3)で表される。

VIS=Vo=RIS×Id ・・・(式3)

【0043】

〔2〕通常負荷状態の回路動作

通常負荷状態の動作波形を図3(a)、IS端子404の電圧波形(1回のスイッチングにおける電圧波形)を図3(b)に示す。通常負荷状態においては、IS端子404の電圧がダイオード204のVfを越えたタイミング(ポイントB1)で傾きが変化する。0VからポイントB1までの電圧(IS端子404の電圧)は、軽負荷状態と同じ傾きで上昇するが、ポイントB1を超えると、分圧抵抗202と203によって決められた分圧比の傾きで増加するようになる(上昇率を切り換えて、傾きが緩やかになる)。ここで、IS端子404の電圧をVIS、電流検出抵抗114により検出された電圧をVo、電流検出抵抗114の抵抗値をRIS、FET107に流れるドレイン電流をId、分圧抵抗202と203の夫々の抵抗値をRa,Rb、ダイオード204の順方向電圧をVf、分圧抵抗202と203とダイオード204の直列回路に流れる電流をiとすると、IS端子404の電圧VISは以下に示す(式4)、(式5)、(式6)で表される。以下の(式4)乃至(式6)によれば、IS端子404の電圧VISがダイオード204の順方向電圧Vfと等しくなったタイミングがポイントB1であることがわかる。

RIS<<Ra,Rbに設定した場合、Id>>iより、

Vo≒Ra×Id・・・(式4)

VIS=Vo−Ra×i、VIS=Vf+Rb×iより、

VIS=((Ra×Vf)+(Rb×Vo))/(Ra+Rb)・・・(式5)

この時のポイントB1の境界条件は、上記(式4)において、VIS=Voとして、

VIS=((Ra×Vf)+(Rb×Vo))/(Ra+Rb)

=((Ra×Vf)+(Rb×VIS))/(Ra+Rb)

(Ra+Rb)×VIS=(Ra×Vf)+(Rb*VIS)・・・(式6)

つまり、VIS=Vfとなり、S端子404の電圧VISがダイオード204の順方向電圧Vfと等しくなったタイミングがポイントB1となる境界条件であることがわかる。

【0044】

〔3〕過負荷状態の回路動作

過負荷状態におけるIS端子404の電圧波形(1回のスイッチングにおける電圧波形)を図4に示す。ここで過負荷状態とは、出力電流が過剰に流れてしまう負荷状態を意味する。スイッチンン具電源としては、過負荷状態を正しく検出して電源IC109の発振動作を停止させる必要がある。IS端子404のピーク電圧が、コンパレータ412の基準電圧414よりも高くなった場合に、電源IC109は発振動作を停止させる。過負荷の検出動作に対しても、電流検出抵抗114によって検出された電圧から、ダイオード204の順方向電圧Vf分を差し引いた電圧を抵抗202と203によって分圧した電圧がIS端子404に入力される。この時の動作波形が図4である。上記の図7の回路と比べて、最終的な過負荷検出の値は同じになる。図4のポイントB2は、このポイントB2でIS端子404のピーク電圧がダイオード201の順方向電圧Vfを越えたことを意味する。このポイントB2から、抵抗202と203の分圧比によって定められた傾きでIS端子404の電圧が上昇していく(上昇率を切り換えて、傾きが緩やかになる)。

【0045】

このように、過負荷状態では、ダイオード204がオンすることで、電流検出抵抗114によって検出された電圧から、ダイオード204の順方向電圧Vf分を差し引いた電圧に対して、抵抗202と203によって分圧された電圧がIS端子404に入力される。これによりIS端子に入力される電圧の傾きが緩やかになり、図7の回路と同じタイミングで必要な負荷(上記の図7の場合と同じ負荷)で正しく過負荷を検出することが可能となる。この電圧の傾きは抵抗202と203の分圧比によって決まるため、ダイオード204の順方向電圧Vfを考慮し、抵抗202と203の分圧比を調整することにより設定することができる。なお、ダイオード204を設けない場合は、点線で示すように過負荷を検出するタイミングが大幅に遅れてしまい、過負荷状態が継続されることによる誤動作(素子の破壊等による)が発生する可能性が高まる。

【0046】

このような過負荷検出の構成は、電源ICとして、通常動作状態でスイッチング素子を停止するための端子と、過負荷を検出するための端子が共通化されているICを用いる場合に特に有効となる。なぜなら、このような電源ICに図1の回路を適用すると、通常動作状態において過負荷を検出する場合の負荷が高くなってしまうため、上記の図7の構成よりも過電流(過負荷)を保護するタイミングが遅れてしまう可能性がある。これでは、スイッチング素子(MOS−FET)や各種素子の定格(耐圧)を上げることになり、素子の大型化やコストアップにつながる。本例の図1の構成であれば、素子の定格を上げずに対応することができる。

【0047】

ここで、IS端子404の電圧をVIS、電流検出抵抗114により検出された電圧をVo、電流検出抵抗114の抵抗値をRIS、FET107に流れるドレイン電流をId、抵抗202と抵抗203の夫々の抵抗値をRa,Rbとし、ダイオード204の順方向電圧Vfにおける、抵抗202と203の夫々の抵抗値RaとRbを設定する方法を以下に説明する。

VIS=((Ra×Vf)+(Rb×Vo))/(Ra+Rb)・・・(式7)

Vo≒Ra×Id・・・(式8)

式(7)、式(8)より、

VIS=((Ra×Vf)+(Rb×Ra×Id))/(Ra+Rb)・・・(式9)

【0048】

上記の(式9)に、過負荷検出のためのドレイン電流値Idと、ダイオード204の順方向電圧Vf、IS端子404が電源ICの発振動作を停止させる電圧VISを入力すれば、必要な過負荷検出のための分圧抵抗202,203の夫々の抵抗値Ra,Rbの算出することができる。

【0049】

以上説明したように、本実施例のスイッチング電源によれば、軽負荷状態におけるトランスから発生する唸り音を低減することができる。さらに、過負荷(過電流)の誤検出を防ぐことができる。

【0050】

(実施例2)

実施例2のスイッチング電源の回路図を図5に示す。図5に示す回路は、上記の図7で示した回路と基本構成は同じである。図5と図7との違いは、電流検出回路部として、電流検出抵抗114と並列に第2と第3の抵抗である抵抗203,抵抗204、スイッチング素子205を直列に接続した回路を接続し、抵抗203と抵抗204の接続点が電源IC109のIS端子404に接続される点である。図5の点線で囲んだ回路が本例の特徴部であり複数の抵抗とスイッチング素子から構成される。具体的には、第1抵抗としての電流検出抵抗114、第2抵抗としての抵抗203、第3抵抗としての抵抗204、スイッチング素子205から構成される回路である。本例においても実施例1と同様に、上記の図7の回路に比べて、軽負荷状態におけるトランスの唸り音を低減することができる。また、唸り音の低減に加えて、過負荷(過電流)の誤検出を防ぐことができる点も特徴である。また、本例のスイッチング電源の動作は実施例1の図1の動作と同様になる。

【0051】

本例の図5の回路では、軽負荷状態においてスイッチング素子205をオフしておけば、電流検出抵抗114によって検出される電圧がそのままIS端子404に入力されるため、FET107に流れる電流が低減する。これにより、コアの電磁力が弱くなるためトランス108唸り音が低減される。

【0052】

ここで、IS端子404に入力される電圧をVIS、電流検出抵抗114により検出された電圧をVo、電流検出抵抗114の抵抗値をRIS、FET107に流れるドレイン電流をIdとすると、IS端子404の電圧VISは以下に示す式で表される。

VIS=Vo=RIS×Id ・・・(式10)

【0053】

過負荷状態においては、スイッチング素子205をオンしておくことで、電流検出抵抗114によって検出された電圧を、スイッチング素子205による電圧降下分を差し引いた電圧に対して抵抗202と203によって分圧された電圧がIS端子404に入力される。これによりIS端子404の電圧の上昇の傾きが緩やかになり、図7の回路と同じタイミングで必要な負荷(上記の図7の場合と同じ負荷)過負荷を検出することが可能となる。また、電圧VISの上昇の傾きは抵抗202と203の抵抗値の比によって決まる。スイッチング素子205による電圧降下分を考慮して、抵抗202と203の分圧比を調整すれば、上記の図7と同様の過負荷の検出が可能になる。

【0054】

ここで、IS端子404の電圧をVIS、電流検出抵抗114により検出された電圧をVo、電流検出抵抗114の抵抗値をRIS、FET107に流れるドレイン電流をId、抵抗202と203の夫々の抵抗値をRa,Rb、抵抗202と203に流れる電流をiとすると、IS端子404の電圧VISは以下に示す(式)で表される。

RIS<<Ra,Rbに設定した場合、Id>>iより、

Vo≒Ra×Id・・・(式11)

VIS=Vo−Ra×i、VIS=Rb×iより、

VIS=(Rb×Vo)/(Ra+Rb)・・・(式12)

【0055】

ここで、本例の実施例1との違いについて説明する。本例では、スイッチング素子205のオン/オフによってIS端子に入力される電圧の上昇率を切り換える構成である。スイッチング素子205のオン/オフによるIS端子404の検出電圧の差を図6に示す。本例では、抵抗203の下流にスイッチング素子205を設け、スイッチング素子205のオン/オフを制御する制御部206(トランス108の2次側)を設けている。これにより、制御部206により、スイッチング素子205のオン/オフを制御することで、分圧用の抵抗202と203の有効/無効を設定することが可能となる。軽負荷状態で装置が動作していない状況においては、制御部206によりスイッチング素子205をオフすることで、トランス108の唸り音を低減するモードで動作させる。通常動作状態等、負荷を必要とする装置の動作中の状況においては、制御部206によりスイッチング素子205をオンすることで分圧抵抗202と203を有効にして、上記の図7と同様の負荷で過負荷が検出されることになる。なお、スイッチング素子205としては、例えば、リレースイッチやMOS−FETを適用可能である。また、制御部206としてはスイッチング電源の搭載された装置の制御部としてのCPU又はASIC等を適用可能である。

【0056】

ここで、IS端子404の電圧をVIS、電流検出抵抗114により検出された電圧をVo、電流検出抵抗114の抵抗値をRIS、FET107に流れるドレイン電流をId、抵抗202と203の夫々の抵抗値をRa,Rbとし、ダイオード204の順方向電圧Vfにおける、分圧抵抗202と203の夫々の抵抗値Ra,Rbを設定する方法を以下に説明する。

VIS=(Rb×Vo)/(Ra+Rb)・・・(式12)

Vo≒Ra×Id・・・(式13)

(式12)、(式13)より、

VIS=(Rb×Ra×Id)/(Ra+Rb)・・・(式13)

上記の(式13)に、過負荷検出のためのドレイン電流値IdとIS端子404が電源ICの発振動作を停止させるための電圧値VISを入力することで、必要な過負荷検出の抵抗202と203の夫々の抵抗値RaとRbを算出することができる。

【0057】

以上説明したように、本実施例のスイッチング電源によれば、軽負荷状態におけるトランスから発生する唸り音を低減することができる。さらに、過電圧(過電流)の誤検出を防ぐことができる。

【0058】

なお、上記実施例1、2とは別の手段として、電流検出抵抗114のラインにカレントトランス等を用いて構成される電流検知回路を設ける方法も考えられる。その場合は、カレントトランスによって検知して出力される電圧と基準電圧とをコンパレータを用いて比較することによってスイッチング素子205のオン/オフを行うことになる。このような構成にすれば、CPUからの制御によらず、自動的にスイッチング素子205のオン/オフを制御することができる。

【0059】

(スイッチング電源の適用例)

次に、上記の実施例1,2で説明したスイッチング電源を、例えば、レーザビームプリンタ、複写機、ファクシミリ等の画像形成装置における低電圧電源に適用することができる。以下にその適用例を説明する。スイッチング電源は、画像形成装置における用紙を搬送する搬送ローラの駆動部であるモータや、その他、アクチュエータ類、コントローラへの電力供給のための電源として適用可能である。

【0060】

図18(a)に画像形成装置の一例であるレーザビームプリンタの概略構成を示す。レーザビームプリンタ200は、画像形成部210として潜像が形成される像担持体としての感光ドラム211、感光ドラムに形成された潜像をトナーで現像する現像部212を備えている。そして感光ドラム211に現像されたトナー像をカセット216から供給された記録媒体としてのシート(不図示)に転写して、シートに転写したトナー像を定着器214で定着してトレイ215に排出する。

【0061】

また、図18(b)画像形成装置の駆動部としてのモータやコントローラへの電源からの電力供給ラインを示す。上記のスイッチング電源は、このような画像形成動作を制御するCPU218有するコントローラへ217の電力供給、また、画像形成のための駆動部としてのモータ219及びモータ220に電力を供給する低圧電源として適用できる。供給する電力として、これらのモータには、例えば、24Vを供給する。例えばモータ219はシートを搬送する搬送ローラを駆動するモータ、モータ220は定着器214を駆動するモータである。また、コントローラ217には、例えば、スイッチング電源から5Vを供給する。

【0062】

レーザビームプリンタのような画像形成装置は、記録材に画像を形成している動作状態と、画像形成を実行しておらず、消費電力を低減するためにモータ等への電力の供給をオフする非動作状態(待機状態、省電力状態ともいう)とに切り換えることができる。例えば、画像形成装置が非動作状態に切り換えられた場合において、上記で説明したスイッチング電源装置を適用すれば、非動作状態における装置の消費電力をより低減することができる。また、過負荷(過電流)の誤検出を防止できる。なお、上記実施例1,2で説明したスイッチング電源は、ここで示した画像形成装置に限らず他の電子機器の低電圧電源としても適用可能である。

【符号の説明】

【0063】

101 インレット

104 整流ダイオードブリッジ

107 スイッチング素子(MOS−FET)

108 トランス

109 電源IC

114 抵抗(電流検出用)

202、203 抵抗(分圧用の抵抗)

204 ダイオード

【特許請求の範囲】

【請求項1】

商用交流電源からの交流電圧を整流及び平滑した電圧をスイッチングして得られた電圧を変換して出力するトランスを有し、前記トランスが出力した電圧を整流及び平滑した電圧を出力するスイッチング電源において、

前記トランスの1次側に入力される電圧をスイッチングするスイッチング手段と、

前記スイッチング手段のスイッチング動作を制御する制御手段と、を備え、

前記トランスの1次側に流れる電流を電圧として検出して前記制御手段に供給する検出手段と、

前記検出手段は、前記スイッチング手段の動作状態に応じて、前記制御手段に供給する電圧を制御することを特徴とするスイッチング電源。

【請求項2】

前記スイッチング手段の動作状態として、前記トランスが出力する電圧が小さく前記スイッチング手段が動作する周波数が低い軽負荷状態と、前記軽負荷状態よりも前記トランスが出力する電圧が大きく前記スイッチング手段が動作する周波数が高い通常負荷状態とを有し、

前記検出手段は、前記通常負荷状態、において、前記制御手段に供給する電圧の上昇率を切り換えることを特徴とする請求項1に記載のスイッチング電源。

【請求項3】

前記スイッチング手段の動作状態として、前記トランスが出力する電圧が小さく前記スイッチング手段が動作する周波数が低い軽負荷状態と、前記軽負荷状態よりも前記トランスが出力する電圧が大きく前記スイッチング手段が動作する周波数が高い過負荷状態とを有し、

前記検出手段は、前記過負荷状態、において、前記制御手段に供給する電圧の上昇率を切り換え、

前記制御手段は、前記過負荷状態において供給された電圧が閾値を超えたら前記スイッチング手段を停止することを特徴とする請求項1に記載のスイッチング電源。

【請求項4】

前記検出手段は、前記スイッチング手段に接続される複数の抵抗とダイオードを含む検出回路であり、前記ダイオードの順方向電圧により、前記上昇率を切り換えることを特徴とする請求項2または3に記載のスイッチング電源。

【請求項5】

前記検出回路は、前記トランスの1次巻線に流れる電流を検出する第1抵抗と、前記第1抵抗に対して、第2抵抗と第3抵抗とダイオードを直列に接続した回路を並列に接続した回路であって、

第2抵抗と第3抵抗の間の値を前記制御手段に供給することを特徴とする請求項4に記載のスイッチング電源。

【請求項6】

前記検出手段は、前記スイッチング手段に接続される複数の抵抗とスイッチング素子を含む検出回路であり、前記スイッチング素子をオンオフすることにより、前記上昇率を切り換えることを特徴とする請求項2または3に記載のスイッチング電源。

【請求項7】

前記検出回路は、前記トランスの1次巻線に流れる電流を検出する第1抵抗と、前記第1抵抗に対して、第2抵抗と第3抵抗とスイッチ素子を直列に接続した回路を並列に接続した回路であって、

第2抵抗と第3抵抗の間の値を前記制御手段に供給することを特徴とする請求項4に記載のスイッチング電源。

【請求項8】

記録材に画像を形成するための画像形成手段と、

前記画像形成手段の動作を制御するコントローラと、

商用交流電源からの交流電圧を整流及び平滑した直流電圧をスイッチングして得られた電圧を変圧して出力するトランスを有し、前記トランスが出力した電圧を整流及び平滑した電圧を前記コントローラに出力するスイッチング電源と、を備え、

前記スイッチング電源は、前記トランスの1次側に入力される電圧をスイッチングするスイッチング手段と、前記スイッチング手段のスイッチング動作を制御する制御手段と、を備え、

前記トランスの1次側に流れる電流を電圧に変換して検出して前記制御手段に供給する検出手段と、

前記検出手段は、前記スイッチング手段の動作状態に応じて、前記制御手段に供給する電圧を制御することを特徴とする画像形成装置。

【請求項9】

前記スイッチング手段の動作状態として、前記トランスが出力する電圧が小さく前記スイッチング手段が動作する周波数が低い軽負荷状態と、前記軽負荷状態よりも前記トランスが出力する電圧が大きく前記スイッチング手段が動作する周波数が高い通常負荷状態とを有し、

前記検出手段は、前記通常負荷状態、において、前記制御手段に供給する電圧の上昇率を切り換えることを特徴とする請求項8に記載の画像形成装置。

【請求項10】

前記スイッチング手段の動作状態として、前記トランスが出力する電圧が小さく前記スイッチング手段が動作する周波数が低い軽負荷状態と、前記軽負荷状態よりも前記トランスが出力する電圧が大きく前記スイッチング手段が動作する周波数が高い過負荷状態とを有し、

前記検出手段は、前記過負荷状態、において、前記制御手段に供給する電圧の上昇率を切り換え、

前記制御手段は、前記過負荷状態において供給された電圧が閾値を超えたら前記スイッチング手段を停止することを特徴とする請求項8に記載の画像形成装置。

【請求項1】

商用交流電源からの交流電圧を整流及び平滑した電圧をスイッチングして得られた電圧を変換して出力するトランスを有し、前記トランスが出力した電圧を整流及び平滑した電圧を出力するスイッチング電源において、

前記トランスの1次側に入力される電圧をスイッチングするスイッチング手段と、

前記スイッチング手段のスイッチング動作を制御する制御手段と、を備え、

前記トランスの1次側に流れる電流を電圧として検出して前記制御手段に供給する検出手段と、

前記検出手段は、前記スイッチング手段の動作状態に応じて、前記制御手段に供給する電圧を制御することを特徴とするスイッチング電源。

【請求項2】

前記スイッチング手段の動作状態として、前記トランスが出力する電圧が小さく前記スイッチング手段が動作する周波数が低い軽負荷状態と、前記軽負荷状態よりも前記トランスが出力する電圧が大きく前記スイッチング手段が動作する周波数が高い通常負荷状態とを有し、

前記検出手段は、前記通常負荷状態、において、前記制御手段に供給する電圧の上昇率を切り換えることを特徴とする請求項1に記載のスイッチング電源。

【請求項3】

前記スイッチング手段の動作状態として、前記トランスが出力する電圧が小さく前記スイッチング手段が動作する周波数が低い軽負荷状態と、前記軽負荷状態よりも前記トランスが出力する電圧が大きく前記スイッチング手段が動作する周波数が高い過負荷状態とを有し、

前記検出手段は、前記過負荷状態、において、前記制御手段に供給する電圧の上昇率を切り換え、

前記制御手段は、前記過負荷状態において供給された電圧が閾値を超えたら前記スイッチング手段を停止することを特徴とする請求項1に記載のスイッチング電源。

【請求項4】

前記検出手段は、前記スイッチング手段に接続される複数の抵抗とダイオードを含む検出回路であり、前記ダイオードの順方向電圧により、前記上昇率を切り換えることを特徴とする請求項2または3に記載のスイッチング電源。

【請求項5】

前記検出回路は、前記トランスの1次巻線に流れる電流を検出する第1抵抗と、前記第1抵抗に対して、第2抵抗と第3抵抗とダイオードを直列に接続した回路を並列に接続した回路であって、

第2抵抗と第3抵抗の間の値を前記制御手段に供給することを特徴とする請求項4に記載のスイッチング電源。

【請求項6】

前記検出手段は、前記スイッチング手段に接続される複数の抵抗とスイッチング素子を含む検出回路であり、前記スイッチング素子をオンオフすることにより、前記上昇率を切り換えることを特徴とする請求項2または3に記載のスイッチング電源。

【請求項7】

前記検出回路は、前記トランスの1次巻線に流れる電流を検出する第1抵抗と、前記第1抵抗に対して、第2抵抗と第3抵抗とスイッチ素子を直列に接続した回路を並列に接続した回路であって、

第2抵抗と第3抵抗の間の値を前記制御手段に供給することを特徴とする請求項4に記載のスイッチング電源。

【請求項8】

記録材に画像を形成するための画像形成手段と、

前記画像形成手段の動作を制御するコントローラと、

商用交流電源からの交流電圧を整流及び平滑した直流電圧をスイッチングして得られた電圧を変圧して出力するトランスを有し、前記トランスが出力した電圧を整流及び平滑した電圧を前記コントローラに出力するスイッチング電源と、を備え、

前記スイッチング電源は、前記トランスの1次側に入力される電圧をスイッチングするスイッチング手段と、前記スイッチング手段のスイッチング動作を制御する制御手段と、を備え、

前記トランスの1次側に流れる電流を電圧に変換して検出して前記制御手段に供給する検出手段と、

前記検出手段は、前記スイッチング手段の動作状態に応じて、前記制御手段に供給する電圧を制御することを特徴とする画像形成装置。

【請求項9】

前記スイッチング手段の動作状態として、前記トランスが出力する電圧が小さく前記スイッチング手段が動作する周波数が低い軽負荷状態と、前記軽負荷状態よりも前記トランスが出力する電圧が大きく前記スイッチング手段が動作する周波数が高い通常負荷状態とを有し、

前記検出手段は、前記通常負荷状態、において、前記制御手段に供給する電圧の上昇率を切り換えることを特徴とする請求項8に記載の画像形成装置。

【請求項10】

前記スイッチング手段の動作状態として、前記トランスが出力する電圧が小さく前記スイッチング手段が動作する周波数が低い軽負荷状態と、前記軽負荷状態よりも前記トランスが出力する電圧が大きく前記スイッチング手段が動作する周波数が高い過負荷状態とを有し、

前記検出手段は、前記過負荷状態、において、前記制御手段に供給する電圧の上昇率を切り換え、

前記制御手段は、前記過負荷状態において供給された電圧が閾値を超えたら前記スイッチング手段を停止することを特徴とする請求項8に記載の画像形成装置。

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【図14】

【図15】

【図16】

【図17】

【図18】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【図14】

【図15】

【図16】

【図17】

【図18】

【公開番号】特開2012−244878(P2012−244878A)

【公開日】平成24年12月10日(2012.12.10)

【国際特許分類】

【出願番号】特願2011−115860(P2011−115860)

【出願日】平成23年5月24日(2011.5.24)

【出願人】(000001007)キヤノン株式会社 (59,756)

【Fターム(参考)】

【公開日】平成24年12月10日(2012.12.10)

【国際特許分類】

【出願日】平成23年5月24日(2011.5.24)

【出願人】(000001007)キヤノン株式会社 (59,756)

【Fターム(参考)】

[ Back to top ]