スイッチ素子の制御手段

【課題】スイッチ素子のスイッチングを高速化できるスイッチ素子の制御手段について、小型化および高効率化すること。

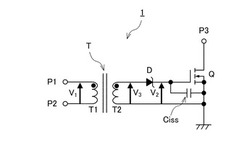

【解決手段】スイッチ素子Qを制御するスイッチ素子制御回路1は、トランスTおよびツェナーダイオードDを備える。ツェナーダイオードDのアノードには、トランスTの2次巻線T2の一端が接続され、ツェナーダイオードDのカソードには、スイッチ素子Qのゲートが接続される。スイッチ素子Qは、ゲート−ソース間に入力容量Cissを内蔵する。

【解決手段】スイッチ素子Qを制御するスイッチ素子制御回路1は、トランスTおよびツェナーダイオードDを備える。ツェナーダイオードDのアノードには、トランスTの2次巻線T2の一端が接続され、ツェナーダイオードDのカソードには、スイッチ素子Qのゲートが接続される。スイッチ素子Qは、ゲート−ソース間に入力容量Cissを内蔵する。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、スイッチ素子の制御手段に関する。

【背景技術】

【0002】

従来より、スイッチ素子に制御信号を供給して、スイッチ素子を制御するスイッチ素子制御回路がある(例えば、非特許文献1参照)。

【0003】

図3は、従来例に係るスイッチ素子制御回路100の回路図である。スイッチ素子制御回路100は、トランスTおよびツェナーダイオードDを備える。トランスTの1次巻線T1の一端には、端子P1が接続され、トランスTの1次巻線T1の他端には、端子P2が接続される。これら端子P1、P2には、電源(図示省略)が接続されており、電源からトランスTの1次巻線T1に電圧が印加されると、トランスTの1次巻線T1の一端から他端、または他端から一端に、電流が流れる。

【0004】

トランスTの2次巻線T2の一端には、NチャネルMOSFETで構成されるスイッチ素子Qのゲートと、ツェナーダイオードDのカソードと、が接続される。スイッチ素子Qのドレインには、端子P3が接続される。この端子P3には、例えば電圧源および負荷が接続される。トランスTの2次巻線T2の他端と、スイッチ素子Qのソースと、ツェナーダイオードDのアノードとは、接地される。

【0005】

以上のスイッチ素子制御回路100では、トランスTの1次巻線T1に印加される電圧に応じて、スイッチ素子Qがスイッチングする。

【0006】

図4は、スイッチ素子制御回路100のタイミングチャートである。V1は、端子P2を基準とした端子P1の電圧を示し、V2は、接地電位を基準としたスイッチ素子Qのゲートの電圧を示す。Iは、トランスTの2次巻線T2の一端からスイッチ素子Qのゲートに向かって流れる電流を示す。なお、図4におけるスイッチ素子制御回路100では、トランスTの2次巻線T2の巻数が所定数であり、トランスTの2次巻線T2のインダクタンスが所定値であるものとする。

【0007】

ここで、時刻t11の直前では、電圧V1、V2および電流Iは、「0」であるものとする。

【0008】

時刻t11において、電圧V1をVAにする。すると、トランスTの1次巻線T1の一端から他端に電流が流れ、この電流に応じた磁界がトランスTの1次巻線T1の周りに発生する。このため、トランスTの2次巻線T2には、電磁誘導により、トランスTの1次巻線T1の周りに発生した磁界に応じた起電力が生じる。その結果、電流IはIAとなり、電圧V2はVBとなる。その後、電圧V2は、時間が経過するに従って低下し、時刻t12では「0」となる。

【0009】

時刻t13において、電圧V1を「0」にする。すると、電流Iは、時間が経過するに従って減少し、時刻t15では「0」より少ない−IBとなる。その後、時間が経過するに従って増加し、時刻t16では「0」となる。

【0010】

時刻t14において、電圧V2は、「0」より低い−VCとなり、その後、時間が経過するに従って上昇し、時刻t15では「0」となる。

【先行技術文献】

【非特許文献】

【0011】

【非特許文献1】http://www.national.com/JPN/an/AN/AN−558.pdf

【発明の概要】

【発明が解決しようとする課題】

【0012】

ところで、図4におけるスイッチ素子制御回路100では、上述のように、トランスTの2次巻線T2の巻数が所定数であり、トランスTの2次巻線T2のインダクタンスが所定値である。そして、電圧V2は、上述のように、電圧V1をVAにした時刻t11においてVBとなった後、電圧V1がVAのままであるにもかかわらず時間が経過するに従って低下し、時刻t12では「0」となる。このため、スイッチ素子Qは、時刻t11においてオン状態になった後、時刻t12までの間にオフ状態になる。

【0013】

以上によれば、図4におけるスイッチ素子制御回路100では、スイッチ素子Qが継続的にオン状態である期間を長期化するのが困難な場合があった。

【0014】

ここで、同一のコアと、同一の線材と、を用いて構成した2つのコイルをコイルL1、L2とする。すると、コイルL1とコイルL2とのインダクタンス比は、コイルL1の巻数を2乗したものと、コイルL2の巻数を2乗したものと、の比に等しくなる。例えば、コイルL1の巻数を10とし、コイルL2の巻数を100とすると、コイルL1とコイルL2とのインダクタンス比は、1:100(=102:1002)となる。このため、コイルの巻数を増加させることで、コイルのインダクタンスを増加させることができる。

【0015】

そこで、図4におけるスイッチ素子制御回路100と比べて、トランスTの2次巻線T2の巻数を増加させ、トランスTの2次巻線T2のインダクタンスを増加させた場合について、図5を用いて検討する。なお、図4におけるスイッチ素子制御回路100と、図5におけるスイッチ素子制御回路100とでは、トランスTの1次巻線T1と2次巻線T2との巻数比は、同一とする。

【0016】

ここで、時刻t21の直前では、電圧V1、V2および電流Iは、「0」であるものとする。

【0017】

時刻t21において、電圧V1をVAにする。すると、上述の時刻t11と同様に、電流IはIAとなる。一方、電圧V2は、時刻t22から時間が経過するに従って上昇し、時刻t24においてVBとなる。

【0018】

時刻t23において、電圧V1を「0」にする。すると、電流Iは、時間が経過するに従って減少し、時刻t25では「0」となる。一方、電圧V2は、時刻t24から時間が経過するに従って低下し、時刻t26では「0」となる。

【0019】

図5におけるスイッチ素子制御回路100では、上述のように、図4におけるスイッチ素子制御回路100と比べて、トランスTの2次巻線T2の巻数が多く、トランスTの2次巻線T2のインダクタンスが大きい。そして、電圧V2は、上述のように、時刻t22から時間が経過するに従って上昇し、時刻t24においてVBとなった後、時間が経過するに従って低下し、時刻t26では「0」となる。このため、スイッチ素子Qは、時刻t22〜t24までの期間でオン状態になった後、時刻t24〜t26までの期間でオフ状態になる。

【0020】

以上によれば、図5におけるスイッチ素子制御回路100では、図4におけるスイッチ素子制御回路100と比べて、スイッチ素子Qが継続的にオン状態である期間が長くなる。このため、図5におけるスイッチ素子制御回路100では、図4におけるスイッチ素子制御回路100と比べて、スイッチ素子Qが継続的にオン状態である期間を長期化しつつ、トランスTの1次巻線T1に電圧を印加する期間を短縮できるので、高効率化できる。

【0021】

ところが、インダクタンスがLであるコイルL3について、このコイルL3の一端を基準としたコイルL3の他端の瞬時電圧をVLとし、コイルL3の他端から一端に流れる瞬時電流をiLとすると、瞬時電圧VLは、式(1)のように表すことができる。

【0022】

【数1】

【0023】

すなわち、瞬時電圧VLの立ち上がりは、瞬時電流iLの傾きに依存し、瞬時電流iLの傾きがゆるやかになるに従って、遅くなる。そして、瞬時電流iLの傾きは、インダクタンスLが高くなるに従って、ゆるやかになる。以上より、インダクタンスLが高くなるに従って、瞬時電圧VLの立ち上がりが遅くなる。

【0024】

このため、図5におけるスイッチ素子制御回路100では、図4におけるスイッチ素子制御回路100と比べて、トランスの2次巻線T2のインダクタンスが大きいので、電圧V1をVAにしてから電圧V2がVBになるまでの時間が長くなり、スイッチ素子Qの立ち上がり時間が遅い。したがって、図5におけるスイッチ素子制御回路100では、スイッチ素子Qのスイッチングの高速化が困難な場合があった。

【0025】

また、図5におけるスイッチ素子制御回路100では、図4におけるスイッチ素子制御回路100と比べて、トランスTの2次巻線T2の巻数が多いので、トランスTが大型化してスイッチ素子制御回路100の小型化が困難な場合があるとともに、トランスTの2次巻線T2における線間容量が増加し、損失が増加してしまう場合があった。

【0026】

上述の課題を鑑み、本発明は、スイッチ素子のスイッチングを高速化できるスイッチ素子の制御手段について、小型化および高効率化することを目的とする。

【課題を解決するための手段】

【0027】

本発明は、上述の課題を解決するために、以下の事項を提案している。

(1)本発明は、スイッチ素子を制御するスイッチ素子の制御手段であって、トランスと、前記トランスの2次巻線の一端と、前記スイッチ素子の制御端子と、の間に直列接続された定電圧手段と、を備え、前記スイッチ素子の制御端子と、前記スイッチ素子の出力端子と、の間には、容量が設けられることを特徴とするスイッチ素子の制御手段を提案している。

【0028】

この発明によれば、トランスと、トランスの2次巻線の一端とスイッチ素子の制御端子との間に直列接続された定電圧手段と、を設けた。また、スイッチ素子の制御端子とスイッチ素子の出力端子との間には、容量を設けた。

【0029】

このため、まず、第1の期間において、トランスの1次巻線に電圧を印加してトランスの2次巻線の他端から一端に電流を流すとともに、定電圧手段を駆動して、スイッチ素子をオン状態にするとともに、容量を充電する。次に、第2の期間において、定電圧手段を駆動して、スイッチ素子の制御端子から電荷が移動するのを防止する。これによれば、スイッチ素子の制御端子の電圧は、第1の期間で充電された容量により保持されるので、スイッチ素子は、オン状態で維持される。次に、第3の期間において、トランスの1次巻線に電圧を印加してトランスの2次巻線の一端から他端に電流を流すとともに、定電圧手段を駆動して、スイッチ素子の制御端子から電荷を移動させて、スイッチ素子をオフ状態にする。

【0030】

以上によれば、第2の期間では、トランスの1次巻線に電圧を印加することなく、スイッチ素子を継続的にオン状態にすることができる。このため、スイッチ素子を継続的にオン状態にするためにトランスの1次巻線に電圧を印加する時間を短縮できるので、高効率化できる。

【0031】

また、以上によれば、トランスの2次巻線のインダクタンスを増加させることなく、スイッチ素子を継続的にオン状態にするためにトランスの1次巻線に電圧を印加する時間を短縮できるので、トランスの2次巻線のインダクタンスの影響を抑え、トランスの2次巻線の電圧波形が鈍るのを抑制できる。これによれば、定電圧手段を介してトランスの2次巻線と接続されているスイッチ素子の制御端子においても、電圧波形が鈍るのを抑制できるため、スイッチ素子の制御端子の電圧の立ち上がり時間および立ち下がり時間を短縮でき、スイッチ素子のスイッチングを高速化できる。

【0032】

また、以上によれば、トランスの2次巻線の巻数を増加させることなく、スイッチ素子を継続的にオン状態にするためにトランスの1次巻線に電圧を印加する時間を短縮できるので、トランスを小型化して、スイッチ素子の制御手段を小型化できるとともに、トランスの2次巻線における線間容量の増加を防止して、さらに高効率化できる。

【0033】

(2)本発明は、(1)のスイッチ素子の制御手段について、前記定電圧手段は、ツェナーダイオードであり、前記トランスの2次巻線の一端には、前記ツェナーダイオードのアノードが接続され、前記スイッチ素子の制御端子には、前記ツェナーダイオードのカソードが接続されることを特徴とするスイッチ素子の制御手段を提案している。

【0034】

この発明によれば、定電圧手段としてツェナーダイオードを設け、トランスの2次巻線の一端には、ツェナーダイオードのアノードを接続し、スイッチ素子の制御端子には、ツェナーダイオードのカソードを接続した。

【0035】

このため、上述の第1の期間においては、トランスの1次巻線に電圧を印加してトランスの2次巻線の他端から一端に電流を流すことで、ツェナーダイオードのアノードの電圧を、ツェナーダイオードのカソードの電圧よりツェナーダイオードの順方向電圧以上高くして、ツェナーダイオードを導通させることができる。一方、上述の第2の期間においては、トランスの1次巻線に電圧を印加するのを停止してトランスの2次巻線に電流を流すのを停止することで、ツェナーダイオードを絶縁させることができる。また、上述の第3の期間においては、トランスの1次巻線に電圧を印加してトランスの2次巻線の一端から他端に電流を流すことで、ツェナーダイオードのアノード電圧を、ツェナーダイオードのカソードの電圧よりツェナーダイオードのツェナー電圧以上低くして、ツェナーダイオードを導通させることができる。

【0036】

(3)本発明は、(1)または(2)のスイッチ素子の制御手段について、前記容量は、前記スイッチ素子の内部に形成されることを特徴とするスイッチ素子の制御手段を提案している。

【0037】

この発明によれば、スイッチ素子の内部に容量を形成したので、上述した効果と同様の効果を奏することができる。

【発明の効果】

【0038】

本発明によれば、スイッチ素子のスイッチングを高速化できるスイッチ素子の制御手段について、高効率化できる。また、この制御手段が備えるトランスを小型化でき、制御手段を小型化できる。

【図面の簡単な説明】

【0039】

【図1】本発明の一実施形態に係るスイッチ素子制御回路の回路図である。

【図2】前記スイッチ素子制御回路のタイミングチャートである。

【図3】従来例に係るスイッチ素子制御回路の回路図である。

【図4】前記スイッチ素子制御回路のタイミングチャートである。

【図5】前記スイッチ素子制御回路のタイミングチャートである。

【発明を実施するための形態】

【0040】

以下、本発明の実施形態について図面を参照しながら説明する。なお、以下の実施形態における構成要素は適宜、既存の構成要素などとの置き換えが可能であり、また、他の既存の構成要素との組合せを含む様々なバリエーションが可能である。したがって、以下の実施形態の記載をもって、特許請求の範囲に記載された発明の内容を限定するものではない。

【0041】

図1は、本発明の一実施形態に係るスイッチ素子制御回路1の回路図である。スイッチ素子制御回路1は、図3に示した従来例に係るスイッチ素子制御回路100とは、ツェナーダイオードDの設けられる位置が異なる。また、スイッチ素子制御回路1が備えるトランスTの1次巻線T1の巻数と2次巻線T2の巻数とは、それぞれ、図4におけるスイッチ素子制御回路100が備えるトランスTの1次巻線T1の巻数と2次巻線T2の巻数に等しい。なお、スイッチ素子制御回路1において、スイッチ素子制御回路100と同一構成要件については、同一符号を付し、その説明を省略する。

【0042】

ツェナーダイオードDは、トランスTの2次巻線T2の一端と、スイッチ素子Qのゲートと、の間に直列接続される。具体的には、トランスTの2次巻線T2の一端には、ツェナーダイオードDのアノードが接続され、スイッチ素子Qのゲートには、ツェナーダイオードDのカソードが接続される。

【0043】

図2は、スイッチ素子制御回路1のタイミングチャートである。V1は、端子P2を基準とした端子P1の電圧を示し、V2は、接地電位を基準としたスイッチ素子Qのゲートの電圧を示し、V3は、接地電位を基準としたトランスTの2次巻線T2の一端の電圧を示す。

【0044】

ここで、時刻t1の直前では、電圧V1、V2、V3は、「0」であるものとする。

【0045】

時刻t1において、電圧V1をVPにする。すると、トランスTの1次巻線T1の一端から他端に電流が流れ、この電流に応じた磁界がトランスTの1次巻線T1の周りに発生する。このため、トランスTの2次巻線T2には、電磁誘導により、トランスTの1次巻線T1の周りに発生した磁界に応じた起電力が生じる。その結果、電圧V3はVRとなる。

【0046】

このため、時刻t1において、ツェナーダイオードDのアノードは、ツェナーダイオードDのカソードよりVRだけ電圧が高くなる。そして、VRは、ツェナーダイオードDの順方向電圧VFより大きい。すなわち、ツェナーダイオードDのアノードは、ツェナーダイオードDのカソードより電圧が高く、かつ、これらの電位差は、ツェナーダイオードDの順方向電圧VFより大きい。したがって、時刻t1では、ツェナーダイオードDに順電流が流れる。

【0047】

その結果、ツェナーダイオードDを介して、トランスTの2次巻線T2の一端からスイッチ素子Qのゲートに電荷が移動することとなる。これによれば、電圧V2はVTとなり、スイッチ素子Qはオン状態となるとともに、スイッチ素子Qのゲート−ソース間にある入力容量Cissが充電される。ここで、VTは、VRからツェナーダイオードDの順方向電圧VFを減算した値に等しく、かつ、ツェナーダイオードDのツェナー電圧VZより小さい。

【0048】

時刻t1〜t3までの期間において、時間が経過するに従って、電圧V1を低下させ、時刻t3において、電圧V1を「0」にする。すると、電圧V3は、時間が経過するに従って低下し、時刻t2ではVTとなり、時刻t4では「0」となる。

【0049】

このため、時刻t1〜t2までの期間では、電圧V2は、電圧V3が低下するに従って低下しようとするが、時刻t1において充電された入力容量CissによりVTで保持される。

【0050】

そして、時刻t2〜t5までの期間では、電圧V3はVTより低くなる。ここで、電圧V3が、電圧V2からツェナーダイオードDのツェナー電圧VZを減算した値以下になると、すなわちツェナーダイオードDのアノードが、ツェナーダイオードDのカソードより電圧が低く、かつ、これらの電位差がツェナーダイオードDのツェナー電圧VZ以上になると、ツェナーダイオードDに逆電流が流れる。ところが、時刻t2〜t5までの期間では、電圧V3は、電圧V2からツェナーダイオードDのツェナー電圧VZを減算した値以下にはならないので、ツェナーダイオードDに逆電流が流れない。

【0051】

このため、時刻t2〜t5までの期間では、電圧V2は、時刻t1において充電された入力容量CissによりVTで保持される。以上より、時刻t1〜t5までの期間では、電圧V2はVTとなり、スイッチ素子Qは継続してオン状態となる。

【0052】

時刻t5において、電圧V1を「0」より低い−VQにする。すると、トランスTの1次巻線T1の他端から一端に電流が流れ、この電流に応じた磁界がトランスTの1次巻線T1の周りに発生する。このため、トランスTの2次巻線T2には、電磁誘導により、トランスTの1次巻線T1の周りに発生した磁界に応じた起電力が生じる。その結果、電圧V3は、「0」より低い−VSとなる。

【0053】

このため、時刻t5において、ツェナーダイオードDのアノードは、ツェナーダイオードDのカソードより「VT+VS」だけ電圧が低くなる。そして、「VT+VS」は、ツェナーダイオードDのツェナー電圧VZより大きい。すなわち、ツェナーダイオードDのアノードは、ツェナーダイオードDのカソードより電圧が低く、かつ、これらの電位差がツェナーダイオードDのツェナー電圧VZより大きくなる。したがって、時刻t5では、ツェナーダイオードDに逆電流が流れる。

【0054】

その結果、ツェナーダイオードDを介して、スイッチ素子QのゲートからトランスTの2次巻線T2の一端に電荷が移動することとなり、電圧V2は「0」より低い−VUとなり、スイッチ素子Qはオフ状態となる。ここで、−VUは、−VSにツェナーダイオードDのツェナー電圧VZを加算した値に等しい。

【0055】

時刻t5〜t6までの期間において、時間が経過するに従って、電圧V1を上昇させ、時刻t6において、電圧V1を「0」にする。すると、電圧V3は、時間が経過するに従って上昇し、時刻t6では「0」となる。

【0056】

以上のスイッチ素子制御回路1によれば、以下の効果を奏することができる。

【0057】

まず、時刻t1において、電圧V1をVPにして、トランスTの1次巻線T1の一端から他端に電流を流す。これによれば、電圧V3がVRとなる。すると、ツェナーダイオードDのアノードは、ツェナーダイオードDのカソードより電圧が高くなり、これらの電位差は、ツェナーダイオードDの順方向電圧VFより大きくなるので、ツェナーダイオードDに順電流が流れる。このため、電圧V2は、ツェナーダイオードDの順方向電圧VFだけVRより低いVTとなり、スイッチ素子Qがオン状態になるとともに、入力容量Cissが充電される。

【0058】

次に、時刻t1〜t3までの期間において、時間が経過するに従って電圧V1を低下させ、時刻t3〜t5までの期間では、電圧V1を「0」にする。これによれば、電圧V3は、時刻t1〜t4までの期間において、時間が経過するに従って低下し、時刻t4〜t5までの期間では、「0」となる。すると、ツェナーダイオードDのアノードは、ツェナーダイオードDのカソードより電圧が低くなるが、これらの電位差は、ツェナーダイオードDのツェナー電圧VZより小さいので、ツェナーダイオードDに順電流および逆電流が流れない。このため、時刻t1〜t5までの期間において、電圧V2は、時刻t1において充電された入力容量CissによりVTで保持され、スイッチ素子Qが継続してオン状態となる。

【0059】

次に、時刻t5において、電圧V1を−VQにして、トランスTの1次巻線T1の他端から一端に電流を流す。これによれば、電圧V3が−VSとなる。すると、ツェナーダイオードDのアノードは、ツェナーダイオードDのカソードより電圧が低くなり、これらの電位差は、ツェナーダイオードDのツェナー電圧VZより大きくなるので、ツェナーダイオードDに逆電流が流れる。このため、電圧V2は、ツェナーダイオードDのツェナー電圧VZだけ−VSより高い−VUとなり、スイッチ素子Qがオフ状態になる。

【0060】

以上によれば、時刻t3〜t5までの期間では、トランスTの1次巻線に電圧を印加することなく、スイッチ素子Qを継続的にオン状態にすることができる。このため、スイッチ素子Qを継続的にオン状態にするためにトランスTの1次巻線T1に電圧を印加する時間を短縮できるので、高効率化できる。

【0061】

また、以上によれば、トランスTの2次巻線T2のインダクタンスを増加させることなく、スイッチ素子Qを継続的にオン状態にするためにトランスTの1次巻線T1に電圧を印加する時間を短縮できるので、トランスTの2次巻線T2のインダクタンスの影響を抑え、トランスTの2次巻線T2の電圧波形が鈍るのを抑制できる。これによれば、ツェナーダイオードDを介してトランスTの2次巻線T2と接続されているスイッチ素子Qのゲートにおいても、電圧波形が鈍るのを抑制できるため、スイッチ素子Qのゲートの電圧の立ち上がり時間および立ち下がり時間を短縮でき、スイッチ素子Qのスイッチングを高速化できる。

【0062】

また、以上によれば、トランスTの2次巻線T2の巻線を増加させることなく、スイッチ素子Qを継続的にオン状態にするためにトランスTの1次巻線T1に電圧を印加する時間を短縮できるので、トランスTを小型化して、スイッチ素子Qを小型化できるとともに、トランスTの2次巻線T2における線間容量の増加を防止して、さらに高効率化できる。

【0063】

本発明は、上述の実施形態に限定されるものではなく、この発明の要旨を逸脱しない範囲内で様々な変形や応用が可能である。

【0064】

例えば、上述の実施形態では、スイッチ素子Qを、NチャネルMOSFETで構成したが、これに限らず、例えばIGBT(Insulated Gate Bipolar Transistorの略)で構成してもよい。

【産業上の利用可能性】

【0065】

本発明は、スイッチ素子に制御信号を供給してスイッチ素子を制御する、制御回路や制御装置に適用できる。

【符号の説明】

【0066】

1、100;スイッチ素子制御回路

Ciss;入力容量

D;ツェナーダイオード

Q;スイッチ素子

T;トランス

【技術分野】

【0001】

本発明は、スイッチ素子の制御手段に関する。

【背景技術】

【0002】

従来より、スイッチ素子に制御信号を供給して、スイッチ素子を制御するスイッチ素子制御回路がある(例えば、非特許文献1参照)。

【0003】

図3は、従来例に係るスイッチ素子制御回路100の回路図である。スイッチ素子制御回路100は、トランスTおよびツェナーダイオードDを備える。トランスTの1次巻線T1の一端には、端子P1が接続され、トランスTの1次巻線T1の他端には、端子P2が接続される。これら端子P1、P2には、電源(図示省略)が接続されており、電源からトランスTの1次巻線T1に電圧が印加されると、トランスTの1次巻線T1の一端から他端、または他端から一端に、電流が流れる。

【0004】

トランスTの2次巻線T2の一端には、NチャネルMOSFETで構成されるスイッチ素子Qのゲートと、ツェナーダイオードDのカソードと、が接続される。スイッチ素子Qのドレインには、端子P3が接続される。この端子P3には、例えば電圧源および負荷が接続される。トランスTの2次巻線T2の他端と、スイッチ素子Qのソースと、ツェナーダイオードDのアノードとは、接地される。

【0005】

以上のスイッチ素子制御回路100では、トランスTの1次巻線T1に印加される電圧に応じて、スイッチ素子Qがスイッチングする。

【0006】

図4は、スイッチ素子制御回路100のタイミングチャートである。V1は、端子P2を基準とした端子P1の電圧を示し、V2は、接地電位を基準としたスイッチ素子Qのゲートの電圧を示す。Iは、トランスTの2次巻線T2の一端からスイッチ素子Qのゲートに向かって流れる電流を示す。なお、図4におけるスイッチ素子制御回路100では、トランスTの2次巻線T2の巻数が所定数であり、トランスTの2次巻線T2のインダクタンスが所定値であるものとする。

【0007】

ここで、時刻t11の直前では、電圧V1、V2および電流Iは、「0」であるものとする。

【0008】

時刻t11において、電圧V1をVAにする。すると、トランスTの1次巻線T1の一端から他端に電流が流れ、この電流に応じた磁界がトランスTの1次巻線T1の周りに発生する。このため、トランスTの2次巻線T2には、電磁誘導により、トランスTの1次巻線T1の周りに発生した磁界に応じた起電力が生じる。その結果、電流IはIAとなり、電圧V2はVBとなる。その後、電圧V2は、時間が経過するに従って低下し、時刻t12では「0」となる。

【0009】

時刻t13において、電圧V1を「0」にする。すると、電流Iは、時間が経過するに従って減少し、時刻t15では「0」より少ない−IBとなる。その後、時間が経過するに従って増加し、時刻t16では「0」となる。

【0010】

時刻t14において、電圧V2は、「0」より低い−VCとなり、その後、時間が経過するに従って上昇し、時刻t15では「0」となる。

【先行技術文献】

【非特許文献】

【0011】

【非特許文献1】http://www.national.com/JPN/an/AN/AN−558.pdf

【発明の概要】

【発明が解決しようとする課題】

【0012】

ところで、図4におけるスイッチ素子制御回路100では、上述のように、トランスTの2次巻線T2の巻数が所定数であり、トランスTの2次巻線T2のインダクタンスが所定値である。そして、電圧V2は、上述のように、電圧V1をVAにした時刻t11においてVBとなった後、電圧V1がVAのままであるにもかかわらず時間が経過するに従って低下し、時刻t12では「0」となる。このため、スイッチ素子Qは、時刻t11においてオン状態になった後、時刻t12までの間にオフ状態になる。

【0013】

以上によれば、図4におけるスイッチ素子制御回路100では、スイッチ素子Qが継続的にオン状態である期間を長期化するのが困難な場合があった。

【0014】

ここで、同一のコアと、同一の線材と、を用いて構成した2つのコイルをコイルL1、L2とする。すると、コイルL1とコイルL2とのインダクタンス比は、コイルL1の巻数を2乗したものと、コイルL2の巻数を2乗したものと、の比に等しくなる。例えば、コイルL1の巻数を10とし、コイルL2の巻数を100とすると、コイルL1とコイルL2とのインダクタンス比は、1:100(=102:1002)となる。このため、コイルの巻数を増加させることで、コイルのインダクタンスを増加させることができる。

【0015】

そこで、図4におけるスイッチ素子制御回路100と比べて、トランスTの2次巻線T2の巻数を増加させ、トランスTの2次巻線T2のインダクタンスを増加させた場合について、図5を用いて検討する。なお、図4におけるスイッチ素子制御回路100と、図5におけるスイッチ素子制御回路100とでは、トランスTの1次巻線T1と2次巻線T2との巻数比は、同一とする。

【0016】

ここで、時刻t21の直前では、電圧V1、V2および電流Iは、「0」であるものとする。

【0017】

時刻t21において、電圧V1をVAにする。すると、上述の時刻t11と同様に、電流IはIAとなる。一方、電圧V2は、時刻t22から時間が経過するに従って上昇し、時刻t24においてVBとなる。

【0018】

時刻t23において、電圧V1を「0」にする。すると、電流Iは、時間が経過するに従って減少し、時刻t25では「0」となる。一方、電圧V2は、時刻t24から時間が経過するに従って低下し、時刻t26では「0」となる。

【0019】

図5におけるスイッチ素子制御回路100では、上述のように、図4におけるスイッチ素子制御回路100と比べて、トランスTの2次巻線T2の巻数が多く、トランスTの2次巻線T2のインダクタンスが大きい。そして、電圧V2は、上述のように、時刻t22から時間が経過するに従って上昇し、時刻t24においてVBとなった後、時間が経過するに従って低下し、時刻t26では「0」となる。このため、スイッチ素子Qは、時刻t22〜t24までの期間でオン状態になった後、時刻t24〜t26までの期間でオフ状態になる。

【0020】

以上によれば、図5におけるスイッチ素子制御回路100では、図4におけるスイッチ素子制御回路100と比べて、スイッチ素子Qが継続的にオン状態である期間が長くなる。このため、図5におけるスイッチ素子制御回路100では、図4におけるスイッチ素子制御回路100と比べて、スイッチ素子Qが継続的にオン状態である期間を長期化しつつ、トランスTの1次巻線T1に電圧を印加する期間を短縮できるので、高効率化できる。

【0021】

ところが、インダクタンスがLであるコイルL3について、このコイルL3の一端を基準としたコイルL3の他端の瞬時電圧をVLとし、コイルL3の他端から一端に流れる瞬時電流をiLとすると、瞬時電圧VLは、式(1)のように表すことができる。

【0022】

【数1】

【0023】

すなわち、瞬時電圧VLの立ち上がりは、瞬時電流iLの傾きに依存し、瞬時電流iLの傾きがゆるやかになるに従って、遅くなる。そして、瞬時電流iLの傾きは、インダクタンスLが高くなるに従って、ゆるやかになる。以上より、インダクタンスLが高くなるに従って、瞬時電圧VLの立ち上がりが遅くなる。

【0024】

このため、図5におけるスイッチ素子制御回路100では、図4におけるスイッチ素子制御回路100と比べて、トランスの2次巻線T2のインダクタンスが大きいので、電圧V1をVAにしてから電圧V2がVBになるまでの時間が長くなり、スイッチ素子Qの立ち上がり時間が遅い。したがって、図5におけるスイッチ素子制御回路100では、スイッチ素子Qのスイッチングの高速化が困難な場合があった。

【0025】

また、図5におけるスイッチ素子制御回路100では、図4におけるスイッチ素子制御回路100と比べて、トランスTの2次巻線T2の巻数が多いので、トランスTが大型化してスイッチ素子制御回路100の小型化が困難な場合があるとともに、トランスTの2次巻線T2における線間容量が増加し、損失が増加してしまう場合があった。

【0026】

上述の課題を鑑み、本発明は、スイッチ素子のスイッチングを高速化できるスイッチ素子の制御手段について、小型化および高効率化することを目的とする。

【課題を解決するための手段】

【0027】

本発明は、上述の課題を解決するために、以下の事項を提案している。

(1)本発明は、スイッチ素子を制御するスイッチ素子の制御手段であって、トランスと、前記トランスの2次巻線の一端と、前記スイッチ素子の制御端子と、の間に直列接続された定電圧手段と、を備え、前記スイッチ素子の制御端子と、前記スイッチ素子の出力端子と、の間には、容量が設けられることを特徴とするスイッチ素子の制御手段を提案している。

【0028】

この発明によれば、トランスと、トランスの2次巻線の一端とスイッチ素子の制御端子との間に直列接続された定電圧手段と、を設けた。また、スイッチ素子の制御端子とスイッチ素子の出力端子との間には、容量を設けた。

【0029】

このため、まず、第1の期間において、トランスの1次巻線に電圧を印加してトランスの2次巻線の他端から一端に電流を流すとともに、定電圧手段を駆動して、スイッチ素子をオン状態にするとともに、容量を充電する。次に、第2の期間において、定電圧手段を駆動して、スイッチ素子の制御端子から電荷が移動するのを防止する。これによれば、スイッチ素子の制御端子の電圧は、第1の期間で充電された容量により保持されるので、スイッチ素子は、オン状態で維持される。次に、第3の期間において、トランスの1次巻線に電圧を印加してトランスの2次巻線の一端から他端に電流を流すとともに、定電圧手段を駆動して、スイッチ素子の制御端子から電荷を移動させて、スイッチ素子をオフ状態にする。

【0030】

以上によれば、第2の期間では、トランスの1次巻線に電圧を印加することなく、スイッチ素子を継続的にオン状態にすることができる。このため、スイッチ素子を継続的にオン状態にするためにトランスの1次巻線に電圧を印加する時間を短縮できるので、高効率化できる。

【0031】

また、以上によれば、トランスの2次巻線のインダクタンスを増加させることなく、スイッチ素子を継続的にオン状態にするためにトランスの1次巻線に電圧を印加する時間を短縮できるので、トランスの2次巻線のインダクタンスの影響を抑え、トランスの2次巻線の電圧波形が鈍るのを抑制できる。これによれば、定電圧手段を介してトランスの2次巻線と接続されているスイッチ素子の制御端子においても、電圧波形が鈍るのを抑制できるため、スイッチ素子の制御端子の電圧の立ち上がり時間および立ち下がり時間を短縮でき、スイッチ素子のスイッチングを高速化できる。

【0032】

また、以上によれば、トランスの2次巻線の巻数を増加させることなく、スイッチ素子を継続的にオン状態にするためにトランスの1次巻線に電圧を印加する時間を短縮できるので、トランスを小型化して、スイッチ素子の制御手段を小型化できるとともに、トランスの2次巻線における線間容量の増加を防止して、さらに高効率化できる。

【0033】

(2)本発明は、(1)のスイッチ素子の制御手段について、前記定電圧手段は、ツェナーダイオードであり、前記トランスの2次巻線の一端には、前記ツェナーダイオードのアノードが接続され、前記スイッチ素子の制御端子には、前記ツェナーダイオードのカソードが接続されることを特徴とするスイッチ素子の制御手段を提案している。

【0034】

この発明によれば、定電圧手段としてツェナーダイオードを設け、トランスの2次巻線の一端には、ツェナーダイオードのアノードを接続し、スイッチ素子の制御端子には、ツェナーダイオードのカソードを接続した。

【0035】

このため、上述の第1の期間においては、トランスの1次巻線に電圧を印加してトランスの2次巻線の他端から一端に電流を流すことで、ツェナーダイオードのアノードの電圧を、ツェナーダイオードのカソードの電圧よりツェナーダイオードの順方向電圧以上高くして、ツェナーダイオードを導通させることができる。一方、上述の第2の期間においては、トランスの1次巻線に電圧を印加するのを停止してトランスの2次巻線に電流を流すのを停止することで、ツェナーダイオードを絶縁させることができる。また、上述の第3の期間においては、トランスの1次巻線に電圧を印加してトランスの2次巻線の一端から他端に電流を流すことで、ツェナーダイオードのアノード電圧を、ツェナーダイオードのカソードの電圧よりツェナーダイオードのツェナー電圧以上低くして、ツェナーダイオードを導通させることができる。

【0036】

(3)本発明は、(1)または(2)のスイッチ素子の制御手段について、前記容量は、前記スイッチ素子の内部に形成されることを特徴とするスイッチ素子の制御手段を提案している。

【0037】

この発明によれば、スイッチ素子の内部に容量を形成したので、上述した効果と同様の効果を奏することができる。

【発明の効果】

【0038】

本発明によれば、スイッチ素子のスイッチングを高速化できるスイッチ素子の制御手段について、高効率化できる。また、この制御手段が備えるトランスを小型化でき、制御手段を小型化できる。

【図面の簡単な説明】

【0039】

【図1】本発明の一実施形態に係るスイッチ素子制御回路の回路図である。

【図2】前記スイッチ素子制御回路のタイミングチャートである。

【図3】従来例に係るスイッチ素子制御回路の回路図である。

【図4】前記スイッチ素子制御回路のタイミングチャートである。

【図5】前記スイッチ素子制御回路のタイミングチャートである。

【発明を実施するための形態】

【0040】

以下、本発明の実施形態について図面を参照しながら説明する。なお、以下の実施形態における構成要素は適宜、既存の構成要素などとの置き換えが可能であり、また、他の既存の構成要素との組合せを含む様々なバリエーションが可能である。したがって、以下の実施形態の記載をもって、特許請求の範囲に記載された発明の内容を限定するものではない。

【0041】

図1は、本発明の一実施形態に係るスイッチ素子制御回路1の回路図である。スイッチ素子制御回路1は、図3に示した従来例に係るスイッチ素子制御回路100とは、ツェナーダイオードDの設けられる位置が異なる。また、スイッチ素子制御回路1が備えるトランスTの1次巻線T1の巻数と2次巻線T2の巻数とは、それぞれ、図4におけるスイッチ素子制御回路100が備えるトランスTの1次巻線T1の巻数と2次巻線T2の巻数に等しい。なお、スイッチ素子制御回路1において、スイッチ素子制御回路100と同一構成要件については、同一符号を付し、その説明を省略する。

【0042】

ツェナーダイオードDは、トランスTの2次巻線T2の一端と、スイッチ素子Qのゲートと、の間に直列接続される。具体的には、トランスTの2次巻線T2の一端には、ツェナーダイオードDのアノードが接続され、スイッチ素子Qのゲートには、ツェナーダイオードDのカソードが接続される。

【0043】

図2は、スイッチ素子制御回路1のタイミングチャートである。V1は、端子P2を基準とした端子P1の電圧を示し、V2は、接地電位を基準としたスイッチ素子Qのゲートの電圧を示し、V3は、接地電位を基準としたトランスTの2次巻線T2の一端の電圧を示す。

【0044】

ここで、時刻t1の直前では、電圧V1、V2、V3は、「0」であるものとする。

【0045】

時刻t1において、電圧V1をVPにする。すると、トランスTの1次巻線T1の一端から他端に電流が流れ、この電流に応じた磁界がトランスTの1次巻線T1の周りに発生する。このため、トランスTの2次巻線T2には、電磁誘導により、トランスTの1次巻線T1の周りに発生した磁界に応じた起電力が生じる。その結果、電圧V3はVRとなる。

【0046】

このため、時刻t1において、ツェナーダイオードDのアノードは、ツェナーダイオードDのカソードよりVRだけ電圧が高くなる。そして、VRは、ツェナーダイオードDの順方向電圧VFより大きい。すなわち、ツェナーダイオードDのアノードは、ツェナーダイオードDのカソードより電圧が高く、かつ、これらの電位差は、ツェナーダイオードDの順方向電圧VFより大きい。したがって、時刻t1では、ツェナーダイオードDに順電流が流れる。

【0047】

その結果、ツェナーダイオードDを介して、トランスTの2次巻線T2の一端からスイッチ素子Qのゲートに電荷が移動することとなる。これによれば、電圧V2はVTとなり、スイッチ素子Qはオン状態となるとともに、スイッチ素子Qのゲート−ソース間にある入力容量Cissが充電される。ここで、VTは、VRからツェナーダイオードDの順方向電圧VFを減算した値に等しく、かつ、ツェナーダイオードDのツェナー電圧VZより小さい。

【0048】

時刻t1〜t3までの期間において、時間が経過するに従って、電圧V1を低下させ、時刻t3において、電圧V1を「0」にする。すると、電圧V3は、時間が経過するに従って低下し、時刻t2ではVTとなり、時刻t4では「0」となる。

【0049】

このため、時刻t1〜t2までの期間では、電圧V2は、電圧V3が低下するに従って低下しようとするが、時刻t1において充電された入力容量CissによりVTで保持される。

【0050】

そして、時刻t2〜t5までの期間では、電圧V3はVTより低くなる。ここで、電圧V3が、電圧V2からツェナーダイオードDのツェナー電圧VZを減算した値以下になると、すなわちツェナーダイオードDのアノードが、ツェナーダイオードDのカソードより電圧が低く、かつ、これらの電位差がツェナーダイオードDのツェナー電圧VZ以上になると、ツェナーダイオードDに逆電流が流れる。ところが、時刻t2〜t5までの期間では、電圧V3は、電圧V2からツェナーダイオードDのツェナー電圧VZを減算した値以下にはならないので、ツェナーダイオードDに逆電流が流れない。

【0051】

このため、時刻t2〜t5までの期間では、電圧V2は、時刻t1において充電された入力容量CissによりVTで保持される。以上より、時刻t1〜t5までの期間では、電圧V2はVTとなり、スイッチ素子Qは継続してオン状態となる。

【0052】

時刻t5において、電圧V1を「0」より低い−VQにする。すると、トランスTの1次巻線T1の他端から一端に電流が流れ、この電流に応じた磁界がトランスTの1次巻線T1の周りに発生する。このため、トランスTの2次巻線T2には、電磁誘導により、トランスTの1次巻線T1の周りに発生した磁界に応じた起電力が生じる。その結果、電圧V3は、「0」より低い−VSとなる。

【0053】

このため、時刻t5において、ツェナーダイオードDのアノードは、ツェナーダイオードDのカソードより「VT+VS」だけ電圧が低くなる。そして、「VT+VS」は、ツェナーダイオードDのツェナー電圧VZより大きい。すなわち、ツェナーダイオードDのアノードは、ツェナーダイオードDのカソードより電圧が低く、かつ、これらの電位差がツェナーダイオードDのツェナー電圧VZより大きくなる。したがって、時刻t5では、ツェナーダイオードDに逆電流が流れる。

【0054】

その結果、ツェナーダイオードDを介して、スイッチ素子QのゲートからトランスTの2次巻線T2の一端に電荷が移動することとなり、電圧V2は「0」より低い−VUとなり、スイッチ素子Qはオフ状態となる。ここで、−VUは、−VSにツェナーダイオードDのツェナー電圧VZを加算した値に等しい。

【0055】

時刻t5〜t6までの期間において、時間が経過するに従って、電圧V1を上昇させ、時刻t6において、電圧V1を「0」にする。すると、電圧V3は、時間が経過するに従って上昇し、時刻t6では「0」となる。

【0056】

以上のスイッチ素子制御回路1によれば、以下の効果を奏することができる。

【0057】

まず、時刻t1において、電圧V1をVPにして、トランスTの1次巻線T1の一端から他端に電流を流す。これによれば、電圧V3がVRとなる。すると、ツェナーダイオードDのアノードは、ツェナーダイオードDのカソードより電圧が高くなり、これらの電位差は、ツェナーダイオードDの順方向電圧VFより大きくなるので、ツェナーダイオードDに順電流が流れる。このため、電圧V2は、ツェナーダイオードDの順方向電圧VFだけVRより低いVTとなり、スイッチ素子Qがオン状態になるとともに、入力容量Cissが充電される。

【0058】

次に、時刻t1〜t3までの期間において、時間が経過するに従って電圧V1を低下させ、時刻t3〜t5までの期間では、電圧V1を「0」にする。これによれば、電圧V3は、時刻t1〜t4までの期間において、時間が経過するに従って低下し、時刻t4〜t5までの期間では、「0」となる。すると、ツェナーダイオードDのアノードは、ツェナーダイオードDのカソードより電圧が低くなるが、これらの電位差は、ツェナーダイオードDのツェナー電圧VZより小さいので、ツェナーダイオードDに順電流および逆電流が流れない。このため、時刻t1〜t5までの期間において、電圧V2は、時刻t1において充電された入力容量CissによりVTで保持され、スイッチ素子Qが継続してオン状態となる。

【0059】

次に、時刻t5において、電圧V1を−VQにして、トランスTの1次巻線T1の他端から一端に電流を流す。これによれば、電圧V3が−VSとなる。すると、ツェナーダイオードDのアノードは、ツェナーダイオードDのカソードより電圧が低くなり、これらの電位差は、ツェナーダイオードDのツェナー電圧VZより大きくなるので、ツェナーダイオードDに逆電流が流れる。このため、電圧V2は、ツェナーダイオードDのツェナー電圧VZだけ−VSより高い−VUとなり、スイッチ素子Qがオフ状態になる。

【0060】

以上によれば、時刻t3〜t5までの期間では、トランスTの1次巻線に電圧を印加することなく、スイッチ素子Qを継続的にオン状態にすることができる。このため、スイッチ素子Qを継続的にオン状態にするためにトランスTの1次巻線T1に電圧を印加する時間を短縮できるので、高効率化できる。

【0061】

また、以上によれば、トランスTの2次巻線T2のインダクタンスを増加させることなく、スイッチ素子Qを継続的にオン状態にするためにトランスTの1次巻線T1に電圧を印加する時間を短縮できるので、トランスTの2次巻線T2のインダクタンスの影響を抑え、トランスTの2次巻線T2の電圧波形が鈍るのを抑制できる。これによれば、ツェナーダイオードDを介してトランスTの2次巻線T2と接続されているスイッチ素子Qのゲートにおいても、電圧波形が鈍るのを抑制できるため、スイッチ素子Qのゲートの電圧の立ち上がり時間および立ち下がり時間を短縮でき、スイッチ素子Qのスイッチングを高速化できる。

【0062】

また、以上によれば、トランスTの2次巻線T2の巻線を増加させることなく、スイッチ素子Qを継続的にオン状態にするためにトランスTの1次巻線T1に電圧を印加する時間を短縮できるので、トランスTを小型化して、スイッチ素子Qを小型化できるとともに、トランスTの2次巻線T2における線間容量の増加を防止して、さらに高効率化できる。

【0063】

本発明は、上述の実施形態に限定されるものではなく、この発明の要旨を逸脱しない範囲内で様々な変形や応用が可能である。

【0064】

例えば、上述の実施形態では、スイッチ素子Qを、NチャネルMOSFETで構成したが、これに限らず、例えばIGBT(Insulated Gate Bipolar Transistorの略)で構成してもよい。

【産業上の利用可能性】

【0065】

本発明は、スイッチ素子に制御信号を供給してスイッチ素子を制御する、制御回路や制御装置に適用できる。

【符号の説明】

【0066】

1、100;スイッチ素子制御回路

Ciss;入力容量

D;ツェナーダイオード

Q;スイッチ素子

T;トランス

【特許請求の範囲】

【請求項1】

スイッチ素子を制御するスイッチ素子の制御手段であって、

トランスと、

前記トランスの2次巻線の一端と、前記スイッチ素子の制御端子と、の間に直列接続された定電圧手段と、を備え、

前記スイッチ素子の制御端子と、前記スイッチ素子の出力端子と、の間には、容量が設けられることを特徴とするスイッチ素子の制御手段。

【請求項2】

前記定電圧手段は、ツェナーダイオードであり、

前記トランスの2次巻線の一端には、前記ツェナーダイオードのアノードが接続され、前記スイッチ素子の制御端子には、前記ツェナーダイオードのカソードが接続されることを特徴とする請求項1に記載のスイッチ素子の制御手段。

【請求項3】

前記容量は、前記スイッチ素子の内部に形成されることを特徴とする請求項1または2に記載のスイッチ素子の制御手段。

【請求項1】

スイッチ素子を制御するスイッチ素子の制御手段であって、

トランスと、

前記トランスの2次巻線の一端と、前記スイッチ素子の制御端子と、の間に直列接続された定電圧手段と、を備え、

前記スイッチ素子の制御端子と、前記スイッチ素子の出力端子と、の間には、容量が設けられることを特徴とするスイッチ素子の制御手段。

【請求項2】

前記定電圧手段は、ツェナーダイオードであり、

前記トランスの2次巻線の一端には、前記ツェナーダイオードのアノードが接続され、前記スイッチ素子の制御端子には、前記ツェナーダイオードのカソードが接続されることを特徴とする請求項1に記載のスイッチ素子の制御手段。

【請求項3】

前記容量は、前記スイッチ素子の内部に形成されることを特徴とする請求項1または2に記載のスイッチ素子の制御手段。

【図1】

【図2】

【図3】

【図4】

【図5】

【図2】

【図3】

【図4】

【図5】

【公開番号】特開2010−279225(P2010−279225A)

【公開日】平成22年12月9日(2010.12.9)

【国際特許分類】

【出願番号】特願2009−132088(P2009−132088)

【出願日】平成21年6月1日(2009.6.1)

【出願人】(000002037)新電元工業株式会社 (776)

【Fターム(参考)】

【公開日】平成22年12月9日(2010.12.9)

【国際特許分類】

【出願日】平成21年6月1日(2009.6.1)

【出願人】(000002037)新電元工業株式会社 (776)

【Fターム(参考)】

[ Back to top ]