スイッチ

【課題】高周波信号の振幅に対する歪みを低減しつつ、スイッチングを実現することが可能なスイッチを提供する。

【解決手段】高周波信号が入力される入力端子と、高周波信号が出力される第1出力端子との間に接続され、入力される高周波信号を第1出力端子から選択的に出力させる第1スイッチング部と、入力端子と、入力された高周波信号が出力される第2出力端子との間に接続され、入力端子に入力される高周波信号を第2出力端子から選択的に出力させる第2スイッチング部とを備え、第1スイッチング部、第2スイッチング部それぞれは、信号線上に設けられるインピーダンス変成器と、エミッタが接地され、コレクタが信号線に接続され、制御電圧に応じた電流がベースに印加されるバイポーラトランジスタと、コレクタが接地され、エミッタが信号線に接続され、制御電圧に応じた電流がベースに印加されるバイポーラトランジスタとを備えるスイッチが提供される。

【解決手段】高周波信号が入力される入力端子と、高周波信号が出力される第1出力端子との間に接続され、入力される高周波信号を第1出力端子から選択的に出力させる第1スイッチング部と、入力端子と、入力された高周波信号が出力される第2出力端子との間に接続され、入力端子に入力される高周波信号を第2出力端子から選択的に出力させる第2スイッチング部とを備え、第1スイッチング部、第2スイッチング部それぞれは、信号線上に設けられるインピーダンス変成器と、エミッタが接地され、コレクタが信号線に接続され、制御電圧に応じた電流がベースに印加されるバイポーラトランジスタと、コレクタが接地され、エミッタが信号線に接続され、制御電圧に応じた電流がベースに印加されるバイポーラトランジスタとを備えるスイッチが提供される。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、スイッチに関する。

【背景技術】

【0002】

例えば無線通信に用いられる高周波信号の経路を切り替えるスイッチには、一般的に、GaAs系化合物半導体のHEMT(High Electron Mobility Transistor。高電子移動度トランジスタ)などが用いられている。ここで、化合物半導体は、ウェハー単価が高く、またウェハーの大口径化が進んでいないため、価格が高いという欠点がある。

【0003】

また、近年、スイッチの低価格化を実現するために、例えばCMOS(Complementary Metal Oxide Semiconductor)系のスイッチの開発もされている。ここで、通常のCMOS(Bulk CMOS)は、基板が低抵抗であるために漏洩電力が発生し、スイッチの特性が劣化する恐れがある。そのため、例えば、CMOS(Complementary Metal Oxide Semiconductor)系のスイッチを用いる場合には、例えば、SOS(Silicon on Sapphire)やSOI(Silicon on Insulator)などの特殊プロセスを導入することによって、スイッチの特性の改善を図っている。しかしながら、上記SOSやSOIなどの特殊プロセスを用いる場合には、結果的にコストの上昇を招いてしまう。

【0004】

このような中、高周波信号の経路を切り替えるスイッチに係る技術が開発されている。ヘテロ接合バイポーラトランジスタ(Heterojunction Bipolar Transistor。以下「HBT」と示す場合がある。)を用いたスイッチに係る技術としては、例えば、特許文献1に記載の技術が挙げられる。

【先行技術文献】

【特許文献】

【0005】

【特許文献1】特開2006−279316号公報

【発明の概要】

【発明が解決しようとする課題】

【0006】

例えばSiGeHBTとBulk CMOSの複合プロセスであるSiGeBiCMOSなどの一般的に用いられているプロセスが用いられた、HBTなどのバイポーラトランジスタを用いてスイッチを実現する場合には、HEMTなどのFETを用いてスイッチを実現する場合よりもスイッチのコストを低減することが可能である。ここで、FETは、対称構造(すなわち、ドレインとソースが固定されない構造)であるため、高周波信号の振幅に対して、順方向動作時と逆方向動作時とにおける特性は同一となる。一方、バイポーラトランジスタでは、順方向動作時と逆方向動作時とにおける特性が同一ではない。そのため、バイポーラトランジスタが用いられるスイッチでは、高周波信号の振幅に対する歪みが発生する可能性がある。

【0007】

例えば特許文献1に記載の技術では、HBTの特性自体を改良しているので、高周波信号の振幅に対する歪みを低減することができる可能性がある。しかしながら、例えば特許文献1に記載の技術を用いる場合には、特殊なプロセスを用いなければならないので、コストの低減は望むべくもない。

【0008】

本発明は、上記問題に鑑みてなされたものであり、本発明の目的とするところは、高周波信号の振幅に対する歪みを低減しつつ、スイッチングを実現することが可能な、新規かつ改良されたスイッチを提供することにある。

【課題を解決するための手段】

【0009】

上記目的を達成するために、本発明のある観点によれば、高周波信号が入力される入力端子と、上記入力端子に入力された上記高周波信号が出力される第1出力端子との間に接続され、上記入力端子に入力される高周波信号を、選択的に上記第1出力端子から出力させる第1スイッチング部と、上記入力端子と、上記入力端子に入力された上記高周波信号が出力される第2出力端子との間に接続され、上記入力端子に入力される高周波信号を、選択的に上記第2出力端子から出力させる第2スイッチング部と、を備え、上記第1スイッチング部は、上記入力端子と上記第1出力端子との間の第1信号線上に設けられる、インピーダンスの変換を行う第1インピーダンス変成器と、エミッタが接地され、コレクタが上記第1信号線に接続され、上記第1スイッチング部におけるスイッチング動作を制御する第1制御電圧に応じた電流がベースに印加される、第1バイポーラトランジスタと、コレクタが接地され、エミッタが上記第1信号線に接続され、上記第1制御電圧に応じた電流がベースに印加される、第2バイポーラトランジスタと、を備え、上記第2スイッチング部は、上記入力端子と上記第2出力端子との間の第2信号線上に設けられる、インピーダンスの変換を行う第2インピーダンス変成器と、エミッタが接地され、コレクタが上記第2信号線に接続され、上記第2スイッチング部におけるスイッチング動作を制御する第2制御電圧に応じた電流がベースに印加される、第3バイポーラトランジスタと、コレクタが接地され、エミッタが上記第2信号線に接続され、上記第2制御電圧に応じた電流がベースに印加される、第4バイポーラトランジスタと、を備えるスイッチが提供される。

【0010】

かかる構成によって、入力端子−出力端子間がオン状態のときには、入力端子−出力端子間の挿入損失を小さくし、入力端子−出力端子間がオフ状態のときには、入力端子−出力端子間のアイソレーションを大きくすることが可能となる。また、かかる構成によって、第1スイッチング部、および第2スイッチング部それぞれにおいて、高周波信号の振幅に対する歪みを低減することができる。よって、かかる構成によって、高周波信号の振幅に対する歪みを低減しつつ、スイッチングを実現することができる。

【発明の効果】

【0011】

本発明によれば、高周波信号の振幅に対する歪みを低減しつつ、スイッチングを実現することができる。

【図面の簡単な説明】

【0012】

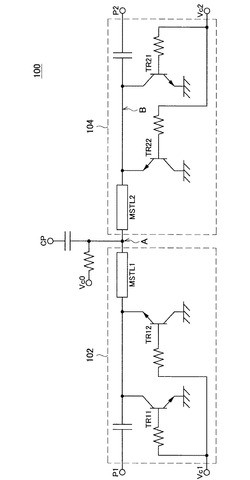

【図1】本発明の第1の実施形態に係るスイッチの構成の一例を示す説明図である。

【図2A】本発明の第1の実施形態に係る第4バイポーラトランジスタを備えることによる効果を説明するための説明図である。

【図2B】本発明の第1の実施形態に係る第4バイポーラトランジスタを備えることによる効果を説明するための説明図である。

【図3】本発明の第2の実施形態に係るスイッチの構成の一例を示す説明図である。

【図4A】本発明の第2の実施形態に係るキャパシタを備えることによる効果を説明するための説明図である。

【図4B】本発明の第2の実施形態に係るキャパシタを備えることによる効果を説明するための説明図である。

【発明を実施するための形態】

【0013】

以下に添付図面を参照しながら、本発明の好適な実施の形態について詳細に説明する。なお、本明細書および図面において、実質的に同一の機能構成を有する構成要素については、同一の符号を付することにより重複説明を省略する。

【0014】

また、以下では、本発明の実施形態に係るスイッチとして、1入力2出力でオン/オフを切り替えるSPDT(Single pole, dual throw)スイッチを例に挙げて説明する。なお、以下では、説明の便宜上、1入力2出力のSPDTについて説明するが、各端子は入力と出力のどちらでもかまわない。また、本発明の実施形態に係るスイッチは、SPDTスイッチに限られない。例えば、本発明の実施形態に係るスイッチは、1入力1出力でオン/オフを切り替えるSPST(Single pole, single throw)スイッチであってもよく、また、1入力3以上出力でオン/オフを切り替えるスイッチであってもよい。本発明の実施形態に係るスイッチは、後述する第1スイッチング部(または第2スイッチング部)を1または2以上備えることによって、多様なスイッチを実現することが可能である。

【0015】

(第1の実施形態)

図1は、本発明の第1の実施形態に係るスイッチ100の構成の一例を示す説明図である。

【0016】

[1]スイッチ100の構成

まず、スイッチ100の構成の一例について説明する。スイッチ100は、高周波信号が入力される入力端子CPと、第1出力端子P1と、第2出力端子P2と、入力端子CPと第1出力端子P1との間に接続される第1スイッチング部102と、入力端子CPと第2出力端子P1との間に接続される第2スイッチング部104とを備える。第1スイッチング部102は、入力端子CPに入力される高周波信号を、選択的に第1出力端子P1から出力させる。また、第2スイッチング部104は、入力端子CPに入力される高周波信号を、選択的に第2出力端子P2から出力させる。

【0017】

ここで、本発明の実施形態に係る高周波信号としては、例えば、長波や、中波、短波、超短波、極超短波、マイクロ波、ミリ波などの無線通信に用いられる周波数の信号(例えば、30[kHz]〜300[GHz]の信号)が挙げられる。なお、本発明の実施形態に係る高周波信号は、上記に限られない。例えば、本発明の実施形態に係る高周波信号は、30[kHz]未満の信号であってもよく、また、300[GHz]より高い周波数の信号であってもよい。

【0018】

スイッチ100では、制御電圧Vc0、Vc1、Vc2の電圧レベル(ハイレベル/ローレベル)に応じて、第1スイッチング部102のオン/オフ動作と、第2スイッチング部104のオン/オフ動作とが制御される。より具体的には、例えば、制御電圧Vc0の電圧レベルをハイレベルに固定すると、第1スイッチング部102は、制御電圧Vc1(第1制御電圧)の電圧レベルがローレベルのときにオン状態となり、制御電圧Vc1の電圧レベルがハイレベルのときにオン状態となる。また、例えば、制御電圧Vc0の電圧レベルをハイレベルに固定すると、第2スイッチング部104は、制御電圧Vc2(第2制御電圧)の電圧レベルがローレベルのときにオン状態となり、制御電圧Vc2の電圧レベルがハイレベルのときにオン状態となる。

【0019】

第1スイッチング部102は、第1インピーダンス変成器MSTL1と、第1バイポーラトランジスタTR11と、第2バイポーラトランジスタTR12とを備える。

【0020】

第1インピーダンス変成器MSTL1は、入力端子CPと第1出力端子P1との間の第1信号線上に設けられ、高抵抗を低抵抗に、低抵抗を高抵抗に変換する役目を果たす。ここで、第1インピーダンス変成器MSTL1としては、例えば、使用周波数の1/4波長線路が挙げられる。

【0021】

第1バイポーラトランジスタTR11は、エミッタが接地され、コレクタが第1信号線に接続され、制御電圧Vc1に応じた電流がベースに印加される。ここで、第1バイポーラトランジスタTR11としては、例えば、SiGeHBTとBulk CMOSの複合プロセスであるSiGeBiCMOSなどの一般的に用いられているプロセスが用いられた、ヘテロ接合バイポーラトランジスタ(HBT)が挙げられる。なお、本発明の実施形態に係る第1バイポーラトランジスタTR11が、SiGeBiCMOSなどのプロセスによるヘテロ接合バイポーラトランジスタに限られないことは、言うまでもない。

【0022】

第2バイポーラトランジスタTR12は、コレクタが接地され、エミッタが第1信号線に接続され、制御電圧Vc1に応じた電流がベースに印加される。ここで、第2バイポーラトランジスタTR12としては、第1バイポーラトランジスタTR11と同様に、例えば、SiGeHBTとBulk CMOSの複合プロセスであるSiGeBiCMOSなどの一般的に用いられているプロセスが用いられた、ヘテロ接合バイポーラトランジスタ(HBT)が挙げられる。なお、本発明の実施形態に係る第2バイポーラトランジスタTR12が、SiGeBiCMOSなどのプロセスによるヘテロ接合バイポーラトランジスタに限られないことは、言うまでもない。

【0023】

第2スイッチング部104は、第2インピーダンス変成器MSTL2と、第3バイポーラトランジスタTR21と、第4バイポーラトランジスタTR22とを備える。

【0024】

第2インピーダンス変成器MSTL2は、入力端子CPと第2出力端子P2との間の第2信号線上に設けられ、高抵抗を低抵抗に、低抵抗を高抵抗に変換する役目を果たす。ここで、第2インピーダンス変成器MSTL2としては、第1インピーダンス変成器MSTL1と同様に、例えば、使用周波数の1/4波長線路が挙げられる。

【0025】

第3バイポーラトランジスタTR21は、エミッタが接地され、コレクタが第2信号線に接続され、制御電圧Vc2に応じた電流がベースに印加される。ここで、第3バイポーラトランジスタTR21としては、例えば、SiGeHBTとBulk CMOSの複合プロセスであるSiGeBiCMOSなどの一般的に用いられているプロセスが用いられた、ヘテロ接合バイポーラトランジスタ(HBT)が挙げられる。なお、本発明の実施形態に係る第3バイポーラトランジスタTR21が、SiGeBiCMOSなどのプロセスによるヘテロ接合バイポーラトランジスタに限られないことは、言うまでもない。

【0026】

第4バイポーラトランジスタTR22は、コレクタが接地され、エミッタが第2信号線に接続され、制御電圧Vc2に応じた電流がベースに印加される。ここで、第4バイポーラトランジスタTR22としては、第3バイポーラトランジスタTR21と同様に、例えば、SiGeHBTとBulk CMOSの複合プロセスであるSiGeBiCMOSなどの一般的に用いられているプロセスが用いられた、ヘテロ接合バイポーラトランジスタ(HBT)が挙げられる。なお、本発明の実施形態に係る第4バイポーラトランジスタTR22が、SiGeBiCMOSなどのプロセスによるヘテロ接合バイポーラトランジスタに限られないことは、言うまでもない。

【0027】

[2]スイッチ100におけるスイッチング動作の一例

次に、スイッチ100におけるスイッチング動作の一例について説明する。以下では、入力端子CP−第1出力端子P1間がオン状態であり、入力端子CP−第2出力端子P2間がオフ状態である場合(すなわち、第1スイッチング部102がオン状態であり、第2スイッチング部104がオフ状態である場合)を例に挙げて説明する。つまり、以下では、制御電圧Vc0の電圧レベルがハイレベル、制御電圧Vc1の電圧レベルがローレベル、制御電圧Vc2の電圧レベルがハイレベルの場合を例に挙げて説明する。なお、上述したように、制御電圧Vc1の電圧レベルをハイレベルとし、制御電圧Vc2の電圧レベルをローレベルとすれば、スイッチ100では、第1スイッチング部102がオフ状態となり、第2スイッチング部104がオン状態となる。

【0028】

制御電圧Vc1の電圧レベルがローレベルのとき、第1バイポーラトランジスタTR11と、第2バイポーラトランジスタTR12とは、オフ状態となるので、入力端子CP−第1出力端子P1間の挿入損失は小さくなる。

【0029】

一方、制御電圧Vc2の電圧レベルがローレベルのとき、第3バイポーラトランジスタTR21と、第4バイポーラトランジスタTR22とは、オン状態となり、図1に示すB点におけるインピーダンスは、グランドと短絡状態となる。よって、入力端子CP−第2出力端子P2間のアイソレーションは大きくなる。

【0030】

また、スイッチ100では、オフ状態である第2スイッチング部104が備える第2インピーダンス変成器MSTL2の作用により、第1スイッチング部102と第2スイッチング104との接続点である図1に示すA点は、開放状態となる。よって、第2スイッチング104が入力端子CP−第1出力端子P1間の挿入損失に与える影響は、最小となる。

【0031】

スイッチ100は、例えば上記のように、オン状態のスイッチング部102の挿入損失を小さくし、オフ状態のスイッチング部104のアイソレーションを大きくすることによって、スイッチングを実現する。

【0032】

上記のように、オフ状態にある第2スイッチング部104は、図1に示すB点におけるインピーダンスを、グランドと短絡状態とすることによって、入力端子CP−第2出力端子P2間のアイソレーションを大きくする。ここで、第2スイッチング部104における第3バイポーラトランジスタTR21と、第4バイポーラトランジスタTR22との役目について、より具体的に説明する。

【0033】

図1に示すB点において、高周波信号の正の振幅は、第3バイポーラトランジスタTR21によって短絡状態となる。一方、高周波信号の負の振幅に対して、第3バイポーラトランジスタTR21は、エミッタからコレクタ方向には電流が流れないため、短絡状態にすることができない。

【0034】

また、第2スイッチング部104において第4バイポーラトランジスタTR22は、エミッタとコレクタとの接続関係が、第3バイポーラトランジスタTR21と逆となっている。よって、第2スイッチング部104では、第4バイポーラトランジスタTR22によって、高周波信号の負の振幅の電流を流すことが可能となるので、短絡状態を保つことができる。

【0035】

図2A、図2Bは、本発明の第1の実施形態に係る第4バイポーラトランジスタTR22を備えることによる効果を説明するための説明図である。図2Aは、入力端子CP−第1出力端子P1間の入力される高周波信号電力に対する挿入損失との関係を、第4バイポーラトランジスタTR22を備える場合と備えない場合それぞれについて示している。また、図2Bは、入力端子CP−第1出力端子P1間の入力される高周波信号電力に対するIMD(Inter Modulation Distortion:相互変調歪)との関係を、第4バイポーラトランジスタTR22を備える場合と備えない場合それぞれについて示している。ここで、図2A、図2Bに示すAは、第4バイポーラトランジスタTR22を備える場合における特性の一例を示しており、また、図2A、図2Bに示すBは、第4バイポーラトランジスタTR22を備えない場合における特性の一例を示している。

【0036】

図2Aに示すように、第4バイポーラトランジスタTR22を備えることによって、第1スイッチング部102では、入力端子CP−第1出力端子P1間の挿入損失を、第4バイポーラトランジスタTR22を備えない場合よりも小さくすることができる。また、図2Bに示すように、第4バイポーラトランジスタTR22を備えることによって、第1スイッチング部102では、IMD(相互変調歪)を、第4バイポーラトランジスタTR22を備えない場合よりも小さくすることができる。

【0037】

なお、上記では、第2スイッチング部104に着目して説明したが、図1に示すように、第1スイッチング部102は、第2スイッチング部104と同様の構成を有する。つまり、第1スイッチング部102がオフ状態のときには、第1バイポーラトランジスタTR11は、第3バイポーラトランジスタTR21と同様の役目を果たし、また、第2バイポーラトランジスタTR12は、第4バイポーラトランジスタTR22と同様の役目を果たす。

【0038】

したがって、本発明の第1の実施形態に係るスイッチ100は、図1に示す構成をとることによって、高周波信号の振幅に対する歪みを低減しつつ、スイッチングを実現することができる。また、スイッチ100は、図1に示す構成をとることによって、高周波信号が大電力の信号である場合においても、歪みを低減することができる。

【0039】

また、スイッチ100は、第1バイポーラトランジスタTR11、第2バイポーラトランジスタTR12、第3バイポーラトランジスタTR21、および第4バイポーラトランジスタTR22それぞれを、例えば、SiGeHBTとBulk CMOSの複合プロセスであるSiGeBiCMOSなどの一般的に用いられているプロセスが用いられた、ヘテロ接合バイポーラトランジスタとしても、歪みの低減とスイッチングの実現とを図ることが可能である。つまり、スイッチ100では、特殊なプロセスを用いる必要はない。

【0040】

したがって、本発明の第1の実施形態に係るスイッチ100は、コストの低減を図ることもできる。

【0041】

(第2の実施形態)

本発明の実施形態に係るスイッチの構成は、図1に示す構成に限られない。図3は、本発明の第2の実施形態に係るスイッチ200の構成の一例を示す説明図である。

【0042】

スイッチ200は、高周波信号が入力される入力端子CPと、第1出力端子P1と、第2出力端子P2と、入力端子CPと第1出力端子P1との間に接続される第1スイッチング部202と、入力端子CPと第2出力端子P1との間に接続される第2スイッチング部204とを備える。第1スイッチング部202は、図1に示す第1スイッチング部102と同様に、入力端子CPに入力される高周波信号を、選択的に第1出力端子P1から出力させる。また、第2スイッチング部204は、図1に示す第2スイッチング部104と同様に、入力端子CPに入力される高周波信号を、選択的に第2出力端子P2から出力させる。

【0043】

ここで、第1スイッチング部202と、図1に示す第1スイッチング部102とを比較すると、第1スイッチング部202は、基本的に図1に示す第1スイッチング部102と同様の構成を有しているが、さらに、第2バイポーラトランジスタTR12のベースに一端が接続され、他端が接地されるキャパシタC1を備えている。また、第2スイッチング部204と、図1に示す第2スイッチング部104とを比較すると、第2スイッチング部204は、基本的に図1に示す第2スイッチング部104と同様の構成を有しているが、さらに、第4バイポーラトランジスタTR22のベースに一端が接続され、他端が接地されるキャパシタC2を備えている。

【0044】

キャパシタC1は、第1スイッチング部202がオン状態(すなわち、第1バイポーラトランジスタTR11、および第2バイポーラトランジスタTR12がオフ状態)である場合において、入力端子CP−第1出力端子P1間の挿入損失の増大と、歪みの劣化とが生じる可能性を低減する役目を果たす。また、キャパシタC2は、第2スイッチング部204がオン状態(すなわち、第3バイポーラトランジスタTR21、および第4バイポーラトランジスタTR22がオフ状態)である場合において、入力端子CP−第2出力端子P2間の挿入損失の増大と、歪みの劣化とが生じる可能性を低減する役目を果たす。

【0045】

より具体的に説明すると、例えば、入力端子CP−第1出力端子P1間がオン状態のとき、第2バイポーラトランジスタTR12は、オフ状態を維持している必要がある。しかしながら、例えば入力端子CPから入力される高周波信号が大電力の信号である場合には、高周波振幅が第2バイポーラトランジスタTR12のベースにリークし、その結果、第2バイポーラトランジスタTR12は、オフ状態を維持できなくなることが起こりうる。

【0046】

スイッチ200は、第2バイポーラトランジスタTR12のベースに一端が接続され、他端が接地されるキャパシタC1を備えることによって、第2バイポーラトランジスタTR12のベースの電位を高周波振幅に対して安定させ、第2バイポーラトランジスタTR12がオフ状態を維持できなくなることを防止する。ここで、キャパシタC1の容量としては、例えば、高周波で短絡となるような容量が挙げられる。より具体的には、キャパシタC1の容量としては、例えば、1[GHz]の周波数に対して2[pF]程度の容量が挙げられる。なお、本発明の実施形態に係るキャパシタC1の容量が、上記に限られないことは、言うまでもない。

【0047】

図4A、図4Bは、本発明の第2の実施形態に係るキャパシタC1を備えることによる効果を説明するための説明図である。図4Aは、入力端子CP−第1出力端子P1間の入力される高周波信号電力に対する挿入損失との関係を、キャパシタC1を備える場合と備えない場合それぞれについて示している。また、図4Bは、入力端子CP−第1出力端子P1間の入力される高周波信号電力に対するIMD(相互変調歪)との関係を、キャパシタC1を備える場合と備えない場合それぞれについて示している。ここで、図4A、図4Bに示すAは、キャパシタC1を備える場合における特性の一例を示しており、また、図4A、図4Bに示すBは、キャパシタC1を備えない場合における特性の一例を示している。

【0048】

図4Aに示すように、キャパシタC1を備えることによって、第1スイッチング部202では、入力端子CP−第1出力端子P1間の挿入損失を、キャパシタC1を備えない場合よりも小さくすることができる。また、図4Bに示すように、キャパシタC1を備えることによって、第1スイッチング部202では、IMD(相互変調歪)を、キャパシタC1を備えない場合よりも小さくすることができる。

【0049】

なお、上記では、第1スイッチング部202に着目して説明したが、図3に示すように、第2スイッチング部204は、第1スイッチング部202と同様の構成を有する。つまり、第2スイッチング部204がオン状態のときには、キャパシタC2は、キャパシタC1と同様の役目を果たす。

【0050】

したがって、本発明の第2の実施形態に係るスイッチ200は、図3に示す構成をとることによって、図1に示す第1の実施形態に係るスイッチ100よりも、さらに高周波信号の振幅に対する歪みを低減しつつ、スイッチングを実現することができる。また、スイッチ200は、図3に示す構成をとることによって、高周波信号が大電力の信号である場合においても、歪みを低減することができる。

【0051】

また、スイッチ200は、図1に示す第1の実施形態に係るスイッチ100と同様に、第1バイポーラトランジスタTR11、第2バイポーラトランジスタTR12、第3バイポーラトランジスタTR21、および第4バイポーラトランジスタTR22それぞれを、例えば、SiGeHBTとBulk CMOSの複合プロセスであるSiGeBiCMOSなどの一般的に用いられているプロセスが用いられた、ヘテロ接合バイポーラトランジスタとしても、歪みの低減とスイッチングの実現とを図ることが可能である。つまり、スイッチ200では、図1に示す第1の実施形態に係るスイッチ100と同様に、特殊なプロセスを用いる必要はない。

【0052】

したがって、本発明の第2の実施形態に係るスイッチ200は、図1に示す第1の実施形態に係るスイッチ100と同様に、コストの低減を図ることもできる。

【0053】

なお、本発明の第2の実施形態に係るスイッチの構成は、図3に示す構成に限られない。例えば、図3では、第1スイッチング部202と第2スイッチング部204との双方が、キャパシタC1またはキャパシタC2を備える構成を示しているが、いずれか一方がキャパシタを備える構成をとることも可能である。上記構成であっても、第2の実施形態の変形例に係るスイッチは、図1に示す第1の実施形態に係るスイッチ100と同等以上の効果を奏することができる。

【0054】

以上、添付図面を参照しながら本発明の好適な実施形態について説明したが、本発明は係る例に限定されないことは言うまでもない。当業者であれば、特許請求の範囲に記載された範疇内において、各種の変更例または修正例に想到し得ることは明らかであり、それらについても当然に本発明の技術的範囲に属するものと了解される。

【0055】

例えば、本発明の実施形態に係るスイッチは、図1に示すスイッチ100、図3に示すスイッチ200(変形例に係るスイッチも含む)の等価回路で構成されていてもよい。

【符号の説明】

【0056】

100、200 スイッチ

102、202 第1スイッチング部

104、204 第2スイッチング部

【技術分野】

【0001】

本発明は、スイッチに関する。

【背景技術】

【0002】

例えば無線通信に用いられる高周波信号の経路を切り替えるスイッチには、一般的に、GaAs系化合物半導体のHEMT(High Electron Mobility Transistor。高電子移動度トランジスタ)などが用いられている。ここで、化合物半導体は、ウェハー単価が高く、またウェハーの大口径化が進んでいないため、価格が高いという欠点がある。

【0003】

また、近年、スイッチの低価格化を実現するために、例えばCMOS(Complementary Metal Oxide Semiconductor)系のスイッチの開発もされている。ここで、通常のCMOS(Bulk CMOS)は、基板が低抵抗であるために漏洩電力が発生し、スイッチの特性が劣化する恐れがある。そのため、例えば、CMOS(Complementary Metal Oxide Semiconductor)系のスイッチを用いる場合には、例えば、SOS(Silicon on Sapphire)やSOI(Silicon on Insulator)などの特殊プロセスを導入することによって、スイッチの特性の改善を図っている。しかしながら、上記SOSやSOIなどの特殊プロセスを用いる場合には、結果的にコストの上昇を招いてしまう。

【0004】

このような中、高周波信号の経路を切り替えるスイッチに係る技術が開発されている。ヘテロ接合バイポーラトランジスタ(Heterojunction Bipolar Transistor。以下「HBT」と示す場合がある。)を用いたスイッチに係る技術としては、例えば、特許文献1に記載の技術が挙げられる。

【先行技術文献】

【特許文献】

【0005】

【特許文献1】特開2006−279316号公報

【発明の概要】

【発明が解決しようとする課題】

【0006】

例えばSiGeHBTとBulk CMOSの複合プロセスであるSiGeBiCMOSなどの一般的に用いられているプロセスが用いられた、HBTなどのバイポーラトランジスタを用いてスイッチを実現する場合には、HEMTなどのFETを用いてスイッチを実現する場合よりもスイッチのコストを低減することが可能である。ここで、FETは、対称構造(すなわち、ドレインとソースが固定されない構造)であるため、高周波信号の振幅に対して、順方向動作時と逆方向動作時とにおける特性は同一となる。一方、バイポーラトランジスタでは、順方向動作時と逆方向動作時とにおける特性が同一ではない。そのため、バイポーラトランジスタが用いられるスイッチでは、高周波信号の振幅に対する歪みが発生する可能性がある。

【0007】

例えば特許文献1に記載の技術では、HBTの特性自体を改良しているので、高周波信号の振幅に対する歪みを低減することができる可能性がある。しかしながら、例えば特許文献1に記載の技術を用いる場合には、特殊なプロセスを用いなければならないので、コストの低減は望むべくもない。

【0008】

本発明は、上記問題に鑑みてなされたものであり、本発明の目的とするところは、高周波信号の振幅に対する歪みを低減しつつ、スイッチングを実現することが可能な、新規かつ改良されたスイッチを提供することにある。

【課題を解決するための手段】

【0009】

上記目的を達成するために、本発明のある観点によれば、高周波信号が入力される入力端子と、上記入力端子に入力された上記高周波信号が出力される第1出力端子との間に接続され、上記入力端子に入力される高周波信号を、選択的に上記第1出力端子から出力させる第1スイッチング部と、上記入力端子と、上記入力端子に入力された上記高周波信号が出力される第2出力端子との間に接続され、上記入力端子に入力される高周波信号を、選択的に上記第2出力端子から出力させる第2スイッチング部と、を備え、上記第1スイッチング部は、上記入力端子と上記第1出力端子との間の第1信号線上に設けられる、インピーダンスの変換を行う第1インピーダンス変成器と、エミッタが接地され、コレクタが上記第1信号線に接続され、上記第1スイッチング部におけるスイッチング動作を制御する第1制御電圧に応じた電流がベースに印加される、第1バイポーラトランジスタと、コレクタが接地され、エミッタが上記第1信号線に接続され、上記第1制御電圧に応じた電流がベースに印加される、第2バイポーラトランジスタと、を備え、上記第2スイッチング部は、上記入力端子と上記第2出力端子との間の第2信号線上に設けられる、インピーダンスの変換を行う第2インピーダンス変成器と、エミッタが接地され、コレクタが上記第2信号線に接続され、上記第2スイッチング部におけるスイッチング動作を制御する第2制御電圧に応じた電流がベースに印加される、第3バイポーラトランジスタと、コレクタが接地され、エミッタが上記第2信号線に接続され、上記第2制御電圧に応じた電流がベースに印加される、第4バイポーラトランジスタと、を備えるスイッチが提供される。

【0010】

かかる構成によって、入力端子−出力端子間がオン状態のときには、入力端子−出力端子間の挿入損失を小さくし、入力端子−出力端子間がオフ状態のときには、入力端子−出力端子間のアイソレーションを大きくすることが可能となる。また、かかる構成によって、第1スイッチング部、および第2スイッチング部それぞれにおいて、高周波信号の振幅に対する歪みを低減することができる。よって、かかる構成によって、高周波信号の振幅に対する歪みを低減しつつ、スイッチングを実現することができる。

【発明の効果】

【0011】

本発明によれば、高周波信号の振幅に対する歪みを低減しつつ、スイッチングを実現することができる。

【図面の簡単な説明】

【0012】

【図1】本発明の第1の実施形態に係るスイッチの構成の一例を示す説明図である。

【図2A】本発明の第1の実施形態に係る第4バイポーラトランジスタを備えることによる効果を説明するための説明図である。

【図2B】本発明の第1の実施形態に係る第4バイポーラトランジスタを備えることによる効果を説明するための説明図である。

【図3】本発明の第2の実施形態に係るスイッチの構成の一例を示す説明図である。

【図4A】本発明の第2の実施形態に係るキャパシタを備えることによる効果を説明するための説明図である。

【図4B】本発明の第2の実施形態に係るキャパシタを備えることによる効果を説明するための説明図である。

【発明を実施するための形態】

【0013】

以下に添付図面を参照しながら、本発明の好適な実施の形態について詳細に説明する。なお、本明細書および図面において、実質的に同一の機能構成を有する構成要素については、同一の符号を付することにより重複説明を省略する。

【0014】

また、以下では、本発明の実施形態に係るスイッチとして、1入力2出力でオン/オフを切り替えるSPDT(Single pole, dual throw)スイッチを例に挙げて説明する。なお、以下では、説明の便宜上、1入力2出力のSPDTについて説明するが、各端子は入力と出力のどちらでもかまわない。また、本発明の実施形態に係るスイッチは、SPDTスイッチに限られない。例えば、本発明の実施形態に係るスイッチは、1入力1出力でオン/オフを切り替えるSPST(Single pole, single throw)スイッチであってもよく、また、1入力3以上出力でオン/オフを切り替えるスイッチであってもよい。本発明の実施形態に係るスイッチは、後述する第1スイッチング部(または第2スイッチング部)を1または2以上備えることによって、多様なスイッチを実現することが可能である。

【0015】

(第1の実施形態)

図1は、本発明の第1の実施形態に係るスイッチ100の構成の一例を示す説明図である。

【0016】

[1]スイッチ100の構成

まず、スイッチ100の構成の一例について説明する。スイッチ100は、高周波信号が入力される入力端子CPと、第1出力端子P1と、第2出力端子P2と、入力端子CPと第1出力端子P1との間に接続される第1スイッチング部102と、入力端子CPと第2出力端子P1との間に接続される第2スイッチング部104とを備える。第1スイッチング部102は、入力端子CPに入力される高周波信号を、選択的に第1出力端子P1から出力させる。また、第2スイッチング部104は、入力端子CPに入力される高周波信号を、選択的に第2出力端子P2から出力させる。

【0017】

ここで、本発明の実施形態に係る高周波信号としては、例えば、長波や、中波、短波、超短波、極超短波、マイクロ波、ミリ波などの無線通信に用いられる周波数の信号(例えば、30[kHz]〜300[GHz]の信号)が挙げられる。なお、本発明の実施形態に係る高周波信号は、上記に限られない。例えば、本発明の実施形態に係る高周波信号は、30[kHz]未満の信号であってもよく、また、300[GHz]より高い周波数の信号であってもよい。

【0018】

スイッチ100では、制御電圧Vc0、Vc1、Vc2の電圧レベル(ハイレベル/ローレベル)に応じて、第1スイッチング部102のオン/オフ動作と、第2スイッチング部104のオン/オフ動作とが制御される。より具体的には、例えば、制御電圧Vc0の電圧レベルをハイレベルに固定すると、第1スイッチング部102は、制御電圧Vc1(第1制御電圧)の電圧レベルがローレベルのときにオン状態となり、制御電圧Vc1の電圧レベルがハイレベルのときにオン状態となる。また、例えば、制御電圧Vc0の電圧レベルをハイレベルに固定すると、第2スイッチング部104は、制御電圧Vc2(第2制御電圧)の電圧レベルがローレベルのときにオン状態となり、制御電圧Vc2の電圧レベルがハイレベルのときにオン状態となる。

【0019】

第1スイッチング部102は、第1インピーダンス変成器MSTL1と、第1バイポーラトランジスタTR11と、第2バイポーラトランジスタTR12とを備える。

【0020】

第1インピーダンス変成器MSTL1は、入力端子CPと第1出力端子P1との間の第1信号線上に設けられ、高抵抗を低抵抗に、低抵抗を高抵抗に変換する役目を果たす。ここで、第1インピーダンス変成器MSTL1としては、例えば、使用周波数の1/4波長線路が挙げられる。

【0021】

第1バイポーラトランジスタTR11は、エミッタが接地され、コレクタが第1信号線に接続され、制御電圧Vc1に応じた電流がベースに印加される。ここで、第1バイポーラトランジスタTR11としては、例えば、SiGeHBTとBulk CMOSの複合プロセスであるSiGeBiCMOSなどの一般的に用いられているプロセスが用いられた、ヘテロ接合バイポーラトランジスタ(HBT)が挙げられる。なお、本発明の実施形態に係る第1バイポーラトランジスタTR11が、SiGeBiCMOSなどのプロセスによるヘテロ接合バイポーラトランジスタに限られないことは、言うまでもない。

【0022】

第2バイポーラトランジスタTR12は、コレクタが接地され、エミッタが第1信号線に接続され、制御電圧Vc1に応じた電流がベースに印加される。ここで、第2バイポーラトランジスタTR12としては、第1バイポーラトランジスタTR11と同様に、例えば、SiGeHBTとBulk CMOSの複合プロセスであるSiGeBiCMOSなどの一般的に用いられているプロセスが用いられた、ヘテロ接合バイポーラトランジスタ(HBT)が挙げられる。なお、本発明の実施形態に係る第2バイポーラトランジスタTR12が、SiGeBiCMOSなどのプロセスによるヘテロ接合バイポーラトランジスタに限られないことは、言うまでもない。

【0023】

第2スイッチング部104は、第2インピーダンス変成器MSTL2と、第3バイポーラトランジスタTR21と、第4バイポーラトランジスタTR22とを備える。

【0024】

第2インピーダンス変成器MSTL2は、入力端子CPと第2出力端子P2との間の第2信号線上に設けられ、高抵抗を低抵抗に、低抵抗を高抵抗に変換する役目を果たす。ここで、第2インピーダンス変成器MSTL2としては、第1インピーダンス変成器MSTL1と同様に、例えば、使用周波数の1/4波長線路が挙げられる。

【0025】

第3バイポーラトランジスタTR21は、エミッタが接地され、コレクタが第2信号線に接続され、制御電圧Vc2に応じた電流がベースに印加される。ここで、第3バイポーラトランジスタTR21としては、例えば、SiGeHBTとBulk CMOSの複合プロセスであるSiGeBiCMOSなどの一般的に用いられているプロセスが用いられた、ヘテロ接合バイポーラトランジスタ(HBT)が挙げられる。なお、本発明の実施形態に係る第3バイポーラトランジスタTR21が、SiGeBiCMOSなどのプロセスによるヘテロ接合バイポーラトランジスタに限られないことは、言うまでもない。

【0026】

第4バイポーラトランジスタTR22は、コレクタが接地され、エミッタが第2信号線に接続され、制御電圧Vc2に応じた電流がベースに印加される。ここで、第4バイポーラトランジスタTR22としては、第3バイポーラトランジスタTR21と同様に、例えば、SiGeHBTとBulk CMOSの複合プロセスであるSiGeBiCMOSなどの一般的に用いられているプロセスが用いられた、ヘテロ接合バイポーラトランジスタ(HBT)が挙げられる。なお、本発明の実施形態に係る第4バイポーラトランジスタTR22が、SiGeBiCMOSなどのプロセスによるヘテロ接合バイポーラトランジスタに限られないことは、言うまでもない。

【0027】

[2]スイッチ100におけるスイッチング動作の一例

次に、スイッチ100におけるスイッチング動作の一例について説明する。以下では、入力端子CP−第1出力端子P1間がオン状態であり、入力端子CP−第2出力端子P2間がオフ状態である場合(すなわち、第1スイッチング部102がオン状態であり、第2スイッチング部104がオフ状態である場合)を例に挙げて説明する。つまり、以下では、制御電圧Vc0の電圧レベルがハイレベル、制御電圧Vc1の電圧レベルがローレベル、制御電圧Vc2の電圧レベルがハイレベルの場合を例に挙げて説明する。なお、上述したように、制御電圧Vc1の電圧レベルをハイレベルとし、制御電圧Vc2の電圧レベルをローレベルとすれば、スイッチ100では、第1スイッチング部102がオフ状態となり、第2スイッチング部104がオン状態となる。

【0028】

制御電圧Vc1の電圧レベルがローレベルのとき、第1バイポーラトランジスタTR11と、第2バイポーラトランジスタTR12とは、オフ状態となるので、入力端子CP−第1出力端子P1間の挿入損失は小さくなる。

【0029】

一方、制御電圧Vc2の電圧レベルがローレベルのとき、第3バイポーラトランジスタTR21と、第4バイポーラトランジスタTR22とは、オン状態となり、図1に示すB点におけるインピーダンスは、グランドと短絡状態となる。よって、入力端子CP−第2出力端子P2間のアイソレーションは大きくなる。

【0030】

また、スイッチ100では、オフ状態である第2スイッチング部104が備える第2インピーダンス変成器MSTL2の作用により、第1スイッチング部102と第2スイッチング104との接続点である図1に示すA点は、開放状態となる。よって、第2スイッチング104が入力端子CP−第1出力端子P1間の挿入損失に与える影響は、最小となる。

【0031】

スイッチ100は、例えば上記のように、オン状態のスイッチング部102の挿入損失を小さくし、オフ状態のスイッチング部104のアイソレーションを大きくすることによって、スイッチングを実現する。

【0032】

上記のように、オフ状態にある第2スイッチング部104は、図1に示すB点におけるインピーダンスを、グランドと短絡状態とすることによって、入力端子CP−第2出力端子P2間のアイソレーションを大きくする。ここで、第2スイッチング部104における第3バイポーラトランジスタTR21と、第4バイポーラトランジスタTR22との役目について、より具体的に説明する。

【0033】

図1に示すB点において、高周波信号の正の振幅は、第3バイポーラトランジスタTR21によって短絡状態となる。一方、高周波信号の負の振幅に対して、第3バイポーラトランジスタTR21は、エミッタからコレクタ方向には電流が流れないため、短絡状態にすることができない。

【0034】

また、第2スイッチング部104において第4バイポーラトランジスタTR22は、エミッタとコレクタとの接続関係が、第3バイポーラトランジスタTR21と逆となっている。よって、第2スイッチング部104では、第4バイポーラトランジスタTR22によって、高周波信号の負の振幅の電流を流すことが可能となるので、短絡状態を保つことができる。

【0035】

図2A、図2Bは、本発明の第1の実施形態に係る第4バイポーラトランジスタTR22を備えることによる効果を説明するための説明図である。図2Aは、入力端子CP−第1出力端子P1間の入力される高周波信号電力に対する挿入損失との関係を、第4バイポーラトランジスタTR22を備える場合と備えない場合それぞれについて示している。また、図2Bは、入力端子CP−第1出力端子P1間の入力される高周波信号電力に対するIMD(Inter Modulation Distortion:相互変調歪)との関係を、第4バイポーラトランジスタTR22を備える場合と備えない場合それぞれについて示している。ここで、図2A、図2Bに示すAは、第4バイポーラトランジスタTR22を備える場合における特性の一例を示しており、また、図2A、図2Bに示すBは、第4バイポーラトランジスタTR22を備えない場合における特性の一例を示している。

【0036】

図2Aに示すように、第4バイポーラトランジスタTR22を備えることによって、第1スイッチング部102では、入力端子CP−第1出力端子P1間の挿入損失を、第4バイポーラトランジスタTR22を備えない場合よりも小さくすることができる。また、図2Bに示すように、第4バイポーラトランジスタTR22を備えることによって、第1スイッチング部102では、IMD(相互変調歪)を、第4バイポーラトランジスタTR22を備えない場合よりも小さくすることができる。

【0037】

なお、上記では、第2スイッチング部104に着目して説明したが、図1に示すように、第1スイッチング部102は、第2スイッチング部104と同様の構成を有する。つまり、第1スイッチング部102がオフ状態のときには、第1バイポーラトランジスタTR11は、第3バイポーラトランジスタTR21と同様の役目を果たし、また、第2バイポーラトランジスタTR12は、第4バイポーラトランジスタTR22と同様の役目を果たす。

【0038】

したがって、本発明の第1の実施形態に係るスイッチ100は、図1に示す構成をとることによって、高周波信号の振幅に対する歪みを低減しつつ、スイッチングを実現することができる。また、スイッチ100は、図1に示す構成をとることによって、高周波信号が大電力の信号である場合においても、歪みを低減することができる。

【0039】

また、スイッチ100は、第1バイポーラトランジスタTR11、第2バイポーラトランジスタTR12、第3バイポーラトランジスタTR21、および第4バイポーラトランジスタTR22それぞれを、例えば、SiGeHBTとBulk CMOSの複合プロセスであるSiGeBiCMOSなどの一般的に用いられているプロセスが用いられた、ヘテロ接合バイポーラトランジスタとしても、歪みの低減とスイッチングの実現とを図ることが可能である。つまり、スイッチ100では、特殊なプロセスを用いる必要はない。

【0040】

したがって、本発明の第1の実施形態に係るスイッチ100は、コストの低減を図ることもできる。

【0041】

(第2の実施形態)

本発明の実施形態に係るスイッチの構成は、図1に示す構成に限られない。図3は、本発明の第2の実施形態に係るスイッチ200の構成の一例を示す説明図である。

【0042】

スイッチ200は、高周波信号が入力される入力端子CPと、第1出力端子P1と、第2出力端子P2と、入力端子CPと第1出力端子P1との間に接続される第1スイッチング部202と、入力端子CPと第2出力端子P1との間に接続される第2スイッチング部204とを備える。第1スイッチング部202は、図1に示す第1スイッチング部102と同様に、入力端子CPに入力される高周波信号を、選択的に第1出力端子P1から出力させる。また、第2スイッチング部204は、図1に示す第2スイッチング部104と同様に、入力端子CPに入力される高周波信号を、選択的に第2出力端子P2から出力させる。

【0043】

ここで、第1スイッチング部202と、図1に示す第1スイッチング部102とを比較すると、第1スイッチング部202は、基本的に図1に示す第1スイッチング部102と同様の構成を有しているが、さらに、第2バイポーラトランジスタTR12のベースに一端が接続され、他端が接地されるキャパシタC1を備えている。また、第2スイッチング部204と、図1に示す第2スイッチング部104とを比較すると、第2スイッチング部204は、基本的に図1に示す第2スイッチング部104と同様の構成を有しているが、さらに、第4バイポーラトランジスタTR22のベースに一端が接続され、他端が接地されるキャパシタC2を備えている。

【0044】

キャパシタC1は、第1スイッチング部202がオン状態(すなわち、第1バイポーラトランジスタTR11、および第2バイポーラトランジスタTR12がオフ状態)である場合において、入力端子CP−第1出力端子P1間の挿入損失の増大と、歪みの劣化とが生じる可能性を低減する役目を果たす。また、キャパシタC2は、第2スイッチング部204がオン状態(すなわち、第3バイポーラトランジスタTR21、および第4バイポーラトランジスタTR22がオフ状態)である場合において、入力端子CP−第2出力端子P2間の挿入損失の増大と、歪みの劣化とが生じる可能性を低減する役目を果たす。

【0045】

より具体的に説明すると、例えば、入力端子CP−第1出力端子P1間がオン状態のとき、第2バイポーラトランジスタTR12は、オフ状態を維持している必要がある。しかしながら、例えば入力端子CPから入力される高周波信号が大電力の信号である場合には、高周波振幅が第2バイポーラトランジスタTR12のベースにリークし、その結果、第2バイポーラトランジスタTR12は、オフ状態を維持できなくなることが起こりうる。

【0046】

スイッチ200は、第2バイポーラトランジスタTR12のベースに一端が接続され、他端が接地されるキャパシタC1を備えることによって、第2バイポーラトランジスタTR12のベースの電位を高周波振幅に対して安定させ、第2バイポーラトランジスタTR12がオフ状態を維持できなくなることを防止する。ここで、キャパシタC1の容量としては、例えば、高周波で短絡となるような容量が挙げられる。より具体的には、キャパシタC1の容量としては、例えば、1[GHz]の周波数に対して2[pF]程度の容量が挙げられる。なお、本発明の実施形態に係るキャパシタC1の容量が、上記に限られないことは、言うまでもない。

【0047】

図4A、図4Bは、本発明の第2の実施形態に係るキャパシタC1を備えることによる効果を説明するための説明図である。図4Aは、入力端子CP−第1出力端子P1間の入力される高周波信号電力に対する挿入損失との関係を、キャパシタC1を備える場合と備えない場合それぞれについて示している。また、図4Bは、入力端子CP−第1出力端子P1間の入力される高周波信号電力に対するIMD(相互変調歪)との関係を、キャパシタC1を備える場合と備えない場合それぞれについて示している。ここで、図4A、図4Bに示すAは、キャパシタC1を備える場合における特性の一例を示しており、また、図4A、図4Bに示すBは、キャパシタC1を備えない場合における特性の一例を示している。

【0048】

図4Aに示すように、キャパシタC1を備えることによって、第1スイッチング部202では、入力端子CP−第1出力端子P1間の挿入損失を、キャパシタC1を備えない場合よりも小さくすることができる。また、図4Bに示すように、キャパシタC1を備えることによって、第1スイッチング部202では、IMD(相互変調歪)を、キャパシタC1を備えない場合よりも小さくすることができる。

【0049】

なお、上記では、第1スイッチング部202に着目して説明したが、図3に示すように、第2スイッチング部204は、第1スイッチング部202と同様の構成を有する。つまり、第2スイッチング部204がオン状態のときには、キャパシタC2は、キャパシタC1と同様の役目を果たす。

【0050】

したがって、本発明の第2の実施形態に係るスイッチ200は、図3に示す構成をとることによって、図1に示す第1の実施形態に係るスイッチ100よりも、さらに高周波信号の振幅に対する歪みを低減しつつ、スイッチングを実現することができる。また、スイッチ200は、図3に示す構成をとることによって、高周波信号が大電力の信号である場合においても、歪みを低減することができる。

【0051】

また、スイッチ200は、図1に示す第1の実施形態に係るスイッチ100と同様に、第1バイポーラトランジスタTR11、第2バイポーラトランジスタTR12、第3バイポーラトランジスタTR21、および第4バイポーラトランジスタTR22それぞれを、例えば、SiGeHBTとBulk CMOSの複合プロセスであるSiGeBiCMOSなどの一般的に用いられているプロセスが用いられた、ヘテロ接合バイポーラトランジスタとしても、歪みの低減とスイッチングの実現とを図ることが可能である。つまり、スイッチ200では、図1に示す第1の実施形態に係るスイッチ100と同様に、特殊なプロセスを用いる必要はない。

【0052】

したがって、本発明の第2の実施形態に係るスイッチ200は、図1に示す第1の実施形態に係るスイッチ100と同様に、コストの低減を図ることもできる。

【0053】

なお、本発明の第2の実施形態に係るスイッチの構成は、図3に示す構成に限られない。例えば、図3では、第1スイッチング部202と第2スイッチング部204との双方が、キャパシタC1またはキャパシタC2を備える構成を示しているが、いずれか一方がキャパシタを備える構成をとることも可能である。上記構成であっても、第2の実施形態の変形例に係るスイッチは、図1に示す第1の実施形態に係るスイッチ100と同等以上の効果を奏することができる。

【0054】

以上、添付図面を参照しながら本発明の好適な実施形態について説明したが、本発明は係る例に限定されないことは言うまでもない。当業者であれば、特許請求の範囲に記載された範疇内において、各種の変更例または修正例に想到し得ることは明らかであり、それらについても当然に本発明の技術的範囲に属するものと了解される。

【0055】

例えば、本発明の実施形態に係るスイッチは、図1に示すスイッチ100、図3に示すスイッチ200(変形例に係るスイッチも含む)の等価回路で構成されていてもよい。

【符号の説明】

【0056】

100、200 スイッチ

102、202 第1スイッチング部

104、204 第2スイッチング部

【特許請求の範囲】

【請求項1】

高周波信号が入力される入力端子と、前記入力端子に入力された前記高周波信号が出力される第1出力端子との間に接続され、前記入力端子に入力される高周波信号を、選択的に前記第1出力端子から出力させる第1スイッチング部と、

前記入力端子と、前記入力端子に入力された前記高周波信号が出力される第2出力端子との間に接続され、前記入力端子に入力される高周波信号を、選択的に前記第2出力端子から出力させる第2スイッチング部と、

を備え、

前記第1スイッチング部は、

前記入力端子と前記第1出力端子との間の第1信号線上に設けられる、インピーダンスの変換を行う第1インピーダンス変成器と、

エミッタが接地され、コレクタが前記第1信号線に接続され、前記第1スイッチング部におけるスイッチング動作を制御する第1制御電圧に応じた電流がベースに印加される、第1バイポーラトランジスタと、

コレクタが接地され、エミッタが前記第1信号線に接続され、前記第1制御電圧に応じた電流がベースに印加される、第2バイポーラトランジスタと、

を備え、

前記第2スイッチング部は、

前記入力端子と前記第2出力端子との間の第2信号線上に設けられる、インピーダンスの変換を行う第2インピーダンス変成器と、

エミッタが接地され、コレクタが前記第2信号線に接続され、前記第2スイッチング部におけるスイッチング動作を制御する第2制御電圧に応じた電流がベースに印加される、第3バイポーラトランジスタと、

コレクタが接地され、エミッタが前記第2信号線に接続され、前記第2制御電圧に応じた電流がベースに印加される、第4バイポーラトランジスタと、

を備えることを特徴とする、スイッチ。

【請求項2】

前記第1スイッチング部は、前記第2バイポーラトランジスタのベースに一端が接続され、他端が接地されるキャパシタをさらに備える、請求項1に記載のスイッチ。

【請求項3】

前記第2スイッチング部は、前記第4バイポーラトランジスタのベースに一端が接続され、他端が接地されるキャパシタをさらに備える、請求項1、または2に記載のスイッチ。

【請求項1】

高周波信号が入力される入力端子と、前記入力端子に入力された前記高周波信号が出力される第1出力端子との間に接続され、前記入力端子に入力される高周波信号を、選択的に前記第1出力端子から出力させる第1スイッチング部と、

前記入力端子と、前記入力端子に入力された前記高周波信号が出力される第2出力端子との間に接続され、前記入力端子に入力される高周波信号を、選択的に前記第2出力端子から出力させる第2スイッチング部と、

を備え、

前記第1スイッチング部は、

前記入力端子と前記第1出力端子との間の第1信号線上に設けられる、インピーダンスの変換を行う第1インピーダンス変成器と、

エミッタが接地され、コレクタが前記第1信号線に接続され、前記第1スイッチング部におけるスイッチング動作を制御する第1制御電圧に応じた電流がベースに印加される、第1バイポーラトランジスタと、

コレクタが接地され、エミッタが前記第1信号線に接続され、前記第1制御電圧に応じた電流がベースに印加される、第2バイポーラトランジスタと、

を備え、

前記第2スイッチング部は、

前記入力端子と前記第2出力端子との間の第2信号線上に設けられる、インピーダンスの変換を行う第2インピーダンス変成器と、

エミッタが接地され、コレクタが前記第2信号線に接続され、前記第2スイッチング部におけるスイッチング動作を制御する第2制御電圧に応じた電流がベースに印加される、第3バイポーラトランジスタと、

コレクタが接地され、エミッタが前記第2信号線に接続され、前記第2制御電圧に応じた電流がベースに印加される、第4バイポーラトランジスタと、

を備えることを特徴とする、スイッチ。

【請求項2】

前記第1スイッチング部は、前記第2バイポーラトランジスタのベースに一端が接続され、他端が接地されるキャパシタをさらに備える、請求項1に記載のスイッチ。

【請求項3】

前記第2スイッチング部は、前記第4バイポーラトランジスタのベースに一端が接続され、他端が接地されるキャパシタをさらに備える、請求項1、または2に記載のスイッチ。

【図1】

【図2A】

【図2B】

【図3】

【図4A】

【図4B】

【図2A】

【図2B】

【図3】

【図4A】

【図4B】

【公開番号】特開2013−98800(P2013−98800A)

【公開日】平成25年5月20日(2013.5.20)

【国際特許分類】

【出願番号】特願2011−240564(P2011−240564)

【出願日】平成23年11月1日(2011.11.1)

【出願人】(594023722)サムソン エレクトロ−メカニックス カンパニーリミテッド. (1,585)

【Fターム(参考)】

【公開日】平成25年5月20日(2013.5.20)

【国際特許分類】

【出願日】平成23年11月1日(2011.11.1)

【出願人】(594023722)サムソン エレクトロ−メカニックス カンパニーリミテッド. (1,585)

【Fターム(参考)】

[ Back to top ]