スタティックランダムアクセスメモリ

【課題】第1の導電型の共通ウェルが形成された半導体基板と、前記半導体基板上の前記共通ウェルに行列状に配列されたメモリセルよりなり、列方向に整列して共通のビット線に接続される一群のメモリセルがメモリセルカラムを形成するメモリセルアレイからなるスタティックランダムアクセスメモリにおいて、隣接カラム群間のソフトエラーの伝搬を抑制する。

【解決手段】隣接する第1および第2のカラム群において、前記第1のカラム群CG1で選択される一のメモリセルカラムの第1導電型ウェルPW(01)と、第2カラム群CG2で同時に選択されるメモリセルカラムの第1導電型ウェルPW(05)は、いずれか一方が、共通ウェル11から、第2導電型の深いウェルDNW1により遮断されており、前記第2導電型の深いウェルDNW1は、行方向に測った場合の一つのカラム群の寸法を超えない寸法を有する。

【解決手段】隣接する第1および第2のカラム群において、前記第1のカラム群CG1で選択される一のメモリセルカラムの第1導電型ウェルPW(01)と、第2カラム群CG2で同時に選択されるメモリセルカラムの第1導電型ウェルPW(05)は、いずれか一方が、共通ウェル11から、第2導電型の深いウェルDNW1により遮断されており、前記第2導電型の深いウェルDNW1は、行方向に測った場合の一つのカラム群の寸法を超えない寸法を有する。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は一般に半導体装置に係り、特にスタティックランダムアクセスメモリを含む半導体記憶装置に関する。

【背景技術】

【0002】

スタティックランダムアクセスメモリ(以下SRAMと記す)は、ワード線により選択されるトランスファトランジスタと、かかるトランスファトランジスタを介してビット線に接続される、フリップフロップ接続された二つのCMOSインバータとよりなる高速半導体記憶素子であり、高速論理回路素子においてCMOS回路など高速論理素子と共に広く使われている。

【先行技術文献】

【特許文献】

【0003】

【特許文献1】特開平11−17134号公報

【特許文献2】特開2000−48564公報

【発明の概要】

【発明が解決しようとする課題】

【0004】

一般にSRAMでは複数のメモリセルが、ワード線方向ないし行方向とビット線方向ないし列方向に配列されて二次元的なメモリセルアレイを構成するが、各々のメモリセルにおいては、前記二つのCMOSインバータを構成する二つのpチャネルMOSトランジスタが、前記メモリセルアレイ中を列方向に延在しているn型ウェル中に形成され、また前記二つのCMOSインバータを構成する二つのnチャネルMOSトランジスタと、前記トランスファトランジスタを構成する二つのnチャネルMOSトランジスタが、前記メモリセルアレイ中を、前記n型ウェルの両側に隣接して平行に延在している一対のp型ウェルの、半分ずつを使って形成される。

【0005】

前記メモリセルアレイ中のメモリセルは、列方向に整列して共通のビット線に接続された一群のメモリセルよりなるメモリセルカラムを複数束ねたカラム群を単位として組織化されており、前記複数のカラム群が行方向に繰り返されている。各々のカラム群には、アドレスデータの一部を供給されて特定のメモリセルカラムを選択するカラム選択回路が設けられている。

【0006】

またSRAMにはアドレスデータの一部を供給されて特定のワード線を選択するワード線選択回路が設けられており、特定のワード線を選択することにより、選択された特定のメモリセルカラム中の特定のメモリセルが選択され、選択されたメモリセルに対して1ビットのデータの書込あるいは読み出しが行われる。

【0007】

このような、メモリセルアレイをカラム群単位で組織化したSRAMでは、一つのカラム群に対して一回に1ビットのデータが読み出しあるいは書き込みされ、また複数のカラム群に対して複数ビットのデータが一度に読み出しあるいは書き込みされる。

【0008】

例えば4ビットのカラム群が64本あるメモリセルアレイでは、第1のカラム群の第1メモリセルカラム、第2のカラム群の第1メモリセルカラム、第3のカラム群の第1メモリセルカラム、・・・に対して一度に1ビットのデータの読み出しがなされ、結果として64ビットデータが一度に読み出される。

【0009】

ところで、このようなSRAMでは、時折外部からの放射線などにより、いわゆるソフトエラーが生じることがあり、例えば第1カラム群の第1メモリセルカラムの選択されたメモリセルにおいてデータの反転が生じる場合がある。

【0010】

このような場合、同じカラム群の他のメモリセルでも、前記放射線のエネルギによりデータが反転している可能性があるが、これら同じカラム群の他のメモリセルは選択されていないためSRAMとしての読み出しに影響はない。そこで、他のカラム群にまで前記放射線の影響が及んでいないとすると、読み出された64ビットデータ中においてエラーは1ビットだけということになる。このような場合、通常のECC(エラー検出および訂正)回路を使うことにより、そのエラーを訂正することができる。

【0011】

ところが本発明の発明者は、本発明の基礎となる研究において、最近の、非常に高集積化されたSRAMの場合、一つのカラム群において生じたソフトエラーの効果が、隣接するカラム群まで波及してしまい、例えば同時に選択される第1メモリセルカラムの第1ビットと第2メモリセルカラムの第2ビットなど、64ビットの読み出しデータ中に2ビットのエラーが含まれる場合が生じることを見出した。

【0012】

このような2ビットやさらに多ビットのエラーは、ECC回路において、より多くの冗長ビット(パリティビット)を設けてやれば対応することはできるが、それではSRAMの面積効率が低下してしまい、SRAMの費用が増大してしまう。

【課題を解決するための手段】

【0013】

一の側面によるランダムアクセスメモリは、第1の導電型の共通ウェルが形成された半導体基板と、前記半導体基板上の前記共通ウェルに行列状に配列されたメモリセルよりなり、列方向に整列して共通のビット線に接続される一群のメモリセルがメモリセルカラムを形成し、前記メモリセルカラムが複数束ねられて複数のカラム群が形成され、前記複数のカラム群が行方向に繰り返される構成のメモリセルアレイと、各々のカラム群に設けられ、アドレスデータの一部を供給されて特定のメモリセルカラムを選択するカラム選択回路と、を含み、前記メモリセルアレイ中には前記複数のメモリセルカラムの各々において、前記メモリセル中の、前記第1の導電型のソースおよびドレイン領域を有するMOSトランジスタのための、前記第1の導電型とは逆の第2導電型ウェルと、前記第2の導電型を有するソースおよびドレイン領域を有するMOSトランジスタのための前記第1の導電型の第1導電型ウェルとが、ビット線方向に、相互に隣接して延在しており、前記複数のカラム群の各々において前記複数のメモリセルカラムはそれぞれのビット線のビットに対応しており、隣接する第1および第2のカラム群において、前記第1のカラム群で選択される一のメモリセルカラムの第1導電型ウェルと、第2カラム群で同時に選択されるメモリセルカラムの第1導電型ウェルとは、いずれか一方が、前記共通ウェルから、第2導電型の深いウェルにより遮断されており、前記第2導電型の深いウェルは、行方向に測った場合の一つのカラム群の寸法を超えない寸法を有する。

【発明の効果】

【0014】

上記一の側面によれば、一のカラム群中の一のメモリセルカラムの第1導電型ウェルおいて放射線などによりソフトエラーが生起したとしても、その影響が隣接するカラム群中の同時に選択されるメモリセルカラムの第1導電型ウェルに伝搬するのを、第2導電型の深いウェルにより遮断でき、また、一のカラム群中の一のメモリセルカラムの第2導電型ウェルおいて放射線などによりソフトエラーが生起したとしても、その影響が隣接するカラム群中の同時に選択されるメモリセルカラムの第2導電型ウェルに、第2導電型の深いウェルを介して伝搬するのを、前記第2導電型の深いウェルを行方向に、一つのカラム群に相当する寸法を超えないように形成することで、遮断することができ、スタティックランダムアクセスメモリのソフトエラー耐性が向上する。

【図面の簡単な説明】

【0015】

【図1】第1の実施形態によるSRAMを示す等価回路図である。

【図2A】図1に対応する1メモリセルを示す平面図である。

【図2B】図2A中、線A−A’に沿った断面図である。

【図2C】図2A中、線B−B’に沿った断面図である。

【図3】第1の実施形態によるSRAMのメモリセルアレイを示す平面図である。

【図4】図3の平面図において、下部のn型ウェルおよびp型ウェルの配列を示した図である。

【図5】第1の実施形態によるSRAMの電気的構成を示した図である。

【図6A】図5の構成におけるエラー検出および訂正回路の原理を説明する第1の図である。

【図6B】図5の構成におけるエラー検出および訂正回路の原理を説明する第2の図である。

【図7】一般的なソフトエラーを説明する図である。

【図8A】図4中、線C−C’に沿った断面図である。

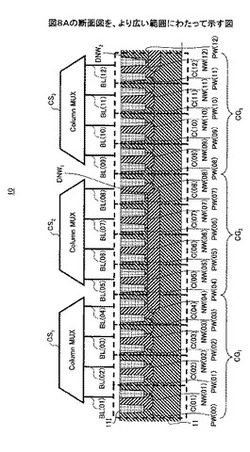

【図8B】図8Aの断面図を、より広い範囲にわたって示す図である。

【図8C】図8Bの一変形例を示す図である。

【図9A】第1の実施形態の比較対照例における問題を説明する断面図である。

【図9B】第1の実施形態の別の比較対照例における問題を説明する断面図である。

【図10】図9Aの比較対照例における問題発生のメカニズムを説明する断面図である。

【図11】第1の実施形態で使われるカラム選択回路の構成を示す回路図である。

【図12】図11の回路図で使われる真理値表の例を示す図である。

【図13】第1の実施形態における深いn型ウェルの行方向への寸法とカラム群の行方向への寸法との関係を示す平面図である。

【図14】第1の実施形態の別の変形例を示す平面図である。

【図15】第2の実施形態によるSRAMを示す平面図である。

【図16】図15中、線D−D’に沿った断面図である。

【図17】第3の実施形態によるSRAMの構成を示す平面図である。

【図18】図17の線E−E’に沿った断面図である。

【図19】第3の実施形態におけるメモリセルカラムの選択を説明するブロック図である。

【図20A】第4の実施形態におけるメモリセルカラムの選択を説明するブロック図である。

【図20B】第4の実施形態によるSRAMの構成を示す断面図である。

【図21A】第5の実施形態におけるメモリセルカラムの選択を説明するブロック図である。

【図21B】第5の実施形態によるSRAMの構成を示す断面図である。

【図21C】第5の実施形態の一変形例を示すブロック図である。

【図22A】第6の実施形態を示すブロック図である。

【図22B】第6の実施形態の一変形例を示すブロック図である。

【図23】第7の実施形態を示すブロック図である。

【図24】第8の実施形態を示す断面図である。

【図25】第8の実施形態の一例を示す断面図である。

【図26】第8の実施形態の選択回路における様々なビット線選択の例を示す図である。

【発明を実施するための形態】

【0016】

[第1の実施形態]

図1は、第1の実施形態によるSRAM10の1メモリセル分の等価回路図を示す。

【0017】

図1を参照するに、前記SRAM10はpチャネルMOSトランジスタよりなる第1のロードトランジスタLT1とnチャネルMOSトランジスタよりなる第1のドライバトランジスタDT1を直列接続した第1のCMOSインバータI1と、pチャネルMOSトランジスタよりなる第2のロードトランジスタLT2とnチャネルMOSトランジスタよりなる第2のドライバトランジスタLD2を直列接続した第2のCMOSインバータI2とよりなるフリップフロップ回路FFを含み、前記第1のロードトランジスタLT1と第1のドライバトランジスタDT1を接続する接続ノードN1は、nチャネルMOSトランジスタよりなりワードラインWLにより制御される第1のトランスファトランジスタTF1を介して第1のビットラインBLに接続される。同様に、前記第2のロードトランジスタLT2と第1のドライバトランジスタDT2を接続する接続ノードN2は、nチャネルMOSトランジスタよりなりワードラインWLにより制御される第2のトランスファトランジスタTF2を介して、前記第1のビットラインの相補的ビットライン/BLに接続される。

【0018】

図2Aは、図1のSRAM10の、1メモリセル分のレイアウト10Lを示す平面図、図2Bおよび図2Cは図2A中、線A−A’およびB−B’に沿った断面図である。

【0019】

図2Aを参照するに、前記SRAM10はSTI型の素子分離領域11Iが形成されたp型シリコン基板11上に形成されており、前記素子分離領域11Iには、前記p型シリコン基板11上をビット線方向BL、すなわち列方向に連続的に、かつ相互に平行に、かつ離間して延在する第1および第2のn型活性領域11A1,11A2が画成されている。また前記素子分離領域11Iには前記第1および第2のn型活性領域11A1,11A2の間に、ビット線方向BLに限られた距離だけ互いに平行に延在する第3および第4のp型活性領域11B1,11B2が、前記p型活性領域11B1が前記n型活性領域11A1と前記p型活性領域11B2の間に位置するように、さらに前記p型活性領域11B2が前記n型活性領域11A2と前記p型活性領域11B1の間に位置するように、画成されている。

【0020】

図2A中、破線は一つのメモリセルの境界を示すが、前記活性領域11A1上にはかかるメモリセルの境界の一方の交点の近傍に、第1の電源電圧Vssを供給される電源コンタクトV1が、また他方の交点にビット線BLに接続されるビットラインコンタクトV2が形成されている。また前記活性領域11A2上には前記電源コンタクトV1に対して点対称な位置に、前記電源電圧Vssを供給される電源コンタクトV3が、また前記ビットラインコンタクトV2に対して点対称な位置に、前記ビット線BLに対し相補的なビット線/BLに接続されるビットラインコンタクトV4が形成されている。ただし前記ビアコンタクトV1は、前記活性領域11A1から左方に延在する延在部11a1に形成され、左隣のメモリセルと共有されている。同様に前記ビアコンタクトV3は、前記活性領域11A2から右方に延在する延在部11a2に形成され、右隣のメモリセルと共有されている。

【0021】

さらに前記活性領域11B1には、前記メモリセルの境界との交点に対応して、第2の電源電圧Vddを供給される電源コンタクトV5が形成されており、また前記活性流域11B2には、前記電源コンタクトV5に対して点対称な位置に前記電源電圧Vddを供給される電源コンタクトV6が形成されている。

【0022】

前記活性領域11A1上には、前記電源コンタクトV1とビット線コンタクトV2の間に図1のドライバトランジスタDT1とトランスファトランジスタTF1とが順次形成されており、前記ドライバトランジスタDT1のゲート電極G1が、前記活性領域11B1を横切ってワード線方向、すなわち行方向に前記活性領域11B2に向かって延在し、前記活性領域11B2の端にビアコンタクトV7において接続されている。その際、前記活性領域11B1とゲート電極G1の交点には、前記ロードトランジスタLT1が形成される。

【0023】

同様に前記活性領域11A2上には、前記電源コンタクトV3とビット線コンタクトV4の間に図1のドライバトランジスタDT2とトランスファトランジスタTF2とが順次形成されており、前記ドライバトランジスタDT2のゲート電極G2が、前記活性領域11B2を横切ってワード線方向、すなわち行方向に前記活性領域11B1に向かって延在し、前記活性領域11B1の端にビアコンタクトV8において接続されている。その際、前記活性領域11B2とゲート電極G2の交点には、前記ロードトランジスタLT2が形成される。

【0024】

さらに前記活性領域11A1と活性領域11B1とは、前記トランジスタDT1とTF1の間のビアコンタクトV9を、前記活性領域11B1のうち前記トランジスタLT1に対して前記電源コンタクトV5とは反対の側に前記ビアコンタクトV8と並んで形成されるビアコンタクトV10に、前記ノードN1に対応する局所配線パタ―ンW1により接続され、これにより前記ロートトランジスタLT1とドライバトランジスタDT1とが、電源電圧Vddが供給される電源コンタクトV5と電源電圧Vssが供給される電源コンタクトV1との間で直列に接続される。

【0025】

同様に前記活性領域11A2と活性領域11B2とは、前記トランジスタDT2とTF2の間のビアコンタクトV11を、前記活性領域11B2のうち前記トランジスタLT2に対して前記電源コンタクトV6とは反対の側に前記ビアコンタクトV7と並んで形成されるビアコンタクトV12に、前記ノードN2に対応する局所配線パタ―ンW2により接続され、これにより前記ロートトランジスタLT2とドライバトランジスタDT2とが、電源電圧Vddが供給される電源コンタクトV6と電源電圧Vssが供給される電源コンタクトV3との間で直列に接続される。

【0026】

さらに前記トランスファトランジスタTF1のゲート電極G3がワート線方向WL,すなわち行方向上、前記活性領域11B1とは反対の方向に延在し、前記メモリセルの境界においてワート線WLとワード線コンタクトV13において接続される。また前記トランスファトランジスタTF2のゲート電極G4がワート線方向WL,すなわち行方向上、前記活性領域11B2とは反対の方向に延在し、前記メモリセルの境界においてワート線WLとワード線コンタクトV14において接続される。

【0027】

図1の等価回路図においてロードトランジスタLT1とLT2はpチャネルMOSトランジスタであり、シリコン基板11中のn型ウェルに形成されているのに対し、ドライバトランジスタDT1,DT2およびトランスファトランジスタTF1,TF2はnチャネルMOSトランジスタであり、シリコン基板11中のp型ウェルに形成されているのに注意すべきである。

【0028】

なお図2A中、白抜きで示したビアコンタクトV7〜V12は前記ゲート電極G1〜G3に対応する配線層をそれぞれの活性領域に接続するビアコンタクトを示しており、黒で示したビアコンタクトV1〜V6,V13,V14はより上層の、すなわちワードラインWL,ビットラインBLが形成される配線層への接続のためのビアコンタクトを示す。前記局所配線パタ―ンW1は、前記活性領域11A1,11B1上に直接に形成してもよい。同様に局所配線パタ―ンW2は、前記活性領域11A2,11B2上に直接に形成してもよい。

【0029】

図2Bは、前記SRAM10のうち、前記線A−A’に沿った断面図を示す。

【0030】

図2Bを参照するに、図2Bの断面では前記p型シリコン基板11の上部にp型ウェル11PWが形成されており、前記p型シリコン基板11上には前記ドライバトランジスタDT1のゲート電極G1がゲート絶縁膜Gox1を介して形成されている。また前記p型ウェル11PW中には前記ゲート電極G1の左右に、n型のソース領域11aおよびn型のドレイン領域11bが形成されている。また同様に前記p型シリコン基板11上には前記トランスファトランジスタTF1のゲート電極G3が、ゲート絶縁膜Gox3を介して形成されており、前記p型ウェル11PW中には前記ゲート電極G3の左右に、n型のソース領域11cおよびn型のドレイン領域11dが形成されている。ここでドレイン領域11bとソース領域11cとは連続した一つのn型拡散領域により形成されている。

【0031】

さらに前記ゲート電極G1とゲート電極G3の間には、前記ゲート電極G1の側壁絶縁膜SW1およびゲート電極G3の側壁絶縁膜SW2を部分的に覆って局所配線パタ―ンW1が、前記ドレイン領域11bおよびソース領域11cに電気的にコンタクトして形成されている。

【0032】

さらに前記シリコン基板11上には層間絶縁膜12が、前記ゲート電極G1およびG3を覆って形成されており、前記層間絶縁膜12には電源電圧Vssを供給する配線パタ―ン13Aにコンタクトして、前記ビアコンタクトV1を構成するビアプラグ12Aが、またビット線BLを構成する配線パタ―ン13Bにコンタクトして前記ビアコンタクトV13を構成するビアプラグ12Bが、それぞれ形成されている。

【0033】

図2Cは、前記SRAM10のうち、前記線B−B’に沿った断面図を示す。

【0034】

図2Cを参照するに、線B−B’に沿った断面では前記p型シリコン基板11の上部にn型ウェル11NWが形成されており、前記ロードトランジスタLT1がかかるn型ウェルNWに形成されている。

【0035】

より具体的には図2Cの断面では図2Bのゲート電極G1がゲート絶縁膜Gox1共々延在してロードトランジスタLT1のゲート電極を構成し、前記n型ウェル11NW中には前記ゲート電極G1の左右に、p型のソース領域11eおよびp型のドレイン領域11fが形成されている。

【0036】

また図2Cの断面では素子分離絶縁膜11I上に前記ロードトランジスタLT2のゲート電極G2となるポリシリコンパタ―ンがその下のゲート絶縁膜Gox2共々延在しており、前記局所配線パタ―ンW1が前記図2Bの断面から連続して延在し、前記p型ドレイン領域11fにコンタクトする。これにより前記n型ソースおよびドレイン領域11b,11cがp型ソース領域11fに電気的に接続される。

【0037】

さらに図2Cの断面では前記ゲート電極G1およびポリシリコンパタ―ンG2は前記層間絶縁膜12により同様に覆われ、前記層間絶縁膜12には、前記ビアコンタクトV10およびV8に対応して共通のビアプラグ12Vが形成され、ビアプラグ12Vは前記局所配線パタ―ンW1を、前記ポリシリコンパタ―ンG2に電気的に接続する。

【0038】

また前記層間絶縁膜12上には電源電圧Vddを供給される配線パタ―ン13Cが形成されており、前記配線パタ―ン13Cが前記層間絶縁膜12中に形成されたビアコンタクトV5に対応するビアプラグ12Cにより、前記p型ソース領域11eに電気的に接続される。

【0039】

その他のトランジスタDT2,TF2およびLT2も同様な断面構造を有しており、説明は省略する。

【0040】

さらに前記シリコン基板11上には層間絶縁膜12が、前記ゲート電極G1を覆って形成されており、前記層間絶縁膜12には電源電圧Vddを供給する配線パタ―ン13Cにコンタクトして、前記ビアコンタクトV5を構成するビアプラグ12Cが形成されている。

【0041】

図3は、図2A〜図2Cのメモリセル10Lを行列状に繰り返し形成したSRAM10のメモリセルアレイを示す平面図である。

【0042】

図3を参照するに、破線で示した図2A〜図2Cのメモリセル10Lが、上下左右を反転させながら、素子分離領域11Iにより表面に活性領域が形成されたシリコン基板11上に繰り返し形成されているのがわかる。また活性領域11A1および11A2が複数のメモリセルに共通に、ビットライン方向BLに延在し、活性領域11B1および11B2はいずれも行方向ないしワード線方向WLに2メモリセル分の長さないし寸法を有し、前記ビットライン方向に互い違いに繰り返されているのがわかる。

【0043】

図4は図3の平面図において、素子分離絶縁膜11Iを除去し、その下のシリコン基板11中のp型ウェルPW(00),PW(01),PW(02),PW(03)・・・およびn型ウェルNW(01),NW(02),NW(03)・・・を露出させた図である。ここで前記p型ウェルPW(00),PW(01),PW(02),PW(03)・・・は、図2Bにおけるp型ウェル11PWに対応し、n型ウェルNW(01),NW(02),NW(03)・・・は、図2Cにおけるn型ウェル11NWに対応する。

【0044】

図4を参照するに、図2A〜図2Cのメモリセル10Lでは、pチャネルMOSトランジスタよりなるロートトランジスタLT1およびLT2に対応して、前記活性領域11B1および11B2はシリコン基板11中のn型ウェルNW(02)に形成されており、一方nチャネルMOSトランジスタよりなるトランスファトランジスタTF1およびドライバトランジスタDT1に対応して前記活性領域11A1が、シリコン基板11中のp型ウェルPW(01)に形成されており、さらにnチャネルMOSトランジスタよりなるトランスファトランジスタTF2およびドライバトランジスタDT2に対応して前記活性領域11A2が、シリコン基板11中のp型ウェルPW(02)に形成されている。

【0045】

各々のウェルはビット線方向BLに連続して延在し、このようなp型ウェルとn型ウェルはワード線方向WLに向かって交互に繰り返し形成されている。

【0046】

なお前記p型ウェルPW(00)の左半分は、前記メモリセル10Lの左隣のメモリセルに共有されており、またp型ウェルPW(03)の右半分は、前記メモリセル10Lの右隣のメモリセルに共有されている。

【0047】

図5は、本実施形態によるSRAM10において、いわゆるソフトエラーの伝搬を回避するために使用するエラー訂正構成を示す。

【0048】

図5を参照するに、C(01)〜C(16)、D(01)〜D(16)は、図3,4で示したメモリセルアレイにおいて、ワード線WL(01)あるいはWL(02)で選択される一連のメモリセルを表す。

【0049】

本実施形態では、これらのメモリセルは、列方向に整列してそれぞれ共通のビット線BL(01),BL(02)・・・に接続された複数のメモリセルカラムMCC(01),MCC(02)・・・の形に組織化されており、そのうちの複数の、図示の例では4本の、メモリセルカラムが束ねられ、全体では、ワード線方向WLに繰り返される複数のカラム群CG1,CG2,CG3,CG4・・・が形成されている。例えばビット線BL(01)〜ビット線BL(04)に対応する4本のメモリセルカラムMCC(01)〜MCC(04)が一つのカラム群CG1を構成し、ビット線BL(05)〜ビット線BL(08)に対応する4本のメモリセルカラムMCC(05)〜MCC(08)が、隣接するカラム群CG2を構成し、ビット線BL(09)〜ビット線BL(12)に対応する4本のメモリセルカラムMCC(09)〜MCC(12)が、さらに隣接するカラム群CG3を構成し、ビット線BL(13)〜ビット線BL(16)に対応する4本のメモリセルカラムMCC(13)〜MCC(16)が、さらに隣接するカラム群CG4を構成する。なお図5においてビット線BL(0)〜BL(16)の各々は、先に図1で説明したビット線BLと相補的ビット線/BLとより構成されている。ビット線/BLの図示は省略している。

【0050】

さらに図5の構成では、これら複数のカラム群CG1,CG2,CG3,CG4・・・にそれぞれ対応して複数のカラム選択回路CS1,CS2,CS3,CS4・・・が設けられており、前記カラム選択回路CS1,CS2,CS3,CS4・・・は、対応するカラム群において一つのメモリセルカラムを選択し、当該メモリセルカラムに対応するビット線上に読み出された電圧信号を、それぞれ対応するセンスアンプSA1,SA2,SA3,SA3・・・に供給する。

【0051】

例えば先にワード線WL(01)によりメモリセルC(01),C(02),C(03)・・・C(16)が選択されている場合に、カラム選択回路CS1がビット線BL(01)に対応したメモリセルカラムMCC(01)を、カラム選択回路CS2がビット線BL(05)に対応したメモリセルカラムMCC(05)を、カラム選択回路CS3がビット線BL(09)に対応したメモリセルカラムMCC(09)を、カラム選択回路CS4がビット線BL(13)に対応したメモリセルカラムMCC(13)を選択したとすると、当該ビット線上に読み出されたメモリセルC(01),C(05),C(09),C(13)の論理状態を表す電圧信号が、前記カラム選択回路CS1,CS2,CS3,CS4を介して対応するセンスアンプSA1,SA2,SA3,SA4にそれぞれ供給される。

【0052】

センスアンプSA1,SA2,SA3,SA4は、通常通り、供給された電圧信号から、それぞれのメモリセルの論理状態を判定することで、情報を読み出す。

【0053】

図5の構成では、このようにして読み出されたメモリセルのデータはエラー検出および訂正回路(ECCロジック)ECCに供給され、図6A、図6Bに示すようにビット線方向およびワード線方向のパリティチェックを行うことにより、ソフトエラーの検出および訂正がなされる。

【0054】

図6A,図6Bは前記エラー検出および訂正回路ECCの原理を示す図である。なお図6AはSRAMのメモリセルアレイ中にエラーの無い場合を、図6Bは8行8列のメモリセルアレイ範囲に1ビットのエラーが存在する場合を示す。

【0055】

図6Aを参照するに、図示の例では各々4ビットのサイズの第1〜第8までのカラム群にそれぞれ対応してカラム選択回路CS1〜CS8が形成されており、それぞれのカラム選択回路においてビット線BL(04),BL(08),BL(12)・・・BL(32)が同時に選択されている。

【0056】

さらにECCロジックではワード線毎にパリティビットAが設けられ、一つのワード線上で選択された8個のメモリセルの読み出し値の合計が、パリティビットAを合わせて偶数になるように構成されている。

【0057】

またECCロジックではビット線毎にパリティビットBが設けられ、一つのビット線上で連続して選択された8個のメモリセルの読み出し値の合計が、パリティビットBを合わせて偶数になるように構成されている。

【0058】

そこでワード線WL(01)〜WL(08)およびパリティビットBの各々について、ビット線BL(04),BL(08),BL(12)・・・BL(32)およびパリティビットAを選択してデータを読み出すことにより、図6Aあるいは図6Bに示すような読み出し値のマトリクスが得られる。

【0059】

エラーがない図6Aの場合には、一つのワード線上で選択されたメモリセルの読み出し値の合計が、パリティビットAを合わせて偶数になっており、また一つのビット線上で選択されたメモリセルの読み出し値の合計が、パリティビットBを合わせて偶数になっている様子がわかる。

【0060】

一方、例えばワード線WL(01)とビット線BL(04)で選択されるメモリセルにエラーがあり、データ値が反転している図6Bの場合、ワード線WL(01)で選択されるメモリセルのデータの合計が、パリティビットAを合わせても奇数となり、このワード線WL(0)上のメモリセルのいずれかにエラーが存在することが検出される。またビット線BL(01)で選択されるメモリセルのデータの合計が、パリティビットBを合わせても奇数となり、このビット線BL(04)上のメモリセルのいずれかにエラーが存在することが検出される。このことから、エラーが生じているのはワード線WL(01)およびビット線BL(04)で選択されるメモリセルであることが確定し、そのデータ「0」を「1」に訂正することでエラーの訂正が行われる。

【0061】

このようなSRAM10においては、ときおり外部放射線などの影響により、ソフトエラーが発生することがあり、先の図5のエラー検出および訂正回路ECCは、このようなソフトエラーの検出および訂正のために使われる。

【0062】

図7は、一般的なpチャネルMOSトランジスタにおけるソフトエラーの概要を説明する図である。

【0063】

図7を参照するに、シリコン基板101上には素子分離領域101Iにより素子領域101Aが形成されており、前記素子領域101Aに対応して前記シリコン基板101中にはn型ウェル101Nが形成されている。また前記シリコン基板101中には、前記n型ウェル101Nを電気的に分離するため、p型ウェル101Pが形成されている。前記p型ウェル101Pはシリコン基板101自身であることが多い。

【0064】

前記シリコン基板101上には、前記素子領域101Aにおいて図示を省略したゲート絶縁膜を介してポリシリコンなどのゲート電極103が形成されており、さらに前記素子領域101Aのうち、前記ゲート電極103の一方の側、図示の例では左側にp型のソース101a領域が、また他方の側にはp型のドレイン領域101bが形成されている。

【0065】

さて前記ソース領域101aに電源電圧Vddを印加し、前記ドレイン領域101bを他のトランジスタ、例えばnチャネルMOSトランジスタ104により接地した前記pチャネルMOSトランジスタの動作状態において図7中に矢印で示すようにα線などの荷電粒子が素子領域101Aを構成するn型ウェル101Nに侵入した場合を考えると、前記n型ウェル101N中において電子−正孔対が前記荷電粒子のエネルギにより励起されるが、励起された電子−正孔対のうち正孔はドレイン領域101bからnチャネルMOSトランジスタ104を介して接地へと逃がされ、前記n型ウェル101N中に電子のみが残留してしまう状況が発生することがある。

【0066】

このようにnウェル101N中に電子のみが残るとその電位が低下し、その結果、n型ウェル101N,p型ソース領域101aおよびp型ドレイン領域101bよりなる寄生バイポーラトランジスタが導通してしまい、ドレイン電流がソース領域101aからドレイン領域101bへと流れる場合がある。

【0067】

このような寄生バイポーラトランジスタの導通が、先のメモリセル10Lにおいて、例えばpチャネルMOSトランジスタLT1あるいはLT2において生じると、フリップフロップFFは状態を反転させてしまい、メモリセル10Lに保持されているデータは反転してしまう。

【0068】

同様な荷電粒子により保持データの反転は、図1のドライバトランジスタLT1あるいはLT2を構成するnチャネルMOSトランジスタにおいても発生しうる。

【0069】

図8Aおよび図8Bは、前記図4における線C−C’に沿ったSRAM10の断面図を示す。図中、先に説明した部分に対応する部分には同一の参照符号を付し、説明を省略する。図8Bは図8Aと同じ構造を、より広い範囲にわたり示した断面図である。なお図8A,図8Bにおいて、シリコン基板11上に形成されるそれぞれのトランジスタのゲート電極などの図示は、簡単のため省略している。

【0070】

図8Aを参照するに、メモリセルC(01)〜C(06)は先の図5のメモリセルC(01)〜C(06)にそれぞれ対応しており、またカラム選択回路CS1,CS2は図6のカラム選択回路CS1,CS2にそれぞれ対応する。なお、より広い範囲を示した図8Bでは、さらにカラム選択回路CS3およびこれに対応するビット線BL(09)〜BL(12)、さらに前記ビット線に接続されるメモリセルカラムに対応したカラム群CG3が示されている。

【0071】

図8Aを参照するに、前記シリコン基板11中には、前記nチャネルMOSトランジスタDT1,TF1あるいはDT2,TF2のためのp型ウェルPW(01)〜PW(05)と前記pチャネルMOSトランジスタLT1.LT2のためのn型ウェルNW(01)〜NW(06)とが交互に繰り返し形成されており、またカラム選択回路CS2に対応するカラム群に含まれるメモリセルカラムでは、それぞれのp型ウェル、すなわちPW(04),PW(05),PW(06)・・・の下に、深いn型ウェルDNW1が形成されているのがわかる。

【0072】

前記カラム選択回路CS2に対応するカラム群の下にこのような深いn型ウェルを形成することにより、カラム選択回路CS1に対応するカラム群のp型ウェル、例えばp型ウェルPW(01)、に荷電粒子などが入来した場合でも、その影響がp型ウェルPW(04)やPW(05)に伝搬するのが、シリコン基板11と前記深いn型ウェルDNWの間のpn接合により遮断される。

【0073】

その際、本実施形態による構成では、図8Bに示すように、前記深いn型ウェルDNW1,DNW2・・・を行方向ないしワード線方向WLに、一つのカラム群に相当する長さないし寸法を超えないように形成する。また本実施形態による構成では、前記p型ウェルPW(00),PW(02)・・・の下に連続して深いn型ウェルを形成し、これに、奇数番目のカラム群CG1,CG3,CG5・・・に対応して行方向ないしワード線方向WLに、一つのカラム群に対応する長さないし寸法で切れ目を繰り返し形成すると見てもよい。ただし図8A,図8Bの構成において、各々のウェルPW(00)〜PW(12),NW(01)〜NW(11),DNW1およびDNW2は、いずれもビット線方向BLに同じ長さだけ延在するため、図面中で横方向の長さないし寸法は、それぞれのウェルの面積に対応している。

【0074】

より具体的には、前記深いn型ウェルDNW1は、図8Bのより広範囲にわたる断面図に示すように実質一つのカラム群に相当する面積に等しく形成されているため、前記カラム選択回路CS2のカラム群の下からカラム選択回路CS1のカラム群の下まで、全面にわたり連続して延在することがない。また深いn型ウェルDNW1とその隣の深いn型ウェルDNW2の間の切れ目も、実質一つのカラム群の面積に等しく形成されている。

【0075】

このため、例えばメモリセルC(01)のn型ウェルNW(01)が、前記深いn型ウェルDNW1を介して同時に選択されるメモリセルC(05)のn型ウェルNW(05)に電気的に接続されることがなく、n型ウェルNW(01)に入来した荷電粒子の影響がn型ウェルNW(04)やNW(05)に及ぶことが回避される。

【0076】

また、例えばメモリセルC(01)のp型ウェルPW(01)が、同時に選択されるメモリセルC(05)のp型ウェルPW(05)に電気的に接続されることがなく、p型ウェルPW(01)に入来した荷電粒子の影響がp型ウェルPW(05)に及ぶことが回避される。

【0077】

これに対し図9Aに示す比較例のように深いn型ウェルDNWを全く形成しなかった場合には、前記p型ウェルPW(01)に生じた荷電粒子入来の影響は、図10に示すようなメカニズムにより、同じカラム群のp型ウェルPW(02),PW(03)のみならず、隣接するカラム群のp型ウェルPW(04)、PW(05)などにも及ぶおそれがある。

【0078】

図10を参照するに、p型ウェルPW(01)において荷電粒子により電子−正孔対が発生し、正孔のみが残った場合、この正孔が前記p型のシリコン基板11を介してp型ウェルPW(04)に到達すると、その電位を上げるように作用し、前記p型ウェルPW(04)に形成されていたnチャネルMOSトランジスタよりなるドライバトランジスタDT1あるいはDT2の寄生バイポーラトランジスタが導通するおそれがある。このような導通が生じると、当該SRAMのメモリセルに保持されているデータは反転してしまう。

【0079】

また図9Bに示す別の比較例のように前記深いn型ウェルDNWを、隣接する二つのカラム群のn型ウェルおよびp型ウェルの下に連続して形成した場合には、例えばn型ウェルNW(01)に荷電粒子が入来してソフトエラーが発生すると、その影響が隣接するカラム群のn型ウェル、例えばNW(05)やNW(06)にまで及び、これらのn型ウェルに形成されているpチャネルMOSトランジスタよりなるロードトランジスタLT1あるいはLT2を導通させ、当該メモリセルに保持されているデータを反転させてしまうおそれがある。

【0080】

このようにソフトエラーが隣接する二つのカラム群で発生すると、図5および図6A,図6Bで説明したエラー検出および訂正回路ECCにおいて2ビットのエラー訂正を行う必要があるが、このような2ビットのエラー訂正はSRAMの面積効率を低下させるため望ましくない。

【0081】

本実施形態によれば、隣接する第1のカラム群と第2のカラム群のいずれか一方に前記深いウェルを行方向ないしワード線方向WLに、一つのカラム群の長さないし寸法を超えないように形成することにより、隣接するカラム群の間でp型ウェルどうし、あるいはn型ウェルどうしの導通を遮断することが可能となり、隣接する二つのカラム群で同時に選択されるメモリセルカラムの一方でソフトエラーが発生しても、それが他方に伝搬することがない。このため本実施形態によれば、このような場合でも1ビットのエラー検出および訂正回路ECCを使ってエラーを訂正することが可能となる。

【0082】

なおこのような荷電粒子の入射が一のカラム群の一のメモリセルで発生しても、同じカラム群中の他のメモリセルはカラム選択回路CS1〜CS3により選択されていないため、データの読み出しに影響は生じない。これら他のメモリセルにおいて生じたエラーは、それが選択された時点で、図5のエラー検出および訂正回路ECCにより訂正することができる。

【0083】

本実施形態は、特に前記活性領域11A1,11A2,11B1,11B2が45nm以下の設計ルールで形成される微細化されたSRAMにおいて有用である。

【0084】

なおこのような構成では、例えばカラム群CG1のメモリセルC(01)p型ウェルあるいはn型ウェルが、隣のカラム群CG2を超えたもう一つとなりのカラム群CG3のメモリセルC(09)の対応するp型ウェルあるいはn型ウェル導通するのは避けられないが、例えばメモリセルC(09)はメモリセルC(01)から、1カラム群に相当する距離だけ離れているため、メモリセルC(09)がメモリセルC(01)と同時に選択されても、本実施形態において想定するようにSRAMの微細化が進んでも、メモリセルC(09)においてソフトエラーが発生するおそれはない。

【0085】

なお本実施形態において前記深いn型ウェルDNW1,DNW2・・・を、図8Cに示すようにそれぞれの端が対応するカラム群の端に一致するように形成することも可能である。

【0086】

図11は、前記図8A〜図8Cのカラム選択回路CS1の構成を示す回路図である。なおカラム選択回路CS2,CS3の構成はカラム選択回路CS1のものと同じであり、説明を省略する。

【0087】

図11を参照するに、カラム選択回路CS1はビット線BL01,/BL01,/BL02,/BL02,BL03,/BL03,BL04,/BL04を共通ビット線VBLおよび/VBLに接続するトランジスタTr0,/Tr0,Tr1,/Tr1,Tr2,/Tr2,Tr3,/Tr3を含み、アドレスデータの一部、例えばアドレスデータA0,A1を供給されるカラムデコーダCDECより対応する選択信号E0〜E3をそれぞれラインD0〜D1上に供給され、ラインD0上の選択信号E0がハイである場合にビット線BL01および/BL01を、それぞれトランジスタT0および/T0および共通ビット線VBLおよび/VBLを介してセンスアンプSA1に供給する。同様に前記カラム選択回路CS1は、ラインD1上の選択信号E1がハイである場合にビット線BL02および/BL02を、それぞれトランジスタT1および/T1および共通ビット線VBLおよび/VBLを介してセンスアンプSA1に供給し、ラインD2上の選択信号E2がハイである場合にビット線BL03および/BL03を、それぞれトランジスタT2および/T2および共通ビット線VBLおよび/VBLを介してセンスアンプSA1に供給し、さらにラインD3上の選択信号E3がハイである場合にビット線BL04および/BL04を、それぞれトランジスタT3および/T3および共通ビット線VBLおよび/VBLを介してセンスアンプSA1に供給する。

【0088】

また前記カラムデコーダは、一方の入力端子にアドレスデータA0を供給され他方の入力端子にアドレスデータA1を供給されるAND回路AND1と、一方の入力端子に前記アドレスデータA0を、インバータINV0を介して供給され他方の入力端子に前記アドレスデータA1を供給されるAND回路AND2と、一方の入力端子に前記アドレスデータA0を供給され他方の入力端子に前記アドレスデータを、インバータINV1を介して供給されるAND回路AND3と、一方の入力端子に前記アドレスデータA0を、前記インバータINV0を介して供給され他方の入力端子に前記アドレスデータを、インバータINV1を介して供給されるAND回路AND4と、を含み、前記入力データA0およびA1の組み合わせにより図12の真理値表に示すような選択信号E0〜E4を形成する。

【0089】

かかる構成により、カラム選択回路CS1により、入来するアドレスデータA0,A1の組み合わせに従って、4本のビット線BL01〜BL04の一つ、従ってこれに対応するメモリセルカラムを選択することが可能である。

【0090】

本実施形態において、例えばメモリセルC(01)においてソフトエラーが発生した場合、同じカラム群に属するメモリセルC(02)〜C(04)においても同様なソフトエラーが発生するおそれがあるが、これらのメモリセルは上記カラム選択回路CS1の作用により非選択であり、読み出しデータにエラーが含まれることはない。またこれらのメモリセルが選択される場合は、ビット線BL(01)に対応するメモリセルカラムの場合と同様に、エラー検出および訂正回路ECCを使ってエラーを訂正することができる。

【0091】

なお図11において前記ビット線BL01,BL02,BL03,BL04は、図5におけるビット線BL(01),BL(02),BL(03).BL(04)にそれぞれ対応する。

【0092】

図13は、本実施形態における前記深いn型ウェルDNWの行方向ないしワード線方向WLへの寸法とカラム群の行方向ないしワード線方向WLへの寸法との関係を示す平面図である。ただし図13はビット線BL(01)〜BL(12)までを示しており、これに対応してカラム選択回路CS1,CS2,CS3が示されている。図5に合わせて図13においても、カラム選択回路CS1に対応するビット線B(01)〜BL(04)までのカラム群をCG1,カラム選択回路CS2に対応するビット線B(05)〜BL(08)までのカラム群をCG2、カラム選択回路CS3に対応するビット線B(09)〜BL(12)までのカラム群をCG3と記す。

【0093】

図13を参照するに、図8A,図8Bの深いn型ウェルDNW1は太枠で囲んだようにカラム群CG2に対応して、かつ一つのカラム群に等しい面積、ないし行方向への寸法で形成されているため、例えばメモリセルC05を構成するp型ウェルは、同時に選択されるメモリセルC01あるいはC09のp型ウェルに対し、前記深いn型ウェルDNWにより分離されている。

【0094】

また前記深いn型ウェルDNWの面積ないし行方向への寸法が一つのカラム群の面積ないし行方向への寸法を超えることがないため、例えばメモリセルC09のn型ウェルが、同時に選択されるメモリセルC05のn型ウェルに、前記深いn型ウェルDNWを介して導通することもない。

【0095】

先にも説明したように、図13などの平面図において、各p型ウェルおよびn型ウェルのビット線方向の寸法は同一であるので、図中に示した行方向すなわちワード線方向へのブラケットの長さは、対応するカラム群あるいはウェルDNWの面積に対応している。

【0096】

なお上記の説明より、前記深いn型ウェルDNWは、その行方向への寸法が一つのカラム群の行方向への寸法を超えない限り、必ずしもいずれかのカラム群、図13の例ではカラム群CG2に一致して設ける必要はなく、図14の変形例に示すように任意にずらして設けることが可能であることは明らかである。

【0097】

ただし図13の本実施形態においても、また図14の変形例においても、一つの深いn型ウェルDNW1と、その隣の深いn型ウェルDNW2とは、一つのカラム群に対応する距離を超えないように、従って行方向に一つのカラム群を超える寸法の空白を生じないように配置される。

【0098】

なお本実施形態の場合、図8BよりわかるようにメモリセルカラムCG1の端に位置するメモリセルC(04)の一方のp型ウェルPW(03)に荷電粒子が入射した場合、前記p型ウェルPW(03)に生じた電位の変動が前記p型シリコン基板11を介して同時に選択されるメモリセルC(08)のp型ウェルPW(08)に影響し、ソフトエラーが例外的に伝搬するおそれがある。またメモリセルC(04)を構成するn型ウェルNW(04)に荷電粒子が入射した場合、当該ウェルに生じた電位の変動が前記深いn型ウェルDNW1を介して、同時に選択されるメモリセルC(08)のn型ウェルNW(08)に影響し、同様な例外的なソフトエラーの伝搬が生じるおそれがある。同様なソフトエラーの例外的な伝搬は、図8Cの実施形態においても生じうる。

【0099】

しかし、それ以外のウェルにおける荷電粒子の入来の影響は、本実施形態においては遮断されており、SRAM10は、図9Aや図9Bに示すような、深いn型ウェルDNWを一切形成しない構成や、メモリセルアレイの下に連続して形成する構成に比べると、ソフトエラー耐性が格段に向上している。

【0100】

このような例外的なソフトエラーの伝搬経路をも遮断できる構成については、以下の実施形態で説明する。

【0101】

[第2の実施形態]

図15および図16は、第2の実施形態によるSRAM20の構成を示す、それぞれ平面図および断面図である。ただし図中、先に説明した部分に対応する部分には同一の参照符号を付し、説明を省略する。図16の断面図は、図15中、線D−D’に沿った断面を示している。図16においても、前記図8A〜8Cと同様に、シリコン基板11上のゲート電極などについては、図示を省略する。

【0102】

図15,図16を参照するに、本実施形態ではカラム選択回路CS2、すなわちビット線BL(05)〜BL(08)に対応するカラム群CG2において、それぞれのp型ウェルの下に限定して、一つのp型ウェルだけをカバーする幅で深いn型ウェルDNW1,DNW2,DNW3,DNW4を、相互に分離して形成している。

【0103】

かかる構成によれば、一つおきに形成されたカラム群CG2,CG4・・・において、それぞれのp型ウェル、例えばPW(04)、PW(05),PW(06)・・・がp型シリコン基板11から、前記深いn型ウェルDNW1,DNW2,DNW3,DNW4のいずれかにより分離され、かつこれらの深いn型ウェルDNW1,DNW2,DNW3,DNW4も、相互に分離されているため、先に図9A,図9Bで説明したような、p型シリコン基板11や深いn型ウェルDNWを介したソフトエラーの伝搬の問題は生じない。

【0104】

先の実施形態の場合、先に図8Bや図8Cで説明したように例外的にソフトエラーの伝搬を許してしまう場合があるが、本実施形態ではこのような例外的なソフトエラーの伝搬経路をも遮断することができる。

【0105】

なおこのような相互に分離した深いn型ウェルDNW1,DNW2,DNW3,DNW4は、一つおきのカラム群CG2,CG4・・・に限定されず、全てのカラム群CG1,CGG2,CG3・・・に、すなわちメモリセルアレイ全体にわたって形成してもよい。

【0106】

[第3の実施形態]

図17および図18は第3の実施形態によるSRAM30の構成を示す。ただし図17および図18中、先に説明した部分には同一の参照符号を付し、説明を省略する。図18においても、前記図8A〜8Cと同様に、シリコン基板11上のゲート電極などについては、図示を省略する。

【0107】

図17,図18を参照するに、本実施形態では各々行方向に、一つのカラム群から1セルカラム分の寸法を差し引いた、3セルカラム分の寸法を有する深いn型ウェルDNW1〜DNW3が、それぞれのカラム群CG1,CG2,CG3に対応して、かつ1メモリセル分の間隔を開けて形成されている。さらに本実施形態ではカラム選択回路CS2が、ビット線BL(05)が選択される際に、メモリセルC(06)を含むメモリセルカラムが選択されるように、またビット線BL(06)が選択される際にメモリセルC(05)を含むメモリセルカラムが選択されるように、構成されている。

【0108】

一方、カラム選択回路CS1およびカラム選択回路CS3では、前記カラム選択回路CS2においてビット線BL(05)が選択される場合に、それぞれビット線BL(01)およびビット線BL(09)が選択され、これにより、メモリセルC(01)を含むメモリセルカラムおよびメモリセルC(09)を含むメモリセルカラムが選択されるように構成されている。

【0109】

このようにカラム選択回路CS1〜CS3を構成することにより、図18においてメモリセルC(01)が選択された場合、同時に選択されるメモリセルC(06)のp型ウェルは、前記深いn型ウェルDNW2によりp型シリコン基板11から完全に分離され、メモリセルC(01)とC(06)の間においてソフトエラーの伝搬は生じない。また図18においてメモリセルC(02)が選択された場合、同時にメモリセルC(05)が選択されるが、メモリC(02)においてp型ウェルは前記深いn型ウェルDNW1により前記p型シリコン基板11から完全に分離されており、やはりメモリセルC(02)とC(05)の間にソフトエラーの伝搬は生じない。尚、本実施形態において、深いn型ウェルDNW1〜DNW3は、各々行方向に一つのカラム群から2セルカラム分の寸法を差し引いた2セルカラム分の寸法以上の幅を有する必要がある。

【0110】

図19は、前記SRAM30の構成を、カラム選択回路CS4および対応するカラム群CG4まで含めて示すブロック図である。

【0111】

図19を参照するに、カラム選択回路CS1〜CS4にはカラム群CG1〜CG4がそれぞれ対応し、カラム選択回路CS2から始めて一つおきに現れるカラム選択回路に、すなわちカラム選択回路CS2,CS4・・・において、ビット線の選択の際に、最初のビット線と次のビット線とが入れ替えられており、また最後のビット線とその一つ前のビット線とが入れ替えられている。例えばカラム選択回路CS2では、ビット線BL(05)とBL(06)とが入れ替わり、ビット線BL(08)とビット線BL(07)とが入れ替わっている。またカラム選択回路CS4ではビット線BL(13)とビット線BL(14)とが入れ替わっており、またビット線BL(16)とビット線BL(15)が入れ替わっている。

【0112】

このような構成は、図18などの断面構造において、一つのメモリセルが一つのn型ウェルと、その両側の半分ずつ、二つのp型ウェルとにより形成されているために設けられている。例えばメモリセルC(01)は、n型ウェルNW(01)と、左隣のメモリセルと共有されているp型ウェルPW(00)、および右隣のメモリセルC(02)と共有されているp型ウェルP(01)とより構成されている。本実施形態では、深いn型ウェルの端部に形成されているメモリセルのうち、前記深いn型ウェルから見て外端部に位置するp型ウェル、例えばカラム群CG1の場合p型ウェルP(00)を含むメモリセルC(01)が選択される場合に、同時に選択される隣接カラム群CG2では対応するメモリセルC(05)を選択せず、当該カラム群CG2における深いn型ウェルDWN2から見て一つ内側のメモリセル、すなわちメモリセルC(06)を選択することで、このような外端部のp型ウェルPW(00)およびPW(04)どうしの導通を回避している。

【0113】

同様に本実施形態では、例えばカラム群CG1において深いn型ウェルDNW1から見て外端のp型ウェルPW(04)を含むメモリセルC(04)が選択される場合に、同時に選択される隣接カラム群CG2では対応するメモリセルC(08)を選択せず、当該カラム群CG2における深いn型ウェルDWN2から見て一つ内側のメモリセル、すなわちメモリセルC(07)を選択することで、このような外端部のp型ウェルPW(04)およびPW(08)どうしの導通を回避している。

【0114】

その結果、前記カラム選択回路CS2あるいはCS4においては、ビット線BL(05)はメモリセルC(06)を含むメモリセルカラムMCC(06)に接続されビット線BL(06)はメモリセルC(05)を含むメモリセルカラムMC(05)に接続される。またビット線BL(08)はメモリセルC(07)を含むメモリセルカラムMCC(07)に接続されビット線BL(07)はメモリセルC(08)を含むメモリセルカラムMCC(08)に接続される。さらにビット線BL(13)はメモリセルC(14)を含むメモリセルカラムMCC(14)に接続されビット線BL(14)はメモリセルC(13)を含むメモリセルカラムMC(13)に接続される。またビット線BL(16)はメモリセルC(15)を含むメモリセルカラムMCC(15)に接続されビット線BL(15)はメモリセルC(16)を含むメモリセルカラムMCC(16)に接続される。

【0115】

これに対しカラム選択回路CS1においては、ビット線BL(01)がメモリセルC(01)を含むメモリセルカラムMCC(01)に接続され、ビット線BL(02)がメモリセルC(02)を含むメモリセルカラムMC(02)に接続され、ビット線BL(03)がメモリセルC(03)を含むメモリセルカラムMCC(03)に接続されビット線BL(04)がメモリセルC(04)を含むメモリセルカラムMCC(04)に接続されるのがわかる。またメモリカラム選択回路CS3については、ビット線BL(09)がメモリセルC(09)を含むメモリセルカラムMCC(09)に接続され、ビット線BL(10)がメモリセルC(10)を含むメモリセルカラムMC(10)に接続され、ビット線BL(11)がメモリセルC(11)を含むメモリセルカラムMCC(11)に接続され、ビット線BL(12)がメモリセルC(12)を含むメモリセルカラムMCC(12)に接続される。

【0116】

本実施形態ではカラム群CG1においてメモリセルC(01)を含むメモリセルカラムMCC(01)がカラム選択回路CS1により選択される際、隣のカラム群CG2においてはメモリセルC(06)を含むメモリセルカラムMCC(06)が選択される。さらに隣のカラム群CG3においてはメモリセルC(09)を含むメモリセルカラムMCC(09)が選択される一方、そのさらに隣のカラム群CG4においては、メモリセルC(14)を含むカラム群MCC(14)が選択される。

【0117】

この場合、メモリセルC(06)を構成するp型ウェルおよびn型ウェルはそのどちらも、メモリセルC(01)を構成する型ウェルおよびn型ウェル、あるいはメモリセルC(09)を構成するp型ウェルおよびn型ウェルから前記深いn型ウェルDNW2により分離されており、いずれかのメモリセルで生じた荷電粒子の入射が他のメモリセルに影響することはない。

【0118】

同様にカラム群CG1においてメモリセルC(02)を含むメモリセルカラムMCC(02)がカラム選択回路CS1により選択される際、隣のカラム群CG2においてはメモリセルC(05)を含むメモリセルカラムMCC(05)が選択される。さらに隣のカラム群CG3においてはメモリセルC(10)を含むメモリセルカラムMCC(10)が選択される一方、そのさらに隣のカラム群CG4においては、メモリセルC(13)を含むカラム群MCC(13)が選択される。

【0119】

この場合、メモリセルC(05)を構成するp型ウェルおよびn型ウェルはどちらも、メモリセルC(02)を構成するp型ウェルおよびn型ウェル、あるいはメモリセルC(13)を構成するp型ウェルおよびn型ウェルから前記深いn型ウェルDNW1あるいはDNW3により分離されており、いずれかのメモリセルで生じた荷電粒子の入射が他のメモリセルに影響することはない。

【0120】

同様にカラム群CG1においてメモリセルC(03)を含むメモリセルカラムMCC(03)がカラム選択回路CS1により選択される際、隣のカラム群CG2においてはメモリセルC(08)を含むメモリセルカラムMCC(08)が選択される。さらに隣のカラム群CG3においてはメモリセルC(11)を含むメモリセルカラムMCC(11)が選択される一方、そのさらに隣のカラム群CG4においては、メモリセルC(16)を含むカラム群MCC(16)が選択される。

【0121】

この場合、メモリセルC(08)を構成するp型ウェルおよびn型ウェルはどちらも、メモリセルC(03)を構成するp型ウェルおよびn型ウェル、あるいはメモリセルC(11)を構成するp型ウェルおよびn型ウェルから、前記深いn型ウェルDNW1,DNW2,DNW3により分離されており、いずれかのメモリセルで生じた荷電粒子の入射が他のメモリセルに影響することはない。

【0122】

同様にカラム群CG1においてメモリセルC(04)を含むメモリセルカラムMCC(04)がカラム選択回路CS1により選択される際、隣のカラム群CG2においてはメモリセルC(07)を含むメモリセルカラムMCC(07)が選択される。さらに隣のカラム群CG3においてはメモリセルC(12)を含むメモリセルカラムMCC(12)が選択される一方、そのさらに隣のカラム群CG4においては、メモリセルC(15)を含むカラム群MCC(15)が選択される。

【0123】

この場合、メモリセルC(07)を構成するp型ウェルおよびn型ウェルはどちらも、メモリセルC(04)を構成するp型ウェルおよびn型ウェル、あるいはメモリセルC(112)を構成するp型ウェルおよびn型ウェルから、前記深いn型ウェルDNW1,DNW2,DNW3により分離されており、いずれかのメモリセルで生じた荷電粒子の入射が他のメモリセルに影響することはない。

【0124】

このように本実施形態のSRAM30では、p型シリコン基板11を介したソフトエラーの伝搬路が深いn型ウェルDNW1,DNW2・・・により完全に遮断され、また前記深いn型ウェルDNW1,DNW2・・・を介したソフトエラーの伝搬路も完全に遮断され、ソフトエラーに対する耐性が、第1の実施形態の場合と比較すると、さらに向上する。

【0125】

なお図19において、メモリセルカラムMCC(01)〜MCC(16)は、図3や図4に示すメモリセルアレイの一部を示している。

【0126】

また図18の断面図よりわかるように、本実施形態では一つの深いn型ウェル、例えばDNW1と、これに隣接する深いn型ウェルDNW2との間に、メモリセル一つ分の寸法の切れ目が存在しており、前記深いn型ウェルDNW1〜DNW3をイオン注入により形成する際に課せられる精度上の制約が緩和され、第2の実施形態と比較してSRAMを含む半導体装置の製造歩留まりを向上させることができる。

【0127】

[第4の実施形態]

図20A,図20Bは、前記第3の実施形態によるカラム選択回路構成をさらに変形した第4の実施形態によるSRAM40の構成を示す。ただし図20Aは前記図19と同様なメモリセルカラム選択のための回路図を示し、図20Bは本実施形態において使われる深いn型ウェルDNW1,DNW2を示す断面図である。図20Bの断面図においても、前記図8A〜8Cと同様に、シリコン基板11上のゲート電極などについては、図示を省略する。

【0128】

ここで図20Bは先の第3の実施形態の断面図と同じであるが、簡単のためシリコン基板11、p型ウェルPW(00)〜PW(16)、n型ウェルNW(01)〜NW(16)、および深いn型ウェルDNW1,DNW2、およびメモリセルC(01)〜C(16)のみを、模式化して示している。素子分離構造11Iの図示は省略している。

【0129】

図20Aを参照するに、本実施形態ではカラム群CG1においてメモリセルC(01)を含むメモリセルカラムMCC(01)がカラム選択回路CS1により選択される際、隣のカラム群CG2においてはメモリセルC(07)を含むメモリセルカラムMCC(07)が選択される。さらに隣のカラム群CG3においてはメモリセルC(09)を含むメモリセルカラムMCC(09)が選択される一方、そのさらに隣のカラム群CG4においては、メモリセルC(15)を含むカラム群MCC(15)が選択される。

【0130】

この場合、メモリセルC(07)を構成するp型ウェルおよびn型ウェルはどちらも、メモリセルC(01)を構成する型ウェルおよびn型ウェル、あるいはメモリセルC(15)を構成するp型ウェルおよびn型ウェルから前記深いn型ウェルDNW1,DNW2,DNW3により分離されており、いずれかのメモリセルで生じた荷電粒子の入射が他のメモリセルに影響することはない。

【0131】

同様にカラム群CG1においてメモリセルC(02)を含むメモリセルカラムMCC(02)がカラム選択回路CS1により選択される際、隣のカラム群CG2においてはメモリセルC(05)を含むメモリセルカラムMCC(05)が選択される。さらに隣のカラム群CG3においてはメモリセルC(09)を含むメモリセルカラムMCC(09)が選択される一方、そのさらに隣のカラム群CG4においては、メモリセルC(13)を含むカラム群MCC(13)が選択される。

【0132】

この場合、メモリセルC(05)を構成するp型ウェルおよびn型ウェルはどちらも、メモリセルC(02)を構成するp型ウェルおよびn型ウェル、あるいはメモリセルC(13)を構成するp型ウェルおよびn型ウェルから前記深いn型ウェルDNW1,DNW2,DNW3により分離されており、いずれかのメモリセルで生じた荷電粒子の入射が他のメモリセルに影響することはない。

【0133】

同様にカラム群CG1においてメモリセルC(03)を含むメモリセルカラムMCC(03)がカラム選択回路CS1により選択される際、隣のカラム群CG2においてはメモリセルC(08)を含むメモリセルカラムMCC(08)が選択される。さらに隣のカラム群CG3においてはメモリセルC(11)を含むメモリセルカラムMCC(11)が選択される一方、そのさらに隣のカラム群CG4においては、メモリセルC(16)を含むカラム群MCC(16)が選択される。

【0134】

この場合、メモリセルC(08)を構成するp型ウェルおよびn型ウェルはどちらも、メモリセルC(03)を構成するp型ウェルおよびn型ウェル、あるいはメモリセルC(11)を構成するp型ウェルおよびn型ウェルから、前記深いn型ウェルDNW1,DNW2,DNW3により分離されており、いずれかのメモリセルで生じた荷電粒子の入射が他のメモリセルに影響することはない。

【0135】

同様にカラム群CG1においてメモリセルC(04)を含むメモリセルカラムMCC(04)がカラム選択回路CS1により選択される際、隣のカラム群CG2においてはメモリセルC(06)を含むメモリセルカラムMCC(06)が選択される。さらに隣のカラム群CG3においてはメモリセルC(12)を含むメモリセルカラムMCC(12)が選択される一方、そのさらに隣のカラム群CG4においては、メモリセルC(14)を含むカラム群MCC(14)が選択される。

【0136】

この場合、メモリセルC(06)を構成するp型ウェルおよびn型ウェルはどちらも、メモリセルC(04)を構成するp型ウェルおよびn型ウェル、あるいはメモリセルC(112)を構成するp型ウェルおよびn型ウェルから、前記深いn型ウェルDNW1,DNW2,DNW3により分離されており、いずれかのメモリセルで生じた荷電粒子の入射が他のメモリセルに影響することはない。

【0137】

このように本実施形態のSRAM40でも、p型シリコン基板11を介したソフトエラーの伝搬路が深いn型ウェルDNW1,DNW2・・・により完全に遮断され、また前記深いn型ウェルDNW1,DNW2・・・を介したソフトエラーの伝搬路も完全に遮断され、ソフトエラーに対する耐性が、第1の実施形態の場合と比較すると、さらに向上する。

【0138】

また図20Bの断面図よりわかるように、本実施形態では一つの深いn型ウェル、例えばDNW1と、これに隣接する深いn型ウェルDNW2との間に、メモリセル一つ分の切れ目が存在しており、前記深いn型ウェルDNW1〜DNW3をイオン注入により形成する際に課せられる精度上の制約が緩和され、第2の実施形態と比較してSRAMを含む半導体装置の製造歩留まりを向上させることができる。

【0139】

[第5の実施形態]

図21A,図21Bは第5の実施形態によるSRAM50の構成を示す。ただし図21Aは前記図19と同様なメモリセルカラム選択のための回路図を示し、図21Bは本実施形態において使われる深いn型ウェルDNW1〜DNW5を示す断面図である。図21Bの断面図においても、前記図8A〜8Cと同様に、シリコン基板11上のゲート電極などについては、図示を省略する。

【0140】

最初に図21Bの断面図を参照するに、本実施形態においても各々の深いn型ウェルDNW1〜DNW5は行方向に3セル分の寸法を有し、1メモリセル分の間隔を開けて形成されており、ただ図20Bの断面図と比較すると、各々のカラム群に対して深いn型ウェルDNW1〜DNW5の位置関係が、2メモリセル分だけワード線方向にずらされているのがわかる。

【0141】

本実施形態では、図21Aに示すように、先の図19と同じカラム選択構成が使われており、カラム選択回路CS2から始めて一つおきに現れるカラム選択回路に、すなわちカラム選択回路CS2,CS4・・・において、ビット線の選択の際に、最初のビット線と次のビット線とが入れ替えられており、また最後のビット線とその一つ前のビット線とが入れ替えられている。例えばカラム選択回路CS2では、ビット線BL(05)とBL(06)とが入れ替わり、ビット線BL(08)とビット線BL(07)とが入れ替わっている。またカラム選択回路CS4ではビット線BL(13)とビット線BL(14)とが入れ替わっており、またビット線BL(16)とビット線BL(15)が入れ替わっている。

【0142】

そこでカラム群CG1においてメモリセルC(01)を含むメモリセルカラムMCC(01)がカラム選択回路CS1により選択される際、隣のカラム群CG2においてはメモリセルC(06)を含むメモリセルカラムMCC(06)が選択される。さらに隣のカラム群CG3においてはメモリセルC(09)を含むメモリセルカラムMCC(09)が選択される一方、そのさらに隣のカラム群CG4においては、メモリセルC(14)を含むカラム群MCC(14)が選択される。

【0143】

この場合、メモリセルC(06)を構成するp型ウェルおよびn型ウェルはそのどちらも、メモリセルC(01)を構成する型ウェルおよびn型ウェル、あるいはメモリセルC(09)を構成するp型ウェルおよびn型ウェルから前記深いn型ウェルDNW2により分離されており、いずれかのメモリセルで生じた荷電粒子の入射が他のメモリセルに影響することはない。

【0144】

同様にカラム群CG1においてメモリセルC(02)を含むメモリセルカラムMCC(02)がカラム選択回路CS1により選択される際、隣のカラム群CG2においてはメモリセルC(05)を含むメモリセルカラムMCC(05)が選択される。さらに隣のカラム群CG3においてはメモリセルC(09)を含むメモリセルカラムMCC(09)が選択される一方、そのさらに隣のカラム群CG4においては、メモリセルC(13)を含むカラム群MCC(13)が選択される。

【0145】

この場合、メモリセルC(05)を構成するp型ウェルおよびn型ウェルはどちらも、メモリセルC(02)を構成するp型ウェルおよびn型ウェル、あるいはメモリセルC(13)を構成するp型ウェルおよびn型ウェルに対し、前記深いn型ウェルDNW1あるいはDNW3により分離されており、いずれかのメモリセルで生じた荷電粒子の入射が他のメモリセルに影響することはない。

【0146】

同様にカラム群CG1においてメモリセルC(03)を含むメモリセルカラムMCC(03)がカラム選択回路CS1により選択される際、隣のカラム群CG2においてはメモリセルC(08)を含むメモリセルカラムMCC(08)が選択される。さらに隣のカラム群CG3においてはメモリセルC(11)を含むメモリセルカラムMCC(11)が選択される一方、そのさらに隣のカラム群CG4においては、メモリセルC(16)を含むカラム群MCC(16)が選択される。

【0147】

この場合、メモリセルC(08)を構成するp型ウェルおよびn型ウェルはどちらも、メモリセルC(03)を構成するp型ウェルおよびn型ウェル、あるいはメモリセルC(11)を構成するp型ウェルおよびn型ウェルから、前記深いn型ウェルDNW1,DNW2,DNW3により分離されており、いずれかのメモリセルで生じた荷電粒子の入射が他のメモリセルに影響することはない。

【0148】

同様にカラム群CG1においてメモリセルC(04)を含むメモリセルカラムMCC(04)がカラム選択回路CS1により選択される際、隣のカラム群CG2においてはメモリセルC(07)を含むメモリセルカラムMCC(07)が選択される。さらに隣のカラム群CG3においてはメモリセルC(12)を含むメモリセルカラムMCC(12)が選択される一方、そのさらに隣のカラム群CG4においては、メモリセルC(15)を含むカラム群MCC(15)が選択される。

【0149】

この場合、メモリセルC(07)を構成するp型ウェルおよびn型ウェルはどちらも、メモリセルC(04)を構成するp型ウェルおよびn型ウェル、あるいはメモリセルC(112)を構成するp型ウェルおよびn型ウェルから、前記深いn型ウェルDNW2により分離されており、いずれかのメモリセルで生じた荷電粒子の入射が他のメモリセルに影響することはない。

【0150】

本実施形態のSRAM50でも、前記第3の実施形態の場合と同様に、p型シリコン基板11を介したソフトエラーの伝搬路が深いn型ウェルDNW1,DNW2・・・により完全に遮断され、また深いn型ウェルDNW1,DNW2・・・を介したソフトエラーの伝搬路も完全に遮断され、ソフトエラーに対する耐性が、第1の実施形態の場合と比較すると、さらに向上する。

【0151】

また図21Bの断面図よりわかるように、本実施形態でも一つの深いn型ウェル、例えばDNW1と、これに隣接する深いn型ウェルDNW2との間に、メモリセル一つ分の切れ目が存在しており、前記深いn型ウェルDNW1〜DNW3をイオン注入により形成する際に課せられる精度上の制約が緩和され、先に説明した第2の実施形態と比較してSRAMを含む半導体装置の製造歩留まりを向上させることができる。

【0152】

なお本実施形態において、カラム選択回路CS2,CS4によるメモリセルカラムの選択を、図21Cの本実施形態の一変形例によるSRAM50Aに示すように変形することも可能である。

【0153】

[第6の実施形態]

なお上記の説明では全ての実施形態において、一つのカラム群が四本のメモリセルカラムを含むものとしたが、上記の説明は、カラム群は多数のメモリセルカラムを含むものであって成立する。

【0154】

例えば図22Aは、前記図17,図18の構成において一つのカラム群が8本のメモリセルカラムを含み、カラムデコーダCDECが3ビットのアドレスデータA0,A1,A2により選択信号E0〜E7を発生し、8本のラインD0〜D8の一つに選択信号を供給することによりカラム選択回路CS1,CS2・・・を駆動する構成のSRAM60のブロック図を示す。図22Aの例では、例えばカラム群CG1が8本のメモリセルカラムMCC(01)〜MCC(08)を含み、またカラム群CG2が8本のメモリセルカラムMCC(09)〜MCC(08)を含む。また図22AのSRAM60では、各々のカラム群CG1,CG2,CG3,CG4・・・が行方向に8セル分の寸法を有し、これに対し深いn型ウェルDNW1〜DNW4が行方向に各々6セル分の寸法を有し、行方向に2セル分の寸法の間隔を隔てて繰り返し形成されている。ただし図22Aではカラム選択回路CS1,CS2およびカラム群CG1,CG2のみを示している。

【0155】

かかる構成でも、一つのカラム群、例えばカラム群CG1において深いn型ウェルDNW1の端に位置するメモリセルカラムMCC(01)が選択される場合、隣接するカラム群CG2の対応するメモリセルカラムMCC(09)を選択する代わりに、カラム群CG2の深いn型ウェルDNW2から見て一つ内側のメモリセルカラムMCC(10)を選択することで、最外端のp型ウェルどうしがp型シリコン基板11を介して導通しソフトエラーが伝搬する問題が解消される。

【0156】

なお、本実施形態のように一つのカラム群に4本を超えるメモリセルカラムが含まれ、またこれに対応してカラム選択回路も四本を超えるビット線を含む構成のSRAMでは、隣接するカラム群、例えばカラム群CG1とカラム群CG2において、それぞれの深いn型ウェルの端に位置するメモリセル、例えばメモリセルC(01)とC(09)どうしの導通を回避するのに、先の図22Aにおけるように、カラム群CG2に対応する深いn型ウェルDNW2の端から一つ内側のメモリセルカラムMCC(10)を前記メモリセルカラムMCC(09)の代わりに選択する以外に、図22Bの変形例60Aに示すように二つ内側のメモリセルカラムMCC(11)など、前記深いn型ウェルDNW2の両端から一本以上内側の、任意のメモリセルカラムを選択することも有効である。

【0157】

[第7の実施形態]

図23は、第7の実施形態によるSRAM70の構成を示すブロック図である。図中、先に説明した部分には対応する参照符号を付し、説明は省略する。

【0158】

図23を参照するに、第7の実施形態は先の第3の実施形態の一変形例になっており、ただカラム選択回路CS2においてビット線BL(05)が選択された場合にメモリセルカラムMCC(06)の代わりにメモリセルカラムMCC(05)が、またビット線BL(06)が選択された場合にメモリセルカラムMCC(05)の代わりにメモリセルカラムMCC(06)が選択され、またカラム選択回路CS4においてビット線BL(13)が選択された場合にメモリセルカラムMCC(14)の代わりにメモリセルカラム(13)が、またビット線BL(14)が選択された場合にメモリセルカラムMCC(13)の代わりにメモリセルカラムMC(14)が選択されるように構成されている。

【0159】

このようなメモリセルカラムの選択を行った場合には、先に図8B,図8Cで説明したのと同様な例外的なソフトエラーの伝搬が、メモリセルカラムMCC(01)とMCC(05)の間、あるいはメモリセルカラムMCC(04)とMCC(08)の間、メモリセルカラムMCC(09)とMCC(13)の間、さらにメモリセルカラムMCC(12)とMCC(16)の間において生じるのが阻止できないが、それ以外のメモリセルカラム相互間でのソフトエラーの伝搬は前記深いn型ウェルDNW1〜DNW4により阻止されており、SRAM70は、例えば図9Aや図9Bで説明した比較対照例に対し、格段に優れたソフトエラー耐性を有している。

【0160】

[第8の実施形態]

図24は、図4に示すメモリセルアレイにおいて一つまたは二つの深いn型ウェルをp型ウェルおよびn型ウェルの下に形成した様々な構成のカラム群を概念的に示す断面図である。

【0161】

図24中、「Macro_0」〜「Macro_17」は様々なカラム群のマクロを示しており、「MCC0」〜「MCC3」は、例えば図5のメモリセルカラムMCC(01)〜MCC(04),MCC(05)〜MCC(08),MCC(09)〜MCC(12),MCC(13)〜MCC(16)・・・のいずれかに、また「MC0」〜「MC3」は、メモリセルC(01)〜C(04),C(05)〜C(08),C(09)〜C(12),C(13)〜C(16)・・・に対応する。

【0162】

また図24中、「sub」はp型シリコン基板11に対応し、「PW」はp型ウェルPW(00)〜PW(04),PW(05)〜PW(08),PW(09)〜PW(12)・・・のいずれかに対応し、「NW」はn型ウェルNW(01)〜N(04),NW(05)〜(08),NW(09)〜NW(12)・・・のいずれかに対応し、「DNW」は深いn型ウェルDNW1,DNW2,DMW3・・・のいずれかに対応する。また図24中、破線はそれぞれのメモリセルに対応している。

【0163】

ここでMacro_0は、一つのカラム群に深いn型ウェルが全く含まれない構成を、Macro_17は、一つのカラム群全体にわたり、深いn型ウェルDNWが形成されている構成に対応する。

【0164】

Macro_1は、カラム群の左端から1メモリセル分だけ内側に入った位置に行方向に1メモリセルカラム分の寸法を有する深いn型ウェルDNWが、左端のメモリセルカラムMCC0とその右隣のメモリセルカラムMCC1の境に形成された構成に対応し、メモリセルカラムMCC0からMCC1にかけて、両者の境のp型ウェルを前記深いn型ウェルDNWにより前記p型シリコン基板11から完全に分離するように形成されている。

【0165】

Macro_2では、前記深いn型ウェルDNWの位置が、前記Macro_1に比べて1メモリセル分だけ右側に移動しており、前記n型ウェルDNWは、メモリセルカラムMCC1とMCC2にかけて、両者の境のp型ウェルを前記p型シリコン基板11から完全に分離するように形成されている。

【0166】

Macro_3では、前記深いn型ウェルDNWの位置が、前記Macro_2に比べて一つ右側に1メモリセル分だけ移動しており、前記n型ウェルDNWは、メモリセルカラムMCC2とMCC3にかけて、両者の境のp型ウェルを前記p型シリコン基板11から完全に分離するように形成されている。

【0167】

またMacro4では、前記深いn型ウェルDNWの位置が前記Macro_3に比べてさらに右側に1メモリセル分移動しており、その結果、前記深いn型ウェルDNWのうち半メモリセル分が、メモリセルカラムMCC3の左端に位置するp型半ウェルの下に形成され、これを前記p型シリコン基板11から分離すると同時に、当該カラム群の右端で残りの半メモリセル分が、メモリセルカラムMCC3の左端に位置するp型半ウェルの下に形成され、これを前記p型シリコン基板11から分離する。

【0168】

次にMacro_5では、前記深いn型ウェルDNWが行方向に2メモリセルカラム分の寸法を有し、メモリセルカラムMCC0の右半分からMCC1の全部、さらにメモリセルカラムMCC2の左半分にわたって形成されており、その結果、前記メモリセルカラムMCC0とメモリセルカラムMCC1の境のp型ウェルおよび前記メモリセルカラムMCC1とメモリセルカラムMCC2の境のp型ウェルとが、前記p型シリコン基板11から前記深いn型ウェルDNWにより完全に分離される。

【0169】

Macro_6では、前記深いn型ウェルが前記Macro_5に比べて右側に1メモリセル分移動して、メモリセルカラムMCC1の右半分からMCC2の全部、さらにメモリセルカラムMCC3の左半分にわたって形成されており、その結果、前記メモリセルカラムMC1とメモリセルカラムMC2の境のp型ウェル、および前記メモリセルカラムMC2とメモリセルカラムMC3の境のp型ウェルがp型シリコン基板11から前記深いn型ウェルDNWにより完全に分離される。

【0170】

Macro_7では、前記深いn型ウェルが前記Macro_6に比べて右側にさらに1メモリセル分移動して、メモリセルカラムMCC2の右半分からMCC3の全部、さらにメモリセルカラムMCC1の右半分にわたって形成されており、その結果、前記メモリセルカラムMC2とメモリセルカラムMC3の境のp型ウェル、および前記メモリセルカラムMC3右端およびメモリセルカラムMC0左端のp型ウェルが、前記深いn型ウェルDNWにより前記p型シリコン基板11から完全に分離される。

【0171】

Macro_8では、前記深いn型ウェルが前記Macro_7に比べて右側にさらに1メモリセル分移動して、メモリセルカラムMCC3の右半分からMCC0の全部、さらにメモリセルカラムMCC1の左半分にわたって形成されており、その結果、前記メモリセルカラムMCC3の右端のp型ウェルおよびメモリセルカラムMCC0の右端のp型ウェルが、かかるn型ウェルDNWにより前記p型シリコン基板11からに分離される。

【0172】

次にMacro_9では、前記深いn型ウェルDNWが行方向に3メモリセルカラム分の寸法を有し、メモリセルカラムMCC0の右半分からメモリセルカラムMCC1およびMCC2の全部、さらにメモリセルカラムMCC3の左半分にわたって形成されており、その結果、前記メモリセルカラムMCC0とMCC1との境のp型ウェル、メモリセルカラムMCC1とMCC2との境のp型ウェル、さらにMCC2とMCC3との境のp型ウェルが、前記p型シリコン基板11から前記深いn型ウェルにより完全に分離される。

【0173】

Macro_10では、前記深いn型ウェルDNWがMacro_9に比べて右側に2メモリセル分移動して、メモリセルカラムMCC2の右半分からMCC3の全部、さらにMCC0の全部およびメモリセルカラムMCC1の左半分にわたって形成されており、その結果、前記メモリセルカラムMC2とMCC3との境のp型ウェル、前記メモリセルカラムMCC3の右端のp型ウェル、さらにメモリセルカラムMCC0の左端のp型ウェルが、前記p型シリコン基板11から前記深いn型ウェルDNWにより完全に分離される。

【0174】

Macro_11では、前記深いn型ウェルDNWがMacro_10に比べて左側に1メモリセル分移動して、メモリセルカラムMCC0の左半分、およびメモリセルカラムMCC1の左半分からMCC2およびMCC3の全部にわたって形成されており、その結果、前記メモリセルカラムMCC0の左端のp型ウェル、および前記メモリセルカラムMC1とMCC2との境のp型ウェル、前記メモリセルカラムMCC2とMCC3の境のp型ウェル、および前記メモリセルカラムMCC3の右端のp型ウェルが、前記p型シリコン基板11から前記深いn型ウェルDNWにより完全に分離される。

【0175】

Macro_12では、前記深いn型ウェルDNWがMacro_10に比べて右側に1メモリセル分移動してメモリセルカラムMCC0およびMCC1の全部、MCC2の左半分、さらにメモリセルカラムMCC3の右半分にわたって形成されており、その結果、前記メモリセルカラムMCC0の左端のp型ウェル、および前記メモリセルカラムMC0とMCC1との境のp型ウェル、前記メモリセルカラムMCC1とMCC2の境のp型ウェル、およびメモリセルカラムMCC3の右端のp型ウェルが、前記p型シリコン基板11から前記深いn型ウェルDNWにより完全に分離される。

【0176】

Macro_13では、メモリセルカラムMCC0とMCC1の境、およびメモリセルカラムMCC2とMCC3の境に、それぞれ行方向に1メモリセルカラム分の寸法の深いn型ウェルDNWが、1メモリセルカラム分の間隔を開けて形成されており、それぞれの境に形成されているp型ウェルが、前記深いn型ウェルDNWにより、p型シリコン基板11から完全に分離される。

【0177】

Macro_14では、前記深いn型ウェルDNWがメモリセルカラムMCC1とMCC2の境に形成されており、メモリセルカラムMCC0の左半分およびメモリセルカラムMCC3の右半分にも形成されており、前記メモリセルカラムMCC1とMCC2の境に形成されたp型ウェル、および前記メモリセルカラムMCC0の左半分およびメモリセルカラムMCC3の右半分にそれぞれ形成されたp型ウェルが、前記深いn型ウェルDNWにより、p型シリコン基板から分離される。

【0178】

Macro_15は、前記Macro_14のうち、右端の深いn型ウェルDNWを省略した場合を、またMacro_16は、前記Macro_14のうち、左端の深いn型ウェルDNWを省略した場合を示す。

【0179】

これらのマクロを組み合わせることによりカラム群CG1,CG2,CG3,CG4・・・として様々な構成を有するSRAMを構成することができる。そのような場合でも、それぞれのカラム群に含まれるp型ウェルのいくつかは、その直下に形成された深いn型ウェルによりp型シリコン基板から分離されるため、このような構成のSRAMにおいては、必ずしも全てのソフトエラー伝搬経路を遮断することができなくても、当該p型ウェルに生じたソフトエラーの伝搬を阻止することができ、SRAMのソフトエラー耐性を向上させることができる。また本実施形態では深いn型ウェルが複数のカラム群にわたり連続して延在することがなく、かかる深いn型ウェルを伝搬して生じるソフトエラーについても、SRAMの耐性を向上させることができる。

【0180】

このようなマクロの組み合わせは、隣接する二つのカラム群について、18×18=324通り考えられるが、Macro_0とMacro_0を並べた構成は、先の図9Aの比較例に対応し、除去しなければならない。さらにMacro_17とMacro_17の組み合わせも、先の図9Bの構成と等しくなり、排除しなければならない。さらにMacro11の右隣にMacro12を配置した場合には、深いn型ウェルの行方向への寸法が1カラム群を超えるため、このような場合を排除すると、本実施形態で考え得るマクロの組み合わせは321通りになる。

【0181】

これらの組み合わせ全てについて説明はしないが、例えば任意にMacro_2とMacro11を組み合わせ、通常のカラム選択回路と同様に各カラム群CG1,CG2においてメモリセルカラムMCC0〜MCC3を順番に選択する構成とした場合、図25に示すように、例えばカラム選択回路CS1においてメモリセルカラムMCC2が選択された場合、カラム選択回路CS2においてもメモリセルカラムMCC2が選択されるが、カラム群CG2においてはメモリセルカラムMCC2を構成するp型ウェルはp型シリコン基板11から深いn型ウェルDNW3により分離されているため、一方のp型ウェルに生じた荷電粒子の影響が他方のp型ウェルに伝搬することはない。またカラム群CG2のメモリセルカラムMCC2においてn型ウェルに荷電粒子が入来したとしても、深いn型ウェルDNW3の行方向への寸法は3メモリセルカラム分を超えないため、これがカラム群CG1のメモリセルカラムMCG2のn型ウェルに伝搬することはない。

【0182】

このように図25の構成は、完全にソフトエラーの伝搬を阻止することはできないが、それでもSRAMのソフトウェア耐性の向上に効果的である。

【0183】

さらに例えば図25の実施形態において、各カラム選択回路毎に、ビット線BL0〜BL3とこれに対応して選択されるメモリセルカラムMCC0〜MCC3の組み合わせを任意に変化させても、メモリセルカラムMCC2およびMCC3においてp型ウェルが深いn型ウェルDNW3により分離される状況は変わらない。

【0184】

図26は、このようなビット線BL0〜BL3とこれに対応して選択されるメモリセルカラムMCC0〜MCC3の組み合わせを、一つのカラム群が4本のメモリセルカラムを含む場合について示したものである。

【0185】

図26を参照するに、この場合にはWIRE0〜WIRE23まで24通りの組み合わせがあり、従ってこの組み合わせを勘案すると、全部で321×24=7704通りの組み合わせが可能となる。

【0186】

このうち、先に図17〜図19で説明した実施形態は、図24におけるMacro_9を各カラム群CG1〜CG4で使い、これにカラムCG1およびCG3では図26のWIRE0の構成を、カラムCG2およびCG4では図26のWIRE7の構成を適用した場合に相当する。この場合には、先にも説明したように、あらゆる経路においてソフトエラーの伝搬を阻止することができる。

【0187】

また先の図20A,図20Bの実施形態は、図24におけるMacro_9を各カラム群CG1〜CG4で使い、これにカラムCG1およびCG3では図26のWIRE0の構成を、カラムCG2およびCG4では図26のWIRE10の構成を適用した場合に相当する。この場合にも、先にも説明したように、あらゆる経路においてソフトエラーの伝搬を阻止することができる。

【0188】

さらに先の図21A,図21Bの実施形態は、図24におけるMacro_10を各カラム群CG1〜CG4で使い、これにカラムCG1およびCG3では図26のWIRE0の構成を、カラムCG2およびCG4では図26のWIRE7の構成を適用した場合に相当する。この場合にも、先にも説明したように、あらゆる経路においてソフトエラーの伝搬を阻止することができる。

【0189】

また上記の説明は、p型とn型を入れ替えた場合であっても成立する。

【0190】

以上、本発明を好ましい実施形態について説明したが、本発明はかかる特定の実施形態に限定されるものではなく、特許請求の範囲に記載した要旨内において様々な変形・変更が可能である。

(付記1)

第1導電型の共通ウェルが形成された半導体基板と、

前記半導体基板上の前記共通ウェルに行列状に配列されたメモリセルよりなり、列方向に整列して共通のビット線に接続される一群のメモリセルがメモリセルカラムを形成し、前記メモリセルカラムが複数束ねられて複数のカラム群が形成され、前記複数のカラム群が行方向に繰り返される構成のメモリセルアレイと、

各々のカラム群に設けられ、アドレスデータの一部を供給されて特定のメモリセルカラムを順次選択するカラム選択回路と、を含み、

前記メモリセルアレイ中には前記複数のメモリセルカラムの各々において、前記メモリセル中の前記第1導電型のソースおよびドレイン領域を有するMOSトランジスタのための、前記第1導電型とは逆の第2導電型の第2導電型ウェルと、前記第2導電型のソースおよびドレイン領域を有するMOSトランジスタのための前記第1導電型の第1導電型ウェルとが、ビット線方向に、相互に隣接して延在しており、

隣接する第1および第2のカラム群において、前記第1のカラム群で選択される一のメモリセルカラムの前記第1導電型ウェルと、第2カラム群で同時に選択されるメモリセルカラムの前記第1導電型ウェルとは、いずれか一方が、前記第1導電型ウェルおよび第2導電型ウェルのいずれよりも深い第2導電型の深いウェルにより前記共通ウェルから遮断されており、

前記第2導電型の深いウェルは行方向に、一つのカラム群を超えない寸法を有することを特徴とするスタティックランダムアクセスメモリ。

(付記2)

さらに前記第2の導電型の深いウェルは、その隣の第2の導電型の深いウェルに対し、一つのカラム群の行方向への寸法を超えない間隔で、離間して形成されていることを特徴とする付記1記載のスタティックランダムアクセスメモリ。

(付記3)

前記第2の導電型の深いウェルは行方向に一つのカラム群に等しい寸法を有し、一の第2導電型の深いウェルと隣の第2導電型の深いウェルとは、行方向に一つのカラム群の寸法に等しい間隔で形成されていることを特徴とする付記1記載のスタティックランダムアクセスメモリ。

(付記4)

前記第1および第2のカラム群にまたがって形成されていることを特徴とする付記3記載のスタティックランダムアクセスメモリ。

(付記5)

前記第2の導電型の深いウェルは、それぞれの一端および他端を、前記対応するカラム群の一端および他端に一致させて形成されていることを特徴とする付記3記載のスタティックランダムアクセスメモリ。

(付記6)

前記第2の導電型の深いウェルは、一つおきに行方向に繰り返されるカラム群において、各々の第1の導電型のウェルの直下に、互いに分離して形成されていることを特徴とする付記1または2記載のスタティックランダムアクセスメモリ。

(付記7)

前記第2導電型の深いウェルの各々は、行方向に一つのメモリセルカラムを超えない寸法で形成されていることを特徴とする付記6記載のランダムアクセスメモリ。

(付記8)

前記第2導電型の深いウェルは前記行方向に、1つのメモリセルカラム群の行方向への寸法から、2メモリセル分の行方向への寸法を差し引いた以上の幅を有していることを特徴とする付記2記載のスタティックランダムアクセスメモリ。

(付記9)

前記半導体基板に垂直な方向から見た場合、前記第2導電型の深いウェルは、対応するカラム群に含まれることを特徴とする付記8記載のスタティックランダムアクセスメモリ。

(付記10)

前記半導体基板に垂直な方向から見た場合、前記第2導電型の深いウェルは、一のカラム群から隣接するカラム群に渡って形成されていることを特徴とする付記8記載のスタティックランダムアクセスメモリ。

(付記11)

前記複数のカラム群の各々において前記カラム選択回路は、当該カラム群の行方向上第1の端から第2の端まで前記半導体基板上で配列した複数のメモリセルカラムを順次選択することを特徴とする付記1〜10のうち、いずれか一項記載のスタティックランダムアクセスメモリ。

(付記12)

前記複数のカラム群のうち一つおきに配列した第1のカラム群に設けられたカラム選択回路よりなる第1のカラム選択回路の各々は、当該カラム群の行方向上第1の端から第2の端まで前記半導体基板上に順次形成された複数のメモリセルカラムを順次選択し、

前記複数のカラム群のうち前記第1のカラム群に隣接する第2のカラム群に設けられたカラム選択回路よりなる第2のカラム選択回路の各々は、当該カラム群の行方向上第1の端から第2の端まで前記半導体基板上に順次形成された複数のメモリセルカラムを、前記第1のカラム選択回路とは異なった順序で選択することを特徴とする付記8〜10のうち、いずれか一項記載のスタティックランダムアクセスメモリ。

(付記13)

前記第2のカラム選択回路は、前記第1のカラム選択回路が前記第1のカラム群の直下に位置する第2導電型の深いウェルよりなる第1の深いウェルの端部に対応するメモリセルカラムを選択する場合、前記第2のカラム群の直下に位置する第2導電型の深いウェルよりなる第2の深いウェルの端部に対応するメモリセルカラムよりも、前記第2の深いウェルから見て行方向上より内側のメモリセルカラムを選択することを特徴とする請求項12記載のスタティックランダムアクセスメモリ。

(付記14)

前記第2のカラム選択回路は、前記第1のカラム選択回路が前記第1のカラム群の直下に位置する第2導電型の深いウェルよりなる第1の深いウェルの端部に対応するメモリセルカラムを選択する場合、前記第2のカラム群の直下に位置する第2導電型の深いウェルよりなる第2の深いウェルの端部に対応するメモリセルカラムよりも、前記第2の深いウェルから見て行方向上で一つ内側のメモリセルカラムを選択することを特徴とする付記12記載のスタティックランダムアクセスメモリ。

(付記15)

前記第2のカラム選択回路は、前記第1のカラム選択回路が前記第1のカラム群の直下に位置する第2導電型の深いウェルよりなる第1の深いウェルの端部に対応するメモリセルカラムを選択する場合、前記第2のカラム群の直下に位置する第2導電型の深いウェルよりなる第2の深いウェルの端部に対応するメモリセルカラムよりも、前記第2の深いウェルから見て行方向上で二つ内側のメモリセルカラムを選択することを特徴とする付記12記載のスタティックランダムアクセスメモリ。

(付記16)

前記カラム群は、少なくとも4本のメモリセルカラムを含むことを特徴とする付記1〜15のうち、いずれか一項記載のスタティックランダムアクセスメモリ。

(付記17)

前記カラム選択回路によって選択された信号に基づいてエラー検出またはエラー訂正を行うことを特徴とする付記1〜16のうち、いずれか一項記載のスタティックランダムアクセスメモリ。

【符号の説明】

【0191】

10,20,30,40,50,60, SRAM

10L メモリセル

11,101 シリコン基板

11A1,11A2,11B1,11B2 活性領域

11I,101I 素子分離領域

11a1,11a2 延在部

11a,11c n型ソース領域

11b,11d n型ドレイン領域

11e,101a p型ソース領域

11f,101b p型ドレイン領域

11PW,101P,PW(01)〜PW(12) p型ウェル

11NW,101N,NW(01)〜NW(12),DNW1,DNW2 n型ウェル

12 層間絶縁膜

12A,12B,12C,12V ビアプラグ

13A〜13C 配線パタ―ン

104 nチャネルMOSトランジスタ

BL,/BL,BL(01)〜BL(16),BL1〜BL4 ビット線

C(01)〜C(16),D(01)〜D(16) メモリセル

CDEC カラムデコーダ

CG1〜CG4 カラム群

CS1〜CS4 カラム選択回路

DNW 深いn型ウェル

DT1,DT2 ドライバトランジスタ

ECC エラー検出訂正回路

G1,G2,G3,G4, 103 ゲート電極

Gox1,Gox2,Gox3,Gox4 ゲート絶縁膜

MCC(01)〜MCC(16) メモリセルカラム

SA1〜SA4 センスアンプ

V1〜V13 ビアコンタクト

W1,W2 局所配線パタ―ン

WL,WL(01)〜WL(08) ワード線

LT1,LT2 ロードトランジスタ

TF1,TF2 トランスファトランジスタ

N1,N2 ノード

WLワード線

Vdd,Vss 電源電圧

【技術分野】

【0001】

本発明は一般に半導体装置に係り、特にスタティックランダムアクセスメモリを含む半導体記憶装置に関する。

【背景技術】

【0002】

スタティックランダムアクセスメモリ(以下SRAMと記す)は、ワード線により選択されるトランスファトランジスタと、かかるトランスファトランジスタを介してビット線に接続される、フリップフロップ接続された二つのCMOSインバータとよりなる高速半導体記憶素子であり、高速論理回路素子においてCMOS回路など高速論理素子と共に広く使われている。

【先行技術文献】

【特許文献】

【0003】

【特許文献1】特開平11−17134号公報

【特許文献2】特開2000−48564公報

【発明の概要】

【発明が解決しようとする課題】

【0004】

一般にSRAMでは複数のメモリセルが、ワード線方向ないし行方向とビット線方向ないし列方向に配列されて二次元的なメモリセルアレイを構成するが、各々のメモリセルにおいては、前記二つのCMOSインバータを構成する二つのpチャネルMOSトランジスタが、前記メモリセルアレイ中を列方向に延在しているn型ウェル中に形成され、また前記二つのCMOSインバータを構成する二つのnチャネルMOSトランジスタと、前記トランスファトランジスタを構成する二つのnチャネルMOSトランジスタが、前記メモリセルアレイ中を、前記n型ウェルの両側に隣接して平行に延在している一対のp型ウェルの、半分ずつを使って形成される。

【0005】

前記メモリセルアレイ中のメモリセルは、列方向に整列して共通のビット線に接続された一群のメモリセルよりなるメモリセルカラムを複数束ねたカラム群を単位として組織化されており、前記複数のカラム群が行方向に繰り返されている。各々のカラム群には、アドレスデータの一部を供給されて特定のメモリセルカラムを選択するカラム選択回路が設けられている。

【0006】

またSRAMにはアドレスデータの一部を供給されて特定のワード線を選択するワード線選択回路が設けられており、特定のワード線を選択することにより、選択された特定のメモリセルカラム中の特定のメモリセルが選択され、選択されたメモリセルに対して1ビットのデータの書込あるいは読み出しが行われる。

【0007】

このような、メモリセルアレイをカラム群単位で組織化したSRAMでは、一つのカラム群に対して一回に1ビットのデータが読み出しあるいは書き込みされ、また複数のカラム群に対して複数ビットのデータが一度に読み出しあるいは書き込みされる。

【0008】

例えば4ビットのカラム群が64本あるメモリセルアレイでは、第1のカラム群の第1メモリセルカラム、第2のカラム群の第1メモリセルカラム、第3のカラム群の第1メモリセルカラム、・・・に対して一度に1ビットのデータの読み出しがなされ、結果として64ビットデータが一度に読み出される。

【0009】

ところで、このようなSRAMでは、時折外部からの放射線などにより、いわゆるソフトエラーが生じることがあり、例えば第1カラム群の第1メモリセルカラムの選択されたメモリセルにおいてデータの反転が生じる場合がある。

【0010】

このような場合、同じカラム群の他のメモリセルでも、前記放射線のエネルギによりデータが反転している可能性があるが、これら同じカラム群の他のメモリセルは選択されていないためSRAMとしての読み出しに影響はない。そこで、他のカラム群にまで前記放射線の影響が及んでいないとすると、読み出された64ビットデータ中においてエラーは1ビットだけということになる。このような場合、通常のECC(エラー検出および訂正)回路を使うことにより、そのエラーを訂正することができる。

【0011】

ところが本発明の発明者は、本発明の基礎となる研究において、最近の、非常に高集積化されたSRAMの場合、一つのカラム群において生じたソフトエラーの効果が、隣接するカラム群まで波及してしまい、例えば同時に選択される第1メモリセルカラムの第1ビットと第2メモリセルカラムの第2ビットなど、64ビットの読み出しデータ中に2ビットのエラーが含まれる場合が生じることを見出した。

【0012】

このような2ビットやさらに多ビットのエラーは、ECC回路において、より多くの冗長ビット(パリティビット)を設けてやれば対応することはできるが、それではSRAMの面積効率が低下してしまい、SRAMの費用が増大してしまう。

【課題を解決するための手段】

【0013】

一の側面によるランダムアクセスメモリは、第1の導電型の共通ウェルが形成された半導体基板と、前記半導体基板上の前記共通ウェルに行列状に配列されたメモリセルよりなり、列方向に整列して共通のビット線に接続される一群のメモリセルがメモリセルカラムを形成し、前記メモリセルカラムが複数束ねられて複数のカラム群が形成され、前記複数のカラム群が行方向に繰り返される構成のメモリセルアレイと、各々のカラム群に設けられ、アドレスデータの一部を供給されて特定のメモリセルカラムを選択するカラム選択回路と、を含み、前記メモリセルアレイ中には前記複数のメモリセルカラムの各々において、前記メモリセル中の、前記第1の導電型のソースおよびドレイン領域を有するMOSトランジスタのための、前記第1の導電型とは逆の第2導電型ウェルと、前記第2の導電型を有するソースおよびドレイン領域を有するMOSトランジスタのための前記第1の導電型の第1導電型ウェルとが、ビット線方向に、相互に隣接して延在しており、前記複数のカラム群の各々において前記複数のメモリセルカラムはそれぞれのビット線のビットに対応しており、隣接する第1および第2のカラム群において、前記第1のカラム群で選択される一のメモリセルカラムの第1導電型ウェルと、第2カラム群で同時に選択されるメモリセルカラムの第1導電型ウェルとは、いずれか一方が、前記共通ウェルから、第2導電型の深いウェルにより遮断されており、前記第2導電型の深いウェルは、行方向に測った場合の一つのカラム群の寸法を超えない寸法を有する。

【発明の効果】

【0014】

上記一の側面によれば、一のカラム群中の一のメモリセルカラムの第1導電型ウェルおいて放射線などによりソフトエラーが生起したとしても、その影響が隣接するカラム群中の同時に選択されるメモリセルカラムの第1導電型ウェルに伝搬するのを、第2導電型の深いウェルにより遮断でき、また、一のカラム群中の一のメモリセルカラムの第2導電型ウェルおいて放射線などによりソフトエラーが生起したとしても、その影響が隣接するカラム群中の同時に選択されるメモリセルカラムの第2導電型ウェルに、第2導電型の深いウェルを介して伝搬するのを、前記第2導電型の深いウェルを行方向に、一つのカラム群に相当する寸法を超えないように形成することで、遮断することができ、スタティックランダムアクセスメモリのソフトエラー耐性が向上する。

【図面の簡単な説明】

【0015】

【図1】第1の実施形態によるSRAMを示す等価回路図である。

【図2A】図1に対応する1メモリセルを示す平面図である。

【図2B】図2A中、線A−A’に沿った断面図である。

【図2C】図2A中、線B−B’に沿った断面図である。

【図3】第1の実施形態によるSRAMのメモリセルアレイを示す平面図である。

【図4】図3の平面図において、下部のn型ウェルおよびp型ウェルの配列を示した図である。

【図5】第1の実施形態によるSRAMの電気的構成を示した図である。

【図6A】図5の構成におけるエラー検出および訂正回路の原理を説明する第1の図である。

【図6B】図5の構成におけるエラー検出および訂正回路の原理を説明する第2の図である。

【図7】一般的なソフトエラーを説明する図である。

【図8A】図4中、線C−C’に沿った断面図である。

【図8B】図8Aの断面図を、より広い範囲にわたって示す図である。

【図8C】図8Bの一変形例を示す図である。

【図9A】第1の実施形態の比較対照例における問題を説明する断面図である。

【図9B】第1の実施形態の別の比較対照例における問題を説明する断面図である。

【図10】図9Aの比較対照例における問題発生のメカニズムを説明する断面図である。

【図11】第1の実施形態で使われるカラム選択回路の構成を示す回路図である。

【図12】図11の回路図で使われる真理値表の例を示す図である。

【図13】第1の実施形態における深いn型ウェルの行方向への寸法とカラム群の行方向への寸法との関係を示す平面図である。

【図14】第1の実施形態の別の変形例を示す平面図である。

【図15】第2の実施形態によるSRAMを示す平面図である。

【図16】図15中、線D−D’に沿った断面図である。

【図17】第3の実施形態によるSRAMの構成を示す平面図である。

【図18】図17の線E−E’に沿った断面図である。

【図19】第3の実施形態におけるメモリセルカラムの選択を説明するブロック図である。

【図20A】第4の実施形態におけるメモリセルカラムの選択を説明するブロック図である。

【図20B】第4の実施形態によるSRAMの構成を示す断面図である。

【図21A】第5の実施形態におけるメモリセルカラムの選択を説明するブロック図である。

【図21B】第5の実施形態によるSRAMの構成を示す断面図である。

【図21C】第5の実施形態の一変形例を示すブロック図である。

【図22A】第6の実施形態を示すブロック図である。

【図22B】第6の実施形態の一変形例を示すブロック図である。

【図23】第7の実施形態を示すブロック図である。

【図24】第8の実施形態を示す断面図である。

【図25】第8の実施形態の一例を示す断面図である。

【図26】第8の実施形態の選択回路における様々なビット線選択の例を示す図である。

【発明を実施するための形態】

【0016】

[第1の実施形態]

図1は、第1の実施形態によるSRAM10の1メモリセル分の等価回路図を示す。

【0017】

図1を参照するに、前記SRAM10はpチャネルMOSトランジスタよりなる第1のロードトランジスタLT1とnチャネルMOSトランジスタよりなる第1のドライバトランジスタDT1を直列接続した第1のCMOSインバータI1と、pチャネルMOSトランジスタよりなる第2のロードトランジスタLT2とnチャネルMOSトランジスタよりなる第2のドライバトランジスタLD2を直列接続した第2のCMOSインバータI2とよりなるフリップフロップ回路FFを含み、前記第1のロードトランジスタLT1と第1のドライバトランジスタDT1を接続する接続ノードN1は、nチャネルMOSトランジスタよりなりワードラインWLにより制御される第1のトランスファトランジスタTF1を介して第1のビットラインBLに接続される。同様に、前記第2のロードトランジスタLT2と第1のドライバトランジスタDT2を接続する接続ノードN2は、nチャネルMOSトランジスタよりなりワードラインWLにより制御される第2のトランスファトランジスタTF2を介して、前記第1のビットラインの相補的ビットライン/BLに接続される。

【0018】

図2Aは、図1のSRAM10の、1メモリセル分のレイアウト10Lを示す平面図、図2Bおよび図2Cは図2A中、線A−A’およびB−B’に沿った断面図である。

【0019】

図2Aを参照するに、前記SRAM10はSTI型の素子分離領域11Iが形成されたp型シリコン基板11上に形成されており、前記素子分離領域11Iには、前記p型シリコン基板11上をビット線方向BL、すなわち列方向に連続的に、かつ相互に平行に、かつ離間して延在する第1および第2のn型活性領域11A1,11A2が画成されている。また前記素子分離領域11Iには前記第1および第2のn型活性領域11A1,11A2の間に、ビット線方向BLに限られた距離だけ互いに平行に延在する第3および第4のp型活性領域11B1,11B2が、前記p型活性領域11B1が前記n型活性領域11A1と前記p型活性領域11B2の間に位置するように、さらに前記p型活性領域11B2が前記n型活性領域11A2と前記p型活性領域11B1の間に位置するように、画成されている。

【0020】

図2A中、破線は一つのメモリセルの境界を示すが、前記活性領域11A1上にはかかるメモリセルの境界の一方の交点の近傍に、第1の電源電圧Vssを供給される電源コンタクトV1が、また他方の交点にビット線BLに接続されるビットラインコンタクトV2が形成されている。また前記活性領域11A2上には前記電源コンタクトV1に対して点対称な位置に、前記電源電圧Vssを供給される電源コンタクトV3が、また前記ビットラインコンタクトV2に対して点対称な位置に、前記ビット線BLに対し相補的なビット線/BLに接続されるビットラインコンタクトV4が形成されている。ただし前記ビアコンタクトV1は、前記活性領域11A1から左方に延在する延在部11a1に形成され、左隣のメモリセルと共有されている。同様に前記ビアコンタクトV3は、前記活性領域11A2から右方に延在する延在部11a2に形成され、右隣のメモリセルと共有されている。

【0021】

さらに前記活性領域11B1には、前記メモリセルの境界との交点に対応して、第2の電源電圧Vddを供給される電源コンタクトV5が形成されており、また前記活性流域11B2には、前記電源コンタクトV5に対して点対称な位置に前記電源電圧Vddを供給される電源コンタクトV6が形成されている。

【0022】

前記活性領域11A1上には、前記電源コンタクトV1とビット線コンタクトV2の間に図1のドライバトランジスタDT1とトランスファトランジスタTF1とが順次形成されており、前記ドライバトランジスタDT1のゲート電極G1が、前記活性領域11B1を横切ってワード線方向、すなわち行方向に前記活性領域11B2に向かって延在し、前記活性領域11B2の端にビアコンタクトV7において接続されている。その際、前記活性領域11B1とゲート電極G1の交点には、前記ロードトランジスタLT1が形成される。

【0023】

同様に前記活性領域11A2上には、前記電源コンタクトV3とビット線コンタクトV4の間に図1のドライバトランジスタDT2とトランスファトランジスタTF2とが順次形成されており、前記ドライバトランジスタDT2のゲート電極G2が、前記活性領域11B2を横切ってワード線方向、すなわち行方向に前記活性領域11B1に向かって延在し、前記活性領域11B1の端にビアコンタクトV8において接続されている。その際、前記活性領域11B2とゲート電極G2の交点には、前記ロードトランジスタLT2が形成される。

【0024】

さらに前記活性領域11A1と活性領域11B1とは、前記トランジスタDT1とTF1の間のビアコンタクトV9を、前記活性領域11B1のうち前記トランジスタLT1に対して前記電源コンタクトV5とは反対の側に前記ビアコンタクトV8と並んで形成されるビアコンタクトV10に、前記ノードN1に対応する局所配線パタ―ンW1により接続され、これにより前記ロートトランジスタLT1とドライバトランジスタDT1とが、電源電圧Vddが供給される電源コンタクトV5と電源電圧Vssが供給される電源コンタクトV1との間で直列に接続される。

【0025】

同様に前記活性領域11A2と活性領域11B2とは、前記トランジスタDT2とTF2の間のビアコンタクトV11を、前記活性領域11B2のうち前記トランジスタLT2に対して前記電源コンタクトV6とは反対の側に前記ビアコンタクトV7と並んで形成されるビアコンタクトV12に、前記ノードN2に対応する局所配線パタ―ンW2により接続され、これにより前記ロートトランジスタLT2とドライバトランジスタDT2とが、電源電圧Vddが供給される電源コンタクトV6と電源電圧Vssが供給される電源コンタクトV3との間で直列に接続される。

【0026】

さらに前記トランスファトランジスタTF1のゲート電極G3がワート線方向WL,すなわち行方向上、前記活性領域11B1とは反対の方向に延在し、前記メモリセルの境界においてワート線WLとワード線コンタクトV13において接続される。また前記トランスファトランジスタTF2のゲート電極G4がワート線方向WL,すなわち行方向上、前記活性領域11B2とは反対の方向に延在し、前記メモリセルの境界においてワート線WLとワード線コンタクトV14において接続される。

【0027】

図1の等価回路図においてロードトランジスタLT1とLT2はpチャネルMOSトランジスタであり、シリコン基板11中のn型ウェルに形成されているのに対し、ドライバトランジスタDT1,DT2およびトランスファトランジスタTF1,TF2はnチャネルMOSトランジスタであり、シリコン基板11中のp型ウェルに形成されているのに注意すべきである。

【0028】

なお図2A中、白抜きで示したビアコンタクトV7〜V12は前記ゲート電極G1〜G3に対応する配線層をそれぞれの活性領域に接続するビアコンタクトを示しており、黒で示したビアコンタクトV1〜V6,V13,V14はより上層の、すなわちワードラインWL,ビットラインBLが形成される配線層への接続のためのビアコンタクトを示す。前記局所配線パタ―ンW1は、前記活性領域11A1,11B1上に直接に形成してもよい。同様に局所配線パタ―ンW2は、前記活性領域11A2,11B2上に直接に形成してもよい。

【0029】

図2Bは、前記SRAM10のうち、前記線A−A’に沿った断面図を示す。

【0030】

図2Bを参照するに、図2Bの断面では前記p型シリコン基板11の上部にp型ウェル11PWが形成されており、前記p型シリコン基板11上には前記ドライバトランジスタDT1のゲート電極G1がゲート絶縁膜Gox1を介して形成されている。また前記p型ウェル11PW中には前記ゲート電極G1の左右に、n型のソース領域11aおよびn型のドレイン領域11bが形成されている。また同様に前記p型シリコン基板11上には前記トランスファトランジスタTF1のゲート電極G3が、ゲート絶縁膜Gox3を介して形成されており、前記p型ウェル11PW中には前記ゲート電極G3の左右に、n型のソース領域11cおよびn型のドレイン領域11dが形成されている。ここでドレイン領域11bとソース領域11cとは連続した一つのn型拡散領域により形成されている。

【0031】

さらに前記ゲート電極G1とゲート電極G3の間には、前記ゲート電極G1の側壁絶縁膜SW1およびゲート電極G3の側壁絶縁膜SW2を部分的に覆って局所配線パタ―ンW1が、前記ドレイン領域11bおよびソース領域11cに電気的にコンタクトして形成されている。

【0032】

さらに前記シリコン基板11上には層間絶縁膜12が、前記ゲート電極G1およびG3を覆って形成されており、前記層間絶縁膜12には電源電圧Vssを供給する配線パタ―ン13Aにコンタクトして、前記ビアコンタクトV1を構成するビアプラグ12Aが、またビット線BLを構成する配線パタ―ン13Bにコンタクトして前記ビアコンタクトV13を構成するビアプラグ12Bが、それぞれ形成されている。

【0033】

図2Cは、前記SRAM10のうち、前記線B−B’に沿った断面図を示す。

【0034】

図2Cを参照するに、線B−B’に沿った断面では前記p型シリコン基板11の上部にn型ウェル11NWが形成されており、前記ロードトランジスタLT1がかかるn型ウェルNWに形成されている。

【0035】

より具体的には図2Cの断面では図2Bのゲート電極G1がゲート絶縁膜Gox1共々延在してロードトランジスタLT1のゲート電極を構成し、前記n型ウェル11NW中には前記ゲート電極G1の左右に、p型のソース領域11eおよびp型のドレイン領域11fが形成されている。

【0036】

また図2Cの断面では素子分離絶縁膜11I上に前記ロードトランジスタLT2のゲート電極G2となるポリシリコンパタ―ンがその下のゲート絶縁膜Gox2共々延在しており、前記局所配線パタ―ンW1が前記図2Bの断面から連続して延在し、前記p型ドレイン領域11fにコンタクトする。これにより前記n型ソースおよびドレイン領域11b,11cがp型ソース領域11fに電気的に接続される。

【0037】

さらに図2Cの断面では前記ゲート電極G1およびポリシリコンパタ―ンG2は前記層間絶縁膜12により同様に覆われ、前記層間絶縁膜12には、前記ビアコンタクトV10およびV8に対応して共通のビアプラグ12Vが形成され、ビアプラグ12Vは前記局所配線パタ―ンW1を、前記ポリシリコンパタ―ンG2に電気的に接続する。

【0038】

また前記層間絶縁膜12上には電源電圧Vddを供給される配線パタ―ン13Cが形成されており、前記配線パタ―ン13Cが前記層間絶縁膜12中に形成されたビアコンタクトV5に対応するビアプラグ12Cにより、前記p型ソース領域11eに電気的に接続される。

【0039】

その他のトランジスタDT2,TF2およびLT2も同様な断面構造を有しており、説明は省略する。

【0040】

さらに前記シリコン基板11上には層間絶縁膜12が、前記ゲート電極G1を覆って形成されており、前記層間絶縁膜12には電源電圧Vddを供給する配線パタ―ン13Cにコンタクトして、前記ビアコンタクトV5を構成するビアプラグ12Cが形成されている。

【0041】

図3は、図2A〜図2Cのメモリセル10Lを行列状に繰り返し形成したSRAM10のメモリセルアレイを示す平面図である。

【0042】

図3を参照するに、破線で示した図2A〜図2Cのメモリセル10Lが、上下左右を反転させながら、素子分離領域11Iにより表面に活性領域が形成されたシリコン基板11上に繰り返し形成されているのがわかる。また活性領域11A1および11A2が複数のメモリセルに共通に、ビットライン方向BLに延在し、活性領域11B1および11B2はいずれも行方向ないしワード線方向WLに2メモリセル分の長さないし寸法を有し、前記ビットライン方向に互い違いに繰り返されているのがわかる。

【0043】

図4は図3の平面図において、素子分離絶縁膜11Iを除去し、その下のシリコン基板11中のp型ウェルPW(00),PW(01),PW(02),PW(03)・・・およびn型ウェルNW(01),NW(02),NW(03)・・・を露出させた図である。ここで前記p型ウェルPW(00),PW(01),PW(02),PW(03)・・・は、図2Bにおけるp型ウェル11PWに対応し、n型ウェルNW(01),NW(02),NW(03)・・・は、図2Cにおけるn型ウェル11NWに対応する。

【0044】

図4を参照するに、図2A〜図2Cのメモリセル10Lでは、pチャネルMOSトランジスタよりなるロートトランジスタLT1およびLT2に対応して、前記活性領域11B1および11B2はシリコン基板11中のn型ウェルNW(02)に形成されており、一方nチャネルMOSトランジスタよりなるトランスファトランジスタTF1およびドライバトランジスタDT1に対応して前記活性領域11A1が、シリコン基板11中のp型ウェルPW(01)に形成されており、さらにnチャネルMOSトランジスタよりなるトランスファトランジスタTF2およびドライバトランジスタDT2に対応して前記活性領域11A2が、シリコン基板11中のp型ウェルPW(02)に形成されている。

【0045】

各々のウェルはビット線方向BLに連続して延在し、このようなp型ウェルとn型ウェルはワード線方向WLに向かって交互に繰り返し形成されている。

【0046】

なお前記p型ウェルPW(00)の左半分は、前記メモリセル10Lの左隣のメモリセルに共有されており、またp型ウェルPW(03)の右半分は、前記メモリセル10Lの右隣のメモリセルに共有されている。

【0047】

図5は、本実施形態によるSRAM10において、いわゆるソフトエラーの伝搬を回避するために使用するエラー訂正構成を示す。

【0048】

図5を参照するに、C(01)〜C(16)、D(01)〜D(16)は、図3,4で示したメモリセルアレイにおいて、ワード線WL(01)あるいはWL(02)で選択される一連のメモリセルを表す。

【0049】

本実施形態では、これらのメモリセルは、列方向に整列してそれぞれ共通のビット線BL(01),BL(02)・・・に接続された複数のメモリセルカラムMCC(01),MCC(02)・・・の形に組織化されており、そのうちの複数の、図示の例では4本の、メモリセルカラムが束ねられ、全体では、ワード線方向WLに繰り返される複数のカラム群CG1,CG2,CG3,CG4・・・が形成されている。例えばビット線BL(01)〜ビット線BL(04)に対応する4本のメモリセルカラムMCC(01)〜MCC(04)が一つのカラム群CG1を構成し、ビット線BL(05)〜ビット線BL(08)に対応する4本のメモリセルカラムMCC(05)〜MCC(08)が、隣接するカラム群CG2を構成し、ビット線BL(09)〜ビット線BL(12)に対応する4本のメモリセルカラムMCC(09)〜MCC(12)が、さらに隣接するカラム群CG3を構成し、ビット線BL(13)〜ビット線BL(16)に対応する4本のメモリセルカラムMCC(13)〜MCC(16)が、さらに隣接するカラム群CG4を構成する。なお図5においてビット線BL(0)〜BL(16)の各々は、先に図1で説明したビット線BLと相補的ビット線/BLとより構成されている。ビット線/BLの図示は省略している。

【0050】

さらに図5の構成では、これら複数のカラム群CG1,CG2,CG3,CG4・・・にそれぞれ対応して複数のカラム選択回路CS1,CS2,CS3,CS4・・・が設けられており、前記カラム選択回路CS1,CS2,CS3,CS4・・・は、対応するカラム群において一つのメモリセルカラムを選択し、当該メモリセルカラムに対応するビット線上に読み出された電圧信号を、それぞれ対応するセンスアンプSA1,SA2,SA3,SA3・・・に供給する。

【0051】

例えば先にワード線WL(01)によりメモリセルC(01),C(02),C(03)・・・C(16)が選択されている場合に、カラム選択回路CS1がビット線BL(01)に対応したメモリセルカラムMCC(01)を、カラム選択回路CS2がビット線BL(05)に対応したメモリセルカラムMCC(05)を、カラム選択回路CS3がビット線BL(09)に対応したメモリセルカラムMCC(09)を、カラム選択回路CS4がビット線BL(13)に対応したメモリセルカラムMCC(13)を選択したとすると、当該ビット線上に読み出されたメモリセルC(01),C(05),C(09),C(13)の論理状態を表す電圧信号が、前記カラム選択回路CS1,CS2,CS3,CS4を介して対応するセンスアンプSA1,SA2,SA3,SA4にそれぞれ供給される。

【0052】

センスアンプSA1,SA2,SA3,SA4は、通常通り、供給された電圧信号から、それぞれのメモリセルの論理状態を判定することで、情報を読み出す。

【0053】

図5の構成では、このようにして読み出されたメモリセルのデータはエラー検出および訂正回路(ECCロジック)ECCに供給され、図6A、図6Bに示すようにビット線方向およびワード線方向のパリティチェックを行うことにより、ソフトエラーの検出および訂正がなされる。

【0054】

図6A,図6Bは前記エラー検出および訂正回路ECCの原理を示す図である。なお図6AはSRAMのメモリセルアレイ中にエラーの無い場合を、図6Bは8行8列のメモリセルアレイ範囲に1ビットのエラーが存在する場合を示す。

【0055】

図6Aを参照するに、図示の例では各々4ビットのサイズの第1〜第8までのカラム群にそれぞれ対応してカラム選択回路CS1〜CS8が形成されており、それぞれのカラム選択回路においてビット線BL(04),BL(08),BL(12)・・・BL(32)が同時に選択されている。

【0056】

さらにECCロジックではワード線毎にパリティビットAが設けられ、一つのワード線上で選択された8個のメモリセルの読み出し値の合計が、パリティビットAを合わせて偶数になるように構成されている。

【0057】

またECCロジックではビット線毎にパリティビットBが設けられ、一つのビット線上で連続して選択された8個のメモリセルの読み出し値の合計が、パリティビットBを合わせて偶数になるように構成されている。

【0058】

そこでワード線WL(01)〜WL(08)およびパリティビットBの各々について、ビット線BL(04),BL(08),BL(12)・・・BL(32)およびパリティビットAを選択してデータを読み出すことにより、図6Aあるいは図6Bに示すような読み出し値のマトリクスが得られる。

【0059】

エラーがない図6Aの場合には、一つのワード線上で選択されたメモリセルの読み出し値の合計が、パリティビットAを合わせて偶数になっており、また一つのビット線上で選択されたメモリセルの読み出し値の合計が、パリティビットBを合わせて偶数になっている様子がわかる。

【0060】

一方、例えばワード線WL(01)とビット線BL(04)で選択されるメモリセルにエラーがあり、データ値が反転している図6Bの場合、ワード線WL(01)で選択されるメモリセルのデータの合計が、パリティビットAを合わせても奇数となり、このワード線WL(0)上のメモリセルのいずれかにエラーが存在することが検出される。またビット線BL(01)で選択されるメモリセルのデータの合計が、パリティビットBを合わせても奇数となり、このビット線BL(04)上のメモリセルのいずれかにエラーが存在することが検出される。このことから、エラーが生じているのはワード線WL(01)およびビット線BL(04)で選択されるメモリセルであることが確定し、そのデータ「0」を「1」に訂正することでエラーの訂正が行われる。

【0061】

このようなSRAM10においては、ときおり外部放射線などの影響により、ソフトエラーが発生することがあり、先の図5のエラー検出および訂正回路ECCは、このようなソフトエラーの検出および訂正のために使われる。

【0062】

図7は、一般的なpチャネルMOSトランジスタにおけるソフトエラーの概要を説明する図である。

【0063】

図7を参照するに、シリコン基板101上には素子分離領域101Iにより素子領域101Aが形成されており、前記素子領域101Aに対応して前記シリコン基板101中にはn型ウェル101Nが形成されている。また前記シリコン基板101中には、前記n型ウェル101Nを電気的に分離するため、p型ウェル101Pが形成されている。前記p型ウェル101Pはシリコン基板101自身であることが多い。

【0064】

前記シリコン基板101上には、前記素子領域101Aにおいて図示を省略したゲート絶縁膜を介してポリシリコンなどのゲート電極103が形成されており、さらに前記素子領域101Aのうち、前記ゲート電極103の一方の側、図示の例では左側にp型のソース101a領域が、また他方の側にはp型のドレイン領域101bが形成されている。

【0065】

さて前記ソース領域101aに電源電圧Vddを印加し、前記ドレイン領域101bを他のトランジスタ、例えばnチャネルMOSトランジスタ104により接地した前記pチャネルMOSトランジスタの動作状態において図7中に矢印で示すようにα線などの荷電粒子が素子領域101Aを構成するn型ウェル101Nに侵入した場合を考えると、前記n型ウェル101N中において電子−正孔対が前記荷電粒子のエネルギにより励起されるが、励起された電子−正孔対のうち正孔はドレイン領域101bからnチャネルMOSトランジスタ104を介して接地へと逃がされ、前記n型ウェル101N中に電子のみが残留してしまう状況が発生することがある。

【0066】

このようにnウェル101N中に電子のみが残るとその電位が低下し、その結果、n型ウェル101N,p型ソース領域101aおよびp型ドレイン領域101bよりなる寄生バイポーラトランジスタが導通してしまい、ドレイン電流がソース領域101aからドレイン領域101bへと流れる場合がある。

【0067】

このような寄生バイポーラトランジスタの導通が、先のメモリセル10Lにおいて、例えばpチャネルMOSトランジスタLT1あるいはLT2において生じると、フリップフロップFFは状態を反転させてしまい、メモリセル10Lに保持されているデータは反転してしまう。

【0068】

同様な荷電粒子により保持データの反転は、図1のドライバトランジスタLT1あるいはLT2を構成するnチャネルMOSトランジスタにおいても発生しうる。

【0069】

図8Aおよび図8Bは、前記図4における線C−C’に沿ったSRAM10の断面図を示す。図中、先に説明した部分に対応する部分には同一の参照符号を付し、説明を省略する。図8Bは図8Aと同じ構造を、より広い範囲にわたり示した断面図である。なお図8A,図8Bにおいて、シリコン基板11上に形成されるそれぞれのトランジスタのゲート電極などの図示は、簡単のため省略している。

【0070】

図8Aを参照するに、メモリセルC(01)〜C(06)は先の図5のメモリセルC(01)〜C(06)にそれぞれ対応しており、またカラム選択回路CS1,CS2は図6のカラム選択回路CS1,CS2にそれぞれ対応する。なお、より広い範囲を示した図8Bでは、さらにカラム選択回路CS3およびこれに対応するビット線BL(09)〜BL(12)、さらに前記ビット線に接続されるメモリセルカラムに対応したカラム群CG3が示されている。

【0071】

図8Aを参照するに、前記シリコン基板11中には、前記nチャネルMOSトランジスタDT1,TF1あるいはDT2,TF2のためのp型ウェルPW(01)〜PW(05)と前記pチャネルMOSトランジスタLT1.LT2のためのn型ウェルNW(01)〜NW(06)とが交互に繰り返し形成されており、またカラム選択回路CS2に対応するカラム群に含まれるメモリセルカラムでは、それぞれのp型ウェル、すなわちPW(04),PW(05),PW(06)・・・の下に、深いn型ウェルDNW1が形成されているのがわかる。

【0072】

前記カラム選択回路CS2に対応するカラム群の下にこのような深いn型ウェルを形成することにより、カラム選択回路CS1に対応するカラム群のp型ウェル、例えばp型ウェルPW(01)、に荷電粒子などが入来した場合でも、その影響がp型ウェルPW(04)やPW(05)に伝搬するのが、シリコン基板11と前記深いn型ウェルDNWの間のpn接合により遮断される。

【0073】

その際、本実施形態による構成では、図8Bに示すように、前記深いn型ウェルDNW1,DNW2・・・を行方向ないしワード線方向WLに、一つのカラム群に相当する長さないし寸法を超えないように形成する。また本実施形態による構成では、前記p型ウェルPW(00),PW(02)・・・の下に連続して深いn型ウェルを形成し、これに、奇数番目のカラム群CG1,CG3,CG5・・・に対応して行方向ないしワード線方向WLに、一つのカラム群に対応する長さないし寸法で切れ目を繰り返し形成すると見てもよい。ただし図8A,図8Bの構成において、各々のウェルPW(00)〜PW(12),NW(01)〜NW(11),DNW1およびDNW2は、いずれもビット線方向BLに同じ長さだけ延在するため、図面中で横方向の長さないし寸法は、それぞれのウェルの面積に対応している。

【0074】

より具体的には、前記深いn型ウェルDNW1は、図8Bのより広範囲にわたる断面図に示すように実質一つのカラム群に相当する面積に等しく形成されているため、前記カラム選択回路CS2のカラム群の下からカラム選択回路CS1のカラム群の下まで、全面にわたり連続して延在することがない。また深いn型ウェルDNW1とその隣の深いn型ウェルDNW2の間の切れ目も、実質一つのカラム群の面積に等しく形成されている。

【0075】

このため、例えばメモリセルC(01)のn型ウェルNW(01)が、前記深いn型ウェルDNW1を介して同時に選択されるメモリセルC(05)のn型ウェルNW(05)に電気的に接続されることがなく、n型ウェルNW(01)に入来した荷電粒子の影響がn型ウェルNW(04)やNW(05)に及ぶことが回避される。

【0076】

また、例えばメモリセルC(01)のp型ウェルPW(01)が、同時に選択されるメモリセルC(05)のp型ウェルPW(05)に電気的に接続されることがなく、p型ウェルPW(01)に入来した荷電粒子の影響がp型ウェルPW(05)に及ぶことが回避される。

【0077】

これに対し図9Aに示す比較例のように深いn型ウェルDNWを全く形成しなかった場合には、前記p型ウェルPW(01)に生じた荷電粒子入来の影響は、図10に示すようなメカニズムにより、同じカラム群のp型ウェルPW(02),PW(03)のみならず、隣接するカラム群のp型ウェルPW(04)、PW(05)などにも及ぶおそれがある。

【0078】

図10を参照するに、p型ウェルPW(01)において荷電粒子により電子−正孔対が発生し、正孔のみが残った場合、この正孔が前記p型のシリコン基板11を介してp型ウェルPW(04)に到達すると、その電位を上げるように作用し、前記p型ウェルPW(04)に形成されていたnチャネルMOSトランジスタよりなるドライバトランジスタDT1あるいはDT2の寄生バイポーラトランジスタが導通するおそれがある。このような導通が生じると、当該SRAMのメモリセルに保持されているデータは反転してしまう。

【0079】

また図9Bに示す別の比較例のように前記深いn型ウェルDNWを、隣接する二つのカラム群のn型ウェルおよびp型ウェルの下に連続して形成した場合には、例えばn型ウェルNW(01)に荷電粒子が入来してソフトエラーが発生すると、その影響が隣接するカラム群のn型ウェル、例えばNW(05)やNW(06)にまで及び、これらのn型ウェルに形成されているpチャネルMOSトランジスタよりなるロードトランジスタLT1あるいはLT2を導通させ、当該メモリセルに保持されているデータを反転させてしまうおそれがある。

【0080】

このようにソフトエラーが隣接する二つのカラム群で発生すると、図5および図6A,図6Bで説明したエラー検出および訂正回路ECCにおいて2ビットのエラー訂正を行う必要があるが、このような2ビットのエラー訂正はSRAMの面積効率を低下させるため望ましくない。

【0081】

本実施形態によれば、隣接する第1のカラム群と第2のカラム群のいずれか一方に前記深いウェルを行方向ないしワード線方向WLに、一つのカラム群の長さないし寸法を超えないように形成することにより、隣接するカラム群の間でp型ウェルどうし、あるいはn型ウェルどうしの導通を遮断することが可能となり、隣接する二つのカラム群で同時に選択されるメモリセルカラムの一方でソフトエラーが発生しても、それが他方に伝搬することがない。このため本実施形態によれば、このような場合でも1ビットのエラー検出および訂正回路ECCを使ってエラーを訂正することが可能となる。

【0082】

なおこのような荷電粒子の入射が一のカラム群の一のメモリセルで発生しても、同じカラム群中の他のメモリセルはカラム選択回路CS1〜CS3により選択されていないため、データの読み出しに影響は生じない。これら他のメモリセルにおいて生じたエラーは、それが選択された時点で、図5のエラー検出および訂正回路ECCにより訂正することができる。

【0083】

本実施形態は、特に前記活性領域11A1,11A2,11B1,11B2が45nm以下の設計ルールで形成される微細化されたSRAMにおいて有用である。

【0084】

なおこのような構成では、例えばカラム群CG1のメモリセルC(01)p型ウェルあるいはn型ウェルが、隣のカラム群CG2を超えたもう一つとなりのカラム群CG3のメモリセルC(09)の対応するp型ウェルあるいはn型ウェル導通するのは避けられないが、例えばメモリセルC(09)はメモリセルC(01)から、1カラム群に相当する距離だけ離れているため、メモリセルC(09)がメモリセルC(01)と同時に選択されても、本実施形態において想定するようにSRAMの微細化が進んでも、メモリセルC(09)においてソフトエラーが発生するおそれはない。

【0085】

なお本実施形態において前記深いn型ウェルDNW1,DNW2・・・を、図8Cに示すようにそれぞれの端が対応するカラム群の端に一致するように形成することも可能である。

【0086】

図11は、前記図8A〜図8Cのカラム選択回路CS1の構成を示す回路図である。なおカラム選択回路CS2,CS3の構成はカラム選択回路CS1のものと同じであり、説明を省略する。

【0087】

図11を参照するに、カラム選択回路CS1はビット線BL01,/BL01,/BL02,/BL02,BL03,/BL03,BL04,/BL04を共通ビット線VBLおよび/VBLに接続するトランジスタTr0,/Tr0,Tr1,/Tr1,Tr2,/Tr2,Tr3,/Tr3を含み、アドレスデータの一部、例えばアドレスデータA0,A1を供給されるカラムデコーダCDECより対応する選択信号E0〜E3をそれぞれラインD0〜D1上に供給され、ラインD0上の選択信号E0がハイである場合にビット線BL01および/BL01を、それぞれトランジスタT0および/T0および共通ビット線VBLおよび/VBLを介してセンスアンプSA1に供給する。同様に前記カラム選択回路CS1は、ラインD1上の選択信号E1がハイである場合にビット線BL02および/BL02を、それぞれトランジスタT1および/T1および共通ビット線VBLおよび/VBLを介してセンスアンプSA1に供給し、ラインD2上の選択信号E2がハイである場合にビット線BL03および/BL03を、それぞれトランジスタT2および/T2および共通ビット線VBLおよび/VBLを介してセンスアンプSA1に供給し、さらにラインD3上の選択信号E3がハイである場合にビット線BL04および/BL04を、それぞれトランジスタT3および/T3および共通ビット線VBLおよび/VBLを介してセンスアンプSA1に供給する。

【0088】

また前記カラムデコーダは、一方の入力端子にアドレスデータA0を供給され他方の入力端子にアドレスデータA1を供給されるAND回路AND1と、一方の入力端子に前記アドレスデータA0を、インバータINV0を介して供給され他方の入力端子に前記アドレスデータA1を供給されるAND回路AND2と、一方の入力端子に前記アドレスデータA0を供給され他方の入力端子に前記アドレスデータを、インバータINV1を介して供給されるAND回路AND3と、一方の入力端子に前記アドレスデータA0を、前記インバータINV0を介して供給され他方の入力端子に前記アドレスデータを、インバータINV1を介して供給されるAND回路AND4と、を含み、前記入力データA0およびA1の組み合わせにより図12の真理値表に示すような選択信号E0〜E4を形成する。

【0089】

かかる構成により、カラム選択回路CS1により、入来するアドレスデータA0,A1の組み合わせに従って、4本のビット線BL01〜BL04の一つ、従ってこれに対応するメモリセルカラムを選択することが可能である。

【0090】

本実施形態において、例えばメモリセルC(01)においてソフトエラーが発生した場合、同じカラム群に属するメモリセルC(02)〜C(04)においても同様なソフトエラーが発生するおそれがあるが、これらのメモリセルは上記カラム選択回路CS1の作用により非選択であり、読み出しデータにエラーが含まれることはない。またこれらのメモリセルが選択される場合は、ビット線BL(01)に対応するメモリセルカラムの場合と同様に、エラー検出および訂正回路ECCを使ってエラーを訂正することができる。

【0091】

なお図11において前記ビット線BL01,BL02,BL03,BL04は、図5におけるビット線BL(01),BL(02),BL(03).BL(04)にそれぞれ対応する。

【0092】

図13は、本実施形態における前記深いn型ウェルDNWの行方向ないしワード線方向WLへの寸法とカラム群の行方向ないしワード線方向WLへの寸法との関係を示す平面図である。ただし図13はビット線BL(01)〜BL(12)までを示しており、これに対応してカラム選択回路CS1,CS2,CS3が示されている。図5に合わせて図13においても、カラム選択回路CS1に対応するビット線B(01)〜BL(04)までのカラム群をCG1,カラム選択回路CS2に対応するビット線B(05)〜BL(08)までのカラム群をCG2、カラム選択回路CS3に対応するビット線B(09)〜BL(12)までのカラム群をCG3と記す。

【0093】

図13を参照するに、図8A,図8Bの深いn型ウェルDNW1は太枠で囲んだようにカラム群CG2に対応して、かつ一つのカラム群に等しい面積、ないし行方向への寸法で形成されているため、例えばメモリセルC05を構成するp型ウェルは、同時に選択されるメモリセルC01あるいはC09のp型ウェルに対し、前記深いn型ウェルDNWにより分離されている。

【0094】

また前記深いn型ウェルDNWの面積ないし行方向への寸法が一つのカラム群の面積ないし行方向への寸法を超えることがないため、例えばメモリセルC09のn型ウェルが、同時に選択されるメモリセルC05のn型ウェルに、前記深いn型ウェルDNWを介して導通することもない。

【0095】

先にも説明したように、図13などの平面図において、各p型ウェルおよびn型ウェルのビット線方向の寸法は同一であるので、図中に示した行方向すなわちワード線方向へのブラケットの長さは、対応するカラム群あるいはウェルDNWの面積に対応している。

【0096】

なお上記の説明より、前記深いn型ウェルDNWは、その行方向への寸法が一つのカラム群の行方向への寸法を超えない限り、必ずしもいずれかのカラム群、図13の例ではカラム群CG2に一致して設ける必要はなく、図14の変形例に示すように任意にずらして設けることが可能であることは明らかである。

【0097】

ただし図13の本実施形態においても、また図14の変形例においても、一つの深いn型ウェルDNW1と、その隣の深いn型ウェルDNW2とは、一つのカラム群に対応する距離を超えないように、従って行方向に一つのカラム群を超える寸法の空白を生じないように配置される。

【0098】

なお本実施形態の場合、図8BよりわかるようにメモリセルカラムCG1の端に位置するメモリセルC(04)の一方のp型ウェルPW(03)に荷電粒子が入射した場合、前記p型ウェルPW(03)に生じた電位の変動が前記p型シリコン基板11を介して同時に選択されるメモリセルC(08)のp型ウェルPW(08)に影響し、ソフトエラーが例外的に伝搬するおそれがある。またメモリセルC(04)を構成するn型ウェルNW(04)に荷電粒子が入射した場合、当該ウェルに生じた電位の変動が前記深いn型ウェルDNW1を介して、同時に選択されるメモリセルC(08)のn型ウェルNW(08)に影響し、同様な例外的なソフトエラーの伝搬が生じるおそれがある。同様なソフトエラーの例外的な伝搬は、図8Cの実施形態においても生じうる。

【0099】

しかし、それ以外のウェルにおける荷電粒子の入来の影響は、本実施形態においては遮断されており、SRAM10は、図9Aや図9Bに示すような、深いn型ウェルDNWを一切形成しない構成や、メモリセルアレイの下に連続して形成する構成に比べると、ソフトエラー耐性が格段に向上している。

【0100】

このような例外的なソフトエラーの伝搬経路をも遮断できる構成については、以下の実施形態で説明する。

【0101】

[第2の実施形態]

図15および図16は、第2の実施形態によるSRAM20の構成を示す、それぞれ平面図および断面図である。ただし図中、先に説明した部分に対応する部分には同一の参照符号を付し、説明を省略する。図16の断面図は、図15中、線D−D’に沿った断面を示している。図16においても、前記図8A〜8Cと同様に、シリコン基板11上のゲート電極などについては、図示を省略する。

【0102】

図15,図16を参照するに、本実施形態ではカラム選択回路CS2、すなわちビット線BL(05)〜BL(08)に対応するカラム群CG2において、それぞれのp型ウェルの下に限定して、一つのp型ウェルだけをカバーする幅で深いn型ウェルDNW1,DNW2,DNW3,DNW4を、相互に分離して形成している。

【0103】

かかる構成によれば、一つおきに形成されたカラム群CG2,CG4・・・において、それぞれのp型ウェル、例えばPW(04)、PW(05),PW(06)・・・がp型シリコン基板11から、前記深いn型ウェルDNW1,DNW2,DNW3,DNW4のいずれかにより分離され、かつこれらの深いn型ウェルDNW1,DNW2,DNW3,DNW4も、相互に分離されているため、先に図9A,図9Bで説明したような、p型シリコン基板11や深いn型ウェルDNWを介したソフトエラーの伝搬の問題は生じない。

【0104】

先の実施形態の場合、先に図8Bや図8Cで説明したように例外的にソフトエラーの伝搬を許してしまう場合があるが、本実施形態ではこのような例外的なソフトエラーの伝搬経路をも遮断することができる。

【0105】

なおこのような相互に分離した深いn型ウェルDNW1,DNW2,DNW3,DNW4は、一つおきのカラム群CG2,CG4・・・に限定されず、全てのカラム群CG1,CGG2,CG3・・・に、すなわちメモリセルアレイ全体にわたって形成してもよい。

【0106】

[第3の実施形態]

図17および図18は第3の実施形態によるSRAM30の構成を示す。ただし図17および図18中、先に説明した部分には同一の参照符号を付し、説明を省略する。図18においても、前記図8A〜8Cと同様に、シリコン基板11上のゲート電極などについては、図示を省略する。

【0107】

図17,図18を参照するに、本実施形態では各々行方向に、一つのカラム群から1セルカラム分の寸法を差し引いた、3セルカラム分の寸法を有する深いn型ウェルDNW1〜DNW3が、それぞれのカラム群CG1,CG2,CG3に対応して、かつ1メモリセル分の間隔を開けて形成されている。さらに本実施形態ではカラム選択回路CS2が、ビット線BL(05)が選択される際に、メモリセルC(06)を含むメモリセルカラムが選択されるように、またビット線BL(06)が選択される際にメモリセルC(05)を含むメモリセルカラムが選択されるように、構成されている。

【0108】

一方、カラム選択回路CS1およびカラム選択回路CS3では、前記カラム選択回路CS2においてビット線BL(05)が選択される場合に、それぞれビット線BL(01)およびビット線BL(09)が選択され、これにより、メモリセルC(01)を含むメモリセルカラムおよびメモリセルC(09)を含むメモリセルカラムが選択されるように構成されている。

【0109】

このようにカラム選択回路CS1〜CS3を構成することにより、図18においてメモリセルC(01)が選択された場合、同時に選択されるメモリセルC(06)のp型ウェルは、前記深いn型ウェルDNW2によりp型シリコン基板11から完全に分離され、メモリセルC(01)とC(06)の間においてソフトエラーの伝搬は生じない。また図18においてメモリセルC(02)が選択された場合、同時にメモリセルC(05)が選択されるが、メモリC(02)においてp型ウェルは前記深いn型ウェルDNW1により前記p型シリコン基板11から完全に分離されており、やはりメモリセルC(02)とC(05)の間にソフトエラーの伝搬は生じない。尚、本実施形態において、深いn型ウェルDNW1〜DNW3は、各々行方向に一つのカラム群から2セルカラム分の寸法を差し引いた2セルカラム分の寸法以上の幅を有する必要がある。

【0110】

図19は、前記SRAM30の構成を、カラム選択回路CS4および対応するカラム群CG4まで含めて示すブロック図である。

【0111】

図19を参照するに、カラム選択回路CS1〜CS4にはカラム群CG1〜CG4がそれぞれ対応し、カラム選択回路CS2から始めて一つおきに現れるカラム選択回路に、すなわちカラム選択回路CS2,CS4・・・において、ビット線の選択の際に、最初のビット線と次のビット線とが入れ替えられており、また最後のビット線とその一つ前のビット線とが入れ替えられている。例えばカラム選択回路CS2では、ビット線BL(05)とBL(06)とが入れ替わり、ビット線BL(08)とビット線BL(07)とが入れ替わっている。またカラム選択回路CS4ではビット線BL(13)とビット線BL(14)とが入れ替わっており、またビット線BL(16)とビット線BL(15)が入れ替わっている。

【0112】

このような構成は、図18などの断面構造において、一つのメモリセルが一つのn型ウェルと、その両側の半分ずつ、二つのp型ウェルとにより形成されているために設けられている。例えばメモリセルC(01)は、n型ウェルNW(01)と、左隣のメモリセルと共有されているp型ウェルPW(00)、および右隣のメモリセルC(02)と共有されているp型ウェルP(01)とより構成されている。本実施形態では、深いn型ウェルの端部に形成されているメモリセルのうち、前記深いn型ウェルから見て外端部に位置するp型ウェル、例えばカラム群CG1の場合p型ウェルP(00)を含むメモリセルC(01)が選択される場合に、同時に選択される隣接カラム群CG2では対応するメモリセルC(05)を選択せず、当該カラム群CG2における深いn型ウェルDWN2から見て一つ内側のメモリセル、すなわちメモリセルC(06)を選択することで、このような外端部のp型ウェルPW(00)およびPW(04)どうしの導通を回避している。

【0113】

同様に本実施形態では、例えばカラム群CG1において深いn型ウェルDNW1から見て外端のp型ウェルPW(04)を含むメモリセルC(04)が選択される場合に、同時に選択される隣接カラム群CG2では対応するメモリセルC(08)を選択せず、当該カラム群CG2における深いn型ウェルDWN2から見て一つ内側のメモリセル、すなわちメモリセルC(07)を選択することで、このような外端部のp型ウェルPW(04)およびPW(08)どうしの導通を回避している。

【0114】

その結果、前記カラム選択回路CS2あるいはCS4においては、ビット線BL(05)はメモリセルC(06)を含むメモリセルカラムMCC(06)に接続されビット線BL(06)はメモリセルC(05)を含むメモリセルカラムMC(05)に接続される。またビット線BL(08)はメモリセルC(07)を含むメモリセルカラムMCC(07)に接続されビット線BL(07)はメモリセルC(08)を含むメモリセルカラムMCC(08)に接続される。さらにビット線BL(13)はメモリセルC(14)を含むメモリセルカラムMCC(14)に接続されビット線BL(14)はメモリセルC(13)を含むメモリセルカラムMC(13)に接続される。またビット線BL(16)はメモリセルC(15)を含むメモリセルカラムMCC(15)に接続されビット線BL(15)はメモリセルC(16)を含むメモリセルカラムMCC(16)に接続される。

【0115】

これに対しカラム選択回路CS1においては、ビット線BL(01)がメモリセルC(01)を含むメモリセルカラムMCC(01)に接続され、ビット線BL(02)がメモリセルC(02)を含むメモリセルカラムMC(02)に接続され、ビット線BL(03)がメモリセルC(03)を含むメモリセルカラムMCC(03)に接続されビット線BL(04)がメモリセルC(04)を含むメモリセルカラムMCC(04)に接続されるのがわかる。またメモリカラム選択回路CS3については、ビット線BL(09)がメモリセルC(09)を含むメモリセルカラムMCC(09)に接続され、ビット線BL(10)がメモリセルC(10)を含むメモリセルカラムMC(10)に接続され、ビット線BL(11)がメモリセルC(11)を含むメモリセルカラムMCC(11)に接続され、ビット線BL(12)がメモリセルC(12)を含むメモリセルカラムMCC(12)に接続される。

【0116】

本実施形態ではカラム群CG1においてメモリセルC(01)を含むメモリセルカラムMCC(01)がカラム選択回路CS1により選択される際、隣のカラム群CG2においてはメモリセルC(06)を含むメモリセルカラムMCC(06)が選択される。さらに隣のカラム群CG3においてはメモリセルC(09)を含むメモリセルカラムMCC(09)が選択される一方、そのさらに隣のカラム群CG4においては、メモリセルC(14)を含むカラム群MCC(14)が選択される。

【0117】

この場合、メモリセルC(06)を構成するp型ウェルおよびn型ウェルはそのどちらも、メモリセルC(01)を構成する型ウェルおよびn型ウェル、あるいはメモリセルC(09)を構成するp型ウェルおよびn型ウェルから前記深いn型ウェルDNW2により分離されており、いずれかのメモリセルで生じた荷電粒子の入射が他のメモリセルに影響することはない。

【0118】

同様にカラム群CG1においてメモリセルC(02)を含むメモリセルカラムMCC(02)がカラム選択回路CS1により選択される際、隣のカラム群CG2においてはメモリセルC(05)を含むメモリセルカラムMCC(05)が選択される。さらに隣のカラム群CG3においてはメモリセルC(10)を含むメモリセルカラムMCC(10)が選択される一方、そのさらに隣のカラム群CG4においては、メモリセルC(13)を含むカラム群MCC(13)が選択される。

【0119】

この場合、メモリセルC(05)を構成するp型ウェルおよびn型ウェルはどちらも、メモリセルC(02)を構成するp型ウェルおよびn型ウェル、あるいはメモリセルC(13)を構成するp型ウェルおよびn型ウェルから前記深いn型ウェルDNW1あるいはDNW3により分離されており、いずれかのメモリセルで生じた荷電粒子の入射が他のメモリセルに影響することはない。

【0120】

同様にカラム群CG1においてメモリセルC(03)を含むメモリセルカラムMCC(03)がカラム選択回路CS1により選択される際、隣のカラム群CG2においてはメモリセルC(08)を含むメモリセルカラムMCC(08)が選択される。さらに隣のカラム群CG3においてはメモリセルC(11)を含むメモリセルカラムMCC(11)が選択される一方、そのさらに隣のカラム群CG4においては、メモリセルC(16)を含むカラム群MCC(16)が選択される。

【0121】

この場合、メモリセルC(08)を構成するp型ウェルおよびn型ウェルはどちらも、メモリセルC(03)を構成するp型ウェルおよびn型ウェル、あるいはメモリセルC(11)を構成するp型ウェルおよびn型ウェルから、前記深いn型ウェルDNW1,DNW2,DNW3により分離されており、いずれかのメモリセルで生じた荷電粒子の入射が他のメモリセルに影響することはない。

【0122】

同様にカラム群CG1においてメモリセルC(04)を含むメモリセルカラムMCC(04)がカラム選択回路CS1により選択される際、隣のカラム群CG2においてはメモリセルC(07)を含むメモリセルカラムMCC(07)が選択される。さらに隣のカラム群CG3においてはメモリセルC(12)を含むメモリセルカラムMCC(12)が選択される一方、そのさらに隣のカラム群CG4においては、メモリセルC(15)を含むカラム群MCC(15)が選択される。

【0123】

この場合、メモリセルC(07)を構成するp型ウェルおよびn型ウェルはどちらも、メモリセルC(04)を構成するp型ウェルおよびn型ウェル、あるいはメモリセルC(112)を構成するp型ウェルおよびn型ウェルから、前記深いn型ウェルDNW1,DNW2,DNW3により分離されており、いずれかのメモリセルで生じた荷電粒子の入射が他のメモリセルに影響することはない。

【0124】

このように本実施形態のSRAM30では、p型シリコン基板11を介したソフトエラーの伝搬路が深いn型ウェルDNW1,DNW2・・・により完全に遮断され、また前記深いn型ウェルDNW1,DNW2・・・を介したソフトエラーの伝搬路も完全に遮断され、ソフトエラーに対する耐性が、第1の実施形態の場合と比較すると、さらに向上する。

【0125】

なお図19において、メモリセルカラムMCC(01)〜MCC(16)は、図3や図4に示すメモリセルアレイの一部を示している。

【0126】

また図18の断面図よりわかるように、本実施形態では一つの深いn型ウェル、例えばDNW1と、これに隣接する深いn型ウェルDNW2との間に、メモリセル一つ分の寸法の切れ目が存在しており、前記深いn型ウェルDNW1〜DNW3をイオン注入により形成する際に課せられる精度上の制約が緩和され、第2の実施形態と比較してSRAMを含む半導体装置の製造歩留まりを向上させることができる。

【0127】

[第4の実施形態]

図20A,図20Bは、前記第3の実施形態によるカラム選択回路構成をさらに変形した第4の実施形態によるSRAM40の構成を示す。ただし図20Aは前記図19と同様なメモリセルカラム選択のための回路図を示し、図20Bは本実施形態において使われる深いn型ウェルDNW1,DNW2を示す断面図である。図20Bの断面図においても、前記図8A〜8Cと同様に、シリコン基板11上のゲート電極などについては、図示を省略する。

【0128】

ここで図20Bは先の第3の実施形態の断面図と同じであるが、簡単のためシリコン基板11、p型ウェルPW(00)〜PW(16)、n型ウェルNW(01)〜NW(16)、および深いn型ウェルDNW1,DNW2、およびメモリセルC(01)〜C(16)のみを、模式化して示している。素子分離構造11Iの図示は省略している。

【0129】

図20Aを参照するに、本実施形態ではカラム群CG1においてメモリセルC(01)を含むメモリセルカラムMCC(01)がカラム選択回路CS1により選択される際、隣のカラム群CG2においてはメモリセルC(07)を含むメモリセルカラムMCC(07)が選択される。さらに隣のカラム群CG3においてはメモリセルC(09)を含むメモリセルカラムMCC(09)が選択される一方、そのさらに隣のカラム群CG4においては、メモリセルC(15)を含むカラム群MCC(15)が選択される。

【0130】

この場合、メモリセルC(07)を構成するp型ウェルおよびn型ウェルはどちらも、メモリセルC(01)を構成する型ウェルおよびn型ウェル、あるいはメモリセルC(15)を構成するp型ウェルおよびn型ウェルから前記深いn型ウェルDNW1,DNW2,DNW3により分離されており、いずれかのメモリセルで生じた荷電粒子の入射が他のメモリセルに影響することはない。

【0131】

同様にカラム群CG1においてメモリセルC(02)を含むメモリセルカラムMCC(02)がカラム選択回路CS1により選択される際、隣のカラム群CG2においてはメモリセルC(05)を含むメモリセルカラムMCC(05)が選択される。さらに隣のカラム群CG3においてはメモリセルC(09)を含むメモリセルカラムMCC(09)が選択される一方、そのさらに隣のカラム群CG4においては、メモリセルC(13)を含むカラム群MCC(13)が選択される。

【0132】

この場合、メモリセルC(05)を構成するp型ウェルおよびn型ウェルはどちらも、メモリセルC(02)を構成するp型ウェルおよびn型ウェル、あるいはメモリセルC(13)を構成するp型ウェルおよびn型ウェルから前記深いn型ウェルDNW1,DNW2,DNW3により分離されており、いずれかのメモリセルで生じた荷電粒子の入射が他のメモリセルに影響することはない。

【0133】

同様にカラム群CG1においてメモリセルC(03)を含むメモリセルカラムMCC(03)がカラム選択回路CS1により選択される際、隣のカラム群CG2においてはメモリセルC(08)を含むメモリセルカラムMCC(08)が選択される。さらに隣のカラム群CG3においてはメモリセルC(11)を含むメモリセルカラムMCC(11)が選択される一方、そのさらに隣のカラム群CG4においては、メモリセルC(16)を含むカラム群MCC(16)が選択される。

【0134】

この場合、メモリセルC(08)を構成するp型ウェルおよびn型ウェルはどちらも、メモリセルC(03)を構成するp型ウェルおよびn型ウェル、あるいはメモリセルC(11)を構成するp型ウェルおよびn型ウェルから、前記深いn型ウェルDNW1,DNW2,DNW3により分離されており、いずれかのメモリセルで生じた荷電粒子の入射が他のメモリセルに影響することはない。

【0135】

同様にカラム群CG1においてメモリセルC(04)を含むメモリセルカラムMCC(04)がカラム選択回路CS1により選択される際、隣のカラム群CG2においてはメモリセルC(06)を含むメモリセルカラムMCC(06)が選択される。さらに隣のカラム群CG3においてはメモリセルC(12)を含むメモリセルカラムMCC(12)が選択される一方、そのさらに隣のカラム群CG4においては、メモリセルC(14)を含むカラム群MCC(14)が選択される。

【0136】

この場合、メモリセルC(06)を構成するp型ウェルおよびn型ウェルはどちらも、メモリセルC(04)を構成するp型ウェルおよびn型ウェル、あるいはメモリセルC(112)を構成するp型ウェルおよびn型ウェルから、前記深いn型ウェルDNW1,DNW2,DNW3により分離されており、いずれかのメモリセルで生じた荷電粒子の入射が他のメモリセルに影響することはない。

【0137】

このように本実施形態のSRAM40でも、p型シリコン基板11を介したソフトエラーの伝搬路が深いn型ウェルDNW1,DNW2・・・により完全に遮断され、また前記深いn型ウェルDNW1,DNW2・・・を介したソフトエラーの伝搬路も完全に遮断され、ソフトエラーに対する耐性が、第1の実施形態の場合と比較すると、さらに向上する。

【0138】

また図20Bの断面図よりわかるように、本実施形態では一つの深いn型ウェル、例えばDNW1と、これに隣接する深いn型ウェルDNW2との間に、メモリセル一つ分の切れ目が存在しており、前記深いn型ウェルDNW1〜DNW3をイオン注入により形成する際に課せられる精度上の制約が緩和され、第2の実施形態と比較してSRAMを含む半導体装置の製造歩留まりを向上させることができる。

【0139】

[第5の実施形態]

図21A,図21Bは第5の実施形態によるSRAM50の構成を示す。ただし図21Aは前記図19と同様なメモリセルカラム選択のための回路図を示し、図21Bは本実施形態において使われる深いn型ウェルDNW1〜DNW5を示す断面図である。図21Bの断面図においても、前記図8A〜8Cと同様に、シリコン基板11上のゲート電極などについては、図示を省略する。

【0140】

最初に図21Bの断面図を参照するに、本実施形態においても各々の深いn型ウェルDNW1〜DNW5は行方向に3セル分の寸法を有し、1メモリセル分の間隔を開けて形成されており、ただ図20Bの断面図と比較すると、各々のカラム群に対して深いn型ウェルDNW1〜DNW5の位置関係が、2メモリセル分だけワード線方向にずらされているのがわかる。

【0141】

本実施形態では、図21Aに示すように、先の図19と同じカラム選択構成が使われており、カラム選択回路CS2から始めて一つおきに現れるカラム選択回路に、すなわちカラム選択回路CS2,CS4・・・において、ビット線の選択の際に、最初のビット線と次のビット線とが入れ替えられており、また最後のビット線とその一つ前のビット線とが入れ替えられている。例えばカラム選択回路CS2では、ビット線BL(05)とBL(06)とが入れ替わり、ビット線BL(08)とビット線BL(07)とが入れ替わっている。またカラム選択回路CS4ではビット線BL(13)とビット線BL(14)とが入れ替わっており、またビット線BL(16)とビット線BL(15)が入れ替わっている。

【0142】

そこでカラム群CG1においてメモリセルC(01)を含むメモリセルカラムMCC(01)がカラム選択回路CS1により選択される際、隣のカラム群CG2においてはメモリセルC(06)を含むメモリセルカラムMCC(06)が選択される。さらに隣のカラム群CG3においてはメモリセルC(09)を含むメモリセルカラムMCC(09)が選択される一方、そのさらに隣のカラム群CG4においては、メモリセルC(14)を含むカラム群MCC(14)が選択される。

【0143】

この場合、メモリセルC(06)を構成するp型ウェルおよびn型ウェルはそのどちらも、メモリセルC(01)を構成する型ウェルおよびn型ウェル、あるいはメモリセルC(09)を構成するp型ウェルおよびn型ウェルから前記深いn型ウェルDNW2により分離されており、いずれかのメモリセルで生じた荷電粒子の入射が他のメモリセルに影響することはない。

【0144】

同様にカラム群CG1においてメモリセルC(02)を含むメモリセルカラムMCC(02)がカラム選択回路CS1により選択される際、隣のカラム群CG2においてはメモリセルC(05)を含むメモリセルカラムMCC(05)が選択される。さらに隣のカラム群CG3においてはメモリセルC(09)を含むメモリセルカラムMCC(09)が選択される一方、そのさらに隣のカラム群CG4においては、メモリセルC(13)を含むカラム群MCC(13)が選択される。

【0145】

この場合、メモリセルC(05)を構成するp型ウェルおよびn型ウェルはどちらも、メモリセルC(02)を構成するp型ウェルおよびn型ウェル、あるいはメモリセルC(13)を構成するp型ウェルおよびn型ウェルに対し、前記深いn型ウェルDNW1あるいはDNW3により分離されており、いずれかのメモリセルで生じた荷電粒子の入射が他のメモリセルに影響することはない。

【0146】

同様にカラム群CG1においてメモリセルC(03)を含むメモリセルカラムMCC(03)がカラム選択回路CS1により選択される際、隣のカラム群CG2においてはメモリセルC(08)を含むメモリセルカラムMCC(08)が選択される。さらに隣のカラム群CG3においてはメモリセルC(11)を含むメモリセルカラムMCC(11)が選択される一方、そのさらに隣のカラム群CG4においては、メモリセルC(16)を含むカラム群MCC(16)が選択される。

【0147】

この場合、メモリセルC(08)を構成するp型ウェルおよびn型ウェルはどちらも、メモリセルC(03)を構成するp型ウェルおよびn型ウェル、あるいはメモリセルC(11)を構成するp型ウェルおよびn型ウェルから、前記深いn型ウェルDNW1,DNW2,DNW3により分離されており、いずれかのメモリセルで生じた荷電粒子の入射が他のメモリセルに影響することはない。

【0148】

同様にカラム群CG1においてメモリセルC(04)を含むメモリセルカラムMCC(04)がカラム選択回路CS1により選択される際、隣のカラム群CG2においてはメモリセルC(07)を含むメモリセルカラムMCC(07)が選択される。さらに隣のカラム群CG3においてはメモリセルC(12)を含むメモリセルカラムMCC(12)が選択される一方、そのさらに隣のカラム群CG4においては、メモリセルC(15)を含むカラム群MCC(15)が選択される。

【0149】

この場合、メモリセルC(07)を構成するp型ウェルおよびn型ウェルはどちらも、メモリセルC(04)を構成するp型ウェルおよびn型ウェル、あるいはメモリセルC(112)を構成するp型ウェルおよびn型ウェルから、前記深いn型ウェルDNW2により分離されており、いずれかのメモリセルで生じた荷電粒子の入射が他のメモリセルに影響することはない。

【0150】

本実施形態のSRAM50でも、前記第3の実施形態の場合と同様に、p型シリコン基板11を介したソフトエラーの伝搬路が深いn型ウェルDNW1,DNW2・・・により完全に遮断され、また深いn型ウェルDNW1,DNW2・・・を介したソフトエラーの伝搬路も完全に遮断され、ソフトエラーに対する耐性が、第1の実施形態の場合と比較すると、さらに向上する。

【0151】

また図21Bの断面図よりわかるように、本実施形態でも一つの深いn型ウェル、例えばDNW1と、これに隣接する深いn型ウェルDNW2との間に、メモリセル一つ分の切れ目が存在しており、前記深いn型ウェルDNW1〜DNW3をイオン注入により形成する際に課せられる精度上の制約が緩和され、先に説明した第2の実施形態と比較してSRAMを含む半導体装置の製造歩留まりを向上させることができる。

【0152】