ストアマージ装置、情報処理装置、ストアマージ方法およびプログラム

【課題】主記憶上の異なるアドレスに対するストア命令が中央処理装置から出力された場合にも記憶装置へのアクセスを抑える。

【解決手段】ストアバッファ回路12が、複数のストア命令を記憶しておく。そして、ストアバッファ回路12は、中央処理装置60からストア命令が出力されると、当該ストア命令と主記憶装置70上で同一のアドレスに対するストア命令を記憶しているか否かを判定し、記憶していると判定した場合は、この記憶しているストア命令をマージ回路11に出力する。これにより、主記憶装置70(記憶装置)へのアクセスを抑えることができる。

【解決手段】ストアバッファ回路12が、複数のストア命令を記憶しておく。そして、ストアバッファ回路12は、中央処理装置60からストア命令が出力されると、当該ストア命令と主記憶装置70上で同一のアドレスに対するストア命令を記憶しているか否かを判定し、記憶していると判定した場合は、この記憶しているストア命令をマージ回路11に出力する。これにより、主記憶装置70(記憶装置)へのアクセスを抑えることができる。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、ストアマージ装置、ストアマージ装置を具備する情報処理装置、ストアマージ方法およびプログラムに関する。

【背景技術】

【0002】

記憶装置へのアクセス頻度を抑える方法の1つに、ストアマージ方法と呼ばれる方法がある。ストアマージ方法では、ストアマージ装置が、記憶装置の同一のライン(記憶装置またはキャッシュがデータの読み書きを行う際の単位ブロック)への複数のストア命令(書込命令)を1つに纏めてから記憶装置に書き込むことにより、記憶装置へのアクセス頻度を抑える。以下では、この複数のストア命令を1つに纏める処理を「マージ処理」と称する。

【0003】

例えば、特許文献1に示されるストアマージ方法では、ストアデータ制御装置(ストアマージ装置)が、キュー(Queue)構造のストアバッファと、同じくキュー構造のライトバッファとを備える。そして、ストアバッファがストア命令を格納し、格納時刻の早いストア命令から順にライトバッファに転送する。

ストア命令の転送を受けたライトバッファは、転送されたストア命令を、BOQ(ライトバッファのデータ格納領域のうち、最後にデータを格納した領域)、または、BOQの次のデータ格納領域のいずれかに格納する。具体的には、転送されたストア命令とBOQのストア命令とが、主記憶上の同一のアドレスに対するストア命令である場合は、マージ処理可能であると判定し、ライトバッファは、転送されたストア命令をBOQに格納することによりマージ処理を行う。一方、転送されたストア命令とBOQのストア命令とが、主記憶上の異なるアドレスに対するストア命令である場合は、マージ処理不可であると判定し、ライトバッファは、転送されたストア命令をBOQの次のデータ格納領域に格納し、この新たにストア命令を格納した領域をBOQとする。また、ライトバッファは、格納時刻の早いストア命令から順に、一次キャッシュ(記憶装置)に出力する。このように、ライトバッファは、マージ処理済みのストア命令を一次キャッシュに出力することにより、一次キャッシュへのアクセス頻度を抑える。

【先行技術文献】

【特許文献】

【0004】

【特許文献1】特開2006−48163号公報

【発明の概要】

【発明が解決しようとする課題】

【0005】

しかしながら、特許文献1に示されるストアマージ方法では、主記憶上の異なるアドレスに対するストア命令が転送される毎に、ライトバッファがストア命令を格納する領域が変更され、この領域の数だけストア命令が一次キャッシュに出力される。すなわち、特許文献1に示されるストアマージ方法では、主記憶上の異なるアドレスに対するストア命令が転送された場合の記憶装置へのアクセスを抑えることはできない。

【0006】

本発明は、このような事情を考慮してなされたものであり、その目的は、主記憶上の異なるアドレスに対するストア命令が転送された場合にも記憶装置へのアクセスを抑えることができるストアマージ装置、情報処理装置、ストアマージ方法およびプログラムを提供することにある。

【課題を解決するための手段】

【0007】

この発明は上述した課題を解決するためになされたもので、本発明の一態様によるストアマージ装置は、複数のデータを記憶可能なストアバッファ回路と、ストア命令の入力を受けると、前記ストアバッファ回路が記憶する前記複数のデータのいずれかと前記ストア命令のデータとをマージ処理可能か否か判定し、マージ処理可能なデータがあると判定したときは、前記ストアバッファ回路の記憶する複数のデータのうちマージ処理可能と判定した前記データを選択するマージ対象データ選択回路と、前記マージ対象データ選択部が選択したデータと前記ストア命令のデータとをマージ処理し、マージ処理されたデータを前記ストアバッファ回路に書き戻すマージ回路と、前記ストアバッファ回路が前記複数のデータのいずれかを出力するよう指示する追出指示信号を出力する追出制御回路と、を具備することを特徴とする。

【0008】

また、本発明の一態様による情報処理装置は、複数のデータを記憶可能な主記憶装置と、前記主記憶装置へのデータの書込命令であるストア命令を出力する中央処理装置と、複数のデータを記憶可能なストアバッファ回路と、前記中央処理装置から前記ストア命令が出力されると、前記ストアバッファ回路が記憶する前記複数のデータのいずれかと前記ストア命令のデータとをマージ処理可能か否か判定し、マージ処理可能なデータがあると判定したときは、前記ストアバッファ回路の記憶する複数のデータのうちマージ処理可能と判定した前記データを選択するマージ対象データ選択回路と、前記マージ対象データ選択部が選択したデータと前記ストア命令のデータとをマージ処理し、マージ処理されたデータを前記ストアバッファ回路に書き戻すマージ回路と、前記ストアバッファ回路が当該ストアバッファ回路の記憶するデータの前記主記憶装置への書込要求を出力するよう指示する追出指示信号を出力する追出制御回路と、を具備することを特徴とする。

【0009】

また、本発明の一態様によるストアマージ方法は、複数のデータを記憶可能なストアバッファ回路を具備するストアマージ装置のストアマージ方法であって、マージ対象データ選択回路が、ストア命令の入力を受けると、前記ストアバッファ回路が記憶する前記複数のデータのいずれかと前記ストア命令のデータとをマージ処理可能か否か判定し、マージ処理可能なデータがあると判定したときは、前記ストアバッファ回路の記憶する複数のデータのうちマージ処理可能と判定した前記データを選択するマージ対象データ選択ステップと、マージ回路が、前記マージ対象データ選択部が選択したデータと前記ストア命令のデータとをマージ処理し、マージ処理されたデータを前記ストアバッファ回路に書き戻すマージステップと、追出制御回路が、前記ストアバッファ回路が前記複数のデータのいずれかを出力するよう指示する追出指示信号を出力する追出制御ステップと、を具備することを特徴とする。

【0010】

また、本発明の一態様によるプログラムは、複数のデータを記憶可能なストアバッファ回路を具備するストアマージ装置としてのコンピュータにストア命令の入力を受けると、前記ストアバッファ回路が記憶する前記複数のデータのいずれかと前記ストア命令のデータとをマージ処理可能か否か判定し、マージ処理可能なデータがあると判定したときは、前記ストアバッファ回路の記憶する複数のデータのうちマージ処理可能と判定した前記データを選択するマージ対象データ選択ステップと、前記マージ対象データ選択部が選択したデータと前記ストア命令のデータとをマージ処理し、マージ処理されたデータを前記ストアバッファ回路に書き戻すマージステップと、前記ストアバッファ回路が前記複数のデータのいずれかを出力するよう指示する追出指示信号を出力する追出制御ステップと、を実行させるためのプログラムである。

【発明の効果】

【0011】

本発明によれば、主記憶上の異なるアドレスに対するストア命令が転送された場合にも記憶装置へのアクセスを抑えることができる。

【図面の簡単な説明】

【0012】

【図1】本発明の一実施形態における情報処理装置の概略構成を示す構成図である。

【図2】同実施形態において、ストアマージ装置が行うマージ処理の例を示す図である。

【図3】同実施形態におけるロード命令およびストア命令のデータ構成を示す構成図である。

【図4】同実施形態におけるマージ回路の概略構成を示す構成図である。

【図5】同実施形態におけるストアバッファ回路の概略構成を示す構成図である。

【図6】同実施形態におけるライトバッファ回路の構造を示す図である。

【図7】同実施形態におけるタイマ回路への入力とタイマ回路が行う動作との関係を示す表である。

【図8】同実施形態におけるタイマ回路の概略構成を示す構成図である。

【図9】同実施形態における追出制御回路への入力と追出制御回路が行う動作との関係を示す表である。

【図10】同実施形態における追出制御回路の概略構成を示す構成図である。

【図11】同実施形態におけるフル検出回路の概略構成を示す構成図である。

【図12】同実施形態において、中央処理装置からロード命令が出力された際の情報処理装置の動作例を示すシーケンス図である。

【図13】同実施形態において、中央処理装置からストア命令が出力された際の情報処理装置1の動作例を示すシーケンス図である。

【図14】同実施形態において、ストアバッファ回路がストア命令を追い出す際の情報処理装置の動作例を示すシーケンス図である。

【図15】同実施形態における読出回路の処理手順を示すフローチャートである。

【図16】同実施形態におけるストアバッファ回路が記憶するデータ量(ストア命令数)の変化を示すグラフである。

【図17】同実施形態におけるタイマ回路の変形例を示す構成図である。

【発明を実施するための形態】

【0013】

以下、図面を参照して、本発明の実施の形態について説明する。

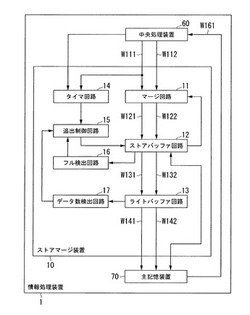

図1は、本発明の一実施形態における情報処理装置の概略構成を示す構成図である。

同図において、情報処理装置1は、ストアマージ装置10と、中央処理装置60と、主記憶装置70とを具備する。ストアマージ装置10は、マージ回路11と、ストアバッファ回路12と、ライトバッファ回路13と、タイマ回路14と、追出制御回路15と、フル検出回路16と、データ数検出回路17とを具備する。また、経路W111、W121、W131、W141は、ストア命令またはロード命令が出力される経路である。経路W112、W122、W132、W142は、ストアデータが出力される経路である。経路W161は、ロードデータが出力される経路である。

【0014】

中央処理装置60は、主記憶装置70に対するデータ書込命令であるストア命令と、書込対象のデータであるストアデータとを出力する。また、中央処理装置60は、主記憶装置70に対するデータ読出命令であるロード命令を出力し、ロード命令に応じたデータを取得する。また、中央処理装置60は、プログラム実行開始時などの処理開始時に、タイマ回路14に対してリセット信号を出力する。

主記憶装置70は、中央処理装置60からのストア命令に従ってデータを記憶し、中央処理装置60からのロード命令に従って、記憶しているデータを出力する。なお、主記憶装置70がキャッシュを備えるようにしてもよい。

【0015】

ストアバッファ回路12は、主記憶装置70よりも高速にアクセス可能なセットアソシアティブ方式の記憶装置を備え、中央処理装置60から出力されるストア命令を記憶する。また、ストアバッファ回路12は、マージ回路11が中央処理装置60から出力されるストアデータに対してマージ処理を行って得られたストアデータを記憶する。また、ストアバッファ回路12は、追出制御回路15から追出指示信号が出力されると、ストア命令およびストアデータをライトバッファ回路13に追い出す。なお、ここでいう「追い出す」処理とは、ストア命令およびストアデータを出力し、当該ストア命令およびストアデータを記憶していた記憶領域に新たなデータを書込可能とする処理である。

【0016】

マージ回路11は、中央処理装置60からストア命令が出力されると、このストア命令と主記憶装置70にて同一のアドレス領域に書き込まれるストア命令のストアデータをストアバッファ回路12から取得し、中央処理装置60から出力されたストア命令のストアデータを、ストアバッファ回路12から読み出されたストアデータに反映させ、反映後のデータをストアバッファ回路12に書き戻す。なお、ここでいう「書き戻す」処理は、ストアバッファ回路12にストアデータを記憶させる処理である。

【0017】

ライトバッファ回路13は、キュー(Queue)構造の記憶装置を備え、ストアバッファ回路12から出力されるストア命令およびストアデータを一時的に保存し、これらストア命令およびストアデータを一定の時間間隔で主記憶装置70に出力する。

【0018】

タイマ回路14は、中央処理装置60からリセット信号が出力された後、中央処理装置60から最初のストア命令またはロード命令が出力されてからの時間をカウントアップする。

フル検出回路16は、ストアバッファ回路12のメモリ使用状況を監視し、メモリ使用状況に応じて、追出処理が必要であることを示すフル検出信号を出力する。

データ数検出回路17は、ライトバッファ回路13の記憶するデータ数を検出する。

追出制御回路15は、タイマ回路のカウントする時間と、フル検出回路16からのフル検出信号と、データ数検出回路17の検出するデータ数とに基づいて、ストアバッファ回路12が追出処理を行う必要があるか否かを判定し、必要ありと判定すると追出処理の実行を指示する追出指示信号を出力する。

【0019】

次に、図2を参照して、ストアデータのマージ処理について説明する。

図2は、ストアマージ装置10が行うマージ処理の例を示す図である。

本実施形態では、中央処理装置60は、ストア命令と共に8バイト(B)のストアデータを出力する。これに対して主記憶装置70は、当該主記憶装置70の記憶領域を64バイト毎に分割したラインを、データの入出力を行う際の単位としている。

【0020】

例えば、中央処理装置60が主記憶装置70に対して24バイトのデータのストアを要求する場合、中央処理装置60は、この24バイトのデータを、図2のストアデータ1、2、3のように8バイト毎に分割し、3つのストア命令を出力する。このストアデータ1、2、3は元々連続するデータなので、主記憶装置70において同一のラインに格納されるべきデータであることが考えられる。

【0021】

この場合、ストアマージ装置10が、中央処理装置60からストア命令を受け取る毎に、主記憶装置70からライン単位でデータを読み出し、ストア命令を反映させたライン単位のデータ書き戻すと、主記憶装置70からのデータ読出と、主記憶装置70へのデータ書込とを、それぞれ3回行う必要がある。

これに対して、ストアマージ装置10が、主記憶装置70からライン単位でデータを読み出し、図2に示すように、中央処理装置60からの3つのストア命令を全て反映させたデータを生成し、生成したデータを書き戻すようにすれば、主記憶装置70からのデータ読出と、主記憶装置70へのデータ書込とが、それぞれ1回で済む。

そこで、ストアマージ装置は、主記憶装置70から読み出したデータに中央処理装置60からのストア命令を反映させた後、直ちに主記憶装置70へストア命令の出力を行わずにストアバッファ回路12に一旦蓄え、後述する一定の事象が発生した後に主記憶装置70にストア命令を出力する。

【0022】

次に、図3を参照してロード命令およびストア命令のデータ構成について説明する。

図3は、ロード命令およびストア命令のデータ構成を示す構成図である。同図に示すように、ロード命令およびストア命令は、いずれも、コマンド格納領域A21と、アドレス格納領域A22〜A24を含み、アドレス格納領域A22〜A24は、上位アドレス格納領域A22と、中位アドレス格納領域A23と、下位アドレス格納領域A24とから構成される。

【0023】

コマンド格納領域A21は、ロード命令とストア命令とを識別するコマンドが格納される領域である。コマンドは、例えば、ロード命令を示す「L」またはストア命令を示す「S」のいずれかの値を取る。

アドレス格納領域A22〜A24には、ロードデータが格納されている主記憶装置70上の記憶領域の先頭アドレス、または、ストアデータが格納されるべき主記憶装置70上の記憶領域の先頭アドレスが格納される。

【0024】

アドレス格納領域A22〜A24のうち、中位アドレス格納領域A23は、ストアバッファ回路12が、後述するエントリを選択するために用いられる。

また、下位アドレス格納領域A24は、中央処理装置60が出力するストアデータの、主記憶装置70のライン中における位置を示し、後述するように、マージ回路11が、中央処理装置60から出力されるストアデータをストアバッファ回路12から読み出されるストアデータに反映させる処理を行うために用いられる。

【0025】

次に、図4を用いてマージ回路11の構成について説明する。

図4は、マージ回路11の概略構成を示す構成図である。同図において、マージ回路11は、シフタ111とマージャ112とを具備する。

シフタ111は、中央処理装置60から経路W111にて出力される命令(ロード命令またはストア命令)を取得すると、当該命令がロード命令かストア命令かを、コマンド格納領域を参照して判定する。

【0026】

そして、ロード命令であると判定した場合は、シフタ111は別段処理を行わない。この場合、中央処理装置60から出力されたロード命令が、そのままストアバッファ回路12に転送される。

一方、取得した命令がストア命令であると判定した場合、マージ回路11は、当該ストア命令に含まれる下位アドレスに基づいて、中央処理装置60から経路W112にて出力されるストアデータ(8バイト)を、主記憶装置70のライン(64バイト)上での位置に合わせてシフトさせる。

【0027】

マージャ112は、ストアバッファ回路12から当該ストア命令に基づいて出力されるライン単位(64バイト)のストアデータを取得し、シフタ111から出力される、シフトされたストアデータをライン単位のストアデータに反映させる。すなわち、マージャ112は、ライン単位64バイトのストアデータのうち、中央処理装置60から出力される8バイトのストアデータに相等する位置のデータを当該8バイトのストアデータのデータに置き換える。

これにより、ストアバッファ回路12からのストアデータと、中央処理装置60からのストアデータとが1つのストアデータにマージされるので、主記憶装置70はマージ後のストアデータのみを記憶すればよい。すなわち、中央処理装置60から出力されたストア命令と、マージ回路11が記憶していたストア命令とが、1つのストア命令にマージされている。

そして、マージャ112は、マージ後のストアデータをストアバッファ回路12に出力することにより、当該ストアデータをストアバッファ回路12に書き戻す。

【0028】

次に、図5を参照して、ストアバッファ回路12の構成について説明する。

図5は、ストアバッファ回路12の概略構成を示す構成図である。同図において、ストアバッファ回路12は、アドレスアレイ121と、データアレイ122と、ストアバッファ制御回路123と、アレイ制御回路124と、読出回路125とを具備する。読出回路125は、命令出力回路126と、ロード命令退避回路127と、データ出力回路128とを具備する。

【0029】

アドレスアレイ121と、データアレイ122とで、セットアソシアティブ方式の記憶装置を構成し、ストア命令およびストアデータを一時的に記憶する。アドレスアレイ121は、ストア命令に含まれるアドレスを記憶し、データアレイ122は、ストアデータを記憶する。

アドレスアレイ121の記憶領域は、m行×n列(m、nは正整数)の領域に分割され、1つの領域に1つのアドレスが格納される。そして、アドレスアレイの各行は、ストア命令の中位アドレス値と1対1に対応付けられており、ストア命令のアドレスは、中位アドレスに応じた行の記憶領域に格納される。各行はn個のアドレス格納領域を有するので、アドレスアレイ121は、中位アドレス値が同一かつ上位アドレスが異なるアドレスを、n個まで記憶し得る。なお、以下では、アドレスアレイ121の各行を「エントリ」と称する。

【0030】

なお、アドレスアレイ121の、有効なアドレス値が格納されていない領域には、アドレス値と識別可能な値(例えば、マイナスの整数値)が格納される。これにより、当該領域が空き領域(新たなデータを書込可能な領域)であることが示される。

また、アドレスアレイ121は、各領域のアドレス値と対応付けて、当該アドレス値が最後にアクセスされた時刻、すなわち、当該ストア命令が最後にアクセスされた時刻を記憶する。

【0031】

なお、ストアバッファ回路12は、主記憶装置70のラインに合わせてライン単位でデータの書込および読出を行う。このため、ストアバッファ回路12は、ストア命令の下位アドレスを無視する。すなわち、上位アドレス値および中位アドレス値が同一であれば、下位アドレス値が異なっていても同一のアドレス値として扱い、データの読出等の処理を行う。

【0032】

データアレイ122の記憶領域も、アドレスアレイ121と同様に、m行×n列の領域に分割され、各行はアドレスアレイ121の各行と1対1に対応付けられ、各列はアドレスアレイの各列と1対1に対応付けられている。これにより、アドレスアレイ121とデータアレイ122とでnウェイ(Way)セットアソシアティブ方式の記憶装置を構成する。

ストアバッファ制御回路123は、マージ回路11から出力される命令や追出制御回路15から出力される追出指示信号を受けて、ストアバッファ回路12の各部を制御する。

【0033】

アレイ制御回路124は、アドレスアレイ121やデータアレイ122に対するストア命令(アドレス値およびストアデータ)の読み出しや書き込みの制御を行う。

具体的には、アレイ制御回路124は、命令や追出指示信号に含まれるアドレス値を読み出し、中位アドレス値に基づいて、アドレスアレイ121の行を選択する。

そして、ストアバッファ制御回路123は、ストア命令を読み出す際は、選択した行の各領域のアドレス値を読出回路125に出力するようアドレスアレイ121を制御する。さらに、アレイ制御回路124は、選択した行の各領域のストアデータを読出回路125に出力するようデータアレイ122を制御する。

【0034】

また、ストア命令を書き込む際は、ストアバッファ制御回路123は、選択した行の領域のうち空き領域を選択し、命令記憶回路123から読み出したアドレス値を、選択した空き領域に書き込む。さらに、書込回路124は、データアレイ122の領域のうち、アドレスを書き込んだアドレスアレイの領域と同じ行かつ同じ列の領域に、マージ回路11から出力されたストアデータを書き込む。

また、アレイ制御回路124は、アドレスアレイ121の行毎に、格納されているアドレスの数を随時計数し、係数結果と当該行を示すアドレス値とをフル検出回路16に随時出力する。

【0035】

読出回路125において、アドレスアレイ121から出力されるアドレス値に基づいてストア命令を生成し、ライトバッファ回路113に出力する。データ出力回路は128、データアレイ122から出力されるストアデータをライトバッファ回路113に出力する。ロード命令退避回路127は、ロード命令を一時的に記憶する。

【0036】

次に、図6を参照して、ライトバッファ回路13の構造について説明する。

図6は、ライトバッファ回路13の構造を示す図である。同図に示すように、ライトバッファ回路13はキュー構造の記憶装置を備える。そして、ライトバッファ回路13の記憶領域は、行L3_0〜L3_p−1のp行分の領域に分割され、各行は、命令の記憶領域A31と、データの記憶領域A32とを備える。

【0037】

同図に示す状態では、ライトバッファ回路13の記憶領域の行L3_iから行L3_j−1までのj行分に命令が格納されており、最も早く命令が格納された行(以下では、「先頭行」と称する)L3_iに対して、次に命令を読み出す行であることを示すリードポインタが設定されている。また、最後に命令が格納された行(以下では、「末尾行」と称する)3_i+j−1の次の行である行L3_i+jに対して、次に命令を書き込む行であることを示すライトポインタが設定されている。

ライトバッファ回路13は、ストアバッファ回路12から出力される命令(ロード命令およびストア命令)を一時保存し、ストアバッファ回路12から出力された順に主記憶装置70に出力する。その際、ライトバッファ回路13は、各命令を一定期間おきに出力することにより、主記憶装置70の負荷が集中しないようにする。

【0038】

次に、図7および8を参照してタイマ回路14の機能および構成について説明する。

図7は、タイマ回路14への入力とタイマ回路14の出力との関係を示す表である。同図に示すように、タイマ回路14は、中央処理装置60からリセット信号が出力されると、カウンタ値を0にリセットする。また、タイマ回路14は、中央処理装置60からリセット信号が出力されていない状態で、中央処理装置60から最初の命令が出力されるとタイマのカウントアップを開始し、以後、中央処理装置60からリセット信号が出力されるまで、サイクル毎にカウントアップを行う。ここで、タイマ回路14がカウントアップを行うサイクルは、時間を測定可能なサイクルであればよい。例えば、情報処理装置1のクロックサイクルを用いることができる。

【0039】

図8は、タイマ回路14の概略構成を示す構成図である。同図において、タイマ回路14は、命令受付回路141と、レジスタ142と、OR回路143および148と、AND回路144および145と、カウンタ146と、カウント信号出力回路147とを具備する。

命令受付回路141は、中央処理装置60から命令が出力されていないときは「0」を出力し、命令が出力されているときは「1」を出力する。

レジスタ142は、命令受付回路141からの出力に基づいて、中央処理装置60からリセット信号が出力された後、最初の命令が出力済みである場合に「1」を出力する。

【0040】

OR回路143は、最初の命令が出力済み、または、タイマ回路14がカウント中の場合に「1」を出力し、それ以外の場合は「0」を出力する。

AND回路144は、最初の命令が出力済み、または、タイマ回路14がカウント中であって、かつ、中央処理装置60からリセット信号が出力されていない場合は「1」を出力し、それ以外の場合は「0」を出力する。

AND回路145は、最初の命令が出力済み、または、タイマ回路14がカウント中であって、かつ、中央処理装置60からリセット信号が出力されていない場合は、カウント信号出力回路147から出力されるカウントアップ信号をカウンタ146に出力する。

【0041】

カウンタ146は、中央処理装置60から出力されるリセット信号によりリセットされ、AND回路145から出力されるカウントアップ信号に従ってカウントアップする。

カウント信号出力回路147は、サイクル毎にカウントアップ信号を出力する。

OR回路148は、カウンタ146の出力するカウント値が0でないときはカウント中であることを示す信号「1」を出力し、カウント値が0のときは「0」を出力する。

かかる構成により、図7に示す入出力が実現される。

【0042】

次に、図9および10を用いて追出制御回路15の機能および構成について説明する。

図9は、追出制御回路15への入力と追出制御回路15の出力との関係を示す表である。同図に示すように、追出制御回路15は、タイマ回路14から出力されるタイマカウント値が、予め設定されたタイマ設定値よりも大きい場合、または、データ数検出回路17から出力されるライトバッファデータ数が、予め設定されたデータ数設定値よりも小さい場合、または、フル検出回路16からエントリフル信号が出力される場合に、追出指示信号として「1」をストアバッファ回路12に出力し、その他の場合は「0」を出力する。追出指示信号「1」は、ストアバッファ回路12からストア命令を追い出すよう指示する信号である。また、追出制御回路15は、フル検出回路16からエントリフル信号が出力される場合は、上述の値「1」に加えてエントリフル信号に含まれるアドレス値を含む追出指示信号を生成し、ストアバッファ回路12に出力する。

【0043】

図10は、追出制御回路15の概略構成を示す構成図である。同図において、追出制御回路15は、レジスタ151および153と、大小比較回路152および154と、AND回路155と、OR回路156と、アドレス付加回路157とを具備する。

レジスタ151は、予め設定されたタイマ設定値を記憶する。大小比較回路152は、タイマ回路14から出力されるタイマカウント値と、レジスタ151の記憶するタイマ設定値とを比較し、タイマカウント値がタイマ設定値よりも大きい場合に「1」を出力し、その他の場合に「0」を出力する。

【0044】

レジスタ153は、予め設定されたデータ数設定値を記憶する。大小比較回路154は、データ数検出回路17から出力されるライトバッファデータ数(ライトバッファ記憶部13が記憶しているデータの数)と、レジスタ153の記憶するデータ数設定値とを比較し、ライトバッファデータ数がデータ数設定値より小さい場合に「1」を出力し、その他の場合に「0」を出力する。

AND回路155は、タイマカウント値がタイマ設定値よりも大きく、かつ、ライトバッファデータ数がデータ数設定値より大きい場合に「1」を出力し、その他の場合に「0」を出力する。

OR回路156は、タイマカウント値がタイマ設定値よりも大きく、かつ、ライトバッファデータ数がデータ数設定値より大きい場合、あるいは、フル検出回路16からエントリフル信号が出力される場合に、追出指示信号として「1」を出力し、その他の場合は「0」を出力する。

アドレス付加回路157は、ストアバッファ回路12のアドレスアレイ121のあるエントリがフルである(当該エントリの全ての領域にアドレスが格納されている)ことを示すエントリフル信号がフル検出回路16から出力されると、エントリフル信号から当該エントリを示すアドレス値を読出し、読み出したアドレス値を追出指示信号に含める。

かかる構成により、図10に示す入出力が実現される。

【0045】

次に図11を参照してフル検出回路16の構成について説明する。

図11は、フル検出回路16の概略構成を示す構成図である。同図において、データ数検出回路17は、レジスタ171と大小比較回路172を具備する。

レジスタ171は、ストアバッファ回路12のway数(アドレスアレイ121の列数)を予め記憶する。大小比較回路171は、ストアバッファ回路12から出力される、アドレスアレイ121の各行に記憶されているアドレス数(ストア命令数)と、レジスタ171の記憶するway数とを比較し、アドレス数がway数より多い行があれば、エントリフル信号として、エントリフルを示す「1」と、当該行を示すアドレス値とを出力する。

【0046】

次に、図12〜14を参照して情報処理装置1の動作について説明する。

図12は、中央処理装置60からロード命令が出力された際の情報処理装置1の動作例を示すシーケンス図である。

まず、中央処理装置60からリセット信号が出力されると(シーケンスS201)、タイマ回路14は、カウンタ値を0にリセットする(シーケンスS202)。

次に、中央処理装置60から最初の命令(ストア命令またはロード命令)が出力されると(シーケンスS211)、タイマ回路14は、カウントアップを開始する(シーケンスS212)。また、マージ回路11は、中央処理装置60から出力された当該命令を、後述する処理手順に従って処理する。

【0047】

その後、中央処理装置60からロード命令が出力されると(シーケンスS221)、マージ回路11は、ロード命令をストアバッファ回路12に出力する(シーケンスS222)。ストアバッファ回路12は、マージ回路11から出力されたロード命令に対応するアドレスのストア命令を記憶しているか否かを判定する。当該ストア命令を記憶していないと判定すると(シーケンスS223)、ストアバッファ回路12は、ロード命令をそのままライトバッファ回路13に出力する(シーケンスS224)。そして、ライトバッファ回路13は、ストアバッファ回路12から出力されるロード命令を一時的に記憶し、主記憶装置70に出力する(シーケンスS225)。ライトバッファ回路13からロード命令の出力を受けた主記憶装置70は、当該ロード命令に基づいてロードデータを中央処理装置60に出力する。

【0048】

なお、ライトバッファ回路13が主記憶装置70に命令を出力する際、主記憶装置70の該当するバンクがビジー状態にありアクセス待ち状態となる場合は、当該命令よりも後から記憶した命令のうち、主記憶装置70の該当するバンクが空き状態にある命令を先に出力するようにしてもよい。例えば、ライトバッファ回路13が、主記憶装置70のバンクごとにキュー構造の記憶装置を備え、バンクごとに並行して命令を出力することにより、記憶装置70の該当するバンクが空き状態にある命令を先に出力できる。

【0049】

また、シーケンスS221と同様、中央処理装置60からロード命令が出力され(シーケンスS231)、シーケンスS222と同様、当該ロード命令がマージ回路11から出力され(シーケンスS232)、ストアバッファ回路12が、当該ロード命令に対応するアドレスのストア命令を記憶していると判定すると(シーケンスS233)、ストアバッファ回路12は、ロード命令を一時的に記憶し、ストア命令をライトバッファ回路13に出力する(追い出す。シーケンスS234)。その後、ストアバッファ回路12は、一時的に記憶していたロード命令をライトバッファ回路13に出力する(シーケンスS235)。

【0050】

そして、ライトバッファ回路13は、シーケンスS234にて出力されたストア命令を主記憶装置70に出力し(シーケンスS236)、その後、シーケンスS235にて出力されたロード命令を主記憶装置70に出力する(シーケンスS237)。

そして、主記憶装置70は、記憶するデータをストア命令に従って更新した後、ロード命令に従ってロードデータを中央処理装置60に出力する。

このように、ストアバッファ回路12がロード命令を一時的に記憶し、先にストア命令を出力することにより、主記憶装置70が、ストア命令の反映されていない誤ったロードデータを中央処理装置60に出力することを防止する。

【0051】

図13は、中央処理装置60からストア命令が出力された際の情報処理装置1の動作例を示すシーケンス図である。

中央処理装置60からストア命令が出力されると(シーケンスS301)、マージ回路11は、当該ストア命令をストアバッファ回路12に出力する(シーケンスS302)。ストアバッファ回路12は、マージ回路11から出力されたストア命令に対応するアドレスのストア命令を記憶しているか否かを判定する。当該ストア命令を記憶していないと判定すると(シーケンスS303)、ストアバッファ回路12は、当該ストア命令に含まれるアドレスを主記憶装置70に出力してストアデータを要求する(シーケンスS304)。そして、主記憶装置70は、要求されたストアデータをストアバッファ回路12に出力する(シーケンスS311)。

【0052】

ストアデータの出力を受けたストアバッファ回路12は、当該ストアデータをマージ回路11に出力する(シーケンスS312)。そして、マージ回路11は、ストアバッファ回路12から出力されたストアデータを、中央処理装置60から出力されたストア命令に従って更新し(シーケンスS313)、ストアデータ更新後のストア命令をストアバッファ回路12に出力する(シーケンスS314)。

ストアバッファ回路12は、マージ回路11から出力されたストア命令を記憶する(シーケンスS315)。

【0053】

また、シーケンスS311と同様、中央処理装置60からストア命令が出力され(シーケンスS321)、シーケンスS312と同様、当該ストア命令がマージ回路11から出力され(シーケンスS322)、ストアバッファ回路12が、当該当該ストア命令に対応するアドレスのストア命令を記憶している判定すると(シーケンスS323)、ストアバッファ回路12は、この記憶しているストア命令をマージ回路11に出力する(追い出す。シーケンスS324)。

【0054】

そして、マージ回路11は、ストアバッファ回路12から出力されたストアデータを、中央処理装置60から出力されたストア命令に従って更新する(シーケンスS325)。これにより、ストアバッファ回路12が記憶していたストア命令と、中央処理装置60から出力されたストア命令とがマージされる。そして、マージ回路11は、ストアデータ更新後のストア命令をストアバッファ回路12に出力する(シーケンスS326)。

ストアバッファ回路12は、マージ回路11から出力されたストア命令を記憶する(シーケンスS327)。

【0055】

図14は、ストアバッファ回路12がストア命令を追い出す際の情報処理装置1の動作例を示すシーケンス図である。

タイマ回路14は、タイマカウント値を追出制御回路15に随時出力する(シーケンスS401)。

また、ストアバッファ回路12は、アドレスアレイ121の各行の使用状況(記憶されているアドレスの数)を、フル検出回路16に随時出力し(シーケンスS411)、フル検出回路16は、ストアバッファ回路12から出力されるアドレスアレイ121の各行の使用状況と、予め記憶している1行に記憶可能なアドレスの数とに基づいて、各行について、残り容量の有無(新たなアドレスおよびストアデータを記憶可能か否か)を判定し、残り容量が無いと判定した場合は、当該行を示すアドレスを含むエントリフル信号を追出制御回路15に出力する。

【0056】

また、ライトバッファ回路13は、命令を記憶している先頭行を行番号にて示すリードポインタと、命令を記憶している末尾行の次の行を行番号にて示すライトポインタとをデータ数検出回路17に出力する(シーケンスS421)。そして、データ数検出回路17は、リードポインタとライトポインタとに基づいてライトバッファ回路13が記憶している命令数を算出し、算出した命令数を追出制御回路15に出力する(シーケンスS422)。

【0057】

そして、追出制御回路15は、タイマ回路14から出力されるタイマカウント値と、フル検出回路16から出力されるアドレスと、データ数検出回路17から出力される命令数とに基づいて、ストアバッファ回路12がストア命令の追い出しを行う必要があるか否かを判定し、追い出しを行う必要があると判定すると(シーケンスS431)、追出処理を指示する追出指示信号をストアバッファ回路12に出力する(シーケンスS432)。

【0058】

ストアバッファ回路12は、追出制御回路15から出力される追出指示信号に従って、ストア命令の追い出しを行う。具体的には、後述するように、追出対象のストア命令を決定し、当該ストア命令をライトバッファ回路13に出力し(シーケンスS433)、当該ストア命令を記憶していた記憶領域を開放して新たなデータを書込可能とする。

そして、ライトバッファ回路13は、ストアバッファ回路12から出力されたストア命令を一時的に記憶した後、主記憶装置70に出力する(シーケンスS434)。ライトバッファ回路から出力されたストア命令を受けた主記憶装置70は、当該ストア命令に従ってデータを更新する。

【0059】

次に、図15を参照して、ストアバッファ回路12が行う処理について説明する。

図15は、ストアバッファ回路12の処理手順を示すフローチャートである。ストアバッファ回路12は、同図の処理を随時繰り返し実行する。

まず、ストアバッファ制御回路123が、マージ回路11からストア命令が出力されたか否かを判定する(ステップS101)。ストア命令が出力されたと判定した場合、当該ストア命令をアレイ制御回路124と命令出力回路126とに出力する。

【0060】

そして、アレイ制御回路124は、当該ストア命令に含まれるアドレス値に対応する行の各領域のアドレスおよびストアデータを、読出回路125に出力するよう、アドレスアレイ121およびデータアレイ122を制御する。具体的には、アレイ制御回路124は、ストア命令に含まれるアドレス値のうち、中位アドレス値に対応する行の各領域に格納されているアドレス値を出力するようアドレスアレイ121を制御する。また、アレイ制御回路124は、当該中位アドレス値に対応する行の各領域に格納されているストアデータを出力するようアドレスアレイ121を制御する。

【0061】

読出回路125の命令出力回路126は、アドレスアレイ121から出力される各領域のデータのいずれかが、ストア命令に含まれるアドレス値にヒットするか否かを判定する(ステップS102)。具体的には、命令出力回路126は、判定対象のアドレス値の上位アドレス値と、アドレスアレイ121から出力された各領域のアドレス値の上位アドレス値とが同一か否かを判定する。上位アドレス値が同一のアドレス値があれば、命令出力回路126は、ヒットと判定し、無ければミスと判定する。

【0062】

ヒットと判定した場合(ステップS102:YES)、命令出力回路126は、データアレイ122に記憶されているストアデータのうち、アドレス値がヒットした領域と同じ行かつ同じ列の領域に格納さているストアデータを取得するよう指示する信号をデータ出力回路128に出力し、データ出力回路128は当該ストアデータを取得する(ステップS103)。

そして、データ出力回路128は、取得したストアデータを、マージ回路11に出力する(ステップS104)。

また、命令出力回路126は、ヒットしたアドレス値を含む開放要求信号をアレイ制御回路124に出力する。アレイ制御回路124は、アドレスアレイ121の、当該アドレス値に対応する領域(アドレスアレイ121の、当該アドレスを記憶している領域)に、アドレス値と識別可能な値を書き込む(ステップS104)。これにより、当該領域が空き領域となる。その後、同図の処理を終了する。

【0063】

一方、ステップS102にてミスと判定した場合(ステップS102:NO)、命令出力回路126は、ストア命令から読み出したアドレス値を含むデータ要求信号を主記憶装置70に出力する。そして、データ出力回路128が、主記憶装置70から出力される、当該アドレス値に対応するラインのデータを取得する(ステップS111)。そして、読出回路125は、取得したデータをマージ回路11に出力する(ステップS112)。その後、同図の処理を終了する。

【0064】

一方、ステップS101にて、ストア命令が出力されていないと判定した場合(ステップS101:NO)、ストアバッファ制御回路123は、マージ回路11からロード命令が出力されたか否かを判定する(ステップS121)。ロード命令が出力されたと判定した場合(ステップS121:YES)、ストアバッファ制御回路123は、当該ロード命令をアレイ制御回路124と命令出力回路126とに出力する。

そして、アレイ制御回路124は、上述したストア命令の場合と同様に、当該ロード命令に含まれるアドレス値に対応する行の各領域のアドレスおよびストアデータを、読出回路125に出力するよう、アドレスアレイ121およびデータアレイ122を制御する。また、読出回路125の命令出力回路126は、上述したストア命令の場合と同様に、アドレスアレイ121から出力される各領域のデータのいずれかが、ストア命令に含まれるアドレス値にヒットするか否かを判定する(ステップS122)。

ヒットすると判定した場合(ステップS122:YES)、命令出力回路126は、ロード命令退避回路127にロード命令を書き込む(ステップS123)。

【0065】

そして、命令出力回路126は、上述したストア命令の場合と同様に、データアレイ122に記憶されているストアデータのうち、アドレス値がヒットした領域と同じ行かつ同じ列の領域に格納さているストアデータを取得するよう指示する信号をデータ出力回路128に出力し、データ出力回路128は当該ストアデータのうち、アドレス値がヒットした領域と同じ行かつ同じ列の領域に格納さているストアデータを取得する(ステップS124)。

また、命令出力回路125は、ストア命令を示すコマンド名(例えば「S」)を予め記憶しておき、当該コマンド名と、ヒットしたアドレス値とに基づいてストア命令を生成する。そして、命令出力回路125は、生成したストア命令をライトバッファ回路13に出力する。また、データ出力回路128は、取得したストアデータをライトバッファ回路13に出力する(ステップS125)。

【0066】

また、命令出力回路126は、ヒットしたアドレス値を含む開放要求信号をアレイ制御回路124に出力する。アレイ制御回路124は、アドレスアレイ121の、当該アドレスに対応する領域に、アドレス値と識別可能な値を書き込む(ステップS126)。これにより、当該領域が空き領域となる。

さらに、命令出力回路126は、ロード命令退避回路127からロード命令を読み出し、読み出したロード命令をライトバッファ回路13に出力する(ステップS127)。その後、同図の処理を終了する。

一方、ステップS122にて、ヒットしないと判定した場合(ステップS122:NO)、命令出力回路126は、ロード命令をライトバッファ回路13に出力する(ステップS131)。その後、同図の処理を終了する。

【0067】

一方、ステップS121にて、ロード命令が出力されていないと判定した場合、ストアバッファ制御回路123は、追出制御回路15から追出指示信号が出力されたか否かを判定する(ステップS141)。追出指示信号が出力されたと判定した場合(ステップS141:YES)、ストアバッファ制御回路123は、当該追出指示信号をアレイ制御回路124と命令出力回路126とに出力する。アレイ制御回路124は、追出対象となるストア命令のアドレス値およびストアデータを、読出回路125に出力するよう、アドレスアレイ121およびデータアレイ122を制御する。そして、命令出力回路126は、アドレスアレイ121から出力されるアドレス値を取得し、データ出力回路128は、データアレイ122から出力されるストアデータを取得する(ステップS142)。

【0068】

ここで、アレイ制御回路124は、追出指示信号にアドレス値が含まれているか否かを判定する。そして、アドレス値が含まれていると判定した場合、アレイ制御回路124は、アドレスアレイ121を参照して、当該アドレス値に対応する行の各領域のうち、最後にアクセスされた時刻が最も古いストア命令を、追出対象のストア命令に決定する。一方、アドレス値が含まれていないと判定した場合、アレイ制御回路124は、アドレスアレイ121を参照して、全領域のうち最後にアクセスされた時刻が最も古いストア命令を、追出対象のストア命令に決定する。

【0069】

そして、命令出力回路126は、ステップS125と同様に、アドレスアレイ121から出力されるアドレスを含む命令を生成し、生成したストア命令をライトバッファ回路13に出力する。また、データ出力回路128は、取得したストアデータをライトバッファ回路13に出力する(ステップS143)。

【0070】

また、命令出力回路126は、取得したアドレス値を含む開放要求信号をアレイ制御回路124に出力する。アレイ制御回路124は、アドレスアレイ121の、当該アドレスに対応する領域に、アドレス値と識別可能な値を書き込む(ステップS126)。これにより、当該領域が空き領域となる。その後、同図の処理を終了する。

一方、ステップS141において、追出指示信号が出力されていないと判定した場合(ステップS141:NO)同図の処理を終了する。

【0071】

次に、図16を参照してストアバッファ回路12が記憶するデータ量について記憶する。

図16は、ストアバッファ回路12が記憶するデータ量(ストア命令数)の変化を示すグラフである。線L131はストアバッファ回路12が記憶するデータ量の変化の例を示す。線L132は、追出制御回路15が、ライトバッファデータ数がデータ数設定値より大きい場合と、エントリフル信号が「1」の場合に追出指示信号として「1」を出力する場合に、ストアバッファ回路12が記憶するデータ量の変化を示すグラフである。

線L131が示すように、最初に命令が出力されてから一定時間は追出制御回路15が追出指示信号の出力を抑制することで、ストアバッファ回路12にストア命令が蓄積され、中央処理装置60からストア命令に対して、ストアバッファ回路12の記憶するストア命令がヒットする率が向上する。これにより、主記憶装置70へのアクセス頻度を抑えることが出来る。

【0072】

以上のように、ストアバッファ回路12が複数のストア命令を記憶してマージ回路11に出力するので、主記憶装置70上の異なるアドレスに対するストア命令が中央処理装置60から出力された場合にも、当該アドレスに対するストアデータをストアバッファ回路12が記憶していることが期待できる。そして、ストアバッファ回路12がストアデータを記憶している場合、主記憶装置70へのアクセスを抑えることができ、主記憶装置70へのアクセス待ちによる中央処理装置60の処理速度低下を防止できる。

【0073】

また、中央処理装置60が、プログラム実行開始時などの処理開始時、すなわち、ストアバッファ回路12の記憶するストア命令の数が少ないと考えられるタイミングでリセット信号を出力し、タイマ回路14は、当該リセット信号が出力された後、中央処理装置60から最初の命令が出力されるとカウントアップを開始する。そして、ストアバッファ回路12は、ライトバッファ回路13の記憶するデータ数がデータ数設定値以下になった場合でも、最初の命令が出力されてから一定時間経過するまでは、ストア命令の追い出しを抑制するので、中央処理装置60からストア命令が出力された際のヒット率を高めることが出来る。

また、最初の命令が出力されてから一定時間経過後は、ライトバッファ回路13の記憶するデータ数がデータ数設定値以下になった場合に、ストアバッファ回路12がストア命令の追い出しを行うので、ライトバッファ回路13の記憶するデータ数(ストア命令の数)の増大を防止でき、ライトバッファ回路が主記憶装置70にアクセスする際のスループット低下を防止できる。

【0074】

なお、タイマ回路の構成は上述したものに限らない。例えば、中央処理装置60がリセット信号を出力せず、タイマ回路自身がリセット信号を生成するようにしてもよい。

図17は、タイマ回路の変形例を示す構成図である。同図において、タイマ回路24は、命令受付回路141と、レジスタ142および241と、OR回路143および148と、AND回路144、145および243と、カウンタ146と、カウント信号出力回路147と、大小比較回路242とを具備する。同図において、図8の各部と同様の機能を有する部分には同一の符号(141〜148)を付し、説明を省略する。

【0075】

レジスタ241は、予め定められたデータ数設定値として「1」を記憶する。大小比較回路242は、データ数検出回路17から経路W241にて出力されるライトバッファデータ数と、レジスタ241の記憶するデータ数設定値とを比較し、ライトバッファデータ数がデータ数設定値より小さい場合、すなわちライトバッファデータ数が0の場合に「1」を出力し、その他の場合に「0」を出力する。AND回路243は、ライトバッファデータ数がデータ数設定値より小さく、かつ、カウンタ146のある桁以上のビット値が1であるとき(例えば、下位から9桁目以上のいずれかの桁のビット値が1であるとき)にカウンタリセット信号「1」を出力し、その他のときに「0」を出力する。

【0076】

この構成により、タイマ回路24がカウントを開始してから一定時間以上が経過し、かつ、ライトバッファデータ数が0であるときにカウンタリセット信号を生成できる。したがって、ライトバッファ回路13が空のときにタイマ回路24がタイマカウント値をリセットして、ストアバッファ回路12がストア命令を蓄積し、中央処理装置60からストア命令が出力された際のヒット率を高めることができる。

ここで、ストアバッファ回路12が蓄積するストア命令の数が増加した場合、ストアバッファ回路12が連続してストア命令を追い出し、ライトバッファ回路13に蓄積される命令の量が増大することが考えられる。この場合、ライトバッファ回路13から主記憶装置70への命令の出力に時間を要し、中央制御装置60がロード命令を出力した際にデータを取得するまでの待ち時間が増大するおそれがある。さらには、ライトバッファ回路13に空き領域がなくなった場合は、ライトバッファ回路13に空き領域が生じるまで、ストアバッファ回路12がストア命令の追出を待つ必要が生じ、処理の遅延につながる。

そこで、上記のように、ライトバッファ回路13が空のときにストアバッファ回路12がストア命令を蓄積することにより、ライトバッファ回路13に大量の命令が蓄積されることを防止でき、待ち時間による処理の遅延を抑制しうる。

【0077】

また、タイマ回路24がカウンタリセット信号を生成するので、中央処理装置60がリセット信号を出力する必要がない。したがって、中央処理装置60とタイマ回路24との間で入出力されるデータ量を削減でき、また、中央処理装置60がカウンタリセット信号を生成する負荷を軽減できる。

【0078】

なお、ストアマージ装置10の全部または一部の機能を実現するためのプログラムをコンピュータ読み取り可能な記録媒体に記録して、この記録媒体に記録されたプログラムをコンピュータシステムに読み込ませ、実行することにより各部の処理を行ってもよい。なお、ここでいう「コンピュータシステム」とは、OSや周辺機器等のハードウェアを含むものとする。

また、「コンピュータシステム」は、WWWシステムを利用している場合であれば、ホームページ提供環境(あるいは表示環境)も含むものとする。

また、「コンピュータ読み取り可能な記録媒体」とは、フレキシブルディスク、光磁気ディスク、ROM、CD−ROM等の可搬媒体、コンピュータシステムに内蔵されるハードディスク等の記憶装置のことをいう。さらに「コンピュータ読み取り可能な記録媒体」とは、インターネット等のネットワークや電話回線等の通信回線を介してプログラムを送信する場合の通信線のように、短時間の間、動的にプログラムを保持するもの、その場合のサーバやクライアントとなるコンピュータシステム内部の揮発性メモリのように、一定時間プログラムを保持しているものも含むものとする。また上記プログラムは、前述した機能の一部を実現するためのものであっても良く、さらに前述した機能をコンピュータシステムにすでに記録されているプログラムとの組み合わせで実現できるものであっても良い。

【0079】

以上、本発明の実施形態を図面を参照して詳述してきたが、具体的な構成はこの実施形態に限られるものではなく、この発明の要旨を逸脱しない範囲の設計変更等も含まれる。

【符号の説明】

【0080】

1 情報処理装置

10 ストアマージ装置

11 マージ回路

12 ストアバッファ回路

13 ライトバッファ回路

14 タイマ回路

15 追出制御回路

16 フル検出回路

17 データ数検出回路

60 中央処理装置

70 主記憶装置

【技術分野】

【0001】

本発明は、ストアマージ装置、ストアマージ装置を具備する情報処理装置、ストアマージ方法およびプログラムに関する。

【背景技術】

【0002】

記憶装置へのアクセス頻度を抑える方法の1つに、ストアマージ方法と呼ばれる方法がある。ストアマージ方法では、ストアマージ装置が、記憶装置の同一のライン(記憶装置またはキャッシュがデータの読み書きを行う際の単位ブロック)への複数のストア命令(書込命令)を1つに纏めてから記憶装置に書き込むことにより、記憶装置へのアクセス頻度を抑える。以下では、この複数のストア命令を1つに纏める処理を「マージ処理」と称する。

【0003】

例えば、特許文献1に示されるストアマージ方法では、ストアデータ制御装置(ストアマージ装置)が、キュー(Queue)構造のストアバッファと、同じくキュー構造のライトバッファとを備える。そして、ストアバッファがストア命令を格納し、格納時刻の早いストア命令から順にライトバッファに転送する。

ストア命令の転送を受けたライトバッファは、転送されたストア命令を、BOQ(ライトバッファのデータ格納領域のうち、最後にデータを格納した領域)、または、BOQの次のデータ格納領域のいずれかに格納する。具体的には、転送されたストア命令とBOQのストア命令とが、主記憶上の同一のアドレスに対するストア命令である場合は、マージ処理可能であると判定し、ライトバッファは、転送されたストア命令をBOQに格納することによりマージ処理を行う。一方、転送されたストア命令とBOQのストア命令とが、主記憶上の異なるアドレスに対するストア命令である場合は、マージ処理不可であると判定し、ライトバッファは、転送されたストア命令をBOQの次のデータ格納領域に格納し、この新たにストア命令を格納した領域をBOQとする。また、ライトバッファは、格納時刻の早いストア命令から順に、一次キャッシュ(記憶装置)に出力する。このように、ライトバッファは、マージ処理済みのストア命令を一次キャッシュに出力することにより、一次キャッシュへのアクセス頻度を抑える。

【先行技術文献】

【特許文献】

【0004】

【特許文献1】特開2006−48163号公報

【発明の概要】

【発明が解決しようとする課題】

【0005】

しかしながら、特許文献1に示されるストアマージ方法では、主記憶上の異なるアドレスに対するストア命令が転送される毎に、ライトバッファがストア命令を格納する領域が変更され、この領域の数だけストア命令が一次キャッシュに出力される。すなわち、特許文献1に示されるストアマージ方法では、主記憶上の異なるアドレスに対するストア命令が転送された場合の記憶装置へのアクセスを抑えることはできない。

【0006】

本発明は、このような事情を考慮してなされたものであり、その目的は、主記憶上の異なるアドレスに対するストア命令が転送された場合にも記憶装置へのアクセスを抑えることができるストアマージ装置、情報処理装置、ストアマージ方法およびプログラムを提供することにある。

【課題を解決するための手段】

【0007】

この発明は上述した課題を解決するためになされたもので、本発明の一態様によるストアマージ装置は、複数のデータを記憶可能なストアバッファ回路と、ストア命令の入力を受けると、前記ストアバッファ回路が記憶する前記複数のデータのいずれかと前記ストア命令のデータとをマージ処理可能か否か判定し、マージ処理可能なデータがあると判定したときは、前記ストアバッファ回路の記憶する複数のデータのうちマージ処理可能と判定した前記データを選択するマージ対象データ選択回路と、前記マージ対象データ選択部が選択したデータと前記ストア命令のデータとをマージ処理し、マージ処理されたデータを前記ストアバッファ回路に書き戻すマージ回路と、前記ストアバッファ回路が前記複数のデータのいずれかを出力するよう指示する追出指示信号を出力する追出制御回路と、を具備することを特徴とする。

【0008】

また、本発明の一態様による情報処理装置は、複数のデータを記憶可能な主記憶装置と、前記主記憶装置へのデータの書込命令であるストア命令を出力する中央処理装置と、複数のデータを記憶可能なストアバッファ回路と、前記中央処理装置から前記ストア命令が出力されると、前記ストアバッファ回路が記憶する前記複数のデータのいずれかと前記ストア命令のデータとをマージ処理可能か否か判定し、マージ処理可能なデータがあると判定したときは、前記ストアバッファ回路の記憶する複数のデータのうちマージ処理可能と判定した前記データを選択するマージ対象データ選択回路と、前記マージ対象データ選択部が選択したデータと前記ストア命令のデータとをマージ処理し、マージ処理されたデータを前記ストアバッファ回路に書き戻すマージ回路と、前記ストアバッファ回路が当該ストアバッファ回路の記憶するデータの前記主記憶装置への書込要求を出力するよう指示する追出指示信号を出力する追出制御回路と、を具備することを特徴とする。

【0009】

また、本発明の一態様によるストアマージ方法は、複数のデータを記憶可能なストアバッファ回路を具備するストアマージ装置のストアマージ方法であって、マージ対象データ選択回路が、ストア命令の入力を受けると、前記ストアバッファ回路が記憶する前記複数のデータのいずれかと前記ストア命令のデータとをマージ処理可能か否か判定し、マージ処理可能なデータがあると判定したときは、前記ストアバッファ回路の記憶する複数のデータのうちマージ処理可能と判定した前記データを選択するマージ対象データ選択ステップと、マージ回路が、前記マージ対象データ選択部が選択したデータと前記ストア命令のデータとをマージ処理し、マージ処理されたデータを前記ストアバッファ回路に書き戻すマージステップと、追出制御回路が、前記ストアバッファ回路が前記複数のデータのいずれかを出力するよう指示する追出指示信号を出力する追出制御ステップと、を具備することを特徴とする。

【0010】

また、本発明の一態様によるプログラムは、複数のデータを記憶可能なストアバッファ回路を具備するストアマージ装置としてのコンピュータにストア命令の入力を受けると、前記ストアバッファ回路が記憶する前記複数のデータのいずれかと前記ストア命令のデータとをマージ処理可能か否か判定し、マージ処理可能なデータがあると判定したときは、前記ストアバッファ回路の記憶する複数のデータのうちマージ処理可能と判定した前記データを選択するマージ対象データ選択ステップと、前記マージ対象データ選択部が選択したデータと前記ストア命令のデータとをマージ処理し、マージ処理されたデータを前記ストアバッファ回路に書き戻すマージステップと、前記ストアバッファ回路が前記複数のデータのいずれかを出力するよう指示する追出指示信号を出力する追出制御ステップと、を実行させるためのプログラムである。

【発明の効果】

【0011】

本発明によれば、主記憶上の異なるアドレスに対するストア命令が転送された場合にも記憶装置へのアクセスを抑えることができる。

【図面の簡単な説明】

【0012】

【図1】本発明の一実施形態における情報処理装置の概略構成を示す構成図である。

【図2】同実施形態において、ストアマージ装置が行うマージ処理の例を示す図である。

【図3】同実施形態におけるロード命令およびストア命令のデータ構成を示す構成図である。

【図4】同実施形態におけるマージ回路の概略構成を示す構成図である。

【図5】同実施形態におけるストアバッファ回路の概略構成を示す構成図である。

【図6】同実施形態におけるライトバッファ回路の構造を示す図である。

【図7】同実施形態におけるタイマ回路への入力とタイマ回路が行う動作との関係を示す表である。

【図8】同実施形態におけるタイマ回路の概略構成を示す構成図である。

【図9】同実施形態における追出制御回路への入力と追出制御回路が行う動作との関係を示す表である。

【図10】同実施形態における追出制御回路の概略構成を示す構成図である。

【図11】同実施形態におけるフル検出回路の概略構成を示す構成図である。

【図12】同実施形態において、中央処理装置からロード命令が出力された際の情報処理装置の動作例を示すシーケンス図である。

【図13】同実施形態において、中央処理装置からストア命令が出力された際の情報処理装置1の動作例を示すシーケンス図である。

【図14】同実施形態において、ストアバッファ回路がストア命令を追い出す際の情報処理装置の動作例を示すシーケンス図である。

【図15】同実施形態における読出回路の処理手順を示すフローチャートである。

【図16】同実施形態におけるストアバッファ回路が記憶するデータ量(ストア命令数)の変化を示すグラフである。

【図17】同実施形態におけるタイマ回路の変形例を示す構成図である。

【発明を実施するための形態】

【0013】

以下、図面を参照して、本発明の実施の形態について説明する。

図1は、本発明の一実施形態における情報処理装置の概略構成を示す構成図である。

同図において、情報処理装置1は、ストアマージ装置10と、中央処理装置60と、主記憶装置70とを具備する。ストアマージ装置10は、マージ回路11と、ストアバッファ回路12と、ライトバッファ回路13と、タイマ回路14と、追出制御回路15と、フル検出回路16と、データ数検出回路17とを具備する。また、経路W111、W121、W131、W141は、ストア命令またはロード命令が出力される経路である。経路W112、W122、W132、W142は、ストアデータが出力される経路である。経路W161は、ロードデータが出力される経路である。

【0014】

中央処理装置60は、主記憶装置70に対するデータ書込命令であるストア命令と、書込対象のデータであるストアデータとを出力する。また、中央処理装置60は、主記憶装置70に対するデータ読出命令であるロード命令を出力し、ロード命令に応じたデータを取得する。また、中央処理装置60は、プログラム実行開始時などの処理開始時に、タイマ回路14に対してリセット信号を出力する。

主記憶装置70は、中央処理装置60からのストア命令に従ってデータを記憶し、中央処理装置60からのロード命令に従って、記憶しているデータを出力する。なお、主記憶装置70がキャッシュを備えるようにしてもよい。

【0015】

ストアバッファ回路12は、主記憶装置70よりも高速にアクセス可能なセットアソシアティブ方式の記憶装置を備え、中央処理装置60から出力されるストア命令を記憶する。また、ストアバッファ回路12は、マージ回路11が中央処理装置60から出力されるストアデータに対してマージ処理を行って得られたストアデータを記憶する。また、ストアバッファ回路12は、追出制御回路15から追出指示信号が出力されると、ストア命令およびストアデータをライトバッファ回路13に追い出す。なお、ここでいう「追い出す」処理とは、ストア命令およびストアデータを出力し、当該ストア命令およびストアデータを記憶していた記憶領域に新たなデータを書込可能とする処理である。

【0016】

マージ回路11は、中央処理装置60からストア命令が出力されると、このストア命令と主記憶装置70にて同一のアドレス領域に書き込まれるストア命令のストアデータをストアバッファ回路12から取得し、中央処理装置60から出力されたストア命令のストアデータを、ストアバッファ回路12から読み出されたストアデータに反映させ、反映後のデータをストアバッファ回路12に書き戻す。なお、ここでいう「書き戻す」処理は、ストアバッファ回路12にストアデータを記憶させる処理である。

【0017】

ライトバッファ回路13は、キュー(Queue)構造の記憶装置を備え、ストアバッファ回路12から出力されるストア命令およびストアデータを一時的に保存し、これらストア命令およびストアデータを一定の時間間隔で主記憶装置70に出力する。

【0018】

タイマ回路14は、中央処理装置60からリセット信号が出力された後、中央処理装置60から最初のストア命令またはロード命令が出力されてからの時間をカウントアップする。

フル検出回路16は、ストアバッファ回路12のメモリ使用状況を監視し、メモリ使用状況に応じて、追出処理が必要であることを示すフル検出信号を出力する。

データ数検出回路17は、ライトバッファ回路13の記憶するデータ数を検出する。

追出制御回路15は、タイマ回路のカウントする時間と、フル検出回路16からのフル検出信号と、データ数検出回路17の検出するデータ数とに基づいて、ストアバッファ回路12が追出処理を行う必要があるか否かを判定し、必要ありと判定すると追出処理の実行を指示する追出指示信号を出力する。

【0019】

次に、図2を参照して、ストアデータのマージ処理について説明する。

図2は、ストアマージ装置10が行うマージ処理の例を示す図である。

本実施形態では、中央処理装置60は、ストア命令と共に8バイト(B)のストアデータを出力する。これに対して主記憶装置70は、当該主記憶装置70の記憶領域を64バイト毎に分割したラインを、データの入出力を行う際の単位としている。

【0020】

例えば、中央処理装置60が主記憶装置70に対して24バイトのデータのストアを要求する場合、中央処理装置60は、この24バイトのデータを、図2のストアデータ1、2、3のように8バイト毎に分割し、3つのストア命令を出力する。このストアデータ1、2、3は元々連続するデータなので、主記憶装置70において同一のラインに格納されるべきデータであることが考えられる。

【0021】

この場合、ストアマージ装置10が、中央処理装置60からストア命令を受け取る毎に、主記憶装置70からライン単位でデータを読み出し、ストア命令を反映させたライン単位のデータ書き戻すと、主記憶装置70からのデータ読出と、主記憶装置70へのデータ書込とを、それぞれ3回行う必要がある。

これに対して、ストアマージ装置10が、主記憶装置70からライン単位でデータを読み出し、図2に示すように、中央処理装置60からの3つのストア命令を全て反映させたデータを生成し、生成したデータを書き戻すようにすれば、主記憶装置70からのデータ読出と、主記憶装置70へのデータ書込とが、それぞれ1回で済む。

そこで、ストアマージ装置は、主記憶装置70から読み出したデータに中央処理装置60からのストア命令を反映させた後、直ちに主記憶装置70へストア命令の出力を行わずにストアバッファ回路12に一旦蓄え、後述する一定の事象が発生した後に主記憶装置70にストア命令を出力する。

【0022】

次に、図3を参照してロード命令およびストア命令のデータ構成について説明する。

図3は、ロード命令およびストア命令のデータ構成を示す構成図である。同図に示すように、ロード命令およびストア命令は、いずれも、コマンド格納領域A21と、アドレス格納領域A22〜A24を含み、アドレス格納領域A22〜A24は、上位アドレス格納領域A22と、中位アドレス格納領域A23と、下位アドレス格納領域A24とから構成される。

【0023】

コマンド格納領域A21は、ロード命令とストア命令とを識別するコマンドが格納される領域である。コマンドは、例えば、ロード命令を示す「L」またはストア命令を示す「S」のいずれかの値を取る。

アドレス格納領域A22〜A24には、ロードデータが格納されている主記憶装置70上の記憶領域の先頭アドレス、または、ストアデータが格納されるべき主記憶装置70上の記憶領域の先頭アドレスが格納される。

【0024】

アドレス格納領域A22〜A24のうち、中位アドレス格納領域A23は、ストアバッファ回路12が、後述するエントリを選択するために用いられる。

また、下位アドレス格納領域A24は、中央処理装置60が出力するストアデータの、主記憶装置70のライン中における位置を示し、後述するように、マージ回路11が、中央処理装置60から出力されるストアデータをストアバッファ回路12から読み出されるストアデータに反映させる処理を行うために用いられる。

【0025】

次に、図4を用いてマージ回路11の構成について説明する。

図4は、マージ回路11の概略構成を示す構成図である。同図において、マージ回路11は、シフタ111とマージャ112とを具備する。

シフタ111は、中央処理装置60から経路W111にて出力される命令(ロード命令またはストア命令)を取得すると、当該命令がロード命令かストア命令かを、コマンド格納領域を参照して判定する。

【0026】

そして、ロード命令であると判定した場合は、シフタ111は別段処理を行わない。この場合、中央処理装置60から出力されたロード命令が、そのままストアバッファ回路12に転送される。

一方、取得した命令がストア命令であると判定した場合、マージ回路11は、当該ストア命令に含まれる下位アドレスに基づいて、中央処理装置60から経路W112にて出力されるストアデータ(8バイト)を、主記憶装置70のライン(64バイト)上での位置に合わせてシフトさせる。

【0027】

マージャ112は、ストアバッファ回路12から当該ストア命令に基づいて出力されるライン単位(64バイト)のストアデータを取得し、シフタ111から出力される、シフトされたストアデータをライン単位のストアデータに反映させる。すなわち、マージャ112は、ライン単位64バイトのストアデータのうち、中央処理装置60から出力される8バイトのストアデータに相等する位置のデータを当該8バイトのストアデータのデータに置き換える。

これにより、ストアバッファ回路12からのストアデータと、中央処理装置60からのストアデータとが1つのストアデータにマージされるので、主記憶装置70はマージ後のストアデータのみを記憶すればよい。すなわち、中央処理装置60から出力されたストア命令と、マージ回路11が記憶していたストア命令とが、1つのストア命令にマージされている。

そして、マージャ112は、マージ後のストアデータをストアバッファ回路12に出力することにより、当該ストアデータをストアバッファ回路12に書き戻す。

【0028】

次に、図5を参照して、ストアバッファ回路12の構成について説明する。

図5は、ストアバッファ回路12の概略構成を示す構成図である。同図において、ストアバッファ回路12は、アドレスアレイ121と、データアレイ122と、ストアバッファ制御回路123と、アレイ制御回路124と、読出回路125とを具備する。読出回路125は、命令出力回路126と、ロード命令退避回路127と、データ出力回路128とを具備する。

【0029】

アドレスアレイ121と、データアレイ122とで、セットアソシアティブ方式の記憶装置を構成し、ストア命令およびストアデータを一時的に記憶する。アドレスアレイ121は、ストア命令に含まれるアドレスを記憶し、データアレイ122は、ストアデータを記憶する。

アドレスアレイ121の記憶領域は、m行×n列(m、nは正整数)の領域に分割され、1つの領域に1つのアドレスが格納される。そして、アドレスアレイの各行は、ストア命令の中位アドレス値と1対1に対応付けられており、ストア命令のアドレスは、中位アドレスに応じた行の記憶領域に格納される。各行はn個のアドレス格納領域を有するので、アドレスアレイ121は、中位アドレス値が同一かつ上位アドレスが異なるアドレスを、n個まで記憶し得る。なお、以下では、アドレスアレイ121の各行を「エントリ」と称する。

【0030】

なお、アドレスアレイ121の、有効なアドレス値が格納されていない領域には、アドレス値と識別可能な値(例えば、マイナスの整数値)が格納される。これにより、当該領域が空き領域(新たなデータを書込可能な領域)であることが示される。

また、アドレスアレイ121は、各領域のアドレス値と対応付けて、当該アドレス値が最後にアクセスされた時刻、すなわち、当該ストア命令が最後にアクセスされた時刻を記憶する。

【0031】

なお、ストアバッファ回路12は、主記憶装置70のラインに合わせてライン単位でデータの書込および読出を行う。このため、ストアバッファ回路12は、ストア命令の下位アドレスを無視する。すなわち、上位アドレス値および中位アドレス値が同一であれば、下位アドレス値が異なっていても同一のアドレス値として扱い、データの読出等の処理を行う。

【0032】

データアレイ122の記憶領域も、アドレスアレイ121と同様に、m行×n列の領域に分割され、各行はアドレスアレイ121の各行と1対1に対応付けられ、各列はアドレスアレイの各列と1対1に対応付けられている。これにより、アドレスアレイ121とデータアレイ122とでnウェイ(Way)セットアソシアティブ方式の記憶装置を構成する。

ストアバッファ制御回路123は、マージ回路11から出力される命令や追出制御回路15から出力される追出指示信号を受けて、ストアバッファ回路12の各部を制御する。

【0033】

アレイ制御回路124は、アドレスアレイ121やデータアレイ122に対するストア命令(アドレス値およびストアデータ)の読み出しや書き込みの制御を行う。

具体的には、アレイ制御回路124は、命令や追出指示信号に含まれるアドレス値を読み出し、中位アドレス値に基づいて、アドレスアレイ121の行を選択する。

そして、ストアバッファ制御回路123は、ストア命令を読み出す際は、選択した行の各領域のアドレス値を読出回路125に出力するようアドレスアレイ121を制御する。さらに、アレイ制御回路124は、選択した行の各領域のストアデータを読出回路125に出力するようデータアレイ122を制御する。

【0034】

また、ストア命令を書き込む際は、ストアバッファ制御回路123は、選択した行の領域のうち空き領域を選択し、命令記憶回路123から読み出したアドレス値を、選択した空き領域に書き込む。さらに、書込回路124は、データアレイ122の領域のうち、アドレスを書き込んだアドレスアレイの領域と同じ行かつ同じ列の領域に、マージ回路11から出力されたストアデータを書き込む。

また、アレイ制御回路124は、アドレスアレイ121の行毎に、格納されているアドレスの数を随時計数し、係数結果と当該行を示すアドレス値とをフル検出回路16に随時出力する。

【0035】

読出回路125において、アドレスアレイ121から出力されるアドレス値に基づいてストア命令を生成し、ライトバッファ回路113に出力する。データ出力回路は128、データアレイ122から出力されるストアデータをライトバッファ回路113に出力する。ロード命令退避回路127は、ロード命令を一時的に記憶する。

【0036】

次に、図6を参照して、ライトバッファ回路13の構造について説明する。

図6は、ライトバッファ回路13の構造を示す図である。同図に示すように、ライトバッファ回路13はキュー構造の記憶装置を備える。そして、ライトバッファ回路13の記憶領域は、行L3_0〜L3_p−1のp行分の領域に分割され、各行は、命令の記憶領域A31と、データの記憶領域A32とを備える。

【0037】

同図に示す状態では、ライトバッファ回路13の記憶領域の行L3_iから行L3_j−1までのj行分に命令が格納されており、最も早く命令が格納された行(以下では、「先頭行」と称する)L3_iに対して、次に命令を読み出す行であることを示すリードポインタが設定されている。また、最後に命令が格納された行(以下では、「末尾行」と称する)3_i+j−1の次の行である行L3_i+jに対して、次に命令を書き込む行であることを示すライトポインタが設定されている。

ライトバッファ回路13は、ストアバッファ回路12から出力される命令(ロード命令およびストア命令)を一時保存し、ストアバッファ回路12から出力された順に主記憶装置70に出力する。その際、ライトバッファ回路13は、各命令を一定期間おきに出力することにより、主記憶装置70の負荷が集中しないようにする。

【0038】

次に、図7および8を参照してタイマ回路14の機能および構成について説明する。

図7は、タイマ回路14への入力とタイマ回路14の出力との関係を示す表である。同図に示すように、タイマ回路14は、中央処理装置60からリセット信号が出力されると、カウンタ値を0にリセットする。また、タイマ回路14は、中央処理装置60からリセット信号が出力されていない状態で、中央処理装置60から最初の命令が出力されるとタイマのカウントアップを開始し、以後、中央処理装置60からリセット信号が出力されるまで、サイクル毎にカウントアップを行う。ここで、タイマ回路14がカウントアップを行うサイクルは、時間を測定可能なサイクルであればよい。例えば、情報処理装置1のクロックサイクルを用いることができる。

【0039】

図8は、タイマ回路14の概略構成を示す構成図である。同図において、タイマ回路14は、命令受付回路141と、レジスタ142と、OR回路143および148と、AND回路144および145と、カウンタ146と、カウント信号出力回路147とを具備する。

命令受付回路141は、中央処理装置60から命令が出力されていないときは「0」を出力し、命令が出力されているときは「1」を出力する。

レジスタ142は、命令受付回路141からの出力に基づいて、中央処理装置60からリセット信号が出力された後、最初の命令が出力済みである場合に「1」を出力する。

【0040】

OR回路143は、最初の命令が出力済み、または、タイマ回路14がカウント中の場合に「1」を出力し、それ以外の場合は「0」を出力する。

AND回路144は、最初の命令が出力済み、または、タイマ回路14がカウント中であって、かつ、中央処理装置60からリセット信号が出力されていない場合は「1」を出力し、それ以外の場合は「0」を出力する。

AND回路145は、最初の命令が出力済み、または、タイマ回路14がカウント中であって、かつ、中央処理装置60からリセット信号が出力されていない場合は、カウント信号出力回路147から出力されるカウントアップ信号をカウンタ146に出力する。

【0041】

カウンタ146は、中央処理装置60から出力されるリセット信号によりリセットされ、AND回路145から出力されるカウントアップ信号に従ってカウントアップする。

カウント信号出力回路147は、サイクル毎にカウントアップ信号を出力する。

OR回路148は、カウンタ146の出力するカウント値が0でないときはカウント中であることを示す信号「1」を出力し、カウント値が0のときは「0」を出力する。

かかる構成により、図7に示す入出力が実現される。

【0042】

次に、図9および10を用いて追出制御回路15の機能および構成について説明する。

図9は、追出制御回路15への入力と追出制御回路15の出力との関係を示す表である。同図に示すように、追出制御回路15は、タイマ回路14から出力されるタイマカウント値が、予め設定されたタイマ設定値よりも大きい場合、または、データ数検出回路17から出力されるライトバッファデータ数が、予め設定されたデータ数設定値よりも小さい場合、または、フル検出回路16からエントリフル信号が出力される場合に、追出指示信号として「1」をストアバッファ回路12に出力し、その他の場合は「0」を出力する。追出指示信号「1」は、ストアバッファ回路12からストア命令を追い出すよう指示する信号である。また、追出制御回路15は、フル検出回路16からエントリフル信号が出力される場合は、上述の値「1」に加えてエントリフル信号に含まれるアドレス値を含む追出指示信号を生成し、ストアバッファ回路12に出力する。

【0043】

図10は、追出制御回路15の概略構成を示す構成図である。同図において、追出制御回路15は、レジスタ151および153と、大小比較回路152および154と、AND回路155と、OR回路156と、アドレス付加回路157とを具備する。

レジスタ151は、予め設定されたタイマ設定値を記憶する。大小比較回路152は、タイマ回路14から出力されるタイマカウント値と、レジスタ151の記憶するタイマ設定値とを比較し、タイマカウント値がタイマ設定値よりも大きい場合に「1」を出力し、その他の場合に「0」を出力する。

【0044】

レジスタ153は、予め設定されたデータ数設定値を記憶する。大小比較回路154は、データ数検出回路17から出力されるライトバッファデータ数(ライトバッファ記憶部13が記憶しているデータの数)と、レジスタ153の記憶するデータ数設定値とを比較し、ライトバッファデータ数がデータ数設定値より小さい場合に「1」を出力し、その他の場合に「0」を出力する。

AND回路155は、タイマカウント値がタイマ設定値よりも大きく、かつ、ライトバッファデータ数がデータ数設定値より大きい場合に「1」を出力し、その他の場合に「0」を出力する。

OR回路156は、タイマカウント値がタイマ設定値よりも大きく、かつ、ライトバッファデータ数がデータ数設定値より大きい場合、あるいは、フル検出回路16からエントリフル信号が出力される場合に、追出指示信号として「1」を出力し、その他の場合は「0」を出力する。

アドレス付加回路157は、ストアバッファ回路12のアドレスアレイ121のあるエントリがフルである(当該エントリの全ての領域にアドレスが格納されている)ことを示すエントリフル信号がフル検出回路16から出力されると、エントリフル信号から当該エントリを示すアドレス値を読出し、読み出したアドレス値を追出指示信号に含める。

かかる構成により、図10に示す入出力が実現される。

【0045】

次に図11を参照してフル検出回路16の構成について説明する。

図11は、フル検出回路16の概略構成を示す構成図である。同図において、データ数検出回路17は、レジスタ171と大小比較回路172を具備する。

レジスタ171は、ストアバッファ回路12のway数(アドレスアレイ121の列数)を予め記憶する。大小比較回路171は、ストアバッファ回路12から出力される、アドレスアレイ121の各行に記憶されているアドレス数(ストア命令数)と、レジスタ171の記憶するway数とを比較し、アドレス数がway数より多い行があれば、エントリフル信号として、エントリフルを示す「1」と、当該行を示すアドレス値とを出力する。

【0046】

次に、図12〜14を参照して情報処理装置1の動作について説明する。

図12は、中央処理装置60からロード命令が出力された際の情報処理装置1の動作例を示すシーケンス図である。

まず、中央処理装置60からリセット信号が出力されると(シーケンスS201)、タイマ回路14は、カウンタ値を0にリセットする(シーケンスS202)。

次に、中央処理装置60から最初の命令(ストア命令またはロード命令)が出力されると(シーケンスS211)、タイマ回路14は、カウントアップを開始する(シーケンスS212)。また、マージ回路11は、中央処理装置60から出力された当該命令を、後述する処理手順に従って処理する。

【0047】

その後、中央処理装置60からロード命令が出力されると(シーケンスS221)、マージ回路11は、ロード命令をストアバッファ回路12に出力する(シーケンスS222)。ストアバッファ回路12は、マージ回路11から出力されたロード命令に対応するアドレスのストア命令を記憶しているか否かを判定する。当該ストア命令を記憶していないと判定すると(シーケンスS223)、ストアバッファ回路12は、ロード命令をそのままライトバッファ回路13に出力する(シーケンスS224)。そして、ライトバッファ回路13は、ストアバッファ回路12から出力されるロード命令を一時的に記憶し、主記憶装置70に出力する(シーケンスS225)。ライトバッファ回路13からロード命令の出力を受けた主記憶装置70は、当該ロード命令に基づいてロードデータを中央処理装置60に出力する。

【0048】

なお、ライトバッファ回路13が主記憶装置70に命令を出力する際、主記憶装置70の該当するバンクがビジー状態にありアクセス待ち状態となる場合は、当該命令よりも後から記憶した命令のうち、主記憶装置70の該当するバンクが空き状態にある命令を先に出力するようにしてもよい。例えば、ライトバッファ回路13が、主記憶装置70のバンクごとにキュー構造の記憶装置を備え、バンクごとに並行して命令を出力することにより、記憶装置70の該当するバンクが空き状態にある命令を先に出力できる。

【0049】

また、シーケンスS221と同様、中央処理装置60からロード命令が出力され(シーケンスS231)、シーケンスS222と同様、当該ロード命令がマージ回路11から出力され(シーケンスS232)、ストアバッファ回路12が、当該ロード命令に対応するアドレスのストア命令を記憶していると判定すると(シーケンスS233)、ストアバッファ回路12は、ロード命令を一時的に記憶し、ストア命令をライトバッファ回路13に出力する(追い出す。シーケンスS234)。その後、ストアバッファ回路12は、一時的に記憶していたロード命令をライトバッファ回路13に出力する(シーケンスS235)。

【0050】

そして、ライトバッファ回路13は、シーケンスS234にて出力されたストア命令を主記憶装置70に出力し(シーケンスS236)、その後、シーケンスS235にて出力されたロード命令を主記憶装置70に出力する(シーケンスS237)。

そして、主記憶装置70は、記憶するデータをストア命令に従って更新した後、ロード命令に従ってロードデータを中央処理装置60に出力する。

このように、ストアバッファ回路12がロード命令を一時的に記憶し、先にストア命令を出力することにより、主記憶装置70が、ストア命令の反映されていない誤ったロードデータを中央処理装置60に出力することを防止する。

【0051】

図13は、中央処理装置60からストア命令が出力された際の情報処理装置1の動作例を示すシーケンス図である。

中央処理装置60からストア命令が出力されると(シーケンスS301)、マージ回路11は、当該ストア命令をストアバッファ回路12に出力する(シーケンスS302)。ストアバッファ回路12は、マージ回路11から出力されたストア命令に対応するアドレスのストア命令を記憶しているか否かを判定する。当該ストア命令を記憶していないと判定すると(シーケンスS303)、ストアバッファ回路12は、当該ストア命令に含まれるアドレスを主記憶装置70に出力してストアデータを要求する(シーケンスS304)。そして、主記憶装置70は、要求されたストアデータをストアバッファ回路12に出力する(シーケンスS311)。

【0052】

ストアデータの出力を受けたストアバッファ回路12は、当該ストアデータをマージ回路11に出力する(シーケンスS312)。そして、マージ回路11は、ストアバッファ回路12から出力されたストアデータを、中央処理装置60から出力されたストア命令に従って更新し(シーケンスS313)、ストアデータ更新後のストア命令をストアバッファ回路12に出力する(シーケンスS314)。

ストアバッファ回路12は、マージ回路11から出力されたストア命令を記憶する(シーケンスS315)。

【0053】

また、シーケンスS311と同様、中央処理装置60からストア命令が出力され(シーケンスS321)、シーケンスS312と同様、当該ストア命令がマージ回路11から出力され(シーケンスS322)、ストアバッファ回路12が、当該当該ストア命令に対応するアドレスのストア命令を記憶している判定すると(シーケンスS323)、ストアバッファ回路12は、この記憶しているストア命令をマージ回路11に出力する(追い出す。シーケンスS324)。

【0054】

そして、マージ回路11は、ストアバッファ回路12から出力されたストアデータを、中央処理装置60から出力されたストア命令に従って更新する(シーケンスS325)。これにより、ストアバッファ回路12が記憶していたストア命令と、中央処理装置60から出力されたストア命令とがマージされる。そして、マージ回路11は、ストアデータ更新後のストア命令をストアバッファ回路12に出力する(シーケンスS326)。

ストアバッファ回路12は、マージ回路11から出力されたストア命令を記憶する(シーケンスS327)。

【0055】

図14は、ストアバッファ回路12がストア命令を追い出す際の情報処理装置1の動作例を示すシーケンス図である。

タイマ回路14は、タイマカウント値を追出制御回路15に随時出力する(シーケンスS401)。

また、ストアバッファ回路12は、アドレスアレイ121の各行の使用状況(記憶されているアドレスの数)を、フル検出回路16に随時出力し(シーケンスS411)、フル検出回路16は、ストアバッファ回路12から出力されるアドレスアレイ121の各行の使用状況と、予め記憶している1行に記憶可能なアドレスの数とに基づいて、各行について、残り容量の有無(新たなアドレスおよびストアデータを記憶可能か否か)を判定し、残り容量が無いと判定した場合は、当該行を示すアドレスを含むエントリフル信号を追出制御回路15に出力する。

【0056】

また、ライトバッファ回路13は、命令を記憶している先頭行を行番号にて示すリードポインタと、命令を記憶している末尾行の次の行を行番号にて示すライトポインタとをデータ数検出回路17に出力する(シーケンスS421)。そして、データ数検出回路17は、リードポインタとライトポインタとに基づいてライトバッファ回路13が記憶している命令数を算出し、算出した命令数を追出制御回路15に出力する(シーケンスS422)。

【0057】

そして、追出制御回路15は、タイマ回路14から出力されるタイマカウント値と、フル検出回路16から出力されるアドレスと、データ数検出回路17から出力される命令数とに基づいて、ストアバッファ回路12がストア命令の追い出しを行う必要があるか否かを判定し、追い出しを行う必要があると判定すると(シーケンスS431)、追出処理を指示する追出指示信号をストアバッファ回路12に出力する(シーケンスS432)。

【0058】

ストアバッファ回路12は、追出制御回路15から出力される追出指示信号に従って、ストア命令の追い出しを行う。具体的には、後述するように、追出対象のストア命令を決定し、当該ストア命令をライトバッファ回路13に出力し(シーケンスS433)、当該ストア命令を記憶していた記憶領域を開放して新たなデータを書込可能とする。

そして、ライトバッファ回路13は、ストアバッファ回路12から出力されたストア命令を一時的に記憶した後、主記憶装置70に出力する(シーケンスS434)。ライトバッファ回路から出力されたストア命令を受けた主記憶装置70は、当該ストア命令に従ってデータを更新する。

【0059】

次に、図15を参照して、ストアバッファ回路12が行う処理について説明する。

図15は、ストアバッファ回路12の処理手順を示すフローチャートである。ストアバッファ回路12は、同図の処理を随時繰り返し実行する。

まず、ストアバッファ制御回路123が、マージ回路11からストア命令が出力されたか否かを判定する(ステップS101)。ストア命令が出力されたと判定した場合、当該ストア命令をアレイ制御回路124と命令出力回路126とに出力する。

【0060】

そして、アレイ制御回路124は、当該ストア命令に含まれるアドレス値に対応する行の各領域のアドレスおよびストアデータを、読出回路125に出力するよう、アドレスアレイ121およびデータアレイ122を制御する。具体的には、アレイ制御回路124は、ストア命令に含まれるアドレス値のうち、中位アドレス値に対応する行の各領域に格納されているアドレス値を出力するようアドレスアレイ121を制御する。また、アレイ制御回路124は、当該中位アドレス値に対応する行の各領域に格納されているストアデータを出力するようアドレスアレイ121を制御する。

【0061】

読出回路125の命令出力回路126は、アドレスアレイ121から出力される各領域のデータのいずれかが、ストア命令に含まれるアドレス値にヒットするか否かを判定する(ステップS102)。具体的には、命令出力回路126は、判定対象のアドレス値の上位アドレス値と、アドレスアレイ121から出力された各領域のアドレス値の上位アドレス値とが同一か否かを判定する。上位アドレス値が同一のアドレス値があれば、命令出力回路126は、ヒットと判定し、無ければミスと判定する。

【0062】

ヒットと判定した場合(ステップS102:YES)、命令出力回路126は、データアレイ122に記憶されているストアデータのうち、アドレス値がヒットした領域と同じ行かつ同じ列の領域に格納さているストアデータを取得するよう指示する信号をデータ出力回路128に出力し、データ出力回路128は当該ストアデータを取得する(ステップS103)。

そして、データ出力回路128は、取得したストアデータを、マージ回路11に出力する(ステップS104)。

また、命令出力回路126は、ヒットしたアドレス値を含む開放要求信号をアレイ制御回路124に出力する。アレイ制御回路124は、アドレスアレイ121の、当該アドレス値に対応する領域(アドレスアレイ121の、当該アドレスを記憶している領域)に、アドレス値と識別可能な値を書き込む(ステップS104)。これにより、当該領域が空き領域となる。その後、同図の処理を終了する。

【0063】

一方、ステップS102にてミスと判定した場合(ステップS102:NO)、命令出力回路126は、ストア命令から読み出したアドレス値を含むデータ要求信号を主記憶装置70に出力する。そして、データ出力回路128が、主記憶装置70から出力される、当該アドレス値に対応するラインのデータを取得する(ステップS111)。そして、読出回路125は、取得したデータをマージ回路11に出力する(ステップS112)。その後、同図の処理を終了する。

【0064】

一方、ステップS101にて、ストア命令が出力されていないと判定した場合(ステップS101:NO)、ストアバッファ制御回路123は、マージ回路11からロード命令が出力されたか否かを判定する(ステップS121)。ロード命令が出力されたと判定した場合(ステップS121:YES)、ストアバッファ制御回路123は、当該ロード命令をアレイ制御回路124と命令出力回路126とに出力する。

そして、アレイ制御回路124は、上述したストア命令の場合と同様に、当該ロード命令に含まれるアドレス値に対応する行の各領域のアドレスおよびストアデータを、読出回路125に出力するよう、アドレスアレイ121およびデータアレイ122を制御する。また、読出回路125の命令出力回路126は、上述したストア命令の場合と同様に、アドレスアレイ121から出力される各領域のデータのいずれかが、ストア命令に含まれるアドレス値にヒットするか否かを判定する(ステップS122)。

ヒットすると判定した場合(ステップS122:YES)、命令出力回路126は、ロード命令退避回路127にロード命令を書き込む(ステップS123)。

【0065】

そして、命令出力回路126は、上述したストア命令の場合と同様に、データアレイ122に記憶されているストアデータのうち、アドレス値がヒットした領域と同じ行かつ同じ列の領域に格納さているストアデータを取得するよう指示する信号をデータ出力回路128に出力し、データ出力回路128は当該ストアデータのうち、アドレス値がヒットした領域と同じ行かつ同じ列の領域に格納さているストアデータを取得する(ステップS124)。

また、命令出力回路125は、ストア命令を示すコマンド名(例えば「S」)を予め記憶しておき、当該コマンド名と、ヒットしたアドレス値とに基づいてストア命令を生成する。そして、命令出力回路125は、生成したストア命令をライトバッファ回路13に出力する。また、データ出力回路128は、取得したストアデータをライトバッファ回路13に出力する(ステップS125)。

【0066】

また、命令出力回路126は、ヒットしたアドレス値を含む開放要求信号をアレイ制御回路124に出力する。アレイ制御回路124は、アドレスアレイ121の、当該アドレスに対応する領域に、アドレス値と識別可能な値を書き込む(ステップS126)。これにより、当該領域が空き領域となる。

さらに、命令出力回路126は、ロード命令退避回路127からロード命令を読み出し、読み出したロード命令をライトバッファ回路13に出力する(ステップS127)。その後、同図の処理を終了する。

一方、ステップS122にて、ヒットしないと判定した場合(ステップS122:NO)、命令出力回路126は、ロード命令をライトバッファ回路13に出力する(ステップS131)。その後、同図の処理を終了する。

【0067】

一方、ステップS121にて、ロード命令が出力されていないと判定した場合、ストアバッファ制御回路123は、追出制御回路15から追出指示信号が出力されたか否かを判定する(ステップS141)。追出指示信号が出力されたと判定した場合(ステップS141:YES)、ストアバッファ制御回路123は、当該追出指示信号をアレイ制御回路124と命令出力回路126とに出力する。アレイ制御回路124は、追出対象となるストア命令のアドレス値およびストアデータを、読出回路125に出力するよう、アドレスアレイ121およびデータアレイ122を制御する。そして、命令出力回路126は、アドレスアレイ121から出力されるアドレス値を取得し、データ出力回路128は、データアレイ122から出力されるストアデータを取得する(ステップS142)。

【0068】

ここで、アレイ制御回路124は、追出指示信号にアドレス値が含まれているか否かを判定する。そして、アドレス値が含まれていると判定した場合、アレイ制御回路124は、アドレスアレイ121を参照して、当該アドレス値に対応する行の各領域のうち、最後にアクセスされた時刻が最も古いストア命令を、追出対象のストア命令に決定する。一方、アドレス値が含まれていないと判定した場合、アレイ制御回路124は、アドレスアレイ121を参照して、全領域のうち最後にアクセスされた時刻が最も古いストア命令を、追出対象のストア命令に決定する。

【0069】

そして、命令出力回路126は、ステップS125と同様に、アドレスアレイ121から出力されるアドレスを含む命令を生成し、生成したストア命令をライトバッファ回路13に出力する。また、データ出力回路128は、取得したストアデータをライトバッファ回路13に出力する(ステップS143)。

【0070】

また、命令出力回路126は、取得したアドレス値を含む開放要求信号をアレイ制御回路124に出力する。アレイ制御回路124は、アドレスアレイ121の、当該アドレスに対応する領域に、アドレス値と識別可能な値を書き込む(ステップS126)。これにより、当該領域が空き領域となる。その後、同図の処理を終了する。

一方、ステップS141において、追出指示信号が出力されていないと判定した場合(ステップS141:NO)同図の処理を終了する。

【0071】

次に、図16を参照してストアバッファ回路12が記憶するデータ量について記憶する。

図16は、ストアバッファ回路12が記憶するデータ量(ストア命令数)の変化を示すグラフである。線L131はストアバッファ回路12が記憶するデータ量の変化の例を示す。線L132は、追出制御回路15が、ライトバッファデータ数がデータ数設定値より大きい場合と、エントリフル信号が「1」の場合に追出指示信号として「1」を出力する場合に、ストアバッファ回路12が記憶するデータ量の変化を示すグラフである。

線L131が示すように、最初に命令が出力されてから一定時間は追出制御回路15が追出指示信号の出力を抑制することで、ストアバッファ回路12にストア命令が蓄積され、中央処理装置60からストア命令に対して、ストアバッファ回路12の記憶するストア命令がヒットする率が向上する。これにより、主記憶装置70へのアクセス頻度を抑えることが出来る。

【0072】

以上のように、ストアバッファ回路12が複数のストア命令を記憶してマージ回路11に出力するので、主記憶装置70上の異なるアドレスに対するストア命令が中央処理装置60から出力された場合にも、当該アドレスに対するストアデータをストアバッファ回路12が記憶していることが期待できる。そして、ストアバッファ回路12がストアデータを記憶している場合、主記憶装置70へのアクセスを抑えることができ、主記憶装置70へのアクセス待ちによる中央処理装置60の処理速度低下を防止できる。

【0073】

また、中央処理装置60が、プログラム実行開始時などの処理開始時、すなわち、ストアバッファ回路12の記憶するストア命令の数が少ないと考えられるタイミングでリセット信号を出力し、タイマ回路14は、当該リセット信号が出力された後、中央処理装置60から最初の命令が出力されるとカウントアップを開始する。そして、ストアバッファ回路12は、ライトバッファ回路13の記憶するデータ数がデータ数設定値以下になった場合でも、最初の命令が出力されてから一定時間経過するまでは、ストア命令の追い出しを抑制するので、中央処理装置60からストア命令が出力された際のヒット率を高めることが出来る。

また、最初の命令が出力されてから一定時間経過後は、ライトバッファ回路13の記憶するデータ数がデータ数設定値以下になった場合に、ストアバッファ回路12がストア命令の追い出しを行うので、ライトバッファ回路13の記憶するデータ数(ストア命令の数)の増大を防止でき、ライトバッファ回路が主記憶装置70にアクセスする際のスループット低下を防止できる。

【0074】

なお、タイマ回路の構成は上述したものに限らない。例えば、中央処理装置60がリセット信号を出力せず、タイマ回路自身がリセット信号を生成するようにしてもよい。

図17は、タイマ回路の変形例を示す構成図である。同図において、タイマ回路24は、命令受付回路141と、レジスタ142および241と、OR回路143および148と、AND回路144、145および243と、カウンタ146と、カウント信号出力回路147と、大小比較回路242とを具備する。同図において、図8の各部と同様の機能を有する部分には同一の符号(141〜148)を付し、説明を省略する。

【0075】

レジスタ241は、予め定められたデータ数設定値として「1」を記憶する。大小比較回路242は、データ数検出回路17から経路W241にて出力されるライトバッファデータ数と、レジスタ241の記憶するデータ数設定値とを比較し、ライトバッファデータ数がデータ数設定値より小さい場合、すなわちライトバッファデータ数が0の場合に「1」を出力し、その他の場合に「0」を出力する。AND回路243は、ライトバッファデータ数がデータ数設定値より小さく、かつ、カウンタ146のある桁以上のビット値が1であるとき(例えば、下位から9桁目以上のいずれかの桁のビット値が1であるとき)にカウンタリセット信号「1」を出力し、その他のときに「0」を出力する。

【0076】

この構成により、タイマ回路24がカウントを開始してから一定時間以上が経過し、かつ、ライトバッファデータ数が0であるときにカウンタリセット信号を生成できる。したがって、ライトバッファ回路13が空のときにタイマ回路24がタイマカウント値をリセットして、ストアバッファ回路12がストア命令を蓄積し、中央処理装置60からストア命令が出力された際のヒット率を高めることができる。

ここで、ストアバッファ回路12が蓄積するストア命令の数が増加した場合、ストアバッファ回路12が連続してストア命令を追い出し、ライトバッファ回路13に蓄積される命令の量が増大することが考えられる。この場合、ライトバッファ回路13から主記憶装置70への命令の出力に時間を要し、中央制御装置60がロード命令を出力した際にデータを取得するまでの待ち時間が増大するおそれがある。さらには、ライトバッファ回路13に空き領域がなくなった場合は、ライトバッファ回路13に空き領域が生じるまで、ストアバッファ回路12がストア命令の追出を待つ必要が生じ、処理の遅延につながる。

そこで、上記のように、ライトバッファ回路13が空のときにストアバッファ回路12がストア命令を蓄積することにより、ライトバッファ回路13に大量の命令が蓄積されることを防止でき、待ち時間による処理の遅延を抑制しうる。

【0077】

また、タイマ回路24がカウンタリセット信号を生成するので、中央処理装置60がリセット信号を出力する必要がない。したがって、中央処理装置60とタイマ回路24との間で入出力されるデータ量を削減でき、また、中央処理装置60がカウンタリセット信号を生成する負荷を軽減できる。

【0078】

なお、ストアマージ装置10の全部または一部の機能を実現するためのプログラムをコンピュータ読み取り可能な記録媒体に記録して、この記録媒体に記録されたプログラムをコンピュータシステムに読み込ませ、実行することにより各部の処理を行ってもよい。なお、ここでいう「コンピュータシステム」とは、OSや周辺機器等のハードウェアを含むものとする。

また、「コンピュータシステム」は、WWWシステムを利用している場合であれば、ホームページ提供環境(あるいは表示環境)も含むものとする。

また、「コンピュータ読み取り可能な記録媒体」とは、フレキシブルディスク、光磁気ディスク、ROM、CD−ROM等の可搬媒体、コンピュータシステムに内蔵されるハードディスク等の記憶装置のことをいう。さらに「コンピュータ読み取り可能な記録媒体」とは、インターネット等のネットワークや電話回線等の通信回線を介してプログラムを送信する場合の通信線のように、短時間の間、動的にプログラムを保持するもの、その場合のサーバやクライアントとなるコンピュータシステム内部の揮発性メモリのように、一定時間プログラムを保持しているものも含むものとする。また上記プログラムは、前述した機能の一部を実現するためのものであっても良く、さらに前述した機能をコンピュータシステムにすでに記録されているプログラムとの組み合わせで実現できるものであっても良い。

【0079】

以上、本発明の実施形態を図面を参照して詳述してきたが、具体的な構成はこの実施形態に限られるものではなく、この発明の要旨を逸脱しない範囲の設計変更等も含まれる。

【符号の説明】

【0080】

1 情報処理装置

10 ストアマージ装置

11 マージ回路

12 ストアバッファ回路

13 ライトバッファ回路

14 タイマ回路

15 追出制御回路

16 フル検出回路

17 データ数検出回路

60 中央処理装置

70 主記憶装置

【特許請求の範囲】

【請求項1】

複数のデータを記憶可能なストアバッファ回路と、

ストア命令の入力を受けると、前記ストアバッファ回路が記憶する前記複数のデータのいずれかと前記ストア命令のデータとをマージ処理可能か否か判定し、マージ処理可能なデータがあると判定したときは、前記ストアバッファ回路の記憶する複数のデータのうちマージ処理可能と判定した前記データを選択するマージ対象データ選択回路と、

前記マージ対象データ選択部が選択したデータと前記ストア命令のデータとをマージ処理し、マージ処理されたデータを前記ストアバッファ回路に書き戻すマージ回路と、

前記ストアバッファ回路が前記複数のデータのいずれかを出力するよう指示する追出指示信号を出力する追出制御回路と、

を具備することを特徴とするストアマージ装置。

【請求項2】

前記追出制御回路は、中央処理装置からリセット信号が出力され、最初の命令が出力されてから所定時間経過した後に、前記追出指示信号を出力することを特徴とする請求項1に記載のストアマージ装置。

【請求項3】

前記ストアバッファ回路が出力するデータを一時的に記憶して出力するライトバッファ回路を具備し、

前記追出制御回路は、前記ライトバッファ回路がデータを記憶していない状態から所定時間経過した後に、前記ライトバッファ回路の記憶するデータ数が所定数以下となると前記追出指示信号を出力することを特徴とする請求項1に記載のストアマージ装置。

【請求項4】

複数のデータを記憶可能な主記憶装置と、

前記主記憶装置へのデータの書込命令であるストア命令を出力する中央処理装置と、

複数のデータを記憶可能なストアバッファ回路と、

前記中央処理装置から前記ストア命令が出力されると、前記ストアバッファ回路が記憶する前記複数のデータのいずれかと前記ストア命令のデータとをマージ処理可能か否か判定し、マージ処理可能なデータがあると判定したときは、前記ストアバッファ回路の記憶する複数のデータのうちマージ処理可能と判定した前記データを選択するマージ対象データ選択回路と、

前記マージ対象データ選択部が選択したデータと前記ストア命令のデータとをマージ処理し、マージ処理されたデータを前記ストアバッファ回路に書き戻すマージ回路と、

前記ストアバッファ回路が当該ストアバッファ回路の記憶するデータの前記主記憶装置への書込要求を出力するよう指示する追出指示信号を出力する追出制御回路と、

を具備することを特徴とする情報処理装置。

【請求項5】

複数のデータを記憶可能なストアバッファ回路を具備するストアマージ装置のストアマージ方法であって、

マージ対象データ選択回路が、ストア命令の入力を受けると、前記ストアバッファ回路が記憶する前記複数のデータのいずれかと前記ストア命令のデータとをマージ処理可能か否か判定し、マージ処理可能なデータがあると判定したときは、前記ストアバッファ回路の記憶する複数のデータのうちマージ処理可能と判定した前記データを選択するマージ対象データ選択ステップと、

マージ回路が、前記マージ対象データ選択部が選択したデータと前記ストア命令のデータとをマージ処理し、マージ処理されたデータを前記ストアバッファ回路に書き戻すマージステップと、

追出制御回路が、前記ストアバッファ回路が前記複数のデータのいずれかを出力するよう指示する追出指示信号を出力する追出制御ステップと、

を具備することを特徴とするストアマージ方法。

【請求項6】

複数のデータを記憶可能なストアバッファ回路を具備するストアマージ装置としてのコンピュータに

ストア命令の入力を受けると、前記ストアバッファ回路が記憶する前記複数のデータのいずれかと前記ストア命令のデータとをマージ処理可能か否か判定し、マージ処理可能なデータがあると判定したときは、前記ストアバッファ回路の記憶する複数のデータのうちマージ処理可能と判定した前記データを選択するマージ対象データ選択ステップと、

前記マージ対象データ選択部が選択したデータと前記ストア命令のデータとをマージ処理し、マージ処理されたデータを前記ストアバッファ回路に書き戻すマージステップと、

前記ストアバッファ回路が前記複数のデータのいずれかを出力するよう指示する追出指示信号を出力する追出制御ステップと、

を実行させるためのプログラム。

【請求項1】

複数のデータを記憶可能なストアバッファ回路と、

ストア命令の入力を受けると、前記ストアバッファ回路が記憶する前記複数のデータのいずれかと前記ストア命令のデータとをマージ処理可能か否か判定し、マージ処理可能なデータがあると判定したときは、前記ストアバッファ回路の記憶する複数のデータのうちマージ処理可能と判定した前記データを選択するマージ対象データ選択回路と、

前記マージ対象データ選択部が選択したデータと前記ストア命令のデータとをマージ処理し、マージ処理されたデータを前記ストアバッファ回路に書き戻すマージ回路と、

前記ストアバッファ回路が前記複数のデータのいずれかを出力するよう指示する追出指示信号を出力する追出制御回路と、

を具備することを特徴とするストアマージ装置。

【請求項2】

前記追出制御回路は、中央処理装置からリセット信号が出力され、最初の命令が出力されてから所定時間経過した後に、前記追出指示信号を出力することを特徴とする請求項1に記載のストアマージ装置。

【請求項3】

前記ストアバッファ回路が出力するデータを一時的に記憶して出力するライトバッファ回路を具備し、

前記追出制御回路は、前記ライトバッファ回路がデータを記憶していない状態から所定時間経過した後に、前記ライトバッファ回路の記憶するデータ数が所定数以下となると前記追出指示信号を出力することを特徴とする請求項1に記載のストアマージ装置。

【請求項4】

複数のデータを記憶可能な主記憶装置と、

前記主記憶装置へのデータの書込命令であるストア命令を出力する中央処理装置と、

複数のデータを記憶可能なストアバッファ回路と、

前記中央処理装置から前記ストア命令が出力されると、前記ストアバッファ回路が記憶する前記複数のデータのいずれかと前記ストア命令のデータとをマージ処理可能か否か判定し、マージ処理可能なデータがあると判定したときは、前記ストアバッファ回路の記憶する複数のデータのうちマージ処理可能と判定した前記データを選択するマージ対象データ選択回路と、

前記マージ対象データ選択部が選択したデータと前記ストア命令のデータとをマージ処理し、マージ処理されたデータを前記ストアバッファ回路に書き戻すマージ回路と、

前記ストアバッファ回路が当該ストアバッファ回路の記憶するデータの前記主記憶装置への書込要求を出力するよう指示する追出指示信号を出力する追出制御回路と、

を具備することを特徴とする情報処理装置。

【請求項5】

複数のデータを記憶可能なストアバッファ回路を具備するストアマージ装置のストアマージ方法であって、

マージ対象データ選択回路が、ストア命令の入力を受けると、前記ストアバッファ回路が記憶する前記複数のデータのいずれかと前記ストア命令のデータとをマージ処理可能か否か判定し、マージ処理可能なデータがあると判定したときは、前記ストアバッファ回路の記憶する複数のデータのうちマージ処理可能と判定した前記データを選択するマージ対象データ選択ステップと、

マージ回路が、前記マージ対象データ選択部が選択したデータと前記ストア命令のデータとをマージ処理し、マージ処理されたデータを前記ストアバッファ回路に書き戻すマージステップと、

追出制御回路が、前記ストアバッファ回路が前記複数のデータのいずれかを出力するよう指示する追出指示信号を出力する追出制御ステップと、

を具備することを特徴とするストアマージ方法。

【請求項6】

複数のデータを記憶可能なストアバッファ回路を具備するストアマージ装置としてのコンピュータに

ストア命令の入力を受けると、前記ストアバッファ回路が記憶する前記複数のデータのいずれかと前記ストア命令のデータとをマージ処理可能か否か判定し、マージ処理可能なデータがあると判定したときは、前記ストアバッファ回路の記憶する複数のデータのうちマージ処理可能と判定した前記データを選択するマージ対象データ選択ステップと、

前記マージ対象データ選択部が選択したデータと前記ストア命令のデータとをマージ処理し、マージ処理されたデータを前記ストアバッファ回路に書き戻すマージステップと、

前記ストアバッファ回路が前記複数のデータのいずれかを出力するよう指示する追出指示信号を出力する追出制御ステップと、

を実行させるためのプログラム。

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【図14】

【図15】

【図16】

【図17】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【図14】

【図15】

【図16】

【図17】

【公開番号】特開2012−43202(P2012−43202A)

【公開日】平成24年3月1日(2012.3.1)

【国際特許分類】

【出願番号】特願2010−184140(P2010−184140)

【出願日】平成22年8月19日(2010.8.19)

【出願人】(000168285)エヌイーシーコンピュータテクノ株式会社 (572)

【Fターム(参考)】

【公開日】平成24年3月1日(2012.3.1)

【国際特許分類】

【出願日】平成22年8月19日(2010.8.19)

【出願人】(000168285)エヌイーシーコンピュータテクノ株式会社 (572)

【Fターム(参考)】

[ Back to top ]