スパッタリング方法および装置

【課題】簡単な構成で、簡単な制御で、逆スパッタの防止による膜の高品質化、組成ズレの制御および成膜の再現性向上を図り、膜質の変化のない高品質な圧電膜、絶縁膜や導電体膜などの薄膜を成膜することができるスパッタリング方法およびスパッタリング装置を提供する。

【解決手段】真空容器内に、ターゲット材を保持するスパッタ電極およびスパッタ電極と対向離間配置され、基板を保持する基板ホルダを有し、さらに基板ホルダのインピーダンスを調整するための調整可能なインピーダンス回路を備えるインピーダンス調整回路とを有し、インピーダンス回路のインピーダンスが調整されることにより、基板ホルダのインピーダンスが調整され、基板の電位が調整されることにより、上記課題を解決する。

【解決手段】真空容器内に、ターゲット材を保持するスパッタ電極およびスパッタ電極と対向離間配置され、基板を保持する基板ホルダを有し、さらに基板ホルダのインピーダンスを調整するための調整可能なインピーダンス回路を備えるインピーダンス調整回路とを有し、インピーダンス回路のインピーダンスが調整されることにより、基板ホルダのインピーダンスが調整され、基板の電位が調整されることにより、上記課題を解決する。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、スパッタリング方法および装置に関し、詳しくは、プラズマを用いた気相成長法により絶縁膜(絶縁体)や誘電膜(誘電体)や、強誘電体(圧電体)組成物などの薄膜の成膜を行うスパッタリング方法、およびこれを実施するために用いられるスパッタリング装置に関するものである。

【背景技術】

【0002】

従来より、圧電膜、絶縁膜、誘電体膜等の薄膜を成膜するために、プラズマを用いた気相成長法により成膜するスパッタリング方法やこれを実施するスパッタリング装置が用いられている。このようなスパッタリング方法および装置では、高真空中でプラズマ放電により生成される高エネルギのArイオン等のプラズマイオンをターゲットに衝突させて、ターゲットの構成元素を放出させ、放出されたターゲットの構成元素を基板の表面に蒸着させることにより、基板上に薄膜を形成している。

【0003】

スパッタリング方法および装置においては、良質な薄膜を形成するために、真空容器内に設けられたスパッタ電極と対向する位置に配置された基板電極に保持された基板の表面に所定の電位を与えてスパッタリングを行っている。

このようなスパッタリング方法および装置で作製される薄膜デバイスにおいては、薄膜内の膜厚、組成および結晶相などを制御し、面内特性のばらつきを押さえることが求められる。

【0004】

このため、スパッタリング装置で薄膜を成膜する場合には、プラズマの状態を均一化させることで、面内を均一にすることが求められる(例えば、特許文献1、2、3、4および5参照)。

特許文献1では、膜厚分布や薄膜の膜組成を均一にするために、ターゲット近傍に磁場を形成するためのマグネットとして、極性や強さを制御できる電磁石を用いて、形成される磁場を制御することにより、異常放電がない均一なプラズマを生成し、ターゲット面内での全面均一エロージョンを実現する技術が開示されている。このように、均一なプラズマを生成するために、ターゲット(カソード)側に工夫することは、良く知られている。

【0005】

ところで、金属ではなく、絶縁物(絶縁体・誘電体・焦電体・圧電体)を成膜する場合は、金属の場合よりさらに、プラズマの均一性が要求されることが知られている。

このため、例えば、特許文献2では、スパッタリング装置の装置側壁の電位に工夫を加えている。特許文献2には、スパッタリング装置で絶縁膜を成膜する場合、側壁を絶縁膜付着とともに電位を制御することで、プラズマを制御し、均一な組成を有する絶縁膜を生成する方法が記載されている。

【0006】

また、上記ターゲット側の工夫や装置側壁の電位の工夫に対し、成膜基板付近のプラズマ状態を制御することで、絶縁膜の成膜を均一化することも試みられている。

特許文献3では、成膜基板とスパッタリング装置とを絶縁することで、均一のプラズマにし、膜中の組成分布が均一な絶縁膜を作製する技術が公開されている。

しかしながら、特許文献1、2および3に開示された技術は、それぞれの点から膜質の改善を図っているが、これだけでは膜質をより均一化するのは不十分であり、そのため、成膜基板付近のマスク・冶具などを工夫することがなされている。

【0007】

特許文献4では、成膜基板付近に設置したマスクを、フローティング電位にしたり、アースに落したり、両者を組合せることで、適切な成膜条件を選択する技術が開示されている。具体的には、成膜マスク(成膜冶具)として、アース電位に接続されたアースマスクと、アース電位から絶縁されたフローティングマスクと、アース電位に接続された部分とアース電位から絶縁された部分とを備えるプラズマ制御マスクとで構成し、プラズマ制御マスクのアース電位に接続された部分とアース電位から絶縁されたフローティング部分との量を調節して、最適な成膜条件としている。

【0008】

また、特許文献5では、被処理基板を保持する基板保持部材と、これに併設され、かつ装置本体との間に絶縁性部材を介して配置された防着部材とを等電位にし、かつフローティングすることにより、異常放電を抑制し、成膜レートを向上させるとともに、膜厚均一性が向上できる技術が開示されている。また、特許文献5では、上述した基板保持部材と防着部材とを等電位にするに加え、防着部材の電位を接地あるいはフローティングに切り替えることにより、絶縁膜と導電膜との膜の種類に応じて電位状態を変えることができるので、上記効果を膜の種類に応じて達成することができる技術を開示している。

【0009】

【特許文献1】特開平6−41740号公報

【特許文献2】特開2007−42919号公報

【特許文献3】特開平7−231045号公報

【特許文献4】特開2001−335930号公報

【特許文献5】特開2006−83459号公報

【発明の開示】

【発明が解決しようとする課題】

【0010】

しかしながら、特許文献4においては、アース部分とフローティング部分を適度な割合にする旨の記載があるが、特に理屈がなく試行錯誤により、最適条件を定めている。そのため、側壁に絶縁物がついたり、ターゲット材料が変化したりといったプラズマ状態の変化に応じて、その度に、試行錯誤を繰り返す必要があるという問題がある。また、特許文献4に開示の技術は、均一な膜厚の薄膜を形成するものであるが、薄膜の電気的特性などの膜質の均一性、例えば、絶縁膜などの絶縁特性の均一性、特に、面内均一性などについては、全く考慮されていないという問題がある。

【0011】

また、特許文献5に関しては、膜厚が均一になることは記載されているが、特許文献4と同様に、薄膜の電気的特性などの膜質、例えば、絶縁膜などの絶縁特性など、絶縁膜の端部の電気特性がどのようになるかといったより細かいところまでは検討されておらず、不十分であるという問題がある。すなわち、特許文献5に開示の技術は、基板保持部材と防着部材とを等電位にすることにより、両者の間の異常放電の発生を防止して、成膜速度を低下させず、膜厚分布を均一にする技術に過ぎず、薄膜の電気的特性などの膜質の均一性、例えば、絶縁膜などの絶縁特性の均一性、特に、面内均一性などについては、全く考慮されていないという問題がある。

【0012】

本発明の目的は、上記従来技術の問題点を解消し、膜質のばらつきや組成ずれがなく、電気的特性などの膜特性の均一性、特に面内均一性に優れた高品質な絶縁膜や導電体膜などの薄膜、例えば絶縁特性の均一性、特に面内均一性に優れた絶縁膜などの薄膜を成膜することができるスパッタリング方法および装置を提供することにある。

【課題を解決するための手段】

【0013】

上記課題を解決するために、本発明者らは、上記目的を達成するために、上記特許文献1〜5を始めとして多くの従来技術を検討し、このような膜特性に優れた高品質な薄膜を成膜することができるスパッタリング方法およびスパッタリング装置について、鋭意研究を重ねた結果、上記特許文献4および5の技術のみでは、絶縁特性や電気的特性などの膜特性が均一にならないということを見出した。すなわち、本発明者等は、特許文献4および5では共に、基板周辺部の電位については考慮されているものの、成膜基板と周辺部との電位の関係について考えられていないことが、絶縁特性や電気的特性などの膜特性が均一にならない原因であり、特に、特許文献5のように、被処理基板としてシリコン基板のような半導体基板に薄膜を成膜する場合に、膜厚を均一化や成膜速度の向上には、基板保持部材と防着部材とを等電位にして、両者の間の異常放電の発生を防止するだけで十分であるが、表面に導電性を有する成膜基板の導電性の表面に圧電幕等の絶縁膜を形成する場合には、これだけでは不十分であり、膜特性を均一にできないことを知見するとともに、膜特性を均一にするには、導電性の表面を有する成膜基板の外側に、導電性の表面と等電位である等電位表面を持つ等電位表面形成部材を設置する必要があることを知見し、本発明に至ったものである。

【0014】

すなわち、本発明の第1の態様は、少なくとも1面に導電性の表面を有する成膜基板に薄膜を成膜するスパッタリング方法であって、前記成膜基板の外側に、この成膜基板の前記導電性の表面と等電位である等電位表面を持つ等電位表面形成部材を設置して、前記成膜基板の前記導電性の表面上に前記薄膜を作製することを特徴とするスパッタリング方法を提供するものである。

【0015】

ここで、前記成膜基板の外側において、前記等電位表面形成部材の前記等電位表面の面積が、前記成膜基板の前記導電性の表面の面積の40%以上であるのが好ましく、また、より好ましくは、70%以上であるのが良く、また、最も好ましくは、150%以上であるのが良い。

また、前記等電位表面形成部材が、前記等電位表面に付着している絶縁膜の厚みが10μm以下の部材であるのが好ましく、また、最も好ましくは、前記等電位表面に絶縁膜が付着していない部材であるのが良い。

また、前記等電位表面形成部材の前記等電位表面に付着する絶縁膜の厚みが、0または10μm以下である間に、前記成膜基板の前記導電性の表面上に前記膜を作製するのが好ましい。

【0016】

また、前記膜を作製する成膜材料が、絶縁体であるのが好ましく、また、より好ましくは、チタン酸鉛もしくはジルコン酸鉛を含むのが良い。

また、前記成膜基板が、導電性基板であるのが好ましい。

また、前記成膜基板の前記導電性の表面と、前記等電位表面形成部材の前記等電位表面とが、導通しているのが好ましい。

また、前記等電位表面形成部材は、前記等電位表面が前記成膜基板の前記導電性の表面より、前記膜を作製する成膜材料に近い側に在るまたは来るように、設置されるのが好ましい。

【0017】

また、上記目的を達成するために、本発明の第2の態様は、真空容器と、この真空容器内に設けられ、スパッタリング用のターゲット材を保持するスパッタ電極と、このスパッタ電極に接続され、前記スパッタ電極に高周波を印加する高周波電源と、前記真空容器内の、前記スパッタ電極と対向する位置に離間して配置され、前記ターゲット材の成分による薄膜が成膜され、少なくとも1面に導電性の表面を有する成膜基板を保持する基板ホルダと、前記基板ホルダに保持される前記成膜基板の外側に設置される前記等電位表面形成部材とを有し、前記等電位表面形成部材は、前記成膜基板の前記導電性の表面と等電位である等電位表面を持ち、前記薄膜は、前記成膜基板の前記導電性の表面上に作製されることを特徴とするスパッタリング装置を提供するものである。

【0018】

ここで、前記等電位表面形成部材は、前記成膜基板の外側における前記等電位表面の面積が、前記成膜基板の前記導電性の表面の面積の40%以上であるのが好ましく、また、より好ましくは、70%以上であるのが良く、また、最も好ましくは、150%以上であるのが良い。

また、前記成膜基板は、導電性基板であるのが好ましい。

また、前記成膜基板の前記導電性の表面と、前記等電位表面形成部材の前記等電位表面とは、導通しているであるのが好ましい。

【0019】

また、前記等電位表面形成部材は、前記等電位表面に付着している絶縁膜の厚みが10μm以下の部材であるのが好ましく、また、最も好ましくは、前記等電位表面に絶縁膜が付着していない部材であるのが良い。

また、前記等電位表面形成部材は、前記等電位表面に付着する絶縁膜の厚みが0または10μm以下であるのが好ましい。

また、前記膜を作製する成膜材料が、絶縁体であるのが好ましい。

また、前記膜を作製する成膜材料が、チタン酸鉛もしくはジルコン酸鉛を含むのが好ましい。

また、前記等電位表面形成部材は、前記等電位表面が前記成膜基板の前記導電性の表面より前記スパッタ電極に近い側に在るまたは来るように、設置されるのが好ましい。

【発明の効果】

【0020】

本発明の第1および第2の態様によれば、膜質のばらつきや組成ずれがなく、電気的特性などの膜特性の均一性、特に、面内均一性に優れた高品質な絶縁膜や導電体膜などの薄膜、例えば絶縁特性の均一性、特に、面内均一性に優れた絶縁膜などの薄膜を成膜することができるという効果を奏する。

特に、膜質のばらつきや組成ズレがなく、PZT等のPb含有ペロブスカイト型酸化物からなり、パイロクロア相の少ないペロブスカイト結晶が安定的に成長し、しかもPb抜けが安定的に抑制され、絶縁特性の均一性、特に、面内均一性に優れた圧電膜を成膜することができるという効果を奏する。

【発明を実施するための最良の形態】

【0021】

以下に、本発明の第1の態様に係るスパッタリング方法および本発明の第2の態様に係るスパッタリング装置について、添付の図面に示す好適な実施形態に基づいて詳細に説明する。

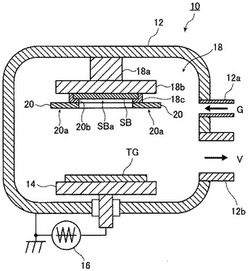

図1は、本発明のスパッタリング方法を実施する本発明のスパッタリング装置の一実施形態の装置構成を概念的に示す概略断面図である。以下では、薄膜として圧電膜を成膜するスパッタリング装置を代表例として説明するが、本発明はこれに限定されないのはいうまでもない。

【0022】

同図に示すように、本発明のスパッタリング装置10は、少なくとも1面に導電性の表面を有する成膜基板(以下、単に基板という)SBの導電性の表面SBa上に、絶縁膜、誘電体膜などの薄膜、特に圧電膜を成膜するための、すなわち、基板SBの導電性の表面SBa上にプラズマを用いた気相成長法(スパッタリング)により圧電膜などの絶縁性薄膜を成膜し、圧電素子などの薄膜デバイスを製造するRFスパッタリング装置であって、ガス導入管12aおよびガス排出管12bを備える真空容器12と、この真空容器(真空チャンバともいう)12内に設けられ、スパッタリング用のターゲット材TGを保持し、プラズマを発生させるスパッタ電極(カソード電極)14と、このスパッタ電極14に接続され、スパッタ電極14に高周波を印加する高周波電源16と、真空容器12内の、スパッタ電極14と対向する位置に配置され、ターゲット材TGの成分による薄膜が成膜される基板SBを保持する基板ホルダ18と、基板ホルダ18に保持される基板SBの外側に設置され、基板SBの導電性の表面SBaと等電位である等電位表面20aを持つ等電位表面形成部材20とを有する。

【0023】

真空容器12は、スパッタリングを行うために所定の真空度を維持する、鉄、ステンレス、アルミニウム等で形成される気密性の高い容器であって、図示例においては、接地され、その内部に成膜に必要なガスを導入するガス導入管12aおよび真空容器12内のガスの排気を行うガス排出管12bが取り付けられている。ガス導入管12aから真空容器12内に導入されるガスとしては、アルゴン(Ar)、または、アルゴン(Ar)と酸素(O2)の混合ガス等を用いることができる。ガス導入管12aは、これらのガスの供給源(図示せず)に接続されている。一方、ガス排出管12bは、真空容器12内を所定の真空度にすると共に、成膜中にこの所定の真空度に維持するために、真空容器12内のガスを排気するため、真空ポンプ等の排気手段に接続されている。

なお、真空容器12としては、スパッタリング装置で利用される真空チャンバ、ベルジャー、真空槽などの種々の真空容器を用いることができる。

【0024】

スパッタ電極14は、真空容器12の内部の上方に配置され、その表面上(図中、上面)に成膜する圧電膜などの薄膜の組成に応じた組成のターゲット材TGを装着し、保持するようになっており、高周波電源16に接続されている。

高周波電源16は、真空容器12内に導入されたArなどのガスをプラズマ化させるための高周波電力(負の高周波)をスパッタ電極14に供給するためのものであり、その一方の端部がスパッタ電極14に接続され、他方の端部が接地されている。なお、高周波電源16がスパッタ電極14に印加する高周波電力は、特に制限的ではなく、例えば13.65MHz、最大5kW、あるいは、最大1kWの高周波電力などを挙げることができるが、例えば50kHz〜2MHz、27.12MHz、40.68MHz、60MHz、1kW〜10kWの高周波電力を用いるのが好ましい。

【0025】

スパッタ電極14は、高周波電源13からの高周波電力(負の高周波)の印加により放電して、真空容器12内に導入されたArなどのガスをプラズマ化し、Arイオン等のプラスイオンを生成させる。したがって、スパッタ電極14は、カソード電極またはプラズマ電極と呼ぶこともできる。

こうして生成されたプラスイオンは、スパッタ電極14に保持されたターゲット材TGをスパッタする。このようにして、プラスイオンにスパッタされたターゲット材TGの構成元素は、ターゲット材TGから放出され、中性あるいはイオン化された状態で、対向離間配置された基板ホルダ18に保持された基板SB上に蒸着される。

こうして、詳細は後述するが、図中に点線で示すように、真空容器12の内部にArイオン等のプラスイオンやターゲット材TGの構成元素やそのイオンなどを含むプラズマ空間Pが形成される。

【0026】

基板ホルダ18は、真空容器12の内部の上方に、スパッタ電極14と対向する位置に離間して配置され、スパッタ電極14に保持されたターゲット材TGの構成元素(成分)が蒸着され、圧電膜などの薄膜が成膜される基板SBを保持、すなわち図中上面から支持するためのものである。なお、基板ホルダ18は、真空容器12の内部の上方に取り付けられる基部18aと、基部18aに取り付けられ、基板SBの外径より大きい外径を持つ基板取付台18bと、基板取付台18bに取り付けられ、先端(図中下端)が内側に折れ曲がった複数のL字状の基板保持部材18cとを有し、基板SBの導電性表面SBaがターゲット材TG(スパッタ電極14)の側に向くように、基板保持部材18cの先端のL字に折れ曲がった部分(以下、L字部という)18dに基板SBの導電性表面SBaが載置される。

なお、基板ホルダ18は、基板保持部材18cによって基板SBを保持するものに限定されず、基板取付台18bに設けられた静電チャック等によって基板SBを静電吸着するものであっても良い。

【0027】

なお、基板ホルダ18(の基板取付台18b)は、基板SBの成膜中に、基板SBを所定温度に、加熱しかつ維持するためのヒータ(図示せず)を備えている。

ここで、本発明のスパッタリング装置10においては、特に、絶縁膜を形成する場合には、基板SBが接地電位になっていない、したがって、基板ホルダ18に保持される基板SBが、接地電位になっていない構造であることが好ましい。すなわち、スパッタリング装置10では、基板SB、したがって、基板ホルダ18の電位がフローティング電位となる構造であるのが好ましい。したがって、基板ホルダ18の基部18aは、特に、絶縁膜を形成する場合には、絶縁性であるのが好ましい。また、基板ホルダ18の基板保持部材18cは、導電性であるのが好ましい。

なお、基板ホルダ18に装着される基板SBのサイズは、特に制限的ではなく、通常の6インチサイズの基板であっても、5インチや、8インチのサイズの基板であってもよいし、5cm角のサイズの基板であってもよい。

【0028】

等電位表面形成部材(以下、単に、等電位板ともいう)20は、本発明の最も特徴とする部分であって、基板ホルダ18の基板保持部材18cの先端のL字部18dの外側、すなわちターゲット材TG(スパッタ電極14)の側に取り付けられるドーナツ状の金属製の板状部材であって、基板保持部材18cの内側包絡線(包絡円)と一致する、もしくはその外側に位置する中心開口20bを持つ。また、等電位板20は、基板SBの外側に、かつスパッタ電極14の側に、配置または設置され、基板SBの導電性の表面SBaと等電位である等電位表面20aを有する。

なお、等電位板20は、基板ホルダ18の基板保持部材18cに取り付けられるものに限定されず、基板取付台18bに直接取り付けられ、基板保持部材18cの先端のL字部18dに接触されまたは接続され、もしくは、基板保持部材18cに保持された基板SBに直接接触され、または接続されるように構成されていても良い。

また、等電位板20と基板SBとを直接接触させる場合、または基板ホルダ18の基板保持部材18cを介して3者を接触させる場合には、接触圧を上げ、接触抵抗の影響を減らすようにするのが好ましい。

また、基板ホルダ18が、基板取付台18bに設けられた静電チャック等によって基板SBを静電吸着する場合には、等電位板20を、基板取付台18bに直接取り付け、静電吸着された基板SBに直接接触されまたは接続するように構成されていても良いし、静電吸着された基板SBに直接取り付けるものであっても良い。

【0029】

ここで、等電位表面形成部材20に形成される等電位表面20aの面積は、等電位である基板SBの導電性の表面SBaの面積の40%以上であるのが好ましく、より好ましくは70%以上であるのが良く、最も好ましくは150%以上であるのが良い。

その理由は、例えば、後述する実験1から明らかなように、面積割合が40%以上では、等電位表面20aがない場合に比べ、確実に、ペロブスカイト構造のチタン酸ジルコン酸鉛(PZT)のような圧電膜を成膜することができるからであり、また、後述する実験4および5の強誘電ヒステリシス測定から明らかなように、70%以上では、中央と端部での分極値の比の値が1.0と見積もられるからであり、中央と端部とで変化がないと考えられるからであり、また、150%以上では、後述する実験2〜5、特に、実験5から明らかなように、成膜回数を繰り返しても、分極値の比が大きくならず、1.0と見積もられるからである。

【0030】

本発明においては、基板SBの外側に、かつスパッタ電極14の側に、基板SBの導電性の表面SBaと等電位である等電位表面20aを形成することにより、基板SBの導電性の表面SBa上に、膜質のばらつきや組成ずれがなく、絶縁特性、電気的特性などの膜特性の均一性、特に面内均一性に優れた高品質な絶縁膜や導電体膜などの薄膜を成膜することができる。

この理由は、完全に解明されているわけではないが、本発明者らには、以下のように考えることができる。

ここで、図1に示すスパッタリング装置10において、基板SBを導電性基板とし、その導電性基板SBだけを設置してスパッタリングした場合、基板SBの周囲が基板SBと等電位でないために、例えば、放電を起こしているAr+のようなイオンの動きが、大きくことなることが考えられる。

【0031】

一方、特許文献4および5で問題にしているように、プラズマ電位と基板電位の差が大きい場合は、Ar+が成膜した膜にぶつかり、逆スパッタを起こす。そのため、逆スパッタが大きいところでは成膜レートが低く、逆スパッタが抑制されている部分では、成膜レートが高いと考えられる。そのため、基板面内で電位の差がある場合、膜厚むらができると考えられる。すなわち、特許文献4および5で解決しているのは、この膜厚むらの課題であると考えられる。

また、等電位面を設けた場合でも、その面積が小さい場合には、または十分に大きくない場合は、その効果があっても、小さく、やはり、Ar+のようなイオンの基板表面への動きが、中央付近と端部で違うためと考えられる。したがって、本発明においては、等電位表面形成部材20に形成される等電位表面20aの面積は、等電位である基板SBの導電性の表面SBaの面積の40%以上であるのが好ましく、より好ましくは70%以上であるのが良く、最も好ましくは150%以上であるのが良い。

【0032】

例えば、チタン酸ジルコン酸鉛(PZT)のような圧電膜を成膜する際に、上述のような膜厚むらができない程度の電位差においても、基板電位の差が基板面内で違った場合、鉛のようなスパッタ率の大きい元素から選択的にスパッタリングされるので、鉛の量が異なってくると考えられる。そのため、基板の周囲に等電位面を設置しない場合は、全体的に逆スパッタリングが大きくて、鉛の抜けが大きいので、ペロブスカイト構造を維持できず、パイロクロア構造になってしまうと考えられる。

一方、等電位面を設置した場合でも、その面積が小さい場合は、特に、成膜初期に、やはり、少なくても、鉛抜けが起こるために、膜全体の組成や結晶相は同じであるが、電気特性に差が生じると考えられる。したがって、上述のように、本発明においては、等電位表面形成部材20に形成される等電位表面20aの面積は、等電位である基板SBの導電性の表面SBaの面積の40%以上であるのが好ましく、より好ましくは70%以上であるのが良く、最も好ましくは150%以上であるのが良い。

【0033】

ところで、このような本発明の技術は、スパッタ膜のプラズマを均一化することで逆スパッタリングを制御し、均一化するというものであるから、どのような材料にも適用することができる。

しかし、等電位面との導通は、成膜する材料が金属や導電体の場合は、容易に取ることができ、成膜する物質が絶縁体の場合は、等電位面が接触を考慮しないと容易に導通が取れなくなることから、絶縁体(絶縁体・誘電体・強誘電体・圧電体・焦電体)などの材料に用いることがより好ましい。

【0034】

また、絶縁体でなくても、逆スパッタリングによって組成の変化が著しい材料などの場合には、面内分布が大きくなることから、スパッタ率が高い、鉛やビスマスや亜鉛などを含む物質の場合に有効である。例えば、チタン酸鉛もしくはジルコン酸鉛を含むチタン酸ジルコン酸鉛(PZT)や、その類似物質、PLZT、PTなどや、その元素置換体、BLSFと呼ばれるビスマス系誘電体、BiFeO3のようなマルチフェロイック材料、Bi系超伝導体、IGZOなどの、Zn含有の半導体などに、より好ましく応用することができる。

特に、鉛が抜けると、容易にパイロクロア相となり、強誘電性がなくなってしまうPZT系材料に好ましく用いることができる。

【0035】

また、本発明において用いられる成膜基板としては、少なくとも1面に導電性の表面を有しており、その1つの導電性の表面に、上述のような成膜材料を成膜することができればどのような基板でも良く、例えば、金属箔や金属基板、導電性セラミックス基板などの導電体や導電性基板や、シリコンやSiO2や、ガラス基板や、セラミックス基板などの絶縁性基板や半導性基板の上に片面(1面)または両面に導電性を付与した基板、例えば絶縁性基板や半導性基板の上に導電性の材料を、たとえば、電極として成膜した基板などを用いることができる。すなわち、本発明は、導電体や導電性基板そのものに成膜する場合も、絶縁性基板や半導性基板の上に導電性の材料を電極として成膜した基板を用いる場合にも適用できる。

【0036】

図示例の装置においては、等電位表面形成部材20の等電位表面20aは、等電位である基板SBの導電性の表面SBaより、スパッタ電極14の側に配置または設置されているのが好ましい。

その理由は、等電位表面形成部材20の等電位表面20aを真空チャンバ12の内壁面の側に形成した場合、Ar+のようなイオンの基板表面への動きが、中央付近と端部で違うためと考えられるからである。

なお、等電位表面形成部材20は、単一の部材であっても、複数の部材から形成されていても良く、また、等電位表面形成部材20の表面に形成される等電位表面20aは、1つの面を形成するものでも、段差のある複数の面で形成されるものであっても良い。

【0037】

ここで、等電位表面形成部材20の、スパッタ電極14の側に、等電位表面20aを形成する方法は、特に制限的ではなく、基板SBの導電性表面SBaと等電位となる面を形成できれば、どのようにしても良く、例えば、基板ホルダ18の基板保持部材18cの先端の少なくともL字部18dの一部、例えば、全部、先端のL字部18dもしくは先端のL字部18d一部を金属などの導電性部材で形成し、基板SBの導電性表面SBaと金属製の等電位板20とを基板保持部材18cの導電性の先端のL字部18dを介して導通させるように構成しても良いし、基板保持部材18cの先端のL字部18dが導電性でない場合には、等電位板20を基板ホルダ18の基板保持部材18cに取り付けるとともに、基板保持部材18cの内側において等電位板20を基板SBの導電性表面SBaとを接触させ、または電気的に接続して、導通させるようにしても良い。

なお、本発明において、等電位板20の当電位表面20aと基板SBの導電性表面SBaとが等電位とするために、両者を導通させるとは、両表面を接触させた時、両表面を導電性部材で接続した時、または、等電位板20と基板SBとを導電性部材で接続した時、両表面間の抵抗が、数Ω、すなわち、10Ω以下、好ましくは、5Ω以下、より好ましくは1Ω以下であることをいう。

【0038】

また、図示例のスパッタリング装置10では、等電位表面形成部材20の等電位表面20aに絶縁膜が付着していると、あるいは成膜を繰り返し続けると、真空チャンバ12内に設置されている等電位板20の等電位表面20aに絶縁膜が付着すると、等電位板20の等電位表面20aが等電位面としての機能が低下してしまい、絶縁膜の厚みが厚くなると、等電位面として機能しなくなってしまう。

したがって、本発明においては、等電位板20は、その等電位表面20aに付着している絶縁膜の厚みが10μm以下であるのが好ましく、より好ましくは、6μm以下であるのが良く、さらに好ましくは、4μm以下であるのが良く、最も好ましくは、等電位表面20aに絶縁膜が付着していない部材であるのが良い。

この理由は、後述する実験5から明らかなように、成膜回数を繰り返して、絶縁膜の厚みが10μmを超えると、等電位表面20aが等電位面として機能しなくなってしまうからである。

【0039】

ここで、本発明のスパッタリング方法およびスパッタリング装置においては、成膜回数を繰り返していると、真空チャンバ12内に設置されている等電位表面形成部材20の等電位表面20aに付着する絶縁膜の厚みが厚くなり、等電位板20の等電位表面20aが等電位面として機能しなくなってしまい、高品質の絶縁膜ができなくなり、歩留まりが悪くなってしまう。このため、真空チャンバ12内に設置されている等電位表面形成部材20の等電位表面20aに付着する絶縁膜の厚みが、0または10μm以下である間に、すなわち、10μmを超えない間に、成膜基板SBの導電性の表面SBa上に薄膜を作製するのが好ましい。なお、等電位表面20a上の絶縁膜の厚みが、6μm以下である間がより好ましく、4μm以下である間がさらに好ましく良く、0である間が最も好ましい。

【0040】

本発明のスパッタリング装置は、基本的に、以上のように構成されるものであり、以下に、その作用および本発明のスパッタリング方法について説明する。

図2は、本発明のスパッタリング方法の一例を示すフローチャートである。

まず、図2に示すように、ステップS10で、図1に示すスパッタリング装置10において、真空容器12内に設けられたスパッタ電極14にスパッタリング用のターゲット材TGを装着して保持させるとともに、真空容器内において、スパッタ電極14と対向する位置に離間して配置され、等電位表面形成部材20が取り付けられた基板ホルダ18に圧電膜などの薄膜を成膜する導電性表面SBaを持つ基板SBを装着して保持させる。

なお、このとき、ステップS12として、基板ホルダ18に装着された基板SBの導電性表面SBaと基板ホルダ18の基板保持部材18cの先端のL字部18dに取り付けられた等電位板20の当電位表面20aとがテスタ等で計測して導通していることを確認する。なお、このステップS10とS12とは、同時に行っても良いし、逆に、ステップS12を先に、ステップS10を後に行っても良い。

【0041】

この後、ステップS14において、真空容器12内が所定に真空度になるまでガス排出管12bから排気し、所定の真空度を維持するように排気し続けながら、ガス導入管12aからアルゴンガス(Ar)などのプラズマ用ガスを所定量づつ供給し続ける。これと同時に、ステップS16において、高周波電源16からスパッタ電極14に高周波(負の高周波電力)を印加して、スパッタ電極14を放電させて、真空容器12内に導入されたArなどのガスをプラズマ化し、Arイオン等のプラスイオンを生成させ、プラズマ空間Pが形成される。

次いで、ステップS18において、こうして形成されたプラズマ空間P内のプラスイオンは、スパッタ電極14に保持されたターゲット材TGをスパッタし、スパッタされたターゲット材TGの構成元素は、ターゲット材TGから放出され、中性あるいはイオン化された状態で、対向離間配置された基板ホルダ18に保持された基板SB上に蒸着され、成膜が開始される。

【0042】

成膜中のプラズマのエネルギを制御し、基板電位を所定のフローティング電位に保つことにより、逆スパッタの防止による膜の高品質化、組成ズレの制御、および成膜の再現性向上を図ることができ、一定の品質の良質な、すなわち膜質の変化のない高品質な圧電膜などの薄膜を成膜することができる(ステップS20)。

なお、本発明において、ステップS10〜ステップS20までの成膜を繰り返し行う場合には、1回の成膜において、基板SBの導電性表面SBaに形成される薄膜の厚みを考慮し、成膜中に等電位板20の当電位表面20aに形成された薄膜の厚みが10μmを超えないように繰り返す必要がある。この際、成膜中に等電位板20の当電位表面20aに形成された薄膜の厚みが10μmを超えていないことが確認できる場合には、ステップS12の基板SBの導電性表面SBaと等電位板20の当電位表面20aとの導通の確認は行わなくても良い。

【0043】

次に、本発明のスパッタリング方法による成膜方法において、好ましいその他の成膜条件に説明する。

本発明のスパッタリングによる成膜方法における成膜条件は、成膜温度Ts(℃)と、成膜時のプラズマ中のプラズマ電位Vs(V)と基板のフローティング電位Vf(V)との差であるVs−Vf(V)と、成膜される前記膜の特性との関係に基づいて決定されるのが好ましい。

ここで、前記関係が求められる前記膜の特性としては、膜の結晶構造および/または膜組成が挙げられる。

【0044】

図3は、図1に示すスパッタリング装置における成膜中の様子を模式的に示す説明図である。

図3に模式的に示すように、スパッタ電極14の放電により真空容器12内に導入されたガスがプラズマ化され、Arイオン等のプラスイオンIpが生成し、スパッタ電極14と基板ホルダ18との間、すなわち、スパッタ電極14に保持されたターゲット材TGと基板ホルダ18に保持された基板SBとの間にプラズマ空間Pが生成される。生成したプラスイオンIpはターゲット材TGをスパッタする。プラスイオンIpにスパッタされたターゲット材TGの構成元素Tpは、ターゲット材TGから放出され中性あるいはイオン化された状態で基板SBに蒸着される。

このとき、基板SBの外側、かつターゲット材TG側の導電性表面SBaには、等電位板20が基板SBと導通するように取り付けられているので、真空容器12内のプラスイオンIpの導電性表面SBaへの動きは、基板SBの導電性表面SBaの中央でも端部でも変わらないので、ターゲット材TGから放出され中性あるいはイオン化されたターゲット材TGの構成元素Tpは、導電性表面SBaに中央でも端部でも均等に蒸着される。このため、得られる蒸着薄膜は、膜質が均一な高品質の膜となると考えられる。

【0045】

プラズマ空間Pの電位は、プラズマ電位Vs(V)となる。本発明では、通常、基板SBは、絶縁体であり、かつ、電気的にアースから絶縁されている。したがって、基板SBはフローティング状態にあり、その電位はフローティング電位Vf(V)となる。ターゲット材TGと基板SBとの間にあるターゲット材TGの構成元素Tpは、プラズマ空間Pの電位と基板SBの電位との電位差Vs−Vfの加速電圧分の運動エネルギーを持って、成膜中の基板SBに衝突すると考えられる。

【0046】

プラズマ電位Vsおよびフローティング電位Vfは、ラングミュアプローブを用いて測定することができる。プラズマP中にラングミュアプローブの先端を挿入し、プローブに印加する電圧を変化させると、例えば、図4に示すような電流電圧特性が得られる(小沼光晴著、「プラズマと成膜の基礎」p.90、日刊工業新聞社発行)。この図4では、電流が0となるプローブ電位がフローティング電位Vfである。この状態は、プローブ表面へのイオン電流と電子電流の流入量が等しくなる点である。絶縁状態にある金属の表面や基板表面はこの電位になっている。プローブ電圧をフローティング電位Vfより高くしていくと、イオン電流は次第に減少し、プローブに到達するのは電子電流だけとなる。この境界の電圧がプラズマ電位Vsである。

プラズマ空間Pと基板SBとの電位差Vs−Vfは、基板SBとターゲット材TGとの間にアースを設置するなどして変えることもできるが、基板SBの基板電位であるフローティング電位Vfを調整することにより変えることもできる。

【0047】

プラズマを用いるスパッタリングにおいて、成膜される膜の特性を左右するファクタとしては、成膜温度、基板の種類、基板に先に成膜された膜があれば下地の組成、基板の表面エネルギー、成膜圧力、雰囲気ガス中の酸素量、投入電極、基板/ターゲット間距離、プラズマ中の電子温度および電子密度、プラズマ中の活性種密度および活性種の寿命等が考えられる。

本発明者らは、多々ある成膜ファクタの中で、成膜される膜の特性は、成膜温度Tsと電位差Vs−Vfとの2つのファクタに大きく依存することを見出し、これらファクタを好適化することにより、良質な膜を成膜できることを見出している。すなわち、成膜温度Tsを横軸にし、電位差Vs−Vfを縦軸にして、膜の特性をプロットすると、ある範囲内において良質な膜を成膜できることを見出している(図5参照)。

【0048】

電位差Vs−Vfが基板SBに衝突するターゲット材TGの構成元素Tpの運動エネルギーに相関することを述べた。下記式に示すように、一般に運動エネルギーEは温度Tの関数で表されるので、基板SBに対して、電位差Vs−Vfは温度と同様の効果を持つと考えられる。

E=1/2mv2=3/2kT

(式中、mは質量、vは速度、kは定数、Tは絶対温度である。)

電位差Vs−Vfは、温度と同様の効果以外にも、表面マイグレーションの促進効果、弱結合部分のエッチング効果などの効果を持つと考えられる。

【0049】

特開2004−119703号公報には、スパッタリング法により圧電膜を成膜する際に、圧電膜にかかる引張応力を緩和するために、基板にバイアスを印加することが提案されている。基板にバイアスを印加することは、基板に突入するターゲットの構成元素のエネルギ量を変えていることになる。しかしながら、特開2004−119703号公報には、プラズマ電位Vs、およびプラズマ電位Vsとフローティング電位Vfとの差である電位差Vs−Vfについて記載されていない。

【0050】

通常、従来のスパッタリング装置などの成膜装置では、プラズマ空間Pと基板SBとの電位差Vs−Vfは、装置の構造によって略決まり、大きく変えることができないので、従来は、電位差Vs−Vfを変えるという発想自体がほとんどなかった。スパッタリング方法ではないが、特開平10−60653号公報に、アモルファスシリコン膜等を高周波プラズマCVD法により成膜する成膜方法において、電位差Vs−Vfを特定の範囲内に制御する成膜方法が開示されている。この発明では、電位差Vs−Vfが基板面上で不均一になることを解消するために、電位差Vs−Vfを特定の範囲内に制御するようにしている。しかしながら、特開平10−60653号公報には、成膜温度TsとVs−Vfと成膜される膜の特性との関係に基づいて、成膜条件を決定することについては記載されていない。

【0051】

このような成膜方法は、本発明のスパッタリング方法を始めとして、プラズマを用いる気相成長法により成膜することが可能なものであれば、いかなる膜にも適用することができる。本発明のスパッタリング方法や、このような成膜方法を適用可能な膜としては、絶縁膜、誘電体膜、および圧電膜等が挙げられる。

このような成膜方法は、1種または複数種のペロブスカイト型酸化物からなる圧電膜(不可避不純物を含んでいてもよい。)の成膜に好ましく適用できる。ペロブスカイト型酸化物からなる圧電膜は、電圧無印加時において自発分極性を有する強誘電体膜である。

【0052】

本発明者らは、このような成膜方法を下記一般式(P)で表される1種または複数種のペロブスカイト型酸化物からなる圧電膜に適用する場合、下記式(1)および(2)を充足する範囲で成膜条件を決定することが好ましいことを見出している(図5参照)。

一般式AaBbO3・・・(P)

(式中、A:Aサイト元素であり、Pbを含む少なくとも1種の元素、B:Bサイトの元素であり、Ti,Zr,V,Nb,Ta,Cr,Mo,W,Mn,Sc,Co,Cu,In,Sn,Ga,Zn,Cd,Fe,Ni,およびランタニド元素からなる群より選ばれた少なくとも1種の元素、O:酸素原子。a=1.0かつb=1.0である場合が標準であるが、これらの数値はペロブスカイト構造を取り得る範囲内で1.0からずれてもよい。)、

Ts(℃)≧400・・・(1)、

−0.2Ts+100<Vs−Vf(V)<−0.2Ts+130・・・(2)

【0053】

上記一般式(P)で表されるペロブスカイト型酸化物としては、チタン酸鉛、チタン酸ジルコン酸鉛(PZT)、ジルコニウム酸鉛、チタン酸鉛ランタン、ジルコン酸チタン酸鉛ランタン、マグネシウムニオブ酸ジルコニウムチタン酸鉛、ニッケルニオブ酸ジルコニウムチタン酸鉛等の鉛含有化合物、および、チタン酸バリウム、チタン酸ビスマスナトリウム、チタン酸ビスマスカリウム、ニオブ酸ナトリウム、ニオブ酸カリウム、ニオブ酸リチウム等の非鉛含有化合物が挙げられる。圧電膜は、これら上記一般式(P)で表されるペロブスカイト型酸化物の混晶系であってもよい。

【0054】

本発明のスパッタリング方法は、下記一般式(P−1)で表されるPZTまたはそのBサイト置換系、およびこれらの混晶系に好ましく適用できる。

Pba(Zrb1Tib2Xb3)O3・・・(P−1)

(式(P−1)中、XはV族およびVI族の元素群より選ばれた少なくとも1種の金属元素である。a>0、b1>0、b2>0、b3≧0。a=1.0であり、かつb1+b2+b3=1.0である場合が標準であるが、これらの数値はペロブスカイト構造を取り得る範囲内で1.0からずれてもよい。)

上記一般式(P−1)で表されるペロブスカイト型酸化物は、d=0のときチタン酸ジルコン酸鉛(PZT)であり、d>0のとき、PZTのBサイトの一部をV族およびVI族の元素群より選ばれた少なくとも1種の金属元素であるXで置換した酸化物である。

Xは、VA族、VB族、VIA族、およびVIB族のいずれの金属元素でもよく、V,Nb,Ta,Cr,Mo,およびWからなる群より選ばれた少なくとも1種であることが好ましい。

【0055】

本発明者らは、上記一般式(P)で表されるペロブスカイト型酸化物からなる圧電膜を成膜する場合、上記式(1)を充足しないTs(℃)<400の成膜条件では、成膜温度が低すぎてペロブスカイト結晶が良好に成長せず、パイロクロア相がメインの膜が成膜されることを見出している(図5参照)。

本発明者らは、さらに、上記一般式(P)で表されるペロブスカイト型酸化物からなる圧電膜を成膜する場合、上記式(1)を充足するTs(℃)≧400の条件では、成膜温度Tsと電位差Vs−Vfが上記式(2)を充足する範囲で成膜条件を決定することで、パイロクロア相の少ないペロブスカイト結晶を安定的に成長させることができ、しかも、Pb抜けを安定的に抑制することができ、結晶構造および膜組成が良好な良質な圧電膜を安定的に成膜することができることを見出している(図5参照)。

【0056】

PZTのスパッタ成膜において、高温成膜するとPb抜けが起こりやすくなることが知られている(特開平6−49638号公報の図2等参照)。本発明者らは、Pb抜けが、成膜温度以外に電位差Vs−Vfにも依存することを見出している。PZTの構成元素であるPb,Zr,およびTiの中で、Pbが最もスパッタ率が大きく、スパッタされやすい。例えば、「真空ハンドブック」((株)アルバック編、オーム社発行)の表8.1.7には、Arイオン300evの条件におけるスパッタ率は、Pb=0.75、Zr=0.48,Ti=0.65であることが記載されている。スパッタされやすいということは、スパッタされた原子が基板面に付着した後に、再スパッタされやすいということである。プラズマ電位と基板の電位との差が大きい程、すなわち、Vs−Vfの差が大きい程、再スパッタの率が高くなり、Pb抜けが生じやすくなると考えられる。このことは、PZT以外のPb含有ペロブスカイト型酸化物でも、同様である。また、スパッタリング法以外のプラズマを用いる気相成長法でも同様である。

【0057】

成膜温度Tsと電位差Vs−Vfがいずれも過小の条件では、ペロブスカイト結晶を良好に成長させることができない傾向にある。また、成膜温度Tsと電位差Vs−Vfのうち少なくとも一方が過大の条件では、Pb抜けが生じやすくなる傾向にある。

すなわち、上記式(1)を充足するTs(℃)≧400の条件では、成膜温度Tsが相対的に低い条件のときには、ペロブスカイト結晶を良好に成長させるために電位差Vs−Vfを相対的に高くする必要があり、成膜温度Tsが相対的に高い条件のときには、Pb抜けを抑制するために、電位差Vs−Vfを相対的に低くする必要がある。これを表したのが、上記式(2)である。

【0058】

本発明者らは、上記一般式(P)で表されるペロブスカイト型酸化物からなる圧電膜を成膜する場合、下記式(1)〜(3)を充足する範囲で成膜条件を決定することで、圧電定数の高い圧電膜が得られることを見出している。

Ts(℃)≧400・・・(1)、

−0.2Ts+100<Vs−Vf(V)<−0.2Ts+130・・・(2)、

10≦Vs−Vf(V)≦35・・・(3)

【0059】

本発明者等は、上記一般式(P)で表されるペロブスカイト型酸化物からなる圧電膜を成膜する場合、成膜温度Ts(℃)=約420の条件では、電位差Vs−Vf(V)=約42Vとすることで、Pb抜けのないペロブスカイト結晶を成長させることができるが、得られる膜の圧電定数d31は、100pm/V程度と低いことを見出している。この条件では、電位差Vs−Vf、すなわち基板に衝突するターゲット材TGの構成元素Tpのエネルギが高すぎるために、膜に欠陥が生じやすく、圧電定数が低下すると考えられる。本発明者等は、上記式(1)〜(3)を充足する範囲で成膜条件を決定することで、圧電定数d31≧130pm/Vの圧電膜を成膜できることを見出している。

【0060】

本発明のスパッタリング方法等のプラズマを用いる気相成長法において、膜特性に対して影響を与えるファクタが、成膜温度Ts(℃)、および、成膜時のプラズマ中のプラズマ電位Vs(V)とフローティング電位Vf(V)との差である電位差Vs−Vf(V)であることを明らかにしたものである。

本発明のスパッタリング方法等の成膜方法によれば、膜特性に対して影響を与える上記2つのファクタと成膜される膜の特性との関係に基づいて、成膜条件を決定する構成としているので、スパッタリング方法等のプラズマを用いる気相成長法により良質な膜を安定的に成膜することができる。

本発明による成膜方法を採用することで、装置条件が変わっても良質な膜を成膜できる条件を容易に見出すことができ、良質な膜を安定的に成膜することができる。

【0061】

本発明のスパッタリング方法による成膜方法は、圧電膜の成膜等に好ましく適用することができる。本発明によれば、ペロブスカイト型酸化物からなる圧電膜の成膜において、パイロクロア相の少ないペロブスカイト結晶を安定的に成長させることが可能となる。本発明によれば、PZT等のPb含有ペロブスカイト型酸化物からなる圧電膜の成膜において、パイロクロア相の少ないペロブスカイト結晶を安定的に成長させることができ、しかもPb抜けを安定的に抑制することが可能となる。

【0062】

上記成膜方法を適用することで、以下の圧電膜を提供することができる。

すなわち、本圧電膜は、下記一般式(P)で表される1種または複数種のペロブスカイト型酸化物からなる圧電膜において、本発明のスパッタリング方法等のプラズマを用いる気相成長法により成膜されたものであり、下記式(1)および(2)を充足する成膜条件で成膜されたものである。

一般式AaBbO3・・・(P)

(式中、A:Aサイト元素であり、Pbを含む少なくとも1種の元素、B:Bサイトの元素であり、Ti,Zr,V,Nb,Ta,Cr,Mo,W,Mn,Sc,Co,Cu,In,Sn,Ga,Zn,Cd,Fe,Ni,およびランタニド元素からなる群より選ばれた少なくとも1種の元素、O:酸素原子。a=1.0かつb=1.0である場合が標準であるが、これらの数値はペロブスカイト構造を取り得る範囲内で1.0からずれてもよい。)、

Ts(℃)≧400・・・(1)、

−0.2Ts+100<Vs−Vf(V)<−0.2Ts+130・・・(2)

【0063】

本発明によれば、パイロクロア相の少ないペロブスカイト結晶構造を有し、しかも、Pb抜けが抑制され、結晶構造および膜組成が良好な良質な圧電膜を安定的に提供することができる。

また、本発明によれば、1.0≦aであるPb抜けのない組成の圧電膜を提供することができ、1.0<aであるPbリッチな組成の圧電膜を提供することもできる。aの上限は特に制限なく、本発明者等は、1.0≦a≦1.3であれば、圧電性能が良好な圧電膜が得られることを見出している。

【0064】

本発明による圧電膜は、下記式(1)〜(3)を充足する成膜条件で成膜されたものであることが好ましい。かかる構成とすることで、圧電定数の高い圧電膜を提供することができる。

Ts(℃)≧400・・・(1)、

−0.2Ts+100<Vs−Vf(V)<−0.2Ts+130・・・(2)、

10≦Vs−Vf(V)≦35・・・(3)

【0065】

こうして得られた本発明による圧電膜は、膜質のばらつきや組成ズレのない高品質な絶縁膜や誘電体膜、特に、PZT等のPb含有ペロブスカイト型酸化物からなり、パイロクロア相の少ないペロブスカイト結晶が安定的に成長し、しかもPb抜けが安定的に抑制された圧電膜であり、インクジェットヘッドなどに用いるのに適した圧電素子として利用することができる。

本発明によって得られる圧電膜、絶縁膜、誘電体膜などの薄膜は、基本的に以上のように構成される。

【0066】

次に、圧電素子およびこれを備えたインクジェットヘッドの構造について説明する。図6は、圧電素子の一実施形態を用いたインクジェットヘッドの一実施形態の要部断面図(圧電素子の厚み方向の断面図)である。視認しやすくするため、構成要素の縮尺は、実際のものとは適宜異ならせてある。

図6に示すように、インクジェットヘッド50は、圧電素子52と、インク貯留吐出部材54と、圧電素子52とインク貯留吐出部材54との間に設けられる振動板56を有する。

まず、圧電素子について説明する。同図に示すように、圧電素子52は、基板58と、基板58上に順次積層された下部電極60、圧電膜62および上部電極64とからなる素子であり、圧電膜62に対して、下部電極60と上部電極64とにより厚み方向に電界が印加されるようになっている。

【0067】

基板58としては、特に制限的ではなく、シリコン、ガラス、ステンレス(SUS)、イットリウム安定化ジルコニア(YSZ)、アルミナ、サファイヤ、シリコンカーバイド等の基板を挙げることができる。なお、基板58として、シリコン基板の表面にSiO2酸化膜が形成されたSOI基板等の積層基板を用いてもよい。

また、下部電極60は、基板58の略全面に形成されており、この上に図中手前側から奥側に延びるライン状の凸部62aがストライプ状に配列したパターンの圧電膜62が形成され、各凸部62aの上に上部電極64が形成されている。

圧電膜62のパターンは、図示するものに限定されず、適宜設計される。なお、圧電膜62は、連続膜でも構わないが、圧電膜62を、連続膜ではなく、互いに分離した複数の凸部62aからなるパターンで形成することで、個々の凸部62aの伸縮がスムーズに起こるので、より大きな変位量が得られ、好ましい。

【0068】

下部電極60の主成分としては、特に制限的ではなく、Au,Pt,Ir,IrO2,RuO2,LaNiO3,およびSrRuO3等の金属または金属酸化物、およびこれらの組合せが挙げられる。

上部電極64の主成分としては、特に制限的ではなく、下部電極60で例示した材料、Al,Ta,Cr,およびCu等の一般的に半導体プロセスで用いられている電極材料、およびこれらの組合せが挙げられる。

圧電膜62は、上述の本発明のスパッタリング方法を適用する成膜方法により成膜された膜である。圧電膜62は、好ましくは、上記一般式(P)で表されるペロブスカイト型酸化物からなる圧電膜である。

下部電極60と上部電極64の厚みは、例えば200nm程度である。圧電膜62の膜厚は特に制限なく、通常1μm以上であり、例えば1〜5μmである。

【0069】

図6に示すインクジェットヘッド50は、概略、上記構成の圧電素子52の基板58の下面に、振動板56を介して、インクが貯留されるインク室(インク貯留室)68およびインク室68から外部にインクが吐出されるインク吐出口(ノズル)70を有するインク貯留吐出部材54が取り付けられたものである。インク室68は、圧電膜62の凸部62aの数およびパターンに対応して、複数設けられている。すなわち、インクジェットヘッド50は、複数の吐出部72を有し、圧電膜62、上部電極64、インク室68およびインクノズル70は、各吐出部72毎に設けられている。一方、下部電極60、基板58および振動板56は、複数の吐出部に共通に設けられているが、これに制限されず、個々に、または幾かずつまとめて設けられていても良い。

インクジェットヘッド50では、後述する好ましい駆動方法により、または従来公知の駆動方法により、圧電素子52の凸部62aに印加する電界強度を凸部62a毎に増減させてこれを伸縮させ、これによってインク室68からのインクの吐出や吐出量の制御が行われる。

本実施形態の圧電素子およびこれを用いるインクジェットヘッドは、基本的に以上のように構成されている。

【0070】

次に、本発明によるインクジェットヘッドを備えるインクジェット式記録装置の構造について説明する。図7は、本発明によるインクジェットヘッドを備えるインクジェット式記録装置の一実施形態の全体構成を示す装置全体図であり、図8は、その部分上面図である。

図示例のインクジェット式記録装置100は、インクの色ごとに設けられた複数のインクジェットヘッド(以下、単に「ヘッド」という)50K,50C,50M,50Yを有する印字部102と、各ヘッド50K,50C,50M,50Yに供給するインクを貯蔵しておくインク貯蔵/装填部114と、記録紙116を供給する給紙部118と、記録紙116のカールを除去するデカール処理部120と、印字部102のノズル面(インク吐出面)に対向して配置され、記録紙116の平面性を保持しながら記録紙116を搬送する吸着ベルト搬送部122と、印字部102による印字結果を読み取る印字検出部124と、印画済みの記録紙(プリント物)を外部に排紙する排紙部126とから概略構成されている。

【0071】

印字部102をなすヘッド50K,50C,50M,50Yが、各々上記実施形態のインクジェットヘッド50(図6参照)である。

デカール処理部120では、巻き癖方向と逆方向に加熱ドラム130により記録紙116に熱が与えられて、デカール処理が実施される。

ロール紙を使用する装置では、図7に示すように、デカール処理部120の後段に裁断用のカッター128が設けられ、このカッターによってロール紙は所望のサイズにカットされる。カッター128は、記録紙116の搬送路幅以上の長さを有する固定刃128Aと、この固定刃128Aに沿って移動する丸刃128Bとから構成されており、印字裏面側に固定刃128Aが設けられ、搬送路を挟んで印字面側に丸刃128Bが配置される。カット紙を使用する装置では、カッター128は不要である。

【0072】

デカール処理され、カットされた記録紙116は、吸着ベルト搬送部122へと送られる。吸着ベルト搬送部122は、ローラ131、132間に無端状のベルト133が巻き掛けられた構造を有し、少なくとも印字部102のノズル面および印字検出部124のセンサ面に対向する部分が水平面(フラット面)となるよう構成されている。

ベルト133は、記録紙116の幅よりも広い幅寸法を有しており、ベルト面には多数の吸引孔(図示略)が形成されている。ローラ131、132間に掛け渡されたベルト133の内側において印字部102のノズル面および印字検出部124のセンサ面に対向する位置には吸着チャンバ134が設けられており、この吸着チャンバ134をファン135で吸引して負圧にすることによってベルト133上の記録紙116が吸着保持される。

【0073】

ベルト133が巻かれているローラ131、132の少なくとも一方にモータ(図示せず)の動力が伝達されることにより、ベルト133は、図7において時計回り方向に駆動され、ベルト133上に保持された記録紙116は、図7において左から右へと搬送される。

なお、縁無しプリント等を印字すると、ベルト133上にもインクが付着するので、ベルト133の外側の所定位置(印字領域以外の適当な位置)にベルト清掃部136が設けられている。

また、吸着ベルト搬送部122により形成される用紙搬送路上において印字部102の上流側に、加熱ファン140が設けられている。加熱ファン140は、印字前の記録紙116に加熱空気を吹き付け、記録紙116を加熱する。印字直前に記録紙116を加熱しておくことにより、インクが着弾後に乾きやすくなる。

【0074】

印字部102は、最大紙幅に対応する長さを有するライン型ヘッドを、紙送り方向と直交方向(主走査方向)に配置した、いわゆるフルライン型のヘッドとなっている(図8参照)。各印字ヘッド50K,50C,50M,50Yは、インクジェット式記録装置100が対象とする最大サイズの記録紙116の少なくとも一辺を超える長さにわたってインク吐出口(ノズル)が複数配列されたライン型ヘッドで構成されている。

記録紙116の送り方向に沿って上流側から、黒(K)、シアン(C)、マゼンタ(M)、イエロー(Y)の順に各色インクに対応したヘッド50K,50C,50M,50Yが配置されている。記録紙116を搬送しつつ、各ヘッド50K,50C,50M,50Yから、それぞれ色インクを吐出することにより、記録紙116上にカラー画像が記録される。

【0075】

印字検出部124は、印字部102の打滴結果を撮像するラインセンサ等からなり、ラインセンサによって読み取った打滴画像からノズルの目詰まり等の吐出不良を検出する。

印字検出部124の後段には、印字された画像面を乾燥させる加熱ファン等からなる後乾燥部142が設けられている。印字後のインクが乾燥するまでは印字面と接触することは避けた方が好ましいので、熱風を吹き付ける方式が好ましい。

後乾燥部142の後段には、画像表面の光沢度を制御するために、加熱・加圧部144が設けられている。加熱・加圧部144では、画像面を加熱しながら、所定の表面凹凸形状を有する加圧ローラ145で画像面を加圧し、画像面に凹凸形状を転写する。

【0076】

こうして得られたプリント物は、排紙部126から排出される。本来プリントすべき本画像(目的の画像を印刷したもの)とテスト印字とは分けて排出することが好ましい。このインクジェット式記録装置100では、本画像のプリント物と、テスト印字のプリント物とを選別してそれぞれの排出部126A、126Bへと送るために排紙経路を切り替える選別手段(図示略)が設けられている。

大きめの用紙に本画像とテスト印字とを同時に並列にプリントする場合には、カッター148を設けて、テスト印字の部分を切り離す構成とすればよい。

本実施形態のインクジェット記記録装置は、基本的に以上のように構成されている。

【0077】

以上、本発明に係るスパッタリング方法および装置について種々の実施形態および実施例を挙げて詳細に説明したが、本発明は、上記実施形態および実施例には限定されず、本発明の要旨を逸脱しない範囲において、各種の改良や設計の変更を行ってもよいのは、もちろんである。

【実施例】

【0078】

以下に、本発明を実施例に基づいて具体的に説明する。

(実験1)

図1に示すスパッタリング装置10として、アルバック社製スパッタ装置を用い、ターゲット材TGとして、Pb1.3Zr0.52Ti0.48Oxの組成の焼結体ターゲットを用い、成膜温度を450℃としてPZT膜を成膜した。成膜基板SBとしては、図9に示すように、電極32として、Ti(Ti層34)を20nm、Ir(Ir層36)を150nm積層した3インチ、厚み625μmのシリコン基板38を用いた。なお、シリコン基板38の表面には、SiO2層4が形成されていた。また、図9に示すように、成膜基板SBの電極32のIr層(電極)36の表面(SBa)上に形成されるPZT膜42の成膜膜厚は、4μmとした。

【0079】

(実施例1)

図10(a)に模式的に示すように、3インチ(76.2mm)の電極32付シリコン基板38(成膜基板SB)を、等電位表面形成部材20となる外径90mmのインコネル板22(成膜冶具)にて支えた。テスタにて、基板SBのIr電極36の表面(導電性表面SBa)とインコネル板22の表面(等電位板20の等電位表面20a)の間の抵抗を計測し、計測された抵抗は、1Ω以下を示し、基板SBのIr電極表面SBaとインコネル板22(等電位板20)の表面22a(等電位表面20a)とは、導通していることを確認した。この状態で成膜を行った。

【0080】

(比較例1)

図10(b)に模式的に示すように、実施例1において、等電位板20として用いた外径90mmのインコネル板22の裏面(基板SB側)にアルミナをコートして、絶縁層24を形成し、絶縁層24上に実施例1で用いた基板SBをセットした。テスタにて、基板SBのIr電極表面SBaとインコネル板22の表面22aとの間の抵抗を計測したところ、その抵抗は、1GΩ以上あり、テスタでは導通が確認できなかった。すなわち、インコネル板22は、等電位板20として機能していないことを確認した。この状態で同様に成膜を行った。

【0081】

(実験1の結果)

実施例1では、ペロブスカイト相のチタン酸ジルコン酸鉛(PZT)の膜(PZT膜42)ができていることを、XRD(X線回折装置)にて確認した。

比較例1では、成膜された膜が、パイロクロア相となり、目的とするチタン酸ジルコン酸鉛の膜が得られなかった。XRF(蛍光X線分析装置)にて膜の組成を計測した結果、鉛量(Pb/(Zr+Ti))は、実施例1では1.05であったが、比較例では0.8であり、本発明を用いないと、成膜中のプラズマが基板SBに集中してしまうため、Pbの抜けが生じて、Pbが不足し、所望の膜ができないことが分かった。なお、XRF測定では、下部電極32のIr層36のイリジウム(Ir)の影響を除くため、ファンダメンタルパラメータ(FP)法を用いた。

これらの結果を表1に示す。

なお、表における導通面積の割合は、等電位板20の等電位表面20aのみの面積を成膜基板SBの導電性表面SBaで除算して求めた。すなわち、導通面積の割合は、90mmのインコネル板22が等電位板20の場合には、(902−76.22)/76.22(=40%)として求め、90mmのインコネル板22と120mmのインコネル板26とが等電位板20の場合には、(1202−76.22)/76.22(=150%)として求めた。

【0082】

(実験2)

実験1で、さらに、均一性を向上させることを狙い、等電位板20として用いた外径90mmのインコネル板22の外側に、外径120mmのインコネル板26を設置した。

(実施例2)

図11に模式的に示すように、インコネル板22(等電位板20)とインコネル板26との間に絶縁性のワッシャ28を挟み、インコネル板26を設置したが、基板SBの電極(導電性表面SBa)とは、電気的に浮かせた状態で成膜した。

実験1と同様に、テスタで導通を確認し、基板SBの電極(導電性表面SBa)は、インコネル板22(等電位板20)の表面22a(等電位表面20a)までは導通しているが、インコネル板26には導通していないことを確認した。すなわち、インコネル板26は、等電位板20として機能していないことを確認した。

【0083】

(実施例3)

図12に模式的に示すように、90mmのインコネル板22と120mmのインコネル板26との間に、導電性のワッシャ30を挟み、基板SBの電極(導電性表面SBa)とインコネル板26との間を導通させ、等電位となるようにした。実験1と同様に、テスタで確認し、基板SBの電極(導電性表面SBa)からインコネル板26の表面26aまで導通していることを確認した。すなわち、インコネル板22およびインコネル板26は、等電位板20を構成し、インコネル板22の表面22aとインコネル板26の表面26aとは、等電位表面20aを構成していた。

実施例1〜3のいずれにおいても、XRDで、単相のペロブスカイト膜(PZT膜42)が全面についている事を確認し、XRFでの組成分析で、いずれも、1.05であることを確認した。

その結果を表1に示す。

【0084】

【表1】

【0085】

表1の結果から明らかなように、実施例1〜3のいずれにおいても、成膜基板SBの外側に等電位面20aを設置したので、ペロブスカイト単相膜を得たことが分かる。実施例1〜3のいずれの方法においても、本発明が良質なチタン酸ジルコン酸鉛の膜(PZT膜42)を作製するのに有効であることが分かった。

【0086】

次に、実施例1〜3で得られた基板SBのPZT膜42に上部電極を成膜し、下部電極と上部電極との間に電圧を印加して、強誘電ヒステリシス測定を計測した。

強誘電ヒステリシス測定の測定位置は、図13に示すように、3インチ(76.2mm)基板SB(PZT膜42)の中央の位置、中央から20mmの位置および中央から35mmの位置の3点とした。

実施例1および3で得られたPZT膜42の強誘電ヒステリシスの測定結果をそれぞれ図14および図15に示す。

図14および図15に示すように、実施例1および実施例3における強誘電ヒステリシス測定に差異があることが分かった。図15に示す実施例3では、面内で同じヒステリシスが得られたが、図14に示す実施例1では、3インチ基板SBの端で、ヒステリシス測定の抗電界に変化が得られた。

【0087】

そこで、PZT膜42の面方向の中央の位置と端部の位置(中央から35mmの位置;図13参照)のそれぞれのヒステリシスの測定点においてPZT膜42を切断し、TEM−EDX(電界放射型透過電子顕微鏡・エネルギ分散型X線分析装置)にて、測定径を50nm程度のスポット径として、図9に示すように、PZT膜42の下部電極32の界面付近の測定位置43a、PZT膜42の深さ方向の中央付近の測定位置43bおよびPZT膜42の上部電極44の界面付近の測定位置43cで、Pb量(=Pb/(Zr+Ti))をいずれの測定位置でも複数点(サンプル)測定した。なお、下部電極32の界面付近の測定位置43aでは、Irにかからない位置で測定した。

【0088】

いずれの測定位置のサンプル(測定点)でも、PZT膜42の中央付近の測定位置43bおよびPZT膜42の上部電極44の界面付近の測定位置43cでは、1程度の鉛量であった。(なお、TEM−EDXの場合は、XRFと比較して測定再現性が悪く、0.95〜1.05の間の鉛量の場合を、1程度とした。)

また、実施例3においては、PZT42膜の下部電極付近の測定位置43aでも、1程度の鉛量であったが、実施例1および2においては、EDXの測定場所(測定位置や測定点)によっては、1程度の鉛量の測定場所と、鉛量が0.8以下の鉛量の測定場所が見られた。

ここで、PZT膜42の面方向の中央の位置と端部の位置(中央から35mmの位置;図13参照)において、0.8以下の鉛量の測定点数を表2に示す。

また、実施例1において、各測定位置43a、43bおよび43cごとにそれぞれ4点ずつ(サンプル数n=4)測定した測定結果を図16に示す。

【0089】

図16から明らかなように、実施例1において、PZT膜42の中央の位置(図13参照)では、いずれの測定位置43a、43bおよび43cでも、4点(サンプル)とも1程度の鉛量であり、鉛(Pb)不足はなかったことが分かった。

一方、PZT膜42の端部の位置(中央から35mmの位置;図13参照)では、測定位置43bおよび43cでは、4点(サンプル)とも1程度の鉛量であり、鉛(Pb)不足はなかったが、PZT膜42の下部電極32の界面付近の測定位置43aでは、4点(サンプル)中3点で、鉛(Pb)不足が生じていたことが分かる。

【0090】

また、図14および図15に示すように、実施例1および実施例3における強誘電ヒステリシス測定に差異があることが分かるので、両者を簡便に比較するため、中央の位置と端部の位置(中央から35mmの位置)の、変化が大きい電界50kV/cmでの分極値の大きさを比較した。その結果、実施例1の分極値が3.2、実施例3の分極値が1.0と見積もられた。また、実施例2の分極値は、2.9と見積もられた。

その結果を表2に示す。

【0091】

【表2】

【0092】

表2から明らかなように、実施例1〜3では、ペロブスカイト単相膜が得られたが、導通面積の割合を増やした方が、下部電極界面付近の均一性も確保できることが分かる。すなわち、同じペロブスカイト膜でも、電気特性が異なり、これは、界面付近の鉛量が違うことによる影響と考えられる。導通面積の割合をより広げた方が、比較例で見られた鉛抜けが、基板の端の方において成膜初期でも抑制できることが分かった。

また、実施例1および2と3との比較からわかるように、成膜基板の外側に設置したインコネル板は、ただ、単にフローティングにして置くだけでは全く効果がなく、置かない場合とほとんど変化がなく、成膜基板と導通して、成膜基板と等電位となっていることが重要であると分かった。

【0093】

(実験3)

(実施例4)

実施例3の120mmのインコネル板26の代わりに、100mm(導通割合170%)のインコネル板を用いて、実験2と同様の実験を行い、ヒステリシスを測定した。

その結果を表3に示す。

表3から明らかなように、実施例4の場合も、実施例3と同様、導通割合170%程度で均一な膜が得られることが確認できた。

以上の各実験から、成膜においては、成膜基板の外側に導通部分を設けることが必須であり、その面積割合は、170%以上あることがより好ましいことが分かった。

【0094】

【表3】

【0095】

(実験4)

実施例3および4において、成膜回数を繰り返すことによる変化を調べた。

その結果を表4に示す。

表4から明らかなように、成膜回数を繰り返すと、等電位面に絶縁膜が付着し、せっかく設置した等電位面が等電位面として機能しなくなると考えられる。

実施例3においては、成膜3回目で、外側の電気特性に変化がみられたが、実施例4においては、成膜を5回繰り返しても、膜全体に変化は見られなかった。そのため、面積割合250%の方が、面積割合170%の場合より好ましいことが分かった。

成膜を4回繰り返した板においては、1回の成膜膜厚である4μmの4倍の16μmの絶縁膜が付着し、5回目の成膜が開始される。そのため、導通面積の割合が170%の場合の絶縁膜厚は、10μm以下が好ましいことが分かった。

【0096】

【表4】

【0097】

(実験5)

スパッタ装置を変え、神港精機製スパッタ装置を用いて、同様の実験を行った。成膜ターゲット材TGの組成は、同一とし、成膜基板SBとしては、IrおよびTiを成膜した実験1〜4で用いたのと同じシリコン基板を、25mm角に切断し、30mmφのインコネル成膜冶具を用いて成膜した。このインコネル成膜冶具の導通面積割合は、13%となった。

(実施例5)

上記条件で成膜し、得られたPZT膜をXRDで測定した結果、ペロブスカイト単相膜であった。

(比較例2)

一方、実施例5で用いたインコネル冶具の裏面に絶縁膜を付け、成膜基板と絶縁した状態で成膜した結果、膜は、パイロクロアとなった。

この実験5の実施例5および比較例2の結果から、成膜冶具の等電位表面の導通面積割合が、13%であっても、本発明の効果が得られることが分かった。もちろん、スパッタ装置の種類によらず、本発明の効果が得られることも分かった。

【産業上の利用可能性】

【0098】

本発明のスパッタリング方法および装置は、スパッタリングなどのプラズマを用いる気相成長法により、圧電膜、絶縁膜、誘電体膜などの薄膜を成膜する場合に適用することができ、インクジェット式記録ヘッド、強誘電体メモリ(FRAM)、および圧力センサ等に用いられる圧電膜等の成膜に適用することができる。

【図面の簡単な説明】

【0099】

【図1】本発明のスパッタリング方法を実施するスパッタリング装置の一実施形態の装置構成を示す概略断面図である。

【図2】本発明のスパッタリング方法の一例を示すフローチャートである。

【図3】図1に示すスパッタリング装置における成膜中の様子を模式的に示す模式図である。

【図4】スパッタリング装置におけるプラズマ電位Vsおよびフローティング電位Vfの測定方法を示す説明図である。

【図5】本発明法で成膜される種々の圧電膜について、成膜温度Tsを横軸にし、電位差Vs−Vfを縦軸にして、XRD測定結果を示すグラフである。

【図6】本発明の圧電素子およびこれを用いるインクジェットヘッドの一実施形態の構造を示す断面図である。

【図7】図6に示すインクジェットヘッドを備えるインクジェット式記録装置の一実施形態の構成を示す構成図である。

【図8】図7に示すインクジェット式記録装置の部分上面図である。

【図9】本発明の実施例で用いられた成膜基板および成膜基板上に成膜された薄膜の構成および測定位置を示す模式的断面図である。

【図10】(a)および(b)は、それぞれ本発明の実施例1および比較例1における成膜基板の周辺構造およびターゲット材を模式的に示す模式的断面図である。

【図11】本発明の実施例2における成膜基板の周辺構造およびターゲット材を模式的に示す模式的断面図である。

【図12】本発明の実施例3における成膜基板の周辺構造およびターゲット材を模式的に示す模式的断面図である。

【図13】本発明の各実施例における強誘電ヒステリシス測定の測定位置を示す概念図である。

【図14】本発明の実施例1における誘電ヒステリシス測定の結果を示すグラフである。

【図15】本発明の実施例3における誘電ヒステリシス測定の結果を示すグラフである。

【図16】本発明の実施例1における鉛量の測定結果を示すグラフである。

【符号の説明】

【0100】

10 スパッタリング装置

12 真空容器

12a ガス導入管

12b ガス排出管

14 スパッタ電極(カソード電極)

16 高周波電源

18 基板ホルダ

18a 基部

18b 基板取付台

18c 基板保持部材

18d L字部18d

20 等電位表面形成部材(等電位板)

20a 等電位表面

20b 中心開口

50、50K,50C,50M,50Y インクジェットヘッド

52 圧電素子

54 インク貯留吐出部材

56 振動板

58 基板(支持基板)

60、64 電極

62 圧電膜

68 インク室

70 インク吐出口

100 インクジェット式記録装置

IP プラスイオン

P プラズマ空間

SB 基板(成膜基板)

SBa 導電性表面

TG ターゲット材

Tp ターゲット材の構成元素

【技術分野】

【0001】

本発明は、スパッタリング方法および装置に関し、詳しくは、プラズマを用いた気相成長法により絶縁膜(絶縁体)や誘電膜(誘電体)や、強誘電体(圧電体)組成物などの薄膜の成膜を行うスパッタリング方法、およびこれを実施するために用いられるスパッタリング装置に関するものである。

【背景技術】

【0002】

従来より、圧電膜、絶縁膜、誘電体膜等の薄膜を成膜するために、プラズマを用いた気相成長法により成膜するスパッタリング方法やこれを実施するスパッタリング装置が用いられている。このようなスパッタリング方法および装置では、高真空中でプラズマ放電により生成される高エネルギのArイオン等のプラズマイオンをターゲットに衝突させて、ターゲットの構成元素を放出させ、放出されたターゲットの構成元素を基板の表面に蒸着させることにより、基板上に薄膜を形成している。

【0003】

スパッタリング方法および装置においては、良質な薄膜を形成するために、真空容器内に設けられたスパッタ電極と対向する位置に配置された基板電極に保持された基板の表面に所定の電位を与えてスパッタリングを行っている。

このようなスパッタリング方法および装置で作製される薄膜デバイスにおいては、薄膜内の膜厚、組成および結晶相などを制御し、面内特性のばらつきを押さえることが求められる。

【0004】

このため、スパッタリング装置で薄膜を成膜する場合には、プラズマの状態を均一化させることで、面内を均一にすることが求められる(例えば、特許文献1、2、3、4および5参照)。

特許文献1では、膜厚分布や薄膜の膜組成を均一にするために、ターゲット近傍に磁場を形成するためのマグネットとして、極性や強さを制御できる電磁石を用いて、形成される磁場を制御することにより、異常放電がない均一なプラズマを生成し、ターゲット面内での全面均一エロージョンを実現する技術が開示されている。このように、均一なプラズマを生成するために、ターゲット(カソード)側に工夫することは、良く知られている。

【0005】

ところで、金属ではなく、絶縁物(絶縁体・誘電体・焦電体・圧電体)を成膜する場合は、金属の場合よりさらに、プラズマの均一性が要求されることが知られている。

このため、例えば、特許文献2では、スパッタリング装置の装置側壁の電位に工夫を加えている。特許文献2には、スパッタリング装置で絶縁膜を成膜する場合、側壁を絶縁膜付着とともに電位を制御することで、プラズマを制御し、均一な組成を有する絶縁膜を生成する方法が記載されている。

【0006】

また、上記ターゲット側の工夫や装置側壁の電位の工夫に対し、成膜基板付近のプラズマ状態を制御することで、絶縁膜の成膜を均一化することも試みられている。

特許文献3では、成膜基板とスパッタリング装置とを絶縁することで、均一のプラズマにし、膜中の組成分布が均一な絶縁膜を作製する技術が公開されている。

しかしながら、特許文献1、2および3に開示された技術は、それぞれの点から膜質の改善を図っているが、これだけでは膜質をより均一化するのは不十分であり、そのため、成膜基板付近のマスク・冶具などを工夫することがなされている。

【0007】

特許文献4では、成膜基板付近に設置したマスクを、フローティング電位にしたり、アースに落したり、両者を組合せることで、適切な成膜条件を選択する技術が開示されている。具体的には、成膜マスク(成膜冶具)として、アース電位に接続されたアースマスクと、アース電位から絶縁されたフローティングマスクと、アース電位に接続された部分とアース電位から絶縁された部分とを備えるプラズマ制御マスクとで構成し、プラズマ制御マスクのアース電位に接続された部分とアース電位から絶縁されたフローティング部分との量を調節して、最適な成膜条件としている。

【0008】

また、特許文献5では、被処理基板を保持する基板保持部材と、これに併設され、かつ装置本体との間に絶縁性部材を介して配置された防着部材とを等電位にし、かつフローティングすることにより、異常放電を抑制し、成膜レートを向上させるとともに、膜厚均一性が向上できる技術が開示されている。また、特許文献5では、上述した基板保持部材と防着部材とを等電位にするに加え、防着部材の電位を接地あるいはフローティングに切り替えることにより、絶縁膜と導電膜との膜の種類に応じて電位状態を変えることができるので、上記効果を膜の種類に応じて達成することができる技術を開示している。

【0009】

【特許文献1】特開平6−41740号公報

【特許文献2】特開2007−42919号公報

【特許文献3】特開平7−231045号公報

【特許文献4】特開2001−335930号公報

【特許文献5】特開2006−83459号公報

【発明の開示】

【発明が解決しようとする課題】

【0010】

しかしながら、特許文献4においては、アース部分とフローティング部分を適度な割合にする旨の記載があるが、特に理屈がなく試行錯誤により、最適条件を定めている。そのため、側壁に絶縁物がついたり、ターゲット材料が変化したりといったプラズマ状態の変化に応じて、その度に、試行錯誤を繰り返す必要があるという問題がある。また、特許文献4に開示の技術は、均一な膜厚の薄膜を形成するものであるが、薄膜の電気的特性などの膜質の均一性、例えば、絶縁膜などの絶縁特性の均一性、特に、面内均一性などについては、全く考慮されていないという問題がある。

【0011】

また、特許文献5に関しては、膜厚が均一になることは記載されているが、特許文献4と同様に、薄膜の電気的特性などの膜質、例えば、絶縁膜などの絶縁特性など、絶縁膜の端部の電気特性がどのようになるかといったより細かいところまでは検討されておらず、不十分であるという問題がある。すなわち、特許文献5に開示の技術は、基板保持部材と防着部材とを等電位にすることにより、両者の間の異常放電の発生を防止して、成膜速度を低下させず、膜厚分布を均一にする技術に過ぎず、薄膜の電気的特性などの膜質の均一性、例えば、絶縁膜などの絶縁特性の均一性、特に、面内均一性などについては、全く考慮されていないという問題がある。

【0012】

本発明の目的は、上記従来技術の問題点を解消し、膜質のばらつきや組成ずれがなく、電気的特性などの膜特性の均一性、特に面内均一性に優れた高品質な絶縁膜や導電体膜などの薄膜、例えば絶縁特性の均一性、特に面内均一性に優れた絶縁膜などの薄膜を成膜することができるスパッタリング方法および装置を提供することにある。

【課題を解決するための手段】

【0013】

上記課題を解決するために、本発明者らは、上記目的を達成するために、上記特許文献1〜5を始めとして多くの従来技術を検討し、このような膜特性に優れた高品質な薄膜を成膜することができるスパッタリング方法およびスパッタリング装置について、鋭意研究を重ねた結果、上記特許文献4および5の技術のみでは、絶縁特性や電気的特性などの膜特性が均一にならないということを見出した。すなわち、本発明者等は、特許文献4および5では共に、基板周辺部の電位については考慮されているものの、成膜基板と周辺部との電位の関係について考えられていないことが、絶縁特性や電気的特性などの膜特性が均一にならない原因であり、特に、特許文献5のように、被処理基板としてシリコン基板のような半導体基板に薄膜を成膜する場合に、膜厚を均一化や成膜速度の向上には、基板保持部材と防着部材とを等電位にして、両者の間の異常放電の発生を防止するだけで十分であるが、表面に導電性を有する成膜基板の導電性の表面に圧電幕等の絶縁膜を形成する場合には、これだけでは不十分であり、膜特性を均一にできないことを知見するとともに、膜特性を均一にするには、導電性の表面を有する成膜基板の外側に、導電性の表面と等電位である等電位表面を持つ等電位表面形成部材を設置する必要があることを知見し、本発明に至ったものである。

【0014】

すなわち、本発明の第1の態様は、少なくとも1面に導電性の表面を有する成膜基板に薄膜を成膜するスパッタリング方法であって、前記成膜基板の外側に、この成膜基板の前記導電性の表面と等電位である等電位表面を持つ等電位表面形成部材を設置して、前記成膜基板の前記導電性の表面上に前記薄膜を作製することを特徴とするスパッタリング方法を提供するものである。

【0015】

ここで、前記成膜基板の外側において、前記等電位表面形成部材の前記等電位表面の面積が、前記成膜基板の前記導電性の表面の面積の40%以上であるのが好ましく、また、より好ましくは、70%以上であるのが良く、また、最も好ましくは、150%以上であるのが良い。

また、前記等電位表面形成部材が、前記等電位表面に付着している絶縁膜の厚みが10μm以下の部材であるのが好ましく、また、最も好ましくは、前記等電位表面に絶縁膜が付着していない部材であるのが良い。

また、前記等電位表面形成部材の前記等電位表面に付着する絶縁膜の厚みが、0または10μm以下である間に、前記成膜基板の前記導電性の表面上に前記膜を作製するのが好ましい。

【0016】

また、前記膜を作製する成膜材料が、絶縁体であるのが好ましく、また、より好ましくは、チタン酸鉛もしくはジルコン酸鉛を含むのが良い。

また、前記成膜基板が、導電性基板であるのが好ましい。

また、前記成膜基板の前記導電性の表面と、前記等電位表面形成部材の前記等電位表面とが、導通しているのが好ましい。

また、前記等電位表面形成部材は、前記等電位表面が前記成膜基板の前記導電性の表面より、前記膜を作製する成膜材料に近い側に在るまたは来るように、設置されるのが好ましい。

【0017】

また、上記目的を達成するために、本発明の第2の態様は、真空容器と、この真空容器内に設けられ、スパッタリング用のターゲット材を保持するスパッタ電極と、このスパッタ電極に接続され、前記スパッタ電極に高周波を印加する高周波電源と、前記真空容器内の、前記スパッタ電極と対向する位置に離間して配置され、前記ターゲット材の成分による薄膜が成膜され、少なくとも1面に導電性の表面を有する成膜基板を保持する基板ホルダと、前記基板ホルダに保持される前記成膜基板の外側に設置される前記等電位表面形成部材とを有し、前記等電位表面形成部材は、前記成膜基板の前記導電性の表面と等電位である等電位表面を持ち、前記薄膜は、前記成膜基板の前記導電性の表面上に作製されることを特徴とするスパッタリング装置を提供するものである。

【0018】

ここで、前記等電位表面形成部材は、前記成膜基板の外側における前記等電位表面の面積が、前記成膜基板の前記導電性の表面の面積の40%以上であるのが好ましく、また、より好ましくは、70%以上であるのが良く、また、最も好ましくは、150%以上であるのが良い。

また、前記成膜基板は、導電性基板であるのが好ましい。

また、前記成膜基板の前記導電性の表面と、前記等電位表面形成部材の前記等電位表面とは、導通しているであるのが好ましい。

【0019】

また、前記等電位表面形成部材は、前記等電位表面に付着している絶縁膜の厚みが10μm以下の部材であるのが好ましく、また、最も好ましくは、前記等電位表面に絶縁膜が付着していない部材であるのが良い。

また、前記等電位表面形成部材は、前記等電位表面に付着する絶縁膜の厚みが0または10μm以下であるのが好ましい。

また、前記膜を作製する成膜材料が、絶縁体であるのが好ましい。

また、前記膜を作製する成膜材料が、チタン酸鉛もしくはジルコン酸鉛を含むのが好ましい。

また、前記等電位表面形成部材は、前記等電位表面が前記成膜基板の前記導電性の表面より前記スパッタ電極に近い側に在るまたは来るように、設置されるのが好ましい。

【発明の効果】

【0020】

本発明の第1および第2の態様によれば、膜質のばらつきや組成ずれがなく、電気的特性などの膜特性の均一性、特に、面内均一性に優れた高品質な絶縁膜や導電体膜などの薄膜、例えば絶縁特性の均一性、特に、面内均一性に優れた絶縁膜などの薄膜を成膜することができるという効果を奏する。

特に、膜質のばらつきや組成ズレがなく、PZT等のPb含有ペロブスカイト型酸化物からなり、パイロクロア相の少ないペロブスカイト結晶が安定的に成長し、しかもPb抜けが安定的に抑制され、絶縁特性の均一性、特に、面内均一性に優れた圧電膜を成膜することができるという効果を奏する。

【発明を実施するための最良の形態】

【0021】

以下に、本発明の第1の態様に係るスパッタリング方法および本発明の第2の態様に係るスパッタリング装置について、添付の図面に示す好適な実施形態に基づいて詳細に説明する。

図1は、本発明のスパッタリング方法を実施する本発明のスパッタリング装置の一実施形態の装置構成を概念的に示す概略断面図である。以下では、薄膜として圧電膜を成膜するスパッタリング装置を代表例として説明するが、本発明はこれに限定されないのはいうまでもない。

【0022】

同図に示すように、本発明のスパッタリング装置10は、少なくとも1面に導電性の表面を有する成膜基板(以下、単に基板という)SBの導電性の表面SBa上に、絶縁膜、誘電体膜などの薄膜、特に圧電膜を成膜するための、すなわち、基板SBの導電性の表面SBa上にプラズマを用いた気相成長法(スパッタリング)により圧電膜などの絶縁性薄膜を成膜し、圧電素子などの薄膜デバイスを製造するRFスパッタリング装置であって、ガス導入管12aおよびガス排出管12bを備える真空容器12と、この真空容器(真空チャンバともいう)12内に設けられ、スパッタリング用のターゲット材TGを保持し、プラズマを発生させるスパッタ電極(カソード電極)14と、このスパッタ電極14に接続され、スパッタ電極14に高周波を印加する高周波電源16と、真空容器12内の、スパッタ電極14と対向する位置に配置され、ターゲット材TGの成分による薄膜が成膜される基板SBを保持する基板ホルダ18と、基板ホルダ18に保持される基板SBの外側に設置され、基板SBの導電性の表面SBaと等電位である等電位表面20aを持つ等電位表面形成部材20とを有する。

【0023】

真空容器12は、スパッタリングを行うために所定の真空度を維持する、鉄、ステンレス、アルミニウム等で形成される気密性の高い容器であって、図示例においては、接地され、その内部に成膜に必要なガスを導入するガス導入管12aおよび真空容器12内のガスの排気を行うガス排出管12bが取り付けられている。ガス導入管12aから真空容器12内に導入されるガスとしては、アルゴン(Ar)、または、アルゴン(Ar)と酸素(O2)の混合ガス等を用いることができる。ガス導入管12aは、これらのガスの供給源(図示せず)に接続されている。一方、ガス排出管12bは、真空容器12内を所定の真空度にすると共に、成膜中にこの所定の真空度に維持するために、真空容器12内のガスを排気するため、真空ポンプ等の排気手段に接続されている。

なお、真空容器12としては、スパッタリング装置で利用される真空チャンバ、ベルジャー、真空槽などの種々の真空容器を用いることができる。

【0024】

スパッタ電極14は、真空容器12の内部の上方に配置され、その表面上(図中、上面)に成膜する圧電膜などの薄膜の組成に応じた組成のターゲット材TGを装着し、保持するようになっており、高周波電源16に接続されている。

高周波電源16は、真空容器12内に導入されたArなどのガスをプラズマ化させるための高周波電力(負の高周波)をスパッタ電極14に供給するためのものであり、その一方の端部がスパッタ電極14に接続され、他方の端部が接地されている。なお、高周波電源16がスパッタ電極14に印加する高周波電力は、特に制限的ではなく、例えば13.65MHz、最大5kW、あるいは、最大1kWの高周波電力などを挙げることができるが、例えば50kHz〜2MHz、27.12MHz、40.68MHz、60MHz、1kW〜10kWの高周波電力を用いるのが好ましい。

【0025】

スパッタ電極14は、高周波電源13からの高周波電力(負の高周波)の印加により放電して、真空容器12内に導入されたArなどのガスをプラズマ化し、Arイオン等のプラスイオンを生成させる。したがって、スパッタ電極14は、カソード電極またはプラズマ電極と呼ぶこともできる。

こうして生成されたプラスイオンは、スパッタ電極14に保持されたターゲット材TGをスパッタする。このようにして、プラスイオンにスパッタされたターゲット材TGの構成元素は、ターゲット材TGから放出され、中性あるいはイオン化された状態で、対向離間配置された基板ホルダ18に保持された基板SB上に蒸着される。

こうして、詳細は後述するが、図中に点線で示すように、真空容器12の内部にArイオン等のプラスイオンやターゲット材TGの構成元素やそのイオンなどを含むプラズマ空間Pが形成される。

【0026】

基板ホルダ18は、真空容器12の内部の上方に、スパッタ電極14と対向する位置に離間して配置され、スパッタ電極14に保持されたターゲット材TGの構成元素(成分)が蒸着され、圧電膜などの薄膜が成膜される基板SBを保持、すなわち図中上面から支持するためのものである。なお、基板ホルダ18は、真空容器12の内部の上方に取り付けられる基部18aと、基部18aに取り付けられ、基板SBの外径より大きい外径を持つ基板取付台18bと、基板取付台18bに取り付けられ、先端(図中下端)が内側に折れ曲がった複数のL字状の基板保持部材18cとを有し、基板SBの導電性表面SBaがターゲット材TG(スパッタ電極14)の側に向くように、基板保持部材18cの先端のL字に折れ曲がった部分(以下、L字部という)18dに基板SBの導電性表面SBaが載置される。

なお、基板ホルダ18は、基板保持部材18cによって基板SBを保持するものに限定されず、基板取付台18bに設けられた静電チャック等によって基板SBを静電吸着するものであっても良い。

【0027】

なお、基板ホルダ18(の基板取付台18b)は、基板SBの成膜中に、基板SBを所定温度に、加熱しかつ維持するためのヒータ(図示せず)を備えている。

ここで、本発明のスパッタリング装置10においては、特に、絶縁膜を形成する場合には、基板SBが接地電位になっていない、したがって、基板ホルダ18に保持される基板SBが、接地電位になっていない構造であることが好ましい。すなわち、スパッタリング装置10では、基板SB、したがって、基板ホルダ18の電位がフローティング電位となる構造であるのが好ましい。したがって、基板ホルダ18の基部18aは、特に、絶縁膜を形成する場合には、絶縁性であるのが好ましい。また、基板ホルダ18の基板保持部材18cは、導電性であるのが好ましい。

なお、基板ホルダ18に装着される基板SBのサイズは、特に制限的ではなく、通常の6インチサイズの基板であっても、5インチや、8インチのサイズの基板であってもよいし、5cm角のサイズの基板であってもよい。

【0028】

等電位表面形成部材(以下、単に、等電位板ともいう)20は、本発明の最も特徴とする部分であって、基板ホルダ18の基板保持部材18cの先端のL字部18dの外側、すなわちターゲット材TG(スパッタ電極14)の側に取り付けられるドーナツ状の金属製の板状部材であって、基板保持部材18cの内側包絡線(包絡円)と一致する、もしくはその外側に位置する中心開口20bを持つ。また、等電位板20は、基板SBの外側に、かつスパッタ電極14の側に、配置または設置され、基板SBの導電性の表面SBaと等電位である等電位表面20aを有する。

なお、等電位板20は、基板ホルダ18の基板保持部材18cに取り付けられるものに限定されず、基板取付台18bに直接取り付けられ、基板保持部材18cの先端のL字部18dに接触されまたは接続され、もしくは、基板保持部材18cに保持された基板SBに直接接触され、または接続されるように構成されていても良い。

また、等電位板20と基板SBとを直接接触させる場合、または基板ホルダ18の基板保持部材18cを介して3者を接触させる場合には、接触圧を上げ、接触抵抗の影響を減らすようにするのが好ましい。

また、基板ホルダ18が、基板取付台18bに設けられた静電チャック等によって基板SBを静電吸着する場合には、等電位板20を、基板取付台18bに直接取り付け、静電吸着された基板SBに直接接触されまたは接続するように構成されていても良いし、静電吸着された基板SBに直接取り付けるものであっても良い。

【0029】

ここで、等電位表面形成部材20に形成される等電位表面20aの面積は、等電位である基板SBの導電性の表面SBaの面積の40%以上であるのが好ましく、より好ましくは70%以上であるのが良く、最も好ましくは150%以上であるのが良い。

その理由は、例えば、後述する実験1から明らかなように、面積割合が40%以上では、等電位表面20aがない場合に比べ、確実に、ペロブスカイト構造のチタン酸ジルコン酸鉛(PZT)のような圧電膜を成膜することができるからであり、また、後述する実験4および5の強誘電ヒステリシス測定から明らかなように、70%以上では、中央と端部での分極値の比の値が1.0と見積もられるからであり、中央と端部とで変化がないと考えられるからであり、また、150%以上では、後述する実験2〜5、特に、実験5から明らかなように、成膜回数を繰り返しても、分極値の比が大きくならず、1.0と見積もられるからである。

【0030】

本発明においては、基板SBの外側に、かつスパッタ電極14の側に、基板SBの導電性の表面SBaと等電位である等電位表面20aを形成することにより、基板SBの導電性の表面SBa上に、膜質のばらつきや組成ずれがなく、絶縁特性、電気的特性などの膜特性の均一性、特に面内均一性に優れた高品質な絶縁膜や導電体膜などの薄膜を成膜することができる。

この理由は、完全に解明されているわけではないが、本発明者らには、以下のように考えることができる。

ここで、図1に示すスパッタリング装置10において、基板SBを導電性基板とし、その導電性基板SBだけを設置してスパッタリングした場合、基板SBの周囲が基板SBと等電位でないために、例えば、放電を起こしているAr+のようなイオンの動きが、大きくことなることが考えられる。

【0031】

一方、特許文献4および5で問題にしているように、プラズマ電位と基板電位の差が大きい場合は、Ar+が成膜した膜にぶつかり、逆スパッタを起こす。そのため、逆スパッタが大きいところでは成膜レートが低く、逆スパッタが抑制されている部分では、成膜レートが高いと考えられる。そのため、基板面内で電位の差がある場合、膜厚むらができると考えられる。すなわち、特許文献4および5で解決しているのは、この膜厚むらの課題であると考えられる。

また、等電位面を設けた場合でも、その面積が小さい場合には、または十分に大きくない場合は、その効果があっても、小さく、やはり、Ar+のようなイオンの基板表面への動きが、中央付近と端部で違うためと考えられる。したがって、本発明においては、等電位表面形成部材20に形成される等電位表面20aの面積は、等電位である基板SBの導電性の表面SBaの面積の40%以上であるのが好ましく、より好ましくは70%以上であるのが良く、最も好ましくは150%以上であるのが良い。

【0032】

例えば、チタン酸ジルコン酸鉛(PZT)のような圧電膜を成膜する際に、上述のような膜厚むらができない程度の電位差においても、基板電位の差が基板面内で違った場合、鉛のようなスパッタ率の大きい元素から選択的にスパッタリングされるので、鉛の量が異なってくると考えられる。そのため、基板の周囲に等電位面を設置しない場合は、全体的に逆スパッタリングが大きくて、鉛の抜けが大きいので、ペロブスカイト構造を維持できず、パイロクロア構造になってしまうと考えられる。

一方、等電位面を設置した場合でも、その面積が小さい場合は、特に、成膜初期に、やはり、少なくても、鉛抜けが起こるために、膜全体の組成や結晶相は同じであるが、電気特性に差が生じると考えられる。したがって、上述のように、本発明においては、等電位表面形成部材20に形成される等電位表面20aの面積は、等電位である基板SBの導電性の表面SBaの面積の40%以上であるのが好ましく、より好ましくは70%以上であるのが良く、最も好ましくは150%以上であるのが良い。

【0033】

ところで、このような本発明の技術は、スパッタ膜のプラズマを均一化することで逆スパッタリングを制御し、均一化するというものであるから、どのような材料にも適用することができる。

しかし、等電位面との導通は、成膜する材料が金属や導電体の場合は、容易に取ることができ、成膜する物質が絶縁体の場合は、等電位面が接触を考慮しないと容易に導通が取れなくなることから、絶縁体(絶縁体・誘電体・強誘電体・圧電体・焦電体)などの材料に用いることがより好ましい。

【0034】

また、絶縁体でなくても、逆スパッタリングによって組成の変化が著しい材料などの場合には、面内分布が大きくなることから、スパッタ率が高い、鉛やビスマスや亜鉛などを含む物質の場合に有効である。例えば、チタン酸鉛もしくはジルコン酸鉛を含むチタン酸ジルコン酸鉛(PZT)や、その類似物質、PLZT、PTなどや、その元素置換体、BLSFと呼ばれるビスマス系誘電体、BiFeO3のようなマルチフェロイック材料、Bi系超伝導体、IGZOなどの、Zn含有の半導体などに、より好ましく応用することができる。

特に、鉛が抜けると、容易にパイロクロア相となり、強誘電性がなくなってしまうPZT系材料に好ましく用いることができる。

【0035】

また、本発明において用いられる成膜基板としては、少なくとも1面に導電性の表面を有しており、その1つの導電性の表面に、上述のような成膜材料を成膜することができればどのような基板でも良く、例えば、金属箔や金属基板、導電性セラミックス基板などの導電体や導電性基板や、シリコンやSiO2や、ガラス基板や、セラミックス基板などの絶縁性基板や半導性基板の上に片面(1面)または両面に導電性を付与した基板、例えば絶縁性基板や半導性基板の上に導電性の材料を、たとえば、電極として成膜した基板などを用いることができる。すなわち、本発明は、導電体や導電性基板そのものに成膜する場合も、絶縁性基板や半導性基板の上に導電性の材料を電極として成膜した基板を用いる場合にも適用できる。

【0036】

図示例の装置においては、等電位表面形成部材20の等電位表面20aは、等電位である基板SBの導電性の表面SBaより、スパッタ電極14の側に配置または設置されているのが好ましい。

その理由は、等電位表面形成部材20の等電位表面20aを真空チャンバ12の内壁面の側に形成した場合、Ar+のようなイオンの基板表面への動きが、中央付近と端部で違うためと考えられるからである。

なお、等電位表面形成部材20は、単一の部材であっても、複数の部材から形成されていても良く、また、等電位表面形成部材20の表面に形成される等電位表面20aは、1つの面を形成するものでも、段差のある複数の面で形成されるものであっても良い。

【0037】

ここで、等電位表面形成部材20の、スパッタ電極14の側に、等電位表面20aを形成する方法は、特に制限的ではなく、基板SBの導電性表面SBaと等電位となる面を形成できれば、どのようにしても良く、例えば、基板ホルダ18の基板保持部材18cの先端の少なくともL字部18dの一部、例えば、全部、先端のL字部18dもしくは先端のL字部18d一部を金属などの導電性部材で形成し、基板SBの導電性表面SBaと金属製の等電位板20とを基板保持部材18cの導電性の先端のL字部18dを介して導通させるように構成しても良いし、基板保持部材18cの先端のL字部18dが導電性でない場合には、等電位板20を基板ホルダ18の基板保持部材18cに取り付けるとともに、基板保持部材18cの内側において等電位板20を基板SBの導電性表面SBaとを接触させ、または電気的に接続して、導通させるようにしても良い。

なお、本発明において、等電位板20の当電位表面20aと基板SBの導電性表面SBaとが等電位とするために、両者を導通させるとは、両表面を接触させた時、両表面を導電性部材で接続した時、または、等電位板20と基板SBとを導電性部材で接続した時、両表面間の抵抗が、数Ω、すなわち、10Ω以下、好ましくは、5Ω以下、より好ましくは1Ω以下であることをいう。

【0038】

また、図示例のスパッタリング装置10では、等電位表面形成部材20の等電位表面20aに絶縁膜が付着していると、あるいは成膜を繰り返し続けると、真空チャンバ12内に設置されている等電位板20の等電位表面20aに絶縁膜が付着すると、等電位板20の等電位表面20aが等電位面としての機能が低下してしまい、絶縁膜の厚みが厚くなると、等電位面として機能しなくなってしまう。

したがって、本発明においては、等電位板20は、その等電位表面20aに付着している絶縁膜の厚みが10μm以下であるのが好ましく、より好ましくは、6μm以下であるのが良く、さらに好ましくは、4μm以下であるのが良く、最も好ましくは、等電位表面20aに絶縁膜が付着していない部材であるのが良い。

この理由は、後述する実験5から明らかなように、成膜回数を繰り返して、絶縁膜の厚みが10μmを超えると、等電位表面20aが等電位面として機能しなくなってしまうからである。

【0039】

ここで、本発明のスパッタリング方法およびスパッタリング装置においては、成膜回数を繰り返していると、真空チャンバ12内に設置されている等電位表面形成部材20の等電位表面20aに付着する絶縁膜の厚みが厚くなり、等電位板20の等電位表面20aが等電位面として機能しなくなってしまい、高品質の絶縁膜ができなくなり、歩留まりが悪くなってしまう。このため、真空チャンバ12内に設置されている等電位表面形成部材20の等電位表面20aに付着する絶縁膜の厚みが、0または10μm以下である間に、すなわち、10μmを超えない間に、成膜基板SBの導電性の表面SBa上に薄膜を作製するのが好ましい。なお、等電位表面20a上の絶縁膜の厚みが、6μm以下である間がより好ましく、4μm以下である間がさらに好ましく良く、0である間が最も好ましい。

【0040】

本発明のスパッタリング装置は、基本的に、以上のように構成されるものであり、以下に、その作用および本発明のスパッタリング方法について説明する。

図2は、本発明のスパッタリング方法の一例を示すフローチャートである。

まず、図2に示すように、ステップS10で、図1に示すスパッタリング装置10において、真空容器12内に設けられたスパッタ電極14にスパッタリング用のターゲット材TGを装着して保持させるとともに、真空容器内において、スパッタ電極14と対向する位置に離間して配置され、等電位表面形成部材20が取り付けられた基板ホルダ18に圧電膜などの薄膜を成膜する導電性表面SBaを持つ基板SBを装着して保持させる。

なお、このとき、ステップS12として、基板ホルダ18に装着された基板SBの導電性表面SBaと基板ホルダ18の基板保持部材18cの先端のL字部18dに取り付けられた等電位板20の当電位表面20aとがテスタ等で計測して導通していることを確認する。なお、このステップS10とS12とは、同時に行っても良いし、逆に、ステップS12を先に、ステップS10を後に行っても良い。

【0041】

この後、ステップS14において、真空容器12内が所定に真空度になるまでガス排出管12bから排気し、所定の真空度を維持するように排気し続けながら、ガス導入管12aからアルゴンガス(Ar)などのプラズマ用ガスを所定量づつ供給し続ける。これと同時に、ステップS16において、高周波電源16からスパッタ電極14に高周波(負の高周波電力)を印加して、スパッタ電極14を放電させて、真空容器12内に導入されたArなどのガスをプラズマ化し、Arイオン等のプラスイオンを生成させ、プラズマ空間Pが形成される。

次いで、ステップS18において、こうして形成されたプラズマ空間P内のプラスイオンは、スパッタ電極14に保持されたターゲット材TGをスパッタし、スパッタされたターゲット材TGの構成元素は、ターゲット材TGから放出され、中性あるいはイオン化された状態で、対向離間配置された基板ホルダ18に保持された基板SB上に蒸着され、成膜が開始される。

【0042】

成膜中のプラズマのエネルギを制御し、基板電位を所定のフローティング電位に保つことにより、逆スパッタの防止による膜の高品質化、組成ズレの制御、および成膜の再現性向上を図ることができ、一定の品質の良質な、すなわち膜質の変化のない高品質な圧電膜などの薄膜を成膜することができる(ステップS20)。

なお、本発明において、ステップS10〜ステップS20までの成膜を繰り返し行う場合には、1回の成膜において、基板SBの導電性表面SBaに形成される薄膜の厚みを考慮し、成膜中に等電位板20の当電位表面20aに形成された薄膜の厚みが10μmを超えないように繰り返す必要がある。この際、成膜中に等電位板20の当電位表面20aに形成された薄膜の厚みが10μmを超えていないことが確認できる場合には、ステップS12の基板SBの導電性表面SBaと等電位板20の当電位表面20aとの導通の確認は行わなくても良い。

【0043】

次に、本発明のスパッタリング方法による成膜方法において、好ましいその他の成膜条件に説明する。

本発明のスパッタリングによる成膜方法における成膜条件は、成膜温度Ts(℃)と、成膜時のプラズマ中のプラズマ電位Vs(V)と基板のフローティング電位Vf(V)との差であるVs−Vf(V)と、成膜される前記膜の特性との関係に基づいて決定されるのが好ましい。

ここで、前記関係が求められる前記膜の特性としては、膜の結晶構造および/または膜組成が挙げられる。

【0044】

図3は、図1に示すスパッタリング装置における成膜中の様子を模式的に示す説明図である。

図3に模式的に示すように、スパッタ電極14の放電により真空容器12内に導入されたガスがプラズマ化され、Arイオン等のプラスイオンIpが生成し、スパッタ電極14と基板ホルダ18との間、すなわち、スパッタ電極14に保持されたターゲット材TGと基板ホルダ18に保持された基板SBとの間にプラズマ空間Pが生成される。生成したプラスイオンIpはターゲット材TGをスパッタする。プラスイオンIpにスパッタされたターゲット材TGの構成元素Tpは、ターゲット材TGから放出され中性あるいはイオン化された状態で基板SBに蒸着される。

このとき、基板SBの外側、かつターゲット材TG側の導電性表面SBaには、等電位板20が基板SBと導通するように取り付けられているので、真空容器12内のプラスイオンIpの導電性表面SBaへの動きは、基板SBの導電性表面SBaの中央でも端部でも変わらないので、ターゲット材TGから放出され中性あるいはイオン化されたターゲット材TGの構成元素Tpは、導電性表面SBaに中央でも端部でも均等に蒸着される。このため、得られる蒸着薄膜は、膜質が均一な高品質の膜となると考えられる。

【0045】

プラズマ空間Pの電位は、プラズマ電位Vs(V)となる。本発明では、通常、基板SBは、絶縁体であり、かつ、電気的にアースから絶縁されている。したがって、基板SBはフローティング状態にあり、その電位はフローティング電位Vf(V)となる。ターゲット材TGと基板SBとの間にあるターゲット材TGの構成元素Tpは、プラズマ空間Pの電位と基板SBの電位との電位差Vs−Vfの加速電圧分の運動エネルギーを持って、成膜中の基板SBに衝突すると考えられる。

【0046】

プラズマ電位Vsおよびフローティング電位Vfは、ラングミュアプローブを用いて測定することができる。プラズマP中にラングミュアプローブの先端を挿入し、プローブに印加する電圧を変化させると、例えば、図4に示すような電流電圧特性が得られる(小沼光晴著、「プラズマと成膜の基礎」p.90、日刊工業新聞社発行)。この図4では、電流が0となるプローブ電位がフローティング電位Vfである。この状態は、プローブ表面へのイオン電流と電子電流の流入量が等しくなる点である。絶縁状態にある金属の表面や基板表面はこの電位になっている。プローブ電圧をフローティング電位Vfより高くしていくと、イオン電流は次第に減少し、プローブに到達するのは電子電流だけとなる。この境界の電圧がプラズマ電位Vsである。

プラズマ空間Pと基板SBとの電位差Vs−Vfは、基板SBとターゲット材TGとの間にアースを設置するなどして変えることもできるが、基板SBの基板電位であるフローティング電位Vfを調整することにより変えることもできる。

【0047】

プラズマを用いるスパッタリングにおいて、成膜される膜の特性を左右するファクタとしては、成膜温度、基板の種類、基板に先に成膜された膜があれば下地の組成、基板の表面エネルギー、成膜圧力、雰囲気ガス中の酸素量、投入電極、基板/ターゲット間距離、プラズマ中の電子温度および電子密度、プラズマ中の活性種密度および活性種の寿命等が考えられる。

本発明者らは、多々ある成膜ファクタの中で、成膜される膜の特性は、成膜温度Tsと電位差Vs−Vfとの2つのファクタに大きく依存することを見出し、これらファクタを好適化することにより、良質な膜を成膜できることを見出している。すなわち、成膜温度Tsを横軸にし、電位差Vs−Vfを縦軸にして、膜の特性をプロットすると、ある範囲内において良質な膜を成膜できることを見出している(図5参照)。

【0048】

電位差Vs−Vfが基板SBに衝突するターゲット材TGの構成元素Tpの運動エネルギーに相関することを述べた。下記式に示すように、一般に運動エネルギーEは温度Tの関数で表されるので、基板SBに対して、電位差Vs−Vfは温度と同様の効果を持つと考えられる。

E=1/2mv2=3/2kT

(式中、mは質量、vは速度、kは定数、Tは絶対温度である。)

電位差Vs−Vfは、温度と同様の効果以外にも、表面マイグレーションの促進効果、弱結合部分のエッチング効果などの効果を持つと考えられる。

【0049】

特開2004−119703号公報には、スパッタリング法により圧電膜を成膜する際に、圧電膜にかかる引張応力を緩和するために、基板にバイアスを印加することが提案されている。基板にバイアスを印加することは、基板に突入するターゲットの構成元素のエネルギ量を変えていることになる。しかしながら、特開2004−119703号公報には、プラズマ電位Vs、およびプラズマ電位Vsとフローティング電位Vfとの差である電位差Vs−Vfについて記載されていない。

【0050】

通常、従来のスパッタリング装置などの成膜装置では、プラズマ空間Pと基板SBとの電位差Vs−Vfは、装置の構造によって略決まり、大きく変えることができないので、従来は、電位差Vs−Vfを変えるという発想自体がほとんどなかった。スパッタリング方法ではないが、特開平10−60653号公報に、アモルファスシリコン膜等を高周波プラズマCVD法により成膜する成膜方法において、電位差Vs−Vfを特定の範囲内に制御する成膜方法が開示されている。この発明では、電位差Vs−Vfが基板面上で不均一になることを解消するために、電位差Vs−Vfを特定の範囲内に制御するようにしている。しかしながら、特開平10−60653号公報には、成膜温度TsとVs−Vfと成膜される膜の特性との関係に基づいて、成膜条件を決定することについては記載されていない。

【0051】

このような成膜方法は、本発明のスパッタリング方法を始めとして、プラズマを用いる気相成長法により成膜することが可能なものであれば、いかなる膜にも適用することができる。本発明のスパッタリング方法や、このような成膜方法を適用可能な膜としては、絶縁膜、誘電体膜、および圧電膜等が挙げられる。

このような成膜方法は、1種または複数種のペロブスカイト型酸化物からなる圧電膜(不可避不純物を含んでいてもよい。)の成膜に好ましく適用できる。ペロブスカイト型酸化物からなる圧電膜は、電圧無印加時において自発分極性を有する強誘電体膜である。

【0052】

本発明者らは、このような成膜方法を下記一般式(P)で表される1種または複数種のペロブスカイト型酸化物からなる圧電膜に適用する場合、下記式(1)および(2)を充足する範囲で成膜条件を決定することが好ましいことを見出している(図5参照)。

一般式AaBbO3・・・(P)

(式中、A:Aサイト元素であり、Pbを含む少なくとも1種の元素、B:Bサイトの元素であり、Ti,Zr,V,Nb,Ta,Cr,Mo,W,Mn,Sc,Co,Cu,In,Sn,Ga,Zn,Cd,Fe,Ni,およびランタニド元素からなる群より選ばれた少なくとも1種の元素、O:酸素原子。a=1.0かつb=1.0である場合が標準であるが、これらの数値はペロブスカイト構造を取り得る範囲内で1.0からずれてもよい。)、

Ts(℃)≧400・・・(1)、

−0.2Ts+100<Vs−Vf(V)<−0.2Ts+130・・・(2)

【0053】

上記一般式(P)で表されるペロブスカイト型酸化物としては、チタン酸鉛、チタン酸ジルコン酸鉛(PZT)、ジルコニウム酸鉛、チタン酸鉛ランタン、ジルコン酸チタン酸鉛ランタン、マグネシウムニオブ酸ジルコニウムチタン酸鉛、ニッケルニオブ酸ジルコニウムチタン酸鉛等の鉛含有化合物、および、チタン酸バリウム、チタン酸ビスマスナトリウム、チタン酸ビスマスカリウム、ニオブ酸ナトリウム、ニオブ酸カリウム、ニオブ酸リチウム等の非鉛含有化合物が挙げられる。圧電膜は、これら上記一般式(P)で表されるペロブスカイト型酸化物の混晶系であってもよい。

【0054】

本発明のスパッタリング方法は、下記一般式(P−1)で表されるPZTまたはそのBサイト置換系、およびこれらの混晶系に好ましく適用できる。

Pba(Zrb1Tib2Xb3)O3・・・(P−1)

(式(P−1)中、XはV族およびVI族の元素群より選ばれた少なくとも1種の金属元素である。a>0、b1>0、b2>0、b3≧0。a=1.0であり、かつb1+b2+b3=1.0である場合が標準であるが、これらの数値はペロブスカイト構造を取り得る範囲内で1.0からずれてもよい。)

上記一般式(P−1)で表されるペロブスカイト型酸化物は、d=0のときチタン酸ジルコン酸鉛(PZT)であり、d>0のとき、PZTのBサイトの一部をV族およびVI族の元素群より選ばれた少なくとも1種の金属元素であるXで置換した酸化物である。

Xは、VA族、VB族、VIA族、およびVIB族のいずれの金属元素でもよく、V,Nb,Ta,Cr,Mo,およびWからなる群より選ばれた少なくとも1種であることが好ましい。

【0055】

本発明者らは、上記一般式(P)で表されるペロブスカイト型酸化物からなる圧電膜を成膜する場合、上記式(1)を充足しないTs(℃)<400の成膜条件では、成膜温度が低すぎてペロブスカイト結晶が良好に成長せず、パイロクロア相がメインの膜が成膜されることを見出している(図5参照)。

本発明者らは、さらに、上記一般式(P)で表されるペロブスカイト型酸化物からなる圧電膜を成膜する場合、上記式(1)を充足するTs(℃)≧400の条件では、成膜温度Tsと電位差Vs−Vfが上記式(2)を充足する範囲で成膜条件を決定することで、パイロクロア相の少ないペロブスカイト結晶を安定的に成長させることができ、しかも、Pb抜けを安定的に抑制することができ、結晶構造および膜組成が良好な良質な圧電膜を安定的に成膜することができることを見出している(図5参照)。

【0056】

PZTのスパッタ成膜において、高温成膜するとPb抜けが起こりやすくなることが知られている(特開平6−49638号公報の図2等参照)。本発明者らは、Pb抜けが、成膜温度以外に電位差Vs−Vfにも依存することを見出している。PZTの構成元素であるPb,Zr,およびTiの中で、Pbが最もスパッタ率が大きく、スパッタされやすい。例えば、「真空ハンドブック」((株)アルバック編、オーム社発行)の表8.1.7には、Arイオン300evの条件におけるスパッタ率は、Pb=0.75、Zr=0.48,Ti=0.65であることが記載されている。スパッタされやすいということは、スパッタされた原子が基板面に付着した後に、再スパッタされやすいということである。プラズマ電位と基板の電位との差が大きい程、すなわち、Vs−Vfの差が大きい程、再スパッタの率が高くなり、Pb抜けが生じやすくなると考えられる。このことは、PZT以外のPb含有ペロブスカイト型酸化物でも、同様である。また、スパッタリング法以外のプラズマを用いる気相成長法でも同様である。

【0057】

成膜温度Tsと電位差Vs−Vfがいずれも過小の条件では、ペロブスカイト結晶を良好に成長させることができない傾向にある。また、成膜温度Tsと電位差Vs−Vfのうち少なくとも一方が過大の条件では、Pb抜けが生じやすくなる傾向にある。

すなわち、上記式(1)を充足するTs(℃)≧400の条件では、成膜温度Tsが相対的に低い条件のときには、ペロブスカイト結晶を良好に成長させるために電位差Vs−Vfを相対的に高くする必要があり、成膜温度Tsが相対的に高い条件のときには、Pb抜けを抑制するために、電位差Vs−Vfを相対的に低くする必要がある。これを表したのが、上記式(2)である。

【0058】

本発明者らは、上記一般式(P)で表されるペロブスカイト型酸化物からなる圧電膜を成膜する場合、下記式(1)〜(3)を充足する範囲で成膜条件を決定することで、圧電定数の高い圧電膜が得られることを見出している。

Ts(℃)≧400・・・(1)、

−0.2Ts+100<Vs−Vf(V)<−0.2Ts+130・・・(2)、

10≦Vs−Vf(V)≦35・・・(3)

【0059】

本発明者等は、上記一般式(P)で表されるペロブスカイト型酸化物からなる圧電膜を成膜する場合、成膜温度Ts(℃)=約420の条件では、電位差Vs−Vf(V)=約42Vとすることで、Pb抜けのないペロブスカイト結晶を成長させることができるが、得られる膜の圧電定数d31は、100pm/V程度と低いことを見出している。この条件では、電位差Vs−Vf、すなわち基板に衝突するターゲット材TGの構成元素Tpのエネルギが高すぎるために、膜に欠陥が生じやすく、圧電定数が低下すると考えられる。本発明者等は、上記式(1)〜(3)を充足する範囲で成膜条件を決定することで、圧電定数d31≧130pm/Vの圧電膜を成膜できることを見出している。

【0060】

本発明のスパッタリング方法等のプラズマを用いる気相成長法において、膜特性に対して影響を与えるファクタが、成膜温度Ts(℃)、および、成膜時のプラズマ中のプラズマ電位Vs(V)とフローティング電位Vf(V)との差である電位差Vs−Vf(V)であることを明らかにしたものである。

本発明のスパッタリング方法等の成膜方法によれば、膜特性に対して影響を与える上記2つのファクタと成膜される膜の特性との関係に基づいて、成膜条件を決定する構成としているので、スパッタリング方法等のプラズマを用いる気相成長法により良質な膜を安定的に成膜することができる。

本発明による成膜方法を採用することで、装置条件が変わっても良質な膜を成膜できる条件を容易に見出すことができ、良質な膜を安定的に成膜することができる。

【0061】

本発明のスパッタリング方法による成膜方法は、圧電膜の成膜等に好ましく適用することができる。本発明によれば、ペロブスカイト型酸化物からなる圧電膜の成膜において、パイロクロア相の少ないペロブスカイト結晶を安定的に成長させることが可能となる。本発明によれば、PZT等のPb含有ペロブスカイト型酸化物からなる圧電膜の成膜において、パイロクロア相の少ないペロブスカイト結晶を安定的に成長させることができ、しかもPb抜けを安定的に抑制することが可能となる。

【0062】

上記成膜方法を適用することで、以下の圧電膜を提供することができる。

すなわち、本圧電膜は、下記一般式(P)で表される1種または複数種のペロブスカイト型酸化物からなる圧電膜において、本発明のスパッタリング方法等のプラズマを用いる気相成長法により成膜されたものであり、下記式(1)および(2)を充足する成膜条件で成膜されたものである。

一般式AaBbO3・・・(P)

(式中、A:Aサイト元素であり、Pbを含む少なくとも1種の元素、B:Bサイトの元素であり、Ti,Zr,V,Nb,Ta,Cr,Mo,W,Mn,Sc,Co,Cu,In,Sn,Ga,Zn,Cd,Fe,Ni,およびランタニド元素からなる群より選ばれた少なくとも1種の元素、O:酸素原子。a=1.0かつb=1.0である場合が標準であるが、これらの数値はペロブスカイト構造を取り得る範囲内で1.0からずれてもよい。)、

Ts(℃)≧400・・・(1)、

−0.2Ts+100<Vs−Vf(V)<−0.2Ts+130・・・(2)

【0063】

本発明によれば、パイロクロア相の少ないペロブスカイト結晶構造を有し、しかも、Pb抜けが抑制され、結晶構造および膜組成が良好な良質な圧電膜を安定的に提供することができる。

また、本発明によれば、1.0≦aであるPb抜けのない組成の圧電膜を提供することができ、1.0<aであるPbリッチな組成の圧電膜を提供することもできる。aの上限は特に制限なく、本発明者等は、1.0≦a≦1.3であれば、圧電性能が良好な圧電膜が得られることを見出している。

【0064】

本発明による圧電膜は、下記式(1)〜(3)を充足する成膜条件で成膜されたものであることが好ましい。かかる構成とすることで、圧電定数の高い圧電膜を提供することができる。

Ts(℃)≧400・・・(1)、

−0.2Ts+100<Vs−Vf(V)<−0.2Ts+130・・・(2)、

10≦Vs−Vf(V)≦35・・・(3)

【0065】

こうして得られた本発明による圧電膜は、膜質のばらつきや組成ズレのない高品質な絶縁膜や誘電体膜、特に、PZT等のPb含有ペロブスカイト型酸化物からなり、パイロクロア相の少ないペロブスカイト結晶が安定的に成長し、しかもPb抜けが安定的に抑制された圧電膜であり、インクジェットヘッドなどに用いるのに適した圧電素子として利用することができる。

本発明によって得られる圧電膜、絶縁膜、誘電体膜などの薄膜は、基本的に以上のように構成される。

【0066】

次に、圧電素子およびこれを備えたインクジェットヘッドの構造について説明する。図6は、圧電素子の一実施形態を用いたインクジェットヘッドの一実施形態の要部断面図(圧電素子の厚み方向の断面図)である。視認しやすくするため、構成要素の縮尺は、実際のものとは適宜異ならせてある。

図6に示すように、インクジェットヘッド50は、圧電素子52と、インク貯留吐出部材54と、圧電素子52とインク貯留吐出部材54との間に設けられる振動板56を有する。

まず、圧電素子について説明する。同図に示すように、圧電素子52は、基板58と、基板58上に順次積層された下部電極60、圧電膜62および上部電極64とからなる素子であり、圧電膜62に対して、下部電極60と上部電極64とにより厚み方向に電界が印加されるようになっている。

【0067】

基板58としては、特に制限的ではなく、シリコン、ガラス、ステンレス(SUS)、イットリウム安定化ジルコニア(YSZ)、アルミナ、サファイヤ、シリコンカーバイド等の基板を挙げることができる。なお、基板58として、シリコン基板の表面にSiO2酸化膜が形成されたSOI基板等の積層基板を用いてもよい。

また、下部電極60は、基板58の略全面に形成されており、この上に図中手前側から奥側に延びるライン状の凸部62aがストライプ状に配列したパターンの圧電膜62が形成され、各凸部62aの上に上部電極64が形成されている。

圧電膜62のパターンは、図示するものに限定されず、適宜設計される。なお、圧電膜62は、連続膜でも構わないが、圧電膜62を、連続膜ではなく、互いに分離した複数の凸部62aからなるパターンで形成することで、個々の凸部62aの伸縮がスムーズに起こるので、より大きな変位量が得られ、好ましい。

【0068】

下部電極60の主成分としては、特に制限的ではなく、Au,Pt,Ir,IrO2,RuO2,LaNiO3,およびSrRuO3等の金属または金属酸化物、およびこれらの組合せが挙げられる。

上部電極64の主成分としては、特に制限的ではなく、下部電極60で例示した材料、Al,Ta,Cr,およびCu等の一般的に半導体プロセスで用いられている電極材料、およびこれらの組合せが挙げられる。

圧電膜62は、上述の本発明のスパッタリング方法を適用する成膜方法により成膜された膜である。圧電膜62は、好ましくは、上記一般式(P)で表されるペロブスカイト型酸化物からなる圧電膜である。

下部電極60と上部電極64の厚みは、例えば200nm程度である。圧電膜62の膜厚は特に制限なく、通常1μm以上であり、例えば1〜5μmである。

【0069】

図6に示すインクジェットヘッド50は、概略、上記構成の圧電素子52の基板58の下面に、振動板56を介して、インクが貯留されるインク室(インク貯留室)68およびインク室68から外部にインクが吐出されるインク吐出口(ノズル)70を有するインク貯留吐出部材54が取り付けられたものである。インク室68は、圧電膜62の凸部62aの数およびパターンに対応して、複数設けられている。すなわち、インクジェットヘッド50は、複数の吐出部72を有し、圧電膜62、上部電極64、インク室68およびインクノズル70は、各吐出部72毎に設けられている。一方、下部電極60、基板58および振動板56は、複数の吐出部に共通に設けられているが、これに制限されず、個々に、または幾かずつまとめて設けられていても良い。

インクジェットヘッド50では、後述する好ましい駆動方法により、または従来公知の駆動方法により、圧電素子52の凸部62aに印加する電界強度を凸部62a毎に増減させてこれを伸縮させ、これによってインク室68からのインクの吐出や吐出量の制御が行われる。

本実施形態の圧電素子およびこれを用いるインクジェットヘッドは、基本的に以上のように構成されている。

【0070】

次に、本発明によるインクジェットヘッドを備えるインクジェット式記録装置の構造について説明する。図7は、本発明によるインクジェットヘッドを備えるインクジェット式記録装置の一実施形態の全体構成を示す装置全体図であり、図8は、その部分上面図である。

図示例のインクジェット式記録装置100は、インクの色ごとに設けられた複数のインクジェットヘッド(以下、単に「ヘッド」という)50K,50C,50M,50Yを有する印字部102と、各ヘッド50K,50C,50M,50Yに供給するインクを貯蔵しておくインク貯蔵/装填部114と、記録紙116を供給する給紙部118と、記録紙116のカールを除去するデカール処理部120と、印字部102のノズル面(インク吐出面)に対向して配置され、記録紙116の平面性を保持しながら記録紙116を搬送する吸着ベルト搬送部122と、印字部102による印字結果を読み取る印字検出部124と、印画済みの記録紙(プリント物)を外部に排紙する排紙部126とから概略構成されている。

【0071】

印字部102をなすヘッド50K,50C,50M,50Yが、各々上記実施形態のインクジェットヘッド50(図6参照)である。

デカール処理部120では、巻き癖方向と逆方向に加熱ドラム130により記録紙116に熱が与えられて、デカール処理が実施される。

ロール紙を使用する装置では、図7に示すように、デカール処理部120の後段に裁断用のカッター128が設けられ、このカッターによってロール紙は所望のサイズにカットされる。カッター128は、記録紙116の搬送路幅以上の長さを有する固定刃128Aと、この固定刃128Aに沿って移動する丸刃128Bとから構成されており、印字裏面側に固定刃128Aが設けられ、搬送路を挟んで印字面側に丸刃128Bが配置される。カット紙を使用する装置では、カッター128は不要である。

【0072】

デカール処理され、カットされた記録紙116は、吸着ベルト搬送部122へと送られる。吸着ベルト搬送部122は、ローラ131、132間に無端状のベルト133が巻き掛けられた構造を有し、少なくとも印字部102のノズル面および印字検出部124のセンサ面に対向する部分が水平面(フラット面)となるよう構成されている。

ベルト133は、記録紙116の幅よりも広い幅寸法を有しており、ベルト面には多数の吸引孔(図示略)が形成されている。ローラ131、132間に掛け渡されたベルト133の内側において印字部102のノズル面および印字検出部124のセンサ面に対向する位置には吸着チャンバ134が設けられており、この吸着チャンバ134をファン135で吸引して負圧にすることによってベルト133上の記録紙116が吸着保持される。

【0073】

ベルト133が巻かれているローラ131、132の少なくとも一方にモータ(図示せず)の動力が伝達されることにより、ベルト133は、図7において時計回り方向に駆動され、ベルト133上に保持された記録紙116は、図7において左から右へと搬送される。

なお、縁無しプリント等を印字すると、ベルト133上にもインクが付着するので、ベルト133の外側の所定位置(印字領域以外の適当な位置)にベルト清掃部136が設けられている。

また、吸着ベルト搬送部122により形成される用紙搬送路上において印字部102の上流側に、加熱ファン140が設けられている。加熱ファン140は、印字前の記録紙116に加熱空気を吹き付け、記録紙116を加熱する。印字直前に記録紙116を加熱しておくことにより、インクが着弾後に乾きやすくなる。

【0074】

印字部102は、最大紙幅に対応する長さを有するライン型ヘッドを、紙送り方向と直交方向(主走査方向)に配置した、いわゆるフルライン型のヘッドとなっている(図8参照)。各印字ヘッド50K,50C,50M,50Yは、インクジェット式記録装置100が対象とする最大サイズの記録紙116の少なくとも一辺を超える長さにわたってインク吐出口(ノズル)が複数配列されたライン型ヘッドで構成されている。

記録紙116の送り方向に沿って上流側から、黒(K)、シアン(C)、マゼンタ(M)、イエロー(Y)の順に各色インクに対応したヘッド50K,50C,50M,50Yが配置されている。記録紙116を搬送しつつ、各ヘッド50K,50C,50M,50Yから、それぞれ色インクを吐出することにより、記録紙116上にカラー画像が記録される。

【0075】

印字検出部124は、印字部102の打滴結果を撮像するラインセンサ等からなり、ラインセンサによって読み取った打滴画像からノズルの目詰まり等の吐出不良を検出する。

印字検出部124の後段には、印字された画像面を乾燥させる加熱ファン等からなる後乾燥部142が設けられている。印字後のインクが乾燥するまでは印字面と接触することは避けた方が好ましいので、熱風を吹き付ける方式が好ましい。

後乾燥部142の後段には、画像表面の光沢度を制御するために、加熱・加圧部144が設けられている。加熱・加圧部144では、画像面を加熱しながら、所定の表面凹凸形状を有する加圧ローラ145で画像面を加圧し、画像面に凹凸形状を転写する。

【0076】

こうして得られたプリント物は、排紙部126から排出される。本来プリントすべき本画像(目的の画像を印刷したもの)とテスト印字とは分けて排出することが好ましい。このインクジェット式記録装置100では、本画像のプリント物と、テスト印字のプリント物とを選別してそれぞれの排出部126A、126Bへと送るために排紙経路を切り替える選別手段(図示略)が設けられている。

大きめの用紙に本画像とテスト印字とを同時に並列にプリントする場合には、カッター148を設けて、テスト印字の部分を切り離す構成とすればよい。

本実施形態のインクジェット記記録装置は、基本的に以上のように構成されている。

【0077】

以上、本発明に係るスパッタリング方法および装置について種々の実施形態および実施例を挙げて詳細に説明したが、本発明は、上記実施形態および実施例には限定されず、本発明の要旨を逸脱しない範囲において、各種の改良や設計の変更を行ってもよいのは、もちろんである。

【実施例】

【0078】

以下に、本発明を実施例に基づいて具体的に説明する。

(実験1)

図1に示すスパッタリング装置10として、アルバック社製スパッタ装置を用い、ターゲット材TGとして、Pb1.3Zr0.52Ti0.48Oxの組成の焼結体ターゲットを用い、成膜温度を450℃としてPZT膜を成膜した。成膜基板SBとしては、図9に示すように、電極32として、Ti(Ti層34)を20nm、Ir(Ir層36)を150nm積層した3インチ、厚み625μmのシリコン基板38を用いた。なお、シリコン基板38の表面には、SiO2層4が形成されていた。また、図9に示すように、成膜基板SBの電極32のIr層(電極)36の表面(SBa)上に形成されるPZT膜42の成膜膜厚は、4μmとした。

【0079】

(実施例1)

図10(a)に模式的に示すように、3インチ(76.2mm)の電極32付シリコン基板38(成膜基板SB)を、等電位表面形成部材20となる外径90mmのインコネル板22(成膜冶具)にて支えた。テスタにて、基板SBのIr電極36の表面(導電性表面SBa)とインコネル板22の表面(等電位板20の等電位表面20a)の間の抵抗を計測し、計測された抵抗は、1Ω以下を示し、基板SBのIr電極表面SBaとインコネル板22(等電位板20)の表面22a(等電位表面20a)とは、導通していることを確認した。この状態で成膜を行った。

【0080】

(比較例1)

図10(b)に模式的に示すように、実施例1において、等電位板20として用いた外径90mmのインコネル板22の裏面(基板SB側)にアルミナをコートして、絶縁層24を形成し、絶縁層24上に実施例1で用いた基板SBをセットした。テスタにて、基板SBのIr電極表面SBaとインコネル板22の表面22aとの間の抵抗を計測したところ、その抵抗は、1GΩ以上あり、テスタでは導通が確認できなかった。すなわち、インコネル板22は、等電位板20として機能していないことを確認した。この状態で同様に成膜を行った。

【0081】

(実験1の結果)

実施例1では、ペロブスカイト相のチタン酸ジルコン酸鉛(PZT)の膜(PZT膜42)ができていることを、XRD(X線回折装置)にて確認した。

比較例1では、成膜された膜が、パイロクロア相となり、目的とするチタン酸ジルコン酸鉛の膜が得られなかった。XRF(蛍光X線分析装置)にて膜の組成を計測した結果、鉛量(Pb/(Zr+Ti))は、実施例1では1.05であったが、比較例では0.8であり、本発明を用いないと、成膜中のプラズマが基板SBに集中してしまうため、Pbの抜けが生じて、Pbが不足し、所望の膜ができないことが分かった。なお、XRF測定では、下部電極32のIr層36のイリジウム(Ir)の影響を除くため、ファンダメンタルパラメータ(FP)法を用いた。

これらの結果を表1に示す。

なお、表における導通面積の割合は、等電位板20の等電位表面20aのみの面積を成膜基板SBの導電性表面SBaで除算して求めた。すなわち、導通面積の割合は、90mmのインコネル板22が等電位板20の場合には、(902−76.22)/76.22(=40%)として求め、90mmのインコネル板22と120mmのインコネル板26とが等電位板20の場合には、(1202−76.22)/76.22(=150%)として求めた。

【0082】

(実験2)

実験1で、さらに、均一性を向上させることを狙い、等電位板20として用いた外径90mmのインコネル板22の外側に、外径120mmのインコネル板26を設置した。

(実施例2)

図11に模式的に示すように、インコネル板22(等電位板20)とインコネル板26との間に絶縁性のワッシャ28を挟み、インコネル板26を設置したが、基板SBの電極(導電性表面SBa)とは、電気的に浮かせた状態で成膜した。

実験1と同様に、テスタで導通を確認し、基板SBの電極(導電性表面SBa)は、インコネル板22(等電位板20)の表面22a(等電位表面20a)までは導通しているが、インコネル板26には導通していないことを確認した。すなわち、インコネル板26は、等電位板20として機能していないことを確認した。

【0083】

(実施例3)

図12に模式的に示すように、90mmのインコネル板22と120mmのインコネル板26との間に、導電性のワッシャ30を挟み、基板SBの電極(導電性表面SBa)とインコネル板26との間を導通させ、等電位となるようにした。実験1と同様に、テスタで確認し、基板SBの電極(導電性表面SBa)からインコネル板26の表面26aまで導通していることを確認した。すなわち、インコネル板22およびインコネル板26は、等電位板20を構成し、インコネル板22の表面22aとインコネル板26の表面26aとは、等電位表面20aを構成していた。

実施例1〜3のいずれにおいても、XRDで、単相のペロブスカイト膜(PZT膜42)が全面についている事を確認し、XRFでの組成分析で、いずれも、1.05であることを確認した。

その結果を表1に示す。

【0084】

【表1】

【0085】

表1の結果から明らかなように、実施例1〜3のいずれにおいても、成膜基板SBの外側に等電位面20aを設置したので、ペロブスカイト単相膜を得たことが分かる。実施例1〜3のいずれの方法においても、本発明が良質なチタン酸ジルコン酸鉛の膜(PZT膜42)を作製するのに有効であることが分かった。

【0086】

次に、実施例1〜3で得られた基板SBのPZT膜42に上部電極を成膜し、下部電極と上部電極との間に電圧を印加して、強誘電ヒステリシス測定を計測した。

強誘電ヒステリシス測定の測定位置は、図13に示すように、3インチ(76.2mm)基板SB(PZT膜42)の中央の位置、中央から20mmの位置および中央から35mmの位置の3点とした。

実施例1および3で得られたPZT膜42の強誘電ヒステリシスの測定結果をそれぞれ図14および図15に示す。

図14および図15に示すように、実施例1および実施例3における強誘電ヒステリシス測定に差異があることが分かった。図15に示す実施例3では、面内で同じヒステリシスが得られたが、図14に示す実施例1では、3インチ基板SBの端で、ヒステリシス測定の抗電界に変化が得られた。

【0087】

そこで、PZT膜42の面方向の中央の位置と端部の位置(中央から35mmの位置;図13参照)のそれぞれのヒステリシスの測定点においてPZT膜42を切断し、TEM−EDX(電界放射型透過電子顕微鏡・エネルギ分散型X線分析装置)にて、測定径を50nm程度のスポット径として、図9に示すように、PZT膜42の下部電極32の界面付近の測定位置43a、PZT膜42の深さ方向の中央付近の測定位置43bおよびPZT膜42の上部電極44の界面付近の測定位置43cで、Pb量(=Pb/(Zr+Ti))をいずれの測定位置でも複数点(サンプル)測定した。なお、下部電極32の界面付近の測定位置43aでは、Irにかからない位置で測定した。

【0088】

いずれの測定位置のサンプル(測定点)でも、PZT膜42の中央付近の測定位置43bおよびPZT膜42の上部電極44の界面付近の測定位置43cでは、1程度の鉛量であった。(なお、TEM−EDXの場合は、XRFと比較して測定再現性が悪く、0.95〜1.05の間の鉛量の場合を、1程度とした。)

また、実施例3においては、PZT42膜の下部電極付近の測定位置43aでも、1程度の鉛量であったが、実施例1および2においては、EDXの測定場所(測定位置や測定点)によっては、1程度の鉛量の測定場所と、鉛量が0.8以下の鉛量の測定場所が見られた。

ここで、PZT膜42の面方向の中央の位置と端部の位置(中央から35mmの位置;図13参照)において、0.8以下の鉛量の測定点数を表2に示す。

また、実施例1において、各測定位置43a、43bおよび43cごとにそれぞれ4点ずつ(サンプル数n=4)測定した測定結果を図16に示す。

【0089】

図16から明らかなように、実施例1において、PZT膜42の中央の位置(図13参照)では、いずれの測定位置43a、43bおよび43cでも、4点(サンプル)とも1程度の鉛量であり、鉛(Pb)不足はなかったことが分かった。

一方、PZT膜42の端部の位置(中央から35mmの位置;図13参照)では、測定位置43bおよび43cでは、4点(サンプル)とも1程度の鉛量であり、鉛(Pb)不足はなかったが、PZT膜42の下部電極32の界面付近の測定位置43aでは、4点(サンプル)中3点で、鉛(Pb)不足が生じていたことが分かる。

【0090】

また、図14および図15に示すように、実施例1および実施例3における強誘電ヒステリシス測定に差異があることが分かるので、両者を簡便に比較するため、中央の位置と端部の位置(中央から35mmの位置)の、変化が大きい電界50kV/cmでの分極値の大きさを比較した。その結果、実施例1の分極値が3.2、実施例3の分極値が1.0と見積もられた。また、実施例2の分極値は、2.9と見積もられた。

その結果を表2に示す。

【0091】

【表2】

【0092】

表2から明らかなように、実施例1〜3では、ペロブスカイト単相膜が得られたが、導通面積の割合を増やした方が、下部電極界面付近の均一性も確保できることが分かる。すなわち、同じペロブスカイト膜でも、電気特性が異なり、これは、界面付近の鉛量が違うことによる影響と考えられる。導通面積の割合をより広げた方が、比較例で見られた鉛抜けが、基板の端の方において成膜初期でも抑制できることが分かった。

また、実施例1および2と3との比較からわかるように、成膜基板の外側に設置したインコネル板は、ただ、単にフローティングにして置くだけでは全く効果がなく、置かない場合とほとんど変化がなく、成膜基板と導通して、成膜基板と等電位となっていることが重要であると分かった。

【0093】

(実験3)

(実施例4)

実施例3の120mmのインコネル板26の代わりに、100mm(導通割合170%)のインコネル板を用いて、実験2と同様の実験を行い、ヒステリシスを測定した。

その結果を表3に示す。

表3から明らかなように、実施例4の場合も、実施例3と同様、導通割合170%程度で均一な膜が得られることが確認できた。

以上の各実験から、成膜においては、成膜基板の外側に導通部分を設けることが必須であり、その面積割合は、170%以上あることがより好ましいことが分かった。

【0094】

【表3】

【0095】

(実験4)

実施例3および4において、成膜回数を繰り返すことによる変化を調べた。

その結果を表4に示す。

表4から明らかなように、成膜回数を繰り返すと、等電位面に絶縁膜が付着し、せっかく設置した等電位面が等電位面として機能しなくなると考えられる。

実施例3においては、成膜3回目で、外側の電気特性に変化がみられたが、実施例4においては、成膜を5回繰り返しても、膜全体に変化は見られなかった。そのため、面積割合250%の方が、面積割合170%の場合より好ましいことが分かった。

成膜を4回繰り返した板においては、1回の成膜膜厚である4μmの4倍の16μmの絶縁膜が付着し、5回目の成膜が開始される。そのため、導通面積の割合が170%の場合の絶縁膜厚は、10μm以下が好ましいことが分かった。

【0096】

【表4】

【0097】

(実験5)

スパッタ装置を変え、神港精機製スパッタ装置を用いて、同様の実験を行った。成膜ターゲット材TGの組成は、同一とし、成膜基板SBとしては、IrおよびTiを成膜した実験1〜4で用いたのと同じシリコン基板を、25mm角に切断し、30mmφのインコネル成膜冶具を用いて成膜した。このインコネル成膜冶具の導通面積割合は、13%となった。

(実施例5)

上記条件で成膜し、得られたPZT膜をXRDで測定した結果、ペロブスカイト単相膜であった。

(比較例2)

一方、実施例5で用いたインコネル冶具の裏面に絶縁膜を付け、成膜基板と絶縁した状態で成膜した結果、膜は、パイロクロアとなった。

この実験5の実施例5および比較例2の結果から、成膜冶具の等電位表面の導通面積割合が、13%であっても、本発明の効果が得られることが分かった。もちろん、スパッタ装置の種類によらず、本発明の効果が得られることも分かった。

【産業上の利用可能性】

【0098】

本発明のスパッタリング方法および装置は、スパッタリングなどのプラズマを用いる気相成長法により、圧電膜、絶縁膜、誘電体膜などの薄膜を成膜する場合に適用することができ、インクジェット式記録ヘッド、強誘電体メモリ(FRAM)、および圧力センサ等に用いられる圧電膜等の成膜に適用することができる。

【図面の簡単な説明】

【0099】

【図1】本発明のスパッタリング方法を実施するスパッタリング装置の一実施形態の装置構成を示す概略断面図である。

【図2】本発明のスパッタリング方法の一例を示すフローチャートである。

【図3】図1に示すスパッタリング装置における成膜中の様子を模式的に示す模式図である。

【図4】スパッタリング装置におけるプラズマ電位Vsおよびフローティング電位Vfの測定方法を示す説明図である。

【図5】本発明法で成膜される種々の圧電膜について、成膜温度Tsを横軸にし、電位差Vs−Vfを縦軸にして、XRD測定結果を示すグラフである。

【図6】本発明の圧電素子およびこれを用いるインクジェットヘッドの一実施形態の構造を示す断面図である。

【図7】図6に示すインクジェットヘッドを備えるインクジェット式記録装置の一実施形態の構成を示す構成図である。

【図8】図7に示すインクジェット式記録装置の部分上面図である。

【図9】本発明の実施例で用いられた成膜基板および成膜基板上に成膜された薄膜の構成および測定位置を示す模式的断面図である。

【図10】(a)および(b)は、それぞれ本発明の実施例1および比較例1における成膜基板の周辺構造およびターゲット材を模式的に示す模式的断面図である。

【図11】本発明の実施例2における成膜基板の周辺構造およびターゲット材を模式的に示す模式的断面図である。

【図12】本発明の実施例3における成膜基板の周辺構造およびターゲット材を模式的に示す模式的断面図である。

【図13】本発明の各実施例における強誘電ヒステリシス測定の測定位置を示す概念図である。

【図14】本発明の実施例1における誘電ヒステリシス測定の結果を示すグラフである。

【図15】本発明の実施例3における誘電ヒステリシス測定の結果を示すグラフである。

【図16】本発明の実施例1における鉛量の測定結果を示すグラフである。

【符号の説明】

【0100】

10 スパッタリング装置

12 真空容器

12a ガス導入管

12b ガス排出管

14 スパッタ電極(カソード電極)

16 高周波電源

18 基板ホルダ

18a 基部

18b 基板取付台

18c 基板保持部材

18d L字部18d

20 等電位表面形成部材(等電位板)

20a 等電位表面

20b 中心開口

50、50K,50C,50M,50Y インクジェットヘッド

52 圧電素子

54 インク貯留吐出部材

56 振動板

58 基板(支持基板)

60、64 電極

62 圧電膜

68 インク室

70 インク吐出口

100 インクジェット式記録装置

IP プラスイオン

P プラズマ空間

SB 基板(成膜基板)

SBa 導電性表面

TG ターゲット材

Tp ターゲット材の構成元素

【特許請求の範囲】

【請求項1】

少なくとも1面に導電性の表面を有する成膜基板に薄膜を成膜するスパッタリング方法であって、前記成膜基板の外側に、この成膜基板の前記導電性の表面と等電位である等電位表面を持つ等電位表面形成部材を設置して、前記成膜基板の前記導電性の表面上に前記薄膜を作製することを特徴とするスパッタリング方法。

【請求項2】

前記成膜基板の外側において、前記等電位表面形成部材の前記等電位表面の面積が、前記成膜基板の前記導電性の表面の面積の40%以上である請求項1に記載のスパッタリング方法。

【請求項3】

前記成膜基板の外側において、前記等電位表面形成部材の前記等電位表面の面積が、前記成膜基板の前記導電性の表面の面積の70%以上である請求項2に記載のスパッタリング方法。

【請求項4】

前記成膜基板の外側において、前記等電位表面形成部材の前記等電位表面の面積が、前記成膜基板の前記導電性の表面の面積の150%以上である請求項3に記載のスパッタリング方法。

【請求項5】

前記等電位表面形成部材が、前記等電位表面に付着している絶縁膜の厚みが10μm以下の部材である請求項1〜4のいずれかに記載のスパッタリング方法。

【請求項6】

前記等電位表面形成部材は、前記等電位表面に絶縁膜が付着していない部材である請求項1〜4のいずれかに記載のスパッタリング方法。

【請求項7】

前記等電位表面形成部材の前記等電位表面に付着する絶縁膜の厚みが、0または10μm以下である間に、前記成膜基板の前記導電性の表面上に前記膜を作製する請求項1〜6のいずれかに記載のスパッタリング方法。

【請求項8】

前記膜を作製する成膜材料が、絶縁体である請求項1〜7のいずれかに記載のスパッタリング方法。

【請求項9】

前記膜を作製する成膜材料が、チタン酸鉛もしくはジルコン酸鉛を含む請求項1〜8のいずれかに記載のスパッタリング方法。

【請求項10】

前記成膜基板が、導電性基板である請求項1〜9のいずれかに記載のスパッタリング方法。

【請求項11】

前記成膜基板の前記導電性の表面と、前記等電位表面形成部材の前記等電位表面とが、導通している請求項1〜10のいずれかに記載のスパッタリング方法。

【請求項12】

真空容器と、

この真空容器内に設けられ、スパッタリング用のターゲット材を保持するスパッタ電極と、

このスパッタ電極に接続され、前記スパッタ電極に高周波を印加する高周波電源と、

前記真空容器内の、前記スパッタ電極と対向する位置に離間して配置され、前記ターゲット材の成分による薄膜が成膜され、少なくとも1面に導電性の表面を有する成膜基板を保持する基板ホルダと、

前記基板ホルダに保持される前記成膜基板の外側に設置される等電位表面形成部材とを有し、

前記等電位表面形成部材は、前記スパッタ電極と対向する側に、前記成膜基板の前記導電性の表面と等電位である等電位表面を持ち、前記薄膜は、前記成膜基板の前記導電性の表面上に作製されることを特徴とするスパッタリング装置。

【請求項13】

前記等電位表面形成部材は、前記成膜基板の外側における前記等電位表面の面積が、前記成膜基板の前記導電性の表面の面積の40%以上である請求項12に記載のスパッタリング装置。

【請求項14】

前記等電位表面形成部材は、前記成膜基板の外側における前記等電位表面の面積が、前記成膜基板の前記導電性の表面の面積の70%以上である請求項13に記載のスパッタリング装置。

【請求項15】

前記等電位表面形成部材は、前記成膜基板の外側における前記等電位表面の面積が、前記成膜基板の前記導電性の表面の面積の150%以上である請求項14に記載のスパッタリング装置。

【請求項16】

前記成膜基板は、導電性基板である請求項12〜15のいずれかに記載のスパッタリング装置。

【請求項17】

前記成膜基板の前記導電性の表面と、前記等電位表面形成部材の前記等電位表面とは、導通している請求項12〜16のいずれかに記載のスパッタリング装置。

【請求項18】

前記等電位表面形成部材は、前記等電位表面に付着している絶縁膜の厚みが10μm以下の部材である請求項12〜17のいずれかに記載のスパッタリング装置。

【請求項19】

前記等電位表面形成部材は、前記等電位表面に絶縁膜が付着していない部材である請求項12〜18のいずれかに記載のスパッタリング装置。

【請求項20】

前記等電位表面形成部材は、前記等電位表面に付着する絶縁膜の厚みが0または10μm以下である請求項12〜19のいずれかに記載のスパッタリング装置。

【請求項21】

前記膜を作製する成膜材料が、絶縁体である請求項12〜20のいずれかに記載のスパッタリング装置。

【請求項22】

前記膜を作製する成膜材料が、チタン酸鉛もしくはジルコン酸鉛を含む請求項12〜21のいずれかに記載のスパッタリング装置。

【請求項23】

前記等電位表面形成部材は、前記等電位表面が前記成膜基板の前記導電性の表面より前記スパッタ電極に近い側に在るように、設置される請求項12〜22のいずれかに記載のスパッタリング装置。

【請求項1】

少なくとも1面に導電性の表面を有する成膜基板に薄膜を成膜するスパッタリング方法であって、前記成膜基板の外側に、この成膜基板の前記導電性の表面と等電位である等電位表面を持つ等電位表面形成部材を設置して、前記成膜基板の前記導電性の表面上に前記薄膜を作製することを特徴とするスパッタリング方法。

【請求項2】

前記成膜基板の外側において、前記等電位表面形成部材の前記等電位表面の面積が、前記成膜基板の前記導電性の表面の面積の40%以上である請求項1に記載のスパッタリング方法。

【請求項3】

前記成膜基板の外側において、前記等電位表面形成部材の前記等電位表面の面積が、前記成膜基板の前記導電性の表面の面積の70%以上である請求項2に記載のスパッタリング方法。

【請求項4】

前記成膜基板の外側において、前記等電位表面形成部材の前記等電位表面の面積が、前記成膜基板の前記導電性の表面の面積の150%以上である請求項3に記載のスパッタリング方法。

【請求項5】

前記等電位表面形成部材が、前記等電位表面に付着している絶縁膜の厚みが10μm以下の部材である請求項1〜4のいずれかに記載のスパッタリング方法。

【請求項6】

前記等電位表面形成部材は、前記等電位表面に絶縁膜が付着していない部材である請求項1〜4のいずれかに記載のスパッタリング方法。

【請求項7】

前記等電位表面形成部材の前記等電位表面に付着する絶縁膜の厚みが、0または10μm以下である間に、前記成膜基板の前記導電性の表面上に前記膜を作製する請求項1〜6のいずれかに記載のスパッタリング方法。

【請求項8】

前記膜を作製する成膜材料が、絶縁体である請求項1〜7のいずれかに記載のスパッタリング方法。

【請求項9】

前記膜を作製する成膜材料が、チタン酸鉛もしくはジルコン酸鉛を含む請求項1〜8のいずれかに記載のスパッタリング方法。

【請求項10】

前記成膜基板が、導電性基板である請求項1〜9のいずれかに記載のスパッタリング方法。

【請求項11】

前記成膜基板の前記導電性の表面と、前記等電位表面形成部材の前記等電位表面とが、導通している請求項1〜10のいずれかに記載のスパッタリング方法。

【請求項12】

真空容器と、

この真空容器内に設けられ、スパッタリング用のターゲット材を保持するスパッタ電極と、

このスパッタ電極に接続され、前記スパッタ電極に高周波を印加する高周波電源と、

前記真空容器内の、前記スパッタ電極と対向する位置に離間して配置され、前記ターゲット材の成分による薄膜が成膜され、少なくとも1面に導電性の表面を有する成膜基板を保持する基板ホルダと、

前記基板ホルダに保持される前記成膜基板の外側に設置される等電位表面形成部材とを有し、

前記等電位表面形成部材は、前記スパッタ電極と対向する側に、前記成膜基板の前記導電性の表面と等電位である等電位表面を持ち、前記薄膜は、前記成膜基板の前記導電性の表面上に作製されることを特徴とするスパッタリング装置。

【請求項13】

前記等電位表面形成部材は、前記成膜基板の外側における前記等電位表面の面積が、前記成膜基板の前記導電性の表面の面積の40%以上である請求項12に記載のスパッタリング装置。

【請求項14】

前記等電位表面形成部材は、前記成膜基板の外側における前記等電位表面の面積が、前記成膜基板の前記導電性の表面の面積の70%以上である請求項13に記載のスパッタリング装置。

【請求項15】

前記等電位表面形成部材は、前記成膜基板の外側における前記等電位表面の面積が、前記成膜基板の前記導電性の表面の面積の150%以上である請求項14に記載のスパッタリング装置。

【請求項16】

前記成膜基板は、導電性基板である請求項12〜15のいずれかに記載のスパッタリング装置。

【請求項17】

前記成膜基板の前記導電性の表面と、前記等電位表面形成部材の前記等電位表面とは、導通している請求項12〜16のいずれかに記載のスパッタリング装置。

【請求項18】

前記等電位表面形成部材は、前記等電位表面に付着している絶縁膜の厚みが10μm以下の部材である請求項12〜17のいずれかに記載のスパッタリング装置。

【請求項19】

前記等電位表面形成部材は、前記等電位表面に絶縁膜が付着していない部材である請求項12〜18のいずれかに記載のスパッタリング装置。

【請求項20】

前記等電位表面形成部材は、前記等電位表面に付着する絶縁膜の厚みが0または10μm以下である請求項12〜19のいずれかに記載のスパッタリング装置。

【請求項21】

前記膜を作製する成膜材料が、絶縁体である請求項12〜20のいずれかに記載のスパッタリング装置。

【請求項22】

前記膜を作製する成膜材料が、チタン酸鉛もしくはジルコン酸鉛を含む請求項12〜21のいずれかに記載のスパッタリング装置。

【請求項23】

前記等電位表面形成部材は、前記等電位表面が前記成膜基板の前記導電性の表面より前記スパッタ電極に近い側に在るように、設置される請求項12〜22のいずれかに記載のスパッタリング装置。

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【図14】

【図15】

【図16】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【図14】

【図15】

【図16】

【公開番号】特開2009−242927(P2009−242927A)

【公開日】平成21年10月22日(2009.10.22)

【国際特許分類】

【出願番号】特願2008−94002(P2008−94002)

【出願日】平成20年3月31日(2008.3.31)

【公序良俗違反の表示】

(特許庁注:以下のものは登録商標)

1.FRAM

【出願人】(306037311)富士フイルム株式会社 (25,513)

【Fターム(参考)】

【公開日】平成21年10月22日(2009.10.22)

【国際特許分類】

【出願日】平成20年3月31日(2008.3.31)

【公序良俗違反の表示】

(特許庁注:以下のものは登録商標)

1.FRAM

【出願人】(306037311)富士フイルム株式会社 (25,513)

【Fターム(参考)】

[ Back to top ]