スパッタリング装置および半導体装置製造方法

【課題】半導体装置基板のスパッタリングプロセスで特に周辺部に付着するパーティクルを抑制できるスパッタリング装置および半導体装置製造方法を提供する。

【解決手段】スパッタリング装置は、真空処理室1内に、ステージ2と、ターゲット4と、デポリング8と、カバーリング7とを備える。またプラズマ発生手段と、ステージ2に静電チャック作用を発生させる直流電源3と、ターゲット4のコンディショニング時にステージ2全体をプラズマから遮蔽して保護するシャッターディスク9と、クリーニング時にステージ2の基板設置面のみを覆ってプラズマから保護する保護ディスク12とを備える。保護ディスク12が上記サイズであることにより、ステージ2の側壁とデポリング8との間の余剰な成膜物も除去が可能となる。

【解決手段】スパッタリング装置は、真空処理室1内に、ステージ2と、ターゲット4と、デポリング8と、カバーリング7とを備える。またプラズマ発生手段と、ステージ2に静電チャック作用を発生させる直流電源3と、ターゲット4のコンディショニング時にステージ2全体をプラズマから遮蔽して保護するシャッターディスク9と、クリーニング時にステージ2の基板設置面のみを覆ってプラズマから保護する保護ディスク12とを備える。保護ディスク12が上記サイズであることにより、ステージ2の側壁とデポリング8との間の余剰な成膜物も除去が可能となる。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、半導体装置基板に金属膜を堆積させるスパッタリング装置および半導体装置製造方法に関する。

【背景技術】

【0002】

半導体装置を製造するスパッタリングプロセスでは、超高真空状態に保たれた真空室にて、半導体装置基板(以下、単に基板ともいう)をステージに載せ、この基板に対向する形で金属ターゲットを設置し、Arのような不活性ガスを供給しながら、基板と金属ターゲット間で、直流もしくは高周波プラズマ放電させることで、金属ターゲットのスパッタリングを行い、基板上に金属膜を堆積させる。

【0003】

近年、半導体装置の微細化に伴い、スパッタリング処理を施す基板の表面形状も、段差の大きい(アスペクト比の高い)形状となってきており、かかる表面への均一な膜の堆積が求められている。この要求に対し、ステージ側でも高周波を印加して、基板近傍に垂直な電界を形成することで、金属ターゲットからスパッタリングされた金属イオン成分を、半導体装置基板に引き込む技術が主流となっている。

【0004】

基板をステージに固定するためには、従来は基板周辺を物理的にステージに押さえる保持具(クランプ)を用いていたが、近年は、基板に造り込んだ半導体装置の取れ数を出来るだけ多くするために、クランプを用いずに静電気によって基板の裏面を吸着する静電チャック方式を用いることが主流である。

【0005】

一般的なスパッタリング装置の構成を図4に示す。真空処理室1に、静電チャック機能を備えたステージ2とターゲット4とを備えている。ステージ2には高周波バイアスが印加可能としている。またターゲット4からのスパッタ膜が真空処理室1に付着しないよう保護するためのカバーリング7およびデポリング8を備えている。

【0006】

さらに、ターゲット4表面の変質層のスパッタリング除去を前処理として行う際にステージ2表面を保護するシャッターディスク9を備えている。このシャッターディスク9は水平方向に駆動可能であり、ステージ2の上下動と連動してステージ2表面上に基板同様な搭載が可能である。場合によっては、段差被覆性を向上するためにプラズマ密度を制御するRF・DC印加が可能なコイル10が備えられる。

【0007】

真空処理室1内には、上述のカバーリング7およびデポリング8を備えていても基板周辺に金属材料からなる膜が堆積することになるが、成膜処理を重ねる事で膜が剥がれてパーティクル源となることから、処理後の半導体装置基板11を真空処理室1から搬出した後に、真空処理室1内に余剰に堆積した膜を除去する手法が提案されている。たとえば特許文献1に、静電チャック面を保護するためにダミー基板を載せて膜を除去する手法が提案されている。

【先行技術文献】

【特許文献】

【0008】

【特許文献1】特開2000−212724公報

【発明の概要】

【発明が解決しようとする課題】

【0009】

近年の半導体装置の微細化に伴い、処理中に半導体装置基板に付着するパーティクルサイズについても、より微細なパーティクルの抑制が求められている。上述した従来のスパッタリングプロセスにおいても、基板周辺に微細なパーティクルが発生しており、これが半導体装置の出来栄えに影響し、歩留まり低下の要因となっている。

【0010】

本発明は、上記問題に鑑み、半導体装置基板のスパッタリングプロセスにおいて特に周辺部に付着するパーティクルを抑制できるスパッタリング装置および半導体装置製造方法を提供することを目的とする。

【課題を解決するための手段】

【0011】

上記課題を解決するために、本発明のスパッタリング装置は、真空処理室内に、半導体装置基板を保持する静電チャック機能を備えるステージと、前記ステージと対向に設置された金属ターゲットと、前記ステージの側壁に沿って設置された第1のカバーリングと、前記第1のカバーリングと前記真空処理室の内面との隙間を覆う第2のカバーリングとを備えるとともに、前記ステージと前記金属ターゲットとの間にプラズマを発生させるプラズマ発生手段と、前記ステージに静電チャック作用を発生させるための直流電源と、前記金属ターゲットのコンディショニング時に前記ステージ全体をプラズマから遮蔽して保護するシャッターディスクと、前記真空処理室内のクリーニング時に前記ステージの基板設置面のみを覆ってプラズマから保護する保護ディスクとを備えたことを特徴とする。

【0012】

本発明者らが、基板周辺のパーティクルについて発生原因を調べたところ、ステージ側壁に膜残りが認められ、これが成膜処理を繰り返すことで膜剥がれを起こし、パーティクル源になっていることがわかった。これは従来、処理室内の余剰な膜を除去する過程で、ステージ表面(静電チャック面)を保護する目的で用いるダミー基板が半導体装置基板と同一サイズであることに起因している。

【0013】

一般的にステージは、成膜処理時に膜が付着しないように半導体装置基板よりも小さいサイズにて設計している。このため、半導体装置基板と同一サイズのダミー基板を用いると、ステージの側壁はダミー基板の影となり、プラズマの回り込みが弱く、膜除去が困難な状況になり、膜が残ってしまう。これが徐々に堆積していくことで膜はがれとなり、パーティクル源になっていると推測される。

【0014】

上記の本発明のスパッタリング装置では、真空処理室内のクリーニング時に用いる保護ディスク(従来のダミー基板に相当する)を、ステージの基板設置面(静電チャック面)のみを覆うサイズとしたことにより、ステージの側壁、つまり第1のカバーリングとの境界部分が保護ディスクの影となることを回避することができ、この部分を十分にプラズマに晒して、付着物を効果的に除去することが可能となる。よって、付着物が堆積してなる膜のはがれ、それにより半導体装置基板の周辺に発生する微細なパーティクルの抑制が可能になる。

【0015】

前記真空処理室に、前記シャッターディスクおよび保護ディスクを互いに上下に格納する格納部と、前記シャッターディスクおよび保護ディスクを前記ステージに対して搬送する機構とを有することが好ましい。

【0016】

前記保護ディスクは不導体材料で形成されていることを特徴とする。不導体材料とは、プラズマに晒されてもパーティクル源や汚染源になりにくいセラミック等の不導体材料を言う。

【0017】

本発明の半導体装置製造方法は、上記のスパッタリング装置を用いて、半導体装置基板に金属膜を堆積させることを特徴とする。具体的には、半導体装置基板に対し所定の成膜処理を施す成膜処理工程間で、保護ディスクをステージ上に設置し、真空処理室内のクリーニングを行う。

【発明の効果】

【0018】

本発明のスパッタリング装置によれば、保護ディスクでステージの基板設置面のみを保護した状態で真空処理室内のクリーニングを行うことにより、ステージの側壁を十分にプラズマに晒して、付着物を効果的に除去することが可能となる。

【0019】

これにより、付着物が堆積してなる膜の形成、膜はがれ、半導体装置基板の周辺に発生する微細なパーティクルの抑制が可能になるほか、半導体装置基板の成膜時に静電チャック不良による温度制御の不具合が発生することや、絶縁破壊の原因となる異常放電の発生を抑制することができる。よって、このスパッタリング装置を用いて半導体装置基板に堆積させる金属膜を安定に成膜できる。

【図面の簡単な説明】

【0020】

【図1】本発明の一実施形態におけるスパッタリング装置の構成図

【図2】図1のスパッタリング装置における処理フローを示す図

【図3】図2の処理フローにおけるスパッタリング装置およびその一部を示す図

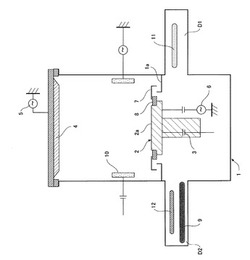

【図4】従来のスパッタリング装置の構成図

【発明を実施するための形態】

【0021】

以下、本発明の実施の形態について、図面を用いて説明する。

図1に示すスパッタリング装置において、1は真空処理室、2は静電チャック機能を発揮するステージ、3はステージ2に静電チャックを発生させるための直流電源、4はターゲット、5はターゲット4に印加する高周波電源、6はステージ2にバイアスを印加する高周波電源である。7はカバーリング、8はデポリング、9はシャッターディスク、10はコイル、11は半導体装置基板、12は保護ディスクである。

【0022】

以下、詳細に説明する。真空処理室1内には、ステージ2と、このステージ2と対向するターゲット4と備えている。ターゲット4は、半導体装置基板11に堆積させる堆積物、例えば配線材となるCo、Ni、Al、Cuを表面に予め堆積している。

【0023】

ステージ2は、上下方向に移動自在に構成されており、バイアス印加できる高周波電源6(あるいは直流電源)と、ステージ2に静電チャックを発生させるための直流電源3とを備えている。ステージ2は、基板設置部2aが他の部分よりも小径をなす段差形状をしている。特許請求の範囲に記載したステージ2はここでは基板設置部2aに該当する。基板設置部2aの直径は処理対象の半導体装置基板11の直径よりもやや小さい。

【0024】

ステージ2の周囲には、ターゲット4からの金属材料が真空処理室1の内壁等の目的外の部分に付着しないように保護するためのカバーリング7およびデポリング8を備えている。デポリング8は、ステージ2の基板設置部2aの側壁に沿うように段差部に取り付けられている。カバーリング7はデポリング3の周辺部を覆って取り付けられており、真空処理室1の内面に周方向に沿って形成されたリング状の凸部1aに係合してデポリング8・凸部1a間の隙間を覆い得る。

【0025】

半導体装置基板11は、水平方向に駆動可能であって(搬送機構は図示せず)、ステージ2の上下動と連動してステージ2の表面上に搭載が可能であるとともに、格納部D1を介して装置外との間で搬入搬出されるようになっている。

【0026】

シャッターディスク9は、ターゲット4表面の変質層のスパッタリング除去を前処理として行う際にステージ2の表面を保護するために用いるものであって、通常は格納部D2に格納されているが、水平方向に駆動可能であり(搬送機構は図示せず)、ステージ2の上下動と連動してステージ2の表面上に半導体装置基板11と同様に搭載が可能である。シャッターディスク9の直径は、半導体装置基板11の直径と同じ、あるいは、カバーリング7の内径と同じとされる。シャッターディスク9の材料には、一般的には、真空処理室と同じアルミニウムを用いる。

【0027】

格納部D2には、真空処理室1のクリーニング時にステージ2の表面を保護するために用いる専用の保護ディスク12も格納されており、この保護ディスク12もシャッターディスク9と同様に水平方向に駆動可能である。従来のダミー基板と同じ役割を担う専用の保護ディスク12を装置内に保有させ、併せてこの保護ディスク12のための搬送機構を備えたものである。

【0028】

図示したように、格納部D2は、シャッターディスク9と保護ディスク12とを二段にして格納するように構成されており、これにより装置設置面積の縮小化が図られている。

搬送機構としては、シャッターディスク9もしくは保護ディスク12を、格納部D2から引き出しもしくは格納するために、上下駆動、回転機構、水平方向への伸縮機構を備えた搬送ロボットを備える。ステージ2も、上下駆動の機構を備え、前記搬送ロボットにより搬送もしくは搬出がなされるシャッターディスク9もしくは保護ディスク12を受け渡し可能な位置まで下降する。保護ディスク12のサイズ等については後述する。

【0029】

その他、ターゲット4に印加する高周波電源5(あるいは直流電源)、段差被覆性を向上するためにプラズマ密度を制御する高周波あるいは直流印加が可能なコイル10を備えている。

【0030】

上記のスパッタリング装置の動作を図2を用いて説明する。

図2(a)に示すように、基板処理に先立つ前処理を行うべく、ステージ2を一旦下げて、シャッターディスク9をステージ2の上方に搬送し、ステージ2を上昇させて、シャッターディスク9をステージ2表面に設置する。

【0031】

次に、図2(b)に示すように、真空度、Ar流量、ターゲット4の電力値を所定の条件に調整して、プラズマPを発生させ、シャッターディスク9に対してスパッタリングを行うことで、ターゲット4表面の変質層を除去する。

【0032】

スパッタリング終了後、図2(c)に示すように、ステージ2の位置を下げ、シャッターディスク9を格納部に格納する。一方で半導体装置基板11を格納部に搬入する。

その後、図2(d)に示すように、半導体装置基板11をステージ2の上方に搬送し、ステージ2を上昇させて、半導体装置基板11をステージ2表面に設置する。そして、ステージ2に所定の電圧を印加して半導体装置基板11を静電チャックによりステージ2に固定する。この固定は半導体装置基板11の温度を安定に制御するためである。

【0033】

次に、真空度、Ar流量、ターゲット4の電流値、バイアス電力、コイル電流を所定の条件に調整して、プラズマPを発生させ、スパッタリングすることで、半導体装置基板11にターゲット4の金属材料を堆積する成膜処理を行う。

【0034】

成膜処理の終了後、図2(e)に示すように、真空処理室1内を一旦排気し、半導体装置基板11を格納部D1を通じて搬出搬入する。

その後、図2(d)、図2(e)に示す動作を繰り返して、複数枚の半導体装置基板11を処理していく。

【0035】

一定枚数の半導体装置基板11の処理の終了後、図2(f)に示すように、保護ディスク12をシャッターディスク9と同様にしてステージ2表面に搬送、設置する。その後、Arのような不活性ガスを導入し、真空度を調整した後、高周波電源6(図1参照)より所定の電力を印加してステージ2近傍にプラズマPを発生させる。この時、ターゲット4には電力を印加しない。

【0036】

この図2(f)に示す処理は、上記のように複数枚の成膜処理が終了する毎に行ってもよいし、1枚毎、あるいはロット終了毎でもよく、任意に選択が可能である。図2(f)に示す処理の後は図2(d)、図2(e)に示す動作に戻る。

【0037】

図3(a)は図2(d)と同じ段階のスパッタリング装置を示し、図3(b)は同装置におけるステージ2の外周部を拡大して示している。

半導体装置基板11の処理を継続する間に、カバーリング7とデポリング8の各上面、および、デポリング8とステージ2との隙間に、スパッタリングに伴う堆積膜13が付着する。

【0038】

この堆積物13の付着、蓄積は、処理を繰り返すほど多くなり、ある程度多くなると半導体装置基板11とステージ2との間に入り込み、静電チャックできなくなる。半導体装置基板11がステージ2から浮き上がるほどに堆積物13が蓄積する前であっても、スパッタ粒子が反射などにより半導体装置基板11とステージとの間に回りこみやすくなり、静電吸着力が弱まり、静電チャックできなくなる。このように静電チャックできなくなることが、温度制御の不具合、あるいは、被堆積物13が剥がれてパーティクル溌塵の要因になることがある。

【0039】

加えて、ステージ2とカバーリング7との絶縁の役割を果たすデポリング8の表面に、金属材料からなる堆積膜13が継続的に形成されることにより、絶縁破壊の原因となり、異常放電が発生するトラブルも発生する。

【0040】

図3(c)は図2(f)と同じ段階のスパッタリング装置を示し、図3(d)は同装置におけるステージ2の外周部を拡大して示している。

この段階のプラズマ処理は、上述のように、保護ディスク12をステージ2表面に設置した後、Ar(あるいはHe)のような不活性ガス雰囲気において、ステージ2に印加する高周波電源6を用いてプラズマ放電をたてるというものである。

【0041】

保護ディスク12を設置するのは、ステージ2の表面がプラズマに晒されないようにカバーするためである。ステージ2表面は静電チャックできるように絶縁膜で覆われているのであるが、この絶縁膜がプラズマによりピンホール発生などのダメージを受けることがあり、通常のスパッタリング処理時、つまりステージ2上に半導体装置基板11を設置してのスパッタリング処理時にこの部分から電子が流れ込むと、半導体装置基板11を正常に静電チャックしなくなるため、ステージ2表面のダメージを防ぐためにカバーしている。

【0042】

保護ディスク12のサイズは、ステージ2における直接接触する部分、つまり、基板設置部2aの表面の直径と同一としている。これにより、ステージ1の基板設置部2aの側壁は保護ディスク12でカバーされることなく、集中してプラズマに晒されることになり、図示するように、ステージ2とデポリング8との間の隙間に堆積した堆積物13も十分にスパッタリング除去することができる。

【0043】

保護ディスク12は、アルミナやイットリアのような不導体材料を用いるのが好ましい。従来のダミー基板のようなSi基板を用いると、プラズマによりSi表面がスパッタリングされ、新たなパーティクルの発生源となるおそれがあるためである。

【0044】

また保護ディスク12はメンテナンス時に洗浄するのが好ましい。さらに、保護ディスク12は、図1に示した格納部D2において上段に格納するのが好ましい。パーティクル等による影響を小さくできるからである。シャッターディスク9との間に仕切り板等を設置すれば上下どちらに設置しても構わない。

【0045】

以上説明したように、本発明のスパッタリング装置によれば、半導体装置基板11の処理を繰り返す間にステージ2の側壁に付着し堆積した不要な膜を十分に除去することができ、静電チャック不良による温度制御の不具合、パーティクル発生を抑えることが可能であり、かつ、絶縁破壊の原因となり異常放電が発生するトラブルも解消できる。

【0046】

このため、本発明のスパッタリング装置において、半導体装置基板に所定の膜を堆積する処理工程間で、保護ディスクをステージ上に設置して真空処理室内のクリーニングを行うことにより;より詳細には、上述のように、シャッターディスクでステージをプラズマから保護しながら金属ターゲットをコンディショニングする工程と、ステージ上に設置した半導体装置基板に前記金属ターゲットからの金属を堆積する工程と、保護ディスクでステージをプラズマから保護しながら真空処理室内をクリーニングする工程とを行うことにより、半導体装置基板に配線となるCo、Ni、Al、Cu等の金属を安定に堆積して、半導体装置を製造することができる。

【産業上の利用可能性】

【0047】

本発明にかかるスパッタリング装置および半導体装置製造方法は、パーティクル改善等に有効であるため、半導体装置基板を静電チャックするステージの側壁に成膜材料が堆積するような半導体製造設備で有用である。

【符号の説明】

【0048】

1 真空処理室

2 ステージ

3 直流電源

4 ターゲット

7 カバーリング

8 デポリング

9 シャッターディスク

11 半導体装置基板

12 保護ディスク

【技術分野】

【0001】

本発明は、半導体装置基板に金属膜を堆積させるスパッタリング装置および半導体装置製造方法に関する。

【背景技術】

【0002】

半導体装置を製造するスパッタリングプロセスでは、超高真空状態に保たれた真空室にて、半導体装置基板(以下、単に基板ともいう)をステージに載せ、この基板に対向する形で金属ターゲットを設置し、Arのような不活性ガスを供給しながら、基板と金属ターゲット間で、直流もしくは高周波プラズマ放電させることで、金属ターゲットのスパッタリングを行い、基板上に金属膜を堆積させる。

【0003】

近年、半導体装置の微細化に伴い、スパッタリング処理を施す基板の表面形状も、段差の大きい(アスペクト比の高い)形状となってきており、かかる表面への均一な膜の堆積が求められている。この要求に対し、ステージ側でも高周波を印加して、基板近傍に垂直な電界を形成することで、金属ターゲットからスパッタリングされた金属イオン成分を、半導体装置基板に引き込む技術が主流となっている。

【0004】

基板をステージに固定するためには、従来は基板周辺を物理的にステージに押さえる保持具(クランプ)を用いていたが、近年は、基板に造り込んだ半導体装置の取れ数を出来るだけ多くするために、クランプを用いずに静電気によって基板の裏面を吸着する静電チャック方式を用いることが主流である。

【0005】

一般的なスパッタリング装置の構成を図4に示す。真空処理室1に、静電チャック機能を備えたステージ2とターゲット4とを備えている。ステージ2には高周波バイアスが印加可能としている。またターゲット4からのスパッタ膜が真空処理室1に付着しないよう保護するためのカバーリング7およびデポリング8を備えている。

【0006】

さらに、ターゲット4表面の変質層のスパッタリング除去を前処理として行う際にステージ2表面を保護するシャッターディスク9を備えている。このシャッターディスク9は水平方向に駆動可能であり、ステージ2の上下動と連動してステージ2表面上に基板同様な搭載が可能である。場合によっては、段差被覆性を向上するためにプラズマ密度を制御するRF・DC印加が可能なコイル10が備えられる。

【0007】

真空処理室1内には、上述のカバーリング7およびデポリング8を備えていても基板周辺に金属材料からなる膜が堆積することになるが、成膜処理を重ねる事で膜が剥がれてパーティクル源となることから、処理後の半導体装置基板11を真空処理室1から搬出した後に、真空処理室1内に余剰に堆積した膜を除去する手法が提案されている。たとえば特許文献1に、静電チャック面を保護するためにダミー基板を載せて膜を除去する手法が提案されている。

【先行技術文献】

【特許文献】

【0008】

【特許文献1】特開2000−212724公報

【発明の概要】

【発明が解決しようとする課題】

【0009】

近年の半導体装置の微細化に伴い、処理中に半導体装置基板に付着するパーティクルサイズについても、より微細なパーティクルの抑制が求められている。上述した従来のスパッタリングプロセスにおいても、基板周辺に微細なパーティクルが発生しており、これが半導体装置の出来栄えに影響し、歩留まり低下の要因となっている。

【0010】

本発明は、上記問題に鑑み、半導体装置基板のスパッタリングプロセスにおいて特に周辺部に付着するパーティクルを抑制できるスパッタリング装置および半導体装置製造方法を提供することを目的とする。

【課題を解決するための手段】

【0011】

上記課題を解決するために、本発明のスパッタリング装置は、真空処理室内に、半導体装置基板を保持する静電チャック機能を備えるステージと、前記ステージと対向に設置された金属ターゲットと、前記ステージの側壁に沿って設置された第1のカバーリングと、前記第1のカバーリングと前記真空処理室の内面との隙間を覆う第2のカバーリングとを備えるとともに、前記ステージと前記金属ターゲットとの間にプラズマを発生させるプラズマ発生手段と、前記ステージに静電チャック作用を発生させるための直流電源と、前記金属ターゲットのコンディショニング時に前記ステージ全体をプラズマから遮蔽して保護するシャッターディスクと、前記真空処理室内のクリーニング時に前記ステージの基板設置面のみを覆ってプラズマから保護する保護ディスクとを備えたことを特徴とする。

【0012】

本発明者らが、基板周辺のパーティクルについて発生原因を調べたところ、ステージ側壁に膜残りが認められ、これが成膜処理を繰り返すことで膜剥がれを起こし、パーティクル源になっていることがわかった。これは従来、処理室内の余剰な膜を除去する過程で、ステージ表面(静電チャック面)を保護する目的で用いるダミー基板が半導体装置基板と同一サイズであることに起因している。

【0013】

一般的にステージは、成膜処理時に膜が付着しないように半導体装置基板よりも小さいサイズにて設計している。このため、半導体装置基板と同一サイズのダミー基板を用いると、ステージの側壁はダミー基板の影となり、プラズマの回り込みが弱く、膜除去が困難な状況になり、膜が残ってしまう。これが徐々に堆積していくことで膜はがれとなり、パーティクル源になっていると推測される。

【0014】

上記の本発明のスパッタリング装置では、真空処理室内のクリーニング時に用いる保護ディスク(従来のダミー基板に相当する)を、ステージの基板設置面(静電チャック面)のみを覆うサイズとしたことにより、ステージの側壁、つまり第1のカバーリングとの境界部分が保護ディスクの影となることを回避することができ、この部分を十分にプラズマに晒して、付着物を効果的に除去することが可能となる。よって、付着物が堆積してなる膜のはがれ、それにより半導体装置基板の周辺に発生する微細なパーティクルの抑制が可能になる。

【0015】

前記真空処理室に、前記シャッターディスクおよび保護ディスクを互いに上下に格納する格納部と、前記シャッターディスクおよび保護ディスクを前記ステージに対して搬送する機構とを有することが好ましい。

【0016】

前記保護ディスクは不導体材料で形成されていることを特徴とする。不導体材料とは、プラズマに晒されてもパーティクル源や汚染源になりにくいセラミック等の不導体材料を言う。

【0017】

本発明の半導体装置製造方法は、上記のスパッタリング装置を用いて、半導体装置基板に金属膜を堆積させることを特徴とする。具体的には、半導体装置基板に対し所定の成膜処理を施す成膜処理工程間で、保護ディスクをステージ上に設置し、真空処理室内のクリーニングを行う。

【発明の効果】

【0018】

本発明のスパッタリング装置によれば、保護ディスクでステージの基板設置面のみを保護した状態で真空処理室内のクリーニングを行うことにより、ステージの側壁を十分にプラズマに晒して、付着物を効果的に除去することが可能となる。

【0019】

これにより、付着物が堆積してなる膜の形成、膜はがれ、半導体装置基板の周辺に発生する微細なパーティクルの抑制が可能になるほか、半導体装置基板の成膜時に静電チャック不良による温度制御の不具合が発生することや、絶縁破壊の原因となる異常放電の発生を抑制することができる。よって、このスパッタリング装置を用いて半導体装置基板に堆積させる金属膜を安定に成膜できる。

【図面の簡単な説明】

【0020】

【図1】本発明の一実施形態におけるスパッタリング装置の構成図

【図2】図1のスパッタリング装置における処理フローを示す図

【図3】図2の処理フローにおけるスパッタリング装置およびその一部を示す図

【図4】従来のスパッタリング装置の構成図

【発明を実施するための形態】

【0021】

以下、本発明の実施の形態について、図面を用いて説明する。

図1に示すスパッタリング装置において、1は真空処理室、2は静電チャック機能を発揮するステージ、3はステージ2に静電チャックを発生させるための直流電源、4はターゲット、5はターゲット4に印加する高周波電源、6はステージ2にバイアスを印加する高周波電源である。7はカバーリング、8はデポリング、9はシャッターディスク、10はコイル、11は半導体装置基板、12は保護ディスクである。

【0022】

以下、詳細に説明する。真空処理室1内には、ステージ2と、このステージ2と対向するターゲット4と備えている。ターゲット4は、半導体装置基板11に堆積させる堆積物、例えば配線材となるCo、Ni、Al、Cuを表面に予め堆積している。

【0023】

ステージ2は、上下方向に移動自在に構成されており、バイアス印加できる高周波電源6(あるいは直流電源)と、ステージ2に静電チャックを発生させるための直流電源3とを備えている。ステージ2は、基板設置部2aが他の部分よりも小径をなす段差形状をしている。特許請求の範囲に記載したステージ2はここでは基板設置部2aに該当する。基板設置部2aの直径は処理対象の半導体装置基板11の直径よりもやや小さい。

【0024】

ステージ2の周囲には、ターゲット4からの金属材料が真空処理室1の内壁等の目的外の部分に付着しないように保護するためのカバーリング7およびデポリング8を備えている。デポリング8は、ステージ2の基板設置部2aの側壁に沿うように段差部に取り付けられている。カバーリング7はデポリング3の周辺部を覆って取り付けられており、真空処理室1の内面に周方向に沿って形成されたリング状の凸部1aに係合してデポリング8・凸部1a間の隙間を覆い得る。

【0025】

半導体装置基板11は、水平方向に駆動可能であって(搬送機構は図示せず)、ステージ2の上下動と連動してステージ2の表面上に搭載が可能であるとともに、格納部D1を介して装置外との間で搬入搬出されるようになっている。

【0026】

シャッターディスク9は、ターゲット4表面の変質層のスパッタリング除去を前処理として行う際にステージ2の表面を保護するために用いるものであって、通常は格納部D2に格納されているが、水平方向に駆動可能であり(搬送機構は図示せず)、ステージ2の上下動と連動してステージ2の表面上に半導体装置基板11と同様に搭載が可能である。シャッターディスク9の直径は、半導体装置基板11の直径と同じ、あるいは、カバーリング7の内径と同じとされる。シャッターディスク9の材料には、一般的には、真空処理室と同じアルミニウムを用いる。

【0027】

格納部D2には、真空処理室1のクリーニング時にステージ2の表面を保護するために用いる専用の保護ディスク12も格納されており、この保護ディスク12もシャッターディスク9と同様に水平方向に駆動可能である。従来のダミー基板と同じ役割を担う専用の保護ディスク12を装置内に保有させ、併せてこの保護ディスク12のための搬送機構を備えたものである。

【0028】

図示したように、格納部D2は、シャッターディスク9と保護ディスク12とを二段にして格納するように構成されており、これにより装置設置面積の縮小化が図られている。

搬送機構としては、シャッターディスク9もしくは保護ディスク12を、格納部D2から引き出しもしくは格納するために、上下駆動、回転機構、水平方向への伸縮機構を備えた搬送ロボットを備える。ステージ2も、上下駆動の機構を備え、前記搬送ロボットにより搬送もしくは搬出がなされるシャッターディスク9もしくは保護ディスク12を受け渡し可能な位置まで下降する。保護ディスク12のサイズ等については後述する。

【0029】

その他、ターゲット4に印加する高周波電源5(あるいは直流電源)、段差被覆性を向上するためにプラズマ密度を制御する高周波あるいは直流印加が可能なコイル10を備えている。

【0030】

上記のスパッタリング装置の動作を図2を用いて説明する。

図2(a)に示すように、基板処理に先立つ前処理を行うべく、ステージ2を一旦下げて、シャッターディスク9をステージ2の上方に搬送し、ステージ2を上昇させて、シャッターディスク9をステージ2表面に設置する。

【0031】

次に、図2(b)に示すように、真空度、Ar流量、ターゲット4の電力値を所定の条件に調整して、プラズマPを発生させ、シャッターディスク9に対してスパッタリングを行うことで、ターゲット4表面の変質層を除去する。

【0032】

スパッタリング終了後、図2(c)に示すように、ステージ2の位置を下げ、シャッターディスク9を格納部に格納する。一方で半導体装置基板11を格納部に搬入する。

その後、図2(d)に示すように、半導体装置基板11をステージ2の上方に搬送し、ステージ2を上昇させて、半導体装置基板11をステージ2表面に設置する。そして、ステージ2に所定の電圧を印加して半導体装置基板11を静電チャックによりステージ2に固定する。この固定は半導体装置基板11の温度を安定に制御するためである。

【0033】

次に、真空度、Ar流量、ターゲット4の電流値、バイアス電力、コイル電流を所定の条件に調整して、プラズマPを発生させ、スパッタリングすることで、半導体装置基板11にターゲット4の金属材料を堆積する成膜処理を行う。

【0034】

成膜処理の終了後、図2(e)に示すように、真空処理室1内を一旦排気し、半導体装置基板11を格納部D1を通じて搬出搬入する。

その後、図2(d)、図2(e)に示す動作を繰り返して、複数枚の半導体装置基板11を処理していく。

【0035】

一定枚数の半導体装置基板11の処理の終了後、図2(f)に示すように、保護ディスク12をシャッターディスク9と同様にしてステージ2表面に搬送、設置する。その後、Arのような不活性ガスを導入し、真空度を調整した後、高周波電源6(図1参照)より所定の電力を印加してステージ2近傍にプラズマPを発生させる。この時、ターゲット4には電力を印加しない。

【0036】

この図2(f)に示す処理は、上記のように複数枚の成膜処理が終了する毎に行ってもよいし、1枚毎、あるいはロット終了毎でもよく、任意に選択が可能である。図2(f)に示す処理の後は図2(d)、図2(e)に示す動作に戻る。

【0037】

図3(a)は図2(d)と同じ段階のスパッタリング装置を示し、図3(b)は同装置におけるステージ2の外周部を拡大して示している。

半導体装置基板11の処理を継続する間に、カバーリング7とデポリング8の各上面、および、デポリング8とステージ2との隙間に、スパッタリングに伴う堆積膜13が付着する。

【0038】

この堆積物13の付着、蓄積は、処理を繰り返すほど多くなり、ある程度多くなると半導体装置基板11とステージ2との間に入り込み、静電チャックできなくなる。半導体装置基板11がステージ2から浮き上がるほどに堆積物13が蓄積する前であっても、スパッタ粒子が反射などにより半導体装置基板11とステージとの間に回りこみやすくなり、静電吸着力が弱まり、静電チャックできなくなる。このように静電チャックできなくなることが、温度制御の不具合、あるいは、被堆積物13が剥がれてパーティクル溌塵の要因になることがある。

【0039】

加えて、ステージ2とカバーリング7との絶縁の役割を果たすデポリング8の表面に、金属材料からなる堆積膜13が継続的に形成されることにより、絶縁破壊の原因となり、異常放電が発生するトラブルも発生する。

【0040】

図3(c)は図2(f)と同じ段階のスパッタリング装置を示し、図3(d)は同装置におけるステージ2の外周部を拡大して示している。

この段階のプラズマ処理は、上述のように、保護ディスク12をステージ2表面に設置した後、Ar(あるいはHe)のような不活性ガス雰囲気において、ステージ2に印加する高周波電源6を用いてプラズマ放電をたてるというものである。

【0041】

保護ディスク12を設置するのは、ステージ2の表面がプラズマに晒されないようにカバーするためである。ステージ2表面は静電チャックできるように絶縁膜で覆われているのであるが、この絶縁膜がプラズマによりピンホール発生などのダメージを受けることがあり、通常のスパッタリング処理時、つまりステージ2上に半導体装置基板11を設置してのスパッタリング処理時にこの部分から電子が流れ込むと、半導体装置基板11を正常に静電チャックしなくなるため、ステージ2表面のダメージを防ぐためにカバーしている。

【0042】

保護ディスク12のサイズは、ステージ2における直接接触する部分、つまり、基板設置部2aの表面の直径と同一としている。これにより、ステージ1の基板設置部2aの側壁は保護ディスク12でカバーされることなく、集中してプラズマに晒されることになり、図示するように、ステージ2とデポリング8との間の隙間に堆積した堆積物13も十分にスパッタリング除去することができる。

【0043】

保護ディスク12は、アルミナやイットリアのような不導体材料を用いるのが好ましい。従来のダミー基板のようなSi基板を用いると、プラズマによりSi表面がスパッタリングされ、新たなパーティクルの発生源となるおそれがあるためである。

【0044】

また保護ディスク12はメンテナンス時に洗浄するのが好ましい。さらに、保護ディスク12は、図1に示した格納部D2において上段に格納するのが好ましい。パーティクル等による影響を小さくできるからである。シャッターディスク9との間に仕切り板等を設置すれば上下どちらに設置しても構わない。

【0045】

以上説明したように、本発明のスパッタリング装置によれば、半導体装置基板11の処理を繰り返す間にステージ2の側壁に付着し堆積した不要な膜を十分に除去することができ、静電チャック不良による温度制御の不具合、パーティクル発生を抑えることが可能であり、かつ、絶縁破壊の原因となり異常放電が発生するトラブルも解消できる。

【0046】

このため、本発明のスパッタリング装置において、半導体装置基板に所定の膜を堆積する処理工程間で、保護ディスクをステージ上に設置して真空処理室内のクリーニングを行うことにより;より詳細には、上述のように、シャッターディスクでステージをプラズマから保護しながら金属ターゲットをコンディショニングする工程と、ステージ上に設置した半導体装置基板に前記金属ターゲットからの金属を堆積する工程と、保護ディスクでステージをプラズマから保護しながら真空処理室内をクリーニングする工程とを行うことにより、半導体装置基板に配線となるCo、Ni、Al、Cu等の金属を安定に堆積して、半導体装置を製造することができる。

【産業上の利用可能性】

【0047】

本発明にかかるスパッタリング装置および半導体装置製造方法は、パーティクル改善等に有効であるため、半導体装置基板を静電チャックするステージの側壁に成膜材料が堆積するような半導体製造設備で有用である。

【符号の説明】

【0048】

1 真空処理室

2 ステージ

3 直流電源

4 ターゲット

7 カバーリング

8 デポリング

9 シャッターディスク

11 半導体装置基板

12 保護ディスク

【特許請求の範囲】

【請求項1】

真空処理室内に、

半導体装置基板を保持する静電チャック機能を備えるステージと、

前記ステージと対向に設置された金属ターゲットと、

前記ステージの側壁に沿って設置された第1のカバーリングと、

前記第1のカバーリングと前記真空処理室の内面との隙間を覆う第2のカバーリングとを備えるとともに、

前記ステージと前記金属ターゲットとの間にプラズマを発生させるプラズマ発生手段と、

前記ステージに静電チャック作用を発生させるための直流電源と、

前記金属ターゲットのコンディショニング時に前記ステージ全体をプラズマから遮蔽して保護するシャッターディスクと、

前記真空処理室内のクリーニング時に前記ステージの基板設置面のみを覆ってプラズマから保護する保護ディスクと

を備えたことを特徴とするスパッタリング装置。

【請求項2】

前記真空処理室に、前記シャッターディスクおよび保護ディスクを互いに上下に格納する格納部と、前記シャッターディスクおよび保護ディスクを前記ステージに対して搬送する機構とを有することを特徴とする請求項1に記載のスパッタリング装置。

【請求項3】

前記保護ディスクは不導体材料で形成されていることを特徴とする請求項1に記載のスパッタリング装置。

【請求項4】

請求項1記載のスパッタリング装置を用いて、半導体装置基板に金属膜を堆積させる

ことを特徴とする半導体装置製造方法。

【請求項1】

真空処理室内に、

半導体装置基板を保持する静電チャック機能を備えるステージと、

前記ステージと対向に設置された金属ターゲットと、

前記ステージの側壁に沿って設置された第1のカバーリングと、

前記第1のカバーリングと前記真空処理室の内面との隙間を覆う第2のカバーリングとを備えるとともに、

前記ステージと前記金属ターゲットとの間にプラズマを発生させるプラズマ発生手段と、

前記ステージに静電チャック作用を発生させるための直流電源と、

前記金属ターゲットのコンディショニング時に前記ステージ全体をプラズマから遮蔽して保護するシャッターディスクと、

前記真空処理室内のクリーニング時に前記ステージの基板設置面のみを覆ってプラズマから保護する保護ディスクと

を備えたことを特徴とするスパッタリング装置。

【請求項2】

前記真空処理室に、前記シャッターディスクおよび保護ディスクを互いに上下に格納する格納部と、前記シャッターディスクおよび保護ディスクを前記ステージに対して搬送する機構とを有することを特徴とする請求項1に記載のスパッタリング装置。

【請求項3】

前記保護ディスクは不導体材料で形成されていることを特徴とする請求項1に記載のスパッタリング装置。

【請求項4】

請求項1記載のスパッタリング装置を用いて、半導体装置基板に金属膜を堆積させる

ことを特徴とする半導体装置製造方法。

【図1】

【図2】

【図3】

【図4】

【図2】

【図3】

【図4】

【公開番号】特開2010−275574(P2010−275574A)

【公開日】平成22年12月9日(2010.12.9)

【国際特許分類】

【出願番号】特願2009−127094(P2009−127094)

【出願日】平成21年5月27日(2009.5.27)

【出願人】(000005821)パナソニック株式会社 (73,050)

【Fターム(参考)】

【公開日】平成22年12月9日(2010.12.9)

【国際特許分類】

【出願日】平成21年5月27日(2009.5.27)

【出願人】(000005821)パナソニック株式会社 (73,050)

【Fターム(参考)】

[ Back to top ]