スパッタリング装置及びスパッタリング成膜方法並びにスパッタリング装置の電源制御方法

【課題】プロセス処理変更のタイミングに同期させて電源制御の変更コマンドを送信することで、シリアル通信の遅れによる誤差をなくし、高精度且つ再現性のよいスパッタリング装置を提供する。

【解決手段】スパッタリング装置は、所定時間サイクルでカソード部に電力供給を行う電源の状態の読み出しを行う電源状態読み出し信号と、所定のタイミングで前記カソード部への電力供給を停止する電力印加停止信号とを電源に対してシリアル通信によって送信する機能を有する電源制御部を備えて構成されており、電源制御部は、電源状態読出しの信号の送信を停止する読出し停止信号を送信して電源の状態の読み出し処理を停止させた後に電力印加停止信号を送信する。

【解決手段】スパッタリング装置は、所定時間サイクルでカソード部に電力供給を行う電源の状態の読み出しを行う電源状態読み出し信号と、所定のタイミングで前記カソード部への電力供給を停止する電力印加停止信号とを電源に対してシリアル通信によって送信する機能を有する電源制御部を備えて構成されており、電源制御部は、電源状態読出しの信号の送信を停止する読出し停止信号を送信して電源の状態の読み出し処理を停止させた後に電力印加停止信号を送信する。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、半導体装置の製造工程などにおいて薄膜を成膜するためのスパッタリング装置及びスパッタリング成膜方法並びにスパッタリング装置の電源制御方法に関する。

【背景技術】

【0002】

近年のデバイスの高密度化に伴い成膜層の膜厚制御の高精度化が求められている。例えば、特許文献1,2に示されている技術によれば、基板の回転角度とシャッタの開閉タイミングまたはスパッタ用DC電源の出力制御をPLC(プログラムロジックコントローラ)を用いたシリアル通信で制御することで高精度の膜厚制御を可能にしている。

【0003】

特許文献1のスパッタリング装置を図3に基づいて説明する。真空容器102の天井部103に二つのターゲット104,105が傾斜した状態で設けられ、成膜チャンバ1の底面部の中央には回転自在に設けられた基板ホルダ107が配置されている。

【0004】

二つのターゲット104,105のいずれか一方を用いてスパッタリング成膜を行う時には、PLCを用いたDC電源制御部115によりシリアル通信で制御されるDC電源112により、必要なターゲットを所定電圧に保持して低圧力放電式のスパッタリングを行うことができる。

【先行技術文献】

【特許文献】

【0005】

【特許文献1】特開2008−294416号公報

【特許文献2】特開2005−008943号公報

【発明の概要】

【発明が解決しようとする課題】

【0006】

しかしながら、特許文献1の技術においては、図4に示すように、電源状態読出しコマンド処理が一定サイクルで繰り返し行われているため、DC電源112の印加停止の制御はそのタイミングで実行している電源状態読出しコマンド処理の終了を待って実行される。つまり、DC電源制御部115からの電源電圧印加停止要求に対して電源状態読出しコマンド処理時間分の遅れ(B)が生じることになる。

【0007】

すなわち電源状態読出しコマンド処理時間分の遅れ(B)は、DC電源制御部115に内蔵されたPLCがスパッタ用のDC電源112からシリアル通信ステータスを読み出すタイミングと、プロセス処理の変更タイミングとが同期されていないためシリアル通信の遅れに起因する誤差である。そのため、スパッタ用DC電源112の出力制御にて成膜層の膜厚制御を行った場合には膜厚に僅かな誤差が生じていた。

【0008】

本発明の目的は、上記問題点に鑑みてなされたものであり、プロセス処理変更のタイミングに同期させて電源制御の変更コマンドを送信することで、シリアル通信の遅れによる誤差をなくし、高精度且つ再現性のよいスパッタリング装置及びスパッタリング成膜方法並びにスパッタリング装置の電源制御方法を提供することにある。

【課題を解決するための手段】

【0009】

上記の目的を達成する本発明に係るスパッタリング装置は、所定時間サイクルでカソード部に電力供給を行う電源の状態の読み出し処理を行う電源状態読み出し信号と、所定のタイミングでカソード部への電力供給を停止する処理を行う電力印加停止信号とを電源に対してシリアル通信によって送信する機能を有する電源制御部を備えて構成されているスパッタリング装置であって、電源制御部は、電源状態読出しの信号の送信を停止させる読出し停止処理を行って電源の状態の読み出し処理を停止させた後に、電力印加停止信号を送信することを特徴とする。

【0010】

あるいは、本発明に係るスパッタリング装置の電源制御方法は、所定時間サイクルでカソード部に電力供給を行う電源の状態の読み出し処理を行う電源状態読み出し信号と、所定のタイミングで前記カソード部への電力供給を停止させる処理を行う電力印加停止信号とを前記電源に対してシリアル通信によって送信する機能を有するスパッタリング装置の電源制御方法であって、電源状態読み出し信号の送信を停止させる読出し停止処理を行って前記電源の状態の読み出し処理を停止させた後に、前記電力印加停止信号を送信する処理を行うことを特徴とする。また、本発明に係るスパッタリング成膜方法は、上記のスパッタリング装置の電源制御方法を用いることを特徴とする。

【発明の効果】

【0011】

本発明によれば、プロセス処理変更のタイミングに同期させてDC電源制御変更コマンドを送信することで、シリアル通信の遅れによる誤差をなくし、シリアル通信の遅れに起因する膜厚の誤差がない成膜処理を行うことができる。例えば、電子デバイス等で各種の材料を順次積層させた積層体の成膜において、各膜厚を極めて高い精度で制御することができ、信頼性の高い積層体を得ることができる。

【0012】

あるいは、本発明の成膜方法によれば、二元系材料からなるデバイス構造の成膜を行う場合でも、各材料のスパッタを極めて高い精度で制御することができ、信頼性の高いデバイス構造体を得ることができる。

【図面の簡単な説明】

【0013】

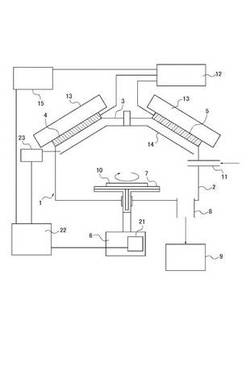

【図1】本発明の一実施形態に係るスパッタリング装置の概略構成図である。

【図2】本発明の一実施形態に係るDC電源への各種制御信号のタイミングを示す説明図である。

【図3】従来のスパッタリング装置の一例を示す概略構成図である。

【図4】従来のスパッタリング装置に備えられたDC電源への各種制御信号のタイミングを示す説明図である。

【発明を実施するための形態】

【0014】

以下に、本発明の一実施形態について図面に基づいて説明する。なお、以下に説明する部材、配置等は発明を具体化した一例であって本発明を限定するものではなく、本発明の趣旨に沿って各種改変できることは勿論である。

【0015】

図1及び2は本発明の一実施形態に係るスパッタリング装置について説明した図であり、図1はスパッタリング装置の概略構成図、図2はDC電源への各種制御信号のタイミングを示す説明図である。なお、ここでは図面の煩雑化を防ぐため一部を除いて省略している。

【0016】

まず、図1に基づいて本実施形態に係るスパッタリング装置の概略構成図を説明する。

スパッタリング装置はカソードを複数備えるマルチカソードタイプの装置であり、真空容器2の天井部3に二つのターゲット4,5が設けられている。これらのターゲット4,5は、天井部3において傾斜した状態で取り付けられている。成膜チャンバ1の底面部の中央には、回転駆動機構6によって回転自在に設けられた基板ホルダ7が配置され、基板ホルダ7上には基板10が水平状態を保って搭載されている。成膜時には基板10は基板ホルダ7の回転に伴い回転される。

【0017】

真空容器2の底部には排気ポート8が設けられ、排気ポート8から排気が行われるように、排気ポート8には排気管を介して排気装置9が接続されている。排気装置9による排気動作によって真空容器2の内部は所要の真空状態、好ましくは10−6Pa以下の圧力レベルに保持される。排気装置9としては、例えば、メインバルブを介して連結されたメインポンプ(クライオポンプもしくはターボ分子ポンプ)と、荒引きバルブを介して連結されたドライポンプを含んだ構成となっている。

【0018】

成膜時、成膜チャンバ1の真空容器2の内部にはプラズマが形成され、プラズマから入射するイオンによってターゲット4,5のいずれかが選択的にスパッタリングされる。放電を発生させる放電ガス(プロセスガスまたはスパッタガス)として、ガス供給部11から、例えばArガスなどが導入される。もちろん、ガス供給部11の設置箇所は図示された箇所に限定されるものではない。

【0019】

真空容器2の天井部3において、ターゲット4,5はそれぞれ基板10の上面(被成膜面)に対して所定角度を向く位置に配置されている。ターゲット4,5は、基板10の被成膜面に対して傾斜して配置されているため、ターゲット4,5の表面の法線は、基板10の被成膜面の法線に対して所定の角度だけ傾斜している。すなわち、ターゲット4,5から基板10に向かうスパッタ粒子は基板10に対して斜方より入射することになる。

【0020】

ターゲット4,5の各々にはDC電源12が接続され、DC電源12からターゲット4,5のいずれかに選択的に所定の電力が印加される。すなわち、ターゲット4,5はDC電源12からの電力が印加されるカソード部を有して構成されている。DC電源12はDC電源制御部15によって、ターゲット4,5に印加する電力が制御される。ターゲット4,5に接続される電源はDC電源に限定されるものではなく、例えば、13.56MHzを供給するRF電源であってもよい。

【0021】

さらに、ターゲット4,5の大気側には磁石ユニット13が配置されている。磁石ユニット13は、電磁石、永久磁石、或いは、これらの組み合わせから構成される。磁石ユニット13によってターゲット4,5の内側表面上に特定の磁界分布が形成される。

【0022】

二つのターゲット4,5のいずれか一方を用いてスパッタリング成膜(スパッタリング成膜処理)を行うときには、DC電源12と磁石ユニット13により、必要なターゲットを所定電圧に保持し、且つ、ターゲット表面上に所定の磁界分布を形成する。これにより、低圧力放電式のスパッタリングを行うことができる。

【0023】

また、二つのターゲット4,5と基板10との間には、回転制御可能に設けられたシャッタ機構14が配置されている。シャッタ機構14は、ターゲットの前面を遮蔽するように配置された略傘状のシャッタ板を有している。シャッタ板には、所定の回転角度に停止されたときに所定のターゲットの前面に位置する開口がいくつか形成されている。ターゲットの前面に開口が位置しているときに、ターゲット前面が遮蔽されなくなるため基板10へのスパッタリングが可能になる。

【0024】

シャッタ機構14の開閉動作によって、二つのターゲット4,5のうちスパッタリング成膜に使用されるターゲットが選択される。なお、シャッタ機構14には公知の機構を用いることができるものとする。上述した構成によって、基板10に対してスパッタリングされたターゲット物質(成膜物質)の斜方入射が実現する。

【0025】

また、基板ホルダ7を回転させる回転駆動機構6、シャッタ機構14を開閉駆動する開閉駆動部23、回転駆動機構6の回転角度を検出する回転角度検出部21、回転角度検出部21により所定の回転角度を検出したときに開閉駆動部23を駆動させてシャッタ機構14を閉じるシャッタ回転制御部22が設けられている。

【0026】

回転角度検出部21は、回転駆動機構6の回転軸に等間隔に放射線状に配置されたスリットを光学センサー等で検知することにより、基板ホルダ7の回転角度を高精度に検出し、その検出信号を、コンピュータ等の演算部(シャッタ回転制御部22)に出力する。

【0027】

本実施形態に係るスパッタリング装置は、シャッタ開の状態となったときから所定時間(C)経過したときにDC電源12からのカソード部への電力供給を停止して成膜動作を終了するように構成されている。具体的には、DC電源制御部15は、所定時間(C)が経過したタイミングで、ターゲット4,5に接続されたDC電源12に対してターゲット4,5への電圧印加を停止する命令(PS Output Off Command)を出力する。

【0028】

また、成膜開始から基板10が所定角度回転したタイミング(時点)で成膜を終了する構成であってもよい。具体的には、成膜開始から基板10が所定の回転角度を回転したことを回転角度検出部21により検出されたときに成膜動作(カソード部への電力供給)を停止するように構成されている。シャッタ回転制御部22は、DC電源制御部15へ検出信号を出力し、DC電源制御部15はこの検出信号により、ターゲット4,5に接続されたDC電源12に対してターゲット4,5への電圧印加を停止する命令を出力する。

【0029】

また、回転角度検出部21により基板ホルダ7が所定角度に位置していると検出されたときに、シャッタの開閉駆動部23はサーボモータを駆動して外部の制御信号によりシャッタ機構14を開あるいは閉の位置に駆動することでスパッタリングを停止する構成であってもよい。具体的には、シャッタ機構14を閉動作するタイミング、若しくは成膜動作を停止するタイミング(所定の回転角度)は、成膜開始から基板10が360°×n+180°+α(nは0を含む自然数、−10°<α<10°)の回転を回転角度検出部21が検出したときとすることができる。

【0030】

次に、図2に示したDC電源12への各種制御信号のタイミングの説明図に基づいて、DC電源12の機能と制御方法について説明する。

DC電源12の設定値を高精度で指定するために、DC電源制御部15はPLCを用いたシリアル通信でDC電源12の制御を行っている。DC電源制御部15は、シリアル通信でDC電源12から電源状態を読み出している。この電源状態の読出しは、電源状態読出しコマンド(電源状態読出しの信号:PS Status Read Command)として常時に繰り返し実行(所定時間サイクル処理)されている。なお、本実施形態における電源状態読出しコマンド処理の読み出しサイクルは50〜200ms程度である。

【0031】

本実施形態におけるDC電源12の制御では、「シャッタ開」の時点に電力印加停止要求(電源電圧印加停止要求)までの時間(C)を加算したタイミングで電源電圧印加停止(電力印加停止信号:PS Output Off Command)を要求する必要がある。このため、この「シャッタ開」の時点に時間(C)を加えたタイミング(時間(C)が経過するタイミング)から所定時間減算した時点で電源状態読出しの停止処理(読出し停止処理:PS Status Read Stop)が行われる。なお、読出し停止処理は、電源状態読出し処理よりも優先度の高い命令として設定されている。

【0032】

電源状態読み出しコマンド(PS Status Read Command)は、DC電源制御部15からDC電源12に対する電源状態のデータ送信命令と、DC電源12からDC電源制御部15に対する電源状態のデータ送信との往復の信号で構成されており、所定のサイクル(読み出しサイクル)を有している。

【0033】

そのため、1サイクル分の読み出しサイクルに要する時間を、時間(C)が経過するタイミングから減算したタイミングに電源状態読出し処理を停止させることにより、電源電圧印加停止の命令が読み電源状態出し処理の実行中にDC電源12に対して送信されることがなくなる。こうして、電源電圧印加停止を、時間(C)が経過するタイミングで確実にDC電源12は受信することができる。

【0034】

なお、1サイクル分の読み出しサイクルとは、DC電源制御部15からDC電源12に対する電源状態のデータ送信命令の繰り返し時間である。また、時間(C)が経過するタイミングから減算する時間は、1サイクル分の読み出しサイクルに要する時間に限られない、すなわち、1サイクルよりも長く2サイクル未満の時間であればよいものとする。

【0035】

そして、DC電源制御部15からの電源電圧印加停止要求に対して、電源電圧印加停止処理を即座に実行できるようにしているため、電源電圧印加停止タイミングの遅れ(D)を、最小限に留めて、精度の良い再現性を得ることができる。なお、シャッタが全開状態になった回転角度を回転角度検出部21が検知したときを「シャッタ開」状態とする。

【0036】

図2に示した各種制御信号のタイミングの説明図について具体的に説明する。

シャッタ開からの電源電圧印加停止要求までの時間(C)は、DC電源制御部15に内蔵されているタイマーによって高精度に管理されている。そして、時間(C)が経過するタイミングから1回分の読み出しサイクルに相当する時間を減算したタイミングで、電源状態読出しコマンド処理の実行を停止させる(PS Status Read Stop)。

【0037】

このため、電源状態読出しコマンド処理(PS Status Read Command)の終了を待つことなく、電源電圧印加停止要求(PS Output Off Command)を実行することができ、電源電圧印加停止要求から実行までのタイムラグ(D)を常に一定時間にすることができる。

【0038】

電源状態読出しコマンド処理の停止についてさらに説明する。

電源状態の読出し処理の停止(PS Status Read Stop)は、PLC内部(DC電源制御部15)でDC電源12との通信停止フラグをONさせて、通信停止フラグがONの間は各種の処理命令送信を実行しないようにされている。

【0039】

電源電圧印加停止要求(PS Output Off Command)により、通信停止フラグがOFF状態にされる。通信停止フラグがOFFにされることより、各種の処理命令の送信処理が再開されるが、再開後1回目に送信されるコマンドは電源電圧印加停止要求(PS Output Off Command)とされているため、電源電圧印加停止要求は確実に実行される。その後、電源状態読出しコマンド処理(PS Status Read Command)のサイクルが再開されることになる。

【0040】

本実施形態においては、電源12への電源電圧印加停止要求について説明したが、シャッタ機構であってもよい。例えば、時間(C)が経過するタイミングでシャッタ機構を回転させて基板10とターゲット4,5を遮蔽する構成にすることができる。

【符号の説明】

【0041】

1,101 成膜チャンバ

2,102 容器

3,103 天井部

4,5,104,105 ターゲット

6,106 回転駆動機構

7,107 基板ホルダ

8 排気ポート

9 排気装置

10 基板

11 ガス供給部

12,112 DC電源

13 磁石ユニット

14 シャッタ機構

15,115 DC電源制御部

21 回転角度検出部

22 シャッタ機構・回転駆動機構制御部

23 開閉駆動部

【技術分野】

【0001】

本発明は、半導体装置の製造工程などにおいて薄膜を成膜するためのスパッタリング装置及びスパッタリング成膜方法並びにスパッタリング装置の電源制御方法に関する。

【背景技術】

【0002】

近年のデバイスの高密度化に伴い成膜層の膜厚制御の高精度化が求められている。例えば、特許文献1,2に示されている技術によれば、基板の回転角度とシャッタの開閉タイミングまたはスパッタ用DC電源の出力制御をPLC(プログラムロジックコントローラ)を用いたシリアル通信で制御することで高精度の膜厚制御を可能にしている。

【0003】

特許文献1のスパッタリング装置を図3に基づいて説明する。真空容器102の天井部103に二つのターゲット104,105が傾斜した状態で設けられ、成膜チャンバ1の底面部の中央には回転自在に設けられた基板ホルダ107が配置されている。

【0004】

二つのターゲット104,105のいずれか一方を用いてスパッタリング成膜を行う時には、PLCを用いたDC電源制御部115によりシリアル通信で制御されるDC電源112により、必要なターゲットを所定電圧に保持して低圧力放電式のスパッタリングを行うことができる。

【先行技術文献】

【特許文献】

【0005】

【特許文献1】特開2008−294416号公報

【特許文献2】特開2005−008943号公報

【発明の概要】

【発明が解決しようとする課題】

【0006】

しかしながら、特許文献1の技術においては、図4に示すように、電源状態読出しコマンド処理が一定サイクルで繰り返し行われているため、DC電源112の印加停止の制御はそのタイミングで実行している電源状態読出しコマンド処理の終了を待って実行される。つまり、DC電源制御部115からの電源電圧印加停止要求に対して電源状態読出しコマンド処理時間分の遅れ(B)が生じることになる。

【0007】

すなわち電源状態読出しコマンド処理時間分の遅れ(B)は、DC電源制御部115に内蔵されたPLCがスパッタ用のDC電源112からシリアル通信ステータスを読み出すタイミングと、プロセス処理の変更タイミングとが同期されていないためシリアル通信の遅れに起因する誤差である。そのため、スパッタ用DC電源112の出力制御にて成膜層の膜厚制御を行った場合には膜厚に僅かな誤差が生じていた。

【0008】

本発明の目的は、上記問題点に鑑みてなされたものであり、プロセス処理変更のタイミングに同期させて電源制御の変更コマンドを送信することで、シリアル通信の遅れによる誤差をなくし、高精度且つ再現性のよいスパッタリング装置及びスパッタリング成膜方法並びにスパッタリング装置の電源制御方法を提供することにある。

【課題を解決するための手段】

【0009】

上記の目的を達成する本発明に係るスパッタリング装置は、所定時間サイクルでカソード部に電力供給を行う電源の状態の読み出し処理を行う電源状態読み出し信号と、所定のタイミングでカソード部への電力供給を停止する処理を行う電力印加停止信号とを電源に対してシリアル通信によって送信する機能を有する電源制御部を備えて構成されているスパッタリング装置であって、電源制御部は、電源状態読出しの信号の送信を停止させる読出し停止処理を行って電源の状態の読み出し処理を停止させた後に、電力印加停止信号を送信することを特徴とする。

【0010】

あるいは、本発明に係るスパッタリング装置の電源制御方法は、所定時間サイクルでカソード部に電力供給を行う電源の状態の読み出し処理を行う電源状態読み出し信号と、所定のタイミングで前記カソード部への電力供給を停止させる処理を行う電力印加停止信号とを前記電源に対してシリアル通信によって送信する機能を有するスパッタリング装置の電源制御方法であって、電源状態読み出し信号の送信を停止させる読出し停止処理を行って前記電源の状態の読み出し処理を停止させた後に、前記電力印加停止信号を送信する処理を行うことを特徴とする。また、本発明に係るスパッタリング成膜方法は、上記のスパッタリング装置の電源制御方法を用いることを特徴とする。

【発明の効果】

【0011】

本発明によれば、プロセス処理変更のタイミングに同期させてDC電源制御変更コマンドを送信することで、シリアル通信の遅れによる誤差をなくし、シリアル通信の遅れに起因する膜厚の誤差がない成膜処理を行うことができる。例えば、電子デバイス等で各種の材料を順次積層させた積層体の成膜において、各膜厚を極めて高い精度で制御することができ、信頼性の高い積層体を得ることができる。

【0012】

あるいは、本発明の成膜方法によれば、二元系材料からなるデバイス構造の成膜を行う場合でも、各材料のスパッタを極めて高い精度で制御することができ、信頼性の高いデバイス構造体を得ることができる。

【図面の簡単な説明】

【0013】

【図1】本発明の一実施形態に係るスパッタリング装置の概略構成図である。

【図2】本発明の一実施形態に係るDC電源への各種制御信号のタイミングを示す説明図である。

【図3】従来のスパッタリング装置の一例を示す概略構成図である。

【図4】従来のスパッタリング装置に備えられたDC電源への各種制御信号のタイミングを示す説明図である。

【発明を実施するための形態】

【0014】

以下に、本発明の一実施形態について図面に基づいて説明する。なお、以下に説明する部材、配置等は発明を具体化した一例であって本発明を限定するものではなく、本発明の趣旨に沿って各種改変できることは勿論である。

【0015】

図1及び2は本発明の一実施形態に係るスパッタリング装置について説明した図であり、図1はスパッタリング装置の概略構成図、図2はDC電源への各種制御信号のタイミングを示す説明図である。なお、ここでは図面の煩雑化を防ぐため一部を除いて省略している。

【0016】

まず、図1に基づいて本実施形態に係るスパッタリング装置の概略構成図を説明する。

スパッタリング装置はカソードを複数備えるマルチカソードタイプの装置であり、真空容器2の天井部3に二つのターゲット4,5が設けられている。これらのターゲット4,5は、天井部3において傾斜した状態で取り付けられている。成膜チャンバ1の底面部の中央には、回転駆動機構6によって回転自在に設けられた基板ホルダ7が配置され、基板ホルダ7上には基板10が水平状態を保って搭載されている。成膜時には基板10は基板ホルダ7の回転に伴い回転される。

【0017】

真空容器2の底部には排気ポート8が設けられ、排気ポート8から排気が行われるように、排気ポート8には排気管を介して排気装置9が接続されている。排気装置9による排気動作によって真空容器2の内部は所要の真空状態、好ましくは10−6Pa以下の圧力レベルに保持される。排気装置9としては、例えば、メインバルブを介して連結されたメインポンプ(クライオポンプもしくはターボ分子ポンプ)と、荒引きバルブを介して連結されたドライポンプを含んだ構成となっている。

【0018】

成膜時、成膜チャンバ1の真空容器2の内部にはプラズマが形成され、プラズマから入射するイオンによってターゲット4,5のいずれかが選択的にスパッタリングされる。放電を発生させる放電ガス(プロセスガスまたはスパッタガス)として、ガス供給部11から、例えばArガスなどが導入される。もちろん、ガス供給部11の設置箇所は図示された箇所に限定されるものではない。

【0019】

真空容器2の天井部3において、ターゲット4,5はそれぞれ基板10の上面(被成膜面)に対して所定角度を向く位置に配置されている。ターゲット4,5は、基板10の被成膜面に対して傾斜して配置されているため、ターゲット4,5の表面の法線は、基板10の被成膜面の法線に対して所定の角度だけ傾斜している。すなわち、ターゲット4,5から基板10に向かうスパッタ粒子は基板10に対して斜方より入射することになる。

【0020】

ターゲット4,5の各々にはDC電源12が接続され、DC電源12からターゲット4,5のいずれかに選択的に所定の電力が印加される。すなわち、ターゲット4,5はDC電源12からの電力が印加されるカソード部を有して構成されている。DC電源12はDC電源制御部15によって、ターゲット4,5に印加する電力が制御される。ターゲット4,5に接続される電源はDC電源に限定されるものではなく、例えば、13.56MHzを供給するRF電源であってもよい。

【0021】

さらに、ターゲット4,5の大気側には磁石ユニット13が配置されている。磁石ユニット13は、電磁石、永久磁石、或いは、これらの組み合わせから構成される。磁石ユニット13によってターゲット4,5の内側表面上に特定の磁界分布が形成される。

【0022】

二つのターゲット4,5のいずれか一方を用いてスパッタリング成膜(スパッタリング成膜処理)を行うときには、DC電源12と磁石ユニット13により、必要なターゲットを所定電圧に保持し、且つ、ターゲット表面上に所定の磁界分布を形成する。これにより、低圧力放電式のスパッタリングを行うことができる。

【0023】

また、二つのターゲット4,5と基板10との間には、回転制御可能に設けられたシャッタ機構14が配置されている。シャッタ機構14は、ターゲットの前面を遮蔽するように配置された略傘状のシャッタ板を有している。シャッタ板には、所定の回転角度に停止されたときに所定のターゲットの前面に位置する開口がいくつか形成されている。ターゲットの前面に開口が位置しているときに、ターゲット前面が遮蔽されなくなるため基板10へのスパッタリングが可能になる。

【0024】

シャッタ機構14の開閉動作によって、二つのターゲット4,5のうちスパッタリング成膜に使用されるターゲットが選択される。なお、シャッタ機構14には公知の機構を用いることができるものとする。上述した構成によって、基板10に対してスパッタリングされたターゲット物質(成膜物質)の斜方入射が実現する。

【0025】

また、基板ホルダ7を回転させる回転駆動機構6、シャッタ機構14を開閉駆動する開閉駆動部23、回転駆動機構6の回転角度を検出する回転角度検出部21、回転角度検出部21により所定の回転角度を検出したときに開閉駆動部23を駆動させてシャッタ機構14を閉じるシャッタ回転制御部22が設けられている。

【0026】

回転角度検出部21は、回転駆動機構6の回転軸に等間隔に放射線状に配置されたスリットを光学センサー等で検知することにより、基板ホルダ7の回転角度を高精度に検出し、その検出信号を、コンピュータ等の演算部(シャッタ回転制御部22)に出力する。

【0027】

本実施形態に係るスパッタリング装置は、シャッタ開の状態となったときから所定時間(C)経過したときにDC電源12からのカソード部への電力供給を停止して成膜動作を終了するように構成されている。具体的には、DC電源制御部15は、所定時間(C)が経過したタイミングで、ターゲット4,5に接続されたDC電源12に対してターゲット4,5への電圧印加を停止する命令(PS Output Off Command)を出力する。

【0028】

また、成膜開始から基板10が所定角度回転したタイミング(時点)で成膜を終了する構成であってもよい。具体的には、成膜開始から基板10が所定の回転角度を回転したことを回転角度検出部21により検出されたときに成膜動作(カソード部への電力供給)を停止するように構成されている。シャッタ回転制御部22は、DC電源制御部15へ検出信号を出力し、DC電源制御部15はこの検出信号により、ターゲット4,5に接続されたDC電源12に対してターゲット4,5への電圧印加を停止する命令を出力する。

【0029】

また、回転角度検出部21により基板ホルダ7が所定角度に位置していると検出されたときに、シャッタの開閉駆動部23はサーボモータを駆動して外部の制御信号によりシャッタ機構14を開あるいは閉の位置に駆動することでスパッタリングを停止する構成であってもよい。具体的には、シャッタ機構14を閉動作するタイミング、若しくは成膜動作を停止するタイミング(所定の回転角度)は、成膜開始から基板10が360°×n+180°+α(nは0を含む自然数、−10°<α<10°)の回転を回転角度検出部21が検出したときとすることができる。

【0030】

次に、図2に示したDC電源12への各種制御信号のタイミングの説明図に基づいて、DC電源12の機能と制御方法について説明する。

DC電源12の設定値を高精度で指定するために、DC電源制御部15はPLCを用いたシリアル通信でDC電源12の制御を行っている。DC電源制御部15は、シリアル通信でDC電源12から電源状態を読み出している。この電源状態の読出しは、電源状態読出しコマンド(電源状態読出しの信号:PS Status Read Command)として常時に繰り返し実行(所定時間サイクル処理)されている。なお、本実施形態における電源状態読出しコマンド処理の読み出しサイクルは50〜200ms程度である。

【0031】

本実施形態におけるDC電源12の制御では、「シャッタ開」の時点に電力印加停止要求(電源電圧印加停止要求)までの時間(C)を加算したタイミングで電源電圧印加停止(電力印加停止信号:PS Output Off Command)を要求する必要がある。このため、この「シャッタ開」の時点に時間(C)を加えたタイミング(時間(C)が経過するタイミング)から所定時間減算した時点で電源状態読出しの停止処理(読出し停止処理:PS Status Read Stop)が行われる。なお、読出し停止処理は、電源状態読出し処理よりも優先度の高い命令として設定されている。

【0032】

電源状態読み出しコマンド(PS Status Read Command)は、DC電源制御部15からDC電源12に対する電源状態のデータ送信命令と、DC電源12からDC電源制御部15に対する電源状態のデータ送信との往復の信号で構成されており、所定のサイクル(読み出しサイクル)を有している。

【0033】

そのため、1サイクル分の読み出しサイクルに要する時間を、時間(C)が経過するタイミングから減算したタイミングに電源状態読出し処理を停止させることにより、電源電圧印加停止の命令が読み電源状態出し処理の実行中にDC電源12に対して送信されることがなくなる。こうして、電源電圧印加停止を、時間(C)が経過するタイミングで確実にDC電源12は受信することができる。

【0034】

なお、1サイクル分の読み出しサイクルとは、DC電源制御部15からDC電源12に対する電源状態のデータ送信命令の繰り返し時間である。また、時間(C)が経過するタイミングから減算する時間は、1サイクル分の読み出しサイクルに要する時間に限られない、すなわち、1サイクルよりも長く2サイクル未満の時間であればよいものとする。

【0035】

そして、DC電源制御部15からの電源電圧印加停止要求に対して、電源電圧印加停止処理を即座に実行できるようにしているため、電源電圧印加停止タイミングの遅れ(D)を、最小限に留めて、精度の良い再現性を得ることができる。なお、シャッタが全開状態になった回転角度を回転角度検出部21が検知したときを「シャッタ開」状態とする。

【0036】

図2に示した各種制御信号のタイミングの説明図について具体的に説明する。

シャッタ開からの電源電圧印加停止要求までの時間(C)は、DC電源制御部15に内蔵されているタイマーによって高精度に管理されている。そして、時間(C)が経過するタイミングから1回分の読み出しサイクルに相当する時間を減算したタイミングで、電源状態読出しコマンド処理の実行を停止させる(PS Status Read Stop)。

【0037】

このため、電源状態読出しコマンド処理(PS Status Read Command)の終了を待つことなく、電源電圧印加停止要求(PS Output Off Command)を実行することができ、電源電圧印加停止要求から実行までのタイムラグ(D)を常に一定時間にすることができる。

【0038】

電源状態読出しコマンド処理の停止についてさらに説明する。

電源状態の読出し処理の停止(PS Status Read Stop)は、PLC内部(DC電源制御部15)でDC電源12との通信停止フラグをONさせて、通信停止フラグがONの間は各種の処理命令送信を実行しないようにされている。

【0039】

電源電圧印加停止要求(PS Output Off Command)により、通信停止フラグがOFF状態にされる。通信停止フラグがOFFにされることより、各種の処理命令の送信処理が再開されるが、再開後1回目に送信されるコマンドは電源電圧印加停止要求(PS Output Off Command)とされているため、電源電圧印加停止要求は確実に実行される。その後、電源状態読出しコマンド処理(PS Status Read Command)のサイクルが再開されることになる。

【0040】

本実施形態においては、電源12への電源電圧印加停止要求について説明したが、シャッタ機構であってもよい。例えば、時間(C)が経過するタイミングでシャッタ機構を回転させて基板10とターゲット4,5を遮蔽する構成にすることができる。

【符号の説明】

【0041】

1,101 成膜チャンバ

2,102 容器

3,103 天井部

4,5,104,105 ターゲット

6,106 回転駆動機構

7,107 基板ホルダ

8 排気ポート

9 排気装置

10 基板

11 ガス供給部

12,112 DC電源

13 磁石ユニット

14 シャッタ機構

15,115 DC電源制御部

21 回転角度検出部

22 シャッタ機構・回転駆動機構制御部

23 開閉駆動部

【特許請求の範囲】

【請求項1】

所定時間サイクルでカソード部に電力供給を行う電源の状態の読み出し処理を行う電源状態読み出し信号と、所定のタイミングで前記カソード部への電力供給を停止する処理を行う電力印加停止信号とを前記電源に対してシリアル通信によって送信する機能を有する電源制御部を備えて構成されているスパッタリング装置であって、

前記電源制御部は、前記電源状態読出しの信号の送信を停止させる読出し停止処理を行って前記電源の状態の読み出し処理を停止させた後に、前記電力印加停止信号を送信することを特徴とするスパッタリング装置。

【請求項2】

前記読出し停止処理は、前記カソード部への電力供給が停止される所定のタイミングから、前記電源の状態の読み出し処理が1サイクル行われる時間を減算したタイミングで行われることを特徴とする請求項1に記載のスパッタリング装置。

【請求項3】

請求項1又は2に記載のスパッタリング装置を用いてスパッタリング成膜処理が行われることを特徴とするスパッタリング成膜方法。

【請求項4】

所定時間サイクルでカソード部に電力供給を行う電源の状態の読み出し処理を行う電源状態読み出し信号と、所定のタイミングで前記カソード部への電力供給を停止させる処理を行う電力印加停止信号とを前記電源に対してシリアル通信によって送信する機能を有するスパッタリング装置の電源制御方法であって、

前記電源状態読み出し信号の送信を停止させる読出し停止処理を行って前記電源の状態の読み出し処理を停止させた後に、前記電力印加停止信号を送信する処理を行うことを特徴とするスパッタリング装置の電源制御方法。

【請求項5】

前記読出し停止処理は、前記カソード部への電力供給が停止される所定のタイミングから前記電源の状態の読み出し処理が1サイクル行われる時間を減算したタイミングで行われることを特徴とする請求項4に記載のスパッタリング装置の電源制御方法。

【請求項1】

所定時間サイクルでカソード部に電力供給を行う電源の状態の読み出し処理を行う電源状態読み出し信号と、所定のタイミングで前記カソード部への電力供給を停止する処理を行う電力印加停止信号とを前記電源に対してシリアル通信によって送信する機能を有する電源制御部を備えて構成されているスパッタリング装置であって、

前記電源制御部は、前記電源状態読出しの信号の送信を停止させる読出し停止処理を行って前記電源の状態の読み出し処理を停止させた後に、前記電力印加停止信号を送信することを特徴とするスパッタリング装置。

【請求項2】

前記読出し停止処理は、前記カソード部への電力供給が停止される所定のタイミングから、前記電源の状態の読み出し処理が1サイクル行われる時間を減算したタイミングで行われることを特徴とする請求項1に記載のスパッタリング装置。

【請求項3】

請求項1又は2に記載のスパッタリング装置を用いてスパッタリング成膜処理が行われることを特徴とするスパッタリング成膜方法。

【請求項4】

所定時間サイクルでカソード部に電力供給を行う電源の状態の読み出し処理を行う電源状態読み出し信号と、所定のタイミングで前記カソード部への電力供給を停止させる処理を行う電力印加停止信号とを前記電源に対してシリアル通信によって送信する機能を有するスパッタリング装置の電源制御方法であって、

前記電源状態読み出し信号の送信を停止させる読出し停止処理を行って前記電源の状態の読み出し処理を停止させた後に、前記電力印加停止信号を送信する処理を行うことを特徴とするスパッタリング装置の電源制御方法。

【請求項5】

前記読出し停止処理は、前記カソード部への電力供給が停止される所定のタイミングから前記電源の状態の読み出し処理が1サイクル行われる時間を減算したタイミングで行われることを特徴とする請求項4に記載のスパッタリング装置の電源制御方法。

【図1】

【図2】

【図3】

【図4】

【図2】

【図3】

【図4】

【公開番号】特開2011−149093(P2011−149093A)

【公開日】平成23年8月4日(2011.8.4)

【国際特許分類】

【出願番号】特願2010−272137(P2010−272137)

【出願日】平成22年12月7日(2010.12.7)

【出願人】(000227294)キヤノンアネルバ株式会社 (564)

【Fターム(参考)】

【公開日】平成23年8月4日(2011.8.4)

【国際特許分類】

【出願日】平成22年12月7日(2010.12.7)

【出願人】(000227294)キヤノンアネルバ株式会社 (564)

【Fターム(参考)】

[ Back to top ]