スピネルフェライト薄膜の製造方法

【課題】積層構造の中にスピネルフェライト薄膜を配置したスピンフィルタ効果素子において、スピネルフェライト薄膜下部の金属電極層の酸化および下部界面の熱拡散を抑制し、上部界面の大気成分による汚染を排除しつつ、(100)優先配向したスピネルフェライト薄膜を製造する方法を提供する。

【解決手段】基板上に(100)優先配向のスピネルフェライト薄膜を製造する方法であって、前記製造方法は、スパッタリング法でスピネルフェライト薄膜もしくはその前駆体となる薄膜を基板上に形成するスパッタ成膜ステップと、その基板を真空中で加熱する真空加熱ステップとを有することを特徴とするスピネルフェライト薄膜の製造方法。

【解決手段】基板上に(100)優先配向のスピネルフェライト薄膜を製造する方法であって、前記製造方法は、スパッタリング法でスピネルフェライト薄膜もしくはその前駆体となる薄膜を基板上に形成するスパッタ成膜ステップと、その基板を真空中で加熱する真空加熱ステップとを有することを特徴とするスピネルフェライト薄膜の製造方法。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、スピンフィルタ効果素子およびそれを利用した磁気デバイスに用いるスピネルフェライト薄膜の製造方法に関する。

【背景技術】

【0002】

スピネル型結晶構造を有したフェライト薄膜(以下、スピネルフェライト薄膜と言う)は、サーミスタ素子(特許文献1〜5参照)やスピンフィルタ効果素子に用いられている(特許文献6〜7参照)。

【0003】

上述のスピネルフェライト薄膜はデバイス特性上スピネル型結晶構造を有し、さらに(100)面に優先配向していることが好ましい。それを実現するための従来技術としては、スパッタリング法によってスピネルフェライト薄膜を基板上に成膜する際、スパッタ成膜中に微量の酸素を添加する(特許文献1〜5、8)、スパッタ成膜中の基板を200℃以上に加熱する(特許文献1〜8)、さらに結晶化を促進するために成膜後に基板を高温で熱処理する(特許文献1〜5、8)方法が知られている。スピネルフェライトのスパッタ成膜中に酸素を添加しない場合では、成膜後の熱処理によって結晶化は促進するが(100)優先配向しないことが知られている(特許文献2、8)。

ところでスピンフィルタ効果素子においては、スピネルフェライト薄膜は積層構造の中に配置され、その膜厚は100nm以下であり、スピネルフェライト層の上下界面のうち少なくとも一方は磁性または非磁性の金属層と接している(特許文献6、7)。

【0004】

図11は特許文献6のスピンフィルタ効果素子の構成を示す断面図である。図11記載のスピンフィルタ効果素子901は、高抵抗のスピネルフェライト912の薄膜が第1の電極である非磁性電極911と第2の電極である強磁性電極913との間に挿入された構造を有している。直流電源914は、第1の電極911と第2の電極913に印加され、外部磁界15が膜面内に平行に印加されている。

【0005】

ここで、高抵抗のスピネルフェライト912は、強磁性を有し、その厚さはトンネル現象が生起するように十分に薄く形成されている。直流電源914は、非磁性電極911からの電子が、スピネルフェライト12中をトンネルして、強磁性電極13へ流れるように、非磁性電極11側を負とする向きに接続する。

【0006】

図12は、特許文献6記載のスピンフィルタ効果素子の動作を説明するためのエネルギー準位を示す模式図である。図12において、Φ↓(下向き矢印)は、第1の電極のフェルミ準位からの高抵抗のスピネルフェライト912の↓(下向き矢印)スピンバンドの電位障壁高さである。また、高抵抗のスピネルフェライト912は、強磁性体であるため、↑(上向き矢印)スピンバンドのエネルギー準位は、Φ↓と異なるΦ↑(上向き矢印)で示す。図12に示すように、Φ↑がΦ↓よりも小さいので、スピン電子e↑のみが、Φ↑のトンネル障壁を介して強磁性電極913側にトンネルすることができる。

【0007】

このように、トンネル障壁がスピンに依存することで、非磁性金属電極911からのトンネル電子による抵抗、または、コンダクタンスは、スピンに依存し、スピンに依存したトンネル現象を示す。すなわち、トンネル障壁はスピンフィルタとして働く。

従って、特許文献6のスピンフィルタ素子901では、高抵抗のスピネルフェライト912のエネルギー準位のスピン分裂が大きいほど、より大きなスピンフィルタ効果が得られる。また、特許文献6のスピンフィルタ素子901では外部磁界915を印加し、このスピンフィルタ効果を利用すると共に、外部磁界により第2電極の強磁性層のスピンを反転させることによって、大きなトンネル磁気抵抗効果が得られる。

【0008】

図11に示す特許文献6のスピンフィルタ効果素子の第2の電極913は、強磁性電極上に、さらに反強磁性層を積層して形成することができる。この構造では、スピンバルブ効果により強磁性電極の磁化は、反強磁性層との交換相互作用により、スピンが1方向に固定されるので、電極913のスピンの平行、反平行を容易に得ることができるため、特許文献6のスピンフィルタ効果素子のTMRは更に大きくなる。

また、特許文献6のスピンフィルタ効果素子の第2の電極913の強磁性電極、または、反強磁性層の上には、さらに保護膜となる非磁性の電極層を堆積させることが好ましい。特許文献6のスピンフィルタ効果素子901は、スパッタ法、蒸着法、レーザアブレーション法、MBE法などの通常の薄膜成膜法を用いて成膜することができる。

【先行技術文献】

【特許文献】

【0009】

【特許文献1】特開昭60−208803号公報

【特許文献2】特開昭63−266801号公報

【特許文献3】特開2000−348905号公報

【特許文献4】特開2000−348903号公報

【特許文献5】特開2008−84991号公報

【特許文献6】特開2004−39672号公報

【特許文献7】特開2009−105415号公報

【特許文献8】特開平4−260695号公報

【発明の概要】

【発明が解決しようとする課題】

【0010】

従来の方法でスピンフィルタ素子用のスピネルフェライト薄膜を成膜すると、スパッタ成膜中にArガスに添加した酸素ガスが下部の金属電極層の表面を酸化させてスピンフィルタ効率を低下させてしまうという問題があった。Arガスのみでスパッタ成膜した場合には、成膜後に熱処理を行うことによって結晶化を促進するが、その場合にはスピネルフェライト薄膜が(100)配向しないという問題があった。成膜中に基板を加熱すると下部の金属電極層とスピネルフェライト薄膜が熱拡散し、スピンフィルタ効率を低下させてしまうという問題があった。また下部の金属電極層の結晶構造がアモルファスである場合には、金属電極層が結晶化してしまうことにより、スピネルフェライト薄膜のスパッタ成膜において、スピネルフェライト薄膜が(100)優先配向しないという問題があった。スピネルフェライト薄膜の成膜後に結晶化を促進するための熱処理を大気中で行うと、その次に成膜される層との界面が大気成分で汚染されてしまうため、スピンフィルタ効率を低下させてしまうという問題があった。

【0011】

そこで本発明は上記事情に鑑みて、積層構造の中にスピネルフェライト薄膜を配置したスピンフィルタ効果素子において、スピネルフェライト薄膜下部の金属電極層の酸化および下部界面の熱拡散を抑制し、上部界面の大気成分による汚染を排除しつつ、(100)優先配向したスピネルフェライト薄膜を製造する方法を提供する。

【課題を解決するための手段】

【0012】

上記目的を達成するために、請求項1記載の発明は、基板上に(100)優先配向のスピネルフェライト薄膜を製造する方法であって、前記製造方法は、スパッタリング法でスピネルフェライト薄膜もしくはその前駆体となる薄膜を基板上に形成するスパッタ成膜ステップと、その基板を真空中で加熱する真空加熱ステップとを有することを特徴とするスピネルフェライト薄膜のスピネルフェライト薄膜の製造方法としたものである。

さらに、請求項2記載の発明は、請求項1に記載の製造方法において、前記スパッタ成膜ステップは、スパッタリングカソードに印加する電圧の周波数が1〜100MHzの高周波であり、スパッタリングカソードに設置するターゲット材料がM:Fe:Oの比率が略x:3−x:4(Mは、Zn、Mn、Co、Ni、Cu、Mg、Li、Feのいずれか1つ、かつ、0<x<3)で構成された複合酸化物ターゲットであり、スパッタリングガスはアルゴンガスのみでその圧力は0.1Pa以下であり、 薄膜が堆積される基板温度は室温であり、前記ターゲットと前記基板との間の距離が100mm以上であることを特徴とするスピネルフェライト薄膜の製造方法としたものである。

さらに、請求項1又は請求項2に記載の製造方法において、前記スパッタ成膜ステップにおける基板が200℃未満であることを特徴とするスピネルフェライト薄膜の製造方法としたものである。

さらに、請求項4記載の発明は、請求項1〜3のいずれか1項に記載の製造方法において、前記基板はCoまたはFeを主成分とし、アモルファス構造を有した磁性金属薄膜が表面に付着していることを特徴とするスピネルフェライト薄膜の製造方法としたものである。

さらに、請求項5記載の発明は、請求項1〜4のいずれか1項に記載の製造方法において、前記スピネルフェライト薄膜の膜厚が100nm以下であることを特徴とするスピネルフェライト薄膜の製造方法としたものである。

【発明の効果】

【0013】

本願の請求項1の発明によれば、スパッタリング法でスピネルフェライト薄膜もしくはその前駆体となる薄膜を基板上に形成するスパッタ成膜ステップと、その基板を真空中で加熱する真空加熱ステップとを有することを特徴とする製造方法を用いることにより、大部分が第二の結晶面を基板面に対して平行となるような結晶粒を多数含むスピネルフェライト多結晶薄膜を形成することが可能となる。そのため、アモルファス構造を有した基板上に、ミラー指数(100)の結晶面を有するスピネルフェライト多結晶薄膜が得ることが可能となる。

本願の請求項2の発明によれば、スパッタリングカソードに印加する電圧の周波数が1〜100MHzの高周波とすることにより、絶縁性の酸化物ターゲットの場合においてもスパッタ成膜することが可能となる。

また、本願の請求項2記載の発明によれば、スパッタリングカソードに設置するターゲット材料がM:Fe:Oの比率が略x:3−x:4(Mは、Zn、Mn、Co、Ni、Cu、Mg、Li、Feのいずれか1つ、かつ、0<x<3)である複合酸化物ターゲットとすることより、基板上にスピネルフェライト薄膜またはその前駆体となる薄膜を形成することが可能となる。

また、本願の請求項2記載の発明によれば、スパッタリングガスとしてアルゴンガスのみを用い、その圧力を0.1Pa以下とすることより、下地層が金属薄膜である場合にその表面がスピネルフェライト薄膜の成膜中に酸化することを抑制することが可能となる。

また、本願の請求項2記載の発明によれば、薄膜が堆積される基板温度を室温とすることより、下地層がアモルファス構造を有した金属である場合に熱による結晶化を防ぐことが可能となる。

さらに、本願の請求項3記載の発明によれば、スパッタ成膜ステップにおける基板を200℃未満とすることにより、下地層がアモルファス構造を有した金属である場合に熱による結晶化を抑制することが可能となる。

さらに、本願の請求項4記載の発明によれば、CoまたはFeを主成分とし、アモルファス構造を有した磁性金属薄膜が表面に付着した基板を用いることにより、スピネルフェライト薄膜の(100)優先配向を促進することが可能となる。

さらに、本願の請求項5記載の発明によれば、スピネルフェライト薄膜の膜厚が100nm以下とすることにより、スピンフィルタ効果素子として有効に動作することが可能となる。

【図面の簡単な説明】

【0014】

【図1】本発明のスピネルフェライト薄膜に成膜に用いるスパッタリング装置の第1の例を示す平面図である。

【図2】本発明のスピネルフェライト薄膜の成膜に用いるスパッタ成膜チャンバーの第1の例の断面図である。

【図3】本発明の製造方法を用いて成膜したスピネルフェライト薄膜のX線回折パターンである。

【図4】本発明のスピネルフェライト薄膜の成膜に用いるスパッタリング装置の第2の例を示す平面図である。

【図5】本発明のスピネルフェライト薄膜に成膜に用いる真空加熱チャンバーの装置構成図である。

【図6】本発明の製造方法を用いて作製したスピンフィルタ効果素子の第1の膜構成図である。

【図7】本発明の製造方法を用いて作製したスピンフィルタ効果素子の第2の膜構成図である。

【図8】本発明の製造方法を用いて作製したスピンフィルタ効果素子の第3の膜構成図である。

【図9】本発明の製造方法を用いて作製したスピンフィルタ効果素子の第4の膜構成図である。

【図10】本発明の製造方法を用いて作製したスピンフィルタ効果素子の第5の膜構成図である。

【図11】従来(特許文献6)のスピンフィルタ効果素子の構成を示す断面図である。

【図12】従来(特許文献6)記載のスピンフィルタ効果素子の動作を説明するためのエネルギー準位を示す模式図である。

【発明を実施するための形態】

【0015】

以下、図面を参照して、本発明の実施の形態を説明するが、本発明は本実施形態に限定

されるものではない。

【0016】

図1と図2を参照して、本発明に係るスパッタリング装置の一実施の形態について説明する。図1は本実施形態のスパッタリング装置を模式的に示す平面図である。また、図2はスパッタ成膜チャンバーの断面図である。なお、図2は図1のスパッタ成膜チャンバーのAOB断面に相当する。

【0017】

図1のスパッタリング装置は、基板搬送ロボット11が設けられた搬送チャンバー12と、搬送チャンバー12に結合されたスパッタリング成膜チャンバー13と、プロセスチャンバー14と、ロードロック室15A、15Bとから構成される。スパッタリング成膜チャンバー13は2つ以上のカソード31を備えたスパッタリング成膜室である。スパッタリング成膜チャンバー13の2つ以上のカソード31には、それぞれ単一の元素又は複数の元素からなる材料で形成された2つ以上のターゲットが固定されている。スパッタリング成膜チャンバー13とプロセスチャンバー14とロードロック室15A、15Bとの間の基板25の移動は、搬送チャンバー12に設けられた基板搬送ロボット11によって行われる。図1において、スパッタリング成膜チャンバー13は1つの真空チャンバー13Aで構成されている。

【0018】

上記に挙げた全てのチャンバーとロードロック室15A、15Bは、各々チャンバー内を真空に排気するための真空ポンプを有していることが好ましく、ロードロック室15A、15B以外のチャンバーは常時真空に維持されている。なお、後述する全ての実施形態において、全てのチャンバーとロードロック室が真空ポンプを有していることを前提としている。

【0019】

ロードロック室15A、15Bはプロセス前に基板25を大気から入れる場合と、プロセス後に基板25を大気に出す場合は大気圧と同等の圧力に維持され、ロードロック室15A、15Bに配置した基板25を真空に排気された搬送チャンバー12内に搬入する場合と、プロセス後に基板25を回収する場合は真空に排気されている。ロードロック室15A、15Bは必ずしも2つある必要は無く1つでも良い。

【0020】

スパッタリング成膜チャンバー13とプロセスチャンバー14とロードロック室15A、15Bのそれぞれの室の間にはゲートバルブ16が設けられている。各ゲートバルブ16は基板25を搬送する場合以外は閉じられている。基板搬送ロボット11はロードロック室15A、15Bから基板25を取り出し、コンピュータプログラムからの命令によって所望のチャンバーに基板25を搬入するようになっている。

【0021】

複数のスパッタリングカソード31を備えたスパッタリング成膜チャンバー13は、図2に示すように真空チャンバー13Aの上部に複数のスパッタリングカソード31を配置している。真空チャンバー13A内部の下方には真空チャンバー13A外部に備えられた動力源(不図示)によって回転可能な基板ステージ33があり、少なくとも成膜時には基板ステージ33の上に薄膜を堆積させるための基板25を載置する。基板25とスパッタリングターゲット32の間にシャッターを配置しておき、電力投入をし続けたままシャッターの開閉によって膜厚を制御しても良い。多層薄膜を成膜する場合は、回転する基板ステージ33上に基板25を載置させたまま上記の成膜操作を順次行えば良い。なお、図1においては、スパッタリング成膜チャンバー13には5種類のターゲット31が設置され、その材質はPtMn,CoFe,Ru、CoFeBである。また、ゲートバルブ16が、Oリング34を介して真空チャンバー13Aの側壁に設けられている。

【0022】

尚、基板ステージ33は、不図示の真空用回転導入機を介して不図示の回転駆動機構に接続されて、真空を維持しながらその中心軸周りに回転可能に構成されており、載置面に載置する基板25を処理面に沿って回転するようになっている。真空用回転導入機としては磁性流体を用いるが、これに限定されるものではない。

基板25の材料としては、例えば、円板状のシリコンウェハを用いるが、これに限定されるものではない。

【0023】

図1に示すように、本実施形態では、不図示の上蓋に5基のスパッタリングカソード31(31a〜40e)が設けられているが、スパッタリングカソード31の数はこれに限定されない。各スパッタリングカソード31は、基板ステージ33上の基板25の処理面に対して傾斜すると共に、基板25の中心軸から面方向へ等間隔を隔ててずらしてオフセット配置されている。具体的には、各スパッタリングカソード31のカソード中心軸は、基板ステージ33の回転軸とは外れて位置し、回転軸から所定の距離を隔てた同心円上に等間隔で配置されている。このように同一の真空チャンバー13A内に複数のスパッタリングカソード31を設けることにより、一つの真空チャンバー13A内で積層膜の成膜が可能である。

【0024】

なお、基板径やスパッタリングターゲット(以後ターゲットと記述する)径は特に限定されないが、基板25中心とスパッタリングカソード31中心をオフセット配置させ、本実施形態のように基板25を回転させる場合には、ターゲット径が基板25径より小さくても均一な成膜が可能である。

【0025】

各スパッタリングカソード31におけるカソードの裏面側には、複数の永久磁石(カソード側磁石)を配置したマグネトロンが備えられ、ターゲットの表面側に磁界を形成するようになっている。

【0026】

各スパッタリングカソード31のカソード表面側には、それぞれ板状のターゲット32が取り付けられる。すなわち、各ターゲット32は、スパッタリングカソード31よりも処理空間側に設けられ、各ターゲット32は斜め下方へ臨んで配置されている。ターゲット材料は、基板25上に成膜する膜の種類によって異なる。なお、本実施形態では、5基のスパッタリング31が配置されているので、例えば、材料成分の異なる5種類のターゲットが取り付けられるが、これに限定されない。

【0027】

各スパッタリングカソード31には、スパッタリングカソード31に電圧を印加する不図示の放電用電源が電気的に接続されている。放電用の電源は直流電源と高周波電源を備えており、高周波電源は周波数が1〜100MHzの高周波となる電圧を印加できるようになっている。また、複数のスパッタリングカソード31に電圧を選択的に印加するが、各スパッタリングカソード31に個別の放電用電源を接続してもよいし、共通電源として選択的に電力供給を行うスイッチ等の切り替え機構を備えるように構成しても構わない。

【0028】

さらに、各スパッタリングカソード31のケーシングには、カソード近傍に放電用の処理ガス(放電用ガス)を供給する不図示の放電用ガス導入系が接続されている。放電用ガスとしては、例えば、ArやKrなどの不活性ガスが使用される。各カソードは基板ホルダ21との間でプラズマ放電を発生し、各カソードユニット40に取り付けられたターゲットをスパッタリング可能である。

【0029】

また、各スパッタリングカソード31の前方には、一部のスパッタリングカソード31と基板ステージ33との間を選択的に遮断する不図示のシャッタが設けられている。このシャッタを選択的に開放することにより複数のスパッタリングカソード31の中から目的のターゲットを選択してスパッタリングを実行することができ、スパッタされている他のターゲットからのコンタミネーションを防止することができる。

【0030】

図5は、真空加熱チャンバーの装置構成図である。図1におけるプロセスチャンバー14が真空加熱チャンバーに相当するものである。

図5において、真空チャンバー14の上部に、ハロゲンランプ102からの加熱光を透過する石英窓103が、真空シール部材(不図示)を介して固定されている。この石英窓103は、ハロゲンランプ102から出力された加熱光を真空チャンバー14に入射させるための入射部として機能する。真空シール部材はバイトン(登録商標)やカルレッツ(登録商標)などの耐熱性の高いものが好ましい。図5に示すように真空チャンバー14と石英窓103との間に石英窓脱着用リング104を設けると、石英窓103の脱着がしやすくなる。石英窓103の大きさは基板25の大きさの1.5倍以上となるようにすることが好ましい。また、大気側には加熱光を放射する放射エネルギー源としてのハロゲンランプ102が配置されている。すなわち、ハロゲンランプ102は、真空チャンバー14の外側に、石英窓103に加熱光を照射するように配置される。放射エネルギー源としては、例えば赤外線といった加熱光を放射するものであればハロゲンランプに限る必要はない。ハロゲンランプ103からの加熱光がOリング106に直接照射しないようにハロゲンランプ102と石英窓103との間にリング状の遮蔽板107を設けておく。遮蔽板107は熱伝導の良いアルミ製とし、冷却水路108を設けることにより、冷却水によって冷やされる構造にする。

【0031】

ハロゲンランプ102下方の真空チャンバー14内部には基板25とほぼ同じ直径の基板ステージ33が配置されている。また、水冷ジャケット110は、基板ステージ33と接触させて配置することも可能である。基板ステージ33は熱伝導率の高い誘電体材料を用いることが好ましく、本実施形態ではAlN(窒化アルミニウム)を用いている。

【0032】

尚、図5では、冷却水路112には、冷却水導入口112aと冷却水排出口12bとが接続されており、冷却水導入口112aにはポンプ(不図示)が接続されているが、かならずしも必要ない。

【0033】

基板ステージ33および水冷ジャケット110にはそれぞれ、基板25の大きさの範囲内で外周部に少なくとも3箇所の貫通穴を空け、該貫通穴に基板25を上下動させるためのリフトピン113が挿入されている。リフトピン113はベローズ111を介して大気側にある上下駆動機構115と接続され、該上下駆動機構115の駆動により上下に昇降するようになっている。上下駆動機構115はモーター駆動式もしくは圧縮空気によるエアシリンダー式を用いれば良い。なお、上下駆動機構115は、後述する制御部(図1では不図示)に接続されており、該制御部が上下駆動機構15の駆動を制御することによりリフトピン113の昇降(上下)は制御される。

【0034】

本実施形態では、少なくとも3本のリフトピン113がそれら先端113aで基板25の下面(処理を施す面と対向する面)を支持することにより、基板25はリフトピン113に保持される。すなわち、上記リフトピン113の先端113aにより基板25が保持されることになるので、各リフトピン113の先端113aがそれぞれ基板保持部として機能する。該リフトピン113に保持された基板25は、制御部による上下駆動機構115の制御により、冷却位置P1、搬送位置P2、加熱位置P3に静止する(停止する)ことができ、また冷却位置P1と加熱位置P3との間を移動することができる。図1では、搬送位置P2および加熱位置P3に静止している状態の基板5を便宜上破線で示している。

【0035】

なお、本明細書において、「冷却位置」とは、基板25を冷却する際に基板25が配置されるべき位置であり、本実施形態では、基板ステージ33に基板25が載置される位置を冷却位置P1としている。なお、冷却位置は、基板が基板支持台に載置される位置に限らず、冷却機能を有する基板支持台から生じる冷却効果が作用する範囲であれば、基板支持台に近接した位置であっても良い。

【0036】

また、「加熱位置」とは、冷却位置とは別個の、基板25を加熱する際に基板25が配置されるべき位置であり、放射エネルギー源と冷却機能を有する基板支持台との間の位置であって、冷却位置P1よりも放射エネルギー源に近い位置に設定される。本実施形態では、加熱位置P3は、石英窓3の近傍に設定されている。

【0037】

さらに、「搬送位置」とは、外部から搬送された基板が最初に保持される位置であって、冷却位置P1と加熱位置P3との間に設定される。本実施形態では、搬送位置P2は、基板搬送用のゲートバルブ16の開口と対向する空間であって該開口の幅の範囲内の空間に設定されている。外部から搬送された基板25は、搬送位置P3にてリフトピン13の先端によって保持され、その後、リフトピン113の昇降により加熱位置P3あるいは冷却位置P1へと移動する。なお、搬送位置P3は、上記空間内に設定されることが好ましいが、該空間以外の位置に設定しても良い。何故ならば、図5では、真空一貫で急速加熱および急速冷却を行うことが重要であり、そのために、同一真空チャンバー内に加熱位置P3と冷却位置P1とを別個に設け、加熱処理を加熱位置P3にて行い、冷却処理を冷却位置P1にて行うことが本質である。よって、該本質要件が実現されていれば、搬送位置は、いずれであっても良いのである。なお、基板25の温度は200℃以上であれば良く、加熱時間は温度や対象となる薄膜の材料や膜厚によって最適値を用いれば良い。

【0038】

図4は、本発明に係るスパッタリング装置の第2の例を示す構成図である。図4記載のスパッタリング装置は、基板搬送ロボット11が設けられた搬送チャンバ−12と、搬送チャンバ−12に結合されたスパッタリング成膜チャンバ−13と、プロセスチャンバー14と、ロードロック室15A、15Bとから構成される。スパッタリング成膜チャンバー13(真空チャンバー13A)は2つ以上のカソード31を備えたスパッタリング成膜室であり、スパッタリング成膜チャンバ−13(真空チャンバー13B)は1つのカソード31を備えたスパッタリング成膜室である。スパッタリング成膜チャンバー13(真空チャンバー13A)の2つ以上のカソード31には、それぞれ単一の元素又は複数の元素からなる材料で形成された2つ以上のターゲットが固定されている。スパッタリング成膜チャンバ−13(真空チャンバー13B)のカソード31には、単一の元素からなる材料で形成されたターゲットが固定されている。スパッタリング成膜チャンバー13(真空チャンバー13A)とスパッタリング成膜チャンバー13(真空チャンバー13B)とプロセスチャンバー14とロードロック室15A、15Bとの間の基板25の移動は、搬送チャンバ−12に設けられた基板搬送ロボット11によって行われる。

【0039】

次に、本発明の基本的な原理について説明する。

本発明者らは、基板上に(100)優先配向のスピネルフェライト薄膜を製造する方法であって、スパッタリング法でスピネルフェライト薄膜もしくはその前駆体となる薄膜を基板上に形成するスパッタ成膜ステップと、その基板を真空中で加熱する真空加熱ステップとを有する製造方法を用いることにより、基板上に、ミラー指数(100)の結晶面を有するスピネルフェライト多結晶薄膜が得られることを見出し、本発明を完成するに至った。ここで、本明細書において、「格子定数」とは、単位格子の結晶軸としての3稜の長さと、3稜が相互になす3種類の角度を合わせた6個の定数をいう。「ミラー指数」とは、結晶面が3つの結晶軸と交わる3点の座標を各格子定数を単位として求め、それぞれの逆数に適当な数をかけて互いに素の整数(h、k、l)として表したものをいう。

【0040】

下記表1は、スピネルフェライト構造を有する酸化物の格子定数と陽イオン分布を示す。

【0041】

【表1】

【0042】

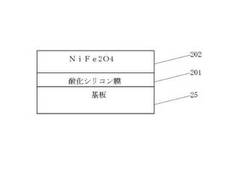

図10は、Si基板25面にアモルファスの酸化シリコン201が100nm形成された酸化膜付きシリコン基板を用いて、図1記載のスパッタリング装置により、絶縁膜(MgO)207を形成し、その後、絶縁膜(MgO)207表面上に、スピネルフェライト多結晶薄膜を形成した場合を示す。スピネルフェライト構造を有する酸化物の格子定数は、絶縁膜(MgO)207の格子定数(4.213Å)の約2倍である。そのため、格子のマッチングがよい。そのため、スパッタリング法でスピネルフェライト薄膜もしくはその前駆体となる薄膜を基板上に形成するスパッタ成膜ステップと、その基板を真空中で加熱する真空加熱ステップとからなる製造方法を用いると、ミラー指数(100)の絶縁膜(MgO)207表面上に、ミラー指数(100)のスピネルフェライト多結晶薄膜が得られることを、発明者は見出した。

【0043】

発明者は、スパッタリングカソードに印加する電圧の周波数が1〜100MHzの高周波とすることにより、絶縁性の酸化物ターゲットの場合においてもスパッタ成膜することが可能となることを見出した。

発明者は、スパッタリングカソードに設置するターゲット材料がM:Fe:Oの比率が略x:3−x:4(Mは、Zn、Mn、Co、Ni、Cu、Mg、Li、Feのいずれか1つ、かつ、0<x<3)である複合酸化物ターゲットとすることより、基板上にスピネルフェライト薄膜またはその前駆体となる薄膜を形成することが可能となることを見出した。

発明者は、スパッタリングガスとしてアルゴンガスのみを用い、その圧力を0.1Pa以下とすることより、下地層が金属薄膜である場合にその表面がスピネルフェライト薄膜の成膜中に酸化することを抑制することが可能となることを見出した。

発明者は、薄膜が堆積される基板温度を室温とすることより、下地層がアモルファス構造を有した金属である場合に熱による結晶化を防ぐことが可能となることを見出した。

発明者は、スパッタ成膜ステップにおける基板を200℃未満とすることにより、下地層がアモルファス構造を有した金属である場合に熱による結晶化を抑制することが可能となることを見出した。

発明者は、CoまたはFeを主成分とし、アモルファス構造を有した磁性金属薄膜が表面に付着した基板を用いることにより、スピネルフェライト薄膜の(100)優先配向を促進することが可能となることを見出した。

発明者は、スピネルフェライト薄膜の膜厚が100nm以下とすることにより、スピンフィルタ効果素子として有効に動作することが可能となることを見出した。

【0044】

次に、図1と図2を参照して、本実施形態のスパッタリング装置の作用と共に、この装置を用いて実施するスピネルフェライト薄膜の製造方法について説明する。

【0045】

本発明に係るスパッタ成膜方法は、まず、基板ステージ33上に処理対象である基板25を設置する。基板25は、例えば、隣接する搬送チャンバー12に備えられた基板搬送ロボット11により、ゲートバルブ16を通じて真空チャンバー13A内の真空度を維持したまま基板ステージ33上に運ばれる。

【0046】

次に、真空チャンバー13Aの内部に不図示の放電用ガス導入系からAr等の放電用ガスを導入する。

【0047】

5基のカソードユニット31には、例えば、それぞれ材料成分の異なる5種類のターゲ

ット32を取り付ける。各ターゲット32は、例えば、円板状を呈し、全て同じサイズに形成されている。前述したように、カソードの傾斜角は本発明の適用においては特に限定されないが、基板25の処理面の法線に対するカソード中心軸の角度θが0°を超えて45°以下の角度を成すようにカソードユニット31を配置することが好ましい。より好ましくは、上記角度θを5°以上35°以下に設定すると、優れた面内均一性が得られる。

【0048】

この状態で、まず、第1のカソードユニット31aのターゲット32a表面に、不図示の電源から放電用電力を供給して、基板ステージ33との間でプラズマ放電を発生させて、第1ターゲット32をスパッタリングし、基板25上に第1層を成膜する。

【0049】

その後、順次電源を切り替え、第2カソードユニット40bから第5カソードユニット

40eについても、同様にして成膜操作を行う。

【0050】

成膜終了後、スパッタ成膜チャンバーのゲートバルブ16を通じて搬送チャンバー12の基板搬送ロボット11によって基板25を搬出し、次いで真空加熱チャンバー14のゲートバルブ16を通じて真空加熱チャンバー14内の基板ステージ33上に基板25を載置する。

【実施例】

【0051】

次に本発明の実施例について図面を用いて説明する。

【実施例1】

【0052】

図6記載のスピネルフェライト薄膜の成膜手順について説明する。未処理基板25をロードロック室15Aから基板搬送ロボット11を用いて、搬送チャンバー12内の不図示の載置台に載置する。次に、基板搬送ロボット11により、基板25をスパッタリング成膜チャンバー13に搬入する。

図2記載のスパッタリングターゲット32として直径164mmのNiFeOの複合酸化物ターゲットを用いた。この時、Ni:Fe:Oの比率は、1:2:4とした。基板25の法線に対するターゲット32の法線の傾斜角を30°、T(ターゲット)/S(基板)距離を240mm、ターゲット32に供給する電力を直流200W、基板25の回転速度を100rpm一定とした。また、基板ステージ33の内部に冷却水を流すことによって成膜中の基板温度を室温に維持した。導入するArガス流量は20sccm、100sccm、200sccmの3通り実施した。この時のArガス圧は、それぞれ0.02、0.1、0.2Paであった(ただし、圧力の値は真空計をとりつける位置や真空計の種類によって誤差が生じるため、実際に放電が起きている空間の圧力は上述の圧力よりも高くなっていることが予想される)。薄膜の膜厚は30nmに統一し、成膜時間によって制御した。成膜後、基板25をスパッタリング成膜チャンバー13(真空チャンバー13A)から、基板搬送ロボット11により、真空加熱チャンバー14に搬送する。基板加熱は、図5記載の真空加熱チャンバー14を用いて行う。ハロゲンランプ102からの輻射線を照射することによって基板25を700℃に加熱し、10分間の真空熱処理を行った。基板25は表面にアモルファスの酸化シリコン201が100nm形成された酸化膜付きシリコン基板を用いた上記酸化膜付きシリコン基板201上にNiFe2O4のスピネルフェライト薄膜を成膜した。図3は成膜した薄膜のX線回折パターンである。尚、図3の(1)はArガス流量20sccm(=0.02Pa)の条件で図3の(2)はArガス流量100sccm(=0.1Pa)の条件で、図3の(3)はArガス流量200sccm(=0.2Pa)の条件でスピネルフェライト薄膜をそれぞれ成膜した場合を示す。いずれの条件においてもNiFe2O4のスピネルフェライト結晶の回折パターンが得られているが、Ar流量が20sccm(=0.02Pa)の条件では、(400)ピークが他の回折ピークと比較して著しく高く、(100)優先配向膜が得られていることがわかった。すなわち、室温、アモルファス下地、100nm以下の薄膜そして酸素添加を行わないというスピンフィルタ効果素子向けのスパッタ成膜条件においても、低ガス圧、ロングスロー(T/S距離が長い)での成膜を行うことにより、真空熱処理後に(100)に優先配向したスピネルフェライト薄膜が実現できることを示している。

【実施例2】

【0053】

図7記載のスピネルフェライト薄膜の成膜手順について説明する。実施例2においては、スパッタ成膜チャンバー13(真空チャンバー13A)内にB濃度を10at%以上含んだCoFeB合金ターゲット32を設置し、NiFeO202を成膜する前に、表面にアモルファスの酸化シリコン201が100nm形成された酸化膜付きシリコン基板201上にアモルファスCoFeB薄膜203を成膜して、次いでNiFeO202を成膜しても、真空熱処理後に(100)優先配向したスピネルフェライト薄膜が得られる。

【実施例3】

【0054】

図7記載のスピネルフェライト薄膜の成膜手順について、図4を用いて説明する。実施例3においては、図4に記載のように、NiFeOのスパッタ成膜チャンバー13(真空チャンバー13A)とは別に類似のスパッタ成膜チャンバー13(真空チャンバー13B)を搬送チャンバー12に追加接続し、そのチャンバー13Bの中でアモルファスCoFeB薄膜203を成膜してから、NiFeO201のスパッタ成膜チャンバー13(真空チャンバー13A)に基板を搬送してNiFeO202をスパッタ成膜しても同様の効果が得られる。

【実施例4】

【0055】

実施例1〜3において、真空加熱チャンバーでの加熱条件は700℃である必要はなく、200℃以上であれば同様の効果が得られる。

【実施例5】

【0056】

実施例1〜4において、スパッタリングターゲット32はNiFeOの複合酸化物でなくても良く、M:Fe:Oの比率が略x:3−x:4(Mは、Zn、Mn、Co、Ni、Cu、Mg、Li、Feのいずれか1つ、かつ、0<x<3)である複合酸化物ターゲットであれば同様の効果が得られる。

【実施例6】

【0057】

実施例1〜5において、T(ターゲット)/S(基板)距離が100mm以上であれば同様の効果が得られる。

【実施例7】

【0058】

図8は、図7記載のアモルファスCoFeB強磁性層の下に反強磁性層205(例えば、PtMn)、さらにその下に反強磁性層205の下地膜204(例えばTa)スピネルフェライト薄膜の上に保護膜となる電極層206(例えば、Ru)を作成した例を示す。なお、反強磁性層205(例えば、PtMn)、下地膜204(例えばTa)、保護膜となる電極層206(例えば、Ru)は、スパッタリング法により作成した。これにより、スピンフィルタ効果が得られる。

【実施例8】

【0059】

図9は、図8記載のスピネルフェライト薄膜上に、絶縁膜207(例えば、MgO)を積層した例を示す。なお、絶縁膜207(例えば、MgO)は、スパッタリング法により作成した。これにより、スピンフィルタ効果が得られる。

【符号の説明】

【0060】

12 搬送チャンバー

13 スパッタリングチャンバー

13A 真空チャンバーA

13B 真空チャンバーB

14 加熱チャンバー

25 基板

31 スパッタリングカソード

32 スパッタリングターゲット

【技術分野】

【0001】

本発明は、スピンフィルタ効果素子およびそれを利用した磁気デバイスに用いるスピネルフェライト薄膜の製造方法に関する。

【背景技術】

【0002】

スピネル型結晶構造を有したフェライト薄膜(以下、スピネルフェライト薄膜と言う)は、サーミスタ素子(特許文献1〜5参照)やスピンフィルタ効果素子に用いられている(特許文献6〜7参照)。

【0003】

上述のスピネルフェライト薄膜はデバイス特性上スピネル型結晶構造を有し、さらに(100)面に優先配向していることが好ましい。それを実現するための従来技術としては、スパッタリング法によってスピネルフェライト薄膜を基板上に成膜する際、スパッタ成膜中に微量の酸素を添加する(特許文献1〜5、8)、スパッタ成膜中の基板を200℃以上に加熱する(特許文献1〜8)、さらに結晶化を促進するために成膜後に基板を高温で熱処理する(特許文献1〜5、8)方法が知られている。スピネルフェライトのスパッタ成膜中に酸素を添加しない場合では、成膜後の熱処理によって結晶化は促進するが(100)優先配向しないことが知られている(特許文献2、8)。

ところでスピンフィルタ効果素子においては、スピネルフェライト薄膜は積層構造の中に配置され、その膜厚は100nm以下であり、スピネルフェライト層の上下界面のうち少なくとも一方は磁性または非磁性の金属層と接している(特許文献6、7)。

【0004】

図11は特許文献6のスピンフィルタ効果素子の構成を示す断面図である。図11記載のスピンフィルタ効果素子901は、高抵抗のスピネルフェライト912の薄膜が第1の電極である非磁性電極911と第2の電極である強磁性電極913との間に挿入された構造を有している。直流電源914は、第1の電極911と第2の電極913に印加され、外部磁界15が膜面内に平行に印加されている。

【0005】

ここで、高抵抗のスピネルフェライト912は、強磁性を有し、その厚さはトンネル現象が生起するように十分に薄く形成されている。直流電源914は、非磁性電極911からの電子が、スピネルフェライト12中をトンネルして、強磁性電極13へ流れるように、非磁性電極11側を負とする向きに接続する。

【0006】

図12は、特許文献6記載のスピンフィルタ効果素子の動作を説明するためのエネルギー準位を示す模式図である。図12において、Φ↓(下向き矢印)は、第1の電極のフェルミ準位からの高抵抗のスピネルフェライト912の↓(下向き矢印)スピンバンドの電位障壁高さである。また、高抵抗のスピネルフェライト912は、強磁性体であるため、↑(上向き矢印)スピンバンドのエネルギー準位は、Φ↓と異なるΦ↑(上向き矢印)で示す。図12に示すように、Φ↑がΦ↓よりも小さいので、スピン電子e↑のみが、Φ↑のトンネル障壁を介して強磁性電極913側にトンネルすることができる。

【0007】

このように、トンネル障壁がスピンに依存することで、非磁性金属電極911からのトンネル電子による抵抗、または、コンダクタンスは、スピンに依存し、スピンに依存したトンネル現象を示す。すなわち、トンネル障壁はスピンフィルタとして働く。

従って、特許文献6のスピンフィルタ素子901では、高抵抗のスピネルフェライト912のエネルギー準位のスピン分裂が大きいほど、より大きなスピンフィルタ効果が得られる。また、特許文献6のスピンフィルタ素子901では外部磁界915を印加し、このスピンフィルタ効果を利用すると共に、外部磁界により第2電極の強磁性層のスピンを反転させることによって、大きなトンネル磁気抵抗効果が得られる。

【0008】

図11に示す特許文献6のスピンフィルタ効果素子の第2の電極913は、強磁性電極上に、さらに反強磁性層を積層して形成することができる。この構造では、スピンバルブ効果により強磁性電極の磁化は、反強磁性層との交換相互作用により、スピンが1方向に固定されるので、電極913のスピンの平行、反平行を容易に得ることができるため、特許文献6のスピンフィルタ効果素子のTMRは更に大きくなる。

また、特許文献6のスピンフィルタ効果素子の第2の電極913の強磁性電極、または、反強磁性層の上には、さらに保護膜となる非磁性の電極層を堆積させることが好ましい。特許文献6のスピンフィルタ効果素子901は、スパッタ法、蒸着法、レーザアブレーション法、MBE法などの通常の薄膜成膜法を用いて成膜することができる。

【先行技術文献】

【特許文献】

【0009】

【特許文献1】特開昭60−208803号公報

【特許文献2】特開昭63−266801号公報

【特許文献3】特開2000−348905号公報

【特許文献4】特開2000−348903号公報

【特許文献5】特開2008−84991号公報

【特許文献6】特開2004−39672号公報

【特許文献7】特開2009−105415号公報

【特許文献8】特開平4−260695号公報

【発明の概要】

【発明が解決しようとする課題】

【0010】

従来の方法でスピンフィルタ素子用のスピネルフェライト薄膜を成膜すると、スパッタ成膜中にArガスに添加した酸素ガスが下部の金属電極層の表面を酸化させてスピンフィルタ効率を低下させてしまうという問題があった。Arガスのみでスパッタ成膜した場合には、成膜後に熱処理を行うことによって結晶化を促進するが、その場合にはスピネルフェライト薄膜が(100)配向しないという問題があった。成膜中に基板を加熱すると下部の金属電極層とスピネルフェライト薄膜が熱拡散し、スピンフィルタ効率を低下させてしまうという問題があった。また下部の金属電極層の結晶構造がアモルファスである場合には、金属電極層が結晶化してしまうことにより、スピネルフェライト薄膜のスパッタ成膜において、スピネルフェライト薄膜が(100)優先配向しないという問題があった。スピネルフェライト薄膜の成膜後に結晶化を促進するための熱処理を大気中で行うと、その次に成膜される層との界面が大気成分で汚染されてしまうため、スピンフィルタ効率を低下させてしまうという問題があった。

【0011】

そこで本発明は上記事情に鑑みて、積層構造の中にスピネルフェライト薄膜を配置したスピンフィルタ効果素子において、スピネルフェライト薄膜下部の金属電極層の酸化および下部界面の熱拡散を抑制し、上部界面の大気成分による汚染を排除しつつ、(100)優先配向したスピネルフェライト薄膜を製造する方法を提供する。

【課題を解決するための手段】

【0012】

上記目的を達成するために、請求項1記載の発明は、基板上に(100)優先配向のスピネルフェライト薄膜を製造する方法であって、前記製造方法は、スパッタリング法でスピネルフェライト薄膜もしくはその前駆体となる薄膜を基板上に形成するスパッタ成膜ステップと、その基板を真空中で加熱する真空加熱ステップとを有することを特徴とするスピネルフェライト薄膜のスピネルフェライト薄膜の製造方法としたものである。

さらに、請求項2記載の発明は、請求項1に記載の製造方法において、前記スパッタ成膜ステップは、スパッタリングカソードに印加する電圧の周波数が1〜100MHzの高周波であり、スパッタリングカソードに設置するターゲット材料がM:Fe:Oの比率が略x:3−x:4(Mは、Zn、Mn、Co、Ni、Cu、Mg、Li、Feのいずれか1つ、かつ、0<x<3)で構成された複合酸化物ターゲットであり、スパッタリングガスはアルゴンガスのみでその圧力は0.1Pa以下であり、 薄膜が堆積される基板温度は室温であり、前記ターゲットと前記基板との間の距離が100mm以上であることを特徴とするスピネルフェライト薄膜の製造方法としたものである。

さらに、請求項1又は請求項2に記載の製造方法において、前記スパッタ成膜ステップにおける基板が200℃未満であることを特徴とするスピネルフェライト薄膜の製造方法としたものである。

さらに、請求項4記載の発明は、請求項1〜3のいずれか1項に記載の製造方法において、前記基板はCoまたはFeを主成分とし、アモルファス構造を有した磁性金属薄膜が表面に付着していることを特徴とするスピネルフェライト薄膜の製造方法としたものである。

さらに、請求項5記載の発明は、請求項1〜4のいずれか1項に記載の製造方法において、前記スピネルフェライト薄膜の膜厚が100nm以下であることを特徴とするスピネルフェライト薄膜の製造方法としたものである。

【発明の効果】

【0013】

本願の請求項1の発明によれば、スパッタリング法でスピネルフェライト薄膜もしくはその前駆体となる薄膜を基板上に形成するスパッタ成膜ステップと、その基板を真空中で加熱する真空加熱ステップとを有することを特徴とする製造方法を用いることにより、大部分が第二の結晶面を基板面に対して平行となるような結晶粒を多数含むスピネルフェライト多結晶薄膜を形成することが可能となる。そのため、アモルファス構造を有した基板上に、ミラー指数(100)の結晶面を有するスピネルフェライト多結晶薄膜が得ることが可能となる。

本願の請求項2の発明によれば、スパッタリングカソードに印加する電圧の周波数が1〜100MHzの高周波とすることにより、絶縁性の酸化物ターゲットの場合においてもスパッタ成膜することが可能となる。

また、本願の請求項2記載の発明によれば、スパッタリングカソードに設置するターゲット材料がM:Fe:Oの比率が略x:3−x:4(Mは、Zn、Mn、Co、Ni、Cu、Mg、Li、Feのいずれか1つ、かつ、0<x<3)である複合酸化物ターゲットとすることより、基板上にスピネルフェライト薄膜またはその前駆体となる薄膜を形成することが可能となる。

また、本願の請求項2記載の発明によれば、スパッタリングガスとしてアルゴンガスのみを用い、その圧力を0.1Pa以下とすることより、下地層が金属薄膜である場合にその表面がスピネルフェライト薄膜の成膜中に酸化することを抑制することが可能となる。

また、本願の請求項2記載の発明によれば、薄膜が堆積される基板温度を室温とすることより、下地層がアモルファス構造を有した金属である場合に熱による結晶化を防ぐことが可能となる。

さらに、本願の請求項3記載の発明によれば、スパッタ成膜ステップにおける基板を200℃未満とすることにより、下地層がアモルファス構造を有した金属である場合に熱による結晶化を抑制することが可能となる。

さらに、本願の請求項4記載の発明によれば、CoまたはFeを主成分とし、アモルファス構造を有した磁性金属薄膜が表面に付着した基板を用いることにより、スピネルフェライト薄膜の(100)優先配向を促進することが可能となる。

さらに、本願の請求項5記載の発明によれば、スピネルフェライト薄膜の膜厚が100nm以下とすることにより、スピンフィルタ効果素子として有効に動作することが可能となる。

【図面の簡単な説明】

【0014】

【図1】本発明のスピネルフェライト薄膜に成膜に用いるスパッタリング装置の第1の例を示す平面図である。

【図2】本発明のスピネルフェライト薄膜の成膜に用いるスパッタ成膜チャンバーの第1の例の断面図である。

【図3】本発明の製造方法を用いて成膜したスピネルフェライト薄膜のX線回折パターンである。

【図4】本発明のスピネルフェライト薄膜の成膜に用いるスパッタリング装置の第2の例を示す平面図である。

【図5】本発明のスピネルフェライト薄膜に成膜に用いる真空加熱チャンバーの装置構成図である。

【図6】本発明の製造方法を用いて作製したスピンフィルタ効果素子の第1の膜構成図である。

【図7】本発明の製造方法を用いて作製したスピンフィルタ効果素子の第2の膜構成図である。

【図8】本発明の製造方法を用いて作製したスピンフィルタ効果素子の第3の膜構成図である。

【図9】本発明の製造方法を用いて作製したスピンフィルタ効果素子の第4の膜構成図である。

【図10】本発明の製造方法を用いて作製したスピンフィルタ効果素子の第5の膜構成図である。

【図11】従来(特許文献6)のスピンフィルタ効果素子の構成を示す断面図である。

【図12】従来(特許文献6)記載のスピンフィルタ効果素子の動作を説明するためのエネルギー準位を示す模式図である。

【発明を実施するための形態】

【0015】

以下、図面を参照して、本発明の実施の形態を説明するが、本発明は本実施形態に限定

されるものではない。

【0016】

図1と図2を参照して、本発明に係るスパッタリング装置の一実施の形態について説明する。図1は本実施形態のスパッタリング装置を模式的に示す平面図である。また、図2はスパッタ成膜チャンバーの断面図である。なお、図2は図1のスパッタ成膜チャンバーのAOB断面に相当する。

【0017】

図1のスパッタリング装置は、基板搬送ロボット11が設けられた搬送チャンバー12と、搬送チャンバー12に結合されたスパッタリング成膜チャンバー13と、プロセスチャンバー14と、ロードロック室15A、15Bとから構成される。スパッタリング成膜チャンバー13は2つ以上のカソード31を備えたスパッタリング成膜室である。スパッタリング成膜チャンバー13の2つ以上のカソード31には、それぞれ単一の元素又は複数の元素からなる材料で形成された2つ以上のターゲットが固定されている。スパッタリング成膜チャンバー13とプロセスチャンバー14とロードロック室15A、15Bとの間の基板25の移動は、搬送チャンバー12に設けられた基板搬送ロボット11によって行われる。図1において、スパッタリング成膜チャンバー13は1つの真空チャンバー13Aで構成されている。

【0018】

上記に挙げた全てのチャンバーとロードロック室15A、15Bは、各々チャンバー内を真空に排気するための真空ポンプを有していることが好ましく、ロードロック室15A、15B以外のチャンバーは常時真空に維持されている。なお、後述する全ての実施形態において、全てのチャンバーとロードロック室が真空ポンプを有していることを前提としている。

【0019】

ロードロック室15A、15Bはプロセス前に基板25を大気から入れる場合と、プロセス後に基板25を大気に出す場合は大気圧と同等の圧力に維持され、ロードロック室15A、15Bに配置した基板25を真空に排気された搬送チャンバー12内に搬入する場合と、プロセス後に基板25を回収する場合は真空に排気されている。ロードロック室15A、15Bは必ずしも2つある必要は無く1つでも良い。

【0020】

スパッタリング成膜チャンバー13とプロセスチャンバー14とロードロック室15A、15Bのそれぞれの室の間にはゲートバルブ16が設けられている。各ゲートバルブ16は基板25を搬送する場合以外は閉じられている。基板搬送ロボット11はロードロック室15A、15Bから基板25を取り出し、コンピュータプログラムからの命令によって所望のチャンバーに基板25を搬入するようになっている。

【0021】

複数のスパッタリングカソード31を備えたスパッタリング成膜チャンバー13は、図2に示すように真空チャンバー13Aの上部に複数のスパッタリングカソード31を配置している。真空チャンバー13A内部の下方には真空チャンバー13A外部に備えられた動力源(不図示)によって回転可能な基板ステージ33があり、少なくとも成膜時には基板ステージ33の上に薄膜を堆積させるための基板25を載置する。基板25とスパッタリングターゲット32の間にシャッターを配置しておき、電力投入をし続けたままシャッターの開閉によって膜厚を制御しても良い。多層薄膜を成膜する場合は、回転する基板ステージ33上に基板25を載置させたまま上記の成膜操作を順次行えば良い。なお、図1においては、スパッタリング成膜チャンバー13には5種類のターゲット31が設置され、その材質はPtMn,CoFe,Ru、CoFeBである。また、ゲートバルブ16が、Oリング34を介して真空チャンバー13Aの側壁に設けられている。

【0022】

尚、基板ステージ33は、不図示の真空用回転導入機を介して不図示の回転駆動機構に接続されて、真空を維持しながらその中心軸周りに回転可能に構成されており、載置面に載置する基板25を処理面に沿って回転するようになっている。真空用回転導入機としては磁性流体を用いるが、これに限定されるものではない。

基板25の材料としては、例えば、円板状のシリコンウェハを用いるが、これに限定されるものではない。

【0023】

図1に示すように、本実施形態では、不図示の上蓋に5基のスパッタリングカソード31(31a〜40e)が設けられているが、スパッタリングカソード31の数はこれに限定されない。各スパッタリングカソード31は、基板ステージ33上の基板25の処理面に対して傾斜すると共に、基板25の中心軸から面方向へ等間隔を隔ててずらしてオフセット配置されている。具体的には、各スパッタリングカソード31のカソード中心軸は、基板ステージ33の回転軸とは外れて位置し、回転軸から所定の距離を隔てた同心円上に等間隔で配置されている。このように同一の真空チャンバー13A内に複数のスパッタリングカソード31を設けることにより、一つの真空チャンバー13A内で積層膜の成膜が可能である。

【0024】

なお、基板径やスパッタリングターゲット(以後ターゲットと記述する)径は特に限定されないが、基板25中心とスパッタリングカソード31中心をオフセット配置させ、本実施形態のように基板25を回転させる場合には、ターゲット径が基板25径より小さくても均一な成膜が可能である。

【0025】

各スパッタリングカソード31におけるカソードの裏面側には、複数の永久磁石(カソード側磁石)を配置したマグネトロンが備えられ、ターゲットの表面側に磁界を形成するようになっている。

【0026】

各スパッタリングカソード31のカソード表面側には、それぞれ板状のターゲット32が取り付けられる。すなわち、各ターゲット32は、スパッタリングカソード31よりも処理空間側に設けられ、各ターゲット32は斜め下方へ臨んで配置されている。ターゲット材料は、基板25上に成膜する膜の種類によって異なる。なお、本実施形態では、5基のスパッタリング31が配置されているので、例えば、材料成分の異なる5種類のターゲットが取り付けられるが、これに限定されない。

【0027】

各スパッタリングカソード31には、スパッタリングカソード31に電圧を印加する不図示の放電用電源が電気的に接続されている。放電用の電源は直流電源と高周波電源を備えており、高周波電源は周波数が1〜100MHzの高周波となる電圧を印加できるようになっている。また、複数のスパッタリングカソード31に電圧を選択的に印加するが、各スパッタリングカソード31に個別の放電用電源を接続してもよいし、共通電源として選択的に電力供給を行うスイッチ等の切り替え機構を備えるように構成しても構わない。

【0028】

さらに、各スパッタリングカソード31のケーシングには、カソード近傍に放電用の処理ガス(放電用ガス)を供給する不図示の放電用ガス導入系が接続されている。放電用ガスとしては、例えば、ArやKrなどの不活性ガスが使用される。各カソードは基板ホルダ21との間でプラズマ放電を発生し、各カソードユニット40に取り付けられたターゲットをスパッタリング可能である。

【0029】

また、各スパッタリングカソード31の前方には、一部のスパッタリングカソード31と基板ステージ33との間を選択的に遮断する不図示のシャッタが設けられている。このシャッタを選択的に開放することにより複数のスパッタリングカソード31の中から目的のターゲットを選択してスパッタリングを実行することができ、スパッタされている他のターゲットからのコンタミネーションを防止することができる。

【0030】

図5は、真空加熱チャンバーの装置構成図である。図1におけるプロセスチャンバー14が真空加熱チャンバーに相当するものである。

図5において、真空チャンバー14の上部に、ハロゲンランプ102からの加熱光を透過する石英窓103が、真空シール部材(不図示)を介して固定されている。この石英窓103は、ハロゲンランプ102から出力された加熱光を真空チャンバー14に入射させるための入射部として機能する。真空シール部材はバイトン(登録商標)やカルレッツ(登録商標)などの耐熱性の高いものが好ましい。図5に示すように真空チャンバー14と石英窓103との間に石英窓脱着用リング104を設けると、石英窓103の脱着がしやすくなる。石英窓103の大きさは基板25の大きさの1.5倍以上となるようにすることが好ましい。また、大気側には加熱光を放射する放射エネルギー源としてのハロゲンランプ102が配置されている。すなわち、ハロゲンランプ102は、真空チャンバー14の外側に、石英窓103に加熱光を照射するように配置される。放射エネルギー源としては、例えば赤外線といった加熱光を放射するものであればハロゲンランプに限る必要はない。ハロゲンランプ103からの加熱光がOリング106に直接照射しないようにハロゲンランプ102と石英窓103との間にリング状の遮蔽板107を設けておく。遮蔽板107は熱伝導の良いアルミ製とし、冷却水路108を設けることにより、冷却水によって冷やされる構造にする。

【0031】

ハロゲンランプ102下方の真空チャンバー14内部には基板25とほぼ同じ直径の基板ステージ33が配置されている。また、水冷ジャケット110は、基板ステージ33と接触させて配置することも可能である。基板ステージ33は熱伝導率の高い誘電体材料を用いることが好ましく、本実施形態ではAlN(窒化アルミニウム)を用いている。

【0032】

尚、図5では、冷却水路112には、冷却水導入口112aと冷却水排出口12bとが接続されており、冷却水導入口112aにはポンプ(不図示)が接続されているが、かならずしも必要ない。

【0033】

基板ステージ33および水冷ジャケット110にはそれぞれ、基板25の大きさの範囲内で外周部に少なくとも3箇所の貫通穴を空け、該貫通穴に基板25を上下動させるためのリフトピン113が挿入されている。リフトピン113はベローズ111を介して大気側にある上下駆動機構115と接続され、該上下駆動機構115の駆動により上下に昇降するようになっている。上下駆動機構115はモーター駆動式もしくは圧縮空気によるエアシリンダー式を用いれば良い。なお、上下駆動機構115は、後述する制御部(図1では不図示)に接続されており、該制御部が上下駆動機構15の駆動を制御することによりリフトピン113の昇降(上下)は制御される。

【0034】

本実施形態では、少なくとも3本のリフトピン113がそれら先端113aで基板25の下面(処理を施す面と対向する面)を支持することにより、基板25はリフトピン113に保持される。すなわち、上記リフトピン113の先端113aにより基板25が保持されることになるので、各リフトピン113の先端113aがそれぞれ基板保持部として機能する。該リフトピン113に保持された基板25は、制御部による上下駆動機構115の制御により、冷却位置P1、搬送位置P2、加熱位置P3に静止する(停止する)ことができ、また冷却位置P1と加熱位置P3との間を移動することができる。図1では、搬送位置P2および加熱位置P3に静止している状態の基板5を便宜上破線で示している。

【0035】

なお、本明細書において、「冷却位置」とは、基板25を冷却する際に基板25が配置されるべき位置であり、本実施形態では、基板ステージ33に基板25が載置される位置を冷却位置P1としている。なお、冷却位置は、基板が基板支持台に載置される位置に限らず、冷却機能を有する基板支持台から生じる冷却効果が作用する範囲であれば、基板支持台に近接した位置であっても良い。

【0036】

また、「加熱位置」とは、冷却位置とは別個の、基板25を加熱する際に基板25が配置されるべき位置であり、放射エネルギー源と冷却機能を有する基板支持台との間の位置であって、冷却位置P1よりも放射エネルギー源に近い位置に設定される。本実施形態では、加熱位置P3は、石英窓3の近傍に設定されている。

【0037】

さらに、「搬送位置」とは、外部から搬送された基板が最初に保持される位置であって、冷却位置P1と加熱位置P3との間に設定される。本実施形態では、搬送位置P2は、基板搬送用のゲートバルブ16の開口と対向する空間であって該開口の幅の範囲内の空間に設定されている。外部から搬送された基板25は、搬送位置P3にてリフトピン13の先端によって保持され、その後、リフトピン113の昇降により加熱位置P3あるいは冷却位置P1へと移動する。なお、搬送位置P3は、上記空間内に設定されることが好ましいが、該空間以外の位置に設定しても良い。何故ならば、図5では、真空一貫で急速加熱および急速冷却を行うことが重要であり、そのために、同一真空チャンバー内に加熱位置P3と冷却位置P1とを別個に設け、加熱処理を加熱位置P3にて行い、冷却処理を冷却位置P1にて行うことが本質である。よって、該本質要件が実現されていれば、搬送位置は、いずれであっても良いのである。なお、基板25の温度は200℃以上であれば良く、加熱時間は温度や対象となる薄膜の材料や膜厚によって最適値を用いれば良い。

【0038】

図4は、本発明に係るスパッタリング装置の第2の例を示す構成図である。図4記載のスパッタリング装置は、基板搬送ロボット11が設けられた搬送チャンバ−12と、搬送チャンバ−12に結合されたスパッタリング成膜チャンバ−13と、プロセスチャンバー14と、ロードロック室15A、15Bとから構成される。スパッタリング成膜チャンバー13(真空チャンバー13A)は2つ以上のカソード31を備えたスパッタリング成膜室であり、スパッタリング成膜チャンバ−13(真空チャンバー13B)は1つのカソード31を備えたスパッタリング成膜室である。スパッタリング成膜チャンバー13(真空チャンバー13A)の2つ以上のカソード31には、それぞれ単一の元素又は複数の元素からなる材料で形成された2つ以上のターゲットが固定されている。スパッタリング成膜チャンバ−13(真空チャンバー13B)のカソード31には、単一の元素からなる材料で形成されたターゲットが固定されている。スパッタリング成膜チャンバー13(真空チャンバー13A)とスパッタリング成膜チャンバー13(真空チャンバー13B)とプロセスチャンバー14とロードロック室15A、15Bとの間の基板25の移動は、搬送チャンバ−12に設けられた基板搬送ロボット11によって行われる。

【0039】

次に、本発明の基本的な原理について説明する。

本発明者らは、基板上に(100)優先配向のスピネルフェライト薄膜を製造する方法であって、スパッタリング法でスピネルフェライト薄膜もしくはその前駆体となる薄膜を基板上に形成するスパッタ成膜ステップと、その基板を真空中で加熱する真空加熱ステップとを有する製造方法を用いることにより、基板上に、ミラー指数(100)の結晶面を有するスピネルフェライト多結晶薄膜が得られることを見出し、本発明を完成するに至った。ここで、本明細書において、「格子定数」とは、単位格子の結晶軸としての3稜の長さと、3稜が相互になす3種類の角度を合わせた6個の定数をいう。「ミラー指数」とは、結晶面が3つの結晶軸と交わる3点の座標を各格子定数を単位として求め、それぞれの逆数に適当な数をかけて互いに素の整数(h、k、l)として表したものをいう。

【0040】

下記表1は、スピネルフェライト構造を有する酸化物の格子定数と陽イオン分布を示す。

【0041】

【表1】

【0042】

図10は、Si基板25面にアモルファスの酸化シリコン201が100nm形成された酸化膜付きシリコン基板を用いて、図1記載のスパッタリング装置により、絶縁膜(MgO)207を形成し、その後、絶縁膜(MgO)207表面上に、スピネルフェライト多結晶薄膜を形成した場合を示す。スピネルフェライト構造を有する酸化物の格子定数は、絶縁膜(MgO)207の格子定数(4.213Å)の約2倍である。そのため、格子のマッチングがよい。そのため、スパッタリング法でスピネルフェライト薄膜もしくはその前駆体となる薄膜を基板上に形成するスパッタ成膜ステップと、その基板を真空中で加熱する真空加熱ステップとからなる製造方法を用いると、ミラー指数(100)の絶縁膜(MgO)207表面上に、ミラー指数(100)のスピネルフェライト多結晶薄膜が得られることを、発明者は見出した。

【0043】

発明者は、スパッタリングカソードに印加する電圧の周波数が1〜100MHzの高周波とすることにより、絶縁性の酸化物ターゲットの場合においてもスパッタ成膜することが可能となることを見出した。

発明者は、スパッタリングカソードに設置するターゲット材料がM:Fe:Oの比率が略x:3−x:4(Mは、Zn、Mn、Co、Ni、Cu、Mg、Li、Feのいずれか1つ、かつ、0<x<3)である複合酸化物ターゲットとすることより、基板上にスピネルフェライト薄膜またはその前駆体となる薄膜を形成することが可能となることを見出した。

発明者は、スパッタリングガスとしてアルゴンガスのみを用い、その圧力を0.1Pa以下とすることより、下地層が金属薄膜である場合にその表面がスピネルフェライト薄膜の成膜中に酸化することを抑制することが可能となることを見出した。

発明者は、薄膜が堆積される基板温度を室温とすることより、下地層がアモルファス構造を有した金属である場合に熱による結晶化を防ぐことが可能となることを見出した。

発明者は、スパッタ成膜ステップにおける基板を200℃未満とすることにより、下地層がアモルファス構造を有した金属である場合に熱による結晶化を抑制することが可能となることを見出した。

発明者は、CoまたはFeを主成分とし、アモルファス構造を有した磁性金属薄膜が表面に付着した基板を用いることにより、スピネルフェライト薄膜の(100)優先配向を促進することが可能となることを見出した。

発明者は、スピネルフェライト薄膜の膜厚が100nm以下とすることにより、スピンフィルタ効果素子として有効に動作することが可能となることを見出した。

【0044】

次に、図1と図2を参照して、本実施形態のスパッタリング装置の作用と共に、この装置を用いて実施するスピネルフェライト薄膜の製造方法について説明する。

【0045】

本発明に係るスパッタ成膜方法は、まず、基板ステージ33上に処理対象である基板25を設置する。基板25は、例えば、隣接する搬送チャンバー12に備えられた基板搬送ロボット11により、ゲートバルブ16を通じて真空チャンバー13A内の真空度を維持したまま基板ステージ33上に運ばれる。

【0046】

次に、真空チャンバー13Aの内部に不図示の放電用ガス導入系からAr等の放電用ガスを導入する。

【0047】

5基のカソードユニット31には、例えば、それぞれ材料成分の異なる5種類のターゲ

ット32を取り付ける。各ターゲット32は、例えば、円板状を呈し、全て同じサイズに形成されている。前述したように、カソードの傾斜角は本発明の適用においては特に限定されないが、基板25の処理面の法線に対するカソード中心軸の角度θが0°を超えて45°以下の角度を成すようにカソードユニット31を配置することが好ましい。より好ましくは、上記角度θを5°以上35°以下に設定すると、優れた面内均一性が得られる。

【0048】

この状態で、まず、第1のカソードユニット31aのターゲット32a表面に、不図示の電源から放電用電力を供給して、基板ステージ33との間でプラズマ放電を発生させて、第1ターゲット32をスパッタリングし、基板25上に第1層を成膜する。

【0049】

その後、順次電源を切り替え、第2カソードユニット40bから第5カソードユニット

40eについても、同様にして成膜操作を行う。

【0050】

成膜終了後、スパッタ成膜チャンバーのゲートバルブ16を通じて搬送チャンバー12の基板搬送ロボット11によって基板25を搬出し、次いで真空加熱チャンバー14のゲートバルブ16を通じて真空加熱チャンバー14内の基板ステージ33上に基板25を載置する。

【実施例】

【0051】

次に本発明の実施例について図面を用いて説明する。

【実施例1】

【0052】

図6記載のスピネルフェライト薄膜の成膜手順について説明する。未処理基板25をロードロック室15Aから基板搬送ロボット11を用いて、搬送チャンバー12内の不図示の載置台に載置する。次に、基板搬送ロボット11により、基板25をスパッタリング成膜チャンバー13に搬入する。

図2記載のスパッタリングターゲット32として直径164mmのNiFeOの複合酸化物ターゲットを用いた。この時、Ni:Fe:Oの比率は、1:2:4とした。基板25の法線に対するターゲット32の法線の傾斜角を30°、T(ターゲット)/S(基板)距離を240mm、ターゲット32に供給する電力を直流200W、基板25の回転速度を100rpm一定とした。また、基板ステージ33の内部に冷却水を流すことによって成膜中の基板温度を室温に維持した。導入するArガス流量は20sccm、100sccm、200sccmの3通り実施した。この時のArガス圧は、それぞれ0.02、0.1、0.2Paであった(ただし、圧力の値は真空計をとりつける位置や真空計の種類によって誤差が生じるため、実際に放電が起きている空間の圧力は上述の圧力よりも高くなっていることが予想される)。薄膜の膜厚は30nmに統一し、成膜時間によって制御した。成膜後、基板25をスパッタリング成膜チャンバー13(真空チャンバー13A)から、基板搬送ロボット11により、真空加熱チャンバー14に搬送する。基板加熱は、図5記載の真空加熱チャンバー14を用いて行う。ハロゲンランプ102からの輻射線を照射することによって基板25を700℃に加熱し、10分間の真空熱処理を行った。基板25は表面にアモルファスの酸化シリコン201が100nm形成された酸化膜付きシリコン基板を用いた上記酸化膜付きシリコン基板201上にNiFe2O4のスピネルフェライト薄膜を成膜した。図3は成膜した薄膜のX線回折パターンである。尚、図3の(1)はArガス流量20sccm(=0.02Pa)の条件で図3の(2)はArガス流量100sccm(=0.1Pa)の条件で、図3の(3)はArガス流量200sccm(=0.2Pa)の条件でスピネルフェライト薄膜をそれぞれ成膜した場合を示す。いずれの条件においてもNiFe2O4のスピネルフェライト結晶の回折パターンが得られているが、Ar流量が20sccm(=0.02Pa)の条件では、(400)ピークが他の回折ピークと比較して著しく高く、(100)優先配向膜が得られていることがわかった。すなわち、室温、アモルファス下地、100nm以下の薄膜そして酸素添加を行わないというスピンフィルタ効果素子向けのスパッタ成膜条件においても、低ガス圧、ロングスロー(T/S距離が長い)での成膜を行うことにより、真空熱処理後に(100)に優先配向したスピネルフェライト薄膜が実現できることを示している。

【実施例2】

【0053】

図7記載のスピネルフェライト薄膜の成膜手順について説明する。実施例2においては、スパッタ成膜チャンバー13(真空チャンバー13A)内にB濃度を10at%以上含んだCoFeB合金ターゲット32を設置し、NiFeO202を成膜する前に、表面にアモルファスの酸化シリコン201が100nm形成された酸化膜付きシリコン基板201上にアモルファスCoFeB薄膜203を成膜して、次いでNiFeO202を成膜しても、真空熱処理後に(100)優先配向したスピネルフェライト薄膜が得られる。

【実施例3】

【0054】

図7記載のスピネルフェライト薄膜の成膜手順について、図4を用いて説明する。実施例3においては、図4に記載のように、NiFeOのスパッタ成膜チャンバー13(真空チャンバー13A)とは別に類似のスパッタ成膜チャンバー13(真空チャンバー13B)を搬送チャンバー12に追加接続し、そのチャンバー13Bの中でアモルファスCoFeB薄膜203を成膜してから、NiFeO201のスパッタ成膜チャンバー13(真空チャンバー13A)に基板を搬送してNiFeO202をスパッタ成膜しても同様の効果が得られる。

【実施例4】

【0055】

実施例1〜3において、真空加熱チャンバーでの加熱条件は700℃である必要はなく、200℃以上であれば同様の効果が得られる。

【実施例5】

【0056】

実施例1〜4において、スパッタリングターゲット32はNiFeOの複合酸化物でなくても良く、M:Fe:Oの比率が略x:3−x:4(Mは、Zn、Mn、Co、Ni、Cu、Mg、Li、Feのいずれか1つ、かつ、0<x<3)である複合酸化物ターゲットであれば同様の効果が得られる。

【実施例6】

【0057】

実施例1〜5において、T(ターゲット)/S(基板)距離が100mm以上であれば同様の効果が得られる。

【実施例7】

【0058】

図8は、図7記載のアモルファスCoFeB強磁性層の下に反強磁性層205(例えば、PtMn)、さらにその下に反強磁性層205の下地膜204(例えばTa)スピネルフェライト薄膜の上に保護膜となる電極層206(例えば、Ru)を作成した例を示す。なお、反強磁性層205(例えば、PtMn)、下地膜204(例えばTa)、保護膜となる電極層206(例えば、Ru)は、スパッタリング法により作成した。これにより、スピンフィルタ効果が得られる。

【実施例8】

【0059】

図9は、図8記載のスピネルフェライト薄膜上に、絶縁膜207(例えば、MgO)を積層した例を示す。なお、絶縁膜207(例えば、MgO)は、スパッタリング法により作成した。これにより、スピンフィルタ効果が得られる。

【符号の説明】

【0060】

12 搬送チャンバー

13 スパッタリングチャンバー

13A 真空チャンバーA

13B 真空チャンバーB

14 加熱チャンバー

25 基板

31 スパッタリングカソード

32 スパッタリングターゲット

【特許請求の範囲】

【請求項1】

基板上に(100)優先配向のスピネルフェライト薄膜を製造する方法であって、前記製造方法は、

スパッタリング法でスピネルフェライト薄膜もしくはその前駆体となる薄膜を基板上に形成するスパッタ成膜ステップと、

その基板を真空中で加熱する真空加熱ステップとを有することを特徴とするスピネルフェライト薄膜の製造方法。

【請求項2】

前記スパッタ成膜ステップは、

スパッタリングカソードに印加する電圧の周波数が1〜100MHzの高周波であり、

スパッタリングカソードに設置するターゲット材料がM:Fe:Oの比率が略x:3−x:4(Mは、Zn、Mn、Co、Ni、Cu、Mg、Li、Feのいずれか1つ、かつ、0<x<3)で構成された複合酸化物ターゲットであり、

スパッタリングガスはアルゴンガスのみでその圧力は0.1Pa以下であり、

薄膜が堆積される基板温度は室温であり、

前記ターゲットと前記基板との間の距離が100mm以上

であることを特徴とする請求項1に記載のスピネルフェライト薄膜の製造方法。

【請求項3】

前記スパッタ成膜ステップにおける基板が200℃未満であることを特徴とする請求項1又は請求項2に記載のスピネルフェライト薄膜の製造方法。

【請求項4】

前記基板はCoまたはFeを主成分とし、アモルファス構造を有した磁性金属薄膜が表面に付着していることを特徴とする請求項1〜3のいずれか1項に記載のスピネルフェライト薄膜の製造方法。

【請求項5】

前記スピネルフェライト薄膜の膜厚が100nm以下であることを特徴とする請求項1〜4のいずれか1項に記載のスピネルフェライト薄膜の製造方法。

【請求項1】

基板上に(100)優先配向のスピネルフェライト薄膜を製造する方法であって、前記製造方法は、

スパッタリング法でスピネルフェライト薄膜もしくはその前駆体となる薄膜を基板上に形成するスパッタ成膜ステップと、

その基板を真空中で加熱する真空加熱ステップとを有することを特徴とするスピネルフェライト薄膜の製造方法。

【請求項2】

前記スパッタ成膜ステップは、

スパッタリングカソードに印加する電圧の周波数が1〜100MHzの高周波であり、

スパッタリングカソードに設置するターゲット材料がM:Fe:Oの比率が略x:3−x:4(Mは、Zn、Mn、Co、Ni、Cu、Mg、Li、Feのいずれか1つ、かつ、0<x<3)で構成された複合酸化物ターゲットであり、

スパッタリングガスはアルゴンガスのみでその圧力は0.1Pa以下であり、

薄膜が堆積される基板温度は室温であり、

前記ターゲットと前記基板との間の距離が100mm以上

であることを特徴とする請求項1に記載のスピネルフェライト薄膜の製造方法。

【請求項3】

前記スパッタ成膜ステップにおける基板が200℃未満であることを特徴とする請求項1又は請求項2に記載のスピネルフェライト薄膜の製造方法。

【請求項4】

前記基板はCoまたはFeを主成分とし、アモルファス構造を有した磁性金属薄膜が表面に付着していることを特徴とする請求項1〜3のいずれか1項に記載のスピネルフェライト薄膜の製造方法。

【請求項5】

前記スピネルフェライト薄膜の膜厚が100nm以下であることを特徴とする請求項1〜4のいずれか1項に記載のスピネルフェライト薄膜の製造方法。

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【公開番号】特開2012−219361(P2012−219361A)

【公開日】平成24年11月12日(2012.11.12)

【国際特許分類】

【出願番号】特願2011−89277(P2011−89277)

【出願日】平成23年4月13日(2011.4.13)

【出願人】(000227294)キヤノンアネルバ株式会社 (564)

【Fターム(参考)】

【公開日】平成24年11月12日(2012.11.12)

【国際特許分類】

【出願日】平成23年4月13日(2011.4.13)

【出願人】(000227294)キヤノンアネルバ株式会社 (564)

【Fターム(参考)】

[ Back to top ]