スペクトラム拡散クロック生成回路及びその制御方法

【課題】変調度が安定しない。

【解決手段】周波数変調した出力発振信号を出力するPLL回路を有するスペクトラム拡散信号生成回路であって、前記PLL回路は、入力した発振制御信号の値に応じた周波数で前記出力発振信号を出力する発振回路を備え、前記PLL回路によりフィードバックされたPLL信号の周波数を変調させる前記発振制御信号を生成し、この前記発振制御信号の最大値と最小値をモニタし、そのモニタ結果により前記発振制御信号の最大値と最小値を調整し、前記出力発振信号の変調度を所定の値に制御する周波数変調部を、有するスペクトラム拡散クロック生成回路。

【解決手段】周波数変調した出力発振信号を出力するPLL回路を有するスペクトラム拡散信号生成回路であって、前記PLL回路は、入力した発振制御信号の値に応じた周波数で前記出力発振信号を出力する発振回路を備え、前記PLL回路によりフィードバックされたPLL信号の周波数を変調させる前記発振制御信号を生成し、この前記発振制御信号の最大値と最小値をモニタし、そのモニタ結果により前記発振制御信号の最大値と最小値を調整し、前記出力発振信号の変調度を所定の値に制御する周波数変調部を、有するスペクトラム拡散クロック生成回路。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、スペクトラム拡散クロック生成回路及びその制御方法に関するものである。

【背景技術】

【0002】

近年、電子機器の高速化、高密度化に伴い、電磁輻射(EMI:Electro Magnetic Interference)が問題となっている。電子機器内のクロックジェネレータ(CG)が単一周波数のクロック信号を発生させるとその周波数及び高調波による電磁輻射が大きくなる。SSCG(Spread Spectrum Clock Generator)は、クロック周波数のわずかに変動させ発振させる、つまり、周波数変調させたクロック信号を生成することで、周波数スペクトルの電力ピークを低減させることができる。

【0003】

ここで、従来のSSCGとして、特許文献1、2の技術が開示されている。まず、特許文献1のSSCG1のブロック構成を図4に示す。図4に示すように、SSCG1は、位相周波数比較器(PFD)10と、チャージポンプ(CP)11と、ローパスフィルタ(LPF)12と、電圧制御発振器(VCO)13と、ループカウンタ(PCNT)14と、変調制御信号部(MODU)15と、インバータ回路16とを有する。

【0004】

SSCG1は、一般的なSSCGの構成である。動作としては、変調制御信号部15がループカウンタ14の分周数を切り替えることでPLL(Phase Locked Loop)の逓倍数を変化させ、出力信号FOの周波数を変調する。

【0005】

特許文献1のSSCG1では、理想的には出力信号の変調プロファイルが三角波状になることを意図している。しかし、SSCG1では、変調した信号がPLLのローパスフィルタ12を通過する際になまってしまい、変調プロファイルが正弦波状になってしまう問題が発生する。なお、変調プロファイルとは、時間に対して出力信号の周波数変化をプロットした形状を示すものとする。

【0006】

図5(a)に変調プロファイルが三角波状の場合、図5(b)に変調プロファイルが正弦波状の場合の周波数スペクトラムの模式図を示す。図5(a)に示すように、変調プロファイルが三角波状になる場合、周波数スペクトラムは、所定の周波数帯域でフラットな特性となる。一方、変調プロファイルが正弦波状になる場合、図5(b)に示すように特定周波数上にピークが発生する。上述のように、SSCG1では、変調プロファイルが正弦波状となってしまうため、出力信号FOの周波数スペクトラムが図5(b)のようにピークをもってしまう。このようなピークが発生する周波数では、ピークを持つ周波数でEMIによる障害が発生し、SSCG1ではEMI低減効果が低くなってしまう。

【0007】

このような問題に対応するため、特許文献2のようなものがある。特許文献2のSSCG2のブロック構成を図6に示す。図6に示すように、SSCG2は、分周回路20と、位相比較器21と、チャージポンプ(CP)22と、ローパスフィルタ(LPF)23と、電圧電流変換器(VIC)24と、加算器25と、電流発振器(ICO)26と、分周回路27と、デジタル・アナログコンバータ(DAC)28と、制御回路29と、分周回路30とを有する。

【0008】

特許文献2のSSCG2では、電流発振器26の手前でダイレクトに変調信号を印加することで、SSCG1で問題となっていた変調した信号がなまってしまうという問題を克服している。

【先行技術文献】

【特許文献】

【0009】

【特許文献1】特開2001−251185号公報

【特許文献2】特開2006−324750号公報

【発明の概要】

【発明が解決しようとする課題】

【0010】

しかし、特許文献2のSSCG2では、構成するPLLの伝達特性のばらつき、及び、電流発振器26の特性のばらつきに変調度が影響されるという問題がある。よって、SSCG1で変調した信号がなまってしまうという問題は解決できるが、周辺温度、電源電圧の変動、製造ばらつき等の諸条件によって変調度がばらつく欠点が存在する。なお、本明細書上において、変調度とは、変調プロファイルの振幅のことを示すものとする。つまり、変調された出力信号の周波数の変化の上限と下限の差を示すものである。

【0011】

ここで、電流発振器26の特性(例えば周辺温度特性)のばらつきによる変調度がばらつくメカニズムを説明する。まず、理想的な電流発振器26の特性のグラフを図7に示す。図7のグラフは、横軸は電流発振器26に入力されるICO制御電流、縦軸は電流発振器26が出力する出力信号CLKoutの発振周波数である。ここで、電圧電流変換器24から出力される基準電流I1は、電流発振器26から出力される変調された出力信号CLKoutの平均周波数に相当するICO制御電流である。SSCG2ではこの基準電流I1を中心として±a倍した電流値の範囲で推移した電流を電流発振器26の入力電流に加算することで発振周波数を任意の幅で変調する。

【0012】

図7では、理想的に電流発振器26が動作しており、ICO制御電流と発振周波数との関係、つまり、I−F変換特性の傾き(以下、ICOゲインと称す)が線形かつ原点を通過する特性となっている。ここで、この条件下で電流発振器26の特性の変化に応じてICOゲインがばらつく場合、例えば、条件1としてICO制御電流の変化に応じて発振周波数の変化が速い場合(FAST)、条件2としてICO制御電流の変化に応じて発振周波数の変化が遅い場合(SLOW)、条件3としてICO制御電流の変化が条件1と2の中間である場合(TYP)を考える。なお、条件1での基準電流I1を「I1F」、条件2での基準電流I1を「I1S」、条件3での基準電流I1を「I1T」とする。

【0013】

図7からもわかるように、条件1〜3のいずれについても、ICOゲインと基準電流I1が比例関係にあるため、基準電流I1を±a倍した電流変化範囲に対応した周波数変調範囲FreqDに変化はない。

【0014】

しかし、実際には、周辺温度や製造条件等で図7に示した理想的な特性をもつ電流発振器26を得ることは非常に難しい。このため、例えば、ICOゲインが線形でない場合や、仮にICOゲインが線形であったとしても原点(電流0A時に発振周波数が0Hzである場合)を通らない場合、周辺温度の変化により、ICO特性のばらつきにより周波数変調範囲が変わってしまう問題がある。例えば、図8にICOゲインが線形でない場合の電流発振器26の特性のグラフを示す。ここで、上述した条件1(FAST)での基準電流I1をa倍した電流変化範囲に対応した周波数変調範囲をFreqDF、同じく条件2(SLOW)での周波数変調範囲をFreqDS、条件2(TYP)での周波数変調範囲をFreqDTとする。この場合、図8からもわかるように、図7で示す理想的な特性の場合異なり、周波数変調範囲FreqDF、FreqDT、FreqDSがそれぞれ同じにならずばらついてしまう。

【0015】

つまり、SSCG2のように、電圧電流変換器24が出力した基準電流I1をモニタし、その基準電流I1で決定した中心点に対して、加算器25により変調度を決定するための電流を増加もしくは減少させる方式では、上記問題を解決することができない。

【課題を解決するための手段】

【0016】

本発明の一態様は、周波数変調した出力発振信号を出力するPLL回路を有するスペクトラム拡散信号生成回路であって、前記PLL回路は、入力した発振制御信号の値に応じた周波数で前記出力発振信号を出力する発振回路を備え、前記PLL回路によりフィードバックされたPLL信号の周波数を変調させる前記発振制御信号を生成し、この前記発振制御信号の最大値と最小値をモニタし、そのモニタ結果により前記発振制御信号の最大値と最小値を調整し、前記出力発振信号の変調度を所定の値に制御する周波数変調部を、有するスペクトラム拡散クロック生成回路である。

【0017】

本発明の別の態様は、周波数変調した出力発振信号を出力するPLL回路を有するスペクトラム拡散信号生成回路の制御方法であって、前記PLL回路が備える発振回路が、入力した発振制御信号の値に応じた周波数で前記出力発振信号を出力し、前記PLL回路によりフィードバックされたPLL信号の周波数を変調させる前記発振制御信号を生成し、前記発振制御信号の最大値と最小値をモニタし、前記モニタした結果により前記発振制御信号の最大値と最小値を調整して前記出力発振信号の変調度を所定の値に制御するスペクトラム拡散信号生成回路の制御方法である。

【0018】

本発明にかかるスペクトラム拡散クロック生成回路によれば、周波数変調した出力発振信号を出力する発振回路の変調度を制御する発振制御信号の最大値と最小値を直接モニタしている。そして、そのモニタ結果をPLL回路とは別に、新たなフィードバックにより前記発振制御信号の最大値と最小値を調整し、前記出力発振信号の変調度を所定の値に制御する。これは、PLL回路の発振回路から見て、発振回路に入力する前の信号をフィードフォワード制御しており、発振回路から出力信号の変調度の中心点を決定し、その中心点から所定の周波数振幅を決定する従来のような制御が必要ない。このため、発振回路の温度変化等の条件に影響されず、安定した変調度で出力発振信号を生成することができる。

【発明の効果】

【0019】

本発明にかかるスペクトラム拡散クロック生成回路は、出力信号の周波数の変調プロファイルの振幅(変調度)のばらつきを低減することができる。

【図面の簡単な説明】

【0020】

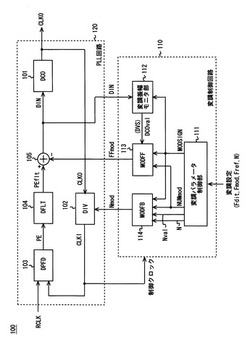

【図1】実施の形態にかかるスペクトラム拡散クロック生成回路のブロック構成図である。

【図2】実施の形態にかかるスペクトラム拡散クロック生成回路の動作フローチャートである。

【図3】実施の形態にかかるスペクトラム拡散クロック生成回路の動作タイミングチャートである。

【図4】従来のスペクトラム拡散クロック生成回路のブロック構成図である。

【図5】三角波状もしくは正弦波状の変調プロファイルによる周波数スペクトラムの違いを説明するためのグラフである。

【図6】従来のスペクトラム拡散クロック生成回路のブロック構成図である。

【図7】従来のスペクトラム拡散クロック生成回路の問題点を説明するためのグラフである。

【図8】従来のスペクトラム拡散クロック生成回路の問題点を説明するためのグラフである。

【発明を実施するための形態】

【0021】

発明の実施の形態

【0022】

以下、本発明を適用した具体的な実施の形態について、図面を参照しながら詳細に説明する。この実施の形態は、本発明を完全デジタルPLL(ADPLL)回路に適用してSSCG100を構成している。図1に本実施の形態にかかるSSCG100の構成の一例を示す。図1に示すように、SSCG100は、変調制御回路110と、PLL回路120とを有する。また、PLL回路120は、デジタル制御発振器(DCO)101と、分周器(DIV)102と、デジタル位相周波数比較器(DPFD)103と、デジタルフィルタ(DFLT)104と、DCO制御コード変調幅加算器105とを有する。

【0023】

デジタル位相周波数比較器(DPFD)103は、リファレンスクロック信号RCLKと、分周器102からのフィードバッククロック信号CLKIとの位相誤差を、デジタル信号である位相誤差検出量信号PEとして出力する。なお、基本的にSSCG100では、デジタル制御発振器101と、分周器102と、デジタル位相周波数比較器103と、デジタルフィルタ104と、DCO制御コード変調幅加算器105で構成されるPLL回路120により、リファレンスクロック信号RCLKとフィードバッククロック信号CLKIとの位相誤差がゼロとなるように動作する。

【0024】

デジタルフィルタ(DFLT)104は、入力した位相誤差検出量信号PEを任意の帯域でフィルタリングして、そのフィルタリングした位相誤差検出量をデジタル信号である位相誤差検出量信号PEfltとして出力する。

【0025】

DCO制御コード変調幅加算器105は、位相誤差検出量信号PEfltと、変調制御回路110からのフィードフォワード変調制御信号FFmodとを演算する。そして、その演算結果をデジタル信号であるDCO制御コードDINとして出力する。ここで、仮にデジタル位相周波数比較器103に入力されるフィードバッククロック信号CLKIに変調がかかっていない場合、デジタルフィルタ104から出力される位相誤差検出量信号PEfltは、PLL回路120がロック状態では一定の値となる。DCO制御コード変調幅加算器105は、このような位相誤差検出量信号PEfltの値に対して三角波状の波形で値が変化するフィードフォワード変調制御信号FFmodの値を減算(もしくは加算)して、DCO制御コードDINとする。より具体的には、位相誤差検出量信号PEflt及びフィードフォワード変調制御信号FFmodから(PEflt−FFmod)を演算し、演算結果をDCO制御コードDINとして出力する。なお、便宜上、各信号を示す符号は、信号名と同時にその信号が有するデジタル値を示すものとし、以降でも同様とする。なお、DCO制御コードDINの値は、予め設定された所定の値p〜p−DCOvalの範囲となる。但し、pは予め設定された所定の値、DCOvalは後述するDCO制御コード変化幅値である。また、変調制御回路110と、DCO制御コード変調幅加算器105とで、周波数変調部を構成するものとする。

【0026】

デジタル制御発振器(DCO)101は、入力したDCO制御コードDINに応じた発振周波数で出力クロック信号CLKOを出力する。但し、DCO制御コードDINは、上述のように、三角波状の波形で値が変化するため、デジタル制御発振器101が出力する出力クロック信号CLKOの周波数も、その三角波状の波形で変動する値に応じて変調される。より具体的には、出力クロック信号CLKOの周波数は、Fref×N〜Fref×N×(1−Fdit)の変調度で変調される。このように、出力クロック信号CLKOのクロック周波数を変動させることで、周波数スペクトルの電力ピークを低減させる。なお、このようにDCO制御コードDINの値の変動によって、出力クロック信号CLKOの周波数が変動することから、DCO制御コードDINの値をモニタすることは、最終的な出力クロック信号CLKOの周波数の変動をモニタすることになる。但し、Fref、N、Fditは後述する制御クロック周波数設定値、基準逓倍数設定値、変調度設定値である。

【0027】

分周器(DIV)102は、デジタル制御発振器101が出力する出力クロック信号CLKOを、変調制御回路110からの逓倍数変調制御信号Nmodの値に応じて分周し、フィードバッククロック信号CLKIとして出力する。この逓倍数変調制御信号Nmodの値は、変調制御回路110により設定される上記フィードフォワード変調制御信号FFmodと連動したものとなっており、分周器102は、上記フィードフォワード変調制御信号FFmodに応じて周波数が変調された出力クロック信号CLKOの変調を打ち消すように動作する。この動作により、分周器102が出力するフィードバッククロック信号CLKIは、周波数変調が除去された信号としてデジタル位相周波数比較器103にフィードバックされる。また、フィードバッククロック信号CLKIは、後述する変調制御回路110の制御クロックとして利用される。このときのフィードバッククロック信号CLKIの周期をT1とする。この周期T1は、後述する制御クロック周波数設定値Frefにより規定される。

【0028】

変調制御回路110は、DCO制御コードDINの最大値、最小値をモニタする。また、そのモニタ結果に応じて、フィードフォワード変調制御信号FFmodを出力する。また、フィードフォワード変調制御信号FFmodの設定と、連動した設定の逓倍数変調制御信号Nmodを出力する。変調制御回路110は、変調パラメータ制御部111と、変調振幅モニタ部112と、フィードフォワード変調制御部(MODFF)113と、フィードバック変調制御部(MODFB)114とを有する。なお、変調制御回路110は、制御クロックに応じて動作している。ここでは、その制御クロックとして分周器(DIV)102からのフィードバッククロック信号CLKIを利用するものとする。但し、制御クロックとして、フィードバッククロック信号CLKI以外の他のクロックを用いてもかまわない。

【0029】

変調パラメータ制御部111は、設定信号として、変調度設定値Fditと、変調プロファイル周波数設定値Fmodと、制御クロック周波数設定値Frefと、基準逓倍数設定値Nとを入力する。変調パラメータ制御部111は、上記変調設定信号に応じて逓倍数変化幅信号Nval及び変調ステップ数信号NUMmodを出力する。また、制御クロック数をカウントし、変調ステップ数NUMmodの所定の倍数に一致するごとに変調極性信号MODSIGNの論理レベルの極性(0もしくは1)を変化させて出力する。なお、変調極性信号MODSIGNの論理レベルが1のとき出力クロック信号CLKOの周波数が増加し、論理レベルが0のとき出力クロック信号CLKOの周波数が減少するよう変調制御回路110で設定される。

【0030】

より具体的には、逓倍数変化幅信号Nvalは、基準逓倍数設定値N及び変調度設定値Fditから、Nval=N×Fditを演算し、その演算結果として変調パラメータ制御部111から出力される。後述するが、この逓倍数変化幅信号Nvalの値の間で逓倍数変調制御信号Nmodが変化する。

【0031】

また、変調ステップ数信号NUMmodは、変調極性信号MODSIGNの論理レベルの極性変化の期間を規定する。例えば、変調極性信号MODSIGNの論理レベルの極性変化の期間をT2とするならば、T2=1/2Fmodとなる。そして、期間T2は、T2=制御クロック1周期(1/Fref)×NUMmodであるため、NUMmod=Fref/2Fmodとなる。このような演算結果として変調ステップ数信号NUMmodが変調パラメータ制御部111から出力される。

【0032】

変調振幅モニタ部112は、DCO制御コード変調幅加算器105からのDCO制御コードDINと、変調パラメータ制御部111からの変調極性信号MODSIGNに応じて、DCO制御コード変化幅値DCOvalを出力する。より具体的には、変調極性信号MODSIGNの1周期のDCO制御コードDINの最大値をDCOmax、最小値をDCOminとして求める。そして、変調極性信号MODSIGNの立ち上がりエッジ及び立ち下がりエッジ毎に、DCO制御コードDINの値の変化幅、つまり、(DCOmax−DCOmin)の演算結果のDCO制御コード変化幅値DCOvalを出力する。但し、PLL回路120のループ帯域(追従速度)と、後述するフィードフォワード変調制御信号FFmodの振幅を決定する速度とが近い場合に、PLL回路120の出力クロック信号CLKOの周波数が不安定になってしまう。このため、変調動作開始から所定の期間、変調振幅モニタ部112は、DCO制御コード変化幅値DCOvalを移動平均した値を制御信号DVSとして、フィードフォワード変調制御部113に出力することが好ましい。この制御信号DVSの値は、最終的にはDCO制御コード変化幅値DCOvalに到達するが、このDCO制御コード変化幅値DCOvalに到達するまで、移動平均のタップ数に応じた所定の期間で段階的に増加(もしくは減少)させることが望ましい。このようにすることでフィードフォワード変調制御信号の振幅を決定する速度を移動平均のタップ数に応じて遅くすることができる。

【0033】

フィードフォワード変調制御部(MODFF)113は、変調パラメータ制御部111からの変調ステップ数信号NUMmod、変調極性信号MODSIGN、及び、変調振幅モニタ部112からのDCO制御コード変化幅値DCOvalに応じて、フィードフォワード変調制御信号FFmodを出力する。より具体的には、変調ステップ数信号NUMmod及びDCO制御コード変化幅値DCOvalから(DCOval/NUMmod)を演算し、演算結果をフィードフォワード変調ステップΔFFstepとする。そして、変調極性信号MODSIGNの各極性(0もしくは1)の期間中に継続して、制御クロックのエッジ毎に、フィードフォワード変調ステップΔFFstepの値を加算もしくは減算して積算する。その積算結果をフィードフォワード変調制御信号FFmodとして出力する。なお、フィードフォワード変調制御信号FFmodの値は、0〜DCOvalの範囲となる。

【0034】

フィードバック変調制御部(MODFB)114は、変調パラメータ制御部111からの変調ステップ数信号NUMmod、変調極性信号MODSIGN、逓倍数変化幅信号Nvalに応じて、逓倍数変調制御信号Nmodを出力する。より具体的には、変調ステップ数信号NUMmod及び逓倍数変化幅信号Nvalから(Nval/NUMmod)を演算し、演算結果を逓倍数変調ステップΔFBstepとする。そして、変調極性信号MODSIGNの各極性(0もしくは1)の期間中に継続して、制御クロックのエッジ毎に、逓倍数変調ステップΔFBstepの値を加算もしくは減算して積算し、その積算結果をフィードバック信号制御信号FBmodとする。なお、フィードバック信号制御信号FBmodの値は、0〜Nvalの範囲となる。そして、基準逓倍数設定値Nとフィードバック信号制御信号FBmodとの差(N−FBmod)を演算し、演算結果を逓倍数変調制御信号Nmodとして出力する。なお、逓倍数変調制御信号Nmodの値は、N−Nval〜Nの範囲となる。

【0035】

以上のようなSSCG100の動作を以下に説明する。まず、図2にSSCG100の動作のフローチャートを示す。図2に示すように、まず変調パラメータ制御部111にて、変調設定信号に応じて逓倍数変化幅信号Nval及び変調ステップ数信号NUMmodを演算して出力する。また、制御クロック数をカウントし、変調ステップ数NUMmodの所定の倍数に一致するごとに変調極性信号MODSIGNの論理レベルの極性(0もしくは1)を変化させて出力する(S101)。

【0036】

そして、変調幅モニタ部112では、変調極性信号MODSIGNの1周期の期間において、DCO制御コードDINの最大値をDCOmax、最小値をDCOminとして求める(S111)。次に、変調極性信号MODSIGNの立ち上がりエッジ及び立ち下がりエッジ毎に、DCO制御コードDINの値の変化幅、つまり、(DCOmax−DCOmin)をDCO制御コード変化幅値DCOvalとして出力する(S112)。これら、ステップS111、S112は、変調振幅幅モニタ部112での動作フロー(FLOW1)である。

【0037】

そして、フィードフォワード変調制御部(MODFF)113では、変調ステップ数信号NUMmod及びステップS112でのDCO制御コード変化幅値DCOvalから(DCOval/NUMmod)を演算し、演算結果をフィードフォワード変調ステップΔFFstepとする(S121)。次に、変調極性信号MODSIGNの各極性(0もしくは1)の期間中に継続して、制御クロックのエッジ毎に、フィードフォワード変調ステップΔFFstepの値を加算もしくは減算して積算する。その積算結果をフィードフォワード変調制御信号FFmodとして出力する(S122)。これら、ステップS121、S122は、フィードフォワード変調制御部113での動作フロー(FLOW2)である。

【0038】

そして、フィードバック変調制御部(MODFB)114では、変調ステップ数信号NUMmod及び逓倍数変化幅信号Nvalから(Nval/NUMmod)を演算し、演算結果を逓倍数変調ステップΔFBstepとする(S131)。次に、変調極性信号MODSIGNの各極性(0もしくは1)の期間中に継続して、制御クロックのエッジ毎に、逓倍数変調ステップΔFBstepの値を加算もしくは減算して積算し、その積算結果をフィードバック信号制御信号FBmodとする(S132)。次に、基準逓倍数設定値Nとフィードバック信号制御信号FBmodとの差(N−FBmod)を演算し、演算結果を逓倍数変調制御信号Nmodとして出力する(S133)。これら、ステップS131〜S133は、フィードバック変調制御部114での動作フロー(FLOW3)である。

【0039】

そして、DCO制御コード変調幅加算器105では、後述するステップS145での位相誤差検出量信号PEflt及びステップS122でのフィードフォワード変調制御信号FFmodから(PEflt−FFmod)を演算し、演算結果をDCO制御コードDINとして出力する(S141)。次に、デジタル制御発振器(DCO)101では、入力したDCO制御コードDINに比例した発振周波数で出力クロック信号CLKOを出力する(S142)。次に、分周器(DIV)102では、デジタル制御発振器101が出力する出力クロック信号CLKOを、ステップS133での逓倍数変調制御信号Nmodの値に応じて分周し、フィードバッククロック信号CLKIとして出力する(S143)。

【0040】

次に、デジタル位相周波数比較器(DPFD)103では、リファレンスクロック信号RCLKと、分周器102からのフィードバッククロック信号CLKIとの位相誤差を、デジタル信号である位相誤差検出量信号PEとして出力する(S144)。次に、デジタルフィルタ(DFLT)104では、入力した位相誤差検出量信号PEを任意の帯域でフィルタリングして、そのフィルタリングした位相誤差検出量をデジタル信号である位相誤差検出量信号PEfltとして出力する(S145)。これら、ステップS141〜S145は、PLL回路120での動作フロー(FLOW4)である。以上が、SSCG100の動作のフローチャートの説明である。

【0041】

ここで、ステップS141〜S145のPLL回路120の動作フロー(FLOW4)により、フィードバックループが形成されていることがわかる。そして、更にFLOW4のフィードバックループとは別に、ステップS111、S112、S121、S122、S141で構成されるフィードバックループが形成されていることがわかる。これは、PLL回路120のフィードバックループとは別に、DCO制御コード変調幅加算器105と、変調振幅モニタ部112と、フィードフォワード変調制御部113とで構成されるフィードバックループである。これは、PLL回路120のデジタル制御発振器101から見て、フィードフォワード制御にあたる。

【0042】

そして、デジタル制御発振器101が出力する出力クロック信号CLKOのクロック周波数の変調度は、上記のようなフィードフォワード制御により制御されている。つまり、デジタル制御発振器101に入力されるDCO制御コードDINの最大値と最小値を変調振幅モニタ部112がモニタし、そのモニタ結果(最大値と最小値の差であるDCOval)に応じたフィードフォワード変調制御信号FFmodをフィードフォワード変調制御部113が出力し、その出力された値をDCO制御コード変調幅加算器105が位相誤差検出量信号PEfltと減算(もしくは加算)演算してDCO制御コードDINを出力する。

【0043】

ここで、従来技術のSSCG2では、電流発振器26から出力される変調された出力信号CLKoutの平均周波数に相当するICO制御電流(発振器制御信号)をモニタする。そして、従来技術のSSCG2は、発振回路(ICO26)の出力信号の変調度の中心点を決定し、その中心点から所定の周波数振幅を決めている。このため、周辺温度の変化や製造ばらつき等の影響により、発振回路(ICO26)の周波数特性が設定したものとずれた場合、発振回路(ICO26)が出力する出力信号の周波数変調範囲もずれる問題があった。

【0044】

一方、本実施の形態のSSCG100では、上述したフィードフォワード制御によりDCO制御コードDINの最大値と最小値をモニタする。このため、SSCG2で上記問題発生の原因となっていた、発振回路(ICO26)からの出力信号の変調度の中心点を決定し、その中心点から所定の周波数振幅を決定する従来のような制御の形態をとっていない。

【0045】

このように、本実施の形態のSSCG100は、出力クロック信号CLKOの変調を、上記フィードフォワード制御によりデジタル制御発振器101に入力されるDCO制御コードDINを制御することで行っており、発振回路(本例のデジタル制御発振器101)の温度変化等の条件に影響されず、安定した変調度で出力発振信号を生成することができる。

【0046】

次に、図2で説明したフローチャート動作による、SSCG100の動作タイミングチャートを図3に示す。なお、以下で説明するSSCG100の動作の前提として、PLL回路120により、リファレンスクロック信号RCLKとフィードバッククロック信号CLKIとの位相誤差がゼロとなるよう基本的なPLL動作が行われているものとする。このため、基本的なPLLとしての動作は、特に必要な箇所以外、ここでは省略する。

【0047】

そして、SSCG100では、上述してきたように、このPLL回路120から出力される出力クロック信号CLKOに軽微な周波数変調をかけることで、スペクトラム拡散を行っている。なお、軽微な周波数変調とは、例えば、出力クロック信号CLKOのクロック周波数が400MHzである場合、20MHz(5%)の変調をかける変調動作を行うことがあげられる。以下のタイミングチャートの動作の説明は、SSCG100が行う周波数変調の動作を示すものであり、図3に示す各信号波形はこの変調動作に対するプロファイル(以下、変調プロファイルと称す)を示すものであることに注意する。

【0048】

まず、変調パラメータ制御部111から、変調設定信号として、変調極性信号MODSIGN、逓倍数制御信号Nmod、変調ステップ数信号NUMmod、基準逓倍数設定値Nが出力されている。この変調設定信号に応じて、逓倍数制御信号Nmodがフィードバック変調制御部114から出力される。

【0049】

図3に示すように、SSCG100の変調動作の初期状態である時刻t0以前では、DCO制御コード変調幅加算器105に入力されるフィードフォワード変調制御信号FFmodがゼロである。このため、SSCG100の周波数変調は、PLL回路120の分周器102の動作のみで行われている。

【0050】

ここで、分周器102の動作のみで変調動作を行っている場合、PLL回路120のPLL動作により、出力クロック信号CLKOの変調度(変調プロファイルの振幅)は設定値(基準逓倍数設定値N、変調度設定値Fdit)に応じて比較的正確に調整される。但し、この場合、PLL回路120でフィードバックされるフィードバッククロック信号CLKIの周波数が時間に対して変化することから、デジタル位相周波数比較器103の位相誤差検出信号PEの変調プロファイルも三角波形状から歪みが生じる。このため、DCO制御コードDINの変調プロファイルも、三角波形状にならず、頂点のなまった正弦波のような波形となる。そして、このDCO制御コードDINに応じて出力される出力クロック信号CLKOの変調プロファイルも同様に三角波形状にならず、頂点のなまった正弦波のような波形となる。

【0051】

ここで、SSCG100では、時刻t0〜t3にかけて、DCO制御コードDINをモニタしている変調振幅モニタ部112が、DCO制御コード変化幅信号DCOvalに到達するまで段階的に値を増加させた制御信号DVSを出力する。なお、図3に示す例では、変調幅モニタ部112は、時刻t3で、制御信号DVSの値がDCO制御コード変化幅値DCOvalに到達するまで4回に分けて段階的に増加させて出力している。これは、変調振幅モニタ部112が、DCO制御コード変化幅値DCOvalを4タップの移動平均により演算して、出力している。もし上述のように制御信号DVSの値を段階的に増加させないと、PLL回路120のループ帯域(追従速度)と、フィードフォワード変調制御信号FFmodの振幅を決定する速度とが近い場合に、PLL回路120の出力クロック信号CLKOの周波数が不安定になってしまう。よって、SSCG100では、このことを防ぐため、制御信号DVSの値を所定の期間にかけて、複数回に分けて段階的に増加させて出力している。なお、上記例では、制御信号DVSの値を4タップの移動平均により演算して出力しているが、更に複数のタップの移動平均を行っても良い。

【0052】

上述のように、段階的に値を増加した制御信号DVSの値により時刻t1からフィードフォワード変調ステップΔFFstepも段階的に増加する。そして、この段階的に増加したフィードフォワード変調ステップΔFFstepに応じて、フィードフォワード変調制御信号FFmodの変調プロファイルの振幅幅も図3に示すように段階的に大きくなる。

【0053】

一方、フィードフォワード変調制御信号FFmodの変調プロファイルの振幅幅が大きくなるごとに、分周器102の出力するフィードバッククロック信号CLKIと、リファレンスクロック信号RCLKとの位相差が小さくなる。つまり、位相誤差検出量信号PE、更には、その位相誤差検出量信号PEをデジタルフィルタ104でフィルタリングしたPEfltも値がゼロに近づいていく。このことから、逓倍数制御信号Nmodに応じて分周器102で行っていた変調動作の影響が段階的に減少していく。

【0054】

例えば、時刻t4以降では、逓倍数制御信号Nmodに応じて分周器102が行う出力クロック信号CLKOの分周動作による周波数変調と、フィードフォワード変調制御信号FFmodに応じて行われる出力クロック信号CLKOの周波数変調が打ち消しあう。このため、分周器102から出力されるフィードバッククロック信号CLKIには、周波数変調がかかっておらず、分周器102の動作のみで変調動作を行っている場合に問題となっていた、位相誤差検出信号PEの変調プロファイルの波形が歪んでいた問題が発生しない。

【0055】

このため、図3に示すように時刻t4以降では、DCO制御コードDINの変調プロファイル、及び、DCO制御コードDINに応じて出力される出力クロック信号CLKOの変調プロファイルも理想的な三角波形状となることができる。以上が、SSCG100の動作の説明である。

【0056】

ここで、SSCG2では変調した信号がなまってしまうという問題は解決できるが、構成するPLLの伝達特性のばらつきや、電流発振器26の特性のばらつきに出力信号FOの変調度が影響されるという問題を有していた。このSSCG2は、所望の変調度を得るために電流発振器26に入力する電流Iinを、基準電流I1を中心に同じ幅(前述したaの値)で増減させ、任意の変調度を実現させていた。このため、図7、図8で説明したように電流発振器26の特性のばらつき等により、変調度が変化してしまう問題があった。

【0057】

更には、この変調度のばらつきを最小限に抑えることと、任意の変調度を得ることの両方を実現するため基準電流I1を何倍にすればよいか、つまりaの値をどのようにするかは、上述したICOゲインが線形でない等の条件下では、設計時に回路シミュレーション等で、慎重に見積もる必要があった。このため設計時間が長期化し、その結果、設計コストが上昇する問題があった。

【0058】

ここで、本実施の形態のSSCG100では、変調動作完了後(例えば、図3の時刻t4以降)の出力クロック信号CLKOの周波数変調に、PLL回路120の逓倍されたフィードバッククロック信号CLKIのPLL動作による変調ではなく、変調振幅モニタ部112、フィードフォワード変調制御部113、DCO制御コード変調幅加算器105で構成される、PLL回路120とは別のフィードバックループ(以後、フィードバックループ1と称す)の動作による変調を行っている。

【0059】

上記変調振幅モニタ部112は、デジタル制御発振器101が入力するDCO制御コードDINの最大値、最小値を直接モニタしている。そして、このDCO制御コードDINの最大値と最小値の差であるDCO制御コード変化幅値DCOvalに応じたフィードフォワード変調制御信号FFmodがDCO制御コード変調幅加算器105に加算されている。

【0060】

ここで上述したように、SSCG2では、出力信号FOの変調度の中心点を決定する基準電流I1がどうしても必要となり、その中心点から同じ値の電流を増減させることになる。しかし、本実施の形態のSSCG100では、SSCG2の電流発振器26に相当するデジタル制御発振器101に入力するDCO制御コードDINを上記フィードバックループ1で生成している。これは、DCO制御コードDINによりデジタル制御発振器101が出力する出力クロック信号CLKOの最高周波数、最低周波数の差を、デジタル制御発振器101に入力されるDCO制御コードDINの最大値、最小値の差としてモニタし、そのDCO制御コードDINの最大値、最小値の差をフィードバックループ1で制御している。このため、SSCG2での問題の原因である出力クロック信号CLKOの変調度の中心点を決定する必要がなく、デジタル制御発振器101の周辺温度等の特性のばらつきの影響を受けない。つまり、SSCG2が有していた問題が発生しない。更には、デジタル制御発振器101の特性のばらつきの影響を受けないため、SSCG2で問題となっていた、設計時間の長期化する問題も発生しない。

【0061】

また、上記ように、PLL回路120とは別のフィードバックループで変調動作が行われるため、PLLのフィルタ特性に制限されることなく任意の変調プロファイルを生成可能となる。このことから、出力クロック信号CLKOの変調プロファイルを理想的な三角波形状にでき、周波数スペクトラムを図5(b)に示すようなフラットな特性にすることができる。

【0062】

ここで、本実施の形態のような完全デジタルPLLでは、アナログPLLで必須のローパスフィルタのような回路面積の増大要因であるアナログ素子を必要としない。その代わりに、デジタルフィルタ等のデジタル信号処理を行うデジタル回路で構成される。デジタル回路は、CMOS技術の微細化により回路面積の縮小が可能である利点を有する。また、位相比較もデジタルデータで行うため、アナログPLLのような、周波数ジャンプによる出力クロック信号への入力クロック信号の漏れも発生しない。加えて、分周器に対する正確な小数点逓倍も可能になる。なお、このような、完全デジタルPLLの例としては、特開2002−76886号公報のような技術がある。

【0063】

ここで、本実施の形態のSSCG100も、完全デジタルPLLであり、フィードバック変調制御部114から出力されるデジタル信号の変調ステップ数信号NUMmodにより分周器102の逓倍数を小数点まで制御することが可能である。よって、PLLを構成する分周器の逓倍数が整数のみしか制御できない場合に比べ、位相比較時の位相誤差を連続的に変化させることができる。これにより、出力クロック信号CLKOの周波数変調の推移も滑らかになり、スプリアスの影響を軽減させることができる。また、上記したアナログPLLに対する他の利点も当然有する。

【0064】

なお、本発明は上記実施の形態に限られたものでなく、趣旨を逸脱しない範囲で適宜変更することが可能である。例えば、図3の例では、SSCG100の変調動作の初期状態である時刻t0ではフィードフォワード変調制御信号FFmodの変調プロファイルの変化幅をゼロとしている。しかし、必ずしも初期状態時にフィードフォワード変調制御信号FFmodの変調プロファイルの変化幅をゼロとする必要はなく、ゼロ以上の任意の値であってもよい。例えば、変調動作の初期状態である時刻t0にフィードフォワード変調制御信号FFmodの変調プロファイルの変化幅を、DCOvalの3倍の値としてもかまわない。この場合でも、変調振幅モニタ部112により行われる移動平均のタップ数後にはフィードフォワード変調制御信号FFmodの変調プロファイルの変化幅値がDCOvalに収束する。結果として、それぞれの信号のプロファイルは、図3の時刻t4以降と同様の波形となる。

【符号の説明】

【0065】

100 SSCG

101 デジタル制御発振器(DCO)

102 分周器(DIV)

103 デジタル位相周波数比較器(DPFD)

104 デジタルフィルタ(DFLT)

105 DCO制御コード変調幅加算器

110 変調制御回路

111 変調パラメータ制御部

112 変調振幅モニタ部

113 フィードフォワード変調制御部(MODFF)

114 フィードバック変調制御部(MODFB)

【技術分野】

【0001】

本発明は、スペクトラム拡散クロック生成回路及びその制御方法に関するものである。

【背景技術】

【0002】

近年、電子機器の高速化、高密度化に伴い、電磁輻射(EMI:Electro Magnetic Interference)が問題となっている。電子機器内のクロックジェネレータ(CG)が単一周波数のクロック信号を発生させるとその周波数及び高調波による電磁輻射が大きくなる。SSCG(Spread Spectrum Clock Generator)は、クロック周波数のわずかに変動させ発振させる、つまり、周波数変調させたクロック信号を生成することで、周波数スペクトルの電力ピークを低減させることができる。

【0003】

ここで、従来のSSCGとして、特許文献1、2の技術が開示されている。まず、特許文献1のSSCG1のブロック構成を図4に示す。図4に示すように、SSCG1は、位相周波数比較器(PFD)10と、チャージポンプ(CP)11と、ローパスフィルタ(LPF)12と、電圧制御発振器(VCO)13と、ループカウンタ(PCNT)14と、変調制御信号部(MODU)15と、インバータ回路16とを有する。

【0004】

SSCG1は、一般的なSSCGの構成である。動作としては、変調制御信号部15がループカウンタ14の分周数を切り替えることでPLL(Phase Locked Loop)の逓倍数を変化させ、出力信号FOの周波数を変調する。

【0005】

特許文献1のSSCG1では、理想的には出力信号の変調プロファイルが三角波状になることを意図している。しかし、SSCG1では、変調した信号がPLLのローパスフィルタ12を通過する際になまってしまい、変調プロファイルが正弦波状になってしまう問題が発生する。なお、変調プロファイルとは、時間に対して出力信号の周波数変化をプロットした形状を示すものとする。

【0006】

図5(a)に変調プロファイルが三角波状の場合、図5(b)に変調プロファイルが正弦波状の場合の周波数スペクトラムの模式図を示す。図5(a)に示すように、変調プロファイルが三角波状になる場合、周波数スペクトラムは、所定の周波数帯域でフラットな特性となる。一方、変調プロファイルが正弦波状になる場合、図5(b)に示すように特定周波数上にピークが発生する。上述のように、SSCG1では、変調プロファイルが正弦波状となってしまうため、出力信号FOの周波数スペクトラムが図5(b)のようにピークをもってしまう。このようなピークが発生する周波数では、ピークを持つ周波数でEMIによる障害が発生し、SSCG1ではEMI低減効果が低くなってしまう。

【0007】

このような問題に対応するため、特許文献2のようなものがある。特許文献2のSSCG2のブロック構成を図6に示す。図6に示すように、SSCG2は、分周回路20と、位相比較器21と、チャージポンプ(CP)22と、ローパスフィルタ(LPF)23と、電圧電流変換器(VIC)24と、加算器25と、電流発振器(ICO)26と、分周回路27と、デジタル・アナログコンバータ(DAC)28と、制御回路29と、分周回路30とを有する。

【0008】

特許文献2のSSCG2では、電流発振器26の手前でダイレクトに変調信号を印加することで、SSCG1で問題となっていた変調した信号がなまってしまうという問題を克服している。

【先行技術文献】

【特許文献】

【0009】

【特許文献1】特開2001−251185号公報

【特許文献2】特開2006−324750号公報

【発明の概要】

【発明が解決しようとする課題】

【0010】

しかし、特許文献2のSSCG2では、構成するPLLの伝達特性のばらつき、及び、電流発振器26の特性のばらつきに変調度が影響されるという問題がある。よって、SSCG1で変調した信号がなまってしまうという問題は解決できるが、周辺温度、電源電圧の変動、製造ばらつき等の諸条件によって変調度がばらつく欠点が存在する。なお、本明細書上において、変調度とは、変調プロファイルの振幅のことを示すものとする。つまり、変調された出力信号の周波数の変化の上限と下限の差を示すものである。

【0011】

ここで、電流発振器26の特性(例えば周辺温度特性)のばらつきによる変調度がばらつくメカニズムを説明する。まず、理想的な電流発振器26の特性のグラフを図7に示す。図7のグラフは、横軸は電流発振器26に入力されるICO制御電流、縦軸は電流発振器26が出力する出力信号CLKoutの発振周波数である。ここで、電圧電流変換器24から出力される基準電流I1は、電流発振器26から出力される変調された出力信号CLKoutの平均周波数に相当するICO制御電流である。SSCG2ではこの基準電流I1を中心として±a倍した電流値の範囲で推移した電流を電流発振器26の入力電流に加算することで発振周波数を任意の幅で変調する。

【0012】

図7では、理想的に電流発振器26が動作しており、ICO制御電流と発振周波数との関係、つまり、I−F変換特性の傾き(以下、ICOゲインと称す)が線形かつ原点を通過する特性となっている。ここで、この条件下で電流発振器26の特性の変化に応じてICOゲインがばらつく場合、例えば、条件1としてICO制御電流の変化に応じて発振周波数の変化が速い場合(FAST)、条件2としてICO制御電流の変化に応じて発振周波数の変化が遅い場合(SLOW)、条件3としてICO制御電流の変化が条件1と2の中間である場合(TYP)を考える。なお、条件1での基準電流I1を「I1F」、条件2での基準電流I1を「I1S」、条件3での基準電流I1を「I1T」とする。

【0013】

図7からもわかるように、条件1〜3のいずれについても、ICOゲインと基準電流I1が比例関係にあるため、基準電流I1を±a倍した電流変化範囲に対応した周波数変調範囲FreqDに変化はない。

【0014】

しかし、実際には、周辺温度や製造条件等で図7に示した理想的な特性をもつ電流発振器26を得ることは非常に難しい。このため、例えば、ICOゲインが線形でない場合や、仮にICOゲインが線形であったとしても原点(電流0A時に発振周波数が0Hzである場合)を通らない場合、周辺温度の変化により、ICO特性のばらつきにより周波数変調範囲が変わってしまう問題がある。例えば、図8にICOゲインが線形でない場合の電流発振器26の特性のグラフを示す。ここで、上述した条件1(FAST)での基準電流I1をa倍した電流変化範囲に対応した周波数変調範囲をFreqDF、同じく条件2(SLOW)での周波数変調範囲をFreqDS、条件2(TYP)での周波数変調範囲をFreqDTとする。この場合、図8からもわかるように、図7で示す理想的な特性の場合異なり、周波数変調範囲FreqDF、FreqDT、FreqDSがそれぞれ同じにならずばらついてしまう。

【0015】

つまり、SSCG2のように、電圧電流変換器24が出力した基準電流I1をモニタし、その基準電流I1で決定した中心点に対して、加算器25により変調度を決定するための電流を増加もしくは減少させる方式では、上記問題を解決することができない。

【課題を解決するための手段】

【0016】

本発明の一態様は、周波数変調した出力発振信号を出力するPLL回路を有するスペクトラム拡散信号生成回路であって、前記PLL回路は、入力した発振制御信号の値に応じた周波数で前記出力発振信号を出力する発振回路を備え、前記PLL回路によりフィードバックされたPLL信号の周波数を変調させる前記発振制御信号を生成し、この前記発振制御信号の最大値と最小値をモニタし、そのモニタ結果により前記発振制御信号の最大値と最小値を調整し、前記出力発振信号の変調度を所定の値に制御する周波数変調部を、有するスペクトラム拡散クロック生成回路である。

【0017】

本発明の別の態様は、周波数変調した出力発振信号を出力するPLL回路を有するスペクトラム拡散信号生成回路の制御方法であって、前記PLL回路が備える発振回路が、入力した発振制御信号の値に応じた周波数で前記出力発振信号を出力し、前記PLL回路によりフィードバックされたPLL信号の周波数を変調させる前記発振制御信号を生成し、前記発振制御信号の最大値と最小値をモニタし、前記モニタした結果により前記発振制御信号の最大値と最小値を調整して前記出力発振信号の変調度を所定の値に制御するスペクトラム拡散信号生成回路の制御方法である。

【0018】

本発明にかかるスペクトラム拡散クロック生成回路によれば、周波数変調した出力発振信号を出力する発振回路の変調度を制御する発振制御信号の最大値と最小値を直接モニタしている。そして、そのモニタ結果をPLL回路とは別に、新たなフィードバックにより前記発振制御信号の最大値と最小値を調整し、前記出力発振信号の変調度を所定の値に制御する。これは、PLL回路の発振回路から見て、発振回路に入力する前の信号をフィードフォワード制御しており、発振回路から出力信号の変調度の中心点を決定し、その中心点から所定の周波数振幅を決定する従来のような制御が必要ない。このため、発振回路の温度変化等の条件に影響されず、安定した変調度で出力発振信号を生成することができる。

【発明の効果】

【0019】

本発明にかかるスペクトラム拡散クロック生成回路は、出力信号の周波数の変調プロファイルの振幅(変調度)のばらつきを低減することができる。

【図面の簡単な説明】

【0020】

【図1】実施の形態にかかるスペクトラム拡散クロック生成回路のブロック構成図である。

【図2】実施の形態にかかるスペクトラム拡散クロック生成回路の動作フローチャートである。

【図3】実施の形態にかかるスペクトラム拡散クロック生成回路の動作タイミングチャートである。

【図4】従来のスペクトラム拡散クロック生成回路のブロック構成図である。

【図5】三角波状もしくは正弦波状の変調プロファイルによる周波数スペクトラムの違いを説明するためのグラフである。

【図6】従来のスペクトラム拡散クロック生成回路のブロック構成図である。

【図7】従来のスペクトラム拡散クロック生成回路の問題点を説明するためのグラフである。

【図8】従来のスペクトラム拡散クロック生成回路の問題点を説明するためのグラフである。

【発明を実施するための形態】

【0021】

発明の実施の形態

【0022】

以下、本発明を適用した具体的な実施の形態について、図面を参照しながら詳細に説明する。この実施の形態は、本発明を完全デジタルPLL(ADPLL)回路に適用してSSCG100を構成している。図1に本実施の形態にかかるSSCG100の構成の一例を示す。図1に示すように、SSCG100は、変調制御回路110と、PLL回路120とを有する。また、PLL回路120は、デジタル制御発振器(DCO)101と、分周器(DIV)102と、デジタル位相周波数比較器(DPFD)103と、デジタルフィルタ(DFLT)104と、DCO制御コード変調幅加算器105とを有する。

【0023】

デジタル位相周波数比較器(DPFD)103は、リファレンスクロック信号RCLKと、分周器102からのフィードバッククロック信号CLKIとの位相誤差を、デジタル信号である位相誤差検出量信号PEとして出力する。なお、基本的にSSCG100では、デジタル制御発振器101と、分周器102と、デジタル位相周波数比較器103と、デジタルフィルタ104と、DCO制御コード変調幅加算器105で構成されるPLL回路120により、リファレンスクロック信号RCLKとフィードバッククロック信号CLKIとの位相誤差がゼロとなるように動作する。

【0024】

デジタルフィルタ(DFLT)104は、入力した位相誤差検出量信号PEを任意の帯域でフィルタリングして、そのフィルタリングした位相誤差検出量をデジタル信号である位相誤差検出量信号PEfltとして出力する。

【0025】

DCO制御コード変調幅加算器105は、位相誤差検出量信号PEfltと、変調制御回路110からのフィードフォワード変調制御信号FFmodとを演算する。そして、その演算結果をデジタル信号であるDCO制御コードDINとして出力する。ここで、仮にデジタル位相周波数比較器103に入力されるフィードバッククロック信号CLKIに変調がかかっていない場合、デジタルフィルタ104から出力される位相誤差検出量信号PEfltは、PLL回路120がロック状態では一定の値となる。DCO制御コード変調幅加算器105は、このような位相誤差検出量信号PEfltの値に対して三角波状の波形で値が変化するフィードフォワード変調制御信号FFmodの値を減算(もしくは加算)して、DCO制御コードDINとする。より具体的には、位相誤差検出量信号PEflt及びフィードフォワード変調制御信号FFmodから(PEflt−FFmod)を演算し、演算結果をDCO制御コードDINとして出力する。なお、便宜上、各信号を示す符号は、信号名と同時にその信号が有するデジタル値を示すものとし、以降でも同様とする。なお、DCO制御コードDINの値は、予め設定された所定の値p〜p−DCOvalの範囲となる。但し、pは予め設定された所定の値、DCOvalは後述するDCO制御コード変化幅値である。また、変調制御回路110と、DCO制御コード変調幅加算器105とで、周波数変調部を構成するものとする。

【0026】

デジタル制御発振器(DCO)101は、入力したDCO制御コードDINに応じた発振周波数で出力クロック信号CLKOを出力する。但し、DCO制御コードDINは、上述のように、三角波状の波形で値が変化するため、デジタル制御発振器101が出力する出力クロック信号CLKOの周波数も、その三角波状の波形で変動する値に応じて変調される。より具体的には、出力クロック信号CLKOの周波数は、Fref×N〜Fref×N×(1−Fdit)の変調度で変調される。このように、出力クロック信号CLKOのクロック周波数を変動させることで、周波数スペクトルの電力ピークを低減させる。なお、このようにDCO制御コードDINの値の変動によって、出力クロック信号CLKOの周波数が変動することから、DCO制御コードDINの値をモニタすることは、最終的な出力クロック信号CLKOの周波数の変動をモニタすることになる。但し、Fref、N、Fditは後述する制御クロック周波数設定値、基準逓倍数設定値、変調度設定値である。

【0027】

分周器(DIV)102は、デジタル制御発振器101が出力する出力クロック信号CLKOを、変調制御回路110からの逓倍数変調制御信号Nmodの値に応じて分周し、フィードバッククロック信号CLKIとして出力する。この逓倍数変調制御信号Nmodの値は、変調制御回路110により設定される上記フィードフォワード変調制御信号FFmodと連動したものとなっており、分周器102は、上記フィードフォワード変調制御信号FFmodに応じて周波数が変調された出力クロック信号CLKOの変調を打ち消すように動作する。この動作により、分周器102が出力するフィードバッククロック信号CLKIは、周波数変調が除去された信号としてデジタル位相周波数比較器103にフィードバックされる。また、フィードバッククロック信号CLKIは、後述する変調制御回路110の制御クロックとして利用される。このときのフィードバッククロック信号CLKIの周期をT1とする。この周期T1は、後述する制御クロック周波数設定値Frefにより規定される。

【0028】

変調制御回路110は、DCO制御コードDINの最大値、最小値をモニタする。また、そのモニタ結果に応じて、フィードフォワード変調制御信号FFmodを出力する。また、フィードフォワード変調制御信号FFmodの設定と、連動した設定の逓倍数変調制御信号Nmodを出力する。変調制御回路110は、変調パラメータ制御部111と、変調振幅モニタ部112と、フィードフォワード変調制御部(MODFF)113と、フィードバック変調制御部(MODFB)114とを有する。なお、変調制御回路110は、制御クロックに応じて動作している。ここでは、その制御クロックとして分周器(DIV)102からのフィードバッククロック信号CLKIを利用するものとする。但し、制御クロックとして、フィードバッククロック信号CLKI以外の他のクロックを用いてもかまわない。

【0029】

変調パラメータ制御部111は、設定信号として、変調度設定値Fditと、変調プロファイル周波数設定値Fmodと、制御クロック周波数設定値Frefと、基準逓倍数設定値Nとを入力する。変調パラメータ制御部111は、上記変調設定信号に応じて逓倍数変化幅信号Nval及び変調ステップ数信号NUMmodを出力する。また、制御クロック数をカウントし、変調ステップ数NUMmodの所定の倍数に一致するごとに変調極性信号MODSIGNの論理レベルの極性(0もしくは1)を変化させて出力する。なお、変調極性信号MODSIGNの論理レベルが1のとき出力クロック信号CLKOの周波数が増加し、論理レベルが0のとき出力クロック信号CLKOの周波数が減少するよう変調制御回路110で設定される。

【0030】

より具体的には、逓倍数変化幅信号Nvalは、基準逓倍数設定値N及び変調度設定値Fditから、Nval=N×Fditを演算し、その演算結果として変調パラメータ制御部111から出力される。後述するが、この逓倍数変化幅信号Nvalの値の間で逓倍数変調制御信号Nmodが変化する。

【0031】

また、変調ステップ数信号NUMmodは、変調極性信号MODSIGNの論理レベルの極性変化の期間を規定する。例えば、変調極性信号MODSIGNの論理レベルの極性変化の期間をT2とするならば、T2=1/2Fmodとなる。そして、期間T2は、T2=制御クロック1周期(1/Fref)×NUMmodであるため、NUMmod=Fref/2Fmodとなる。このような演算結果として変調ステップ数信号NUMmodが変調パラメータ制御部111から出力される。

【0032】

変調振幅モニタ部112は、DCO制御コード変調幅加算器105からのDCO制御コードDINと、変調パラメータ制御部111からの変調極性信号MODSIGNに応じて、DCO制御コード変化幅値DCOvalを出力する。より具体的には、変調極性信号MODSIGNの1周期のDCO制御コードDINの最大値をDCOmax、最小値をDCOminとして求める。そして、変調極性信号MODSIGNの立ち上がりエッジ及び立ち下がりエッジ毎に、DCO制御コードDINの値の変化幅、つまり、(DCOmax−DCOmin)の演算結果のDCO制御コード変化幅値DCOvalを出力する。但し、PLL回路120のループ帯域(追従速度)と、後述するフィードフォワード変調制御信号FFmodの振幅を決定する速度とが近い場合に、PLL回路120の出力クロック信号CLKOの周波数が不安定になってしまう。このため、変調動作開始から所定の期間、変調振幅モニタ部112は、DCO制御コード変化幅値DCOvalを移動平均した値を制御信号DVSとして、フィードフォワード変調制御部113に出力することが好ましい。この制御信号DVSの値は、最終的にはDCO制御コード変化幅値DCOvalに到達するが、このDCO制御コード変化幅値DCOvalに到達するまで、移動平均のタップ数に応じた所定の期間で段階的に増加(もしくは減少)させることが望ましい。このようにすることでフィードフォワード変調制御信号の振幅を決定する速度を移動平均のタップ数に応じて遅くすることができる。

【0033】

フィードフォワード変調制御部(MODFF)113は、変調パラメータ制御部111からの変調ステップ数信号NUMmod、変調極性信号MODSIGN、及び、変調振幅モニタ部112からのDCO制御コード変化幅値DCOvalに応じて、フィードフォワード変調制御信号FFmodを出力する。より具体的には、変調ステップ数信号NUMmod及びDCO制御コード変化幅値DCOvalから(DCOval/NUMmod)を演算し、演算結果をフィードフォワード変調ステップΔFFstepとする。そして、変調極性信号MODSIGNの各極性(0もしくは1)の期間中に継続して、制御クロックのエッジ毎に、フィードフォワード変調ステップΔFFstepの値を加算もしくは減算して積算する。その積算結果をフィードフォワード変調制御信号FFmodとして出力する。なお、フィードフォワード変調制御信号FFmodの値は、0〜DCOvalの範囲となる。

【0034】

フィードバック変調制御部(MODFB)114は、変調パラメータ制御部111からの変調ステップ数信号NUMmod、変調極性信号MODSIGN、逓倍数変化幅信号Nvalに応じて、逓倍数変調制御信号Nmodを出力する。より具体的には、変調ステップ数信号NUMmod及び逓倍数変化幅信号Nvalから(Nval/NUMmod)を演算し、演算結果を逓倍数変調ステップΔFBstepとする。そして、変調極性信号MODSIGNの各極性(0もしくは1)の期間中に継続して、制御クロックのエッジ毎に、逓倍数変調ステップΔFBstepの値を加算もしくは減算して積算し、その積算結果をフィードバック信号制御信号FBmodとする。なお、フィードバック信号制御信号FBmodの値は、0〜Nvalの範囲となる。そして、基準逓倍数設定値Nとフィードバック信号制御信号FBmodとの差(N−FBmod)を演算し、演算結果を逓倍数変調制御信号Nmodとして出力する。なお、逓倍数変調制御信号Nmodの値は、N−Nval〜Nの範囲となる。

【0035】

以上のようなSSCG100の動作を以下に説明する。まず、図2にSSCG100の動作のフローチャートを示す。図2に示すように、まず変調パラメータ制御部111にて、変調設定信号に応じて逓倍数変化幅信号Nval及び変調ステップ数信号NUMmodを演算して出力する。また、制御クロック数をカウントし、変調ステップ数NUMmodの所定の倍数に一致するごとに変調極性信号MODSIGNの論理レベルの極性(0もしくは1)を変化させて出力する(S101)。

【0036】

そして、変調幅モニタ部112では、変調極性信号MODSIGNの1周期の期間において、DCO制御コードDINの最大値をDCOmax、最小値をDCOminとして求める(S111)。次に、変調極性信号MODSIGNの立ち上がりエッジ及び立ち下がりエッジ毎に、DCO制御コードDINの値の変化幅、つまり、(DCOmax−DCOmin)をDCO制御コード変化幅値DCOvalとして出力する(S112)。これら、ステップS111、S112は、変調振幅幅モニタ部112での動作フロー(FLOW1)である。

【0037】

そして、フィードフォワード変調制御部(MODFF)113では、変調ステップ数信号NUMmod及びステップS112でのDCO制御コード変化幅値DCOvalから(DCOval/NUMmod)を演算し、演算結果をフィードフォワード変調ステップΔFFstepとする(S121)。次に、変調極性信号MODSIGNの各極性(0もしくは1)の期間中に継続して、制御クロックのエッジ毎に、フィードフォワード変調ステップΔFFstepの値を加算もしくは減算して積算する。その積算結果をフィードフォワード変調制御信号FFmodとして出力する(S122)。これら、ステップS121、S122は、フィードフォワード変調制御部113での動作フロー(FLOW2)である。

【0038】

そして、フィードバック変調制御部(MODFB)114では、変調ステップ数信号NUMmod及び逓倍数変化幅信号Nvalから(Nval/NUMmod)を演算し、演算結果を逓倍数変調ステップΔFBstepとする(S131)。次に、変調極性信号MODSIGNの各極性(0もしくは1)の期間中に継続して、制御クロックのエッジ毎に、逓倍数変調ステップΔFBstepの値を加算もしくは減算して積算し、その積算結果をフィードバック信号制御信号FBmodとする(S132)。次に、基準逓倍数設定値Nとフィードバック信号制御信号FBmodとの差(N−FBmod)を演算し、演算結果を逓倍数変調制御信号Nmodとして出力する(S133)。これら、ステップS131〜S133は、フィードバック変調制御部114での動作フロー(FLOW3)である。

【0039】

そして、DCO制御コード変調幅加算器105では、後述するステップS145での位相誤差検出量信号PEflt及びステップS122でのフィードフォワード変調制御信号FFmodから(PEflt−FFmod)を演算し、演算結果をDCO制御コードDINとして出力する(S141)。次に、デジタル制御発振器(DCO)101では、入力したDCO制御コードDINに比例した発振周波数で出力クロック信号CLKOを出力する(S142)。次に、分周器(DIV)102では、デジタル制御発振器101が出力する出力クロック信号CLKOを、ステップS133での逓倍数変調制御信号Nmodの値に応じて分周し、フィードバッククロック信号CLKIとして出力する(S143)。

【0040】

次に、デジタル位相周波数比較器(DPFD)103では、リファレンスクロック信号RCLKと、分周器102からのフィードバッククロック信号CLKIとの位相誤差を、デジタル信号である位相誤差検出量信号PEとして出力する(S144)。次に、デジタルフィルタ(DFLT)104では、入力した位相誤差検出量信号PEを任意の帯域でフィルタリングして、そのフィルタリングした位相誤差検出量をデジタル信号である位相誤差検出量信号PEfltとして出力する(S145)。これら、ステップS141〜S145は、PLL回路120での動作フロー(FLOW4)である。以上が、SSCG100の動作のフローチャートの説明である。

【0041】

ここで、ステップS141〜S145のPLL回路120の動作フロー(FLOW4)により、フィードバックループが形成されていることがわかる。そして、更にFLOW4のフィードバックループとは別に、ステップS111、S112、S121、S122、S141で構成されるフィードバックループが形成されていることがわかる。これは、PLL回路120のフィードバックループとは別に、DCO制御コード変調幅加算器105と、変調振幅モニタ部112と、フィードフォワード変調制御部113とで構成されるフィードバックループである。これは、PLL回路120のデジタル制御発振器101から見て、フィードフォワード制御にあたる。

【0042】

そして、デジタル制御発振器101が出力する出力クロック信号CLKOのクロック周波数の変調度は、上記のようなフィードフォワード制御により制御されている。つまり、デジタル制御発振器101に入力されるDCO制御コードDINの最大値と最小値を変調振幅モニタ部112がモニタし、そのモニタ結果(最大値と最小値の差であるDCOval)に応じたフィードフォワード変調制御信号FFmodをフィードフォワード変調制御部113が出力し、その出力された値をDCO制御コード変調幅加算器105が位相誤差検出量信号PEfltと減算(もしくは加算)演算してDCO制御コードDINを出力する。

【0043】

ここで、従来技術のSSCG2では、電流発振器26から出力される変調された出力信号CLKoutの平均周波数に相当するICO制御電流(発振器制御信号)をモニタする。そして、従来技術のSSCG2は、発振回路(ICO26)の出力信号の変調度の中心点を決定し、その中心点から所定の周波数振幅を決めている。このため、周辺温度の変化や製造ばらつき等の影響により、発振回路(ICO26)の周波数特性が設定したものとずれた場合、発振回路(ICO26)が出力する出力信号の周波数変調範囲もずれる問題があった。

【0044】

一方、本実施の形態のSSCG100では、上述したフィードフォワード制御によりDCO制御コードDINの最大値と最小値をモニタする。このため、SSCG2で上記問題発生の原因となっていた、発振回路(ICO26)からの出力信号の変調度の中心点を決定し、その中心点から所定の周波数振幅を決定する従来のような制御の形態をとっていない。

【0045】

このように、本実施の形態のSSCG100は、出力クロック信号CLKOの変調を、上記フィードフォワード制御によりデジタル制御発振器101に入力されるDCO制御コードDINを制御することで行っており、発振回路(本例のデジタル制御発振器101)の温度変化等の条件に影響されず、安定した変調度で出力発振信号を生成することができる。

【0046】

次に、図2で説明したフローチャート動作による、SSCG100の動作タイミングチャートを図3に示す。なお、以下で説明するSSCG100の動作の前提として、PLL回路120により、リファレンスクロック信号RCLKとフィードバッククロック信号CLKIとの位相誤差がゼロとなるよう基本的なPLL動作が行われているものとする。このため、基本的なPLLとしての動作は、特に必要な箇所以外、ここでは省略する。

【0047】

そして、SSCG100では、上述してきたように、このPLL回路120から出力される出力クロック信号CLKOに軽微な周波数変調をかけることで、スペクトラム拡散を行っている。なお、軽微な周波数変調とは、例えば、出力クロック信号CLKOのクロック周波数が400MHzである場合、20MHz(5%)の変調をかける変調動作を行うことがあげられる。以下のタイミングチャートの動作の説明は、SSCG100が行う周波数変調の動作を示すものであり、図3に示す各信号波形はこの変調動作に対するプロファイル(以下、変調プロファイルと称す)を示すものであることに注意する。

【0048】

まず、変調パラメータ制御部111から、変調設定信号として、変調極性信号MODSIGN、逓倍数制御信号Nmod、変調ステップ数信号NUMmod、基準逓倍数設定値Nが出力されている。この変調設定信号に応じて、逓倍数制御信号Nmodがフィードバック変調制御部114から出力される。

【0049】

図3に示すように、SSCG100の変調動作の初期状態である時刻t0以前では、DCO制御コード変調幅加算器105に入力されるフィードフォワード変調制御信号FFmodがゼロである。このため、SSCG100の周波数変調は、PLL回路120の分周器102の動作のみで行われている。

【0050】

ここで、分周器102の動作のみで変調動作を行っている場合、PLL回路120のPLL動作により、出力クロック信号CLKOの変調度(変調プロファイルの振幅)は設定値(基準逓倍数設定値N、変調度設定値Fdit)に応じて比較的正確に調整される。但し、この場合、PLL回路120でフィードバックされるフィードバッククロック信号CLKIの周波数が時間に対して変化することから、デジタル位相周波数比較器103の位相誤差検出信号PEの変調プロファイルも三角波形状から歪みが生じる。このため、DCO制御コードDINの変調プロファイルも、三角波形状にならず、頂点のなまった正弦波のような波形となる。そして、このDCO制御コードDINに応じて出力される出力クロック信号CLKOの変調プロファイルも同様に三角波形状にならず、頂点のなまった正弦波のような波形となる。

【0051】

ここで、SSCG100では、時刻t0〜t3にかけて、DCO制御コードDINをモニタしている変調振幅モニタ部112が、DCO制御コード変化幅信号DCOvalに到達するまで段階的に値を増加させた制御信号DVSを出力する。なお、図3に示す例では、変調幅モニタ部112は、時刻t3で、制御信号DVSの値がDCO制御コード変化幅値DCOvalに到達するまで4回に分けて段階的に増加させて出力している。これは、変調振幅モニタ部112が、DCO制御コード変化幅値DCOvalを4タップの移動平均により演算して、出力している。もし上述のように制御信号DVSの値を段階的に増加させないと、PLL回路120のループ帯域(追従速度)と、フィードフォワード変調制御信号FFmodの振幅を決定する速度とが近い場合に、PLL回路120の出力クロック信号CLKOの周波数が不安定になってしまう。よって、SSCG100では、このことを防ぐため、制御信号DVSの値を所定の期間にかけて、複数回に分けて段階的に増加させて出力している。なお、上記例では、制御信号DVSの値を4タップの移動平均により演算して出力しているが、更に複数のタップの移動平均を行っても良い。

【0052】

上述のように、段階的に値を増加した制御信号DVSの値により時刻t1からフィードフォワード変調ステップΔFFstepも段階的に増加する。そして、この段階的に増加したフィードフォワード変調ステップΔFFstepに応じて、フィードフォワード変調制御信号FFmodの変調プロファイルの振幅幅も図3に示すように段階的に大きくなる。

【0053】

一方、フィードフォワード変調制御信号FFmodの変調プロファイルの振幅幅が大きくなるごとに、分周器102の出力するフィードバッククロック信号CLKIと、リファレンスクロック信号RCLKとの位相差が小さくなる。つまり、位相誤差検出量信号PE、更には、その位相誤差検出量信号PEをデジタルフィルタ104でフィルタリングしたPEfltも値がゼロに近づいていく。このことから、逓倍数制御信号Nmodに応じて分周器102で行っていた変調動作の影響が段階的に減少していく。

【0054】

例えば、時刻t4以降では、逓倍数制御信号Nmodに応じて分周器102が行う出力クロック信号CLKOの分周動作による周波数変調と、フィードフォワード変調制御信号FFmodに応じて行われる出力クロック信号CLKOの周波数変調が打ち消しあう。このため、分周器102から出力されるフィードバッククロック信号CLKIには、周波数変調がかかっておらず、分周器102の動作のみで変調動作を行っている場合に問題となっていた、位相誤差検出信号PEの変調プロファイルの波形が歪んでいた問題が発生しない。

【0055】

このため、図3に示すように時刻t4以降では、DCO制御コードDINの変調プロファイル、及び、DCO制御コードDINに応じて出力される出力クロック信号CLKOの変調プロファイルも理想的な三角波形状となることができる。以上が、SSCG100の動作の説明である。

【0056】

ここで、SSCG2では変調した信号がなまってしまうという問題は解決できるが、構成するPLLの伝達特性のばらつきや、電流発振器26の特性のばらつきに出力信号FOの変調度が影響されるという問題を有していた。このSSCG2は、所望の変調度を得るために電流発振器26に入力する電流Iinを、基準電流I1を中心に同じ幅(前述したaの値)で増減させ、任意の変調度を実現させていた。このため、図7、図8で説明したように電流発振器26の特性のばらつき等により、変調度が変化してしまう問題があった。

【0057】

更には、この変調度のばらつきを最小限に抑えることと、任意の変調度を得ることの両方を実現するため基準電流I1を何倍にすればよいか、つまりaの値をどのようにするかは、上述したICOゲインが線形でない等の条件下では、設計時に回路シミュレーション等で、慎重に見積もる必要があった。このため設計時間が長期化し、その結果、設計コストが上昇する問題があった。

【0058】

ここで、本実施の形態のSSCG100では、変調動作完了後(例えば、図3の時刻t4以降)の出力クロック信号CLKOの周波数変調に、PLL回路120の逓倍されたフィードバッククロック信号CLKIのPLL動作による変調ではなく、変調振幅モニタ部112、フィードフォワード変調制御部113、DCO制御コード変調幅加算器105で構成される、PLL回路120とは別のフィードバックループ(以後、フィードバックループ1と称す)の動作による変調を行っている。

【0059】

上記変調振幅モニタ部112は、デジタル制御発振器101が入力するDCO制御コードDINの最大値、最小値を直接モニタしている。そして、このDCO制御コードDINの最大値と最小値の差であるDCO制御コード変化幅値DCOvalに応じたフィードフォワード変調制御信号FFmodがDCO制御コード変調幅加算器105に加算されている。

【0060】

ここで上述したように、SSCG2では、出力信号FOの変調度の中心点を決定する基準電流I1がどうしても必要となり、その中心点から同じ値の電流を増減させることになる。しかし、本実施の形態のSSCG100では、SSCG2の電流発振器26に相当するデジタル制御発振器101に入力するDCO制御コードDINを上記フィードバックループ1で生成している。これは、DCO制御コードDINによりデジタル制御発振器101が出力する出力クロック信号CLKOの最高周波数、最低周波数の差を、デジタル制御発振器101に入力されるDCO制御コードDINの最大値、最小値の差としてモニタし、そのDCO制御コードDINの最大値、最小値の差をフィードバックループ1で制御している。このため、SSCG2での問題の原因である出力クロック信号CLKOの変調度の中心点を決定する必要がなく、デジタル制御発振器101の周辺温度等の特性のばらつきの影響を受けない。つまり、SSCG2が有していた問題が発生しない。更には、デジタル制御発振器101の特性のばらつきの影響を受けないため、SSCG2で問題となっていた、設計時間の長期化する問題も発生しない。

【0061】

また、上記ように、PLL回路120とは別のフィードバックループで変調動作が行われるため、PLLのフィルタ特性に制限されることなく任意の変調プロファイルを生成可能となる。このことから、出力クロック信号CLKOの変調プロファイルを理想的な三角波形状にでき、周波数スペクトラムを図5(b)に示すようなフラットな特性にすることができる。

【0062】

ここで、本実施の形態のような完全デジタルPLLでは、アナログPLLで必須のローパスフィルタのような回路面積の増大要因であるアナログ素子を必要としない。その代わりに、デジタルフィルタ等のデジタル信号処理を行うデジタル回路で構成される。デジタル回路は、CMOS技術の微細化により回路面積の縮小が可能である利点を有する。また、位相比較もデジタルデータで行うため、アナログPLLのような、周波数ジャンプによる出力クロック信号への入力クロック信号の漏れも発生しない。加えて、分周器に対する正確な小数点逓倍も可能になる。なお、このような、完全デジタルPLLの例としては、特開2002−76886号公報のような技術がある。

【0063】

ここで、本実施の形態のSSCG100も、完全デジタルPLLであり、フィードバック変調制御部114から出力されるデジタル信号の変調ステップ数信号NUMmodにより分周器102の逓倍数を小数点まで制御することが可能である。よって、PLLを構成する分周器の逓倍数が整数のみしか制御できない場合に比べ、位相比較時の位相誤差を連続的に変化させることができる。これにより、出力クロック信号CLKOの周波数変調の推移も滑らかになり、スプリアスの影響を軽減させることができる。また、上記したアナログPLLに対する他の利点も当然有する。

【0064】

なお、本発明は上記実施の形態に限られたものでなく、趣旨を逸脱しない範囲で適宜変更することが可能である。例えば、図3の例では、SSCG100の変調動作の初期状態である時刻t0ではフィードフォワード変調制御信号FFmodの変調プロファイルの変化幅をゼロとしている。しかし、必ずしも初期状態時にフィードフォワード変調制御信号FFmodの変調プロファイルの変化幅をゼロとする必要はなく、ゼロ以上の任意の値であってもよい。例えば、変調動作の初期状態である時刻t0にフィードフォワード変調制御信号FFmodの変調プロファイルの変化幅を、DCOvalの3倍の値としてもかまわない。この場合でも、変調振幅モニタ部112により行われる移動平均のタップ数後にはフィードフォワード変調制御信号FFmodの変調プロファイルの変化幅値がDCOvalに収束する。結果として、それぞれの信号のプロファイルは、図3の時刻t4以降と同様の波形となる。

【符号の説明】

【0065】

100 SSCG

101 デジタル制御発振器(DCO)

102 分周器(DIV)

103 デジタル位相周波数比較器(DPFD)

104 デジタルフィルタ(DFLT)

105 DCO制御コード変調幅加算器

110 変調制御回路

111 変調パラメータ制御部

112 変調振幅モニタ部

113 フィードフォワード変調制御部(MODFF)

114 フィードバック変調制御部(MODFB)

【特許請求の範囲】

【請求項1】

周波数変調した出力発振信号を出力するPLL回路を有するスペクトラム拡散信号生成回路であって、

前記PLL回路は、入力した発振制御信号の値に応じた周波数で前記出力発振信号を出力する発振回路を備え、

前記PLL回路によりフィードバックされたPLL信号の周波数を変調させる前記発振制御信号を生成し、この前記発振制御信号の最大値と最小値をモニタし、そのモニタ結果により前記発振制御信号の最大値と最小値を調整することで、前記出力発振信号の変調度を所定の値に制御する周波数変調部を有する

スペクトラム拡散クロック生成回路。

【請求項2】

前記周波数変調部は、加算器と、制御部を備え、

前記加算器は、前記周波数変調部に入力される前記PLL回路によりフィードバックされたPLL信号に応じた値に、第1の周波数変調制御信号の値を加算し、前記発振制御信号として出力し、

前記制御部は、前記加算器が出力した前記発振制御信号の値の最大値と最小値をモニタし、そのモニタ結果に応じて、前記出力発振信号の変調度を所定の値となるような前記第1の周波数変調制御信号を前記加算器に出力する

請求項1に記載のスペクトラム拡散クロック生成回路。

【請求項3】

前記PLL回路は、分周器と、位相比較器と、フィルタを有し、

前記分周器は、逓倍数変調制御信号に応じた値で前記出力発振信号を分周したフィードバック信号を出力し、

前記位相比較器は、前記フィードバック信号と、リファレンス信号との位相誤差を位相誤差検出量信号として出力し、

前記フィルタは、前記位相誤差検出量信号を所定の帯域でフィルタリングして、前記加算器に出力する

請求項2に記載のスペクトラム拡散クロック生成回路。

【請求項4】

前記PLL回路は、完全デジタルPLL回路である

請求項3に記載のスペクトラム拡散クロック生成回路。

【請求項5】

前記制御回路は、変調パラメータ制御部と、変調振幅モニタ部と、フィードフォワード変調制御部と、フィードバック変調制御部とを有し、

前記変調パラメータ制御部は、入力設定信号に応じて、前記分周器の逓倍数の変化を規定する逓倍数変化幅信号、及び、前記出力発振信号の周波数変調の変調度を規定する変調ステップ数信号、及び、前記出力発振信号の周波数変調の1周期を規定する変調極性信号を出力し、

前記変調振幅モニタ部は、前記発振制御信号をモニタし、変調極性信号に対応した1周期での前記発振制御信号の最大値と最小値の差を変化幅値として出力し、

前記フィードフォワード変調制御部は、前記変化幅値と、前記変調ステップ数信号と、変調極性信号に応じて、前記第1の周波数変調制御信号を出力し、

前記フィードバック変調制御部は、逓倍数変化幅信号と、前記変調ステップ数信号と、変調極性信号に応じて、前記逓倍数変調制御信号を出力する

請求項4に記載のスペクトラム拡散クロック生成回路。

【請求項6】

前記変調振幅モニタ部は、移動平均により、所定の回数に分けて段階的に前記変化幅値を変化させて出力する

請求項5に記載のスペクトラム拡散クロック生成回路。

【請求項7】

前記分周器の前記逓倍数変調制御信号に応じた逓倍数の変化は、前記発振制御信号に応じて出力される前記出力発振信号の周波数変化と同位相となる

請求項5もしくは請求項6に記載のスペクトラム拡散クロック生成回路。

【請求項8】

周波数変調した出力発振信号を出力するPLL回路を有するスペクトラム拡散信号生成回路の制御方法であって、

前記PLL回路が備える発振回路が、入力した発振制御信号の値に応じた周波数で前記出力発振信号を出力し、

前記PLL回路によりフィードバックされたPLL信号の周波数を変調させる前記発振制御信号を生成し、

前記発振制御信号の最大値と最小値をモニタし、

前記モニタした結果により前記発振制御信号の最大値と最小値を調整して前記出力発振信号の変調度を所定の値に制御する

スペクトラム拡散信号生成回路の制御方法。

【請求項1】

周波数変調した出力発振信号を出力するPLL回路を有するスペクトラム拡散信号生成回路であって、

前記PLL回路は、入力した発振制御信号の値に応じた周波数で前記出力発振信号を出力する発振回路を備え、

前記PLL回路によりフィードバックされたPLL信号の周波数を変調させる前記発振制御信号を生成し、この前記発振制御信号の最大値と最小値をモニタし、そのモニタ結果により前記発振制御信号の最大値と最小値を調整することで、前記出力発振信号の変調度を所定の値に制御する周波数変調部を有する

スペクトラム拡散クロック生成回路。

【請求項2】

前記周波数変調部は、加算器と、制御部を備え、

前記加算器は、前記周波数変調部に入力される前記PLL回路によりフィードバックされたPLL信号に応じた値に、第1の周波数変調制御信号の値を加算し、前記発振制御信号として出力し、

前記制御部は、前記加算器が出力した前記発振制御信号の値の最大値と最小値をモニタし、そのモニタ結果に応じて、前記出力発振信号の変調度を所定の値となるような前記第1の周波数変調制御信号を前記加算器に出力する

請求項1に記載のスペクトラム拡散クロック生成回路。

【請求項3】

前記PLL回路は、分周器と、位相比較器と、フィルタを有し、

前記分周器は、逓倍数変調制御信号に応じた値で前記出力発振信号を分周したフィードバック信号を出力し、

前記位相比較器は、前記フィードバック信号と、リファレンス信号との位相誤差を位相誤差検出量信号として出力し、

前記フィルタは、前記位相誤差検出量信号を所定の帯域でフィルタリングして、前記加算器に出力する

請求項2に記載のスペクトラム拡散クロック生成回路。

【請求項4】

前記PLL回路は、完全デジタルPLL回路である

請求項3に記載のスペクトラム拡散クロック生成回路。

【請求項5】

前記制御回路は、変調パラメータ制御部と、変調振幅モニタ部と、フィードフォワード変調制御部と、フィードバック変調制御部とを有し、

前記変調パラメータ制御部は、入力設定信号に応じて、前記分周器の逓倍数の変化を規定する逓倍数変化幅信号、及び、前記出力発振信号の周波数変調の変調度を規定する変調ステップ数信号、及び、前記出力発振信号の周波数変調の1周期を規定する変調極性信号を出力し、

前記変調振幅モニタ部は、前記発振制御信号をモニタし、変調極性信号に対応した1周期での前記発振制御信号の最大値と最小値の差を変化幅値として出力し、

前記フィードフォワード変調制御部は、前記変化幅値と、前記変調ステップ数信号と、変調極性信号に応じて、前記第1の周波数変調制御信号を出力し、

前記フィードバック変調制御部は、逓倍数変化幅信号と、前記変調ステップ数信号と、変調極性信号に応じて、前記逓倍数変調制御信号を出力する

請求項4に記載のスペクトラム拡散クロック生成回路。

【請求項6】

前記変調振幅モニタ部は、移動平均により、所定の回数に分けて段階的に前記変化幅値を変化させて出力する

請求項5に記載のスペクトラム拡散クロック生成回路。

【請求項7】

前記分周器の前記逓倍数変調制御信号に応じた逓倍数の変化は、前記発振制御信号に応じて出力される前記出力発振信号の周波数変化と同位相となる

請求項5もしくは請求項6に記載のスペクトラム拡散クロック生成回路。

【請求項8】

周波数変調した出力発振信号を出力するPLL回路を有するスペクトラム拡散信号生成回路の制御方法であって、

前記PLL回路が備える発振回路が、入力した発振制御信号の値に応じた周波数で前記出力発振信号を出力し、

前記PLL回路によりフィードバックされたPLL信号の周波数を変調させる前記発振制御信号を生成し、

前記発振制御信号の最大値と最小値をモニタし、

前記モニタした結果により前記発振制御信号の最大値と最小値を調整して前記出力発振信号の変調度を所定の値に制御する

スペクトラム拡散信号生成回路の制御方法。

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【公開番号】特開2011−234104(P2011−234104A)

【公開日】平成23年11月17日(2011.11.17)

【国際特許分類】

【出願番号】特願2010−102262(P2010−102262)

【出願日】平成22年4月27日(2010.4.27)

【出願人】(302062931)ルネサスエレクトロニクス株式会社 (8,021)

【Fターム(参考)】

【公開日】平成23年11月17日(2011.11.17)

【国際特許分類】

【出願日】平成22年4月27日(2010.4.27)

【出願人】(302062931)ルネサスエレクトロニクス株式会社 (8,021)

【Fターム(参考)】

[ Back to top ]