スーパージャンクション構造を有する半導体装置

【課題】高温環境下で半導体装置に長時間逆バイアスを与えた場合であってもリーク電流が増加したり耐圧が低下したりすることのない、スーパージャンクション構造を有する半導体装置を提供する。

【解決手段】n−型半導体層(第1導電型の半導体層)114と、活性領域R1に形成された複数の柱状埋込層118と、活性領域R1に形成されたショットキーバリアメタル層(第1電極層)132と、耐圧領域R2に形成された複数のガードリング層(環状柱状埋込層)124と、耐圧領域R2及び周辺領域R3に形成された絶縁層130とを備える、スーパージャンクション構造を有する半導体装置であって、周辺領域R3に形成された第2ガードリング層(第2環状柱状埋込層)136と、周辺領域R3に形成された環状導電層142とをさらに備える、スーパージャンクション構造を有する半導体装置100。

【解決手段】n−型半導体層(第1導電型の半導体層)114と、活性領域R1に形成された複数の柱状埋込層118と、活性領域R1に形成されたショットキーバリアメタル層(第1電極層)132と、耐圧領域R2に形成された複数のガードリング層(環状柱状埋込層)124と、耐圧領域R2及び周辺領域R3に形成された絶縁層130とを備える、スーパージャンクション構造を有する半導体装置であって、周辺領域R3に形成された第2ガードリング層(第2環状柱状埋込層)136と、周辺領域R3に形成された環状導電層142とをさらに備える、スーパージャンクション構造を有する半導体装置100。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、スーパージャンクション構造を有する半導体装置に関する。

【背景技術】

【0002】

スーパージャンクション構造を有する半導体装置が知られている(例えば、特許文献1参照。)。図15は、従来のスーパージャンクション構造を有する半導体装置900を説明するために示す図である。図15(a)は従来のスーパージャンクション構造を有する半導体装置900の平面図であり、図15(b)は従来のスーパージャンクション構造を有する半導体装置900の断面図である。図15(b)は図15(a)のA−A断面図である。なお、図15(a)においては、理解を容易にするために、柱状埋込層918、環状柱状埋込層924及びショットキーバリアメタル層932のみを示している。

【0003】

従来のスーパージャンクション構造を有する半導体装置900は、図15に示すように、n−型半導体層(第1導電型の半導体層)914と、活性領域R1における半導体層914の表面に形成され、p型シリコン(第2導電型の半導体材料)からなる複数の柱状埋込層918と、活性領域R1におけるn−型半導体層914の表面上に形成されたアノード電極層としてのショットキーバリアメタル層(第1電極層)932と、活性領域R1を囲む耐圧領域R2におけるn−型半導体層914の表面に形成され、p型シリコンからなる複数のガードリング(環状柱状埋込層)924と、耐圧領域R2及び耐圧領域R2を囲む周辺領域R3におけるn−型半導体層914の表面上に形成された絶縁層930と、カソード電極層950とを備える、ショットキーバリアダイオードである。なお、図15(b)中、符号912はn+型半導体基板を示し、符号910は半導体基体を示し、符号920はp型高濃度オーミック拡散領域を示し、符号926はショットキーバリアメタル電界緩和領域を示し、符号928は中継拡散領域を示し、符号933はアノード電極層を示す。

【0004】

従来のスーパージャンクション構造を有する半導体装置900によれば、活性領域を囲む耐圧領域R2におけるn−型シリコン層914の表面には複数(例えば数十本)のガードリング924が設けられているため、逆バイアス時には空乏層が活性領域R1から耐圧領域R2の最外周部まで伸長するため、スーパージャンクション構造を有する半導体装置の耐圧を高くすることができる。

【先行技術文献】

【特許文献】

【0005】

【特許文献1】特開2004−6595号公報

【発明の概要】

【発明が解決しようとする課題】

【0006】

しかしながら、本発明の発明者の研究によれば、従来のスーパージャンクション構造を有する半導体装置900には以下のような問題があることがわかった。すなわち、従来のスーパージャンクション構造を有する半導体装置900においては、高温環境下で半導体装置に長時間逆バイアスを与えた場合には、リーク電流が増加したり耐圧が低下したりするという問題があることがわかった。

【0007】

そこで、本発明はこのような問題を解決するためになされたものであり、高温環境下で半導体装置に長時間逆バイアスを与えた場合であってもリーク電流が増加したり耐圧が低下したりすることのない、スーパージャンクション構造を有する半導体装置を提供することを目的とする。

【課題を解決するための手段】

【0008】

[1]本発明のスーパージャンクション構造を有する半導体装置は、第1導電型の半導体層と、活性領域における前記半導体層の表面に形成され、第2導電型の半導体材料からなる複数の柱状埋込層と、前記活性領域における前記半導体層の表面上に形成された第1電極層と、活性領域を囲む耐圧領域における前記半導体層の表面に形成され、第2導電型の半導体材料からなる複数の環状柱状埋込層と、前記耐圧領域及び当該耐圧領域を囲む周辺領域における前記半導体層の表面上に形成された絶縁層とを備える、スーパージャンクション構造を有する半導体装置であって、前記周辺領域における前記半導体層の表面に形成され、第2導電型の半導体材料からなる第2環状柱状埋込層と、前記周辺領域における前記絶縁層上に形成された環状導電層とをさらに備えることを特徴とする。

【0009】

[2]本発明のスーパージャンクション構造を有する半導体装置においては、前記絶縁層は、前記周辺領域における前記第2環状柱状埋込層が形成されている領域において開口部を有し、前記環状導電層は、前記開口部を介して、前記第2環状柱状埋込層に接続されていることが好ましい。

【0010】

[3]本発明のスーパージャンクション構造を有する半導体装置においては、前記環状導電層に接続されている第2環状柱状埋込層の表面近傍には、第2導電型の高濃度拡散領域が形成されていることが好ましい。

【0011】

[4]本発明のスーパージャンクション構造を有する半導体装置においては、前記絶縁層は、前記周辺領域における前記第2環状柱状埋込層が形成されていない領域において開口部を有し、前記環状導電層は、前記開口部を介して、前記半導体層に接続されていることも好ましい。

【0012】

[5]本発明のスーパージャンクション構造を有する半導体装置においては、前記環状導電層に接続されている領域における前記半導体層の表面には、第1導電型の高濃度拡散領域が形成されていることが好ましい。

【0013】

[6]本発明のスーパージャンクション構造を有する半導体装置においては、最外周の第2環状柱状埋込層よりも外周側に伸びる前記第2環状導電層の幅寸法は、第2環状柱状埋込層の深さ寸法よりも大きいことが好ましい。

【0014】

[7]本発明のスーパージャンクション構造を有する半導体装置においては、前記環状導電層として、複数の環状導電層を備えることが好ましい。

【0015】

[8]本発明のスーパージャンクション構造を有する半導体装置においては、前記第2環状柱状埋込層として、複数の第2環状柱状埋込層を備えることが好ましい。

【0016】

[9]本発明のスーパージャンクション構造を有する半導体装置においては、前記環状導電層は、最内周の第2環状柱状埋込層に接続されていることが好ましい。

【発明の効果】

【0017】

本発明のスーパージャンクション構造を有する半導体装置によれば、後述する実施例1及び2からも明らかなように、高温環境下で半導体装置に長時間逆バイアスを与えた場合であってもリーク電流が増加したり耐圧が低下したりすることがなくなる。

【0018】

なお、現段階ではそのメカニズムの詳細は明らかでないが、後述する図5に示すように、本発明のスーパージャンクション構造を有する半導体装置の場合には、第2環状柱状埋込層と、当該第2環状柱状埋込層の上方に形成された環状導電層とをさらに備えることから、逆バイアス時には第1電極層と環状導電層とがそれぞれキャパシターの2つの電極として機能するようになるため、高温環境下で半導体装置に長時間逆バイアスを与えた場合などに絶縁層の表面において生成することがある可動イオンが、第1電極層と環状導電層との間の電位差によりどちらかの電極に捕獲され、その結果、可動イオンの存在に起因してリーク電流が増加したり耐圧が低下したりすることがなくなるためであると本発明の発明者らは推測している。

【図面の簡単な説明】

【0019】

【図1】実施形態1に係るスーパージャンクション構造を有する半導体装置100を説明するために示す図である。

【図2】実施形態1に係るスーパージャンクション構造を有する半導体装置100を製造する方法を説明するために示す図である。

【図3】実施形態1に係るスーパージャンクション構造を有する半導体装置100を製造する方法を説明するために示す図である。

【図4】実施形態1に係るスーパージャンクション構造を有する半導体装置100を製造する方法を説明するために示す図である。

【図5】実施形態1に係るスーパージャンクション構造を有する半導体装置100の作用・効果を説明するために示す図である。

【図6】実施形態2に係るスーパージャンクション構造を有する半導体装置100aの断面図である。

【図7】実施形態3に係るスーパージャンクション構造を有する半導体装置100bの断面図である。

【図8】実施形態4に係るスーパージャンクション構造を有する半導体装置100cの断面図である。

【図9】実施形態5に係るスーパージャンクション構造を有する半導体装置100dの断面図である。

【図10】実施形態6に係るスーパージャンクション構造を有する半導体装置100eの断面図である。

【図11】実施形態7に係るスーパージャンクション構造を有する半導体装置200の断面図である。

【図12】実施形態8に係るスーパージャンクション構造を有する半導体装置300の断面図である。

【図13】実施例1の評価結果を示す図である。

【図14】実施例2の評価結果を示す図である。

【図15】従来のスーパージャンクション構造を有する半導体装置900を説明するために示す図である。

【発明を実施するための形態】

【0020】

以下、本発明のスーパージャンクション構造を有する半導体装置について、図に示す実施の形態に基づいて説明する。

【0021】

[実施形態1]

1.実施形態1に係るスーパージャンクション構造を有する半導体装置100の構成

まず、実施形態1に係るスーパージャンクション構造を有する半導体装置100の構成を説明する。

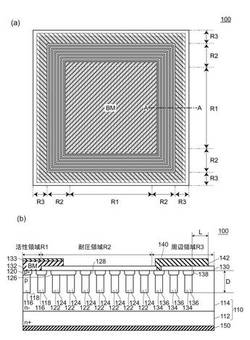

図1は、実施形態1に係るスーパージャンクション構造を有する半導体装置100を説明するために示す図である。図1(a)は実施形態1に係るスーパージャンクション構造を有する半導体装置100の平面図であり、図1(b)は実施形態1に係るスーパージャンクション構造を有する半導体装置100の断面図である。図1(b)は図1(a)のA−A断面図である。なお、図1(a)においては、理解を容易にするために、柱状埋込層118、環状柱状埋込層124、第2環状柱状埋込層136、ショットキーバリアメタル層132及び環状導電層142のみを示している。

【0022】

実施形態1に係るスーパージャンクション構造を有する半導体装置100は、スーパージャンクション構造を有するショットキーバリアダイオードであり、図1(a)に示すように、活性領域R1と、活性領域R1を囲む耐圧領域R2と、耐圧領域R2を囲む周辺領域R3とに分画されている。

【0023】

そして、実施形態1に係るスーパージャンクション構造を有する半導体装置100は、図1(b)に示すように、n−型半導体層(第1導電型の半導体層)114と、活性領域R1におけるn−型半導体層114の表面に形成され、p型シリコン(第2導電型の半導体材料)からなる複数の柱状埋込層118と、活性領域R1におけるn−型半導体層114の表面上に形成されたアノード電極層としてのショットキーバリアメタル層(第1電極層)132と、活性領域R1を囲む耐圧領域R2におけるn−型半導体層114の表面に形成され、p型シリコンからなる複数のガードリング(環状柱状埋込層)124と、耐圧領域R2及び当該耐圧領域R2を囲む周辺領域R3におけるn−型半導体層114の表面上に形成された絶縁層130と、カソード電極層150とを備える、ショットキーバリアダイオードである。なお、図1(b)中、符号112はn+型半導体基板を示し、符号110は半導体基体を示し、符号120はp型高濃度オーミック拡散領域を示し、符号126はショットキーバリアメタル電界緩和領域を示し、符号128は中継拡散領域を示し、符号133はアノード電極層を示す。

【0024】

そして、実施形態1に係るスーパージャンクション構造を有する半導体装置100は、周辺領域R3におけるn−型半導体層114の表面に形成され、p型半導体材料からなる第2環状柱状埋込層136と、周辺領域R3における絶縁層130上に形成された環状導電層142とをさらに備える。

【0025】

実施形態1に係るスーパージャンクション構造を有する半導体装置100においては、絶縁層130は、周辺領域R3における第2環状柱状埋込層136が形成されている領域において開口部140を有し、環状導電層142は、開口部140を介して、第2環状柱状埋込層136に接続されている。

【0026】

実施形態1に係るスーパージャンクション構造を有する半導体装置100においては、環状導電層142に接続されている第2環状柱状埋込層136の表面近傍には、p型高濃度拡散領域(第2導電型の高濃度拡散領域)138が形成されている。

【0027】

実施形態1に係るスーパージャンクション構造を有する半導体装置100においては、最外周の第2環状柱状埋込層136よりも外周側に伸びる環状導電層142の幅寸法Lは、第2環状柱状埋込層136の深さ寸法Dよりも大きい(図1(b)参照。)。

【0028】

n−型半導体層114は、n+型半導体基板112の上部にエピタキシャル成長させることにより形成されたものであって、n+型半導体基板112とn−型半導体層114とで半導体基体110を構成する。n−型半導体層114の厚さは、例えば6μm〜70μmであり、n−型半導体層の不純物濃度は、例えば2×1014cm−3〜5×1016cm−3である。

【0029】

柱状埋込層118は、n−型半導体層114における活性領域R1に形成した第1トレンチ116の内部にエピタキシャル成長させて形成したp型半導体材料(第2導電型半導体材料)からなる。柱状埋込層118の本数は使用目的や構造に合わせて適宜設定することができる。p型半導体材料の不純物濃度は、例えば2×1014cm−3〜5×1016cm−3である。

【0030】

柱状埋込層118の深さは、例えば5μm〜50μmであり、幅は、例えば0.5μm〜5μmである。柱状埋込層118は、それぞれ第1間隔d1で平行に形成されている。第1間隔d1は、例えば1μm〜15μmである。

【0031】

環状柱状埋込層124は、n−型半導体層114における耐圧領域R2に形成した第2トレンチ122の内部にエピタキシャル成長させて形成したp型半導体材料(第2導電型半導体材料)からなる。環状柱状埋込層124の本数は例えば5本〜50本であるが、使用目的や構造に合わせて適宜設定することができる。p型半導体材料の不純物濃度は、例えば2×1014cm−3〜5×1016cm−3である。

【0032】

環状柱状埋込層124の深さは、例えば5μm〜50μmであり、幅は、例えば0.5μm〜5μmである。環状柱状埋込層124は、それぞれ第1間隔d1で平行に形成されている。第1間隔d1は、例えば1μm〜15μmである。

【0033】

第2環状柱状埋込層136は、n−型半導体層114における周辺領域R3に形成した第3トレンチ134の内部にエピタキシャル成長させて形成したp型半導体材料(第2導電型半導体材料)からなる。第2環状柱状埋込層136の本数は例えば1本〜10本であるが、使用目的や構造に合わせて適宜設定することができる。p型半導体材料の不純物濃度は、例えば2×1014cm−3〜5×1016cm−3である。

【0034】

第2環状柱状埋込層136の深さは、例えば5μm〜50μmであり、幅は、例えば0.5μm〜5μmである。環状柱状埋込層124は、それぞれ第1間隔d1で平行に形成されている。第1間隔d1は、例えば1μm〜15μmである。

【0035】

絶縁層130は、シリコン酸化膜からなる。ショットキーバリアメタル層132は、n−型半導体層114とはショットキー接合を形成し、柱状埋込層118とはオーミック接合を形成する。ショットキーバリアメタル層132の材料は例えば白金であり、ショットキーバリアメタル層132の厚さは例えば10nmである。ショットキーバリアメタル層132の上方にはアノード電極層133が形成されている。アノード電極層133の材料は、金属(例えばアルミニウム)であり、アノード電極層133の厚さは例えば3000nmである。環状導電層142の材料は、金属(例えばアルミニウム)であり、環状導電層142の厚さは例えば3000nmである。カソード電極層150は、電極材料である金属(例えばニッケル)を半導体基体110の裏面に蒸着して形成する。カソード電極層150の厚さは、例えば2000nmである。

【0036】

2.実施形態1に係るスーパージャンクション構造を有する半導体装置100を製造する方法

次に、実施形態1に係るスーパージャンクション構造を有する半導体装置100を製造する方法を以下に示す各工程に沿って説明する。

図2〜図4は、実施形態1に係るスーパージャンクション構造を有する半導体装置を製造する方法を説明するために示す図である。図2(a)〜図2(d)、図3(a)〜図3(d)及び図4(a)〜図4(d)は各工程図である。

【0037】

1.半導体基体準備工程

まず、n+型半導体基板112と、n+型半導体基板112の表面側にエピタキシャル成長法により形成したn−型半導体層114とを有する半導体基体110を準備する(図2(a)参照。)。n+型半導体基板112としては、例えばシリコン基板を用いることができるが、炭化珪素SiCや窒化ガリウムGaNからなる基板を用いてもよい。

【0038】

2.各柱状埋込層形成工程

次に、活性領域R1に柱状埋込層118を形成し、耐圧領域R2に環状柱状埋込層124を形成するとともに、周辺領域R3に第2環状柱状埋込層136を形成する。各柱状埋込層形成工程は、トレンチ形成工程と、各柱状埋込層形成工程と、p型高濃度拡散領域形成工程とからなる(図2(b)〜図3(d)参照。)。

【0039】

2−1.トレンチ形成工程

トレンチ形成工程においては、まず、n−型半導体層114を熱酸化することによりn−型半導体層114の上部にトレンチマスクとなる酸化膜M1を形成する(図2(b)参照。)。続いて、図示しないレジスト膜(厚さ:例えば0.8μm。)を形成し、写真工程を実施することにより、柱状埋込層118、環状柱状埋込層124及び第2環状柱状埋込層136の形成位置に開口部を設け、当該開口部における絶縁膜Mをドライエッチングにより除去する(図2(c)参照。)。次に、レジスト膜を取り除き、その後、絶縁膜Mをマスクとしてn−型半導体層114をドライエッチングすることにより、n−型半導体層114の表面に第1トレンチ116、第2トレンチ122及び第3トレンチ134を形成する(図2(d)参照。)。

【0040】

2−2.各柱状埋込層形成工程

各柱状埋込層形成工程においては、第1トレンチ116、第2トレンチ122及び第3トレンチ134の内面について、ケミカルドライエッチングや犠牲酸化、水素アニール等により、トレンチ形成工程のドライエッチングによるダメージ層除去を行った後、p型不純物を含むドーパントガスを導入しながら絶縁膜M表面の高さ位置を超える高さ位置までp型の単結晶半導体材料をエピタキシャル成長させる(図3(a)参照。)。その後、CMP法によって、形成されたキャップ部を絶縁膜Mの表面まで研磨し、その後、絶縁膜Mの開口部内に埋め込まれているp型の単結晶半導体材料を絶縁膜Mの底面まで絶縁膜Mをマスクとしてドライエッチングする。その後、絶縁膜Mをウェットエッチングにより除去する(図3(b)参照。)。

【0041】

2−3.p型高濃度拡散領域形成工程

次に、p型高濃度オーミック拡散領域120,ショットキーバリアメタル電界緩和領域126、中継拡散領域128及びp型高濃度拡散領域138に対応する領域に開口部を有するマスクM2を形成し、このマスクM2を介して、イオン注入法によりp型不純物(例えばボロンイオン)を半導体基体110の表面に導入する(図3(c)参照。)。

その後、半導体基体110に熱処理を施すことにより、p型高濃度オーミック拡散領域120,ショットキーバリアメタル電界緩和領域126、中継拡散領域128及びp型高濃度拡散領域138を形成する(図3(d)参照。)。

【0042】

3.絶縁層形成工程

次に、CVD法により厚さ500nmのシリコン酸化膜を形成した後、活性領域R1及び開口部140に対応する開口を有するマスクM3を用いてシリコン酸化膜のエッチングを行うことによりシリコン酸化膜を除去して、絶縁層130を形成する(図4(a)参照。)。

【0043】

4.ショットキーバリアメタル層形成工程

次に、半導体基体110の表面側から、スパッタ法により、例えば厚さ10nmの白金膜を形成し、所定形状にパターニングした後、半導体基体110を熱処理することにより、ショットキーバリアメタル層132を形成する(図4(b)参照。)。

【0044】

5.環状導電層形成工程

次に、半導体基体110の表面側から、スパッタ法により、例えば厚さ3000nmのアルミニウム膜を形成し、所定形状にパターニングすることによって、アノード電極層133及び環状導電層142を形成する(図4(c)参照。)。

【0045】

6.カソード電極層形成工程

次に、半導体基体110の裏面側に位置するn+型半導体基板112の裏面側に、スパッタ法により、例えば厚さ500nmのニッケル膜を形成することにより、カソード電極層150を形成する(図4(d)参照。)。

【0046】

上記の工程を順次実施することにより、実施形態1に係るスーパージャンクション構造を有する半導体装置100を製造することができる。

【0047】

3.実施形態1に係るスーパージャンクション構造を有する半導体装置100の効果

実施形態1に係るスーパージャンクション構造を有する半導体装置100によれば、後述する実施例1及び2からも明らかなように、高温環境下で半導体装置に長時間逆バイアスを与えた場合であってもリーク電流が増加したり耐圧が低下したりすることがなくなる。

【0048】

図5は、実施形態1に係るスーパージャンクション構造を有する半導体装置100の作用・効果を説明するために示す図である。図5(a)は実施形態1に係るスーパージャンクション構造を有する半導体装置100における逆バイアス時の可動イオンの動きを示す図であり、図5(b)は従来のスーパージャンクション構造を有する半導体装置900における逆バイアス時の可動イオンの動きを示す図である。

【0049】

現段階ではそのメカニズムの詳細は明らかでないが、実施形態1に係るスーパージャンクション構造を有する半導体装置100の場合には、第2環状柱状埋込層136と、当該第2環状柱状埋込層136の上方に形成された環状導電層142とをさらに備えることから、逆バイアス時にはショットキーバリアメタル層132と環状導電層142とがそれぞれキャパシターの2つの電極として機能するようになる。このため、高温環境下で半導体装置に長時間逆バイアスを与えた場合などに絶縁層130の表面において生成することがある可動イオンが、図5に示すように、ショットキーバリアメタル層132と環状導電層142との間の電位差によりどちらかの電極に捕獲され(負の可動イオンは環状導電層142に捕獲され、正の可動イオンはショットキーバリアメタル層132に捕獲される。)、その結果、可動イオンの存在に起因してリーク電流が増加したり耐圧が低下したりすることがなくなるためであると本発明の発明者らは推測している。

【0050】

また、実施形態1に係るスーパージャンクション構造を有する半導体装置100によれば、逆バイアス時には、環状導電層142がカソード電極層150の電位に近い電位を有する第2環状柱状埋込層136に接続されることになるため、ショットキーバリアメタル層132と環状導電層142との間に大きな電位差が発生する。その結果、可動イオンは、ショットキーバリアメタル層132と環状導電層142との間に発生する大きな電位差によりどちらかの電極に確実に捕獲されるようになる。

【0051】

また、実施形態1に係るスーパージャンクション構造を有する半導体装置100によれば、環状導電層142に接続されている第2環状柱状埋込層136の表面近傍には、p型高濃度拡散領域(第2導電型の高濃度拡散領域)138が形成されているため、環状導電層142と第2環状柱状埋込層136との間の抵抗を極めて小さいものにすることが可能となり、ショットキーバリアメタル層132と環状導電層142との間に発生する電位差を毀損することがない。

【0052】

さらにまた、実施形態1に係るスーパージャンクション構造を有する半導体装置100によれば、最外周の第2柱状埋込層136よりも外周側に伸びる環状導電層142の幅寸法が第2環状柱状埋込層136の深さ寸法よりも大きいため、最外の第2環状柱状埋込層136から外周側に伸びる空乏層の上方には環状導電層142が配置されることになり、最外の第2環状柱状埋込層136から外周側に伸びる空乏層の上部の電位が、カソード電極層150の電位に近い電位に固定されるため、可動イオンの影響を受けない安定した電位となる。

【0053】

[実施形態2]

図6は、実施形態2に係るスーパージャンクション構造を有する半導体装置100aの断面図である。

【0054】

実施形態2に係るスーパージャンクション構造を有する半導体装置100aは、基本的には実施形態1に係るスーパージャンクション構造を有する半導体装置100と同様の構成を有するが、図6に示すように、2本の環状導電層142,142aを備える点で、実施形態1に係るスーパージャンクション構造を有する半導体装置100の場合とは異なる。

【0055】

このように、実施形態2に係るスーパージャンクション構造を有する半導体装置100aは、複数の環状導電層142,142aを備える点で、実施形態1に係るスーパージャンクション構造を有する半導体装置100の場合とは異なるが、第2環状柱状埋込層136と、当該第2環状柱状埋込層136の上方に形成された環状導電層142及び環状導電層142aとを備えることから、実施形態1に係るスーパージャンクション構造を有する半導体装置100の場合と同様に、高温環境下で半導体装置に長時間逆バイアスを与えた場合であってもリーク電流が増加したり耐圧が低下したりすることがなくなる。

【0056】

また、実施形態2に係るスーパージャンクション構造を有する半導体装置100aによれば、2本の環状導電層142,142aを備えるため、可動イオンを効率良く捕獲することが可能となる。

【0057】

なお、実施形態2に係るスーパージャンクション構造を有する半導体装置100aにおいては、環状導電型層として2本の環状導電層を備えるものであるが、本発明はこれに限定されるものではない。例えば、環状導電型層として3本以上の環状導電層を備えるものであってもよい。

【0058】

なお、実施形態2に係るスーパージャンクション構造を有する半導体装置100aは、2本の環状導電層142,142aを備える点以外の点においては実施形態1に係るスーパージャンクション構造を有する半導体装置100と同様の構成を有するため、実施形態1に係るスーパージャンクション構造を有する半導体装置100が有する効果のうち該当する効果を有する。

【0059】

[実施形態3]

図7は、実施形態3に係るスーパージャンクション構造を有する半導体装置100bの断面図である。

【0060】

実施形態3に係るスーパージャンクション構造を有する半導体装置100bは、基本的には実施形態1に係るスーパージャンクション構造を有する半導体装置100と同様の構成を有するが、図7に示すように、絶縁層に開口部が形成されていない点で、実施形態1に係るスーパージャンクション構造を有する半導体装置100の場合とは異なる。

【0061】

このように、実施形態3に係るスーパージャンクション構造を有する半導体装置100bは、絶縁層に開口部が形成されていない点で、実施形態1に係るスーパージャンクション構造を有する半導体装置100の場合とは異なるが、実施形態1に係るスーパージャンクション構造を有する半導体装置100の場合と同様に、第2環状柱状埋込層136と、当該第2環状柱状埋込層136の上方に形成された環状導電層142bとをさらに備えることから、高温環境下で半導体装置に長時間逆バイアスを与えた場合であってもリーク電流が増加したり耐圧が低下したりすることがなくなる。

【0062】

なお、実施形態3に係るスーパージャンクション構造を有する半導体装置100bにおいては、絶縁層に開口部が形成されていないため、環状導電層142bが第2環状柱状埋込層136と同電位にはならないが、環状導電層142bは、絶縁層130aを介して第2環状柱状埋込層136に容量結合されることとなるため、実施形態1に係るスーパージャンクション構造を有する半導体装置100の場合と同様に、ショットキーバリアメタル層132と環状導電層142との間には大きな電位差が発生し、これによって、高温環境下で半導体装置に長時間逆バイアスを与えた場合などに絶縁層の表面において生成することがある可動イオンが、ショットキーバリアメタル層132と環状導電層142との間の電位差によりどちらかの電極に捕獲され、その結果、可動イオンの存在に起因してリーク電流が増加したり耐圧が低下したりすることがなくなる。

【0063】

なお、実施形態3に係るスーパージャンクション構造を有する半導体装置100bは、絶縁層に開口部が形成されていない点以外の点においては実施形態1に係るスーパージャンクション構造を有する半導体装置100と同様の構成を有するため、実施形態1に係るスーパージャンクション構造を有する半導体装置100が有する効果のうち該当する効果を有する。

【0064】

[実施形態4]

図8は、実施形態4に係るスーパージャンクション構造を有する半導体装置100cの断面図である。

【0065】

実施形態4に係るスーパージャンクション構造を有する半導体装置100cは、基本的には実施形態1に係るスーパージャンクション構造を有する半導体装置100と同様の構成を有するが、環状導電層142cが開口部140aを介してn−型半導体層114に接続されている点で、実施形態1に係るスーパージャンクション構造を有する半導体装置100の場合とは異なる。すなわち、実施形態4に係るスーパージャンクション構造を有する半導体装置100cにおいては、図8に示すように、環状導電層142cが、第2環状柱状埋込層136が形成されていない領域に形成された開口部140aを介して、n−型半導体層114に接続されている。また、環状導電層142cに接続されている領域におけるn−型半導体層114の表面には、n+型高濃度拡散領域146が形成されている。

【0066】

このように、実施形態4に係るスーパージャンクション構造を有する半導体装置100cは、環状導電層142cが開口部140aを介してn−型半導体層114に接続されている点で、実施形態1に係るスーパージャンクション構造を有する半導体装置100の場合とは異なるが、実施形態1に係るスーパージャンクション構造を有する半導体装置100の場合と同様に、第2環状柱状埋込層136と、当該第2環状柱状埋込層136の上方に形成された環状導電層142cとをさらに備えることから、環状導電層142cがカソード電極150に近い電位に固定され、ショットキーバリアメタル層132と環状導電層142cとの間に発生した電位差により可動イオンが捕獲されるようになるため、高温環境下で半導体装置に長時間逆バイアスを与えた場合であってもリーク電流が増加したり耐圧が低下したりすることがなくなる。

【0067】

なお、実施形態4に係るスーパージャンクション構造を有する半導体装置100cは、環状導電層142cが開口部140aを介してn−型半導体層114に接続されている点以外の点においては実施形態1に係るスーパージャンクション構造を有する半導体装置100と同様の構成を有するため、実施形態1に係るスーパージャンクション構造を有する半導体装置100が有する効果のうち該当する効果を有する。

【0068】

[実施形態5]

図9は、実施形態5に係るスーパージャンクション構造を有する半導体装置100dの断面図である。

【0069】

実施形態5に係るスーパージャンクション構造を有する半導体装置100dは、基本的には実施形態1に係るスーパージャンクション構造を有する半導体装置100と同様の構成を有するが、形成されている第2環状柱状埋込層136の数が実施形態1に係るスーパージャンクション構造を有する半導体装置100の場合とは異なる。すなわち、実施形態5に係るスーパージャンクション構造を有する半導体装置100dにおいては、図9に示すように、1本の第2環状柱状埋込層136が形成されている。

【0070】

このように、実施形態5に係るスーパージャンクション構造を有する半導体装置100dは、形成されている第2環状柱状埋込層136の数が実施形態1に係るスーパージャンクション構造を有する半導体装置100の場合とは異なるが、実施形態1に係るスーパージャンクション構造を有する半導体装置100の場合と同様に、第2環状柱状埋込層136と、当該第2環状柱状埋込層136の上方に形成された環状導電層142dとをさらに備えることから、高温環境下で半導体装置に長時間逆バイアスを与えた場合であってもリーク電流が増加したり耐圧が低下したりすることがなくなる。

【0071】

なお、実施形態5に係るスーパージャンクション構造を有する半導体装置100dは、形成されている第2環状柱状埋込層136の数以外の点においては実施形態1に係るスーパージャンクション構造を有する半導体装置100と同様の構成を有するため、実施形態1に係るスーパージャンクション構造を有する半導体装置100が有する効果のうち該当する効果を有する。

【0072】

[実施形態6]

図10は、実施形態6に係るスーパージャンクション構造を有する半導体装置100eの断面図である。

【0073】

実施形態6に係るスーパージャンクション構造を有する半導体装置100eは、基本的には実施形態5に係るスーパージャンクション構造を有する半導体装置100dと同様の構成を有するが、環状導電層142dが形成されている領域のさらに外側に第2環状柱状埋込層136とは別の第3環状柱状埋込層136aが形成されている点で、実施形態5に係るスーパージャンクション構造を有する半導体装置100dの場合とは異なる。すなわち、実施形態6に係るスーパージャンクション構造を有する半導体装置100eにおいては、図10に示すように、(1本の第2環状柱状埋込層136の上方に位置する)環状導電層142dが形成されている領域のさらに外側に第2環状柱状埋込層136とは別の第3環状柱状埋込層136aが2本形成されている。

【0074】

このように、実施形態6に係るスーパージャンクション構造を有する半導体装置100eは、環状導電層142dが形成されている領域のさらに外側に第2環状柱状埋込層136とは別の第3環状柱状埋込層136aが形成されている点で、実施形態5に係るスーパージャンクション構造を有する半導体装置100dの場合とは異なるが、実施形態5に係るスーパージャンクション構造を有する半導体装置100dの場合と同様に、第2環状柱状埋込層136と、当該第2環状柱状埋込層136の上方に形成された環状導電層142dとをさらに備えることから、高温環境下で半導体装置に長時間逆バイアスを与えた場合であってもリーク電流が増加したり耐圧が低下したりすることがなくなる。

【0075】

また、実施形態6に係るスーパージャンクション構造を有する半導体装置100eによれば、環状導電層142dが形成されている領域のさらに外側に第2環状柱状埋込層136とは別の第3環状柱状埋込層136aが形成されているため、第2環状柱状埋込層136近傍の電界を緩和でき耐圧が安定する。

【0076】

なお、実施形態6に係るスーパージャンクション構造を有する半導体装置100dは、環状導電層142dが形成されている領域のさらに外側に第2環状柱状埋込層136とは別の第3環状柱状埋込層136aが形成されている点以外の点においては実施形態5に係るスーパージャンクション構造を有する半導体装置100dと同様の構成を有するため、実施形態5に係るスーパージャンクション構造を有する半導体装置100dが有する効果のうち該当する効果を有する。

【0077】

[実施形態7]

図11は、実施形態7に係るスーパージャンクション構造を有する半導体装置200の断面図である。実施形態7に係るスーパージャンクション構造を有する半導体装置200は、図11に示すように、n−型半導体層(第1導電型の半導体層)214と、活性領域R1におけるn−型半導体層214の表面に形成され、p型半導体材料(第2導電型の半導体材料)からなる複数の柱状埋込層218と、活性領域R1におけるn−型半導体層214の表面に形成されたp+型拡散層220と、活性領域R1におけるn−型半導体層214の表面上に形成されたアノード電極層(第1電極層)232と、活性領域R1を囲む耐圧領域R2におけるn−型半導体層214の表面に形成され、p型半導体材料からなる複数のガードリング(環状柱状埋込層)224と、耐圧領域R2及び当該耐圧領域R2を囲む周辺領域R3におけるn−型半導体層214の表面上に形成された絶縁層230と、カソード電極層250と、周辺領域R3におけるn−型半導体層214の表面に形成され、p型半導体材料からなる第2環状柱状埋込層236と、周辺領域R3における絶縁層230上に形成された環状導電層242とを備える、pnダイオードである。なお、図11中、符号212はn+型半導体基板を示し、符号210は半導体基体を示し、符号216,符号222及び符号234は溝を示し、符号220はp型高濃度オーミック拡散領域を示し、符号226はアノード電極電界緩和領域を示し、符号228は中継拡散領域を示す。

【0078】

このように、実施形態7に係るスーパージャンクション構造を有する半導体装置200は、pnダイオードである点で実施形態1に係るスーパージャンクション構造を有する半導体装置100の場合とは異なるが、第2環状柱状埋込層236と、当該第2環状柱状埋込層236の上方に形成された環状導電層242とを備えることから、実施形態1に係るスーパージャンクション構造を有する半導体装置100の場合と同様に、高温環境下で半導体装置に長時間逆バイアスを与えた場合であってもリーク電流が増加したり耐圧が低下したりすることがなくなる。

【0079】

なお、実施形態7に係るスーパージャンクション構造を有する半導体装置200は、pnダイオードである点以外の点においては実施形態1に係るスーパージャンクション構造を有する半導体装置100と同様の構成を有するため、実施形態1に係るスーパージャンクション構造を有する半導体装置100が有する効果のうち該当する効果を有する。

【0080】

[実施形態8]

図12は、実施形態8に係るスーパージャンクション構造を有する半導体装置300の断面図である。実施形態8に係るスーパージャンクション構造を有する半導体装置300は、図12に示すように、n−型半導体層(第1導電型の半導体層)314と、活性領域R1におけるn−型半導体層314の表面に形成され、p型半導体材料(第2導電型の半導体材料)からなる複数の柱状埋込層318と、活性領域R1におけるn−型半導体層314の表面に形成されたp型ボディ領域360、p型ボディ領域360の表面に形成されたn+型ソース領域362及びp+型コンタクト領域364と、活性領域R1におけるn−型半導体層314の表面上に形成されたゲート絶縁層372、ゲート電極層370及び層間絶縁層374並びにソース電極層(第1電極層)332と、活性領域R1を囲む耐圧領域R2におけるn−型半導体層314の表面に形成され、p型半導体材料からなる複数のガードリング(環状柱状埋込層)324と、耐圧領域R2及び当該耐圧領域R2を囲む周辺領域R3におけるn−型半導体層314の表面上に形成された絶縁層330と、ドレイン電極層350と、周辺領域R3におけるn−型半導体層314の表面に形成され、第2導電型の半導体材料からなる第2環状柱状埋込層336と、周辺領域R3における絶縁層330上に形成された環状導電層342とを備える、パワーMOSFETである。なお、図12中、符号312はn+型半導体基板を示し、符号310は半導体基体を示し、符号316,符号322及び符号334は溝を示し、符号326はソース電極電界緩和領域を示し、符号328は中継拡散領域を示す。

【0081】

このように、実施形態8に係るスーパージャンクション構造を有する半導体装置300は、パワーMOSFETである点で、実施形態1に係るスーパージャンクション構造を有する半導体装置100の場合とは異なるが、第2環状柱状埋込層336と、当該第2環状柱状埋込層336の上方に形成された環状導電層342とを備えることから、実施形態1に係るスーパージャンクション構造を有する半導体装置100の場合と同様に、高温環境下で半導体装置に長時間逆バイアスを与えた場合であってもリーク電流が増加したり耐圧が低下したりすることがなくなる。

【0082】

なお、実施形態8に係るスーパージャンクション構造を有する半導体装置300は、パワーMOSFETである点以外の点においては実施形態1に係るスーパージャンクション構造を有する半導体装置100と同様の構成を有するため、実施形態1に係るスーパージャンクション構造を有する半導体装置100が有する効果のうち該当する効果を有する。

【0083】

[実施例1]

実施例1は、本発明のスーパージャンクション構造を有する半導体装置によれば、高温環境下で半導体装置に長時間逆バイアスを与えた場合であってもリーク電流が増加しないことを説明するための実施例である。

【0084】

1.試料

実施形態1に係るスーパージャンクション構造を有する半導体装置100を実施例1とした。一方、実施形態1に係るスーパージャンクション構造を有する半導体装置100から第2環状柱状埋込層136及び環状導電層142を除去した構造の、スーパージャンクション構造を有する半導体装置(すなわち従来のスーパージャンクション構造を有する半導体装置900)を比較例1とした。

【0085】

2.評価方法

実施例1に係るスーパージャンクション構造を有する半導体装置100及び比較例1に係るスーパージャンクション構造を有する半導体装置900の評価は、実施例1に係るスーパージャンクション構造を有する半導体装置100及び比較例1に係るスーパージャンクション構造を有する半導体装置900をそれぞれ10個準備し、これらをBT試験機にセットした後、高温環境下(150℃)で逆バイアス(250V)を印加した状態で300時間、リーク電流を測定することにより行った。

【0086】

3.評価結果

図13は、実施例1の評価結果を示す図である。

図13からも明らかなように、比較例1に係るスーパージャンクション構造を有する半導体装置900においては、上記の条件でリーク電流が100倍から1000倍増加したのに対して、実施例1に係るスーパージャンクション構造を有する半導体装置100においては、上記した条件であっても全くリーク電流が増加しなかった。

【0087】

[実施例2]

実施例2は、本発明のスーパージャンクション構造を有する半導体装置によれば、高温環境下で半導体装置に長時間逆バイアスを与えた場合であっても耐圧が低下しないことを示す実施例である。

【0088】

1.試料

実施形態1に係るスーパージャンクション構造を有する半導体装置100を実施例2とした。一方、実施形態1に係るスーパージャンクション構造を有する半導体100から第2環状柱状埋込層136及び環状導電層142を除去した構造の、スーパージャンクション構造を有する半導体装置(すなわち従来のスーパージャンクション構造を有する半導体装置900)を比較例2とした。

【0089】

2.評価方法

実施例2に係るスーパージャンクション構造を有する半導体装置100及び比較例2に係るスーパージャンクション構造を有する半導体装置900の評価は、実施例2に係るスーパージャンクション構造を有する半導体装置100及び比較例2に係るスーパージャンクション構造を有する半導体装置900をそれぞれ1個準備し、これらを高温環境下(150℃)で逆バイアス(250V)を印加した状態で長時間(63時間又は2042時間)保持する前と後で耐圧波形を測定することによりBT試験評価を行った。

【0090】

3.評価結果

図14は、実施例2の評価結果を示す図である。

図14からも明らかなように、比較例2に係るスーパージャンクション構造を有する半導体装置900においては、高温逆バイアス下で63時間保持したことにより、耐圧が360Vから250Vに低下したのに対して、実施例2に係るスーパージャンクション構造を有する半導体装置100においては、高温逆バイアス下で63時間又は2042時間保持した場合であっても耐圧が360Vのまま全く低下しなかった。

【0091】

以上、本発明を上記の実施形態に基づいて説明したが、本発明は上記の実施形態に限定されるものではない。その趣旨を逸脱しない範囲において種々の態様において実施することが可能であり、例えば、次のような変形も可能である。

【0092】

(1)上記実施形態1においては、環状導電層142として、アノード電極層133と同一工程で形成されるアルミニウム層を用いたが、本発明はこれに限定されるものではない。例えば、ショットキーバリアメタル層132及びアノード電極層133とそれぞれ同一工程で形成される白金層及びアルミニウム層を用いることもできる。また、アルミニウム以外の金属層、金属層以外の導電層(例えばポリシリコン層又はドープトポリシリコン層)などを用いることもできる。

【0093】

(2)上記各実施形態においては、第1導電型をn型とし、第2導電型をp型とした場合を例にとって本発明を説明したが、本発明はこれに限定されるものではない。例えば、第1導電型をp型とし、第2導電型をn型とした場合にも本発明を適用可能である。

【0094】

(3)上記各実施形態1〜6においては、スーパージャンクション構造を有する半導体装置として、ショットキーバリアダイオードを用い、実施形態7においてはpnダイオードを用い、実施形態8においてはパワーMOSFETを用いたが、本発明はこれに限定されるものではない。これら以外のスーパージャンクション構造を有する半導体装置(ショットキーバリアダイオード、pnダイオード及びパワーMOSFET以外の半導体装置(例えばサイリスター、IGBTなど。)や、これらの半導体装置を含む各種複合半導体装置など。)を用いることもできる。

【符号の説明】

【0095】

100,100a,100b,100c,100d,100e,200,300…スーパージャンクション構造を有する半導体装置、110,210,310,910…半導体基体、112,212,312,912…n+型半導体基板、114,214,314,914…n−型半導体層、116,216,316,916…第1トレンチ、118,218,318,918…柱状埋込層、120,920…p型高濃度オーミック拡散領域、122,222,322,922…第2トレンチ、124,224,324,924…環状柱状埋込層、126,926…ショットキーバリアメタル電界緩和領域、128,228,328,928…中継拡散領域、130,130a,230,330,930…絶縁層、132,932…ショットキーバリアメタル層(第1電極層)、133,933…アノード電極層、134,234,334…第3トレンチ、136,236,336…第2環状柱状埋込層、138,238,338…p型高濃度拡散領域、140,140a,240,340…開口部、142,242,342…環状導電層、144,944…空乏層の終端部、150,250,950…カソード電極層、220…p+型拡散領域、226…アノード電極層電界緩和領域、232…アノード電極層(第1電極層)、326…ソース電極層電界緩和領域、332…ソース電極層(第1電極層)、350…ドレイン電極層、360…p型ボディ領域、362…n+型ソース領域、364…p+型コンタクト領域、370…ゲート電極、372…ゲート絶縁層、374…層間絶縁層、R1…活性領域、R2…耐圧領域、R3…周辺領域

【技術分野】

【0001】

本発明は、スーパージャンクション構造を有する半導体装置に関する。

【背景技術】

【0002】

スーパージャンクション構造を有する半導体装置が知られている(例えば、特許文献1参照。)。図15は、従来のスーパージャンクション構造を有する半導体装置900を説明するために示す図である。図15(a)は従来のスーパージャンクション構造を有する半導体装置900の平面図であり、図15(b)は従来のスーパージャンクション構造を有する半導体装置900の断面図である。図15(b)は図15(a)のA−A断面図である。なお、図15(a)においては、理解を容易にするために、柱状埋込層918、環状柱状埋込層924及びショットキーバリアメタル層932のみを示している。

【0003】

従来のスーパージャンクション構造を有する半導体装置900は、図15に示すように、n−型半導体層(第1導電型の半導体層)914と、活性領域R1における半導体層914の表面に形成され、p型シリコン(第2導電型の半導体材料)からなる複数の柱状埋込層918と、活性領域R1におけるn−型半導体層914の表面上に形成されたアノード電極層としてのショットキーバリアメタル層(第1電極層)932と、活性領域R1を囲む耐圧領域R2におけるn−型半導体層914の表面に形成され、p型シリコンからなる複数のガードリング(環状柱状埋込層)924と、耐圧領域R2及び耐圧領域R2を囲む周辺領域R3におけるn−型半導体層914の表面上に形成された絶縁層930と、カソード電極層950とを備える、ショットキーバリアダイオードである。なお、図15(b)中、符号912はn+型半導体基板を示し、符号910は半導体基体を示し、符号920はp型高濃度オーミック拡散領域を示し、符号926はショットキーバリアメタル電界緩和領域を示し、符号928は中継拡散領域を示し、符号933はアノード電極層を示す。

【0004】

従来のスーパージャンクション構造を有する半導体装置900によれば、活性領域を囲む耐圧領域R2におけるn−型シリコン層914の表面には複数(例えば数十本)のガードリング924が設けられているため、逆バイアス時には空乏層が活性領域R1から耐圧領域R2の最外周部まで伸長するため、スーパージャンクション構造を有する半導体装置の耐圧を高くすることができる。

【先行技術文献】

【特許文献】

【0005】

【特許文献1】特開2004−6595号公報

【発明の概要】

【発明が解決しようとする課題】

【0006】

しかしながら、本発明の発明者の研究によれば、従来のスーパージャンクション構造を有する半導体装置900には以下のような問題があることがわかった。すなわち、従来のスーパージャンクション構造を有する半導体装置900においては、高温環境下で半導体装置に長時間逆バイアスを与えた場合には、リーク電流が増加したり耐圧が低下したりするという問題があることがわかった。

【0007】

そこで、本発明はこのような問題を解決するためになされたものであり、高温環境下で半導体装置に長時間逆バイアスを与えた場合であってもリーク電流が増加したり耐圧が低下したりすることのない、スーパージャンクション構造を有する半導体装置を提供することを目的とする。

【課題を解決するための手段】

【0008】

[1]本発明のスーパージャンクション構造を有する半導体装置は、第1導電型の半導体層と、活性領域における前記半導体層の表面に形成され、第2導電型の半導体材料からなる複数の柱状埋込層と、前記活性領域における前記半導体層の表面上に形成された第1電極層と、活性領域を囲む耐圧領域における前記半導体層の表面に形成され、第2導電型の半導体材料からなる複数の環状柱状埋込層と、前記耐圧領域及び当該耐圧領域を囲む周辺領域における前記半導体層の表面上に形成された絶縁層とを備える、スーパージャンクション構造を有する半導体装置であって、前記周辺領域における前記半導体層の表面に形成され、第2導電型の半導体材料からなる第2環状柱状埋込層と、前記周辺領域における前記絶縁層上に形成された環状導電層とをさらに備えることを特徴とする。

【0009】

[2]本発明のスーパージャンクション構造を有する半導体装置においては、前記絶縁層は、前記周辺領域における前記第2環状柱状埋込層が形成されている領域において開口部を有し、前記環状導電層は、前記開口部を介して、前記第2環状柱状埋込層に接続されていることが好ましい。

【0010】

[3]本発明のスーパージャンクション構造を有する半導体装置においては、前記環状導電層に接続されている第2環状柱状埋込層の表面近傍には、第2導電型の高濃度拡散領域が形成されていることが好ましい。

【0011】

[4]本発明のスーパージャンクション構造を有する半導体装置においては、前記絶縁層は、前記周辺領域における前記第2環状柱状埋込層が形成されていない領域において開口部を有し、前記環状導電層は、前記開口部を介して、前記半導体層に接続されていることも好ましい。

【0012】

[5]本発明のスーパージャンクション構造を有する半導体装置においては、前記環状導電層に接続されている領域における前記半導体層の表面には、第1導電型の高濃度拡散領域が形成されていることが好ましい。

【0013】

[6]本発明のスーパージャンクション構造を有する半導体装置においては、最外周の第2環状柱状埋込層よりも外周側に伸びる前記第2環状導電層の幅寸法は、第2環状柱状埋込層の深さ寸法よりも大きいことが好ましい。

【0014】

[7]本発明のスーパージャンクション構造を有する半導体装置においては、前記環状導電層として、複数の環状導電層を備えることが好ましい。

【0015】

[8]本発明のスーパージャンクション構造を有する半導体装置においては、前記第2環状柱状埋込層として、複数の第2環状柱状埋込層を備えることが好ましい。

【0016】

[9]本発明のスーパージャンクション構造を有する半導体装置においては、前記環状導電層は、最内周の第2環状柱状埋込層に接続されていることが好ましい。

【発明の効果】

【0017】

本発明のスーパージャンクション構造を有する半導体装置によれば、後述する実施例1及び2からも明らかなように、高温環境下で半導体装置に長時間逆バイアスを与えた場合であってもリーク電流が増加したり耐圧が低下したりすることがなくなる。

【0018】

なお、現段階ではそのメカニズムの詳細は明らかでないが、後述する図5に示すように、本発明のスーパージャンクション構造を有する半導体装置の場合には、第2環状柱状埋込層と、当該第2環状柱状埋込層の上方に形成された環状導電層とをさらに備えることから、逆バイアス時には第1電極層と環状導電層とがそれぞれキャパシターの2つの電極として機能するようになるため、高温環境下で半導体装置に長時間逆バイアスを与えた場合などに絶縁層の表面において生成することがある可動イオンが、第1電極層と環状導電層との間の電位差によりどちらかの電極に捕獲され、その結果、可動イオンの存在に起因してリーク電流が増加したり耐圧が低下したりすることがなくなるためであると本発明の発明者らは推測している。

【図面の簡単な説明】

【0019】

【図1】実施形態1に係るスーパージャンクション構造を有する半導体装置100を説明するために示す図である。

【図2】実施形態1に係るスーパージャンクション構造を有する半導体装置100を製造する方法を説明するために示す図である。

【図3】実施形態1に係るスーパージャンクション構造を有する半導体装置100を製造する方法を説明するために示す図である。

【図4】実施形態1に係るスーパージャンクション構造を有する半導体装置100を製造する方法を説明するために示す図である。

【図5】実施形態1に係るスーパージャンクション構造を有する半導体装置100の作用・効果を説明するために示す図である。

【図6】実施形態2に係るスーパージャンクション構造を有する半導体装置100aの断面図である。

【図7】実施形態3に係るスーパージャンクション構造を有する半導体装置100bの断面図である。

【図8】実施形態4に係るスーパージャンクション構造を有する半導体装置100cの断面図である。

【図9】実施形態5に係るスーパージャンクション構造を有する半導体装置100dの断面図である。

【図10】実施形態6に係るスーパージャンクション構造を有する半導体装置100eの断面図である。

【図11】実施形態7に係るスーパージャンクション構造を有する半導体装置200の断面図である。

【図12】実施形態8に係るスーパージャンクション構造を有する半導体装置300の断面図である。

【図13】実施例1の評価結果を示す図である。

【図14】実施例2の評価結果を示す図である。

【図15】従来のスーパージャンクション構造を有する半導体装置900を説明するために示す図である。

【発明を実施するための形態】

【0020】

以下、本発明のスーパージャンクション構造を有する半導体装置について、図に示す実施の形態に基づいて説明する。

【0021】

[実施形態1]

1.実施形態1に係るスーパージャンクション構造を有する半導体装置100の構成

まず、実施形態1に係るスーパージャンクション構造を有する半導体装置100の構成を説明する。

図1は、実施形態1に係るスーパージャンクション構造を有する半導体装置100を説明するために示す図である。図1(a)は実施形態1に係るスーパージャンクション構造を有する半導体装置100の平面図であり、図1(b)は実施形態1に係るスーパージャンクション構造を有する半導体装置100の断面図である。図1(b)は図1(a)のA−A断面図である。なお、図1(a)においては、理解を容易にするために、柱状埋込層118、環状柱状埋込層124、第2環状柱状埋込層136、ショットキーバリアメタル層132及び環状導電層142のみを示している。

【0022】

実施形態1に係るスーパージャンクション構造を有する半導体装置100は、スーパージャンクション構造を有するショットキーバリアダイオードであり、図1(a)に示すように、活性領域R1と、活性領域R1を囲む耐圧領域R2と、耐圧領域R2を囲む周辺領域R3とに分画されている。

【0023】

そして、実施形態1に係るスーパージャンクション構造を有する半導体装置100は、図1(b)に示すように、n−型半導体層(第1導電型の半導体層)114と、活性領域R1におけるn−型半導体層114の表面に形成され、p型シリコン(第2導電型の半導体材料)からなる複数の柱状埋込層118と、活性領域R1におけるn−型半導体層114の表面上に形成されたアノード電極層としてのショットキーバリアメタル層(第1電極層)132と、活性領域R1を囲む耐圧領域R2におけるn−型半導体層114の表面に形成され、p型シリコンからなる複数のガードリング(環状柱状埋込層)124と、耐圧領域R2及び当該耐圧領域R2を囲む周辺領域R3におけるn−型半導体層114の表面上に形成された絶縁層130と、カソード電極層150とを備える、ショットキーバリアダイオードである。なお、図1(b)中、符号112はn+型半導体基板を示し、符号110は半導体基体を示し、符号120はp型高濃度オーミック拡散領域を示し、符号126はショットキーバリアメタル電界緩和領域を示し、符号128は中継拡散領域を示し、符号133はアノード電極層を示す。

【0024】

そして、実施形態1に係るスーパージャンクション構造を有する半導体装置100は、周辺領域R3におけるn−型半導体層114の表面に形成され、p型半導体材料からなる第2環状柱状埋込層136と、周辺領域R3における絶縁層130上に形成された環状導電層142とをさらに備える。

【0025】

実施形態1に係るスーパージャンクション構造を有する半導体装置100においては、絶縁層130は、周辺領域R3における第2環状柱状埋込層136が形成されている領域において開口部140を有し、環状導電層142は、開口部140を介して、第2環状柱状埋込層136に接続されている。

【0026】

実施形態1に係るスーパージャンクション構造を有する半導体装置100においては、環状導電層142に接続されている第2環状柱状埋込層136の表面近傍には、p型高濃度拡散領域(第2導電型の高濃度拡散領域)138が形成されている。

【0027】

実施形態1に係るスーパージャンクション構造を有する半導体装置100においては、最外周の第2環状柱状埋込層136よりも外周側に伸びる環状導電層142の幅寸法Lは、第2環状柱状埋込層136の深さ寸法Dよりも大きい(図1(b)参照。)。

【0028】

n−型半導体層114は、n+型半導体基板112の上部にエピタキシャル成長させることにより形成されたものであって、n+型半導体基板112とn−型半導体層114とで半導体基体110を構成する。n−型半導体層114の厚さは、例えば6μm〜70μmであり、n−型半導体層の不純物濃度は、例えば2×1014cm−3〜5×1016cm−3である。

【0029】

柱状埋込層118は、n−型半導体層114における活性領域R1に形成した第1トレンチ116の内部にエピタキシャル成長させて形成したp型半導体材料(第2導電型半導体材料)からなる。柱状埋込層118の本数は使用目的や構造に合わせて適宜設定することができる。p型半導体材料の不純物濃度は、例えば2×1014cm−3〜5×1016cm−3である。

【0030】

柱状埋込層118の深さは、例えば5μm〜50μmであり、幅は、例えば0.5μm〜5μmである。柱状埋込層118は、それぞれ第1間隔d1で平行に形成されている。第1間隔d1は、例えば1μm〜15μmである。

【0031】

環状柱状埋込層124は、n−型半導体層114における耐圧領域R2に形成した第2トレンチ122の内部にエピタキシャル成長させて形成したp型半導体材料(第2導電型半導体材料)からなる。環状柱状埋込層124の本数は例えば5本〜50本であるが、使用目的や構造に合わせて適宜設定することができる。p型半導体材料の不純物濃度は、例えば2×1014cm−3〜5×1016cm−3である。

【0032】

環状柱状埋込層124の深さは、例えば5μm〜50μmであり、幅は、例えば0.5μm〜5μmである。環状柱状埋込層124は、それぞれ第1間隔d1で平行に形成されている。第1間隔d1は、例えば1μm〜15μmである。

【0033】

第2環状柱状埋込層136は、n−型半導体層114における周辺領域R3に形成した第3トレンチ134の内部にエピタキシャル成長させて形成したp型半導体材料(第2導電型半導体材料)からなる。第2環状柱状埋込層136の本数は例えば1本〜10本であるが、使用目的や構造に合わせて適宜設定することができる。p型半導体材料の不純物濃度は、例えば2×1014cm−3〜5×1016cm−3である。

【0034】

第2環状柱状埋込層136の深さは、例えば5μm〜50μmであり、幅は、例えば0.5μm〜5μmである。環状柱状埋込層124は、それぞれ第1間隔d1で平行に形成されている。第1間隔d1は、例えば1μm〜15μmである。

【0035】

絶縁層130は、シリコン酸化膜からなる。ショットキーバリアメタル層132は、n−型半導体層114とはショットキー接合を形成し、柱状埋込層118とはオーミック接合を形成する。ショットキーバリアメタル層132の材料は例えば白金であり、ショットキーバリアメタル層132の厚さは例えば10nmである。ショットキーバリアメタル層132の上方にはアノード電極層133が形成されている。アノード電極層133の材料は、金属(例えばアルミニウム)であり、アノード電極層133の厚さは例えば3000nmである。環状導電層142の材料は、金属(例えばアルミニウム)であり、環状導電層142の厚さは例えば3000nmである。カソード電極層150は、電極材料である金属(例えばニッケル)を半導体基体110の裏面に蒸着して形成する。カソード電極層150の厚さは、例えば2000nmである。

【0036】

2.実施形態1に係るスーパージャンクション構造を有する半導体装置100を製造する方法

次に、実施形態1に係るスーパージャンクション構造を有する半導体装置100を製造する方法を以下に示す各工程に沿って説明する。

図2〜図4は、実施形態1に係るスーパージャンクション構造を有する半導体装置を製造する方法を説明するために示す図である。図2(a)〜図2(d)、図3(a)〜図3(d)及び図4(a)〜図4(d)は各工程図である。

【0037】

1.半導体基体準備工程

まず、n+型半導体基板112と、n+型半導体基板112の表面側にエピタキシャル成長法により形成したn−型半導体層114とを有する半導体基体110を準備する(図2(a)参照。)。n+型半導体基板112としては、例えばシリコン基板を用いることができるが、炭化珪素SiCや窒化ガリウムGaNからなる基板を用いてもよい。

【0038】

2.各柱状埋込層形成工程

次に、活性領域R1に柱状埋込層118を形成し、耐圧領域R2に環状柱状埋込層124を形成するとともに、周辺領域R3に第2環状柱状埋込層136を形成する。各柱状埋込層形成工程は、トレンチ形成工程と、各柱状埋込層形成工程と、p型高濃度拡散領域形成工程とからなる(図2(b)〜図3(d)参照。)。

【0039】

2−1.トレンチ形成工程

トレンチ形成工程においては、まず、n−型半導体層114を熱酸化することによりn−型半導体層114の上部にトレンチマスクとなる酸化膜M1を形成する(図2(b)参照。)。続いて、図示しないレジスト膜(厚さ:例えば0.8μm。)を形成し、写真工程を実施することにより、柱状埋込層118、環状柱状埋込層124及び第2環状柱状埋込層136の形成位置に開口部を設け、当該開口部における絶縁膜Mをドライエッチングにより除去する(図2(c)参照。)。次に、レジスト膜を取り除き、その後、絶縁膜Mをマスクとしてn−型半導体層114をドライエッチングすることにより、n−型半導体層114の表面に第1トレンチ116、第2トレンチ122及び第3トレンチ134を形成する(図2(d)参照。)。

【0040】

2−2.各柱状埋込層形成工程

各柱状埋込層形成工程においては、第1トレンチ116、第2トレンチ122及び第3トレンチ134の内面について、ケミカルドライエッチングや犠牲酸化、水素アニール等により、トレンチ形成工程のドライエッチングによるダメージ層除去を行った後、p型不純物を含むドーパントガスを導入しながら絶縁膜M表面の高さ位置を超える高さ位置までp型の単結晶半導体材料をエピタキシャル成長させる(図3(a)参照。)。その後、CMP法によって、形成されたキャップ部を絶縁膜Mの表面まで研磨し、その後、絶縁膜Mの開口部内に埋め込まれているp型の単結晶半導体材料を絶縁膜Mの底面まで絶縁膜Mをマスクとしてドライエッチングする。その後、絶縁膜Mをウェットエッチングにより除去する(図3(b)参照。)。

【0041】

2−3.p型高濃度拡散領域形成工程

次に、p型高濃度オーミック拡散領域120,ショットキーバリアメタル電界緩和領域126、中継拡散領域128及びp型高濃度拡散領域138に対応する領域に開口部を有するマスクM2を形成し、このマスクM2を介して、イオン注入法によりp型不純物(例えばボロンイオン)を半導体基体110の表面に導入する(図3(c)参照。)。

その後、半導体基体110に熱処理を施すことにより、p型高濃度オーミック拡散領域120,ショットキーバリアメタル電界緩和領域126、中継拡散領域128及びp型高濃度拡散領域138を形成する(図3(d)参照。)。

【0042】

3.絶縁層形成工程

次に、CVD法により厚さ500nmのシリコン酸化膜を形成した後、活性領域R1及び開口部140に対応する開口を有するマスクM3を用いてシリコン酸化膜のエッチングを行うことによりシリコン酸化膜を除去して、絶縁層130を形成する(図4(a)参照。)。

【0043】

4.ショットキーバリアメタル層形成工程

次に、半導体基体110の表面側から、スパッタ法により、例えば厚さ10nmの白金膜を形成し、所定形状にパターニングした後、半導体基体110を熱処理することにより、ショットキーバリアメタル層132を形成する(図4(b)参照。)。

【0044】

5.環状導電層形成工程

次に、半導体基体110の表面側から、スパッタ法により、例えば厚さ3000nmのアルミニウム膜を形成し、所定形状にパターニングすることによって、アノード電極層133及び環状導電層142を形成する(図4(c)参照。)。

【0045】

6.カソード電極層形成工程

次に、半導体基体110の裏面側に位置するn+型半導体基板112の裏面側に、スパッタ法により、例えば厚さ500nmのニッケル膜を形成することにより、カソード電極層150を形成する(図4(d)参照。)。

【0046】

上記の工程を順次実施することにより、実施形態1に係るスーパージャンクション構造を有する半導体装置100を製造することができる。

【0047】

3.実施形態1に係るスーパージャンクション構造を有する半導体装置100の効果

実施形態1に係るスーパージャンクション構造を有する半導体装置100によれば、後述する実施例1及び2からも明らかなように、高温環境下で半導体装置に長時間逆バイアスを与えた場合であってもリーク電流が増加したり耐圧が低下したりすることがなくなる。

【0048】

図5は、実施形態1に係るスーパージャンクション構造を有する半導体装置100の作用・効果を説明するために示す図である。図5(a)は実施形態1に係るスーパージャンクション構造を有する半導体装置100における逆バイアス時の可動イオンの動きを示す図であり、図5(b)は従来のスーパージャンクション構造を有する半導体装置900における逆バイアス時の可動イオンの動きを示す図である。

【0049】

現段階ではそのメカニズムの詳細は明らかでないが、実施形態1に係るスーパージャンクション構造を有する半導体装置100の場合には、第2環状柱状埋込層136と、当該第2環状柱状埋込層136の上方に形成された環状導電層142とをさらに備えることから、逆バイアス時にはショットキーバリアメタル層132と環状導電層142とがそれぞれキャパシターの2つの電極として機能するようになる。このため、高温環境下で半導体装置に長時間逆バイアスを与えた場合などに絶縁層130の表面において生成することがある可動イオンが、図5に示すように、ショットキーバリアメタル層132と環状導電層142との間の電位差によりどちらかの電極に捕獲され(負の可動イオンは環状導電層142に捕獲され、正の可動イオンはショットキーバリアメタル層132に捕獲される。)、その結果、可動イオンの存在に起因してリーク電流が増加したり耐圧が低下したりすることがなくなるためであると本発明の発明者らは推測している。

【0050】

また、実施形態1に係るスーパージャンクション構造を有する半導体装置100によれば、逆バイアス時には、環状導電層142がカソード電極層150の電位に近い電位を有する第2環状柱状埋込層136に接続されることになるため、ショットキーバリアメタル層132と環状導電層142との間に大きな電位差が発生する。その結果、可動イオンは、ショットキーバリアメタル層132と環状導電層142との間に発生する大きな電位差によりどちらかの電極に確実に捕獲されるようになる。

【0051】

また、実施形態1に係るスーパージャンクション構造を有する半導体装置100によれば、環状導電層142に接続されている第2環状柱状埋込層136の表面近傍には、p型高濃度拡散領域(第2導電型の高濃度拡散領域)138が形成されているため、環状導電層142と第2環状柱状埋込層136との間の抵抗を極めて小さいものにすることが可能となり、ショットキーバリアメタル層132と環状導電層142との間に発生する電位差を毀損することがない。

【0052】

さらにまた、実施形態1に係るスーパージャンクション構造を有する半導体装置100によれば、最外周の第2柱状埋込層136よりも外周側に伸びる環状導電層142の幅寸法が第2環状柱状埋込層136の深さ寸法よりも大きいため、最外の第2環状柱状埋込層136から外周側に伸びる空乏層の上方には環状導電層142が配置されることになり、最外の第2環状柱状埋込層136から外周側に伸びる空乏層の上部の電位が、カソード電極層150の電位に近い電位に固定されるため、可動イオンの影響を受けない安定した電位となる。

【0053】

[実施形態2]

図6は、実施形態2に係るスーパージャンクション構造を有する半導体装置100aの断面図である。

【0054】

実施形態2に係るスーパージャンクション構造を有する半導体装置100aは、基本的には実施形態1に係るスーパージャンクション構造を有する半導体装置100と同様の構成を有するが、図6に示すように、2本の環状導電層142,142aを備える点で、実施形態1に係るスーパージャンクション構造を有する半導体装置100の場合とは異なる。

【0055】

このように、実施形態2に係るスーパージャンクション構造を有する半導体装置100aは、複数の環状導電層142,142aを備える点で、実施形態1に係るスーパージャンクション構造を有する半導体装置100の場合とは異なるが、第2環状柱状埋込層136と、当該第2環状柱状埋込層136の上方に形成された環状導電層142及び環状導電層142aとを備えることから、実施形態1に係るスーパージャンクション構造を有する半導体装置100の場合と同様に、高温環境下で半導体装置に長時間逆バイアスを与えた場合であってもリーク電流が増加したり耐圧が低下したりすることがなくなる。

【0056】

また、実施形態2に係るスーパージャンクション構造を有する半導体装置100aによれば、2本の環状導電層142,142aを備えるため、可動イオンを効率良く捕獲することが可能となる。

【0057】

なお、実施形態2に係るスーパージャンクション構造を有する半導体装置100aにおいては、環状導電型層として2本の環状導電層を備えるものであるが、本発明はこれに限定されるものではない。例えば、環状導電型層として3本以上の環状導電層を備えるものであってもよい。

【0058】

なお、実施形態2に係るスーパージャンクション構造を有する半導体装置100aは、2本の環状導電層142,142aを備える点以外の点においては実施形態1に係るスーパージャンクション構造を有する半導体装置100と同様の構成を有するため、実施形態1に係るスーパージャンクション構造を有する半導体装置100が有する効果のうち該当する効果を有する。

【0059】

[実施形態3]

図7は、実施形態3に係るスーパージャンクション構造を有する半導体装置100bの断面図である。

【0060】

実施形態3に係るスーパージャンクション構造を有する半導体装置100bは、基本的には実施形態1に係るスーパージャンクション構造を有する半導体装置100と同様の構成を有するが、図7に示すように、絶縁層に開口部が形成されていない点で、実施形態1に係るスーパージャンクション構造を有する半導体装置100の場合とは異なる。

【0061】

このように、実施形態3に係るスーパージャンクション構造を有する半導体装置100bは、絶縁層に開口部が形成されていない点で、実施形態1に係るスーパージャンクション構造を有する半導体装置100の場合とは異なるが、実施形態1に係るスーパージャンクション構造を有する半導体装置100の場合と同様に、第2環状柱状埋込層136と、当該第2環状柱状埋込層136の上方に形成された環状導電層142bとをさらに備えることから、高温環境下で半導体装置に長時間逆バイアスを与えた場合であってもリーク電流が増加したり耐圧が低下したりすることがなくなる。

【0062】

なお、実施形態3に係るスーパージャンクション構造を有する半導体装置100bにおいては、絶縁層に開口部が形成されていないため、環状導電層142bが第2環状柱状埋込層136と同電位にはならないが、環状導電層142bは、絶縁層130aを介して第2環状柱状埋込層136に容量結合されることとなるため、実施形態1に係るスーパージャンクション構造を有する半導体装置100の場合と同様に、ショットキーバリアメタル層132と環状導電層142との間には大きな電位差が発生し、これによって、高温環境下で半導体装置に長時間逆バイアスを与えた場合などに絶縁層の表面において生成することがある可動イオンが、ショットキーバリアメタル層132と環状導電層142との間の電位差によりどちらかの電極に捕獲され、その結果、可動イオンの存在に起因してリーク電流が増加したり耐圧が低下したりすることがなくなる。

【0063】

なお、実施形態3に係るスーパージャンクション構造を有する半導体装置100bは、絶縁層に開口部が形成されていない点以外の点においては実施形態1に係るスーパージャンクション構造を有する半導体装置100と同様の構成を有するため、実施形態1に係るスーパージャンクション構造を有する半導体装置100が有する効果のうち該当する効果を有する。

【0064】

[実施形態4]

図8は、実施形態4に係るスーパージャンクション構造を有する半導体装置100cの断面図である。

【0065】

実施形態4に係るスーパージャンクション構造を有する半導体装置100cは、基本的には実施形態1に係るスーパージャンクション構造を有する半導体装置100と同様の構成を有するが、環状導電層142cが開口部140aを介してn−型半導体層114に接続されている点で、実施形態1に係るスーパージャンクション構造を有する半導体装置100の場合とは異なる。すなわち、実施形態4に係るスーパージャンクション構造を有する半導体装置100cにおいては、図8に示すように、環状導電層142cが、第2環状柱状埋込層136が形成されていない領域に形成された開口部140aを介して、n−型半導体層114に接続されている。また、環状導電層142cに接続されている領域におけるn−型半導体層114の表面には、n+型高濃度拡散領域146が形成されている。

【0066】

このように、実施形態4に係るスーパージャンクション構造を有する半導体装置100cは、環状導電層142cが開口部140aを介してn−型半導体層114に接続されている点で、実施形態1に係るスーパージャンクション構造を有する半導体装置100の場合とは異なるが、実施形態1に係るスーパージャンクション構造を有する半導体装置100の場合と同様に、第2環状柱状埋込層136と、当該第2環状柱状埋込層136の上方に形成された環状導電層142cとをさらに備えることから、環状導電層142cがカソード電極150に近い電位に固定され、ショットキーバリアメタル層132と環状導電層142cとの間に発生した電位差により可動イオンが捕獲されるようになるため、高温環境下で半導体装置に長時間逆バイアスを与えた場合であってもリーク電流が増加したり耐圧が低下したりすることがなくなる。

【0067】

なお、実施形態4に係るスーパージャンクション構造を有する半導体装置100cは、環状導電層142cが開口部140aを介してn−型半導体層114に接続されている点以外の点においては実施形態1に係るスーパージャンクション構造を有する半導体装置100と同様の構成を有するため、実施形態1に係るスーパージャンクション構造を有する半導体装置100が有する効果のうち該当する効果を有する。

【0068】

[実施形態5]

図9は、実施形態5に係るスーパージャンクション構造を有する半導体装置100dの断面図である。

【0069】

実施形態5に係るスーパージャンクション構造を有する半導体装置100dは、基本的には実施形態1に係るスーパージャンクション構造を有する半導体装置100と同様の構成を有するが、形成されている第2環状柱状埋込層136の数が実施形態1に係るスーパージャンクション構造を有する半導体装置100の場合とは異なる。すなわち、実施形態5に係るスーパージャンクション構造を有する半導体装置100dにおいては、図9に示すように、1本の第2環状柱状埋込層136が形成されている。

【0070】

このように、実施形態5に係るスーパージャンクション構造を有する半導体装置100dは、形成されている第2環状柱状埋込層136の数が実施形態1に係るスーパージャンクション構造を有する半導体装置100の場合とは異なるが、実施形態1に係るスーパージャンクション構造を有する半導体装置100の場合と同様に、第2環状柱状埋込層136と、当該第2環状柱状埋込層136の上方に形成された環状導電層142dとをさらに備えることから、高温環境下で半導体装置に長時間逆バイアスを与えた場合であってもリーク電流が増加したり耐圧が低下したりすることがなくなる。

【0071】

なお、実施形態5に係るスーパージャンクション構造を有する半導体装置100dは、形成されている第2環状柱状埋込層136の数以外の点においては実施形態1に係るスーパージャンクション構造を有する半導体装置100と同様の構成を有するため、実施形態1に係るスーパージャンクション構造を有する半導体装置100が有する効果のうち該当する効果を有する。

【0072】

[実施形態6]

図10は、実施形態6に係るスーパージャンクション構造を有する半導体装置100eの断面図である。

【0073】

実施形態6に係るスーパージャンクション構造を有する半導体装置100eは、基本的には実施形態5に係るスーパージャンクション構造を有する半導体装置100dと同様の構成を有するが、環状導電層142dが形成されている領域のさらに外側に第2環状柱状埋込層136とは別の第3環状柱状埋込層136aが形成されている点で、実施形態5に係るスーパージャンクション構造を有する半導体装置100dの場合とは異なる。すなわち、実施形態6に係るスーパージャンクション構造を有する半導体装置100eにおいては、図10に示すように、(1本の第2環状柱状埋込層136の上方に位置する)環状導電層142dが形成されている領域のさらに外側に第2環状柱状埋込層136とは別の第3環状柱状埋込層136aが2本形成されている。

【0074】

このように、実施形態6に係るスーパージャンクション構造を有する半導体装置100eは、環状導電層142dが形成されている領域のさらに外側に第2環状柱状埋込層136とは別の第3環状柱状埋込層136aが形成されている点で、実施形態5に係るスーパージャンクション構造を有する半導体装置100dの場合とは異なるが、実施形態5に係るスーパージャンクション構造を有する半導体装置100dの場合と同様に、第2環状柱状埋込層136と、当該第2環状柱状埋込層136の上方に形成された環状導電層142dとをさらに備えることから、高温環境下で半導体装置に長時間逆バイアスを与えた場合であってもリーク電流が増加したり耐圧が低下したりすることがなくなる。

【0075】

また、実施形態6に係るスーパージャンクション構造を有する半導体装置100eによれば、環状導電層142dが形成されている領域のさらに外側に第2環状柱状埋込層136とは別の第3環状柱状埋込層136aが形成されているため、第2環状柱状埋込層136近傍の電界を緩和でき耐圧が安定する。

【0076】

なお、実施形態6に係るスーパージャンクション構造を有する半導体装置100dは、環状導電層142dが形成されている領域のさらに外側に第2環状柱状埋込層136とは別の第3環状柱状埋込層136aが形成されている点以外の点においては実施形態5に係るスーパージャンクション構造を有する半導体装置100dと同様の構成を有するため、実施形態5に係るスーパージャンクション構造を有する半導体装置100dが有する効果のうち該当する効果を有する。

【0077】

[実施形態7]

図11は、実施形態7に係るスーパージャンクション構造を有する半導体装置200の断面図である。実施形態7に係るスーパージャンクション構造を有する半導体装置200は、図11に示すように、n−型半導体層(第1導電型の半導体層)214と、活性領域R1におけるn−型半導体層214の表面に形成され、p型半導体材料(第2導電型の半導体材料)からなる複数の柱状埋込層218と、活性領域R1におけるn−型半導体層214の表面に形成されたp+型拡散層220と、活性領域R1におけるn−型半導体層214の表面上に形成されたアノード電極層(第1電極層)232と、活性領域R1を囲む耐圧領域R2におけるn−型半導体層214の表面に形成され、p型半導体材料からなる複数のガードリング(環状柱状埋込層)224と、耐圧領域R2及び当該耐圧領域R2を囲む周辺領域R3におけるn−型半導体層214の表面上に形成された絶縁層230と、カソード電極層250と、周辺領域R3におけるn−型半導体層214の表面に形成され、p型半導体材料からなる第2環状柱状埋込層236と、周辺領域R3における絶縁層230上に形成された環状導電層242とを備える、pnダイオードである。なお、図11中、符号212はn+型半導体基板を示し、符号210は半導体基体を示し、符号216,符号222及び符号234は溝を示し、符号220はp型高濃度オーミック拡散領域を示し、符号226はアノード電極電界緩和領域を示し、符号228は中継拡散領域を示す。

【0078】

このように、実施形態7に係るスーパージャンクション構造を有する半導体装置200は、pnダイオードである点で実施形態1に係るスーパージャンクション構造を有する半導体装置100の場合とは異なるが、第2環状柱状埋込層236と、当該第2環状柱状埋込層236の上方に形成された環状導電層242とを備えることから、実施形態1に係るスーパージャンクション構造を有する半導体装置100の場合と同様に、高温環境下で半導体装置に長時間逆バイアスを与えた場合であってもリーク電流が増加したり耐圧が低下したりすることがなくなる。

【0079】

なお、実施形態7に係るスーパージャンクション構造を有する半導体装置200は、pnダイオードである点以外の点においては実施形態1に係るスーパージャンクション構造を有する半導体装置100と同様の構成を有するため、実施形態1に係るスーパージャンクション構造を有する半導体装置100が有する効果のうち該当する効果を有する。

【0080】

[実施形態8]

図12は、実施形態8に係るスーパージャンクション構造を有する半導体装置300の断面図である。実施形態8に係るスーパージャンクション構造を有する半導体装置300は、図12に示すように、n−型半導体層(第1導電型の半導体層)314と、活性領域R1におけるn−型半導体層314の表面に形成され、p型半導体材料(第2導電型の半導体材料)からなる複数の柱状埋込層318と、活性領域R1におけるn−型半導体層314の表面に形成されたp型ボディ領域360、p型ボディ領域360の表面に形成されたn+型ソース領域362及びp+型コンタクト領域364と、活性領域R1におけるn−型半導体層314の表面上に形成されたゲート絶縁層372、ゲート電極層370及び層間絶縁層374並びにソース電極層(第1電極層)332と、活性領域R1を囲む耐圧領域R2におけるn−型半導体層314の表面に形成され、p型半導体材料からなる複数のガードリング(環状柱状埋込層)324と、耐圧領域R2及び当該耐圧領域R2を囲む周辺領域R3におけるn−型半導体層314の表面上に形成された絶縁層330と、ドレイン電極層350と、周辺領域R3におけるn−型半導体層314の表面に形成され、第2導電型の半導体材料からなる第2環状柱状埋込層336と、周辺領域R3における絶縁層330上に形成された環状導電層342とを備える、パワーMOSFETである。なお、図12中、符号312はn+型半導体基板を示し、符号310は半導体基体を示し、符号316,符号322及び符号334は溝を示し、符号326はソース電極電界緩和領域を示し、符号328は中継拡散領域を示す。

【0081】

このように、実施形態8に係るスーパージャンクション構造を有する半導体装置300は、パワーMOSFETである点で、実施形態1に係るスーパージャンクション構造を有する半導体装置100の場合とは異なるが、第2環状柱状埋込層336と、当該第2環状柱状埋込層336の上方に形成された環状導電層342とを備えることから、実施形態1に係るスーパージャンクション構造を有する半導体装置100の場合と同様に、高温環境下で半導体装置に長時間逆バイアスを与えた場合であってもリーク電流が増加したり耐圧が低下したりすることがなくなる。

【0082】

なお、実施形態8に係るスーパージャンクション構造を有する半導体装置300は、パワーMOSFETである点以外の点においては実施形態1に係るスーパージャンクション構造を有する半導体装置100と同様の構成を有するため、実施形態1に係るスーパージャンクション構造を有する半導体装置100が有する効果のうち該当する効果を有する。

【0083】

[実施例1]

実施例1は、本発明のスーパージャンクション構造を有する半導体装置によれば、高温環境下で半導体装置に長時間逆バイアスを与えた場合であってもリーク電流が増加しないことを説明するための実施例である。

【0084】

1.試料

実施形態1に係るスーパージャンクション構造を有する半導体装置100を実施例1とした。一方、実施形態1に係るスーパージャンクション構造を有する半導体装置100から第2環状柱状埋込層136及び環状導電層142を除去した構造の、スーパージャンクション構造を有する半導体装置(すなわち従来のスーパージャンクション構造を有する半導体装置900)を比較例1とした。

【0085】

2.評価方法

実施例1に係るスーパージャンクション構造を有する半導体装置100及び比較例1に係るスーパージャンクション構造を有する半導体装置900の評価は、実施例1に係るスーパージャンクション構造を有する半導体装置100及び比較例1に係るスーパージャンクション構造を有する半導体装置900をそれぞれ10個準備し、これらをBT試験機にセットした後、高温環境下(150℃)で逆バイアス(250V)を印加した状態で300時間、リーク電流を測定することにより行った。

【0086】

3.評価結果

図13は、実施例1の評価結果を示す図である。

図13からも明らかなように、比較例1に係るスーパージャンクション構造を有する半導体装置900においては、上記の条件でリーク電流が100倍から1000倍増加したのに対して、実施例1に係るスーパージャンクション構造を有する半導体装置100においては、上記した条件であっても全くリーク電流が増加しなかった。

【0087】

[実施例2]

実施例2は、本発明のスーパージャンクション構造を有する半導体装置によれば、高温環境下で半導体装置に長時間逆バイアスを与えた場合であっても耐圧が低下しないことを示す実施例である。

【0088】

1.試料

実施形態1に係るスーパージャンクション構造を有する半導体装置100を実施例2とした。一方、実施形態1に係るスーパージャンクション構造を有する半導体100から第2環状柱状埋込層136及び環状導電層142を除去した構造の、スーパージャンクション構造を有する半導体装置(すなわち従来のスーパージャンクション構造を有する半導体装置900)を比較例2とした。

【0089】

2.評価方法

実施例2に係るスーパージャンクション構造を有する半導体装置100及び比較例2に係るスーパージャンクション構造を有する半導体装置900の評価は、実施例2に係るスーパージャンクション構造を有する半導体装置100及び比較例2に係るスーパージャンクション構造を有する半導体装置900をそれぞれ1個準備し、これらを高温環境下(150℃)で逆バイアス(250V)を印加した状態で長時間(63時間又は2042時間)保持する前と後で耐圧波形を測定することによりBT試験評価を行った。

【0090】

3.評価結果

図14は、実施例2の評価結果を示す図である。

図14からも明らかなように、比較例2に係るスーパージャンクション構造を有する半導体装置900においては、高温逆バイアス下で63時間保持したことにより、耐圧が360Vから250Vに低下したのに対して、実施例2に係るスーパージャンクション構造を有する半導体装置100においては、高温逆バイアス下で63時間又は2042時間保持した場合であっても耐圧が360Vのまま全く低下しなかった。

【0091】

以上、本発明を上記の実施形態に基づいて説明したが、本発明は上記の実施形態に限定されるものではない。その趣旨を逸脱しない範囲において種々の態様において実施することが可能であり、例えば、次のような変形も可能である。

【0092】

(1)上記実施形態1においては、環状導電層142として、アノード電極層133と同一工程で形成されるアルミニウム層を用いたが、本発明はこれに限定されるものではない。例えば、ショットキーバリアメタル層132及びアノード電極層133とそれぞれ同一工程で形成される白金層及びアルミニウム層を用いることもできる。また、アルミニウム以外の金属層、金属層以外の導電層(例えばポリシリコン層又はドープトポリシリコン層)などを用いることもできる。

【0093】

(2)上記各実施形態においては、第1導電型をn型とし、第2導電型をp型とした場合を例にとって本発明を説明したが、本発明はこれに限定されるものではない。例えば、第1導電型をp型とし、第2導電型をn型とした場合にも本発明を適用可能である。

【0094】

(3)上記各実施形態1〜6においては、スーパージャンクション構造を有する半導体装置として、ショットキーバリアダイオードを用い、実施形態7においてはpnダイオードを用い、実施形態8においてはパワーMOSFETを用いたが、本発明はこれに限定されるものではない。これら以外のスーパージャンクション構造を有する半導体装置(ショットキーバリアダイオード、pnダイオード及びパワーMOSFET以外の半導体装置(例えばサイリスター、IGBTなど。)や、これらの半導体装置を含む各種複合半導体装置など。)を用いることもできる。

【符号の説明】

【0095】

100,100a,100b,100c,100d,100e,200,300…スーパージャンクション構造を有する半導体装置、110,210,310,910…半導体基体、112,212,312,912…n+型半導体基板、114,214,314,914…n−型半導体層、116,216,316,916…第1トレンチ、118,218,318,918…柱状埋込層、120,920…p型高濃度オーミック拡散領域、122,222,322,922…第2トレンチ、124,224,324,924…環状柱状埋込層、126,926…ショットキーバリアメタル電界緩和領域、128,228,328,928…中継拡散領域、130,130a,230,330,930…絶縁層、132,932…ショットキーバリアメタル層(第1電極層)、133,933…アノード電極層、134,234,334…第3トレンチ、136,236,336…第2環状柱状埋込層、138,238,338…p型高濃度拡散領域、140,140a,240,340…開口部、142,242,342…環状導電層、144,944…空乏層の終端部、150,250,950…カソード電極層、220…p+型拡散領域、226…アノード電極層電界緩和領域、232…アノード電極層(第1電極層)、326…ソース電極層電界緩和領域、332…ソース電極層(第1電極層)、350…ドレイン電極層、360…p型ボディ領域、362…n+型ソース領域、364…p+型コンタクト領域、370…ゲート電極、372…ゲート絶縁層、374…層間絶縁層、R1…活性領域、R2…耐圧領域、R3…周辺領域

【特許請求の範囲】

【請求項1】

第1導電型の半導体層と、

活性領域における前記半導体層の表面に形成され、第2導電型の半導体材料からなる複数の柱状埋込層と、

前記活性領域における前記半導体層の表面上に形成された第1電極層と、

活性領域を囲む耐圧領域における前記半導体層の表面に形成され、第2導電型の半導体材料からなる複数の環状柱状埋込層と、

前記耐圧領域及び当該耐圧領域を囲む周辺領域における前記半導体層の表面上に形成された絶縁層とを備える、スーパージャンクション構造を有する半導体装置であって、

前記周辺領域における前記半導体層の表面に形成され、第2導電型の半導体材料からなる第2環状柱状埋込層と、

前記周辺領域における前記絶縁層上に形成された環状導電層とをさらに備えることを特徴とする、スーパージャンクション構造を有する半導体装置。

【請求項2】

請求項1に記載のスーパージャンクション構造を有する半導体装置において、

前記絶縁層は、前記周辺領域における前記第2環状柱状埋込層が形成されている領域において開口部を有し、

前記環状導電層は、前記開口部を介して、前記第2環状柱状埋込層に接続されていることを特徴とする、スーパージャンクション構造を有する半導体装置。

【請求項3】

請求項2に記載のスーパージャンクション構造を有する半導体装置において、

前記環状導電層に接続されている第2環状柱状埋込層の表面近傍には、第2導電型の高濃度拡散領域が形成されていることを特徴とする、スーパージャンクション構造を有する半導体装置。

【請求項4】

請求項1に記載のスーパージャンクション構造を有する半導体装置において、

前記絶縁層は、前記周辺領域における前記第2環状柱状埋込層が形成されていない領域において開口部を有し、

前記環状導電層は、前記開口部を介して、前記半導体層に接続されていることを特徴とする、スーパージャンクション構造を有する半導体装置。

【請求項5】

請求項4に記載のスーパージャンクション構造を有する半導体装置において、

前記環状導電層に接続されている領域における前記半導体層の表面には、第1導電型の高濃度拡散領域が形成されていることを特徴とする、スーパージャンクション構造を有する半導体装置。

【請求項6】

請求項1〜5のいずれかに記載のスーパージャンクション構造を有する半導体装置において、

最外周の第2環状柱状埋込層よりも外周側に伸びる前記第2環状導電層の幅寸法は、第2環状柱状埋込層の深さ寸法よりも大きいことを特徴とする、スーパージャンクション構造を有する半導体装置。

【請求項7】

請求項1〜6のいずれかに記載のスーパージャンクション構造を有する半導体装置において、

前記環状導電層として、複数の環状導電層を備えることを特徴とする、スーパージャンクション構造を有する半導体装置。

【請求項8】

請求項1〜7のいずれかに記載のスーパージャンクション構造を有する半導体装置において、

前記第2環状柱状埋込層として、複数の第2環状柱状埋込層を備えることを特徴とする、スーパージャンクション構造を有する半導体装置。

【請求項9】

請求項8に記載の、スーパージャンクション構造を有する半導体装置において、

前記環状導電層は、最内周の第2環状柱状埋込層に接続されていることを特徴とする、スーパージャンクション構造を有する半導体装置。

【請求項1】

第1導電型の半導体層と、

活性領域における前記半導体層の表面に形成され、第2導電型の半導体材料からなる複数の柱状埋込層と、

前記活性領域における前記半導体層の表面上に形成された第1電極層と、

活性領域を囲む耐圧領域における前記半導体層の表面に形成され、第2導電型の半導体材料からなる複数の環状柱状埋込層と、

前記耐圧領域及び当該耐圧領域を囲む周辺領域における前記半導体層の表面上に形成された絶縁層とを備える、スーパージャンクション構造を有する半導体装置であって、

前記周辺領域における前記半導体層の表面に形成され、第2導電型の半導体材料からなる第2環状柱状埋込層と、

前記周辺領域における前記絶縁層上に形成された環状導電層とをさらに備えることを特徴とする、スーパージャンクション構造を有する半導体装置。

【請求項2】

請求項1に記載のスーパージャンクション構造を有する半導体装置において、

前記絶縁層は、前記周辺領域における前記第2環状柱状埋込層が形成されている領域において開口部を有し、

前記環状導電層は、前記開口部を介して、前記第2環状柱状埋込層に接続されていることを特徴とする、スーパージャンクション構造を有する半導体装置。

【請求項3】

請求項2に記載のスーパージャンクション構造を有する半導体装置において、

前記環状導電層に接続されている第2環状柱状埋込層の表面近傍には、第2導電型の高濃度拡散領域が形成されていることを特徴とする、スーパージャンクション構造を有する半導体装置。

【請求項4】

請求項1に記載のスーパージャンクション構造を有する半導体装置において、

前記絶縁層は、前記周辺領域における前記第2環状柱状埋込層が形成されていない領域において開口部を有し、

前記環状導電層は、前記開口部を介して、前記半導体層に接続されていることを特徴とする、スーパージャンクション構造を有する半導体装置。

【請求項5】

請求項4に記載のスーパージャンクション構造を有する半導体装置において、

前記環状導電層に接続されている領域における前記半導体層の表面には、第1導電型の高濃度拡散領域が形成されていることを特徴とする、スーパージャンクション構造を有する半導体装置。

【請求項6】

請求項1〜5のいずれかに記載のスーパージャンクション構造を有する半導体装置において、

最外周の第2環状柱状埋込層よりも外周側に伸びる前記第2環状導電層の幅寸法は、第2環状柱状埋込層の深さ寸法よりも大きいことを特徴とする、スーパージャンクション構造を有する半導体装置。

【請求項7】

請求項1〜6のいずれかに記載のスーパージャンクション構造を有する半導体装置において、

前記環状導電層として、複数の環状導電層を備えることを特徴とする、スーパージャンクション構造を有する半導体装置。

【請求項8】

請求項1〜7のいずれかに記載のスーパージャンクション構造を有する半導体装置において、

前記第2環状柱状埋込層として、複数の第2環状柱状埋込層を備えることを特徴とする、スーパージャンクション構造を有する半導体装置。

【請求項9】

請求項8に記載の、スーパージャンクション構造を有する半導体装置において、

前記環状導電層は、最内周の第2環状柱状埋込層に接続されていることを特徴とする、スーパージャンクション構造を有する半導体装置。

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【図14】

【図1】

【図15】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【図14】

【図1】

【図15】

【公開番号】特開2013−102087(P2013−102087A)

【公開日】平成25年5月23日(2013.5.23)

【国際特許分類】

【出願番号】特願2011−245656(P2011−245656)

【出願日】平成23年11月9日(2011.11.9)

【出願人】(000002037)新電元工業株式会社 (776)

【Fターム(参考)】

【公開日】平成25年5月23日(2013.5.23)

【国際特許分類】

【出願日】平成23年11月9日(2011.11.9)

【出願人】(000002037)新電元工業株式会社 (776)

【Fターム(参考)】

[ Back to top ]