セットアップ/ホールドタイム測定装置

【課題】テスト信号に応じて外部クロック信号からデータ信号と内部クロック信号を生成し、読取り/書込み動作無しでバッファリングされたデータの状態によってセットアップ/ホールドタイムを測定できるようにしたセットアップ/ホールドタイム測定装置を提供する。

【解決手段】外部クロック信号をカウント信号によって遅延させ、テスト信号に応答して、前記遅れた外部クロック信号から内部クロック信号及びデータ信号を生成するデータ生成部と、前記内部クロック信号に同期して、前記データ信号をバッファリングした信号をラッチするデータラッチと、前記テスト信号に応答して、前記データラッチ部でラッチされたデータ信号からフラグ信号を生成するフラグ信号生成部と、前記フラグ信号に応答して前記カウント信号をカウンティングするカウンターと、を含む構成とした。

【解決手段】外部クロック信号をカウント信号によって遅延させ、テスト信号に応答して、前記遅れた外部クロック信号から内部クロック信号及びデータ信号を生成するデータ生成部と、前記内部クロック信号に同期して、前記データ信号をバッファリングした信号をラッチするデータラッチと、前記テスト信号に応答して、前記データラッチ部でラッチされたデータ信号からフラグ信号を生成するフラグ信号生成部と、前記フラグ信号に応答して前記カウント信号をカウンティングするカウンターと、を含む構成とした。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、半導体メモリー装置に係り、より詳細には、データのセットアップ/ホールドタイムを效率的に測定できるようにしたセットアップ/ホールドタイム測定装置に関する。

【背景技術】

【0002】

近年、マイクロ・プロセッサの動作速度が速くなるに伴い、外部クロックに同期してデータ信号を入出力する同期式DRAM(SDRAM(Synchronous Dynamic Random Access Memory))が用いられている。これは、DRAM(Dynamic Random Access Memory)がマイクロ・プロセッサの動作速度を追従するには力不足であるから、DRAMとマイクロ・プロセッサとの速度ギャップを小さくし、システム性能を改善するためである。

【0003】

同期式DRAM(SDRAM)は、外部クロック信号に同期した内部クロック信号を用いてデータの入出力を行う。このような同期式DRAM(SDRAM)は、内部クロック信号によってデータの入出力が行なわれるので、高速のデータ転送が可能になる。

【0004】

一方、同期式DRAM(SDRAM)から正常にデータを読取り/書込みするためには、内部クロック信号に対して正常なセットアップ/ホールドタイム(setup/hold time)を確保することが重要である。ここで、セットアップタイム(setup time)は、入力されるデータが外部クロック信号を基準に一定時間前に印加される時間を意味し、ホールドタイム(hold time)は、入力される信号が外部クロック信号を基準に一定時間保持された時間を意味する。すなわち、セットアップタイム(setup time)及びホールドタイム(hold time)は、データの有効ウィンド(data valid window)を基準に前、後の時間を意味する。

【0005】

従来、データのセットアップ/ホールドタイム(setup/hold time)の測定は、外部装備で入力データとクロック信号間の遅延区間を変化させながら、読取り/書込み動作を通じて入力されるデータと出力パッドに出力されるデータの値を比較する方式で行われてきた。

【0006】

本出願と関連のある技術が、特許文献1に開示されている。

【特許文献1】米国特許第6097230号明細書

【発明の開示】

【発明が解決しようとする課題】

【0007】

しかしながら、このようなセットアップ/ホールドタイム(setup/hold time)測定方式は、入力データとクロック信号間の遅延区間を変化させるための外部装備を必要とし、入力されるデータと出力パッドに出力されるデータの値を比較するためには読取り/書込み動作が行わればならず、効率性が低下するという問題があった。

【0008】

本発明は、上記の問題点を解決するためのもので、その目的は、テスト信号に応じて外部クロック信号からデータ信号と内部クロック信号を生成し、読取り/書込み動作無しでバッファリングされたデータの状態によってセットアップ/ホールドタイムを測定できるようにしたセットアップ/ホールドタイム測定装置を提供することにある。

【課題を解決するための手段】

【0009】

上記の目的を達成するために、本発明の一つの観点では、外部クロック信号をカウント信号によって遅延させ、テスト信号に応答して、前記遅れた外部クロック信号から内部クロック信号及びデータ信号を生成するデータ生成部と、前記内部クロック信号に同期して、前記データ信号をバッファリングした信号をラッチするデータラッチと、前記テスト信号に応答して、前記データラッチ部でラッチされたデータ信号からフラグ信号を生成するフラグ信号生成部と、前記フラグ信号に応答して、前記カウント信号をカウンティングするカウンターと、を含むセットアップ/ホールドタイム測定装置が提供される。

【0010】

前記データ生成部は、前記外部クロック信号を、前記カウント信号によって決定された遅延区間だけ遅延させる遅延部と、前記テスト信号に応答して、前記外部クロック信号及び前記遅延部の出力信号から前記内部クロック信号及びデータ信号を生成するマルチプレクサと、を含むと良い。

【0011】

前記遅延部は、前記カウント信号に応答して選択的にイネーブルされる複数の遅延素子を含み、前記遅延部の遅延区間は、前記複数の遅延素子のうち、イネーブルされた遅延素子の数によって決定されることが好ましい。

【0012】

前記マルチプレクサは、前記テスト信号に応答して、前記外部クロック信号または前記遅延部の出力信号を選択的に前記内部クロック信号として伝達する第1の伝達部と、前記テスト信号に応答して、前記外部クロック信号または前記遅延部の出力信号を選択的に前記データ信号として伝達する第2の伝達部と、を含むと良い。

【0013】

前記データラッチは、前記内部クロック信号をバッファリングした信号に応答して、前記データ信号をバッファリングした信号をラッチし、駆動信号を生成する駆動信号生成部と、前記駆動信号に応答して出力ノードを駆動する駆動部と、を含むと良い。

【0014】

前記データラッチは、前記出力ノードの信号をラッチするラッチと、リセット信号に応答して前記出力ノードのレベルを設定するリセット素子と、をさらに含んでも良い。

【0015】

前記フラグ信号生成部は、前記テスト信号に応答して、前記データラッチ部でラッチされたデータ信号が既に設定されたレベルである場合にイネーブルされる前記フラグ信号を生成すると好ましい。

【0016】

前記セットアップ/ホールドタイム測定装置は、前記フラグ信号及び前記テスト信号に応答して前記カウンティング信号をパッドに出力する出力部をさらに含むと良い。

【0017】

前記出力部は、前記フラグ信号に応答して前記カウント信号を伝達する伝達部と、前記テスト信号に応答して前記伝達部の出力信号をラッチするラッチ部と、を含むと良い。

【0018】

また、上記の目的を達成するために、他のアスペクトによれば、複数のカウント信号に応答して選択的にイネーブルされる複数の遅延素子を含み、外部クロック信号を所定区間遅延させる遅延部と、テスト信号に応答して、前記外部クロック信号または前記遅延部の出力信号を選択的に伝達し、内部クロック信号及びデータ信号を生成するマルチプレクサと、前記データ信号をバッファリングし、複数の内部データ信号を生成する複数のバッファーと、前記内部クロック信号に同期して前記複数の内部データ信号をラッチし、複数のサンプリングデータ信号を抽出するデータラッチと、前記テスト信号に応答して前記複数のサンプリングデータ信号から第1及び第2のフラグ信号を生成するフラグ信号生成部と、前記第1及び第2のフラグ信号に応答して前記複数のカウント信号をカウンティングするカウンターと、を含むセットアップ/ホールドタイム測定装置が提供される。

【発明を実施するための最良の形態】

【0019】

本発明に好適な実施の形態について、図面に基づいて説明する。ただし、下記の実施形態は本発明を例示するためのもので、本発明の権利保護範囲を制限するためのものではない。

【0020】

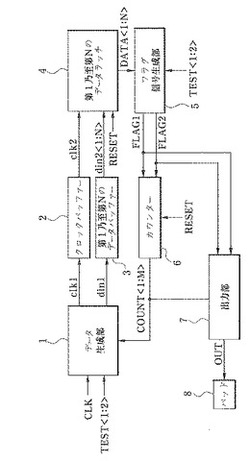

本発明の実施形態に係るセットアップ/ホールドタイム測定装置の構成及び機能について、図1乃至6を用いて説明する。

【0021】

図1は、本発明の一実施形態に係るセットアップ/ホールドタイム測定装置の構成を示すブロック図である。

【0022】

図1に示すように、本実施形態に係るセットアップ/ホールドタイム測定装置は、データ生成部1、クロックバッファー2、第1乃至第Nのデータバッファー3、第1乃至第Nのデータラッチ4、フラグ信号生成部5、カウンター6、出力部7及びパッド8を備えて構成される。

【0023】

図2を参照すると、データ生成部1は、遅延部10及びマルチプレクサ12を備えて構成される。

【0024】

遅延部10は、第1乃至第Mの遅延素子delay<1:M>から構成され、第1乃至第Mの遅延素子delay<1:M>はそれぞれ、第1乃至第Mのカウント信号COUNT<1:M>に応答してイネーブルされる。遅延部10は、外部クロックCLKを所定区間遅延させて遅延クロックCLKdを生成する。ここで、遅延部10の遅延区間は、第1乃至第Mの遅延素子delay<1:M>のうち、第1乃至第Mのカウント信号COUNT<1:M>によってイネーブルされた遅延素子の数によって決定される。例えば、第1乃至第Mの遅延素子delay<1:M>がそれぞれ単位遅延区間を有し、第1乃至第Mのカウント信号COUNT<1:M>によって第1乃至第Mの遅延素子delay<1:M>のうちK個の遅延素子がイネーブルされる場合、遅延部10の遅延区間は単位遅延区間のK倍になる。

【0025】

図3を参照すると、マルチプレクサ12は、第1の伝達部120及び第2の伝達部122を備えて構成される。

【0026】

第1の伝達部120は、第2のテスト信号TEST<2>に応答して、外部クロックCLKまたは遅延クロックCLKdを選択的に伝達するインバータIV11,IV12と、第1のテスト信号TEST<1>とインバータIV11,IV12の出力信号とを受信し否定論理積演算を行うことによって、第1の内部クロック信号clk1を生成するNANDゲートND10と、を備えて構成される。

【0027】

第2の伝達部122は、第2のテスト信号TEST<2>に応答して、外部クロックCLKまたは遅延クロックCLKdを選択的に伝達するインバータIV14,IV15と、第1のテスト信号TEST<1>とインバータIV14,IV15の出力信号とを受信し否定論理積演算を行うことによって、データ信号din1を生成するNANDゲートND11と、を備えて構成される。

【0028】

クロックバッファー2は、第1の内部クロック信号clk1をバッファリングし、第2の内部クロック信号clk2を生成する。クロックバッファー2は、一般的なクロックバッファー回路にすれば良い。

【0029】

第1乃至第Nのデータバッファー3は、データ信号din1を受信し、それぞれ、第1乃至第Nの内部データ信号din2を生成する。第1乃至第Nのデータバッファー3は、一般的なデータバッファー回路にし、本実施形態において第1乃至第Nのデータバッファー3の位置はそれぞれ別に設定されることが好ましい。これは、半導体メモリー装置において多様な回路に含まれた多数のデータバッファーを具現するためである。このように第1乃至第Nのデータバッファー3の位置を様々に設定すると、データ信号din1の転送される距離が異なってくることになり、よって、第1乃至第Nのデータバッファー3で生成される第1乃至第Nの内部データ信号din2の遅延区間も様々に設定される。

【0030】

図4を参照すると、第1乃至第Nのデータラッチ4は、第2の内部クロック信号clk2に応答して、第1乃至第Nの内部データ信号din2をラッチし、プルアップ信号PU及びプルダウン信号PDを生成する駆動信号生成部40と、プルアップ信号PU及びプルダウン信号PDに応答して、ノードnd40を駆動する駆動部42と、リセット信号RESETに応答してノードnd40をプルアップ駆動するリセット素子44と、ノードnd40の信号をラッチし、第1乃至第Nのサンプリングデータ信号DATA<1:N>を生成するラッチ46と、を備えて構成される。第1乃至第Nのデータラッチ4は、いずれも同じ回路的構成を有するので、図4のようにN個の回路を一つの図面に挙げて示した。

【0031】

図5を参照すると、フラグ信号生成部5は、第1乃至第Nのサンプリングデータ信号DATA<1:N>を受信し否定論理積演算を行うNANDゲートND50と、第1及び第2のテスト信号TEST<1:2>に応答してNANDゲートND50の出力信号をラッチし第1のフラグ信号FLAG1を生成するラッチ51と、第1乃至第Nのサンプリングデータ信号DATA<1:N>を受信し否定論理和演算を行うNORゲートNR50と、第1及び第2のテスト信号TEST<1:2>に応答してNORゲートNR50の出力信号をラッチし、第2のフラグ信号FLAG2を生成するラッチ53と、を備えて構成される。ラッチ51及びラッチ53は、第1及び第2のテスト信号TEST<1:2>に応答して選択的に動作するが、第1のテスト信号TEST<1>がハイレベルである状態において、第2のテスト信号TEST<2>がローレベルである場合にラッチ51が動作し、第2のテスト信号TEST<2>がハイレベルである場合にラッチ53が動作する。

【0032】

カウンター6は、第1のフラグ信号FLAG1及び第2のフラグ信号FLAG2に応答して、第1乃至第Mのカウント信号COUNT<1:M>をカウンティングする。本実施形態のカウンター6は、第1のフラグ信号FLAG1がハイレベル、または、第2のフラグ信号FLAG2がローレベルである場合にカウンティング動作を中断し、第1のフラグ信号FLAG1がローレベル、または、第2のフラグ信号FLAG2がハイレベルである場合にカウンティング動作を行うようにする。例えば、第1乃至第Mのカウント信号COUNT<1:M>が‘00,…,01'である状態において、第1のフラグ信号FLAG1がローレベルまたは第2のフラグ信号FLAG2がハイレベルの状態として入力されると、カウンター6は、第1乃至第Mのカウント信号COUNT<1:M>を‘00,…,11'状態としてカウンティングする。すなわち、第1乃至第Mのカウント信号のうち、ハイレベルにイネーブルされた信号の数を増加させる。

【0033】

図6を参照すると、出力部7は、伝達部70とラッチ部72とを備えて構成される。

【0034】

伝達部70は、第1のフラグ信号FLAG1に応答して第1乃至第Mのカウント信号COUNT<1:M>を伝達する伝達ゲートT70と、第2のフラグ信号FLAG2に応答して第1乃至第Mのカウント信号COUNT<1:M>を伝達する伝達ゲートT71と、を備えて構成される。伝達ゲートT70は、第1のフラグ信号FLAG1がハイレベルである場合に第1乃至第Mのカウント信号COUNT<1:M>を伝達し、伝達ゲートT71は、第2のフラグ信号FLAG2がローレベルである場合に第1乃至第Mのカウント信号COUNT<1:M>を伝達する。

【0035】

ラッチ部72は、第1及び第2のテスト信号TEST<1:2>に応答して伝達ゲートT70の出力信号をラッチするラッチ720と、第1及び第2のテスト信号TEST<1:2>に応答して伝達ゲートT71の出力信号をラッチするラッチ722と、を備えて構成される。ラッチ部72において、第1のテスト信号TEST<1>がハイレベルである状態において、第2のテスト信号TEST<2>がローレベルである場合にラッチ720が動作し、第2のテスト信号TEST<2>がハイレベルである場合にラッチ722が動作する。

【0036】

次に、このように構成されたセットアップ/ホールドタイム測定装置の動作について、図7及び図8を参照して詳細に説明する。

【0037】

第1のテスト信号TEST<1>がハイレベルであり、第2のテスト信号TEST<2>がローレベルである場合におけるセットアップ/ホールドタイム測定装置の動作について、図7を参照して説明する。

【0038】

まず、データ生成部1は、外部クロックCLKを受信し、第1の内部クロック信号clk1及びデータ信号din1を生成する。

【0039】

より具体的には、遅延部10は、外部クロックCLKを所定区間遅延させて遅延クロックCLKdを生成する。この時、遅延部10の遅延区間は、第1乃至第Mの遅延素子delay<1:M>のうち、第1乃至第Mのカウント信号COUNT<1:M>によってイネーブルされた遅延素子の数によって決定される。例えば、第1乃至第Mのカウント信号COUNT<1:M>のうち、第1乃至第Kのカウント信号COUNT<1: K>がハイレベルである場合、第1乃至第Kの遅延素子delay<1:K>がイネーブルされるので、遅延部10の遅延区間は、第1乃至第Kの遅延素子delay<1:K>のそれぞれの遅延区間、すなわち、単位遅延区間のK倍に設定される。本実施形態は、初期状態において遅延部10の遅延区間がdに設定された場合とした。

【0040】

マルチプレクサ12は、第1及び第2のテスト信号TEST<1:2>に応答して、遅延部10で生成された遅延クロックCLKdと外部クロックCLKとを第1の内部クロック信号clk1またはデータ信号din1として選択的に伝達する。上述したように、第1のテスト信号TEST<1>はハイレベルであり、第2のテスト信号TEST<2>はローレベルであるから、インバータIV11,IV14がターンオンされ、外部クロックCLKはデータ信号din1として出力され、遅延クロックCLKdは第1の内部クロック信号clk1として出力される。

【0041】

続いて、クロックバッファー2は、第1の内部クロック信号clk1をバッファリングし、第2の内部クロック信号clk2を生成する。また、第1乃至第Nのデータバッファー3は、データ信号din1を受信し、それぞれ第1乃至第Nの内部データ信号din2<1:N>を生成する。図7に示すように、第1乃至第Nの内部データ信号din2<1:N>は、第1乃至第Nのデータバッファー3の位置によって様々に形成されるが、これは、前述したように、第1乃至第Nのデータバッファー3に入力されるデータ信号din1が互いに異なる遅延区間の影響を受けながら転送されてくるためである。

【0042】

次に、第1乃至第Nのデータラッチ4は、第2の内部クロック信号clk2の立ち上がりエッジに同期して第1乃至第Nの内部データ信号din2<1:N>をラッチし、第1乃至第Nのサンプリングデータ信号DATA<1:N>を生成する。図7に示すように、第2の内部クロック信号clk2の立ち上がりエッジで第1乃至第N−1の内部データ信号din2<1:N−1>はハイレベルであるのに対し、第N内部データ信号din2<N>はローレベルであるから、第1乃至第N−1のサンプリングデータ信号DATA<1:N−1>はハイレベルになり、第Nサンプリングデータ信号DATA<N>はローレベルになる。

【0043】

続いて、フラグ信号生成部5は、第1乃至第Nのサンプリングデータ信号DATA<1:N>を受信し、第1のフラグ信号FLAG1を生成する。すなわち、ハイレベルの第1のテスト信号TEST<1>とローレベルの第2のテスト信号TEST<2>によってラッチ51が動作し、NANDゲートND50は、ローレベルの第Nサンプリングデータ信号DATA<N>によってローレベルの第1のフラグ信号FLAG1を生成する。

【0044】

次に、カウンター6は、ローレベルの第1のフラグ信号FLAG1を受信し、第1乃至第Mのカウント信号COUNT<1:M>をカウンティングする。例えば、第1乃至第Mのカウント信号COUNT<1:M>のうち、第1乃至第Kのカウント信号COUNT<1:K>がハイレベルである状態においてローレベルの第1のフラグ信号FLAG1が入力される場合、カウンター6がカウンティング動作を行い、第1乃至第K+1のカウント信号COUNT<1:K+1>はハイレベルになる。したがって、第1乃至第Mの遅延素子delay<1:M>のうち、イネーブルされる遅延素子の数はK+1個となり、遅延部10の遅延区間が増加する。

【0045】

カウンター6のカウンティング動作は、第1乃至第Nのサンプリングデータ信号DATA<1:N>がいずれもハイレベルとして生成され、ハイレベルの第1のフラグ信号FLAG1が生成されるまで繰り返し行われる。

【0046】

ハイレベルの第1のフラグ信号FLAG1が生成されると、出力部7の伝達ゲートT70がターンオンされ、ラッチ720は、ハイレベルの第1のテスト信号TEST<1>とローレベルの第2のテスト信号TEST<2>によって動作するので、第1乃至第Mのカウント信号COUNT<1:M>がパッド8を通じて出力される。出力された第1乃至第Mのカウント信号COUNT<1:M>のうち、ハイレベルにイネーブルされた信号の数から遅延部10の遅延区間を確認でき、これにより、セットアップ/ホールドタイムを測定することができる。

【0047】

次に、第1のテスト信号TEST<1>がハイレベルであり、第2のテスト信号TEST<2>がハイレベルである場合におけるセットアップ/ホールドタイム測定装置の動作について、図8を参照して説明する。

【0048】

まず、データ生成部1は、外部クロックCLKを受信し、第1の内部クロック信号clk1及びデータ信号din1を生成する。

【0049】

より具体的に、遅延部10は、外部クロックCLKを所定区間遅延させ、遅延クロックCLKdを生成する。この時、遅延部10の遅延区間は、第1乃至第Mの遅延素子delay<1:M>のうち、第1乃至第Mのカウント信号COUNT<1:M>によりイネーブルされた遅延素子の数によって決定される。例えば、第1乃至第Mのカウント信号COUNT<1:M>のうち、第1乃至第Kのカウント信号COUNT<1: K>がハイレベルである場合に、第1乃至第Kの遅延素子delay<1:K>がイネーブルされるので、遅延部10の遅延区間は、第1乃至第Kの遅延素子delay<1:K>のそれぞれの遅延区間、すなわち、単位遅延区間のK倍に設定される。本実施形態において、初期状態で遅延部10の遅延区間はdに設定された場合と仮定した。

【0050】

マルチプレクサ12は、第1及び第2のテスト信号TEST<1:2>に応答して、遅延部10で生成された遅延クロックCLKdと外部クロックCLKを第1の内部クロック信号clk1またはデータ信号din1として選択的に伝達する。前述したように、第1のテスト信号TEST<1>及び第2のテスト信号TEST<2>はハイレベルであるので、インバータIV12,IV15がターンオンされ、外部クロックCLKは第1の内部クロック信号clk1として出力され、遅延クロックCLKdはデータ信号din1として出力される。

【0051】

続いて、クロックバッファー2は、第1の内部クロック信号clk1をバッファリングし、第2の内部クロック信号clk2を生成する。また、第1乃至第Nのデータバッファー3は、データ信号din1を受信し、それぞれ第1乃至第Nの内部データ信号din2<1:N>を生成する。図8に示すように、第1乃至第Nの内部データ信号din2<1:N>は、第1乃至第Nのデータバッファー3の位置によって様々に形成されるが、これは、前述したように、第1乃至第Nのデータバッファー3に入力されるデータ信号din1が互いに異なる遅延区間の影響を受けながら転送されてくるためである。

【0052】

次に、第1乃至第Nのデータラッチ4は、第2の内部クロック信号clk2の立ち上がりエッジに同期して第1乃至第Nの内部データ信号din2<1:N>をラッチし、第1乃至第Nのサンプリングデータ信号DATA<1:N>を生成する。図8に示すように、第2の内部クロック信号clk2の立ち上がりエッジにおいて第1乃至第N−1の内部データ信号din2<1:N−1>はローレベルであるのに対し、第Nの内部データ信号din2<N>はハイレベルであるから、第1乃至第N−1のサンプリングデータ信号DATA<1:N−1>はローレベルになり、第Nサンプリングデータ信号DATA<N>はハイレベルになる。

【0053】

続いて、フラグ信号生成部5は、第1乃至第Nのサンプリングデータ信号DATA<1:N>を受信し、第2のフラグ信号FLAG2を生成する。すなわち、ハイレベルの第1のテスト信号TEST<1>とハイレベルの第2のテスト信号TEST<2>によってラッチ53が動作し、NORゲートNR50は、ハイレベルの第Nサンプリングデータ信号DATA<N>によってハイレベルの第2のフラグ信号FLAG2を生成する。

【0054】

次に、カウンター6は、ハイレベルの第2のフラグ信号FLAG2を受信し、第1乃至第Mのカウント信号COUNT<1:M>をカウンティングする。例えば、第1乃至第Mのカウント信号COUNT<1:M>のうち、第1乃至第Kのカウント信号COUNT<1:K>がハイレベルである状態においてハイレベルの第2のフラグ信号FLAG2が入力される場合に、カウンター6はカウンティング動作を行い、第1乃至第K+1のカウント信号COUNT<1:K+1>がハイレベルになる。したがって、第1乃至第Mの遅延素子delay<1:M>のうち、イネーブルされる遅延素子の数がK+1個になり、遅延部10の遅延区間は増加する。

【0055】

カウンター6のカウンティング動作は、第1乃至第Nのサンプリングデータ信号DATA<1:N>がいずれもローレベルとして生成され、ローレベルの第2のフラグ信号FLAG2が生成されるまで繰り返し行われる。

【0056】

ローレベルの第2のフラグ信号FLAG2が生成されると、出力部7の伝達ゲートT71がターンオンされ、ラッチ722は、ハイレベルの第1のテスト信号TEST<1>とハイレベルの第2のテスト信号TEST<2>により動作するので、第1乃至第Mのカウント信号COUNT<1:M>がパッド8を通じて出力される。出力された第1乃至第Mのカウント信号COUNT<1:M>のうち、ハイレベルにイネーブルされた信号の数から遅延部10の遅延区間を確認でき、これにより、セットアップ/ホールドタイムを測定することができる。

【図面の簡単な説明】

【0057】

【図1】本発明の一実施形態に係るセットアップ/ホールドタイム測定装置の構成の一例を示すブロック図である。

【図2】図1におけるデータ生成部の構成の一例を示すブロック図である。

【図3】図2に示すマルチプレクサの回路図である。

【図4】図1に示すデータラッチの回路図である。

【図5】図1に示すフラグ信号生成部の回路図である。

【図6】図1に示す出力部の回路図である。

【図7】図1に示すセットアップ/ホールドタイム測定装置の動作を説明するためのタイミング図である。

【図8】図1に示すセットアップ/ホールドタイム測定装置の動作を説明するためのタイミング図である。

【符号の説明】

【0058】

1 データ生成部

10 遅延部

12 マルチプレクサ

2 クロックバッファー

3 第1乃至第Nのデータバッファー

4 第1乃至第Nのデータラッチ

5 フラグ信号生成部

6 カウンター

7 出力部

8 パッド

【技術分野】

【0001】

本発明は、半導体メモリー装置に係り、より詳細には、データのセットアップ/ホールドタイムを效率的に測定できるようにしたセットアップ/ホールドタイム測定装置に関する。

【背景技術】

【0002】

近年、マイクロ・プロセッサの動作速度が速くなるに伴い、外部クロックに同期してデータ信号を入出力する同期式DRAM(SDRAM(Synchronous Dynamic Random Access Memory))が用いられている。これは、DRAM(Dynamic Random Access Memory)がマイクロ・プロセッサの動作速度を追従するには力不足であるから、DRAMとマイクロ・プロセッサとの速度ギャップを小さくし、システム性能を改善するためである。

【0003】

同期式DRAM(SDRAM)は、外部クロック信号に同期した内部クロック信号を用いてデータの入出力を行う。このような同期式DRAM(SDRAM)は、内部クロック信号によってデータの入出力が行なわれるので、高速のデータ転送が可能になる。

【0004】

一方、同期式DRAM(SDRAM)から正常にデータを読取り/書込みするためには、内部クロック信号に対して正常なセットアップ/ホールドタイム(setup/hold time)を確保することが重要である。ここで、セットアップタイム(setup time)は、入力されるデータが外部クロック信号を基準に一定時間前に印加される時間を意味し、ホールドタイム(hold time)は、入力される信号が外部クロック信号を基準に一定時間保持された時間を意味する。すなわち、セットアップタイム(setup time)及びホールドタイム(hold time)は、データの有効ウィンド(data valid window)を基準に前、後の時間を意味する。

【0005】

従来、データのセットアップ/ホールドタイム(setup/hold time)の測定は、外部装備で入力データとクロック信号間の遅延区間を変化させながら、読取り/書込み動作を通じて入力されるデータと出力パッドに出力されるデータの値を比較する方式で行われてきた。

【0006】

本出願と関連のある技術が、特許文献1に開示されている。

【特許文献1】米国特許第6097230号明細書

【発明の開示】

【発明が解決しようとする課題】

【0007】

しかしながら、このようなセットアップ/ホールドタイム(setup/hold time)測定方式は、入力データとクロック信号間の遅延区間を変化させるための外部装備を必要とし、入力されるデータと出力パッドに出力されるデータの値を比較するためには読取り/書込み動作が行わればならず、効率性が低下するという問題があった。

【0008】

本発明は、上記の問題点を解決するためのもので、その目的は、テスト信号に応じて外部クロック信号からデータ信号と内部クロック信号を生成し、読取り/書込み動作無しでバッファリングされたデータの状態によってセットアップ/ホールドタイムを測定できるようにしたセットアップ/ホールドタイム測定装置を提供することにある。

【課題を解決するための手段】

【0009】

上記の目的を達成するために、本発明の一つの観点では、外部クロック信号をカウント信号によって遅延させ、テスト信号に応答して、前記遅れた外部クロック信号から内部クロック信号及びデータ信号を生成するデータ生成部と、前記内部クロック信号に同期して、前記データ信号をバッファリングした信号をラッチするデータラッチと、前記テスト信号に応答して、前記データラッチ部でラッチされたデータ信号からフラグ信号を生成するフラグ信号生成部と、前記フラグ信号に応答して、前記カウント信号をカウンティングするカウンターと、を含むセットアップ/ホールドタイム測定装置が提供される。

【0010】

前記データ生成部は、前記外部クロック信号を、前記カウント信号によって決定された遅延区間だけ遅延させる遅延部と、前記テスト信号に応答して、前記外部クロック信号及び前記遅延部の出力信号から前記内部クロック信号及びデータ信号を生成するマルチプレクサと、を含むと良い。

【0011】

前記遅延部は、前記カウント信号に応答して選択的にイネーブルされる複数の遅延素子を含み、前記遅延部の遅延区間は、前記複数の遅延素子のうち、イネーブルされた遅延素子の数によって決定されることが好ましい。

【0012】

前記マルチプレクサは、前記テスト信号に応答して、前記外部クロック信号または前記遅延部の出力信号を選択的に前記内部クロック信号として伝達する第1の伝達部と、前記テスト信号に応答して、前記外部クロック信号または前記遅延部の出力信号を選択的に前記データ信号として伝達する第2の伝達部と、を含むと良い。

【0013】

前記データラッチは、前記内部クロック信号をバッファリングした信号に応答して、前記データ信号をバッファリングした信号をラッチし、駆動信号を生成する駆動信号生成部と、前記駆動信号に応答して出力ノードを駆動する駆動部と、を含むと良い。

【0014】

前記データラッチは、前記出力ノードの信号をラッチするラッチと、リセット信号に応答して前記出力ノードのレベルを設定するリセット素子と、をさらに含んでも良い。

【0015】

前記フラグ信号生成部は、前記テスト信号に応答して、前記データラッチ部でラッチされたデータ信号が既に設定されたレベルである場合にイネーブルされる前記フラグ信号を生成すると好ましい。

【0016】

前記セットアップ/ホールドタイム測定装置は、前記フラグ信号及び前記テスト信号に応答して前記カウンティング信号をパッドに出力する出力部をさらに含むと良い。

【0017】

前記出力部は、前記フラグ信号に応答して前記カウント信号を伝達する伝達部と、前記テスト信号に応答して前記伝達部の出力信号をラッチするラッチ部と、を含むと良い。

【0018】

また、上記の目的を達成するために、他のアスペクトによれば、複数のカウント信号に応答して選択的にイネーブルされる複数の遅延素子を含み、外部クロック信号を所定区間遅延させる遅延部と、テスト信号に応答して、前記外部クロック信号または前記遅延部の出力信号を選択的に伝達し、内部クロック信号及びデータ信号を生成するマルチプレクサと、前記データ信号をバッファリングし、複数の内部データ信号を生成する複数のバッファーと、前記内部クロック信号に同期して前記複数の内部データ信号をラッチし、複数のサンプリングデータ信号を抽出するデータラッチと、前記テスト信号に応答して前記複数のサンプリングデータ信号から第1及び第2のフラグ信号を生成するフラグ信号生成部と、前記第1及び第2のフラグ信号に応答して前記複数のカウント信号をカウンティングするカウンターと、を含むセットアップ/ホールドタイム測定装置が提供される。

【発明を実施するための最良の形態】

【0019】

本発明に好適な実施の形態について、図面に基づいて説明する。ただし、下記の実施形態は本発明を例示するためのもので、本発明の権利保護範囲を制限するためのものではない。

【0020】

本発明の実施形態に係るセットアップ/ホールドタイム測定装置の構成及び機能について、図1乃至6を用いて説明する。

【0021】

図1は、本発明の一実施形態に係るセットアップ/ホールドタイム測定装置の構成を示すブロック図である。

【0022】

図1に示すように、本実施形態に係るセットアップ/ホールドタイム測定装置は、データ生成部1、クロックバッファー2、第1乃至第Nのデータバッファー3、第1乃至第Nのデータラッチ4、フラグ信号生成部5、カウンター6、出力部7及びパッド8を備えて構成される。

【0023】

図2を参照すると、データ生成部1は、遅延部10及びマルチプレクサ12を備えて構成される。

【0024】

遅延部10は、第1乃至第Mの遅延素子delay<1:M>から構成され、第1乃至第Mの遅延素子delay<1:M>はそれぞれ、第1乃至第Mのカウント信号COUNT<1:M>に応答してイネーブルされる。遅延部10は、外部クロックCLKを所定区間遅延させて遅延クロックCLKdを生成する。ここで、遅延部10の遅延区間は、第1乃至第Mの遅延素子delay<1:M>のうち、第1乃至第Mのカウント信号COUNT<1:M>によってイネーブルされた遅延素子の数によって決定される。例えば、第1乃至第Mの遅延素子delay<1:M>がそれぞれ単位遅延区間を有し、第1乃至第Mのカウント信号COUNT<1:M>によって第1乃至第Mの遅延素子delay<1:M>のうちK個の遅延素子がイネーブルされる場合、遅延部10の遅延区間は単位遅延区間のK倍になる。

【0025】

図3を参照すると、マルチプレクサ12は、第1の伝達部120及び第2の伝達部122を備えて構成される。

【0026】

第1の伝達部120は、第2のテスト信号TEST<2>に応答して、外部クロックCLKまたは遅延クロックCLKdを選択的に伝達するインバータIV11,IV12と、第1のテスト信号TEST<1>とインバータIV11,IV12の出力信号とを受信し否定論理積演算を行うことによって、第1の内部クロック信号clk1を生成するNANDゲートND10と、を備えて構成される。

【0027】

第2の伝達部122は、第2のテスト信号TEST<2>に応答して、外部クロックCLKまたは遅延クロックCLKdを選択的に伝達するインバータIV14,IV15と、第1のテスト信号TEST<1>とインバータIV14,IV15の出力信号とを受信し否定論理積演算を行うことによって、データ信号din1を生成するNANDゲートND11と、を備えて構成される。

【0028】

クロックバッファー2は、第1の内部クロック信号clk1をバッファリングし、第2の内部クロック信号clk2を生成する。クロックバッファー2は、一般的なクロックバッファー回路にすれば良い。

【0029】

第1乃至第Nのデータバッファー3は、データ信号din1を受信し、それぞれ、第1乃至第Nの内部データ信号din2を生成する。第1乃至第Nのデータバッファー3は、一般的なデータバッファー回路にし、本実施形態において第1乃至第Nのデータバッファー3の位置はそれぞれ別に設定されることが好ましい。これは、半導体メモリー装置において多様な回路に含まれた多数のデータバッファーを具現するためである。このように第1乃至第Nのデータバッファー3の位置を様々に設定すると、データ信号din1の転送される距離が異なってくることになり、よって、第1乃至第Nのデータバッファー3で生成される第1乃至第Nの内部データ信号din2の遅延区間も様々に設定される。

【0030】

図4を参照すると、第1乃至第Nのデータラッチ4は、第2の内部クロック信号clk2に応答して、第1乃至第Nの内部データ信号din2をラッチし、プルアップ信号PU及びプルダウン信号PDを生成する駆動信号生成部40と、プルアップ信号PU及びプルダウン信号PDに応答して、ノードnd40を駆動する駆動部42と、リセット信号RESETに応答してノードnd40をプルアップ駆動するリセット素子44と、ノードnd40の信号をラッチし、第1乃至第Nのサンプリングデータ信号DATA<1:N>を生成するラッチ46と、を備えて構成される。第1乃至第Nのデータラッチ4は、いずれも同じ回路的構成を有するので、図4のようにN個の回路を一つの図面に挙げて示した。

【0031】

図5を参照すると、フラグ信号生成部5は、第1乃至第Nのサンプリングデータ信号DATA<1:N>を受信し否定論理積演算を行うNANDゲートND50と、第1及び第2のテスト信号TEST<1:2>に応答してNANDゲートND50の出力信号をラッチし第1のフラグ信号FLAG1を生成するラッチ51と、第1乃至第Nのサンプリングデータ信号DATA<1:N>を受信し否定論理和演算を行うNORゲートNR50と、第1及び第2のテスト信号TEST<1:2>に応答してNORゲートNR50の出力信号をラッチし、第2のフラグ信号FLAG2を生成するラッチ53と、を備えて構成される。ラッチ51及びラッチ53は、第1及び第2のテスト信号TEST<1:2>に応答して選択的に動作するが、第1のテスト信号TEST<1>がハイレベルである状態において、第2のテスト信号TEST<2>がローレベルである場合にラッチ51が動作し、第2のテスト信号TEST<2>がハイレベルである場合にラッチ53が動作する。

【0032】

カウンター6は、第1のフラグ信号FLAG1及び第2のフラグ信号FLAG2に応答して、第1乃至第Mのカウント信号COUNT<1:M>をカウンティングする。本実施形態のカウンター6は、第1のフラグ信号FLAG1がハイレベル、または、第2のフラグ信号FLAG2がローレベルである場合にカウンティング動作を中断し、第1のフラグ信号FLAG1がローレベル、または、第2のフラグ信号FLAG2がハイレベルである場合にカウンティング動作を行うようにする。例えば、第1乃至第Mのカウント信号COUNT<1:M>が‘00,…,01'である状態において、第1のフラグ信号FLAG1がローレベルまたは第2のフラグ信号FLAG2がハイレベルの状態として入力されると、カウンター6は、第1乃至第Mのカウント信号COUNT<1:M>を‘00,…,11'状態としてカウンティングする。すなわち、第1乃至第Mのカウント信号のうち、ハイレベルにイネーブルされた信号の数を増加させる。

【0033】

図6を参照すると、出力部7は、伝達部70とラッチ部72とを備えて構成される。

【0034】

伝達部70は、第1のフラグ信号FLAG1に応答して第1乃至第Mのカウント信号COUNT<1:M>を伝達する伝達ゲートT70と、第2のフラグ信号FLAG2に応答して第1乃至第Mのカウント信号COUNT<1:M>を伝達する伝達ゲートT71と、を備えて構成される。伝達ゲートT70は、第1のフラグ信号FLAG1がハイレベルである場合に第1乃至第Mのカウント信号COUNT<1:M>を伝達し、伝達ゲートT71は、第2のフラグ信号FLAG2がローレベルである場合に第1乃至第Mのカウント信号COUNT<1:M>を伝達する。

【0035】

ラッチ部72は、第1及び第2のテスト信号TEST<1:2>に応答して伝達ゲートT70の出力信号をラッチするラッチ720と、第1及び第2のテスト信号TEST<1:2>に応答して伝達ゲートT71の出力信号をラッチするラッチ722と、を備えて構成される。ラッチ部72において、第1のテスト信号TEST<1>がハイレベルである状態において、第2のテスト信号TEST<2>がローレベルである場合にラッチ720が動作し、第2のテスト信号TEST<2>がハイレベルである場合にラッチ722が動作する。

【0036】

次に、このように構成されたセットアップ/ホールドタイム測定装置の動作について、図7及び図8を参照して詳細に説明する。

【0037】

第1のテスト信号TEST<1>がハイレベルであり、第2のテスト信号TEST<2>がローレベルである場合におけるセットアップ/ホールドタイム測定装置の動作について、図7を参照して説明する。

【0038】

まず、データ生成部1は、外部クロックCLKを受信し、第1の内部クロック信号clk1及びデータ信号din1を生成する。

【0039】

より具体的には、遅延部10は、外部クロックCLKを所定区間遅延させて遅延クロックCLKdを生成する。この時、遅延部10の遅延区間は、第1乃至第Mの遅延素子delay<1:M>のうち、第1乃至第Mのカウント信号COUNT<1:M>によってイネーブルされた遅延素子の数によって決定される。例えば、第1乃至第Mのカウント信号COUNT<1:M>のうち、第1乃至第Kのカウント信号COUNT<1: K>がハイレベルである場合、第1乃至第Kの遅延素子delay<1:K>がイネーブルされるので、遅延部10の遅延区間は、第1乃至第Kの遅延素子delay<1:K>のそれぞれの遅延区間、すなわち、単位遅延区間のK倍に設定される。本実施形態は、初期状態において遅延部10の遅延区間がdに設定された場合とした。

【0040】

マルチプレクサ12は、第1及び第2のテスト信号TEST<1:2>に応答して、遅延部10で生成された遅延クロックCLKdと外部クロックCLKとを第1の内部クロック信号clk1またはデータ信号din1として選択的に伝達する。上述したように、第1のテスト信号TEST<1>はハイレベルであり、第2のテスト信号TEST<2>はローレベルであるから、インバータIV11,IV14がターンオンされ、外部クロックCLKはデータ信号din1として出力され、遅延クロックCLKdは第1の内部クロック信号clk1として出力される。

【0041】

続いて、クロックバッファー2は、第1の内部クロック信号clk1をバッファリングし、第2の内部クロック信号clk2を生成する。また、第1乃至第Nのデータバッファー3は、データ信号din1を受信し、それぞれ第1乃至第Nの内部データ信号din2<1:N>を生成する。図7に示すように、第1乃至第Nの内部データ信号din2<1:N>は、第1乃至第Nのデータバッファー3の位置によって様々に形成されるが、これは、前述したように、第1乃至第Nのデータバッファー3に入力されるデータ信号din1が互いに異なる遅延区間の影響を受けながら転送されてくるためである。

【0042】

次に、第1乃至第Nのデータラッチ4は、第2の内部クロック信号clk2の立ち上がりエッジに同期して第1乃至第Nの内部データ信号din2<1:N>をラッチし、第1乃至第Nのサンプリングデータ信号DATA<1:N>を生成する。図7に示すように、第2の内部クロック信号clk2の立ち上がりエッジで第1乃至第N−1の内部データ信号din2<1:N−1>はハイレベルであるのに対し、第N内部データ信号din2<N>はローレベルであるから、第1乃至第N−1のサンプリングデータ信号DATA<1:N−1>はハイレベルになり、第Nサンプリングデータ信号DATA<N>はローレベルになる。

【0043】

続いて、フラグ信号生成部5は、第1乃至第Nのサンプリングデータ信号DATA<1:N>を受信し、第1のフラグ信号FLAG1を生成する。すなわち、ハイレベルの第1のテスト信号TEST<1>とローレベルの第2のテスト信号TEST<2>によってラッチ51が動作し、NANDゲートND50は、ローレベルの第Nサンプリングデータ信号DATA<N>によってローレベルの第1のフラグ信号FLAG1を生成する。

【0044】

次に、カウンター6は、ローレベルの第1のフラグ信号FLAG1を受信し、第1乃至第Mのカウント信号COUNT<1:M>をカウンティングする。例えば、第1乃至第Mのカウント信号COUNT<1:M>のうち、第1乃至第Kのカウント信号COUNT<1:K>がハイレベルである状態においてローレベルの第1のフラグ信号FLAG1が入力される場合、カウンター6がカウンティング動作を行い、第1乃至第K+1のカウント信号COUNT<1:K+1>はハイレベルになる。したがって、第1乃至第Mの遅延素子delay<1:M>のうち、イネーブルされる遅延素子の数はK+1個となり、遅延部10の遅延区間が増加する。

【0045】

カウンター6のカウンティング動作は、第1乃至第Nのサンプリングデータ信号DATA<1:N>がいずれもハイレベルとして生成され、ハイレベルの第1のフラグ信号FLAG1が生成されるまで繰り返し行われる。

【0046】

ハイレベルの第1のフラグ信号FLAG1が生成されると、出力部7の伝達ゲートT70がターンオンされ、ラッチ720は、ハイレベルの第1のテスト信号TEST<1>とローレベルの第2のテスト信号TEST<2>によって動作するので、第1乃至第Mのカウント信号COUNT<1:M>がパッド8を通じて出力される。出力された第1乃至第Mのカウント信号COUNT<1:M>のうち、ハイレベルにイネーブルされた信号の数から遅延部10の遅延区間を確認でき、これにより、セットアップ/ホールドタイムを測定することができる。

【0047】

次に、第1のテスト信号TEST<1>がハイレベルであり、第2のテスト信号TEST<2>がハイレベルである場合におけるセットアップ/ホールドタイム測定装置の動作について、図8を参照して説明する。

【0048】

まず、データ生成部1は、外部クロックCLKを受信し、第1の内部クロック信号clk1及びデータ信号din1を生成する。

【0049】

より具体的に、遅延部10は、外部クロックCLKを所定区間遅延させ、遅延クロックCLKdを生成する。この時、遅延部10の遅延区間は、第1乃至第Mの遅延素子delay<1:M>のうち、第1乃至第Mのカウント信号COUNT<1:M>によりイネーブルされた遅延素子の数によって決定される。例えば、第1乃至第Mのカウント信号COUNT<1:M>のうち、第1乃至第Kのカウント信号COUNT<1: K>がハイレベルである場合に、第1乃至第Kの遅延素子delay<1:K>がイネーブルされるので、遅延部10の遅延区間は、第1乃至第Kの遅延素子delay<1:K>のそれぞれの遅延区間、すなわち、単位遅延区間のK倍に設定される。本実施形態において、初期状態で遅延部10の遅延区間はdに設定された場合と仮定した。

【0050】

マルチプレクサ12は、第1及び第2のテスト信号TEST<1:2>に応答して、遅延部10で生成された遅延クロックCLKdと外部クロックCLKを第1の内部クロック信号clk1またはデータ信号din1として選択的に伝達する。前述したように、第1のテスト信号TEST<1>及び第2のテスト信号TEST<2>はハイレベルであるので、インバータIV12,IV15がターンオンされ、外部クロックCLKは第1の内部クロック信号clk1として出力され、遅延クロックCLKdはデータ信号din1として出力される。

【0051】

続いて、クロックバッファー2は、第1の内部クロック信号clk1をバッファリングし、第2の内部クロック信号clk2を生成する。また、第1乃至第Nのデータバッファー3は、データ信号din1を受信し、それぞれ第1乃至第Nの内部データ信号din2<1:N>を生成する。図8に示すように、第1乃至第Nの内部データ信号din2<1:N>は、第1乃至第Nのデータバッファー3の位置によって様々に形成されるが、これは、前述したように、第1乃至第Nのデータバッファー3に入力されるデータ信号din1が互いに異なる遅延区間の影響を受けながら転送されてくるためである。

【0052】

次に、第1乃至第Nのデータラッチ4は、第2の内部クロック信号clk2の立ち上がりエッジに同期して第1乃至第Nの内部データ信号din2<1:N>をラッチし、第1乃至第Nのサンプリングデータ信号DATA<1:N>を生成する。図8に示すように、第2の内部クロック信号clk2の立ち上がりエッジにおいて第1乃至第N−1の内部データ信号din2<1:N−1>はローレベルであるのに対し、第Nの内部データ信号din2<N>はハイレベルであるから、第1乃至第N−1のサンプリングデータ信号DATA<1:N−1>はローレベルになり、第Nサンプリングデータ信号DATA<N>はハイレベルになる。

【0053】

続いて、フラグ信号生成部5は、第1乃至第Nのサンプリングデータ信号DATA<1:N>を受信し、第2のフラグ信号FLAG2を生成する。すなわち、ハイレベルの第1のテスト信号TEST<1>とハイレベルの第2のテスト信号TEST<2>によってラッチ53が動作し、NORゲートNR50は、ハイレベルの第Nサンプリングデータ信号DATA<N>によってハイレベルの第2のフラグ信号FLAG2を生成する。

【0054】

次に、カウンター6は、ハイレベルの第2のフラグ信号FLAG2を受信し、第1乃至第Mのカウント信号COUNT<1:M>をカウンティングする。例えば、第1乃至第Mのカウント信号COUNT<1:M>のうち、第1乃至第Kのカウント信号COUNT<1:K>がハイレベルである状態においてハイレベルの第2のフラグ信号FLAG2が入力される場合に、カウンター6はカウンティング動作を行い、第1乃至第K+1のカウント信号COUNT<1:K+1>がハイレベルになる。したがって、第1乃至第Mの遅延素子delay<1:M>のうち、イネーブルされる遅延素子の数がK+1個になり、遅延部10の遅延区間は増加する。

【0055】

カウンター6のカウンティング動作は、第1乃至第Nのサンプリングデータ信号DATA<1:N>がいずれもローレベルとして生成され、ローレベルの第2のフラグ信号FLAG2が生成されるまで繰り返し行われる。

【0056】

ローレベルの第2のフラグ信号FLAG2が生成されると、出力部7の伝達ゲートT71がターンオンされ、ラッチ722は、ハイレベルの第1のテスト信号TEST<1>とハイレベルの第2のテスト信号TEST<2>により動作するので、第1乃至第Mのカウント信号COUNT<1:M>がパッド8を通じて出力される。出力された第1乃至第Mのカウント信号COUNT<1:M>のうち、ハイレベルにイネーブルされた信号の数から遅延部10の遅延区間を確認でき、これにより、セットアップ/ホールドタイムを測定することができる。

【図面の簡単な説明】

【0057】

【図1】本発明の一実施形態に係るセットアップ/ホールドタイム測定装置の構成の一例を示すブロック図である。

【図2】図1におけるデータ生成部の構成の一例を示すブロック図である。

【図3】図2に示すマルチプレクサの回路図である。

【図4】図1に示すデータラッチの回路図である。

【図5】図1に示すフラグ信号生成部の回路図である。

【図6】図1に示す出力部の回路図である。

【図7】図1に示すセットアップ/ホールドタイム測定装置の動作を説明するためのタイミング図である。

【図8】図1に示すセットアップ/ホールドタイム測定装置の動作を説明するためのタイミング図である。

【符号の説明】

【0058】

1 データ生成部

10 遅延部

12 マルチプレクサ

2 クロックバッファー

3 第1乃至第Nのデータバッファー

4 第1乃至第Nのデータラッチ

5 フラグ信号生成部

6 カウンター

7 出力部

8 パッド

【特許請求の範囲】

【請求項1】

外部クロック信号をカウント信号によって遅延させ、テスト信号に応答して、前記遅れた外部クロック信号から内部クロック信号及びデータ信号を生成するデータ生成部と、

前記内部クロック信号に同期して、前記データ信号をバッファリングした信号をラッチするデータラッチと、

前記テスト信号に応答して、前記データラッチ部でラッチされたデータ信号からフラグ信号を生成するフラグ信号生成部と、

前記フラグ信号に応答して、前記カウント信号をカウンティングするカウンターと、

を含むセットアップ/ホールドタイム測定装置。

【請求項2】

前記データ生成部は、

前記外部クロック信号を、前記カウント信号によって決定された遅延区間だけ遅延させる遅延部と、

前記テスト信号に応答して、前記外部クロック信号及び前記遅延部の出力信号から前記内部クロック信号及びデータ信号を生成するマルチプレクサと、

を含む、請求項1に記載のセットアップ/ホールドタイム測定装置。

【請求項3】

前記遅延部は、前記カウント信号に応答して選択的にイネーブルされる複数の遅延素子を含み、

前記遅延部の遅延区間は、前記複数の遅延素子のうち、イネーブルされた遅延素子の数によって決定される、請求項2に記載のセットアップ/ホールドタイム測定装置。

【請求項4】

前記マルチプレクサは、

前記テスト信号に応答して、前記外部クロック信号または前記遅延部の出力信号を選択的に前記内部クロック信号として伝達する第1の伝達部と、

前記テスト信号に応答して、前記外部クロック信号または前記遅延部の出力信号を選択的に前記データ信号として伝達する第2の伝達部と、

を含む、請求項2に記載のセットアップ/ホールドタイム測定装置。

【請求項5】

前記データラッチは、

前記内部クロック信号をバッファリングした信号に応答して、前記データ信号をバッファリングした信号をラッチし、駆動信号を生成する駆動信号生成部と、

前記駆動信号に応答して出力ノードを駆動する駆動部と、

を含む、請求項1に記載のセットアップ/ホールドタイム測定装置。

【請求項6】

前記データラッチは、

前記出力ノードの信号をラッチするラッチと、

リセット信号に応答して前記出力ノードのレベルを設定するリセット素子と、

を更に含む、請求項5に記載のセットアップ/ホールドタイム測定装置。

【請求項7】

前記フラグ信号生成部は、前記テスト信号に応答して、前記データラッチ部でラッチされたデータ信号が既に設定されたレベルである場合にイネーブルされる前記フラグ信号を生成する、請求項1に記載のセットアップ/ホールドタイム測定装置。

【請求項8】

前記フラグ信号及び前記テスト信号に応答して前記カウンティング信号をパッドに出力する出力部をさらに含む、請求項1に記載のセットアップ/ホールドタイム測定装置。

【請求項9】

前記出力部は、

前記フラグ信号に応答して前記カウント信号を伝達する伝達部と、

前記テスト信号に応答して前記伝達部の出力信号をラッチするラッチ部と、

を含む、請求項8に記載のセットアップ/ホールドタイム測定装置。

【請求項10】

複数のカウント信号に応答して選択的にイネーブルされる複数の遅延素子を含み、外部クロック信号を所定区間遅延させる遅延部と、

テスト信号に応答して、前記外部クロック信号または前記遅延部の出力信号を選択的に伝達し、内部クロック信号及びデータ信号を生成するマルチプレクサと、

前記データ信号をバッファリングし、複数の内部データ信号を生成する複数のバッファーと、

前記内部クロック信号に同期して前記複数の内部データ信号をラッチし、複数のサンプリングデータ信号を抽出するデータラッチと、

前記テスト信号に応答して前記複数のサンプリングデータ信号から第1及び第2のフラグ信号を生成するフラグ信号生成部と、

前記第1及び第2のフラグ信号に応答して前記複数のカウント信号をカウンティングするカウンターと、

を含むセットアップ/ホールドタイム測定装置。

【請求項11】

前記遅延部の遅延区間は、前記複数の遅延素子のうち、イネーブルされる遅延素子の数によって決定される、請求項10に記載のセットアップ/ホールドタイム測定装置。

【請求項12】

前記マルチプレクサは、

前記テスト信号に応答して、前記外部クロック信号または前記遅延部の出力信号を選択的に前記内部クロック信号として伝達する第1の伝達部と、

前記テスト信号に応答して、前記外部クロック信号または前記遅延部の出力信号を選択的に前記データ信号として伝達する第2の伝達部と、

を含む、請求項10に記載のセットアップ/ホールドタイム測定装置。

【請求項13】

前記複数のバッファーは、

前記データ信号をバッファリングして第1の内部データ信号を生成する第1のバッファーと、

前記データ信号をバッファリングして第2の内部データ信号を生成する第2のバッファーと、

を含む、請求項10に記載のセットアップ/ホールドタイム測定装置。

【請求項14】

前記データラッチは、

前記内部クロック信号をバッファリングした信号に応答して前記第1の内部データ信号をラッチし、第1のサンプリングデータ信号を抽出する第1のデータラッチと、

前記内部クロック信号をバッファリングした信号に応答して前記第2の内部データ信号をラッチし、第2のサンプリングデータ信号を抽出する第2のデータラッチと、

を含む、請求項13に記載のセットアップ/ホールドタイム測定装置。

【請求項15】

前記第1のデータラッチは、

前記内部クロック信号をバッファリングした信号に応答して前記第1の内部データ信号をラッチし、駆動信号を生成する駆動信号生成部と、

前記駆動信号に応答して出力ノードを駆動する駆動部と、

を含む、請求項14に記載のセットアップ/ホールドタイム測定装置。

【請求項16】

前記第2のデータラッチは、

前記内部クロック信号をバッファリングした信号に応答して前記第2の内部データ信号をラッチし、駆動信号を生成する駆動信号生成部と、

前記駆動信号に応答して出力ノードを駆動する駆動部と、

を含む、請求項14に記載のセットアップ/ホールドタイム測定装置。

【請求項17】

前記フラグ信号生成部は、前記テスト信号に応答して前記第1及び第2のサンプリングデータ信号がいずれも既に設定されたレベルである場合にイネーブルされる前記第1及び第2のフラグ信号を生成する、請求項14に記載のセットアップ/ホールドタイム測定装置。

【請求項18】

前記フラグ信号生成部は、

前記第1及び第2のサンプリングデータ信号を受信し、論理演算を行う第1の論理素子と、

前記テスト信号に応答して前記第1の論理素子の出力信号をラッチし、前記第1のフラグ信号として伝達する第1のラッチと、

前記第1及び第2のサンプリングデータ信号を受信し、論理演算を行う第2の論理素子と、

前記テスト信号に応答して前記第2の論理素子の出力信号をラッチし、前記第2のフラグ信号として伝達する第2のラッチと、

を含む、請求項15に記載のセットアップ/ホールドタイム測定装置。

【請求項19】

前記第1の論理素子は、否定論理積演算を行い、

前記第2の論理素子は、否定論理和演算を行う、請求項18に記載のセットアップ/ホールドタイム測定装置。

【請求項20】

前記第1及び第2のラッチは、前記テスト信号に応答して選択的に動作する、請求項18に記載のセットアップ/ホールドタイム測定装置。

【請求項21】

前記第1及び第2のフラグ信号及び前記テスト信号に応答して前記カウンティング信号をパッドに出力する出力部をさらに含む、請求項10に記載のセットアップ/ホールドタイム測定装置。

【請求項22】

前記出力部は、

前記第1のフラグ信号に応答して前記カウント信号を伝達する第1の伝達素子と、

前記第2のフラグ信号に応答して前記カウント信号を伝達する第2の伝達素子と、

前記テスト信号に応答して前記第1の伝達素子の出力信号をラッチする第1のラッチと、

前記テスト信号に応答して前記第2の伝達素子の出力信号をラッチする第2のラッチと、

を含む、請求項21に記載のセットアップ/ホールドタイム測定装置。

【請求項23】

前記第1及び第2のラッチは、前記テスト信号に応答して選択的に動作する、請求項22に記載のセットアップ/ホールドタイム測定装置。

【請求項1】

外部クロック信号をカウント信号によって遅延させ、テスト信号に応答して、前記遅れた外部クロック信号から内部クロック信号及びデータ信号を生成するデータ生成部と、

前記内部クロック信号に同期して、前記データ信号をバッファリングした信号をラッチするデータラッチと、

前記テスト信号に応答して、前記データラッチ部でラッチされたデータ信号からフラグ信号を生成するフラグ信号生成部と、

前記フラグ信号に応答して、前記カウント信号をカウンティングするカウンターと、

を含むセットアップ/ホールドタイム測定装置。

【請求項2】

前記データ生成部は、

前記外部クロック信号を、前記カウント信号によって決定された遅延区間だけ遅延させる遅延部と、

前記テスト信号に応答して、前記外部クロック信号及び前記遅延部の出力信号から前記内部クロック信号及びデータ信号を生成するマルチプレクサと、

を含む、請求項1に記載のセットアップ/ホールドタイム測定装置。

【請求項3】

前記遅延部は、前記カウント信号に応答して選択的にイネーブルされる複数の遅延素子を含み、

前記遅延部の遅延区間は、前記複数の遅延素子のうち、イネーブルされた遅延素子の数によって決定される、請求項2に記載のセットアップ/ホールドタイム測定装置。

【請求項4】

前記マルチプレクサは、

前記テスト信号に応答して、前記外部クロック信号または前記遅延部の出力信号を選択的に前記内部クロック信号として伝達する第1の伝達部と、

前記テスト信号に応答して、前記外部クロック信号または前記遅延部の出力信号を選択的に前記データ信号として伝達する第2の伝達部と、

を含む、請求項2に記載のセットアップ/ホールドタイム測定装置。

【請求項5】

前記データラッチは、

前記内部クロック信号をバッファリングした信号に応答して、前記データ信号をバッファリングした信号をラッチし、駆動信号を生成する駆動信号生成部と、

前記駆動信号に応答して出力ノードを駆動する駆動部と、

を含む、請求項1に記載のセットアップ/ホールドタイム測定装置。

【請求項6】

前記データラッチは、

前記出力ノードの信号をラッチするラッチと、

リセット信号に応答して前記出力ノードのレベルを設定するリセット素子と、

を更に含む、請求項5に記載のセットアップ/ホールドタイム測定装置。

【請求項7】

前記フラグ信号生成部は、前記テスト信号に応答して、前記データラッチ部でラッチされたデータ信号が既に設定されたレベルである場合にイネーブルされる前記フラグ信号を生成する、請求項1に記載のセットアップ/ホールドタイム測定装置。

【請求項8】

前記フラグ信号及び前記テスト信号に応答して前記カウンティング信号をパッドに出力する出力部をさらに含む、請求項1に記載のセットアップ/ホールドタイム測定装置。

【請求項9】

前記出力部は、

前記フラグ信号に応答して前記カウント信号を伝達する伝達部と、

前記テスト信号に応答して前記伝達部の出力信号をラッチするラッチ部と、

を含む、請求項8に記載のセットアップ/ホールドタイム測定装置。

【請求項10】

複数のカウント信号に応答して選択的にイネーブルされる複数の遅延素子を含み、外部クロック信号を所定区間遅延させる遅延部と、

テスト信号に応答して、前記外部クロック信号または前記遅延部の出力信号を選択的に伝達し、内部クロック信号及びデータ信号を生成するマルチプレクサと、

前記データ信号をバッファリングし、複数の内部データ信号を生成する複数のバッファーと、

前記内部クロック信号に同期して前記複数の内部データ信号をラッチし、複数のサンプリングデータ信号を抽出するデータラッチと、

前記テスト信号に応答して前記複数のサンプリングデータ信号から第1及び第2のフラグ信号を生成するフラグ信号生成部と、

前記第1及び第2のフラグ信号に応答して前記複数のカウント信号をカウンティングするカウンターと、

を含むセットアップ/ホールドタイム測定装置。

【請求項11】

前記遅延部の遅延区間は、前記複数の遅延素子のうち、イネーブルされる遅延素子の数によって決定される、請求項10に記載のセットアップ/ホールドタイム測定装置。

【請求項12】

前記マルチプレクサは、

前記テスト信号に応答して、前記外部クロック信号または前記遅延部の出力信号を選択的に前記内部クロック信号として伝達する第1の伝達部と、

前記テスト信号に応答して、前記外部クロック信号または前記遅延部の出力信号を選択的に前記データ信号として伝達する第2の伝達部と、

を含む、請求項10に記載のセットアップ/ホールドタイム測定装置。

【請求項13】

前記複数のバッファーは、

前記データ信号をバッファリングして第1の内部データ信号を生成する第1のバッファーと、

前記データ信号をバッファリングして第2の内部データ信号を生成する第2のバッファーと、

を含む、請求項10に記載のセットアップ/ホールドタイム測定装置。

【請求項14】

前記データラッチは、

前記内部クロック信号をバッファリングした信号に応答して前記第1の内部データ信号をラッチし、第1のサンプリングデータ信号を抽出する第1のデータラッチと、

前記内部クロック信号をバッファリングした信号に応答して前記第2の内部データ信号をラッチし、第2のサンプリングデータ信号を抽出する第2のデータラッチと、

を含む、請求項13に記載のセットアップ/ホールドタイム測定装置。

【請求項15】

前記第1のデータラッチは、

前記内部クロック信号をバッファリングした信号に応答して前記第1の内部データ信号をラッチし、駆動信号を生成する駆動信号生成部と、

前記駆動信号に応答して出力ノードを駆動する駆動部と、

を含む、請求項14に記載のセットアップ/ホールドタイム測定装置。

【請求項16】

前記第2のデータラッチは、

前記内部クロック信号をバッファリングした信号に応答して前記第2の内部データ信号をラッチし、駆動信号を生成する駆動信号生成部と、

前記駆動信号に応答して出力ノードを駆動する駆動部と、

を含む、請求項14に記載のセットアップ/ホールドタイム測定装置。

【請求項17】

前記フラグ信号生成部は、前記テスト信号に応答して前記第1及び第2のサンプリングデータ信号がいずれも既に設定されたレベルである場合にイネーブルされる前記第1及び第2のフラグ信号を生成する、請求項14に記載のセットアップ/ホールドタイム測定装置。

【請求項18】

前記フラグ信号生成部は、

前記第1及び第2のサンプリングデータ信号を受信し、論理演算を行う第1の論理素子と、

前記テスト信号に応答して前記第1の論理素子の出力信号をラッチし、前記第1のフラグ信号として伝達する第1のラッチと、

前記第1及び第2のサンプリングデータ信号を受信し、論理演算を行う第2の論理素子と、

前記テスト信号に応答して前記第2の論理素子の出力信号をラッチし、前記第2のフラグ信号として伝達する第2のラッチと、

を含む、請求項15に記載のセットアップ/ホールドタイム測定装置。

【請求項19】

前記第1の論理素子は、否定論理積演算を行い、

前記第2の論理素子は、否定論理和演算を行う、請求項18に記載のセットアップ/ホールドタイム測定装置。

【請求項20】

前記第1及び第2のラッチは、前記テスト信号に応答して選択的に動作する、請求項18に記載のセットアップ/ホールドタイム測定装置。

【請求項21】

前記第1及び第2のフラグ信号及び前記テスト信号に応答して前記カウンティング信号をパッドに出力する出力部をさらに含む、請求項10に記載のセットアップ/ホールドタイム測定装置。

【請求項22】

前記出力部は、

前記第1のフラグ信号に応答して前記カウント信号を伝達する第1の伝達素子と、

前記第2のフラグ信号に応答して前記カウント信号を伝達する第2の伝達素子と、

前記テスト信号に応答して前記第1の伝達素子の出力信号をラッチする第1のラッチと、

前記テスト信号に応答して前記第2の伝達素子の出力信号をラッチする第2のラッチと、

を含む、請求項21に記載のセットアップ/ホールドタイム測定装置。

【請求項23】

前記第1及び第2のラッチは、前記テスト信号に応答して選択的に動作する、請求項22に記載のセットアップ/ホールドタイム測定装置。

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【公開番号】特開2010−9735(P2010−9735A)

【公開日】平成22年1月14日(2010.1.14)

【国際特許分類】

【出願番号】特願2008−306704(P2008−306704)

【出願日】平成20年12月1日(2008.12.1)

【出願人】(591024111)株式会社ハイニックスセミコンダクター (1,189)

【氏名又は名称原語表記】HYNIX SEMICONDUCTOR INC.

【住所又は居所原語表記】San 136−1,Ami−Ri,Bubal−Eup,Ichon−Shi,Kyoungki−Do,Korea

【Fターム(参考)】

【公開日】平成22年1月14日(2010.1.14)

【国際特許分類】

【出願日】平成20年12月1日(2008.12.1)

【出願人】(591024111)株式会社ハイニックスセミコンダクター (1,189)

【氏名又は名称原語表記】HYNIX SEMICONDUCTOR INC.

【住所又は居所原語表記】San 136−1,Ami−Ri,Bubal−Eup,Ichon−Shi,Kyoungki−Do,Korea

【Fターム(参考)】

[ Back to top ]