セット機器及びセット機器の制御方法

【課題】メモリカードに保存したマイコンのアプリケーション命令コードを読み出しを高速化する。

【解決手段】メインマイコンLSI1100とカードホストLSI1200とメモリカード1300aとがそれぞれ所定のカードバス仕様に準拠したカードバスの信号線CD1110a,CD1200a及びクロック信号線CK1110a,CK1200aにより接続されている。boot検出回路1240のバススイッチ制御信号1240aによりI/O回路1250a、1250bの制御方向をアプリケーション命令コードを読み出す方向に設定する。

【解決手段】メインマイコンLSI1100とカードホストLSI1200とメモリカード1300aとがそれぞれ所定のカードバス仕様に準拠したカードバスの信号線CD1110a,CD1200a及びクロック信号線CK1110a,CK1200aにより接続されている。boot検出回路1240のバススイッチ制御信号1240aによりI/O回路1250a、1250bの制御方向をアプリケーション命令コードを読み出す方向に設定する。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、メモリカードに対応した組み込みモジュールを制御する機能を有するセット機器に関する。

【背景技術】

【0002】

携帯電話端末等では、SDカード等の小型カードメディアのスロットが搭載され、外部記憶媒体として多く利用されている。この小型カードメディアを制御するため、携帯電話端末内のマイコンLSIの外部にカードホストLSIを接続し、このカードホストLSIによって小型カードメディアにアクセスしている。小型カードメディアには、マイコンLSIが使用するアプリケーション命令コードが保持されている。また、マイコンLSIが起動する際には、アプリケーション命令コードを、小型カードメディアからマイコンLSIに転送する処理が実施される。

【0003】

この転送処理に関して、例えば特許文献1には、ホストコントローラと、メモリカード用レベルシフタと、メモリカードが接続された構成において、伝送方向情報更新データにてモードレジスタを設定することで、外部信号CMDDIRやDATDIRあるいは、モードレジスタ設定値によって、メモリカード用レベルシフタのI/O方向が切替可能であると示されている。

【0004】

そして、特許文献1によるアプリケーション命令コードの転送に関わる処理は、ホストコントローラが伝送方向情報データを送信し、モードレジスタを設定して、メモリカード用レベルシフタのI/O方向を固定し、カードバス規格に準拠したアプリケーション命令コード読み出しコマンドを発行し、メモリカードが前記コマンドを受信し、メモリカードがアプリケーション命令コードを出力し、ホストコントローラが前記アプリケーション命令コードを受信する。

【0005】

そして、ホストコントローラがアプリケーション命令コードを受信し終えると、再度伝送方向情報データを送信し、モードレジスタを設定するといったとても煩雑な方法でなされる。

【0006】

また、特許文献2には、マイコンモジュールと、カードホストLSIと、複数のSDカードが、SDバスにて接続され、SDカードに対して並列にアクセス可能である構成において、マイコンから、SDカードバスコマンドを送信することによって、SDカードホストI/Fを経由して、マイコンとSDカードが接続されるか、マイコンとSDカードが、バススイッチを介して直接接続されるかを切替可能であると示されている。

【0007】

そして、特許文献2によるアプリケーション命令コードの転送に関わる処理は、マイコンモジュールがカードバスコマンドを発行して、マイコンとSDカードが、バススイッチを介しての直接接続と、カードホストLSIのI/O方向の固定とを実施し、カードバス規格に準拠したアプリケーション命令コード読み出しコマンドを発行し、SDカードが前記コマンドを受信し、SDカードがアプリケーション命令コードを出力し、マイコンが前記アプリケーション命令コードを受信する。

【0008】

そして、マイコンがアプリケーション命令コードを受信し終えると、再度カードバスコマンドを発行して、SDカードホストI/Fを経由してマイコンとSDカードを接続する

といったとても煩雑な方法でなされる。

【先行技術文献】

【特許文献】

【0009】

【特許文献1】特許第4158935号公報

【特許文献2】特開2010−73186号公報

【発明の概要】

【発明が解決しようとする課題】

【0010】

特許文献1の構成において、システムの起動時にメモリカードに保持されたアプリケーション命令コードを読み出す処理を実施する場合、カードバス規格に準拠した前記コードを読み出すためのコマンドを発行する前に、伝送方向情報データを発行して、モードレジスタを設定する必要がある。また、前記コードの読み出しが終了すれば、再度伝送方向情報データを発行して、モードレジスタを設定する必要がある。

【0011】

また、特許文献2の構成において、システムの起動時にSDカードに保持されたアプリケーション命令コードを読み出す処理を実施する場合、カードバス規格に準拠した前記コードを読み出すためのコマンドを発行する前に、SDカードバス規格に準拠しないカードバスコマンドを発行する必要がある。また、前記コードの読み出しが終了すれば、再度SDカードバス規格に準拠しないカードバスコマンドを発行し、SDカードホストI/Fを経由してマイコンとSDカードを接続する必要がある。

【0012】

そのため、特許文献1や特許文献2の構成においては、アプリケーション命令コードの読み出しコマンドを発行する前あるいはアプリケーション命令コードの受信後に、レジスタ設定や接続切替処理が必要であるため、システム起動に時間を要する。

【0013】

また、SDカードバス規格に準拠しないカードバスコマンドが必要であり、マイコンモジュールとSDカードの直結構成にて使用していた設計資産を容易に流用することができない。

【0014】

本発明はこれらの課題を解決せんがために、なされたものである。

【課題を解決するための手段】

【0015】

上記の課題を解決するため、本発明は、マイコンと、前記マイコンに使用されるアプリケーション命令コードを保持した、一つ以上のメモリカードと、前記マイコンと前記メモリカードを接続するデータパスと、前記アプリケーション命令コードの読み出し要求を検出し、前記データパスを制御する信号を出力するboot検出回路とを備えていることを特徴とする。

【発明の効果】

【0016】

アプリケーション命令コードを読み出す処理において、データパスを制御するために、レジスタ設定やコマンド送信を実施する必要がなく、システムの高速化が実現できる。また、レジスタ設定やコマンド送信をするために、予め決められたカードバス規格に準拠していないコマンドを設計する必要が無い。

【図面の簡単な説明】

【0017】

【図1】本発明の実施形態に係るセット機器の構成図である。

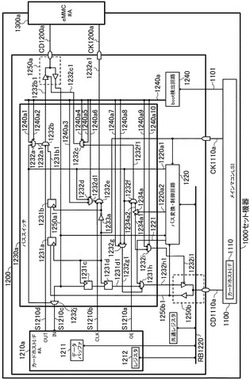

【図2】本発明の実施形態に係るセット機器のバススイッチとその周辺回路の詳細構成図である。

【図3】本発明の実施形態に係るセット機器のシステム起動から通常アクセス開始までのクロック及びコマンドのタイミングチャートの一例である。

【発明を実施するための形態】

【0018】

図1は本発明の実施形態1に関わるセット機器(1000)の構成図である。

【0019】

以下、その構成について説明する。

【0020】

図1に示すように、セット機器(1000)は、メモリカードとしてeMMC(Embedded MultiMedia Card)(1300a,1300b,1300c)が、カードバス(CB1200a,CB1200b,CB1200c)を介して接続されおり、マイコンモジュールとしてのメインマイコンLSI(1100)(以下、ACPUと呼ぶこととする)及びカードホストLSI(1200)を備えている。

【0021】

カードホストLSIは、カードホストI/F(1210a,1210b,1210c)、バス変換・制御回路1220、バススイッチ(1230a,CB1230b,CB1230c)及びboot検出回路1240を備えている。

【0022】

ACPU(1100)は、カードホストI/F(1110)を備えており、カードホストI/F(1110)は、eMMC(1300a, 1300b, 1300c)を制御する機能を有する。

【0023】

ここで、図1を用いて、セット機器(1000)の起動時に、eMMC(1300a)からACPU(1100)に対して、様々な処理を実施するために使用するアプリケーション命令コードをデータパスを通して転送する際の動作概略を説明する。

【0024】

まず、ACPU(1100)は、外部信号(1101)をHighレベルに制御し、アプリケーション命令コードの読み出し要求を通知する(第1のステップ)。

【0025】

すると、boot検出回路(1240)は、外部信号(1101)がHighレベルに制御されたことすなわちアプリケーション命令コードの読み出し要求を検出し、I/O回路の入出力制御部を制御する信号(1240a,1240b,1240c)を出力する(第2のステップ)。

【0026】

次に、ACPU(1100)は、内部のコマンド送信部からeMMC(1300a)に対して予め決められたカードバス規格に準拠したアプリケーション命令コードを読み出すためのコマンド(CMD)を信号線(CB1110)を介して送信する。この送信されたコマンド(CMD)は、ACPU(1100)とeMMC(1300a)のデータパスである信号線(CB1110)からバススイッチ(1230a)、信号線(CB1200a)を経由して、eMMC(1300a)に到達する(第3のステップ)。

【0027】

次に、eMMC(1300a)は、アプリケーション命令コードを信号線(CB1200a)を介して出力する。この出力されたアプリケーション命令コードは、ACPU(1100)とeMMC(1300a)のデータパスである信号線(CB1200a)からバススイッチ(1230a)、信号線(CB1110)を経由して、ACPU(1100)に到達する(第4のステップ)。

【0028】

次に、ACPU(1100)は、予め決められた量のアプリケーション命令コードを受信し終えると、外部信号(1101)をLowレベルに制御し、アプリケーション命令コードの読み出し要求を解除する(第5のステップ)。

【0029】

次に、boot検出回路(1240)が、外部信号(1101)がLowレベルに制御されたこと、すなわちアプリケーション命令コードの読み出し要求を解除されたことを検出する。すると、カードホストI/F(1210a,1210b,1210c)は、信号線(CB1110,CB1200a,CB1200b,CB1200c)の信号伝達方向を制御する。その結果、ACPU(1100)とeMMC(1300a)との間は、インターフェース部内のカードホストI/F(1210a,1210b,1210c)を介して接続される(第6のステップ)。

【0030】

図2は、図1におけるバススイッチ(1230a)とその周辺回路の詳細構成図である。ここで、バススイッチ(1230a,1230b,1230c)は同様の構成であるため、図2では代表してバススイッチ(1230a)を図示している。

【0031】

図2において、カードホストLSI(1200)は、カードホストI/F(1210a)、バススイッチ(1230a)、バス変換・制御回路(1220)、I/O回路(1250a,1250b)及びboot検出回路(1240)を備えている。なお、カードホストLSI(1200)は、eMMC(1300a)向けカードバス仕様におけるマスターとしても機能し、複数のカードバスと接続することが可能である。

【0032】

カードホストI/F(1210a)は、カードホストI/F(1110)からのコマンドなどを格納するレジスタ(1212)とFIFO構成のデータバッファ(1211)とを備えている。

【0033】

バススイッチ(1230a)は、コマンド(CMD)信号やデータ(DAT)信号の経路に関して、カードホストI/F(1210a)を介する経路と、介さない経路との切替えを実施する。なお、その切替えは、カードホストI/F(1210a)、バス変換・制御回路(1220)、またはboot検出回路(1240)により実施される。

【0034】

バス変換・制御回路(1220)は、ACPU(1100)から予め決められたカードバス仕様に準拠したコマンド(CMD)信号や、予め決められたカードバス仕様に準拠していないコマンド(CMD)信号を受け、I/O回路(1250a,1250b)の方向制御や、コマンド(CMD)、データ(DAT)の経路切替えのための信号を生成する。

【0035】

I/O回路(1250a,1250b)は、カードホストLSI(1200)における外部I/Fである。ここで、便宜上I/O回路(1250a,1250b)は、それぞれ一つ図示しているが、これに限定されない。例えば、本実施形態では、I/O回路(1250a,1250b)はそれぞれ、コマンド(CMD)信号用のI/Oが一つとデータ(DAT)信号用のI/Oが八つの計九つを備えている。

【0036】

boot検出回路(1240)は、ACPU(1100)からアプリケーション命令コードの読み出し要求があることを検出すると、バススイッチ制御信号(1240a)を出力する。

【0037】

より具体的には、ACPU(1100)により外部信号(1101)がHigh/Lowレベルに制御されたとき、その制御に応じてバススイッチ(1230a)及びI/O回路(1250a,1250b)を制御するためのバススイッチ制御信号(1240a)を出力する。

【0038】

以下、図2を用いて、eMMC(1300a)に格納されたACPU(1100)のアプリケーション命令コードを読み出す動作をより具体的に説明する。

【0039】

まず、第2のステップである入出力方向の固定について、図2を用いて、より具体的に説明する。ACPU(1100)は、セット機器(1000)の起動時に、外部信号(1101)をHighレベルに制御し、アプリケーション命令コードの読み出し要求を通知する。boot検出回路(1240)は、外部信号(1101)がHighレベルに制御されたことを検出すると、バススイッチ(1230a)を制御するためのバススイッチ制御信号(1240a)を出力する。

【0040】

なお、バススイッチ制御信号(1240a)は、バススイッチ制御信号(1240a1,1240a2,1240a3,1240a4,1240a5,1240a6,1240a7,1240a8,1240a9,1240a10)を含んでいる。また、バススイッチ制御信号(1240a)は、バススイッチのセレクタ(1232a,1232c,1232d,1232g,1232i)にそれぞれ供給される。

【0041】

セレクタ(1232a)は、バス変換・制御回路(1220)で生成されたコマンド(CMD)信号及びデータ(DAT)信号の経路切替信号(1220a1)、またはboot検出回路で生成されたバススイッチ制御信号(1240a1)のいずれかをバススイッチ制御信号(1240a2)に基づいて選択する。なお、アプリケーション命令コードの読み出しを実施する場合は、セレクタ(1232a)は、バススイッチ制御信号(1240a1)を選択し、出力信号(1232a1)として出力する。

【0042】

セレクタ(1232b)のうち、コマンド(CMD)信号用のセレクタ(1232b)は、カードホストI/F(1210a)のコマンド(CMD)信号(1210d)、または信号線(CD1110a)からI/O回路(1250b)のバッファを介して出力されたコマンド(CMD)信号(1250b1)が、レジスタ(1231a,1231b)を介して出力された信号(1231b1)のいずれかをセレクタ(1232a)の出力信号(1232a1)に基づいて選択する。なお、アプリケーション命令コードの読み出しを実施する場合は、コマンド用のセレクタ(1232b)は、信号線(CD1110a)から入力されたコマンド(CMD)信号を選択し、信号(1232b1)として出力する。このとき、セレクタ(1232b)のうちデータ(DAT)信号用のセレクタ(1232b)は、データ(DAT)信号をeMMC(1300a)に出力する必要がないため、その制御は不要である。

【0043】

セレクタ(1232c)は、バススイッチ制御信号(1240a5)、またはセレクタ(1232f)の出力のいずれかをバススイッチ制御信号(1240a4)に基づいて選択する。なお、アプリケーション命令コードの読み出しを実施する場合は、セレクタ(1232c)は、バススイッチ制御信号(1240a5)を選択し、I/O方向制御信号(1232c1)として出力する。このとき、コマンド(CMD)信号のI/O方向制御信号(1232c1)はI/O回路(1250a)を出力方向に制御する一方、データ(DAT)信号のI/O方向制御信号(1232c1)はI/O回路(1250a)を入力方向にそれぞれ制御する。その結果、I/O回路(1250a)は、セレクタ(1232b)において選択し、出力されたコマンド(CMD)信号(1232b1)を信号線(CD1200a)に出力する。

【0044】

セレクタ(1232d)は、バス変換・制御回路で生成された信号(1220a1)、またはバススイッチ制御信号(1240a3)のいずれかをバススイッチ制御信号(1240a6)に基づいて選択する。なお、アプリケーション命令コードの読み出しを実施する場合は、セレクタ(1232d)はバススイッチ制御信号(1240a3)を選択し、出力信号(1232d1)として出力する。

【0045】

セレクタ(1232e)は、カードホストI/F(1210a)で生成されたクロック(S1210b)、またはACPU(1100)から入力されたクロック(CK1110a)をインバータ(1233a)で反転した信号のいずれかをセレクタ(1232d)の出力信号(1232d1)に基づいて選択する。なお、アプリケーション命令コードの読み出しを実施する場合は、セレクタ(1232e)はクロック(CK1110a)をインバータ(1233a)で反転した信号を選択し、クロック信号線(CK1200a)に出力する。

【0046】

セレクタ(1232g)は、バス変換・制御回路で生成された信号(1220a1)、またはバススイッチ制御信号(1240a8)のいずれかをバススイッチ制御信号(1240a7)に基づいて選択する。なお、セレクタ(1232g)はアプリケーション命令コードの読み出しを実施する場合は、バススイッチ制御信号(1240a8)を選択し、信号(1232g1)として出力する。

【0047】

セレクタ(1232h)のうち、データ(DAT)信号用のセレクタ(1232h)は、eMMC(1300a)から、バススイッチ(1230a)、カードホストI/F(1210a)及びバス変換・制御回路(1220)を経て出力されたデータ(DAT)信号(1221)、またはeMMC(1300a)からバススイッチ(1230a)のレジスタ(1231c、1231d)を経て出力されたデータ(DAT)信号(1231d1)のいずれかをセレクタ(1232g)の出力信号(1232g1)に基づいて選択する。なお、アプリケーション命令コードの読み出しを実施する場合は、セレクタ(1232h)はデータ(DAT)信号(1231d1)を選択し、信号(1232h1)として出力する。このとき、コマンド(CMD)信号用のセレクタ(1232h)は、コマンド(CMD)信号をACPU(1100)に出力する必要がないので、その制御は不要である。

【0048】

セレクタ(1232i)は、バス変換・制御回路(1220)からインバータ(1234a)を介して出力された信号(1234a1)、またはバススイッチ制御信号(1240a9)のいずれかをバススイッチ制御信号(1240a10)に基づいて選択する。なお、アプリケーション命令コードの読み出しを実施する場合は、セレクタ(1232i)はバススイッチ制御信号(1240a9)を選択し、信号(1232i1)として出力する。このとき、データ(DAT)信号のI/O方向制御信号(1232i1)はI/O回路(1250b)を出力方向に制御する一方、コマンド(CMD)信号のI/O方向制御信号(1232i1)はI/O回路(1250b)を入力方向にそれぞれ制御する。その結果、I/O回路(1250b)は、セレクタ(1232h)において選択し、出力されたデータ(DAT)信号(1232h1)を信号線(CD1110a)に出力する。

【0049】

次に、第3のステップであるACPU(1100)のコマンド(CMD)の発行からeMMC(1300a)への到達までについて、図2を用いて、より具体的に説明する。

【0050】

ACPU(1100)は、内部のコマンド送信部からeMMC(1300a)に対して予め決められたカードバス規格に準拠したアプリケーション命令コードを読み出すためのコマンド(CMD)を信号線(CB1110)を介して発行する。ここで、アプリケーション命令コードの読み出しの場合は、コマンド(CMD)信号用のI/O回路(1250b)は入力方向に制御されているため、コマンド(CMD)信号はカードホストLSI(1200)に入力される。そして、この入力されたコマンド(CMD)信号は、レジスタ(1231a,1231b)、及びセレクタ(1232b)を経てI/O回路(1250a)に入力される。ここで、アプリケーション命令コードの読み出しの場合は、コマンド(CMD)信号用のI/O回路(1250a)は出力方向に制御されているため、コマンド(CMD)信号は信号線(CD1200a)を介してeMMC(1300a)に出力される。

【0051】

次に、第4のステップであるeMMC(1300a)のアプリケーション命令コードの出力からACPU(1100)への到達までについて、図2を用いて、より具体的に説明する。

【0052】

コマンド(CMD)信号がeMMC(1300a)に入力されると、eMMC規格に従い、eMMC(1300a)からアプリケーション命令コードが信号線(CD1200a)を介して出力される。ここで、アプリケーション命令コードの読み出しの場合は、データ(DAT)信号用のI/O回路(1250a)は入力方向に制御されているため、データ(DAT)信号はカードホストLSI(1200)に入力される。そして、この入力されたデータ(DAT)信号は、レジスタ(1231c,1231d)及び、セレクタ(1232h)を経てI/O回路(1250b)に入力される。ここで、アプリケーション命令コードの読み出しの場合は、データ(DAT)信号用のI/O回路(1250b)は出力方向に制御されているため、データ(DAT)信号は信号線(CD1110a)を介してACPU(1100)に出力される。

【0053】

次に、第5のステップ及び第6のステップであるアプリケーション命令コードの受信完了からACPU(1100)とeMMC(1300a)との間がインターフェース部内のカードホストI/F(1210a,1210b,1210c)を介して接続されるまでについて、図2を用いて、より具体的に説明する。

【0054】

ACPU(1100)は、アプリケーション命令コードの受信が完了すると、外部信号(1101)をLowレベルに制御する。そして、boot検出回路(1240)は、外部信号(1101)がLowレベルに制御されたことを検出すると、バススイッチ制御信号(1240a)を出力する。

【0055】

このとき、バススイッチ制御信号(1240a)を受けて、各セレクタ(1232a〜1232i)は下記のように制御される。

【0056】

セレクタ(1232a)は、バススイッチ制御信号(1240a2)に基づいて、バス変換・制御回路の出力信号(1220a1)を選択し、信号(1232a1)として出力する。

【0057】

セレクタ(1232b)は、セレクタ(1232a)から出力された信号(1232a1)に基づいて、カードホストI/F(1210a)から出力された信号(S1210d)を選択し、信号(1232b1)として出力する。

【0058】

セレクタ(1232c)は、バススイッチ制御信号(1240a4)に基づいて、セレクタ(1232f)から出力された信号(1232f1)を選択し、信号(1232c1)として出力する。

【0059】

セレクタ(1232d)は、バススイッチ制御信号(1240a6)に基づいて、バス変換・制御回路(1220)から出力された信号(1220a1)を選択し、信号(1232d1)として出力する。

【0060】

セレクタ(1232e)は、セレクタ(1232d)から出力された信号(1232d1)に基づいて、カードホストI/F(1210a)から出力されたクロック(S1210b)を選択し、クロック信号線(CK1200a)に出力する。

【0061】

セレクタ(1232f)は、バス変換・制御回路(1220)から出力された信号(1220a1)に基づいて、カードホストI/F(1210a)から出力された信号(S1210a)を選択し、信号(1232f1)として出力する。

【0062】

セレクタ(1232g)は、バススイッチ制御信号(1240a7)に基づいて、バス変換・制御回路から出力された信号(1220a1)を選択し、信号(1232g1)として出力する。

【0063】

セレクタ(1232h)は、セレクタ(1232g)から出力された信号(1232g1)に基づいて、カードホストI/F(1210a)から出力され、レジスタバス(RB1220)及びバス変換・制御回路(1220)を経た信号(1221)を選択し、信号(1232h1)として出力する。

【0064】

セレクタ(1232i)は、バススイッチ制御信号(1240a10)に基づいて、カードホストI/F(1210a)から出力され、レジスタバス(RB1220)、バス変換・制御回路(1220)、及びインバータ(1234a)を経た信号(1234a1)が選択を選択し、信号(1232i1)として出力する。

【0065】

そして、これらの各セレクタ(1232a〜1232i)の制御後、ACPU(1100)は、信号線(CD1110a)にコマンド(CMD)を出力することによって、カードホストLSI(1200)内部のカードホストI/F(1210a)にコマンド(CMD)がバッファリングされ、eMMC(1300a)などのカードホストLSI(1200)に接続された複数のデバイスに対して並列に、読み出し、書込み及び消去といったアクセスを開始する。

【0066】

このように本実施形態によると、ACPU(1100)とカードホストLSI(1200)とeMMC(1300a,1300b,1300c)とが、予め決められたカードバス仕様で接続され、ACPU(1100)からeMMC(1300a,1300b,1300c)に対して並列にアクセスできるセット機器(1000)において、システム起動時のアプリケーション命令コードの読み出す処理においてカードホストLSI(1200)のI/O回路(1250a,1250b)の方向を設定するために、レジスタ設定やコマンド送信を実施する必要がなく、システム起動の高速化が実現できる。また、レジスタ設定やコマンド送信をするために、予め決められたカードバス規格に準拠していないコマンド(CMD)を設計する必要が無い。

【0067】

なお、バススイッチ(1230a)にあるフリップフロップ(1231a,1231b,1231c,1231d)はあっても良いし、無くても良い。

【0068】

また、バススイッチ(1230a)にあるインバータ(1233a)は、クロックデューティー比調整のためにあっても良いし、無くても良い。

【0069】

また、図2のバススイッチ(1230a)にあるセレクタなどは、図2のような個別の実装に限定されない。例えば、同じ論理値になるものは同一信号線にするといった論理圧縮をして実装しても良い。

【0070】

また、アプリケーション命令コードの読み出しを実施するためにHighレベルに制御する信号線(1101)は、図2のようなACPU(1100)から出力する形に限定されない。例えば、ACPU(1100)から信号は出力せずに、予め決められた時間だけHighレベルに制御されるような構成であっても良い。また、予め決められた時間だけ、Highレベルに制御する手段は、カウンタ回路であっても良いし、容量素子と抵抗素子から構成される時定数回路のようなものであっても良い。

【0071】

また、アプリケーション命令コードの読み出し要求をACPU(1100)からカードホストLSI(1200)に伝える手段は、外部信号(1101)の代わりに、コマンド(CMD)信号線(CD1110a)や、クロック信号線(CK1110a)を使用しても良い。

【0072】

また、アプリケーション命令コードの読み出し要求をコマンド(CMD)信号線(CD1110a)や、クロック信号線(CK1110a)を使用してカードホストLSI(1200)に伝える際、図3に示すように、コマンド(CD1110a)がHighレベルであり、かつ、アプリケーション命令コードの読み出しのためのコマンドを発行する前の期間(3002)において、クロック(CK1110a)のエッジ数をカウントし、予め決められたカウント数より少なければ、アプリケーション命令コードの読み出し要求があると判断する一方、予め決められたカウント数より多ければ、アプリケーション命令コードの読み出し要求がないと判断するものとしても良い。

【0073】

また、アプリケーション命令コードの読み出しを終了するためにLowレベルに制御する信号線(1101)は、図2のように、ACPU(1100)から出力されても良いし、ACPU(1100)から出力されず、予め決められた時間が経過すると自動でLowレベルに制御されるような構成であっても良い。

【0074】

また、アプリケーション命令コードの読み出しの終了をACPU(1100)からカードホストLSI(1200)に伝える手段は、信号線(1101)の代わりに、コマンド(CMD)信号線(CD1110a)と、クロック信号線(CK1110a)を使用しても良い。

【0075】

また、アプリケーション命令コードの読み出しの終了は、図3に示すように、外部信号(1101)の代わりに、アプリケーション命令コードの読み出し終了のとき(3004)において、コマンド(CD1110a)がHighレベルになることで判断するものとしても良い。

【0076】

また、上記はシステムの起動時に限定されるものではない。

【0077】

また、eMMCの代わりに、SDやeSD、MMCなどのメモリカードを用いてもよい。

【0078】

また、アプリケーション命令コードをACPU(1100)に転送する際、セット機器(1000)の起動時に、外部信号(1101)をLowに制御して、アプリケーション命令コードの読出しを終了する際に、外部信号(1101)をHighレベルに制御しても良い。

【産業上の利用可能性】

【0079】

本発明では、カードバス構成を採用するシステム初期化時のプログラムリード処理を高速化できるので、より早いシステムの起動に有用である。

【符号の説明】

【0080】

1000 セット機器

1100 メインマイコンLSI(マイコン)

1110,1210a,1210b,1210c カードホストI/F

1200 カードホストLSI

1211 データバッファ

1220 バス変換・制御回路

1230a,1230b,1230c バススイッチ(入出力制御部)

1240 boot回路

1240a,1240b,1240c バススイッチ制御信号

1250a,1250b I/O回路(入力部、出力部)

1300a,1300b,1300c eMMC(メモリカード)

【技術分野】

【0001】

本発明は、メモリカードに対応した組み込みモジュールを制御する機能を有するセット機器に関する。

【背景技術】

【0002】

携帯電話端末等では、SDカード等の小型カードメディアのスロットが搭載され、外部記憶媒体として多く利用されている。この小型カードメディアを制御するため、携帯電話端末内のマイコンLSIの外部にカードホストLSIを接続し、このカードホストLSIによって小型カードメディアにアクセスしている。小型カードメディアには、マイコンLSIが使用するアプリケーション命令コードが保持されている。また、マイコンLSIが起動する際には、アプリケーション命令コードを、小型カードメディアからマイコンLSIに転送する処理が実施される。

【0003】

この転送処理に関して、例えば特許文献1には、ホストコントローラと、メモリカード用レベルシフタと、メモリカードが接続された構成において、伝送方向情報更新データにてモードレジスタを設定することで、外部信号CMDDIRやDATDIRあるいは、モードレジスタ設定値によって、メモリカード用レベルシフタのI/O方向が切替可能であると示されている。

【0004】

そして、特許文献1によるアプリケーション命令コードの転送に関わる処理は、ホストコントローラが伝送方向情報データを送信し、モードレジスタを設定して、メモリカード用レベルシフタのI/O方向を固定し、カードバス規格に準拠したアプリケーション命令コード読み出しコマンドを発行し、メモリカードが前記コマンドを受信し、メモリカードがアプリケーション命令コードを出力し、ホストコントローラが前記アプリケーション命令コードを受信する。

【0005】

そして、ホストコントローラがアプリケーション命令コードを受信し終えると、再度伝送方向情報データを送信し、モードレジスタを設定するといったとても煩雑な方法でなされる。

【0006】

また、特許文献2には、マイコンモジュールと、カードホストLSIと、複数のSDカードが、SDバスにて接続され、SDカードに対して並列にアクセス可能である構成において、マイコンから、SDカードバスコマンドを送信することによって、SDカードホストI/Fを経由して、マイコンとSDカードが接続されるか、マイコンとSDカードが、バススイッチを介して直接接続されるかを切替可能であると示されている。

【0007】

そして、特許文献2によるアプリケーション命令コードの転送に関わる処理は、マイコンモジュールがカードバスコマンドを発行して、マイコンとSDカードが、バススイッチを介しての直接接続と、カードホストLSIのI/O方向の固定とを実施し、カードバス規格に準拠したアプリケーション命令コード読み出しコマンドを発行し、SDカードが前記コマンドを受信し、SDカードがアプリケーション命令コードを出力し、マイコンが前記アプリケーション命令コードを受信する。

【0008】

そして、マイコンがアプリケーション命令コードを受信し終えると、再度カードバスコマンドを発行して、SDカードホストI/Fを経由してマイコンとSDカードを接続する

といったとても煩雑な方法でなされる。

【先行技術文献】

【特許文献】

【0009】

【特許文献1】特許第4158935号公報

【特許文献2】特開2010−73186号公報

【発明の概要】

【発明が解決しようとする課題】

【0010】

特許文献1の構成において、システムの起動時にメモリカードに保持されたアプリケーション命令コードを読み出す処理を実施する場合、カードバス規格に準拠した前記コードを読み出すためのコマンドを発行する前に、伝送方向情報データを発行して、モードレジスタを設定する必要がある。また、前記コードの読み出しが終了すれば、再度伝送方向情報データを発行して、モードレジスタを設定する必要がある。

【0011】

また、特許文献2の構成において、システムの起動時にSDカードに保持されたアプリケーション命令コードを読み出す処理を実施する場合、カードバス規格に準拠した前記コードを読み出すためのコマンドを発行する前に、SDカードバス規格に準拠しないカードバスコマンドを発行する必要がある。また、前記コードの読み出しが終了すれば、再度SDカードバス規格に準拠しないカードバスコマンドを発行し、SDカードホストI/Fを経由してマイコンとSDカードを接続する必要がある。

【0012】

そのため、特許文献1や特許文献2の構成においては、アプリケーション命令コードの読み出しコマンドを発行する前あるいはアプリケーション命令コードの受信後に、レジスタ設定や接続切替処理が必要であるため、システム起動に時間を要する。

【0013】

また、SDカードバス規格に準拠しないカードバスコマンドが必要であり、マイコンモジュールとSDカードの直結構成にて使用していた設計資産を容易に流用することができない。

【0014】

本発明はこれらの課題を解決せんがために、なされたものである。

【課題を解決するための手段】

【0015】

上記の課題を解決するため、本発明は、マイコンと、前記マイコンに使用されるアプリケーション命令コードを保持した、一つ以上のメモリカードと、前記マイコンと前記メモリカードを接続するデータパスと、前記アプリケーション命令コードの読み出し要求を検出し、前記データパスを制御する信号を出力するboot検出回路とを備えていることを特徴とする。

【発明の効果】

【0016】

アプリケーション命令コードを読み出す処理において、データパスを制御するために、レジスタ設定やコマンド送信を実施する必要がなく、システムの高速化が実現できる。また、レジスタ設定やコマンド送信をするために、予め決められたカードバス規格に準拠していないコマンドを設計する必要が無い。

【図面の簡単な説明】

【0017】

【図1】本発明の実施形態に係るセット機器の構成図である。

【図2】本発明の実施形態に係るセット機器のバススイッチとその周辺回路の詳細構成図である。

【図3】本発明の実施形態に係るセット機器のシステム起動から通常アクセス開始までのクロック及びコマンドのタイミングチャートの一例である。

【発明を実施するための形態】

【0018】

図1は本発明の実施形態1に関わるセット機器(1000)の構成図である。

【0019】

以下、その構成について説明する。

【0020】

図1に示すように、セット機器(1000)は、メモリカードとしてeMMC(Embedded MultiMedia Card)(1300a,1300b,1300c)が、カードバス(CB1200a,CB1200b,CB1200c)を介して接続されおり、マイコンモジュールとしてのメインマイコンLSI(1100)(以下、ACPUと呼ぶこととする)及びカードホストLSI(1200)を備えている。

【0021】

カードホストLSIは、カードホストI/F(1210a,1210b,1210c)、バス変換・制御回路1220、バススイッチ(1230a,CB1230b,CB1230c)及びboot検出回路1240を備えている。

【0022】

ACPU(1100)は、カードホストI/F(1110)を備えており、カードホストI/F(1110)は、eMMC(1300a, 1300b, 1300c)を制御する機能を有する。

【0023】

ここで、図1を用いて、セット機器(1000)の起動時に、eMMC(1300a)からACPU(1100)に対して、様々な処理を実施するために使用するアプリケーション命令コードをデータパスを通して転送する際の動作概略を説明する。

【0024】

まず、ACPU(1100)は、外部信号(1101)をHighレベルに制御し、アプリケーション命令コードの読み出し要求を通知する(第1のステップ)。

【0025】

すると、boot検出回路(1240)は、外部信号(1101)がHighレベルに制御されたことすなわちアプリケーション命令コードの読み出し要求を検出し、I/O回路の入出力制御部を制御する信号(1240a,1240b,1240c)を出力する(第2のステップ)。

【0026】

次に、ACPU(1100)は、内部のコマンド送信部からeMMC(1300a)に対して予め決められたカードバス規格に準拠したアプリケーション命令コードを読み出すためのコマンド(CMD)を信号線(CB1110)を介して送信する。この送信されたコマンド(CMD)は、ACPU(1100)とeMMC(1300a)のデータパスである信号線(CB1110)からバススイッチ(1230a)、信号線(CB1200a)を経由して、eMMC(1300a)に到達する(第3のステップ)。

【0027】

次に、eMMC(1300a)は、アプリケーション命令コードを信号線(CB1200a)を介して出力する。この出力されたアプリケーション命令コードは、ACPU(1100)とeMMC(1300a)のデータパスである信号線(CB1200a)からバススイッチ(1230a)、信号線(CB1110)を経由して、ACPU(1100)に到達する(第4のステップ)。

【0028】

次に、ACPU(1100)は、予め決められた量のアプリケーション命令コードを受信し終えると、外部信号(1101)をLowレベルに制御し、アプリケーション命令コードの読み出し要求を解除する(第5のステップ)。

【0029】

次に、boot検出回路(1240)が、外部信号(1101)がLowレベルに制御されたこと、すなわちアプリケーション命令コードの読み出し要求を解除されたことを検出する。すると、カードホストI/F(1210a,1210b,1210c)は、信号線(CB1110,CB1200a,CB1200b,CB1200c)の信号伝達方向を制御する。その結果、ACPU(1100)とeMMC(1300a)との間は、インターフェース部内のカードホストI/F(1210a,1210b,1210c)を介して接続される(第6のステップ)。

【0030】

図2は、図1におけるバススイッチ(1230a)とその周辺回路の詳細構成図である。ここで、バススイッチ(1230a,1230b,1230c)は同様の構成であるため、図2では代表してバススイッチ(1230a)を図示している。

【0031】

図2において、カードホストLSI(1200)は、カードホストI/F(1210a)、バススイッチ(1230a)、バス変換・制御回路(1220)、I/O回路(1250a,1250b)及びboot検出回路(1240)を備えている。なお、カードホストLSI(1200)は、eMMC(1300a)向けカードバス仕様におけるマスターとしても機能し、複数のカードバスと接続することが可能である。

【0032】

カードホストI/F(1210a)は、カードホストI/F(1110)からのコマンドなどを格納するレジスタ(1212)とFIFO構成のデータバッファ(1211)とを備えている。

【0033】

バススイッチ(1230a)は、コマンド(CMD)信号やデータ(DAT)信号の経路に関して、カードホストI/F(1210a)を介する経路と、介さない経路との切替えを実施する。なお、その切替えは、カードホストI/F(1210a)、バス変換・制御回路(1220)、またはboot検出回路(1240)により実施される。

【0034】

バス変換・制御回路(1220)は、ACPU(1100)から予め決められたカードバス仕様に準拠したコマンド(CMD)信号や、予め決められたカードバス仕様に準拠していないコマンド(CMD)信号を受け、I/O回路(1250a,1250b)の方向制御や、コマンド(CMD)、データ(DAT)の経路切替えのための信号を生成する。

【0035】

I/O回路(1250a,1250b)は、カードホストLSI(1200)における外部I/Fである。ここで、便宜上I/O回路(1250a,1250b)は、それぞれ一つ図示しているが、これに限定されない。例えば、本実施形態では、I/O回路(1250a,1250b)はそれぞれ、コマンド(CMD)信号用のI/Oが一つとデータ(DAT)信号用のI/Oが八つの計九つを備えている。

【0036】

boot検出回路(1240)は、ACPU(1100)からアプリケーション命令コードの読み出し要求があることを検出すると、バススイッチ制御信号(1240a)を出力する。

【0037】

より具体的には、ACPU(1100)により外部信号(1101)がHigh/Lowレベルに制御されたとき、その制御に応じてバススイッチ(1230a)及びI/O回路(1250a,1250b)を制御するためのバススイッチ制御信号(1240a)を出力する。

【0038】

以下、図2を用いて、eMMC(1300a)に格納されたACPU(1100)のアプリケーション命令コードを読み出す動作をより具体的に説明する。

【0039】

まず、第2のステップである入出力方向の固定について、図2を用いて、より具体的に説明する。ACPU(1100)は、セット機器(1000)の起動時に、外部信号(1101)をHighレベルに制御し、アプリケーション命令コードの読み出し要求を通知する。boot検出回路(1240)は、外部信号(1101)がHighレベルに制御されたことを検出すると、バススイッチ(1230a)を制御するためのバススイッチ制御信号(1240a)を出力する。

【0040】

なお、バススイッチ制御信号(1240a)は、バススイッチ制御信号(1240a1,1240a2,1240a3,1240a4,1240a5,1240a6,1240a7,1240a8,1240a9,1240a10)を含んでいる。また、バススイッチ制御信号(1240a)は、バススイッチのセレクタ(1232a,1232c,1232d,1232g,1232i)にそれぞれ供給される。

【0041】

セレクタ(1232a)は、バス変換・制御回路(1220)で生成されたコマンド(CMD)信号及びデータ(DAT)信号の経路切替信号(1220a1)、またはboot検出回路で生成されたバススイッチ制御信号(1240a1)のいずれかをバススイッチ制御信号(1240a2)に基づいて選択する。なお、アプリケーション命令コードの読み出しを実施する場合は、セレクタ(1232a)は、バススイッチ制御信号(1240a1)を選択し、出力信号(1232a1)として出力する。

【0042】

セレクタ(1232b)のうち、コマンド(CMD)信号用のセレクタ(1232b)は、カードホストI/F(1210a)のコマンド(CMD)信号(1210d)、または信号線(CD1110a)からI/O回路(1250b)のバッファを介して出力されたコマンド(CMD)信号(1250b1)が、レジスタ(1231a,1231b)を介して出力された信号(1231b1)のいずれかをセレクタ(1232a)の出力信号(1232a1)に基づいて選択する。なお、アプリケーション命令コードの読み出しを実施する場合は、コマンド用のセレクタ(1232b)は、信号線(CD1110a)から入力されたコマンド(CMD)信号を選択し、信号(1232b1)として出力する。このとき、セレクタ(1232b)のうちデータ(DAT)信号用のセレクタ(1232b)は、データ(DAT)信号をeMMC(1300a)に出力する必要がないため、その制御は不要である。

【0043】

セレクタ(1232c)は、バススイッチ制御信号(1240a5)、またはセレクタ(1232f)の出力のいずれかをバススイッチ制御信号(1240a4)に基づいて選択する。なお、アプリケーション命令コードの読み出しを実施する場合は、セレクタ(1232c)は、バススイッチ制御信号(1240a5)を選択し、I/O方向制御信号(1232c1)として出力する。このとき、コマンド(CMD)信号のI/O方向制御信号(1232c1)はI/O回路(1250a)を出力方向に制御する一方、データ(DAT)信号のI/O方向制御信号(1232c1)はI/O回路(1250a)を入力方向にそれぞれ制御する。その結果、I/O回路(1250a)は、セレクタ(1232b)において選択し、出力されたコマンド(CMD)信号(1232b1)を信号線(CD1200a)に出力する。

【0044】

セレクタ(1232d)は、バス変換・制御回路で生成された信号(1220a1)、またはバススイッチ制御信号(1240a3)のいずれかをバススイッチ制御信号(1240a6)に基づいて選択する。なお、アプリケーション命令コードの読み出しを実施する場合は、セレクタ(1232d)はバススイッチ制御信号(1240a3)を選択し、出力信号(1232d1)として出力する。

【0045】

セレクタ(1232e)は、カードホストI/F(1210a)で生成されたクロック(S1210b)、またはACPU(1100)から入力されたクロック(CK1110a)をインバータ(1233a)で反転した信号のいずれかをセレクタ(1232d)の出力信号(1232d1)に基づいて選択する。なお、アプリケーション命令コードの読み出しを実施する場合は、セレクタ(1232e)はクロック(CK1110a)をインバータ(1233a)で反転した信号を選択し、クロック信号線(CK1200a)に出力する。

【0046】

セレクタ(1232g)は、バス変換・制御回路で生成された信号(1220a1)、またはバススイッチ制御信号(1240a8)のいずれかをバススイッチ制御信号(1240a7)に基づいて選択する。なお、セレクタ(1232g)はアプリケーション命令コードの読み出しを実施する場合は、バススイッチ制御信号(1240a8)を選択し、信号(1232g1)として出力する。

【0047】

セレクタ(1232h)のうち、データ(DAT)信号用のセレクタ(1232h)は、eMMC(1300a)から、バススイッチ(1230a)、カードホストI/F(1210a)及びバス変換・制御回路(1220)を経て出力されたデータ(DAT)信号(1221)、またはeMMC(1300a)からバススイッチ(1230a)のレジスタ(1231c、1231d)を経て出力されたデータ(DAT)信号(1231d1)のいずれかをセレクタ(1232g)の出力信号(1232g1)に基づいて選択する。なお、アプリケーション命令コードの読み出しを実施する場合は、セレクタ(1232h)はデータ(DAT)信号(1231d1)を選択し、信号(1232h1)として出力する。このとき、コマンド(CMD)信号用のセレクタ(1232h)は、コマンド(CMD)信号をACPU(1100)に出力する必要がないので、その制御は不要である。

【0048】

セレクタ(1232i)は、バス変換・制御回路(1220)からインバータ(1234a)を介して出力された信号(1234a1)、またはバススイッチ制御信号(1240a9)のいずれかをバススイッチ制御信号(1240a10)に基づいて選択する。なお、アプリケーション命令コードの読み出しを実施する場合は、セレクタ(1232i)はバススイッチ制御信号(1240a9)を選択し、信号(1232i1)として出力する。このとき、データ(DAT)信号のI/O方向制御信号(1232i1)はI/O回路(1250b)を出力方向に制御する一方、コマンド(CMD)信号のI/O方向制御信号(1232i1)はI/O回路(1250b)を入力方向にそれぞれ制御する。その結果、I/O回路(1250b)は、セレクタ(1232h)において選択し、出力されたデータ(DAT)信号(1232h1)を信号線(CD1110a)に出力する。

【0049】

次に、第3のステップであるACPU(1100)のコマンド(CMD)の発行からeMMC(1300a)への到達までについて、図2を用いて、より具体的に説明する。

【0050】

ACPU(1100)は、内部のコマンド送信部からeMMC(1300a)に対して予め決められたカードバス規格に準拠したアプリケーション命令コードを読み出すためのコマンド(CMD)を信号線(CB1110)を介して発行する。ここで、アプリケーション命令コードの読み出しの場合は、コマンド(CMD)信号用のI/O回路(1250b)は入力方向に制御されているため、コマンド(CMD)信号はカードホストLSI(1200)に入力される。そして、この入力されたコマンド(CMD)信号は、レジスタ(1231a,1231b)、及びセレクタ(1232b)を経てI/O回路(1250a)に入力される。ここで、アプリケーション命令コードの読み出しの場合は、コマンド(CMD)信号用のI/O回路(1250a)は出力方向に制御されているため、コマンド(CMD)信号は信号線(CD1200a)を介してeMMC(1300a)に出力される。

【0051】

次に、第4のステップであるeMMC(1300a)のアプリケーション命令コードの出力からACPU(1100)への到達までについて、図2を用いて、より具体的に説明する。

【0052】

コマンド(CMD)信号がeMMC(1300a)に入力されると、eMMC規格に従い、eMMC(1300a)からアプリケーション命令コードが信号線(CD1200a)を介して出力される。ここで、アプリケーション命令コードの読み出しの場合は、データ(DAT)信号用のI/O回路(1250a)は入力方向に制御されているため、データ(DAT)信号はカードホストLSI(1200)に入力される。そして、この入力されたデータ(DAT)信号は、レジスタ(1231c,1231d)及び、セレクタ(1232h)を経てI/O回路(1250b)に入力される。ここで、アプリケーション命令コードの読み出しの場合は、データ(DAT)信号用のI/O回路(1250b)は出力方向に制御されているため、データ(DAT)信号は信号線(CD1110a)を介してACPU(1100)に出力される。

【0053】

次に、第5のステップ及び第6のステップであるアプリケーション命令コードの受信完了からACPU(1100)とeMMC(1300a)との間がインターフェース部内のカードホストI/F(1210a,1210b,1210c)を介して接続されるまでについて、図2を用いて、より具体的に説明する。

【0054】

ACPU(1100)は、アプリケーション命令コードの受信が完了すると、外部信号(1101)をLowレベルに制御する。そして、boot検出回路(1240)は、外部信号(1101)がLowレベルに制御されたことを検出すると、バススイッチ制御信号(1240a)を出力する。

【0055】

このとき、バススイッチ制御信号(1240a)を受けて、各セレクタ(1232a〜1232i)は下記のように制御される。

【0056】

セレクタ(1232a)は、バススイッチ制御信号(1240a2)に基づいて、バス変換・制御回路の出力信号(1220a1)を選択し、信号(1232a1)として出力する。

【0057】

セレクタ(1232b)は、セレクタ(1232a)から出力された信号(1232a1)に基づいて、カードホストI/F(1210a)から出力された信号(S1210d)を選択し、信号(1232b1)として出力する。

【0058】

セレクタ(1232c)は、バススイッチ制御信号(1240a4)に基づいて、セレクタ(1232f)から出力された信号(1232f1)を選択し、信号(1232c1)として出力する。

【0059】

セレクタ(1232d)は、バススイッチ制御信号(1240a6)に基づいて、バス変換・制御回路(1220)から出力された信号(1220a1)を選択し、信号(1232d1)として出力する。

【0060】

セレクタ(1232e)は、セレクタ(1232d)から出力された信号(1232d1)に基づいて、カードホストI/F(1210a)から出力されたクロック(S1210b)を選択し、クロック信号線(CK1200a)に出力する。

【0061】

セレクタ(1232f)は、バス変換・制御回路(1220)から出力された信号(1220a1)に基づいて、カードホストI/F(1210a)から出力された信号(S1210a)を選択し、信号(1232f1)として出力する。

【0062】

セレクタ(1232g)は、バススイッチ制御信号(1240a7)に基づいて、バス変換・制御回路から出力された信号(1220a1)を選択し、信号(1232g1)として出力する。

【0063】

セレクタ(1232h)は、セレクタ(1232g)から出力された信号(1232g1)に基づいて、カードホストI/F(1210a)から出力され、レジスタバス(RB1220)及びバス変換・制御回路(1220)を経た信号(1221)を選択し、信号(1232h1)として出力する。

【0064】

セレクタ(1232i)は、バススイッチ制御信号(1240a10)に基づいて、カードホストI/F(1210a)から出力され、レジスタバス(RB1220)、バス変換・制御回路(1220)、及びインバータ(1234a)を経た信号(1234a1)が選択を選択し、信号(1232i1)として出力する。

【0065】

そして、これらの各セレクタ(1232a〜1232i)の制御後、ACPU(1100)は、信号線(CD1110a)にコマンド(CMD)を出力することによって、カードホストLSI(1200)内部のカードホストI/F(1210a)にコマンド(CMD)がバッファリングされ、eMMC(1300a)などのカードホストLSI(1200)に接続された複数のデバイスに対して並列に、読み出し、書込み及び消去といったアクセスを開始する。

【0066】

このように本実施形態によると、ACPU(1100)とカードホストLSI(1200)とeMMC(1300a,1300b,1300c)とが、予め決められたカードバス仕様で接続され、ACPU(1100)からeMMC(1300a,1300b,1300c)に対して並列にアクセスできるセット機器(1000)において、システム起動時のアプリケーション命令コードの読み出す処理においてカードホストLSI(1200)のI/O回路(1250a,1250b)の方向を設定するために、レジスタ設定やコマンド送信を実施する必要がなく、システム起動の高速化が実現できる。また、レジスタ設定やコマンド送信をするために、予め決められたカードバス規格に準拠していないコマンド(CMD)を設計する必要が無い。

【0067】

なお、バススイッチ(1230a)にあるフリップフロップ(1231a,1231b,1231c,1231d)はあっても良いし、無くても良い。

【0068】

また、バススイッチ(1230a)にあるインバータ(1233a)は、クロックデューティー比調整のためにあっても良いし、無くても良い。

【0069】

また、図2のバススイッチ(1230a)にあるセレクタなどは、図2のような個別の実装に限定されない。例えば、同じ論理値になるものは同一信号線にするといった論理圧縮をして実装しても良い。

【0070】

また、アプリケーション命令コードの読み出しを実施するためにHighレベルに制御する信号線(1101)は、図2のようなACPU(1100)から出力する形に限定されない。例えば、ACPU(1100)から信号は出力せずに、予め決められた時間だけHighレベルに制御されるような構成であっても良い。また、予め決められた時間だけ、Highレベルに制御する手段は、カウンタ回路であっても良いし、容量素子と抵抗素子から構成される時定数回路のようなものであっても良い。

【0071】

また、アプリケーション命令コードの読み出し要求をACPU(1100)からカードホストLSI(1200)に伝える手段は、外部信号(1101)の代わりに、コマンド(CMD)信号線(CD1110a)や、クロック信号線(CK1110a)を使用しても良い。

【0072】

また、アプリケーション命令コードの読み出し要求をコマンド(CMD)信号線(CD1110a)や、クロック信号線(CK1110a)を使用してカードホストLSI(1200)に伝える際、図3に示すように、コマンド(CD1110a)がHighレベルであり、かつ、アプリケーション命令コードの読み出しのためのコマンドを発行する前の期間(3002)において、クロック(CK1110a)のエッジ数をカウントし、予め決められたカウント数より少なければ、アプリケーション命令コードの読み出し要求があると判断する一方、予め決められたカウント数より多ければ、アプリケーション命令コードの読み出し要求がないと判断するものとしても良い。

【0073】

また、アプリケーション命令コードの読み出しを終了するためにLowレベルに制御する信号線(1101)は、図2のように、ACPU(1100)から出力されても良いし、ACPU(1100)から出力されず、予め決められた時間が経過すると自動でLowレベルに制御されるような構成であっても良い。

【0074】

また、アプリケーション命令コードの読み出しの終了をACPU(1100)からカードホストLSI(1200)に伝える手段は、信号線(1101)の代わりに、コマンド(CMD)信号線(CD1110a)と、クロック信号線(CK1110a)を使用しても良い。

【0075】

また、アプリケーション命令コードの読み出しの終了は、図3に示すように、外部信号(1101)の代わりに、アプリケーション命令コードの読み出し終了のとき(3004)において、コマンド(CD1110a)がHighレベルになることで判断するものとしても良い。

【0076】

また、上記はシステムの起動時に限定されるものではない。

【0077】

また、eMMCの代わりに、SDやeSD、MMCなどのメモリカードを用いてもよい。

【0078】

また、アプリケーション命令コードをACPU(1100)に転送する際、セット機器(1000)の起動時に、外部信号(1101)をLowに制御して、アプリケーション命令コードの読出しを終了する際に、外部信号(1101)をHighレベルに制御しても良い。

【産業上の利用可能性】

【0079】

本発明では、カードバス構成を採用するシステム初期化時のプログラムリード処理を高速化できるので、より早いシステムの起動に有用である。

【符号の説明】

【0080】

1000 セット機器

1100 メインマイコンLSI(マイコン)

1110,1210a,1210b,1210c カードホストI/F

1200 カードホストLSI

1211 データバッファ

1220 バス変換・制御回路

1230a,1230b,1230c バススイッチ(入出力制御部)

1240 boot回路

1240a,1240b,1240c バススイッチ制御信号

1250a,1250b I/O回路(入力部、出力部)

1300a,1300b,1300c eMMC(メモリカード)

【特許請求の範囲】

【請求項1】

マイコンと、

前記マイコンに使用されるアプリケーション命令コードを保持した一つ以上のメモリカードと、

前記マイコンと前記メモリカードを接続するデータパスと、

前記アプリケーション命令コードの読み出し要求を検出し、前記データパスを制御する信号を出力するboot検出回路とを備えている

ことを特徴とするセット機器。

【請求項2】

予め決められたカードバス仕様のコマンドを用いて、メモリカードに保持されたアプリケーション命令コードを読み出すセット機器であって、

前記予め決められたカードバス仕様のコマンドを送信する第1のコマンド部と、前記アプリケーション命令コード等のデータを受信する第1のデータ部とを備えているカードインターフェースを持つマイコンと、

I/O回路とインターフェース部とboot検出回路とを備えているカードホストLSIと、

前記予め決められたカードバス仕様のコマンドを受信するコマンド受信部と、前記アプリケーション命令コードを送信するデータ送信部とを備えているカードインターフェースと、アプリケーション命令コードを保持するデータ保持部とを備えているメモリカードとを備えており、

前記I/O回路は、前記コマンド及び前記データを入力する入力部と、前記コマンド及び前記データを出力する出力部と、入出力方向を切替える入出力制御部とを備えており、

前記インターフェース部は、前記コマンド及び前記データをバッファリングするデータバッファ部と、前記I/O回路の前記入出力制御部を制御する入出力制御信号出力部を備えており、

前記boot検出回路は、前記アプリケーション命令コードの読み出し要求を検出し、前記I/O回路の前記入出力制御部を制御する信号を出力する

ことを特徴とするセット機器。

【請求項3】

請求項2記載のセット機器を制御する制御方法であって、

前記セット機器の起動時に、前記マイコンが前記カードホストLSIに、前記アプリケーション命令コードの読み出し要求を通知する第1のステップと、

前記boot検出回路が、前記アプリケーション命令コードの読み出し要求を検出し、前記I/O回路の前記入出力制御部を制御して入出力方向を固定し、前記マイコンと前記メモリカードとの間を、前記データバッファ部を経由せずに接続する第2のステップと、

前記マイコンの前記第1のコマンド部から、前記アプリケーション命令コードの読み出しコマンドを発行し、前記メモリカードの前記第2のコマンド部が、前記読み出しコマンドを受信する第3のステップと、

前記メモリカードの前記第2のデータ部から、前記アプリケーション命令コードが出力され、前記マイコンの前記第1のデータ部が、前記アプリケーション命令コードを受信する第4のステップと、

前記マイコンが、前記アプリケーション命令コードの読み出し要求を解除する第5のステップと、

前記boot検出回路が、前記アプリケーション命令コードの読み出し要求の解除を検出し、前記インターフェース部の前記入出力制御信号出力部により、前記I/O回路の前記入出力制御部を制御し、前記マイコンと前記メモリカードとの間を、前記データバッファ部を経由して接続する第6のステップとを有する

ことを特徴とするセット機器の制御方法。

【請求項1】

マイコンと、

前記マイコンに使用されるアプリケーション命令コードを保持した一つ以上のメモリカードと、

前記マイコンと前記メモリカードを接続するデータパスと、

前記アプリケーション命令コードの読み出し要求を検出し、前記データパスを制御する信号を出力するboot検出回路とを備えている

ことを特徴とするセット機器。

【請求項2】

予め決められたカードバス仕様のコマンドを用いて、メモリカードに保持されたアプリケーション命令コードを読み出すセット機器であって、

前記予め決められたカードバス仕様のコマンドを送信する第1のコマンド部と、前記アプリケーション命令コード等のデータを受信する第1のデータ部とを備えているカードインターフェースを持つマイコンと、

I/O回路とインターフェース部とboot検出回路とを備えているカードホストLSIと、

前記予め決められたカードバス仕様のコマンドを受信するコマンド受信部と、前記アプリケーション命令コードを送信するデータ送信部とを備えているカードインターフェースと、アプリケーション命令コードを保持するデータ保持部とを備えているメモリカードとを備えており、

前記I/O回路は、前記コマンド及び前記データを入力する入力部と、前記コマンド及び前記データを出力する出力部と、入出力方向を切替える入出力制御部とを備えており、

前記インターフェース部は、前記コマンド及び前記データをバッファリングするデータバッファ部と、前記I/O回路の前記入出力制御部を制御する入出力制御信号出力部を備えており、

前記boot検出回路は、前記アプリケーション命令コードの読み出し要求を検出し、前記I/O回路の前記入出力制御部を制御する信号を出力する

ことを特徴とするセット機器。

【請求項3】

請求項2記載のセット機器を制御する制御方法であって、

前記セット機器の起動時に、前記マイコンが前記カードホストLSIに、前記アプリケーション命令コードの読み出し要求を通知する第1のステップと、

前記boot検出回路が、前記アプリケーション命令コードの読み出し要求を検出し、前記I/O回路の前記入出力制御部を制御して入出力方向を固定し、前記マイコンと前記メモリカードとの間を、前記データバッファ部を経由せずに接続する第2のステップと、

前記マイコンの前記第1のコマンド部から、前記アプリケーション命令コードの読み出しコマンドを発行し、前記メモリカードの前記第2のコマンド部が、前記読み出しコマンドを受信する第3のステップと、

前記メモリカードの前記第2のデータ部から、前記アプリケーション命令コードが出力され、前記マイコンの前記第1のデータ部が、前記アプリケーション命令コードを受信する第4のステップと、

前記マイコンが、前記アプリケーション命令コードの読み出し要求を解除する第5のステップと、

前記boot検出回路が、前記アプリケーション命令コードの読み出し要求の解除を検出し、前記インターフェース部の前記入出力制御信号出力部により、前記I/O回路の前記入出力制御部を制御し、前記マイコンと前記メモリカードとの間を、前記データバッファ部を経由して接続する第6のステップとを有する

ことを特徴とするセット機器の制御方法。

【図1】

【図2】

【図3】

【図2】

【図3】

【公開番号】特開2012−174054(P2012−174054A)

【公開日】平成24年9月10日(2012.9.10)

【国際特許分類】

【出願番号】特願2011−36190(P2011−36190)

【出願日】平成23年2月22日(2011.2.22)

【出願人】(000005821)パナソニック株式会社 (73,050)

【Fターム(参考)】

【公開日】平成24年9月10日(2012.9.10)

【国際特許分類】

【出願日】平成23年2月22日(2011.2.22)

【出願人】(000005821)パナソニック株式会社 (73,050)

【Fターム(参考)】

[ Back to top ]