セラミック体の製造方法

【課題】内部に導電体を含むセラミック体において導電体とセラミック体の間の空隙への水分の浸入をより効果的に防止することが可能なセラミック体の製造方法を提供する。

【解決手段】内部電極層11a、11c、11eの左側の端面がセラミック積層体10の左側の表面で露出しておらず、かつ、内部電極層11a、11c、11eの右側の端面がセラミック積層体10の右側の表面で露出しているセラミック積層体10を、酸化物ゾルを含む液体104に浸漬し、セラミック積層体10の左側の表面から距離を隔てた位置に対向電極102を配置し、対向電極102と内部電極層11a、11c、11eとの間に電界を印加することによって、電気泳動法により内部電極層11a、11c、11eとセラミック積層体10の左側の表面の間の領域10g、10h、10i内の空隙に酸化物ゾルを浸入させた後、熱処理することにより、空隙を酸化物で充填する。

【解決手段】内部電極層11a、11c、11eの左側の端面がセラミック積層体10の左側の表面で露出しておらず、かつ、内部電極層11a、11c、11eの右側の端面がセラミック積層体10の右側の表面で露出しているセラミック積層体10を、酸化物ゾルを含む液体104に浸漬し、セラミック積層体10の左側の表面から距離を隔てた位置に対向電極102を配置し、対向電極102と内部電極層11a、11c、11eとの間に電界を印加することによって、電気泳動法により内部電極層11a、11c、11eとセラミック積層体10の左側の表面の間の領域10g、10h、10i内の空隙に酸化物ゾルを浸入させた後、熱処理することにより、空隙を酸化物で充填する。

【発明の詳細な説明】

【技術分野】

【0001】

この発明は、一般的にはセラミック体の製造方法に関し、特定的には、内部に導電体を含むセラミック体の製造方法、例えば、積層セラミックコンデンサ等のチップ型のセラミック電子部品の製造方法に関するものである。

【背景技術】

【0002】

従来から、セラミック体の一例である積層セラミックコンデンサは、以下のようにして製造される。

【0003】

まず、セラミック原料粉末を含むスラリーを準備する。このスラリーをシートに成形し、セラミックグリーンシートを作製する。セラミックグリーンシートの表面上には、内部電極層の原材料である導電性ペーストを所定のパターンに従って塗布する。この導電性ペーストは、金属粉末、溶剤およびワニスから構成される。

【0004】

次に、導電性ペーストが塗布された複数のセラミックグリーンシートを積層し、熱圧着することにより、一体化された生の積層体を作製する。この生の積層体を焼成することにより、セラミック積層体を作製する。このセラミック積層体の内部には、複数の内部電極層が形成されている。内部電極層の一部の端面は、セラミック積層体の外部表面に露出している。

【0005】

次に、内部電極層の一部の端面が露出したセラミック積層体の外表面の上に、外部電極層の原材料である導電性ペーストを塗布した後、焼き付ける。この導電性ペーストは、金属粉末、ガラスフリット、溶剤およびワニスから構成される。これにより、特定の内部電極層に電気的に接続されるように、セラミック積層体の外表面の上に外部電極層が形成される。

【0006】

最後に、はんだ付け性能を高めるために、必要に応じて外部電極層の表面にめっき層を形成する。

【0007】

上記の製造工程において、たとえば、外部電極層の表面にめっき層を形成する場合に、外部電極層に存在する微細な空隙から水分が浸入する。また、セラミック体の一例である積層セラミックコンデンサを高湿環境下で使用した場合にも、外部電極層に存在する微細な空隙から水分が浸入する。このように外部電極層から浸入した水分が、セラミック積層体の内部に存在する内部電極層とセラミック層との間の界面の微細な空隙に水分が到達することにより、絶縁抵抗の低下を引き起こすという問題がある。

【0008】

そこで、たとえば、特開2001−102247号公報(以下、特許文献1という)では、上記の問題を解決するためのチップ型電子部品の構成が提案されている。特許文献1で提案されたチップ型電子部品は、矩形状セラミック基体の両端部に厚膜下地導体層、表面めっき層からなる外部端子電極を形成してなるチップ型電子部品において、外部端子電極に、撥水性を有する部材を含浸させている。このようにすることにより、チップ型電子部品を湿度の高い場所に放置した場合も、外部端子電極のポーラス部分に水分が浸入することを抑制している。その結果、水分が表面めっき層、厚膜下地導体層を通って、電子部品素体に到達するのが防止されている。

【0009】

また、たとえば、特開平2−301113号公報(以下、特許文献2という)では、上記の問題を解決するための積層セラミック電子部品の構成とその製造方法が提案されている。特許文献2で提案された積層セラミック電子部品は、セラミック積層体内または外部電極内の隙間、ボア、ピンホール等の欠陥を無機酸化物で埋めたものである。また、特許文献2で提案された積層セラミック電子部品の製造方法は、セラミック積層体またはセラミック積層体に外部電極を形成した後、これを金属アルコキシド等の有機金属溶液中に浸漬してセラミック積層体内または外部電極内の隙間、ボア、ピンホール等の欠陥内に有機金属を含浸させた後、加熱することにより有機金属を無機酸化物に分解するものである。このようにすることにより、水分が上記の隙間やボアに浸入することを抑制している。

【0010】

なお、たとえば、特表2003−508627号公報(以下、特許文献3という)では、セラミックコーティングの表面の空隙をゾル−ゲル電気泳動堆積を用いて封止する方法が記載されている。この場合、一例としてカソードが金属支持体上の多孔質セラミックコーティングであり、アノードとしては白金が用いられ、カソードとアノードとの間に電界が印加されることにより電気泳動が行われる。

【先行技術文献】

【特許文献】

【0011】

【特許文献1】特開2001−102247号公報

【特許文献2】特開平2−301113号公報

【特許文献3】特表2003−508627号公報

【発明の概要】

【発明が解決しようとする課題】

【0012】

特許文献1に記載されたチップ型電子部品の構成では、外部端子電極に撥水性の物質が残留する。このため、後工程でめっき層を形成する場合に、外部端子電極の表面においてめっき析出不良が発生しやすくなり、はんだ付けでチップ型電子部品を基板等に実装する場合に不良が発生する場合がある。

【0013】

また、特許文献1に記載されたチップ型電子部品の構成では、外部端子電極に残留する撥水性物質の量が少なければ、電子部品素体へ水分が浸入するのを抑制する効果が得られず、外部端子電極に残留する撥水性物質の量が多ければ、めっき析出不良が発生する。このため、外部端子電極に、撥水性を有する部材を含浸させるための処理条件を制御することが困難である。

【0014】

一方、特許文献2では、セラミック積層体を金属アルコキシド等の有機金属溶液中に浸漬してセラミック積層体内または外部電極内の隙間等の欠陥内に無機酸化物を埋め込んでいる。しかし、この方法では、ナノレベルの微細な空隙にまで無機酸化物を充填することができないので、水分が空隙に浸入するのを抑制する効果が不十分である。

【0015】

なお、特許文献3では、金属支持体上の多孔質セラミックコーティングの表面の空隙をゾル−ゲル電気泳動堆積を用いて封止する方法が開示されているだけであり、内部に導電体を含むセラミック体を製造する方法については何ら示唆されていない。

【0016】

そこで、この発明の目的は、内部に導電体を含むセラミック体において導電体とセラミック体の間の空隙への水分の浸入をより効果的に防止することが可能なセラミック体の製造方法を提供することである。

【課題を解決するための手段】

【0017】

この発明に従ったセラミック体の製造方法は、内部に導電体を含むセラミック体の製造方法であって、導電体の一方の端面がセラミック体の第1の表面から離れた内部にあって第1の表面で露出しておらず、かつ、導電体の他方の端面がセラミック体の第1の表面と異なる第2の表面で露出しているセラミック体を対象とするものであり、以下のステップを備える。

【0018】

(a)酸化物ゾルまたは酸化物粒子を含む液体にセラミック体を浸漬するステップ。

【0019】

(b)上記の液体中においてセラミック体の第1の表面に対向するように第1の表面から距離を隔てた位置に対向電極を配置し、対向電極と導電体との間に電界を印加することによって、電気泳動法により導電体とセラミック体の第1の表面の間の領域内の空隙に酸化物ゾルまたは酸化物粒子を浸入させるステップ。

【0020】

(c)導電体とセラミック体の第1の表面の間の領域内の空隙に浸入した酸化物ゾルまたは酸化物粒子を熱処理することにより、導電体とセラミック体の第1の表面の間の領域内の空隙を酸化物で充填するステップ。

【0021】

この発明のセラミック体の製造方法において採用される電気泳動法では、セラミック体の内部に存在する導電体がカソードとして用いられ、セラミック体の外部に存在する対向電極がアノードとして用いられ、導電体と対向電極との間に電界が印加される。このため、電界強度を相対的に高くすることができるので、電気泳動法により、酸化物ゾルまたは酸化物粒子を導電体とセラミック体の第1の表面の間の領域内に存在するナノレベルの微細な空隙にまで浸入させることができる。

【0022】

そして、導電体とセラミック体の間の第1の表面の間の領域内の空隙に浸入した酸化物ゾルまたは酸化物粒子を熱処理することにより、導電体とセラミック体の第1の表面の間の領域内に存在するナノレベルの微細な空隙にまで酸化物を充填させることができる。

【0023】

したがって、内部に導電体を含むセラミック体において導電体とセラミック体の間の空隙への水分の浸入をより効果的に防止することが可能になる。

【0024】

この発明のセラミック体の製造方法において、セラミック体が、積層された複数のセラミック層と、各々が複数のセラミック層の間に介在した複数の導電体層とを含むセラミック積層体であることが好ましい。

【0025】

この場合、セラミック積層体からなるセラミック電子部品の製造方法に本発明の製造方法を適用することができる。たとえば、本発明の製造方法を適用すると、セラミック積層体を含む電子部品において、外部電極層を形成する前に、酸化物を、導電体とセラミック体の第1の表面の間の領域内に存在するナノレベルの微細な空隙にまで充填させることによって、導電体とセラミック体の間の空隙への水分の浸入をより効果的に防止することが可能になる。したがって、外部電極層の表面にめっき析出を阻害する物質が残留することがない。これにより、後工程でめっき層を形成する場合に、外部端子電極の表面においてめっき析出不良が発生することもなく、はんだ付けでチップ型電子部品を基板等に実装する場合に不良が発生することもない。

【0026】

なお、セラミック積層体からなるセラミック電子部品の製造方法に本発明の製造方法を適用する場合、既存の製造プロセスに、上記の(a)と(b)のステップを追加するだけでよい。この場合、上記の(c)のステップは、外部電極層の焼成時に行われる。これにより、大きな製造コストの増大を伴わずに、導電体とセラミック体の間の空隙への水分の浸入をより効果的に防止することが可能になる。

【0027】

セラミック体が上記のセラミック積層体である場合、酸化物が、Si、Ti、Mg、Mn、BaおよびSrからなる群より選ばれた少なくとも一種の元素を含むことが好ましい。

【0028】

この場合、セラミック積層体からなるセラミック電子部品において、たとえば、セラミック体の主成分がBa1−xSrxTiO3(0≦x≦1)、一例としてBaTiO3であり、副成分または添加物がSiO2、MgO、MnOであるので、上記の元素を含む酸化物が空隙を充填してもセラミック電子部品の特性に影響を与えることがない。

【0029】

また、セラミック体が上記のセラミック積層体である場合、酸化物ゾルまたは酸化物粒子を浸入させるステップにおいて、印加される電界は、50V/m以上50kV/m以下であることが好ましい。

【0030】

この範囲内の電界をセラミック積層体に印加することにより、電気泳動法によって、酸化物ゾルまたは酸化物粒子を導電体とセラミック積層体の第1の表面の間の領域内に存在するナノレベルの微細な空隙にまで十分に浸入させることができる。

【発明の効果】

【0031】

以上のようにこの発明によれば、内部に導電体を含むセラミック体において導電体とセラミック体の間の空隙への水分の浸入をより効果的に防止することが可能になる。これにより、たとえば、チップ型の積層セラミックコンデンサ等の積層セラミック電子部品の製造方法に本発明を適用することによって、絶縁抵抗の低下を防止することができ、積層セラミック電子部品の信頼性を向上させることができる。

【図面の簡単な説明】

【0032】

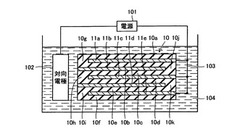

【図1】この発明の一つの実施の形態として、セラミック体の一例である積層セラミックコンデンサの第1の製造工程を示す概略的な断面図である。

【図2】この発明の一つの実施の形態として、セラミック体の一例である積層セラミックコンデンサの第2の製造工程を示す概略的な断面図である。

【発明を実施するための形態】

【0033】

本発明のセラミック体の製造方法の一つの実施の形態である積層セラミックコンデンサの製造方法について説明する。

【0034】

まず、セラミック原料粉末を含むスラリーを準備する。このスラリーをシートに成形し、セラミックグリーンシートを作製する。セラミックグリーンシートの表面上には、内部電極層の原材料である導電性ペーストを所定のパターンに従って塗布する。この導電性ペーストは、金属粉末、溶剤およびワニスから構成される。

【0035】

次に、導電性ペーストが塗布された複数のセラミックグリーンシートを積層し、熱圧着することにより、一体化された生の積層体を作製する。この生の積層体を焼成することにより、図1に示されるような、セラミック体としてのセラミック積層体10を作製する。このようにして作製された直方体状のセラミック積層体10は、複数の(図では一例として6つの)積層されたセラミック層10a、10b、10c、10d、10e、10fと、複数のセラミック層10a、10b、10c、10d、10e、10f間の界面に沿って形成された複数の(図では一例として5つの)内部電極層11a、11b、11c、11d、11eとを備えている。このようにして、セラミック積層体10の内部には、内部の導電体として複数の内部電極層11a〜11eが形成されている。

【0036】

図1では、内部電極層11a、11c、11eの左側の端面が、セラミック積層体10の左側の端面から間隔(または領域)10g、10h、10iだけ離れた内部にあって左側の端面で露出しておらず、内部電極層11a、11c、11eの右側の端面が、セラミック積層体10の左側の端面と異なる右側の端面で露出している。内部電極層11b、11dの右側の端面が、セラミック積層体10の右側の端面から間隔(または領域)10j、10kだけ離れた内部にあって右側の端面で露出しておらず、内部電極層11b、11dの左側の端面が、セラミック積層体10の右側の端面と異なる左側の端面で露出している。このようにして、内部電極層11a〜11eの左側または右側の端面がセラミック積層体10の外表面にまで到達するように形成されている。セラミック積層体10の左側の端面にまで引き出される内部電極層11b、11dと右側の端面にまで引き出される内部電極層11a、11c、11eとが、セラミック積層体10の内部において、誘電体としてのセラミック層10a、10b、10c、10d、10e、10fの各々を介して静電容量を取得できるように交互に配置されている。

【0037】

なお、セラミック層10a〜10fは、たとえば、BaTiO3系化合物を含むセラミック材料からなる。内部電極層11a〜11eの導電材料は、コスト低減の点から、ニッケルまたはニッケル合金であることが好ましい。

【0038】

次に、上述のようにして作製されたセラミック積層体10を、図1に示すように、酸化物ゾルまたは酸化物ナノ粒子を含む液体、たとえば、BaTiO3、SiO2等の酸化物のゾルまたはナノ粒子を含むエタノール等の液体104に浸漬する。

【0039】

その後、図1に示すように、液体104中においてセラミック積層体10の左側の表面に対向するように左側の表面から距離を隔てた位置に、たとえば、白金(Pt)線等からなる対向電極102を配置する。セラミック積層体10の右側の表面で露出している内部電極層11a、11c、11eの右側の端面のそれぞれを配線103で接続する。そして、対向電極102をアノードとして用い、内部電極層11a、11c、11eをカソードとして用いて、電源101によって、対向電極102と内部電極層11a、11c、11eの各々との間に電界を印加することによって、電気泳動法により、内部電極層11a、11c、11eの各々とセラミック積層体10の左側の表面の間の領域10g、10h、10i内に存在する空隙に酸化物のゾルまたはナノ粒子を浸入させる。

【0040】

上記の電気泳動法による処理を終えた後、同様にして、液体104中においてセラミック積層体10の右側の表面に対向するように右側の表面から距離を隔てた位置に対向電極102を配置する。セラミック積層体10の左側の表面で露出している内部電極層11b、11dの左側の端面のそれぞれを配線103で接続する。そして、対向電極102をアノードとして用い、内部電極層11b、11dをカソードとして用いて、電源101によって、対向電極102と内部電極層11b、11dの各々との間に電界を印加することによって、電気泳動法により、内部電極層11b、11dの各々とセラミック積層体10の右側の表面の間の領域10j、10k内に存在する空隙に酸化物のゾルまたはナノ粒子を浸入させる。

【0041】

その後、内部電極層11a〜11eの各々とセラミック積層体10の左側または右側の表面の間の領域10g〜10k内に存在する空隙に浸入した酸化物のゾルまたはナノ粒子を熱処理することにより、内部電極層11a〜11eの各々とセラミック積層体10の左側または右側の表面の間の領域10g〜10k内に存在する空隙を、たとえば、BaTiO3、SiO2等の酸化物で充填する。この熱処理工程は、以下で説明する外部電極層の形成工程で行われる。

【0042】

図2に示すように、内部電極層11の一部の端面が露出したセラミック積層体10の外表面の上に、外部電極層12の原材料である導電性ペーストを塗布した後、焼き付ける。この導電性ペーストは、金属粉末、ガラスフリット、溶剤およびワニスから構成される。これにより、特定の内部電極層11に電気的に接続されるように、セラミック積層体10の外表面の上に外部電極層12が形成される。この外部電極層12の形成工程においてセラミック積層体10が熱処理されるので、内部電極層11a〜11eの各々とセラミック積層体10の左側または右側の表面の間の領域10g〜10k内に存在する空隙が、たとえば、BaTiO3、SiO2等の酸化物で充填される。

【0043】

このようにして、前述した静電容量を取り出すために、セラミック積層体10の外表面上であって、端面上には、内部電極層11のいずれか特定のものに電気的に接続されるように、外部電極層12が形成される。外部電極層12に含まれる導電材料としては、内部電極層11の場合と同じ導電材料を用いることができ、さらに、銀、パラジウム、銀−パラジウム合金なども用いることができる。外部電極層12は、上記の金属または合金の粉末にガラスフリットを添加して得られた導電性ペーストを付与し、焼き付けることによって形成される。なお、上記の説明では外部電極層12として厚膜外部電極の例を示したが、外部電極層12は、厚膜外部電極に限定されず、スパッタリングによって形成される薄膜外部電極でもよく、めっきによって形成される電極でもよく、その他の形成方法による電極でもよい。

【0044】

最後に、はんだ付け性能を高めるために、必要に応じて外部電極層12の表面に第1と第2のめっき層13、14を形成する。このようにして、外部電極層12上には、必要に応じて、ニッケル、銅などからなる第1のめっき層13が形成され、さらにその上には、半田、錫などからなる第2のめっき層14が形成される。以上のようにして、積層セラミックコンデンサ1が製造される。

【0045】

上述したこの発明の一つの実施の形態である積層セラミックコンデンサ1の製造方法において採用される電気泳動法では、セラミック積層体10の内部に存在する内部電極層11a〜11eがカソードとして用いられ、セラミック積層体10の外部に存在する対向電極102がアノードとして用いられ、内部電極層11a〜11eと対向電極102との間に電界が印加される。このため、電界強度を相対的に高くすることができるので、電気泳動法により、酸化物ゾルまたは酸化物粒子を内部電極層11a〜11eとセラミック積層体10の表面の間の領域内に存在するナノレベルの微細な空隙にまで浸入させることができる。

【0046】

そして、内部電極層11a〜11eとセラミック積層体10の表面の間の領域内の空隙に浸入した酸化物ゾルまたは酸化物粒子を熱処理することにより、内部電極層11a〜11eとセラミック積層体10の表面の間の領域内に存在するナノレベルの微細な空隙にまで酸化物を充填させることができる。

【0047】

したがって、内部に導電体を含むセラミック積層体10において内部電極層11a〜11eとセラミック積層体10の間の空隙への水分の浸入をより効果的に防止することが可能になる。これにより、たとえば、チップ型の積層セラミックコンデンサ1等の積層セラミック電子部品の製造方法に本発明を適用することによって、絶縁抵抗の低下を防止することができ、積層セラミック電子部品の信頼性を向上させることができる。しかし、少なくとも、内部に導電体を含み、導電体の一方の端面がセラミック体の第1の表面から離れた内部にあって第1の表面で露出しておらず、かつ、導電体の他方の端面がセラミック体の第1の表面と異なる第2の表面で露出しているセラミック体の製造方法であれば、本発明の製造方法を適用することにより、導電体とセラミック体の間の空隙への水分の浸入を効果的に防止することが可能となる。たとえば、上記のセラミック体と導電体が膜や層等の形態で形成されていても、本発明の製造方法を適用することができる。

【0048】

上記の実施の形態では、セラミック積層体10からなるセラミック電子部品の一例として積層セラミックコンデンサ1の製造方法に本発明の製造方法を適用している。この場合、セラミック積層体10を含む積層セラミックコンデンサ1等の電子部品において、外部電極層12を形成する前に、酸化物を、内部電極層11a〜11eとセラミック積層体10の表面の間の領域内に存在するナノレベルの微細な空隙にまで充填させることによって、内部電極層11a〜11eとセラミック積層体10の間の空隙への水分の浸入をより効果的に防止することが可能になる。したがって、外部電極層12の表面にめっき析出を阻害する物質が残留することがない。これにより、後工程で第1のめっき層13や第2のめっき層14を形成する場合に、外部端子電極としての外部電極層12の表面においてめっき析出不良が発生することもなく、はんだ付けでチップ型電子部品を基板等に実装する場合に不良が発生することもない。

【0049】

なお、セラミック積層体10からなる積層セラミックコンデンサ1等のセラミック電子部品の製造方法に本発明の製造方法を適用する場合、既存の製造プロセスに、上記の浸漬ステップと電気泳動法によるステップを追加するだけでよい。この場合、上記の熱処理のステップは、外部電極層の焼成時に行われる。これにより、大きな製造コストの増大を伴わずに、内部電極層11a〜11eとセラミック積層体10の間の空隙への水分の浸入をより効果的に防止することが可能になる。

【0050】

また、上記の浸漬ステップにおいて用いられる液体に含まれるゾルまたはナノ粒子は、Si、Ti、Mg、Mn、BaおよびSrからなる群より選ばれた少なくとも一種の元素を含む酸化物からなるのが好ましい。この場合、セラミック積層体10からなる積層セラミックコンデンサ1等のセラミック電子部品において、たとえば、セラミック積層体10の主成分がBa1−xSrxTiO3(0≦x≦1)、一例としてBaTiO3であり、副成分または添加物がSiO2、MgO、MnOであるので、Si、Ti、Mg、Mn、BaおよびSrからなる群より選ばれた少なくとも一種の元素を含む酸化物が空隙を充填してもセラミック電子部品の特性に影響を与えることがない。

【0051】

さらに、セラミック積層体10からなる積層セラミックコンデンサ1等のセラミック電子部品の製造方法に本発明の製造方法を適用する場合、内部電極層11a〜11eとセラミック積層体10の間の空隙への水分の浸入をより効果的に防止することが可能になり、絶縁抵抗の低下を防止することができるので、積層セラミック電子部品におけるセラミック積層体10の設計、外部電極層12の設計、第1のめっき層13や第2のめっき層14の設計等において自由度を高めることができる。

【実施例】

【0052】

(実施例1)

本発明の実施例1として試料番号1〜6について、図1に示すように、ニッケルからなる多数の内部電極層11a〜11eが交互に両端面に露出した、積層セラミックコンデンサ1用の焼成後のセラミック積層体10(大きさ2.0mm×1.2mm×1.2mm)を各100個作製した。セラミック積層体10を構成する多数のセラミック層10a〜10fの組成は、主成分としてBaTiO3を含み、副成分として主成分100モル部に対して2モル部のDy、2モル部のMg、0.5モル部のMnを含む。多数のセラミック層10a〜10fの各々の厚みは0.8μmであり、多数の内部電極層11a〜11eの各々の厚みは0.6μmであった。

【0053】

次に、上述のようにして作製されたセラミック積層体10を、図1に示すように、平均粒径が15nmのBaTiO3ゾルをエタノール中に分散したBaTiO3ゾル分散溶液である液体104に浸漬した。BaTiO3ゾルは、酢酸バリウムとチタンアルコキシドを用いて作製した溶液を加水分解して作製した。

【0054】

その後、図1に示すように、液体104中においてセラミック積層体10の左側の表面に対向するように左側の表面から1cmの距離を隔てた位置に、白金(Pt)線からなる対向電極102を配置した。セラミック積層体10の右側の表面で露出している多数の内部電極層11a、11c、11eの右側の端面のそれぞれを配線103で接続した。そして、対向電極102をアノードとして用い、多数の内部電極層11a、11c、11eをカソードとして用いて、試料番号1〜6について、電源101によって、対向電極102と多数の内部電極層11a、11c、11eの各々との間に、表1に示す電界を印加して、表1に示す時間保持することによって、電気泳動法により、内部電極層11a、11c、11eの各々とセラミック積層体10の左側の表面の間の領域10g、10h、10i内に存在する空隙にBaTiO3ゾルを浸入させた。

【0055】

上記の処理を終えた後、同様にして、液体104中においてセラミック積層体10の右側の表面に対向するように右側の表面から1cmの距離を隔てた位置に対向電極102を配置した。セラミック積層体10の左側の表面で露出している多数の内部電極層11b、11dの左側の端面のそれぞれを配線103で接続した。そして、対向電極102をアノードとして用い、多数の内部電極層11b、11dをカソードとして用いて、試料番号1〜6について、電源101によって、対向電極102と多数の内部電極層11a、11c、11eの各々との間に、表1に示す電界を印加して、表1に示す時間保持することによって、電気泳動法により、内部電極層11b、11dの各々とセラミック積層体10の右側の表面の間の領域10j、10k内に存在する空隙にBaTiO3ゾルを浸入させた。

【0056】

なお、電気泳動法による酸化物ゾルの空隙への浸入量は電界の大きさに依存するので、電界の大きさを変更した場合には、試料番号1〜6についてその浸入量が等しくなるように印加時間を変化させた。

【0057】

電気泳動法による処理を終えた後、試料番号1〜6のセラミック積層体10を温度50℃で24時間、オーブン内で乾燥させた後、さらに温度100℃で1時間、乾燥させた。

【0058】

なお、比較のため、試料番号7〜8について、図1に示すように、ニッケルからなる多数の内部電極層11a〜11eが交互に両端面に露出した、積層セラミックコンデンサ1用の焼成後のセラミック積層体10(大きさ2.0mm×1.2mm×1.2mm)を各100個作製した。試料番号7のセラミック積層体10を、図1に示すように、平均粒径が15nmのBaTiO3ゾルをエタノール中に分散したBaTiO3ゾル分散溶液である液体104に浸漬して取り出し、温度50℃で24時間、オーブン内で乾燥させた後、さらに温度100℃で1時間、乾燥させた。試料番号8のセラミック積層体10については何も処理しなかった。

【0059】

以上のようにして得られた試料番号1〜8のセラミック積層体10の各々について、図2に示すように、内部電極層11の一部の端面が露出したセラミック積層体10の外表面の上に、外部電極層12の原材料である銅(Cu)ペーストをディップ法により塗布した後、温度800℃で焼き付けた。これにより、特定の内部電極層11に電気的に接続されるように、セラミック積層体10の外表面の上に外部電極層12が形成された。さらに電解めっき法により、外部電極層12の表面上に、ニッケル(Ni)からなる第1のめっき層13を形成し、さらにその上に、錫(Sn)からなる第2のめっき層14を形成した。以上のようにして、試料番号1〜8の積層セラミックコンデンサ1を作製した。なお、得られた試料番号1〜8の積層セラミックコンデンサ1は4.3Vの定格電圧を想定して作製されたものである。

【0060】

得られた試料番号1〜8の積層セラミックコンデンサ1について、温度85℃、相対湿度85%の条件下で、定格電圧の4倍の電圧を印加することによって、耐湿負荷試験を1000時間、5000時間行った。それぞれの耐湿負荷試験後の絶縁不良個数を調査した。積層セラミックコンデンサ1の絶縁抵抗値が1MΩ未満になると、絶縁不良であると判断した。調査結果を表1に示す。

【0061】

【表1】

【0062】

(実施例2)

本発明の実施例2として試料番号9〜14について、図1に示すように、ニッケルからなる多数の内部電極層11a〜11eが交互に両端面に露出した、積層セラミックコンデンサ1用の焼成後のセラミック積層体10(大きさ2.0mm×1.2mm×1.2mm)を各100個作製した。セラミック積層体10を構成する多数のセラミック層10a〜10fの組成は、主成分としてBaTiO3を含み、副成分として主成分100モル部に対して2モル部のDy、2モル部のMg、0.5モル部のMnを含む。多数のセラミック層10a〜10fの各々の厚みは0.8μmであり、多数の内部電極層11a〜11eの各々の厚みは0.6μmであった。

【0063】

次に、上述のようにして作製されたセラミック積層体10を、図1に示すように、平均粒径が50nmのSiO2ゾルをエタノール中に分散したSiO2ゾル分散溶液である液体104に浸漬した。SiO2ゾルは、シリカの金属アルコキシドであるテトラエトキシシラン(TEOS)を加水分解して作製した。

【0064】

その後、図1に示すように、液体104中においてセラミック積層体10の左側の表面に対向するように左側の表面から1cmの距離を隔てた位置に、白金(Pt)線からなる対向電極102を配置した。セラミック積層体10の右側の表面で露出している多数の内部電極層11a、11c、11eの右側の端面のそれぞれを配線103で接続した。そして、対向電極102をアノードとして用い、多数の内部電極層11a、11c、11eをカソードとして用いて、試料番号9〜14について、電源101によって、対向電極102と多数の内部電極層11a、11c、11eの各々との間に、表2に示す電界を印加して、表2に示す時間保持することによって、電気泳動法により、内部電極層11a、11c、11eの各々とセラミック積層体10の左側の表面の間の領域10g、10h、10i内に存在する空隙にSiO2ゾルを浸入させた。

【0065】

上記の処理を終えた後、同様にして、液体104中においてセラミック積層体10の右側の表面に対向するように右側の表面から1cmの距離を隔てた位置に対向電極102を配置した。セラミック積層体10の左側の表面で露出している多数の内部電極層11b、11dの左側の端面のそれぞれを配線103で接続した。そして、対向電極102をアノードとして用い、多数の内部電極層11b、11dをカソードとして用いて、試料番号9〜14について、電源101によって、対向電極102と多数の内部電極層11a、11c、11eの各々との間に、表2に示す電界を印加して、表2に示す時間保持することによって、電気泳動法により、内部電極層11b、11dの各々とセラミック積層体10の右側の表面の間の領域10j、10k内に存在する空隙にSiO2ゾルを浸入させた。

【0066】

なお、電気泳動法による酸化物ゾルの空隙への浸入量は電界の大きさに依存するので、電界の大きさを変更した場合には、試料番号9〜14についてその浸入量が等しくなるように印加時間を変化させた。

【0067】

電気泳動法による処理を終えた後、試料番号9〜14のセラミック積層体10を温度50℃で24時間、オーブン内で乾燥させた後、さらに温度100℃で1時間、乾燥させた。

【0068】

なお、比較のため、試料番号15〜16について、図1に示すように、ニッケルからなる多数の内部電極層11a〜11eが交互に両端面に露出した、積層セラミックコンデンサ1用の焼成後のセラミック積層体10(大きさ2.0mm×1.2mm×1.2mm)を各100個作製した。試料番号15のセラミック積層体10を、図1に示すように、平均粒径が50nmのSiO2ゾルをエタノール中に分散したSiO2ゾル分散溶液である液体104に浸漬して取り出し、温度50℃で24時間、オーブン内で乾燥させた後、さらに温度100℃で1時間、乾燥させた。試料番号16のセラミック積層体10については何も処理しなかった。

【0069】

以上のようにして得られた試料番号9〜16のセラミック積層体10の各々について、図2に示すように、内部電極層11の一部の端面が露出したセラミック積層体10の外表面の上に、外部電極層12の原材料である銅(Cu)ペーストをディップ法により塗布した後、温度800℃で焼き付けた。これにより、特定の内部電極層11に電気的に接続されるように、セラミック積層体10の外表面の上に外部電極層12が形成された。さらに電解めっき法により、外部電極層12の表面上に、ニッケル(Ni)からなる第1のめっき層13を形成し、さらにその上に、錫(Sn)からなる第2のめっき層14を形成した。以上のようにして、試料番号9〜16の積層セラミックコンデンサ1を作製した。なお、得られた試料番号9〜16の積層セラミックコンデンサ1は4.3Vの定格電圧を想定して作製されたものである。

【0070】

得られた試料番号9〜16の積層セラミックコンデンサ1について、温度85℃、相対湿度85%の条件下で、定格電圧の4倍の電圧を印加することによって、耐湿負荷試験を1000時間、5000時間行った。それぞれの耐湿負荷試験後の絶縁不良個数を調査した。積層セラミックコンデンサ1の絶縁抵抗値が1MΩ未満になると、絶縁不良であると判断した。調査結果を表2に示す。

【0071】

【表2】

【0072】

表1と表2に示す結果から、試料番号2〜5、試料番号10〜13の積層セラミックコンデンサ1については、電気泳動法により内部電極層11a〜11eとセラミック積層体10の表面の間の領域内の空隙に浸入した酸化物ゾルまたは酸化物粒子を、外部電極層12の形成時において熱処理することにより、内部電極層11a〜11eとセラミック積層体10の表面の間の領域内に存在するナノレベルの微細な空隙にまで酸化物を十分に充填させることができるので、耐湿負荷試験において内部電極層11a〜11eとセラミック積層体10の間の空隙への水分の浸入をより効果的に防止することが可能になり、絶縁抵抗の低下を防止することができることがわかる。

【0073】

試料番号7と15の積層セラミックコンデンサ1については、セラミック積層体10を酸化物ゾル分散溶液に浸漬したが電界を印加しなかったので、セラミック積層体10内の空隙に酸化物粒子が充填されなかったため、耐湿負荷試験で良好な結果が得られなかったことがわかる。

【0074】

試料番号8と16の積層セラミックコンデンサ1については、セラミック積層体10に対して何も処理されなかったので、耐湿負荷試験で良好な結果が得られなかったことがわかる。

【0075】

試料番号1と9の積層セラミックコンデンサ1については、電界10V/mの印加で電気泳動法による処理をセラミック積層体10に施しても、電界が小さいために酸化物ゾルが十分に泳動されなかったことに起因して、セラミック積層体10内の空隙に酸化物粒子が十分に充填されなかったので、耐湿負荷試験で良好な結果が得られなかったものと考えられる。

【0076】

試料番号6と14の積層セラミックコンデンサ1については、電界100kV/m(100000V/m)の印加で電気泳動法による処理をセラミック積層体10に施しても、電界が大きいために酸化物粒子の流れが速すぎることに起因して、セラミック積層体10内の空隙に酸化物粒子が十分に充填されなかったので、耐湿負荷試験で良好な結果が得られなかったものと考えられる。

【0077】

以上の結果から、実施例1と2で作製されたセラミック積層体10の場合、電界50V/m〜50kV/mの印加で電気泳動法による処理をセラミック積層体10に施すことが、セラミック積層体10内の空隙に酸化物粒子を十分に充填させるのに良好な条件であることがわかる。

【0078】

今回開示された実施の形態や実施例はすべての点で例示であって制限的なものではないと考慮されるべきである。本発明の範囲は以上の実施の形態や実施例ではなく、特許請求の範囲によって示され、特許請求の範囲と均等の意味および範囲内でのすべての修正や変形を含むものであることが意図される。

【符号の説明】

【0079】

1:積層セラミックコンデンサ、10:セラミック積層体、10a,10b,10c,10d,10e,10f:セラミック層、11,11a,11b,11c,11d,11e:内部電極層、12:外部電極層、13:第1のめっき層、14:第2のめっき層、101:電源、102:対向電極、103:配線、104:液体。

【技術分野】

【0001】

この発明は、一般的にはセラミック体の製造方法に関し、特定的には、内部に導電体を含むセラミック体の製造方法、例えば、積層セラミックコンデンサ等のチップ型のセラミック電子部品の製造方法に関するものである。

【背景技術】

【0002】

従来から、セラミック体の一例である積層セラミックコンデンサは、以下のようにして製造される。

【0003】

まず、セラミック原料粉末を含むスラリーを準備する。このスラリーをシートに成形し、セラミックグリーンシートを作製する。セラミックグリーンシートの表面上には、内部電極層の原材料である導電性ペーストを所定のパターンに従って塗布する。この導電性ペーストは、金属粉末、溶剤およびワニスから構成される。

【0004】

次に、導電性ペーストが塗布された複数のセラミックグリーンシートを積層し、熱圧着することにより、一体化された生の積層体を作製する。この生の積層体を焼成することにより、セラミック積層体を作製する。このセラミック積層体の内部には、複数の内部電極層が形成されている。内部電極層の一部の端面は、セラミック積層体の外部表面に露出している。

【0005】

次に、内部電極層の一部の端面が露出したセラミック積層体の外表面の上に、外部電極層の原材料である導電性ペーストを塗布した後、焼き付ける。この導電性ペーストは、金属粉末、ガラスフリット、溶剤およびワニスから構成される。これにより、特定の内部電極層に電気的に接続されるように、セラミック積層体の外表面の上に外部電極層が形成される。

【0006】

最後に、はんだ付け性能を高めるために、必要に応じて外部電極層の表面にめっき層を形成する。

【0007】

上記の製造工程において、たとえば、外部電極層の表面にめっき層を形成する場合に、外部電極層に存在する微細な空隙から水分が浸入する。また、セラミック体の一例である積層セラミックコンデンサを高湿環境下で使用した場合にも、外部電極層に存在する微細な空隙から水分が浸入する。このように外部電極層から浸入した水分が、セラミック積層体の内部に存在する内部電極層とセラミック層との間の界面の微細な空隙に水分が到達することにより、絶縁抵抗の低下を引き起こすという問題がある。

【0008】

そこで、たとえば、特開2001−102247号公報(以下、特許文献1という)では、上記の問題を解決するためのチップ型電子部品の構成が提案されている。特許文献1で提案されたチップ型電子部品は、矩形状セラミック基体の両端部に厚膜下地導体層、表面めっき層からなる外部端子電極を形成してなるチップ型電子部品において、外部端子電極に、撥水性を有する部材を含浸させている。このようにすることにより、チップ型電子部品を湿度の高い場所に放置した場合も、外部端子電極のポーラス部分に水分が浸入することを抑制している。その結果、水分が表面めっき層、厚膜下地導体層を通って、電子部品素体に到達するのが防止されている。

【0009】

また、たとえば、特開平2−301113号公報(以下、特許文献2という)では、上記の問題を解決するための積層セラミック電子部品の構成とその製造方法が提案されている。特許文献2で提案された積層セラミック電子部品は、セラミック積層体内または外部電極内の隙間、ボア、ピンホール等の欠陥を無機酸化物で埋めたものである。また、特許文献2で提案された積層セラミック電子部品の製造方法は、セラミック積層体またはセラミック積層体に外部電極を形成した後、これを金属アルコキシド等の有機金属溶液中に浸漬してセラミック積層体内または外部電極内の隙間、ボア、ピンホール等の欠陥内に有機金属を含浸させた後、加熱することにより有機金属を無機酸化物に分解するものである。このようにすることにより、水分が上記の隙間やボアに浸入することを抑制している。

【0010】

なお、たとえば、特表2003−508627号公報(以下、特許文献3という)では、セラミックコーティングの表面の空隙をゾル−ゲル電気泳動堆積を用いて封止する方法が記載されている。この場合、一例としてカソードが金属支持体上の多孔質セラミックコーティングであり、アノードとしては白金が用いられ、カソードとアノードとの間に電界が印加されることにより電気泳動が行われる。

【先行技術文献】

【特許文献】

【0011】

【特許文献1】特開2001−102247号公報

【特許文献2】特開平2−301113号公報

【特許文献3】特表2003−508627号公報

【発明の概要】

【発明が解決しようとする課題】

【0012】

特許文献1に記載されたチップ型電子部品の構成では、外部端子電極に撥水性の物質が残留する。このため、後工程でめっき層を形成する場合に、外部端子電極の表面においてめっき析出不良が発生しやすくなり、はんだ付けでチップ型電子部品を基板等に実装する場合に不良が発生する場合がある。

【0013】

また、特許文献1に記載されたチップ型電子部品の構成では、外部端子電極に残留する撥水性物質の量が少なければ、電子部品素体へ水分が浸入するのを抑制する効果が得られず、外部端子電極に残留する撥水性物質の量が多ければ、めっき析出不良が発生する。このため、外部端子電極に、撥水性を有する部材を含浸させるための処理条件を制御することが困難である。

【0014】

一方、特許文献2では、セラミック積層体を金属アルコキシド等の有機金属溶液中に浸漬してセラミック積層体内または外部電極内の隙間等の欠陥内に無機酸化物を埋め込んでいる。しかし、この方法では、ナノレベルの微細な空隙にまで無機酸化物を充填することができないので、水分が空隙に浸入するのを抑制する効果が不十分である。

【0015】

なお、特許文献3では、金属支持体上の多孔質セラミックコーティングの表面の空隙をゾル−ゲル電気泳動堆積を用いて封止する方法が開示されているだけであり、内部に導電体を含むセラミック体を製造する方法については何ら示唆されていない。

【0016】

そこで、この発明の目的は、内部に導電体を含むセラミック体において導電体とセラミック体の間の空隙への水分の浸入をより効果的に防止することが可能なセラミック体の製造方法を提供することである。

【課題を解決するための手段】

【0017】

この発明に従ったセラミック体の製造方法は、内部に導電体を含むセラミック体の製造方法であって、導電体の一方の端面がセラミック体の第1の表面から離れた内部にあって第1の表面で露出しておらず、かつ、導電体の他方の端面がセラミック体の第1の表面と異なる第2の表面で露出しているセラミック体を対象とするものであり、以下のステップを備える。

【0018】

(a)酸化物ゾルまたは酸化物粒子を含む液体にセラミック体を浸漬するステップ。

【0019】

(b)上記の液体中においてセラミック体の第1の表面に対向するように第1の表面から距離を隔てた位置に対向電極を配置し、対向電極と導電体との間に電界を印加することによって、電気泳動法により導電体とセラミック体の第1の表面の間の領域内の空隙に酸化物ゾルまたは酸化物粒子を浸入させるステップ。

【0020】

(c)導電体とセラミック体の第1の表面の間の領域内の空隙に浸入した酸化物ゾルまたは酸化物粒子を熱処理することにより、導電体とセラミック体の第1の表面の間の領域内の空隙を酸化物で充填するステップ。

【0021】

この発明のセラミック体の製造方法において採用される電気泳動法では、セラミック体の内部に存在する導電体がカソードとして用いられ、セラミック体の外部に存在する対向電極がアノードとして用いられ、導電体と対向電極との間に電界が印加される。このため、電界強度を相対的に高くすることができるので、電気泳動法により、酸化物ゾルまたは酸化物粒子を導電体とセラミック体の第1の表面の間の領域内に存在するナノレベルの微細な空隙にまで浸入させることができる。

【0022】

そして、導電体とセラミック体の間の第1の表面の間の領域内の空隙に浸入した酸化物ゾルまたは酸化物粒子を熱処理することにより、導電体とセラミック体の第1の表面の間の領域内に存在するナノレベルの微細な空隙にまで酸化物を充填させることができる。

【0023】

したがって、内部に導電体を含むセラミック体において導電体とセラミック体の間の空隙への水分の浸入をより効果的に防止することが可能になる。

【0024】

この発明のセラミック体の製造方法において、セラミック体が、積層された複数のセラミック層と、各々が複数のセラミック層の間に介在した複数の導電体層とを含むセラミック積層体であることが好ましい。

【0025】

この場合、セラミック積層体からなるセラミック電子部品の製造方法に本発明の製造方法を適用することができる。たとえば、本発明の製造方法を適用すると、セラミック積層体を含む電子部品において、外部電極層を形成する前に、酸化物を、導電体とセラミック体の第1の表面の間の領域内に存在するナノレベルの微細な空隙にまで充填させることによって、導電体とセラミック体の間の空隙への水分の浸入をより効果的に防止することが可能になる。したがって、外部電極層の表面にめっき析出を阻害する物質が残留することがない。これにより、後工程でめっき層を形成する場合に、外部端子電極の表面においてめっき析出不良が発生することもなく、はんだ付けでチップ型電子部品を基板等に実装する場合に不良が発生することもない。

【0026】

なお、セラミック積層体からなるセラミック電子部品の製造方法に本発明の製造方法を適用する場合、既存の製造プロセスに、上記の(a)と(b)のステップを追加するだけでよい。この場合、上記の(c)のステップは、外部電極層の焼成時に行われる。これにより、大きな製造コストの増大を伴わずに、導電体とセラミック体の間の空隙への水分の浸入をより効果的に防止することが可能になる。

【0027】

セラミック体が上記のセラミック積層体である場合、酸化物が、Si、Ti、Mg、Mn、BaおよびSrからなる群より選ばれた少なくとも一種の元素を含むことが好ましい。

【0028】

この場合、セラミック積層体からなるセラミック電子部品において、たとえば、セラミック体の主成分がBa1−xSrxTiO3(0≦x≦1)、一例としてBaTiO3であり、副成分または添加物がSiO2、MgO、MnOであるので、上記の元素を含む酸化物が空隙を充填してもセラミック電子部品の特性に影響を与えることがない。

【0029】

また、セラミック体が上記のセラミック積層体である場合、酸化物ゾルまたは酸化物粒子を浸入させるステップにおいて、印加される電界は、50V/m以上50kV/m以下であることが好ましい。

【0030】

この範囲内の電界をセラミック積層体に印加することにより、電気泳動法によって、酸化物ゾルまたは酸化物粒子を導電体とセラミック積層体の第1の表面の間の領域内に存在するナノレベルの微細な空隙にまで十分に浸入させることができる。

【発明の効果】

【0031】

以上のようにこの発明によれば、内部に導電体を含むセラミック体において導電体とセラミック体の間の空隙への水分の浸入をより効果的に防止することが可能になる。これにより、たとえば、チップ型の積層セラミックコンデンサ等の積層セラミック電子部品の製造方法に本発明を適用することによって、絶縁抵抗の低下を防止することができ、積層セラミック電子部品の信頼性を向上させることができる。

【図面の簡単な説明】

【0032】

【図1】この発明の一つの実施の形態として、セラミック体の一例である積層セラミックコンデンサの第1の製造工程を示す概略的な断面図である。

【図2】この発明の一つの実施の形態として、セラミック体の一例である積層セラミックコンデンサの第2の製造工程を示す概略的な断面図である。

【発明を実施するための形態】

【0033】

本発明のセラミック体の製造方法の一つの実施の形態である積層セラミックコンデンサの製造方法について説明する。

【0034】

まず、セラミック原料粉末を含むスラリーを準備する。このスラリーをシートに成形し、セラミックグリーンシートを作製する。セラミックグリーンシートの表面上には、内部電極層の原材料である導電性ペーストを所定のパターンに従って塗布する。この導電性ペーストは、金属粉末、溶剤およびワニスから構成される。

【0035】

次に、導電性ペーストが塗布された複数のセラミックグリーンシートを積層し、熱圧着することにより、一体化された生の積層体を作製する。この生の積層体を焼成することにより、図1に示されるような、セラミック体としてのセラミック積層体10を作製する。このようにして作製された直方体状のセラミック積層体10は、複数の(図では一例として6つの)積層されたセラミック層10a、10b、10c、10d、10e、10fと、複数のセラミック層10a、10b、10c、10d、10e、10f間の界面に沿って形成された複数の(図では一例として5つの)内部電極層11a、11b、11c、11d、11eとを備えている。このようにして、セラミック積層体10の内部には、内部の導電体として複数の内部電極層11a〜11eが形成されている。

【0036】

図1では、内部電極層11a、11c、11eの左側の端面が、セラミック積層体10の左側の端面から間隔(または領域)10g、10h、10iだけ離れた内部にあって左側の端面で露出しておらず、内部電極層11a、11c、11eの右側の端面が、セラミック積層体10の左側の端面と異なる右側の端面で露出している。内部電極層11b、11dの右側の端面が、セラミック積層体10の右側の端面から間隔(または領域)10j、10kだけ離れた内部にあって右側の端面で露出しておらず、内部電極層11b、11dの左側の端面が、セラミック積層体10の右側の端面と異なる左側の端面で露出している。このようにして、内部電極層11a〜11eの左側または右側の端面がセラミック積層体10の外表面にまで到達するように形成されている。セラミック積層体10の左側の端面にまで引き出される内部電極層11b、11dと右側の端面にまで引き出される内部電極層11a、11c、11eとが、セラミック積層体10の内部において、誘電体としてのセラミック層10a、10b、10c、10d、10e、10fの各々を介して静電容量を取得できるように交互に配置されている。

【0037】

なお、セラミック層10a〜10fは、たとえば、BaTiO3系化合物を含むセラミック材料からなる。内部電極層11a〜11eの導電材料は、コスト低減の点から、ニッケルまたはニッケル合金であることが好ましい。

【0038】

次に、上述のようにして作製されたセラミック積層体10を、図1に示すように、酸化物ゾルまたは酸化物ナノ粒子を含む液体、たとえば、BaTiO3、SiO2等の酸化物のゾルまたはナノ粒子を含むエタノール等の液体104に浸漬する。

【0039】

その後、図1に示すように、液体104中においてセラミック積層体10の左側の表面に対向するように左側の表面から距離を隔てた位置に、たとえば、白金(Pt)線等からなる対向電極102を配置する。セラミック積層体10の右側の表面で露出している内部電極層11a、11c、11eの右側の端面のそれぞれを配線103で接続する。そして、対向電極102をアノードとして用い、内部電極層11a、11c、11eをカソードとして用いて、電源101によって、対向電極102と内部電極層11a、11c、11eの各々との間に電界を印加することによって、電気泳動法により、内部電極層11a、11c、11eの各々とセラミック積層体10の左側の表面の間の領域10g、10h、10i内に存在する空隙に酸化物のゾルまたはナノ粒子を浸入させる。

【0040】

上記の電気泳動法による処理を終えた後、同様にして、液体104中においてセラミック積層体10の右側の表面に対向するように右側の表面から距離を隔てた位置に対向電極102を配置する。セラミック積層体10の左側の表面で露出している内部電極層11b、11dの左側の端面のそれぞれを配線103で接続する。そして、対向電極102をアノードとして用い、内部電極層11b、11dをカソードとして用いて、電源101によって、対向電極102と内部電極層11b、11dの各々との間に電界を印加することによって、電気泳動法により、内部電極層11b、11dの各々とセラミック積層体10の右側の表面の間の領域10j、10k内に存在する空隙に酸化物のゾルまたはナノ粒子を浸入させる。

【0041】

その後、内部電極層11a〜11eの各々とセラミック積層体10の左側または右側の表面の間の領域10g〜10k内に存在する空隙に浸入した酸化物のゾルまたはナノ粒子を熱処理することにより、内部電極層11a〜11eの各々とセラミック積層体10の左側または右側の表面の間の領域10g〜10k内に存在する空隙を、たとえば、BaTiO3、SiO2等の酸化物で充填する。この熱処理工程は、以下で説明する外部電極層の形成工程で行われる。

【0042】

図2に示すように、内部電極層11の一部の端面が露出したセラミック積層体10の外表面の上に、外部電極層12の原材料である導電性ペーストを塗布した後、焼き付ける。この導電性ペーストは、金属粉末、ガラスフリット、溶剤およびワニスから構成される。これにより、特定の内部電極層11に電気的に接続されるように、セラミック積層体10の外表面の上に外部電極層12が形成される。この外部電極層12の形成工程においてセラミック積層体10が熱処理されるので、内部電極層11a〜11eの各々とセラミック積層体10の左側または右側の表面の間の領域10g〜10k内に存在する空隙が、たとえば、BaTiO3、SiO2等の酸化物で充填される。

【0043】

このようにして、前述した静電容量を取り出すために、セラミック積層体10の外表面上であって、端面上には、内部電極層11のいずれか特定のものに電気的に接続されるように、外部電極層12が形成される。外部電極層12に含まれる導電材料としては、内部電極層11の場合と同じ導電材料を用いることができ、さらに、銀、パラジウム、銀−パラジウム合金なども用いることができる。外部電極層12は、上記の金属または合金の粉末にガラスフリットを添加して得られた導電性ペーストを付与し、焼き付けることによって形成される。なお、上記の説明では外部電極層12として厚膜外部電極の例を示したが、外部電極層12は、厚膜外部電極に限定されず、スパッタリングによって形成される薄膜外部電極でもよく、めっきによって形成される電極でもよく、その他の形成方法による電極でもよい。

【0044】

最後に、はんだ付け性能を高めるために、必要に応じて外部電極層12の表面に第1と第2のめっき層13、14を形成する。このようにして、外部電極層12上には、必要に応じて、ニッケル、銅などからなる第1のめっき層13が形成され、さらにその上には、半田、錫などからなる第2のめっき層14が形成される。以上のようにして、積層セラミックコンデンサ1が製造される。

【0045】

上述したこの発明の一つの実施の形態である積層セラミックコンデンサ1の製造方法において採用される電気泳動法では、セラミック積層体10の内部に存在する内部電極層11a〜11eがカソードとして用いられ、セラミック積層体10の外部に存在する対向電極102がアノードとして用いられ、内部電極層11a〜11eと対向電極102との間に電界が印加される。このため、電界強度を相対的に高くすることができるので、電気泳動法により、酸化物ゾルまたは酸化物粒子を内部電極層11a〜11eとセラミック積層体10の表面の間の領域内に存在するナノレベルの微細な空隙にまで浸入させることができる。

【0046】

そして、内部電極層11a〜11eとセラミック積層体10の表面の間の領域内の空隙に浸入した酸化物ゾルまたは酸化物粒子を熱処理することにより、内部電極層11a〜11eとセラミック積層体10の表面の間の領域内に存在するナノレベルの微細な空隙にまで酸化物を充填させることができる。

【0047】

したがって、内部に導電体を含むセラミック積層体10において内部電極層11a〜11eとセラミック積層体10の間の空隙への水分の浸入をより効果的に防止することが可能になる。これにより、たとえば、チップ型の積層セラミックコンデンサ1等の積層セラミック電子部品の製造方法に本発明を適用することによって、絶縁抵抗の低下を防止することができ、積層セラミック電子部品の信頼性を向上させることができる。しかし、少なくとも、内部に導電体を含み、導電体の一方の端面がセラミック体の第1の表面から離れた内部にあって第1の表面で露出しておらず、かつ、導電体の他方の端面がセラミック体の第1の表面と異なる第2の表面で露出しているセラミック体の製造方法であれば、本発明の製造方法を適用することにより、導電体とセラミック体の間の空隙への水分の浸入を効果的に防止することが可能となる。たとえば、上記のセラミック体と導電体が膜や層等の形態で形成されていても、本発明の製造方法を適用することができる。

【0048】

上記の実施の形態では、セラミック積層体10からなるセラミック電子部品の一例として積層セラミックコンデンサ1の製造方法に本発明の製造方法を適用している。この場合、セラミック積層体10を含む積層セラミックコンデンサ1等の電子部品において、外部電極層12を形成する前に、酸化物を、内部電極層11a〜11eとセラミック積層体10の表面の間の領域内に存在するナノレベルの微細な空隙にまで充填させることによって、内部電極層11a〜11eとセラミック積層体10の間の空隙への水分の浸入をより効果的に防止することが可能になる。したがって、外部電極層12の表面にめっき析出を阻害する物質が残留することがない。これにより、後工程で第1のめっき層13や第2のめっき層14を形成する場合に、外部端子電極としての外部電極層12の表面においてめっき析出不良が発生することもなく、はんだ付けでチップ型電子部品を基板等に実装する場合に不良が発生することもない。

【0049】

なお、セラミック積層体10からなる積層セラミックコンデンサ1等のセラミック電子部品の製造方法に本発明の製造方法を適用する場合、既存の製造プロセスに、上記の浸漬ステップと電気泳動法によるステップを追加するだけでよい。この場合、上記の熱処理のステップは、外部電極層の焼成時に行われる。これにより、大きな製造コストの増大を伴わずに、内部電極層11a〜11eとセラミック積層体10の間の空隙への水分の浸入をより効果的に防止することが可能になる。

【0050】

また、上記の浸漬ステップにおいて用いられる液体に含まれるゾルまたはナノ粒子は、Si、Ti、Mg、Mn、BaおよびSrからなる群より選ばれた少なくとも一種の元素を含む酸化物からなるのが好ましい。この場合、セラミック積層体10からなる積層セラミックコンデンサ1等のセラミック電子部品において、たとえば、セラミック積層体10の主成分がBa1−xSrxTiO3(0≦x≦1)、一例としてBaTiO3であり、副成分または添加物がSiO2、MgO、MnOであるので、Si、Ti、Mg、Mn、BaおよびSrからなる群より選ばれた少なくとも一種の元素を含む酸化物が空隙を充填してもセラミック電子部品の特性に影響を与えることがない。

【0051】

さらに、セラミック積層体10からなる積層セラミックコンデンサ1等のセラミック電子部品の製造方法に本発明の製造方法を適用する場合、内部電極層11a〜11eとセラミック積層体10の間の空隙への水分の浸入をより効果的に防止することが可能になり、絶縁抵抗の低下を防止することができるので、積層セラミック電子部品におけるセラミック積層体10の設計、外部電極層12の設計、第1のめっき層13や第2のめっき層14の設計等において自由度を高めることができる。

【実施例】

【0052】

(実施例1)

本発明の実施例1として試料番号1〜6について、図1に示すように、ニッケルからなる多数の内部電極層11a〜11eが交互に両端面に露出した、積層セラミックコンデンサ1用の焼成後のセラミック積層体10(大きさ2.0mm×1.2mm×1.2mm)を各100個作製した。セラミック積層体10を構成する多数のセラミック層10a〜10fの組成は、主成分としてBaTiO3を含み、副成分として主成分100モル部に対して2モル部のDy、2モル部のMg、0.5モル部のMnを含む。多数のセラミック層10a〜10fの各々の厚みは0.8μmであり、多数の内部電極層11a〜11eの各々の厚みは0.6μmであった。

【0053】

次に、上述のようにして作製されたセラミック積層体10を、図1に示すように、平均粒径が15nmのBaTiO3ゾルをエタノール中に分散したBaTiO3ゾル分散溶液である液体104に浸漬した。BaTiO3ゾルは、酢酸バリウムとチタンアルコキシドを用いて作製した溶液を加水分解して作製した。

【0054】

その後、図1に示すように、液体104中においてセラミック積層体10の左側の表面に対向するように左側の表面から1cmの距離を隔てた位置に、白金(Pt)線からなる対向電極102を配置した。セラミック積層体10の右側の表面で露出している多数の内部電極層11a、11c、11eの右側の端面のそれぞれを配線103で接続した。そして、対向電極102をアノードとして用い、多数の内部電極層11a、11c、11eをカソードとして用いて、試料番号1〜6について、電源101によって、対向電極102と多数の内部電極層11a、11c、11eの各々との間に、表1に示す電界を印加して、表1に示す時間保持することによって、電気泳動法により、内部電極層11a、11c、11eの各々とセラミック積層体10の左側の表面の間の領域10g、10h、10i内に存在する空隙にBaTiO3ゾルを浸入させた。

【0055】

上記の処理を終えた後、同様にして、液体104中においてセラミック積層体10の右側の表面に対向するように右側の表面から1cmの距離を隔てた位置に対向電極102を配置した。セラミック積層体10の左側の表面で露出している多数の内部電極層11b、11dの左側の端面のそれぞれを配線103で接続した。そして、対向電極102をアノードとして用い、多数の内部電極層11b、11dをカソードとして用いて、試料番号1〜6について、電源101によって、対向電極102と多数の内部電極層11a、11c、11eの各々との間に、表1に示す電界を印加して、表1に示す時間保持することによって、電気泳動法により、内部電極層11b、11dの各々とセラミック積層体10の右側の表面の間の領域10j、10k内に存在する空隙にBaTiO3ゾルを浸入させた。

【0056】

なお、電気泳動法による酸化物ゾルの空隙への浸入量は電界の大きさに依存するので、電界の大きさを変更した場合には、試料番号1〜6についてその浸入量が等しくなるように印加時間を変化させた。

【0057】

電気泳動法による処理を終えた後、試料番号1〜6のセラミック積層体10を温度50℃で24時間、オーブン内で乾燥させた後、さらに温度100℃で1時間、乾燥させた。

【0058】

なお、比較のため、試料番号7〜8について、図1に示すように、ニッケルからなる多数の内部電極層11a〜11eが交互に両端面に露出した、積層セラミックコンデンサ1用の焼成後のセラミック積層体10(大きさ2.0mm×1.2mm×1.2mm)を各100個作製した。試料番号7のセラミック積層体10を、図1に示すように、平均粒径が15nmのBaTiO3ゾルをエタノール中に分散したBaTiO3ゾル分散溶液である液体104に浸漬して取り出し、温度50℃で24時間、オーブン内で乾燥させた後、さらに温度100℃で1時間、乾燥させた。試料番号8のセラミック積層体10については何も処理しなかった。

【0059】

以上のようにして得られた試料番号1〜8のセラミック積層体10の各々について、図2に示すように、内部電極層11の一部の端面が露出したセラミック積層体10の外表面の上に、外部電極層12の原材料である銅(Cu)ペーストをディップ法により塗布した後、温度800℃で焼き付けた。これにより、特定の内部電極層11に電気的に接続されるように、セラミック積層体10の外表面の上に外部電極層12が形成された。さらに電解めっき法により、外部電極層12の表面上に、ニッケル(Ni)からなる第1のめっき層13を形成し、さらにその上に、錫(Sn)からなる第2のめっき層14を形成した。以上のようにして、試料番号1〜8の積層セラミックコンデンサ1を作製した。なお、得られた試料番号1〜8の積層セラミックコンデンサ1は4.3Vの定格電圧を想定して作製されたものである。

【0060】

得られた試料番号1〜8の積層セラミックコンデンサ1について、温度85℃、相対湿度85%の条件下で、定格電圧の4倍の電圧を印加することによって、耐湿負荷試験を1000時間、5000時間行った。それぞれの耐湿負荷試験後の絶縁不良個数を調査した。積層セラミックコンデンサ1の絶縁抵抗値が1MΩ未満になると、絶縁不良であると判断した。調査結果を表1に示す。

【0061】

【表1】

【0062】

(実施例2)

本発明の実施例2として試料番号9〜14について、図1に示すように、ニッケルからなる多数の内部電極層11a〜11eが交互に両端面に露出した、積層セラミックコンデンサ1用の焼成後のセラミック積層体10(大きさ2.0mm×1.2mm×1.2mm)を各100個作製した。セラミック積層体10を構成する多数のセラミック層10a〜10fの組成は、主成分としてBaTiO3を含み、副成分として主成分100モル部に対して2モル部のDy、2モル部のMg、0.5モル部のMnを含む。多数のセラミック層10a〜10fの各々の厚みは0.8μmであり、多数の内部電極層11a〜11eの各々の厚みは0.6μmであった。

【0063】

次に、上述のようにして作製されたセラミック積層体10を、図1に示すように、平均粒径が50nmのSiO2ゾルをエタノール中に分散したSiO2ゾル分散溶液である液体104に浸漬した。SiO2ゾルは、シリカの金属アルコキシドであるテトラエトキシシラン(TEOS)を加水分解して作製した。

【0064】

その後、図1に示すように、液体104中においてセラミック積層体10の左側の表面に対向するように左側の表面から1cmの距離を隔てた位置に、白金(Pt)線からなる対向電極102を配置した。セラミック積層体10の右側の表面で露出している多数の内部電極層11a、11c、11eの右側の端面のそれぞれを配線103で接続した。そして、対向電極102をアノードとして用い、多数の内部電極層11a、11c、11eをカソードとして用いて、試料番号9〜14について、電源101によって、対向電極102と多数の内部電極層11a、11c、11eの各々との間に、表2に示す電界を印加して、表2に示す時間保持することによって、電気泳動法により、内部電極層11a、11c、11eの各々とセラミック積層体10の左側の表面の間の領域10g、10h、10i内に存在する空隙にSiO2ゾルを浸入させた。

【0065】

上記の処理を終えた後、同様にして、液体104中においてセラミック積層体10の右側の表面に対向するように右側の表面から1cmの距離を隔てた位置に対向電極102を配置した。セラミック積層体10の左側の表面で露出している多数の内部電極層11b、11dの左側の端面のそれぞれを配線103で接続した。そして、対向電極102をアノードとして用い、多数の内部電極層11b、11dをカソードとして用いて、試料番号9〜14について、電源101によって、対向電極102と多数の内部電極層11a、11c、11eの各々との間に、表2に示す電界を印加して、表2に示す時間保持することによって、電気泳動法により、内部電極層11b、11dの各々とセラミック積層体10の右側の表面の間の領域10j、10k内に存在する空隙にSiO2ゾルを浸入させた。

【0066】

なお、電気泳動法による酸化物ゾルの空隙への浸入量は電界の大きさに依存するので、電界の大きさを変更した場合には、試料番号9〜14についてその浸入量が等しくなるように印加時間を変化させた。

【0067】

電気泳動法による処理を終えた後、試料番号9〜14のセラミック積層体10を温度50℃で24時間、オーブン内で乾燥させた後、さらに温度100℃で1時間、乾燥させた。

【0068】

なお、比較のため、試料番号15〜16について、図1に示すように、ニッケルからなる多数の内部電極層11a〜11eが交互に両端面に露出した、積層セラミックコンデンサ1用の焼成後のセラミック積層体10(大きさ2.0mm×1.2mm×1.2mm)を各100個作製した。試料番号15のセラミック積層体10を、図1に示すように、平均粒径が50nmのSiO2ゾルをエタノール中に分散したSiO2ゾル分散溶液である液体104に浸漬して取り出し、温度50℃で24時間、オーブン内で乾燥させた後、さらに温度100℃で1時間、乾燥させた。試料番号16のセラミック積層体10については何も処理しなかった。

【0069】

以上のようにして得られた試料番号9〜16のセラミック積層体10の各々について、図2に示すように、内部電極層11の一部の端面が露出したセラミック積層体10の外表面の上に、外部電極層12の原材料である銅(Cu)ペーストをディップ法により塗布した後、温度800℃で焼き付けた。これにより、特定の内部電極層11に電気的に接続されるように、セラミック積層体10の外表面の上に外部電極層12が形成された。さらに電解めっき法により、外部電極層12の表面上に、ニッケル(Ni)からなる第1のめっき層13を形成し、さらにその上に、錫(Sn)からなる第2のめっき層14を形成した。以上のようにして、試料番号9〜16の積層セラミックコンデンサ1を作製した。なお、得られた試料番号9〜16の積層セラミックコンデンサ1は4.3Vの定格電圧を想定して作製されたものである。

【0070】

得られた試料番号9〜16の積層セラミックコンデンサ1について、温度85℃、相対湿度85%の条件下で、定格電圧の4倍の電圧を印加することによって、耐湿負荷試験を1000時間、5000時間行った。それぞれの耐湿負荷試験後の絶縁不良個数を調査した。積層セラミックコンデンサ1の絶縁抵抗値が1MΩ未満になると、絶縁不良であると判断した。調査結果を表2に示す。

【0071】

【表2】

【0072】

表1と表2に示す結果から、試料番号2〜5、試料番号10〜13の積層セラミックコンデンサ1については、電気泳動法により内部電極層11a〜11eとセラミック積層体10の表面の間の領域内の空隙に浸入した酸化物ゾルまたは酸化物粒子を、外部電極層12の形成時において熱処理することにより、内部電極層11a〜11eとセラミック積層体10の表面の間の領域内に存在するナノレベルの微細な空隙にまで酸化物を十分に充填させることができるので、耐湿負荷試験において内部電極層11a〜11eとセラミック積層体10の間の空隙への水分の浸入をより効果的に防止することが可能になり、絶縁抵抗の低下を防止することができることがわかる。

【0073】

試料番号7と15の積層セラミックコンデンサ1については、セラミック積層体10を酸化物ゾル分散溶液に浸漬したが電界を印加しなかったので、セラミック積層体10内の空隙に酸化物粒子が充填されなかったため、耐湿負荷試験で良好な結果が得られなかったことがわかる。

【0074】

試料番号8と16の積層セラミックコンデンサ1については、セラミック積層体10に対して何も処理されなかったので、耐湿負荷試験で良好な結果が得られなかったことがわかる。

【0075】

試料番号1と9の積層セラミックコンデンサ1については、電界10V/mの印加で電気泳動法による処理をセラミック積層体10に施しても、電界が小さいために酸化物ゾルが十分に泳動されなかったことに起因して、セラミック積層体10内の空隙に酸化物粒子が十分に充填されなかったので、耐湿負荷試験で良好な結果が得られなかったものと考えられる。

【0076】

試料番号6と14の積層セラミックコンデンサ1については、電界100kV/m(100000V/m)の印加で電気泳動法による処理をセラミック積層体10に施しても、電界が大きいために酸化物粒子の流れが速すぎることに起因して、セラミック積層体10内の空隙に酸化物粒子が十分に充填されなかったので、耐湿負荷試験で良好な結果が得られなかったものと考えられる。

【0077】

以上の結果から、実施例1と2で作製されたセラミック積層体10の場合、電界50V/m〜50kV/mの印加で電気泳動法による処理をセラミック積層体10に施すことが、セラミック積層体10内の空隙に酸化物粒子を十分に充填させるのに良好な条件であることがわかる。

【0078】

今回開示された実施の形態や実施例はすべての点で例示であって制限的なものではないと考慮されるべきである。本発明の範囲は以上の実施の形態や実施例ではなく、特許請求の範囲によって示され、特許請求の範囲と均等の意味および範囲内でのすべての修正や変形を含むものであることが意図される。

【符号の説明】

【0079】

1:積層セラミックコンデンサ、10:セラミック積層体、10a,10b,10c,10d,10e,10f:セラミック層、11,11a,11b,11c,11d,11e:内部電極層、12:外部電極層、13:第1のめっき層、14:第2のめっき層、101:電源、102:対向電極、103:配線、104:液体。

【特許請求の範囲】

【請求項1】

内部に導電体を含み、前記導電体の一方の端面がセラミック体の第1の表面から離れた内部にあって第1の表面で露出しておらず、かつ、前記導電体の他方の端面が前記セラミック体の第1の表面と異なる第2の表面で露出しているセラミック体の製造方法であって、

酸化物ゾルまたは酸化物粒子を含む液体にセラミック体を浸漬するステップと、

前記液体中において前記セラミック体の第1の表面に対向するように第1の表面から距離を隔てた位置に対向電極を配置し、前記対向電極と前記導電体との間に電界を印加することによって、電気泳動法により前記導電体と前記セラミック体の第1の表面の間の領域内の空隙に前記酸化物ゾルまたは前記酸化物粒子を浸入させるステップと、

前記導電体と前記セラミック体の第1の表面の間の領域内の空隙に浸入した前記酸化物ゾルまたは前記酸化物粒子を熱処理することにより、前記導電体と前記セラミック体の第1の表面の間の領域内の空隙を酸化物で充填するステップとを備えた、セラミック体の製造方法。

【請求項2】

前記セラミック体が、積層された複数のセラミック層と、各々が前記複数のセラミック層の間に介在した複数の導電体層とを含むセラミック積層体である、請求項1に記載のセラミック体の製造方法。

【請求項3】

前記酸化物が、Si、Ti、Mg、Mn、BaおよびSrからなる群より選ばれた少なくとも一種の元素を含む、請求項2に記載のセラミック体の製造方法。

【請求項4】

前記酸化物ゾルまたは前記酸化物粒子を浸入させるステップにおいて、印加される電界は、50V/m以上50kV/m以下である、請求項2または請求項3に記載のセラミック体の製造方法。

【請求項1】

内部に導電体を含み、前記導電体の一方の端面がセラミック体の第1の表面から離れた内部にあって第1の表面で露出しておらず、かつ、前記導電体の他方の端面が前記セラミック体の第1の表面と異なる第2の表面で露出しているセラミック体の製造方法であって、

酸化物ゾルまたは酸化物粒子を含む液体にセラミック体を浸漬するステップと、

前記液体中において前記セラミック体の第1の表面に対向するように第1の表面から距離を隔てた位置に対向電極を配置し、前記対向電極と前記導電体との間に電界を印加することによって、電気泳動法により前記導電体と前記セラミック体の第1の表面の間の領域内の空隙に前記酸化物ゾルまたは前記酸化物粒子を浸入させるステップと、

前記導電体と前記セラミック体の第1の表面の間の領域内の空隙に浸入した前記酸化物ゾルまたは前記酸化物粒子を熱処理することにより、前記導電体と前記セラミック体の第1の表面の間の領域内の空隙を酸化物で充填するステップとを備えた、セラミック体の製造方法。

【請求項2】

前記セラミック体が、積層された複数のセラミック層と、各々が前記複数のセラミック層の間に介在した複数の導電体層とを含むセラミック積層体である、請求項1に記載のセラミック体の製造方法。

【請求項3】

前記酸化物が、Si、Ti、Mg、Mn、BaおよびSrからなる群より選ばれた少なくとも一種の元素を含む、請求項2に記載のセラミック体の製造方法。

【請求項4】

前記酸化物ゾルまたは前記酸化物粒子を浸入させるステップにおいて、印加される電界は、50V/m以上50kV/m以下である、請求項2または請求項3に記載のセラミック体の製造方法。

【図1】

【図2】

【図2】

【公開番号】特開2010−171108(P2010−171108A)

【公開日】平成22年8月5日(2010.8.5)

【国際特許分類】

【出願番号】特願2009−10665(P2009−10665)

【出願日】平成21年1月21日(2009.1.21)

【出願人】(000006231)株式会社村田製作所 (3,635)

【Fターム(参考)】

【公開日】平成22年8月5日(2010.8.5)

【国際特許分類】

【出願日】平成21年1月21日(2009.1.21)

【出願人】(000006231)株式会社村田製作所 (3,635)

【Fターム(参考)】

[ Back to top ]