センサコントローラ

【課題】 波形データや画像データのような大容量データを短い時間で(例えば速い周期で)伝送し、伝送されたデータを用いて様々な連携動作を行うことを可能とするセンサコントローラを提供する。

【解決手段】 プログラム可能な論理回路とセンサコントローラの動作を制御するCPUとを有する制御部と、他のセンサコントローラとの接続に用いることのできるユニット間コネクタと、制御部とユニット間コネクタとの間の信号伝送経路であって、プログラム可能な論理回路とユニット間コネクタとの間に設けられたセンシングデータ伝送経路を含むユニット間経路とを備える。ユニット間コネクタに他のセンサコントローラが接続されたときに、プログラム可能な論理回路と当該他のセンサコントローラのプログラム可能な論理回路との間でセンシングデータの伝送を行うことができる。

【解決手段】 プログラム可能な論理回路とセンサコントローラの動作を制御するCPUとを有する制御部と、他のセンサコントローラとの接続に用いることのできるユニット間コネクタと、制御部とユニット間コネクタとの間の信号伝送経路であって、プログラム可能な論理回路とユニット間コネクタとの間に設けられたセンシングデータ伝送経路を含むユニット間経路とを備える。ユニット間コネクタに他のセンサコントローラが接続されたときに、プログラム可能な論理回路と当該他のセンサコントローラのプログラム可能な論理回路との間でセンシングデータの伝送を行うことができる。

【発明の詳細な説明】

【技術分野】

【0001】

この発明は、画像データや波形データ等といった大容量データを取り扱うセンシングシステムの構築に好適なセンサコントローラに関する。

【背景技術】

【0002】

2次元撮像素子を用いた変位センサとしては、信号処理ユニットとセンサヘッドユニットとが分離独立したものが知られている(特許文献1参照)。センサヘッドには投光用のレーザダイオードと受光用のCCDとが含まれている。CCDから得られる信号に基づいて生成された映像信号は電気コードを介して信号処理ユニットへと送られる。信号処理ユニットはマイクロプロセッサを主体として構成されるCPUとプログラム可能な論理回路であるFPGA(Field Programmable Gate Array)とを含んでいる。CPUは主として計測処理や表示制御処理を担う。FPGAは主として画像処理を担う。

【0003】

PSD(位置検出素子)を用いた変位センサとしては、信号処理部と検出部とが分離独立したものが知られている(特許文献2参照)。検出部は投光用の光源と受光用のPSDとを含んでいる。PSDからはアナログ検出信号が出力される。このアナログ検出信号は、電気コードを介して、信号処理部へと送られる。信号処理部の中枢は、マイクロプロセッサを主体としたCPUにより構成されている。CPUは、検出部から送られてくるアナログ検出信号に基づいて距離を算出する。信号処理部同士は、隣接状態において、中継ユニットを介してコネクタ接続される。信号処理部は、自己が算出した距離データを、隣接する信号処理部へと、コネクタを介して伝送する。隣接する信号処理部は、送られてきた距離データと自己が算出した距離データとを用いて段差距離等を演算する。

【先行技術文献】

【特許文献】

【0004】

【特許文献1】特開2002−357408(特に図4)

【特許文献2】特開2002−286413

【発明の概要】

【発明が解決しようとする課題】

【0005】

特許文献1に記載の変位センサにあっては、信号処理ユニットにFPGAが含まれているため、高度な画像処理も行うことができる。しかし、隣接する信号処理ユニット間におけるデータ伝送の機能は存在しない。そのため、複数のセンサヘッド又は信号処理ユニットの相互連携動作を行うことはできない。

【0006】

特許文献2に記載の変位センサにあっては、隣接信号処理部間におけるデータ伝送機能は有するが、これはCPU間通信であるため、伝送容量が限られる。検出周期に合わせるなどのために速い周期でデータ伝送したい場合に、距離の算出データのような演算結果の値は送れるが、データ量の多い波形データや画像データを送ることはできない。

【0007】

この発明は、このような従来の問題点に着目してなされたものであり、その目的とするところは、他のセンサコントローラとの間で波形データや画像データのような大容量データを短い時間で(例えば速い周期で)相互に伝送し、伝送されたデータを用いて様々な連携動作を行うことができるようにしたセンサコントローラ(例えば、センサの信号処理ユニット)を提供することにある。

【課題を解決するための手段】

【0008】

本発明のセンサコントローラは、1つのユニットとして構成される。このセンサコントローラには、プログラム可能な論理回路とセンサコントローラの動作を制御するCPUとを有する制御部と、他のセンサコントローラとの接続に用いることのできるユニット間コネクタと、制御部とユニット間コネクタとの間の信号伝送経路であって、プログラム可能な論理回路とユニット間コネクタとの間に設けられたセンシングデータ伝送経路を含むユニット間経路と、を備えている。

【0009】

それにより、ユニット間コネクタに他のセンサコントローラが接続されたときに、プログラム可能な論理回路と当該他のセンサコントローラのプログラム可能な論理回路との間でセンシングデータの伝送を行うことができるようにされている。

【0010】

このような構成によれば、他のセンサコントローラとの間でセンシングデータの伝送を高速に行うことが容易となる。また、制御部にはプログラム可能な論理回路が含まれていることから、開発過程におけるハードウェア構成の変更が少なくて済み、センサコントローラのメーカにとって開発(試作、設計変更)が容易となる。また、メーカにとっては、機能(特に、ハードウェア処理に依存する機能)の異なるシリーズ製品の品揃えを容易にするプラットフォームが提供される。

【0011】

ここで、この明細書における『プログラム可能な論理回路』は、ハードウェア回路をプログラムすることのできる集積回路である。集積回路の中に回路をプログラムすることのできる部分と回路が固定的に形成されている部分とがある場合には、回路をプログラムすることのできる部分がプログラム可能な論理回路である。プログラム可能な論理回路は、複数の集積回路によって構成してもよい。ハードウェア回路をプログラムすることのできる集積回路は、PLD(Programmable Logic Device)、FPGA(Field Programmable Gate Array)、CPLD(Complex PLD)等の名称で市場に提供されており、いずれも本発明に用いることができる。これらの集積回路の一例は、積和回路、ルックアップテーブル、フリップフロップ、メモリ、配線ライン、配線間のスイッチ等の回路要素を組み合わせることにより、デバイス間の接続、データ通信、シグナルプロセッシング、データ表示、タイミングとコントロール操作、その他通常、システムに含まれる機能の殆ど全てを実行するようにプログラムすることができるものである。

【0012】

この明細書における『センシングデータ』は、一般にセンサヘッドが出力する映像信号、電圧値、電圧波形のような生データと、生データを演算処理して得られた特徴量、判定結果のような加工済みデータとのいずれをも指す。

【0013】

本発明のセンサコントローラのユニット間コネクタは、第1ユニット間コネクタ及び第2ユニット間コネクタからなるものとすることができる。また、ユニット間経路は、第1ユニット間コネクタに接続する第1ユニット間経路と第2ユニット間コネクタに接続する第2ユニット間経路とからなるものとすることができる。この場合に、第1ユニット間経路に含まれるセンシングデータ伝送経路と第2ユニット間経路に含まれるセンシングデータ伝送経路とは、プログラム可能な論理回路の外部において互いに分離しているようにすることができる。

【0014】

このような構成によれば、必要に応じて第1ユニット間コネクタ側のセンシングデータの伝送と第2ユニット間コネクタ側のセンシングデータの伝送とを独立に行うことができる。

【0015】

本発明のセンサコントローラは、センシングデータを対象とした処理内容が変化するように、プログラム可能な論理回路の回路データの少なくとも一部を変更する手段又はプログラム可能な論理回路に設定するパラメータを変更する手段を備えていてもよい。

【0016】

このような構成によれば、センシング目的に応じてセンサコントローラのハードウェア処理に依存するセンシングデータの処理内容(特にはデータ伝送経路及び/又は演算処理内容)を変更することができる。特に、複数のセンサコントローラを連係して動作させるセンシングシステムを構築する場合に、少ない機種数のセンサコントローラで検出目的に応じた多様なセンシングシステムを構築することが可能となる。ユーザにとって、センサコントローラの機能の詳細を購入前に確定する必要がなく、試行錯誤しながらセンシングシステムの機能を最適化していくことが可能となる。

【0017】

本発明のセンサコントローラは、第1クロック信号を出力する発振器と、ユニット間コネクタから入力される第2クロック信号を伝送するクロック経路と、第1クロック信号及び第2クロック信号のいずれかを選択してプログラム可能な論理回路に与えるクロック切替回路と、をさらに備えるものであってもよい。

【0018】

このような構成によれば、プログラム可能な論理回路は、自ユニットの発振器が出力するクロック信号を用いて動作することが可能であり、接続された他のセンサコントローラから得られるクロック信号を用いて動作することも可能である。自ユニットの発振器が出力するクロック信号を用いて動作する場合のセンサコントローラは、他のセンサコントローラと接続せずに単体で動作することがきる。他のセンサコントローラから得られるクロック信号を用いる場合は、当該他のセンサコントローラとの間でプログラム可能な論理回路のクロックが同期しているので、センシングデータを高速に伝送することがいっそう容易になる。クロック切替回路をプログラム可能な論理回路の中に設け、選択したクロック信号をプログラム可能な論理回路の中の必要な部分に与えるようにしてもよい。

【0019】

本発明のセンサコントローラは、第1ユニット間コネクタ及び第2ユニット間コネクタを備える場合において、第1クロック信号を出力する発振器と、第1ユニット間コネクタから入力される第2クロック信号を伝送する第1クロック経路と、第1クロック信号及び第2クロック信号のいずれかを選択してプログラム可能な論理回路に与えるクロック切替回路と、選択されたクロック信号を第2ユニット間コネクタに出力するための第2クロック経路と、をさらに備えるようにしてもよい。

【0020】

このようなセンサコントローラを用いれば、3台以上のセンサコントローラが直列に接続されたセンシングシステムであって、すべてのセンサコントローラのプログラム可能な論理回路に共通のクロック信号が与えられるセンシングシステムを構築することができる。

【0021】

本発明のセンサコントローラは、ユニット間経路中に、CPUと接続されるデータ伝送経路をさらに備え、それにより、ユニット間コネクタに他のセンサコントローラが接続されたときに、CPUと当該他のセンサコントローラのCPUとの間でデータ伝送を行うことができるようにしてもよい。

【0022】

このような構成によれば、プログラム可能な論理回路同士の間のデータ伝送経路とは別に、CPU同士の間のデータ伝送経路を設けることにより、データ伝送についての役割分担が可能となる。

【0023】

本発明のセンサコントローラは、センサヘッドとの接続に用いることのできるセンサヘッド接続部と、プログラム可能な論理回路とセンサヘッド接続部との間を繋いでセンシングデータを伝送するセンサヘッド経路と、をさらに備えていてもよい。

【0024】

このような構成によれば、自ユニットに接続されるセンサヘッドから直接にデータを取得して、様々なセンシング動作を行うことができる。ここで、センサヘッド接続部は、センサヘッドコネクタとして構成することができる。センサヘッドコネクタは、センサコントローラのケースに固定して設けることができるし、センサコントローラのケースから引き出されたケーブルの先に設けることもできる。センサヘッドコネクタを設けずにセンサコントローラとセンサヘッドとをケーブルで直接接続する場合には、センサヘッド接続部は、センサコントローラとセンサヘッドとを繋ぐケーブルである。センサコントローラとセンサヘッドとが無線通信によって接続される場合には、センサヘッド接続部は、センサコントローラに設けられる無線通信の送受信部である。

【0025】

このとき、プログラム可能な論理回路にプログラムされる回路としては、ユニット間経路又はセンサヘッド経路を経由して取得されたセンシングデータを対象として演算処理を行うための演算処理回路と、ユニット間経路及びセンサヘッド経路のいずれかを選択的に演算処理回路に接続するデータ経路切替回路と、を含んでいてもよい。

【0026】

ここで、『プログラム可能な論理回路にプログラムされる回路』は、センサコントローラを起動していないときにもプログラム可能な論理回路にプログラムされた状態が維持されている回路と、センサコントローラが起動した後にセンサコントローラが有する記憶手段からプログラム可能な論理回路に回路データがロードされることによりプログラムされる回路との、両方を含む概念である。

【0027】

本発明のセンサコントローラは、プログラム可能な論理回路にプログラムされる回路としては、ユニット間経路を経由して取得されたセンシングデータを対象として演算処理を行うための演算処理回路をさらに含み、それにより、ユニット間コネクタに他のセンサコントローラが接続されたときに、当該他のセンサコントローラから取得したセンシングデータを対象に演算処理を行うことができるようにしてもよい。

【0028】

本発明のセンサコントローラは、プログラム可能な論理回路には記憶手段が接続されており、プログラム可能な論理回路にプログラムされる回路は、ユニット間経路を経由して取得されたセンシングデータを前記記憶手段に格納するためのデータ経路を含み、それにより、ユニット間コネクタに他のセンサコントローラが接続されたときに、当該他のセンサコントローラから取得したセンシングデータを記憶することができるようにしてもよい。

【0029】

次に、本発明の第1のセンシングシステムは、それぞれ1つのユニットとして構成された複数のセンサコントローラが直列に接続されたものである。このセンシングシステムにおける各センサコントローラは、プログラム可能な論理回路とセンサコントローラの動作を制御するCPUとを有する制御部と、他のセンサコントローラとの接続に用いることのできるユニット間コネクタと、制御部とユニット間コネクタとの間の信号伝送経路であって、プログラム可能な論理回路とユニット間コネクタとの間に設けられたセンシングデータ伝送経路を含むユニット間経路と、を備え、それにより、ユニット間コネクタに他のセンサコントローラが接続されたときに、プログラム可能な論理回路と当該他のセンサコントローラのプログラム可能な論理回路との間でセンシングデータの伝送を行うことができるようにしたものである。このセンシングシステムにおける少なくとも1つのセンサコントローラは、センサヘッドとの接続に用いることのできるセンサヘッド接続部と、プログラム可能な論理回路とセンサヘッド接続部との間を繋いでセンシングデータを伝送するセンサヘッド経路と、をさらに備え、そのセンサコントローラの少なくとも1つにはセンサヘッドが接続される。このセンシングシステムは、センサヘッドが接続されたセンサコントローラの内の1台である第1のセンサコントローラから、他のセンサコントローラの内の1台である第2のセンサコントローラにセンシングデータが伝送されるものである。

【0030】

第1のセンシングシステムにおいて、各センサコントローラのユニット間コネクタは、第1ユニット間コネクタ及び第2ユニット間コネクタからなるものとすることができる。また、各センサコントローラのユニット間経路は、第1ユニット間コネクタに接続する第1ユニット間経路と第2ユニット間コネクタに接続する第2ユニット間経路とからなるものとすることができる。この場合に、第1ユニット間経路に含まれるセンシングデータ伝送経路と第2ユニット間経路に含まれるセンシングデータ伝送経路とは、プログラム可能な論理回路の外部において互いに分離しているようにすることができる。

【0031】

第1のセンシングシステムにおいて、第1のセンサコントローラから第2のセンサコントローラに伝送されるセンシングデータは、第1のセンサコントローラに接続されたセンサヘッドから出力されるセンシングデータであってもよい。

【0032】

さらに、第1のセンサコントローラは、センサヘッドとの接続に用いることのできるセンサヘッド接続部と、プログラム可能な論理回路とセンサヘッド接続部との間を繋いでセンシングデータを伝送するセンサヘッド経路とをさらに備え、プログラム可能な論理回路の中に、センシングデータを対象として演算処理を行うための演算処理回路と、センサヘッド経路を経由して取得されたセンシングデータを演算処理回路及びユニット間経路に分岐させて与えるデータ経路とを含むセンサコントローラであり、第2のセンサコントローラのプログラム可能な論理回路にプログラムされる回路は、ユニット間経路を経由して取得されたセンシングデータを対象として演算処理を行うための演算処理回路を含み、それにより、センシングシステムは同一のセンシングデータを対象に並列に演算処理することができるようにしてもよい。

【0033】

第1のセンシングシステムにおいて、第1のセンサコントローラは、センサヘッドとの接続に用いることのできるセンサヘッド接続部と、プログラム可能な論理回路とセンサヘッド接続部との間を繋いでセンシングデータを伝送するセンサヘッド経路とをさらに備え、プログラム可能な論理回路の中に、センシングデータを対象とした演算処理を行うための演算処理回路を含むセンサコントローラであり、第1のセンサコントローラから第2のセンサコントローラに伝送されるセンシングデータは、第1のセンサコントローラに接続されたセンサヘッドから出力されたセンシングデータを、第1のセンサコントローラが演算処理した結果であるセンシングデータであってもよい。

【0034】

第1のセンシングシステムにおいて、第2のセンサコントローラのプログラム可能な論理回路にプログラムされる回路は、ユニット間経路を経由して取得されたセンシングデータを対象として演算処理を行うための演算処理回路を含むものであってもよい。

【0035】

第1のセンシングシステムにおいて、第2のセンサコントローラのプログラム可能な論理回路には記憶手段が接続されており、第2のセンサコントローラのプログラム可能な論理回路にプログラムされる回路はユニット間経路を経由して取得されたセンシングデータを前記記憶手段に格納するためのデータ経路を含むものであってもよい。

【0036】

第1のセンシングシステムにおいて、少なくとも1つのセンサコントローラは、クロック信号を出力する発振器と、ユニット間経路中のクロック信号の伝送経路とを備え、クロック信号をプログラム可能な論理回路とユニット間経路中のクロック信号の伝送経路とに対して同時に出力可能とされ、他のすべてのセンサコントローラは、ユニット間経路中にプログラム可能な論理回路に接続し得るクロック信号の伝送経路を備え、それにより、センシングシステム中のすべてのセンサコントローラが共通のクロック信号によりプログラム可能な論理回路を駆動することができるようにしてもよい。

【0037】

このような構成によれば、センシングデータを送信するセンサコントローラとそのデータを受信するセンサコントローラとの間でプログラム可能な論理回路のクロックが同期しているので、センシングデータを高速に伝送することがいっそう容易になる。

【0038】

第1のセンシングシステムにおいて、各センサコントローラは第1ユニット間コネクタ及び第2ユニット間コネクタを備える場合において、すべてのセンサコントローラは、第1クロック信号を出力する発振器と、第1ユニット間コネクタから入力される第2クロック信号を伝送する第1クロック経路と、第1クロック信号及び第2クロック信号のいずれかを選択してプログラム可能な論理回路に与えるクロック切替回路と、選択されたクロック信号を第2ユニット間コネクタに出力するための第2クロック経路と、をさらに備え、センサコントローラの列の端に位置して第2ユニット間コネクタにのみ他のセンサコントローラが接続されているセンサコントローラにおいては、クロック切替回路が第1クロック信号を選択し、他のすべてのセンサコントローラにおいては、クロック切替回路が第2クロック信号を選択することにより、センシングシステム中のすべてのセンサコントローラが共通のクロック信号によりプログラム可能な論理回路を駆動することができるようにしてもよい。

【0039】

このような構成によれば、クロック信号をセンサコントローラを通して共通に用いるセンシングシステムに、自ユニットの発振器を用いて単体でも動作できるセンサコントローラを組み込むことができ、センシングシステム専用の(自ユニットの発振器を持たない)センサコントローラを用意する必要がない。

【0040】

第1のセンシングシステムにおいて、すべてのセンサコントローラは、ユニット間経路中に、CPUと接続されるデータ伝送経路を備え、それにより、直接接続されたセンサコントローラのCPU同士の間でデータ伝送を行うことができるようにしてもよい。

【0041】

本発明の第2のセンシングシステムは、それぞれ1つのユニットとして構成された複数のセンサコントローラが直列に接続されたものであって、このセンシングシステムにおいて、各センサコントローラは、プログラム可能な論理回路とセンサコントローラの動作を制御するCPUとを有する制御部と、他のセンサコントローラとの接続に用いることのできるユニット間コネクタと、制御部とユニット間コネクタとの間の信号伝送経路であって、プログラム可能な論理回路とユニット間コネクタとの間に設けられたセンシングデータ伝送経路を含むユニット間経路と、を備え、それにより、ユニット間コネクタに他のセンサコントローラが接続されたときに、プログラム可能な論理回路と当該他のセンサコントローラのプログラム可能な論理回路との間でセンシングデータの伝送を行うことができるようにしたものであり、少なくとも1つのセンサコントローラは、センサヘッドとの接続に用いることのできるセンサヘッド接続部と、プログラム可能な論理回路とセンサヘッド接続部との間を繋いでセンシングデータを伝送するセンサヘッド経路と、をさらに備え、そのセンサコントローラの少なくとも1つにはセンサヘッドが接続されており、各センサコントローラの前記制御部は、トリガ信号が与えられることによりいずれかのセンサヘッドから出力されたセンシングデータを対象としたセンシング処理を行い、センシング処理が完了したときに処理完了状態となり、センシング対象についての判定結果が特定の結果であるときに特定判定状態となるものであり、各センサコントローラは、処理完了状態であるかどうか及び特定判定状態であるかどうかに関連する信号を接続された他のセンサコントローラとの間で送信及び/又は受信することが可能であり、それにより、少なくとも1つの特定センサコントローラは、すべてのセンサコントローラが処理完了状態であること及びすべてのセンサコントローラが特定判定状態であることを検出可能にされており、前記特定センサコントローラは、前記検出がされたときに、統合判定信号を出力するものである。

【0042】

このような構成によれば、各センサコントローラにトリガ信号が与えられた後、各センサコントローラの判定結果が出そろった後に、すべてのセンサコントローラの判定結果が特定の結果であるときに、特定センサコントローラから統合判定信号が出力される。したがって、センシングシステムから統合的な判定結果を得ることができる。しかも、センサコントローラ間で判定結果が出るタイミングがずれる場合にも、判定結果が出そろうまでの過渡的な時期において統合的な判定結果が不安定になることを避けることができる。典型的には、判定結果は合格又は不合格のいずれかであり、特定判定状態は合格の状態である。この場合には、統合判定信号が出力されることは、すべてのセンサコントローラが合格の判定をしたことを意味する。トリガ信号は、各センサコントローラに共通に与えてもよく、個別に与えてもよい。各センサコントローラは、1つのセンシング処理が完了すると、次のセンシング処理のためのトリガ信号を受け付けることが可能である待機状態となるようにしてもよい。この場合は、この待機状態を処理完了状態として扱うことができる。

【0043】

第2のセンシングシステムにおいて、トリガ信号は、センシングシステムの外部からセンサコントローラの1つに入力され、そのセンサコントローラからユニット間コネクタを経由して他の各センサコントローラに入力されるようにしもよい。

【0044】

このような構成によれば、センシングシステムに接続するトリガ信号線が1つだけでよい。トリガ信号を入力するセンサコントローラを、統合判定信号を出力するセンサコントローラと一致させれば、配線作業がさらに容易となる。

【0045】

第2のセンシングシステムにおいて、センサコントローラの列の第1の端に位置するセンサコントローラと、第2の端に位置し統合判定信号を出力する特定センサコントローラとを含み、第1の端に位置するセンサコントローラは、第2の端側に接続されているセンサコントローラに対し、処理完了状態であるときに完了信号を出力し、特定判定状態であるときに特定判定信号を出力するものであり、センサコントローラの列の第2の端に位置する特定センサコントローラは、第1の端側に接続されているセンサコントローラから完了信号を入力すること、自ユニットが処理完了状態であること、第1の端側に接続されているセンサコントローラから特定判定信号を入力すること、及び自ユニットが特定判定状態であること、を条件として統合判定信号を出力するものであってもよい。

【0046】

このセンシングシステムは、さらにセンサコントローラの列の第1の端及び第2の端以外に位置するセンサコントローラを含み、第1の端及び第2の端以外に位置するセンサコントローラは、第1の端側に接続されているセンサコントローラから完了信号を入力し、かつ、自ユニットが処理完了状態であるときに、第2の端側に接続されているセンサコントローラに完了信号を出力するとともに、第1の端側に接続されているセンサコントローラから特定判定信号を入力し、かつ、自ユニットが特定判定状態であるときに、第2の端側に接続されているセンサコントローラに特定判定信号を出力するものであってもよい。

【0047】

このような構成によれば、特定センサコントローラは、自ユニットに接続されているセンサコントローラから完了信号を入力することにより他のすべてのセンサコントローラが処理完了状態であることを知ることができ、さらに自ユニットも処理完了状態であればすべてのセンサコントローラが処理完了状態であると決定できる。また、特定センサコントローラは、自ユニットに接続されているセンサコントローラから特定判定信号を入力することにより他のすべてのセンサコントローラが特定判定状態であることを知ることができ、さらに自ユニットも特定判定状態であればすべてのセンサコントローラが特定判定状態であると決定できる。特定センサコントローラは、すべてのセンサコントローラが処理完了状態であり、かつ、すべてのセンサコントローラが特定判定状態であるときに、統合判定信号を出力する。

【0048】

第2のセンシングシステムにおいて、センサコントローラの列の第1の端に位置するセンサコントローラと、第2の端に位置し統合判定信号を出力する特定センサコントローラと、第1の端及び第2の端以外に位置するセンサコントローラとを含み、第1の端に位置するセンサコントローラは、第2の端側に接続されているセンサコントローラに対し、特定判定状態であるときに特定判定信号を出力し、処理完了状態であるときに完了信号を出力するものであり、センサコントローラ列の第1の端及び第2の端以外に位置するセンサコントローラは、第1の端側に接続されているセンサコントローラから完了信号を入力し、かつ、自ユニットが処理完了状態であるときに、第2の端側に接続されているセンサコントローラに完了信号を出力するとともに、第1の端側に接続されているセンサコントローラから入力した1又は複数の特定判定信号を第2の端側に接続されているセンサコントローラに中継して出力し、それと並列に、自ユニットが特定判定状態であるときに第2の端側に接続されているセンサコントローラに特定判定信号を出力するものであり、センサコントローラの列の第2の端に位置する特定センサコントローラは、第1の端側に接続されているセンサコントローラから完了信号を入力すること、自ユニットが処理完了状態であること、第1の端側に接続されているセンサコントローラから自ユニット以外のすべてのセンサコントローラについての特定判定信号を入力すること、及び自ユニットが特定判定状態であること、を条件として統合判定信号を出力するものであってもよい。

【0049】

このような構成によれば、特定センサコントローラは、自ユニットに接続されているセンサコントローラから完了信号を入力することにより他のすべてのセンサコントローラが処理完了状態であることを知ることができ、さらに自ユニットも処理完了状態であればすべてのセンサコントローラが処理完了状態であると決定できる。また、特定センサコントローラは、自ユニットに接続されているセンサコントローラから自ユニット以外の各センサコントローラの特定判定信号を入力することにより自ユニット以外のすべてのセンサコントローラの判定結果を知ることができ、さらに自ユニットの判定結果とあわせて、すべてのセンサコントローラが特定判定状態であるかどうかを決定できる。特定センサコントローラは、すべてのセンサコントローラが処理完了状態であり、かつ、すべてのセンサコントローラが特定判定状態であるときに、統合判定信号を出力する。

【0050】

第2のセンシングシステムを構成するセンサコントローラとしては、第1ユニット間コネクタ及び第2ユニット間コネクタを備える本発明のセンサコントローラであって、さらに以下の特徴を有するものを用いることができる。

【0051】

センシングシステムにおけるセンサコントローラの位置にかかわらず共通する特徴として、センサコントローラの制御部は、トリガ信号が与えられることによりセンシング処理を行い、センシング処理が完了したときに処理完了状態となり、センシング対象についての判定結果が特定の結果であるときに特定判定状態となるものである。

【0052】

さらに次の特徴を有するセンサコントローラは、センシングシステムの一端に配置され、統合判定信号を出力する特定センサコントローラとして用いることができる。すなわち、センサコントローラの制御部は、第1ユニット間コネクタを介して他のセンサコントローラが処理完了状態であることを表す完了信号を入力すること、自ユニットが処理完了状態であること、第1ユニット間コネクタを介して他のセンサコントローラが特定判定状態であることを表す特定判定信号を入力すること、及び自ユニットが特定判定状態であること、を条件として統合判定信号を出力する処理を行うものである、又はセンサコントローラは制御部にそのような処理を行わせるように設定するための手段を備えるものである。

【0053】

次の特徴を有するセンサコントローラは、センシングシステムの両端以外の位置に配置されるセンサコントローラとして用いることができる。すなわち、センサコントローラの制御部は、第1ユニット間コネクタを介して第1完了信号を入力すること及び自ユニットが処理完了状態であることを条件として、第2ユニット間コネクタを介して第2完了信号を出力し、さらに、第1ユニット間コネクタを介して第1特定判定信号を入力すること及び自ユニットが特定判定状態であることを条件として、第2ユニット間コネクタを介して第2特定判定信号を出力する処理を行うものである、又はセンサコントローラは制御部にそのような処理を行わせるように設定するための手段を備えるものである。

【0054】

次の特徴を有するセンサコントローラは、センシングシステムの特定センサコントローラと反対側の端に配置されるセンサコントローラとして用いることができる。すなわち、センサコントローラの制御部は、処理完了状態であるときに、第2ユニット間コネクタを介して完了信号を出力し、さらに、特定判定状態であるときに、第2ユニット間コネクタを介して特定判定信号を出力する処理を行うものである、又はセンサコントローラは制御部にそのような処理を行わせるように設定するための手段を備えるものである。

【0055】

いずれの位置に配置されるセンサコントローラも、外部からユニット間コネクタを介さずに外部トリガ信号を入力可能とされ、かつ、ユニット間コネクタを介してユニット間トリガ信号を入力可能とされたものであってもよく、外部トリガ信号及びユニット間トリガ信号のいずれかを選択し、選択したトリガ信号に基づき、前記制御部に内部トリガ信号を出力するトリガ制御回路をさらに備えたものとすることができる。

【0056】

さらに、センサコントローラの内部に、一方のユニット間コネクタに入力されたユニット間トリガ信号を他方のユニット間コネクタに伝送する信号経路を設けてもよい。

【0057】

トリガ制御回路は、さらに、外部トリガ信号を選択したときには、外部トリガ信号に基づきユニット間トリガ信号を出力するものであってもよい。

【0058】

第2のセンシングシステムを構成するセンサコントローラとしては、第1ユニット間コネクタ及び第2ユニット間コネクタを備える本発明のセンサコントローラであって、さらに次の特徴を有するものを用いることができる。すなわち、センサコントローラの制御部は、トリガ信号が与えられることによりセンシング処理を行い、センシング対象についての判定結果が特定の結果であるときに特定判定状態となるものであり、さらに、第1ユニット間コネクタを介して第1特定判定信号を入力すること及び自ユニットが特定判定状態であることを条件として、第2ユニット間コネクタを介して第2特定判定信号を出力する処理を行うものである、又はセンサコントローラは制御部にそのような処理を行わせるように設定するための手段を備えるものである。

【0059】

以上述べた中で、『そのような処理を行わせるように設定する』ことには、プログラム可能な論理回路の中の回路をそのような処理を行うように設定すること、そのような処理を行うプログラムを選択すること、及びそのような処理を行うようにプログラムに与えられるパラメータを設定することが含まれる。『設定するための手段』には、設定の指示を与えるためのセンサコントローラに設けられた操作スイッチ、設定のためにセンサコントローラが提示するメニュー、センサコントローラの外部から設定の指示を与えるための信号を受け付けることが含まれる。

【発明の効果】

【0060】

本発明によれば、波形データや画像データのような大容量データを短い時間で(例えば速い周期で)他のセンサコントローラとの間で伝送し、伝送されたデータを用いて様々な連携動作を行うことができるようにしたセンサコントローラ(例えば、センサの信号処理ユニット)を提供することができる。

【図面の簡単な説明】

【0061】

【図1】センサコントローラの外観斜視図である。

【図2】センサコントローラ連装状態の外観斜視図である。

【図3】センシング中のセンサヘッドの外観斜視図である。

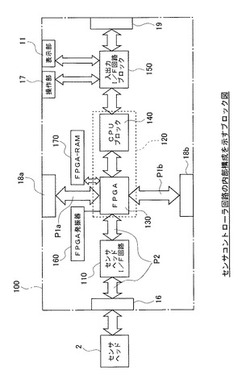

【図4】センサコントローラ回路の内部構成を示すブロック図である。

【図5】センサヘッド回路の詳細を示すブロック図である。

【図6】センサヘッドインタフェース回路の詳細を示すブロック図である。

【図7】他のセンサヘッドインタフェース回路の詳細を示すブロック図である。

【図8】FPGA及びCPUとユニット間コネクタとの接続関係を示す信号系統図である。

【図9】FPGA内部回路の詳細を示すブロック図である。

【図10】タイミング変換回路の詳細を示すブロック図である。

【図11】データ経路切替回路の詳細を示すブロック図である。

【図12】CPUブロックの詳細を示すブロック図である。

【図13】入出力インタフェース回路ブロックの詳細を示すブロック図である。

【図14】CPUのゼネラルフローチャート(単体動作時)である。

【図15】センサコントローラ回路(演算ユニット)の内部構成を示すブロック図である。

【図16】センシングシステムAの構成図である。

【図17】撮像素子の水平走査線上に得られる光強度分布を示すグラフである。

【図18】センシングシステムAの動作フローチャート(その1)である。

【図19】センシングシステムAの動作フローチャート(その2)である。

【図20】センシングシステムAの動作フローチャート(その3)である。

【図21】CPUによるセンシング処理のフローチャートである。

【図22】データの流れ(その1)である。

【図23】データの流れ(その2)である。

【図24】データの流れ(その3)である。

【図25】データの流れ(その4)である。

【図26】データの流れ(その5)である。

【図27】データの流れ(その6)である。

【図28】センサコントローラ(拡張メモリユニット)の内部構成を示すブロック図である。

【図29】センシングシステムBの構成図である。

【図30】撮像素子の水平走査線上に得られる光強度分布を示すグラフである。

【図31】センシングシステムBの動作フローチャート(その1)である。

【図32】変位センサ機能と視覚センサ機能とを併有するセンサヘッドの構造図である。

【図33】センサコントローラ回路の内部構成を示すブロック図である。

【図34】FPGA内部回路の詳細を示すブロック図である。

【図35】センシングシステムCのトリガ信号とOK信号についての構成図である。

【図36】センサコントローラ回路のOK信号に関する他の実施形態を示すブロック図である。

【図37】ユニット間I/F回路を有するセンサコントローラ回路の内部構成を示すブロック図である。

【図38】FPGAとその他の回路ブロックとを集積化した集積回路を有するセンサコントローラ回路の内部構成を示すブロック図である。

【発明を実施するための形態】

【0062】

以下に、この発明の好適な実施の一形態を添付図面に基づいて詳細に説明する。尚、本発明の及ぶ範囲は、以下の実施形態の記載に限定されないことは言うまでもなく、本発明の及ぶ範囲は特許請求の範囲の記載によって特定されることは言うまでもない。

【0063】

センサコントローラの外観斜視図が図1に示されている。同図に示されるように、センサコントローラ1はケース10を有する1つのユニットとして構成される。ケース10の正面10aは上下に略2分割されており、上部領域には表示部11が設けられている。この例にあっては、表示部11は、セグメント表示器11aと液晶式キャラクタ表示器11bとから構成されている。

【0064】

ケース10の正面10aの下部領域は、操作部配置領域とされている。この操作部配置領域には、下端縁を支点として手前に開く操作部蓋12が設けられている。操作部蓋12を開けると、その内部には、数値キー、ファンクションキー、スライドスイッチ等といった各種の操作子が配置されている。

【0065】

ケース10の左右の側面(図では右側面10dのみを示す)には、ユニット間コネクタが設けられている。これら左右のユニット間コネクタのそれぞれにはユニット間コネクタ蓋(図では、右側の蓋15のみを示す)が設けられている。図では、ユニット間コネクタ蓋(右)15は、閉じられた状態にあり、これがスライド式に開かれると、内部には第1のポートと第2のポートとが存在する。後述するように、これら第1及び第2のポートは、中継コネクタ片7の第1ポート7aと第2ポート7bとに対応する。

【0066】

ケース10の下面10cには、USBコネクタ13とRS−232Cコネクタ14とが設けられている。これらのコネクタ13,14はセンサコントローラ1とパソコン(PC)等との通信を行うために使用される。ケース10の下面10cからは外部接続コード3が引き出されている。この外部接続コード3内には電源線、外部入力線、外部出力線などが含まれている。これらの外部入出力線は例えばプログラマブル・コントローラ(PLC)等に接続される。後述するように、ケース10はDINレール5に装着可能とされ、DINレールクランパ8はその際に使用される。

【0067】

センサコントローラ連装状態の外観斜視図が図2に示されている。同図に示されるように、この例にあっては、3台のセンサコントローラ1a,1b,1cが、横一列に整列された状態で、DINレール5を介して、制御盤内の取付板等に装着されている。この装着状態における各ケースの上面10bには、センサヘッドコネクタ16がそれぞれ設けられている。このセンサヘッドコネクタ16には、後述するように、センサヘッド2から引き出されたケーブル4の先端に取り付けられたセンサヘッドコネクタ4aが装着される。

【0068】

センシング中のセンサヘッドの外観斜視図が図3に示されている。同図に示されるように、センサヘッド2のケース20からはセンサケーブル4が引き出され、その先端にはセンサヘッドコネクタ4aが取り付けられている。このセンサヘッドコネクタ4aが、センサコントローラ1のケース10のセンサヘッドコネクタ16に結合される。

【0069】

センサヘッド2のケース20内には、投光用の半導体レーザダイオード(LD)と受光用の2次元撮像素子(例えば、CCDイメージセンサ、CMOSイメージセンサ等)が設けられている。センサヘッド2は、半導体レーザダイオード(LD)から発せられたレーザ光をスリット光の状態にして対象物体6に照射する。図において、L1はスリット光の照射光である。対象物体6上の照射光像IMはセンサヘッド2内に設けられたレンズにより2次元撮像素子の受光面上に結像される。図中、L2はスリット光の反射光である。ここで、投光光軸と受光光軸とは所定の角度をなしている。スリット光の進行方向と垂直な面についてのスリット光の断面の長手方向は、投光光軸と受光光軸とがなす面に対して垂直となっている。センサヘッド2から対象物体6までの距離が変化すると、2次元撮像素子の受光面上のスリット光の像は、スリット光の長手方向と直交な方向に移動する。2次元撮像素子の水平走査方向は、スリット光の像の移動方向に合わせられている。2次元撮像素子の水平走査線上の光強度のピーク位置が対象物体までの距離を表している。スリット光を用いているので、スリット光の長手方向についての距離の分布を一挙に測定することができる。

【0070】

センサコントローラ回路の内部構成を示すブロック図が図4に示されている。同図に示されるように、センサコントローラ回路100は、センサヘッドコネクタ16と、第1ユニット間コネクタ(右)18aと、第2ユニット間コネクタ(左)18bと、外部I/Fコネクタ19とからなる4系統のコネクタを有している。センサヘッドコネクタ16には、先に図3を参照して説明したように、センサヘッド2から引き出されたセンサケーブル4の先端に取り付けられたセンサヘッドコネクタ4aが接続される。第1ユニット間コネクタ(右)18a及び第2ユニット間コネクタ(左)18bには、それぞれ右隣又は左隣にそれぞれ隣接する他のユニットが、図1に示される中継コネクタ片7を介して接続される。外部I/Fコネクタ19は、図1に示されるUSBコネクタ13、RS−232Cコネクタ14、及び外部接続コード3を総称するものであり、この外部I/Fコネクタ19を介してパソコン(PC)やプログラマブル・コントローラ(PLC)等への接続が行われる。

【0071】

センサコントローラ100の内部には、センサヘッドI/F回路110と、制御部120と、入出力I/F回路ブロック150と、FPGA発振器160と、FPGA−RAM170とが含まれている。

【0072】

制御部120と第1ユニット間コネクタ(右)18aとの間には、FPGA130と第1ユニット間コネクタ(右)18aとの間のセンシングデータ伝送経路を含む第1ユニット間経路P1aが設けられており、制御部120と第2ユニット間コネクタ(左)18bとの間には、FPGA130と第2ユニット間コネクタ(左)18bとの間のセンシングデータ伝送経路を含む、第2ユニット間経路P1bが設けられている。また、センサヘッドコネクタ16とFPGA130との間にはセンシングデータを伝送するセンサヘッド経路P2が設けられ、その途中にセンサヘッドI/F回路110が設けられている。

【0073】

制御部120は、プログラム可能な論理回路であるFPGA130とセンサコントローラの動作を制御するCPUブロック140とを有する。CPUブロック140には、マイクロプロセッサ(CPU)やその周辺回路が含まれている。FPGA130は、回路データをダウンロードすることによって回路構成をプログラム(コンフィグレーション)することが可能なLSI(大規模集積回路)である。

【0074】

FPGA130は、論理ブロック、スイッチマトリクス、クロスポイントスイッチの組み合わせによって、任意の論理回路を擬似的に実現する。論理ブロックは、メモリとマルチプレクサとを組み合わせたLUT(Look Up Table)によって、様々な論理を実現する。スイッチマトリクスとクロスポイントスイッチは、それぞれの論理ブロック間の接続を行うが、この接続自体もメモリによって制御される。また、FPGA130は、外部とデータのやり取りをするためにI/Oブロックを用いる。

【0075】

FPGAには、アンチフューズタイプ、EEPROMタイプ、フラッシュROMタイプ、SRAMタイプ等がある。アンチフューズタイプは、中の回路の接続点がフューズで出来ていて、不要な部分を焼き切って回路を構成し、他は半導体スイッチのオン/オフデータをメモリのデータによって決めるタイプである。

【0076】

本実施形態のFPGA130はSRAMタイプであり、電源を入れる度にFPGAチップへ回路データをダウンロードする必要がある。SRAMタイプに代えてEEPROMタイプやフラッシュROMタイプのFPGAを用いれば、回路データの消去や別の回路データのダウンロードをするまでは、電源を切ってもプログラムした回路構成を維持できる。

【0077】

FPGA−RAM170は、プログラム可能な論理回路に接続された『記憶手段』に相当する。本実施形態では、FPGA130の中の演算処理回路のワーキングメモリとしての高速性を重視してSRAMが用いられている。この記憶手段としては、高速性よりも大容量であることが重視される場合には、フラッシュメモリのような書き換え可能な半導体メモリやハードディスク装置等を用いることもできる。

【0078】

この例では、ユニット間コネクタ(18a,18b)及びユニット間経路(P1a,P1b)は左右両側に設けられているが、いずれか一方だけでも差し支えない。特に、センシングデータの伝送方向を固定した設計においては、機能的にデータ伝送の最上流や最下流に設置されることが予定される機種の場合には、接続が必要な側にだけユニット間コネクタ及びユニット間経路を設けることが考えられる。

【0079】

以下、センサヘッド回路200及びセンサコントローラ回路100の内部詳細説明を行うが、それらの説明は次の事項を前提としている。図示された信号又はデータの伝送経路は、1本の線で表されていても複数の線を意味する場合もある。『制御信号』の用語は、回路の動作を制御するために用いられる信号という広い意味であり、イネーブル信号、リード/ライト信号、アドレス信号、割込信号、切替信号、タイミング指示信号等を含む。

【0080】

センサヘッド回路の詳細を示すブロック図が図5に示されている。このセンサヘッド回路200は、図3に示されるセンサヘッド2内の電気回路である。同図に示されるように、センサヘッド回路200は、シリアル/パラレル変換回路210と、半導体レーザダイオード(LD)220と、発光ダイオード(LED)230と、2次元撮像素子240と、撮像素子駆動回路250と、センサヘッド発振器260と、パラレル/シリアル変換回路270と、センサヘッドROM280とを含んでいる。また、このセンサヘッド回路200は、センサケーブル4を介してセンサコントローラ1から供給される電源(+12V,0V)を受けて動作する。

【0081】

シリアル/パラレル変換回路210は、センサコントローラから送られてくる設定信号及び投光制御信号をシリアル/パラレル変換することによって、LD_ON(レーザ制御信号)、LED(センサLED制御信号)、DATA_OUT(センサ設定信号)を生成出力する。

【0082】

LD_ON(レーザ制御信号)を受けて、センシング用の投光に用いる光源であるLD220が駆動される。LED(センサLED制御信号)を受けて、センサヘッド2に設けられた図示しない表示器であるLED230が駆動される。DATA_OUT(センサ設定信号)は撮像素子駆動回路250に送られる。

【0083】

センサ設定信号は、CMOS2次元撮像素子の読み出す画素の領域の指定、シャッタスピード(電荷蓄積時間)の指定、一定周期で連続的に撮像するかセンサコントローラからのトリガを受けて撮像するかの撮像モード指定などを行うための信号である。

【0084】

2次元撮像素子240はこの例ではCMOS型が使用されている。尚、2次元撮像素子240としてはCCD型を用いることもできる。先に図3を参照して説明したように、LD220からの光はスリット光に変換された後、対象物体6に照射される。対象物体6上の照射光像IMはセンサヘッド内に設けられたレンズ(図示せず)により2次元撮像素子240上に結像される。投光光軸と受光光軸とは所定の角度をなしている。

【0085】

スリット光の進行方向と垂直な面についてのスリット光の断面の長手方向は、投光光軸と受光光軸とがなす面に対して垂直となっている。センサヘッドから対象物体までの距離が変化すると、2次元撮像素子240上のスリット光の像は、スリット光の長手方向と垂直な方向に移動する。2次元撮像素子240の水平走査方向は、スリット光の像の移動方向に合わせられている。2次元撮像素子240の水平走査線上の光強度のピーク位置が対象物体までの距離を表している。スリット光を用いているので、スリット光の長手方向についての距離の分布を一挙に測定することができる。

【0086】

2次元撮像素子240における撮像動作は、撮像素子駆動回路250から供給される制御信号に基づいて行われ、撮像の結果得られた出力は撮像素子駆動回路250へと送られる。

【0087】

撮像素子駆動回路250では、2次元撮像素子240から得られた出力に基づいて、DATA_IN(デジタル映像信号)、HD(水平同期信号)及びVD(垂直同期信号)を生成する。これら3つの信号は、パラレル/シリアル変換回路270を介してパラレル/シリアル変換された後、映像信号としてセンサコントローラ1へと送られる。

【0088】

以上述べた、シリアル/パラレル変換回路210、2次元撮像素子240、撮像素子駆動回路250、パラレル/シリアル変換回路270の動作は、センサヘッド発振器260から与えられるクロックに同期して行われる。また、センサヘッドROM280には、センサヘッドの型式データが記憶されている。

【0089】

次に、センサコントローラ回路100側の詳細について説明する。センサヘッドI/F回路の詳細を示すブロック図が図6に示されている。同図に示されるように、センサヘッドI/F回路110は、シリアル/パラレル変換回路111と、パラレル/シリアル変換回路112と、センサヘッドI/F発振器113とを含んでいる。

【0090】

シリアル/パラレル変換回路111は、センサケーブル4を介してセンサヘッド2から送られてくる映像信号を、シリアル/パラレル変換することによって、DATA_IN(センシングデータ)、HD(水平同期信号)、VD(垂直同期信号)を生成出力する。

【0091】

パラレル/シリアル変換回路112は、制御部120から送られてくるDATA_OUT(センサ設定信号)、LED(センサLED制御信号)、LD_ON(レーザ制御信号)を、パラレル/シリアル変換することによって、設定信号、投光制御信号を生成する。こうして生成された設定信号、投光制御信号は、センサケーブル4を介してセンサヘッド2へと送られる。

【0092】

尚、電源(+12V,0V)は、このセンサヘッドI/F回路110を経由してセンサヘッド回路200へと送られる。センサヘッド回路200のセンサヘッドROM280から読み出された型式データは、センサヘッドI/F回路110を経由して、制御部120へと送られる。

【0093】

他のセンサヘッドI/F回路の詳細を示すブロック図が図7に示されている。このセンサヘッドI/F回路110Aは、センサヘッドがアナログ映像信号を出力する場合に採用される。図において、A/D変換回路111Aは、センサケーブル4を介してセンサヘッド2から送られてくるアナログ映像信号を、A/D変換することによって、DATA_IN(センシングデータ)を生成する。

【0094】

バッファ112A,113Aは、センサケーブル4を介してセンサヘッド2から送られてくるHD(水平同期信号)及びVD(垂直同期信号)を、センサコントローラ回路100内の制御部120へと中継する。

【0095】

バッファ114A,115A,116Aは、センサコントローラ回路100の制御部120から送られてくるDATA_OUT(センサ設定信号)、LED(センサLED制御信号)、LD_ON(レーザ制御信号)を、センサヘッド2へと中継する。

【0096】

デジタル制御用センサヘッドI/F回路110と同様に、センサヘッドI/F回路110Aは、型式データ及び電源(+12V,0V)を中継する。

【0097】

FPGA及びCPUとユニット間コネクタとの接続関係を示す信号系統図が図8に示されている。ユニット間データの伝送経路(センシングデータ伝送経路)は、8本のパラレルデータ線である。これにより高速なデータ伝送が実現される。

【0098】

ユニット間制御信号には、通信先(例えばデータの出力を要求する相手)のユニットを特定するためのユニット番号を表す信号が含まれる。ユニット間データの伝送経路とユニット間制御信号の伝送経路とを複数組設けることにより、データ伝送をさらに高速化したり、異なるデータを並行して伝送することを可能にしてもよい。

【0099】

本実施形態では、ユニット間データの伝送は双方向であるが、例えば右側を入力専用、左側を出力専用(又はその反対)というように、伝送方向を固定してもよい。そのように伝送方向が決まっていると、センサコントローラを複数接続した場合の伝送設定が容易になる。センサコントローラ内の回路の簡素化も図ることができる。

【0100】

CPU間通信はシリアル通信である。ユニット間データの伝送に比べて通信速度が遅いので、画像データを演算処理して得られた演算結果の値のようにデータ量の少ないセンシングデータの送信や、センサコントローラのユニット番号設定のような初期設定や、動作中の種々の設定変更のための通信に適している。通信速度が遅い代わりに、ソフトウェアによって自由に通信内容を決めることができるので、通信内容の柔軟性に富んでいる。このような通信を、ユニット間データの高速伝送を妨げることなく行うことができる。尚、CPU間通信の伝送経路は、FPGA130の中を経由するようにしてもよい。

【0101】

FPGA内部回路の詳細を示すブロック図が図9に示されている。同図に示されるように、FPGA130には、タイミング変換回路131と、データ経路切替回路132と、演算処理回路133と、レジスタ134と、クロック切替回路135と、タイミング生成回路136と、バッファ137とが含まれている。

【0102】

レジスタ134は、FPGA130内の回路やFPGA130の入出力線とCPUバスとの間のデータ伝送に用いられるメモリである。

【0103】

クロック切替回路135は、FPGA発振器160が出力するクロック信号(第1クロック信号)か、他のセンサコントローラから第1ユニット間コネクタ18aを経由して入力されるユニット間クロック信号(第2クロック信号)かのいずれかをCPUブロック140からのクロック切替信号による指示に従い選択してFPGA130内部に内部クロック信号として供給する。さらに、選択されたクロック信号は第2ユニット間コネクタ18bに出力される。

【0104】

タイミング生成回路136は、タイミング変換回路131、データ経路切替回路132、演算処理回路133のそれぞれに対して制御信号を出力することにより、これらの回路が協調したタイミングで動作できるように、それぞれの回路の動作を調整する。

【0105】

演算処理回路133は、センシング目的に応じてその内容が設計される。センシングデータが画像データである場合は、ノイズ除去、エッジ強調、階調変換、二値化、平均値演算、ピーク位置抽出、面積抽出、重心位置抽出などを行う演算回路ブロックを組み合わせて構成される。演算対象とするセンシングデータは画像データには限らず、時系列的に取得される多値データであってもよい。例えば、PSD(Position Sensitive Device)を用いた変位センサの出力は、時系列的に変化するアナログ信号として得られるが、これを一定周期でデジタル変換した(サンプリングした)データを対象として、ノイズ除去、特徴量抽出などを行う演算回路ブロックを組み合わせた演算処理回路を構成してもよい。

【0106】

この場合にも、FPGA130は演算内容に応じて配線されたハードウェアにより演算処理を行うため、CPUとプログラムにより演算を行う場合に比べて高速な演算が可能であるから、サンプリング周期を小さくすることが可能となり、これによって短い時間のうちに生起する現象をセンシングの対象とすることができる。

【0107】

演算処理回路における演算は、FPGA130に接続されたFPGA−RAM170をワーキングメモリとして利用しながら行うようにしてもよい。演算処理回路133における演算は、例えば1フレームの画像のような或るまとまった量のデータを単位として行うようにしてもよいし、走査線数本分のラインバッファを利用するなどして、連続的に取得されるデータに対して順次処理を行い、その結果を連続的に出力するパイプライン方式の演算とすることもできる。

【0108】

FPGA内部回路に含まれるタイミング変換回路の詳細を示すブロック図が図10に示されている。同図に示されるように、タイミング変換回路131は、書込制御回路1311と、デュアルポートラインメモリ1312と、読出制御回路1313とを含んでいる。このタイミング変換回路131の機能は、センサヘッド2側のクロックの速度とセンサコントローラ1側のクロックの速度との相違を許容しつつ、センサコントローラに対して最適なタイミングでデータの読み出しを可能とするものである。すなわち、このタイミング変換回路131にあっては、デュアルポートラインメモリ1312への書き込みはセンサヘッドI/F回路110と共通のクロック信号(CLK_IN)により制御され、デュアルポートラインメモリ1312からの読み出しはFPGA130の内部クロック信号により制御される。

【0109】

データ経路切替回路の詳細を示すブロック図が図11に示されている。同図に示されるように、データ経路切替回路132は、制御線切替回路(A)1321と、制御線切替回路(B)1322と、制御線切替回路(C)1323と、データ線切替回路(A)1324と、データ線切替回路(B)1325と、データ線切替回路(C)1326とを含んでいる。

【0110】

各データ線切替回路1324〜1326及び各制御線切替回路1321〜1323は、CPUブロック140からのデータ経路切替信号により、その入力と出力との接続関係が決定される。

【0111】

例えば、データ線切替回路(A)1324は、ユニット間データ(右)の線(この実施形態では8本のパラレルデータ線)を、データ線切替回路(B)1325及び(C)1326に接続する線(データ線切替回路(A)下方最右端の線、実際にはこれも8本のパラレルデータ線)に接続することができ、また、どこにも接続しないこともできる。さらに、データ線切替回路(A)1324の下方から入力する3本の線(実際にはそれぞれ8本のパラレルデータ線)のいずれかをユニット間データ線(右)の線に接続することができる。

【0112】

データ線切替回路(A)、(B)、(C)1324〜1326を適切に制御することにより、タイミング変換回路131から、すなわちセンサヘッド2から入力したデータをユニット間データ(右)、ユニット間データ(左)、演算処理回路133のうちの1つ、2つ、又は3つ全てに出力することができる。また、どこにも出力しないこともできる。

【0113】

ユニット間データ(右)から入力したデータは、ユニット間データ(左)及び演算処理回路133の両方又は一方に出力することができるし、何れにも出力しないこともできる。ユニット間データ(左)から入力したデータは、ユニット間データ(右)及び演算処理回路133の両方又は一方に出力することができる。何れにも出力しないこともできる。演算処理回路133から入力したデータは、ユニット間データ(右)及びユニット間データ(左)の両方又は一方に出力することができる。何れにも出力しないこともできる。

【0114】

制御線切替回路(A)、(B)、(C)1321〜1323についても同様であるが、制御線切替回路1321〜1323についてはタイミング変換回路131から、すなわちセンサヘッド2からデータを入力する経路が存在しない。

【0115】

CPUブロックの詳細を示すブロック図が図12に示されている。同図に示されるように、CPUブロック140は、マイクロプロセッサを主体として構成されるCPU141と、シリアル通信I/F回路142と、CPU−ROM143と、CPU−RAM144とが含まれている。

【0116】

CPU−ROM143には、CPUにセンサコントローラの動作を制御させるためのプログラム及び電源投入直後にFPGA130にロードするための回路データが格納されている。

【0117】

CPU141、シリアル通信I/F回路142、CPU−ROM143、CPU−RAM144は、CPUバスを介して結ばれている。CPUバスはFPGAと入出力I/F回路ブロックとの双方に接続されている。シリアル通信I/F回路142は、右側に隣接するセンサコントローラのCPUブロックと左側に隣接するセンサコントローラのCPUブロックとにそれぞれユニット間コネクタを介して接続される。

【0118】

入出力I/F回路ブロックの詳細を示すブロック図が図13に示されている。同図に示されるように、入出力I/F回路ブロック150は、操作部入力回路151と、表示部出力回路152と、D/A変換器153と、パラレルI/F回路154と、RS−232Cインタフェース回路155と、USBインタフェース回路156とを含んでいる。

【0119】

操作部入力回路151は操作部17を構成する数値キー、ファンクションキー、スライドスイッチからの出力を入力するためのインタフェースとして機能する。表示部出力回路152は、表示部11に対する表示データ出力のためのインタフェースとして機能する。D/A変換器153は、外部接続コード3に含まれる出力線上にアナログ信号を出力するためのインタフェースとして機能する。パラレルインタフェース回路154は、外部接続コード3に含まれる信号線との間でパラレルデータのやり取りを行うためのインタフェースとして機能する。RS−232Cインタフェース回路155は、RS−232Cコネクタ14との間でデータをやり取りするためのインタフェースとして機能する。USBインタフェース回路156は、USBコネクタ13との間でデータのやり取りを行うためのインタフェースとして機能する。

【0120】

これらの操作部入力回路151、表示部出力回路152、D/A変換器153、パラレルインタフェース回路154、RS−232Cインタフェース回路155及びUSBインタフェース回路156は、CPUブロック140に繋がるCPUバスへと接続されている。尚、入出力インタフェース回路ブロック150には、メモリカードを接続するためのインタフェースを設けることもできる。

【0121】

CPU141のゼネラルフローチャート(単体動作時)が図14に示されている。同図に示されるように、このゼネラルフローチャートに示される処理の全体は、ルーチン処理と割込処理とから構成される。ルーチン処理としては、FPGA130に回路データをロードする処理(ステップ1401)、操作入力処理(ステップ1402)、外部入力処理(ステップ1403)、外部出力処理(ステップ1404)及び表示処理(ステップ1405)を含んでいる。また、割込処理としては、センシング処理(ステップ1411)を含んでいる。

【0122】

ルーチン処理は、電源投入よりスタートする。処理が開始されると、まずFPGA130に回路データをロードした後(ステップ1401)、操作入力処理(ステップ1402)、外部入力処理(ステップ1403)、外部出力処理(ステップ1404)、表示処理(ステップ1405)を繰り返し実行しながら、無限ループ状態となる。

【0123】

電源投入により処理がスタートすると、FPGA130に回路データをロードした後は(ステップ1401)、CPUは電源オフまで無限ループを繰り返す(ステップ1402〜1405)。FPGA130からの割込や外部入力からの割込があると、CPUはFPGA130からセンシングデータについての演算処理結果を取得して所定のセンシング処理を実行する(ステップ1411)。

【0124】

FPGA130への回路データのロードは、CPU−ROM143に圧縮格納されている回路データをCPU−RAM144に解凍展開し、CPU−RAM144からFPGA130に回路データを転送することにより行われる。

【0125】

この他、RS−232CやUSB等のインタフェースを経由して外部から回路データを入力して、或いは他のセンサコントローラとの間の通信により他のセンサコントローラから回路データを入力して、CPU−RAM144に格納し、これをFPGA130に転送することにより、電源投入時に限らず、動作中においても回路データの変更を可能とすることができる。

【0126】

FPGA130に設定されるパラメータの変更は、RS−232CやUSB等のインタフェースを経由して外部からの指示により行うことができる。操作部17からのキー入力によって行うこともできる。他のセンサコントローラとの間の通信により他のセンサコントローラからの指示により行うこともできる。

【0127】

外部からの回路データや設定パラメータの入力とFPGA130への反映は、検出対象物6の状況や検出環境が変化したことに応じて行うことができる。

【0128】

FPGA130の回路データや設定パラメータを複数用意しておき、状況に応じてFPGA130にロードする回路データや設定パラメータを選択するようにしてもよい。このような選択も、検出対象物6の状況や検出環境が変化したことに応じて行うことができる。このような変化は、外部から知らされる場合の他、センシングデータに基づいてセンサコントローラが自ら判断するようにすることもできる。

【0129】

回路データや設定パラメータの選択を行う他の例として、センサヘッド2からセンサヘッド2の機種を特定する型式データを取得し、取得した型式データに応じて、回路データを変更することができる。このようにすれば、型式データの異なる機種を複数用意し(この場合センサヘッドのその他の構成は同じであっても構わない)、型式データに応じて計測精度が特に高くなるような演算処理回路の構成にしたり、計測所要時間が特に短くなるような演算処理回路の構成にしたり、処理の内容(例えば透明板である対象物のおもて面のみを対象とした距離計測をするか、おもて面と裏面の両方の距離計測をするか)が異なる演算処理回路の構成にしたりすることができる。

【0130】

そうすると、ユーザはセンシングの目的とセンサヘッドの型式とを対応させて管理し(目的自体をセンサヘッドに表示してもよい)、目的に応じたセンサヘッドを接続するとセンサコントローラの回路が目的に合うように変化するというような使い方ができる。また、センサヘッドに回路データや設定パラメータを格納しておき、センサヘッドからセンサコントローラへ回路データや設定パラメータを転送するようにしてもよい。

【0131】

センサコントローラ回路(演算ユニット)の内部構成を示すブロック図が図15に示されている。同図に示されるように、このセンサコントローラ回路100Aは、図4において先に説明したセンサコントローラ回路100と比べると、センサヘッドコネクタ16、センサヘッドインタフェース回路110、及びセンサヘッド経路P2が存在しない。このセンサコントローラ回路100A(演算ユニット)は、センサコントローラが複数接続されたセンシングシステムにおいて、他のセンサコントローラからセンシングデータを取得して、それに対する演算処理を行う場合などに使用される。

【0132】

次に、本発明のセンサコントローラ100,100Aを用いて構成されたセンシングシステムAの構成図が図16に示されている。同図において、コントローラAは、図15に示されるものであり、コントローラB及びCは図4に示されるものである。コントローラB及びCにはセンサヘッド2がそれぞれ接続される。これらのセンサヘッド2の構成は、先に、図3及び図5に示されたものである。これらのコントローラA〜Cには、図18〜図20の処理を実行することによって、図示のユニット番号『0』〜『2』が付与されている。

【0133】

次に、撮像素子の水平走査線上に得られる光強度分布が図17に示されている。図において、光強度のピークに対応する画素の位置が対象物までの距離に対応している。図16に示されるコントローラCに接続されたセンサヘッド2は、水平に置かれた板状対象物体の上方に設置され、その上面(おもて面)までの距離を計測している。コントローラBに接続されたセンサヘッド2は、同じ対象物体の下方に設置され、その下面(裏面)までの距離を計測している。コントローラB,Cでそれぞれ計測された距離データ(センシングデータ)は、コントローラAに送られる。コントローラAには、2つのセンサヘッドの間の距離が設定されており、その情報と、コントローラA及びBから取得した距離データを用いて、対象物体の厚みを算出する。算出結果は、コントローラCの入出力インタフェース回路ブロック150を経由してユーザ所望のインタフェースにより外部に出力される。厚みが規定範囲内にあるか否かを判定して、その判定結果を出力してもよい。

【0134】

図16に示されるセンシングシステムAは、センサヘッド2を対象物体6の同じ側に並べて配置して、それぞれの計測対象位置の高さの差(段差)の計測に用いることもできる。

【0135】

次に、センシングシステムAの動作フローチャート(その1〜その3)が図18〜図20に示されている。図18において処理が開始されると、まず各コントローラA〜Cにおいては、右側ユニット有無の確認処理を行う(ステップ101,201,301)。図16に示されるセンシングシステムAの構成図を前提とすると、コントローラAにおける確認結果は『右側ユニットあり』、コントローラBにおける確認結果は『右側ユニットあり』となるのに対し、コントローラCにおける確認結果は『右側ユニットなし』となる。

【0136】

続いて、左側ユニット有無の確認処理が行われる(ステップ102,202,302)。同様に、センシングシステムAの構成図を前提とすると、コントローラAにおける確認結果は『左側ユニットなし』となるのに対し、コントローラBにおける確認結果は『左側ユニットあり』、コントローラCにおける確認結果は『左側ユニットあり』となる。

【0137】

続いて、クロック切替回路の設定処理が行われる(ステップ103,203,303)。このとき、コントローラAにおいては、右ユニットからのクロック入力を使用するようクロック切替回路の設定が行われ、コントローラBにおいても、右ユニットからのクロック入力を使用するようクロック切替回路の設定が行われる。これに対して、コントローラCにおいては、自ユニットの発振器を使用するようクロック切替回路の設定が行われる。

【0138】

続いて、センサヘッドの有無と型式確認処理が行われる(ステップ104,204,304)。このとき、コントローラAにおける確認結果は『センサヘッドなし』となるのに対し、コントローラBにおける確認結果は『センサヘッドあり』となり、コントローラCにおける確認結果も『センサヘッドあり』とされる。

【0139】

続いて、計測準備設定処理が行われる(ステップ105,205,305)。コントローラAにおける計測準備設定処理においては、(1)2つの計測結果を用いた演算処理のためのCPUプログラムパラメータを設定する処理、(2)データ経路切替回路を、右側ユニットから入力した計測結果をCPUへ送り出すように設定する処理、を実行する。コントローラBにおける計測準備設定処理においては、(1)センサヘッドの型式に応じて、演算処理回路パラメータ及びCPUプログラムパラメータを設定する処理、(2)距離計測を設定する処理、(3)データ経路切替回路を、(a)センサヘッドから入力したデータについては演算処理回路へと、(b)CPUが出力した計測結果については左側ユニットへと、(c)右側ユニットから入力した計測結果は左側ユニットへと、設定する処理を実行する。コントローラCにおける計測準備設定処理においては、(1)センサヘッドの型式に応じて、演算処理回路パラメータ及びCPUプログラムパラメータを設定する処理、(2)距離計測を設定する処理、(3)データ経路切替回路を、(a)センサヘッドから入力したデータを演算処理回路へと、(b)CPUが出力した計測結果については左側ユニットへと、設定する処理を実行する。

【0140】

図19に移って、各コントローラA〜Cにおいて、計測準備設定処理(ステップ105,205,305)が完了したならば、続いて、コントローラA,B,C間で適宜に交信することによって、コントローラA〜Cのそれぞれにユニット番号を付する処理が実行される。

【0141】

まず、コントローラAにおいては、自らのユニット番号を0とする(ステップ106)。続いて、自らのユニット番号+1(=1)の番号を右側のユニットへと出力する(ステップ107)。コントローラBにおいては、ユニット番号を左側のユニットから取得するまで待機する(ステップ206)。待機中にユニット番号を左側のユニットから取得したならば、この例では、取得したユニット番号『1』を自らのユニット番号とする(ステップ207)。続いて、自らのユニット番号+1(=2)の番号を右側のユニットへ出力する(ステップ208)。コントローラCでは、ユニット番号を左側のユニットから取得するまで待機する(ステップ306)。待機中にユニット番号を左側のユニットから取得したならば、この例では取得したユニット番号『2』を自らのユニット番号とする(ステップ307)。

【0142】

続いて、最大ユニット番号である『2』を左側のユニットへと出力する(ステップ308)。コントローラBでは、最大ユニット番号を右側のユニットから取得するまで待機する(ステップ209)。待機中に最大ユニット番号を右側のユニットから取得したならば、この例では、最大ユニット番号である『2』を左側のユニットへと出力する(ステップ210)。コントローラAでは、最大ユニット番号を右側のユニットから取得するまで待機する(ステップ108)。

【0143】

以上の処理を実行する結果、コントローラA,B,Cにはそれぞれ自らのユニット番号が設定され、同時にコントローラA,B,Cは、システムを構成する最大ユニット番号を知ることができる。

【0144】

図20へ移って、このようにして、各コントローラA,B,Cにおいて、クロック切替回路の設定処理、センサヘッドの有無と型式確認処理、計測準備設定処理、ユニット番号決定処理などが終了したならば、以後3台のコントローラA〜Cを相互に連繋しつつ、計測動作が実行される。

【0145】

すなわち、まずコントローラAからコントローラBに対して、ユニット番号『2』の計測結果の取得要求が発行される(ステップ109)。続いて、コントローラBでは、コントローラAからの取得要求をコントローラCへと中継する(ステップ211)。続いてコントローラCでは、取得要求を受信した後(ステップ309)、自ユニットの計測結果を左側ユニットであるコントローラBへと出力する(ステップ310)。続いてコントローラBでは、計測結果をコントローラCからコントローラAへと中継する(ステップ212)。続いて、コントローラAでは、ユニット番号『2』の計測結果を取得する(ステップ110)。

【0146】

続いてコントローラAからコントローラBに対して、ユニット番号『1』の計測結果の取得要求が発行される(ステップ111)。続いて、コントローラBでは、取得要求を受信すると共に(ステップ213)、計測結果を左側ユニットであるコントローラAへと出力する(ステップ214)。続いて、コントローラAでは、ユニット番号1の計測結果を取得する(ステップ112)。続いて、コントローラAでは、ユニット番号『1』及び『2』の計測結果より厚みを演算する(ステップ113)。以上一連の処理が、所定の終了指令が与えられるまで(ステップ114,215,311)、繰り返し実行される。

【0147】

このように、図19のフローチャートを実行することにより、コントローラCは、自ユニットの発振器を使用するクロック切替回路が設定され、コントローラA及びBは、右ユニットからのクロック入力を使用するようクロック切替回路が設定される。すなわち、全てのコントローラのFPGAはコントローラCの発振器が出力するクロック信号を用いて動作する。これにより、各コントローラのFPGA間に同期通信を行うことが容易になる。しかも、通信のためのクロック信号がFPGAにプログラムされている演算処理回路などの内部回路のクロック信号とも同期しているため、FPGA内部回路に対するセンシングデータの入出力を効率よく行うことができる。

【0148】

このセンシングシステムによれば、全コントローラにクロック信号を供給するコントローラの発振器の発振周波数を変更すれば、システム全体のFPGAのクロック周波数を変更することができる。このようなシステムのクロック周波数の変更は、クロック信号を供給するコントローラの発振器の周波数を調整可能にすることによって実現することができる。或いは、クロック信号を供給するコントローラを、異なる発振周波数の発振器を有するコントローラに置き換えることによって実現することができる。例えば、センシングシステムAのコントローラCを、より速い発振周波数の発振器を有するコントローラに置き換えることにより、システム全体の処理速度を向上させることができる。

【0149】

次に、CPUによるセンシング処理のフローチャートが図21に示されている。FPGA130は、センサヘッド2から画像データを周期的に取得して演算処理している。FPGA130は、1画面分の演算処理が完了すると、結果をレジスタに格納して、CPU141に割込みをかける。CPU141はこの割込があると、図21のフローチャートの動作を開始する。

【0150】

図21において処理が開始されると、まずCPU141は、FPGA130から画素単位で表された計測結果を取得する(ステップ2101)。続いて、CPU141は、計測結果をmm単位の実座標へ変換する(ステップ2102)。続いて、CPU141は、実座標に変換した計測結果をCPU−RAM144に格納する(ステップ2103)。続いてCPU141は、実座標に変換した計測結果をFPGA130に出力する(ステップ2104)。この、実座標に変換した計測結果をFPGA130に出力するステップにおいて、必要であればデータ経路切替回路132に指示を出して、実座標に変換した計測結果が適切なユニット間コネクタ、すなわち接続された他のセンサコントローラに向けて伝送されるようにする。続いて、CPU141は、CPU−RAM144に格納されている計測結果をしきい値と比較し、比較判定結果をCPU−RAM144に格納する(ステップ2105)。

【0151】

CPU−RAM144に格納された計測結果と比較判定結果は、外部からの要求があれば入出力インタフェース回路ブロック150を経由して、いずれかインタフェースにより出力される。外部からの要求がなくても、周期的に又は常時出力するようにしてもよい。

【0152】

図22〜27には、データの流れ(その1〜その6)が示されている。これらのデータの流れを実現するように、CPU141からの指示により、データ経路切替回路132が設定される。この設定は、必要に応じて時系列的に変化する。

【0153】

データの流れ(その1)が図22に示されている。図において、( )内の算用数字はデータの送られる順番を表している。図において、データ(2)はセンサヘッドI/F回路110から入力されたデータ(1)が演算処理回路133により演算処理された結果である。データ(3)はデータ(2)がCPU141により演算処理された結果である。データ(4)はデータ(3)が演算処理回路133を通り抜けたものであり、ユニット間コネクタ(左)18bに出力される。

【0154】

図22に示されるデータの流れ(その1)は、センシングシステムAのコントローラCに接続されたセンサヘッドから出力されるセンシングデータの、コントローラCにおけるデータの流れが該当する。コントローラBについても同様である。図中破線で示されるように、センサヘッドから出力されるセンシングデータが分岐して他のコントローラに同時に送るようにすることもできる。これは、後述する図29のセンシングシステムBのコントローラAにおけるデータの流れが該当する。尚、データ(3)、データ(4)に代えてCPU間通信を利用することもできる。

【0155】

データの流れ(その2)が図23に示されている。図23に示されるデータの流れ(その2)は、センシングシステムAのコントローラBが、コントローラCから出力される演算結果のセンシングデータをコントローラAに中継する場合が該当する。

【0156】

データの流れ(その3)が図24に示されている。このデータの流れ(その3)は、後述する図29のセンシングシステムBのコントローラBにおけるデータの流れが該当する。データ(1)は接続された他のセンサコントローラからのセンシングデータである。例えば、図29に示されるコントローラBの場合には、コントローラCに接続されたセンサヘッドから出力されるセンシングデータである。その後のデータの流れは図22と同様である。

【0157】

データの流れ(その4)が図25に示されている。このデータの流れ(その4)は、演算処理回路133に入力されたセンシングデータが一旦FPGA−RAM170に格納され、格納されたデータを用いながら演算処理回路133において演算処理が行われる。その他は図22と同様である。

【0158】

データの流れ(その5)が図26に示されている。このデータの流れ(その5)は、図25と同様に、FPGA−RAM170に格納されたデータを用いて演算処理が行われた後、演算結果がFPGA−RAM170に格納される。演算結果はCPU141にも送られる。例えば、FPGA−RAM170に格納される演算結果は画像データであり、CPU141に送られる演算結果は特徴量の値であるというように、両演算結果が互いに異なるものであってもよい。FPGA−RAM170に格納された演算結果は、他のセンサコントローラに向けて送出される。

【0159】

データの流れ(その6)が図27に示されている。このデータの流れ(その6)は、演算処理回路133に入力されるセンシングデータ(図ではセンサヘッドからであるが、他のセンサコントローラからであってもよい)をパイプライン処理回路133aによってパイプライン処理して出力する。パイプライン処理の結果は、演算処理回路133における他の処理に利用してもよい。例えば、複数のセンサコントローラで分担して互いに異なる内容のパイプライン処理を行うことにより、複雑な画像処理をリアルタイムに行うことができる。データ経路切替回路132を経由する演算処理回路133に対する入力と出力とを同時に行うので、図11に示されるデータ経路切替回路132をもう1組増設する必要がある。但し、パイプライン処理専用とされたセンサコントローラの場合には、1組のデータ経路切替回路は演算処理回路への入力専用、もう1組は演算処理回路からの出力専用であるから、各データ経路切替回路を必要な配線だけに簡素化することができる。

【0160】

次に、センサコントローラ(拡張メモリユニット)の内部構成を示すブロック図が図28に示されている。同図に示されるように、このセンサコントローラ(拡張メモリユニット)100B内には、フラッシュメモリ180が含まれており、このフラッシュメモリ180がFPGA130に接続されている。また、センサヘッドインタフェース回路や入出力インタフェース回路ブロックなどは存在しない。このセンサコントローラ100Bによれば、他のセンサコントローラから入力したセンシングデータをフラッシュメモリ180に格納し、格納したセンシングデータを他のセンサコントローラに出力する機能を有する。すなわち、データロガーとして使用することができる。

【0161】

センシングシステムの他の実施形態であるセンシングシステムBの構成図が図29に示されている。このセンシングシステムBは透明板の厚み計測を目的とするセンシングシステムである。センシングシステムAの場合と同一のセンサヘッド2がコントローラCにのみ接続されている。

【0162】

撮像素子の水平走査線上に得られた光強度分布が図30に示されている。センサヘッドの撮像素子上には、透明板のおもて面(センサヘッドが設けられている側の面)からの反射光による光強度分布のピークと、透明板の裏面からの反射光による光強度分布のピークが得られる。

【0163】

センシングシステムBにおいては、コントローラCのデータ経路切替回路132は、センサヘッド2からのセンシングデータを分岐して、コントローラCの演算処理回路と、コントローラBとの両方に送る。コントローラCは、距離の小さい側から最初のピーク、すなわち、おもて面に対応するピークについて距離計測を行う。コントローラBは、距離の小さい側から2番目のピーク、すなわち、裏面に対応するピークについて距離計測を行う。コントローラAは、コントローラB、Cから計測結果を取得し、それらの値の差から透明板の厚みを求める。透明板の屈折率を考慮した補正演算も行われる。

【0164】

センシングシステムBの動作フローチャート(その1)が図31に示されている。尚、同フローチャート(その2,その3)については、図19及び図20の各フローチャートと同様である。図18との相違点は、コントローラB及びコントローラCにおける計測準備設定処理(ステップ205B,305C)のみである。

【0165】

すなわち、コントローラBにおける計測準備設定処理(ステップ205B)においては、(1)コントローラCに接続されているセンサヘッドの型式に応じて、演算処理回路パラメータ及びCPUプログラムパラメータを設定する処理、(2)裏面までの距離計測を設定する処理、(3)データ経路切替回路を、(a)右側ユニットから入力したデータを演算処理回路へ、(b)CPUが出力した計測結果を左側ユニットへ、(c)右側ユニットから入力した計測結果を左側ユニットへ、それぞれ設定する。

【0166】

また、コントローラCにおける計測準備設定処理(ステップ305C)においては、(1)センサヘッドの型式に応じて、演算処理回路パラメータ及びCPUプログラムパラメータを設定する処理、(2)おもて面までの距離計測を設定する処理、(3)データ経路切替回路を、(a)センサヘッドから入力したデータを演算処理回路及び左側ユニットへ、(b)CPUが出力した計測結果を左側ユニットへ、設定する処理を実行する。

【0167】

次に、変位センサ機能と視覚センサ機能とを併有するセンサヘッドの構造図が図32に示されている。このセンサヘッドは、センシングシステムBのセンサヘッドとして使用することができる。図は、センサヘッドユニットのケース側面を開口してその内部を示すものである。図において、201は計測用光源を構成する赤色レーザダイオード素子、202は計測用投光光学系を構成するレンズ組立体、203は計測対象物体上の計測位置を含むその周辺領域を斜めから見た画像を取得するための斜視画像取得光学系を構成するレンズ組立体、204はレンズ組立体203の光軸を折り曲げるためのミラー、205は計測対象物体上の計測位置を含むその周辺領域を正面から見た画像を取得するための正視画像取得光学系を構成するレンズ組立体、206は斜視画像取得光学系を介して取得される斜めから見た画像と正視画像取得光学系を介して取得される正面から見た画像とをそれぞれ光電変換して各画像に対応する映像信号を生成する撮像手段としての2次元CCD素子である。

【0168】

このセンサヘッド2においては、レーザ点灯時にレンズ組立体203を経由する光路により測距用のレーザ光照射光像が、レーザ消灯時にレンズ組立体205を経由する光路により計測位置周辺を含む正視画像が得られる。正視画像は、対象物体上のマークの位置を特定するような、通常のカメラで取得した画像を対象とするのと同じような画像処理の対象とすることができる。このセンサヘッドは、測距用の画像と正視画像とを交互に出力する。測距用の画像データはセンシングシステムBのコントローラCで演算処理され、マーク位置特定用の正視画像はコントローラBで演算処理される。対象物の表面がほぼ平坦であるとすると、コントローラAでは、マーク位置の3次元座標を特定することができる。

【0169】

センシングシステムAにおいて、コントローラCに変位センサを接続し、コントローラBにカメラを接続することによっても、同様に、マーク位置の3次元座標の測定を行うことができる。

【0170】

センシングシステムBの他の応用例として、センサヘッドとしてカメラを接続し、コントローラCとBとで異なる内容の画像処理を行うことができる。例えば、撮像された画像に文字とバーコードが写っている場合に、コントローラCで文字の特定を、コントローラBでバーコードの復号を行うことができる。

【0171】

センシングシステムBの他の応用例として、コントローラBにおいて、センサヘッドからのセンシングデータと、コントローラCで処理された結果のセンシングデータとの両方を用いて演算処理することができる。この場合は、コントローラBにおいてコントローラCの演算結果を単に中継するのでなく、コントローラBの演算処理回路に入力するような変更が行われる。例えば、センサヘッドとしてカメラを接続し、撮像された画像にバーコードが写っている場合に、コントローラCにおいてパイプライン処理を利用して画像の入力完了と同時にバーコードの位置と回転角とを算出し、この結果を直ちにコントローラBに送る。コントローラBでは画像入力完了後すぐにバーコードの位置と回転角との情報を得るから、この情報を利用して直ちにバーコードの復号を始めることができる。

【0172】

センシングシステムAにおいて、コントローラBを増設して、センシング対象箇所を増やすことができる。たとえば、長方形の板状対象物の4つの角付近と中心との5箇所で同時に測距を行い、その結果からコントローラAにおいて、対象物の平坦度を算出することができる。

【0173】

センサコントローラに接続するセンサヘッドとしては、2次元撮像素子を用いるものに限らず、1次元撮像素子を用いるセンサや、アナログ信号(又はそれがデジタル化された信号)を出力するようなセンサを広く採用することができる。

【0174】

以上、センサコントローラの実施形態をFPGAにプログラムされる回路の内容が決定されているものとして説明してきた。実際にセンサコントローラをセンシングに用いるためには、このようにFPGAの回路内容が決定されていることが必要である。

【0175】

ところで、図4、図15、又は図28に示すような内部構成を有するが、FPGAにプログラムされる回路内容がいまだ決定されていないユニットも本発明の実施形態である。このようなユニットは、いわばセンサコントローラのプラットフォーム製品である。プラットフォーム製品は、そのメーカ自身によって、FPGAにプログラムされる回路の内容が決定されたセンサコントローラを生産するために利用できるだけでなく、プラットフォーム製品のままで流通させることもできる。この場合、FPGAにプログラムされる回路の内容の決定は、センシングを行うユーザや、ユーザーのためにセンシングシステムを構築する事業者や、センサコントローラを組み込む装置の製造業者によって行われる。これらのメーカ以外の者が決定又は選択するFPGAの回路データは、プラットフォーム製品のメーカが提供してもよいし、第三者が開発することも考えられる。

【0176】

本発明のセンサコントローラのユニット間経路は、左右のユニット間コネクタの間を直結する貫通バスラインとして構成することができ、このバスラインにプログラム可能な論理回路を接続するようにしてもよい。しかし、実施形態として説明したように、ユニット間経路を、プログラム可能な論理回路及び一方のユニット間コネクタの間の経路と、プログラム可能な論理回路及び他方のユニット間コネクタの間の経路とに分けておくことにより、次のような利点が得られる。

【0177】

すなわち、ユニット間経路を貫通バスラインとした場合は、複数のセンサコントローラを連結したセンシングシステム全体で一つの共通のバスラインが形成されるのに対し、プログラム可能な論理回路をはさんでユニット間経路を分けた場合は、センサコントローラの一方側と他方側とで同時に異なる内容のデータ伝送を行うことが可能となる。例えば、複数のセンサコントローラを連結して多段のパイプライン処理を行うことができる。それだけでなく、必要なときにプログラム可能な論理回路の内部で両側のユニット間経路を接続させれば、貫通バスラインを形成して、隣接していないセンサコントローラ間で時間遅れのないデータ伝送を行うことも可能となる。このように、センサコントローラの内部でプログラム可能な論理回路をはさんでユニット間経路を分ける構成は、センシングシステムに柔軟性をもたらす。

【0178】

センシングシステムの柔軟性には、センサコントローラがプログラム可能な論理回路のほかにCPUを内蔵していることも貢献している。CPUを内蔵することにより、具体的な使用場面に応じて各センサコントローラ及びセンシングシステムの機能を変更することが容易になる。特に、図4の実施形態のセンサコントローラのように、センサヘッドを接続可能であって、外部との電気的インタフェース(外部接続コード、外部I/Fコネクタ)及び人とのインタフェース(操作部、表示部)を備えたものは、他のセンサコントローラと連結せずに単体のセンサとしても使用が可能であるという高度な柔軟性を備える。

【0179】

本発明の実施形態であるプラットフォーム製品は、多様な構成のセンサヘッドとの組み合わせに適用することができることも特徴的である。特に、撮像素子を備えたセンサヘッドをデータ源とする画像データの処理にも、アナログ出力の物理量変換器(フォトダイオード、PSD、検知コイルなどのデバイスやそれらにアンプ、発振回路などを付加したもの)を備えたセンサヘッドをデータ源とする波形データの処理にも適用することができる。このプラットフォーム製品は、ユニット間で画像データを伝送する能力を有しているので、アナログデータをデジタル化した多値データを扱う場合には、ある時間範囲にわたる多値データの時系列集合である波形データを、ユニット間で一括して伝送することができる。

【0180】

次に、センサコントローラ回路の他の実施形態の内部構成を示すブロック図が図33に示されている。このセンサコントローラ回路100Cには、図4のセンサコントローラ回路100に対して、外部I/Fコネクタ19からFPGA130に外部トリガ信号を伝送する外部トリガ信号線、及びFPGA130から外部I/Fコネクタ19に統合OK信号(統合判定信号)を伝送する統合OK信号線が追加されている。外部トリガ信号及び統合OK信号の外部との間の伝送には、外部接続コード3に含まれているパラレル信号線の内の2本が利用される。このセンサコントローラに接続されているセンサヘッド2は、2次元撮像素子を内蔵したカメラである。表示部11には、高精細のカラー液晶表示画面が含まれており、センサヘッド2で撮像した画像や画像処理後の画像を表示することができる。また、計測範囲を示す図形などもこの画面に表示することにより計測条件の設定操作を容易にしている。

【0181】

センサコントローラ回路100Cに含まれているFPGA130の内部回路の詳細を示すブロック図が図34に示されている。図34のFPGA内部回路は、以下の点で図9のFPGA内部回路と異なる。

【0182】

センサヘッドに対するLED(センサLED制御信号)及びLD_ON(レーザ制御信号)の出力が含まれていない。

【0183】

タイミング生成回路136に代えて、トリガ制御回路138が設けられている。図9のFPGAが自発的に周期的なセンシング動作を行うのに対し、図34のFPGAはトリガ信号の入力に基づいてセンシング動作を行う。トリガ制御回路138に入力されるトリガ信号には、外部トリガ信号とユニット間トリガ信号の2種類がある。外部トリガ信号は外部接続コード3を介してセンサコントローラの外部から与えられる。ユニット間トリガ信号線は第1ユニット間コネクタ18aと第2ユニット間コネクタ18bとを結んでおり、ユニット間トリガ信号は、いずれかのユニット間コネクタに接続された他のセンサコントローラから与えられる。トリガ制御回路138は、レジスタ134を介したCPUからの設定(図示せず)により、外部トリガ信号とユニット間トリガ信号のいずれかを選択する。トリガ制御回路138は、選択したトリガ信号の入力に基づき、いくつかの内部トリガ信号を出力する。内部トリガ信号の出力先は、センサヘッド2(センサヘッドI/F回路110を経由)、タイミング変換回路131、データ経路切替回路132、演算処理回路133、及びCPU141である。CPU141に対して内部トリガ信号は割込み信号として働く。これらの内部トリガ信号が出力されるタイミングは、各回路ブロックが協調してセンシング動作を行うことができるように適宜調整されている。また、外部トリガ信号が与えられてから所定の遅延時間が経過した後にセンシング動作を開始するように、遅延時間を設定することもできる。

【0184】

CPU141は、1回のセンシング処理が終了して処理完了状態となると、Enable信号とOK信号とをFPGA130に対して出力する。これらの信号のためには、伝達の時間遅れを避けるため、レジスタ134を経由しない直通経路が設けられている。Enable信号は、センシング処理が完了して次回のセンシング処理のための待機状態にあることを示す信号であり、電圧レベルハイが待機状態(イネーブル状態)、電圧レベルローが処理中状態(ビジー状態)を表す。OK信号は、判定結果が特定の判定状態であること、すなわちこの実施形態では判定結果が合格であることを示す信号であり、電圧レベルハイが合格(OK)、電圧レベルローが不合格(NG)を表す。OK信号の状態は、次回のセンシング処理が完了するまでの間維持される。

【0185】

ANDゲート回路1301は、CPU141からFPGA130に入力されたEnable信号及び第1ユニット間コネクタ18aからFPGA130に入力されたユニット間Enable信号(第1完了信号)を入力し、論理演算の結果であるユニット間Enable信号(第2完了信号)を第2ユニット間コネクタ18bに出力する。第1ユニット間コネクタ18aから入力されたユニット間Enable信号の信号線は、第1ユニット間コネクタ18aに他のセンサコントローラが接続されていないときにANDゲート回路1301への入力がハイレベルとなるように、プルアップ抵抗1302によってプルアップされている。ANDゲート回路1301の出力であるユニット間Enable信号は、分岐されてCPU141及び外部接続コードの中のパラレル信号線の1つにも接続されている。これにより、CPU141及び外部の信号受信者は、センサコントローラが複数直列に接続されたセンシングシステムにおいて、自ユニット及び自ユニットよりも第1ユニット間コネクタ18a側に接続されたすべてのユニットが処理完了状態であることを知ることができる。

【0186】

ANDゲート回路1303は、CPU141からFPGA130に入力されたOK信号及び第1ユニット間コネクタ18aからFPGA130に入力されたユニット間OK信号(第1特定判定信号)を入力し、論理演算の結果であるユニット間OK信号(第2特定判定信号)を第2ユニット間コネクタ18bに出力する。第1ユニット間コネクタ18aから入力されたユニット間OK信号の信号線は、第1ユニット間コネクタ18aに他のセンサコントローラが接続されていないときにANDゲート回路1303への入力がハイレベルとなるように、プルアップ抵抗1304によってプルアップされている。ANDゲート回路1303の出力であるユニット間OK信号は、分岐されてCPU141及び外部接続コードの中のパラレル信号線の1つにも接続されている。これにより、CPU141及び外部の信号受信者は、センサコントローラが複数直列に接続されたセンシングシステムにおいて、自ユニット及び自ユニットよりも第1ユニット間コネクタ18a側に接続されたすべてのユニットが特定判定状態であることを知ることができる。自ユニットが、センシングシステムにおけるユニット間OK信号の下流側(この場合は第2ユニット間コネクタ18b側)の端に位置するときには、外部接続コードに出力されるユニット間OK信号は、すなわちセンシングシステムのすべてのセンサコントローラによる判定結果が特定の結果(この実施形態では合格)であることを示す統合判定信号(この実施形態では統合OK信号)である。

【0187】

このセンサコントローラを3台直列に接続して構成したセンシングシステムCの構成図が図35に示されている。図16のセンシングシステムAの構成図と異なり、図35ではトリガ信号及びOK信号に関する構成のみを示している。センシングシステムAの場合と同様の動作により、各センサコントローラにはユニット番号が付与される。カメラであるセンサヘッド2が各センサコントローラに接続されており、各センサコントローラは接続されたセンサヘッド2から入力した画像に対して処理を行い、処理の結果をあらかじめ設定された基準と比較することにより、合格かどうかの判定を行う。そして、センシングシステム全体としては、例えば一つのワークを各センサヘッド2で互いに異なる角度から撮影し、又は一つのワークの互いに異なる箇所を撮影し、すべての撮影画像を対象にした判定結果が合格であるときに統合判定結果が合格であるとする。

【0188】

センサヘッド2を一部のセンサコントローラにのみ接続し、センサヘッド2が接続されていないセンサコントローラは、他のセンサコントローラから処理すべきセンシングデータを受信するようにしてもよい。例えば、コントローラAにのみセンサヘッド2を接続し、センサコントローラB及びCにはコントローラAから画像を転送する。そして、各センサコントローラにおいて、共通の画像の互いに異なる部分を対象にして処理を行い、又は共通の画像に対して互いに異なる種類の画像処理を行い、処理の結果をそれぞれあらかじめ設定された基準と比較することにより、合格かどうかの判定を行う。そして、センシングシステム全体としては、すべてのセンサコントローラによる判定結果が合格であるときに統合判定結果が合格であるとする。

【0189】

図35で、実線で表された信号線は、システムの動作上有効に用いられている信号が伝送されている信号線であり、破線で表された信号線は、存在はしているがシステムの動作上有効に用いられている信号が伝送されていない信号線である。

【0190】

外部トリガ信号はコントローラAに入力される。コントローラAのトリガ制御回路138は外部トリガ信号を選択し、外部トリガ信号に基づきユニット間トリガ信号を出力する。ただし、センシングシステムCの中のいずれかのセンサコントローラが処理中状態(ビジー状態)であるときに外部トリガ信号を入力した場合は、コントローラAはその外部トリガ信号を無効なものとして扱い、ユニット間トリガ信号を出力しない。外部トリガ信号が無効とされたことをCPU141が外部に報知するようにしてもよい。コントローラB及びCのトリガ制御回路138はユニット間トリガ信号を選択する。その結果、外部トリガ信号は、センシングシステムCの全体に対してセンシング処理のトリガをかけることになる。ユニット間トリガ信号を利用せずに、各コントローラに個別に外部トリガ信号を与えるようにしてもよい。

【0191】

各センサコントローラのANDゲート回路1303に関係する配線からわかるとおり、すべてのCPU141がOK信号を出力したときに、統合OK信号が出力される。

【0192】

図示を省略しているが、Enable信号についてもOK信号と同様の配線となり、すべてのCPU141がEnable信号を出力したときに、コントローラAからユニット間Enable信号が外部に出力される。

【0193】

しかし、各センサコントローラがセンシング処理に要する時間は同一とは限らず、また、各センサコントローラの内部トリガ信号の遅延時間が異なっていたり、各センサコントローラに互いに異なるタイミングで外部トリガ信号が与えられたりする場合がある。したがって、各センサコントローラがセンシング処理を完了して処理完了状態となる時刻は互いに異なる場合がある。一方、センサコントローラが処理完了状態となるまでは、前回のセンシング処理が完了したときに出力されたOK信号の状態が維持されているため、センシングシステム全体に対する1つの外部トリガ信号又は各センサコントローラに個別に互いに関連したタイミングで入力される一群の外部トリガ信号に基づくセンシング処理が、一部のセンサコントローラでは完了しているがすべてのセンサコントローラでは完了していない過渡的な期間においては、統合OK信号がセンシングシステム全体の判定結果を正しく表していないことになる。そこで、コントローラAから外部に出力されるユニット間Enable信号をモニタすることにより、すべてのセンサコントローラが処理完了状態となったのを確認した上で、そのときの統合OK信号を利用するようにすれば、センシングシステム全体の判定結果を正しく利用することができる。あるいは、センシングシステムに外部トリガ信号を与えてから、センシング処理が完了するのに十分な時間が経過するのを待ってから統合OK信号を利用することによっても、センシングシステム全体の判定結果を正しく利用することができる。

【0194】

しかし、本実施の形態では、センシングシステムの利用をより容易にするために、すべてのセンサコントローラが処理完了状態であるときに限り、統合OK信号を出力するようにしている。このようにすれば、統合OK信号は、常にセンシングシステム全体の判定結果を正しく表している。具体的には、ユニット番号0に定められたコントローラAのCPU141は、CPU141に入力されるユニット間Enable信号(図34のANDゲート回路1301の出力)をモニタして、この信号がハイレベルであるときに限り、判定結果にしたがってOK信号を出力するようにしている。

【0195】

同様の機能は、コントローラAのANDゲート回路1303を3入力タイプのものに変更し、CPU141からのOK信号及び第1ユニット間コネクタ18aからのユニット間OK信号に加えて、ANDゲート回路1301の出力信号もANDゲート回路1303に入力するようにFPGA130内の回路構成を変更することによっても実現することができる。このような回路構成の変更は、ユニット番号が0となったことを条件として、CPU141からレジスタ134を経由して回路変更の指示を与えることによって行うことができる。この場合には、CPU141は、モニタ入力しているユニット間Enable信号の状態にかかわらず、センシング処理が完了すれば直ちに、判定結果にしたがってANDゲート回路1303に入力されるOK信号を出力する。

【0196】

センサコントローラ回路のOK信号に関する他の実施形態を示すブロック図が図36に示されている。この実施形態では、ユニット間OK信号はパラレル信号線によって伝送される。ただし、第1ユニット間コネクタ18aから第2ユニット間コネクタ18bに至る信号線は、端子(a)から端子(b)へ、端子(b)から端子(c)へ、というように、1つずつ接続する端子がずらされている。そして、第2ユニット間コネクタ18bの端子(a)には、CPU141が出力するOK信号が与えられる。この実施形態においては、統合OK信号を出力する特定センサコントローラのほかに、ユニット間OK信号のパラレル信号線の数以内のセンサコントローラを接続してセンシングシステムを構成することができる。この実施形態では、ユニット間OK信号のパラレル信号線を3本としたが、この信号線の数は任意に定めることができる。

【0197】

第1ユニット間コネクタ18aから入力されたすべてのユニット間OK信号はANDゲート回路1305によりAND演算され、その出力がCPU141に入力される。CPU141は、ANDゲート回路1305の出力がハイレベルであること(OK信号が入力されること)及び自ユニットの判定結果が合格であることを条件に、統合OK信号を外部に出力する。この実施形態においてもEnable信号に関しては先の実施形態と同じであり、CPU141は、ユニット間Enable信号がハイである場合に限り、統合OK信号を出力可能とすることにより、各センサコントローラの判定結果が出そろうまでの過渡的な期間において誤った統合OK信号を出力することを防止している。

【0198】

ANDゲート回路1305を設ける代わりに、第1ユニット間コネクタ18aから入力されたすべてのユニット間OK信号を直接CPU141に入力し、プログラムの処理によってAND演算するようにしてもよい。このようにすれば、統合OK信号を出力する特定センサコントローラは、各センサコントローラの判定結果を個別に知ることができ、その情報を利用して、統合OK信号のほかに、判定結果に関するより詳しい情報を出力することもできる。

【0199】

統合判定信号を得るための構成は、以上説明してきたような論理ゲート回路を用いる構成に限らず、CPU141におけるプログラム処理によって同様の機能を実行してもよい。その場合には、処理完了状態や特定判定状態の伝達をCPU間通信によって行うことも可能である。もっとも、統合判定信号を早く出力するためには論理ゲート回路を用いる構成の方が有利である。

【0200】

統合判定信号を出力する特定センサコントローラをセンシングシステムの端以外の位置に置くことも可能である。そのためには、論理ゲート回路を用いる場合も、プログラム処理による場合も、処理完了状態や特定判定状態の伝達をセンシングシステムの両端のセンサコントローラから特定センサコントローラに向かって行うようにすればよい。

【0201】

ところで、以下に列挙する発明は、プログラム可能な論理回路とCPUとを含む制御回路を有するセンサコントローラに限らず、さまざまな制御回路の構成を有するセンサコントローラに適用することができる。この場合の制御回路は、例えば、CPUを有するがプログラム可能な論理回路を有さないもの、専用に設計された集積回路であるものなどであってもよい。

【0202】

(1) 1つのユニットとして構成されたセンサコントローラであって、センシング処理を行う制御回路と、他のセンサコントローラとの接続に用いることのできる第1ユニット間コネクタ及び第2ユニット間コネクタと、第1クロック信号を出力する発振器と、第1ユニット間コネクタから入力される第2クロック信号を伝送する第1クロック経路と、第1クロック信号及び第2クロック信号のいずれかを選択して制御回路の少なくともデータ伝送に関与する部分に与えるクロック切替回路と、選択されたクロック信号を第2ユニット間コネクタに出力するための第2クロック経路と、を備えるセンサコントローラ。

【0203】

このような構成によれば、従来のセンサコントローラではセンサコントローラ間で十分高速なデータ伝送ができなかったという課題を解決することができる。このような構成によれば、制御回路の少なくともデータ伝送に関与する部分は、自ユニットの発振器が出力するクロック信号を用いて動作することが可能であり、接続された他のセンサコントローラから得られるクロック信号を用いて動作することも可能である。他のセンサコントローラから得られるクロック信号を用いる場合は、当該他のセンサコントローラとの間で制御回路のクロックが同期しているので、センシングデータを高速に伝送することが容易になる。このようなセンサコントローラを用いれば、3台以上のセンサコントローラが直列に接続されたセンシングシステムであって、すべてのセンサコントローラの制御回路の少なくともデータ伝送に関与する部分に共通のクロック信号が与えられるセンシングシステムを構築することができる。

【0204】

(2) 1つのユニットとして構成されたセンサコントローラであって、センシング処理を行う制御回路と、センサヘッドと接続するためのコネクタとを備え、前記制御回路は、センサヘッドから型式データのようなセンサヘッドを特定する情報又は回路データ、設定パラメータのようなセンサコントローラの機能又は性能を規定する情報を取得し、取得した情報に応じてセンシングデータの処理にかかわる前記制御回路の機能又は性能を変化させるものである、センサコントローラ。

【0205】

このような構成によれば、従来のセンサコントローラが有していた、センサコントローラの機能や性能を変化させ又は設定するためには操作スイッチによる設定操作を行うか外部のコンピュータ等に接続して設定操作を行うかしなければならなかったという課題を解決することができ、より簡単にセンサコントローラの機能又は性能を設定することができる。なお、センサヘッドの出力に現れる個体差を補正するための情報をセンサヘッドから取得して単にセンサヘッド出力の補正を行うことは、ここでいうセンサコントローラの機能又は性能を変化させることに該当しない。この発明(2)では、ユニット間コネクタは必須の要素ではない。

【0206】

(3) それぞれ1つのユニットとして構成された複数のセンサコントローラが直列に接続されたセンシングシステムであって、各センサコントローラは、センシング処理を行う制御回路と、他のセンサコントローラとの接続に用いることのできるユニット間コネクタと、を備え、各センサコントローラの前記制御回路は、トリガ信号が与えられることによりセンシング処理を行い、センシング処理が完了したときに処理完了状態となり、センシング対象についての判定結果が特定の結果であるときに特定判定状態となるものであり、各センサコントローラは、処理完了状態であるかどうか及び特定判定状態であるかどうかに関連する信号を接続された他のセンサコントローラとの間で送信及び/又は受信することが可能であり、それにより、少なくとも1つの特定センサコントローラは、すべてのセンサコントローラが処理完了状態であること及びすべてのセンサコントローラが特定判定状態であることを検出可能にされており、前記特定センサコントローラは、前記検出がされたときに、統合判定信号を出力するものである、センシングシステム。

【0207】

このような構成によれば、従来のセンシングシステムでは、それに含まれるすべてのセンサコントローラが特定判定状態となったことを外部から知ることが容易でなかった課題を解決することができる。このような構成によれば、各センサコントローラにトリガ信号が与えられた後、各センサコントローラの判定結果が出そろった後に、すべてのセンサコントローラの判定結果が特定の結果であるときに、特定センサコントローラから統合判定信号が出力される。したがって、センシングシステムから統合的な判定結果を得ることができる。しかも、センサコントローラ間で判定結果が出るタイミングがずれる場合にも、判定結果が出そろうまでの過渡的な時期において統合判定信号が不安定になることを避けることができる。典型的には、判定結果は合格又は不合格のいずれかであり、特定判定状態は合格の状態である。この場合には、統合判定信号が出力されることは、すべてのセンサコントローラが合格の判定をしたことを意味する。トリガ信号は、各センサコントローラに共通に与えてもよく、個別に与えてもよい。各センサコントローラは、1つのセンシング処理が完了すると、次のセンシング処理のためのトリガ信号を受け付けることが可能である待機状態となるようにしてもよい。この場合は、この待機状態を処理完了状態として扱うことができる。

【0208】

このようなセンシングシステムを構成するセンサコントローラとしては、第1ユニット間コネクタ及び第2ユニット間コネクタを備え、さらに以下の特徴を有するものを用いることができる。

【0209】

センシングシステムにおけるセンサコントローラの位置にかかわらず共通する特徴として、センサコントローラの制御回路は、トリガ信号が与えられることによりセンシング処理を行い、センシング処理が完了したときに処理完了状態となり、センシング対象についての判定結果が特定の結果であるときに特定判定状態となるものである。

【0210】

さらに次の特徴を有するセンサコントローラは、センシングシステムの一端に配置され、統合判定信号を出力する特定センサコントローラとして用いることができる。すなわち、センサコントローラの制御回路は、第1ユニット間コネクタを介して他のセンサコントローラが処理完了状態であることを表す完了信号を入力すること、自ユニットが処理完了状態であること、第1ユニット間コネクタを介して他のセンサコントローラが特定判定状態であることを表す特定判定信号を入力すること、及び自ユニットが特定判定状態であること、を条件として統合判定信号を出力する処理を行うものである、又はセンサコントローラは制御回路がそのような処理を行うように設定するための手段を備えるものである。

【0211】

次の特徴を有するセンサコントローラは、センシングシステムの両端以外の位置に配置されるセンサコントローラとして用いることができる。すなわち、センサコントローラの制御回路は、第1ユニット間コネクタを介して第1完了信号を入力すること及び自ユニットが処理完了状態であることを条件として、第2ユニット間コネクタを介して第2完了信号を出力し、さらに、第1ユニット間コネクタを介して第1特定判定信号を入力すること及び自ユニットが特定判定状態であることを条件として、第2ユニット間コネクタを介して第2特定判定信号を出力する処理を行うものである、又はセンサコントローラは制御回路がそのような処理を行うように設定するための手段を備えるものである。

【0212】

次の特徴を有するセンサコントローラは、センシングシステムの特定センサコントローラと反対側の端に配置されるセンサコントローラとして用いることができる。すなわち、センサコントローラの制御回路は、処理完了状態であるときに、第2ユニット間コネクタを介して完了信号を出力し、さらに、特定判定状態であるときに、第2ユニット間コネクタを介して特定判定信号を出力する処理を行うものである、又はセンサコントローラは制御回路がそのような処理を行うように設定するための手段を備えるものである。

【0213】

(4) 1つのユニットとして構成されたセンサコントローラであって、センシング処理を行う制御回路と、他のセンサコントローラとの接続に用いることのできる第1ユニット間コネクタ及び第2ユニット間コネクタとを備え、前記制御回路は、トリガ信号が与えられることによりセンシング処理を行い、センシング対象についての判定結果が特定の結果であるときに特定判定状態となるものであり、さらに、第1ユニット間コネクタを介して第1特定判定信号を入力すること及び自ユニットが特定判定状態であることを条件として、第2ユニット間コネクタを介して第2特定判定信号を出力する処理を行うものである、又は制御部がそのような処理を行うようにセンサコントローラを設定するための手段を備える、センサコントローラ。

【0214】

このような構成のセンサコントローラを用いれば、従来のセンサコントローラでは、センサコントローラを3台以上直列に接続した場合に、すべてのセンサコントローラが特定判定状態となったことを外部から知ることが容易でなかった課題を解決し、直列に接続されたすべてのセンサコントローラが特定判定状態となったときに1つの統合判定信号を出力するセンシングシステムを容易に構築することができる。

【0215】

ところで、図4に示すセンサコントローラにおいては、図8を参照して説明したように、ユニット間のセンシングデータ伝送経路はFPGA130とユニット間コネクタ180a、180bとを直結する8本のパラレルデータ線であった。ユニット間のセンシングデータ伝送経路は、これに限らず、図37に示すような構成とすることもできる。図37に示す構成は、第1ユニット間経路P1aの途中に第1ユニット間I/F回路190aが設けられ、第2ユニット間経路P1bの途中に第2ユニット間I/F回路190bが設けられている点が図4に示す構成と異なる。ユニット間I/F回路190a、190bは、図6に示したセンサヘッドI/F回路と同様に、シリアル/パラレル変換回路及びパラレル/シリアル変換回路を有しており、FPGA130との間ではセンシングデータのパラレル伝送を行い、ユニット間コネクタ180a又は180bを介して接続される他のセンサコントローラとの間ではセンシングデータのシリアル伝送を行う。このようにすれば、センサコントローラ同士をユニット間コネクタによって直接接続するのではなく、ケーブルを介して接続し、かつ、高速にセンシングデータを伝送することが容易になる。もちろん、図4に示すようにユニット間I/F回路を設けることなくセンサコントローラ間のセンシングデータの伝送をパラレル伝送で行う場合にも、ケーブルを介してセンサコントローラ間を接続することは可能である。

【0216】

センサコントローラ回路のどの部分を一つの集積回路に形成するかについては、いろいろな場合がありうる。図38にFPGAとそれ以外の回路ブロックとを集積化した一例を示す。この例においては、センサコントローラ回路100の全体としては図37に示すものと同一のブロック構成であり、FPGA130、CPU141、センサヘッドI/F回路110、及びユニット間I/F回路190a、190bが1チップの集積回路125の中に収められている。図38に示す構成では、図37のCPUブロック140に含まれる回路の内、CPU141が集積回路125に収められ、その他の回路であるシリアル通信I/F回路142、CPU−ROM143及びCPU−RAM144が集積回路125の外部に備えられる。集積回路125の中のFPGA130以外の回路ブロックは、集積回路の作成プロセスにおいて固定的に形成されるものであり、プログラム可能な、すなわちリコンフィグラブルな回路ではない。もっとも、これらの回路ブロックの一部又は全部をFPGAにプログラムされた回路として、一時的に又は恒久的に出現させるようにすることもできる。プログラムされた回路としてCPUを有し、かつ、CPUとしては用いられていないプログラム可能な論理回路部分を有するセンサコントローラも、制御部にプログラム可能な論理回路とCPUとを有するセンサコントローラの一つの実施形態である。

【符号の説明】

【0217】

1,1a,1b,1c センサコントローラ

2 センサヘッド

3 外部接続コード

4 センサケーブル

4a センサヘッドコネクタ

5 DINレール

6 対象物体

7 中継コネクタ片

7a 第1ポート(右)

7b 第2ポート(右)

8 DINレールクランパ

10 ケース

10a 正面

10b 上面

10c 下面

11 表示部

11a セグメント表示器

11b 液晶式キャラクタ表示器

12 操作部蓋

13 USBコネクタ

14 RS−232Cコネクタ

15 ユニット間コネクタ蓋(右)

16 センサヘッドコネクタ

17 操作部

18a 第1ユニット間コネクタ(右)

18b 第2ユニット間コネクタ(左)

20 ケース

100 センサコントローラ回路

110 センサヘッドインタフェース回路

110A センサヘッドインタフェース回路の別の例

111 シリアル/パラレル変換回路

111A A/D変換回路

112 パラレル/シリアル変換回路

113 センサヘッドインタフェース発振器

112A〜116A バッファ回路

117A センサヘッドインタフェース発振器

120 制御部

125 集積回路

130 FPGA

131 タイミング変換回路

132 データ経路切替回路

133 演算処理回路

133a パイプライン処理回路

134 レジスタ

135 クロック切替回路

136 タイミング生成回路

137 バッファ

138 トリガ制御回路

140 CPUブロック

141 CPU

142 シリアル通信インタフェース回路

143 CPU−ROM

144 CPU−RAM

150 入出力インタフェース回路ブロック

151 操作部入力回路

152 表示部出力回路

153 D/A変換器

154 パラレルインタフェース回路

155 RS−232Cインタフェース回路

156 USBインタフェース回路

160 FPGA発振器

170 FPGA−RAM

180 フラッシュメモリ

190a 第1ユニット間I/F回路(右)

190b 第2ユニット間I/F回路(左)

200 センサヘッド回路

201 赤色レーザダイオード素子

202,203,205 レンズ組立体

204 ミラー

206 2次元CCD

210 シリアル/パラレル変換回路

220 半導体レーザダイオード(LD)

230 発光ダイオード(LED)

240 2次元撮像素子

250 撮像素子駆動回路

260 センサヘッド発振器

270 パラレル/シリアル変換回路

280 センサヘッド(ROM)

1301 ANDゲート回路(Enable信号用)

1302 プルアップ抵抗(Enable信号用)

1303 ANDゲート回路(OK信号用)

1304 プルアップ抵抗(OK信号用)

1305 ANDゲート回路

1311 書込制御回路

1312 デュアルポートラインメモリ

1313 読出制御回路

1321 制御線切替回路A

1322 制御線切替回路B

1323 制御線切替回路C

1324 データ線切替回路A

1325 データ線切替回路B

1326 データ線切替回路C

L1 スリット光の照射光

L2 スリット光の反射光

IM スリット光の照射光像

P1a 第1ユニット間経路

P1b 第2ユニット間経路

P2 センサヘッド経路

【技術分野】

【0001】

この発明は、画像データや波形データ等といった大容量データを取り扱うセンシングシステムの構築に好適なセンサコントローラに関する。

【背景技術】

【0002】

2次元撮像素子を用いた変位センサとしては、信号処理ユニットとセンサヘッドユニットとが分離独立したものが知られている(特許文献1参照)。センサヘッドには投光用のレーザダイオードと受光用のCCDとが含まれている。CCDから得られる信号に基づいて生成された映像信号は電気コードを介して信号処理ユニットへと送られる。信号処理ユニットはマイクロプロセッサを主体として構成されるCPUとプログラム可能な論理回路であるFPGA(Field Programmable Gate Array)とを含んでいる。CPUは主として計測処理や表示制御処理を担う。FPGAは主として画像処理を担う。

【0003】

PSD(位置検出素子)を用いた変位センサとしては、信号処理部と検出部とが分離独立したものが知られている(特許文献2参照)。検出部は投光用の光源と受光用のPSDとを含んでいる。PSDからはアナログ検出信号が出力される。このアナログ検出信号は、電気コードを介して、信号処理部へと送られる。信号処理部の中枢は、マイクロプロセッサを主体としたCPUにより構成されている。CPUは、検出部から送られてくるアナログ検出信号に基づいて距離を算出する。信号処理部同士は、隣接状態において、中継ユニットを介してコネクタ接続される。信号処理部は、自己が算出した距離データを、隣接する信号処理部へと、コネクタを介して伝送する。隣接する信号処理部は、送られてきた距離データと自己が算出した距離データとを用いて段差距離等を演算する。

【先行技術文献】

【特許文献】

【0004】

【特許文献1】特開2002−357408(特に図4)

【特許文献2】特開2002−286413

【発明の概要】

【発明が解決しようとする課題】

【0005】

特許文献1に記載の変位センサにあっては、信号処理ユニットにFPGAが含まれているため、高度な画像処理も行うことができる。しかし、隣接する信号処理ユニット間におけるデータ伝送の機能は存在しない。そのため、複数のセンサヘッド又は信号処理ユニットの相互連携動作を行うことはできない。

【0006】

特許文献2に記載の変位センサにあっては、隣接信号処理部間におけるデータ伝送機能は有するが、これはCPU間通信であるため、伝送容量が限られる。検出周期に合わせるなどのために速い周期でデータ伝送したい場合に、距離の算出データのような演算結果の値は送れるが、データ量の多い波形データや画像データを送ることはできない。

【0007】

この発明は、このような従来の問題点に着目してなされたものであり、その目的とするところは、他のセンサコントローラとの間で波形データや画像データのような大容量データを短い時間で(例えば速い周期で)相互に伝送し、伝送されたデータを用いて様々な連携動作を行うことができるようにしたセンサコントローラ(例えば、センサの信号処理ユニット)を提供することにある。

【課題を解決するための手段】

【0008】

本発明のセンサコントローラは、1つのユニットとして構成される。このセンサコントローラには、プログラム可能な論理回路とセンサコントローラの動作を制御するCPUとを有する制御部と、他のセンサコントローラとの接続に用いることのできるユニット間コネクタと、制御部とユニット間コネクタとの間の信号伝送経路であって、プログラム可能な論理回路とユニット間コネクタとの間に設けられたセンシングデータ伝送経路を含むユニット間経路と、を備えている。

【0009】

それにより、ユニット間コネクタに他のセンサコントローラが接続されたときに、プログラム可能な論理回路と当該他のセンサコントローラのプログラム可能な論理回路との間でセンシングデータの伝送を行うことができるようにされている。

【0010】

このような構成によれば、他のセンサコントローラとの間でセンシングデータの伝送を高速に行うことが容易となる。また、制御部にはプログラム可能な論理回路が含まれていることから、開発過程におけるハードウェア構成の変更が少なくて済み、センサコントローラのメーカにとって開発(試作、設計変更)が容易となる。また、メーカにとっては、機能(特に、ハードウェア処理に依存する機能)の異なるシリーズ製品の品揃えを容易にするプラットフォームが提供される。

【0011】

ここで、この明細書における『プログラム可能な論理回路』は、ハードウェア回路をプログラムすることのできる集積回路である。集積回路の中に回路をプログラムすることのできる部分と回路が固定的に形成されている部分とがある場合には、回路をプログラムすることのできる部分がプログラム可能な論理回路である。プログラム可能な論理回路は、複数の集積回路によって構成してもよい。ハードウェア回路をプログラムすることのできる集積回路は、PLD(Programmable Logic Device)、FPGA(Field Programmable Gate Array)、CPLD(Complex PLD)等の名称で市場に提供されており、いずれも本発明に用いることができる。これらの集積回路の一例は、積和回路、ルックアップテーブル、フリップフロップ、メモリ、配線ライン、配線間のスイッチ等の回路要素を組み合わせることにより、デバイス間の接続、データ通信、シグナルプロセッシング、データ表示、タイミングとコントロール操作、その他通常、システムに含まれる機能の殆ど全てを実行するようにプログラムすることができるものである。

【0012】

この明細書における『センシングデータ』は、一般にセンサヘッドが出力する映像信号、電圧値、電圧波形のような生データと、生データを演算処理して得られた特徴量、判定結果のような加工済みデータとのいずれをも指す。

【0013】

本発明のセンサコントローラのユニット間コネクタは、第1ユニット間コネクタ及び第2ユニット間コネクタからなるものとすることができる。また、ユニット間経路は、第1ユニット間コネクタに接続する第1ユニット間経路と第2ユニット間コネクタに接続する第2ユニット間経路とからなるものとすることができる。この場合に、第1ユニット間経路に含まれるセンシングデータ伝送経路と第2ユニット間経路に含まれるセンシングデータ伝送経路とは、プログラム可能な論理回路の外部において互いに分離しているようにすることができる。

【0014】

このような構成によれば、必要に応じて第1ユニット間コネクタ側のセンシングデータの伝送と第2ユニット間コネクタ側のセンシングデータの伝送とを独立に行うことができる。

【0015】

本発明のセンサコントローラは、センシングデータを対象とした処理内容が変化するように、プログラム可能な論理回路の回路データの少なくとも一部を変更する手段又はプログラム可能な論理回路に設定するパラメータを変更する手段を備えていてもよい。

【0016】

このような構成によれば、センシング目的に応じてセンサコントローラのハードウェア処理に依存するセンシングデータの処理内容(特にはデータ伝送経路及び/又は演算処理内容)を変更することができる。特に、複数のセンサコントローラを連係して動作させるセンシングシステムを構築する場合に、少ない機種数のセンサコントローラで検出目的に応じた多様なセンシングシステムを構築することが可能となる。ユーザにとって、センサコントローラの機能の詳細を購入前に確定する必要がなく、試行錯誤しながらセンシングシステムの機能を最適化していくことが可能となる。

【0017】

本発明のセンサコントローラは、第1クロック信号を出力する発振器と、ユニット間コネクタから入力される第2クロック信号を伝送するクロック経路と、第1クロック信号及び第2クロック信号のいずれかを選択してプログラム可能な論理回路に与えるクロック切替回路と、をさらに備えるものであってもよい。

【0018】

このような構成によれば、プログラム可能な論理回路は、自ユニットの発振器が出力するクロック信号を用いて動作することが可能であり、接続された他のセンサコントローラから得られるクロック信号を用いて動作することも可能である。自ユニットの発振器が出力するクロック信号を用いて動作する場合のセンサコントローラは、他のセンサコントローラと接続せずに単体で動作することがきる。他のセンサコントローラから得られるクロック信号を用いる場合は、当該他のセンサコントローラとの間でプログラム可能な論理回路のクロックが同期しているので、センシングデータを高速に伝送することがいっそう容易になる。クロック切替回路をプログラム可能な論理回路の中に設け、選択したクロック信号をプログラム可能な論理回路の中の必要な部分に与えるようにしてもよい。

【0019】

本発明のセンサコントローラは、第1ユニット間コネクタ及び第2ユニット間コネクタを備える場合において、第1クロック信号を出力する発振器と、第1ユニット間コネクタから入力される第2クロック信号を伝送する第1クロック経路と、第1クロック信号及び第2クロック信号のいずれかを選択してプログラム可能な論理回路に与えるクロック切替回路と、選択されたクロック信号を第2ユニット間コネクタに出力するための第2クロック経路と、をさらに備えるようにしてもよい。

【0020】

このようなセンサコントローラを用いれば、3台以上のセンサコントローラが直列に接続されたセンシングシステムであって、すべてのセンサコントローラのプログラム可能な論理回路に共通のクロック信号が与えられるセンシングシステムを構築することができる。

【0021】

本発明のセンサコントローラは、ユニット間経路中に、CPUと接続されるデータ伝送経路をさらに備え、それにより、ユニット間コネクタに他のセンサコントローラが接続されたときに、CPUと当該他のセンサコントローラのCPUとの間でデータ伝送を行うことができるようにしてもよい。

【0022】

このような構成によれば、プログラム可能な論理回路同士の間のデータ伝送経路とは別に、CPU同士の間のデータ伝送経路を設けることにより、データ伝送についての役割分担が可能となる。

【0023】

本発明のセンサコントローラは、センサヘッドとの接続に用いることのできるセンサヘッド接続部と、プログラム可能な論理回路とセンサヘッド接続部との間を繋いでセンシングデータを伝送するセンサヘッド経路と、をさらに備えていてもよい。

【0024】

このような構成によれば、自ユニットに接続されるセンサヘッドから直接にデータを取得して、様々なセンシング動作を行うことができる。ここで、センサヘッド接続部は、センサヘッドコネクタとして構成することができる。センサヘッドコネクタは、センサコントローラのケースに固定して設けることができるし、センサコントローラのケースから引き出されたケーブルの先に設けることもできる。センサヘッドコネクタを設けずにセンサコントローラとセンサヘッドとをケーブルで直接接続する場合には、センサヘッド接続部は、センサコントローラとセンサヘッドとを繋ぐケーブルである。センサコントローラとセンサヘッドとが無線通信によって接続される場合には、センサヘッド接続部は、センサコントローラに設けられる無線通信の送受信部である。

【0025】

このとき、プログラム可能な論理回路にプログラムされる回路としては、ユニット間経路又はセンサヘッド経路を経由して取得されたセンシングデータを対象として演算処理を行うための演算処理回路と、ユニット間経路及びセンサヘッド経路のいずれかを選択的に演算処理回路に接続するデータ経路切替回路と、を含んでいてもよい。

【0026】

ここで、『プログラム可能な論理回路にプログラムされる回路』は、センサコントローラを起動していないときにもプログラム可能な論理回路にプログラムされた状態が維持されている回路と、センサコントローラが起動した後にセンサコントローラが有する記憶手段からプログラム可能な論理回路に回路データがロードされることによりプログラムされる回路との、両方を含む概念である。

【0027】

本発明のセンサコントローラは、プログラム可能な論理回路にプログラムされる回路としては、ユニット間経路を経由して取得されたセンシングデータを対象として演算処理を行うための演算処理回路をさらに含み、それにより、ユニット間コネクタに他のセンサコントローラが接続されたときに、当該他のセンサコントローラから取得したセンシングデータを対象に演算処理を行うことができるようにしてもよい。

【0028】

本発明のセンサコントローラは、プログラム可能な論理回路には記憶手段が接続されており、プログラム可能な論理回路にプログラムされる回路は、ユニット間経路を経由して取得されたセンシングデータを前記記憶手段に格納するためのデータ経路を含み、それにより、ユニット間コネクタに他のセンサコントローラが接続されたときに、当該他のセンサコントローラから取得したセンシングデータを記憶することができるようにしてもよい。

【0029】

次に、本発明の第1のセンシングシステムは、それぞれ1つのユニットとして構成された複数のセンサコントローラが直列に接続されたものである。このセンシングシステムにおける各センサコントローラは、プログラム可能な論理回路とセンサコントローラの動作を制御するCPUとを有する制御部と、他のセンサコントローラとの接続に用いることのできるユニット間コネクタと、制御部とユニット間コネクタとの間の信号伝送経路であって、プログラム可能な論理回路とユニット間コネクタとの間に設けられたセンシングデータ伝送経路を含むユニット間経路と、を備え、それにより、ユニット間コネクタに他のセンサコントローラが接続されたときに、プログラム可能な論理回路と当該他のセンサコントローラのプログラム可能な論理回路との間でセンシングデータの伝送を行うことができるようにしたものである。このセンシングシステムにおける少なくとも1つのセンサコントローラは、センサヘッドとの接続に用いることのできるセンサヘッド接続部と、プログラム可能な論理回路とセンサヘッド接続部との間を繋いでセンシングデータを伝送するセンサヘッド経路と、をさらに備え、そのセンサコントローラの少なくとも1つにはセンサヘッドが接続される。このセンシングシステムは、センサヘッドが接続されたセンサコントローラの内の1台である第1のセンサコントローラから、他のセンサコントローラの内の1台である第2のセンサコントローラにセンシングデータが伝送されるものである。

【0030】

第1のセンシングシステムにおいて、各センサコントローラのユニット間コネクタは、第1ユニット間コネクタ及び第2ユニット間コネクタからなるものとすることができる。また、各センサコントローラのユニット間経路は、第1ユニット間コネクタに接続する第1ユニット間経路と第2ユニット間コネクタに接続する第2ユニット間経路とからなるものとすることができる。この場合に、第1ユニット間経路に含まれるセンシングデータ伝送経路と第2ユニット間経路に含まれるセンシングデータ伝送経路とは、プログラム可能な論理回路の外部において互いに分離しているようにすることができる。

【0031】

第1のセンシングシステムにおいて、第1のセンサコントローラから第2のセンサコントローラに伝送されるセンシングデータは、第1のセンサコントローラに接続されたセンサヘッドから出力されるセンシングデータであってもよい。

【0032】

さらに、第1のセンサコントローラは、センサヘッドとの接続に用いることのできるセンサヘッド接続部と、プログラム可能な論理回路とセンサヘッド接続部との間を繋いでセンシングデータを伝送するセンサヘッド経路とをさらに備え、プログラム可能な論理回路の中に、センシングデータを対象として演算処理を行うための演算処理回路と、センサヘッド経路を経由して取得されたセンシングデータを演算処理回路及びユニット間経路に分岐させて与えるデータ経路とを含むセンサコントローラであり、第2のセンサコントローラのプログラム可能な論理回路にプログラムされる回路は、ユニット間経路を経由して取得されたセンシングデータを対象として演算処理を行うための演算処理回路を含み、それにより、センシングシステムは同一のセンシングデータを対象に並列に演算処理することができるようにしてもよい。

【0033】

第1のセンシングシステムにおいて、第1のセンサコントローラは、センサヘッドとの接続に用いることのできるセンサヘッド接続部と、プログラム可能な論理回路とセンサヘッド接続部との間を繋いでセンシングデータを伝送するセンサヘッド経路とをさらに備え、プログラム可能な論理回路の中に、センシングデータを対象とした演算処理を行うための演算処理回路を含むセンサコントローラであり、第1のセンサコントローラから第2のセンサコントローラに伝送されるセンシングデータは、第1のセンサコントローラに接続されたセンサヘッドから出力されたセンシングデータを、第1のセンサコントローラが演算処理した結果であるセンシングデータであってもよい。

【0034】

第1のセンシングシステムにおいて、第2のセンサコントローラのプログラム可能な論理回路にプログラムされる回路は、ユニット間経路を経由して取得されたセンシングデータを対象として演算処理を行うための演算処理回路を含むものであってもよい。

【0035】

第1のセンシングシステムにおいて、第2のセンサコントローラのプログラム可能な論理回路には記憶手段が接続されており、第2のセンサコントローラのプログラム可能な論理回路にプログラムされる回路はユニット間経路を経由して取得されたセンシングデータを前記記憶手段に格納するためのデータ経路を含むものであってもよい。

【0036】

第1のセンシングシステムにおいて、少なくとも1つのセンサコントローラは、クロック信号を出力する発振器と、ユニット間経路中のクロック信号の伝送経路とを備え、クロック信号をプログラム可能な論理回路とユニット間経路中のクロック信号の伝送経路とに対して同時に出力可能とされ、他のすべてのセンサコントローラは、ユニット間経路中にプログラム可能な論理回路に接続し得るクロック信号の伝送経路を備え、それにより、センシングシステム中のすべてのセンサコントローラが共通のクロック信号によりプログラム可能な論理回路を駆動することができるようにしてもよい。

【0037】

このような構成によれば、センシングデータを送信するセンサコントローラとそのデータを受信するセンサコントローラとの間でプログラム可能な論理回路のクロックが同期しているので、センシングデータを高速に伝送することがいっそう容易になる。

【0038】

第1のセンシングシステムにおいて、各センサコントローラは第1ユニット間コネクタ及び第2ユニット間コネクタを備える場合において、すべてのセンサコントローラは、第1クロック信号を出力する発振器と、第1ユニット間コネクタから入力される第2クロック信号を伝送する第1クロック経路と、第1クロック信号及び第2クロック信号のいずれかを選択してプログラム可能な論理回路に与えるクロック切替回路と、選択されたクロック信号を第2ユニット間コネクタに出力するための第2クロック経路と、をさらに備え、センサコントローラの列の端に位置して第2ユニット間コネクタにのみ他のセンサコントローラが接続されているセンサコントローラにおいては、クロック切替回路が第1クロック信号を選択し、他のすべてのセンサコントローラにおいては、クロック切替回路が第2クロック信号を選択することにより、センシングシステム中のすべてのセンサコントローラが共通のクロック信号によりプログラム可能な論理回路を駆動することができるようにしてもよい。

【0039】

このような構成によれば、クロック信号をセンサコントローラを通して共通に用いるセンシングシステムに、自ユニットの発振器を用いて単体でも動作できるセンサコントローラを組み込むことができ、センシングシステム専用の(自ユニットの発振器を持たない)センサコントローラを用意する必要がない。

【0040】

第1のセンシングシステムにおいて、すべてのセンサコントローラは、ユニット間経路中に、CPUと接続されるデータ伝送経路を備え、それにより、直接接続されたセンサコントローラのCPU同士の間でデータ伝送を行うことができるようにしてもよい。

【0041】

本発明の第2のセンシングシステムは、それぞれ1つのユニットとして構成された複数のセンサコントローラが直列に接続されたものであって、このセンシングシステムにおいて、各センサコントローラは、プログラム可能な論理回路とセンサコントローラの動作を制御するCPUとを有する制御部と、他のセンサコントローラとの接続に用いることのできるユニット間コネクタと、制御部とユニット間コネクタとの間の信号伝送経路であって、プログラム可能な論理回路とユニット間コネクタとの間に設けられたセンシングデータ伝送経路を含むユニット間経路と、を備え、それにより、ユニット間コネクタに他のセンサコントローラが接続されたときに、プログラム可能な論理回路と当該他のセンサコントローラのプログラム可能な論理回路との間でセンシングデータの伝送を行うことができるようにしたものであり、少なくとも1つのセンサコントローラは、センサヘッドとの接続に用いることのできるセンサヘッド接続部と、プログラム可能な論理回路とセンサヘッド接続部との間を繋いでセンシングデータを伝送するセンサヘッド経路と、をさらに備え、そのセンサコントローラの少なくとも1つにはセンサヘッドが接続されており、各センサコントローラの前記制御部は、トリガ信号が与えられることによりいずれかのセンサヘッドから出力されたセンシングデータを対象としたセンシング処理を行い、センシング処理が完了したときに処理完了状態となり、センシング対象についての判定結果が特定の結果であるときに特定判定状態となるものであり、各センサコントローラは、処理完了状態であるかどうか及び特定判定状態であるかどうかに関連する信号を接続された他のセンサコントローラとの間で送信及び/又は受信することが可能であり、それにより、少なくとも1つの特定センサコントローラは、すべてのセンサコントローラが処理完了状態であること及びすべてのセンサコントローラが特定判定状態であることを検出可能にされており、前記特定センサコントローラは、前記検出がされたときに、統合判定信号を出力するものである。

【0042】

このような構成によれば、各センサコントローラにトリガ信号が与えられた後、各センサコントローラの判定結果が出そろった後に、すべてのセンサコントローラの判定結果が特定の結果であるときに、特定センサコントローラから統合判定信号が出力される。したがって、センシングシステムから統合的な判定結果を得ることができる。しかも、センサコントローラ間で判定結果が出るタイミングがずれる場合にも、判定結果が出そろうまでの過渡的な時期において統合的な判定結果が不安定になることを避けることができる。典型的には、判定結果は合格又は不合格のいずれかであり、特定判定状態は合格の状態である。この場合には、統合判定信号が出力されることは、すべてのセンサコントローラが合格の判定をしたことを意味する。トリガ信号は、各センサコントローラに共通に与えてもよく、個別に与えてもよい。各センサコントローラは、1つのセンシング処理が完了すると、次のセンシング処理のためのトリガ信号を受け付けることが可能である待機状態となるようにしてもよい。この場合は、この待機状態を処理完了状態として扱うことができる。

【0043】

第2のセンシングシステムにおいて、トリガ信号は、センシングシステムの外部からセンサコントローラの1つに入力され、そのセンサコントローラからユニット間コネクタを経由して他の各センサコントローラに入力されるようにしもよい。

【0044】

このような構成によれば、センシングシステムに接続するトリガ信号線が1つだけでよい。トリガ信号を入力するセンサコントローラを、統合判定信号を出力するセンサコントローラと一致させれば、配線作業がさらに容易となる。

【0045】

第2のセンシングシステムにおいて、センサコントローラの列の第1の端に位置するセンサコントローラと、第2の端に位置し統合判定信号を出力する特定センサコントローラとを含み、第1の端に位置するセンサコントローラは、第2の端側に接続されているセンサコントローラに対し、処理完了状態であるときに完了信号を出力し、特定判定状態であるときに特定判定信号を出力するものであり、センサコントローラの列の第2の端に位置する特定センサコントローラは、第1の端側に接続されているセンサコントローラから完了信号を入力すること、自ユニットが処理完了状態であること、第1の端側に接続されているセンサコントローラから特定判定信号を入力すること、及び自ユニットが特定判定状態であること、を条件として統合判定信号を出力するものであってもよい。

【0046】

このセンシングシステムは、さらにセンサコントローラの列の第1の端及び第2の端以外に位置するセンサコントローラを含み、第1の端及び第2の端以外に位置するセンサコントローラは、第1の端側に接続されているセンサコントローラから完了信号を入力し、かつ、自ユニットが処理完了状態であるときに、第2の端側に接続されているセンサコントローラに完了信号を出力するとともに、第1の端側に接続されているセンサコントローラから特定判定信号を入力し、かつ、自ユニットが特定判定状態であるときに、第2の端側に接続されているセンサコントローラに特定判定信号を出力するものであってもよい。

【0047】

このような構成によれば、特定センサコントローラは、自ユニットに接続されているセンサコントローラから完了信号を入力することにより他のすべてのセンサコントローラが処理完了状態であることを知ることができ、さらに自ユニットも処理完了状態であればすべてのセンサコントローラが処理完了状態であると決定できる。また、特定センサコントローラは、自ユニットに接続されているセンサコントローラから特定判定信号を入力することにより他のすべてのセンサコントローラが特定判定状態であることを知ることができ、さらに自ユニットも特定判定状態であればすべてのセンサコントローラが特定判定状態であると決定できる。特定センサコントローラは、すべてのセンサコントローラが処理完了状態であり、かつ、すべてのセンサコントローラが特定判定状態であるときに、統合判定信号を出力する。

【0048】

第2のセンシングシステムにおいて、センサコントローラの列の第1の端に位置するセンサコントローラと、第2の端に位置し統合判定信号を出力する特定センサコントローラと、第1の端及び第2の端以外に位置するセンサコントローラとを含み、第1の端に位置するセンサコントローラは、第2の端側に接続されているセンサコントローラに対し、特定判定状態であるときに特定判定信号を出力し、処理完了状態であるときに完了信号を出力するものであり、センサコントローラ列の第1の端及び第2の端以外に位置するセンサコントローラは、第1の端側に接続されているセンサコントローラから完了信号を入力し、かつ、自ユニットが処理完了状態であるときに、第2の端側に接続されているセンサコントローラに完了信号を出力するとともに、第1の端側に接続されているセンサコントローラから入力した1又は複数の特定判定信号を第2の端側に接続されているセンサコントローラに中継して出力し、それと並列に、自ユニットが特定判定状態であるときに第2の端側に接続されているセンサコントローラに特定判定信号を出力するものであり、センサコントローラの列の第2の端に位置する特定センサコントローラは、第1の端側に接続されているセンサコントローラから完了信号を入力すること、自ユニットが処理完了状態であること、第1の端側に接続されているセンサコントローラから自ユニット以外のすべてのセンサコントローラについての特定判定信号を入力すること、及び自ユニットが特定判定状態であること、を条件として統合判定信号を出力するものであってもよい。

【0049】

このような構成によれば、特定センサコントローラは、自ユニットに接続されているセンサコントローラから完了信号を入力することにより他のすべてのセンサコントローラが処理完了状態であることを知ることができ、さらに自ユニットも処理完了状態であればすべてのセンサコントローラが処理完了状態であると決定できる。また、特定センサコントローラは、自ユニットに接続されているセンサコントローラから自ユニット以外の各センサコントローラの特定判定信号を入力することにより自ユニット以外のすべてのセンサコントローラの判定結果を知ることができ、さらに自ユニットの判定結果とあわせて、すべてのセンサコントローラが特定判定状態であるかどうかを決定できる。特定センサコントローラは、すべてのセンサコントローラが処理完了状態であり、かつ、すべてのセンサコントローラが特定判定状態であるときに、統合判定信号を出力する。

【0050】

第2のセンシングシステムを構成するセンサコントローラとしては、第1ユニット間コネクタ及び第2ユニット間コネクタを備える本発明のセンサコントローラであって、さらに以下の特徴を有するものを用いることができる。

【0051】

センシングシステムにおけるセンサコントローラの位置にかかわらず共通する特徴として、センサコントローラの制御部は、トリガ信号が与えられることによりセンシング処理を行い、センシング処理が完了したときに処理完了状態となり、センシング対象についての判定結果が特定の結果であるときに特定判定状態となるものである。

【0052】

さらに次の特徴を有するセンサコントローラは、センシングシステムの一端に配置され、統合判定信号を出力する特定センサコントローラとして用いることができる。すなわち、センサコントローラの制御部は、第1ユニット間コネクタを介して他のセンサコントローラが処理完了状態であることを表す完了信号を入力すること、自ユニットが処理完了状態であること、第1ユニット間コネクタを介して他のセンサコントローラが特定判定状態であることを表す特定判定信号を入力すること、及び自ユニットが特定判定状態であること、を条件として統合判定信号を出力する処理を行うものである、又はセンサコントローラは制御部にそのような処理を行わせるように設定するための手段を備えるものである。

【0053】

次の特徴を有するセンサコントローラは、センシングシステムの両端以外の位置に配置されるセンサコントローラとして用いることができる。すなわち、センサコントローラの制御部は、第1ユニット間コネクタを介して第1完了信号を入力すること及び自ユニットが処理完了状態であることを条件として、第2ユニット間コネクタを介して第2完了信号を出力し、さらに、第1ユニット間コネクタを介して第1特定判定信号を入力すること及び自ユニットが特定判定状態であることを条件として、第2ユニット間コネクタを介して第2特定判定信号を出力する処理を行うものである、又はセンサコントローラは制御部にそのような処理を行わせるように設定するための手段を備えるものである。

【0054】

次の特徴を有するセンサコントローラは、センシングシステムの特定センサコントローラと反対側の端に配置されるセンサコントローラとして用いることができる。すなわち、センサコントローラの制御部は、処理完了状態であるときに、第2ユニット間コネクタを介して完了信号を出力し、さらに、特定判定状態であるときに、第2ユニット間コネクタを介して特定判定信号を出力する処理を行うものである、又はセンサコントローラは制御部にそのような処理を行わせるように設定するための手段を備えるものである。

【0055】

いずれの位置に配置されるセンサコントローラも、外部からユニット間コネクタを介さずに外部トリガ信号を入力可能とされ、かつ、ユニット間コネクタを介してユニット間トリガ信号を入力可能とされたものであってもよく、外部トリガ信号及びユニット間トリガ信号のいずれかを選択し、選択したトリガ信号に基づき、前記制御部に内部トリガ信号を出力するトリガ制御回路をさらに備えたものとすることができる。

【0056】

さらに、センサコントローラの内部に、一方のユニット間コネクタに入力されたユニット間トリガ信号を他方のユニット間コネクタに伝送する信号経路を設けてもよい。

【0057】

トリガ制御回路は、さらに、外部トリガ信号を選択したときには、外部トリガ信号に基づきユニット間トリガ信号を出力するものであってもよい。

【0058】

第2のセンシングシステムを構成するセンサコントローラとしては、第1ユニット間コネクタ及び第2ユニット間コネクタを備える本発明のセンサコントローラであって、さらに次の特徴を有するものを用いることができる。すなわち、センサコントローラの制御部は、トリガ信号が与えられることによりセンシング処理を行い、センシング対象についての判定結果が特定の結果であるときに特定判定状態となるものであり、さらに、第1ユニット間コネクタを介して第1特定判定信号を入力すること及び自ユニットが特定判定状態であることを条件として、第2ユニット間コネクタを介して第2特定判定信号を出力する処理を行うものである、又はセンサコントローラは制御部にそのような処理を行わせるように設定するための手段を備えるものである。

【0059】

以上述べた中で、『そのような処理を行わせるように設定する』ことには、プログラム可能な論理回路の中の回路をそのような処理を行うように設定すること、そのような処理を行うプログラムを選択すること、及びそのような処理を行うようにプログラムに与えられるパラメータを設定することが含まれる。『設定するための手段』には、設定の指示を与えるためのセンサコントローラに設けられた操作スイッチ、設定のためにセンサコントローラが提示するメニュー、センサコントローラの外部から設定の指示を与えるための信号を受け付けることが含まれる。

【発明の効果】

【0060】

本発明によれば、波形データや画像データのような大容量データを短い時間で(例えば速い周期で)他のセンサコントローラとの間で伝送し、伝送されたデータを用いて様々な連携動作を行うことができるようにしたセンサコントローラ(例えば、センサの信号処理ユニット)を提供することができる。

【図面の簡単な説明】

【0061】

【図1】センサコントローラの外観斜視図である。

【図2】センサコントローラ連装状態の外観斜視図である。

【図3】センシング中のセンサヘッドの外観斜視図である。

【図4】センサコントローラ回路の内部構成を示すブロック図である。

【図5】センサヘッド回路の詳細を示すブロック図である。

【図6】センサヘッドインタフェース回路の詳細を示すブロック図である。

【図7】他のセンサヘッドインタフェース回路の詳細を示すブロック図である。

【図8】FPGA及びCPUとユニット間コネクタとの接続関係を示す信号系統図である。

【図9】FPGA内部回路の詳細を示すブロック図である。

【図10】タイミング変換回路の詳細を示すブロック図である。

【図11】データ経路切替回路の詳細を示すブロック図である。

【図12】CPUブロックの詳細を示すブロック図である。

【図13】入出力インタフェース回路ブロックの詳細を示すブロック図である。

【図14】CPUのゼネラルフローチャート(単体動作時)である。

【図15】センサコントローラ回路(演算ユニット)の内部構成を示すブロック図である。

【図16】センシングシステムAの構成図である。

【図17】撮像素子の水平走査線上に得られる光強度分布を示すグラフである。

【図18】センシングシステムAの動作フローチャート(その1)である。

【図19】センシングシステムAの動作フローチャート(その2)である。

【図20】センシングシステムAの動作フローチャート(その3)である。

【図21】CPUによるセンシング処理のフローチャートである。

【図22】データの流れ(その1)である。

【図23】データの流れ(その2)である。

【図24】データの流れ(その3)である。

【図25】データの流れ(その4)である。

【図26】データの流れ(その5)である。

【図27】データの流れ(その6)である。

【図28】センサコントローラ(拡張メモリユニット)の内部構成を示すブロック図である。

【図29】センシングシステムBの構成図である。

【図30】撮像素子の水平走査線上に得られる光強度分布を示すグラフである。

【図31】センシングシステムBの動作フローチャート(その1)である。

【図32】変位センサ機能と視覚センサ機能とを併有するセンサヘッドの構造図である。

【図33】センサコントローラ回路の内部構成を示すブロック図である。

【図34】FPGA内部回路の詳細を示すブロック図である。

【図35】センシングシステムCのトリガ信号とOK信号についての構成図である。

【図36】センサコントローラ回路のOK信号に関する他の実施形態を示すブロック図である。

【図37】ユニット間I/F回路を有するセンサコントローラ回路の内部構成を示すブロック図である。

【図38】FPGAとその他の回路ブロックとを集積化した集積回路を有するセンサコントローラ回路の内部構成を示すブロック図である。

【発明を実施するための形態】

【0062】

以下に、この発明の好適な実施の一形態を添付図面に基づいて詳細に説明する。尚、本発明の及ぶ範囲は、以下の実施形態の記載に限定されないことは言うまでもなく、本発明の及ぶ範囲は特許請求の範囲の記載によって特定されることは言うまでもない。

【0063】

センサコントローラの外観斜視図が図1に示されている。同図に示されるように、センサコントローラ1はケース10を有する1つのユニットとして構成される。ケース10の正面10aは上下に略2分割されており、上部領域には表示部11が設けられている。この例にあっては、表示部11は、セグメント表示器11aと液晶式キャラクタ表示器11bとから構成されている。

【0064】

ケース10の正面10aの下部領域は、操作部配置領域とされている。この操作部配置領域には、下端縁を支点として手前に開く操作部蓋12が設けられている。操作部蓋12を開けると、その内部には、数値キー、ファンクションキー、スライドスイッチ等といった各種の操作子が配置されている。

【0065】

ケース10の左右の側面(図では右側面10dのみを示す)には、ユニット間コネクタが設けられている。これら左右のユニット間コネクタのそれぞれにはユニット間コネクタ蓋(図では、右側の蓋15のみを示す)が設けられている。図では、ユニット間コネクタ蓋(右)15は、閉じられた状態にあり、これがスライド式に開かれると、内部には第1のポートと第2のポートとが存在する。後述するように、これら第1及び第2のポートは、中継コネクタ片7の第1ポート7aと第2ポート7bとに対応する。

【0066】

ケース10の下面10cには、USBコネクタ13とRS−232Cコネクタ14とが設けられている。これらのコネクタ13,14はセンサコントローラ1とパソコン(PC)等との通信を行うために使用される。ケース10の下面10cからは外部接続コード3が引き出されている。この外部接続コード3内には電源線、外部入力線、外部出力線などが含まれている。これらの外部入出力線は例えばプログラマブル・コントローラ(PLC)等に接続される。後述するように、ケース10はDINレール5に装着可能とされ、DINレールクランパ8はその際に使用される。

【0067】

センサコントローラ連装状態の外観斜視図が図2に示されている。同図に示されるように、この例にあっては、3台のセンサコントローラ1a,1b,1cが、横一列に整列された状態で、DINレール5を介して、制御盤内の取付板等に装着されている。この装着状態における各ケースの上面10bには、センサヘッドコネクタ16がそれぞれ設けられている。このセンサヘッドコネクタ16には、後述するように、センサヘッド2から引き出されたケーブル4の先端に取り付けられたセンサヘッドコネクタ4aが装着される。

【0068】

センシング中のセンサヘッドの外観斜視図が図3に示されている。同図に示されるように、センサヘッド2のケース20からはセンサケーブル4が引き出され、その先端にはセンサヘッドコネクタ4aが取り付けられている。このセンサヘッドコネクタ4aが、センサコントローラ1のケース10のセンサヘッドコネクタ16に結合される。

【0069】

センサヘッド2のケース20内には、投光用の半導体レーザダイオード(LD)と受光用の2次元撮像素子(例えば、CCDイメージセンサ、CMOSイメージセンサ等)が設けられている。センサヘッド2は、半導体レーザダイオード(LD)から発せられたレーザ光をスリット光の状態にして対象物体6に照射する。図において、L1はスリット光の照射光である。対象物体6上の照射光像IMはセンサヘッド2内に設けられたレンズにより2次元撮像素子の受光面上に結像される。図中、L2はスリット光の反射光である。ここで、投光光軸と受光光軸とは所定の角度をなしている。スリット光の進行方向と垂直な面についてのスリット光の断面の長手方向は、投光光軸と受光光軸とがなす面に対して垂直となっている。センサヘッド2から対象物体6までの距離が変化すると、2次元撮像素子の受光面上のスリット光の像は、スリット光の長手方向と直交な方向に移動する。2次元撮像素子の水平走査方向は、スリット光の像の移動方向に合わせられている。2次元撮像素子の水平走査線上の光強度のピーク位置が対象物体までの距離を表している。スリット光を用いているので、スリット光の長手方向についての距離の分布を一挙に測定することができる。

【0070】

センサコントローラ回路の内部構成を示すブロック図が図4に示されている。同図に示されるように、センサコントローラ回路100は、センサヘッドコネクタ16と、第1ユニット間コネクタ(右)18aと、第2ユニット間コネクタ(左)18bと、外部I/Fコネクタ19とからなる4系統のコネクタを有している。センサヘッドコネクタ16には、先に図3を参照して説明したように、センサヘッド2から引き出されたセンサケーブル4の先端に取り付けられたセンサヘッドコネクタ4aが接続される。第1ユニット間コネクタ(右)18a及び第2ユニット間コネクタ(左)18bには、それぞれ右隣又は左隣にそれぞれ隣接する他のユニットが、図1に示される中継コネクタ片7を介して接続される。外部I/Fコネクタ19は、図1に示されるUSBコネクタ13、RS−232Cコネクタ14、及び外部接続コード3を総称するものであり、この外部I/Fコネクタ19を介してパソコン(PC)やプログラマブル・コントローラ(PLC)等への接続が行われる。

【0071】

センサコントローラ100の内部には、センサヘッドI/F回路110と、制御部120と、入出力I/F回路ブロック150と、FPGA発振器160と、FPGA−RAM170とが含まれている。

【0072】

制御部120と第1ユニット間コネクタ(右)18aとの間には、FPGA130と第1ユニット間コネクタ(右)18aとの間のセンシングデータ伝送経路を含む第1ユニット間経路P1aが設けられており、制御部120と第2ユニット間コネクタ(左)18bとの間には、FPGA130と第2ユニット間コネクタ(左)18bとの間のセンシングデータ伝送経路を含む、第2ユニット間経路P1bが設けられている。また、センサヘッドコネクタ16とFPGA130との間にはセンシングデータを伝送するセンサヘッド経路P2が設けられ、その途中にセンサヘッドI/F回路110が設けられている。

【0073】

制御部120は、プログラム可能な論理回路であるFPGA130とセンサコントローラの動作を制御するCPUブロック140とを有する。CPUブロック140には、マイクロプロセッサ(CPU)やその周辺回路が含まれている。FPGA130は、回路データをダウンロードすることによって回路構成をプログラム(コンフィグレーション)することが可能なLSI(大規模集積回路)である。

【0074】

FPGA130は、論理ブロック、スイッチマトリクス、クロスポイントスイッチの組み合わせによって、任意の論理回路を擬似的に実現する。論理ブロックは、メモリとマルチプレクサとを組み合わせたLUT(Look Up Table)によって、様々な論理を実現する。スイッチマトリクスとクロスポイントスイッチは、それぞれの論理ブロック間の接続を行うが、この接続自体もメモリによって制御される。また、FPGA130は、外部とデータのやり取りをするためにI/Oブロックを用いる。

【0075】

FPGAには、アンチフューズタイプ、EEPROMタイプ、フラッシュROMタイプ、SRAMタイプ等がある。アンチフューズタイプは、中の回路の接続点がフューズで出来ていて、不要な部分を焼き切って回路を構成し、他は半導体スイッチのオン/オフデータをメモリのデータによって決めるタイプである。

【0076】

本実施形態のFPGA130はSRAMタイプであり、電源を入れる度にFPGAチップへ回路データをダウンロードする必要がある。SRAMタイプに代えてEEPROMタイプやフラッシュROMタイプのFPGAを用いれば、回路データの消去や別の回路データのダウンロードをするまでは、電源を切ってもプログラムした回路構成を維持できる。

【0077】

FPGA−RAM170は、プログラム可能な論理回路に接続された『記憶手段』に相当する。本実施形態では、FPGA130の中の演算処理回路のワーキングメモリとしての高速性を重視してSRAMが用いられている。この記憶手段としては、高速性よりも大容量であることが重視される場合には、フラッシュメモリのような書き換え可能な半導体メモリやハードディスク装置等を用いることもできる。

【0078】

この例では、ユニット間コネクタ(18a,18b)及びユニット間経路(P1a,P1b)は左右両側に設けられているが、いずれか一方だけでも差し支えない。特に、センシングデータの伝送方向を固定した設計においては、機能的にデータ伝送の最上流や最下流に設置されることが予定される機種の場合には、接続が必要な側にだけユニット間コネクタ及びユニット間経路を設けることが考えられる。

【0079】

以下、センサヘッド回路200及びセンサコントローラ回路100の内部詳細説明を行うが、それらの説明は次の事項を前提としている。図示された信号又はデータの伝送経路は、1本の線で表されていても複数の線を意味する場合もある。『制御信号』の用語は、回路の動作を制御するために用いられる信号という広い意味であり、イネーブル信号、リード/ライト信号、アドレス信号、割込信号、切替信号、タイミング指示信号等を含む。

【0080】

センサヘッド回路の詳細を示すブロック図が図5に示されている。このセンサヘッド回路200は、図3に示されるセンサヘッド2内の電気回路である。同図に示されるように、センサヘッド回路200は、シリアル/パラレル変換回路210と、半導体レーザダイオード(LD)220と、発光ダイオード(LED)230と、2次元撮像素子240と、撮像素子駆動回路250と、センサヘッド発振器260と、パラレル/シリアル変換回路270と、センサヘッドROM280とを含んでいる。また、このセンサヘッド回路200は、センサケーブル4を介してセンサコントローラ1から供給される電源(+12V,0V)を受けて動作する。

【0081】